IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY

# A Circuit Modeling Technique for the ISO 7637-3 Capacitive Coupling Clamp Test

Niels Lambrecht, H. Pues, *Member, IEEE*, Daniël De Zutter, *Fellow, IEEE*, and Dries Vande Ginste, *Senior Member, IEEE*

Abstract—In this paper, we propose a transmission-line modeling technique for the ISO 7637-3 capacitive coupling clamp (CCC) test. Besides modeling the test bench, special attention is devoted to the CCC itself, for which an equivalent circuit is constructed based on the concept of surface transfer impedance and surface transfer admittance. The overall model is validated by means of measurements using a nonlinear circuit as device-under-test, as such demonstrating the appositeness to mimick the CCC test in simulations during the design phase.

*Index Terms*—Capacitive coupling clamp (CCC), electrical fast transient (EFT) pulse, IEC 61000-4-4, ISO 7637-3, nonlinear, tansient immunity.

## I. INTRODUCTION

**E** LECTRICAL fast transient (EFT) disturbances represent one of the most serious threats to the operation of electronic systems. The electromagnetic (EM) energy resulting from an EFT event easily couples to cables connected to electronic equipment. Consequently, voltage pulses appear at the electronic system's ports, adversely affecting signal integrity and causing operation upsets. These effects are expected to become worse due to the continuous miniaturization trend in integrated circuits (IC) manufacturing and the resulting reduction of power supply voltages that are making electronic systems even more vulnerable.

Recognizing the importance of EFTs for designers, whose aim is to achieve electromagnetic compatibility (EMC) of equipment, international standards—such as the International Electrotechnical Commission (IEC) 61000-4-4—have been developed to provide test methods for the characterization of electronic system immunity to fast transient disturbances [1]– [3]. Such immunity tests are usually performed when the first prototype is ready or even just before production and, in case of failures, equipment reworking and redesign results in additional costs and delays. The electromagnetic compatibility (EMC) test discussed in this paper is the ISO 7637-3 capacitive coupling

Manuscript received April 26, 2017; revised August 18, 2017 and October 18, 2017; accepted October 19, 2017. (*Corresponding author: Niels Lambrecht.*)

N. Lambrecht, D. D. Zutter, and V. Ginste are with the IDLab/Electromagnetics Group, Department of Information Technology, Ghent University/imec B-9052, Ghent, Belgium (e-mail: niels.lambrecht@ugent.be; daniel. dezutter@ugent.be; Dries.VandeGinste@UGent.be).

H. Pues is with the Melexis Technologies N.V., 3980 Tessenderlo, Belgium (e-mail: hpu@melexis.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TEMC.2017.2765690

clamp (CCC) method [4]. The CCC test is a broadband EMC test suitable for coupling fast transient pulses, which typically occur as a result of switching processes. A first method to model the ISO 7637-3 CCC is given in [5] and [6], where its properties are measured and characterized by making use of a vector network analyzer. Another technique to model the injection clamp is via a full-wave approach [7] to allow reproducing the response of the device in the time domain. As full-wave simulators typically consume a lot of CPU time, an alternative way is to construct circuit models that mimic the behavior of the injection clamp [8]–[10]. However, these models were solely based on calculating mutual inductances and capacitances and do not fully encompass all transmission-line (TL) effects.

In this paper, we propose an efficient technique, using the TL theory and the concept of surface transfer impedance and surface transfer admittance, to model the CCC as well as the CCC test bench. The proposed circuit equivalent of the CCC test setup is validated by means of measurements, leveraging a nonlinear circuit as device-under-test (DUT). As such, the appositeness to mimick the CCC test in simulations during the design phase of susceptible equipment is demonstrated.

The remainder of this paper is organized as follows. In Section II, a thorough description of the CCC test is given. The modeling technique for the CCC is explained in Section III. The model of the CCC test bench is explained in Section IV. Section V deals with the validation of the developed circuit model, via comparison with measurements using a nonlinear active DUT. Finally, some concluding remarks are formulated in Section VI.

## II. DESCRIPTION OF THE ISO 7637-3 CCC TEST

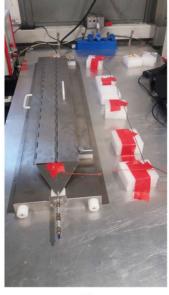

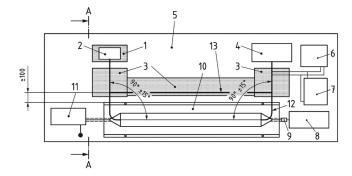

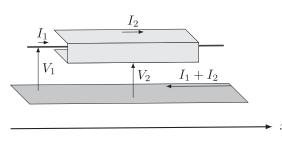

The ISO 7637-3 CCC test uses an injection clamp (see Fig. 1), which is a mechanical test fixture consisting of two metallic plates connected to each other, placed above a ground plane. As is depicted in Fig. 2, the wires under test are located inside the coupling clamp, i.e., between the two plates, while the other wires of the wire harness are placed at least 100 mm away from the coupling test fixture at a height of 50 mm above the ground plane. As in other module-level automotive EMC tests, the wire harness connects the DUT (at a height of 50 mm above the ground plane) with a load simulator (load box). The test is performed with a total harness length of 1700 mm.

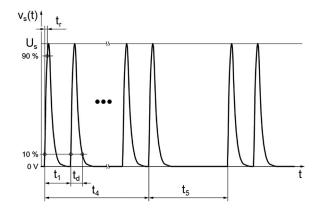

An EFT generator introduces a predefined disturbance via the coupling clamp. The EFT pulse is depicted in Fig. 3 and is

0018-9375 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

(a)

(b)

Fig. 1. ISO 7637-3 CCC test setup. (a) Top view. (b) Side view.

Fig. 2. Default ISO 7637-3 CCC test setup [4], where 1=insulation support, 2 = DUT, 3 = insulation support for test harness, 4 = load simulator, 5 = ground plane, 6 = power supply, 7 = battery, 8 = oscilloscope (50  $\Omega$ ), 9 = 50  $\Omega$ , 10 = CCC and 11 = transient pulses generator, 12 = lines to be tested, and 13 = lines not to be tested.

described by a traditional double-exponential pulse (1), where the parameters  $\alpha$ ,  $\beta$ , and U0 determine its shape, as

$$v_s(t) = U0 \left( e^{-\alpha t} - e^{-\beta t} \right). \tag{1}$$

In practice, the physical parameters such as rise time  $t_r$ , 10% pulse width  $t_d$  and maximum amplitude  $U_S$ , indicated in Fig. 3, can be easily related to  $\alpha$ ,  $\beta$ , and U0 [11]. In [4], different

Fig. 3. Fast transient pulse 3b [4].

Fig. 4. Inner and external TL model of the CCC.

test levels are defined to apply in the CCC test. In this paper, we will test with the pulse 3b shown in Fig. 3 at level II. This test level corresponds to the following parameter values:  $U_S = 60 \text{ V}$ ,  $t_r = 5 \text{ ns}$ ,  $t_d = 0.15 \mu \text{s}$ ,  $t_1 = 100 \mu \text{s}$ ,  $t_4 = 10 \text{ ms}$ , and  $t_5 = 90 \text{ ms}$ . These parameters correspond to  $\alpha = 5.06 \times 10^6$ ,  $\beta = 3.806 \times 10^8$ , and U0 = 64.45.

# III. TL MODEL OF THE ISO 7637-3 CCC

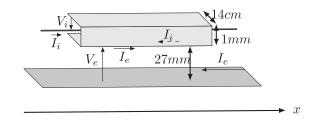

In our model, we consider the injection via the coupling clamp as a shielding problem, i.e., we look at the clamp as if it is shielding the wire harness inside it. Inspired by [12], we analyze the coupling of the field that is present between the outer surface of the clamp and the ground plane to the wire harness, by describing the problem with the help of two distinct TLs, i.e., an external TL and an internal TL (see Fig. 4). Here, the external TL consists of the ground plane and the outer surface of the clamp. This *external* line has a current  $I_e$  flowing on the exterior of the clamp and the ground plane acts as return path. This external line also has a voltage difference  $V_e$  between the exterior of the clamp and the ground plane. The internal line consists of the wire harness and the interior part of the clamp. This internal line has a current  $I_i$  flowing on the wire harness, and the internal surface of the shield acts as return path. There is also a voltage difference  $V_i$  between the wire harness and the internal surface of the shield. As discussed later, the coupling between these two TLs occurs via the surface transfer impedance  $Z_t$  and the surface transfer admittance  $Y_t$ . In this paper, for notational conciseness, we consider a wire harness of two wires, where one wire runs inside the injection clamp and the other one runs next to it. The theory described in this paper can however be generalized to N > 2 wires.

$v_{s}(t) \stackrel{I_{e}}{\xleftarrow{}} V_{e} \stackrel{I_{e}}{\swarrow} Z_{L}$

Fig. 5. MTL model of the CCC.

Although the cross section of the CCC fixture has approximately a triangular shape, in this paper, we approximate it by a rectangular cross section (see Fig. 4). As the height of the opening (1 mm) is much smaller than the width of the fixture (14 cm), this approximation will have little influence on the accuracy of the model, and it expedites the simulations.

# A. Calculation of the TLs' Parameters

We start our analysis by considering the CCC as a multiconductor TL (MTL) where all voltages are defined with respect to the ground plane (see Fig. 5). This MTL is governed by the following Telegrapher's equations:

$$\frac{d}{dx}\begin{bmatrix}V_1\\V_2\end{bmatrix} + \begin{bmatrix}Z_{11} & Z_{12}\\Z_{21} & Z_{22}\end{bmatrix}\begin{bmatrix}I_1\\I_2\end{bmatrix} = 0$$

(2)

$$\frac{d}{dx}\begin{bmatrix}I_1\\I_2\end{bmatrix} + \begin{bmatrix}Y_{11} & Y_{12}\\Y_{21} & Y_{22}\end{bmatrix}\begin{bmatrix}V_1\\V_2\end{bmatrix} = 0.$$

(3)

By making use of the technique proposed in [13], we easily obtain the per-unit-length (p.u.l.) parameters, being the impedance and admittance matrices' elements  $Z_{ij}$  and  $Y_{ij}$  (i, j=1,2). Note that, given reciprocity,  $Z_{12} = Z_{21}$  and  $Y_{12} = Y_{21}$ .

Next, we relate the MTL of Fig. 5 to the situation depicted in Fig. 4, consisting of two distinct TLs. The internal and external TL are described by the following equations [14]:

$$\frac{d}{dx} \begin{bmatrix} V_i \\ I_i \end{bmatrix} + \begin{bmatrix} 0 & Z_i \\ Y_i & 0 \end{bmatrix} \begin{bmatrix} V_i \\ I_i \end{bmatrix} = \begin{bmatrix} 0 & Z_t \\ -Y_t & 0 \end{bmatrix} \begin{bmatrix} V_e \\ I_e \end{bmatrix}$$

(4)

$$\frac{d}{dx} \begin{bmatrix} V_e \\ I_e \end{bmatrix} + \begin{bmatrix} 0 & Z_e \\ Y_e & 0 \end{bmatrix} \begin{bmatrix} V_e \\ I_e \end{bmatrix} = \begin{bmatrix} 0 & Z_t \\ -Y_t & 0 \end{bmatrix} \begin{bmatrix} V_i \\ I_i \end{bmatrix}$$

(5)

and the coupling between the two is provided by the surface transfer impedance  $Z_t$  and the surface transfer admittance  $Y_t$ . As Fig. 4 on the one hand and Fig. 5 on the other hand describe the same system, the following relations are readily obtained:

$$V_1 = V_i + V_e \tag{6a}$$

$$V_2 = V_e \tag{6b}$$

$$I_1 = I_i \tag{6c}$$

$$I_2 = I_e - I_i. \tag{6d}$$

Fig. 6. Schematic of the external TL.

Substitution of (6) into (2) and (3) and identification with (4) and (5) yields

$$Z_t = Z_{22} - Z_{12} \tag{7a}$$

$$Y_t = Y_{11} + Y_{12} \tag{7b}$$

$$Z_i = Z_{22} + Z_{11} - 2Z_{12} \tag{7c}$$

$$Y_i = Y_{11} \tag{7d}$$

$$Z_e = Z_{22} \tag{7e}$$

$$Y_e = Y_{11} + 2Y_{21} + Y_{22}.$$

(7f)

Hence, by looking at the injection clamp as an MTL (see Fig. 5) and calculating its p.u.l. parameters, we can easily deduce the sought-for surface transfer impedance  $Z_t$ , the surface transfer admittance  $Y_t$  and the p.u.l. impedances  $Z_i$  and  $Z_e$  and admittances  $Y_i$  and  $Y_e$  of the internal and external TL, respectively. Note that these p.u.l. impedances and admittances can be written as  $Z_i = R_i + j\omega L_i$ ,  $Y_i = G_i + j\omega C_i$  and  $Z_e = R_e + j\omega C_i$  $j\omega L_e, Y_e = G_e + j\omega C_e$ , with  $\omega$  the angular frequency,  $R_i$  and  $R_e$  the p.u.l. resistances,  $L_i$  and  $L_e$  the p.u.l. inductances,  $G_i$  and  $G_e$  the p.u.l. conductances and  $C_i$  and  $C_e$  the p.u.l. capacitances of the internal and external TL, respectively. For illustration, we give the p.u.l. parameters of the CCC fixture up to 100 MHz (see Table I). This frequency range is sufficient as the bandwidth of the signal is only about  $\frac{1}{\pi 5ns} = 63.6$  MHz. In our model, the small dielectric losses are neglected. It is also noticed that, up to the numerical precision of the simulations,  $C_{11} = -C_{12}$  and  $L_{12} = L_{22}$ , which is due to the fact that conductor 1 is nearly entirely enclosed by conductor 2. In what follows, we will use the "weak coupling assumption" [15], neglecting the coupling of the internal TL to the external TL. This amounts to putting  $Z_t$  and  $Y_t$  to zero in (5) while retaining the coupling terms in (4).

#### B. External TL

The external TL (as shown in Fig. 6) is given by the exterior of the clamp and the ground plane.

In time-harmonic regime and adopting the weak coupling assumption, we obtain the following equations:

$$\frac{dV_e(x)}{dx} = -Z_e I_e(x) \tag{8}$$

$$\frac{dI_e(x)}{dx} = -Y_e V_e(x). \tag{9}$$

$C_{11} \left[ \frac{pF}{m} \right]$  $C_{12} \left[ \frac{\mathrm{pF}}{\mathrm{m}} \right]$  $C_{22} \left[ \frac{\mathrm{pF}}{\mathrm{m}} \right]$  $R_{11} \left[ \frac{m\Omega}{m} \right]$  $R_{22} \left[ \frac{m\Omega}{m} \right]$ f [MHz]  $L_{11} \left[ \frac{\mathrm{nH}}{\mathrm{m}} \right]$  $L_{12} \left[ \frac{\mathrm{nH}}{\mathrm{m}} \right]$  $L_{22} \left[ \frac{nH}{m} \right]$  $R_{12} \left[ \frac{\mathrm{m}\Omega}{\mathrm{m}} \right]$ 35.6-35.699.3 505.2175.1175.1128.12.92.910 35.6-35.699.3492.6174.7174.7380.99.29.230 35.6-35.699.3490.2174.7174.7651.715.815.835.622.360 -35.699.3489.2174.7917.022.3174.7100 35.6-35.699.3488.6174.6174.61174.028.628.6

TABLE I P.U.L. PARAMETERS OF CCC FIXTURE

And hence

1

$$V_e(x) = Ae^{-k_e x} + Be^{k_e x} \tag{10}$$

$$I_e(x) = \frac{1}{Z_{C,e}} \left( A e^{-k_e x} - B e^{k_e x} \right)$$

(11)

with

$$Z_{C,e} = \sqrt{\frac{Z_e}{Y_e}} \tag{12}$$

$$k_e = \sqrt{Z_e Y_e}.\tag{13}$$

The square roots in (12) and (13) are defined such that  $\Im(k_e) > 0$ and  $\Re(k_e) > 0$ . The clamp, its far-end load  $Z_L$ , and the EFT source resistor  $Z_q$  are specified in the standards such that  $Z_{C,e} =$  $Z_g = Z_L = 50 \ \Omega$ . Hence, given this matching, B = 0 in (10) and (11) and  $A = \frac{v_s(s)}{2}$ , with  $s = j\omega$ , i.e., the frequency-domain equivalent of  $v_s(t)$  (1).

## C. Internal TL

To solve the internal TL, we use the *chain parameter matrix* (CPM) formulation [15]. This leads to the following equations:

$$\begin{bmatrix} V_i(L) \\ I_i(L) \end{bmatrix} = \mathbf{\Phi}(L) \begin{bmatrix} V_i(0) \\ I_i(0) \end{bmatrix} + \begin{bmatrix} V_{FT} \\ I_{FT} \end{bmatrix}$$

(14)

where  $\Phi(L)$  is the 2×2 chain parameter matrix (since we assume that only one wire runs into the injection clamp).

$$\Phi(L) = \begin{bmatrix} \frac{1}{2} \left( e^{k_i L} + e^{-k_i L} \right) & -Z_{C,i} \frac{1}{2} \left( e^{k_i L} - e^{-k_i L} \right) \\ \frac{-1}{Z_{C,i}} \frac{1}{2} \left( e^{k_i L} - e^{-k_i L} \right) & \frac{1}{2} \left( e^{k_i L} + e^{-k_i L} \right) \end{bmatrix}.$$

(15)

Here,  $k_i = \sqrt{Z_i Y_i}$  and  $Z_{C,i} = \sqrt{\frac{Z_i}{Y_i}}$ .  $V_{FT}$  and  $I_{FT}$  are the equivalent source terms at the end of the TL, given by

$$\begin{bmatrix} V_{FT} \\ I_{FT} \end{bmatrix} = \int_0^L \mathbf{\Phi}(L-\tau) \begin{bmatrix} V_d(\tau) \\ I_d(\tau) \end{bmatrix} d\tau$$

(16)

where  $V_d$  and  $I_d$  are distributed voltage and current sources along the line. In our case, these distributed sources appear because of the coupling of the external TL to the internal TL by means of the transfer surface impedance and transfer surface admittance, as follows:

$$V_d(\tau) = Z_t I_e(\tau) \tag{17}$$

$$I_d(\tau) = -Y_t V_e(\tau). \tag{18}$$

The source terms  $V_{FT}$  and  $I_{FT}$  are expressed as

$$V_{FT} = \int_{0}^{L} \Phi_{11}(L-\tau) \frac{Z_{t}}{Z_{C,e}} V_{e}(\tau) \,\mathrm{d}\tau$$

-  $\int_{0}^{L} \Phi_{12}(L-\tau) Y_{t} V_{e}(\tau) \,\mathrm{d}\tau$  (19)

$$I_{FT} = \int_{0}^{L} \Phi_{21}(L-\tau) \frac{Z_{t}}{Z_{C,e}} V_{e}(\tau) \,\mathrm{d}\tau$$

-  $\int_{0}^{L} \Phi_{22}(L-\tau) Y_{t} V_{e}(\tau) \,\mathrm{d}\tau.$  (20)

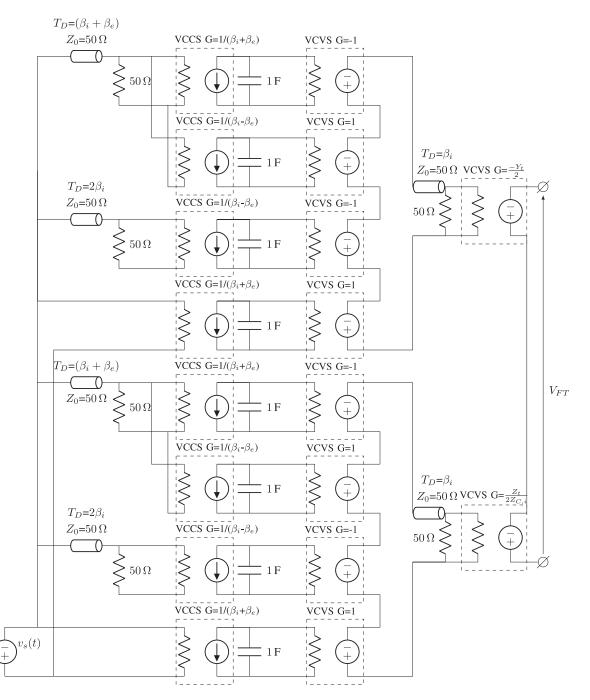

D. Circuit Model of the Equivalent Source Terms  $V_{FT}$  and  $I_{FT}$

In the ISO 7637-3 [4], a transient signal is injected and measured at the DUT end of the CCC. In (19) and (20), we obtained an expression for the source terms  $V_{FT}$  and  $I_{FT}$  in the frequency domain. Hence, using these expressions would make it necessary to take the Fourier transformation of the injected disturbance signal, apply (19) and (20) and take the inverse Fourier transform of the result. This not only causes overhead but would also result in the occurrence of the Gibbs phenomenon due to the fast pulses. Even more importantly, this would also imply that nonlinear DUTs cannot be assessed. These issues are solved by reformulating (19) and (20) in the Laplace domain and by constructing a circuit equivalent that allows rapid transient analysis in any commercial circuit solver. Transforming (19) and (20) to the Laplace domain ( $s = j\omega$ ), neglecting the very small losses, yields

$$V_{FT}(s) = \int_{0}^{L} \frac{1}{2} \left( e^{s\beta_{i}(L-\tau)} + e^{-s\beta_{i}(L-\tau)} \right) e^{-s\beta_{e}\tau} \frac{Z_{t}}{Z_{C,e}} \, \mathrm{d}\tau$$

$$- \int_{0}^{L} -Z_{C,i} \frac{1}{2} \left( e^{s\beta_{i}(L-\tau)} - e^{-s\beta_{i}(L-\tau)} \right)$$

$$Y_{t} e^{-s\beta_{e}\tau} \, \mathrm{d}\tau$$

(21)

$$I_{FT}(s) = \int_{0}^{L} \frac{1}{2} \left( e^{s\beta_{i}(L-\tau)} - e^{-s\beta_{i}(L-\tau)} \right) \frac{Z_{t}}{Z_{C,e}} e^{-s\beta_{e}\tau} d\tau - \int_{0}^{L} \frac{1}{2} \left( e^{s\beta_{i}(L-\tau)} + e^{-s\beta_{i}(L-\tau)} \right) Y_{t} e^{-s\beta_{e}\tau} d\tau.$$

(22)

Analytically performing the integration of (21) and (22), the following closed form is obtained for  $V_{FT}(s)$  and

Fig. 7. Circuit model of the equivalent voltage source  $V_{FT}$  (23).

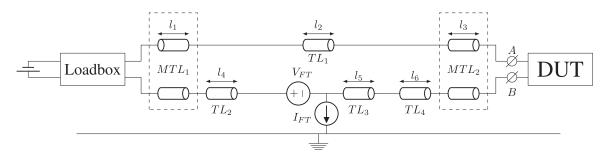

Fig. 8. TL modeling of the ISO 7637-3 CCC test bench (see Table II).

6

TABLE II

Dimensions of the TL Model of the ISO 7637-3 CCC Test Bench

| Dimension | Value | Dimension | Value |

|-----------|-------|-----------|-------|

| $l_1$     | 0.4 m | $l_3$     | 0.4 m |

| $l_2$     | 1.0 m | $l_4$     | 0.1 m |

| $l_5$     | 1.0 m | $l_6$     | 0.1 m |

$$I_{FT}(s)$$

:

$$V_{FT}(s)e^{-s\beta_{i}L} = \frac{-Z_{C,i}Y_{t}v_{s}(s)}{2} \left[ \frac{e^{-s(\beta_{i}+\beta_{e})L}-1}{s(\beta_{i}+\beta_{e})L} + \frac{e^{-s(\beta_{i}+\beta_{e})L}-e^{-2s\beta_{i}L}}{s(\beta_{i}-\beta_{e})} \right] \\ + \frac{Z_{t}v_{s}(s)}{2Z_{C,i}} \left[ \frac{e^{-s(\beta_{i}+\beta_{e})L}-1}{-s(\beta_{i}+\beta_{e})} + \frac{e^{-s(\beta_{i}+\beta_{e})L}-e^{-2s\beta_{i}L}}{s(\beta_{i}-\beta_{e})} \right]$$

(23)

$$I_{FT}(s)e^{-s\beta_{i}L} = \frac{-v_{s}(s)Y_{t}}{2} \left[ \frac{1-e^{-s(\beta_{i}+\beta_{e})L}}{s(\beta_{i}+\beta_{e})} - \frac{e^{-s(\beta_{i}+\beta_{e})L}-e^{-2s\beta_{i}L}}{s(\beta_{i}+\beta_{e})} \right]$$

$$+ \frac{e^{-s(\beta_{i}+\beta_{e})L} - e^{-2s\beta_{i}L}}{s(\beta_{i}-\beta_{e})} \bigg] \\ + \frac{Z_{t}v_{s}(s)}{2(Z_{C,i})^{2}} \bigg[ \frac{e^{-s(\beta_{i}+\beta_{e})L} - 1}{s(\beta_{i}+\beta_{e})} \\ + \frac{e^{-s(\beta_{i}+\beta_{e})L} - e^{-2s\beta_{i}L}}{s(\beta_{i}-\beta_{e})} \bigg]$$

(24)

with L = 1 m,  $\beta_i = \sqrt{L_i C_i}$ , and  $\beta_e = \sqrt{L_e C_e}$ . From (23) and (24), we construct an equivalent circuit using the following Laplace domain—time-domain correspondences,  $V(s)e^{-sT}$   $\Leftrightarrow$ v(t-T) and  $\frac{V(s)}{s} \Leftrightarrow \int_0^t v(t) dt$ . In (23) and (24), the right-hand side and left-hand side is multiplied by a retardation operator  $e^{-s\beta_i L}$ . This is needed to eliminate advancing time operators  $e^{+s\beta_i L}$  that appear in the right-hand sides of (23) and (24) during the integration. This retardation operator can be implemented by a simple TL model to take the delay into account. The equivalent circuit model of (23) is depicted in Fig. 7, a similar circuit for  $I_{FT}$  can be deduced from (24). From Fig. 7, it can be seen that the delay factors are modeled by a TL terminated by its characteristic impedance while the scaling factors are included in the voltage-controlled current sources. The integration factor 1/s is modeled by taking a current source loaded with a capacitor of 1 F. The integrated voltage is then measured across this capacitor. This is done for every term in (23). Summation is obtained by placing all the voltage-controlled voltage sources in series, where an extra delay line with  $T_D = \beta_i$  takes the retardation operator  $e^{-s\beta_i L}$  into account.

## IV. MODELING OF THE TESTBENCH

Using the circuit equivalents of (23) and (24), we can now construct an equivalent circuit model of the entire ISO 7637-3 CCC test setup (see Fig. 8). The CCC injection clamp

Fig. 9. Voltage across the 10-k $\Omega$  resistor DUT.

that encompasses the victim wire is represented by TL<sub>3</sub> with propagation factor  $k_i$  and characteristic impedance  $Z_{C,i}$  and voltage source  $V_{FT}$  and current source  $I_{FT}$ . TL<sub>1</sub> represents the wire that is placed (at least) 100 mm away from the coupling test fixture and at a height of 50 mm above the ground plane.  $TL_2$ and TL<sub>4</sub> represent the parts of the victim wire outside the clamp and not running alongside the wire represented by TL<sub>1</sub>. MTL<sub>1</sub> and MTL<sub>2</sub> represent the two parts of the wire harness where the wires run next to each other, connected to the load box and DUT, respectively. To model this wire harness as an MTL, we applied the same method as in [16]. The load box and the DUT are connected to the two ends of the wire harness. The load box is a passive impedance, readily characterized by means of S-parameter measurements or simulations, and it is described in the EMC test plan. At the other end of the wire harness, the DUT is connected. The two-terminal nonlinear and passive DUTs considered here, are described further in Section V.

#### V. VALIDATION OF THE PROPOSED MODEL

To validate and illustrate the appositeness of our proposed model, we use passive and nonlinear DUTs. We measure the voltages at the DUTs and compare this with the simulation result of our model.

## A. Passive DUT

As passive DUTs we use a 10-k $\Omega$  resistor and a 100-nF capacitor, representing DUTs with a high input impedance and a capacitance input stage, respectively. The purpose of these passive DUTs is to validate the proposed model of the test setup without having to deal with a potential inaccurate model of the DUT. The voltage across the resistor is depicted in Fig. 9. Fig. 10 shows the voltage across the capacitor. As can be seen, our model accurately predicts the peak amplitude of the signal waveform and its envelope. Also, there is a good correspondence concerning the ringing frequency between simulations and measurements. For example, for the 10 k $\Omega$  DUT (see Fig. 9), in measurement, we have a ringing frequency of 13.7 MHz, while in simulation 16.1 MHZ, is observed.

Fig. 10. Voltage across a 100-nF capacitor DUT.

Fig. 11. Schematic of the controlled series VR.

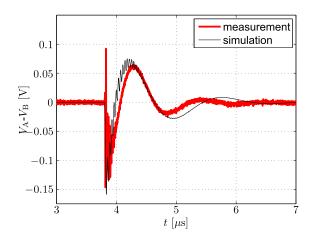

Fig. 12. Input voltage of the VR when we inject a fast transient pulse 3b level II.

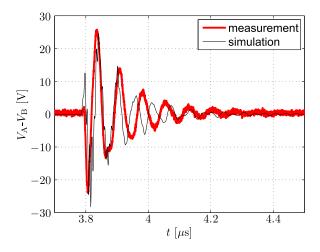

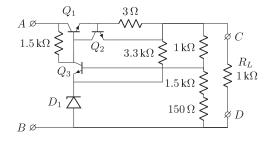

## B. Nonlinear DUT

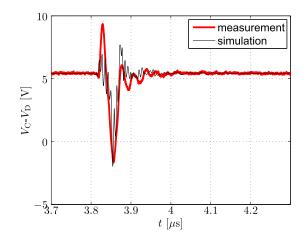

As an example of a nonlinear DUT, a low drop-out voltage regulator (VR) with schematic shown in Fig. 11 is selected. This DUT was also used in [17] to validate the RI-130 test model [18]. To validate our CCC test model, we measure the voltage at the input of the VR, i.e., between nodes A and B, during the test when we inject a fast transient pulse 3b level II. The result is shown in Fig. 12. We also observe the waveform between nodes C and D, shown in Fig. 13. Similar as for the passive DUTs and owing to imperfections of the test setup, the ringing frequency is not exactly the same when comparing simulations with measurements. Additionally, we cannot expect the circuit

Fig. 13. Output voltage of the VR when we inject a fast transient pulse 3b level II.

model data to correspond exactly with the measurements, as the model of the DUT itself also has limited accuracy. Nonetheless, as clearly demonstrated, the proposed model predicts all salient features of the output signal and input signal of the VR, and in particular, the magnitude of the disturbance peaks and the duration of the disturbance is accurately modeled. This is of critical importance and it allows the circuit designer to analyze the immunity of his/her circuit during the design phase. It is important to mention that the CPU time to run the simulation is only 4.83 s on a workstation equipped with a i7-4770 CPU at 3.40 GHz with 32 GB RAM, which demonstrates the efficiency of the circuit modeling approach.

## VI. CONCLUSION

In this paper, we have proposed a circuit modeling technique for the ISO 7637-3 CCC test. Special attention has been devoted to the modeling of the CCC where the concept of the surface transfer impedance and surface transfer admittance was leveraged. The overall model was validated by means of measurements using a nonlinear VR as DUT. Good accuracy and efficiency was demonstrated. Consequently, the equivalent model can be used to assess the immunity of novel circuits and devices in their design phase.

#### REFERENCES

- Testing and Measurement Techniques—Electrical Fast Transient/Burst Immunity Test, IEC Std. IEC 61000-4-4, 3rd ed., 2012.

- [2] F. Martzloff and T. Leedy, "Electrical fast transient tests: applications and limitations," in *Proc. Conf. Rec. IEEE Ind. Appl. Soc. Annu. Meeting*, 1989. [Online]. Available: http://dx.doi.org/10.1109/IAS.1989.96859

- B. Cormier and W. Boxleitner, "Electrical fast transient (EFT) testing-an overview," in *Proc. IEEE 1991 Int. Symp. Electromagn. Compat.*, 1991.

[Online]. Available: http://dx.doi.org/10.1109/ISEMC.1991.148240

- [4] Road Vehicles Electrical Disturbances From Conduction and Coupling Part 3: Electrical Transient Transmission by Capacitive and Inductive Coupling via Lines Other Than Supply Lines, ISO 7637-3, 3rd ed., 2016.

- [5] D. Smith, "An investigation into the performance of the IEC 1000-4-4 capacitive clamp," in *Proc. Elect. Overstress/Electrostatic Discharge Symp.*, 1996. [Online]. Available: http://dx.doi.org/10.1109/ EOSESD.1996.865145

- [6] S. Radman, I. Bacic, and K. Malaric, "Capacitive coupling clamp," in Proc. 2008 16th Int. Conf. Software, Telecommun. Comput. Netw., 2008. [Online]. Available: http://dx.doi.org/10.1109/SOFTCOM.2008.4669455

- [7] S. Caniggia, E. Dudenhoeffer, and F. Maradei, "Full-wave investigation of EFT injection clamp calibration setup," in *Proc. 2010 IEEE Int. Symp. Electromagn. Compat.*, Jul. 2010. [Online]. Available: http://dx.doi.org/10.1109/ISEMC.2010.5711345

- [8] F. Musolino and F. Fiori, "Modeling the IEC 61000-4-4 EFT injection clamp," *IEEE Trans. Electromagn. Compat.*, vol. 50, no. 4, pp. 869–875, Nov. 2008. [Online]. Available: http://dx.doi.org/10.1109/ TEMC.2008.2004603

- J. Hallon and M. Bittera, "Directivity of capacitive clamp for EFT pulses injection," in *Proc. 2014 24th Int. Conf. Radioelektronika*, Apr. 2014.

[Online]. Available: http://dx.doi.org/10.1109/Radioelek.2014.6828459

- [10] S. Bauer, B. Deutschmann, and G. Winkler, "Prediction of the robustness of integrated circuits against EFT/burst," in *Proc. 2015 IEEE Int. Symp. Electromagn. Compat.*, Aug. 2015. [Online]. Available: http://dx.doi.org/10.1109/ISEMC.2015.7256130

- [11] M. Magdowski and R. Vick, "Estimation of the mathematical parameters of double-exponential pulses using the Nelder-Mead algorithm," *IEEE Trans. Electromagn. Compat.*, vol. 52, no. 4, pp. 1060–1062, Nov. 2010. [Online]. Available: http://dx.doi.org/10.1109/TEMC.2010.2052621

- [12] A. Orlandi, "Circuit model for bulk current injection test on shielded coaxial cables," *IEEE Trans. Electromagn. Compat.*, vol. 45, no. 4, pp. 602–615, Nov. 2003. [Online]. Available: http://dx.doi.org/10.1109/ TEMC.2003.819060

- [13] T. Demeester and D. De Zutter, "Quasi-TM transmission line parameters of coupled lossy lines based on the Dirichlet to Neumann Boundary operator," *IEEE Trans. Microw. Theory Techn.*, vol. 56, no. 7, pp. 1649–1660, Jul. 2008.

- [14] L. Qi, X. Cui, and X. Gu, "A simple method for measuring complex transfer impedance and admittance of shielded cable in substations," in *Proc. 2006 17th Int. Zurich Symp. Electromagn. Compat.*, 2006. [Online]. Available: http://dx.doi.org/10.1109/EMCZUR.2006.215018

- [15] C. R. Paul, Analysis of Multiconductor Transmission Lines. New York, NY, USA: Wiley, 1994.

- [16] N. Lambrecht, C. Gazda, H. Pues, D. De Zutter, and D. Vande Ginste, "Efficient circuit modeling technique for the analysis and optimization of ISO 10605 field coupled electrostatic discharge (ESD) robustness of nonlinear devices," *IEEE Trans. Electromagn. Compat.*, vol. 58, no. 4, pp. 971–980, Aug. 2016. [Online]. Available: http://dx.doi.org/10.1109/TEMC.2016.2553173

- [17] N. Lambrecht, H. Pues, D. De Zutter, and D. Vande Ginste, "Modeling of contact bounce in a transient electromagnetic compatibility test for the analysis and optimization of nonlinear devices," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 2, pp. 541–544, Apr. 2017. [Online]. Available: http://dx.doi.org/10.1109/TEMC.2016.2618345

- [18] Electromagnetic Compatibility Specification For Electrical/Electronic Components and Subsystems, Ford Std. FMC1278, Jul. 2015. [Online]. Available: www.fordemc.com/docs/download/FMC1278.pdf.

**Hugo Pues** (S'76–M'82) was born in Leuven, Belgium, in 1954. He received the Electromechanical Engineering degree and the Doctoral degree in applied sciences from KU Leuven (Catholic University of Leuven), Leuven, Belgium, in 1977 and 1983, respectively.

His doctoral research focused on bandwidth enhancement techniques for microstrip antennas. In 1983, he joined ERA Technology, Leatherhead, U.K., where he was involved in antenna design projects and the development of electromagnetic method-of-

moments software. In 1984, he returned to KU Leuven, where he was involved in research work on microstrip integrated circuits, microwave power applications, and computational electromagnetics. In 1987, he joined Emerson & Cuming Microwave Products, Geel, Belgium (now a unit of Laird Technologies), where he managed the development and implementation of advanced computer-aided design and testing techniques for absorbing materials and anechoic chambers. In 1998, he joined Option, Leuven, where he assisted in the development of mobile data applications. In 2001, he joined M-TEC Wireless, Mechelen, Belgium (no longer existing), where he assisted in the development of wireless LAN applications. In 2003, he joined Melexis Technologies, Tessenderlo, Belgium, where he is currently a Senior Development Engineer with research interests focused on automotive electromagnetic compatibility (EMC), module- and integrated circuit (IC)-level EMC modeling and testing, and IC design for EMC compliance.

**Daniël De Zutter (F'00)** was born in 1953. He received the M.Sc. degree in electrical engineering, in 1976, the Ph.D. degree in field of electromagnetics, in 1981, and a degree equivalent to the French Aggrégation or the German Habilitation, in 1984, all from the Gent University.

He was a full Professor of electromagnetics. Between 2004 and 2008, he served as the Dean of the Faculty of Engineering, Ghent University, Ghent, Belgium, and he was the Head of the Department of Information Technology between 2010 and 2016.

His research focusses on all aspects of circuit and electromagnetic modeling of high-speed and high-frequency interconnections and packaging, on electromagnetic compatibility and numerical solutions of Maxwell's equations. As an author or coauthor, he has contributed to more than 220 international journal papers (cited in the Web of Science) and 250 papers in conference proceedings.

Prof. De Zutter was an Associate Editor for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

**Dries Vande Ginste** (SM'12) received the M.S. and the Ph.D. degrees in electrical engineering from Ghent University, Gent, Belgium, in 2000 and 2005, respectively.

He is currently an Associate Professor with the Department of Information Technology, Ghent University, and a Guest Professor at imec. In June and July 2004, he was a Visiting Scientist with the Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Champaign, IL, USA. From September to November 2011,

he was a Visiting Professor with the Electromagnetic Compatibility Group, Dipartimento di Elettronica, Politecnico di Torino, Torino, Italy. He has authored or coauthored more than 150 papers in international journals and in conference proceedings. His research interests include computational electromagnetics, electromagnetic compatibility, signal and power integrity, and antenna design.

Dr. Vande Ginste received the International Union of Radio Science (URSI) Young Scientist Award at the 2011 URSI General Assembly and Scientific Symposium, the Best Poster Paper Award at the 2012 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), the Best Paper Award at the 2013 IEEE Workshop on Signal and Power Integrity (SPI), the Best Paper Award at the 2013 IEEE International Conference on Electrical Performance of Electronic Packaging and Systems, and the Best Paper Award at the 2016 IEEE EDAPS. He served as the cochair of the 2014 IEEE Workshop on SPI.

**Niels Lambrecht** was born in 1989. He received the M.Sc. degree in electrical engineering from Ghent University, Ghent, Belgium, in 2014.

Since 2014, he has been working toward the Ph.D. degree with Ghent University under the guidance of Prof. D. De Zutter and D. Vande Ginste in the Electromagnetics Group, Department of Information Technology.

His M.S. dissertation tackled computational modeling of surface roughness effects in copper using a 2.5-D boundary element method for conductive me-

dia. His research interests include the modeling of electromagnetic compatibility tests and signal integrity issues.