### **University of Pisa**

PhD School of Engineering: "Leonardo Da Vinci"

PhD program in "Applied Electromagnetism in electrical and biomedical engineering, electronics, smart sensors, nano-technologies"

# On the Energy Efficiency of Networked Systems

ING-INF/05

*Author:* Luca Niccolini Advisors: Prof. Giuseppe Iannaccone

Dr. Gianluca Iannaccone

#### Abstract

Energy is a first-class resource for datacenter operators since its cost is the biggest limiting factor in scaling a large computing facility. The solution embraced by major operators is to build their facilities in strategic geographical locations and to abandon expensive specialized hardware for cheap commodity systems. However, such systems are not efficient when it comes to energy and a considerable amount of research effort has been put in finding a solution to this problem. Furthermore, the need for more programmable and flexible networking devices is pushing the need for hardware commoditization also within the datacenter network.

In this thesis we propose two solutions aimed at improving the overall energy efficiency of a datacenter facility. The first addresses efficiency in computing, by proposing a different hardware architecture for server systems. We propose a hybrid architecture that blends traditional server processors with very-low-power processors from the mobile devices world. The second solution envisions the usage of current server platforms as network switches or routers and provides guidelines for the implementation of power saving algorithms that do not affect peak performance while saving up to 50% power.

This work is based on both theoretical modeling and simulation and experimentation with real-world prototypes.

ii

# Acknowledgments

This work would have not been possible without the help, the support and the sympathy of many people.

My advisors first: Giuseppe and Gianluca, they have guided me throughout these three years and they have given me the opportunity to work on the challenging problems exposed in this thesis. Sylvia Ratnasamy for our insightful discussions on the relations between high-speed networking and energy efficiency, and Luigi Rizzo for his very pragmatic approach, always ready to analyze the code and start optimizing it.

Sometimes I wonder how these years would have been like without my old friends and the new ones I met living in Pisa, Berkeley and San Francisco. I have never been lonely and I want to thank them all.

Thanks to Claudio, Caterina and Agata for being my family for almost two years. Thanks to all the guys from the lab in Pisa, to Valentina in particular, without her these pages wouldn't have been printed (literally), and to Martina for being always angry and for creating the chaos in every occasion. Thanks to Massimo, a very good friend.

When I first flew to Berkeley I never expected to meet my "missing brother": Elias, a European Intellectual but mostly a true friend.

I want to thank those who have always been with me even when we were geographically distant, David, Carlo and Tommaso.

A special thanks goes to Chiara who decided to embark with me in this journey.

Needless to say, having a lovely and supportive family has helped more than everything else. I want to thank my mother, my father, my sister and all my relatives. My grandfather in particular who stimulated in me the interest in computing for the first time, perhaps without even knowing it. He loved numbers and statistics in his own way. He kept track of everything he could, from the area of the land he cultivated and the efficiency of his vineyard to the cards that were played during Briscola matches. This thesis is dedicated to him.

iv

# Contents

| 1 | Intr       | oduction                           | n                                  | 1  |  |

|---|------------|------------------------------------|------------------------------------|----|--|

|   | 1.1        | Motiva                             | tion                               | 1  |  |

|   | 1.2        | Problem                            | m Space                            | 2  |  |

|   |            | 1.2.1                              | Reducing Power Usage Effectiveness | 3  |  |

|   |            | 1.2.2                              | Reducing IT costs                  | 4  |  |

|   | 1.3        | Thesis                             | Overview and Contribution          | 9  |  |

| 2 | Background |                                    |                                    |    |  |

|   | 2.1        | Small a                            | and Big cores                      | 11 |  |

|   | 2.2        | Suppor                             | rt for power management            | 12 |  |

| 3 | Hyb        | rid Data                           | acenters                           | 15 |  |

|   | 3.1        | Hybrid Server Prototype            |                                    | 17 |  |

|   |            | 3.1.1                              | Prototype architecture             | 17 |  |

|   |            | 3.1.2                              | Software configuration             | 19 |  |

|   |            | 3.1.3                              | Experimental results               | 21 |  |

|   | 3.2        | Latenc                             | y and power model                  | 24 |  |

|   |            | 3.2.1                              | Response Latency                   | 24 |  |

|   |            | 3.2.2                              | Power Usage                        | 25 |  |

|   |            | 3.2.3                              | Model validation                   | 25 |  |

|   | 3.3        | Evaluating hybrid server design 27 |                                    |    |  |

|   | 3.4        | Related                            | d Work                             | 31 |  |

| 4  | Ene                        | rgy-pro                               | portional Router                      | 33 |  |  |  |

|----|----------------------------|---------------------------------------|---------------------------------------|----|--|--|--|

|    | 4.1                        | Decon                                 | structing Power Usage                 | 36 |  |  |  |

|    |                            | 4.1.1                                 | Server architecture                   | 36 |  |  |  |

|    |                            | 4.1.2                                 | Workload                              | 37 |  |  |  |

|    |                            | 4.1.3                                 | Power characterization                | 38 |  |  |  |

|    | 4.2                        | Addre                                 | ssing Software Inefficiencies         | 40 |  |  |  |

|    | 4.3                        | Studying the Design Space             |                                       |    |  |  |  |

|    |                            | 4.3.1                                 | Single core case                      | 42 |  |  |  |

|    |                            | 4.3.2                                 | Multiple cores                        | 46 |  |  |  |

|    | 4.4                        | Impler                                | mentation                             | 52 |  |  |  |

|    |                            | 4.4.1                                 | Online adaptation algorithm           | 54 |  |  |  |

|    |                            | 4.4.2                                 | Assigning queues to cores dynamically | 55 |  |  |  |

|    | 4.5                        | Evalua                                | ation                                 | 57 |  |  |  |

|    | 4.6                        | Testbed setup and Additional measures |                                       |    |  |  |  |

|    |                            | 4.6.1                                 | Measuring Latency                     | 63 |  |  |  |

|    |                            | 4.6.2                                 | Sleep states                          | 63 |  |  |  |

|    |                            | 4.6.3                                 | Traffic Burstiness                    | 65 |  |  |  |

|    | 4.7                        | Relate                                | d Work                                | 69 |  |  |  |

| 5  | Conclusion and Future Work |                                       |                                       |    |  |  |  |

|    | 5.1                        | Conclu                                | usion                                 | 71 |  |  |  |

|    | 5.2                        | Future                                | Work                                  | 72 |  |  |  |

| Bi | Bibliography               |                                       |                                       |    |  |  |  |

# Chapter 1

# Introduction

### 1.1 Motivation

The backbone of today's computing infrastructure is powered by large-scale computing facilities, commonly known as *datacenters*. A typical datacenter hosts tens of thousand commodity servers connected by thousands networking devices and presents challenging scaling problems at all the design levels [90]. However, energy costs constitute the most limiting factor in scaling a datacenter today.

With energy consumption in the order of tens of MegaWatts and electricity bills up to tens of Millions Dollars per year, power-related costs represent a high fraction of the total operating expenses for a datacenter and are growing faster than equipment costs for both computing and networking. Power-related costs represent the second recurring cost, second only to labor. For this reason major datacenter operators like Google, Amazon.com, Microsoft and Yahoo! are building their facilities close to energy sources, where energy is cheap [92].

Scaling-out by adding more and more cheap commodity hardware, and relying on fault-tolerant software to deal with (unavoidable) frequent failures, has been proven a successful approach to achieve large scale while keeping hardware expenses relatively low. The trend toward using cheap commodity hardware is called "commoditization".

Unfortunately, the hardware available today is not *energy-proportional* [60]. An ideal energy-proportional system would consume zero energy while active and waiting for some work to execute. Current servers, instead, consume approximately 50% of their maximum power while running at down to 20% of their max-

imum load. Furthermore, the average utilization of a single server is far from its peak utilization, making the hardware work in its most inefficient operating region.

Commoditization is in progress also for the datacenter network. Similarly to the computing infrastructure the goal is to build a scalable and reliable architecture by using cheap off-the-shelf devices [111]. Inside their own datacenters, operators ask maximum flexibility from the network in order to quickly deploy new network protocols and mechanisms that can efficiently harness the particular network topology [50, 80, 82, 83]. Programmable switches and routers based on the same architecture as servers have been proposed as a means to achieve innovation at speed [33, 71, 74]. However, the move towards commodity servers as network devices suffers from the energy issues introduced above since networks are typically overprovisioned and switching devices operate at low utilization on average.

Energy efficiency improvements at the server and switch/router level have the potential to benefit from the datacenter scale. Even small savings on a single device are amplified by the huge number of devices in a computing facility and by the increasing number of datacenters around the globe.

The contribution of this dissertation is twofold. First, we propose to reduce the energy consumption of computing by using heterogeneous multicore servers. An heterogeneous design includes traditional high-performance and high-energy components coupled with a low-speed and low-power subsystem exploited to maintain external availability and run the workload in periods of low utilization. Then, we address the problem of energy efficiency of packet-processing applications running on commodity multicore servers and we advocate the implementation of smart algorithms, that optimally operate the available computing resources, in order to improve the overall energy efficiency.

### 1.2 Problem Space

Energy is a fast growing concern both for industry and society. While some alarms have been sounded recently about the energy impact of computing [64], and of the Internet in particular [29], we believe that the current computing and networking technologies have a high potential for reducing the energy that society wastes everyday. Furthermore, the total energy consumed and embodied in the Internet, estimated by Raghavan *et al.* [112], is negligible compared to the overall energy used by society, with the total power absorbed by datacenters worldwide representing only 1.3% of the global energy consumption [95].

We focus on the energy efficiency of datacenters as a means to achieve a better scaling of computing facilities by lowering expenses for operators. The energy consumed in a datacenter is logically divided in two categories: (i) the energy absorbed by IT equipment; (ii) the energy indirectly consumed to keep the above equipment operational. The former represents the electricity spent to perform the main operations for which the datacenter has been built, *i.e.* computing, networking and storage. The latter denotes the energy overhead and includes, among other sinks, the power distribution and transformation infrastructure, the airflow and cooling system, the lighting infrastructure and personnel offices.

The overall efficiency of a single facility is expressed in terms of the *Power* Usage Effectiveness (*PUE*) metric. PUE is defined as the ratio between the total energy absorbed by the facility and the energy utilized by IT devices (after power conversion). The ideal PUE value is 1.0 and implies that all the energy entering a datacenter is spent for useful work.

Given this classification of datacenters energy the work towards its reduction follows two parallel paths: (i) *Reducing PUE* and (ii) *Reducing the IT costs*.

#### 1.2.1 Reducing Power Usage Effectiveness

The U.S. Environmental Protection Agency published a report [64] in 2007 showing that computing was responsible for 1.5% of the total U.S. energy consumption, with datacenters being a big fraction of that. Also the average datacenter, at the time, was reported to operate with a 100% energy overhead, *i.e.* with a PUE of 2.0. Since then, a lot of effort has been put in reducing this overhead through the sharing of best practices [9] and measurement data [13] that were before retained by operators as corporate secrets.

Best practices include how to continuously and correctly measure the PUE, how to realize efficient cooling systems by leveraging free external resources (like cold air and water) and how to properly place the servers to maximize the air flow, how to distribute power by reducing the number of AC/DC conversions and how to harness reusable energy sources and recyclable materials to reduce the environmental impact.

Cooperation between major operators has been fostered by initiatives such as "Climate Savers Computing" [9] and "The Green Grid" [41] and eventually resulted in a community effort with Facebook releasing the whole design of their new datacenters as an opensource project [27]. The project includes the technical specifications at each design level, from custom motherboard schematics and

3

server chassis design [77] to electrical design of power distribution to the mechanical airflow system [28].

As a result of this engineering work the PUE in large-scale datacenters is now approaching its theoretical minimum, with the best-in-class operators advertising a one year average<sup>1</sup> of 1.14 [13] and a seasonal minimum of 1.07 [11]. This optimization process is slowing the growth of datacenter electricity usage with the actual values being significantly lower than the most optimistic predictions in 2007 [95].

#### 1.2.2 Reducing IT costs

Minimizing the total cost of ownership (TCO) of IT equipment is a challenging problem since it directly involves possible optimization both in hardware and software. It is the topic of active research in Academia and industry and the proposed solutions reflect the evolution of datacenters towards today's warehouse-sized general-purpose computers [90].

**Workload specific.** A first approach, that keeps the base hardware architecture untouched, is to explore software solutions for optimizing power consumption in presence of specific workloads [121]. Early days datacenters hosted few tens of servers clustered together to run one specific application, such as high-performance computations or distributed databases. With the rise of cloud computing [56] however, datacenters should be able to run diverse workloads, ranging from on-line data-intensive queries [107] that require low latency, to long-running MapReduce [2, 4, 72] batch jobs that need high computing throughput and large network bandwidth. Furthermore, with Infrastructure as a Service (IaaS) [3,22,30] and Platfrom as a Service (PaaS) [12, 14, 42, 44] solutions the user has complete control over his own virtual machines and applications and no assumption can be made on the workload that the datacenter will run. Thus, the datacenter is seen as a general-purpose warehouse-scale computer [90], and workload-specific optimization are not generally applicable. With one exception.

The one specific-workload that is common to all the computing facilities and whose optimization are widely applicable is the one related to networking and packet processing applications. Switching, routing and other packet-processing

<sup>&</sup>lt;sup>1</sup>Large datacenters are built in zones where it is possible to use external air or water for cooling, for this reason there is a seasonal fluctuation of the PUE due to external weather condition and temperature.

applications typically run on dedicated hardware and provide network connectivity to computing and storage hosts.

Our work on optimizing network devices for energy efficiency leverages the trend towards commoditizing the network in datacenters. New network topologies [49, 80, 82, 83] have been proposed to flatten the network. These architectures seek for a higher bisection bandwidth and lower over-subscription rates by exploiting multiple paths inside the local network. They have the potential to reduce equipment cost by installing cheaper devices. The problem with advanced topologies is that they require fundamental changes in the way packet forwarding is performed. High level forwarding-plane protocols, like OpenFlow have the role to blur the existing gap between traditional MAC layer (L2) and network layer (L3) packet forwarding and are pushing the need for more flexibility and programmability from the networking devices.

We believe that the solution to achieve the flexibility requested by this fastchanging environment is the deployment of programmable routers based on the same general-purpose server architecture used for computing and storage. A network like this can accommodate changes at the speed of software deployment. Furthermore, software developers can benefit from a well-known programming environment and Instruction Set Architecture [33,74].

**Low-power manycore.** A natural approach to build an energy-efficient computing infrastructure is to use energy-efficient hardware building blocks. The fast growth of the mobile devices market has pushed the design of low-power processors and platforms in order to maximize devices' battery life. Despite being intrinsically low-performance, these platforms are more efficient than traditional server hardware in terms of *instructions per Joule*. Mobile systems design, targeted at low-power operations, has lead to well-balanced systems while in the server world we are assisting at an ever increasing performance gap between CPU, Memory and I/O. Processor cores for mobile devices are indicated as *small* cores, or more colloquially as *wimpy* cores, due to the reduced number of transistors needed to implement their functionalities. Conversely, server processors with multiple out-of-order execution engines and large multi-level caches are also indicated as *big* or *browny* cores.

Several attempts have been made to run datacenter-like applications on systems built by a high number of low-power elaboration units. These solutions differ in their integration scale and can be divided in tightly-coupled and loosely-coupled designs. The authors of FAWN (a Fast Array of Wimpy Nodes) [53] successfully explored the ability to run a key-value storage service on an array of loosely-coupled (ethernet connected) nodes powered by a 500 MHz AMD Geode CPU and flash storage. They show that a FAWN-like architecture can be cost-effective for distributed storage seek-bound workloads.

Some industry solutions, recently appeared on the market, implement a finer scale integration of low-power cores. Seamicro product line includes platforms with up to 768 1.6 GHz Intel Atom cores in one single box [36], thanks to a high-speed integrated network fabric, and have been adopted, among others, by Mozilla to power their web-servers [35] and by eHarmony [10] for distributed data analysis with Hadoop [4]. Tilera pushes low-power cores integration even further, selling a 64-core system-on-a-chip [62] that includes 1 and 10 Gbps network, PCIe and DDR2 controllers. Each core has a shallow pipeline, for low-power operations and more predictable performance. Fast intra-core communication is achieved by means of a multi-layer mesh network and on-core L2 caches are leveraged to implement a distributed L3 cache. Experience with memcache [76] in-memory key-value storage shows that the TilePRO64 system is three times more energy-efficient than a Xeon based system [63].

However, it has been shown that solutions with a large number of low-power cores are not appropriate for all the datacenter workloads, resulting in significant performance slowdown for the most demanding applications like parallel databases [99], web-search [91] and massive-data sort [123]. A high-scale datacenter must be general purpose, it should be able to run diverse workloads, most of them unknown at design time. The main drawback of low-power manycore architectures is that the single nodes are highly constrained in their hardware capabilities. Usually they have a 2 - 4 GB addressable memory bound and a low number of connections for disk I/O. This lack of hardware capabilities imposes strict constraints on the application programmer. Furthermore, many-core architectures force a shift in the programming model and may require a complete code refactoring in order to benefit from the high core count.

Software development is an important factor to take in consideration when computing the cost of a new hardware infrastructure in the datacenter. Hölzle [89] proposes a rule of thumb for which it is not economically advantageous to switch to a *wimpy* architecture if the single core performance is less than half the performance of current *browny* cores.

Energy proportionality. A different approach to reduce power expenses in a

large computing facility is to address the non-proportionality of the servers.

Many of these efforts focus on cluster-level solutions that dynamically consolidate work on a small number of servers. Thanks to this, underutilized servers can be turned off at will and computation moved between machines if needed [113, 120]. Load balancers and task schedulers are instrumented with a prediction component, based on previous history. Prediction results are exploited to starve some machines of requests and consequently turn them off. The overall goal is to obtain a quasi-power-proportional ensemble with non power-proportional building blocks by consolidating the load, with server or rack granularity.

To further improve the proportionality of the system as a whole, hardware heterogeneity can be exploited. In a datacenter with two different types of clusters, the classic one with blade servers and a low-power one with low-power systems, the latter can be leveraged to serve requests in a long low-load period [96, 110]. Solutions in this space affect hardware provisioning costs, charging the operator of the burden to provide its facility with both systems to handle high-load and proxy-systems for low load.

The general downside of consolidation techniques is that servers on/off cycles <sup>2</sup> and the workload consolidation overhead are in the order of tens of seconds. Consolidation being typically achieved through virtualization and live migration of virtual machines [59, 67, 69, 105]. Furthermore, it is challenging to predict the incoming load on a fine timescale [24, 81]. One more problem with consolidation is that network reachability is lost when machines are turned off. Most datacenters run distributed key-value storage and distributed filesytems [66, 70, 73, 76, 79] in which replicas are distributed among all the servers. Thus, a node not performing computation might be required because it holds a replica that other nodes need for their computation. For this reason, cloud providers are reluctant to turn off computers, not to affect high availability. As an example, Amazon's solution to increase the overall server utilization while amortizing the cost of keeping servers idle is to offer a service in which spare resources are offered at a variable price [1], depending on the overall datacenter utilization, and users can bid on the instantaneous price.

A more integrated approach to power proportionality is to solve the problem for a single server in order to benefit from the massive scale of the datacenter and to hide the power saving mechanisms from the programmer as much as possible. A solution in which a system can quickly transition to a deep sleep state while

$<sup>^{2}</sup>$ Current commodity servers do not expose system low-power states that are found in desktop machines such as standby and suspend (*i.e.* ACPI S3, S4 and S5 states).

still maintaining external network visibility and availability is needed to allow perserver power-proportional behavior [48, 106]. Servers running multiple services at the same time shows short idle periods in the sub-second scale, making practically unfeasible to completely shut down the machine as proposed by consolidation approaches.

We explore a similar approach to that first proposed by Meisner *et al.* [106] requiring that the system is never unavailable to serve incoming requests. Despite large periods of low utilization, servers are rarely completely idle and in the case of latency-sensitive workloads active low-power states are the only solution to reasonably scale down energy consumption with server load [107]. We leverage hardware heterogeneity at the platform level by exploring the benefits of a system that mixes high-performance energy-inefficient processors (with big cores) and low-speed high-efficiency processors (with small cores). We believe that such hybrid architectures comprising small cores and big ones can provide energy benefits at the single-server level, by maintaining availability through small cores and waking up big cores when the load increases so that service-level agreements (SLA) are not violated.

The idea of hybrid architectures for energy-efficiency is not new, systems using mixed processors are starting to appear in the mobile devices market. Major manufacturers, like NVidia, ARM and Qualcomm are pushing solutions with a big and small cores mix [45, 47] or with cores operated at different frequencies and voltages [46]. A hybrid design helps to increase energy efficiency by lowering the power envelope of the system. Furthermore, the heterogeneous hardware design can be made transparent to application programmers. In the aforementioned mobile platforms for example, small cores are used to run background tasks, such as checking e-mails, while big cores are awakened whenever high computational power is needed, typically for multimedia tasks. The switch between small and big cores is completely managed by the firmware, allowing the programmer to abstract from the underlying hardware technology.

We study the problem of heterogeneous multi-core in server hardware and explore the feasibility of mixed architectures with current high-end processors and mobile processors, specifically within the Intel Xeon and Atom processor families [18].

### **1.3** Thesis Overview and Contribution

The demand for highly-parallel computation on massive amounts of data is increasing at a fast pace, pushing datacenter operators to enlarge their facilities or build bigger ones. Today, datacenters are limited in scale by energy consumption with 80% of the recurrent costs scaling with electricity costs.

In this thesis we tackle the problem of energy-efficiency of the networking infrastructure and power-proportionality of the computing machinery in large-scale datacenters. Our focus is on the power-proportionality of the basic building blocks: general-purpose servers and packet-processing devices.

In Chapter 2 we present the hardware mechanisms that today's' systems implement, and that motivate our work, with a specific focus on those supported by the Operating System. Then in Chapter 3 and Chapter 4 we present the main contribution of this thesis that is twofold:

• In Chapter 3 we make the case for *hybrid datacenters*. We address the challenges in building a computing infrastructure that blends low power platforms with high performance ones. We show how these designs can handle diverse workloads with different service level agreements in an energy efficient fashion. We evaluate the feasibility of our approach through experiments and then discuss the design challenges and options of hybrid datacenters.

Given the positive results of this analysis, we propose a hybrid multiprocessor architecture for energy-proportional web servers and datacenters, to achieve significant energy savings at the price of small increase in service delay. The server consists of a subsystem with low-power cores, always on and serving user requests when load is low, and a high-performance subsystem, by default in sleep mode, woken up only when the load is high. Through experiments on a hardware prototype and an accurate timing and power model of the server we assess the performance and the energy benefits for a Web server. Finally, we explore design guidelines for future energyproportional systems.

• In Chapter 4 we approach energy-efficiency in datacenter networks. We aim at improving the efficiency of packet-processing applications running on commodity server hardware without compromising their performance. We investigate the design of a router that consumes power in proportion to the rate of incoming traffic. We start with an empirical study of power

consumption in current software routers, decomposing the total power consumption into its component causes. Informed by this analysis, we develop software mechanisms that exploit the underlying hardware power management features for more energy-efficient packet processing. We incorporate these mechanisms into Click [93] and demonstrate a router that matches the peak performance of the original (unmodified) router while consuming up to half the power at low loads, with negligible impact on the packet forwarding latency.

In Chapter 5 we draw our conclusion, address the applicability of our work and provide ideas and plans for future work.

# Chapter 2

# Background

In this chapter we present the hardware features and mechanisms that can be found in modern processors and that motivates our work.

#### 2.1 Small and Big cores

Traditionally, power efficient designs attempt to find the right balance between two distinct, and often conflicting, requirements: (i) deliver high performance at peak power (i.e., maximize compute capacity for a given power budget) and (ii) scale power consumption with load (i.e., energy proportionality and very low power operations). A fundamental challenge in finding a good balance is that, when it comes to processor design, the mechanisms that satisfy the two requirements above are significantly different. High performance requires mechanisms to mask memory and I/O latencies using large multi-level caches (today's server processors use three cache levels with the last-level cache projected to soon reach 24MB [17]), large translation lookaside buffers, out-of-order execution, high speed buses, and support for a large number of pending memory requests. These mechanisms result in large transistor counts leading to high leakage power and overall high power consumption. In a modern high end processor, less than 20% of the transistor count is dedicated to the actual cores [117, 122]. This is reflected in the processor high power consumption. In our work we measured the power needed to keep the "uncore" components active while reducing the "core" power consumption to the minimum possible. We found that approximately 25 W are needed for a modern 6 cores Westmere CPU.

Mobile processors designs, on the other hand, focus on those processor features with low-power operations. For example, the Atom processor [78] includes an in-order pipeline that can execute two instructions per cycle, a small L2 cache and power-efficient clock distribution. The Atom simple micro-architecture implements only those features that give the best performance per watt. A strong design constraint during the processor design has been to implement a feature only if it guarantees "1% performance increase, for less than 1% power increase" [61]. *E.g.*, simultaneous multi-threading has been implemented (in higher-end models of the Atom family) since it provides a 36% performance improvement versus only a 19% increase in power.

This results in a strongly reduced transistor count with low leakage power and limited power consumption at low load. Further, Atom design is focused on allowing quick and frequent transitions to a very low power state (e.g., 80 mW with less than 100  $\mu$ s exit latency [78]).

### 2.2 Support for power management

Modern systems provide a variety of power management mechanisms that operate at all levels in the platform. Some are only visible to the hardware while others can be controlled directly by the operating system. Here, we introduce the basic controls that are exposed to the operating system and we briefly summarize the mechanisms only available to the hardware.

**Core idle states (C-states).** Each core in a package can be independently put into one of several *low power* or "idle" states, which are numbered from C1 to Cn. The state C0 is present on all platforms and refers to a core that is executing instructions and consuming the highest amount of power since all the areas within the core are powered on. Higher numbered states indicate that a successively larger portion of the core is turned off resulting in a lower power draw. The particular C states that are supported are vendor and processor specific. The Westmere processors we use in Chapter 4 offers three C states (C1, C3 and C6) and allows to put each core, independently from others on the same package, in different "idleness" states.

A core enters into a C state either by executing a HALT or MONITOR/MWAIT instruction. The state entered is set using special registers of the CPU. The wakeup event can be either an interrupt or a write access to the monitored memory range specified by the MWAIT. C states are exited (to return to the C0 state) when the

desired triggering event occurs. Considering the larger amount of circuitry turned off, higher idle states take longer to revert back to the fully operational C0 state. The time to return from a higher numbered C state back to C0 is termed the *exit latency* of the state.

As an example, when in C1 the core is *clock gated* (the clock distribution into the core is blocked), but the core is still drawing power. Going from C1 to C0 only requires the clock distribution to be re-enabled; thus, the time it takes to execute the first instruction (after being in C1) is comparable to that of a cache miss.

In C3, the L1 and L2 caches are flushed and turned off. In C6, in addition to turning off the clock and the caches, the core is *power gated* (power distribution into the core is disabled) after the core's state is written to a reserved part of the L3 cache. Consequently, the time to enter/exit C3 and C6 is much higher (compared to C1) due to the need to save and restore state, and to allow the voltage levels to stabilize. Furthermore, on wakeup the core will start with a cold cache, which results in lower performance.

The time to exit from a C-state is called "exit latency", and we will measure it for our system in Section 4.6.2.

**Processor performance states (P-states).** While a processor core is in active C0 state, its power consumption is determined by the voltage and operating frequency, which can be changed with Dynamic Voltage and Frequency Scaling (DVFS). In DVFS, voltage and frequency are scaled in tandem. This is because a particular frequency requires a minimum voltage for the circuit to operate in a stable and reliable way. When voltage is reduced, transistors take longer to switch, and signals take longer to propagate, leading to the circuit becoming unstable. To preserve stability and correctness, the operating frequency must also be lowered.

Modern processors offer a number of frequency and voltage combinations, each of which is termed a P state. P0 is the highest performing state (pegged at the maximum voltage required by the highest operating frequency); subsequent P states operate at progressively lower frequencies and voltages. Transitions between P states require time to stabilize the frequency, but the transition can be applied while the processor is executing instructions, without halting or freezing the core nor flushing caches. While in general, cores can have independent power planes, most processors incorporate a shared voltage rail across the cores, which forces a shared P-state between cores belonging to the same package. Effectively, all the cores run at a frequency that is dictated by the most hungry core. The processor in our system offers 14 P states with frequencies ranging from 1.6 GHz to 3.3 GHz.

Additional power states. Even though we do not use them directly in our system, we need to mention two additional classes of power states: processor throttle states (T-states) and platform sleep states (S-states). T-states force the processor frequency to be lowered when power dissipation approaches the thermal limit to prevent the processor, or other subsystems, from being damaged. T-states are similar to P-states, but they are managed by the core's firmware and cannot be controlled from software.

Turbo Boost [20] is an Intel proprietary mechanism that aims at increasing the performance of a system that is not fully using all its cores while assuring that processor power constraints are never violated. Turbo Boost is activated for cores that are in the active C0 states when only a subset of the cores in the package is active. In such particular circumstances the maximum operating frequency of the active cores can be increased while still meeting the power, current and temperature limits of the processor package. Akin to T-states, "boost-states" are only visible to hardware and can potentially introduce non-predictable performance increases since its activation depends on the workload and on the operating conditions (*i.e.* number of active cores, estimated current consumption, estimated power consumption and measured processor temperature). In the following work the Turbo Boost techniques have been disabled in order to get repeatable experiments and measures.

S-states are defined for the entire system (not just the processor). S0 is the active state, while in higher states portions of the system are turned off after saving their state to RAM or persistent storage. The S-states reflect various degrees of system-wide sleep and correspond to the familiar "stand-by" and "hibernation" modes of laptops and desktop. The transition times involved in the S-states are measured in seconds. We do not consider them in our work because the latencies involved are much higher than the latencies high-speed services can tolerate and also because server systems typically do not implement such features.

# Chapter 3

# **Hybrid Datacenters**

A more efficient use of energy is a key challenge for modern datacenter design: it would enable significant reduction of costs and increase of computing power density per unit volume. Datacenters' building blocks are commodity servers, providing ease of deployment, low costs and familiar programming environments. However, current servers - and therefore datacenters - are not energy efficient, specifically at low load. Barroso *et al.* [60] report that more than 40% of energy is consumed to keep servers online while not executing any useful work, and each server is typically used below 50% of its peak performance. Hence, the call for *energy-proportional* systems, defined as systems whose power consumption is proportional to the computing load.

In this chapter we show that a hybrid server architecture is a promising option for achieving energy proportionality while paying a small additional cost in performance. A hybrid multi-core architecture consists of a mix of low-power cores and high-performance cores that coexist on the same motherboard and are coordinated by the operating system or by the application. Low-power and high-performance cores are classified respectively as "small" and "big" cores since advanced features (such as large caches, out-of-order execution, etc.) affect core area by requiring a larger number of transistors.

The basic concept is extremely simple: small cores are always on, keeping the system responsive and serving user requests when the load is low. Big cores are by default in a deep stand-by mode, and are woken up only when the load is high. This approach is able to exploit several trends in semiconductor and processor technology. First, with the introduction of the Atom processor ("small" core in our terminology) there is now a low-power alternative to the traditional server processor (Xeon product line) that shares the same instruction set architecture (ISA). Sharing the same ISA allows for providing a single, and familiar, programming environment to developers. A hybrid system is therefore equivalent to a traditional server and requires no changes to the datacenter architecture or the management processes of datacenter operators. Second, the performance of small cores is continuously increasing to meet users' expectation of a full Internet experience on smartphones, netbooks and tablets. Most importantly, battery life and small form factor requirements force designers to select and implement energy-efficient features and mechanisms for improving performance per Watt [61]. Finally, high performance cores are adopting power saving features (clock gating, power gating, etc.) that permit individual cores and other subsystems within the same server to be turned off to maximize energy efficiency at low load [19].

It has been recently pointed out that despite large periods of low utilization, servers are rarely completely idle and in the case of latency-sensitive workloads active low-power states are the only solution to reasonably scale down energy consumption with server load [107]. Therefore, we believe that hybrid architectures comprising small cores with big ones can provide energy benefits at the single-server level, by maintaining availability through small cores and waking up big cores when the load increases so that service-level agreements (SLA) are not violated.

We presented the key concept in a position paper [68]: here we present a complete analysis showing experimental results on a prototype hardware with realistic workloads. Using the prototype we derive and validate a simple, yet accurate, model of the service delay and power on the hybrid system. We then use that model to assess the feasibility of the hybrid approach as well as explore the design space. Specifically, we study the design space along two dimensions: the ratio of small vs. big cores in the system and the relative performance of small core vs. big cores when processing Web requests. We show that the current small core performance levels make hybrid multicore design feasible and that hybrid designs are an extremely promising solution to achieve energy proportionality.

The rest of the chapter is structured as follows. In the next section we describe the prototype system and present experimental results with different types of Web server workloads. Then, in Section 3.2, we develop a high-level model of the hybrid server architecture, capable of accurately simulating timing performance and time-dependent power consumption. The model is validated, in terms of accuracy in the estimation of distributions of service delay times, through comparison with experiments on the hardware prototype. In Section 3.3 we use the latency and power model to explore various design options and estimate the energy savings that can be achieved. We review related work in Section 3.4.

## 3.1 Hybrid Server Prototype

We begin our analysis by measuring the performance of a hybrid architecture research prototype. In the following subsections we describe the hardware and software configuration and discuss experimental results.

#### **3.1.1 Prototype architecture**

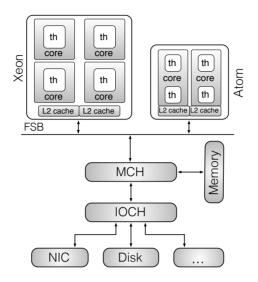

The hybrid server prototype is based on a standard dual-socket motherboard suited for Intel Xeon Harpertown [18] and compatible CPUs; however, the first socket hosts an Intel Atom 330 processor, mounted by means of an adaptation board. The board maps Atom pins to the Xeon socket and adjusts voltages accordingly. Figure 3.1 shows a high-level view of the system with the two CPUs connected to the northbridge chipset (MCH) through a shared front side bus (FSB). MCH manages access to shared memory and to peripherals through the I/O controller (IOCH).

Table 3.1 summarizes the main differences between the two CPUs. Since the original purpose of the prototype was demonstrating hybrid server feasibility, some tweaks have been made to achieve interoperability at the expense of overall performance, degrading some Xeon features to those supported by Atom. For example, Xeon clock and bus frequencies have been reduced to make the FSB work at the maximum sustainable frequency of the Atom, *i.e.*, 533 MHz. For this reason the big CPU (a Xeon X5450) is constrained to a 1.2 GHz operating frequency, much lower than the 3 GHz maximum clock rate. Furthermore, cache coherency is achieved by making the smaller cache ignore snoops for entries that exceed its size.

Atom and Xeon processors have different microarchitectures but implement partially-overlapping Instruction Set Architectures (ISAs). They both have full x86 compatibility exhibiting some differences only in instruction set extensions (*e.g.* SSE instructions [39]). However, operating system support is needed to let the applications abstract from these asymmetries [114].

The server runs the HeterOS operating system [100], developed from Intel, that is a 64-bit compliant OS providing the following improvements on top of Linux:

Migration on fault: an application can execute instructions known only to a sub-

Figure 3.1: Prototype hardware architecture. FSB is the Front Side Bus, MCH is the Northbridge chipset, IOCH is the I/O controller.

set of cores. The operating system handles unknown instruction exceptions and migrates the process that caused the fault to a core that understands the instruction;

*Dynamic scheduling*: HeterOS provides both *slow cores first* and *fast cores first* scheduling policies. They dynamically reschedule tasks, based on performance metrics, to take advantage of CPU bound and I/O bound phases within the same execution flow.

As already mentioned, the hybrid server prototype is not optimized for power consumption, and therefore exhibits high power consumption when only the Atom is active. The main reason for that is the legacy shared-bus architecture, where the bus is always on and MCH and IOCH do not have sleep states. Measured wall power is 228 W at idle and 268 W at maximum load. For this reason, we will use experiments to verify the feasibility of our proposal and to validate our model for a hybrid server. Then, we will use the model to explore the performance achievable if power saving features were fully implemented.

| Name           | Xeon X5450 | Atom 330 |

|----------------|------------|----------|

| Clock rate     | 1.2GHz     | 1.6GHz   |

| Threads        | 4          | 4        |

| Cores          | 4          | 2        |

| Hyperthreading | No         | Yes      |

| L2 Cache       | 2x6MB      | 2x512KB  |

Table 3.1: Main differences between CPUs in the hybrid server prototype. They have the same number of threads thanks to Atom implementing hyperthreading.

#### 3.1.2 Software configuration

Here we describe the software setup used to assess the performance of our hybrid architecture prototype serving HTTP requests. The workbench consists of a request generator connected to the server through a 1 Gbps Ethernet link.

**Request generator.** The client machine runs multiple instances of the *http\_load* [15] request generator in order to increase the request rate up to the maximum load sustainable by the server. By using this tool, requests can be generated at a constant rate or with a specified degree of parallelism. The client machine also measures per-request latency by computing it as the interval between the connection instantiation at the server and the time the response is received by the client.

**Web server.** The software stack on the server machine is based on the *Lighttpd* [21] Web server and its *FastCGI* module. Lighttpd is a lightweight and modular Web server while FastCGI is a typical solution for boosting the execution of dynamic requests. It defines a communication protocol between the Web server worker threads and external processes, using sockets as the communication channel. FastCGI processes are created at Web server startup and can run on the server machine as well as remotely. In the FastCGI working model processes are persistent and serve more than one request, saving the time needed in legacy CGI systems to fork one process per request.

Processes are distributed in a way that enables us to exploit multicore parallelism. Lighttpd runs one worker thread on the first Atom core while FastCGI processes run on both the Xeon and Atom processors. The worker thread is responsible for accepting all the incoming requests and scheduling them on the most

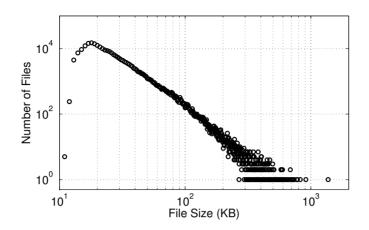

Figure 3.2: Dataset file sizes follow a power-law distribution

suitable FastCGI process. We want requests to be allocated to a core and to run on it until completion, without incurring in rescheduling overhead.

**Scheduler.** In our solution, processes are statically assigned to cores with a one to one mapping. We modified the FastCGI module to make it aware of the underlying asymmetric processor set and changed the default load-balancing algorithm into a threshold-based scheduler. The scheduler allocates incoming requests to small cores when the load (as measured by the number of concurrent requests) is below a defined threshold  $(S_t)$  and to big cores when the threshold is reached. The threshold can be larger than the number of small cores, in that case pending requests are queued and their execution is deferred. The threshold effectively is a knob to trade-off power consumption for latency since increasing  $S_t$  reduces the duty cycle of large cores. With this simple mechanism we create opportunities for big cores to go in their deepest sleep state whenever the server is underutilized. In Section 3.3 we analyze the effectiveness of this mechanism in terms of energy efficiency.

**Dataset.** We collected a 10 GB dataset from the English version of Wikipedia. Our dataset is composed of 250,000 files with sizes ranging from 6 KB to 1.4 MB. This is a representative dataset for Web applications that work with plain HTML files. Figure 3.2 shows that file size in the dataset follows a Zipf distribution, as in Ref. [58].

**Workload.** The definition of a workload that is both simple and representative of the applications of today's datacenters is not straightforward. Servers in virtualized environments and MapReduce nodes must be as general purpose as possible. Instead, in the underlying infrastructure that powers large websites, most servers act as specialized back-end nodes running only one kind of requests on their fragment of the whole dataset (e.g. memcached nodes, message search). We consider the following workloads to be executed on files in our dataset:

readfile: statically serve the file as is; ksort: sort (key, value) pairs based on key values; compress: deflate the input file using gzip; count: computes a histogram of bytes.

The workloads above allow us to explore different deployment scenarios. The readfile workload represents the traditional Web server; the other three instead require to process and perform computation on the input data before sending the response to the client. The computations vary in complexity and the subsystems (CPU, memory, I/O) they employ. The workloads are conceptually simple and do not represent applications in which slow blocking database requests are made. However, they are representative for servers managing a high number of concurrent connections with low latency. Exploring more complex workloads is a major part of our future work.

#### 3.1.3 Experimental results

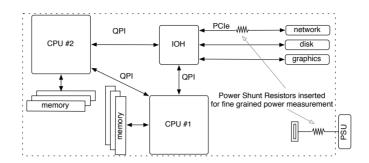

In order to assess the service delay implications in systems with an hybrid set of processors, we stress the server by gradually increasing the input query rate up to the maximum sustainable load. We only report results for the *count* workload since results for other workloads exhibits a very similar behavior.

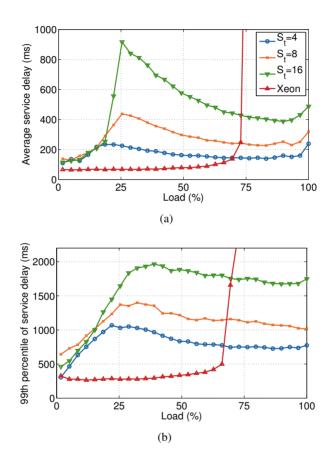

Figure 3.3 reports the system performance in terms of service delay. It shows values for the average service delay (top) and the 99th percentile of the service delay (bottom). Each curve represents a different value for the scheduling threshold  $S_t$ , *i.e.*, the maximum number of simultaneous requests served by small cores.

By setting  $S_t = 0$  we force the system to use big cores only. As can be seen they sustain up to 75% of the maximum load of the hybrid solution. All the other curves have a peak around 25% of the maximum load, where requests are being processed almost exclusively by low-performance cores. When the load increases further, requests are forwarded to big cores and performance improves, until saturation of the whole system is reached. From Figure 3.3 we evince a 3X speedup for our Xeon processor compared to Atom. Even if both processors operate at the same clock frequency, the Atom cores are much slower as they do not implement all performance boosting techniques of a Xeon core (such as out-of-order processing, aggressive speculation, and instruction transformation).

Figure 3.3: Experiment on hybrid prototype server: Average (a) and 99th percentile (b) service delay for the *count* workload for scheduling threshold  $S_t = 0, 4, 8, 16$ . Note that for  $S_t = 0$  only Xeon is active.

### 3.2 Latency and power model

In this section we present a high-level model for timing and power consumption of a hybrid server. The model is validated with experiments on the prototype and then used to assess achievable energy savings and performance.

#### 3.2.1 Response Latency

The hybrid architecture we consider is a system with two distinct types of elaboration units — a small CPU with low-power cores and a big CPU with highperformance cores — which share a single infrastructure. A scheduler is responsible for the allocation of incoming requests between processors, *i.e.*, it selects a CPU c for each incoming request.

A CPU can run  $T^c$  concurrent execution threads (see Table 3.1). When it is fully loaded (*i.e.*, if  $load = T^c$ ) incoming requests are queued and will start being served as soon as one of the execution units becomes available. The total service delay a request experiences is then the sum of two contributions: *queuing delay* and *execution delay*. For each CPU we only model execution delay since queuing delay directly depends on the requests execution speed and on the arrival process.

For a given workload type, service time is a function of the size of the requested file, of the processor selected by the scheduler and of the number of currently active requests (*load*). The file size determines the number of instructions to run while the instantaneous processor load is an index for the inter-process interference due to competition for shared resources (*i.e.* L2 and L3 caches, shared bus,  $\cdots$ ). Let t be the time a request starts being served and c the CPU that serves the request. The service delay D is computed as

$$D(\text{file}, load, c) = \alpha(c) + \text{size}(\text{file})^{\gamma} \cdot \beta(c, load)$$

(3.1)

$\alpha$  models the time needed to accept a request before starting the execution, and depends only on the type of processor.  $\beta$  accounts for the performance of processor c at a given load and is a workload-dependent coefficient. Given the restricted range of file sizes in the dataset we express the dependency on file size as a power function with exponent  $\gamma$ .

#### 3.2.2 Power Usage

It has been shown that the CPU is the most energy-proportional component in a server system [60], thanks to idle sleep states (C-States) with short transition times and active sleep states (P-States) that trade execution speed for energy. Other components, such as memory, disks and high speed buses either do not implement sleep states or are rarely completely idle, even if underutilized [107]. The trend in server architectures however, is promising due to the progressive integration of memory and I/O controllers on the processor die. This can affect power consumption in two ways. First, the shared bus is replaced by point to point links (*e.g.* Quick-Path Interconnect, QPI) that allow for more fine grained power control. Second, the hardware logic dedicated to interfacing with memory and peripherals directly depends on the CPU power state and can quickly transition to and from deep sleep states.

Without loss of generality, for the purpose of evaluating power consumption we can logically divide the whole system into subsystems each associated to a given CPU. The total power consumption P(t) can be written as

$$P(t) = \sum_{c} P^{c}(t),$$

where  $P^{c}(t)$  is the power consumption of the subsystem associated to CPU *c*. Each subsystem can be in three different energy states: *active*, *sleep* and *transition*, depending on the state of the corresponding CPU.

Let us consider the subsystem associated to CPU c: its instantaneous power consumption,  $P^c(t)$ , is a function of the state:  $P^c_{\text{sleep}}$  is the power consumption of the CPU in sleep state. During transition between active and sleep state, power consumption is approximated by  $P^c_{idle}$ , power dissipation when the CPU is idle. Finally, when CPU is active, power is proportional to the instantaneous processor load  $L^c$ :

$$P^{c}(t) = P^{c}_{idle} + \frac{P^{c}_{max} - P^{c}_{idle}}{T^{c}} \cdot L^{c}(t), \qquad (3.2)$$

where  $P_{max}^c$  is power consumption at 100% utilization.

#### 3.2.3 Model validation

The model has been implemented in an event-driven simulator using the *simpy* [37] framework and has been tested against experimental data. Traces from experiments in Section 3.1.3 are used as input to the simulator in order to replicate the request arrival pattern.

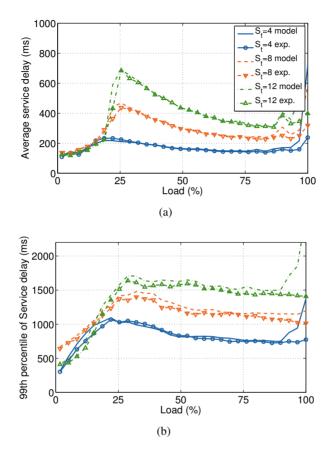

Figure 3.4: Comparison between simulation and experiments for average (a) and 99th percentile (b) of service delay.

Values of the model coefficients have been experimentally measured using the test bench presented in Section 3.1.2 and instructing the request generator to issue a fixed number N of simultaneous requests. For each  $N \leq T^c$  requests are immediately executed and no queuing occurs. We generated random requests across the whole dataset spectrum and measured the execution delay of each request. For each CPU and load level we compute model parameters  $\alpha$  and  $\beta$ , introduced in Section 3.2.1, using Equation 3.1 to fit the experimental data. In our case we obtain a good fit with a linear function, *i.e.*, for  $\gamma = 1$ .

Figure 3.4 shows the request service delay, average (left) and 99th percentile (right) for the *count* workload. Lines with symbols represent experimental data,

simple lines simulation results. As can be seen, despite its simplicity, our model correctly replicates the behavior of the real system with a delay peak in correspondence of slow cores saturation and a performance speedup as soon as the scheduler starts allocating requests to fast cores. The error introduced by the model is within few percentage points even for the 99th percentile, which is harder to replicate than the average.

We validate our assumption by showing that the model correctly predicts the system behavior for different values of the scheduler threshold  $S_t(4, 8, 12)$ . The threshold indeed only affects queuing delay on small cores. For example when the threshold is set to the number of small cores (*i.e.*,  $S_t = T$ ) there are no pending requests and queuing delay is null on small cores.

## **3.3** Evaluating hybrid server design

Based on the model described in the previous section, we assess power consumption of hybrid multicore architectures as a function of load and evaluate achievable energy savings and performance.

As mentioned, our prototype would not be adequate to achieve significant energy saving, because idle power is too high and Xeon performance is intentionally suppressed for the sake of interoperability.

To evaluate achievable power consumption for an optimized board, we measured power consumption of an AtomN450 netbook, which exhibited the same 10 W dynamic range as the Atom 330 but lower idle power. It consumes 12.1 W with no load and 20.4 W at maximum load. Then, we consider a fully performing Xeon as large CPU, with power at peak of 320 W.

We also assume that the subsystem associated to the large CPU can be turned to a low-power standby mode in low-load time intervals, and is awakened by the scheduler only when needed.

Reasonably, the power consumed in a sleep state can be expressed as a fraction of  $P_{idle}$ . In the following we consider two cases,  $P_s = 0$  and  $P_s = 0.25 \cdot P_{idle}$ . The first is an ideal case and is used, coupled with a zero transition time, to consider an ideal optimistic situation, whereas the second case is very conservative, and should represent a pessimistic case. Coordinated sleep states among components cannot be as fast as CPU sleep states (C-states) which have transition latencies in the order of microseconds. For this reason we consider transition times  $t_t$  up to tens of milliseconds.

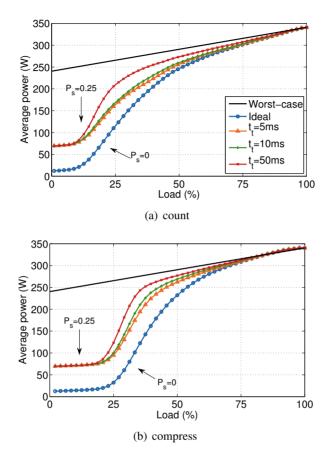

Figure 3.5: Average power consumption vs. system load for the *Count* (a), and *Compress* (b) workloads.

Figure 3.5 shows the average power consumption over the entire load range for the *count* 3.5(a) and the *compress* 3.5(b) workload.

The thick straight line represents the worst-case scenario, *i.e.*, a system that consumes the sum of idle power for the two subsystems at idle and the sum of peak power at maximum. Different transition times  $t_t$  are considered, corresponding to  $t_t = 5, 10, 50$  ms.

Note how all the solutions presented exhibit good energy proportionality, compared to the worst case, thanks to the low energy of the small CPU subsystem and to efficient sleep states of the large CPU subsystem. When the load increases above 70% all the power curves converge towards the worst case scenario. This is due to

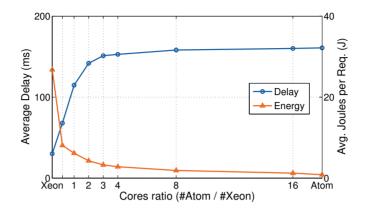

Figure 3.6: Average delay and average energy cost per request for different small to big cores ratio.

the lack of idle periods that the big CPU can exploit to undergo the transition to a sleep state.

The real advantage, in energy terms, is due to the fact that a typical server only spend a small fraction of time in high load region and has a low load for most of the time. In our solution power dissipation is small at low load, when only the small CPU subsystem is active. This come at the price of increased latency in servicing requests as we have shown in the previous section.

To better understand the latency vs. energy savings trade-off we can use our service delay model of Section 3.2 to evaluate several what-if scenarios. In particular the model allows us to explore the design space across two dimensions: i) the ratio of small to big cores, and ii) the relative performance of small to big cores.

Along the first dimension, as the number of small cores increases, more requests will be served by small cores and the overall average service delay will be larger. On the other hand, energy usage will be lower because high power big cores can be idle longer.

Figure 3.6 shows the average service delay and average energy spent per request as a function of the ratio of number of Atom cores to Xeon cores. To derive this figure we used as input a request load that mirrors the utilization distribution reported in [60] for Google's datacenters. From the figure a designer can pick a desired average service latency (or energy per request) and obtain the best number of Atom cores to reach that performance. Furthermore, the model shows at what point adding more Atom cores has little impact on latency or energy usage. This is expected as for those ratios, all requests are always served by the Atom cores and the Xeon cores stay always idle. The actual value is workload-dependent (a ratio of 8 in our case) and datacenter operators can estimate the load of requests and choose the best operating point accordingly.

The second dimension, the relative performance of cores, allows us to understand the impact of technology advances. Given the size and growth prospects of today's mobile and tablet markets, a significant development effort is dedicated to improve the performance of small low-power cores. 3.7(a) and 3.7(b) plot the average response delay and energy per request as a function of the "Atom speedup", *i.e.*, as we vary the performance of the Atom cores while keeping the Xeon cores the same. We also scale power usage linearly with performance in keeping with Atom's design constraint for which a feature is implemented only if it provides a "1% performance increase for less than 1% power increase" [61]. The workload is the same as before and follows the utilization distribution similar to [60].

Each line in the plots corresponds to a ratio of Atom vs. Xeon cores from one to four. The figures show two interesting trends. As the Atom performance drops below 0.5 of the current performance, there is very little energy advantage in using more Atom cores. This is because the processing time of the Atom cores is so large that more incoming requests need to be handled by the Xeon. As a consequence, Xeon cores have very few opportunities to transition to an idle state. At the other side of the spectrum, as the performance of the Atom cores increases adding more small cores has little impact on the response delay but helps in reducing energy per request significantly. If Atom cores were twice as fast as the cores in our hybrid prototype, the energy per request could be almost halved incurring a negligible service delay penalty.

Figure 3.7: Average delay (a) and average energy cost per request (b) for different slow-core performance (speedup is normalized to the performance of current Atom available on the market)

## 3.4 Related Work

The idea of hybrid or heterogeneous architectures is not new. At the datacenter level, several proposals have been put forward in the literature to include arrays of low-power systems next to high performance ones [36,53,81,96] that could handle low-load scenarios or specific I/O-intensive workloads. These proposals however require changing the way datacenters are designed and maintained and have seen little adoption by datacenters operators. Further, developers need to refactor their code to accomodate for the two different architectures that present very different memory and I/O bandwidth constraints. Hybrid systems that share the same memory banks and I/O subsystems enable the same codebase to achieve high single-thread performance when required and otherwise keep power consumption low.

At the system or processor level, asymmetric multicore processors (AMPs)

have been proposed as natural successors of chip multi-processors (CMPs) since they can provide energy efficiency in the execution of parallel threads, due to a large number of small cores, while improving performance of sequential phases through big cores. A large body of work in this field addresses the problem at the single-chip level [54, 85, 97, 98, 125] through theoretical analysis and simulations using synthetic workloads. We base our analysis on a real prototype akin to the one used by Reddy *et al.* [114]. Access to a working system allows for actual experimentation with real workloads as opposed to previous works that use FPGAsynthesized CPUs [124] or symmetric multiprocessors (SMP) architectures with cores tuned to work at different frequencies [57, 100].

## Chapter 4

# **Energy-proportional Router**

The network infrastructure is often viewed as an attractive target for energy-efficient design since routers are provisioned for peak loads but operate at low average utilization levels - e.g., studies report network utilization levels of <5% in enterprises [109], 30-40% in large ISPs [75], and a 5x variability in ADSL networks [104]. At the same time, network equipment is notoriously inefficient at low load - e.g., a survey of network devices [65, 103] reveals that the power consumed when a router is not forwarding *any* packets is between 80-90% of its peak power consumed when processing packets at full line rate. Thus although in theory networks offer significant opportunity for energy efficiencies, these savings are rarely realized in practice.

This inefficiency is increasingly problematic as traffic volumes continue their rapid growth and has led to growing attention in both research and industry [7, 16, 65, 75, 84, 103, 104, 109]. In anecdotal evidence: discussions with a major ISP revealed that infrastructure power consumption represents their second largest monthly recurring cost (second only to labor)<sup>1</sup> and we see calls for research on the topic from router vendors [8].

To date however, there have been no published reports on attempts to actually build an energy-efficient router. Motivated by this deficiency, we thus tackle the question of how one might build such an energy-efficient router.

The traditional challenge in building an energy efficient system lies in the inherent tradeoff between energy consumption and various performance metrics—in our case, forwarding rate and latency. We cannot compromise on peak forwarding

<sup>&</sup>lt;sup>1</sup>Private commn. Stuart Elby, VP of Network Architecture, Verizon.

rates since the incoming traffic rate is dictated by factors external to a given router (and since we do not want to modify routing protocols). We can however explore options that tradeoff latency for improved efficiency. The ability to do so requires: (1) that the underlying hardware expose primitives for low-power operation and (2) higher-level algorithms that invoke these primitives to best effect. Our work focuses on developing these higher-layer algorithms, and we do so in the context of general-purpose server hardware.

General-purpose hardware typically offers system designers three 'knobs' for low-power operation: (i) regulate the frequency (and hence power consumption) at which individual CPU cores process work, (ii) put an idle core into a 'sleep' state (powering down sub-components of the idle core) (iii) consolidate packet processing onto fewer cores (adjusting the number of active cores).

As we shall see, not only do each of the above offer very different performancevs-power tradeoffs, they also lend themselves to very different strategies in terms of the power management algorithms we must develop. For example, sleep-mode savings are best exploited by maximizing idle times which implies processing work as quickly as possible, while frequency-scaling is best exploited by processing work as slowly as possible which reduces idle times.

The question of how to best combine the above hardware options is, to our knowledge, still an area of active research for most application contexts and is entirely uncharted territory for networking applications. We thus start by studying the energy savings enabled by different hardware options, for different traffic workloads. Building on this understanding, we develop a unified power management algorithm that invokes different options as appropriate, dynamically adapting to load for optimal savings. We implement this algorithm in a Click software router [94] and demonstrate that its power consumption scales in proportion to the input traffic rate while introducing little latency overhead. For real-world traffic traces, our prototype records a 50% reduction in power consumption, with no additional packet drops, and only a small (less than 10  $\mu$ s) cost in packet forwarding latency. To our knowledge, this is the first demonstration of an energy-efficient router prototype.

Before proceeding, we elaborate on our choice of general-purpose hardware as prototyping platform and how this impacts the applicability of our work. To some extent, our choice is borne of necessity: to our knowledge, current network hardware does not offer low-power modes of operation (or, at least, none exposed to third-party developers); in contrast, server hardware does incorporate such support, with standard software interfaces and support in all major operating systems. That said, current network equipment may employ very different hardware options and hence we expand more concretely on the applicability of our work to each:

- Our work applies directly to software routers built on commodity x86 hardware, an area of growing interest in recent research [55, 74, 86, 102] with commercial adoption in the lower-end router market [43].

- Network appliances load-balancers, WAN optimizers, firewalls, IDS, *etc.* commonly rely on x86 hardware [5, 32] and these form an increasingly important component of the network infrastructure *e.g.*, a recent paper [119] revealed that an enterprise network of ~ 900 routers deployed over 600 appliances! Our work is likewise directly applicable to such appliances.

- Commercial routers typically rely on network processors (NPs) rather than generalpurpose ones. While the specifics of our results may not apply directly to NPs, we expect that the overall methodology by which we compare and combine different power options will be of relevance. This is because the power modes that x86 hardware offers reflect fundamental technology options – turning cores on/off, frequency and voltage scaling, clock gating, *etc.* – and hence it is likely that NP designers will pursue similar approaches.<sup>2</sup>

- Many routers rely on specialized ASICs, particularly for simple low-level tasks such as checksum calculations; it is unclear what form of power modes ASICs will evolve to offer and hence we conservatively assume our work does not apply to these.

- Finally, we note a growing trend towards equipment that *augments* the traditional ASIC and NP-based platform with general-purpose CPUs in the form of 'beefed up' control planes (*e.g.*, Arista Networks), as one of multiple heterogeneous dataplane engines (*e.g.*, Cavium) or as 'service blades' on the data-plane (*e.g.*, Cisco's Application eXtension Platform [6]).

More generally, we believe our results can positively influence the hardware support for power management that emerges in specialized NPs and ASICs by demonstrating: what magnitude of energy savings are possible using basic hardware primitives; what performance tradeoff comes with these savings; and which of the feasible kinds of hardware primitives maximize benefits.

<sup>&</sup>lt;sup>2</sup>NPs, like modern multi-core systems, use a large number of computation cores/engines executing network software in parallel [40].

The remainder of this chapter is organized as follows. We start with a review of the power consuption of current software routers (Section 4.1). We continue with techniques to reduce power by eliminating software inefficiencies (Section 4.2) and then study the tradeoffs between different power management options (Section 4.3). We present the design and implementation of our unified power management algorithm in Section 4.4 and the evaluation of our prototype in Section 4.5. We finish with an overview of related work.

## 4.1 Deconstructing Power Usage

A necessary step before attempting the design of a power proportional router is to understand the contribution of each server component to the overall power usage.

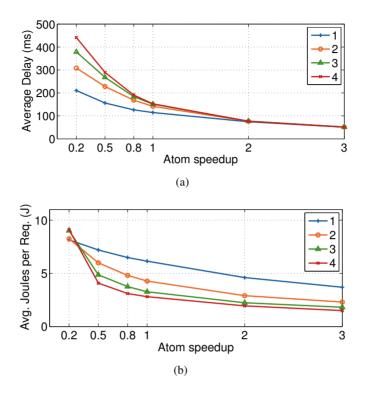

#### 4.1.1 Server architecture

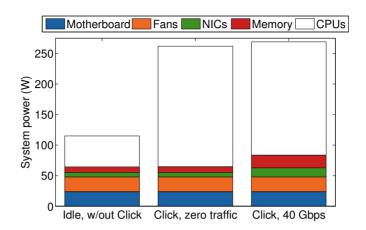

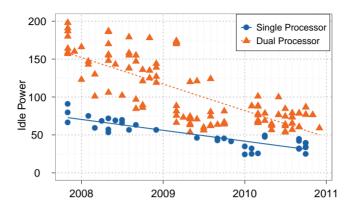

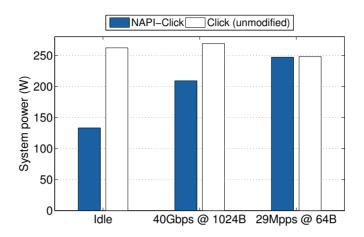

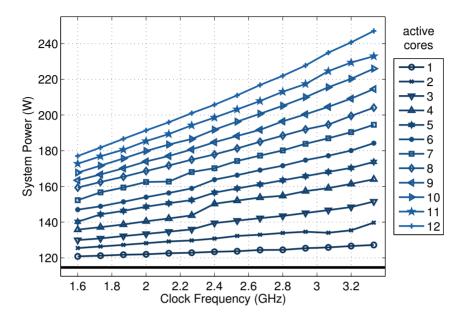

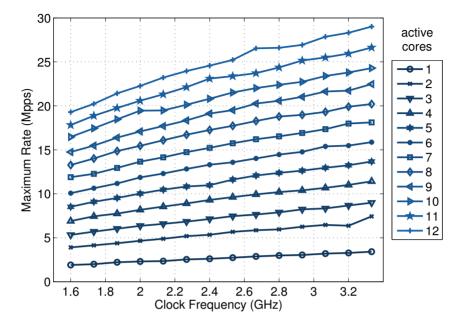

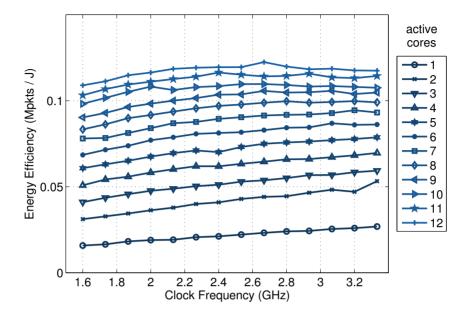

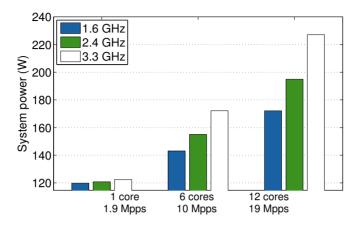

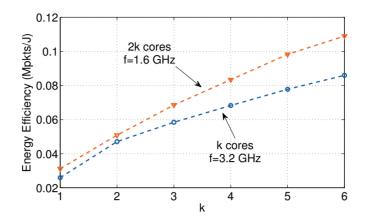

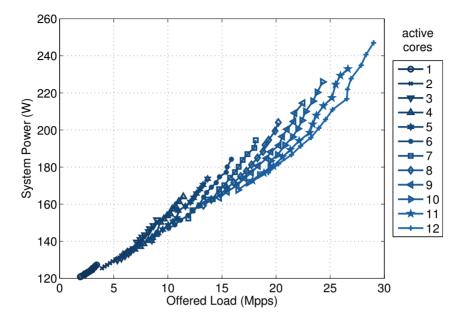

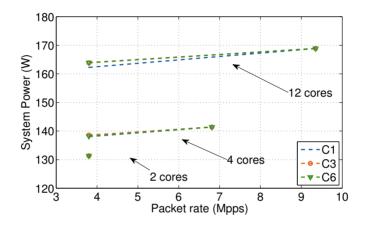

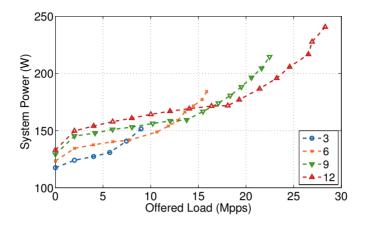

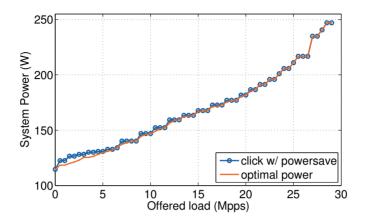

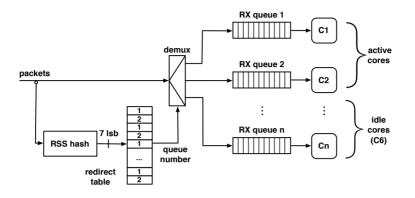

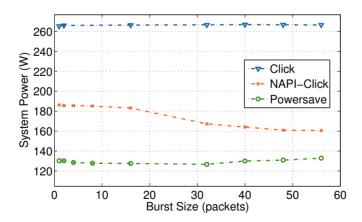

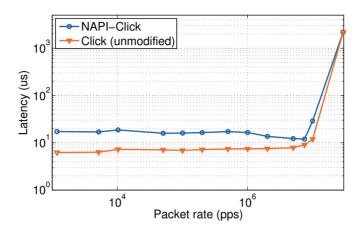

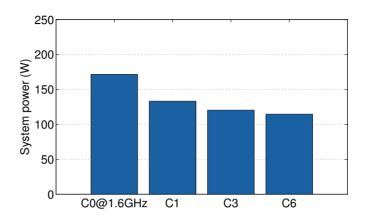

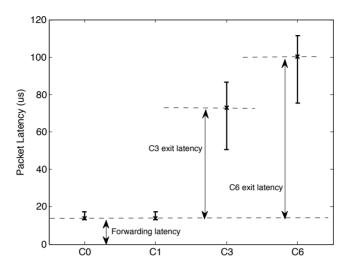

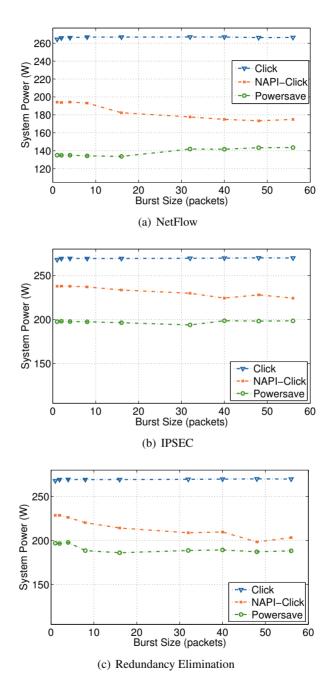

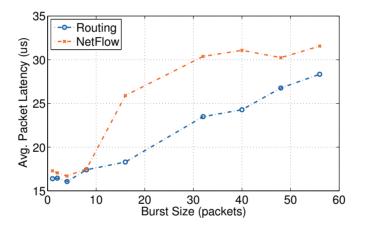

For our study, we chose an off-the-shelf server based on the Intel Xeon processor that is commonly used in datacenter and enterprise environments. The overall architecture is similar to that in servers from other manufacturers. Figure 4.1 shows a simplified diagram of the components that make up the server: our server has two CPU processors each of which consists of six cores packaged onto a single die along with several "uncore" components (L3 caches, memory controllers, power control unit, *etc.*).