# University of Pisa and Scuola Superiore Sant'Anna

Master Degree in Computer Science and Networking Laurea Magistrale in Informatica e Networking

Master Thesis

# Cost Models for Structured Parallel Programming on Shared Memory Architectures

Candidate

Alberto Bandettini

Supervisor

Prof. Marco Vanneschi

Academic Year 2010/2011

ii

# Ringraziamenti

Il ciclo universitario sta volgendo al termine e, come doveroso, è giusto ringraziare chi, nel corso di questi anni, mi è stato vicino e ha permesso tutto questo.

In primis quindi vorrei ringraziare Fabio, con cui ho affrontato buona parte delle difficoltà incontrate in questi ultimi due anni e, cosa non da poco, gli innumerevoli viaggi da Lucca. Detto chiaro: "Leporini, è fatta!"

Un altro sentito grazie va a Daniele Buono che ha sottratto tempo utile al suo lavoro per offrire il suo supporto (e il suo simulatore) allo studio effettuato per la tesi.

Voglio poi ringraziare il Prof. Vanneschi, che è stato un fondamentale punto di riferimento durante la mia vita universitaria.

E poi, ovviamente, tutta la mia famiglia che, da una parte, mi ha sempre incitato a non mollare e, dall'altra, ha sopperito a qualsiasi esigenza. Un enorme grazie va quindi a mio padre Guido e mia madre Emanuela, a Claudia, Matteo, Gemma, Roberto e Elena. Spero vivamente che la gioia del successo ripaghi anche solo in parte i sacrifici fatti.

Un caloroso grazie va anche a tutti gli amici di università che hanno riempito le mie giornate con battute e scherzi rendendo questo percorso a ostacoli molto, ma molto, meno arduo. Credetemi! Un grazie quindi (rullo di tamburi) ad Andrea Lottarini (in arte Gufetto) e al nostro mitico BitCreekPeer che non va scordato, al sindacalista Tiziano De Matteis ("bon per te Tizi"), a Andrea Bozzi (Ingegner Umberto Boszi che sta sempre in vacanza), ad Alessio Pascucci che ogni lunedì mattina ascolta con attenzione le mie prodezze calcistiche (Pascu sarà bene stampare anche questa settimana la classifica capocannonieri), a Luiggi, il Menca (forza Juve, siamo forti quest'anno), il sardo Vespa e Daniele Virgilio (anno 1.5 di MCSN) che, dato le sue doti di scrittura, di Virgilio ha solo il nome. E ancora, Andrea Farruggia con il suo flebile tono di voce, Matteo Fulgeri (detto anche FullGay) e la sua compagna Federica Bertozzi che, a breve, si metteranno insieme perché fatti l'uno per l'altra anche se per ora non se ne sono resi conto. Anna, Paolo, Emilio (o Miglio), Nebbia, Manuel e chi più ne ha più ne metta. Anche gli altri del corso come Filippo, Davide, il gazzettino Angela, Emnet, o meglio i suoi capelli, che dopo MOD è in grado di leggere questa pagina, la Martinelli con le sue torte, il Giuliani, la fisica Francesca *and so on* senza scordarsi nessuno.

GRAZIE!

iv

# Contents

| Intr                                     | roducti                                                                         | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                         |  |  |

|------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Sha                                      | red M                                                                           | emory Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                         |  |  |

| 2.1 Processing Nodes                     |                                                                                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           |  |  |

| -                                        |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |  |  |

|                                          | 2.2.1                                                                           | Base Latency in Networks with Wormhole Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                        |  |  |

|                                          | 2.2.2                                                                           | Base Latency in Time-Slot Networks on chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                        |  |  |

|                                          | 2.2.3                                                                           | Direct and Indirect Interconnection Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18                                                        |  |  |

| 2.3 Shared Memory                        |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |  |  |

|                                          | 2.3.1                                                                           | UMA and NUMA Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22                                                        |  |  |

|                                          | 2.3.2                                                                           | Base and Under-Load Memory Access Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24                                                        |  |  |

|                                          |                                                                                 | ronization and Cache Coherence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24                                                        |  |  |

| 2.5 Cost Model and Abstract Architecture |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |  |  |

|                                          |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |  |  |

| Que                                      | eueing                                                                          | Theory Concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                        |  |  |

| <b>Que</b><br>3.1                        | -                                                                               | Theory Concepts<br>ption and Characterization of a Queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>31</b><br>31                                           |  |  |

| -                                        | Descri                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                           |  |  |

| 3.1                                      | Descri                                                                          | ption and Characterization of a Queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31                                                        |  |  |

| 3.1                                      | Descri<br>Notab                                                                 | ption and Characterization of a Queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31<br>34                                                  |  |  |

| 3.1                                      | Descri<br>Notab<br>3.2.1<br>3.2.2                                               | ption and Characterization of a Queue $\dots \dots \dots \dots$<br>ly important Queues $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31<br>34<br>34                                            |  |  |

| 3.1<br>3.2<br>3.3                        | Descri<br>Notab<br>3.2.1<br>3.2.2<br>Netwo                                      | ption and Characterization of a Queue $\dots \dots \dots \dots \dots$<br>ly important Queues $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31<br>34<br>34<br>35                                      |  |  |

| 3.1<br>3.2<br>3.3                        | Descri<br>Notab<br>3.2.1<br>3.2.2<br>Netwo                                      | ption and Characterization of a Queue $\dots \dots \dots \dots \dots$<br>ly important Queues $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31<br>34<br>34<br>35<br>35                                |  |  |

| 3.1<br>3.2<br>3.3<br>Cos                 | Descri<br>Notab<br>3.2.1<br>3.2.2<br>Netwo                                      | ption and Characterization of a Queue $\dots$ $\dots$ $\dots$ ption and Characterization of a Queue $\dots$ $\dots$ provide $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31<br>34<br>34<br>35<br>35<br><b>39</b>                   |  |  |

| 3.1<br>3.2<br>3.3<br>Cos                 | Descri<br>Notab<br>3.2.1<br>3.2.2<br>Netwo<br>t Mod<br>Proces                   | ption and Characterization of a Queue $\dots$ $\dots$ $\dots$ ly important Queues $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31<br>34<br>34<br>35<br>35<br>35<br><b>39</b><br>40<br>40 |  |  |

| 3.1<br>3.2<br>3.3<br>Cos                 | Descri<br>Notab<br>3.2.1<br>3.2.2<br>Netwo<br>t Mod<br>Proces<br>4.1.1<br>4.1.2 | ption and Characterization of a Queue $\dots \dots \dots \dots$<br>ly important Queues $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$<br>The $M/M/1$ Queue $\dots \dots \dots$<br>The $M/G/1$ Queue $\dots \dots \dots$<br>rks of Queues $\dots \dots \dots$<br>els for Shared Memory Architectures<br>ssors-Memory System as Closed Queueing Network $\dots \dots$<br>Formalization of the Model $\dots \dots \dots \dots \dots \dots \dots \dots$ | 31<br>34<br>35<br>35<br>35<br><b>39</b><br>40<br>40<br>42 |  |  |

|                                          | <ul> <li>Sha</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ul>     | Shared Me         2.1       Process         2.2       Interce         2.2.1       2.2.1         2.2.2       2.2.3         2.3       Shared         2.3.1       2.3.2         2.4       Synchr                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>2.2 Interconnection Structures</li></ul>         |  |  |

|          |                                                           | 4.2.1                                                                              | Formalization of the Model                                                                      | 44  |  |  |  |  |  |

|----------|-----------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

|          |                                                           | 4.2.2                                                                              | Assumptions                                                                                     | 46  |  |  |  |  |  |

|          |                                                           | 4.2.3                                                                              | Model Resolution                                                                                | 49  |  |  |  |  |  |

|          | 4.3                                                       | A vari                                                                             | iant of the Client-Server Model: Heterogeneous Clients .                                        | 51  |  |  |  |  |  |

|          |                                                           | 4.3.1                                                                              | Definition                                                                                      | 52  |  |  |  |  |  |

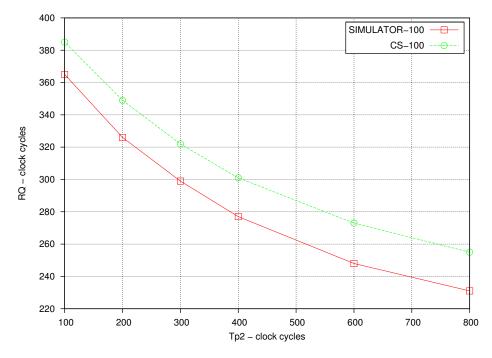

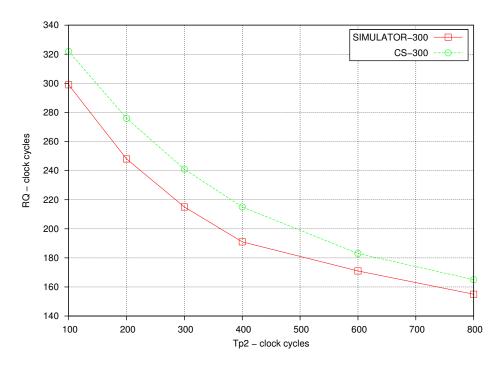

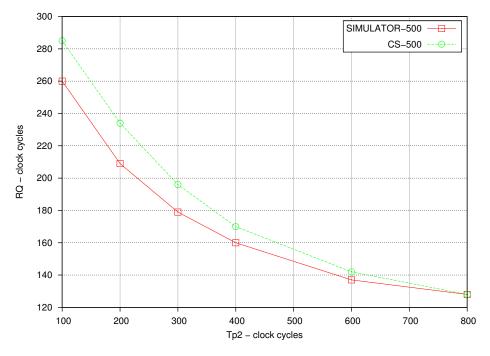

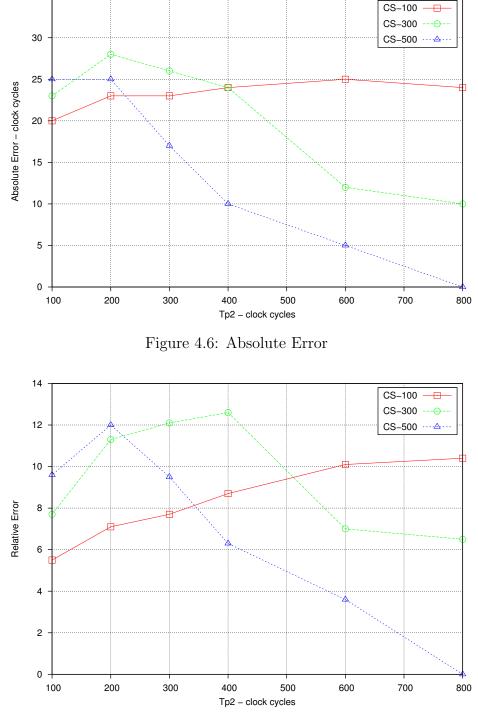

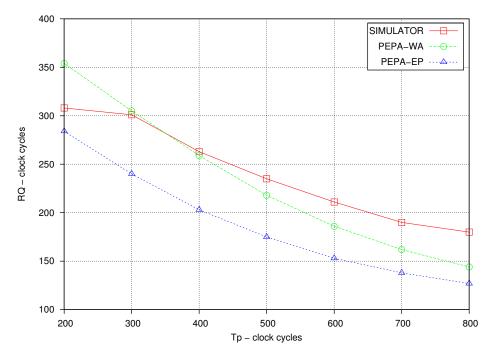

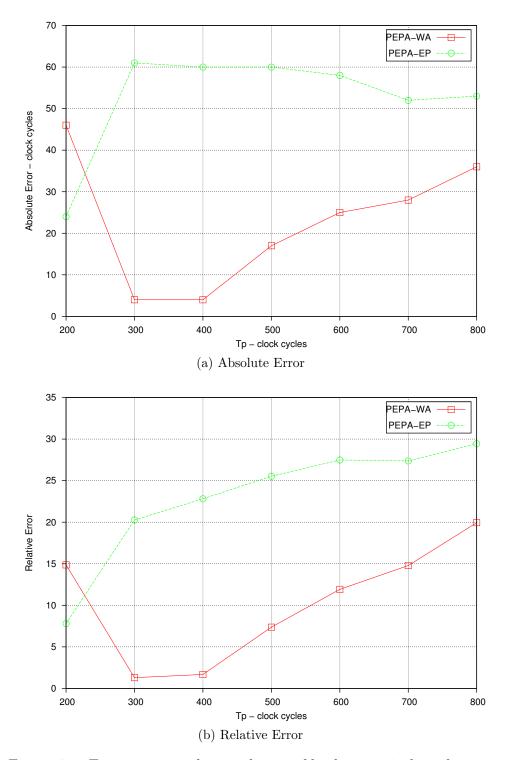

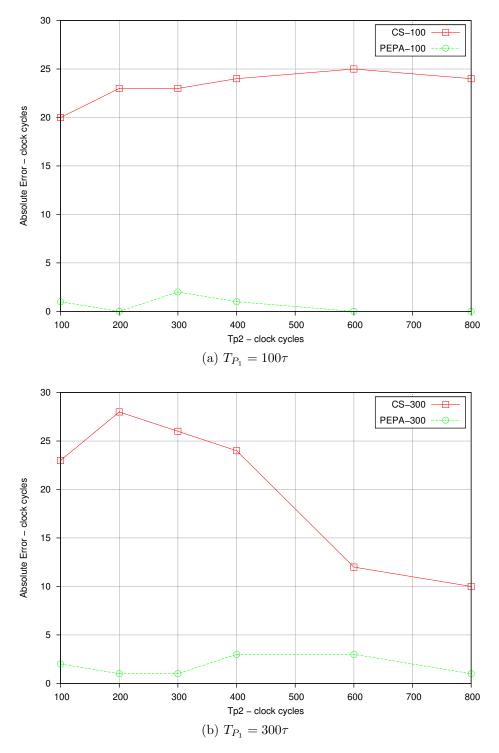

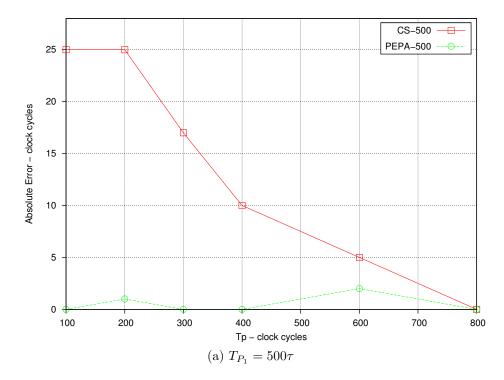

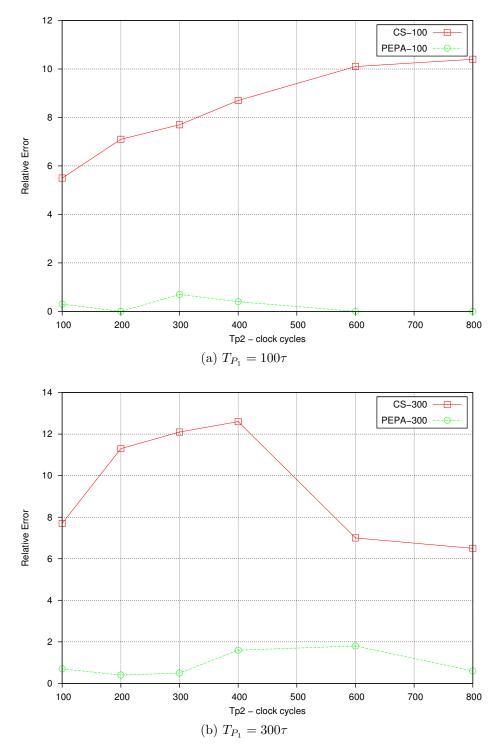

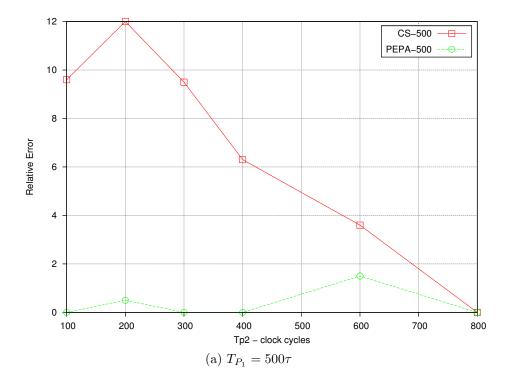

|          |                                                           | 4.3.2                                                                              | Comparison against the Queuing Network Simulator .                                              | 52  |  |  |  |  |  |

|          |                                                           | 4.3.3                                                                              | Comments                                                                                        | 58  |  |  |  |  |  |

|          | 4.4                                                       | Concl                                                                              | usions                                                                                          | 59  |  |  |  |  |  |

| <b>5</b> | Stochastic Process Algebra Formalization of Client-Server |                                                                                    |                                                                                                 |     |  |  |  |  |  |

|          | Mo                                                        | del                                                                                |                                                                                                 | 61  |  |  |  |  |  |

|          | 5.1                                                       | PEPA                                                                               | a: a Process Algebra for Quantitative Analysis                                                  | 63  |  |  |  |  |  |

|          | 5.2                                                       |                                                                                    | PA Formalism for Client-Server Model with Request-                                              |     |  |  |  |  |  |

|          |                                                           | Reply                                                                              | Behaviour                                                                                       | 68  |  |  |  |  |  |

|          |                                                           | 5.2.1                                                                              |                                                                                                 | 68  |  |  |  |  |  |

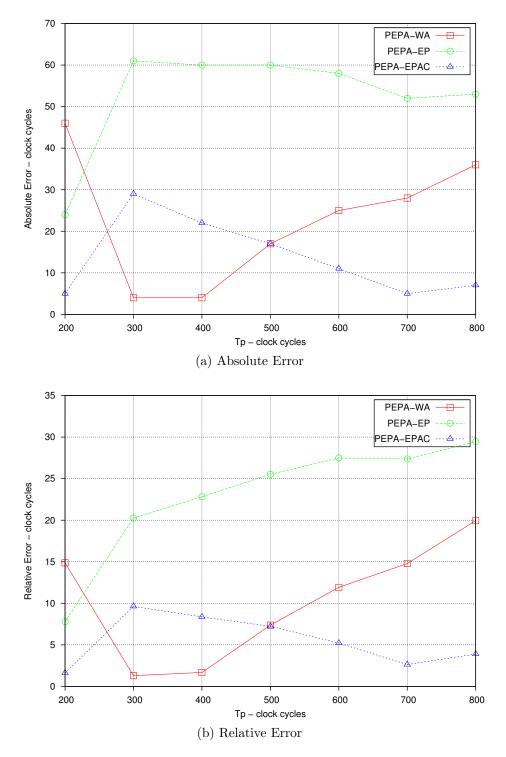

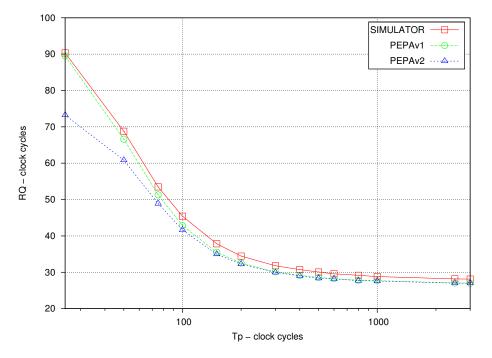

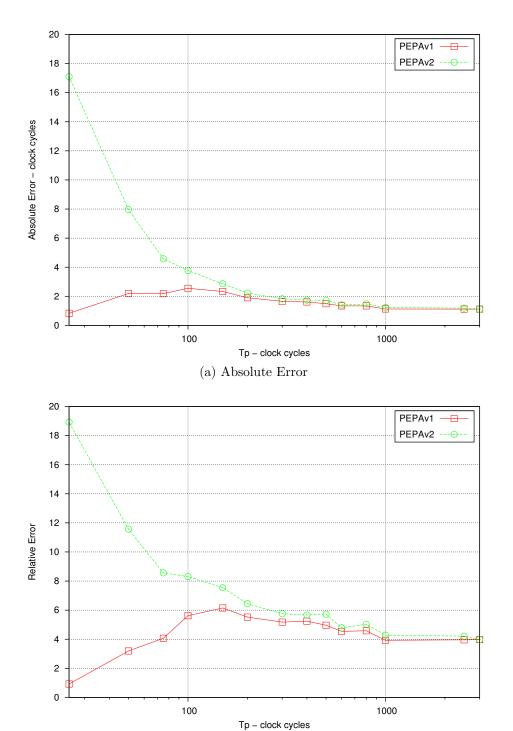

|          |                                                           | 5.2.2                                                                              | Quantitative Comparison with respect to other Reso-                                             |     |  |  |  |  |  |

|          |                                                           |                                                                                    | lution Techniques                                                                               | 70  |  |  |  |  |  |

|          | 5.3                                                       | Concl                                                                              | usion $\ldots$ | 74  |  |  |  |  |  |

| 6        | Adv                                                       | vanced                                                                             | Cost Models: impact of the Parallel Application                                                 | 75  |  |  |  |  |  |

|          | 6.1                                                       | Proce                                                                              | sses Classes and Processes Phases                                                               | 76  |  |  |  |  |  |

|          |                                                           | 6.1.1                                                                              | Classes of Processes                                                                            | 77  |  |  |  |  |  |

|          |                                                           | 6.1.2                                                                              | Process Phases                                                                                  | 79  |  |  |  |  |  |

|          | 6.2                                                       | How to deal with more Phases $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |                                                                                                 |     |  |  |  |  |  |

|          | 6.3                                                       | Proce                                                                              | ss Phases Modelling                                                                             | 82  |  |  |  |  |  |

|          |                                                           | 6.3.1                                                                              | Phases by mean of Weighted Average Value                                                        | 83  |  |  |  |  |  |

|          |                                                           | 6.3.2                                                                              | Explicit Phases                                                                                 | 86  |  |  |  |  |  |

|          |                                                           | 6.3.3                                                                              | Phases by means of Average Clients                                                              | 91  |  |  |  |  |  |

|          |                                                           | 6.3.4                                                                              | Explicit Phases with Average Clients                                                            | 92  |  |  |  |  |  |

|          |                                                           | 6.3.5                                                                              | Comments                                                                                        | 96  |  |  |  |  |  |

|          | 6.4                                                       | Heter                                                                              | ogeneous Clients in PEPA                                                                        | 96  |  |  |  |  |  |

|          |                                                           | 6.4.1                                                                              | Definition                                                                                      | 97  |  |  |  |  |  |

|          |                                                           | 6.4.2                                                                              | Quantitative Comparison with respect to other Reso-                                             |     |  |  |  |  |  |

|          |                                                           |                                                                                    | lution Techniques                                                                               | 98  |  |  |  |  |  |

|          | 6.5                                                       | Concl                                                                              | usion                                                                                           | 106 |  |  |  |  |  |

## ${\rm Contents} \quad {\bf vii}$

| <b>7</b> | Adv                         | vanced | Cost Models: Hierarchical Shared Memory            | 107      |

|----------|-----------------------------|--------|----------------------------------------------------|----------|

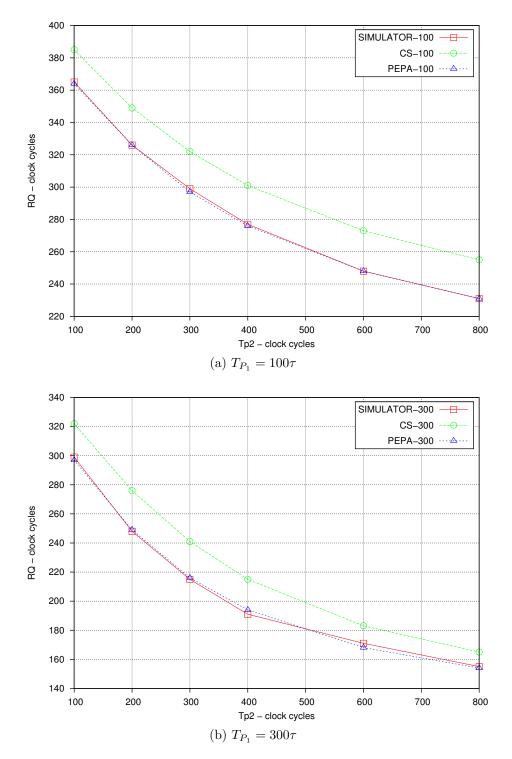

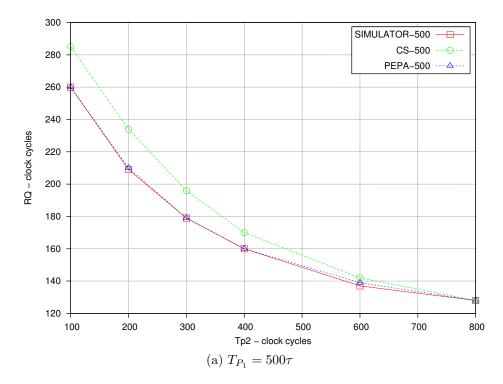

|          | 7.1                         | Hierar | chical Client-Server Model with Request-Reply Beha | viour107 |

|          |                             | 7.1.1  | Definition                                         | 111      |

|          |                             | 7.1.2  | Quantitative Comparison against the Simulation .   | 115      |

|          | 7.2                         | Conclu | usion                                              | 120      |

| 8        | Conclusion and Future Works |        |                                                    |          |

| Re       | efere                       | nces   |                                                    | 124      |

viii CONTENTS

# Chapter 1 Introduction

The *High Performance Computing* (HPC) field studies the hardware-software interaction and applications characterized by requirements for high processing bandwidth, low response time, high efficiency and scalability.

Currently, *multiprocessors* and *multi-cores* are an important evolution/revolution from the technological point of view. These architectures are very complex and heterogeneous systems with parallelism exploited at processes level. The trend in multi-cores architectures seems that the number of cores per chip is expected to double every two years. The idea is to substitute few complex and power-consuming CPUs with many smaller and simpler CPUs that can deliver better performance per watt. An important role is played by high bandwidth and low latency interconnection structures with limited degree (especially on-chip) while shared memory starts to be organized in hierarchies.

All this aspects have enormous implications from the software point of view. We point out that these architectures can be exploited efficiently provided that applications are able to do it. In spite of this relevant architectural change, the actual programming tools are at very low-level for a programmer without profound knowledge in the HPC field. Further, performance prediction and/or performance portability is missing or it is still in an initial phase. Summarizing, a wide gap still exists between shared memory architectures and parallel programming development tolls.

We advocate that a structured and methodological approach is able to reach this targets by mean of *structured parallelism programming* (or *skeleton* based parallel programming) in which a limited set of paradigms aims

#### 2 Introduction

to provide standard and effective rules for composing parallel computations in a machine independent manner. The programmers have to use paradigms to realize the parallel application. The freedom of the programmer is limited but if paradigms allow composition, parametrization and ad-hoc parallelism, they become very easy to use from the programmer point of view and very useful to optimize from the compiler point of view. In fact, having a fixed set of paradigms the compiler has to "reason" completely on them inserting optimizations that could be platform-dependent or choosing the best implementation for the underlying architecture. All this means performance improvement without direct intervention of programmers.

This important target is both application and architecture dependent and could be accomplished by a *performance cost model* in association with a simplified view of the concrete architecture, i.e. the so called *abstract architecture* [20]. Considering that, a parallel compiler must be supplied of

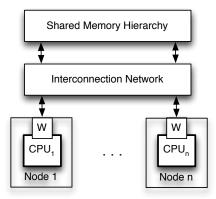

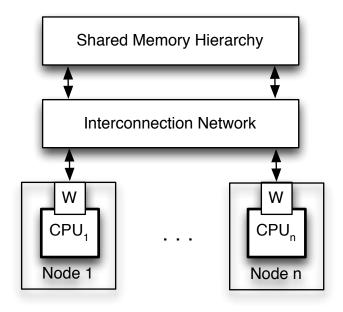

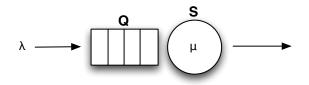

- an **abstract architecture**, that is a simplified view of the concrete architecture able to describe the essential performance properties and abstract from all the others that are useless. It aims to throw away details belonging to different concrete architectures and emphasizes all the most important and general ones. An abstract architecture for shared memory architectures could be the one in Figure 1.1 wherein there exist many processing nodes as processes and the interconnection structure is fully interconnected.

- a **cost model** associated to the abstract architecture. This cost model have to sum up all the features of the concrete architecture, the interprocess communication run-time support and the impact of the parallel application. Further, we strongly advocated that a cost model should be easy to use and conceptually simple to understand.

We remark that a complete and accurate cost model for these architectures is still missing and the aim of this thesis is just to give a contribution in this direction. We want to study how a detailed shared memory architecturedependent cost model for parallel applications can be realized with particular care about the impact of the parallel application.

The aim is to use cost models in the compiler technology in order to statically performs optimizations for parallel applications in the same way

Figure 1.1: Simplified view of Shared Memory Architecture

that nowadays compilers do for sequential code. This should allow programmers to write in an easier way, i.e. using high-level and user-friendly tools, parallel applications that exploit the underlying architecture as well because compilers are able either to choose the right implementation or to use lowlevel libraries, that are very important for the performance point of view. Further, performance portability should be maintained among different concrete architectures. To our knowledge, there is no other work moving in this specific direction a part our main source of reference [20].

At processes level a parallel application can be viewed as a collection of cooperating processes via message passing. Formally, it is a graph wherein nodes are processes and arcs are communication channels among processes. This graph can be the result of a first compilation phase totally architecture independent and successively it can be easily mapped onto the abstract architecture for shared memory architecture because it has the same topology. All the outstanding concrete features are captured in two functions called  $T_{send}$  and  $T_{calc}$ . These functions are evaluated taking into account several characteristics of the concrete architecture, e.g. interconnection structure, processing node, memory access latency and so on. At this point, the parallel compiler has all the elements to introduce the architecture dependency according to the cost model. As already told, this way to operate allows optimizations or choices among various implementations in such a way performance predictability and/or portability can be achieved.

Anyway, the idea to sum up all the salient features of a concrete archi-

#### 4 Introduction

tecture in only two functions is, on one side, very powerful and easy to use but, on the other side, it is not a quite simple derivation.

In shared memory architectures various kind of resources are shared, e.g. memory modules and interconnection structures. The shared memory characteristic has, at the same time, pros and cons. On an hand it allows an easy way to design *run-time support* for interprocess communication, i.e. the implementation of *send* and *receive*, as an extension of the uniprocessor run-time support that takes into account important issues peculiar to shared memory architectures like synchronization or cache coherence. On the other hand, since all the processing nodes have to access the shared memory for loading data or to communicate, the memory becomes a source of performance degradation due to conflicts. So the effectiveness of the shared memory approach depends on the *latency* incurred on memory accesses as well as the *bandwidth* of information transfer that can be supported. We can consider conflicts on shared memory the major source of performance degradation in these architectures. Considering that,  $T_{send}$  and  $T_{calc}$  will be principally affected by this phenomenon so a cost model should describe this situation in a proper way in order to ensure at least performance prediction.

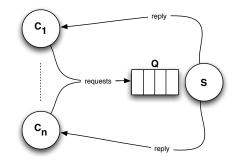

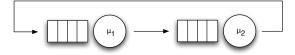

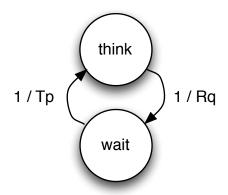

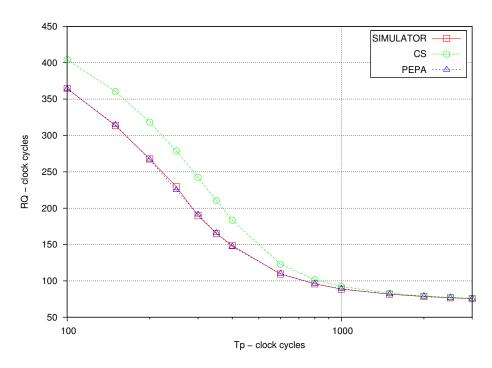

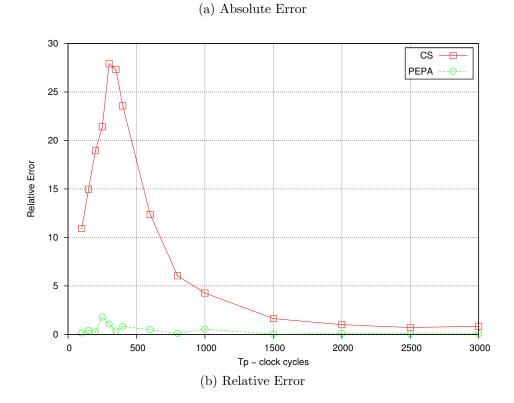

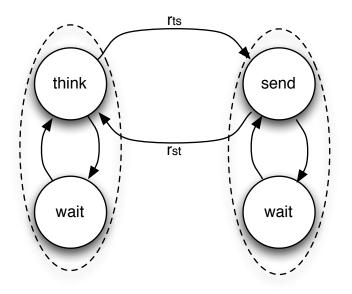

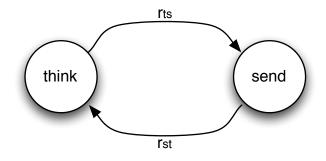

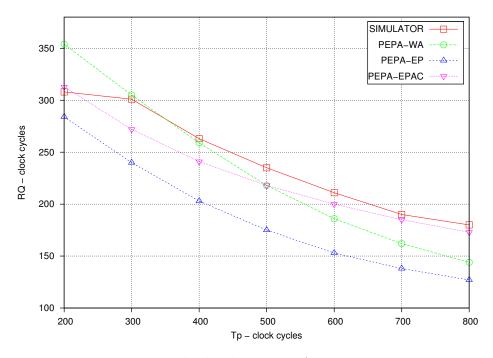

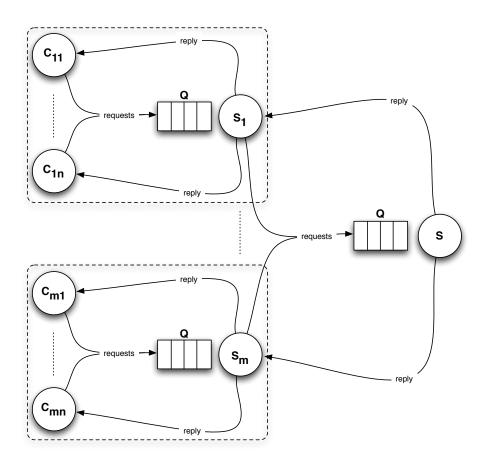

Formally, the impact of shared memory conflicts can be modelled as a *client-server* queuing system wherein clients  $C_i$  are processing nodes accessing the same macro-module while the server S is exactly that memory module, thus the under-load memory access latency is the *server response time* (conventionally called  $R_Q$ ). Figure 1.2 shows this model that will be focus of interest in all the thesis.

Figure 1.2: Client-Server System with Request-Reply behaviour.

In [20] the model is described through the following system of equations:

$$\begin{cases}

T_{cl} = T_P + R_Q \\

R_Q = W_Q(T_s, T_A) + t_{a0} \\

\rho = \frac{T_S}{T_A} \\

T_A = \frac{T_{cl}}{p} \\

\rho < 1

\end{cases}$$

(1.1)

Each client  $C_i$  generates the next request only when the result of the previous one has been received. The behaviour of a client can be considered cyclic: local computational periods of average length  $T_P$  alternates to waiting ones  $(R_Q)$ , leading to a certain client average inter-departure time  $T_{cl}$ . Once we know  $T_{cl}$  we can determine the server average inter-arrival time  $T_A$  as  $\frac{T_{cl}}{p}$  applying the Aggregate inter-arrival time Theorem. Finally, the server response time  $R_Q$  is given by the average waiting time  $W_Q$  in the queue Qplus a constant known in advance that is the base latency  $t_{a0}$  of the server. Of course,  $W_Q$  depends on the type of queue placed in front of the server. The last expression points out that the system has a self-stabilizing behaviour (the utilization factor  $\rho$  of the server is less than one) so a steady-state solution exists. In this analytical approach we can find  $R_Q$  as resolution of a second degree equation in  $\rho$ .

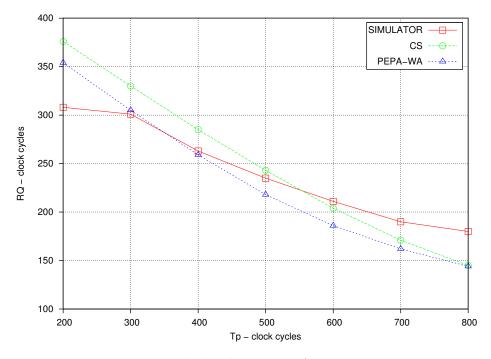

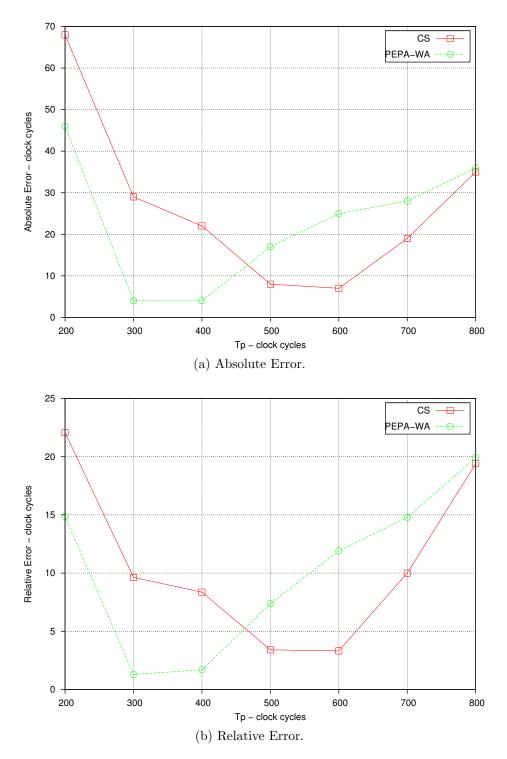

In the following, the client-server model will be described in other formalisms, e.g. either as closed queuing network or as Continued Time Markov Chain (CTMC), and  $R_Q$  will be predicted through more resolution techniques, e.g. analytical and numerical. The reason is that we want to find a way to enhance the model for new behaviours and to improve its accuracy without increase the complexity of the resolution as much.

From this point of view, we know that Markov chains are a very powerful mathematical tool able to represent the behaviour of complex and concurrent systems as could be the Processors-Memory subsystem in shared memory architectures. Further, many numerical resolution techniques exist for moderately sized CTMC while iterative methods can be applied in case huge sizes are involved. Of course, Markov chains are difficult to build so we would

#### 6 Introduction

want to abstract from them and also from their resolution techniques.

For this purpose during the thesis, we will use a high level description language for Markov chains called *Performance Evaluation Process Algebra* (PEPA). It belongs to the *Stochastic Process Algebras* class and its usability comes out from the very formal interpretation of its expressions that is provided by an operational semantic. As we will see in Chapter 5, PEPA is a paradigm able to specify Markov chains that allows to express a complex system as composition of smaller components. These characteristics in addition to the high level approach, fit PEPA also as formalism to enhance and to solve the client-server model. To our knowledge, this is the first attempt to use PEPA for performance modelling in the HPC field.

We advocate that PEPA is *flexible* formalism for the client-server model able to reach *accuracy* in under-load memory access latency estimations and able to *accommodate* parallel application constraints.

For flexibility we mean a formalism able to adapt itself nimbly to even drastic architectural and/or application dependent changes. This ability is necessary in order to deal changes with no much effort and without increase a lot the resolution complexity of the model. A notable example could be the architectural passage from non-hierarchical shared memory to shared memory hierarchies that are very common in multi-cores architectures. For its relevance, this aspect will be treated in depth in a chapter.

Further, the accuracy aspect is very important for quantitative reasons. In order to be used, a performance cost model has to be precise. From this point of view, both analytical and numerical resolution techniques have been analysed and compared during the thesis. Of course, not always the more accurate solution is the best choice in terms of complexity so a good trade-off between this two contrasting requirements is needed.

Finally, we would want a formalism also able to taken into account the impact of the parallel application executed on the shared memory architecture. In other words, this means to satisfy application constraints. Notable examples could be an application composed by different processes or just processes exploiting a complex internal behaviour. We will treat this topics in depth.

**Organization of the Thesis** The thesis is organized in 8 chapters. The first one is just this Introduction that aims to focus on the context, the objective and the structure of this thesis.

Chapter 2 provides an overview of the main concepts about multiprocessors and multi-cores exploiting parallelism at processes level.

Chapter 3 summarizes the most important results of Queuing Theory that will be useful for future treatments. We recall that also the client-server model with request-reply behaviour reported in [20] is based on Queuing Theory.

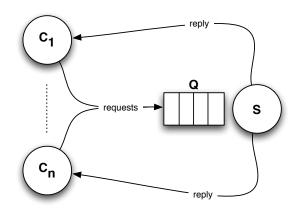

Chapter 4 introduces two cost models for the Processors-Memory system: the former maps the system into a Closed Queuing Network while the latter is the client-server model already introduced. We will see pro and cons of both and their resolutions and we will propose a first variant of the second one taking into account a first application constraint: heterogeneous processes.

In order to enhance the model to take into account new architectural or application dependent aspects without increase the complexity, the PEPA formalism will be proposed in Chapter 5. Therefore, analysis and comparisons with other resolution techniques will be shown.

Chapter 6 examines the impact of parallel applications, i.e. applications composed either by different processes or with processes exploiting a complex internal behaviour. Also in this case, the theoretical contribution will be joined to experiments.

The shared memory hierarchy modelling and relative results will be treated in Chapter 7.

Finally, Chapter 8 draws the conclusions.

#### Introduction

# Chapter 2

# Shared Memory Architectures

In this chapter we describe the main concepts about a class of parallel *Multiple Instruction Stream Multiple Data Stream* (MIMD) architectures: *multiprocessors* and *multi-cores* exploiting parallelism at processes level [20, 7, 17]. Obviously, we do not want to give a complete treatment of these architectures in this thesis, that can be found in [20, 7], but only the key concepts that will be used in chapters to come. So we will start summarizing the important topics for multiprocessors and successively we will extend them with particular care about multi-cores.

At first sight, a multiprocessor can be seen as a set of *processing nodes* that share one or more levels of memory hierarchy and are able to exchange firmware messages along an *interconnection structure*.

As we will see in this chapter, the processing nodes in a multiprocessor are general purpose CPUs possibly with a local memory and/or some I/O units while the interconnection structure is usually a trade off between performance and cost of the interconnection. The shared memory peculiarity means that any CPU is able to address any location of the physical memory. In other words, the result of the translation from logical addresses to physical ones can be any location of main memory. Moreover, lower levels in memory hierarchy can be shared.

The messages exchanged between processing nodes are used to implement shared memory accesses or explicit interprocessor communication, e.g. for process low-level scheduling like a decentralized process wake-up in *anonymous processors*. It is worthwhile to stress the fact that these messages are low level messages , so they must not be confused with messages at process

#### 10 Shared Memory Architectures

#### level.

The shared memory characteristic has, at the same time, pros and cons. On an hand it allows an easy way to design *run-time support* for interprocess communication, i.e. the implementation of *send* and *receive* if processes cooperate via message passing like in [20], because it is an extension of the uniprocessor run-time support, that takes into account important issues of *synchronization* or *cache coherence*. On the other hand, since all the processing nodes have to access the shared memory for loading data or to communicate, the memory becomes a source of performance degradation due to conflicts. So the effectiveness of the shared memory approach depends on the *latency* incurred on memory accesses as well as the *bandwidth* of information transfer that can be supported. Formally, this last aspect can be modelled as a *client-server* queuing system in which clients are processing nodes and servers are the memory modules, thus the memory access latency is the *server response time*. Anyway, we will see this model in very depth in the next chapter because it will be focus of interest in the rest of the thesis.

In the following of this chapter, we will deal with the structure and the properties of multiprocessors and relevant considerations will also be made for multi-cores.

Multi-cores, or *Chip MultiProcessor* (CMP), can be considered shared memory multiprocessors integrated on a single chip.

Therefore many results found for multiprocessor architectures are also valid for multi-cores, especially with a number of cores on the same chip relatively low. But the trend in shared memory architectures seems that the number of cores is expected to double every two years (Moore law applied to the number of cores on chip). In fact, the idea is to substitute few complex and power-consuming CPUs with many smaller and simpler CPUs that can deliver better performance per watt. It is worthwhile to point out that this last aspect is true provided that the software is able to exploit efficiently these architectures. In spite of this relevant architectural change, the actual programming tools are very low-level tools for a programmer without profound knowledge in this field. Further, performance prediction and/or performance portability is missing or it is still in an initial phase. As explained in [20], this targets could be accomplished by a *performance cost model*, that takes into account the features of different concrete architectures, in association

#### 2.1. Processing Nodes 11

Figure 2.1: Simplified view of Shared Memory Architecture

with a simplified view of these architectures, the so called *abstract architecture*. Obviously, this is not a simple task but we will explain how it can also be achieved for complex architectures, like multiprocessors and multi-cores, using the structured and methodological approach utilized in [20]. However, we remark that a complete and precise cost model for these architectures is still missing and the aim of this thesis is to give a contribution in this direction with particular care about the impact of the parallel application. To achieve this goal is therefore necessary to investigate in depth important architectural factors, e.g. processing nodes, interconnection structures, shared memory hierarchy, cache coherence solutions and so on, and we are going to do this.

# 2.1 Processing Nodes

We focus on processing nodes that are composed by general purpose CPUs because in this way is possible to build multiprocessors or multi-cores on top of uniprocessor products exploiting all the advantages related to modularity. Successively, they themselves can be in turn building blocks for larger-scale

#### 12 Shared Memory Architectures

systems. This approach must however preserve the interoperability. For this purpose an *interface unit* W for each processing node is present. This unit has at least to be able to intercept all the memory requests and to transform them into proper firmware messages that will be sent either to the interconnection structure (*external* messages) or to some local units (*internal* messages) like a local memory (if present). Further, W has to be able to create proper firmware messages used for explicit communication between processing nodes.

It is important to notice that a potential re-utilization of uniprocessor architectures in greater contexts is not always free. In fact, some assembler and/or firmware mechanisms have to be already present in the uniprocessor design. Notable examples for shared memory architectures are synchronization mechanisms (requiring proper assembler instructions or annotations in the format of some assembler instruction) and cache management for the maintaining of coherent information among processing nodes. Anyway, this topics will be mentioned apart in the following.

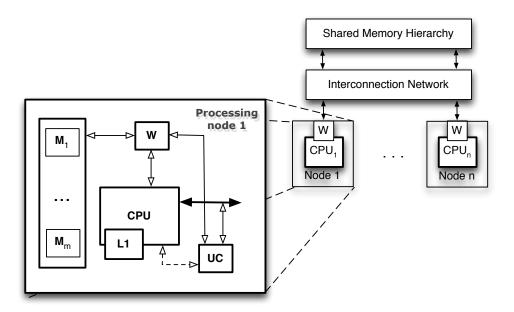

A processing node in a shared memory architecture may have in general the schema visible in the Figure 2.2. As mentioned above, many features are common in both multiprocessors and multi-cores but slight differences may arise. We have:

- the CPU is a *pipeline* or *super-scalar* uniprocessor (with private data and instructions caches L1) exploding *Instruction Level Parallelism* (ILP), that is parallelism at firmware level. The CPU complexity can differ for various aspects that affect the performance of sequential code. In general, if it is required the maintenance of sequential performance, more complex CPUs are used. Otherwise, few large CPUs can be substituted with many simpler CPUs with a gain in efficiency and power consumption. Exclusively for multi-cores architectures, the CPU complexity could be influenced by the limited chip size because a trade-off between the features of each component on chip must be designed. It is worthwhile to note that if there are not hard constraints, hardware multi-threading, especially in the form of *Simultaneous Multi Threading* (SMT), is being used to exploit parallelism at firmware level

- the I/O Communication Unit (UC) is provided for explicit interpro-

cessor communication support. As we have mentioned above, though the majority of run-time support information are accessible in shared memory via memory instructions, there are some cases in which direct firmware messages between processing nodes are preferable. Notable examples are for processor synchronization and process low-level scheduling

- the interface unit W is directly connected to a local memory LM (if present) and some I/O units like UC. Moreover, dedicated links are also present toward the interconnection structure to allow information exchanges

- a local memory LM is used in general for caching information. This means to decrease the instruction service time as in uniprocessor architectures (local benefit) and, peculiarly of shared memory architectures, it reduces the shared memory conflicts as well as the interconnection structure congestion with a global performance improvement. The local memory may be a private memory of the processing node (for instance, it realizes the second or the third level of cache hierarchy) or, alternatively, LM may play a double role: it is integrating part of shared memory (so it can be addressed by all the other processing nodes) and, at the same time, it continues to operate as private memory support for the processing node. Exclusively for next generation multi-cores architectures, we can image that, looking at the Moore law applied to the number of cores, if LM is not private it will not be shared among all the cores but only among groups of cores due to performance degradations as a consequence of the slower memory access time

Looking at the explanation of a processing node in a shared memory architecture we can recognize that its structure is prevalently a uniprocessor architecture with firmware-assembler mechanisms to interoperate and coordinate with other processing nodes. So the structure of a processing node principally affects the performance of the sequential code but, in case a parallel application is executing on these architectures, the global performance depends by other factors like the impact of interconnection structures and/or the memory congestion. In the next sections we will treat this topics.

#### 14 Shared Memory Architectures

Figure 2.2: Processing Node in a Shared Memory Architecture

## 2.2 Interconnection Structures

The job of an interconnection structure in a MIMD parallel machine is to transfer firmware messages from any source node to any desired destination node in an efficient way that is, low latency and high bandwidth, that are features suitable for scalable highly parallel machines. This holds for both classes of MIMD architectures, i.e. shared memory multiprocessors and distributed memory multicomputers, but for the former class it is also important to do not fall into the pin count problem.

As we already know from the literature, many types of interconnection structure exist. In this context we do not want to list all of them with their features, that can be easily consulted in the literature, but we want to focus on same aspects that will be useful in future treatments. A detailed explanation of this topic can be found in [7].

In shared memory architectures, processing nodes communicate explicitly between them or with the memory modules across a sequence of links and switches. In the following, we will call all the entities that want to communicate through the interconnection structure, i.e. processing nodes and memory modules, as nodes. As usually in networking domain, an interconnection structure (or network) can be formally viewed as a graph

$$N = (V, E)$$

where V is the set of nodes and switches and E is the set of links between them. The path from a source node to a destination node is called *route* and it is calculated by a *routing algorithm*. It is out of our scope to give complete treatment of routing strategies and algorithms so we only mention that routing can be *deterministic*, i.e. the path is determined solely by its source and destination, or *adaptive*, i.e. the choice of the path is influenced by dynamic events as traffic intensity along the way. Further, another important characteristic of a network is how information traverse the route (*switching*) strategy). Basically, it may happen in *circuit switching*, i.e. the path between source and destination is established and reserved until it is necessary, or in packet switching. In the latter, the information are divided into packets individually routed from the source to the destination since each packet is carrying routing and sequencing information in addition to a portion of data. As we already know, this approach allows a better utilization of the network because resources are only occupied while a packet is traversing them so we will assume that interconnection structures that we are going to take into account will be packet switching networks.

From our point of view, it is important to understand that the above routing strategies can be directly accomplished by switches at firmware level. These units perform the so called *flow control* too. The flow control determines when a message can move along its route and it is absolutely necessary in case whenever two or more messages attempt to use the same network resource at the same time. For solving it, switches may adopt the classical *store-and-forward* technique or a more sophisticated strategy called *wormhole* flow control. In the latter, each packet is further subdivided in *flits*. Switches consider flits belonging to the same packet (that is still the unit of routing) as an input stream that must be forwarded in the same output port selected by the routing algorithm. Doing that, it is possible to achieve all the benefits due to a pipeline behaviour provided that the switches bandwidth per flit is high enough (and this holds because switches operate at firmware level). In this case, we can consider wormhole flow control as an

#### 16 Shared Memory Architectures

additional source of parallelism. Further, this technique has another important property: flits of the same packet are not entirely buffered before being forwarding so the buffering area is minimized. Owning to this property, the interconnection structures with this kind of flow control are very suitable for networks on chip because the smaller occupied area. Taking into account the increasing number of cores per chip these solutions are going to become very attractive for multi-cores architectures. In the following we will assume networks with wormhole flow control.

As mentioned above, an interconnection structure is a trade-off between cost of the interconnect and performance. Network latency and the bandwidth are critical parameters for measuring performance goodness while the number of bidirectional links and the occupied area should be considered for the cost of interconnect. Formally, we define the *base network latency* as the time needed to establish a communication through the network between a source and a destination *without contention*. In general it depends by many architectural characteristics, e.g average network distance, message length, routing, flow control strategy and so on, but it is not a function of the traffic. Instead, in case conflicts on the network are taken into account, we have the so called *under-load network latency*. For future aspects, it is important to evaluate in detail the base latency in a network with wormhole flow control. In the next subsection, we will see how this can be made.

## 2.2.1 Base Latency in Networks with Wormhole Flow Control

First of all, it is worthwhile to say that pipelined communications also occur in other firmware units (like memory interface units) that are involved in the path for achieving a destination, e.g. a memory module. Considering that, we can extend the wormhole behaviour to such that units and do not only consider the switches of the interconnection structure in the evaluation of the base latency.

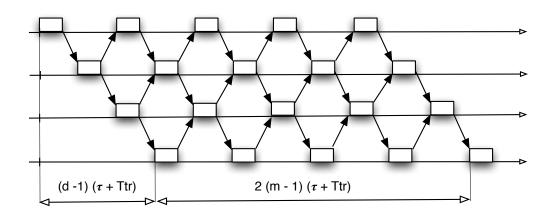

As reported in [20], if we consider a firmware message of m words that travels d firmware units (as in the Figure 2.3) and assuming that

• flit size is equal to a word

Figure 2.3: Base Latency in pipeline behaviour with level transaction firmware interfaces (d = 4 units and message length of m = 5 words)

- every unit has clock cycle  $\tau$

- every link has transmission latency  $T_{tr}$

- level transaction firmware interfaces

we have that the base latency is

$$t_{a0} = (2m + d - 3)(\tau + T_{tr}) \tag{2.1}$$

#### 2.2.2 Base Latency in Time-Slot Networks on chip

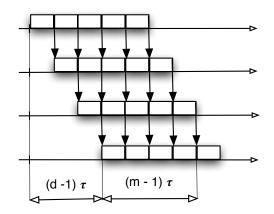

The above formula is in general a very good approximation but, in case the interconnection structure is completely on chip (like in multi-cores), further consideration should be taken into account. First of all, the transmission latency on chip is very negligible so  $T_{tr} = 0$ . Moreover, we have verified experimentally on a concrete architecture that firmware units do not wait for an acknowledgement before being sent the next flit since they are not more using level transaction protocols but specialized communication protocols, e.g. time slots based, are involved in order to reduce the latency (Figure 2.4). Therefore, the derivation of the base latency becomes

$$t_{a0} = (d+m-2)\tau \tag{2.2}$$

#### 18 Shared Memory Architectures

Figure 2.4: Base Latency in pipeline behaviour on chip  $(T_{tr} = 0)$  and time slot based communication firmware protocols (d = 4 units and message length of m = 5 words)

Another important fact came out from our study. The latency is further on reduced because units waiting for an information start to work immediately after the reception of the first part of the information, i.e. a word if the considered hierarchy is processor-first level cache or the first cache block if the hierarchy is first level cache-second level cache and so on, and no more after all the information.

## 2.2.3 Direct and Indirect Interconnection Structures

In the following of this section, we will study base latency and bandwidth as a function of the number n of nodes as in [20, 7]. As we can image, we would want low latency and high bandwidth on one side and we would not want to deal with the pin-count problem on the other side.

Since we are talking about interconnection structures for highly parallel machines, we should not take into consideration traditional buses that are no capable of simultaneous transfers (hence the bandwidth is O(1)) or fully connected crossbars (that are not physically realizable when the number n of nodes grows because the cost is  $O(n^2)$ ). In spite of this, buses and crossbars are actually used. A notable example is the internal structure of switches that is usually a crossbar connecting all the input ports with all the output ports. Anyway, their use is only made in case the number of nodes is low. If

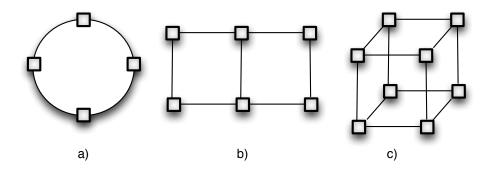

Figure 2.5: Most important Direct Networks with Limited Degree

an higher number of nodes is involved, other interconnection structures must be chosen.

In the so called *limited degree* networks, a node is directly connected to a small subset of other nodes or it is indirectly connected to every other node by an intermediate path of switches. These interconnection structures can be distinguished for their *topology* in *direct* or *indirect* networks.

In the former case, point-to-point dedicated links connect nodes in some fixed topology. Each node is connected to one and only one switch possibly through the interface unit W. Of course, communication between not adjacent nodes will travel intermediate nodes that will forward the information to the destination. Notable examples of direct networks are *rings* (2.5 a), *meshes* (2.5 b) and *cubes* (2.5 c).

In indirect networks, nodes are not directly connected as before but they are connected only with a subset of switches that, in turn, have a limited number of neighbours. i.e. other switches or nodes. In general, more than one switch is used in order to establish a communication between nodes. Notable examples are *trees*, *butterflies* and *fat trees*.

Briefly, we are going to summarize the most important features of some widely known interconnection structures. Rings have a base latency O(n), meshes or two-dimensional cubes have  $O(\sqrt{n})$  while butterflies, trees of fat trees  $O(\log n)$ . With respect to a tree, the so called fat tree has the channel capacity that doubles at each level from the leaves to the root in order to compensate the increasing congestion. It is worthwhile to say that all the cited interconnection structures connect nodes of the same type except the

#### 20 Shared Memory Architectures

butterfly that is principally used to allow communication between nodes of different types (for example n CPUs with n memory modules). Moreover, it can be used in a very elegant way to implement the so called *Generalized Fat Tree* that plays substantially two roles: it can be used as a fat tree and as a butterfly achieving an efficient solution in architectures where CPU-CPU and CPU-memory communications belong logically to different networks (like in UMA architectures).

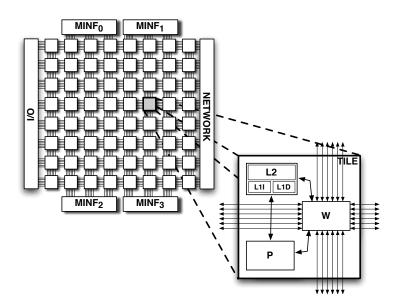

Nowadays multiprocessors utilize more rings to communicate or, if the number of processing nodes is high, fat trees or generalized fat trees are used. In multi-cores architectures, the area of the chip is an hard constraint that limits many architectural choices as we have mentioned for the CPU complexity. Considering that, is not physically possible (until now) to fit complex interconnection structures on chip. Therefore, in case an high number of cores is involved, meshes are used because they have good scalability and easy realization on chip. A notable example of real multi-cores architecture using a mesh as interconnection structure is the Tilera TileGX. As we can see in Figure 2.6, the Tilera Tile64 is a 64 cores architecture specifically made for network processing in which every core has the instruction cache and data cache. Further, a second level of cache L2 realizes the private local memory. The next level in memory hierarchy is the shared memory level: there are four interfaces toward it at the borders of the chip. The mesh is used for explicit communication among cores but it also used for core-memory communication. In spite of this, it is important to notice that the mesh should only be used for the interconnection of the cores.

It is worthwhile to notice that, contrarily to many actual multi-cores, this architecture is not exploding an hierarchical shared memory organization. Anyway, shared memory hierarchies are widely coming out as a consequence of the integration of memories on chip, so nowadays the necessity to model this aspect should be treated. In the chapters to come we will deal with this.

# 2.3 Shared Memory

As we have said, a single physical address space across all the processing nodes in shared memory architectures is involved. This allows an easy way to design an efficient run-time support for interprocess communication be-

Figure 2.6: Tilera Tile64

cause it occurs implicitly as a result of conventional memory accesses instructions like happened in uniprocessor architectures. On the other hand, since many processing nodes are present, it may happen that more than one processing node wants to access the shared memory at the same time. Doing that, processing nodes cause congestion in the interconnection structure as well. Further, more hierarchical levels of shared memory could aggravate the congestion.

Firstly, assume that the congestion probability in the interconnection structure is very low. As soon as possible, we will see that this assumption is true in various conditions. At this point, we can assume that the major source of performance degradation is due to the queue in front of the shared memory. We already know that local memories may reduce conflicts on shared memory but, anyway, the design of the shared memory in a proper way is very important from the performance point of view. In particular, we need high bandwidth and a minimal contention on the memory. These goals can be achieved by mean of *modular memory with interleaved organization*. These memories are organized in macro modules with their own organization that can be interleaved or sequential. At this level, the interleaved organization has the principal effect to reduce the contention on memory modules. Moreover, a single macro module can be realized either with an interleaved internal organization or with just one module with *long word*. Often, the number of the internal modules, or the number of words in a long word, coincides with the cache block size because it allows high bandwidth transfers of cache blocks.

## 2.3.1 UMA and NUMA Architectures

Another important point that is worth to explain is the shared memory organization in multiprocessor architectures. This characteristic is used to classify architectures on the base of the relative distance of the shared memory modules with respect to processing nodes. The accesses can be mainly performed in two styles:

- 1. in *uniform access memory* (UMA) memory accesses take the same time no matter which CPU requests them

- 2. in *non uniform access memory* (NUMA) some memory accesses are much faster than others depending on which CPU ask for which word or block

In the former, the memory modules are equidistant from the processing nodes. This means that the base latency to access them is the same independently both from the processing node and requested word. In spite of this symmetry, (private) local memories are used inside processing nodes in order to capitalize on the advantages about caching as mentioned above.

In the last memory organization, the symmetry about memory accesses is not more present. If we look at the typical schema of a processing node reported in Figure 2.2, we can consider the shared memory as the union of all the local memories of the processing nodes:

$$M = \bigcup_{i=1}^{n} LM_i$$

Hence LM is not more exclusively private of a processing node, but it can be accessed from the external ones. However, every processing node accesses own local memory in a very shorter time with respect to external ones that must travel the interconnection structure. Thus, every processing node in shared memory multiprocessors has its own interface toward the memory so no conflicts are present in accessing the interface. This does not hold any more for multi-cores architectures because it is not physically realizable to put a memory interface in the same chip for every core. This constraint creates an ulterior source of performance degradation.

The distinction between UMA and NUMA shared memory organizations can be also effectuated for multi-cores. If the number of cores is low or there is a single interface, the architecture *seems* UMA, otherwise it should be considered NUMA. This is the case of the Tilera Tile64 (Figure 2.6) since it has four shared memory interfaces placed at the borders of the chip and all the cores access them though the mesh. Of course, different cores access the same memory module with different base latencies.

Until now we were assuming interconnection structures with low probability of conflicts. It is important to keep in mind that if this does not hold we should take into account the impact due to congestion on networks. Likely, we know that there exist networks (fat trees, generalized fat trees) that minimize the conflicts so we can assume the above property for at least multiprocessors. Instead, we can assume that it also holds for multi-cores because the performance degradation due to interconnection structures realized on chip is negligible with respect to the memory impact. The reasons should be the sophisticated techniques (as wormhole flow control and time slot based communication protocols) that have been used and the difference in frequency clock between the chip with the cores and the memory. This has further been verified experimentally on a real architecture from our research group and more information can be found in [15].

In the following, we will abstract from the interconnection structure and we concentrate only on shared memory performance degradation. However, it is worthwhile to stress that, even if interconnection structure congestion is negligible, the impact of the network latency must be taken into account from the performance point of view. In the next subsection we are going to see how the interconnection structure latency impact on the evaluation of the base memory access latency.

## 2.3.2 Base and Under-Load Memory Access Latency

The base latency to access a shared memory memory will be a fundamental parameter for our treatment. Assuming that the architecture is *unloaded*, i.e. any conflict is present, it can be defined as the time that a firmware unit, e.g. the second level cache, asking for a memory access, must wait before it receives (the first part of) the memory reply.

We can evaluate the base memory access latency using the approach introduced in 2.2.1. In fact, as we already told, if all the traversed firmware units operate in a pipeline behaviour we can easily estimate this value only knowing the number d of traversed units and the length of the memory request and reply firmware messages.

It is important to stress the fact that the base memory access time does not taken into all the time lost due to congestion on shared memory modules. Therefore, it cannot be a good evaluation of the time that a unit spent for waiting a reply in case conflict are present in the architecture. As we already defined for networks, if we add the impact of the congestion we have the so called *under-load memory access latency*. Following the approach presented in [20], in chapters to come we will see how this value can be estimated.

# 2.4 Synchronization and Cache Coherence

As we already mentioned, shared memory architectures must provide assemblerfirmware mechanism for two critical aspects that are:

- 1. synchronization. Having many processing nodes and a physical shared memory space, shared information among processes can be accesses at the same time by different CPUs. If sequences of *indivisible operations* must be performed (like in interprocess communication run-time support), *locking* mechanisms are needed (in addition to disable interrupts like in uniprocessor)

- 2. *cache coherence*. As we have already told, in shared memory architectures caching is important for local and global performance improvement. However, in presence of private cache hierarchy per processing

node, shared information among processes must be maintained consistent because it may happen that in hierarchies of different processing nodes the value of the same data differs