Università di Pisa

DIPARTIMENTO DI INFORMATICA DOTTORATO DI RICERCA IN INFORMATICA

Ph.D. Thesis

## On expressing different concurrency paradigms on virtual execution environment

Cristian Dittamo

SUPERVISOR Dr. Antonio Cisternino

November 22, 2010

## Abstract

Virtual execution environments (VEE) such as the Java Virtual Machine (JVM) and the Microsoft Common Language Runtime (CLR) have been designed when the dominant computer architecture featured a Von-Neumann interface to programs: a single processor hiding all the complexity of parallel computations inside its design. Programs are expressed in an intermediate form that is executed by the VEE that defines an abstract computational model in which the concurrency model has been influenced by these design choices and it basically exposes the multi-threading model of the underlying operating system. Recently computer systems have introduced computational units in which concurrency is explicit and under program control. Relevant examples are the Graphical Processing Units (GPU such as Nvidia or AMD) and the Cell BE architecture which allow for explicit control of single processing units, local memories and communication channels. Unfortunately programs designed for Virtual Machines cannot access to these resources since are not available through the abstractions provided by the VEE. A major redesign of VEEs seems to be necessary in order to bridge this gap. In this thesis we study the problem of exposing non-Von Neumann computing resources within the Virtual Machine without need for a redesign of the whole execution infrastructure. In this work we express parallel computations relying on extensible meta-data and reflection to encode information. Meta-programming techniques are then used to rewrite the program into an equivalent one using the special purpose underlying architecture. We provide a case study in which this approach is applied to compiling Common Intermediate Language (CIL) methods to multi-core GPUs; we show that it is possible to access these non-standard computing resources without any change to the virtual machine design.

To my parents and my nephew.

## Acknowledgments

Many people have directly or indirectly partaken in making this thesis possible. First of all, I wish to thank my supervisor Antonio Cisternino who always supported and encouraged me, leaving me the freedom of experimenting with many different topics in different area. I wish also to thank Vincenzo Gervasi and prof. Börger for their advices on ASM modeling.

For the uncountable discussions on computer science and life we had in these three years, I also wish to thank my friends and colleagues of the CVSLab: Davide, Gabriele, Marco, Nicole, Simone, Stefano P., Stefano S.

For their invaluable contribute to make better my personal life, I wish to thank my friends: Alba, Andrea, Anna, Daniele, Daniele M., Davide, Fedele, Federica, Gaspare, Giacomo, Ilaria, Luca, Nicola, Pippo, Stefania, Veronica, and Veronika.

Last but not least I wish to thank my parents, Dina and Filiberto, that always supported me in what to do most, and Letizia, my nephew, that makes it so nice all times I come back to my hometown, and make it so hard to leave again right after.

# Contents

|   | Introduction ix |         |                                                                                                    |  |

|---|-----------------|---------|----------------------------------------------------------------------------------------------------|--|

|   | I.1             | Resear  | ch problem                                                                                         |  |

|   | I.2             | Proble  | m statement                                                                                        |  |

|   | I.3             | Resear  | ch scope                                                                                           |  |

|   | I.4             | Resear  | ch contributions                                                                                   |  |

|   | I.5             | Organ   | ization and Reading plans                                                                          |  |

| 1 | Moo             | dels of | execution 1                                                                                        |  |

|   | 1.1             | A brie  | f introduction to the Abstract State Machines                                                      |  |

|   |                 | 1.1.1   | Basic (single-agent) ASM                                                                           |  |

|   |                 | 1.1.2   | Control State ASM                                                                                  |  |

|   |                 | 1.1.3   | ASM Multi-agents                                                                                   |  |

|   | 1.2             | Model   | s of Sequential execution                                                                          |  |

|   |                 | 1.2.1   | RAM                                                                                                |  |

|   |                 | 1.2.2   | $RAM_L$ : RAM ASM model with race conditions management . 9                                        |  |

|   | 1.3             | Model   | s of Parallel execution                                                                            |  |

|   |                 | 1.3.1   | Shared memory                                                                                      |  |

|   |                 | 1.3.2   | Distributed memory 15                                                                              |  |

|   | 1.4             | Model   | of GPGPUs 19                                                                                       |  |

|   |                 | 1.4.1   | The computational model                                                                            |  |

|   |                 | 1.4.2   | The memory model $\ldots \ldots 23$ |  |

|   |                 | 1.4.3   | The architecture model                                                                             |  |

|   |                 | 1.4.4   | ASM ground model                                                                                   |  |

| 2 | Exp             | ressing | g concurrency paradigms on VEEs 35                                                                 |  |

|   | 2.1             |         | l Execution Environment: design and capabilities                                                   |  |

|   | 2.2             |         | ly Typed Execution Environment                                                                     |  |

|   |                 | 2.2.1   | Machine model and state                                                                            |  |

|   |                 | 2.2.2   | CLR compilation toolchain                                                                          |  |

|   |                 | 2.2.3   | Just In Time compilation                                                                           |  |

|   |                 | 2.2.4   | Meta-data                                                                                          |  |

|   |                 | 2.2.5   | Common Intermediate Language                                                                       |  |

|   |                 | 2.2.6   | Delegate                                                                                           |  |

|          |                   | 2.2.7             | Isolation and security boundaries                                                                                             | 46              |  |  |

|----------|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

|          |                   | 2.2.8             | Communication inter-domain                                                                                                    | 46              |  |  |

|          |                   | 2.2.9             | Interoperability via the Platform Invocation Services                                                                         | 46              |  |  |

|          | 2.3               | Meta-             | - •                                                                                                                           | 48              |  |  |

|          | 2.4               |                   |                                                                                                                               |                 |  |  |

|          |                   | 2.4.1             | Interface                                                                                                                     | 50              |  |  |

|          |                   | 2.4.2             | Custom annotation                                                                                                             | 50              |  |  |

|          |                   | 2.4.3             | Object system                                                                                                                 | 53              |  |  |

|          |                   | 2.4.4             | Quotation                                                                                                                     | 56              |  |  |

|          | 2.5               | Our a             | pproach: types + metadata                                                                                                     | 56              |  |  |

|          |                   | 2.5.1             | Definitions                                                                                                                   | 58              |  |  |

|          |                   | 2.5.2             | Definitions for STEEs                                                                                                         | 58              |  |  |

|          |                   | 2.5.3             | Expressing the RAM on the CLI                                                                                                 | 62              |  |  |

|          |                   | 2.5.4             |                                                                                                                               | 63              |  |  |

|          |                   | 2.5.5             | Expressing the H-PRAM on the CLI                                                                                              | 68              |  |  |

|          |                   | 2.5.6             | Expressing the LogP on the CLI                                                                                                | 69              |  |  |

|          |                   | 2.5.7             | Expressing the GPGPUs model on the CLI                                                                                        | 69              |  |  |

|          |                   | 2.5.8             | Formal definition of the CIL to GPGPU compiler $\ldots$                                                                       | 70              |  |  |

| ი        | Der               | - 11 - 1 <b>:</b> |                                                                                                                               | 73              |  |  |

| 3        | <b>Par</b><br>3.1 |                   | 1                                                                                                                             | 73<br>74        |  |  |

|          | $3.1 \\ 3.2$      |                   |                                                                                                                               |                 |  |  |

|          | 3.2               | 3.2.1             |                                                                                                                               | 75<br>76        |  |  |

|          |                   | 3.2.1<br>3.2.2    | 1 0 1                                                                                                                         | $\frac{70}{78}$ |  |  |

|          |                   | 3.2.2<br>3.2.3    |                                                                                                                               | 70<br>81        |  |  |

|          |                   | 3.2.3<br>3.2.4    | 0 0                                                                                                                           | 86              |  |  |

|          |                   | 0.2.4             | GPGPU programming languages                                                                                                   | 00              |  |  |

| 4        | <b>4-</b> C       |                   | 1                                                                                                                             | 05              |  |  |

|          | 4.1               | Comp              | iling from MSIL to PTX                                                                                                        |                 |  |  |

|          |                   | 4.1.1             | The philosophy                                                                                                                |                 |  |  |

|          |                   | 4.1.2             | 1                                                                                                                             |                 |  |  |

|          | 4.2               | Organ             | nization of the compiler                                                                                                      |                 |  |  |

|          |                   | 4.2.1             | Data Structures                                                                                                               |                 |  |  |

|          |                   | 4.2.2             | Code Analyzer                                                                                                                 | 18              |  |  |

|          |                   | 4.2.3             | Parser                                                                                                                        | 20              |  |  |

|          |                   | 4.2.4             | Code Generator                                                                                                                | 22              |  |  |

|          |                   | 4.2.5             | Runtime support                                                                                                               | 25              |  |  |

| <b>5</b> | Eva               | luatio            | n 1'                                                                                                                          | 27              |  |  |

| -        | 5.1               |                   | elbrot algorithm $\ldots \ldots 1$ |                 |  |  |

|          | U.T               | 5.1.1             | Implementation details and results                                                                                            |                 |  |  |

|          | 5.2               |                   | nne Twister algorithm                                                                                                         |                 |  |  |

|          | - · <b>-</b>      | 5.2.1             | Implementation details and results                                                                                            |                 |  |  |

|          |                   |                   | ±                                                                                                                             |                 |  |  |

#### 0.0. CONTENTS

| Conclusions     |                                 |     |  |  |  |

|-----------------|---------------------------------|-----|--|--|--|

| C.1             | Thesis summary                  | 135 |  |  |  |

| C.2             | Suggestions for Future Research | 136 |  |  |  |

| Bibliography 13 |                                 |     |  |  |  |

### Bibliography

CONTENTS

iv

# List of Tables

| PTX and CIL types mapping                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mapping of MSIL instructions and Node classes. For the sake of brevity we do<br>not consider efficient encoding versions of MSIL instructions. For a complete list,<br>please see the ECMA 335, partition III [1] |

|                                                                                                                                                                                                                   |

| Nvidia GeForce G210M specification: main features                                                                                                                                                                 |

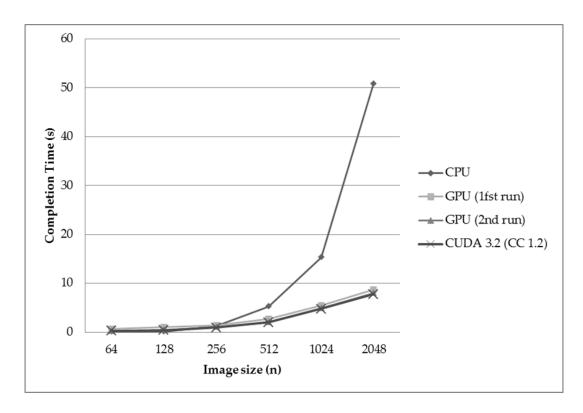

| Comparison of completion times executing the Mandelbrot $Kernel$ on a CPU dual-                                                                                                                                   |

| core and on a GPU. In order to evaluate the overhead introduced by <b>4-Centauri</b> ,                                                                                                                            |

| the CT is computed twice, i.e. in the second run no compilation is performed.                                                                                                                                     |

| Moreover, we compared the <b>4-Centauri</b> compiled <i>Kernel</i> with a Nvidia CUDA                                                                                                                             |

| implementation of it                                                                                                                                                                                              |

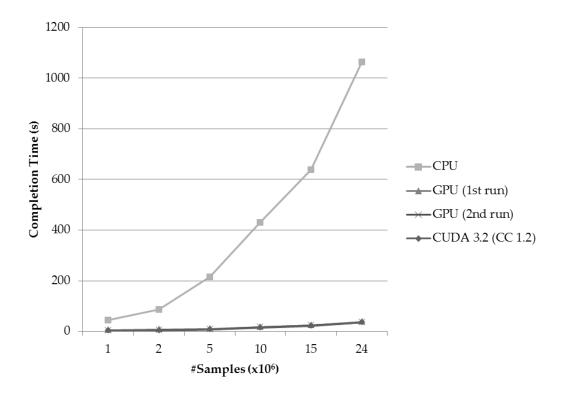

| Comparison of completion times executing the Mersenne-Twister Kernel on a                                                                                                                                         |

| CPU dual-core and on a GPU. In order to evaluate the overhead introduced by                                                                                                                                       |

| 4-Centauri, the CT is computed twice, i.e. in the second run no compilation                                                                                                                                       |

| is performed. Moreover, we compared the <b>4-Centauri</b> compiled Kernel with a                                                                                                                                  |

| Nvidia CUDA implementation of it                                                                                                                                                                                  |

|                                                                                                                                                                                                                   |

LIST OF TABLES

# List of Figures

| I.1 | The performance increase of GPUs and CPUs over the last decade (using the                   |     |     |

|-----|---------------------------------------------------------------------------------------------|-----|-----|

|     | "texels per second" metric).                                                                | •   | х   |

| I.2 | The CLR's Multiple Instructions Multiple Data computational model is different              |     |     |

|     | from the GPUs' SIMD one. How does a JIT compiler can map these models? $\ .$                | •   | xii |

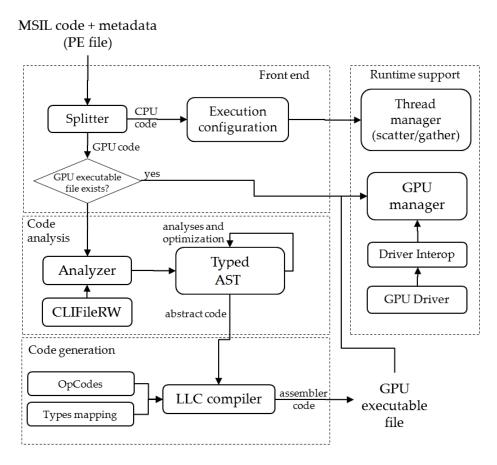

| I.3 | The 4-Centauri compiler: first a IL code is parsed to find out through an-                  |     |     |

|     | notations, which part will execute on a CPU and which will execute on GPU,                  |     |     |

|     | if available; then two layer of abstraction in code manipulation are given: one             |     |     |

|     | more generic used for basic class file manipulation that leverages the CLR, and             |     |     |

|     | one more specific for GPU intermediate code (e.g. Nvidia PTX) generation that               |     |     |

|     | leverages the Nvidia CUDA driver.                                                           | •   | XV  |

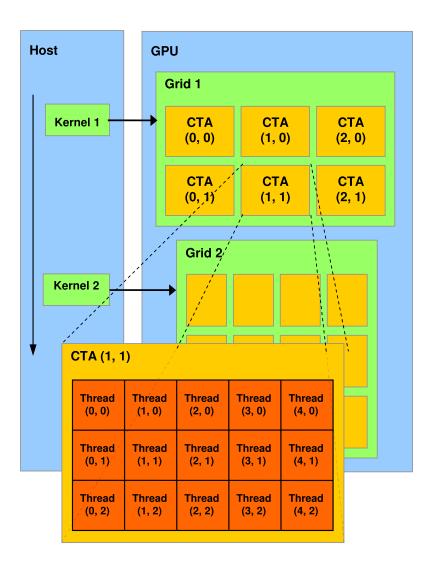

| 1.1 | Nvidia GPU Computational model. A cooperative thread array (CTA) is a set                   |     |     |

|     | of concurrent threads that execute the same kernel program. A grid is a set of              |     |     |

|     | CTAs that execute independently                                                             | •   | 22  |

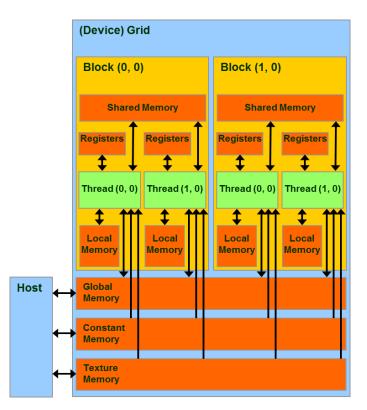

| 1.2 | Nvidia Memory Hierarchy.                                                                    | •   | 24  |

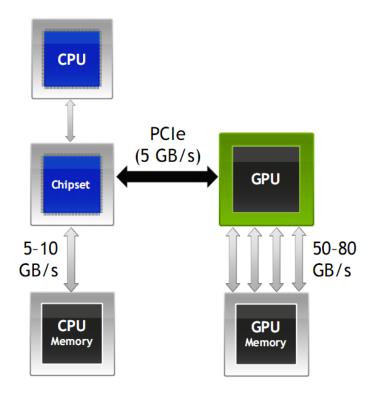

| 1.3 | Architectural view of data transfer between CPU and GPU (with averaged ob-                  |     |     |

|     | served bandwidth) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   |     | 25  |

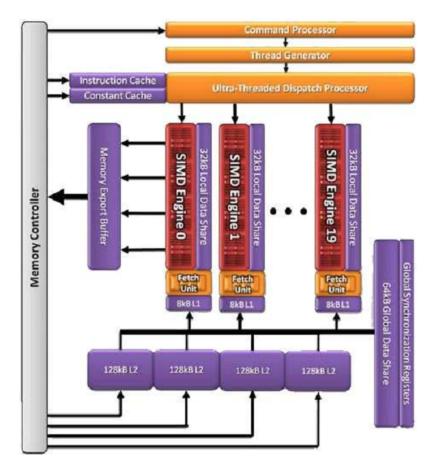

| 1.4 | AMD Cypress architecture building blocks.                                                   | •   | 26  |

| 1.5 | Block diagram of the Nvidia GF100 GPU                                                       |     | 29  |

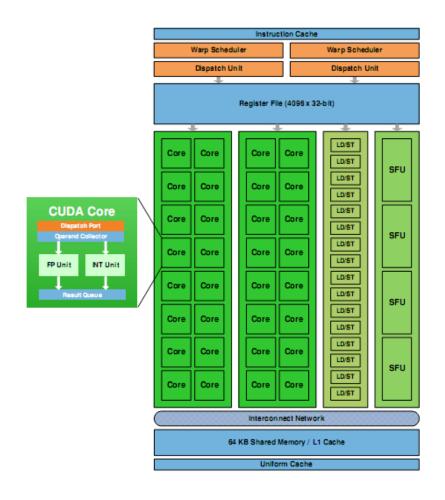

| 1.6 | Nvidia Streaming Multi-processor architecture.                                              | •   | 30  |

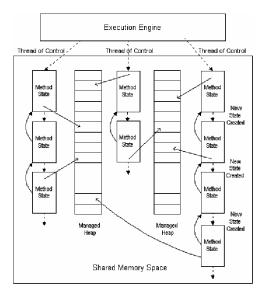

| 2.1 | CLI Machine State Model                                                                     |     | 38  |

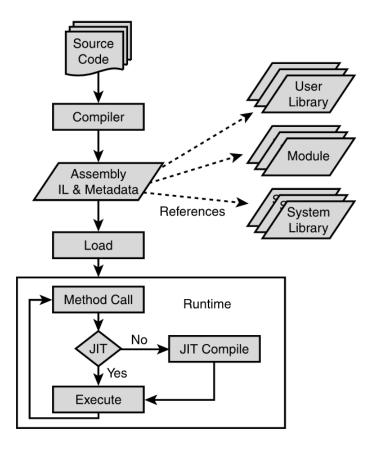

| 2.2 | Basic CLR toolchain: from source code to its execution. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | •   | 40  |

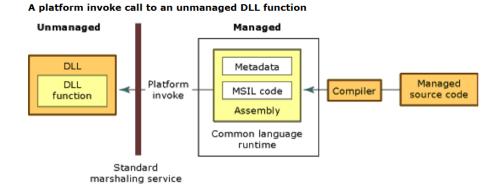

| 2.3 | A platform invoke call to an unmanaged DLL function. Figure in the article "A               |     |     |

|     | Closer Look at Platform Invoke" of the .<br>NET Framework Developer's Guide. $\ .$          | •   | 47  |

| 2.4 | Mapping a C# class members to the GPGPU memory hierarchy                                    | •   | 57  |

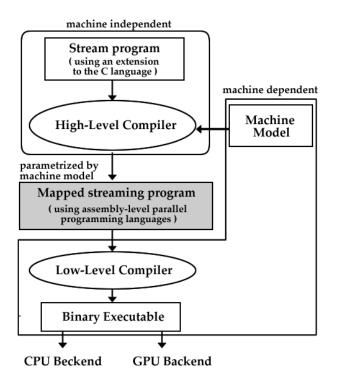

| 3.1 | Two-level compilation approach.                                                             | . 1 | .00 |

| 4.1 | 4-Centauri software stack.                                                                  | . 1 | 07  |

| 4.2 | Two-level compilation model                                                                 | . 1 | .09 |

| 4.3 | Organization of the <b>4-Centauri</b> compiler                                              | . 1 | 14  |

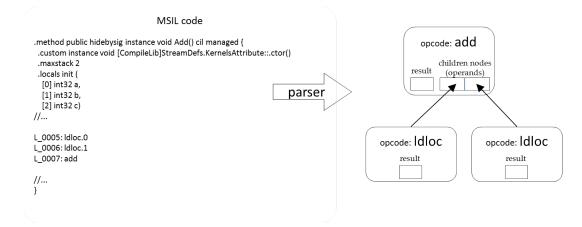

| 4.4 | <b>4-Centauri</b> parser component. Given a MSIL code as input it builds parse tree         |     |     |

|     | using Node data structure.                                                                  | . 1 | 22  |

#### LIST OF FIGURES

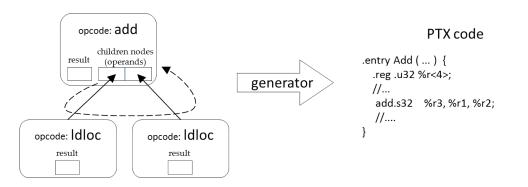

| 4.5 | <b>4-Centauri</b> generator component. Given a parse tree as input generates a PTX code. The visit is postfix                                                                                                                                                                                                                                            |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Comparison of completion times executing the Mandelbrot <i>Kernel</i> on a CPU dual-<br>core and on a GPU. In order to evaluate the overhead introduced by <b>4-Centauri</b> ,<br>the CT is computed twice, i.e. in the second run no compilation is performed.<br>Moreover, we compared the <b>4-Centauri</b> compiled <i>Kernel</i> with a Nvidia CUDA |

| 5.2 | implementation of it.k                                                                                                                                                                                                                                                                                                                                   |

## Introduction

### I.1 Research problem

Over the last decade the performance of computation devices has steadily grown. In general-purpose processors (CPUs), the number of cores<sup>1</sup> in a processor has increased rapidly following Moore's Law as applied to traditional microprocessors. The multi-core paradigm has become the primary method for providing performance improvements. However, sequential performance is limited by three factors or "walls": power, memory and Instruction Level Parallelism (ILP). Power is a "wall" because heat dissipation has reached a physical limit. It gets worse as gates get smaller, meaning a significant increase in clock speed without expensive cooling is not possible without a breakthrough in the technology of materials [2]. Memory is a "wall" because memory performance improvement lags increasingly behind the processor one [3]. ILP is a limit because sequential performance acceleration using ILP has stalled due to two reasons: the success of speculative execution is difficult to predict, and ILP causes an increase in power consumption without linear speedup in application performance. Patterson [4] expressed the relationship between sequential performance and these limitations with the following formula

brick wall for sequential performance = power wall + memory wall + ILP wall

The solution adopted by major CPU vendors places multiple cores onto a single die to exploit TLP<sup>2</sup>. These issues have encouraged researchers to explore other execution models that match the intrinsic constraints of the underlying VLSI<sup>3</sup> technology and the parallelism in emerging applications [5].

One result of this exploration is an increasing interest in special-purpose architectures, e.g. graphics hardware (GPUs) [6] and Cell BE [7], and in hybrid solutions e.g. the Intel Larrabee [8] now called Knights Corner.

The need for efficient real-time specialized processing of 3D meshes silently introduced an architecture model designed for computer games in ordinary PCs, called

<sup>&</sup>lt;sup>1</sup>Cores are multiple copies of a processor that are placed onto a single die to exploit Thread Level of Parallelism (TLP).

<sup>&</sup>lt;sup>2</sup>Thread Level Parallelism

<sup>&</sup>lt;sup>3</sup>Very Large Scale Integration

GPU. It breaks with conventional Von-Neumann architectures and programming models, because it explicitly exposes parallel programming interfaces in a general purpose system in the form of a Single Instruction Multiple Data (SIMD) processor.

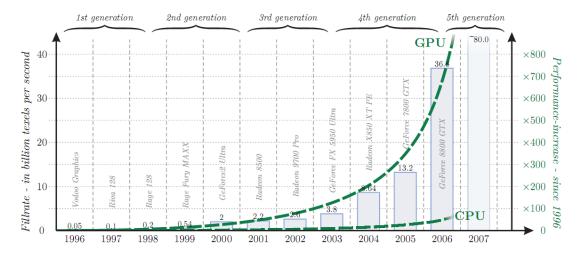

Commodity graphics hardware has evolved tremendously over the last years. It started with basic polygon rendering via 3dfx's Voodoo Graphics in 1996, and continued with custom vertex manipulation four years later. The GPU has improved to a full-grown graphics-driven processing architecture with a speed-performance approx.750 times higher than a decade before (1996:50mtex/s, 2006:36,8btex/s). This makes the GPU evolve much faster than the CPU, which became approximately 50 times faster in the same period (1996:66 SPECfp2000, 2006:3010 SPECfp2000) [9]. Figure I.1 shows the GPU performance over the past ten years and how the gap between CPU and GPU performances grows wider. Experts believe that this evolution will continue for the next five years at least.

Figure I.1: The performance increase of GPUs and CPUs over the last decade (using the "texels per second" metric).

As the name implies, the GPU was initially designed for accelerating graphical tasks. For instance, the real-time 3D visual effects, e.g. interactive cinematic lighting system [10, 11], demanded by games, cinematography and other interactive 3D applications, require efficient hardware-based rendering [12].

However, GPUs were soon being exploited for performing non-graphical computations, for instance, the work of Lengyel et al. uses GPUs to compute robot motion [13], the CypherFlow project by Kedem and Ishihara exploits GPU to decipher encrypted data [14], and a GPU-based computation of Voronoi diagrams has been presented by Hoff et al. [15]. Nevertheless, most of the general-purpose algorithms implemented for GPUs stay in the academic field and have not yet found their way into industrial software engineering. The primary reason is that GPU-based application development is much more complex, mainly because the developer has to be an expert in two domains: the application domain, and computer graphics.

#### I.1. RESEARCH PROBLEM

This approach has been influenced by the entertainment and special-effects industry, where software developers create the so-called "rendering engine" and graphics artists use the engine to create the so-called "shader programs" that compute visual phenomena. Most of the existing GPU-based development systems are founded on this programming model, e.g. RenderMan [16], Interact-SL [17], and Cg [18].

However, these development systems are ill suited for expressing general purpose computations. Being domain specific languages, they require the programmer to perform morphism from his own problem space to the CG problem space. This requires to encode the input in a CG friendly way and to decode the output of a program that must be equivalent to that needed in the original problem space.

Furthermore, because CPU and GPU-based code is developed in different programming languages, additional binding code is required to "glue" the different functionalities together. This means that changing the graphics-oriented programming model and corresponding GPU development tools may significantly reduce development complexity. For this reason since 2005 the two major GPU vendors, Nvidia and AMD, have proposed fully programmable processing units, called General Purpose GPU (GPGPU), that support non-graphics development frameworks, such as Nvidia CUDA [19], AMD CAL [20], and AMD Brook+ [21]. However, they still separate between CPU and GPU-based code.

The increasing flexibility of GPUs has enabled many applications outside the original narrow tasks for which GPUs were originally designed, but many applications still exist for which GPUs are not (and likely never will be) well suited. Word processing, for example, is a classic example of a "pointer chasing" application, dominated by memory communication and is difficult to parallelize.

This presents a set of challenges in algorithm design. One problem facing the designers of parallel and distributed systems is how to simplify the writing of programs for these systems and to augment the adaptivity of software to current, as well as, future architectures. Proposals range from automatic program transformation systems [22, 23, 24, 25, 26] that extract parallelism from sequential programs, to the use of side-effect-free languages [27, 28, 29, 30], to the use of languages and systems where the programmer must explicitly manage all aspects of communication, synchronization, and parallelism [20, 19, 31]. The problem with fully automatic schemes is that they are best suited for detecting fine grain parallelism because programmers do not fully describe the semantics of a domain, depriving the translator of high level optimizations, besides explicit parallel programming may complicate the programming task.

The need for flexibility is not related to GPU programming only but also for execution environments. In particular, in the last few years research interest has been progressively increasing in Virtual Execution Environments (VEEs), such as Java Virtual Machine (JVM) [32] and .NET Common Language (CLR) [33]. VEEs are appreciated for many reasons, such as program portability across different architectures, the ability to monitor program execution, which has proven important to enforce security aspects, the tailoring of execution onto specific architectures, and certain capabilities such as dynamic loading and reflection, which allow programs to adapt their execution depending on several environment factors, including the underlying computing architecture.

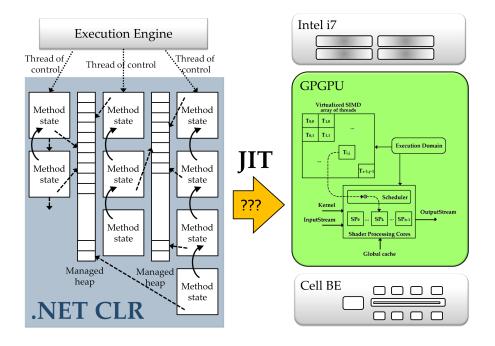

VEEs abstract aspects of the host execution environment by interposing a layer that mediates program execution through dynamic examination and translation of the program's instructions before its execution on the host CPU, as illustrated on Figure I.2. In VEEs' design was inspired by mid-90's architectures, single CPU with Von Neumann model dominating the scene when they emerged, making it harder to exploit the computing power made available by new special-purpose processors, such as GPUs and Cell BE, in a seamless way.

Figure I.2: The CLR's Multiple Instructions Multiple Data computational model is different from the GPUs' SIMD one. How does a JIT compiler can map these models?

In fact, the Just-In-Time (JIT) compiler module of a virtual machine can hardly exploit the power of these non-conventional processing units, since the program is expressed in an intermediate language (IL) for an abstract computation system not providing explicit representation for them. Nevertheless, there are ways to access these new computing processors by exposing specific services that bypass the VEE services.

The diverging gap between the abstract definition of the computing system and the actual architecture may significantly affect the ability of VEE programs to really exploit the computing power of modern systems, possibly undermining the whole approach eventually abandoning it altogether and losing the many benefits that come with these VEEs. An alternative may be an acceptance that the real scope of these virtual execution environments cannot eventually avoid the need for an underlying layer of software, that coordinates pre-written software exploiting these capabilities through VEE interoperability services, as it was for Visual Basic programmers when their world was limited to the available set of C++ based COM components.

### I.2 Problem statement

This thesis focuses on the problem of exposing non-conventional computing devices to VEE programs without changing the VEE base definition. Even though the problem may be tackled for specific computing devices such as GPUs or Cell BE, we will consider it from a broader perspective of exposing models of parallel computing into VEEs using a general and consistent approach showing that there is no need for a general redesign of these execution environments to adapt to non-conventional computing systems.

## I.3 Research scope

To assist the reader, we summarize the key boundaries from the outset.

#### Models of parallel computation

Modern microprocessor architectures have considerably changed from the past: from the classical *Von Neumann* architecture to the current SIMD architecture of the GPU and the multi-core architecture of the Cell BE microprocessor. Each one of these microprocessors is completely different from the other in computational, memory and programming models. For these reasons, on expression of computational models at VEE level of abstraction, we considers two classes of parallel execution models based on shared and distributed memory respectively. Indeed, our work is not tailored to a specific architecture or execution model.

#### Parallelism exploitation

Indeed, the correct and efficient design of parallel programs requires to consider several different concerns, that are difficult to separate during program development. How the computation is performed using processing elements (such as processes and threads), and how these communicate, are non-functional aspects of a program since they do not contribute to define the result of the computation but only how it is performed.

#### • Existing approaches

Several complementary approaches may help programmers achieve the construction of parallel applications.

A way to deploy concurrency without need of change in the programming model encapsulate concurrency together with domain knowledge in common reusable library components [34, 35, 36]. For example, Tarditi et al. [37] have developed a library, named *Accelerator*, that uses data parallelism to program GPUs for general purpose uses under .NET CLR. The main advantage is that no aspect of the GPU is exposed to the programmers, only high level dataparallel operations: the programmer must use specific data(-parallel) types to program the GPU instead of the CPU. This technique can work very well, although use of multiple such libraries in the same program requires better synchronization and resource management techniques than are currently available.

Another approach integrates concurrency and coordination into traditional languages. To build parallel applications, traditional sequential languages are extended with new features to allow programmers to explicitly guide program decomposition into parallel subtasks, as well as provide atomicity and isolation when those subtasks interact with shared data structures [38, 31, 39, 29, 19, 20]. For instance, IBM X10 [29] extends the Java sequential core language with non-functional aspects (e.g. *place, activities, clocks*, (distributed, multi-dimensional) arrays, etc.) to expose a "virtual shared-memory multi-processor" computational model.

A different technique raises semantic level to eliminate explicit sequencing. Parallelism can be more effectively exploited by avoiding procedural languages and using domain-specific systems based on rules or constraints [27, 21, 40, 41, 28]. Programming styles that are more declarative specify intent rather than sequencing of primitives and thus inherently permit parallel implementations that leverage the concurrency and transaction mechanisms of the system. For instance, the RapidMind Development Platform [42] allows developers to use standard C++ to create concurrent/parallel applications that run on GPUs, the Cell BE, and multi-core CPUs. It provides a single unified programming model, adding types and procedures to standard ISO C++ and relying on a dynamic compiler and run-time management system for parallel processing. OpenGL [43] and DirectX10 [44] is another successful domain-specific declarative API for graphics workloads. Many more systems have been proposed in the long history of parallel programming and we will discuss those more relevant to our work throughout the dissertation.

• Our approach

To efficiently develop general-purpose applications that are accelerated by the special-purpose architectures, a different approach is needed with respect to

xiv

#### I.3. RESEARCH SCOPE

those emerging for specific systems such as Nvidia CUDA and AMD CAL on GPUs: the software developer creates the complete "software" that contains code for the main and special-purpose processors at the same time. This means that there is a single development environment, where the same programming language is used to define CPU and, for instance, GPU-based code side by side, and no binding code is required that connects the variables of the different processor platforms.

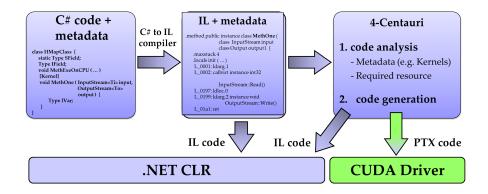

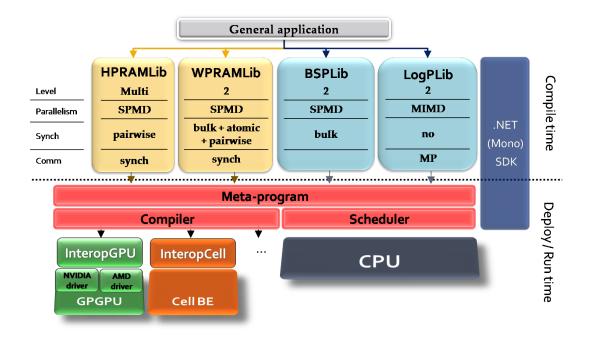

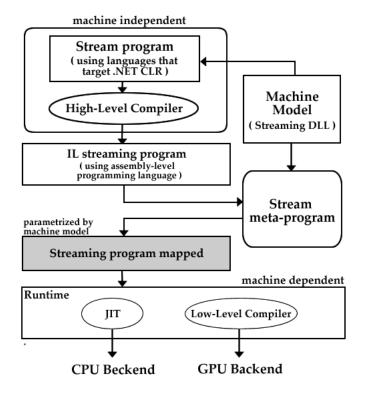

Subscribing the "separation of concerns" concept, typical of Aspect Oriented Programming (AOP) [45], we recognize the importance in our solution of using proper tools to program the non-functional aspects related to parallelism exploitation, e.g. optimizations, communication and synchronization management, etc. We propose a set of types and meta-data that can be used by programmers to consciously "suggest" how a parallel application can be automatically derived from the code. This is different from the standard AOP approach where join points are defined using patterns, making the programmer unaware of program transformation details that will be applied afterwards. Our underlying assumption is that the programmer can make better granularity and partitioning decisions, while the compiler can correctly manage synchronization. Since those types and meta-data express the main features of a parallel execution model, our meta-program, called **4-Centauri**, can derive how to compile source code to exploit a special-purpose architecture capabilities, as shown in Figure I.3.

Figure I.3: The 4-Centauri compiler: first a IL code is parsed to find out through annotations, which part will execute on a CPU and which will execute on GPU, if available; then two layer of abstraction in code manipulation are given: one more generic used for basic class file manipulation that leverages the CLR, and one more specific for GPU intermediate code (e.g. Nvidia PTX) generation that leverages the Nvidia CUDA driver.

This way it is possible to preserve the illusion of the system directly executing the program as the programmer wrote it, with no user-visible optimizations. This constraint has several consequences that distinguish our work from other optimizing compiler implementations:

- Programmers are free to edit any procedure at the CLI level, keeping in mind which is the execution model of their implementation.

- Programmers are able to understand the execution of the program and any errors in it solely in terms of the source code and the source language constructs. This requirement on the debugging and monitoring interface to the system disallows any internal optimizations that would shatter the illusion of the implementation directly executing the source program as written. Programmers should be unaware of how their programs get compiled or optimized.

- The programmer should be isolated even from the mere fact that the programs are getting compiled at all. No explicit commands to compile a method or program should ever be given, even after programming changes. The programmer just runs the program.

**4-Centauri** is a compiler prototype developed as proof-of-concept. Since it is a prototype, we limit our consideration of computational models to the special-purpose one provided by GPUs.

#### Virtual Execution Environment

Although VMs in the form of *abstract machines* have been around for a long time (since the mid-1960s) [46, 47], the advent of Java has made them a common technique for implementing new languages, particularly those intended for use in heterogeneous environments. One of the reasons of this success is due to the (extensible) *reflection model* provided by VEEs. They enable dynamic access to the representation of the application, and allow the program to change its behavior while running depending on its current execution state [48, 49]. This dissertation describes an extension to a particular class of run-time support that we call Strongly Typed Execution Environment (STEE) whose relevant members are Sun JVM and Microsoft CLR.

**Strongly Typed Execution Environment (Model).** A STEE provides an extensible type system and reflection capabilities. It guarantees both that types can be established at run-time, and values are only accessed by using the operators defined on them. STEE has information about running programs, such as the state and liveness of local variables in a method; all extant objects and object references, including reachability information. Examples of STEE are the Common Language Infrastructure (CLI), the Common Language (CLR) and the Java Virtual Machine (JVM).

We limit our consideration of STEE to CLI because:

#### I.4. RESEARCH CONTRIBUTIONS

- CLI is the standard ECMA 335 [1].

- CLI is language neutral and enables multi-language applications to be developed. To assist this interoperability, a Common Type System (CTS) [1] is defined together with a Common Language Specification (CLS) [1] a set of rules that each component of the application must obey.

- there is a world-wide community of developers that uses CLI, in particular its implementations CLR, under Windows, and Mono, under Linux systems.

### I.4 Research contributions

The main contributions of this thesis are:

- We show how to express the main features of the above mentioned models at VEE level without making any changes neither to the VEE design nor to its modules (e.g. JIT).

- We provide a feasible mapping between main models of parallel computations and that exposed by the VEE such as CLI, so that this work is not tailored to neither a specific architecture nor a single execution model.

- We introduce a meta-program, named **4-Centauri**, that translates a Common Intermediate Language (CIL) [1] program into a modern, mass-market, special-purpose architecture intermediate language program, such as Nvidia PTX. The goal is to provide a single and unified programming model without losing expressiveness, forcing the use of a single source language or changing the design of the VM itself.

Since we are interested in defining suitable mappings between abstract parallel computing models and VEEs resources we give a formal specification for each fundamental model of parallel computation useful to understand if and how it can be exposed into the execution environment in a consistent way. These specifications will be well-suited to study their main features, by using the Abstract State Machines (ASM) framework.

## I.5 Organization and Reading plans

The thesis is structured as follows:

• Chapter 1 surveys the main models of parallel execution highlighting their computational, memory, and execution aspects that are most relevant for our

purposes. For each of them, a formal specification is given by using the Abstract State Machine (ASM) method, a mathematically well-founded framework for system design and analysis. To make this thesis self-contained, a basic introduction to ASM is provided in this chapter.

- Chapter 2 provides a basic introduction to the Virtual Execution Environment (VEE) design and capabilities, in particular of a special type of VEE, named Strongly Typed Execution Environment (STEE). Therefore, it reviews existing approaches for exposing underlying architecture features to STEEs level. It introduces our approach based on types and meta-data, and, for each model of parallel execution, presents a mapping on the CLI leveraging ASM model defined in the previous chapter. In particular, it focuses on GPGPUs mapping on CLR, providing a formal definition and a proof of correctness of it.

- Chapter 3 reviews different approaches to parallel programming that have been studied and have inspired our solution. In particular, our discussion focuses on GPGPUs existing main programming languages: Nvidia CUDA, AMD CAL, Nvidia PTX and AMD IL.

- Chapter 4 introduces our implementation of the mapping between GPGPUs and CLR, named **4-Centauri**. This meta-programming tool is able to translate Common Intermediate Language (CIL) to Nvidia PTX language leveraging special meta-data provided by programmers. A detailed description of **4-Centauri** design and main features are provided. At the end of this chapter, some examples of compilation are presented.

- Chapter 5 provides the evaluation of the **4-Centauri** compiler by using a classical algorithm in graphics.

- Chapter 6 presents the conclusions of this thesis and discusses future work.

# Chapter 1

## Models of execution

While new hardware architectures offer much more computing power, they make writing software that can fully benefit from the hardware much harder. In scientific applications, improved performance has historically been achieved by having highly trained specialists modify existing programs to run efficiently as new hardware became available. However, rewriting programs is far too costly, so most organizations focused on rewriting small portions only of the mission critical programs called Kernels. In the optimal case, mission-critical applications spent 80%-90% of their execution time in these *Kernels*, which represent a small percentage of the application code. This rewriting was time consuming, and organizations had to balance the risk of introducing subtle bugs into well-tested programs against the benefit of increased speed at every significant hardware upgrade. All bets were off if the organization did not have the source code for the critical components. In contrast, commercial vendors have become accustomed to a world where all existing programs get faster with each new hardware generation. Software developers could confidently build new innovative software that barely run on the then current hardware, knowing that it would run quite well on the next generation machine at the same cost. This will no longer occur for sequential codes, but the goal of new software development tools must be to retain this very desirable characteristic as we move into the era of many-core computing. Designers of parallel algorithms for modern computers have to face at least four sources of considerable challenges. First, the underlying computational substrate is much more intricate than it is for conventional sequential computing, thus the design effort is much more onerous. Second, the resulting algorithms have to compete with and outperform existing sequential algorithms that are often better understood and highly optimized. Third, the ultimate reward of all this effort is limited, at best a speedup of a constant factor: the number of processors. Fourth, machines differ, and speedups obtained on one machine may not translate to speedups on others, resulting in a design effort that may be substantially wasted. A good computational model can simplify the complicated work of the software architect, algorithm designer and program developer while mapping their work effectively onto real computers. Such a computational model is sometimes also called

Bridging model [50]. The bridging model between the sequential computer and algorithm designer/program developer is the Von Neumann [51] and RAM (Random Access Machine) Model [52]. However, no commonly recognized bridging models are found between parallel computer and parallel programs, and no other model exists that can map a user's parallel program so smoothly onto parallel computers as the Von Neumann and RAM Model do. This situation is largely due to the immature parallel computer design that should take into account many different architectures for parallel computers that change rapidly each year.

Skillicorn presents three requirements for a model of parallel computation [53]:

- architecture independence, a model is general enough to represent a range of architecture types;

- congruence over an architecture, the real costs of execution on that architecture are reflected at the model level;

- intellectual manageability, a model must abstract away from the task of specifying and managing the parallelism.

There are several levels at which a model of parallel computation may exist, that are classified by McColl [54].

In the following sections, we examine models principally identified as *cost model* in the McColl's classification. For each model we developed a formal representation of its datapath. Our ground model is uniform to architectural features such as the register-file size, the datapath width, the instruction set, etc. We focus on describing how different models of parallel computation access memory. Therefore, we abstract all the instructions that are not related to memory management. We consider that the computational task of a processor is specified as an ordered sequence of instructions. The execution of the instructions follows a state transition semantics, therefore the models described in following sections behave like a finite state machine. Each execution phase is reflected in our ground models by control states. For these reasons our formal representations are based on the Abstract State Machines (ASM) method.

As proven in [55, 56, 57], ASMs have introduced a software design and analysis method which provides the right level of abstraction to capture the essential characteristics of existing architectural models and to describe them in a simple, uniform manner that clearly defines functionalities.

The method bridges the gap between non-HPC<sup>1</sup> programmers understanding and formulation of real-world architectures and the deployment of their algorithmic solutions by code-executing machines on changing platforms (i.e. special-purpose

<sup>&</sup>lt;sup>1</sup>High Performance Computing

architectures). It covers within a single conceptual framework both design and analysis, for procedural single-agent (e.g. single processor CPU) and for asynchronous multiple-agent systems (e.g. multi-core CPU and many-core GPUs).

## 1.1 A brief introduction to the Abstract State Machines

ASMs represent a mathematically well founded framework for system design and analysis introduced by Gurevich as Evolving Algebras [58]. At the end of '90 Börger and Stärk in [56] have applied ASMs to the software engineering allowing to build models in a faithful and objectively checkable manner. Therefore, using ASMs is possible to turn descriptions expressed in application domain (e.g. model of parallel computations) into precise abstract definitions, which we were comfortable to manipulate as a semantically well-founded form of pseudo-code over abstract data.

#### 1.1.1 Basic (single-agent) ASM

The ASMs are defined in [55, 56]. A brief summary is presented here in order to make the thesis self-contained.

An basic (single-agent) ASM is a transition system which transforms structures of a given signature, i.e. finite sets of so called transition *rules* of form

#### if Condition then Updates

where the *Condition* is a closed predicate logic formula of the underlying signature without free variables, whose interpretation evaluates to true or false. *Updates* is a finite set of assignments of the form  $f(t_1,...,t_n) := t$  whose execution is to be understood as changing (or defining if there was none) in parallel the value of the occurring functions f at the indicated arguments to the indicated value. The notion of ASM *states* is the notion of mathematical structures where data come as abstract objects, i.e. as elements of sets (also called *domains* or *universes*, one for each category of data), which are equipped with basic operations and predicates.

In any given state, first all parameters  $t_i$ , t are evaluated to their values, say  $v_i$ , v, then the value of  $f(v_1,...,v_n)$  is updated to v which represents the value of  $f(v_1,...,v_n)$  in the next state. Such pairs of a function name f and an argument  $(v_1,...,v_n)$  are called *locations*, location-value pairs (loc, v) are called *updates*.

An ASM computation step in a given state consists in executing simultaneously all updates of all transition rules whose guard is true in the state, if these updates are consistent, in which case the result of their execution yields the next state. In the case of inconsistency the computation does not yield a next state. A set of updates is called consistent if it contains no pair of updates with the same location, i.e. no two elements (loc, v), (loc, v') with  $v \neq v'$ .

Simultaneous execution is enhanced by the following notation to express the simultaneous execution of a rule R for each x satisfying a given condition  $\varphi$ :

```

forall x with \varphi

R

```

where  $\varphi$  is a Boolean-valued expression that determines which x is/are applicable, and R a rule. Typically, x will have some free occurrences in R which are bound by the respective quantifier.

Similarly non-determinism can be expressed by rules of the form

```

\begin{array}{c} \textbf{choose} \ x \ \textbf{ with } \varphi \\ \mathbf{R} \end{array}

```

where  $\varphi$  is a Boolean-valued expression and R a rule. The meaning of such an ASM rule is to execute rule R with an arbitrary x chosen among those satisfying the selection property  $\varphi$ . If there exists no such x, nothing is done. It is possible to use combinations of **where**, **let**, **if** - **then** -**else**, etc. which are easily reducible to the above basic definitions. When dealing with multi-agent systems we use sets of agents each executing its own ASM.

#### 1.1.2 Control State ASM

In the rest of the thesis we use a special class of ASMs, called *control state ASMs*, which allows one to define machines providing the main control structure of Finite State Machines (FSMs) synchronous parallelism and the possibility to manipulate data structures. A *control state* ASM is an ASM whose rules are all of the following form:

```

\begin{array}{ll} \text{if } ctl\_state = i & \text{then} \\ \text{if } cond_1 & \text{then} \\ rule_1 \\ ctl\_state := j_1 \\ & \dots \\ \text{if } cond_n & \text{then} \\ rule_n \\ ctl\_state := j_n \end{array}

```

The finitely many control states  $ctl\_state \in 1,...,m$  resemble the so-called 'internal' states of FSMs. In a given control state *i*, these machines do nothing when no condition  $cond_i$  is satisfied.

#### 1.1.3 ASM Multi-agents

In [56] the single-agent ASMs are extended to two kind of multi-agent ASMs: synchronous (sync ASM) and asynchronous ASMs (async ASM), which support modularity for design of large systems. A multi-agent synchronous ASM is defined as a set of agents which execute their own basic ASMs in parallel, synchronized using an implicit global system clock. Semantically async ASM is equivalent to the set of all its constituent single-agent ASMs, operating in the global states over the union of the signatures of each component. The practical usefulness of sync ASMs derives from the possibility of equipping each agent with its own set of states and rules and of defining and analyzing the interaction between components using precise interfaces over common locations.

An asynchronous ASM is given by a family of pairs (a, ASM(a)) of pairwise different agents, elements of a possibly dynamic finite set AGENT, each executing its basic ASM ASM(a). A run of an *async* ASM, also called a partially ordered run is a partially ordered set (M, <) of moves (execution of rules) m of its agents satisfying the following conditions:

- finite history: each move has only finitely many predecessors, i.e. for each m∈ M the set {m'|m' < m} is finite;</li>

- sequentiality of agents: the set of moves  $\{m | m \in M, a \text{ performs } m\}$  of every agent  $a \in Agent$  is linearly ordered by <;

- coherence: each finite initial segment X of (M, <) has an associated state  $\sigma(X)$ , i.e. the result of all moves in X with m executed before m' if m < m', which for every maximal element  $m \in X$  is the result of applying move m in state  $\sigma(X m)$ .

The moves of the single agents can be atomic or durative, but for simplicity the preceding definition of distributed runs assumes actions to be atomic. Multi-agent ASMs provide a theoretical basis for a coherent global system view for concurrent sequential computations of single agents, each executing its own sequential ASM, at its own pace and with atomic actions applied in its own local states, including input from the environment as monitored functions.

The relation between global and local states is supported by the use of the reserved name *self* in functions and rules to denote the agents which are executing the underlying "same" but differently instantiated basic or sync ASM, similar to the use of *this* in object-oriented programming to denote the object for which the currently executed instance method has been invoked.

### **1.2** Models of Sequential execution

Before examining models of parallel execution, a brief introduction is made of RAM, the simplest model of sequential execution, providing the background from which the models of parallel execution were developed. After RAM, we will present  $RAM_L$  that extends the RAM ASM model with race condition managements rules.

#### 1.2.1 RAM

The random-access machine (RAM) models the essential features of the traditional sequential computer. The RAM is modeled by a Finite State Machine, a central processing unit, (CPU). It implements a fetch-and-execute cycle in which it alternately reads an instruction from a program stored in the random-access memory and executes it. In the RAM model there are two types of memory that differ in size and access speed: a register-file RF, that is a very fast memory but it has a small number of storage units, and a random-access memory, that is slower than RF but it has a large number of storage units. All operations are performed by the CPU on data stored in its registers.

**Definition 1.2.1.** The **RF** is the single processor local memory that can be accessed by only one agent at a time.

A CPU typically has a set of instructions, such as arithmetic and logical ones, memory load and store ones for moving data between memory locations and registers, etc. A RAM program is a finite sequence of assembly language instructions. A valid program is one for which each jump instruction goes to an existing label. We assume for simplicity of exposition and without loss of generality that the last instruction of code is HALT. Since we are not interested here in what a CPU computes during its execution, our view of use and assignment actions is simple: an assignment action changes the value of either a memory unit or a register, and a use action does nothing; for this reason we introduce the NOP macros.

#### ASM ground model

We start by developing a simple abstract mathematical model, called M, of the RAM processor architecture, which is the starting point for the stepwise formalization of other processor architectures. In our model we define the following universes:

- UNITADDR is a memory  $unit^2$ .

- VAL is the data held in either a memory unit or a register.

- REGISTER is the finite set of registers in the RF .

- OPCODE = {HALT, OTHER, LOAD, STORE, LOCK, UNLOCK, SEND, RECEIVE}.

- INSTRUCTION is the instruction set of a processor<sup>3</sup>.

<sup>&</sup>lt;sup>2</sup>Based on the real architecture, a memory unit can be either a location, page, or segment. <sup>3</sup>In literature this set is also called Instruction Set Architecture (ISA)

#### 1.2. MODELS OF SEQUENTIAL EXECUTION

- VALIDINSTR = {HALT, OTHER, LOAD, STORE}. This is the sub-set of instructions that can be executed by the current machine M.

- EXECUTOR  $\subseteq$  AGENT, a sub-set of all possible agents. Each agent, called *executor*, executes a list of instructions selected from the INSTRUCTION set.

And we introduce the following functions:

• static

- op: INSTRUCTION  $\rightarrow$  OPCODE returns the opcode of a given instruction.

- memUnitAdr : INSTRUCTION  $\rightarrow$  UNITADDR returns the address of the given instruction.

- value : INSTRUCTION  $\rightarrow$  VAL returns the value of a given instruction's operand.

- controlled

- regfile : REGISTER  $\rightarrow$  VAL returns the value held in the given register

- $-mem: UNITADDR \rightarrow VAL$  returns the value held at the given address

- monitored

- legal : INSTRUCTION × EXECUTOR  $\rightarrow$  BOOLEAN returns true if a given executor executes a given instruction  $\in$  VALIDINSTR at all points in time.

We define two functions for memory access because of cost difference in access time required for different types of memory.

The main rule of M provides a formal model of the RAM processor fetch-and-execute cycle:

$M(e) \equiv$ case state(e) ofFetch : FETCH(e)Execute : EXEC(currinstr(e), e)

where *currinstr* holds the current instruction that is executed by an executor e, and *state* holds the current state of M. We have defined two macros, *FETCH* and *EXEC*, one for each phase of the fetch-and-execute cycle. When *state*(e) is equal to *FETCH*, M non-deterministically chooses the next instruction to execute. The *state* is updated to *Execute* such that in the next run M will execute the *EXEC* macro. Following are the rules for both macros:

$\begin{aligned} \textbf{FETCH}(e) &\equiv \\ \textbf{choose } instr \textbf{ in INSTRUCTION with } legal(instr, e) \textbf{ in} \\ currinstr(e) &:= instr \\ state(e) &:= Execute \end{aligned}$

Which instruction is selected depends on the result given by the *legal* function. This function guarantees that, given a  $e \in \text{Executor}$ , M(e) never computes any instruction  $\notin \text{VALIDINSTR}$ .

```

\begin{split} \textbf{EXEC}(instr, e) &\equiv \\ \textbf{case} \ op(instr) \ \textbf{of} \\ \text{HALT} : HALT(e) \\ \text{STORE} : STORE(memUnitAdr(instr), val(instr), e) \\ \text{LOAD} : LOAD(memUnitAdr(instr), reg(instr), e) \\ \text{LOCK} : LOCK(memUnitAdr(instr), e) \\ \text{UNLOCK} : UNLOCK(memUnitAdr(instr), e) \\ \text{SEND} : SEND(d, value, e) \\ \text{RECEIVE} : RECV(s, destReg, e) \\ \text{OTHER} : NOP \end{split}

```

To move data between memory units and RF in a RAM processor, there are two memory instructions: *load* and *store*. Reading data means to access a memory unit at the address held in a register and load it in another register. Writing data means to store data in a memory unit at the address held in a given register. This is formalized in the following two rules:

| $LOAD(adr, reg, e) \equiv$  | $STORE(adr, value, e) \equiv$ |

|-----------------------------|-------------------------------|

| regfile(reg, e) := mem(adr) | mem(adr) := value             |

| state(e) := Fetch           | state(e) := Fetch             |

In this RAM model the other macros do not change the state of M.

| $LOCK(adr, e) \equiv$                | $\mathbf{SEND}(d, value, e) \equiv$       | $HALT(e) \equiv$                     |

|--------------------------------------|-------------------------------------------|--------------------------------------|

| NOP                                  | NOP                                       | $\mathit{state}(e) := \mathit{idle}$ |

| $\mathbf{UNLOCK}(adr, e) \equiv NOP$ | $\mathbf{RECV}(s, destReg, e) \equiv NOP$ |                                      |

| NOP                                  | NOP                                       |                                      |

When M executes the HALT macro, the control state is updated to *idle*. This means that no more updates to the M' state will be performed. The assumption for the initial state of M is:

- state(e) := Fetch

- currinstr(e) := undef

# **1.2.2** $RAM_L$ : **RAM ASM** model with race conditions management

In this section we refine the basic single-core architecture of the RAM model considering a multiple threads running on the same processor. In this scenario, multiple executors act concurrently, therefore we must introduce new rules to manage synchronization problems; i.e. conflicts on shared resources which could result when concurrent executors access the same memory units at the same time. For this reason:

1. we extend the VALIDINSTR universe with two instructions, LOCK and UNLOCK, such that the new set of valid instructions is:

VALIDINSTR = {HALT, OTHER, LOAD, STORE, LOCK, UNLOCK}

- 2. we define three new functions:

- $owner: UNITADDR \rightarrow EXECUTOR$ returns the executor that has obtained a lock on a given memory unit address

- lockcnt: UNITADDR × EXECUTOR  $\rightarrow$  INTEGER counts the number of locks required by a given executor on a unit of memory. For *lockcnt* there is a injective function *succ* (the successor function) such that *succ*(lockcnt) is a natural number.

- locked: UNITADDR × EXECUTOR  $\rightarrow$  BOOLEAN where

$locked(adr, e) = \begin{cases} true & lockcnt(adr, e) > 0\\ false & otherwise \end{cases}$

3. we define two new macros, *LOCK* and *UNLOCK*, that are used by executors to acquire and release locks on a given address. They are formalized in the following two rules:

```

\begin{aligned} \textbf{LOCK}(adr, e) &\equiv \\ \textbf{if} \ owner(adr) &= e \ \textbf{then} \\ \ lockcnt(adr, e) &:= \ lockcnt(adr, e) + 1 \\ state(e) &:= \ Fetch \\ \textbf{else} \\ \textbf{if} \ owner(adr) &= \ undef \ \textbf{then} \\ \ owner(adr) &:= \ e \\ \ lockcnt(adr, e) &:= \ 1 \\ state(e) &:= \ Fetch \end{aligned}

```

In the second *else* branch, the state(e) := Execute such that in the next run the LOCK instruction will be executed continuously until the *owner*(adr) is either equal to *e* or *undef*.

```

\begin{aligned} \textbf{UNLOCK(adr,e)} &\equiv \\ \textbf{if } owner(adr) &= e \textbf{ then} \\ \textbf{if } lockcnt(adr,e) &= 1 \textbf{ then} \\ owner(adr) &:= undef \\ lockcnt(adr,e) &:= lockcnt(adr,e) - 1 \\ state(e) &:= Fetch \end{aligned}

```

where the dynamic function *lockcnt* the number of times an agent has to exit the LOCK before it is released, and *owner* returns the executor that has obtained the current lock.

The main rule of M and both the FETCH and EXEC macros remain unchanged in this model.

#### Data transfer from to memory

To avoid race conditions for each memory access the processor must first check whether or not an executor has already requested a lock on a given address. This is done by calling the static function *locked*:

| $	t LOAD(adr,reg,e) \equiv$                                      | ${\sf STORE}({\sf adr},{\sf value},{\sf e})\equiv$ |  |  |

|------------------------------------------------------------------|----------------------------------------------------|--|--|

| $\mathbf{if} \ \mathit{locked}(\mathit{adr}, e) \ \mathbf{then}$ | $\mathbf{if} \ locked(adr, e) \ \mathbf{then}$     |  |  |

| regfile(reg, e) := mem(adr)                                      | mem(adr) := value                                  |  |  |

| state(e) := Fetch                                                | state(e) := Fetch                                  |  |  |

In both macros, if a given adr is locked by another executor, the state(e) := Execute, such that in the next M runs the lock test will continue to be performed, until the lock on that adr will be released.

The assumption for the initial state of M is:

- state(e) := Fetch

- currinstr(e) := undef

- owner(adr) := undef, for all  $adr \in UNITADDR$

- lockcnt(adr,e) := 0, for all  $adr \in UNITADDR$  and  $e \in EXECUTOR$

There is an important theorem to state about synchronization management.

**Theorem 1.2.2.** Let  $e \in \text{EXECUTOR}$ , and let  $adr \in \text{UNITADDR}$ , UNLOCK(adr, e) does not release a lock that e has not acquired on adr before.

*Proof.* Since the LOCK(adr, e) will update the control state variable state(e) to *Fetch*, and execute the next instruction, iff e acquires a lock on adr.

#### **1.3** Models of Parallel execution

Having introduced the main models of sequential execution, this section surveys a selection of models of parallel execution. Parallel computation models can be classified into two categories according to the memory model of their target parallel computers: shared and distributed memory models [59, 60]. For each model we highlight three fundamental aspects: memory and synchronization management, and communication cost.

#### 1.3.1 Shared memory

#### PRAM

With the success of the RAM model for sequential computation, a natural way to model parallel computation is to extend this model with parallel processing capability: P independent processors that share one common global memory pool. Such parallel computational model, named PRAM, was first proposed by Fortune and Wyllie [61]. It consists of an unbounded number, P, of processors working synchronously. Execution may be in either SIMD<sup>4</sup> or MIMD<sup>5</sup> mode, thus with a single or multiple flows of control respectively.

**Synchronization.** The RAM processor can execute instructions concurrently in unit time and in lock-step with automatic and free synchronizations.

**Memory levels.** Each processor is a RAM machine with a set of registers rather than a local memory. All processors share an unbounded global memory, via which they communicate. With the only memory being the global memory, this is a one-level memory model.

**Memory access.** Concurrent access to the global memory is allowed and only takes one unit of time to be finished. There are several variations of the PRAM model [59] which make different assumptions on concurrent memory access arbitration mechanism. The less restricted variation is the CRCW PRAM model, which allows concurrent read and concurrent write to the same memory unit with a mechanism for arbitrating (Priority, Common and Arbitrary) simultaneous writes to the same unit. By restricting the simultaneous write to one processor, the CREW PRAM model was proposed in [61]. In such a model, simultaneous read to the same unit was still allowed while only one processor may attempt to write to a unit. The most restricted form of the PRAM model is the EREW PRAM model, which requires that no two processors can simultaneously access any given memory unit.

<sup>&</sup>lt;sup>4</sup>Single Instruction, Multiple Data

<sup>&</sup>lt;sup>5</sup>Multiple Instruction Multiple Data

Advantages. Algorithm designers can focus on the fundamental computational difficulties and on the logical structure of parallel computations required to solve the problem. It is easy to program because it is a simple extension of the RAM model: the instruction set is composed of the RAM one plus a global read and write. It hides issues like reliability, synchronization, message passing, and other machine-related problems. The basic work measure is the product of the time to perform the algorithm and the number of processors used. This model provides a total expressibility, since there are no constraints on the forms of computation and communication which may be performed.

Disadvantages. It does not take into account the latency and bandwidth costs of communication. There is no abstraction from managing many parallel threads and synchronization. Since the PRAM is too abstract for realistic implementation, there are several variants that take into account different aspects of parallel architecture: asynchrony (APRAM [62] and Asynchronous PRAM [63]), memory contentions management (Module Parallel Computer [64]), latency (LPRAM [65] and BPRAM [66]), and hierarchical parallelism (YPRAM [67]).

**ASM ground model.** The PRAM model extends the  $RAM_L$  one with two more memory access rules. PRAM considers three different memory access rules: EREW (as for  $RAM_L$ ), CREW and CRCW. For each of these we define different LOADand STORE macros. In the last two rules, the management of read and read/write respectively is left to programmers.

| • <i>EREW</i> (Exclusive Read, Exclusive Write) |                                                |

|-------------------------------------------------|------------------------------------------------|

| $LOAD(adr,reg,e) \equiv$                        | $STORE(adr,value,e) \equiv$                    |

| $\mathbf{if} \ locked(adr, e) \ \mathbf{then}$  | $\mathbf{if} \ locked(adr, e) \ \mathbf{then}$ |

| regfile(reg, e) := mem(adr)                     | mem(adr) := value                              |

| state(e) := Fetch                               | state(e) := Fetch                              |

| • <i>CREW</i> (Concurrent Read, Exclusive Write | e)                                             |

(Concurrent Read, clusive

| $LOAD(adr, reg, e) \equiv$  | SIORE(adr,value,e) =     |

|-----------------------------|--------------------------|

|                             | if $locked(adr, e)$ then |

| regfile(reg, e) := mem(adr) | mem(adr) := value        |

| state(e) := Fetch           | state(e) := Fetch        |

• CRCW (Concurrent Read, Concurrent Write)  $LOAD(adr, reg, e) \equiv$  $STORE(adr,value,e) \equiv$ regfile(reg, e) := mem(adr)mem(adr) := valuestate(e) := Fetchstate(e) := Fetch

The main rule of M as well as the FETCH and EXEC macros and the initial state remain unchanged in this model.

#### 1.3. MODELS OF PARALLEL EXECUTION

#### H-PRAM