Daniele Ludovici

## Performance Analysis of RR and FQ Algorithms in Reconfigurable Routers

Tesi di Laurea Specialistica

Università di Pisa

Anno Accademico 2005/2006

## UNIVERSITÀ DI PISA Facoltà di Ingegneria

Corso di Laurea Specialistica in Ingegneria Informatica

# Performance Analysis of RR and FQ Algorithms in Reconfigurable Routers

## Tesi di Daniele Ludovici

| Relatori:                  |  |

|----------------------------|--|

| Prof. Luciano Lenzini      |  |

| Prof. Cosimo Antonio Prete |  |

| Candidato:                 |  |

| Daniele Ludovici           |  |

Computer Engineering Mekelweg 4, 2628 CD Delft The Netherlands http://ce.et.tudelft.nl/

## Performance Analysis of RR and FQ Algorithms in Reconfigurable Routers

### Daniele Ludovici

Currently, we are witnessing a trend in network routers to include reconfigurable hardware structures to provide flexibility at improved performance levels when compared to software-only implementations. This permits the run-time reconfiguration of the hardware resources, i.e., to change their functionality (for example, from one scheduling algorithm to another), to adapt to changing network scenarios. In particular, different scheduling algorithms are more efficient in handling a specific mix of incoming packet traffic in terms of various criteria (e.g., delay, jitter, throughput, and packet loss). Therefore, reconfigurable hardware is able to provide improved performance levels and to allow more efficient algorithms to be utilized when different incoming packet traffic patterns are encountered. This project investigates the possibilities to improve upon end-to-end delays, jitter, throughput, and packet loss by exploiting the availability of a flexible hardware structure such as an field-programmable gate array (FPGA). The aim of the project is to provide an overview on adaptive scheduling using reconfigurable hardware. Consequently, we investigate different scheduling algorithms that provide QoS provisioning for traffic streams that are sensitive to

packet delay and jitter, e.g., mpeg video traffic. The investigation utilizes the NS-2 simulator for which we generate realistic network scenarios. Our approach is based on understanding which kind of traffic is passing in the network, and subsequently change the scheduling algorithm accordingly in the core router to meet specific performance requirements. The investigated scheduling algorithms are taken from two well-known families, i.e., Round Robin (RR) and Fair Queuing (FQ). Our investigation confirmed the idea on the behavior of the two investigated scheduling algorithm: WFQ outperforms WRR in terms of end-to-end delay, jitter and throughput but it is more expensive than it at a computational level. Nonetheless, it is possible to find a tradeoff between the required area in FPGA and the level of performance desired for a kind of stream.

Faculty of Electrical Engineering, Mathematics and Computer Science

to my family, for the infinite love and support they give me every day of my life

## Contents

| $\mathbf{Li}$             | t of Figures                                           | vii             |

|---------------------------|--------------------------------------------------------|-----------------|

| $\mathbf{Li}$             | t of Tables v                                          | iii             |

| A                         | knowledgements                                         | ix              |

| $\mathbf{R}^{\mathrm{i}}$ | ngraziamenti                                           | x               |

| 1                         | Introduction 1.1 Quality of Service                    | <b>1</b><br>1   |

|                           | 1.1.1 QoS parameters $\dots$ 1.2 Coole 6 Model a labor | 3               |

|                           | 1.2       Goals & Methodology                          | $\frac{4}{5}$   |

| 2                         | Scheduling Algorithms                                  | 7               |

| _                         | 2.1 Classification of Scheduling Algorithms            | 7               |

|                           | 2.2 FIFO (First In First Out)                          | 8               |

|                           | 2.3 Priority Scheduling                                | 8               |

|                           | 2.4 Fair Scheduling Algorithms                         | 9               |

|                           | 2.4.1 Round Robin $\ldots$                             | 9               |

|                           | • 0 0                                                  | 11              |

|                           | 2.5 Summary                                            | 15              |

| 3                         | 1                                                      | 17              |

|                           |                                                        | 17              |

|                           |                                                        | 17              |

|                           | 8                                                      | $\frac{20}{21}$ |

|                           | č                                                      | $\frac{21}{21}$ |

|                           | • 0                                                    | $\frac{21}{22}$ |

|                           |                                                        | $\frac{22}{22}$ |

|                           |                                                        | ${23}$          |

|                           |                                                        | 24              |

|                           |                                                        | 26              |

|                           | 3.5 Competing Streams                                  | 28              |

|                           |                                                        | 28              |

|                           | 3.5.2 Poisson                                          | 28              |

|              | $3.6 \\ 3.7 \\ 3.8$ | Motivation       29         Cost Analysis       31         Summary       32                                               |

|--------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|

| 4            |                     | difications to NS-2       33         Monitor Agent       33         Support for Reconfiguration to the Simulator       37 |

|              |                     | 4.2.1 Reconfiguration Delay                                                                                               |

|              | 4.3                 | Weighted Fair Queuing Implementation                                                                                      |

|              |                     | 4.3.1 Formulas                                                                                                            |

|              |                     | 4.3.2 The code                                                                                                            |

|              |                     | 4.3.3 GPS properties and complexity 48                                                                                    |

|              | 4.4                 | Summary 49                                                                                                                |

| <b>5</b>     | Sim                 | ulations 50                                                                                                               |

| 0            | 5.1                 | Confidence Intervals                                                                                                      |

|              | 5.2                 | Random Variables                                                                                                          |

|              | 5.3                 | Fairness Evaluation                                                                                                       |

|              | 5.4                 | Simulation Scenario                                                                                                       |

|              | 5.5                 | Traffic Load Variation                                                                                                    |

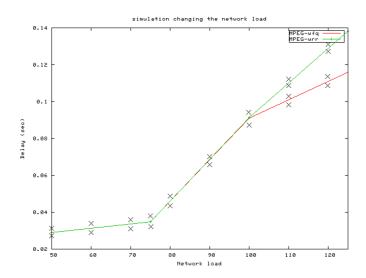

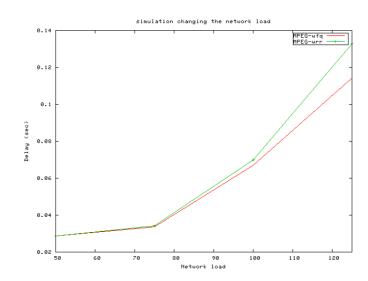

|              |                     | 5.5.1 Delay                                                                                                               |

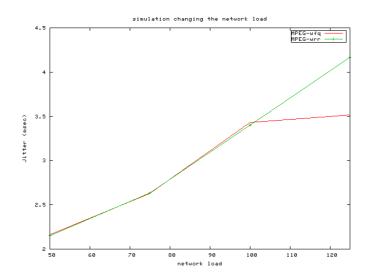

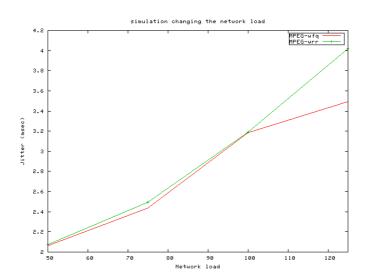

|              |                     | 5.5.2 Jitter                                                                                                              |

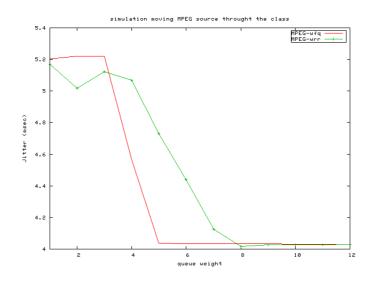

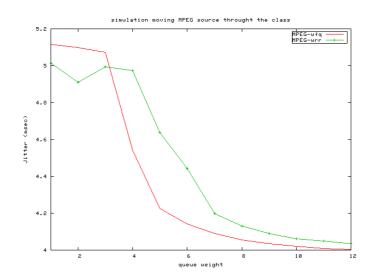

|              | 5.6                 | Queue Weight Variation                                                                                                    |

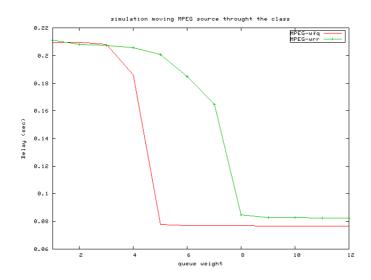

|              |                     | 5.6.1 Delay                                                                                                               |

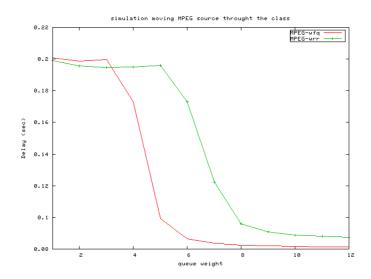

|              |                     | 5.6.2 Jitter                                                                                                              |

|              | 5.7                 | Splitting Traffic                                                                                                         |

|              | 5.8                 | Final Reflections                                                                                                         |

|              | 5.9                 | Summary                                                                                                                   |

| 6            | Cor                 | clusions and Future Research 68                                                                                           |

| 0            | 6.1                 | Summary                                                                                                                   |

|              | 6.2                 | Main contributions                                                                                                        |

|              | 6.3                 | Future Research Directions       69                                                                                       |

|              | 0.0                 |                                                                                                                           |

| Bi           | bliog               | graphy 73                                                                                                                 |

| $\mathbf{A}$ | $\mathbf{MP}$       | EG-4 Source Code 74                                                                                                       |

| В            | Diff                | Serv Module 80                                                                                                            |

| С            | Ove                 | erview on FPGAs 112                                                                                                       |

|              | C.1                 | What is a FPGA                                                                                                            |

|              |                     | C.1.1 Historical Roots                                                                                                    |

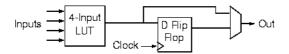

| C.1.2 | Architecture                           |  |  |  |  |  | 114 |

|-------|----------------------------------------|--|--|--|--|--|-----|

| C.1.3 | FPGA design and programming            |  |  |  |  |  | 115 |

| C.1.4 | FPGA with Central Processing Unit Core |  |  |  |  |  | 116 |

|                                                          | 7 MS                                                |  |  |  |  |

|----------------------------------------------------------|-----------------------------------------------------|--|--|--|--|

|                                                          |                                                     |  |  |  |  |

| AF Assured Forwarding                                    |                                                     |  |  |  |  |

| ASCII American Standard Code for Information Interchange |                                                     |  |  |  |  |

| ASIC Application Specific Integrated Circuit             |                                                     |  |  |  |  |

| <b>CBR</b> Costant Bitrate                               |                                                     |  |  |  |  |

| CLB Configurable Logic                                   | Block                                               |  |  |  |  |

| CPLD Complex Programm                                    | able Logic Device                                   |  |  |  |  |

| DRR Deficit Round Robin                                  | 1                                                   |  |  |  |  |

| DSP Digital Signal Proce                                 | ssor                                                |  |  |  |  |

| Diffserv Differentieted Service                          | ces                                                 |  |  |  |  |

| <b>FCFS</b> First Come First Se                          | rved                                                |  |  |  |  |

| FPGA Field Programmable Gate Array                       |                                                     |  |  |  |  |

| <b>FQ</b> Fair Queuing                                   |                                                     |  |  |  |  |

| GPS General Processor S                                  | haring                                              |  |  |  |  |

| IntServ Integrated Services                              |                                                     |  |  |  |  |

| NAM Network Animator                                     |                                                     |  |  |  |  |

| NS-2 Network Simulator                                   | v2                                                  |  |  |  |  |

| <b>OO</b> Object Oriented                                |                                                     |  |  |  |  |

| QoS Quality of Service                                   |                                                     |  |  |  |  |

| PGPS Packet Generalized                                  | Processor Sharing                                   |  |  |  |  |

| <b>RED</b> Random Early Dete                             | ction                                               |  |  |  |  |

| <b>RR</b> Round Robin                                    |                                                     |  |  |  |  |

| SLA Service Level Agree                                  |                                                     |  |  |  |  |

| -                                                        | <b>SLS</b> Service Level Specification              |  |  |  |  |

| <b>SP</b> Strict Priority                                | J                                                   |  |  |  |  |

| <b>TES</b> Transform Expand S                            | Sample                                              |  |  |  |  |

| $W^2FQ+$ Worst Case Weighte                              | W <sup>2</sup> FQ+ Worst Case Weighted Fair Queuing |  |  |  |  |

| WFQ Weighted Fair Queu                                   | ing                                                 |  |  |  |  |

| WRR Weighted Round Ro                                    | bin                                                 |  |  |  |  |

| 1.1                                                         | A QoS-aware Network Model                                                                                                                                                                                            | 2                                                                                                                      |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6$                    | WRR Scheduler                                                                                                                                                                                                        | 8<br>9<br>10<br>11<br>12<br>15                                                                                         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | C++ and OTcl: The DualityArchitectural View of NS-2NAM: Network AnimatorOutputDifferent Queue Management mechanismsScenario with different kind of queuesDevices in a Diffserv DomainAudio and Video in the Internet | <ol> <li>17</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>22</li> <li>25</li> <li>26</li> <li>32</li> </ol> |

| 4.1<br>4.2                                                  |                                                                                                                                                                                                                      | 33<br>37                                                                                                               |

| $5.11 \\ 5.12$                                              | Network Scenario for Fairness Evaluation                                                                                                                                                                             | 53<br>56<br>57<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>64<br>65                                                   |

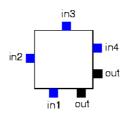

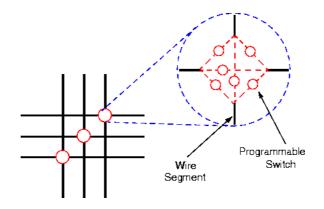

| C.1<br>C.2<br>C.3<br>C.4                                    | FPGA [21]                                                                                                                                                                                                            | 14<br>14                                                                                                               |

| C.5 Xilinx FPGA | 117 |

|-----------------|-----|

|-----------------|-----|

## List of Tables

| Part of TCL code using MPEG4 source                 |

|-----------------------------------------------------|

| Configuration lines to add in the NS-2 default file |

| Excerpt of CBR Tcl code                             |

| Excerpt of Poisson Tcl code 29                      |

| Trace-file Example                                  |

| Set of simulations with reconfiguration 40          |

| Packet drop for Round Robin                         |

| Packet drop for $RR \rightarrow WRR$                |

| Packet drop for WRR                                 |

| Code Mapping Device Delay, C++                      |

| Code Mapping Device Delay, Tcl                      |

| T-Student                                           |

| Tracefile setup                                     |

| Fairness evaluation with MPEG4 and CBR              |

| Fairness evaluation with MPEG4 and Poisson          |

| Fairness evaluation with MPEG4 and our VBR 56       |

| Fairness evaluation with CBR and our VBR 57         |

| Delay evaluation with CBR and our VBR 57            |

| Simulation Plan 1                                   |

| Simulation Plan 2                                   |

| $O_{\rm eff} = M_{\rm eff} + 1$                     |

| Queue Weights                                       |

|                                                     |

## Acknowledgements

This work represents a very important step for my life and i would like to thank all the people that supported me during this period.

First of all, i would like to thank Stephan Wong for the valuable guidance through my work, for his infinite patience and the advice he suggested to me during the development of this thesis. Moreover, the great friendship he showed me from the beginning.

Thanks to Stamatis Vassiliadis for the opportunity he gave me to study in his group and the great confidence shown in all of our discussions.

I really thank all the people i have met in the CE group that have contributed to make this experience unforgettable.

Daniele Ludovici Delft, The Netherlands 2006 Quelle che state leggendo sono le ultime righe che scrivo per completare questo lavoro che è sbocciato nella terra dei tulipani, delle canape e delle bitterballen. E stata una grande avventura per la quale devo ringraziare in ordine sparso le persone che mi hanno accompagnato in questi mesi di soggiorno esterofilo: Giacomino, Sergio, Alessandro, Lecorbudar, Mikko, Dimitris, Arcilio, Yizhi, Maristella, Gino, Mattia, Maximilian, Roberto, Lars, Juhan, gli olandesi di cui non ricordo i nomi, la mia cara Bea, Gianni, Lo Maestro, Joaho, Daniel, Andrea, Roberto, Mauro, Christian, tutti i ragazzi del CE-group che mi hanno sempre fatto sentire a casa e tutte le altre centinaia di persone che ho conosciuto e di cui non mi ricordo in questo momento. I sette mesi olandesi mi hanno dato tanto ma forse mi hanno tolto anche qualcosa... qualcosa che mi ha sempre incoraggiato a non mollare mai e a cercare sempre il meglio per me, per questo non potrò che esserti per sempre grato, grazie Pamy. Prima dei tulipani c'è stata la torre pendente, Pisa mi rimarrà per sempre nel cuore grazie agli amici di casa Guelfi che hanno reso questi anni di permanenza un vivere in famiglia. Peppino e le nostre lunghe chiacchierate. Gabriele, tutta la pasta che m'ha fatto mangiare e i gol che per lui ho rifinito. Daniele e le nottate a vedere Smallville e altre serie TV insieme. Grazie a Stefano e Rocco B. fedeli compagni di corso e impagabili amici di strada. Grazie a Rocco V. per i suoi gol mangiati e la tagliata con la rucola. Grazie a Valerio, il suo saper fotografare e il suo passo felpato nel giocare a calcetto. Grazie ad Andrea, la sua pizza al pesto e il suo saper compilare. Grazie a Giuseppe (Re Artù) Arturi. Grazie a tutte quelle della casa "di la": Maddalena, Elisabetta, Giulia, Cristina, Olga, Anna, Marianeve, Sara, M.Elisa e tutte quelle che non hanno passato il casting ma avrebbero voluto. Grazie a Filippo e il suo folle modo di essermi amico. Grazie a Nino e la siora Baglini per tutta la comprensione dimostrataci nel sopportarci come vicini. Grazie a tutti quelli contro i quali ho inveito giocando a calcetto e che mi hanno lasciato il setto nasale al suo posto. Grazie ad Angelo, Antonio e Massimo. Grazie a Mad-house per le cene al crostino, Elisqui e il suo maledetto gatto, Gianfa e la sua logorroica dolcezza, Francesca e il suo sorridere sempre, Valeria che mi assomiglia in quanto essere panda femmina. Grazie a Gianluca che sopporta Elisqui. Grazie agli amici di Perl.it. Non ci sarebbe stata Pisa senza i 747 metri sul livello del mare più belli del mondo, grazie a tutti i miei amici di sempre, Diego e Sandro, Annalisa e Michela, Donato tuttofare, Verdura e Cilento ormai ballerini, Cervo e Cirillo, Zio Lauro, Carlo, Francesca, Tucio, i cugini Mario e Gianluca, Andrea, Simona e ora anche Alessandro :-), Giovanna, Celentano e Borra, McGuiver e Manganozzo, Piero e Ileana, Francesco che non mi è venuto a trovare e Desy, i cuginetti Luca, Marcolino e Marco, tutti gli zii che ho. Grazie a Mauro per avermi fatto appassionare all'informatica e per esser l'amico unico che è. Grazie a tutti gli insegnanti che ho avuto e in particolare a quelli che mi hanno trasmesso la voglia di viaggiare. Grazie a Zio Spartaco a Zia Graziella. Grazie a Nonna Natalina e Zia Laura per l'immenso amore che avete per me. Un pensiero ai miei nonni che anche da lassù saranno tanto felici.

Grazie a mia madre, mio padre e mio fratello per avermi convinto ad inseguire i miei sogni sempre e comunque.

Daniele Ludovici Delft, The Netherlands 2006

1

Currently, we are witnessing a trend in network routers to include FPGA structures to provide flexibility in scheduler implementations at improved performance levels when compared to software-only implementations. This allows run-time reconfiguration of, e.g., scheduling algorithms utilized, to adapt to changing network scenarios. This thesis describes the project that investigate the possibilities to improve upon end-to-end delays, jitter, throughput, and packet loss by exploiting the availability of a flexible hardware structure such as an FPGA.

This chapter introduces the main argument of this thesis. First of all, we give an overview about the concept of Quality of Service (QoS), discussing its differences with the best-effort approach and justifying the motivations that lead to the development of a new paradigm for the Internet. Subsequently, we introduce the most important metrics for the QoS, i.e., end-to-end delay, jitter, throughput, and packet loss. Finally, we point out the objectives and the motivations of the project described in this thesis.

## 1.1 Quality of Service

Internet and computer networks are becoming part of our daily life, a change that affects universities, commercial organizations, and consumers. These networks support a huge amount of different applications like e-mail, web, audio, and video services, including television on demand and file transfer. Furthermore, the requirements for these applications are growing quickly, and probably this fact will continue in the near future. Recently, the provision of service guarantees has become an important issue, which was caused by both the heterogeneity of application requirements and the growing commercialization of the Internet. It is not possible to sell products as television-on-demand or audio streaming with a network infrastructure that does not guarantee on the desired service level.

Currently, the Internet is based on the best-effort model, which means "as much as possible, as soon as possible". According to this definition, each packet has the same expectation of treatment as it transits a network. Even if this could be enough for traditional Internet applications, such as web, e-mail, news groups, etc., new multimedia applications and services create a new demand to bring different levels of service to packet traffic. The main reason is that, depending on a service, and if possible on the desired level of this service, the traffic characteristics and its requirements for network transport functionality may vary. For instance, some of these applications are telnet sessions that usually generate low traffic but have high interactivity requirements; some are file transfer protocol (FTP) sessions with bursts of kilobytes or even megabytes, for which the throughput is a fundamental aspect compared with the interactivity; some are hypertext transfer protocol (HTTP) transactions that open a transport connection to transmit a handful of packets but do not need an high bandwidth utilization and some are audio or video streams that require a good bandwidth utilization, a low delay as well as a low jitter. If the Internet handles all data in the same way, then it can result in unacceptable, if not completely unusable, service. For example, if video and file transfer traffic are mixed together in the same part of the network, then the file transfer can experience congestion and packet losses due to the video applications that send data at the constant rate. In turn, the video traffic will not slow down, but will experience losses and poor voice quality due to the presence of the bursty file transfer operations. Therefore, the enhanced Internet architecture should provide different service classes to indicate the treatment of individual packets and flows and to allocate the suitable resources for all of them.

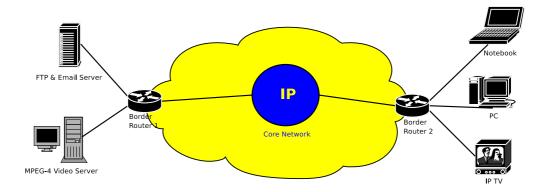

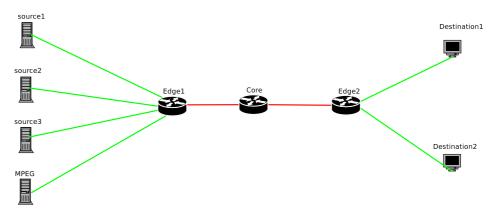

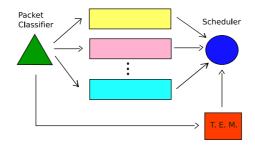

Figure 1.1: A QoS-aware Network Model

The objective of network QoS is to quantify the treatment that a particular packet can expect. A good QoS architecture should provide a way to specify performance objectives for different classes of packets, as well as suggestions on how to meet those performance goals. It has to be clear that QoS cannot create additional bandwidth. When some packets get better treatment, other packets will get worse treatment. Therefore, the objective of QoS is to distribute resources in such a way that all the performance objectives are met.

The QoS stems from the concept that some traffic is more important compared to other and should be treated accordingly. In addition, economical reasons exist such as the Internet has become mission-critical for commercial companies. In an environment, a provider can offer services with specific performance level associating them with a cost consequently, it is possible for the provider to tie the provided expected performance level (or quality) with a price for the service. From the customer's point of view (either a provider, a user, or another organization), the first step towards the QoS is the Service Level Agreement (SLA), which is negotiated with a provider. The SLA defines the QoS requirements, the anticipated load, actions to take if the load increases the negotiated value for the service level, pricing etc. Since the SLA includes rules and actions in the human readable form, it has to be translated into the machine readable representation. For these purposes, the SLA is partitioned into several documents. The Service Level Objectives (SLO) specifies metrics and operation information to enforce and monitor the SLA. The Service Level Specification (SLS) specifies the handling of a customers traffic by a service provider.

To characterize the QoS requirements and actions in the SLS, a provider and a customer must specify them with a set of well-known parameters, or performance metrics, so that a provider can translate them into the router configuration. The fundamental parameters are throughput, delay, jitter, and packet loss [16].

#### 1.1.1 QoS parameters

In this section, the most important QoS parameters are introduced. A definition is provided with a short description of the meaning of the parameter.

**Throughput** specifies the amount of bytes (or bits) that an application can send during a time unit without losses. It is one of the most important parameters because most applications include it in the set of their QoS requirements. It should be noted that the throughput stands for the long-term rate of an application. Due to the packet-based nature of most networks, the short-term rate may differ from the long-term value. Therefore, it is usually the case that the throughput refers to the average rate of an application. Consequently, one can use other parameters such as the maximum or the rate and the minimum rate.

**Packet delay** is a fundamental characteristic of a packet-switched network and it represents the delay required to deliver a packet from a source to destination. It is also called *end-to-end* delay. Each packet inside a network is routed to its destination via a sequence of intermediate nodes. Therefore, the *end-to-end* delay is the sum of the delays experienced at each hop on the way to the destination. It is possible to think about such delay as consisting of two components, a fixed one which includes the transmission delay at a node and propagation delay on the link to the next node, and a variable component which includes the processing and queueing delays at the node.

**Jitter** specifies the delay variation between two consecutive packets. It is an important parameter for the interactive applications, such as on-line audio and video conversations. Since data exchange between two applications involves sending a significant number of packets, it is often the case that jitter specifies the maximum delay variation observed between the two consecutive packets. However, one can also use a smoothing equation to obtain some mean value over the sequence of packets. Regardless of the interpretation, ideally the jitter should equal to zero because the bigger its value is, the larger the buffer of a receiving application must be to compensate for the delay variations between the packets.

**Packet loss**, as its name indicates, characterizes the number of dropped packets during transmission. This parameter is critical for those applications that perform guaranteed data delivery because every time a router drops a packet, a sending application has to retransmit it, which results in ineffective bandwidth utilization. It is also important for some real-time applications since packet drops reduce the quality of transmitted video and/or audio data. Since the number of dropped packets depends on the duration of a session, the packet loss is expressed usually as a ratio of the number of dropped packets to the overall number of packets [16].

**Fairness**: considering an allocation problem: i users, a vector x where the i-th coordinates represent the allocation for user i, i.e., the rate to which the user i can emit data. A feasible allocation of rates x is "max-min fair" if and only if an increase of any rate within the domain of feasible allocations must be at the cost of a decrease of some already smaller rate. Depending on the problem, a max-min fair allocation may or may not exist. However, if it exists, it is unique. The name "max-min" stems from the idea that it is forbidden to decrease the share of sources that have small values, therefore, in some sense, the flows with small values are privileged.

### 1.2 Goals & Methodology

How can reconfigurable hardware structures, e.g., FPGAs, be efficiently used in routers to improve their performance in terms of, for example, end-to-end delay, jitter, and throughput for different types of network traffic?

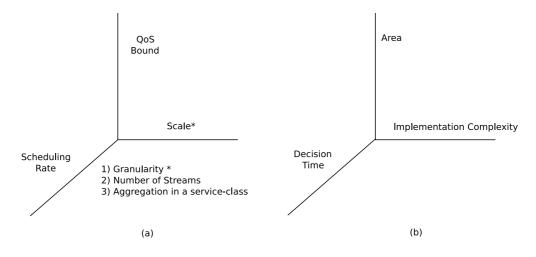

Certainly, knowledge of the traffic characteristics in a certain network scenario may lead to different choices in the system configuration. This knowledge is not always available a priori, therefore the approach is to dynamically understand which kind of traffic is travelling inside the backbone and changing the scheduling algorithm accordingly. This choice can bring a performance improvement in terms of different network metrics. The problem of using an FPGA can be viewed also from the efficiency point of view, that is, using different scheduler algorithms takes more or less space in the hardware device depending on the choice. An investigation on the different possibilities adopting one choice or the other is necessary and also a tradeoff between them can be found. It is possible to think of using this available space on the device with the possibility to handle more stream sessions simultaneously or try to improve the performance of the cheaper algorithm using a different approach in the traffic management.

To reach these goals, this work provides an overview on adaptive scheduling using reconfigurable hardware, giving some guidelines which would help a network administrator in choosing the configuration which best fits to the requirements of his scenario. Consequently, we investigate different scheduling algorithms that provide QoS guarantees for traffic streams that are sensitive to packet delay and jitter, e.g., MPEG video traffic. The investigation has been carried out with the NS-2 simulator [18] which represents a standard de facto for research in the networking environment. The main steps of this work are:

- add a real-time traffic source in NS-2 to evaluate the performance of our approach in a realistic scenario;

- add an experimental support for the run-time reconfiguration of the scheduling algorithm in the simulator module implementing the scheduler;

- add the Weighted Fair Queuing scheduler to the simulator and test it;

- evaluate the trend of QoS metrics with or without the modification;

- evaluate the benefits that the reconfiguration can give in terms of saved FPGA area.

For the first evaluation, the approach is mainly based on understanding which kind of traffic is passing in the network and change the scheduling algorithm in the core router to meet certain performance requirements. For the WFQ scheduler testing, a test suite is constructed composed of a particular scenario and an ad-hoc script that has been created. To evaluate the benefits in terms of saved FPGA area, a comparison between two schedulers was performed. The investigated scheduling algorithms are taken from two well-known families, i.e., Round Robin (RR) and Fair Queuing (FQ).

### 1.3 Overview

The remainder of the thesis is organized as follow: Chapter 2 gives an overview about the two big algorithm families: *round-robin* and *fair queuing* providing a classification of scheduling algorithms and giving a description of them, introducing which ones we are going to use in our simulations. Chapter 3 describes the simulation environment as well as the differentiated services architecture for the IP QoS; in this chapter the MPEG4 model is introduced and its support in the simulator described together with a cost analysis of the implementation in FPGA of the chosen algorithms. Chapter 4 presents the *monitor agent* developed to trace the results in the simulator, also the modifications that are needed to support the reconfigurability are described; at the end of the chapter, the WFQ implementation in NS-2, an algorithm that is not available with the standard simulator distribution and that has been added, is presented. In Chapter 5, the methodology to evaluate the results of the experiments is described, and the results of these simulations are presented and analyzed. Chapter 6 summarizes the work with the last reflections and gives some ideas for future investigations.

In this chapter, an overview of the scheduling algorithms available in the network simulator will be provided, and the choice of two of these strategies is explained basing on some of their characteristics.

The selection of an appropriate scheduling algorithm is a key point to build a network environment with QoS capabilities. Considering a simple case, a service provider has to share the output bandwidth between all data flows such that each flow obtains a fair portion of bandwidth resources. In this approach, we are assuming that each single flow has the same requirements. However, due to the diversity of the existent applications, a data flow may require a certain minimum amount of the output bandwidth, and this can lead to unequal bandwidth allocation between flows. Therefore, a service provider has to choose the correct disciplines to ensure that the requirements of all the data flows are met.

## 2.1 Classification of Scheduling Algorithms

A service discipline can be classified as either work-conserving or non-workconserving [26]. With a *work-conserving* discipline, a scheduler is never idle when there is a packet to send. With a non-work-conserving discipline, each packet is assigned an eligible time, this parameter represent the time for the packet departure and if no packet is eligible, none will be transmitted even when a scheduler is idle; with such kind of disciplines, a scheduler can be idle at any time, in an effort to smooth out the traffic pattern [4]. Both these classes have drawbacks and advantages. The work-conserving disciplines are suitable for those environments in which applications can adjust their transmission rates and can react to the packet losses. Indeed, if there are available bandwidth resources, the application can start to send more data achieving the higher throughput and the better network utilization. If later a congestion occurs, some number of packets will be dropped which will signal the sending application to slow down the data transmission. Though the work-conserving disciplines allow to completely utilize the output bandwidth, they alter the traffic profile as packets move from one node to another. Usually the traffic profile represents the temporal properties of a traffic stream and it is represented in terms of rate and burst size. As a result, the provision of the end-to-end guarantees, and especially the delay guarantees, becomes an art that involves many network management solutions. As opposed to this, the non-work-conserving disciplines do not change the traffic profile because the

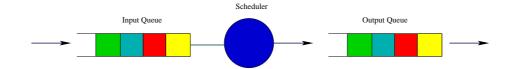

Figure 2.1: FIFO Scheduler

server delays the packet transmission to respect this profile; this behavior simplifies the provision of the end-to-end guarantees. The non-work-conserving disciplines eliminate traffic distortions by delaying packets and, thus, preserving the traffic profile. However, as mentioned above, some bandwidth resources remain unutilized. At the moment, most manufactures of the telecommunication equipment rely upon the work-conserving disciplines. The main reason is that they allow to utilize bandwidth resources more efficiently. Furthermore, two QoS frameworks proposed by the IETF rely upon the work-conserving schedulers. Hence, we will also focus on this class of scheduling disciplines [16].

## 2.2 FIFO (First In First Out)

This is the classical scheduling algorithm deployed in the best-effort approach in the Internet and it is also know as FCFS (First Come First Served, Figure 2.1). With this algorithm, the data are sent in the same order in which they are received. The complexity of this approach is very low and it is also very efficient to implement in hardware. It is a work-conserving algorithm and because its characteristics it has been adopted by a large number of network architectures. Unfortunately, FIFO has several limitations:

- it does not provide fairness;

- the support to control congestion is limited.

This kind of scheduler is not suitable for stream like *multimedia traffic*, because it is not able to isolate real-time sessions from best effort ones. In this case, there is no way to guarantee a specific level of quality to real-time sessions.

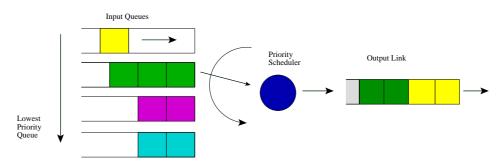

## 2.3 Priority Scheduling

Priority Queuing is one of the first attempts utilized to provide different services and it is able to isolate the sessions among these services.

The concept is as follows: the traffic is inserted into different queues that are served according to their priority. Highest priority queues are served as soon as they have packets. This mechanism can bring to *starvation* if highest priority classes have a large amount of traffic and therefore it is not fair. This mechanism is work-conserving and it is particularly interesting when the network has a small amount of high priority traffic (for example real-time sessions), because the performance of the best effort traffic is not worsened too much.

The highest priority class has the entire output link bandwidth available. The class that follows has the entire link bandwidth decreased by the amount used by the first class, and so on. Therefore, traffic within each class is influenced only by the traffic sent by the classes that have a higher priority than itself. This algorithm

Figure 2.2: Priority Queuing Scheduler

is not very robust because it requires an admission control in order to ensure that the highest priority class does not receive too much bandwidth. Moreover, there are several situations where the service guaranteed by priority queuing is much better than the service required by the sessions. In this case, the priority queuing is not able to delay a high priority packet in order to increase the service pattern for other sessions; for these reasons priority queuing is not a good choice for a network mixing best effort and real-time traffic [1].

## 2.4 Fair Scheduling Algorithms

The Fair Queuing algorithm was originally proposed in [12] by Nagle in order to solve the problem of malicious or erratic TCP implementations. The goal of the algorithm is to guarantee each session with a fair share of network resources, even though some sessions are transmitting at a much higher rate than the allocated one. This class of algorithm is defined fair, because it allows the fair sharing of the bandwidth among all the users [14].

#### 2.4.1 Round Robin

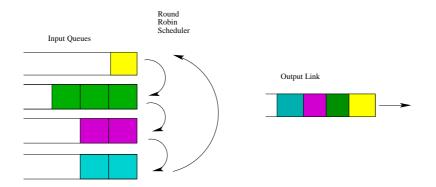

Round Robin (RR) scheduling represents the simplest solution for the controlled bandwidth sharing. Using this scheduling algorithm, a packet is dequeued in a so-called *round-robin manner* and outputs one packet from a queue. Of course, it is not possible to provide any QoS capabilities with such a scheme. Nagle's idea was to maintain, at each node, a separate queue for each traffic sources and to transmit packets at the head of queues in round-robin order. Empty queues are skipped, so that, given n active sources, the overall effect is to allow each source to send one packet every n packets transmitted on the link because each source has to wait a complete round to be served the next time.

Figure 2.3: Round Robin Scheduler

Having n queues with n users, each of them gets exactly  $\frac{1}{n}$  of the total link bandwidth. This approach suffers from several limitations:

- it ignores packet lengths, so it works well (with respect to fairness) just when the average packet size over the flow duration is the same for all flows;

- the performance depends on the arrival pattern; a packet arriving at an empty queue, just after its turn in the round-robin, must wait until the other (n-1) queues have been served;

- it requires a-priori knowledge of the number of sessions (because we put the traffic of each session in a separate queue) but in most cases this is not realistic.

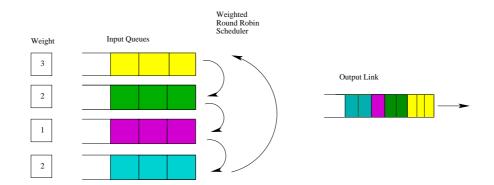

#### 2.4.1.1 WRR - Weighted Round Robin

The WRR scheduler works in a cyclic manner, serving consequently the input queues. The weight is a variable that indicates how many packets have to be sent for each cycle from each queue. If a queue has fewer packets than the value of the weight, the WRR scheduler outputs the existent number of packets and begins to serve the next queue. The WRR scheduler does not take the size of the transmitted packets into account. As a result, it is difficult to predict the actual bandwidth that each queue obtains. In other words, it is difficult to use only the weight values as the means to specify the amount of the output bandwidth. Suppose that  $w_i$  is the value of the weight associated with the *i*th queue. If  $L_i$  is the mean packet size of the *i*th input queue, then  $w_iL_i$  bytes of data are sent during each cycle on average. If there are *m* input queues, then it is easy to show that the average

Figure 2.4: WRR Scheduler

amount of data transmitted from all queues during one cycle can be approximated by:

$$\sum_{i=1}^{m} w_i L_i \tag{2.1}$$

Expression 2.1 is referred to as the *frame size*. Taking the mean packet size and weights of all queues into account, it is possible to approximate the output bandwidth for the given kth queue:

$$\frac{w_k L_k}{\sum_i w_i L_i} B, \quad k \in (1, m)$$

(2.2)

where B specifies the output bandwidth of an interface, on which a router implements WRR. By approximating the average bandwidth of each queue, it is possible to provide the QoS guarantees [16].

#### 2.4.1.2 DRR - Deficit Round Robin

Deficit Round Robin is one modification of WRR to improve the fairness. DRR can guarantee fairness in terms of throughput. In DRR, the packet scheduler maintains a state variable called *Deficit-Counter* to control the amount of dequeued traffic precisely. A quantity called Quantum is added to *Deficit-Counter* in each round. If the length of the packet at the top of the queue is less than *Deficit-Counter*, the packet scheduler can dequeue the packet and then subtracts the packet length from *Deficit-Counter*. Otherwise, it accesses the next queue.

Although DRR requires only O(1) processing work per packet in order to guarantee bandwidth, it must calculate the length of every packet and the calculation of the packet length takes computational resources of the router [25].

#### 2.4.2 Fair Queuing algorithms

The problem of fair network resource allocation has led to the development of a class of algorithms that provide tight end-to-end delay bounds and efficient re-

source utilization. These algorithms try to approximate the ideal behavior of the Generalized Processor Sharing algorithm (GPS), which is described in the following section.

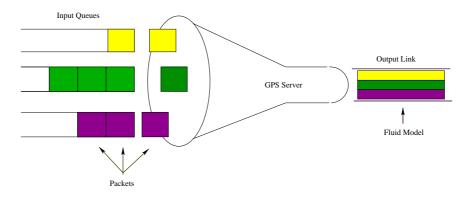

#### 2.4.2.1 GPS - Generalized Processor Sharing

GPS [13] has been proposed by Parekh and Gallager in 1993, it is based on a fluid model, so it assumes that the input traffic is infinitely divisible and that all sessions can be served at the same time. This is a work-conserving server and it guarantees each session to receive a *service rate*  $g_i$  of at least:

$$g_i = \frac{\theta_i}{\sum_{j=1}^N \theta_j} r \tag{2.3}$$

where r is the server rate and  $\theta_i$  is the weight for the *i*-th session.

GPS treats each packet as infinitely divisible, so the scheduler picks a small piece of data from each session and transmits it on the output link. Because this assumption, GPS can transmit a *fluid flow* instead of bits. For example, having two sessions m and n, each of which with weight 1, an algorithm like *Bit by Bit Round Robin* transmits one bit of the first session and a bit of the second session. GPS, instead, always uses half bandwidth transmitting session m data and the other half transmitting session n data. An important feature of GPS is that it

Figure 2.5: Graphical representation of a GPS Server

is possible to compute a worst-case delay bound for leaky bucket<sup>1</sup> constrained sessions. However, GPS is impractical because it assumes the server can serve all the sessions simultaneously and the traffic is infinitely divisible. Therefore, it needs to be approximated by a packet algorithm. In the next section we are going to introduce two of these: WFQ and WF<sup>2</sup>Q+.

<sup>&</sup>lt;sup>1</sup>the leaky-bucket implementation is used to control the rate at which traffic is sent to the network. A leaky bucket provides a mechanism by which bursty traffic can be shaped to present a steady stream of traffic to the network, as opposed to traffic with erratic bursts of low-volume and high-volume flows [20].

#### 2.4.2.2 WFQ - Weighted Fair Queuing

One of the first scheduling algorithm proposed to approximate GPS was WFQ, it schedules packets according to their arrival time, size, and the associated weight. Upon the arrival of a new packet, a "virtual finish time" is calculated and the packet is scheduled for departure in the right order with respect to the other packets. This "virtual finish time" represents the time at which the same packet would finish to be served in the GPS system. Then, WFQ outputs packets in the ascending order of the virtual finish time. Such an approach enables the sharing of resources between service classes in a fair and predictable way. Furthermore, it is possible to estimate the bandwidth allocation and the worst-case delay performance, which makes the use of the WFQ discipline very attractive for the provision of QoS, and especially for the provision of the end-to-end guarantees. Suppose that B is the total throughput of an output link on which a router implements WFQ. If all sessions of the WFQ scheduler are active, then each class receives a portion of the total bandwidth, which is determined by its weight  $w_i$  and is equal to  $w_i B$ . B is the available bandwidth. Hence, to simplify the expression, we assume that it holds for all weights  $w_i$  that

$$\sum_{i} w_i = 1, \quad w_i \in (0, 1) \tag{2.4}$$

By knowing the QoS requirements of all data flows, we can find values for  $w_i$  such that all the QoS guarantees are ensured.

#### 2.4.2.3 QoS requirements

It is possible to associate each service class with a proper weight w that indicates the allocated bandwidth. Having  $N_i$  active flows within the *i*-th class, then each flow gets a bandwidth that can be approximated by:

$$B_i^f = \frac{w_i B}{N_i} \tag{2.5}$$

$B_i^f$  can be viewed as one of the QoS parameters that specifies the required bandwidth of a flow belonging to the *i*-th service class. Thus, the minimum value of the weight, which provides the necessary amount of bandwidth for every flow, is given by

$$w_i \ge N_i \frac{B_i^f}{B} \tag{2.6}$$

The inequality states that a provider can allocate more resources than necessary. Therefore, if the network has free bandwidth resources, then a provider can allocate, either explicitly or implicitly, more bandwidth to a service class.

Due to buffering, scheduling, and transmission of packets, the size of a router's queue varies all the time. On the other hand, the length of a queue in a routing

node has an impact on the queuing delay and on the overall end-to-end delay of a packet. It can be shown that under WFQ the worst-case queuing delay is given by the following expression, where  $L^{max}$  denotes the maximum packet size:

$$D = \frac{\sigma}{\rho} + \frac{L^{max}}{B} \tag{2.7}$$

In (2.7), it has been assumed that each incoming flow is regulated by the *token* bucket [2] with the bucket depth  $\sigma$  and the token rate  $\rho$ . Parameters  $\sigma$  and  $\rho$  can be viewed as the maximum burst size and the long term bounding rate respectively.

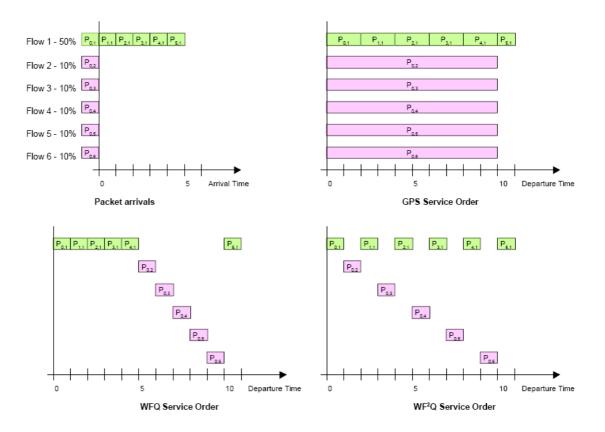

#### 2.4.2.4 WF<sup>2</sup>Q+ - Worst Case Weighted Fair Queuing

$WF^2Q+$  is less complex to implement compared with WFQ because it uses a system virtual function that is calculated from the packet system itself and not from GPS, indeed, another advantage is that, there is no need to stamp each packet with its start and finish time, instead it is sufficient to have just one start and finish time for each connection.  $WF^2Q+$  approximates GPS more closely, its delay is better than WFQ in a lot of cases, but not always. It has been shown that  $WF^2Q+$  does not always outperform WFQ for real-time sources [22]. WFQ presents a better delay than  $WF^2Q+$  in situations with bursty traffic with variable packet size, which are typical with real-time sources, of course the augment of end-to-end delay for multimedia traffic, gives better delay guarantees for all other source non-real time traffic in the network. For this reason WFQ has been chosen for our investigation. However, for completeness we introduce the main idea of  $WF^2Q+$  in this section.

In  $WF^2Q$ + the rule to pick up a packet from a queue is lightly modified by the WFQ rule:

- **WFQ:** the packet having the lower exiting time according to the correspondent GPS system, will be the first one to exit under the WFQ scheduler.

- $WF^2Q+$ : the packet having the lower exiting time according to the correspondent GPS system, and that has already started its service under the GPS scheduler, will be the first one to exit under  $WF^2Q+$  scheduler.

This difference can be understood looking at the Figure 2.6. At time 1 the situation is the following:

- WFQ: the first packet finishing its service under GPS is  $Pkt_{1,1}$  and it will be scheduled in WFQ;

- WF<sup>2</sup>Q+: the packets having already started their service under GPS are  $Pkt_{0,2}$ ,  $Pkt_{0,3}$ ,  $Pkt_{0,4}$  and  $Pkt_{0,5}$ . The first one that will finish is  $Pkt_{0,2}$  (but another one should also be scheduled in this example, because they are

Figure 2.6: Different packet output between WFQ and WF<sup>2</sup>Q+ (picked from [14])

finishing all together), so this will be the next packet being scheduled by  $WF^2Q+$ .

WF<sup>2</sup>Q+ represents an improvement from the implementation point of view compared with WFQ because it exploits a different virtual function to take into account the virtual time, and it is also an improvement for the complexity viewpoint (O(N) against O(log(N))).

## 2.5 Summary

In this chapter, the *round-robin* and the *fair queuing* families of algorithms have been presented. A classification of these scheduling disciplines has been furnished and each algorithm has been described. The *FIFO* and *priority* scheduler are unsuitable to provide fairness as well as QoS guarantees. The priority scheduler can also bring to the starvation if the high priority classes have a large amount of traffic to send. RR, WRR, and DRR have been described as representative of the *round-robin* families. These algorithms are simple to implement but they do not provide QoS guarantees and in certain situation they cannot share correctly the bandwidth to the competing streams. The *fair queuing* family has been introduced presenting the theoretical model of General Processor Sharing (GPS) from which all the approximations are based on. The most well-known of this algorithm approximation have been presented: weighted fair queueing (WFQ) and worst case weighted fair queuing (WF<sup>2</sup>Q+). They are more complex to implement compared with the *round robin* algorithms. This chapter introduces the NS-2 Network Simulator; then, we discuss the Diffserv support presenting in the simulator through the Nortel Diffserv module [17]. Another section introduces the MPEG4 model that has been used in the simulations. The last part of the chapter is dedicated to the motivation leading to the use of an FPGA and the cost analysis of WFQ and WRR in hardware.

## 3.1 NS-2 - The Network Simulator

### 3.1.1 Overview

NS-2 is an event driven network simulator developed at UC Berkeley that simulates several IP networks. It implements network protocols such as TCP and UDP, traffic source behavior such as FTP, Telnet, Web, CBR and VBR, router queue management mechanism such as Drop Tail, RED and CBQ, routing algorithms such as Dijkstra, and more. NS-2 also implements multicasting and some of the MAC layer protocols for LAN simulations. The NS-2 project is now a part of the VINT project that develops tools for simulation results display, analysis and converters for network topologies. NS-2 is written in C++ and OTcl, Tcl is a script language with object-oriented extensions developed at MIT<sup>1</sup>. The core of the simulator is written in C++ instead the simulation setup is written in Tcl. To add a component in the simulator, as a scheduler or a network object, the C++ code needs to be modified while to setup and run a simulation, a Tcl scenario has to be created.

<sup>&</sup>lt;sup>1</sup>Massachusetts Institute of Technology

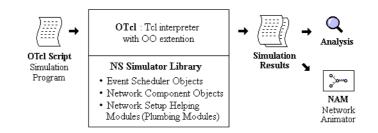

Figure 3.1: Simplified User's View of NS-2

As depicted in Figure 3.1, in a simplified user's view, NS-2 is OTcl script interpreter, that has a set of simulation libraries. Within these, there are network setup (plumbing) module libraries, they are implemented as member functions of the base simulator object. In other words, to use NS-2, a program in OTcl script language has to be written.

To create and run a network simulation:

- write an OTcl script initializing an event scheduler;

- set up the network topology using network objects and library functions;

- define traffic paths:

- set traffic source and destination;

- define time to start sending traffic and when stop;

- define characteristics between links connecting nodes;

- set a method to trace the results;

- start the simulator object.

The term "plumbing" is used for a network setup, because setting up a network can be viewed as plumbing possible data paths among network objects by setting the "neighbor" pointer of an object to the address of an appropriate object. If a new network object has to be written, it has to be created either by writing a new object or by making a compound object from the object library, and plumb the data path through the object. This might be a complicated job, but the plumbing OTcl modules actually make it very easy. The power of NS-2 comes from this plumbing.

Another major component of NS-2 beside network objects is the event scheduler. An event in NS-2 is a packet ID that is unique for a packet with scheduled time and a pointer to an object that handles the event. In NS-2, an event scheduler keeps track of simulation time and fires all the events in the event queue scheduled for the current time by invoking appropriate network components, which usually are the ones who issued the events, and let them do the appropriate action associated with packet pointed by the event. Network components communicate with one another passing packets, however this does not consume actual simulation time. All the network components that need to spend some simulation time handling a packet (i.e., need a delay) use the event scheduler by issuing an event for the packet and waiting for the event to be fired to itself before doing further action handling the packet. For example, a network switch component that simulates a switch with 20 microseconds of switching delay issues an event for a packet to be switched to the scheduler as an event 20 microsecond later. The scheduler after 20

microsecond dequeues the event and fires it to the switch component, which then passes the packet to an appropriate output link component.

Another use of an event scheduler is timer. For example, TCP needs a timer to keep track of a packet transmission time out for retransmission (transmission of a packet with the same TCP packet number but different NS-2 packet ID). Timers use event schedulers in a similar manner that delay does. The only difference is that the timer measures a time value associated with a packet and does an appropriate action related to that packet after a certain time goes by, and does not simulate a delay.

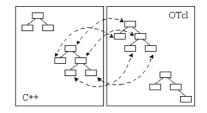

NS-2 is written not only in OTcl but in C++ too. For efficiency reason, NS-2 separates the data path implementation from control path implementations. In order to reduce packet and event processing time (not simulation time), the event scheduler and the basic network component objects in the data path are written and compiled using C++. These compiled objects are made available to the OTcl interpreter through an OTcl linkage that creates a matching OTcl object for each of the C++ objects, and makes the control functions and the configurable variables specified by the C++ object act as member functions and member variables of the corresponding OTcl object. In this way, the controls of the C++ objects are given to OTcl. It is also possible to add member functions and variables to a C++object. The objects in C++ that do not need to be controlled in a simulation or internally used by another object do not need to be linked to OTcl. Likewise, an object (not in the data path) can be entirely implemented in OTcl. Figure 3.2 shows an object hierarchy example in C++ and OTcl. One thing to note in the figure is that for C++ objects that have an OTcl linkage forming a hierarchy, there is a matching OTcl object hierarchy very similar to that of C++.

Figure 3.2: C++ and OTcl: The Duality

Figure 3.3 shows the general architecture of NS-2. In this figure a general user (not an NS-2 developer) can be thought of standing at the left bottom corner, designing and running simulations in Tcl using the simulator objects in the OTcl library. The event schedulers and most of the network components are implemented in C++ and available to OTcl through an OTcl linkage that is implemented using tcl. The whole thing together makes NS-2, which is a OO (object-oriented) extended Tcl interpreter with network simulator libraries.

| Event<br>Scheduler | ns-2                 |

|--------------------|----------------------|

| telel otel tels.0  | Network<br>Component |

Figure 3.3: Architectural View of NS-2

## 3.2 Getting results in NS-2

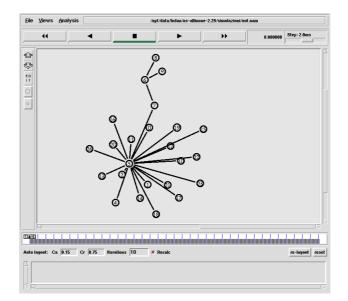

This section explains how to obtain NS-2 simulation results. As shown in Figure 3.1, when a simulation is finished, NS-2 produces one or more text-based output files that contain detailed simulation data, if specified to do so in the input Tcl (or more specifically, OTcl) script. The data can be used for simulation analysis or as an input to a graphical simulation display tool called Network Animator (NAM) that is developed as a part of VINT project [18]. NAM (Figure 3.4) has a nice graphical user interface similar to that of a CD player (play, fast forward, rewind, pause and so on), and also has a display speed controller. Furthermore, it can graphically present information such as throughput and number of packet drops at each link, although the graphical information cannot be used for accurate simulation analysis. As we'll see later in Section 4.1, we have developed a module

Figure 3.4: NAM: Network Animator

to keep track of some metrics without have to use the NS-2 tracefile, this solution is useful because with a long time simulation these tracefiles would generate a big huge amount of files with a lot of data that are not interesting for our investigation.

The next section presents the module that we have used to differentiate the traffic and an overview of Diffserv Architecture.

## 3.3 Differentiated Services Architecture for IP QoS

In the traditional IP networks the service offered to the end-user is best-effort ("as much as possible as soon as possible"); in this kind of model, every user packets compete equally for network resources. This model doesn't give support to multimedia traffic and mission-critical applications, because it doesn't permit to differentiate the traffic. Much more attention has been placed on developing IP Quality of Service (QoS), which allows network operators to differentiate the traffic basing on different level of treatment [17].

Differentiated Services, or DiffServ, is an IP QoS architecture based on packet marking that allows packets to be prioritized according to user requirements. A scheme known as Assured Forwarding (AF) has been proposed as a potential user of Diffserv. Assured Forwarding provides differential treatment of traffic by discarding lower priority packets during congestion times. Although the Assured Forwarding mechanism does not explicitly require a particular queue type, it is suited for RED (Random Early Detection) [17].

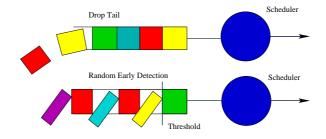

#### 3.3.1 Queue Management

When the buffer in a queue is becoming full, the *Queue Management* algorithm is used to decide which packet has to be dropped. This algorithm works on a single queue of the network node, if there are more queues on that node, more instances of a queue management are needed. It is also possible to have, within the single node, a queue treated with *RED* management and another one treated with *Drop Tail*.

Figure 3.5: Different Queue Management mechanisms

#### 3.3.2 Drop Tail

When there is no more space on the buffer, the last arrived packets are dropped. This is the simplest approach called *Drop Tail*. The available space in the queue depends on the buffering mechanism deployed in that network node: different queue management could be employed for each queue.

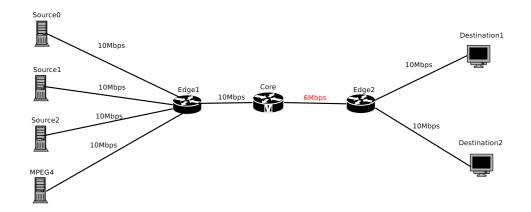

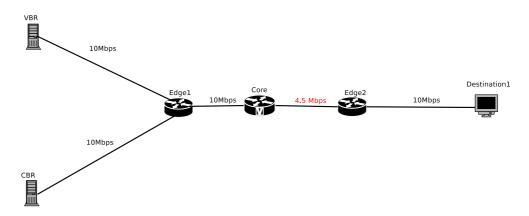

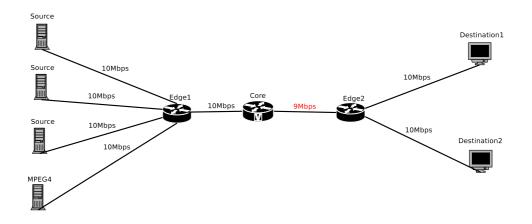

This algorithm suffers from limitation, because the packets are discarded when the queue is full and the network utilization varies a lot. Supposing to have a TCP source, experimenting a certain number of losses, the two agents decrease their sending rate. With this behavior, the network oscillates between high traffic and low traffic and it is not able to create an equilibrium. Moreover there can be malicious effects due to the source synchronization, where one source does not experiment any drop and another does [14]. In our simulations, this kind of queue has been utilized on the links connecting the edge routers with the sources and the destinations as shown in Figure 3.6, these links are green; instead the RED queue has been employed in the links between edge and core router and in the figure these are red.

Figure 3.6: Scenario with different kind of queues

#### 3.3.3 An Overview of RED

RED (Random Early Detection) is a congestion avoidance algorithm that can be implemented in routers. The basic queue algorithm for routers is known as Drop Tail. Drop Tail queues simply accept any packet that arrives when there is sufficient buffer space and drop any packet that arrives when there is insufficient buffer space.

RED gateways instead attempt to detect incoming congestion by computing a weighted average queue size, since a sustained long queue is a sign of network congestion. Its behavior is based on a threshold: RED mechanism starts the dropping process when the number of packets stored is larger than this value. The number of packets dropped (i.e., the probability that an incoming packet has to be dropped) increases as soon as the number of queued packets increases. When the number of packet reaches the maximum queue size, all the incoming packets are dropped (drop probability equal to 1). In this condition the RED algorithm has the same behavior of the Drop Tail one. RED keeps traces of the past status of the queue. The variable (number of packets in queue) that indicate that the algorithm has to start dropping packets does not depend simply on the amount of packets in queue, but it is calculated by means of an exponential moving weighted average function (EMWA) that is able to discriminate a short term burst and a long term congestion. Short-term bursts are quite common in the Internet because of the bursty nature of data traffic. In this case the algorithm does not operate. Vice versa, it must intervene when, for a certain amount of time, the number of packets in queue is above a certain threshold. This means that the network is starting to be overloaded so that it is likely to experiment congestion in a short time interval. RED operates only in presence of a responsible end-to-end adjustment mechanism. RED itself (i.e., dropping packets) is not enough to decrease the amount of traffic into the network. The congestion is avoided thanks to the TCP responsiveness that, in presence of drops, decreases the rate of the incoming traffic because of its typical sawtooth behavior. Clearly this approach does not work with malicious sources. RED cooperates with the enhanced version of TCP (TCP NewReno, TCP SACK) in decreasing the sawtooth behavior that is a peculiar characteristic of this protocol. Drop Tail can discard a lot of packets together so that a TCP session can experiment more than a packet loss per window of data. This triggers a timeout and the throughput of that session decreases. With RED is less likely to experiment more than one loss per window of data: TCP can recover with the Fast Retransmit Algorithm and the session does not experiment any timeouts.

For a RED gateway that drops packets, rather than marking a congestion bit, the following three phases sum up its algorithm:

- Phase 1: Normal Operation. If the average queue size is less than the minimum threshold, no packets are dropped.

- Phase 2: Congestion Avoidance. If the average queue size is between the minimum and maximum thresholds, packets are dropped with a certain probability. This probability is a function of the average queue size, so that larger queues lead to higher drop probabilities.

- Phase 3: Congestion Control. If the average queue size is greater than the maximum threshold, all incoming packets are dropped.

### 3.3.4 Multiple RED Parameters

The Diffserv architecture provides QoS by dividing traffic into different categories, marking each packet with a code point that indicates its category, and scheduling packets according to their code points. The Assured Forwarding mechanism is a group of code points that can be used in a Diffserv network to define four classes of traffic, each of which has three drop precedences. Those drop precedences enable differential treatment of traffic within a single class.

Assured Forwarding uses the RED mechanism by enqueuing all packets for a single class into one physical queue that is made up of three virtual queues (one for each drop precedence). Different RED parameters are used for the virtual queues, causing packets from one virtual queue to be dropped more frequently than packets from another. Using a proper traffic shaper on the edge router, a not conform traffic can be moved from a virtual queue with a higher drop preference to another one with lower; then this declassed traffic will be penalized during the congestion phase.

For example, one code point might be used for assured traffic and another for best effort traffic. The assured packet virtual queue will have higher minimum and maximum thresholds than those of best effort queue, meaning that best effort packets will enter the congestion avoidance and congestion control phase prior to assured packets.

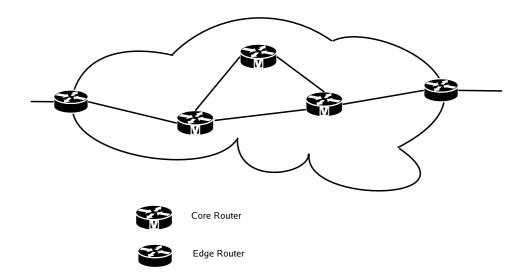

### 3.3.5 Diffserv Architecture

The Diffserv architecture has three major components:

- **Policy:** is specified by network administrator about the level of service a class of traffic should receive in the network.

- Edge router: router marks packets with a code point according to the policy specified.

- **Core router:** examines packets' code point marking and forwarding them accordingly.

DiffServ attempts to restrict complexity to only the edge routers.

A policy specifies which traffic receives a particular level of service in the network. Although a policy and resource manager is a necessary component of a Diffserv network that allows an administrator to communicate policies to the edge and core devices, it is not important for the NS-2 Diffserv implementation. Instead, policy information is simply specified for each edge and core device through the Tcl scripts.

Figure 3.7: Devices in a Diffserv Domain

The notion of edge and core devices, as illustrated in Figure 3.7, is key to the understanding of the NS-2 Diffserv implementation.

#### Edge Router Responsibilities:

- examining incoming packets and classifying them according to policy specified by the network administrator;

- marking packets with a code point that reflects the desired level of service;

- ensuring that user traffic adheres to its policy specifications, by shaping and policing traffic.

#### Core Router Responsibilities:

- ensuring that user traffic adheres to its policy specifications, by shaping and policing traffic;

- forwarding incoming packets according to their markings. (Core routers provide a reaction to the marking done by edge routers).

The DiffServ architecture provides QoS by dividing traffic into different categories, marking each packet with a code point that indicates its category, and scheduling packets accordingly. The DiffServ module in NS-2 can support four classes of traffic, each of which has three dropping precedences allowing differential treatment of traffic within a single class. Packets in a single class of traffic are enqueued into one corresponding physical RED queue, which contains three virtual queues (one for each drop precedence). Different RED parameters can be configured for virtual queues, causing packets from one virtual queue to be dropped more frequently than packets from another. A packet with a lower dropping precedence is given better treatment in times of congestion because it is assigned a code point that corresponds to a virtual queue with relatively lenient RED parameters.

All these features allow to differentiate a multimedia stream by other kinds of traffic, and to think about internal modification of the scheduler, to permit reconfiguration in case of particular condition as the ingress of a particular stream. This simulator module has been exploited for this reason and modified as presented in Chapter 4.

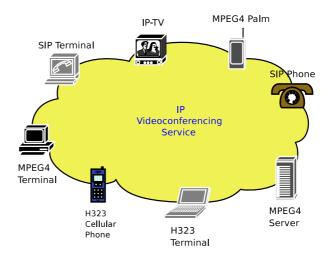

### 3.4 MPEG4 Model

Our investigation is focused on the study of QoS applied to delay sensitive traffic types, e.g. MPEG4. For this reason, an an MPEG4 traffic source to NS-2 was added. This traffic generator uses the *Transform Expand Sample Methodology*. We have chosen such kind of traffic source because the transfer of digital video will be a crucial component of the design of future home networking applications. This transfer was made feasible by the advancement of digital video encoding techniques that reduced the bandwidth required for this transfer to a practical level. MPEG4 is an encoding technique that is suitable for home networking applications with its low bit rate. It also has the advantage that allows viewers to interact with encoded objects. One of the motivations behind establishing the ISO Moving-Picture-Experts-Group (MPEG) family of standards for digital video encoding is that a lot of researchers and communication experts believe that, sooner or later, all the devices that are part of our daily life will be connected to the Internet.

Figure 3.8: Audio and Video in the Internet

Connecting those devices and appliances to the Internet will require the transfer of video or at least will include video transfer as an enhancement. This family of standards includes MPEG1, MPEG2, and MPEG4. MPEG4 is the one that is most suitable for the Internet [5]. The main feature of importance to the network is MPEG4's capability of real-time adaptive encoding. This enhances network utilization and enables MPEG4 senders to be more responsive to changes in network conditions. It generates video in three different frame types (I, P, and B) that serve to encode different portions of the video signal in different levels of quality.

This kind of traffic generator can be used to study MPEG4 behavior and performance through simulation. This is relevant because it permit us to reproduce a more realistic scenario to simulate multimedia transfer on the Internet. Our objective is to study this performance and properties combined in a Diffserv environment using simulation. This traffic generator is able to generate traffic that has almost the same first and second order statistics as an original trace of MPEG4 frames that is generated using an MPEG4 encoder [7]. The source code of this traffic generator is in the Appendix A.

Table 3.1 contains a chunk of TCL code to set up a MPEG4 traffic generator in NS-2.

```

set source [$ns node]

set udp0 [new Agent/UDP]

$ns attach-agent $source $udp0

set vdo [new Application/Traffic/MPEG4]

$vdo set initialSeed_ 0.4