## UNIVERSITÀ DI PISA

## Facoltà di Ingegneria

Corso di Laurea Specialistica in Ingegneria Elettronica Anno accademico 2003/2004

TESI DI LAUREA SPECIALISTICA

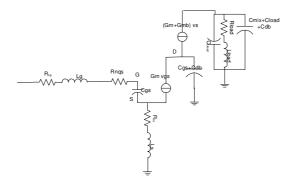

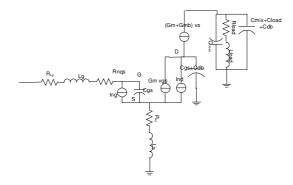

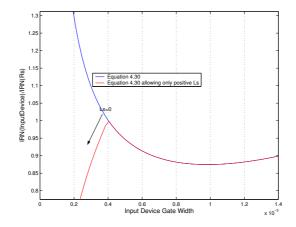

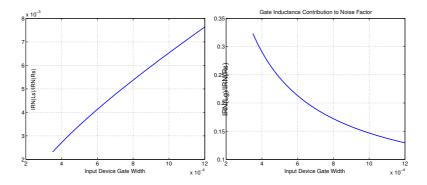

## Metodologia per la caratterizzazione di amplificatori a basso rumore per UMTS

Relatori:

Prof. Bruno Neri

Ing. Fernando De Bernardinis

Prof. Rinaldo Castello

Candidato: Simone Gambini

# Contents

| 1        | Introduction       |                                                                               |                 |  |  |  |

|----------|--------------------|-------------------------------------------------------------------------------|-----------------|--|--|--|

|          | 1.1                | A bit of Background                                                           | 1               |  |  |  |

|          | 1.2                | UMTS receivers and goal of the work                                           | 3               |  |  |  |

|          | 1.3                | Roadmap                                                                       | 4               |  |  |  |

| <b>2</b> | Syst               | tem Level Modeling                                                            | 5               |  |  |  |

|          | 2.1                | Model Requirements                                                            | 5               |  |  |  |

|          | 2.2                | Input independent representations of nonlinear systems                        | 5               |  |  |  |

|          |                    | 2.2.1 Describing Functions and Generalized describing Functions               | 5               |  |  |  |

|          |                    | 2.2.2 Wiener-Volterra series                                                  | 6               |  |  |  |

|          |                    | 2.2.3 Relation between Volterra series and Describing function representation | 7               |  |  |  |

|          |                    | 2.2.4 Linear Periodically Time-Varying Systems                                | 8               |  |  |  |

|          | 2.3                | Proposed continuous time model                                                | 9               |  |  |  |

|          |                    | 2.3.1 Discrete-Time modeling                                                  | 11              |  |  |  |

|          |                    | 2.3.2 Frequency Domain model                                                  | 11              |  |  |  |

|          |                    | 2.3.3 Tone Based Model                                                        | 12              |  |  |  |

|          | 2.4                | Complexity evaluation for the proposed models                                 | 12              |  |  |  |

|          | 2.5                | Model Implementation                                                          | 16              |  |  |  |

|          | 2.6                | Sensitivity Analysis                                                          | 18              |  |  |  |

|          |                    | 2.6.1 Building Blocks Models                                                  | 18              |  |  |  |

| 3        | Device Modeling 22 |                                                                               |                 |  |  |  |

| J        | 3.1                | Integrated Inductor Model                                                     | 22              |  |  |  |

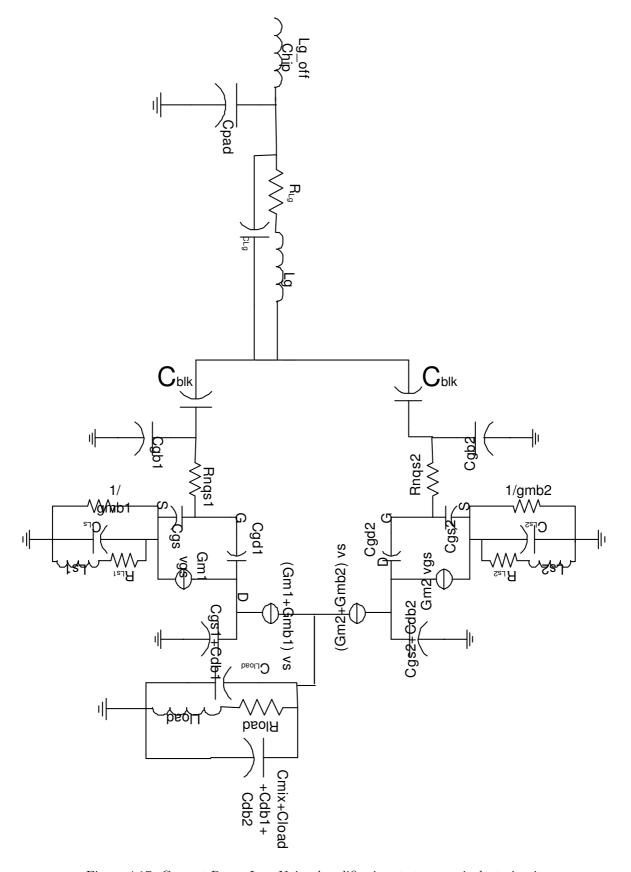

|          | $3.1 \\ 3.2$       | Small Signals Models for transistor extrinsic parts                           | $\frac{22}{25}$ |  |  |  |

|          | 0.2                | 3.2.1 Overlap Capacitances                                                    | $\frac{25}{25}$ |  |  |  |

|          |                    | 3.2.2 Junction Diodes                                                         | 20<br>26        |  |  |  |

|          | 3.3                | Intrinsic Transistor Modeling                                                 | 20<br>26        |  |  |  |

|          | 0.0                | 3.3.1 Model Topology selection                                                | 20<br>26        |  |  |  |

|          |                    | 3.3.2 Long Channel Model                                                      | 20<br>26        |  |  |  |

|          |                    | 3.3.3 Small signal parameters                                                 | 20<br>29        |  |  |  |

|          |                    | 3.3.4 Noise                                                                   | $\frac{23}{30}$ |  |  |  |

|          |                    | 3.3.5 Non-Quasi Static Model                                                  | 33              |  |  |  |

|          | 3.4                | Large Signal Characteristics                                                  | 33              |  |  |  |

|          | 0.4                |                                                                               | 55              |  |  |  |

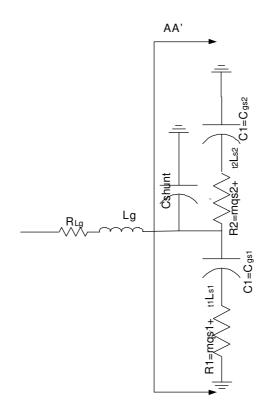

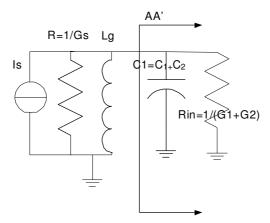

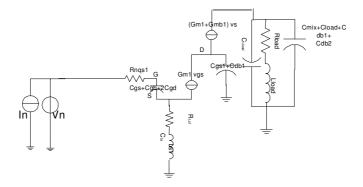

| <b>4</b> |                    | v Noise Amplifier Analysis                                                    | 35              |  |  |  |

|          | 4.1                | Input Matching                                                                | 35              |  |  |  |

|          | 4.2                | Noise                                                                         | 39              |  |  |  |

|          |                    | 4.2.1 Simplified Input Matching Equations                                     | 40              |  |  |  |

### CONTENTS

|              |                | 4.2.2Noise Analysis                                             | $40\\44$ |

|--------------|----------------|-----------------------------------------------------------------|----------|

|              | 4.3            | Gain                                                            | 48       |

|              | 4.4            | Distortion                                                      | 48       |

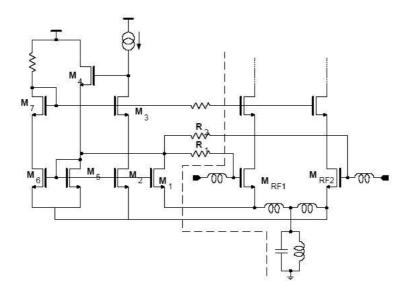

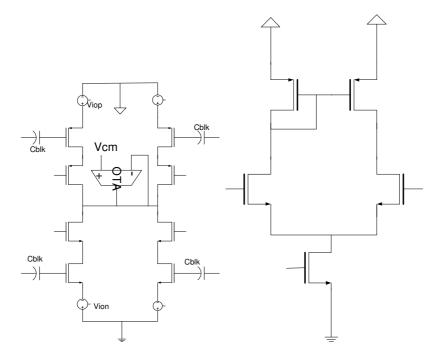

|              | 4.5            | Current Reuse LNA                                               | 53       |

|              |                | 4.5.1 Input Matching                                            | 55       |

|              | 4.6            | Gain                                                            | 55       |

|              | 4.7            | Noise                                                           | 57       |

|              |                | 4.7.1 Simplified Input Matching Equations                       | 57       |

|              |                | 4.7.2 Noise Analysis                                            | 59       |

|              | 4.8            | Distortion                                                      | 61       |

|              | 4.9            | Conclusions                                                     | 61       |

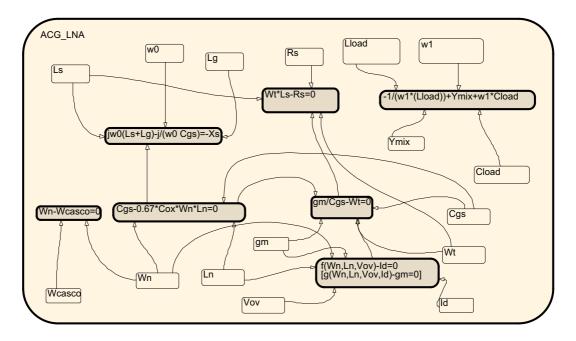

| 5            |                | v Noise Amplifier Model                                         | 62       |

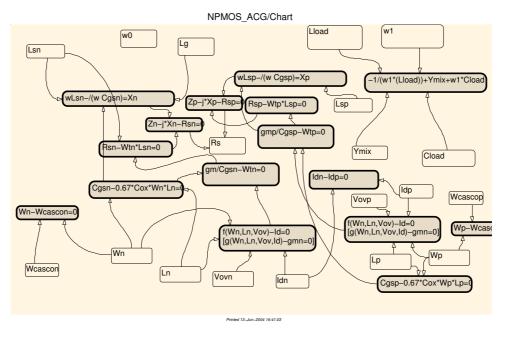

|              | 5.1            | Analog Constraint Graphs                                        | 62       |

|              |                | 5.1.1 Client Server Process                                     | 62       |

|              |                | 5.1.2 NMOS low noise amplifiers                                 | 63       |

|              |                | 5.1.3 Bias Circuit                                              | 64       |

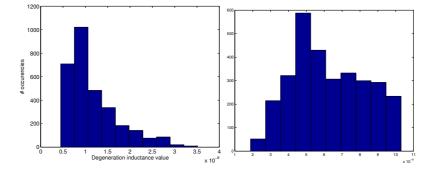

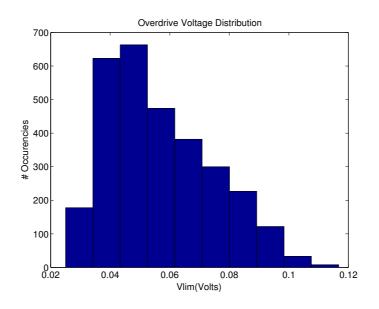

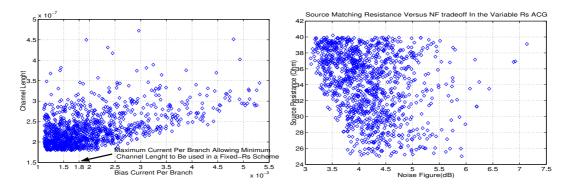

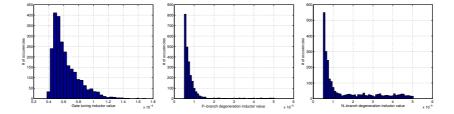

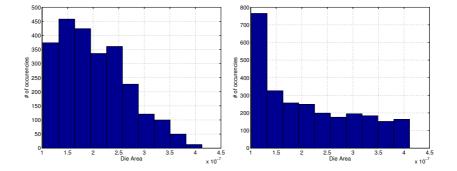

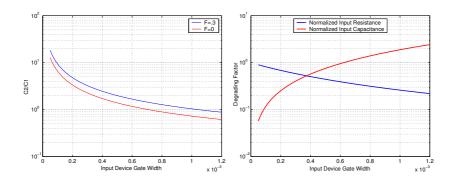

|              |                | 5.1.4 Results from input space sampling                         | 65       |

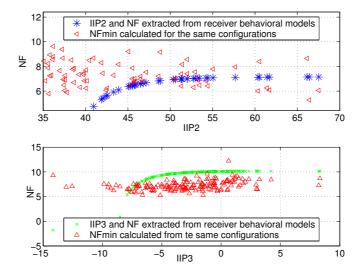

|              |                | 5.1.5 Alternative Analog Constraint Graph                       | 68       |

|              |                | 5.1.6 Results from input and output space sampling              | 69       |

|              |                | 5.1.7 Accuracy and conservativity of the used sets of equations | 70       |

|              | 5.2            | Current Reuse Amplifiers                                        | 71       |

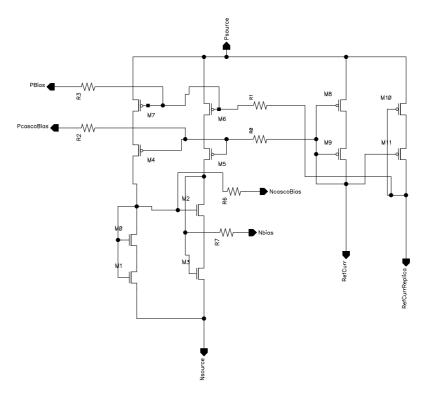

|              |                | 5.2.1 Bias circuit                                              | 71       |

|              |                | 5.2.2 Current Reuse Amplifier Analog Constraint Graphs          | 74       |

|              | 5.3            | Conclusions                                                     | 77       |

|              | 5.4            | Communication problems                                          | 78       |

|              | 5.5            | Interface Model                                                 | 80       |

|              | 5.6            | Low Noise Amplifier Linear and Nonlinear response model         | 82       |

|              | 5.7            | Platform Implementation                                         | 85       |

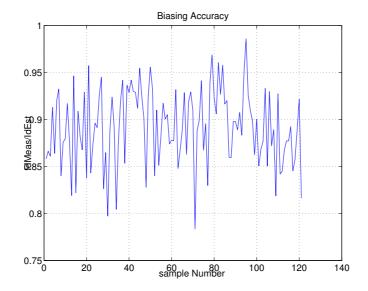

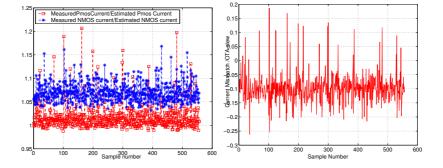

|              | 5.8            | Model Accuracy                                                  | 87       |

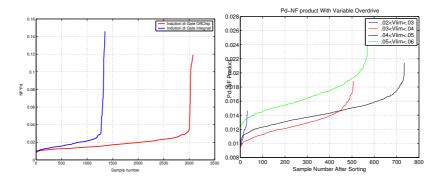

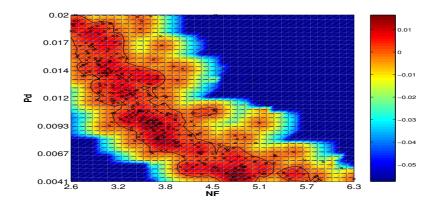

|              | 5.9            | System Level Optimization                                       | 88       |

|              |                | 5.9.1 Output Space Interpolation                                | 88       |

|              |                | 5.9.2 Optimazion                                                | 88       |

| 6            | Con            | clusions                                                        | 94       |

| Α            | $\mathbf{Sho}$ | rt-Channel MOS Model equations                                  | 96       |

| в            | Inp            | out Matching equations used in "Naive" NPMOS amplifier          | 98       |

| $\mathbf{C}$ | Effe           | ct of Pad Capacitance on input matching equations               | 99       |

| D            | Thi            | rd order distortion arising from second order nonlinear terms   | 101      |

3

### CONTENTS

A mio Padre, Diego Gambini

#### CONTENTS

**Ringraziamenti** Senza l'aiuto, i consigli e il supporto dell'Ing.Federico Vincis, questo lavoro non sarebbe arrivato neanche a metá.

L'Ing. Vincis non é solo incapace di fare male il proprio lavoro , ma si adopera anche per migliorare quello di chiunque abbia bisogno di lui in laboratorio con un'assenza di egoismo che non mi era mai capitato di osservare prima. É stato un onore lavorare con te Fede!

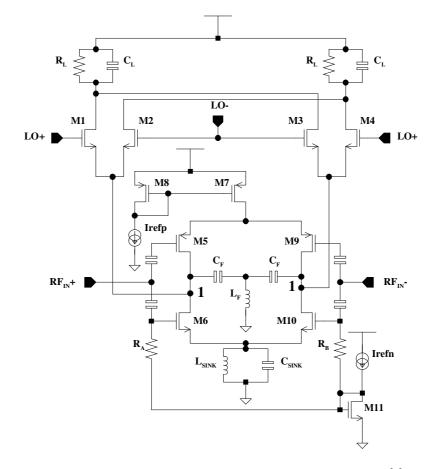

Un ringraziamento anche ai Prof.Rinaldo Castello e Francesco Svelto dell'Universitá degli studi di Pavia, per la cortesia dimostrata nel fornire il design del ricevitore, e nelle visite effettuate presso il dipartimento di Elettronica dell'Universitá di Pavia stessa per discutere il progresso del lavoro.

Grazie anche a mia madre e a mio fratello Francesco(a.k.a. Jann). Non ci sono parole per spiegare quello che mi avete dato. Grazie a Fabione, a mio nonno Andrea, alle mie nonne Edra, Enrica e Clara, a tutti i miei zii e le mie zie, compresi Zio Fosco e Zia Gabriella e Zio Mauro.

Grazie ai miei amici di Via S.Martino Stefano, Luca, Marco e Gabriele a Marta e Rossella, per le molte ottime cene e la compagnia ancora migliore offerte senza parsimonia. Grazie anche a Lorenzo, a Federico Maria Franzé e a tutti i miei amici di Piombino ovvero il Cetto, il Guero, il Buddha, il Sire, Iggio, i Rain Day, ovvero Ballack, lo Zanna, il Ross, il Gegia; a Gregory, Fede, Sara e la Gianfa, Ezio e il Villa. Grazie a Sanerio, ZonZibi, Steiner, al Ghignoletto, a Tiziano e al Mao per degnarmi ogni tanto di scendere da Bologna a considerarmi.

Infine, Grazie al Prof. Bruno Neri a all'Ing. Fernando De Bernardinis, che hanno avuto con me piú pazienza di quanto mi sarei aspettato in piú di una occasione.

Grazie

# Chapter 1

# Introduction

This thesis deals with the aged and traditionally prickly subject of Analog Design automation. As many other works, it is an attempt to capture and bridle into sets of equations and mathematical formalism that field of electronic design that, more than any other, has allowed whoever is part of it to define himself as "a lonely cowboy".

Despite many people think attempts in this sense are either intellectual crimes, or efforts with less probability of success than the fight of Lacoonte against the sea-snakes, this work was carried on with care, and interesting, although certainly non-definitive results were found. I hope readers will then temporarily forget their romantic idea of the figure of Analog Designer, and listen to the way this hopeless battle was fought.

## 1.1 A bit of Background

In recent years, the continuous scaling of digital CMOS technology has allowed an increasingly high number of functionalities to be implemented on a single chip; the increase in silicon potential has by far outpaced the corresponding evolution both of the designers capability to handle such an increased complexity and of the developed design aids; as a result, an increasingly wide "productivity gap" has appeared in the electronic industry. This is especially true for analog design, and most for what concerns system level design. Structured design patterns, which are the keystone to develop design automation, are all but established in the analog arena, so that even for a simple task such as sizing a two stage op-amp, unnumbered different choices and approximations may drive the design process toward different solutions. The approaches followed may be roughly summarized in equations-driven approaches, and simulation-driven approaches. The former approach is well represented by the works by M.Del MarHershenson([13] [14]), based on convex optimization theory, where a particular formulation of a  $1\mu$ , two stage op-amp circuit equations is introduced, that allows using efficient inner point algorithms to find the global optimum for any set of specifications. Although extremely interesting and powerful, this approach, as well as all of the known equation-based design automation patterns, has a critical point to cope with: the accuracy of the chosen device model, which is further constrained to generate equations posynomially representable. Developing models of this kind may be extremely time consuming, especially for deep submicron technologies and when small signal block nonlinear performance is a concern. On the other hand, simulation based approaches use the power of state of art transistor compact models to measure circuit performances. As a drawback, the optimization has to be performed on a generally nonconvex domain by means of expensive stochastic global algorithms (simulated annealing), so that the computational time increases exponentially with the number of considered degrees of freedom. Although

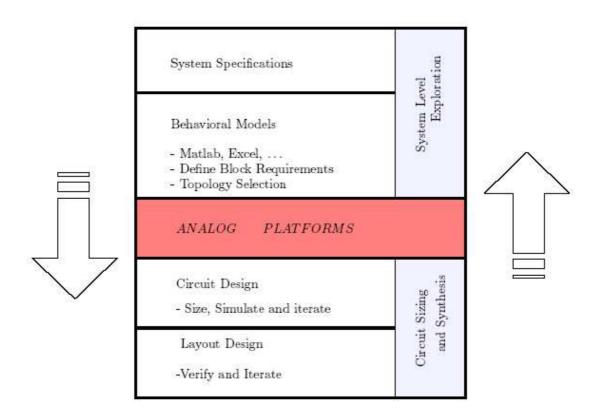

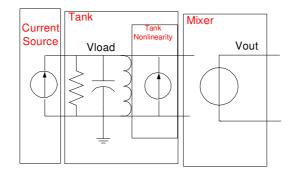

Figure 1.1: Analog Platform based design flow

useful to rapidly achieve high performance synthesis of small circuits, these methods fail both in treating large designs and in solving the theoretical problem of determining whether a given topology can or cannot satisfy a given set of specifications.

The above described scenario also has a detrimental influence on an higher level task such as architecture selection of a radio-receiver. The impossibility to claim rigorously claim feasible a set of system level performances for a given topology makes propagations of constraints to the different building blocks of any architecture based on previous design experience rather than on quantitative arguments. Experienced technical staff is therefore required in order to avoid system-circuit level design iterations that may increase the product time to market.

Even from the brief discussion above, it clearly appears that the key point in analog electronic system design is establishing a solid link between the architectural and the circuital level of abstraction, allowing high level design space exploration to be performed while enforcing blocks feasibility by construction. The platform paradigm is an attempt in this direction.

We may think an Analog Platform as an interface component between the system design world and the circuit design world. The system side of the analog platform is made up of a set of behavioral models. The circuit size is made up of class of ciruit instances described through an Analog Constraint Graph(ACG; see below).Simulation is used to relate this two sides, i.e. to extract from circuit instances satisfying the ACG, the parameters quantitatively describing the behavioral models(we'll call te set of these parameters output space or O-space). Encapsulating a circuit in an analog platform means using the platform infrastructure to avoid giving unsatisfiable performance specifications to such a circuit, in that any attempt to specify circuit performances is now filtered by the platfrom, as clarified by figure (1.1). Once provided of sets of suitable behavioral models, both the above described equation based and the simulation based design automation approaches may be fit into this description. For a simulationdriven design automation engine, behavioral models are related to circuit sizings through equations. This comes at the expense of generality and accuracy. For simulation driven sutomation engines, mapping of sizings into higher-level performances happens through direct simulation. The main drawback , besides the scarce intellectual satisfaction deriving from nonglobality of the solution, is the exponential rise in computational time with increasing circuit dimension as, basing on the assumption of inaccuracy of equation-based approaches, only bounding boxes (i.e.  $X \in [a, b]$ ) constraints are imposed on design variables.

As mentioned above, for the platform approach, circuit performances are still measured through simulation; on the other hand, circuit sizings may only be such that a set equations referred to in the following as Analog Constraint Graph(ACG) is satisfied. The set of equations "shapes" input space, consistently reducing its size. Another innovation of the platform paradigm comes from output space interpolation. The general idea is to feed a neural network(in [56] a statistical classifier) with the measured performances and to stop the sampling process when the machine learning process ends. This allows a further decrease in the number of simulations required to explore the performance space. Now , we summarily describe platform based design flow, which is graphically summarized in (1.1). Supposing to be designing a system such as an ADC or an integrated radio exploiting analog platforms, system level exploration and optimization may be performed using platform specific behavioral models. Thanks to the use of platform paradigm , these specifications are reachable BY CONSTRUCTION. At this point, the inverse of the performance evaluation function is used to derive optimal sizing of the building blocks themselves.

To transform the preceding discussion into an operating methodology, care must be put in two points:

- 1. Definition of blocks output space and behavioral models

- 2. Definition of the Analog Constraint Graph of each block, and of the necessary device model

## 1.2 UMTS receivers and goal of the work

The Universal Mobile standard for Telecommunication(UMTS) has been recently introduced into the consumer electronics market as an enabling technology for high data rate cellular communication. It is a Frequency-Duplex, code division multiple access(CDMA) based, direct sequence spread spectrum standard with operating frequencies in the 2GHz range. The details about chosen modulation format, despreading gain, and data frame structure are reported in [11] and won't be reproduced here. For the purpose of this work, operating bandwidths, signal multiplexing schemes and intermodulation tests are a sufficient background. The UMTS uplink bandwidth (Base station receives, mobile unit transmits) lies between 1.92 and 1.98GHz, while the downlink is collocated between 2.11 and 2.17GHz. Signals are partitioned in twelve nearby slots in the assigned 60MHz bandwidth, and further code-division multiplexed. Of this 5MHz overall channel bandwidths, only 3.84MHz have informative content, the rest being guard-band. Being UMTS a frequency duplex standard, receiver linearity is critical, as all incoming signals are superimposed to a transmitter leakage spaced only a few tens of megahertz from the signals itself, and probably much larger in amplitude. If a direct conversion architecture as that reported in [2] is chosen, linearity considerations must be applied to both second and third order distortion [54]. Role of high linearity design is further underscored if active mixers are chosen, which, introducing a flicker noise component that degrades the receiver noise figure, reducing system distortion budget. Research efforts have therefore been carried out in the past to understand correct ways to model intermodulation

4

distortion in RF building blocks([51], [50]), and to account for this distortion at a system level([55], [11], [2]), to enable aware architectural choices. When linearity constraints are conjuncted with noise constraints, radio receiver design space becomes extremely narrow (and in a real design one should account for I/Q imbalance, which was not made in this work). System level tradeoffs must be therefore accurate, and understanding the way the parameters describing blocks are related(e.g. relation between gain and linearity simultaneously achievable by a given block at a given current consumption) is a must. This work started from an exhisting design of direct conversion UMTS receiver, developed at the University of Pavia and described in ([11],[50],[2]), with the aim to develop and test a design space exploration tool for UMTS CMOS radio receivers, which, based on the platform paradigm described above, could constitute a solid system level framework act to confirm or improve results presented in [2], [11] and [50] and based more conventional approaches(i.e. design experience and simple behavioral models).

## 1.3 Roadmap

As the main critics that the design community usually addresses to works in the field of analog design automation are dependence on technology or application, and lack of a scientific approach (i.e. there is no quantitative way to "measure performances" of a design methodology, so that there is no quantitative way to "design" a design methodology), I'll apply the platform paradigm to the case study in such a way to make it most immune to these critics. Designing an analog platform quantitatively means understanding what properties must have the behavioral models used in the system optimization phase, and what accuracy is required by the modeled system for the various model components(linear and nonlinear responses, gain). We'll perform this analysis in the next chapter. Dependence on technology and application is imbued in the Analog Constraint Graph and in the behavioral model. An analog constraint graph based on rough device models, and conceived with in mind one precise application, will unavoidably be inaccurate when a different technology or a different application is modeled. The same holds for behavioral models as well. As a result, a considerable amount of time will be spent in studying accurate device models for use in the ACG, and in solving specific problems introduced by the use of so accurate models in the context of a platform paradigm. Also, a careful analysis of the sources of nonidealities (noise and distortion) in the modeled amplifiers will be performed to understand the accuracy of the proposed behavioral model. Particular emphasis will be on understanding third order nonlinearity arising at the LNA-Mixer interface port, a subject that, to the author's knowledge, has never been treated in depth in RF design literature. This is the subject of chapter 3 and 4. Pieces are put together in chapter 5. Here, a behavioral model is proposed for the low noise amplifier that keeps into account linear and nonlinear effects arising from communication with the mixer. This model is parametrized in terms of simultaneously selected LNA output space parameters. System optimization of the receiver based on the proposed set of behavioral model is also performed and discussed. Conclusions follow.

## Chapter 2

# System Level Modeling

### 2.1 Model Requirements

Real feasibility of system level design crucially depends on the chosen behavioral models. Models should be accurate enough to allow realistic estimates of system-level non-idealities, and yet simple enough to be practical for hand-exploration of system potentialities, or at least to achieve reasonable computation time if fed to a numerical optimizer. The accuracy and simplicity requirements obviously are contrasting, so that a tradeoff is unavoidable. This chapter deals with representations of mildly nonlinear RadioFrequency circuits and systems. Complexity arising from nonlinearity is in this case added to complexity deriving from the large differences in time constants which is typical of Radio Frequency communication systems.

Two different representations(Volterra Series and Describing Functions) are discussed and compared. A set of models based on Volterra series is proposed, and the complexity of this models is evaluated; finally, sensitivity analysis is used to relate block model parameters accuracy to receiver signal to noise plus interferer ratio accuracy predictions.

## 2.2 Input independent representations of nonlinear systems

Whereas linear systems excited with a purely sinusoidal input respond with a purely sinusoidal output of different phase and frequency, nonlinear systems exhibit totally different behavior: spectral components of the outputs always includes harmonics of the input tone; while subharmonics are sometimes encountered as well. Even if we only choose to deal with steady state response, initial conditions and input waveform play a critical role in determining the spectral component of the output. To avoid this kind of complications, we chose to model only asymptotically stable nonlinear systems which do not exhibit subharmonic lock. The minimum requisite of our representation is that it has to be input independent, i.e. the set of parameters appearing in the model equations must NOT depend on the input waveform. Examples of this kind of models are both describing functions and Volterra series based models.

#### 2.2.1 Describing Functions and Generalized describing Functions

Describing functions theory is well known in the field of nonlinear control systems theory [7], where it has mainly been used for the stability analysis of nonlinear systems. They have also been used in local oscillator design [6]. Consider now a stationary SISO nonlinear system excited with a sinusoid of frequency  $f_1$  and amplitude A. If the system is asymptotically stable, steady-state response y(t) will then be periodic with frequency fundamental frequency  $f_2$ . We define  $n_{th}$  order describing function of the system the quantity

$$G_n(f_1, A) = \frac{\int_0^{\frac{1}{nf_2}} y(t)e^{(j2nf_2\pi t)}}{A}$$

(2.1)

i.e. the ratio of the  $n_{th}$  harmonic of the output spectrum to the amplitude of the input. If the system under exam is linear, then this function does not depend on A and reduces to the frequency response of the linear system. If on the other hand the system is a memoryless nonlinear system, frequency dependence disappears. This description may be used without any extra workload to deal with systems which exhibit subharmonic lock. If this does not happen anyway,  $f_2 = f_1$  holds. To better understand the nature of this description, suppose that the nonlinear system of interest is excited by a single tone at frequency  $f_2$ , and followed by a band-pass filter of central frequency  $kf_2$  and bandwidth  $B \leq f_2$ . If this happens the system output will contain only the k-th harmonic, and a  $k_{th}$  order describing function will be an exact representation of the system whenever a single tone excitation is provided (This also is a methodology to measure describing functions). The main problem with this kind of representation however occurs when the system is excited with arbitrary inputs. Two tone input waveforms with tones at frequency  $f_1^1 and f_1^2$ , and amplitudes  $A_1 and A_2$  will give an output with frequency  $f_2 = GCD(f_1^2, f_1^1)$ . We may define a generalized second order describing function to cope with these situations. In general, m-tones input may be described by a n-th order generalized describing function, defined as

$$G_n(f_1...f_m; A_1...A_M) = \int_0^{\frac{1}{nf_o}} y(t)e^{2j\pi f_o nt}dt$$

(2.2)

$$f_o = GCDf_i i = 1...m \tag{2.3}$$

We remark here that

$$G_n(f_1, 0, 0, ..., 0; A_1, 0, ..., 0) = G_n(f_1, A_1)$$

so that the single tone describing functions may be derived from the multiple tone ones. It is also apparent that the most general representation of this kind for a nonlinear system is an application  $G^*$ :  $(R \times C)^{\infty} \to (R \times C)^{\infty}$  (i.e. an application form the space of non-periodic spectra to the space of nonperiodic spectra), so that machine memory needs unavoidably put a limit on the attainable frequency resolution of any implementation of this method. Another major disadvantage of describing functions is the scarce modularity of this approach. Consider a memoryless nonlinear system with  $f_2$  periodic output and linear feedback network with frequency response  $\beta(f)$ . Moreover, suppose  $\beta(f_2) = -1, \beta(f), f \neq$  $f_2 = 0$  (ideal bandpass feedback), and suppose the system is characterized by  $G_1 = \frac{e^A}{A}$ . Overall first order describing function could be found simultaneously solving

$$in(t) = A - e^{in(t)}$$

$\int_{0}^{1/f_2} y(t)dt = e^{in(t)}$

Which cannot be made analytically. These problems discourage the direct use of describing functions when efficient behavioral models are needed; describing functions remain however a useful conceptual tool to their exact nature.

#### 2.2.2 Wiener-Volterra series

Wiener-Volterra series expansion of a nonlinear system may be derived in different ways, each highlighting one particular feature of the model.In [12], a methodology for deriving the expressions of Volterra kernels of a circuit containing nonlinear capacitors, resistors and current sources directly from nodal equations is shown. In [58] on the other hand, the relation between state-space representation of a

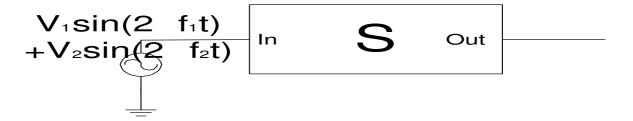

Figure 2.1: Intermodulation test

nonlinear system and its Volterra expansion is highlighted. Whatever derivation is followed, the output of a Volterra represented nonlinear system may be written as:

$$y(t) = h_1(t) \bullet x(t) + h_2(t_1, t_2) \bullet (x(t_1)x(t_2)) + \dots + h_N(t_1\dots t_N) \bullet \Pi_1^N x(t_i)$$

(2.4)

Here, dots represent convolution operations, and quantities  $h_i$  are called generalized impulse response functions, or Volterra Kernels, of order i. If Fourier transform of both members is taken, equation (2.5) is obtained:

$$Y(f) = H_1(f)X(f) + \int_{f_1 = -\infty}^{f_1 = +\infty} H_2(f - f_1, f_1)X(f - f_1)X(f_1)df_1 + \dots$$

(2.5)

Where quantities  $H_i$  are obtained as i-dimensional Fourier transforms of the i-th order Volterra Kernels. Volterra expansion has been proven to achieve uniform convergence over compact sets([58]); while global uniform convergence is only achieved for a particular class of systems , referred to in [21] as fadingmemory systems. Major problems of Volterra representation come from system identification. Despite different nonlinear terms give spectrally superposed responses, a frequency domain approach based on (2.5) is the most natural choice; however, it requires accurate choice of input frequencies([20]). Moreover, the number of frequency points chosen for identification has a sensible impact on model accuracy [8] and cannot be optimally determined a priori. A different approach could be that of building Volterra models from circuit analysis and device models, as suggested in [12]. Although useful from a circuit design perspective, this approach cannot be accurate from a quantitative standpoint due to the lack of sufficiently accurate device models [35]. Volterra modeling anyway presents sensible advantages over describing functions, principally in the fact that the a fixed set of kernels may be used for describing the system under any kind of inputs; and in the greater modularity of the approach (See [12] for a description of the ways of deriving a Volterra representation for a system obtained from the arbitrary connection of Volterra described systems).

#### 2.2.3 Relation between Volterra series and Describing function representation

In order to understand the connection between Volterra and describing function representation of a nonlinear system, consider figure (2.1) The system S is excited with two sinusoidal tones of amplitudes  $A_1$  and  $A_2$  and frequencies  $f_1$  and  $f_2$  such that  $f_1 - f_2 = f^* = GCD(f_1, f_2)$ . Therefore,  $f_1 = kf^*$ ,  $f_2 = (k+1)f^*$  holds. If we choose to adopt a describing functions based representation, third order intermodulation product evaluates to :

$$IMD_3^{1,DF} = G_{k+2}(A_1, A_2, f_1, f_2)$$

$$IMD_3^{2,DF} = G_{k-1}(A_1, A_2, f_1, f_2)$$

#### CHAPTER 2. SYSTEM LEVEL MODELING

. If a third order Volterra representation is assumed on the other hand, we have:

$$IMD_3^{1,V} = \frac{1}{4}H_3(f_2, f_2, -f_1)A_2^2A_1$$

$$IMD_3^{2,V} = \frac{1}{4}H_3(f_1, f_1, -f_{-2})A_1^2A_2$$

If harmonic responses are now considered, we have

$$y(f_1)^V = H_1(f_1)A_1 + \frac{3}{4}H_3(f_1, f_1, -f_1)A_1^3$$

$$y(f_1)^{DF} = G_k(A_1, 0, f_1, f_2)$$

We suppose now to be dealing with a memoryless nonlinear system, so that y(t)=g[x(t)] with  $g: R \to R$ . If nonlinear system transformation g is assumed analytical and  $A_1 + A_2 \leq r_g$  where  $r_g$  is the convergence radius of the Taylor series expansion of g, we may integrate per per series to arrive at

$$G_{k+1}(f_1, f_2, A_1, A_2) = \int_0^{\frac{1}{f^*}} g(A_1 \cos(2\pi f_1 t) + A_2 \cos(2\pi f_2 t)) \exp(2(k+1)\pi f^* t) dt = \sum_{i=0}^\infty \int_0^{\frac{1}{f^*}} \frac{a_i}{i!} (A_1 \cos(2\pi f_1 t) + A_2 \cos(2\pi f_2 t))^i \exp(2\pi (k+1)f^* t) dt$$

(2.6)

When the polynomial operator is applied to the sum of sinusoids, all harmonics of the GCD of these two sinusoids are generated. Due to the orthogonality property of sinusoidal functions, however, only contributions at frequency  $(k + 1)f^* = 2f_2 - f_1$  give to describing function a non zero contribution. We know one of these terms to be given by the cubic nonlinear term  $a_3$ . Under the hypothesis made of  $f_1/f_2 = k/(k-1)$ , it can be shown using elementary discrete mathematics [26] that other terms contributing to output at  $(k + 1)f^*$  occur for nonlinear coefficients  $3 + n \cdot (2k - 1)$  where  $n \in N$ . This is a very interesting result. Suppose in fact a maximum nonlinearity order M is to be considered(i.e. suppose to know that for values input signals occurring in practice, function g is well approximated by the first M terms of its Taylor expansion): in this a different number of nonlinear terms will contribute to nonlinear distortion depending on system input frequencies. Moreover we also see that if k is high the intermodulation response of the system will be third-order nonlinearity dominated, independently of the overall system nonlinearity. Repeating preceding calculations for the first order one input describing functions  $G_1$  gives:

$$G_1(A_1) = \sum_{i=0}^{\infty} A_1^{2i} \frac{a_{2i+1}}{(2i+1)!}$$

(2.7)

so that effectively all of the odd nonlinear polynomial coefficients contribute to gain compression or expansion. We also see that whenever third order nonlinearity is assumed dominant, a tradeoff occurs between identifying gain compression and intermodulation distortion characteristics of the system.

#### 2.2.4 Linear Periodically Time-Varying Systems

Linear Periodically time varying systems have been introduced in Electrical Engineering to deal with nonlinear systems exhibiting a strongly nonlinear behavior with respect to one input port and an almost linear behavior with respect to other excitations. The classical example of this situation is mixer RF port modeling([22],[4]), although great results have been obtained as well in [24],[3] for phase noise modeling. A linear Periodically time varying system is described by a an impulse response function,  $h(t, t-\tau) = h(t+T, t+T-\tau)$ ). Conversely to the LTI case, dependence on t must be explicitly included. Output to such a system at time t is calculated via superposition integral:

$$V_u(t) = \int_0^t h(t, t - \tau) u(\tau)$$

(2.8)

Due to  $h(t, t - \tau)$  periodicity in t, we may expand it as a Fourier Series:

$$h(t) = \sum_{k=0}^{\infty} h_k(\tau) \exp\left(j * k * 2 * \pi \tau/T\right)$$

(2.9)

Substituing (2.9) into (2.8), we have

$$V_u(t) = \sum_{k=0}^{\infty} h_k(\tau) \exp\left(j * k * 2 * \pi \tau/T\right) \bullet u(\tau)$$

(2.10)

$$V_u(f) = \sum_{k=0}^{\infty} h_k(f)u(f - k/T)$$

(2.11)

This modeling methodology the basis of Spectre Periodic AC analysis, and is especially useful when response to the large tone may be efficiently and accurately calculated. Labeled H(V, f) the voltage dependent system transfer function and  $O(f_1, A_1)$  the operator result of the solution of steady state circuit equations with input frequency  $f_1$  and amplitude  $A_1$ , then saying the circuit is approximated by a PSS + PAC behavior is equivalent to saying that  $H(O(f_1, A_1), f_2) \mid_2 A_2$  (where  $\mid_2$  denotes second harmonic) is an expression of the second order system describing functions. As a result, conclusions drawn in the previous chapter about describing functions may be extended to the case of LPTV systems and PSS + PAC representations.

### 2.3 Proposed continuous time model

Proposed models were built in a Volterra Series framework. Developed models are suited to all those systems which can be represented by a signal flow graph made of arbitrarily connected Linear Time Invariant and Polynomially Nonlinear systems. The major problem with modeling RF systems is the existence of narrow band signals centered around high frequency carriers. We deal with this kind of signals using a slight modification of classical complex-envelope theory [23]. The main difference with classical theory is that there could be the need of feeding a signal with a spectrum consisting of narrow band signals centered around harmonics of a fundamental carrier  $f_0$ . Consider for now the case of an input spectrum made up of N equally spaced tones, fed into a system such that its output y(t) is related to the input x(t) by  $y(t) = x(t)^2$ . If  $c_0, c_1, ..., c_N$  are the tones amplitudes, and calling the output spectrum  $o_0, ..., o_{2N}$ , we may write:

$$o_{i} = \sum_{k=i}^{N} c_{k} c_{i-k} = \vec{c} \bullet \vec{c}(i)$$

(2.12)

$$c_{-i} = \bar{c}_i \tag{2.13}$$

$$i = 0...2N$$

Suppose now a higher nonlinearity order is present. We may see the operation of calculating the output of a such a nonlinear system built of two steps: in a first step, power of the input signal up to the order of nonlinearity K are calculated, later these are scaled by the polynomial coefficients and added.

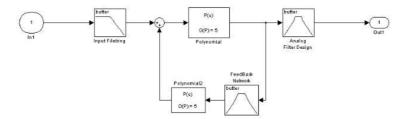

Figure 2.2: Example of system structure

In order to calculate the third order terms  $o'_i = 0...3N$  once second order response  $o_i(t)i = 0...2N$  is known, it is sufficient combining such a second order response with the input in a manner similar to the one described above:

$$o_i' = \sum o_k c_{i-k} = \vec{o} \bullet \vec{c}(i) \tag{2.14}$$

Fastest way to do this is using fast convolution algorithms, which are present in MATLAB library. We further notice that all the information necessary to perform calculations is contained in the  $c_i, i \ge 0$ , as  $c_{-i} = \bar{c_i}$  holds. The model of computation may be summarized as follows:

- 1. Given  $\vec{c}$ , compute  $c_i, i < 0$  and define  $\tilde{c} = [\vec{c}, c_i, i < 0]$

- 2. Put  $o_0 = \tilde{c}$

- 3. Put  $o_i = o_{i-1} \bullet \tilde{c}$ . Repeat this step for i=1 to N

- 4. For i < N 1 (nonlinearity order), zero pad  $o_i$  so that  $dim(o_i) = dim(o_N)$  holds  $\forall i$

- 5. Compute  $\sum_{i\geq 0} o_i$

Now, it is important to notice that even though this model of computation has been described for timeindependent  $c_i$ , it is still valid as long as these coefficients are a slowly varying function of time. The signal is then a quasi-sinusoidal signal, or a multi carrier narrow-band signal. Mathematical condition for this to hold is that the narrow-band spectra centered around the harmonics at the output of the nonlinear block are disjoint, i.e.

$$B_{in} \le \frac{f_{carrier}}{2K} \tag{2.15}$$

Where  $B_{in}$  is the maximum of the bandwidths of input signal complex envelopes, and K is the nonlinearity order.

#### 2.3.1 Discrete-Time modeling

Even though the use of baseband equivalent representation saves substantial computational time for narrow band signals, the use of a variable step integration process for solving model equations may still be an overkill. This overhead may be reduced through a discrete time implementation. This transformation solely regards the frequency dependent part, as memoryless nonlinear blocks are left unchanged. Filters are converted to baseband equivalent representation and discretized by sampling their continuous time frequency response with step  $\Delta F$ , and using a MATLAB optimization algorithm to find the optimal IIR representation has been preferred due the better stability properties of the MATLAB IIR filters nonlinear phase response synthesis tool with respect to the FIR filters one. The discretization frequency  $\Delta F$  is related to the output signal bandwidth B , to the sampling frequency and to the execution time of the system by the relation:

$$\Delta F = \frac{2B}{T_{tot} f_{sample}} = \frac{4 * B^2}{T_{tot}} \tag{2.16}$$

If, as it is the case in the proposed model, frequency resolution may be chosen by the user, then (2.16) may be used to choose  $T_{tot}$  the model execution time. Discrete-time models introduce an extra-degree of freedom in the modeling effort, allowing to trade off frequency resolution for computational time as highlighted by equation(2.16). Anyway, neither this class of models solves the main disadvantage of building time-domain models, which arises when multiple nonlinear blocks are connected in series. In these circumstances, overall nonlinearity rises exponentially, exponentially increasing output signal bandwidth. If we suppose to model a radio as a cascade of three third order nonlinear blocks, representing LNA, mixer and baseband chain, an overall nonlinearity of twenty seventh order is obtained. Recalling that UMTS carrier is about 2Ghz, equation 2.15 stops being satisfied when  $B_{in} \approx 37Mhz$ . This reduced value does not allow, for example, to perform the UMTS intermodulation test. Furthermore it is worth noticing how, even for the standard, 1 channel UMTS bandwidth of 5Mhz, the maximum required computation time has decreased up to a value of 3.7nS, which is extremely short. If time-domain simulation remains the choice, this complexity increase may be dealt with by adding after each an anti aliasing filter with cutoff frequency  $f_{max} \leq B_{in}$ .

Obviously, this comes at the expense of accuracy.

#### 2.3.2 Frequency Domain model

If now Fourier transform of 2.14 is taken, then one obtains

$$O_{h}^{i}(f) = \sum_{k=-M}^{k=M} O_{k}^{i-1} \bullet C_{h-k}$$

(2.17)

We remark that  $\vec{C}$  is the Fourier transform of  $\vec{c}$  and as such, is composed by N vectors(one for each of the input carrier harmonics). Each vector will have  $K' = \frac{B}{\Delta F}$  components. Equation(2.17) is quite more complex than (2.14). We see that elements of  $O^{i-1}$  and C (which are vectors) are convolved and then summed in a convolutional way. In order to get better understanding of this process, consider Kronecker Product[17] between two vectors  $\vec{a}, \vec{b}$ . This will be a matrix G such that:

$$G_{i,j} = a_i * b_j$$

Summing the elements on the k-th non principal diagonal of G:

$$S_k = \sum_{j=-M}^{M} a_j b_{k-j} = (\vec{a} \bullet \vec{b})(k)$$

(2.18)

If now we make the hypothesis  $a_i \forall i$  is a K' elements row vector, and substitute multiplication in (??), with convolution, we get to (2.17). Further notice that not due to hermitian symmetry of spectra, it is not necessary to calculate all the terms of the Kronecker product: posing  $dim(O^i) = M, dim(C) = N$ , and recalling that  $M \ge N$ , we see that only the non-principal diagonals of index  $i \ge -(M - N), i \le N$  need to be considered. In this representation, linear filtering is equivalent to element-wise multiplication with a NxK' matrix, which represents the system frequency response sampled as described by (2.19):

$$H_{i,j} = H(i * f_c + j * \Delta F) \tag{2.19}$$

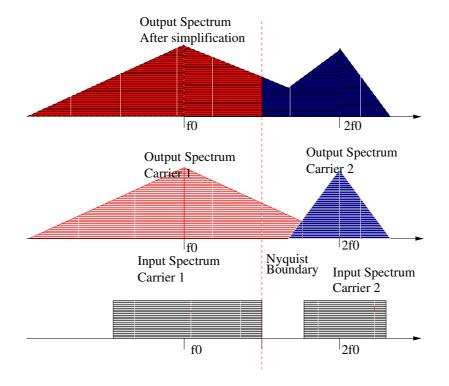

We further recall this model is inherently a continuous time model, so that there is no need for solving differential equations in this model. This eliminates the need for the tradeoff between frequency resolution and execution time proper of time-domain models. If calculations performed with this model have to be compared with a discrete time model, the aforementioned tradeoff is obviously reintroduced, as in order to obtain a frequency resolution of  $\Delta F$ , a system with input bandwidth B and sampling frequency  $f_c$  has produce exactly  $N = \frac{2B}{\Delta F}$  samples, which in takes us back to equation (2.16). Finally, we also see that the minimum computation time dependence on considered nonlinearity order here is absent(there is no execution time). However, equation (2.15) still has to hold if spectra corresponding to different harmonics do not have to overlap. If this equation should not hold for some block on the other hand, spectral superposition may easily be computed. This information may be easily be used to update the spectral description matrix (See [9]). Reader will anyway notice that if this happens, there is certainly less and less gain in computational complexity from using a multi-carrier baseband equivalent model. We'll make an example to see how this happens. Suppose input bandwidth is 80Mhz, and there is only one carrier with frequency is 200Mhz. For a nonlinearity of order 3, baseband equivalent spectrum around carrier fundamental becomes 240Mhz, while that around harmonic number 2 and DC is 160Mhz. Baseband equivalent spectra are superposed now, but is no matter if superposed zones are simplified before next nonlinear operations are performed. The transformation is shown in figure (2.3)

#### 2.3.3 Tone Based Model

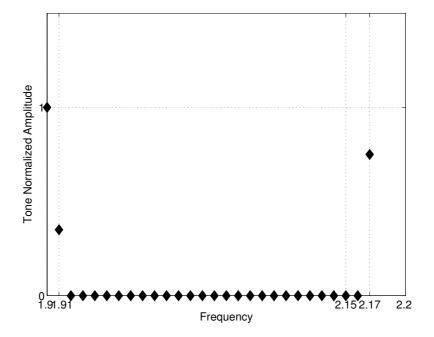

There are circumstances under which the proposed vector based model performs quite badly form a computational efficiency perspective. These may be generically classified as those where the input is made up of a very few tones, with strongly variable spacing. Consider for example the situation of figure (2.4). In order to obtain a vector based representation for this spectrum, a resolution of  $\Delta F_1$  has to be chosen. The spectrum is thus described by a vector of  $2 + \frac{\Delta F_2}{\Delta F_1}$  elements, while if input frequencies were specified along with amplitudes, a  $3 \times 2$  matrix would be enough. Even though complexity analysis of the models has not yet been performed, it is intuitive to understand how this situation becomes unfair when  $\frac{\Delta F_2}{\Delta F_1} \gg 1$ . To deal with these situations a list based input representation is chosen. Input is now described as a  $K \times 2$  matrix, where K is the number of input tones, and only nonzero spectral components are represented. Nonlinear operations and filtering are performed only for those frequencies that included in the input and output spectra, saving a big deal of computation time in case of input sparse spectra.

## 2.4 Complexity evaluation for the proposed models

All of the proposed models are equivalent, in that they predict steady state behavior of system under exam, for any kind of inputs:therefore, use of one or another model solely depends on what has the lowest complexity and highest ease of use. Refer to the model shown in figure (2.2).Here we have discrete time execution, input signal bandwidth B around M harmonics.Filter frequency resolution is still  $\Delta F$ , and nonlinearity order N. From (2.16) we find  $\frac{T_{sim}}{T_{exec}} = \frac{2B*N}{\Delta F}$  which is the number of timesteps needed.For each timestep, output of 2 IIR filter and a nonlinear block has to be calculated. Supposing for the sake of

Figure 2.3: Spectral superposition and simplification for FD models if (2.15) doe not hold

Figure 2.4: Example of spectrum ill-conditioned for a vectorial frequency domain model (frequency domain stiff system): the total bandwidth is imposed by  $f_3 - f_1 = 280MHz$ , while  $\Delta F = f_2 - f_1 = 10MHz$ : a 28-element vector is required for vectorial representation, despite only three tones are present.

#### CHAPTER 2. SYSTEM LEVEL MODELING

simplicity this filters to have the same order s, then this takes (N+1)s multiplications for each timestep, for each harmonic (The term N is due to the fact the as in *SIMULINK* multirate model execution is supported, filter collocated after the nonlinear block will have an execution time N times higher than the one preceding it, as reflected by 2.16). Input harmonics are M, while output harmonics are NM. Then number of multiplications required to calculate filter outputs is  $N \cdot (M+1) \cdot (N+1) \cdot s$ . For the nonlinear block, N convolutions have to be performed. If these are calculated using a fast convolution algorithm([17]), each convolution requires calculating two FFTs, a product and a IFFT. Computational expense for computing the FFT of a j-elements vector is  $j \log j$ , so that complexity for each convolutional step may be written as:

$$3(j_1 + j_2 - 1)(1 + \log(j_1 + j_2 - 1))$$

For the case in exam, put  $D_i = dim(o_i)$ ,  $D_{in} = dim(C_{in})$ :

$$N_{mult} = \frac{2 * B * N}{\Delta F} (N(M+1)(N+1)s + \sum_{i=1}^{N-1} D_i \log (D_i) + D_{in} \log (D_{in})...$$

(2.20)

$$+(D_{in} + D_i - 1)\log(D_{in} + D_i - 1)$$

(2.21)

$$D_{i+1} = D_i + D_{in} - 1 \tag{2.22}$$

$$D_1 = 2M + 1 = D_{in} \tag{2.23}$$

It is easy to prove that

$$D_i = 2 * M * (i) + 1$$

, so that the nonlinear terms contribution becomes:

$$N_{mult}^{NL} = \sum_{i=1}^{N-1} 3(2M \cdot (i+1) + 1) \log (2M \cdot (i+1) + 1))$$

(2.24)

Linear dependence on input bandwidth is apparent through the factor  $\frac{2B\cdot N}{\Delta F}$ , which also shows an hyperbolic dependence on frequency resolution.Dependence on N and M is super linear, and in particular, dependence on N is stronger the higher is M. Consider now the frequency domain model. Here all computations are performed at the same time(there are no timesteps). We further suppose all of the channels to have the same bandwidth, and thus the same number of elements in each row.Filtering operations each require vector multiplication: if M channels are present, each with  $\frac{2B}{\Delta F}$  channels are present at the input, at the output there will be M channels, each with  $\frac{2N\cdot B}{\Delta F}$  components. Thus, total number of operations for the linear part is  $\frac{2BM}{\Delta F}(N+1)$ . For the nonlinear part, N convolutive steps have to be performed. For each of this steps, the non-principal diagonals of a Kronecker product matrix are considered. We remark that these matrices are obtained from vector products in the form  $\vec{b} \diamond \vec{a}$ , with  $\dim(\vec{b}) \ge \dim(\vec{a})$ . Moreover, we recall that only positive output harmonics are calculated. Consider than a  $(2N+1) \times 2M + 1$  matrix A, and define i-th non principal diagonal the set of coefficients  $A_{(2N-i-k),+k}$ . Because of the imposed size constraints, one finds:

$$2N - i - k \in (0, 2N) \to k \in (-i, 2N - i)$$

(2.25)

$$k \in (0, 2M) \tag{2.26}$$

$$i = N - M - 1...2N \tag{2.27}$$

Solving (2.27) yelds

$$k \in (0, 2M+1)i \ge 2(N-M) \tag{2.28}$$

$$k \in (0, 2N - i)i \prec 2(N - M) \tag{2.29}$$

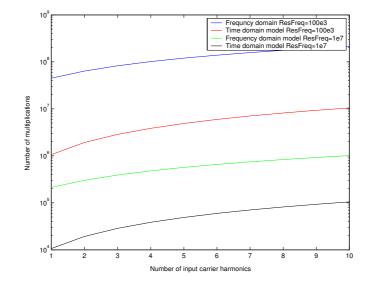

Figure 2.5: Comparison of complexity of time and frequency domain models

Thus, number of convolutions to be computed is

$$N_{conv} = (N - M + 1)(2M + 1) + \sum_{i=0}^{2(N-M)} 2N - i = (N - M + 1)(2M + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 1) - (N - M)(2(N - M) + 1) + 2N(2(N - M) + 2N(2(N - M) + 1) + 2N(2(N - M) + 2N(2(N - M) + 1) + 2N(2(N - M) + 2N(2(N - M$$

, and after rearranging terms:

$$N_{conv} = 2N^2 - 4M^2 + 2NM + 2M + 2N + 1$$

(2.30)

Each convolution is made between a vector of length  $j_1$  and one of length  $j_2$ , and finally complexity becomes:

$$\sum_{i=1}^{N} N_{conv}^{i} \cdot C_{conv}^{i} \quad (2.31)$$

$$N_{conv}^{i} = 2(2(M-i)+1)^{2} - 4(2M+1)^{2} + 2(2M+1)^{2} + 4i(2M+1) + 2(2(2M+i)+2) + 1 \quad (2.32)$$

$$C_{conv}^{i} = 3(1 + \frac{2B(i+1)}{\Delta F})\log(1 + \frac{2B(i+1)}{\Delta F}) \quad (2.33)$$

Evaluation of the preceding formulas show that time-domain model requires about one order of magnitude less multiplications than a frequency domain one.On the other hand, frequency domain model has been implemented in MATLAB, which is naturally a faster environment than Simulink: as a result,difference in execution times is not so bad. However, the frequency domain model was not used in this work, as the tone based model is better suited to the spectra of isgnals used [2] to perform UMTS tests. For what regards the aforementioned tone based model, computations are here performed directly. Suppose that the tone based represented model is excited with M tones.Input filter computations will then require M multiplications. Before taking care of the output filtering step, the nonlinear block is examined. We need to compute both the frequencies and the amplitudes of the tones which build up the output spectrum. The model used computes all of the output tones, and then simplifies eventual outputs with the same frequency. For a signal made up of M tones, fed into a nonlinearity of order N, number of output tones is

$$N_{outTone} = \sum_{i=1}^{N} (2M+1)^{i} = \frac{(2M+1)((2M+1)^{N}-1)}{2M}$$

Where positive and negative tones are considered in the final expression. As usual, the factor 2M+1 derives from the need to consider both positive and negative frequencies in these computations. Many of these tones will actually have the same frequency and thus will be recompacted after simplification. Moreover, it is the simplification process itself to give to each output tone the correct multiplicity. A different approach might rely on calculating output tones multiplicity symbolically, and calculating only the terms resulting different from symbolic analysis. Obviously, this approach does not eliminates the need for simplification to be made after computing nonlinear terms, but dramatically reduces the number of output tones. Supposing a nonlinear product of order j is considered, with M positive input tones, say  $f_1...f_M$ , plus DC, output frequencies may be written as

$$F_o = \sum_{\sum n_i = j} n_i f_i$$

. Coefficients for each of these output frequencies may be derived from elementary combinatorial calculus(see for example [15]) to be equal to

$$C_o = \frac{j!}{\prod_{\sum n_i = j} n_i!}$$

Also notice that this approach actually requires performing operations on just M+1 tones, as one can use hermitian simmetry to eliminate the negative side of the spectrum. Although this approach might seem appealing, it requires coefficients  $C_o$  to be either calculated or stored, adding "hidden" complexity. For this reason, it is not practical to implement tone based models when either the nonlinearity order or the number of input tones is exceedingly high. Conversely, they represent a conceptually simple approach, and they are effective for low-complexity, sparse spectra as those used in UTRA-FDD tests.

### 2.5 Model Implementation

**Time Domain Model** All time domain models have been implemented in  $Simulink^R$ , and completed of MATLAB scripts used to set their parameters and execute them from command line ([10]). The blocks have been and parametrized in function of the input bandwidth, so that execution time of each block is automatically calculated to be the minimum such that conditions of 2.16 hold. As already mentioned, in the early phase of the work filters were converted to baseband and discretized using a general frequency domain approach and MATLAB algorithms for IIR filters synthesis. This choice was made in order to produce the maximum stability and generality of the approach, especially when nonlinear phase response filters are a concern. In light of the knowledge acquired in the course of work, we saw that most filters can be modeled as second order bandpass sections with a low quality factor; furthermore predicting phase response generally falls outside the scope of behavioral models. In light of these details, filter synthesis process could be re-evaluated at the purpose of replacing IIR filters with FIR filters and decreasing the computational effort associated with performing the Filter Synthesis. One of the problems encountered during the use of complex valued time domain models lies in evaluating intermodulation distortion terms. As previously stated, a two tone input of amplitude  $A_0, A_1$  and frequency separation  $\Delta F$  is represented in this model as  $V_{in} = A_0 + A_1 \exp j2\pi\Delta F t$ . Third order intermodulation products lie at  $f_1 = f_0 - \Delta F$ ,  $f_2 = f_0 + 2\Delta F$ , so one of these terms is actually

spectrally superimposed on one of the signals in this complex representation. To separate these two contributions, complex processing is performed on the signal itself. In detail, third order contributions at frequency  $f_0 \pm \Delta F$  become:  $-\frac{A_1^3}{4} \exp(2 \cdot \pi \cdot \Delta F t) + \frac{A_0^2 \hbar A_1}{4} \exp(-(j \cdot 2\pi \Delta F t))$  Which are superimposed to the linear term  $k_1 A_1 \exp((j \cdot 2\pi \cdot \Delta F))$ . Separating signal real and imaginary part and considering their value at  $t = t^*$

$$-\frac{|A^{2}|B}{4}\cos(x+2\phi_{a}) + (|A| - |A^{3}/4|)\cos(x+\phi_{a}) = Re(V_{u}(t))$$

$$+\frac{|A^{2}|B}{4}\sin(x+2\phi_{a}) + (|A| - |A^{3}/4|)\sin(x+\phi_{a}) = Im(V_{u}(t))$$

and finally

$$|IM| = \frac{\frac{Re(V_u)}{\cos(x+2\phi_a)} - \frac{Im(V_u)}{\sin(x+2\phi_a)}}{2}$$

(2.34)

$$|S| = \frac{\frac{Re(V_u)}{\cos(x+\phi_a)} + \frac{Im(V_u)}{\sin(x+\phi_a)}}{2}$$

(2.35)

Where  $S = |A - A^3/4|$  and  $x = 2 \cdot \pi \Delta F t^*$  and  $\phi_a$  is known. Similar problems also arise in the definition of input signals, so that ad-hoc signal and noise sources have also been developed. It may be interesting to detail the implementation of a pulse generator and of thermal and flicker noise generators. Consider for example a PSK modulated signal, which may be written as  $s(t) = \cos(2\pi f_c t + \Phi_K)$ . When this signal is considered in presence of a second sinusoid of frequency  $f_1 = f_c - \Delta F$  and amplitude  $A_1$ , representing transmitter leakage or another interferer, time varying phasor representa  $(A_1 + A_2 \exp(j2\pi\Delta F t + \Phi_K) = A_1 + A_2 \cos(\Phi_K)\cos(2\pi\Delta F t) - jA_2\sin(\Phi_K)\sin(2\pi\Delta F t)$ . Real and Imaginary part are generated separated and fed into the system.

For a white noise source, it is known ([23])that defined  $N_0$  the flat power spectral density, its band-pass equivalent is given by

$$n_i(t) + j \cdot n_q(t) \tag{2.36}$$

with  $n_i$  and  $n_q$  gaussian uncorrelated processes and  $S(n_i) = S(n_q) = \frac{N_0}{2}$ . The in phase and in quadarature terms are egenrated through  $MATLAB^R$  Band Limited White Noise block, and then phase shifted and added. Finally, flicker noise is generated through the algorithm reported in [46]. Notice that this generator is inherently real because carrier frequencies are supposed much higher than flicker noise corner frequencies of the modeled devices. Obviously all of random seeds of different noise sources are generated randomly at the beginning of the execution phase of the model itself, so as to minimize the correlation amongst sequences generated by the same source at different executions and samples of different source during the same execution.

**Frequency Domain Model** Because of the previously calculated high complexity, frequency domain model was never used in practice, despite the core scripts have been implemented and tested in MATLAB or simple input signals.

**Tone Based Model** The nonlinear tone based model implementation is due to F.Vincis and is described in ([1]). The use of this model resulted in a significant improvement in simulation time and ease of data access and interpretation with respect to the time domain model for the input signals assumed in [2] as test vectors, so that this model has been used as the engine of the optimization process descirbed in 5.9.2.

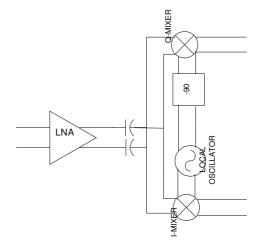

Figure 2.6: Receiver front end architecture

## 2.6 Sensitivity Analysis

In any attempt to build behavioral models of a class of circuit instances, model accuracy requirements have to be accurately evaluated. If the model is supposed to be used human operated system-level exploration, usually the accuracy requirements are very relaxed, especially if the intended operator is an experienced circuit designer, which can use behavioral models informations just as qualitative hints on circuits sizings. If on the other hand automated synthesis has to be performed, accuracy requirements are much more stringent. The effort reuired by the development of this kind of models is such that a quantitative way to trade-off accuracy on different circuit performances, given an application, must be envisioned. This section proceeds as follows: starting from receiver architecture, structure of the behavioral model of each block is chosen(i.e. block nonlinearity order, filter orders etc.) ; using the parameters of this model, expressions for the signal to noise plus distortion(signal to noise floor) ratio predicted by the model are given. Sensitivity analysis is finally applied to these equations, so as to relate global model accuracy requirements constraints to model parameters accuracy. In the following, we'll refer to a frequency domain description, however, because of the previously stated relation between time and frequency domain models, all of the following derivations also hold for time-domain models.

#### 2.6.1 Building Blocks Models

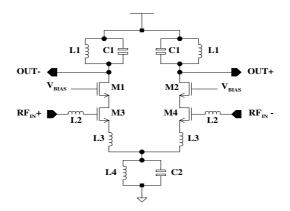

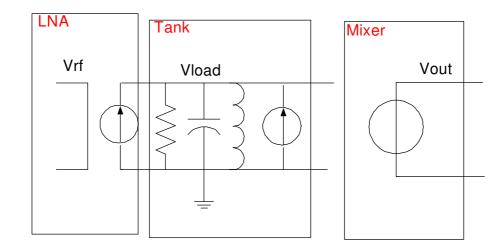

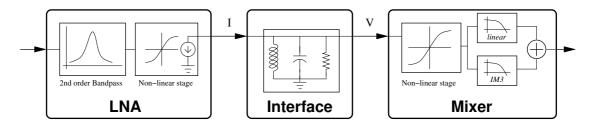

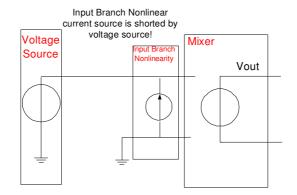

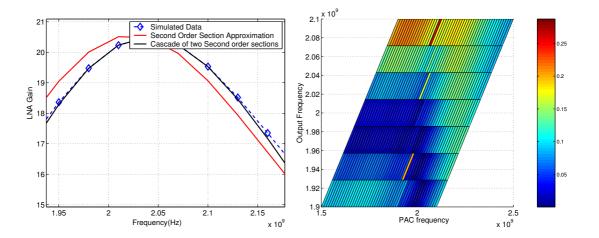

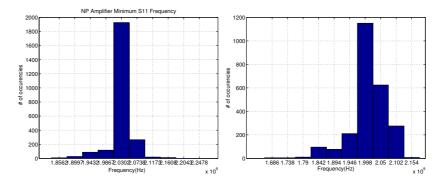

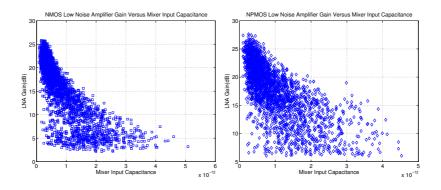

For the remaining part of the section, we'll suppose the front end to be composed of the cascade connection of a LNA and a mixer. This structure is depicted in 2.6 The mixer local oscillator port is supposed to be driven by a local oscillator, characterized by the corner frequency of the Lorentzian portion of its phase noise spectrum  $f_c$ . As local oscillator was not modeled, this parameter is supposed to exhibit a third order nonlinear behavior, with gain and nonlinear coefficients showing for the moment unspecified dependence on frequency. Finally, notice that 2.6 underlines the AC coupling between the LNA and each of the I and Q mixers: as a consequence, LNA contributions to overall second order intermodulation distortion are neglected and LNA may be characterized by an odd function. Consider now the expression reported in [2], expressing compliance of a front end to UMTS standard system requirements.

$$\frac{S}{N+I} \ge 7 - SPG[dB] \tag{2.37}$$

#### CHAPTER 2. SYSTEM LEVEL MODELING

Where SPG is the despreading gain, for the case of 12.2kBs UMTS transmission equal to 25 and the value of 7 is the SNR value required by a PSK modulation to achieve a BER of  $10^{-3}$  First of all, notice that 2.37 is a conservative constraint as in fact, UMTS data frame includes a cyclic redundancy check code that contributes to SNR with an asymptotic decoding gain [23] of approximately 2.6dB which is not included in the derivation of 2.37. This equation has to hold both for the case of sensitivity test and for the third order intercept test. In both cases, we assume two sinusoidal inputs are applied to the system, characterized by amplitudes  $A_1$  and  $A_2$  and frequencies  $f_1$  and  $f_2$ . Then equation 2.37 splits into

$$\frac{P_2^2}{IIP_2} + 4KTR_sBW * F + P_{Leakage}^{Tx}PN_{135Mhz} \le -99dBm$$

$$(2.38)$$

$$\frac{P_2^2 P_1}{IIP_3^2} (1 + PN_{67.5}) + 4KTR_s BW * F + P_1 PN_{135Mhz} + P_2 PN_{67.5Mhz} \le -96dBm$$

(2.39)

These equations may be seen as a generalization of the ones reported in [2], and are useful in a system design phase. Here, they will be used to derive accuracy requirements fro the chosen behavioral models, using sensitivity analysis. In order to simplify this task, we'll express these equations in terms of building blocks behavioral model parameters, rather than in terms of system performance indexes. We get:

$$\frac{P_2^2 k_2^2 G_{LNA}^2}{G_{MIX}^2} + 4KT R_s BW * F + P_{Leakage}^{Tx} G_{Mix}^2 P N_{135Mhz} \le -99dBm \qquad (2.40)$$

$$\frac{P_2^2 P_1 (k_3^{LNA} G_{Mix} + G_{LNA}^3 k_3^{Mix}))^2}{G_{LNA}^2 G_{Mix}^2} + 4KT R_s BW * F + P_{Leakage}^{Tx} P N_{135Mhz} \le -96dBm \qquad (2.41)$$

$$F = F_{LNA} + \frac{\left(\frac{IRN_{Mix}}{4*KT*R_sBW} - 1\right)}{G_{LNA}^2} \qquad (2.42)$$

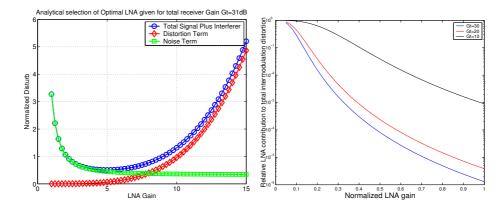

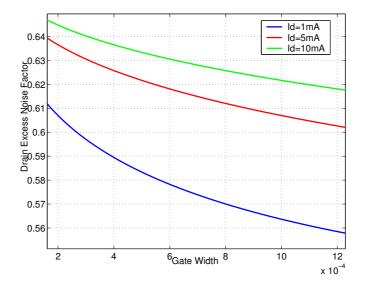

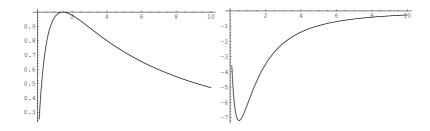

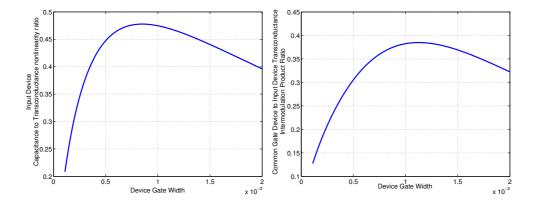

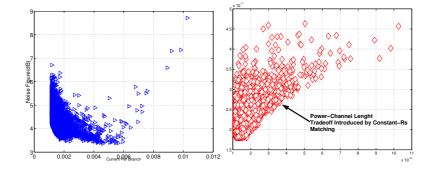

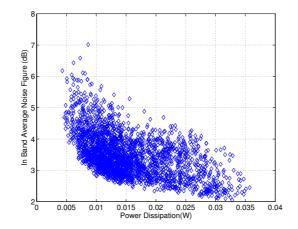

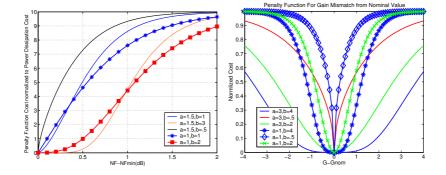

These equations can be used to get some understanding of the LNA-Mixer cascade. Note that second order nonlinearity is introduced by mixer alone, while third order nonlinearity has contribution from both low noise amplifier and mixer. The relative magnitude of these contributions depends on the gain and nonlinear coefficients of the individual blocks. Neglecting the interdependence of  $IM_3^{LNA}$  and  $IM_3^{MIX}$  on gain, it is interesting to look at the curve in figure 2.7, representing the relative contribution of LNA nonlinearity overall third order intermodulation distortion. We see that, while this contribution is dominant at low values of LNA gain, it vanishes as gain is increased. For a real design, and assuming  $G_{LNA} + G_{Mix}$  constant, LNA third order nonlinearity will increase as Gain is increased, while mixer nonlinear coefficient  $k_3$  decreases (for a given power dissipation). As a result, a more realistic curve would probably show a floor for the relative LNA contribution to distortion for high gain values. Similarly, assuming a fixed overall gain  $G_T(e.g. 31[dB])$  as cited in [2]), relative contribution of LNA to noise factor of the cascade increases with increasing LNA gain, decreasing as a consequence mixer noise importance, while increasing second order distortion. As for an inductively degenerated topology LNA gain is largely determined by the tuned load, while Noise Figure is dominated by input stage parameters, it makes sense to study the way distortion and noise interact in determining the interference floor for the second order intermodulation test. If  $k_2^{Mix}$ ,  $NF_{LNA}$ ,  $IRN_{Mix}$  and  $G_T$  are assumed constant, we it is found

$$N + I \approx \frac{P_2^2 k_2^2 G_{LNA}^4}{G_T^2} + 4KT R_s BW(F_{LNA} + \frac{F_{MIX} - 1}{G_{LNA}^2})$$

Where the term due to reciprocal mixing was neglected, being independent of LNA gain. Plots of this quantity are reported in figure 2.7. Specified all other parameters, an optimum Low Noise Amplifier exists, that minimizes the value of N + I. Using elementary calculus, we see that this occurs at

$$G_{LNA}^{Opt} = \left(\frac{2KTR_s \cdot BW \cdot (F_{Mix} - 1)G_T^2}{P_2k_2^2}\right)^{\frac{1}{6}} \approx \left(\frac{2IRN_{Mixer} \cdot BW \cdot G_T^2}{P_2^2k_2^2}\right)^{\frac{1}{6}}$$

(2.43)

Figure 2.7: Present system design methodology examples: optimal gain selection(left) and third order intermodulation distortion partition computation(Computation performed for design in [2])

, where  $F_{Mix} \gg 1$  was considered. For example, design reported in [2] reports 31dB gain, as well as  $k_2 = 20 \cdot 10^{-3}$ ,  $F_{Mix} = 24.465$ . This leads to  $G_{LNA}^{OPT} = 16.35dB$ .

Although useful from a system design perspective, these observations cannot be accurate, as they neglect actual relations amongst circuit performances. For example, in the latter analysis we did not consider connections between mixer second order distortion, here summarized by parameter  $k_2$ , and mixer conversion Gain  $G_{mix}$ , or between any of these quantities and the input referred noise. These relations may hardly be expressed analytically for a relatively complex system as a downconverter; nonetheless an experienced designer may use its knowledge of circuits to interpret results from these oversimplified analysis in a critical fashion. For example, it easy to notice that downconverter linearity is expected to improve while gain decreases, while at the same time IRN will probably increase. These considerations lead to deriving a Low Noise Amplifier Gain specification slightly higher than the value predicted using 2.43(For the design in  $[2], G_{LNA} = 18 dB$ . However, intuition does not always give optimal results, especially when designers are not skilled as skilled as authors of [2]. When put in a design automation perspective equations 2.38, 2.39 may be used to derive performance constraints on the proposed behavioral model accuracy. We perform this task through sensitivity analysis. This step is crucial in our modeling efforts, allowing model accuracy on linear performance to be traded for accuracy on linear performances, which are much easier to predict, therefore reducing the modeling effort. Labeled  $P_2 = \frac{P_2^2 k_2^2 G_{LNA}^2}{G_{MIX}^2}$  the nonlinear contribution to second order distortion test noise floor, and  $P_3 = \frac{P_2^2 P_1 (k_3^{LNA} G_{MiX} + G_{LNA}^2 k_3^{Mix}))^2}{G_{LNA}^2 G_{MiX}^2}$  the nonlinearity contribution to noise floor in the third order intermodulation test; applying sensitivity analysis to equations(2.40-2.42), we obtain

$$\frac{\Delta N}{N} \approx 2 \frac{\Delta G_{LNA}}{G_{LNA}} \frac{F_{Mix}}{F_{Receiv}} \qquad (2.44)$$

$$\frac{\Delta P_2}{P_2} = -2\frac{G_{Mix}}{G_{Mix}} + 2\frac{\Delta G_{LNA}}{G_{LNA}} + 2\frac{\Delta k_2^{MIX}}{k_2^{MIX}} \qquad (2.45)$$

$$\frac{\Delta P_3}{P_3} \approx \frac{\Delta G_{LNA}}{G_{LNA}} \frac{-2G_{MIX}k_3^{LNA} + 4G_{LNA}^3k_3^{MIX}}{G_{MIX}k_3^{LNA} + G_{LNA}^3k_3^{MIX}} + \frac{\Delta G_{MIX}}{G_{MIX}} \frac{-2G_{LNA}^3k_3^{MIX}}{G_{MIX}k_3^{LNA} + G_{LNA}^3k_3^{MIX}} + \frac{\Delta G_{MIX}}{G_{MIX}k_3^{LNA} + G_{LNA}^3k_3^{MIX}} + \frac{\Delta G_{MIX}}{G_{MIX}k_3^{MIX}} \frac{G_{LNA}^3k_3^{MIX}}{G_{MIX}k_3^{MIX} + G_{LNA}^3k_3^{MIX}} + \frac{\Delta K_3^{MIX}}{K_3^{MIX}} \frac{G_{LNA}^3k_3^{MIX}}{G_{MIX}k_3^{MIX} + G_{LNA}^3k_3^{MIX}}$$

(2.46)

Substituting back into 2.38,2.39:

$$\frac{\Delta D_2}{D_2} = 2\left(-\frac{G_{Mix}}{G_{Mix}} + \frac{\Delta k_2^{MIX}}{k_2^{MIX}}\right)\left(1 - \frac{N}{D}\right) + 2\frac{\Delta G_{LNA}}{G_{LNA}}\left(\left(1 - \frac{N}{D}\right) - \frac{F_{Mix}}{F_{Receiv}}\frac{N}{D}\right) \le \epsilon$$

(2.47)

$$\frac{\Delta D_3}{D_3} = \frac{\Delta G_{LNA}}{G_{LNA}} \left(2\frac{F_{Mix}}{F_{Receiv}}\frac{N}{D} + a_1\right) + \frac{\Delta k_3^{LNA}}{k_3^{LNA}}a_2 + \frac{\Delta k_3^{MIX}}{k_3^{MIX}}a_3 + a_4\frac{\Delta G_{MIX}}{G_{MIX}} \le \epsilon$$

(2.48)

$$a_1 = \frac{-2G_{MIX}k_3^{LNA} + 4G_{LNA}^3k_3^{MIX}}{G_{MIX}k_3^{LNA} + G_{LNA}^3k_3^{MIX}}(1 - \frac{N}{D})$$

(2.49)

$$a_2 = \frac{2G_{MIX}k_3^{LNA}}{G_{MIX}k_3^{LNA} + G_{LNA}^3k_3^{MIX}}(1 - \frac{N}{D})$$

(2.50)

$$a_3 = \frac{G_{LNA}^3 k_3^{MIX}}{G_{MIX} k_3^{MIX} + G_{LNA}^3 k_3^{MIX}} (1 - \frac{N}{D})$$

(2.51)

$$a_4 = \frac{-2G_{LNA}^3 k_3^{MIX}}{G_{MIX} k_3^{LNA} + G_{LNA}^3 k_3^{MIX}} (1 - \frac{N}{D})$$

(2.52)

Where  $\epsilon$  is the tolerable error and  $D_2$  and  $D_3$  respectively represent the total disturb component in the second and in the third order intermodulation performance tests. If now we assume error on model parameters to be independently distributed random variables, we may add variances. Resulting equations respectively represent an ellipsoid in  $R^3$  and an ellipsoid in  $R^4$ . These ellipsoids describe the way accuracy on different system parameters may be traded. We will exploit this derivation to reduce to the minimum the accuracy specifications on non-linear responses, which are harder to measure and model. Considering for example performances extracted from design described in [2], we find  $k_3^{LNA} = .75$ ,  $k_3^{MIX} = 6.7$ ,  $a_1 =$  $3, a_2 = .0011, a_3 = 1.5, a_4 = -1.5$ ,  $F_{Mix}/F_{tot} = .47$ ,  $N/D_2 = .5$ ,  $N/D_3 = .25$ . Notice that errors on the mixer second order nonlinearity parameter  $k_2$  basically depend on simulation convergence issues, causing an inherent trade-off between accuracy and simulation time. Details about how this trade-off has been addressed in this work are exposed in [1]. However, accuracy within 4% is obtained in most cases. For LNA linear gain, accuracy obtainable with the proposed model is order of 10%. Same holds for the case of mixer. Now we can invert previous relations for  $\epsilon = .5$  and find:

$$\frac{\Delta D_2}{D_2} \approx .12 \tag{2.53}$$

$$(\frac{\Delta k_3^{MIX}}{k_3^{MIX}})^2 2.25 \le .04 \tag{2.54}$$

Where  $k_3^{LNA}$  was neglected due to extremely low sensitivity to this parameter. For a relative error on  $k_3^{LNA}$  of  $\pm 50\%$ , required relative error on mixer  $k_3$  is about 15%. As shown later, such a low relative error value is not easily met when on a widespread number of designs as those generated from an ACG.

## Chapter 3

# **Device Modeling**

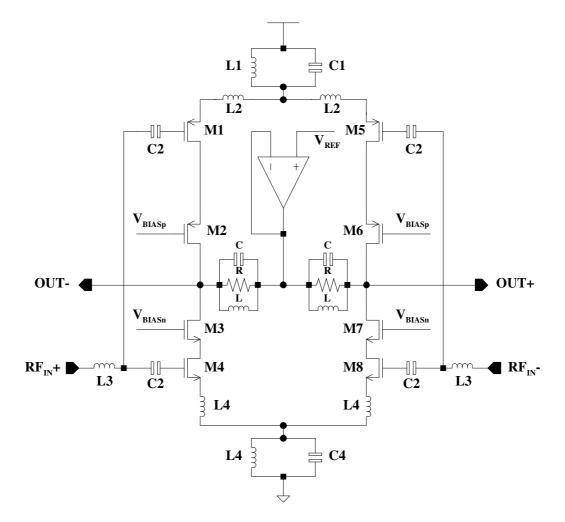

We introduced in a previous chapter how one of the main problems of platform based design is the dependence of the explored space on the chosen set of constraints imposed through the Analog Constraint Graph, and through these on the chosen device model. A model as accurate as possible should be chosen to allow re usability of the ACG, i.e. portability of the ACG itself on the maximum number of technologies or applications with minimal changes. Moreover, accurate device models are needed for the identification of effects that dominate the non-ideal behavior of a given circuit; and for getting insight on the modeling strategy itself.

As this works deals with low-noise amplifier modeling, noise performance and input matching reliability are the major concerns. Extrinsic and intrinsic capacitive effects in the active devices, integrated inductors and device noise sources have then been investigated.

## 3.1 Integrated Inductor Model

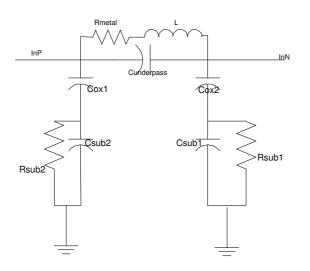

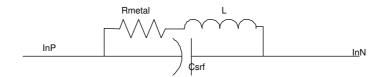

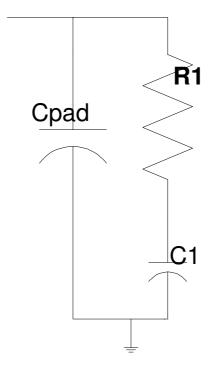

The crucial role played by integrated inductors in determining the performances of RF systems is wellknown.As a result, numerous models have been developed through the years, together with methods to improve performance metrics of integrated inductors(quality factor Q, self resonant frequency SRF), while maintaining compatibility with CMOS technology. All of the prosed models have the topology reported in figure 3.1.All of the prosed models have the topology reported in figure 3.1. Despite its accuracy, exact expressions for the parameters of this model are not readily available, so that design-kit models are usually built extracting these value from accurate 3D electromagnetic simulators such as HFSS. As models of this kind obviously are not suited for automatic design, in this work we used a simplified model such as that depicted in 3.2. This model allows exact predictions of Q and Self Resonant Frequency. Parameters L, R and C may be expressed in terms of inductance value L,operating frequency  $\omega_0$ ,quality factor Q and self resonant frequency  $\omega_{SRF}$  as

$$R_{series} = \frac{\omega_0 L}{Q} \tag{3.1}$$

$$C = \frac{1}{L(\omega_{srf}^2 + \frac{\omega_0^2}{Q^2})}$$

(3.2)

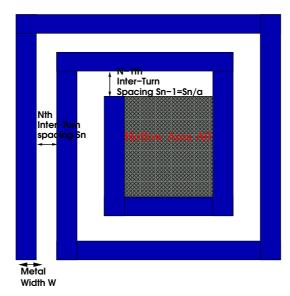

Another parameter of great importance for integrated inductors is die area occupation. An integrated inductor usually has an intrinsic area on the order of  $100\mu \times 100\mu$ , which must be added to an almost equally large area reserved by design kit spacing rules. An empirical formula to estimate inductors area

Figure 3.1: Complete equivalent circuit of integrated inductors

Figure 3.2: Simplified equivalent circuit of integrated inductors

Figure 3.3: Physical meaning of the parameters in equation 3.5

given their inductance value([33]) is:

$$A_{tot} = \left(\frac{1.3 \cdot 10^{-7} A_m^{\frac{3}{2}}}{L W_m^{1.75} W_{spacing}^{.25}}\right)^6 \tag{3.3}$$

Where  $A_m$  is the metal area,  $W_m$  the metal width and  $W_{spacing}$  the distance between nearby tracks. In the initial phase of the work, this formula was not known and another expression was developed for square inductors by expressing the area as a function of the number of turns, spacing and hollow area. First notice that length of  $i_{th}$  turn is related to the length of the  $(i - 1)_{th}$  turn (see figure 3.3 by  $L_i = L_{i-1} + 5(W_m + aS_{i-1}) = L_0 + 5 \cdot i \cdot W_m + \frac{a^{1+i}-1}{a-1}S_0$ , where  $W_m$  is the metal width of each turn,  $L_0 = 3\sqrt{A_0}$  the first turn perimeter ( $A_0$  is the central hollow area [45]), and spacings between successive turns are assumed described by a geometrical sequence of reason a, i.e.  $S_{i+1} = a \cdot S_i$ . Then  $A = L_N^2$  and

$$A = (3\sqrt{A_0} + 5(N-1)W_m + S_0 \frac{a^N - 1}{a-1})^2 \qquad ifa > 1$$

(3.4)

$$A = (3\sqrt{A_0} + 5(N-1)(W_m + S_0))^2 \qquad ifa = 1$$

(3.5)

N can be found by solving for the inductance value, assumed to grow linearly with the overall metal length ([6]) and thus expressed as

$$L = \alpha(\sum_{i=0}^{N} L_i) = \alpha(N(L_0) + \frac{N(N-1)}{2}W_m + \frac{a(a^N - 1) - N}{a - 1}S_0 \qquad ifa > 1$$

(3.6)

$$L = N \cdot L_0 + \frac{N(N-1)}{2}(W_m + S_0) \qquad ifa = 1$$

(3.7)

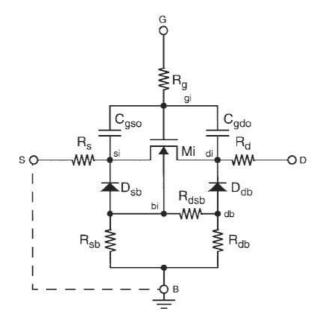

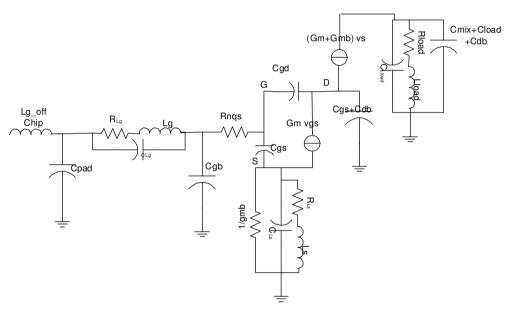

Figure 3.4: MOSFET equivalent circuit, including extrinsic components