# A Compact Modular Multilevel DC-DC Converter for High Step-ratio MV and HV Use

Xin Xiang, Student Member IEEE, Xiaotian Zhang, Member IEEE, Thomas Luth, Michael M. C. Merlin, Member IEEE, and Timothy C. Green, Senior Member, IEEE

Abstract-In multi-terminal dc networks or future dc grids, there is an important role for high step-ratio dc-dc conversion to interface a high voltage network to lower voltage infeeds or offtakes. The efficiency and controllability of dc-dc conversion will be expected to be similar to modular multi-level ac-dc converters. This paper presents a modular multilevel dc-dc converter with a high step-ratio for medium voltage and high voltage applications. Its topology on high-voltage side is derived from the half-bridge single-phase inverter with stacks of sub-modules replacing each of the switch positions. A near-square-wave current operation is proposed which near-constant instantaneous power achieves for single-phase conversion, leading to reduced stack capacitor and filter volume and also increased the power device utilization. A controller for energy balancing and current tracking is designed. The soft-switching operation on the low-voltage side is demonstrated. The high step-ratio is accomplished by combination of inherent half-bridge ratio, sub-module stack modulation and transformer turns-ratio, which also offers flexibility to satisfy wide-range conversion requirement. The theoretical analysis of this converter is verified by simulation of a full-scale 40MW, 200 kV converter with 146 sub-modules and also through experimental testing of a down-scaled prototype at 4.5 kW, 1.5 kV with 18 sub-modules.

Index Terms-Modular multilevel converter, compact volume, high step-ratio, dc grids.

#### NOMENCLATURE

| $C_h$            | Control headroom                                |

|------------------|-------------------------------------------------|

| D                | Duty-cycle of the near-square-wave              |

| $E_S$            | Sum of the energy stored in all capacitors      |

| $E_{Ts}, E_{Bs}$ | Energy stored in the top stack and bottom stack |

| $f_o, f_s$       | Operation frequency, switching frequency        |

| $f_r$            | SM sorting and selection frequency              |

| $i_{Bac}$        | AC component of the bottom stack current        |

Manuscript received April 18, 2017; revised August 17, 2017 and December 15; accepted December, 28, 2017. This work was supported by the Reconfigurable Distribution Networks project under EPSRC Grant EP/K036327/1 and the Delta Foundation Grant DREG2016009. There are no datasets associated with this work to report.

X. Xiang, T. Luth, M. M. C. Merlin and T. C. Green are with the Electrical and Electronic Engineering Department, Imperial College London, London, SW7 2AZ, U.K. (e-mail: x.xiang14@imperial.ac.uk; thomas.luth06@imperial.ac.uk; michael.merlin@imperial.ac.uk; t.green@imperial.ac.uk ).

X. Zhang is with Department of Electrical Engineering, Xi'an Jiaotong University, Xi'an, 710049, China. (e-mail: xiaotian@xjtu.edu.cn).

| $i_{Bcp}$               | Current through the bottom dc-link capacitor $C_B$              |

|-------------------------|-----------------------------------------------------------------|

| i <sub>Bdc</sub>        | DC component of the bottom stack current                        |

| i <sub>Di</sub>         | Current through the rectifier diodes $D_i$ ( $i = 1, 2, 3, 4$ ) |

| i <sub>H</sub>          | Current on the high-voltage side                                |

| i <sub>L</sub>          | Current on the low-voltage side                                 |

| $i_{N1}$                | Current on the transformer primary side                         |

| $i_{N2}$                | Current on the transformer secondary side                       |

| $i_{Tac}$               | AC component of the top stack current                           |

| <i>i</i> <sub>Tcp</sub> | Current through the top dc-link capacitor $C_T$                 |

| $i_{Tdc}$               | DC component of the top stack current                           |

| $i_{Ts}, i_{Bs}$        | Current through the top stack and bottom stack                  |

| $n_{B-}$                | On-state SM number in the bottom stack                          |

| n <sub>SM</sub>         | SM total number                                                 |

| $n_T, n_B$              | SM number in the top stack and bottom stack                     |

| $n_{T-}$                | On-state SM number in the top stack                             |

| Р                       | Power rating                                                    |

| R                       | Overall step-ratio                                              |

| $r_S$ , $r_T$           | Stack modulation ratio, transformer turns-ratio                 |

| $T_o, T_s$              | Operation cycle, switching cycle                                |

| $V_{Bj}$                | Capacitor voltage of the <i>j</i> th SM in the bottom stack     |

| $v_{Bl}$                | Voltage across the bottom arm inductor $L_B$                    |

| $V_{CB}$                | Voltage across the bottom dc-link capacitor $C_B$               |

| $v_{CT}$                | Voltage across the top dc-link capacitor $C_T$                  |

| $V_{Di}$                | Voltage across the rectifier diodes $D_i$ ( $i = 1, 2, 3, 4$ )  |

| $\mathcal{V}_H$         | Voltage on the high-voltage side dc link                        |

| $v_L$                   | Voltage on the low-voltage side dc link                         |

| $v_{N1}$                | Voltage on the transformer primary side                         |

| $v_{N2}$                | Voltage on the transformer secondary side                       |

| VSM                     | Average value of the SM capacitor voltages                      |

| $v_{Tj}$                | Capacitor voltage of the <i>j</i> th SM in the top stack        |

| $v_{Tl}$                | Voltage across the top arm inductor $L_T$                       |

| $v_{Ts}$ , $v_{Bs}$     | Voltage across the top stack and bottom stack                   |

| $\delta_{dc}$           | Voltage tolerance of dc-link capacitor                          |

| $\delta_{SM}$           | Voltage tolerance of SM capacitor                               |

| *                       | Superscript for controller reference value                      |

| $\lfloor x \rfloor$     | Floor (the largest integer less than or equal to $x$ )          |

## I. INTRODUCTION

C TRANSMISISON is becoming the preferred option for Dlarge-scaled renewable energy integration [1]. The rapid development of High Voltage Direct Current (HVDC) technology in last decade is facilitating the evolution of dc transmission from point-to-point connections to multi-terminal networks and dc grids [2]. In a multi-terminal dc network, there is a role for the high power throughput but low voltage ratio

(HPLR) [3] dc-dc conversion for connecting two HVDC links of similar but not identical voltage [4], [5]. There is also a role for the low power throughput but high voltage ratio (LPHR) [3] dc-dc conversion for interfacing a high voltage network to lower voltage infeeds or offtakes, often termed as 'dc tap', which was first proposed in [6] and developed in [7]–[9] with different topologies and control schemes.

Although there is no full-scale practical project for dc tap up to date, it has attracted much interest in recent years for both academic research and industrial development to satisfy the demand and architecture for future dc grids [10]–[16]. It could collect power from small-scale offshore wind farms (OWF) near the cable routes by tapping into the HVDC link directly [10], [11], and the LPHR conversion can also tap out a small fraction of the link power to service demand in remote communities with inadequate ac supplies but which are crossed by the HVDC corridors [12]–[14]. A growing role for conversion between HVDC and Medium Voltage Direct Current (MVDC) grids is also anticipated [15], [16].

At low voltage (LV), high step-ratio dc-dc converters have been extensively investigated [17] but the use of a single device and high switching frequency make the application to high voltage difficult. The multi-module concept has been applied to classic LV dc-dc topologies, notably the dual-active-bridge (DAB), for medium voltage (MV) applications [18] using parallel or series arrangements to mitigate the voltage and current stress on each device. The modular DAB topology is central to solid state transformer [19] and has attracted interest for MVDC networks [20]. However, the large number of module transformers and their onerous insulation requirement raise difficulties in high voltage (HV) and high step-ratio applications. In addition, the lack of fault tolerance capability is another drawback for modular DAB converter [21]. The full-bridge three-level DAB or single-active-bridge (SAB) dc-dc converters was proposed and developed as a promising solution for dc collection [22], [23], facilitating the integration of wind turbines into a MVDC link, but the three-level operation would also face some serious challenges on practical design if applied directly in the high voltage conversion.

The difficulties and drawbacks in DAB or SAB can be avoided by using modular multi-level converter (MMC) [24], [25] in front-to-front configuration. The front-to-front MMC brings its advantages of modularity and controllability to interfacing two different HVDC links and can block propagation of fault current from one dc link to the other [26], [27]. However, it is not a low-cost option for LPHR applications since the power devices utilization is usually lower than other competing topologies [15], [18]. The concept of the auto dc transformer based on MMC technology was proposed in [28], [29]. High power-device utilization was attained leading to a reduced cost compared to the front-to-front design but the large filter required [28] and difficulty with dc fault management [29] would undermine this advantage. Incorporating the MMC principle with the classic dc-dc circuits in resonant mode has been reported for high-voltage and high step-ratio conversion [30]. However, the switches on its high-voltage side must withstand both high voltage and high current stress, which

restricts the application scope.

The MMC principle with full-bridge or half-bridge SMs has also been applied to the full-bridge single-phase DAB circuit for ac-ac [31] or dc-dc conversion [32] in MV and HV applications. Trapezoidal voltage or square-wave voltage modulation were used to decrease the converter volume and therefore the cost [33]. They share the advantages of the DAB converter from LV and MV applications and also inherit the good features of MMC for HV applications. The proposal in this paper is to evolve these topologies and modulation for LPHR conversion and develop a cost-effective dc tap design for multi-terminal dc networks or dc grids. On the high-voltage side, the circuit is changed to a half-bridge single-phase inverter with stack of half-bridge SMs replacing each of the switch positions. Considering the high step-ratio conversion, the low-voltage side use а diode/active bridge rectifier arrangement for unidirectional/bidirectional power flow, simplifying the configuration and also achieving soft-switching operation.

The overall volume of a conversion system and its associated weight is one of the most important factors in the estimation and evaluation for its overall cost [5], [32], [33], especially in the offshore cases where the platform cost is extremely expensive [34], [35]. Given that the practical volume of the valve halls is mainly governed by the isolation distances and maintenance separation between SM stacks of different phases [36], [37], the total space occupied by this two-stack half-bridge single-phase converter would be smaller for this dc tap LPHR application than the symmetrical front-to-front arrangement which needs 12 stacks (3-phase configuration) or 8 stacks (full-bridge configuration) to accomplish the dc-ac-dc conversion. Further, continuous instantaneous power flow is desirable to obviate large smoothing capacitance on the dc buses and reduce the SM capacitor volume and so near-square-wave current operation is proposed in this paper. It will be shown that this also benefits power device utilization. High step-ratio voltage conversion can be achieved by combination of inherent half-bridge ratio, stack modulation and transformer ratio, which also provides flexibility in design and operation to meet the wide-range voltage conversion. The basic concept of this topology was first proposed in conference proceedings [38]. This paper significantly develops the concept with detailed operation principles and control scheme in Section II and Section III respectively. The specific investigation on circuit performance is provided in Section IV, and the theoretical analysis is verified by full-scale example simulation in Section V and also through down-scaled prototype experiments in Section VI.

# II. TOPOLOGY DESCRIPTION AND OPERATING PRINCIPLES

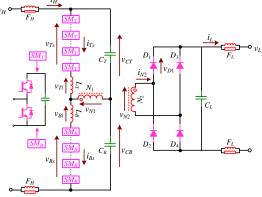

The schematic of the converter is illustrated in Fig. 1. The high-voltage side contains two stacks of half-bridge SMs,  $SM_T$  and  $SM_B$  in the top and bottom arm respectively, forming a single phase MMC configuration with arm inductors  $L_T$  and  $L_B$ . There are  $n_{SM}$  SMs in total, divided equally between top and bottom stacks. The primary winding of the transformer ( $r_T = N_1/N_2$ ) is connected between the phase midpoint and a neutral point created by two dc-link capacitors  $C_T$  and  $C_B$ . For illustration, a simple full-bridge diode rectifier (formed of series

connected diodes appropriate to the voltage rating) is chosen to connect the transformer secondary winding to a smoothing capacitor  $C_L$  on the low-voltage side. Controllable devices can be used in rectifier for bidirectional power flow.  $F_H$  and  $F_L$  are filters on the high-voltage and low-voltage sides, formed of parallel inductors and resistors to confine ac current components to circulate within the converter.

Fig. 1. LPHR modular multilevel dc-dc converter.

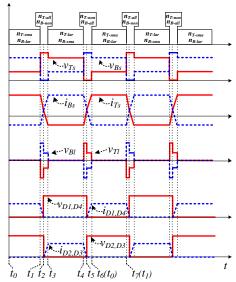

Fig. 2. Voltage and current waveforms in one operation cycle.

Fig. 2 shows that there are six stages in one operation cycle. The equivalent circuits for the first three stages over  $t_0$ - $t_3$  are given in Fig. 3. The other half of the cycle,  $t_3$ - $t_6$ , is symmetrical to  $t_0$ - $t_3$ . The arrows in Fig. 1 define the voltage and current reference directions for the waveforms of Fig. 2 (and the rest of the paper), and the arrows in Fig. 3 display the actual current flow in each stage.  $n_T$  and  $n_B$  are used to describe the number of SMs in the on-state (meaning that the upper switch is on and the lower is off) for the top stack and bottom stack respectively. It is worth noting that the total number of SMs inserted between positive terminal and negative terminal of the high-voltage dc link is not constant, and the sum of  $v_{Ts}$  and  $v_{Bs}$  varies in different operation stages. The operating principles for each stage will be analysed in detail in the following subsections.

## A. Stage 1: Positive Steady-State $(t_0-t_1)$

In this stage, a small number of the SMs in the top stack  $(n_{T-sma})$  and a large number of the SMs in the bottom stack

$(n_{B-lar})$  are in the on-state, generating steady voltage values of  $v_{Ts}(t_0)$  and  $v_{Bs}(t_0)$ . Summed together they match the high-side dc-link voltage  $v_H$  but the split is such that a positive voltage is applied to the transformer winding. The stack voltages are described in (1) and (2) under the assumptions that  $v_{CT}$  and  $v_{CB}$  are balanced and all SM capacitor voltages are equal to  $v_{SM}$ . The sum of  $v_{Ts}$  and  $v_{Bs}$  equals to  $v_H$ , shown in (3), and the voltages across the top arm inductor and bottom arm inductor are both 0. This stage is considered to be the positive steady-state. The stack currents through the arm inductors maintain at values of  $i_{Ts}(t_0)$  and  $i_{Bs}(t_0)$ , expressed in (4) and (5). Diodes  $D_1$  and  $D_4$  are in conduction whereas  $D_2$  and  $D_3$  are reverse-biased.

$$v_{Ts}(t) = v_{Ts}(t_0) = \frac{v_H}{2} - r_T v_L = n_{T-sma} \cdot v_{SM}$$

(1)

$$v_{Bs}(t) = v_{Bs}(t_0) = \frac{v_H}{2} + r_T v_L = n_{B-lar} \cdot v_{SM}$$

(2)

$$v_{Ts}(t) + v_{Bs}(t) = (n_{T-sma} + n_{B-lar}) \cdot v_{SM} = v_H$$

(3)

$$i_{TS}(t) = i_{TS}(t_0) = i_H + \frac{c_L}{2r_T}$$

(4)

$$i_{BS}(t) = i_{BS}(t_0) = i_H - \frac{i_L}{2r_T}$$

(5)

## B. Stage 2: Force Current Reversal $(t_1-t_2)$

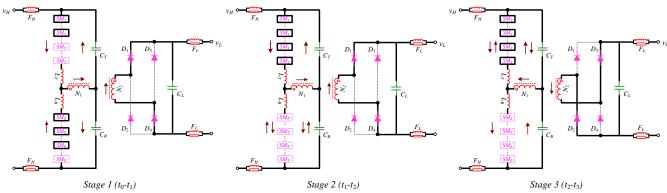

A rapid current reversal is required for the near-square-wave operation and to achieve this all of the SMs in the top stack are turned on  $(n_{T-all})$  at  $t_1$  and all SMs in the bottom are turned off  $(n_{B-non})$  to impose the largest possible negative voltage across the arm inductor. Fig. 3 shows the commutation of the stack currents during this short stage. The stack voltage and current relationship over this period are given in (6)–(9). It needs to note that the controller can preset a slope limiter for the transient currents in (8) and (9), especially for the low current operation. The inserted SM number in transient stages and transient waveform are adjustable according to the controller capability and practical requirements.

$$v_{Ts}(t) = n_{T-all} \cdot v_{SM} = n_T \cdot v_{SM} = \frac{n_{SM}}{2} \cdot v_{SM} \tag{6}$$

$$v_{BS}(t) = n_{B-non} \cdot v_{SM} = 0 \tag{7}$$

$$i_{TS}(t) = i_{TS}(t_1) + \frac{1}{L_T} \left[ \frac{\nu_H}{2} - \nu_{TS}(t) - r_T \nu_L \right] (t - t_1)$$

(8)

$$i_{BS}(t) = i_{BS}(t_1) + \frac{1}{L_B} \left[ \frac{v_H}{2} - v_{BS}(t) + r_T v_L \right] (t - t_1)$$

(9)

The control headroom  $C_h$  shown in (10), is the additional negative voltage available over and above that which will be needed to maintain the negative steady-state current. A larger value allows a faster transition of current and a waveform closer to square. Some relevant research on additional SMs insertion was also discussed in [39], [40]. The extra full-bridge SMs was designed to assist the turn-off operation of thyristors [39]. The redundant SMs in [40] was used to compensate the failed non-redundant SMs in other arms and improve reliability. The additional half-bridge SMs here are utilized to generate an adjustable control headroom for faster current transition, which has different roles and purposes in the operation with [39], [40].

$$C_{h} = \frac{n_{T-all,B-all} - n_{T-lar,B-lar}}{n_{T-all,B-all}} = \frac{n_{SM} - (n_{T-lar} + n_{B-lar})}{n_{SM}}$$

(10)

The sum of  $v_{T_s}$  and  $v_{B_s}$  in this stage can be expressed as (11). Compared with (3), it can be found this value would be smaller than  $v_H$  in the normal operation unless the control headroom  $C_h$

Fig. 3. Equivalent circuits and operation analysis.

is very large in the design.

$$v_{Ts}(t) + v_{Bs}(t) = (n_{T-lar} + \frac{C_h}{1 - C_h} n_{T-lar}) \cdot v_{SM}$$

(11)

This stage ends when  $i_{D1}$  and  $i_{D4}$  reduce to zero at  $t_2$ . Note that  $v_{D1}$  and  $v_{D4}$  enter reverse-bias after  $i_{D1}$  and  $i_{D4}$  drop to zero and thus the soft-switching turn-off operation is achieved.

# C. Stage 3: Establish Negative Steady-State $(t_2-t_3)$

Having commuted the diodes, it is now necessary to establish the steady negative current. Initially, the SMs are kept the same states until  $t_3$ , at which point the stack currents reach the new steady values of  $i_{Ts}(t_3)$  and  $i_{Bs}(t_3)$  and the transient period is finished. As Fig. 3 illustrates, after the transformer current changed direction at  $t_2$ , the slopes of  $i_{Ts}$  and  $i_{Bs}$  became shallower for  $t_2$ – $t_3$  because  $D_2$  and  $D_3$  are in conduction and the low-side voltage appears in the opposite sense.

# D. Stage 4: Negative Steady-State $(t_3-t_4)$

At  $t_3$ , with the new currents established, the controller turns off some of SMs in the top stack (the number turned on reduces from  $n_{T-all}$  to  $n_{T-lar}$ ) and turns on a small number in the bottom stack ( $n_{B-sma}$ ). This is a symmetrical case to Stage 1, and the description of stack voltage and current are similar to (1)–(5) but with the top and bottom stack value replacing each other.

# E. Stage 5 $(t_4-t_5)$ and Stage 6 $(t_5-t_6)$

All of the SMs in the top stack are turned off  $(Tn_{non})$  and all SMs in the bottom are turned on  $(Bn_{all})$  at  $t_4$  to rapidly reduce the negative current to zero. The diodes commutate at  $t_5$  (the end of Stage 5) and the current continues its transition toward the positive steady value. The operational principles of Stages 5 and 6 are the same as Stages 2 and 3. The control headroom is used again to accelerate the current transition. When stack currents reach their steady-state values,  $i_{Ts}(t_6)$  and  $i_{Bs}(t_6)$ , the converter returns to Stage 1 and the next cycle of operation begins.

#### III. ENERGY MANAGEMENT AND CONTROL SCHEME

The energy stored in each stack is expressed as (12) under the assumption that all the SM capacitances are equal to  $C_{SM}$ , and the reference value for the total energy is given in (13).

$$E_{Ts,Bs} = \sum_{j=1}^{\frac{n_{SM}}{2}} \frac{1}{2} C_{SM} v_{Tj,Bj}^2$$

(12)

$$E_{S}^{*} = \frac{1}{2} C_{SM} v_{SM}^{*2} \cdot n_{SM}$$

(13)

The objective of energy management is twofold: maintain the sum of  $E_{Ts}$  and  $E_{Bs}$  equal  $E_{S}^{*}$ , shown in (14), and keep the difference between them to zero, given in (15).

$$E_{Ts} + E_{Bs} = E^*$$

(14)

$E_{Ts} - E_{Bs} = 0$  (15)

The analysis in Section II-A and II-D of the two steady-state stages revealed that the stack voltages comprise a dc offset  $v_H/2$  and an ac component  $\pm r_T v_L$ . The stack currents also comprise a dc component  $i_H$  and an ac current  $\pm i_L/2r_T$ . The energy exchange  $\Delta E$  in one operation cycle can be approximated as (16) by neglecting the very short transient period.

$$\Delta E_{Ts,Bs} = \left(\frac{v_H}{2} \mp r_T v_L\right) \left(i_H \pm \frac{i_L}{2r_T}\right) \cdot \frac{T_o}{2} + \left(\frac{v_H}{2} \pm r_T v_L\right) \left(i_H \mp \frac{i_L}{2r_T}\right) \cdot \frac{T_o}{2} = \frac{(v_H i_H - v_L i_L) \cdot T_o}{2} = 0$$

(16)

It can be seen that energy deviations from the ac and dc terms are zero over an operation cycle without extra balancing control. The stack energy of this converter is naturally balanced if the original state satisfies the conditions in (14) and (15). A transient energy drift or an initially unbalanced state can be corrected by adding an extra dc component  $\Delta i_{dc}$  and an ac component  $\pm \Delta i_{ac}/2r_T$  into the stack currents and thereby the stack energy exchanges are adjusted according to (17).

$$\Delta E'_{TS,BS} = \left(\frac{v_H}{2} \mp r_T v_L\right) \left[ (i_H + \Delta i_{dc}) \pm \frac{i_L \pm \Delta i_{ac}}{2r_T} \right] \cdot \frac{T_o}{2} \\ + \left(\frac{v_H}{2} \pm r_T v_L\right) \left[ (i_H + \Delta i_{dc}) \mp \frac{i_L \pm \Delta i_{ac}}{2r_T} \right] \cdot \frac{T_o}{2} \\ = \frac{\left[ v_H (i_H + \Delta i_{dc}) - \left[ v_L (i_L \pm \Delta i_{ac}) \right] \cdot T_o}{2}$$

(17)

Then, the sum and difference of the energy exchanges for the two stacks are given in (18) and (19), which reveal the adjustments for sum and difference of the stack energies are decoupled in this converter:  $\Delta i_{dc}$  alone sets the change in the sum and  $\Delta i_{ac}$  alone sets the change in the difference.

$$\Delta E'_{TS} + \Delta E'_{BS} = v_H \Delta i_{dc} T_o \tag{18}$$

$$\Delta E'_{TS} - \Delta E'_{BS} = -\nu_L \Delta i_{ac} T_o \tag{19}$$

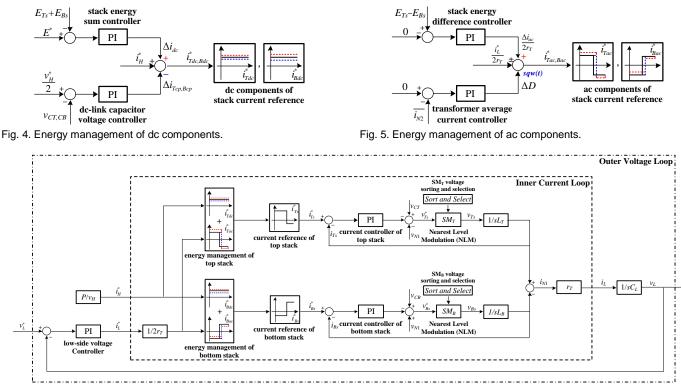

The use of proportional-integral (PI) controllers for the energy management of the sum and difference of stack energies are illustrated in Fig. 4 and Fig. 5. Fig. 4 shows three terms combining to the dc components of stack current references,  $i_{Tdc}^*$  and  $i_{Bdc}^*$ , namely: an adjustment for stack energy sum  $\Delta i_{dc}$ ; the high-voltage side current reference  $i_H^*$  and an adjustment for the dc-link capacitor voltage balance  $\Delta i_{Tcp,Bcp}$ . Fig. 5 shows three terms combining to form the ac components of stack current references,  $i_{Tac}^*$  and  $i_{Bac}^*$ , namely: an adjustment for the stack current references,  $i_{Tac}^*$  and  $i_{Bac}^*$ , namely: an adjustment for the stack current references,  $i_{Tac}^*$  and  $i_{Bac}^*$ , namely: an adjustment for the stack

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIE.2018.2793249, IEEE Transactions on Industrial Electronics

#### IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS

Fig. 6. Control scheme.

energy difference  $\Delta i_{ac}/2r_T$ ; the low-voltage side current reference  $i_L^*/2r_T$  and a duty-cycle adjustment  $\Delta D$  for transformer average current neutralization. The complete stack current references for top and bottom,  $i_{Ts}^*$  and  $i_{Bs}^*$ , including all the balancing terms, are summarized in (20), in which the square-wave function sqw(t) for each operation cycle,  $T_o$ , is defined as (21).

$$i_{Ts,Bs}^* = i_{Tdc,Bdc}^* + i_{Tac,Bac}^*$$

$$= i_H^* + \Delta i_{dc} - \Delta i_{Tcp,Bcp} \pm \frac{i_L^* \pm \Delta i_{ac}}{2r_T} \cdot sqw(t)$$

(20)

$$sqw(t) = \begin{cases} 1, \ 0 < t \le \frac{T_o}{2} + T_o \cdot \Delta D \\ -1, \ \frac{T_o}{2} + T_o \cdot \Delta D < t \le T_o \end{cases}$$

(21)

The entire control scheme is shown in Fig. 6. It comprises an outer loop to regulate  $v_L$  which sets the principal reference for the inner current loop to which the balancing terms are added according to the energy management algorithms from Fig. 4 and Fig. 5. The detailed expression for stack current references is shown in (20). The inner loop can be used for the current source mode (CSM) operation, in which the converter is controlled to interface dc grids at different voltage levels. By adding the outer loop for voltage control, this converter is operated in voltage source mode (VSM) to collect the power from OWF or feed the power to some remote area loads. The modulation scheme in Fig. 6 is a classic Nearest Level Modulation (NLM) [24], [25] to balance all SM capacitor voltages close to  $v_{SM}^*$ . The stack sorts the SMs in the order of SM capacitor voltage, and the first  $N_{NLM}$ SMs with lowest voltages are inserted into the stack when the stack current direction is charging SM capacitors while the highest  $N_{NLM}$  SMs are switched into the stack when the current direction is discharging  $(N_{NLM} = |v_{T_S,B_S}^* / v_{SM}^*|)$ .

## IV. CIRCUIT PERFORMANCE ANALYSIS

In this section, performance of this converter is analyzed and the operational advantages and limitations are discussed.

#### A. SM Capacitor Sizing

SM capacitor size typically accounts for more than half the volume of each SM in the classic MMC [41], [42] and SM capacitor size is therefore an important design consideration. The size is dictated by the maximum stack energy deviation and the capacitor voltage tolerance. The energy deviation for this near-square-wave converter is given in (22),

$$dE_{Ts,Bs} = \int_0^t v_{Ts,Bs}(t) \cdot i_{Ts,Bs}(t) dt$$

=

$$\int_0^t \left[ \frac{v_H}{2} \mp \frac{v_H}{2r_s} \cdot sqw(t) \right] [i_H \pm r_s i_H \cdot sqw(t)] dt \qquad (22)$$

where  $r_S = v_H/2v_{N1}$ , known as the stack modulation ratio, sets the voltage conversion achieved within the stack itself.

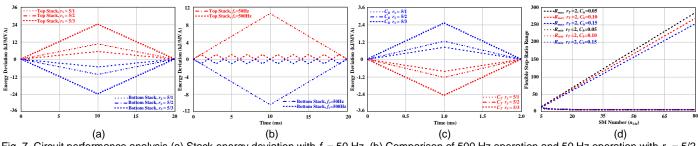

The energy deviations for near-square-wave operation at 50 Hz with various values of  $r_s$ , are shown in Fig. 7(a) and are seen to be isosceles triangles with their peaks occurring mid cycle. Smaller  $r_s$  value gives smaller energy deviation but at the penalty of needing a larger transformer ratio to achieve the same overall voltage step-ratio which, according to (2), requires more SMs in each stack. Because the ac stage is entirely internal to the converter, the operation frequency can be increased to 250–500 Hz [5] for a reduction in volume and weight of the SM capacitors. As Fig. 7(b) shows, the energy deviations for 500 Hz operation is, as expected, ten times smaller for 50 Hz. The maximum value is about 1 kJ/MVA with stack ratio  $r_s=5/2$ , and the deviation can be further reduced to nearly 3% of that in the classic MMC when operated with the same modulation ratio

Fig. 7. Circuit performance analysis (a) Stack energy deviation with  $f_o = 50$  Hz. (b) Comparison of 500 Hz operation and 50 Hz operation with  $r_s = 5/2$ . (c) Energy deviation for high-voltage link dc capacitors with  $f_o = 500$  Hz. (d) Flexible step-ratio range.

[42]. This is also a smaller deviation than other modulation methods for MMC dc-dc converters operating in the same frequency range [4], [15], [32]. This 500 Hz medium frequency operation would also benefit other passive components' sizing in the converter, such as the internal transformer and arm inductors. Their volume can be decreased to less than 1/3 of that for 50 Hz standard frequency operation [43], [44].

The operation frequency could be pushed higher [45], [46] for some applications but switching loss and transformer limitations need to be considered.

#### B. DC-link Capacitor Sizing

The energy deviations for  $C_T$  and  $C_B$  on the high-voltage side, plotted in Fig. 7(c), are similar to those of the stacks but with the deviations in the opposite sense. Near-square-wave operation is also advantageous in achieving a small energy deviation and small capacitor stack for  $C_T$  and  $C_B$ . On the low-voltage side, the instantaneous power flow is near-constant, and the required capacitance value and physical volume of  $C_L$  can be small because it needs only absorb the ripple arising from the imperfect square-wave current transitions.

#### C. Power Device Utilization

ι

The extent to which the power devices in a modular converter utilize their current and voltage ratings is an important factor in assessing the performance of that converter. The near-square-wave current operation utilizes the current rating of SMs well compared to the sinusoidal case and uses nearly all of the SMs throughout a half-cycle. The voltage and current expressions of the top stack during the positive half-cycle of sinusoidal operation are shown in (23) and (24), under the assumption that the power factor is 1 and for the same power rating and same voltage ratio conversion as the analysis in (1) and (4). The stack current maximum value from (24) and (4) are compared in (25).

$$v_{Ts\_sin}(t) = \frac{v_H}{2} - r_T v_L sin\theta$$

(23)

$$i_{Ts\_sin}(t) = i_H + \frac{i_L}{r_T} sin\theta$$

(24)

$$\iota = \frac{i_{Ts\_sin\_max}}{i_{Ts\_sqw\_max}} = \frac{i_H + \frac{r_L}{r_T}}{i_H + \frac{i_L}{2r_T}} = \frac{1 + 2r_S}{1 + r_S} \ge 1.5 \ (r_S \ge 1)$$

(25)

The peak value of the ac current component in sinusoidal operation is twice that needed in near-square-wave operation for the same power conversion because the RMS values of voltage and current that set the power are both a factor of  $\sqrt{2}$  less than the peak values. As (25) shows this also, sinusoidal operation

requires power devices with a current rating at least 50% higher than near-square-wave case. This is partially offset by the need for circa 15% extra power devices to create the control headroom for the rapid reversal of near-square-wave current.

## D. Flexible Step-Ratio Range

The step-ratio of this converter is achieved by combination of inherent half-bridge ratio, stack modulation and transformer turns-ratio. This combination gives this converter flexibility in design and operation to meet a wide range of requirements.

Starting from the voltage relationships in (1) and (2), the overall step-ratio can be derived in (26).

$$R = \frac{v_H}{v_L} = 2r_S r_T = \frac{2(n_{T-lar} + n_{T-sma})}{n_{T-lar} - n_{T-sma}} \cdot \frac{N_1}{N_2}$$

(26)

The maximum and minimum values of (26) that can be achieved for a given number of SMs and a given control headroom are presented in (27) and (28).

$$R_{max} = 2(2n_{T-lar} - 1) \cdot \frac{N_1}{N_2} = 2[(1 - C_h)n_{SM} - 1] \cdot \frac{N_1}{N_2}$$

(27)

$$R_{min} = \frac{2(n_{T-lar}+1)}{n_{T-lar}-1} \cdot \frac{N_1}{N_2} = \frac{2[(1-C_h)n_{SM}+2]}{(1-C_h)n_{SM}-2} \cdot \frac{N_1}{N_2}$$

(28)

During the design process, the ratio between  $r_s$  and  $r_T$  can be adjusted to achieve various optimal objectives such as minimizing the physical volume, maximizing efficiency or reducing total cost. To illustrate the flexibility during operation (i.e. once the transformer turns-ratio is decided) the range of maximum and minimum *R* with a turns-ratio of 2 are plotted in Fig. 7(d) for various choices of control headroom. Varying the combinations for  $n_{T-sma}$  and  $n_{T-lar}$  makes available  $n_{SM}(n_{SM}-2)/4$ choices of step-ratio which for converters with tens or hundreds of SMs gives a large degree of operational flexibility.

The modulation scheme can be also flexible according to different conversion requirements in the practical applications.

When this converter serves as a dc tap for LPHR applications, the overall step-ratio is very high and the power throughput is expected to be less than 10% of the transmission link power [8], [13], [14]. For this application, the transformer power rating and voltage rating (less than 20 kV) will be much smaller than that in the front-to-front configuration for interconnecting two different HVDC links (more than 400 kV) [4], [5], [27]. Although the near-square-wave operation may pose a challenge on transformers due to the partial discharge, the benefits of reduced conversion volume and higher power utilization have stimulated the innovation and rapid development in transformer design for recent years, including the optimization of core/winding material and structure [47]–[49]. A laboratory prototype of medium frequency and medium voltage

near-square-wave transformer is newly announced up to 5 MW demonstration [50]. Alternatively, the experience and technology of small dv/dt filter, which has been widely used in high-power medium voltage motor drives up to 20 kV operation [51], [52], can be also utilized here in practical considerations.

In the meantime, as analyzed in Section II, the inserted SM number in transient stages and transient waveform are both adjustable according to the actual requirements. For the low step-ratio conversion, the trapezoidal voltage modulation [27] can be also implemented in the stacks as the preferred choice to fulfill the high power and high voltage conversion.

# E. Soft-Switching Operation

Analysis of the current-reversal stages (Stage 2 and Stage 5) showed that the rectifier current can be reduced to zero before the commutation happens so that zero-current-switching (ZCS) turn-off operation can be achieved for all the rectifier diodes. For Stage 3 and Stage 6 where the new current is established by turning on the alternate diodes, soft-switching operation is obtained inherently since rectifier diodes have the natural zero-voltage-switching (ZVS) capability. In the case where the rectifier is formed by active devices, both ZVS turn-on and ZCS turn-off operation can still be achieved when the power flow is from the high-voltage to the low-voltage side. If the power flow is reversed, ZCS turn-off capability is maintained by the control scheme but ZVS turn-on may not be possible in all situations.

# V. APPLICATION EXAMPLE AND SIMULATION ANALYSIS

This section presents a set of simulations of a full-scale near-square-wave current converter in order to validate the theoretical analysis and explore an application example of making a connection between HVDC and MVDC grids.

The converter is rated at 40 MW for conversion between a 200 kV HVDC link and a 20 kV MVDC grid. The SMs in high-voltage side have a reference voltage of 2.4 kV. Control headroom of 17% is provided and therefore 73 SMs are used in each stack. The ratio of power rating to SM number is still comparable to the standard MMC design [4], [25], [26]. In the low-voltage side, diodes are series connected to support  $v_L$ . The operation frequency is set at 500 Hz as a trade-off between the volume and the power losses. As an illustration, the overall step-ratio of 10:1 is composed of the inherent ratio of 2:1 of the half-bridge, a stack modulation ratio of 5:2 and a transformer turns-ratio of 2:1. The simulation parameters for this example are summarized in Table I. The simulation was conducted in the Matlab/Simulink using also the Artemis library.

TABLE I

SIMULATION PARAMETERS FOR THE APPLICATION EXAMPLE

| Parameter | Value            | Parameter                                                      | Value         |

|-----------|------------------|----------------------------------------------------------------|---------------|

| Р         | 40 MW            | $f_o$                                                          | 500 Hz        |

| $v_H$     | 200 kV (±100 kV) | $f_r$                                                          | 9.7 rot/cycle |

| $v_L$     | 20 kV            | $C_{SM}$                                                       | 1.0 mF        |

| VSM       | 2.4 kV           | $C_T C_B$                                                      | 45 μF         |

| $C_h$     | 17%              | $C_L$                                                          | 60 µF         |

| $n_T n_B$ | 73               | $E_S$                                                          | 21.7 kJ/MVA   |

| $r_S$     | 5/2              | $\delta_{\scriptscriptstyle dc}\delta_{\scriptscriptstyle SM}$ | 10%, 5%       |

| $r_T$     | 2/1              | $L_T L_B$                                                      | 1.2 mH        |

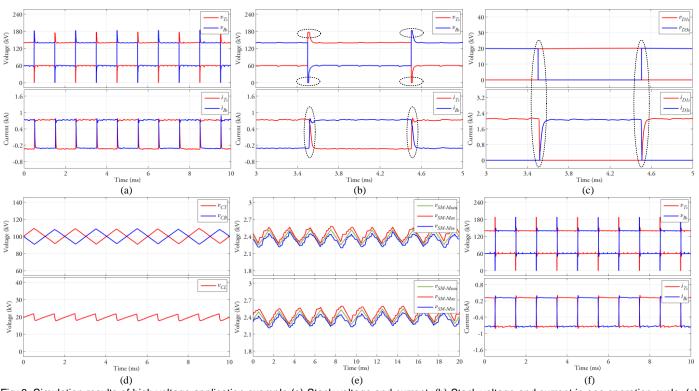

Simulation results are shown in Fig. 8. The stack voltages and currents in Fig. 8(a) are both near-square-waves with dc offsets as expected from (1)-(5). The top stack voltage in positive steady state (Stage 1) is about 60 kV while the bottom stack voltage is around 140 kV. The negative steady state (Stage 4) is symmetrical to the positive steady state with the top stack and bottom stack values replacing each other. Fig. 8(b) shows one cycle in more detail and illustrates the use of the control headroom to commutate the stack currents and synchronize them with the stack voltages. The modulation scheme implemented in this full-scale simulation is a classic NLM with SM voltage sorting and selection algorithm, illustrated in Fig. 6. Since there is a large number of SMs in the stack, the voltage error between  $v_{Ts,Bs}^*$  and  $N_{NLM}v_{SM}^*$  is negligible compared to the relatively large value of  $v_{Ts,Bs}^*$ , and NLM is accurate enough for tracking. The ripples in Fig. 8(a) and Fig. 8(b) are caused by SM sorting and selection. The rectifier waveforms in Fig. 8(c) show that the near-square-wave current from the high-voltage side is rectified and appears in the low-voltage link as a near-continuous current with brief dips toward zero. This feature significantly reduces the capacitance required for  $C_L$ compared with single-phase sinusoidal operation. It can be observed that the diodes that are being commutated off have currents that drop to zero before their voltage enters reverse-bias and that those turning on have currents that rise after their voltage reaches forward-bias. Both ZCS turn-off and ZVS turn-on are achieved in this example.

The dc-link capacitor may bring about some fault current in the event of a dc-side fault. However, it is also worth noting that the fault current caused by the dc-link capacitor will not go through any power device of the converter, allowing for using slow protection means [53], [54], which is inevitable in most medium-voltage and high-voltage converters for multi-terminal dc network or dc grid applications (including the popular 3-phase or single-phase front-to-front converters [32], [33]), so the presented circuit is not inferior in this sense. On the other hand, the dc-link capacitance in this converter can be relatively small thanks to the near-square-wave current modulation and medium frequency operation. The efficacy of the energy balancing is examined in Fig. 8(d) and Fig. 8(e). Fig. 8(d) shows that  $v_{CT}$  and  $v_{CB}$  are well-balanced with 45 µF  $C_T$  and  $C_B$ , and the deviation of  $v_{CL}$  is less than 10% of the nominal with 60  $\mu$ F  $C_L$ . It would be possible to reduce further this capacitance if additional control headroom were provided allowing the rate-of-change of current during commutation to be increased. The mean, maximum and minimum voltage values of the SM capacitors in each stack are shown in Fig. 8(e). It can be seen that the set of SM capacitor voltages are well-controlled and all are within 5% of the reference value of 2.4 kV. The sum of energy stored in all capacitors, including SM capacitors and dc-link capacitors is only 21.7 kJ/MVA in the application example.

A power losses model based on IEC 61803 and IEC 62751 [55] was built into the Simulink simulation using manufacturer's data for the chosen devices, namely, the MITSUBISHI CM1000HC-66R for the SM IGBTs and the MITSUBISHI press-pack diode FD3000AU-120DA in

Fig. 8. Simulation results of high voltage application example (a) Stack voltage and current. (b) Stack voltage and current in one operation cycle. (c) Rectifier voltage and current. (d) DC-link capacitors voltage deviation. (e) SM voltage deviation in top and bottom stack. (f) Power Flow Reversal.

series connection for the rectifier. The model reports the conduction and switching loss of each device during the simulation period. The estimation of transformer power loss is based on the Steinmetz equation [46]–[48]. The magnetic core is assumed to be constructed from AK Steel Lite Carlite M-2 electrical steel with a lamination thickness of 0.18 mm and the peak operational flux density was set at 1.62T Litz wire using round copper was chosen for primary and secondary windings, and the number of strands in each bundle was optimized for minimal ac resistance [56].

The power losses result for this case study is given in Table II and represents an overall efficiency of 98.0%. The IGBT switching loss was the largest term, as might be expected, given the need to create a medium frequency ac component of 500 Hz compared to 50/60 Hz for a typical ac-dc converter. Recognizing the high step-ratio conversion and internal transformer isolation, the efficiency is reasonable for a LPHR application. The efficiency could be improved by decreasing the operation frequency, and therefore also the switching power loss, but at a volume penalty for the capacitors and transformer.

As mentioned in Section II, this converter can pass power in the reverse direction if the low-voltage side rectifier diodes are replaced by IGBTs. Results for reverse power flow results are shown in Fig. 8(f). The dc offset and ac component of stack voltage are identical to those in Fig. 8(a), but the stack currents are phase-shifted by half a cycle with respect to the voltage.

| TABLE II                           |          |  |  |

|------------------------------------|----------|--|--|

| SIMULATION RESULTS OF POWER LOSSES |          |  |  |

| Power Losses Components            | Value    |  |  |

| Stack IGBT Conduction              | 256.6 kW |  |  |

| Stack IGBT Switching               | 274.3 kW |  |  |

| Rectifier Diodes Conduction | 58.7 kW  |

|-----------------------------|----------|

| Rectifier Diodes Switching  | 22.5 kW  |

| Transformer Core            | 108.4 kW |

| Transformer Windings        | 88.2 kW  |

| Other Passives              | 8.5 kW   |

| Total Loss                  | 817.2 kW |

## VI. ASSESSMENT OF EXPERIMENTAL RESULTS

To verify further the theoretical analysis and support the simulation results, a down-scaled laboratory prototype was built with maximum power and high-side voltage at 9 kW and 2 kV respectively (see Fig. 9). The control scheme was implemented on an OPAL real-time controller. The OPAL controller also manages the gate signals to the converter and records sampled voltages and currents from the converter.

Fig. 9. Down-scaled laboratory prototype.

Fig. 10. Experimental results of the down-scaled prototype (a) Stack voltage and current. (b) Arm inductor voltage and current. (c) Voltage and current at both terminals. (d) SM voltage deviation in top and bottom stack. (e) Current source mode operation. (f) Voltage source mode operation.

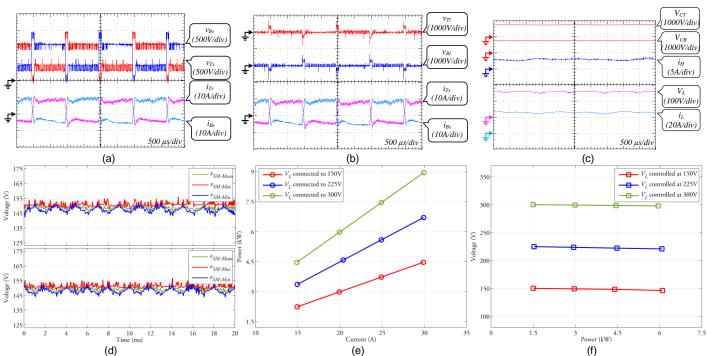

The parameters in experiment demonstration are listed in Table III. Noting that there are only 9 SMs in each stack, NLM is not sufficient for accurate tracking and so additional pulse width modulation (PWM) is applied to one extra SM which will be the  $N_{NLM}$ +1 SM in the voltage order. It provides the voltage difference between  $v_{TS,BS}^*$  and  $N_{NLM}v_{SM}^*$ .

Experimental results are given in Fig. 10. Fig. 10(a) shows the stack voltage and current are both, as expected, near-square-wave with dc offset of  $v_{H}/2$  and  $i_{H}$  respectively. The high frequency voltage ripple that can be seen is the result of PWM of the  $N_{NLM}+1$  SM. Fig. 10(b) demonstrates the use of control headroom to create voltage pulses across the arm inductors which force the the commutation of stack currents and reduce the transition time. These experimental results validate the theoretical analysis in Section II and simulation results in Section V.

To demonstrate the energy balancing results, the voltages and currents at both terminals are shown in Fig. 10(c) and the ranges of SM capacitor voltages are shown in Fig. 10(d). The voltages across  $C_T$  and  $C_B$ , in Fig. 10(c), are seen to be well-balanced at 750 V. It also verifies the voltage step-ratio in this test is 10:1 and current ratio between two terminals is 1:10. The minimum and maximum SM capacitor voltages in Fig 10(d) confirm that the balancing is within 5% of the nominal value of 150 V.

To illustrate current-source-operation, the low-voltage terminal was connected to a voltage source (set variously at 150V, 225 V and 300 V), and the circuit is controlled by the current loop of Fig. 6. By adjusting the current references, the power absorbed by the low-voltage terminal was varied as shown in Fig. 10(e). To illustrate voltage-source-operation, a variable resistor was connected to the low-voltage side and the outer voltage loop of Fig. 6 was employed. Fig. 10(f) shows that  $V_L$  was well-controlled at steady values (voltage reference set

variously at 150 V, 225 V and 300 V) as the variable resistor was changed from light to heavy load.

| 0                                                 |        |           |        |  |  |

|---------------------------------------------------|--------|-----------|--------|--|--|

|                                                   |        | TABLE III |        |  |  |

| EXPERIMENT PARAMETERS OF THE LABORATORY PROTOTYPE |        |           |        |  |  |

| Parameter                                         | Value  | Parameter | Value  |  |  |

| Р                                                 | 4.5 kW | $n_T n_B$ | 9      |  |  |

| $v_H$                                             | 1500 V | $f_o$     | 500 Hz |  |  |

| $v_L$                                             | 150 V  | $r_S$     | 5/2    |  |  |

| $v_{SM}$                                          | 150 V  | $r_T$     | 2/1    |  |  |

#### VII. CONCLUSION

A modular multilevel dc-dc converter has been presented in which a high step-ratio is achieved by a combination of inherent half-bridge ratio, SM stack modulation and transformer turn-ratio thereby giving a degree of design and operation flexibility. The converter has good potential for operation as a dc tap or as a dc transformer for future dc grids.

The topology on the high-voltage side is half-bridge single-phase inverter with stacks of SMs in each of the switch positions to withstand the high-side voltage stress. The high-voltage side processes all the power by only two SM stacks, so the total volume required by stack isolation can be kept low. Compactness is further advanced by using near-square-wave current operation which has been shown to yield a low SM capacitance size, further aided by operation in the medium frequency range. Near-square-wave current operation means instantaneous power flow is near-constant even for single-phase such that the dc smoothing capacitors can be small compared to sinusoidal operation.

A set of control loops and an energy balancer were presented. Rapid current reversal is aided by providing control headroom in the form of additional SM over those required for steady-state. It was shown that soft-switching of the diodes or This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIE.2018.2793249, IEEE Transactions on Industrial Electronics

analysis was verified against simulations of a full-scale (40 MW, 200 kV) example and further verified against experiments on a down-scaled (4.5 kW, 1.5 kV) prototype.

#### REFERENCES

- [1] E. Solas, G. Abad, J. A. Barrena, S. Aurtenetxea, A. Cárcar and L. Zając, "Modular Multilevel Converter With Different Submodule Concepts-Part II: Experimental Validation and Comparison for HVDC Application," in IEEE Trans. on Ind. Electron., vol. 60, no. 10, pp. 4536-4545, Oct. 2013.

- [2] A. Egea-Alvarez, F. Bianchi, A. Junyent-Ferre, G. Gross and O. Gomis-Bellmunt, "Voltage Control of Multiterminal VSC-HVDC Transmission Systems for Offshore Wind Power Plants: Design and Implementation in a Scaled Platform," in IEEE Trans. on Ind. Electron., vol. 60, no. 6, pp. 2381-2391, June 2013.

- C. D. Barker, C. C. Davidosn, D. R. Trainer, and R. S. Whitehouse [3] "Requirements of DC-DC converters to facilitate large DC grids," Cigre, SC B4 HVDC and Power Electronics, 2012.

- [4] T. Luth, M. M. C. Merlin, T. C. Green, F. Hassan, and C. D. Barker, "High-frequency operation of a dc/ac/dc system for HVDC applications," IEEE Trans. Power Electron., vol. 29, no. 8, pp. 4107-4115, August. 2014.

- G. P. Adam, I. A. Gowaid, S. J. Finney, D. Holliday, and B. W. Williams, [5] "Review of dc-dc converters for multi-terminal HVDC transmission networks", IET Power Electron., vol. 9, no. 2, 2016.

- U. Lamm, E. Uhlmann, and P. Danfors, "Some aspects of tapping of HVDC [6] transmission systems," Direct Current, vol. 8, May 1963.

- [7] M. P. Bahrman, M. H. Baker, J. Bowles, R. Bunch, J. Lemay, W. F. Long, J. McConnach, R. W. Menzies, J. R. Reeve and M. Szechtman, "Integration of small taps into (existing) HVDC links," IEEE Trans. Power Del., vol. 10, pp. 1699-1706, July 1995.

- M. Aredes, C. Portela and F. C. Machado, "A 25-MW soft-switching HVDC tap [8] for ±500-kV transmission lines," in IEEE Trans. on Power Del., vol. 19, no. 4, pp. 1835-1842, Oct. 2004.

- D. Jovcic and B. T. Ooi, "Tapping on HVDC lines using DC transformers," [9] Elect. Power Syst. Res., vol. 81, no. 2, pp. 561-569, Feb. 2011.

- [10] Y. Hu, R. Zeng, W. Cao, J. Zhang, and S. J. Finney, "Design of a Modular, High Step-Up Ratio DC-DC Converter for HVDC Applications Integrating Offshore Wind Power", IEEE Trans. Ind. Electron., vol. 63, no.4, pp. 2190-2202, 2016.

- [11] C. Meyer, M. Hoing, A. Peterson and R. W. De Doncker, "Control and Design of DC Grids for Offshore Wind Farms," in IEEE Trans on Ind. Appl., vol. 43, no. 6, pp. 1475-1482, Nov.-Dec. 2007.

- [12] M. Aredes, R. Dias, A. Aquino, C. Portela, and E. Watanabe, "Going the distance power-electronics-based solutions for long-range bulk power transmission, IEEE Ind. Electron. Magazine, vol. 5, no.1, Mar. 2011, pp. 36-48.

- [13] J. Maneiro, S. Tennakoon and C. Barker, "Scalable shunt connected HVDC tap using the DC transformer concept," 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, 2014, pp. 1-10.

- [14] B. Li, M. Guan, D. Xu, R. Li, G. P. Adam and B. Williams, "A series HVDC power tap using modular multilevel converters," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-7.

- [15] S. P. Engel, M. Stieneker, N. Soltau, S. Rabiee, H. Stagge and R. W. De Doncker, 'Comparison of the Modular Multilevel DC Converter and the Dual-Active Bridge Converter for Power Conversion in HVDC and MVDC Grids," IEEE Trans. Power Electron., vol. 30, no. 1, pp. 124-137, Jan. 2015.

- [16] D. Jovcic, et al., "DC-DC converters in HVDC Grids and for connections to HVDC systems," B4-76, CIGRE, 2016.

- [17] W. Li and X. He, "Review of Non-isolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications", IEEE Trans. on Ind. Electron., vol. 58, no. 4, pp. 1239-1250, April 2011.

- [18] B. Zhao, Q Song, W. Liu and Y. Sun, "Overview of dual-active-bridge isolated bidirectional dc-dc converter for high-frequency-link power- conversion system," IEEE Trans. Power Electron., vol. 29, no.8 pp. 4091-4106, Aug. 2014.

- H. Qin and J. W. Kimball, "Solid-state transformer architecture using ac-ac [19] dual-active-bridge converter," IEEE Trans. Ind. Electron., vol. 60, no. 9, pp. 3720-3730, Sep. 2013.

- [20] B. Zhao, Q. Song, J. Li, Q. Sun, W. Liu, "Full-Process Operation, Control and Experiments of Modular High-Frequency-Link DC Transformer Based on Dual-Active-Bridge for Flexible MVDC Distribution: A Practical Tutorial," in IEEE Trans. on Power Electron., vol. no.99, pp.1-1.

- [21] J. Zhang, Z. Wang and S. Shao, "A Three-Phase Modular Multilevel DC-DC Converter for Power Electronic Transformer Applications," in IEEE J. Emerg. Sel. Topics Power Electron., vol. 5, no. 1, pp. 140-150, March 2017.

- [22] X. Ruan, B. Li, Q. Chen, S. C. Tan and C. K. Tse, "Fundamental Considerations of Three-Level DC-DC Converters: Topologies, Analyses, and Control," in IEEE Trans. on Circuits and Systems I: Regular Papers, vol. 55, no. 11, pp. 3733-3743, Dec. 2008.

- switches in the low-voltage side is possible. The theoretical [23] F. Deng and Z. Chen, "Control of Improved Full-Bridge Three-Level DC/DC Converter for Wind Turbines in a DC Grid," in IEEE Trans. on Power Electron., vol. 28, no. 1, pp. 314-324, Jan. 2013.

- [24] A. Lesnicar and R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range", IEEE Bologna Power Tech Conference Proceedings, 2003, pp. 1-6.

- [25] S. Debnath, J. Qin, B, Bahrani, M. Saeedifard and P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review", IEEE Trans. Power Electron, vol. 30, no. 1, pp. 37-53, Jan. 2015.

- [26] I. A. Gowaid, G. P. Adam, A. M. Massoud, S. Ahmed, D. Holliday and B. W. Williams, "Quasi Two-Level Operation of Modular Multilevel Converter for Use in a High-Power DC Transformer With DC Fault Isolation Capability,' in IEEE Trans. on Power Electron., vol. 30, no. 1, pp. 108-123, Jan. 2015.

- [27] I. A. Gowaid, G. P. Adam, S. Ahmed, D. Holliday and B. W. Williams, "Analysis and Design of a Modular Multilevel Converter With Trapezoidal Modulation for Medium and High Voltage DC-DC Transformers," in IEEE Trans. on Power Electron., vol. 30, no. 10, pp. 5439-5457, Oct. 2015.

- [28] G. J. Kish, M. Ranjram, and P. W. Lehn, "A modular multilevel dc/dc converter with fault blocking capability for HVDC interconnects," IEEE Trans. Power Electron., vol. 30, no. 1, pp. 148-162, Jan. 2015.

- A. Schön, et al., "A new HVDC-DC converter with inherent fault clearing [29] capability", Power Electronics and Applications (EPE), 2013 15th European Conference on, Lille, 2013, pp. 1-10.

- X. Zhang, T. C. Green and A. Junyent-Ferré, "A New Resonant Modular [30] Multilevel Step-Down DC-DC Converter with Inherent-Balancing," in IEEE Trans. on Power Electron., vol. 30, no. 1, pp. 78-88, Jan. 2015.

- [31] M. Glinka and R. Marquardt, "A new AC/AC multilevel converter family," in IEEE Trans. on Ind. Electron., vol. 52, no. 3, pp. 662-669, June 2005.

- S. Kenzelmann, A. Rufer, D. Dujic, F. Canales, and Y. R. de Novaes, "Isolated [32] DC/DC Structure Based on Modular Multilevel Converter," IEEE Trans. on Power Electron., vol. 30, no. 1, pp. 89-98, Jan. 2015.

- [33] B. Zhao, Q. Song, J. Li, Y. Wang and W. Liu, "High-Frequency-Link Modulation Methodology of DC-DC Transformer Based on Modular Multilevel Converter for HVDC Application: Comprehensive Analysis and Experimental Verification," in IEEE Trans. on Power Electron., vol. 32, no. 5, pp. 3413-3424, May 2017.

- [34] P. Bresesti, W. L. Kling, R. L. Hendriks and R. Vailati, "HVDC Connection of Offshore Wind Farms to the Transmission System," in IEEE Trans. on Energy Conversion, vol. 22, no. 1, pp. 37-43, March 2007.

- D. Elliott, K. R. W. Bell, S. J. Finney, R. Adapa. C. Brozio, J. Yu, K. Hussain, "A [35] Comparison of AC and HVDC Options for the Connection of Offshore Wind Generation in Great Britain," in IEEE Trans on Power Del., vol. 31, no. 2, pp. 798-809, April 2016.

- [36] ABB, HVDC Light: It's time to connect. [Online]. Available: new.abb.com/docs/default-source/ewea-doc/hvdc-light.pdf

- D. Retzmann. Siemens. HVDC Station Layout, Equipment LCC & VSC and [37] Integration of Renewables using HVDC [Online]. Available: www.ptd.siemens.de/Cigre\_AUS\_2011\_HVDC\_&\_GridAccess\_tutorial\_Re.pdf

- [38] T. Lüth, M. M. C. Merlin and T. C. Green, "Modular multilevel DC/DC converter architectures for HVDC taps," 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, 2014, pp. 1-10.

- P. Li, S. J. Finney, and D. Holliday, "Active-Forced-Commutated Bridge Using [39] Hybrid Devices for High Efficiency Voltage Source Converters," IEEE Trans. on Power Electron., vol. 32, no.4, pp. 2485-2489, 2017.

- J. Kucka, D. Karwatzki and A. Mertens, "Enhancing the Reliability of Modular [40] Multilevel Converters Using Neutral Shift," in IEEE Trans. on Power Electron., vol. 32, no. 12, pp. 8953-8957, Dec. 2017.

- [41] K. Ilves, S. Norrga, L. Harnefors and H. P. Nee, "On Energy Storage Requirements in Modular Multilevel Converters", IEEE Trans. on Power Electron., vol. 29, no. 1, pp. 77-88, Jan. 2014.

- [42] K. Ilves, A. Antonopoulos, S. Norrga and H. P. Nee, "A New Modulation Method for the Modular Multilevel Converter Allowing Fundamental Switching Frequency," in IEEE Trans. on Power Electron., vol. 27, no. 8, pp. 3482-3494, Aug. 2012.

- [43] M. A. Bahmani, T. Thiringer, A. Rabiei and T. Abdulahovic, "Comparative Study of a Multi-MW High-Power Density DC Transformer With an Optimized High-Frequency Magnetics in All-DC Offshore Wind Farm," in IEEE Trans. on Power Del., vol. 31, no. 2, pp. 857-866, April 2016.

- U. Drofenik, "A 150kW Medium Frequency Transformer Optimized for Maximum Power Density," 2012 7th International Conference on Integrated [44] Power Electronics Systems (CIPS), Nuremberg, 2012, pp. 1-6.

- Z. Xing, X. Ruan, H. You, X. Yang, D. Yao and C. Yuan, "Soft-Switching [45] Operation of Isolated Modular DC/DC Converters for Application in HVDC Grids," IEEE Trans. on Power Electron., vol. 31, pp. 2753-2766, April 2016.

- [46] N. Soltau, D. Eggers, K. Hameyer and R. W. De Doncker, "Iron Losses in a Medium-Frequency Transformer Operated in a High-Power DC-DC Converter", IEEE Trans. on Magnetics, vol. 50, no. 2, pp. 953-956, Feb. 2014.

- [47] I. Villar, U. Viscarret, I. Etxeberria-Otadui and A. Rufer, "Global Loss Evaluation Methods for Non-sinusoidally Fed Medium-Frequency Power Transformers", *IEEE Trans. Ind. Electron.*, vol.56, pp.4132-4140, Oct. 2009.

- [48] P. Huang, C. Mao, D. Wang, L. Wang, Y. Duan, J. Qiu, G. Xu, H. Cai, "Optimal Design and Implementation of High-voltage High-power Silicon Steel Core Medium Frequency Transformer," in *IEEE Trans. on Ind. Electronics*, vol. 64, no. 6, pp. 4391-4401, June 2017.

- [49] M. Bahmani, "Design and Optimization Considerations of Medium-Frequency Power Transformers in High-Power DC-DC Applications," PhD thesis, Chalmers University of Technology Gothenburg, Sweden, 2016.

- [50] N. Soltau, H. Stagge, R. W. De Doncker and O. Apeldoorn, "Development and demonstration of a medium-voltage high-power DC-DC converter for DC distribution systems," 2014 IEEE 5th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Galway, 2014, pp. 1-8.

- [51] J. K. Steinke, "Use of an LC filter to achieve a motor-friendly performance of the PWM voltage source inverter," in *IEEE Trans. on Energy Conversion*, vol. 14, no. 3, pp. 649-654, Sep 1999.

Xin Xiang (S'17) received the B.Sc. degree in Electrical Engineering from Harbin Institute of Technology, China in 2011 and the M.Sc. degree in Electrical Engineering from Zhejiang University, China in 2014. He is currently working toward the Ph.D. degree in Imperial College London, U.K. under the supervision of Prof. Tim C. Green. His research interests include the design and control of high-power converters for high-voltage transmission technologies and medium-voltage

distribution applications.

Xiaotian Zhang (S'11–M'12) was born in Xi'an, China, in 1983. He received the B.S. and M.S. degrees in electrical engineering from Xi'an Jiaotong University, Xi'an, China, in 2006 and 2009, respectively, and the Ph.D. degree (with honors) in electrical engineering and electronics from the University of Liverpool, Liverpool, U.K., in 2012. Until 2015, he was with the Department of Electrical Engineering, Imperial College London, U.K. He is currently an Associate Professor in the

Department of Electrical Engineering, Xi'an Jiaotong University. His research interests include control and design of HVDC converters.

**Thomas Luth** received the M.Eng degree (first class Hons.) and Ph. D. degree from Imperial College, London, U.K., in 2010 and 2014, both in electrical and electronic engineering. His research interests include power electronics and transmission technologies. His work currently focuses on dc/dc converters for HVDC applications.

**Michael M. C. Merlin** (M'12) received the electrical engineering degree from the Ecole National Superieur de l'Electronique et de ses Applications (ENSEA), Cergy, France, in 2008 and the M.Sc. degree in control systems then the Ph.D. degree in electrical engineering from Imperial College, London, U.K. in 2008 and 2013 respectively. He became a Lecturer at the University of Edinburgh in 2017. His main research interest are design, optimization and

control of power converters, more specifically of the modular types which use stacks of sub-modules to achieve high power efficiency and waveform quality.

- [52] M. Mechlinski, S. Schröder, J. Shen and R. W. De Doncker, "Grounding Concept and Common-Mode Filter Design Methodology for Transformerless MV Drives to Prevent Bearing Current Issues," in *IEEE Trans. on Ind. Appl.*, no.99, pp.1-1.

- [53] M. Hajian, L. Zhang and D. Jovcic, "DC Transmission Grid With Low-Speed Protection Using Mechanical DC Circuit Breakers," in *IEEE Trans. on Power Del.*, vol. 30, no. 3, pp. 1383-1391, June 2015.

- [54] C. Barker, R. Whitchouse, A. Adamczyk, and M. Boden, "Designing fault tolerant HVDC networks with a limited need for HVDC circuit breaker operation," B4-112, CIGRE, 2014.

- [55] P. S. Jones and C. C. Davidson, "Calculation of power losses for MMC-based VSC HVDC stations", in *Proc. EPE*, 2013, pp. 1–10.

- [56] F. Tourkhani and P. Viarouge, "Accurate analytical model of winding losses in round Litz wire windings," *IEEE Trans. on Magnetics*, vol.37, no.1, pp.538-543, Jan 2001.

**Timothy C. Green** (M'89–SM'02) received a B.Sc. (Eng) (first class honours) from Imperial College London, UK in 1986 and a Ph.D. from Heriot-Watt University, Edinburgh, UK in 1990. He is a Professor of Electrical Power Engineering at Imperial College London, and Director of the Energy Futures Lab with a role fostering interdisciplinary energy research. He also leads the HubNet consortium of UK universities. His research interest is in using the flexibility of power

electronics to accommodate new generation patterns and new forms of load, such as EV charging, as part of the emerging smart grid. In HVDC he has contributed converter designs that reduce losses while also providing control functions assist AC system integration. In distribution systems, he has pioneered the use of soft open points and the study of stability of grid connected inverters.