### Reconfigurable high efficiency class-F power amplifier using CMOS-MEMS technology

### Mitra Gilasgar

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional (http://upcommons.upc.edu/tesis) **UPCommons** i. el repositori cooperatiu TDX (http://www.tdx.cat/) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA** La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<u>http://upcommons.upc.edu/tesis</u>) y el repositorio cooperativo TDR (<u>http://www.tdx.cat/?locale-attribute=es</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual **únicamente para usos privados enmarcados** en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons (*framing*). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

WARNING On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutional repository **UPCommons** (http://upcommons.upc.edu/tesis) and the cooperative repository TDX (http://www.tdx.cat/?localeattribute=en) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# Reconfigurable High Efficiency Class-F Power Amplifier Using CMOS-MEMS Technology

Author Mitra Gilasgar

Thesis Advisors Prof. Lluís Pradell Prof. Antoni Barlabé

A thesis submitted to the Universitat Politècnica de Catalunya (UPC) in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

Department of Signal Theory and Communications

Ph.D. program on Signal Theory and Communications RF & Microwave Systems, Devices and Materials Group Barcelona, April 2017

Thesis written by Mitra Gilasgar

Reconfigurable High Efficiency Class-F Power Amplifier Using CMOS-MEMS Technology

Ph.D. program on Signal Theory and Communications Universitat Politècnica de Catalunya (UPC)

This work has been supported by the "Ministerio de Economía y Competitividad" through the FPI fellowship program with grant BES-2011-051305 and in frame of the projects TEC2013-48102-C2-1-P and TEC2016-78028-C3-1-P.

To my mother for teaching me everything, making mathematics beautiful, and for all she has done for me, and To my father for believing me, motivating me and for being there in every step I took.

The sun will shine someday.

This thesis has been supported by the Ministerio de Economía y Competitividad with PhD grant (BES-2011-051305) for four years and the travel grant (EEBB-I-13-07796) for a six month stay in Canada, in the frame of the projects (TEC2013-48102-C2-1-P and TEC2016-78028-C3-1-P).

### Acknowledgments

This thesis is a result of years devoted to research and study and I would like to acknowledge all the wonderful people who have been part of this journey with me.

First and foremost I wish to thank my supervisors, Prof. Lluís Pradell and Prof. Antoni Barlabé for their continuous support throughout this doctoral research. I have been very fortunate to be their student and I have learned a lot from them. I appreciate all the motivations, patience and knowledge they have given to me during this time and I will always look up to them as excellent examples of great teachers and human beings.

I would like to show my gratitude toward Dr. José-Luis González, who helped me during my arrival to UPC and was very supportive in one of the hardest times of my life. Not to forget Prof. Eva Vidal for her support and care for me.

I want to make a special thank to Prof. **Jordi Romeu** for his trust in me and accepting me as a researcher in his group, which changed my life and is something I will never forget.

My sincere thanks go to Prof. **Raafat Mansour**, head of CIRFE, who provided me an opportunity to join his team as a visiting researcher, and gave access to the research facilities during my short stays in the University of Waterloo. I also would like to thank Dr. **Maher Bakri-Kassem** from the American University of Sharjah for his contribution to the MEMS design in the CMOS-MEMS PA of this thesis. In addition, I would like to thank Dr. **Siamak Fouladi** for his kindness to answer my questions through email.

Prof. **Francesc Moll** from the electronic department of UPC deserves special thanks. He provided me the access to the CMOS technology and Cadence environment and was willing to help along the way whenever a problem appeared.

TSC-D3 staff Joaquim Giner, Albert Marton, and Rubén Tardío provided help and support on implementation of several boards. Joaquim sat with me and showed me how Altium works and gave full support when I was designing several PCB for which I want to thank him specifically. Not to forget **Teresa Pons** and **Aynie Khoe** who helped me many times on paperwork related things and for my travels. I would like to thank the IT crowd, **Santiago Perez** from C4, **Josep Ma. Haro** and **Ferran Alvaro** from D3 for their availability and immediate help with IT issues.

Needless to say, I want to thank my dear friends, for all the good times and their support during the tough times: Alexandra Sevastianova and Raisa Pesel who became my best friends during my stay in Canada and made me feel I was at home, spending amazing times together, Dena Alavi for being such a great friend in Barcelona and the lovely postcards I kept receiving from her after she left, and Yenlin Chen for her emotional support during the writing of this thesis. I like to thank Silvia Teresa Sandy-Martinez, Omid Ghahabi, and Hadis Mahdavi for being amazingly kind and such true friends.

I would like to thank my office mates Eduardo Makhul, Marc Pons, Adrián Contreras, Dennis Andrade-Miceli, Geoffrey Lee and also my colleague from Ampleon, Netherlands Jos van der Zanden for all the help they have offered me and all the productive discussions either face to face or through emails.

To be able to write this thesis and consequently this acknowledgment is all because **my parents** supported me fully and unconditionally. My mother is the first teacher in my life who set an example of dedication and hard work for me. I like to thank her for teaching me to follow my dreams and goals and to be strong. The trust I received from my father during all my life has kept me motivated to move toward my goals. He never doubted me and gave me full trust on my decisions especially when I decided to do my PhD in Spain. I like to thank my brothers, **Mansour** for all the Skypes and talks to cheer me up during the times I was down and **Amirreza** for bringing happiness to every moment of my life. I also want to thank my **grandmother**, apart from spending my childhood in her house every day after school, I am so thankful for those six months she welcomed me in her house so I could fully focus on preparation for entrance exam of master studies without worrying about anything else.

And I want to thank my best friend in life, **Lázaro**, who was a shoulder for me in all the tough days and a great accompany for all the happy days. His presences in every step of this journey made it easier for me and a great memory to remember.

### Abstract

The increasing demand for wireless products to be part of our daily lives brings the need for longer battery lifetime, smaller size and lower cost. To increase battery lifetime, high efficiency power amplifiers (PAs) are needed; To make them smaller, integration or reconfiguration is aimed and to reach lower costs, technologies such as CMOS are final goals. However integration of high efficiency PA in CMOS is challenging due to the technology limitations which restricts the achievable output power and efficiency of the PA. In order to bring solutions for the above-mentioned requirements, in this thesis novel reconfigurable class-F PAs, frequency-reconfiguration, CMOS integration, impedance-reconfiguration and CMOS-MEMS implementation are addressed.

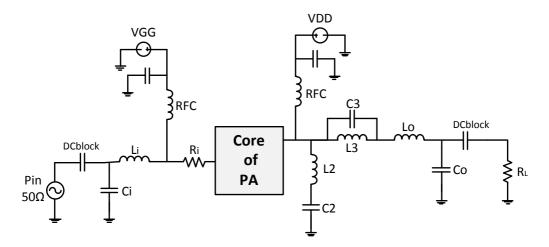

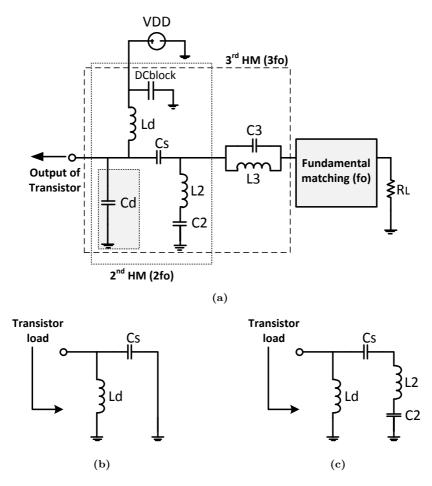

Starting with a single frequency operation, a novel class-F PA for mobile applications is proposed in which with a proper harmonic tuning structure the need for extra filtering sections is eliminated, achieving an excellent harmonic-suppression level. This topology uses transmission lines and is developed to cover multiple frequency bands for purpose of global coverage with aim of size reduction. Three novel frequency reconfigurable PAs are proposed using MEMS and semiconductor switches to accomplish class-F operation at two frequencies. The main novelty of this structure is that the reconfiguration is done not only at fundamental frequency but also at harmonics with reduced number of tuning elements. Moreover, by proper placement of the switches in the stubs, the maximum voltages over the switches are minimized. The proposed structure overcomes the narrow band performance of class-F, giving an efficiency more than 60% over a 225 MHz and 175 MHz bandwidth at 900 MHz and 1800 MHz respectively. Measurement results showed high performance at both frequency bands giving 69.5% and 57.9% PAE at 900 MHz and 1800 MHz respectively.

A novel CMOS class-F PA is proposed that controls up to the  $3^{rd}$  harmonic and can adapt to load variations due to the effect of the human body on mobile phones. It enables the integration of the PA with other devices in a single chip leading to better matching, higher performance, lower cost and smaller size. In addition, it achieves load impedance reconfigurability by using impedance tuner in its output network and by proper tuning of the network, effects of load variation on the performance are compensated. Two designs at 2.4 GHz have been done using either MOS varactors or MEMS variable capacitors as tuning devices. The design using MOS varactors show a maximum measured values of 26% PAE and 19.2 dBm output power for 50 $\Omega$  load. For loads other than 50 $\Omega$  an improvement of 15% for PAE and 4.4 dB for output power is obtained in comparison to non-tuned one. The second design is done using MEMS variable capacitors integrated in CMOS technology through a mask-less post-processing technique. Simulations results for 50 $\Omega$  load show a peak PAE of 32.8% while delivering 18.2 dBm output power.

## Contents

| 1        | Intr                         | oducti  | on 1                                                 |  |  |  |  |  |  |  |

|----------|------------------------------|---------|------------------------------------------------------|--|--|--|--|--|--|--|

|          | 1.1                          | Motiva  | ation                                                |  |  |  |  |  |  |  |

|          | 1.2                          |         | zives                                                |  |  |  |  |  |  |  |

|          | 1.3                          | Thesis  | Outline                                              |  |  |  |  |  |  |  |

| <b>2</b> | State of The Art 7           |         |                                                      |  |  |  |  |  |  |  |

|          | 2.1                          | High I  | Efficiency Class-F PAs                               |  |  |  |  |  |  |  |

|          | 2.2                          |         | band Operation                                       |  |  |  |  |  |  |  |

|          |                              | 2.2.1   | Concurrent Multi-band PAs                            |  |  |  |  |  |  |  |

|          |                              | 2.2.2   | Broadband PAs                                        |  |  |  |  |  |  |  |

|          |                              | 2.2.3   | Frequency Reconfigurable PAs 14                      |  |  |  |  |  |  |  |

|          | 2.3                          | Imped   | ance Tuners                                          |  |  |  |  |  |  |  |

| 3        | Power Amplifier Fundamentals |         |                                                      |  |  |  |  |  |  |  |

|          | 3.1                          |         | Amplifier Metrics    22                              |  |  |  |  |  |  |  |

|          |                              | 3.1.1   | Power                                                |  |  |  |  |  |  |  |

|          |                              | 3.1.2   | Gain                                                 |  |  |  |  |  |  |  |

|          |                              | 3.1.3   | Efficiency                                           |  |  |  |  |  |  |  |

|          |                              | 3.1.4   | Stability                                            |  |  |  |  |  |  |  |

|          | 3.2                          | Power   | Amplifier Classes and Topologies                     |  |  |  |  |  |  |  |

|          |                              | 3.2.1   | Linear PAs: Classes A, B, AB, and C 27               |  |  |  |  |  |  |  |

|          |                              | 3.2.2   | Switching PAs: Classes D, E, and F                   |  |  |  |  |  |  |  |

|          | 3.3                          | The C   | lass-F Power Amplifier Basics                        |  |  |  |  |  |  |  |

|          |                              | 3.3.1   | Maximally Flat Waveforms                             |  |  |  |  |  |  |  |

|          |                              | 3.3.2   | Quarter-wave Transmission Line Class-F               |  |  |  |  |  |  |  |

|          |                              | 3.3.3   | Multi-Harmonic Resonator Implementation of Class-F   |  |  |  |  |  |  |  |

|          |                              | 3.3.4   | Fully Transmission Line Implementation of Class-F 34 |  |  |  |  |  |  |  |

|          | 3.4                          | Load-l  | Pull Technique                                       |  |  |  |  |  |  |  |

| 4        | Cla                          | ss-F Po | ower Amplifier Basic Operation and Analysis 39       |  |  |  |  |  |  |  |

|          | 4.1                          |         | sed Class-F Power Amplifier Topology                 |  |  |  |  |  |  |  |

|          | 4.2                          | -       | at 900 MHz Operating Frequency                       |  |  |  |  |  |  |  |

|          |                              | 4.2.1   | Load Pull Analysis                                   |  |  |  |  |  |  |  |

|          |                              | 4.2.2   | Stability                                            |  |  |  |  |  |  |  |

|          |                              | 4.2.3   | Simulation Results                                   |  |  |  |  |  |  |  |

|          |                                                        | 4.2.4   | Fabrication                                             |     |                        |     | . 49  |

|----------|--------------------------------------------------------|---------|---------------------------------------------------------|-----|------------------------|-----|-------|

|          |                                                        | 4.2.5   | Measurement Results                                     |     |                        |     |       |

|          | 4.3                                                    | Design  | at 1800 MHz Operating Frequency                         |     |                        |     |       |

|          |                                                        | 4.3.1   | Load Pull / Source Pull Analysis                        |     |                        |     |       |

|          |                                                        | 4.3.2   | Stability                                               |     |                        |     |       |

|          |                                                        | 4.3.3   | Simulation Results                                      |     |                        |     |       |

|          |                                                        | 4.3.4   | Fabrication                                             |     |                        |     |       |

|          |                                                        | 4.3.5   | Measurement Results                                     |     |                        |     |       |

|          |                                                        | 1.010   |                                                         |     |                        | •   |       |

| <b>5</b> | Dual-Frequency Reconfiguration Class-F Power Amplifier |         |                                                         |     |                        |     |       |

|          | 5.1                                                    | Propos  | sed Dual-Frequency Reconfiguration Concept              |     |                        |     | . 66  |

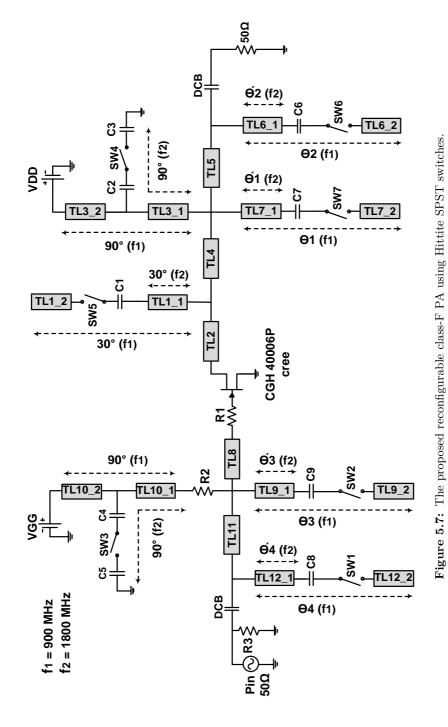

|          | 5.2                                                    | Freque  | ency Reconfigurable PA using Hittite SPST Switches      |     |                        |     | . 68  |

|          |                                                        | 5.2.1   | Introduction to Hittite Switches                        |     |                        |     | . 68  |

|          |                                                        | 5.2.2   | Input and Output Matching Network Design                |     |                        |     | . 68  |

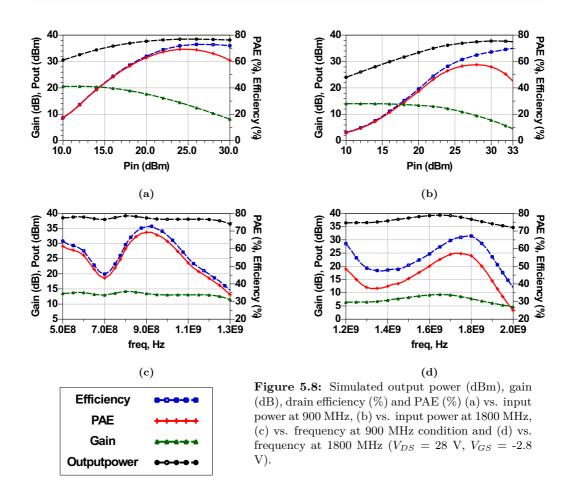

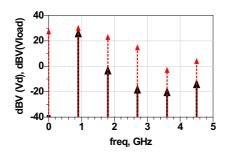

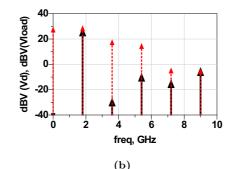

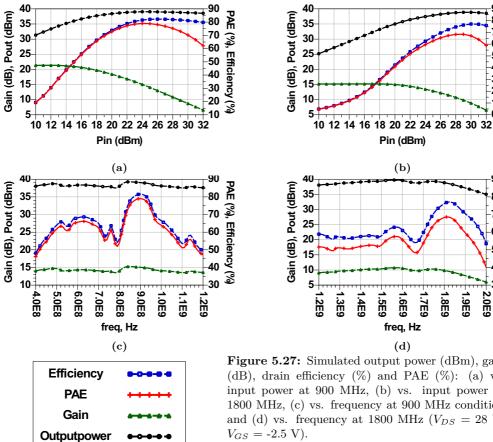

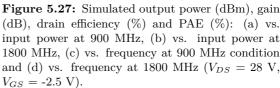

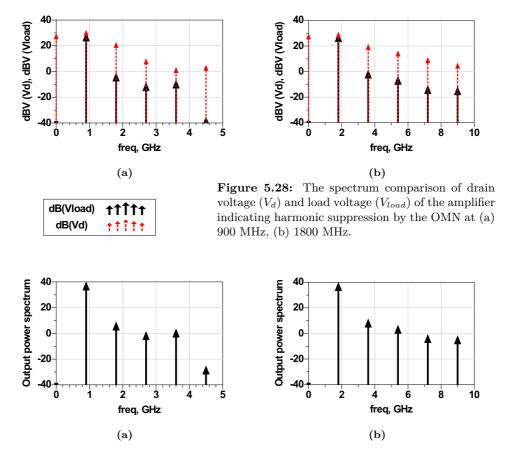

|          |                                                        | 5.2.3   | Simulation Results                                      |     |                        |     |       |

|          |                                                        | 5.2.4   | Fabrication                                             |     |                        |     | . 73  |

|          |                                                        | 5.2.5   | Measurement Results                                     |     |                        |     | . 74  |

|          |                                                        | 5.2.6   | Study for Device Reliability                            |     |                        |     | . 75  |

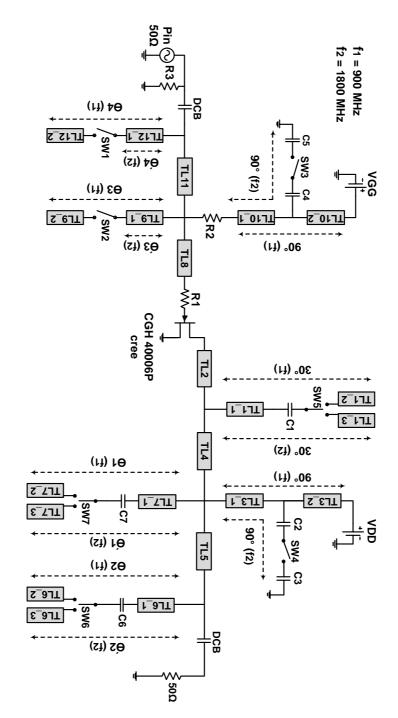

|          | 5.3                                                    | Freque  | ency Reconfigurable PA using MEMS Switches - Design A.  |     |                        |     |       |

|          |                                                        | 5.3.1   | Introduction to MEMS Switches                           |     |                        |     |       |

|          |                                                        | 5.3.2   | Input and Output Matching Network Design                |     |                        |     |       |

|          |                                                        | 5.3.3   | Simulation Results                                      |     |                        |     |       |

|          |                                                        | 5.3.4   | Fabrication                                             |     |                        |     |       |

|          |                                                        | 5.3.5   | Measurement Results                                     |     |                        |     |       |

|          | 5.4                                                    |         | ency Reconfigurable PA using MEMS Switches - Design B.  |     |                        |     |       |

|          | 0.1                                                    | 5.4.1   | Input and Output Matching Network Design                |     |                        |     |       |

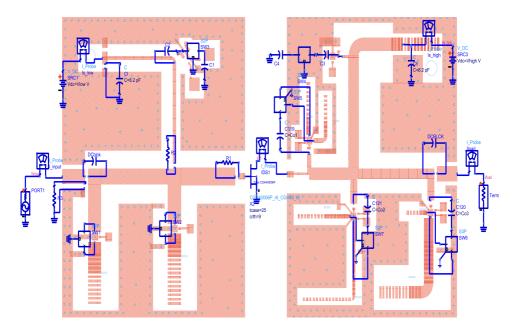

|          |                                                        | 5.4.2   | Simulation Results                                      |     |                        |     |       |

|          |                                                        | 5.4.3   | Fabrication                                             |     |                        |     |       |

|          |                                                        | 5.4.4   | Measurement Results                                     |     |                        |     |       |

|          |                                                        | 5.4.5   | Summary                                                 |     |                        |     |       |

|          |                                                        | 0.4.0   | Summary                                                 | • • | •                      | ·   | . 100 |

| 6        | Pow                                                    | ver Red | configurable class-F PA Integrated in CMOS Techno       | lo  | $\mathbf{g}\mathbf{y}$ |     | 105   |

|          | 6.1                                                    |         | e Output Matching Network for a Class-F PA using Lumped |     |                        |     |       |

|          | 6.2                                                    |         | of Different PA Configuration and Voltage Capability    |     |                        |     |       |

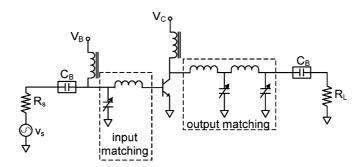

|          | 6.3                                                    |         | sed Reconfigurable Class-F Power Amplifier              |     |                        |     |       |

|          | 6.4                                                    | -       | oull Analysis                                           |     |                        |     |       |

|          | 6.5                                                    |         | in CMOS Technology                                      |     |                        |     |       |

|          | 6.6                                                    | Power   | Amplifier Implementation                                |     |                        |     | . 115 |

|          | 6.7                                                    |         |                                                         |     |                        |     |       |

|          | 6.8                                                    |         | rement setup                                            |     |                        |     |       |

|          | 6.9                                                    |         | rement Results                                          |     |                        |     |       |

|          | 0.0                                                    | 6.9.1   | $50\Omega$ Load                                         |     |                        |     |       |

|          |                                                        | 6.9.2   | Variable Load                                           |     |                        |     |       |

|          |                                                        | 0.5.2   |                                                         | • • | •                      | •   | . 121 |

| 7        | $\mathbf{CM}$                                          | OS P    | ower Reconfigurable Class-F PA using MEMS               | Va  | ari                    | iał | ole   |

|          |                                                        | acitor  |                                                         |     |                        |     | 137   |

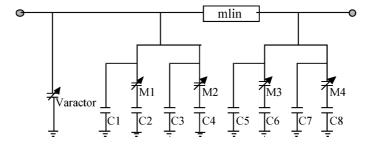

|          | 7.1                                                    |         | sed Reconfigurable Class-F Power Amplifier              |     |                        |     |       |

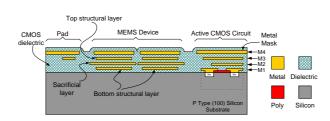

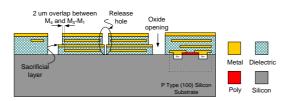

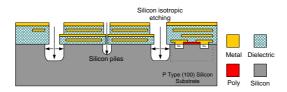

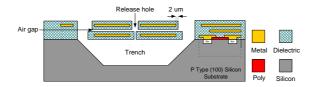

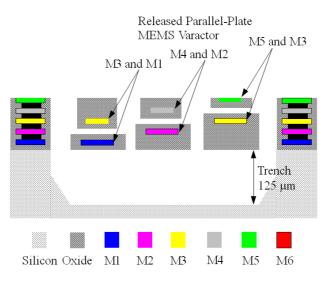

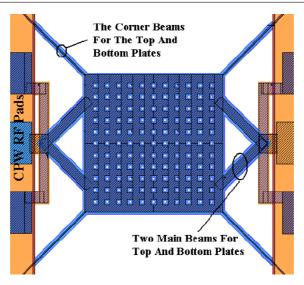

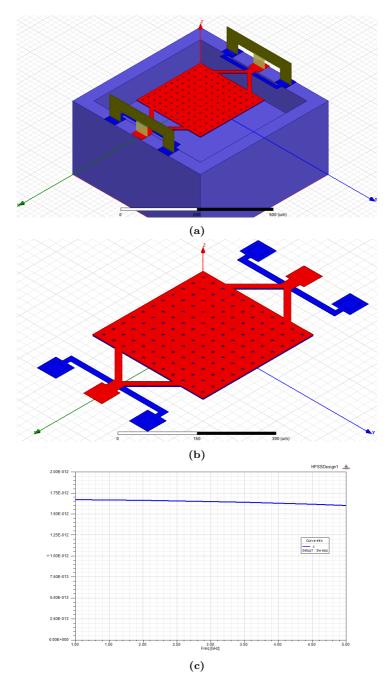

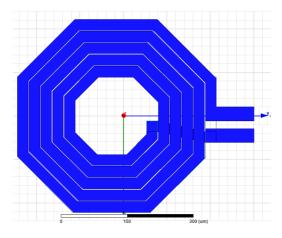

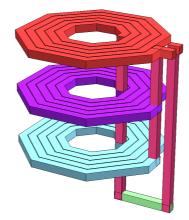

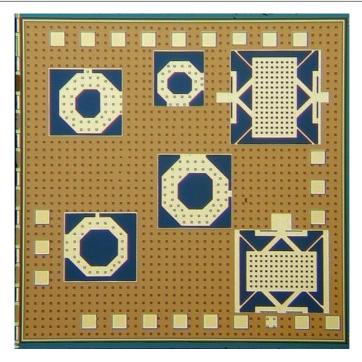

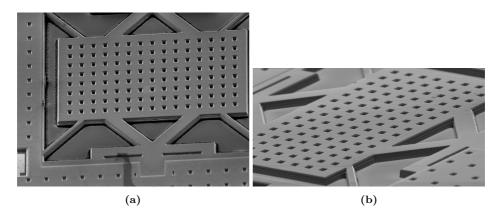

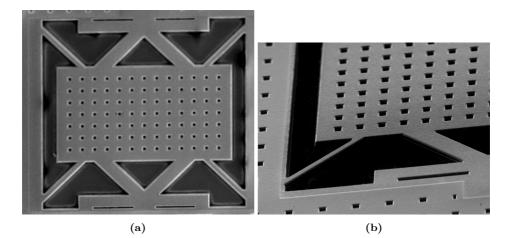

|          | 7.2                                                    | -       | electromechanical Systems (MEMS) in CMOS Technology.    |     |                        |     |       |

|          | –                                                      |         |                                                         |     | -                      |     |       |

|                 | 7.3                  | Inductor Implementation        | 141 |  |  |  |  |  |  |

|-----------------|----------------------|--------------------------------|-----|--|--|--|--|--|--|

|                 | 7.4                  | Power Amplifier Implementation | 145 |  |  |  |  |  |  |

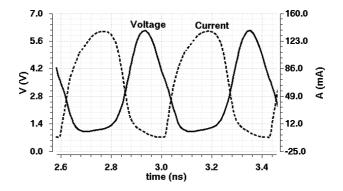

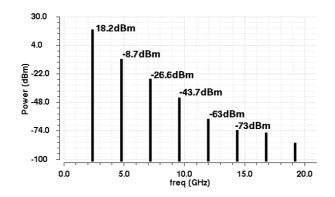

|                 | 7.5                  | Simulation Results             | 145 |  |  |  |  |  |  |

| 8               | Con                  | clusion                        | 151 |  |  |  |  |  |  |

|                 | 8.1                  | Main Conclusions               | 152 |  |  |  |  |  |  |

|                 | 8.2                  | Future Research Lines          | 154 |  |  |  |  |  |  |

| Acronyms        |                      |                                |     |  |  |  |  |  |  |

| List of Figures |                      |                                |     |  |  |  |  |  |  |

| Li              | List of Tables       |                                |     |  |  |  |  |  |  |

| Bibliography    |                      |                                |     |  |  |  |  |  |  |

| Lis             | List of Publications |                                |     |  |  |  |  |  |  |

## Chapter 1 Introduction

This chapter describes the motivation of the study that was carried out within this doctoral activity and the main objectives to be fulfilled. The structure of this doctoral dissertation is presented to point out specifically what are the main contributions of each chapter and how they are linked to the fundamental goals.

#### 1.1 Motivation

There is an ever-increasing demand for wireless communication products such as cellular phones, wireless local area networks (WLAN), and wireless computer peripherals to be part of our daily lives. Among the whole transmitter building blocks, power amplifiers (PAs) are the most critical blocks because of their high power consumption. Advances in wireless systems demand longer battery lifetime, smaller size and lower cost, bringing a great need for PAs to be highly efficient, work under different conditions and in the case of mobile handsets, to be integrated with other devices in a single chip [1]. If the efficiency of the PA is not high, it results in short battery lifetime of the device. In addition, dissipated power transforms to heat, which can bring reliability issues and degrade the lifetime of the PA itself.

High efficiency is achieved at the expense of linearity and finding a trade-off between the two is one of the most challenging aspects of the PA design. In wireless Global Systems for Mobile Communications (GSM) standard, nonlinearity of amplifiers is not an issue since it uses Gaussian Minimum Shift Keying (GMSK) constant envelope modulation. With advances in wireless systems, the usage of Quadrature Amplitude Modulation (QAM) or Orthogonal Frequency Division Multiplexing (OFDM) are essential to maximize data rates in a limited bandwidth. However, in both cases the transmitted signal exhibits both amplitude and phase information, which are normally amplified by linear and inefficient amplifiers. In addition to that, transmitted signal exhibits high peak-to-average power ratio (PAPR) which hampers the efficiency of linear amplifiers and results in PAs operating at an average output power well below its One method to increase the efficiency of a linear PA is envelope optimum value. tracking (ET) technique where it maximizes the efficiency versus output power by constantly adjusting the power supply voltage. Alternatively, Kahn envelope elimination and restoration (EER) technique [2] is a method for linearity enhancement of a high efficiency PAs which enables the use of high efficiency PAs in linear systems.

In mobile communication networks, it is desired that RF front ends and consequently PAs can adapt to different conditions that arise in wireless applications such as a change in bias, frequency, load impedance or power. The increasing demand of wireless devices for global coverage results in the need for systems to cover multiple frequency bands. To achieve the multi-band coverage, multi-band transceivers, and consequently multi-band PAs are needed. Another condition is load impedance variation which happens when a user holds the mobile phone and the strong interaction between head, hand, and antenna causes a change in antenna impedance [3, 4] leading to a reduced performance. Using reconfigurable matching networks (MN) instead of a fixed matching network brings new opportunities to recover the performance in terms of efficiency and power while operating under different conditions. The reconfiguration is usually achieved by use of varactors or switches.

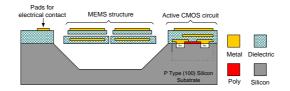

To enable integration of all mobile circuitry in a single unit, the use of complementary metal oxide semiconductor (CMOS) is inevitable. CMOS technology offers high integration level with low cost. Although most handset components are integrated in CMOS technology, the PA is still the most difficult block to implement in CMOS [5] due to the low breakdown voltage, the conductive substrate, and the sheet-resistance of the poly silicon that limit the output power and efficiency of the PA. However, by integration of a PA with other devices on a single chip better matching and higher performance will be achieved in addition to lower cost and smaller size.

Reconfigurable matching networks incorporate integrated varactors or switches which can be implemented either using CMOS components or microelectromechanical system (MEMS). RF MEMS devices have an intrinsically low loss and are compatible with highfrequency fabrication methods. Reconfigurable MNs that incorporate MEMS switches or variable capacitors show the least degradation of overall performance in the PA and are most widely used in hybrid circuits. To use MEMS devices in CMOS technology, they can be fabricated on a different substrate and flip-chip bonded onto a CMOS chip [6], however, flip-chip bonding involves relatively high costs. A single-chip implementation of MEMS devices integrated in CMOS [7] eliminates the problems of hybrid bonding and packaging parasitics hence improving performance and lowering the cost.

In order to achieve high efficiency, the switching PAs [8] have a minimum overlap between the drain current and voltage waveforms, resulting in lower power dissipation than linear amplifiers. Among the high efficiency PA classes, the class-E PA is attractive due to its simple load network. In addition, class-E overcomes the device parasitic capacitance problem of class-D. However, class-E PA suffers from voltage stress in the device output which, depending on the application might be harmful. The voltage swing on the drain of a class-E PA can reach up to 3.6 times the drain supply voltage  $V_{DD}$ , while only 2 times  $V_{DD}$  is possible for a class-F PA, therefore, for the implementation on low breakdown technologies such as CMOS, a class-F PA is more suitable despite having a more complex load network.

#### 1.2 Objectives

The focus of this dissertation is to provide different topologies to implement a reconfigurable high efficiency class-F PA. After a general review of different classes of PAs and its fundamentals, high efficiency class-F PAs are studied and a new topology is proposed. The major focus of this thesis is on reconfiguration techniques provided for class-F PAs. The work has focused on two reconfiguration types: *frequency* and *load*

*impedance.* The proposed reconfigurable structures control up to  $3^{rd}$  harmonic with a proper harmonic tuning network. The integrated and reconfigurable PA design in CMOS is intended for Bluetooth application which brings new opportunities for PAs to be integrated with other components in the handset. The works of this research include:

- Design, development, and fabrication of novel single frequency high efficiency class-F PA: A single frequency class-F PA topology is proposed and designed to meet requirements of high efficiency, high power, and high harmonic rejection while matched to  $50\Omega$  input and output impedance. The proposed topology provides a very low total harmonic distortion (THD) which eliminates the need for extra filtering section. Two boards are designed and fabricated at two different frequencies and high performance was achieved from each board while they fulfilled the matching requirement of  $|S_{11}|$  and  $|S_{22}|$  being less than -10 dB for  $50\Omega$  source and load impedance.

- Design, development, and fabrication of novel frequency reconfigurable class-F PAs: A complete study of frequency reconfiguration and its structure is developed for class-F PA with the requirements of providing high efficiency and high power at each frequency band. The proposed dual-band frequency PA switches between two different frequency bands while maintaining high efficiency and power at each band. Frequency-reconfiguration is achieved by input and output reconfiguration using Single Pole Single Throw (SPST) and Single Pole Double Throw (SPDT) switches. Three different reconfigurable circuits are developed using semiconductor either Hittite switches or MEMS switches. The MEMS switches showed higher power capability and lower loss resulting in a higher performance of the PA.

- Design, development, and implementation of a novel impedance reconfigurable class-F PA in standard CMOS technology: A new reconfigurable class-F PA is proposed and designed at 2.4 GHz to meet several requirements such as adjustment of a variable load impedance, small size, high efficiency and enough power for the Bluetooth application. This PA addresses the effect of load variation which is caused by proximity effect of head and hand on the cellphones. Impedance-reconfiguration is achieved by reconfiguring the output network using an impedance tuner. The impedance tuner incorporates two MOS variable capacitors and also provides the proper harmonic termination at fundamental frequency and harmonics. The proposed structure proves the ability of the PA to compensate for the drop of the overall performance by means of tuning varactors.

• Design, development, and implementation of a novel impedance reconfigurable class-F PA in CMOS-MEMS technology: This reconfigurable class-F PA has the same topology as the previous reconfigurable class-F PA and is intended for impedance load variation. However, this design incorporates MEMS analog variable capacitors instead of MOS variable capacitors with the intention to compare the PA with two different kinds of variable components. The MEMS capacitors are monolithically integrated in CMOS without the need for extra mask layer. The results of this PA are unavailable since it is under post processing. It is expected that this PA gives higher output power since MEMS switches have lower loss compared to MOS varactors.

#### **1.3** Thesis Outline

This doctoral dissertation is organized in seven chapters. The **first chapter** introduces the motivation, objective and outline of this thesis. **Chapters 2** to **7** contain the main contributions of this doctoral research as following:

- Chapter 2 provides state of the art of power amplifiers. It focuses on class-F PA structures, multi-band operation, and impedance reconfiguration. A literature review of class-F PAs in CMOS is also provided.

- **Chapter 3** gives a general overview of PA fundamentals, definitions and different classes of operation, going into detail on class-F PA.

- Chapter 4 new structure for class-F PA is proposed and two fixed single frequency class-F PAs are designed, fabricated and measured, one at 900 MHz and one at 1800 MHz.

- Chapter 5 focuses on the change in the frequency band. It describes and presents the topology for three different frequency-reconfigurable class-F PAs working at two frequencies, 900 MHz and 1800 MHz. The discrete PAs are designed and fabricated on a PCB which can switch between two frequencies independently. Measurement results and comparison with simulations are provided.

- Chapter 6 describes and presents a topology for impedance reconfiguration. The change in load impedance is done aiming Bluetooth application and the reconfigurable PA is designed and integrated in TSMS 0.18µ-CMOS technology.

- Chapter 7 describes and presents a topology for impedance reconfiguration. The change in load impedance is done aiming Bluetooth application and the reconfigurable PA is designed and integrated in TSMS 0.18µ-CMOS technology.

The capacitors in this design are CMOS-MEMS capacitors that are released by post-processing without the need for extra mask.

And finally, the document is concluded in **chapter 8**, summarizing the main results and contributions presented.

## Chapter 2 State of The Art

This chapter is dedicated to the state of the art in power amplifiers, with special focus on reconfigurability, both on frequency and on power.

2

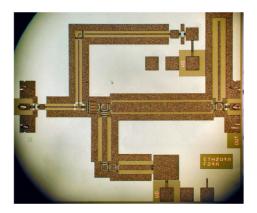

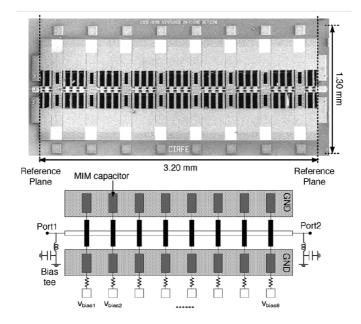

**Figure 2.1:** Chip microphotograph of the class-F PA MMIC using GaAs pHEMT presented in [9].

#### 2.1 High Efficiency Class-F PAs

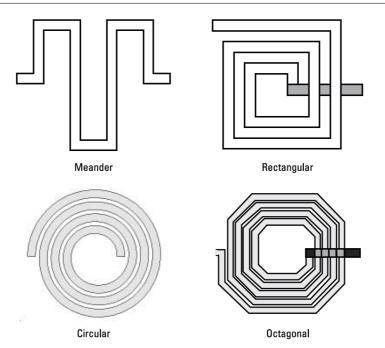

The choice of PA class and also design components depends on the operating frequency and the active device technology. At microwave frequencies, transmission line (TL) networks are preferred because implementing lumped element multi-resonators at these frequencies is difficult. Alternatively, for integration approaches, lumped elements should be used since TL networks consume a large area at this frequency. However, reaching up to millimeter-wave frequency, even integrated matching networks (MN) are preferred to be implemented using TL [9], not only because lumped elements exhibit important parasitics but also because TL can be very small due to the wavelength at these frequencies (Fig. 2.1).

Class-E and Class-F (and their inverse classes) have been the main core of high efficiency PAs in recent years. As explained before in introduction, class-E has a simple load network compared to class-F PA, but it suffers from high voltage swing at its drain, which can reach up to 3.6 times  $V_{DD}$  while this value is only 2 times  $V_{DD}$  for class-F PAs. This high voltage swing brings reliability concerns for low breakdown technologies. Therefore high breakdown technologies such as GaN and LDMOS can be used for both class-E and class-F PAs, but for implementation on low breakdown technologies such as CMOS a class-F PA is a better option. Therefore, in this thesis the focus has been on class-F PAs and with the aim of integration on CMOS technology, the following state of the art is presented. The literature review is focused on single frequency class-F PAs based on TL/discrete implementation and lumped element integration in CMOS technology. In section 2.2 multi-band class-F PAs are divided into three groups of concurrent multi-band PAs, Broadband PAs, and Frequency reconfigurable PAs. Since part of this thesis is devoted to PA design and load effect compensation using

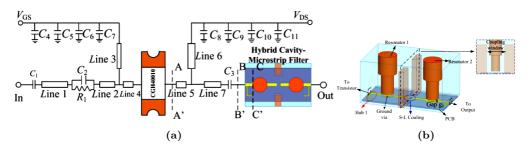

**Figure 2.2:** (a) A class-F PA incorporating hybrid cavity-microstrip band pass filter, and ((b)) 3D structure of Hybrid cavity-microstrip BPF configuration [10].

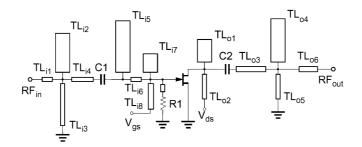

Figure 2.3: Schematic of the class-F PA presented in [11].

reconfigurable output matching network (OMN) using an impedance tuner, in section 2.3 impedance tuners and different structures have been explained.

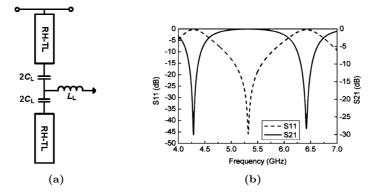

Class-F and its dual, inverse class-F (Class- $F^{-1}$ ), have been the focus of many works with high efficiency requirements resulting to many reported high efficiency class-F PAs with hybrid implementation in the literature [10–20]. The output filter of the class-F PA has also been proposed by using hybrid cavity-microstrip band-pass-filters (BPF) [10] bringing advantages such as heat sinking and easy integration with transistors or by generalized-Chebyshev bandpass filter [11] to work over a particular bandwidth. Both approaches are shown in Fig. 2.2 and Fig. 2.3 respectively. A full study of the two classes in terms of the optimum load impedance, output power, and efficiency according to the conduction angle are provided by [12] and [13].

As the RF front-end is continuing to grow in complexity, there is a great need to integrate the PAs with other devices on a single chip. Conventional PAs for GSM cell phones tend to be designed using separate chips made of GaAs pHEMT [9,21,22], SiGe bipolar transistors [23,24] or GaN MMIC [25] with additional discrete components that do not integrate well and increase cost notably. Nowadays, most handset components from baseband to receiving path are implemented in CMOS technology, except PA block.

To enable integration of all mobile circuitry in a single unit, the use of CMOS [26–34]

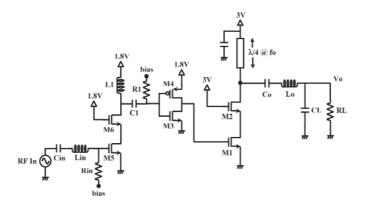

Figure 2.4: A lumped element class-F PA fully integrated in CMOS, using combination of thin and thick transistors to increase the power capability [29].

or BiCMOS technology [35,36] are ultimate goals because of their low cost and high level of integration. However, the PA is considered the most difficult block to implement in CMOS both as a component and as part of the final application due to inherent limiting technology characteristics from CMOS, to say: low breakdown voltage, the conductive substrate and the high sheet-resistance of the poly silicon. These characteristics pose a challenge that limits the output power, efficiency, linearity, and gain of the PA.

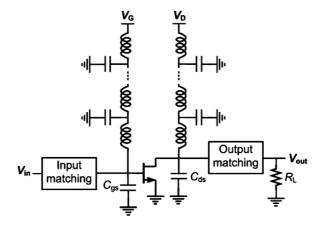

The low-resistivity of the substrate in CMOS technology is the main factor for having a low quality factor (Q) of on-chip inductors and transformers thus increasing the power losses and lowering the performance at higher operating frequencies [37]. An alternative approach is to implement low loss MNs using off-chip components such as discrete passives [26], transformers [38,39] or bond wires as high-Q inductors [26–28]. However, these are not fully integrated solutions and are not suitable for the purpose of fully monolithic handsets.

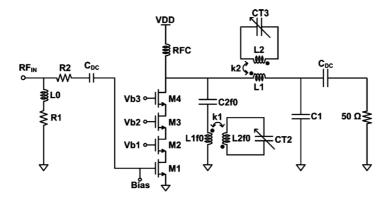

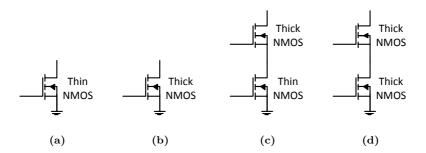

In integrated circuit (IC) design under millimeter-wave, lumped element MNs are inevitable for reducing the die area and cost. As CMOS works under low supply voltage, techniques such as power combining [40, 41] and stacked transistors [42] are used to increase the output power. To overcome the low breakdown voltage issue of CMOS transistors, a cascode structure using a mixture of thin and thick gate oxide transistors is presented in [29]. The combination of a thin and a thick transistor, shown in Fig. 2.4, enables the PA to achieve higher output power in deep sub-micron CMOS technology without having issues with breakdown voltage.

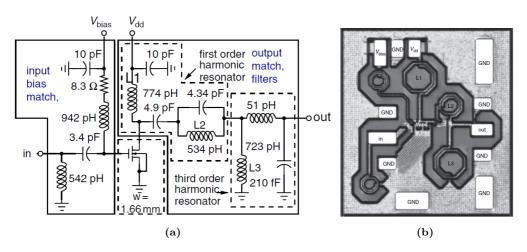

For better results of CMOS designs, layout parasitics, specifically the ones from metal interconnections, should be calculated in advance [30]. The circuit diagram of a fully integrated 5 - 6 GHz class-F PA in 0.18 $\mu$ m CMOS presented in [33] and its fabricated

**Figure 2.5:** ((a))A lumped element class-F PA for CMOS integration, and ((b)) fabricated circuit [33].

circuit is shown in Fig. 2.5.

#### 2.2 Multi-band Operation

The increasing demand of wireless devices for global coverage results in the need for systems to cover multiple frequency bands. To achieve the multi-band coverage, multi-band transceivers and multi-band PAs are needed. There are several works on multi-band operation in envelope tracking amplifiers [43,44] and Doherty amplifiers [39,45–47] where they incorporate high efficiency multi-band PAs in their configurations. A power amplifier is an important part of RF systems and it is desired that the PA could be adjusted according to the application and external conditions.

Achieving multi-band operation for highly efficient amplifier circuits such as class-F is more challenging than in linear ones because in highly efficient PAs not only correct fundamental load matching is needed, but also a proper harmonic impedance termination should be provided for each of the bands. In this section literature addressing that topic will be reviewed.

A conventional approach for multi-band operation is to use multi-branch designs which use multiple circuits in parallel, each of them designed at a single-frequency. However, due to the passive and active elements redundancy, this approach results in a large area and thus becomes more expensive. The occupied area is a critical requirement for PA either in the base station or handsets and it is desired to have as small area as possible, not only for cost reasons but also for miniaturization purposes. To avoid a costly and

Figure 2.6: Concurrent dual-band class-F PA proposed in [53].

large multi-branch design, there are three ways to realize multi-band systems, namely *Concurrent multi-band PAs, Broadband PAs, and Reconfigurable PAs.*

#### 2.2.1 Concurrent Multi-band PAs

Concurrent multi-band MNs achieve matching concurrently in multiple individual frequency bands without the use of neither switch nor reconfigurable elements. The reported high efficiency concurrent PAs are often dual band [48–50] or triple band [51] PAs. The methodology for a multi-band passive network is well explained by Colantonio in [52] where also a dual-band PA design that matches the impedance at fundamental frequency and harmonics is provided.

There are different multi-band class-F PAs reported using slightly different approaches [53–55]. Negra in [53] uses resonators at different frequencies to obtain concurrent dual-band and multi-harmonic operation. The termination network, shown in Fig. 2.6, requires 5 resonators. Nikandish in [54] proposes a harmonic termination ladder technique which can be used for termination of an arbitrary number of harmonics in single-band or concurrent multi-band class-F PAs, shown in Fig. 2.7. Kui Zhu in the other hand, in [55] proposes to simplify the termination network, at the expense of reduced generality.

The proposed class-F PA in [56], depicted in Fig. 2.8, operates at two frequencies simultaneously by using a combination of class-F mode for one band and inverse class-F mode for the other band. Although this is a very interesting approach, its main limitation is on the band-frequencies ratio, where a ratio of 1:1.5 is required.

Another dual-band class-F PA is implemented in [57] using composite right/left-handed transmission line (CRLH-TL). The illustrated approach in Fig. 2.9

Figure 2.7: High-efficiency class-F PAs proposed in [54].

Figure 2.8: Dual-band approach by combination of class-F mode for one band and inverse class-F mode for the other band proposed in [56].

shows an interesting characteristic as it can create dual-band harmonic trap which can be used in dual-band PAs.

#### 2.2.2 Broadband PAs

Broadband saturated power amplifiers have been reported as part of multi-band [44,58, 59] and wide-band [60] Envelope Tracking Transmitters and in Doherty amplifiers [45, 46]. A methodology for designing broadband PAs based on second-harmonic impedance manipulation is provided in [61].

A concept called continuous-mode PA often called class-J or recently continuous class-F [62–64] and continuous inverse class-F [65] enhances the bandwidth through the use of various voltage waveforms that deliver a constant RF performance across a desired frequency band. A broadband Doherty PA based on the continuous-mode technique has

**Figure 2.9:** composite right/left-handed transmission line (CRLH-TL): ((a)) Model, ((b)) S-parameter response [57].

also been reported [45]. The more detailed explanation of the continuous-mode approach can be read in [66,67].

#### 2.2.3 Frequency Reconfigurable PAs

Concurrent multi-band and broadband circuits show a reduced performance compared to the narrow-band ones. Alternatively, reconfigurable circuits achieve working at multiple frequency bands while maintaining a good performance of narrow-band circuits. So by developing a reconfigurable structure, one can take benefits of the narrow band performance and multi-band operation at the same time.

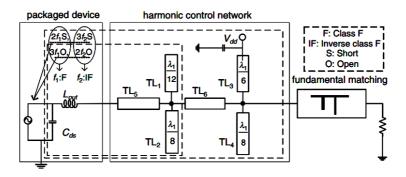

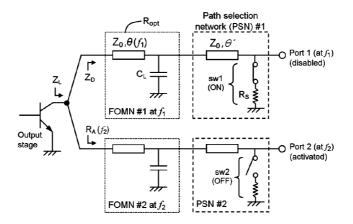

RF PAs with reconfigurable impedance tuning networks that are aimed for multi-band operation are presented in [40, 41, 68–71]. Frequency Reconfigurable PAs are designed often for dual or triple band operation. A design methodology for multi-band reconfigurable OMN has been presented in [72]. The proposed PA depicted in Fig. 2.10 consists of two sections, one for power reconfiguration and one for frequency reconfiguration, for practical handset applications.

There have been works toward integration of multi-band transmitter and therefore multi-band PAs in CMOS [68, 73–75] and BiCMOS technologies [76–79]. With both linearity and efficiency becoming a simultaneous requirement of the PAs, more works have been done in the linearization of the class-F PA at a single frequency of operation [38, 80–83] and at multi-band operation [68, 73, 84, 85].

In [73] a partial CMOS multi-band WCDMA/LTE PA incorporating class-F PA is reported. However, the good performance is subject to implement reconfiguration via external Integrated Passive Device (IPD) in a technology that overcomes CMOS passive structure limitations.

Figure 2.10: Fully integrated multi-band class-F PA presented in [72].

Figure 2.11: Fully integrated multi-band class-F PA presented in [68].

Recent works covered in section 2.1 show that the class-F PA can be integrated in CMOS technology, yet, among the limited number of reconfigurable class-F PAs of the current section, mostly a fully monolithic approach is not used. For example, Yin [84] proposes a class-F PA integrated in CMOS technology where the harmonic control is done off-chip, or Kim [85] incorporates off-chip OMN and feedback. One fully integrated multi-band class-F PA is presented by Sessou in [68]. The proposed class-F PA is illustrated in fig. 2.11, the reconfigurability is achieved through the use of integrated transformers and parallel capacitors.

#### 2.3 Impedance Tuners

Another condition that is interesting in RF systems is that the PA could be adjusted according to the application and external conditions such as load impedance variation.

Figure 2.12: Circuit implementation of a variable capacitor presented in [86].

When a user holds the mobile phone there is a strong interaction between hand, head, and antenna which causes a change in antenna impedance [3, 4] leading to a reduced performance. As the input and output impedances of transistors vary with operating condition, it is necessary to have a tunable impedance MN. Impedance tuners on this application lead to higher efficiency and wider bandwidth, therefore, they can be found in the reconfigurable amplifiers, smart telecommunication systems, millimeter-wave instrumentation, noise parameter measurements and load-pull measurements of active devices.

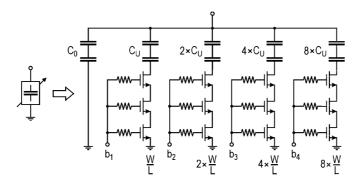

Impedance tuners [40, 40, 86–96] convert the impedance values at their output to a known impedance value at their input. The tunable MN for reconfigurable RF frontends presented in [97] includes a harmonic tuning, the feature demanded in high efficiency PA design. Some other topologies for adaptive impedance tuners are presented in [86, 98]. Other works that aimed for output power control use on-chip power combiners [99], bondwires and switched capacitors [100], or a combination of an adaptive power supply and impedance tuning using varactor diodes [101]. Techniques for adaptive control of impedance MNs which provide automatic compensation of antenna mismatch are presented in [102].

Many impedance tuners achieve tuning typically using MOS varactors [88], diodes [92, 96], switches [91], and more recently MEMS devices [7, 87, 90, 95]. Semiconductor varactors have acceptable impedance coverage and handle high power up to 30 dBm at frequencies up to 5 GHz. MEMS have the lowest insertion loss and a large tuning range at frequencies up to 40 GHz, but they need a high actuation voltage and have larger switching times. A circuit implementation of capacitor bank by means of transistors presented in [86] is shown in Fig. 2.12. Different structures for an impedance tuner from the literature are provided in Fig. 2.13 and Fig. 2.14.

RF-MEMS technology is particularly attractive for the tuner integration because of

Figure 2.13: Adaptive power amplifier using impedance tuner in its input and output MNs presented in [89].

Figure 2.14: Tunable load comprising transformer and MOS-varactor bank presented in [88].

Figure 2.15: Double stub impedance tuner with four MEMS switches  $(M_1-M_4)$  of a varactor presented in [90].

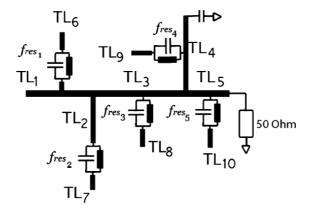

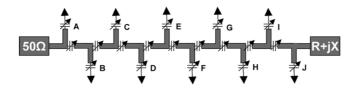

the available reconfigurable devices and the high performances they exhibit. A higher impedance span can be achieved by using stubs and the higher number of stubs results in a higher impedance coverage and bandwidth. Impedance tuning MNs have been demonstrated based on double-stub [95], quad-stub [90], up to ten-stub [96]. Examples are shown in Fig. 2.15 for double stub and Fig. 2.16 for ten stub impedance tuner.

Figure 2.16: Adaptive power amplifier using impedance tuner in its input and output MNs presented in [96].

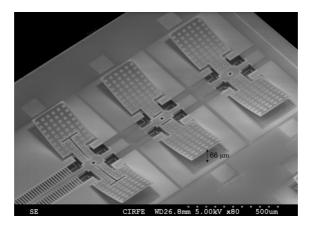

Figure 2.17: Scanning Electron Microscope (SEM) image of the fabricated CMOS RF MEMS switches in [103].

Many reconfigurable networks based on RF MEMS capacitive switches have been proposed. An example of MEMS switch fabricated in CMOS technology is shown in Fig. 2.17. An impedance tuner incorporating eight MEMS switches built in  $0.35\mu$ m CMOS technology is presented in Fig. 2.18.

Figure 2.18: (top) Photograph and (bottom) diagram of a tunable MEMS impedancematching network integrated in a standard  $0.35\mu$ m CMOS technology [104].

# B Chapter 3 Power Amplifier Fundamentals

This chapter provides RF power amplifier fundamentals. General metrics of amplifier such as power, gain, efficiency, linearity, and stability are explained. Different classes of power amplifiers consisting linear and switched mode amplifiers are briefly described with a more detail explanation on class-F power amplifiers.

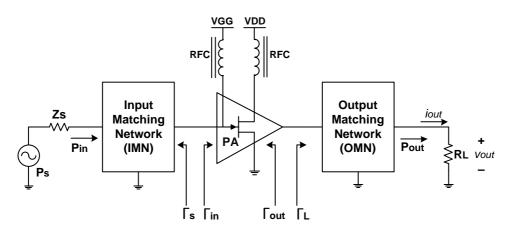

Figure 3.1: Basic power amplifier diagram.

## 3.1 Power Amplifier Metrics

The performance of amplifiers in this thesis are evaluated according to the metrics such as power, efficiency, and gain. Therefore it is important to define the evaluation metrics before studying the objective amplifier. For this purpose the basic circuit of Fig. 3.1 should be considered.

#### 3.1.1 Power

**Output Power**  $(P_{out})$ : One of the most important characteristics of a power amplifier is to be able to deliver a certain amount of power into a load. This power is called output power or delivered power and is usually measured in dBm or watt. There are two ways to measure the power, instantaneous power and average power, which are defined in equations (3.1) and (3.2) respectively.

$$P_{ins} = p(t) = v(t) \cdot i(t) \tag{3.1}$$

$$P_{avg} = \langle P \rangle = \frac{1}{T} \int_0^T p(t) dt \tag{3.2}$$

Output power delivered at fundamental frequency can be calculated from the phasors as the following:

$$P_{fund} = \frac{1}{2} \Re \left[ V_{out} |_{fund} \cdot I^*_{out} |_{fund} \right]$$

(3.3)

However, there are different definitions specified for it due to the behavior of amplifiers changing from linear to saturation region. Amplifier's output power is considered to have

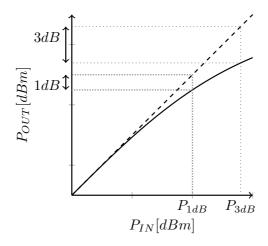

Figure 3.2:  $P_{1dB}$  and  $P_{3dB}$  definition.

a linear relation to its input power until  $P_{1dB}$ , which is the power at which output power drops 1 dB below its linear expected value. This is shown in Fig. 3.2. With the same idea,  $P_{3dB}$  is defined as the input power where the output power drops 3 dB below its linear expected value.  $P_{1dB}$  is used in literature as the point where amplifier starts to be nonlinear, while  $P_{3dB}$  is commonly used in practice to define final stage power in high power amplifiers<sup>1</sup>.

When the amplifier has to operate with modulated signals, also the *average* power is specified.

**DC Power**  $(P_{DC})$  is the power used from the power supply, in all DC terminals (for a typical MOSFET: drain and gate). By a proper implementation of bias feeding networks with RF chokes or  $\lambda/4$  TL, the power supply only has to provide the average current and average voltage. The DC power is calculated as in equation 3.4.

$$P_{DC}(W) = \langle V_{drain} \rangle \cdot \langle I_{drain} \rangle + \langle V_{gate} \rangle \cdot \langle I_{gate} \rangle$$

(3.4)

In the case of single stage PA like the PAs in this thesis, only one gate and one drain supply are considered. Gate DC power can be neglected, as it accounts lower than 0.1% of drain power<sup>2</sup>.

<sup>&</sup>lt;sup>1</sup>Using  $P_{1dB}$  instead of  $P_{3dB}$  would lead to bigger devices (barely twice) and lower efficiency.

$<sup>^{2}</sup>$ GaN transistors have a typical maximum gate current below 1 mA/mm and gate voltage of -2V to -3V, in contrast with a drain current capability of more than 100 mA/mm and a drain voltage higher than 28V.

Input Power  $(P_{in})$  is the RF power that is used to drive the amplifier. When using high gain linear amplifiers (gain stages typically) the input power can be neglected for efficiency calculation, as 20 dB gain means less than 1% of overall power. On the other hand, when considering high power amplifiers with a modest gain (final stages) input power is higher and it is important to consider this power, not only for efficiency calculations but also for driving requirements.

#### 3.1.2 Gain

Gain is the ratio between output power and input power in watts or their difference in dB:

$$G(dB) = 10\log_{10}\left(\frac{P_{out}(W)}{P_{in}(W)}\right) = P_{out}(dBm) - P_{in}(dBm)$$

(3.5)

Gain is constant at low input power and as the input power is increased, the amplifier starts compressing and gain starts decreasing. Hence two gain calculations can be made, and they are used differently.

**Small signal gain** corresponds to  $|S_{21}|^2$  parameter, and it is often used in signal amplifiers such as Low Noise Amplifiers (LNA) and receiving sections. As it is measured under very low input power (deep back-off) the behavior is linear, and hence cannot be extrapolated for high power amplifiers where compression effects and non-linear parasitics play a key role in amplifier's behavior.

Large signal gain  $(G_p)$  is obtained with the PA working at higher power, where nonlinear effects such as non-linear capacitances and amplifier saturation take place. At low power levels, the gain is linear, but as power increases the gain decreases. Due to the non-linear behavior, simulation of  $G_p$  should be done by Harmonic Balance.

#### 3.1.3 Efficiency

The efficiency of the PA defines how well it can deliver the required output power with minimum power dissipated in the device. So ideally it is desired to deliver all the supply power (DC power) and input power to the output. There are three different ways to define amplifier efficiency:

**Drain Efficiency**  $(\eta_D, \mathbf{DE})$  measures the efficiency of the amplifier in converting DC power into output RF. It neglects the power which is lost by driving the amplifier.

$$\eta_D = \frac{P_{RFout}(W)}{P_{DC}(W)} \tag{3.6}$$

**Power Added Efficiency (PAE)** measures amplifier efficiency considering DC power and also the input power used to drive it. Note that with high gain amplifiers (G > 20dB) the difference between  $\eta_D$  and PAE is smaller than 1%, but for a modest gain of 10 dB, the difference reaches up to 10%.

$$PAE(\%) = 100 \cdot \frac{P_{RFout}(W) - P_{RFin}(W)}{P_{DC_{tot}}(W)} = \eta_D \cdot \left(1 - \frac{1}{G}\right)$$

(3.7)

**Overall Efficiency (OE)** measures overall amplifier efficiency. It is more flexible compared to PAE because it can incorporate other supporting circuits, such as voltage regulators or digital pre-distortion (DPD).

$$\eta_{O} = \frac{P_{out}(W)}{P_{DC}(W) + P_{in}(W)} = \frac{P_{out}(W)}{\sum_{k \neq out} P_{k}(W)}$$

(3.8)

#### 3.1.4 Stability

Stability is one of the most important factors in the PA that should be addressed from the early stage of the design. Stability issues occur in amplifiers due to different reasons. Physically, an amplifier is unstable when it has positive feedback, or in other words, when input or output resistances are negative ( $\Gamma_{in} > 1$  or  $\Gamma_{out} > 1$ ) [105]. Oscillation can happen at low frequency or at RF frequency. If PA is unstable at low frequency this usually can be fixed by choosing a proper decoupling capacitor in the supply of the PA, for both drain and gate. However, the RF instability comes from the circuit design, therefore making it stable means changing the input and output matching networks structure and components.

Typically, the Rollett's stability factor (K), defined by equation 3.9, is used to evaluate amplifier stability. By sweeping the input signal from DC to higher frequencies, and plotting the K factor, the stability of the device can be determined.

$$\begin{cases} K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|^2} \\ \Delta = |S_{11}S_{11} - S_{12}S_{21}| \end{cases}$$

(3.9)

There is one stability circle for  $\Gamma_L$  called output stability circle and one for  $\Gamma_S$  called input stability circle. If  $|S_{11}| < 1$  and  $|S_{22}| < 1$ , then the area which includes the center of the Smith Chart is stable. The  $\mu$ -factor is the distance from the center of the Smith Chart to the nearest point of instability on the stability circles. The  $\mu$ -factor of the load  $(\mu')$  and source ( $\mu$ )are respectively derived from equations 3.10 and 3.11.

$$\mu' = \frac{1 - |S_{11}|^2}{|S_{22} - S_{11} \triangle| + |S_{12} S_{21}|}$$

(3.10)

$$\mu = \frac{1 - |S_{22}|^2}{|S_{11} - S_{22} \triangle| + |S_{21} S_{12}|}$$

(3.11)

Unconditional stability: For the amplifier to be unconditionally stable it should meet  $|\Gamma_{in}| < 1$  and  $|\Gamma_{out}| < 1$  for all possible combination of source and load impedances and frequencies. In unilateral amplifiers  $(S_{12} = 0)$  fulfilling only  $|S_{11}| < 1$  and  $|S_{22}| < 1$  signify unconditional stability. For non-unilateral amplifiers, K > 1 and  $|\Delta| < 1$  for all range of frequencies and all impedance values is the way to determine unconditionally stable amplifier. However the value of k-factor can not be used directly on the degree of stability, But  $\mu'$  and  $\mu$  have a direct relationship with how stable is the circuit.  $\mu' > 1$  and  $\mu > 1$  is an indication of unconditional stability and the higher value of  $\mu'$  and  $\mu$  means a more stable circuit.

**Conditional stability:** If the above conditions are met for only a certain range of frequencies or impedance values, the amplifier is called *conditionally stable*. A conditionally stable amplifier can become unstable by interactions of the bias network, and careful design is mandatory in those cases.

Stability improvement techniques: Typically when the PA is unstable, it needs a more lossy matching network in order to become stable which lowers the gain and efficiency of the amplifier. Stability can be improved by adding series or shunt resistor in the input of the active device. Stability circles that are on the left side of Smith Chart suggest stability improvement by series resistance, while stability circles placed on the right side of Smith Chart suggest adding shunt resistance. Stability circles on the top or bottom are best solved with both a series and shunt resistance. In integrated designs, the use of lossy substrate lead to components (inductors) with lower Q and hence improved stability.

# 3.2 Power Amplifier Classes and Topologies

An RF power amplifier can be realized in numerous different ways, depending on the topology and biasing conditions. In the following, the different amplifier classes [8] are summarized.

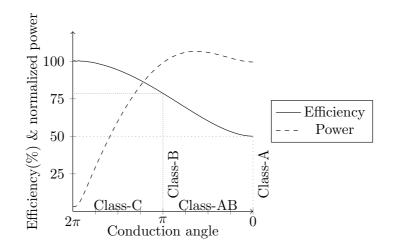

#### 3.2.1 Linear PAs: Classes A, B, AB, and C

Consider the general amplifier of Fig. 3.3. In the case of linear amplifiers, the active device is used as a current controlled source. The class of operation is defined by the biasing point, which states the quiescent current  $(I_{dq})$ .

Figure 3.3: General Amplifier Scheme.

**Class-A** power amplifier places the bias point in the middle of the curve, at  $I_{max}/2$ . That ensures that full voltage excursion is available without clipping. Therefore, linearity is excellent, only posing issues at very high power when clipping occurs. However, as the transistor is biased in middle point ( $2\pi$  conduction angle) the efficiency is limited to 50%.

**Class-B** power amplifier places the bias point exactly at zero, limiting voltage excursion to half period. The output signal is recovered filtering the fundamental. Due to the conducting angle of  $\pi$ , efficiency reaches up to 78.5% ( $\pi/4$ ), boosting more than 50% efficiency of class-A. However, as conduction angle is  $\pi$ , the gain is 3 dB lower than in Class-A.

**Class-AB** power amplifier places the bias point at some point between zero and  $I_{max}/2$ , leading to a performance between class-A and class-B. The exact bias point will determine

Figure 3.4: Efficiency depending on conduction angle.

the behavior of the amplifier. However, due to the change in operating mode from class-A to class-B, it exhibits a soft gain compression characteristic in the transition, which is not desired to preserve linearity. Biasing in deep class-AB is referred when the amplifier is biased with  $I_{dq}$  about 5% to 10% of  $I_{max}$ .

**Class-C** power amplifier places the bias point at cut-off, reducing conduction angle below  $\pi$ . However, the cost of a reduced conduction angle is a lower usage of the transistor, lower gain, and lower output power, depending on how deep in class-C the amplifier is operated. As conduction angle is completely dependent on the signal amplitude, the gain is also non-constant.

#### 3.2.2 Switching PAs: Classes D, E, and F

In order to decrease power dissipation in the amplifier, the overlap of voltage and current in the transistor should be minimal. One straightforward method for achieving that is to use the transistor as a switch instead of as a current controlled source. By operating the transistor either in cut-off (open circuit) or triode region (short circuit), either current or voltage are zero respectively.

**Class-D** power amplifiers are composed of two switches, creating a square voltage. In an ideal case, as depicted in Fig. 3.5, switches create a square-wave voltage, which contains the fundamental along with the odd harmonics. Then a filter tuned at fundamental removes other harmonic components, providing a high efficiency amplification.

Figure 3.5: Class-D PA basic scheme.

However, in real applications, there are several non-idealities that limit its performance. For instance: transistor output capacitance is charged and discharged every switching cycle. To overcome that limitation, Zero Voltage Switching (ZVS) should be adopted. A straightforward way of achieving that is by swapping voltage and current waveforms, implementing what is called current mode class-D (CMCD) [106]. Nonetheless, even in current mode operation, several non-idealities still are important and the topology is used up to UHF frequencies.

**Class-E** power amplifier (Fig. 3.6) also uses the transistor as a switch, but in their output shaping network design they include the transistor output capacitance. The shaping network not only provides correct voltage shaping but also creates ZVS conditions and zero current turn-on. Compared with Class-D, it has lower switching loss but higher conduction loss due to the increased current in the active device. However, its main drawback is the high drain voltage and lower transistor utilization factor compared with other classes.

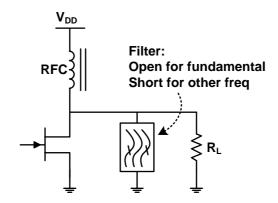

**Class-F** power amplifier contains certain harmonic terminations in the active device's load impedance [107]. It uses an infinite number of resonators in the output matching network (OMN) and creates drain voltage and current waveform with no overlap between them, resulting in low power consumption and high efficiency. If the current and voltage shapes are swapped, an inverse class-F (class- $F^{-1}$ ) is created. Implementing a class-F or inverse class-F with a GaN transistor results to a higher output power level compared to class-E. However, a complex load network is needed for a proper harmonic termination in class-F PA, increasing the complexity of the design. Class-F amplifiers are explained in detail in section 3.3.

Figure 3.6: Class-E amplifier basic scheme.

However, it should be pointed that there is a limitation on the number of harmonics that can be tuned from device output. Not only due to the increasing complexity as harmonics are added, but also due to parasitic capacitance on active device output [8]. A large capacitance will become a short circuit at higher harmonic orders at microwave operating frequencies. Therefore at 900 MHz and higher frequencies, device technologies such as Gallium Arsenide (GaAs) or Gallium Nitride (GaN) are required in order to make a full harmonic tuned Class-F.

### 3.3 The Class-F Power Amplifier Basics

Previously the different classes of amplifiers have been introduced. In current section, the operation and design of Class-F PAs will be addressed in detail.

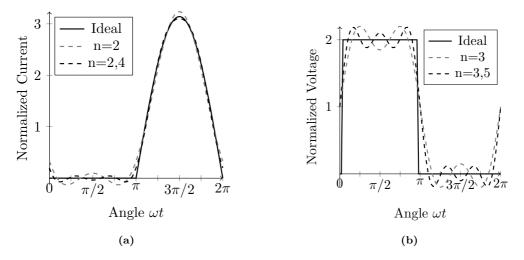

An ideal class-F PA should have no overlap between the drain voltage and current. This is achieved by having a square drain voltage and half-sinusoidal current as depicted in Fig. 3.7 and described by equations 3.12 [108].

$$\omega t \Big|_{0}^{\pi} \begin{cases} v(\omega t) = 2V_{cc} \\ i(\omega t) = 0 \end{cases} \quad \omega t \Big|_{\pi}^{2\pi} \begin{cases} v(\omega t) = 0 \\ i(\omega t) = 2I_{R}\sin(\omega t) \end{cases}$$

(3.12)

Expanding the waveforms in their general Fourier terms leads to equation 3.13. It can be seen that with an unlimited number of harmonic tuners, ideal waveforms and consequently 100% efficiency will be obtained. However, that is not feasible in practice since only a limited number of harmonics can be tuned effectively, lowering the maximum achievable efficiency. Studies show that termination of harmonics higher than  $3^{rd}$  order has little effect on efficiency improvement and it increases the complexity of the circuit

Figure 3.7: Normalized class-F drain waveform for ideal case and number of harmonics taken into account: (a) Current, and (b) Voltage.

[109].

$$\begin{cases} v(\omega t) = V_{cc} + V_1 \sin(\omega t) + \sum_{n=3,5,7...}^{\infty} V_n \sin(n\omega t) \\ i(\omega t) = I_0 - I_1 \sin(\omega t) + \sum_{n=2,4,6...}^{\infty} I_n \cos(n\omega t) \end{cases}$$

(3.13)

#### 3.3.1 Maximally Flat Waveforms

One of the different methods to achieve Class-F operation is by the usage of maximally flat waveforms<sup>3</sup>. The goal of this approach [108] is to maximize efficiency by ensuring that voltage is as low as possible during the current peak at  $\omega t = 3\pi/2$ . To achieve Class-F operation by the usage of maximally flat waveforms and to maximize efficiency, the voltage should be as low as possible during the current peak at  $\omega t = 3\pi/2$ . The implementation of maximally flat voltage requires the even-order derivatives of voltage to be zero at  $\omega t = 3\pi/2$ . The general flat voltage equation 3.14 allows extracting a set of equations depending on the number of harmonics N considered (3, 5, 7, ...). Similar process can be carried out for currents, at  $\omega t = \pi/2$  for even harmonics, leading to

$<sup>^{3}</sup>$ The term "Maximally Flat Waveforms" is used by Raab in [110], later on by Grevenikov and Sokal in [108] and many other academic sources refer to this concept with the same term. Although there is not wave in the drain of transistor, which makes using the term "Waveform" partially incorrect, in this thesis it has been used the same as used by the authors to preserve the Nomenclature and consistency with academic texts.

| Current Harmonics | Voltage Harmonic |         |             |                 |                         |

|-------------------|------------------|---------|-------------|-----------------|-------------------------|

|                   | 1                | $1,\!3$ | $1,\!3,\!5$ | $1,\!3,\!5,\!7$ | $1,\!3,\!5,\!,\!\infty$ |

| 1                 | 0.500            | 0.563   | 0.586       | 0.598           | 0.637                   |

| 1,2               | 0.667            | 0.750   | 0.781       | 0.798           | 0.849                   |

| 1,2,4             | 0.711            | 0.800   | 0.833       | 0.851           | 0.905                   |

| 1,2,4,6           | 0.731            | 0.823   | 0.857       | 0.875           | 0.931                   |

| $1,2,4,,\infty$   | 0.785            | 0.884   | 0.920       | 0.940           | 1.000                   |

**Table 3.1:** Performance of class-F PA for various combinations of harmonics considered in current and voltage [108, 110].

equation 3.15.

$$\forall_{n=2,4,\dots}^{N-1} \left\{ \frac{d^n v}{d(\omega t)^n} = (-1)^{n/2} \left( \sum_{m=1,3,5\dots}^N m^n V_m \sin(m\omega t) \right) = 0$$

(3.14)

$$\forall_{n=2,4,\dots}^{N} \left\{ \frac{d^{n}i}{d(\omega t)^{n}} = (-1)^{\frac{n-1}{2}} \left( I_{1}\sin(\omega t) + \sum_{m=2,4,6\dots}^{N} m^{n}I_{m}\cos(m\omega t) \right) = 0 \quad (3.15)$$

The system of equations comprised by both equations 3.14 and 3.15 should be solved, obtaining the different voltages and currents needed. As a result, a fast analysis can be done to obtain the impact of the number of ternubared harmonics on the drain efficiency, provided in table 3.1 [108, 110].

So the summary is that from the voltage and current shape description in equation 3.13, it can be observed that voltage has all of the odd harmonics while current has all of the even harmonics. By preserving the odd harmonics in the drain voltage and preserving even harmonics in drain current, an ideal square voltage and half-sine current waveform are shaped respectively. Having them maximally flat with no overlap between them leads to the best compromise between efficiency and output power. This is the basic requirement of the class-F OMN, a harmonically matched network that provides open circuit (OC) at odd harmonic and short circuit (SC) at even harmonics. In the following, the conventional practical implementation of a class-F PA is explained.

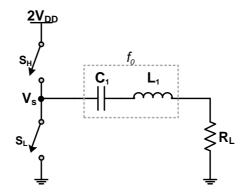

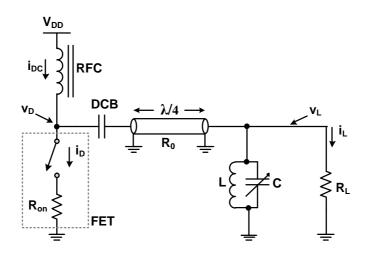

#### 3.3.2 Quarter-wave Transmission Line Class-F

A conventional way to implement class-F PA (and preferred for high frequencies) is depicted in Fig. 3.8. Such implementation, provided by Raab in 1976 [111], uses a  $\lambda/4$ TL and an LC tank in parallel to the load. The purpose of the LC tank is to provide a low impedance at all harmonics except fundamental. The  $\lambda/4$  TL acts as an impedance converter, inverting the impedance at the odd harmonics, where  $L = \lambda/4 + n\lambda/2$  and propagating the low impedance at even harmonics where  $L = n\lambda/2$ .

Figure 3.8: Class-F PA implementation using a  $\lambda/4$  TL.

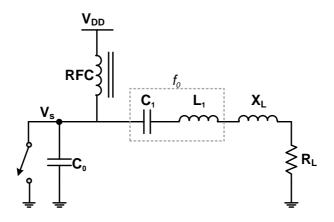

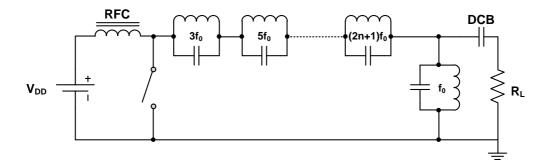

#### 3.3.3 Multi-Harmonic Resonator Implementation of Class-F

Another method to achieve class-F operation is illustrated in Fig. 3.9, showing the implementation of series of LC tank circuits, each tuned at a different odd harmonic, providing a high impedance in the drain (hence low current). To ensure full current at even harmonics, a low output impedance is provided via a capacitor, which is shunted with an inductor at the fundamental. This methodology was widely used with vacuum tubes [108,111].

Figure 3.9: General class-F PA implementation using multi-harmonic resonators.

A conventional class-F PA with limited harmonic resonator proposed by Raab [110]

Figure 3.10: Conventional Class-F PA OMN configurations using multi-harmonic resonators of  $3^{rd}$  order [110].

is shown in Fig. 3.10, where only  $3^{rd}$  order harmonics is considered in the OMN. This reference provides calculations for predicting the voltage and current shape depending on the different combination of harmonics. It assumes an ideal LC filter and ideal current source as the active device with no on-resistance nor output capacitance. It can be seen that by increasing the number of harmonics to infinite an ideal square shape and an ideal half-sine shape will be generated.

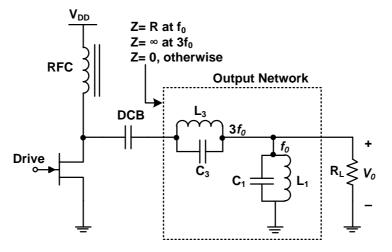

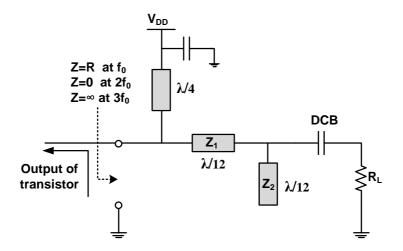

#### 3.3.4 Fully Transmission Line Implementation of Class-F

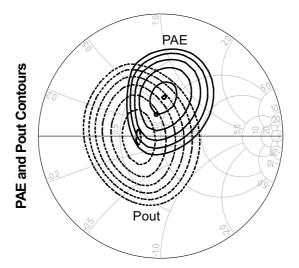

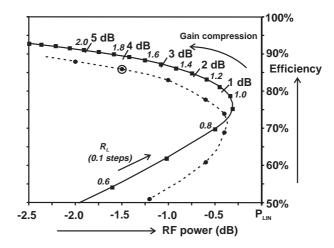

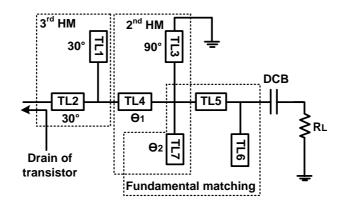

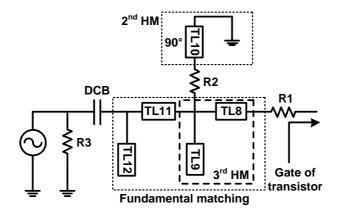

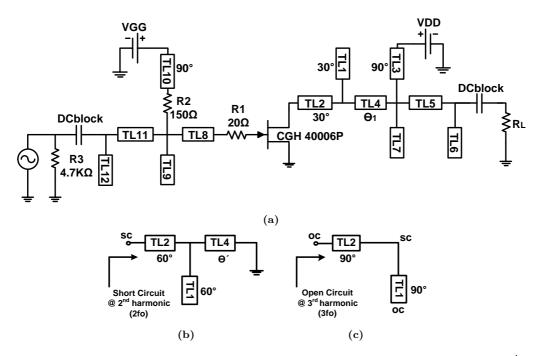

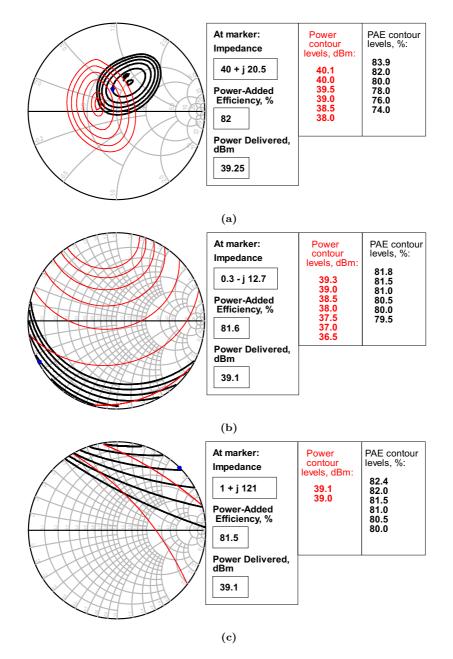

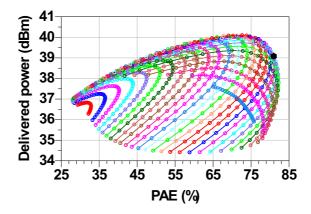

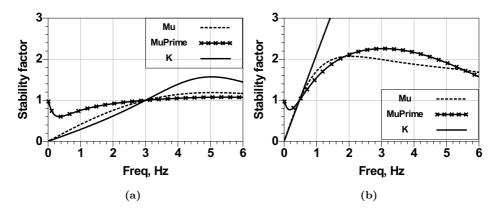

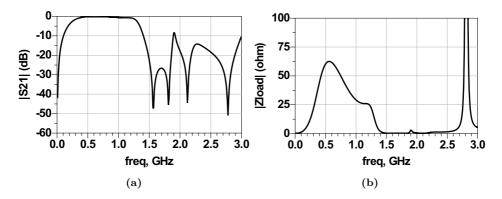

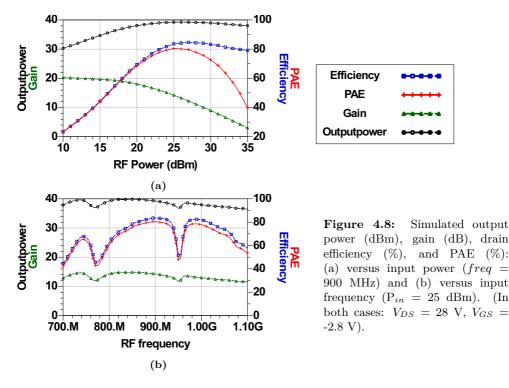

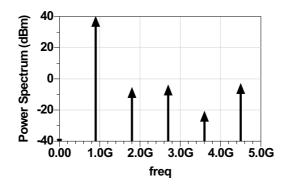

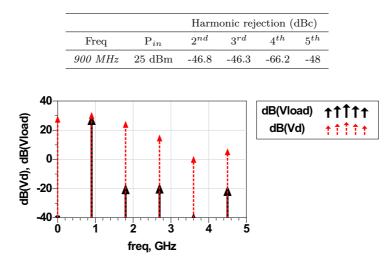

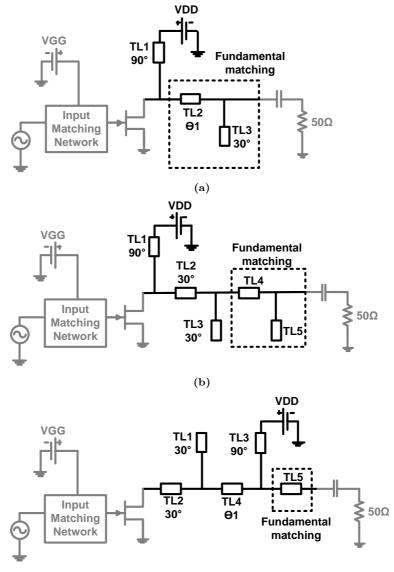

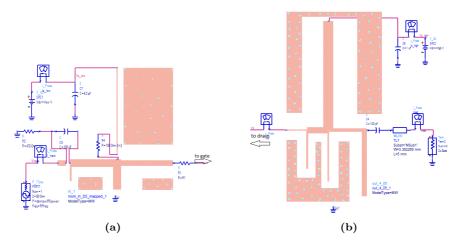

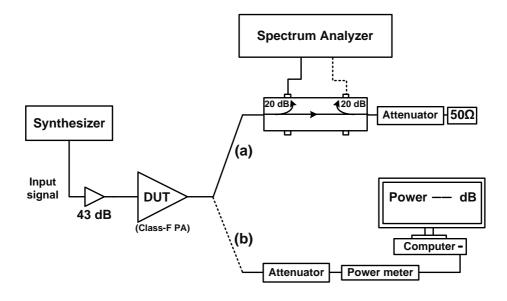

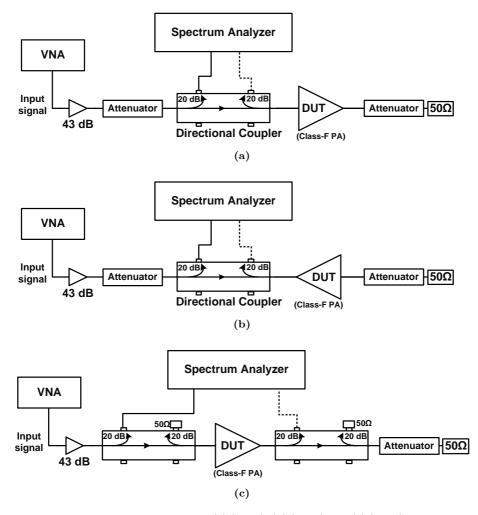

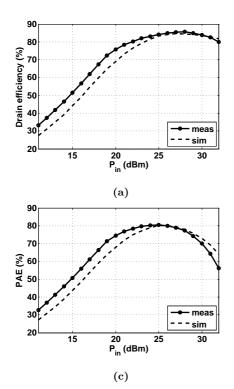

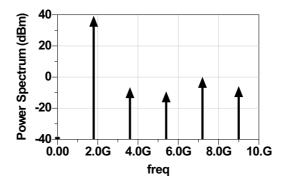

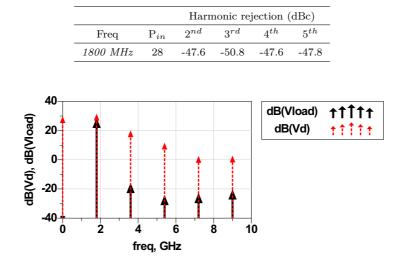

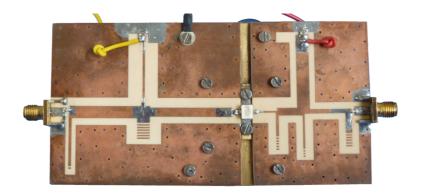

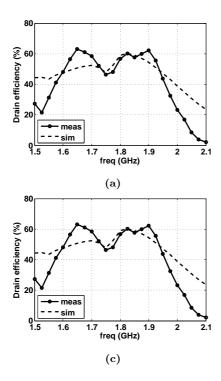

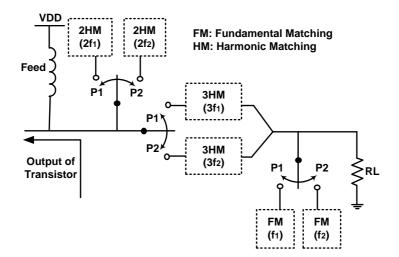

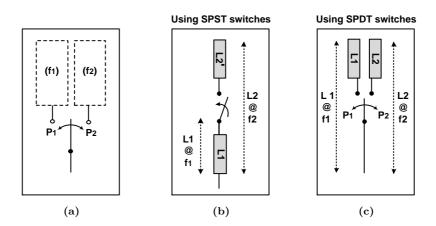

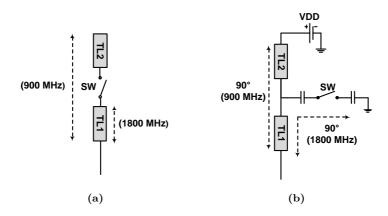

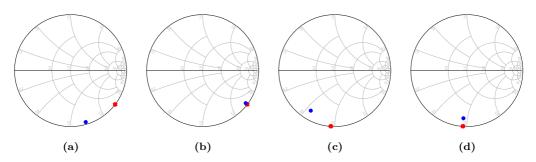

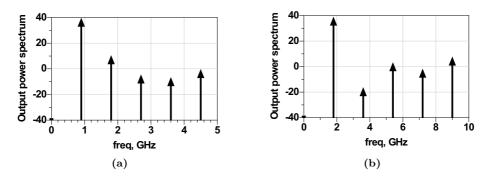

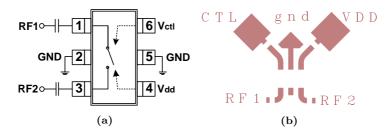

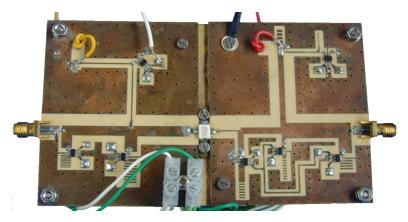

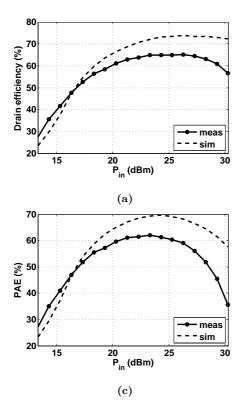

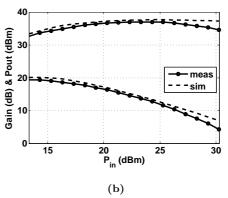

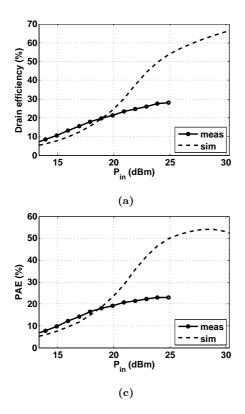

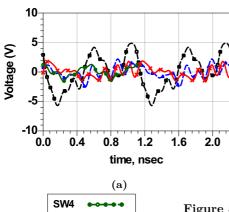

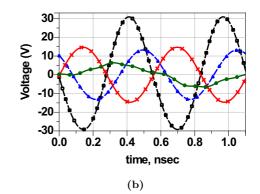

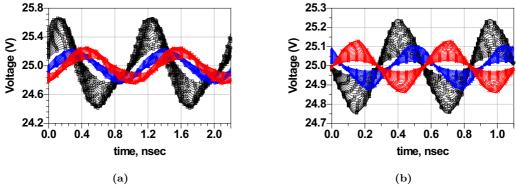

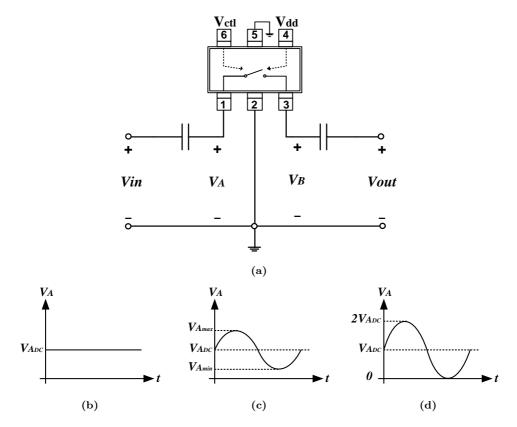

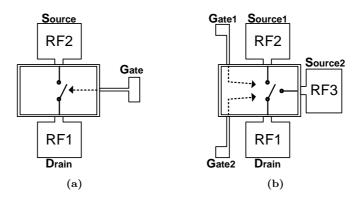

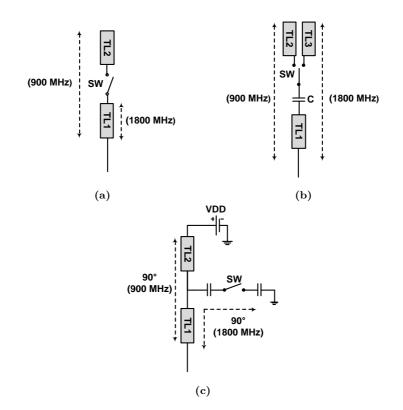

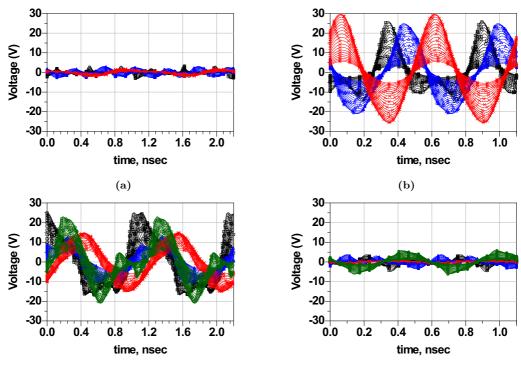

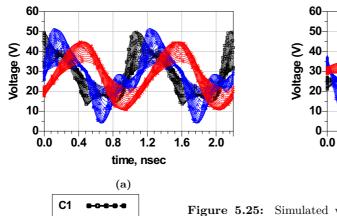

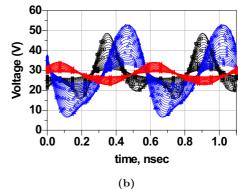

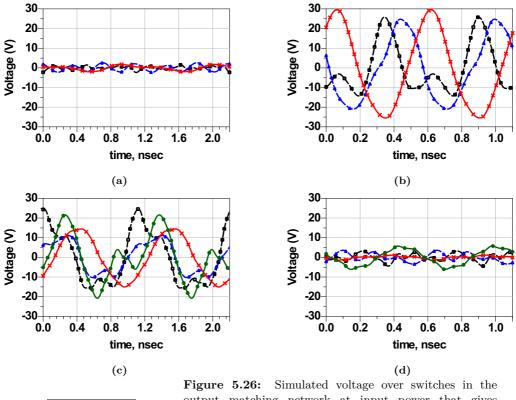

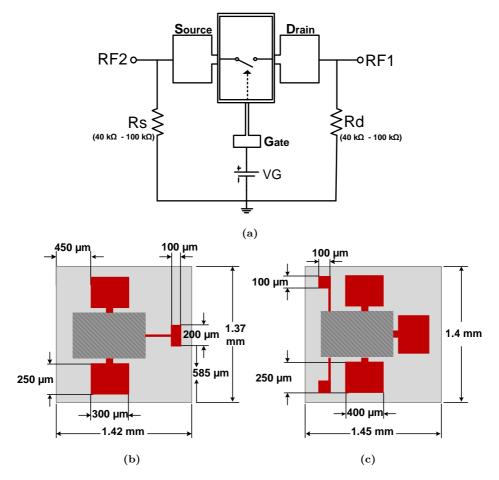

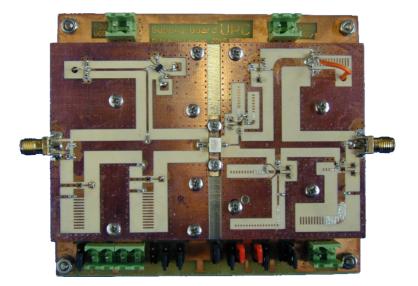

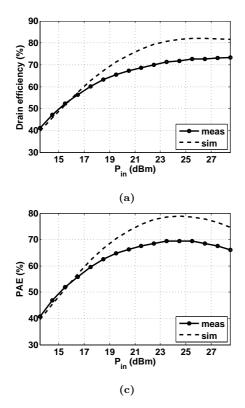

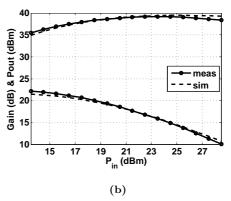

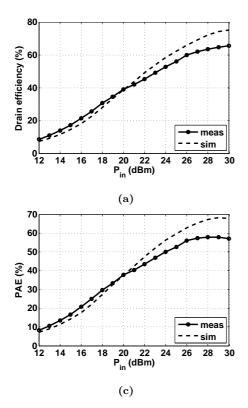

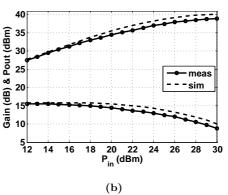

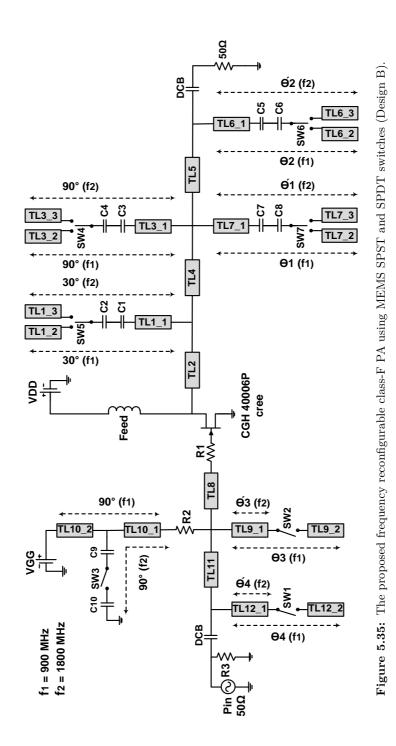

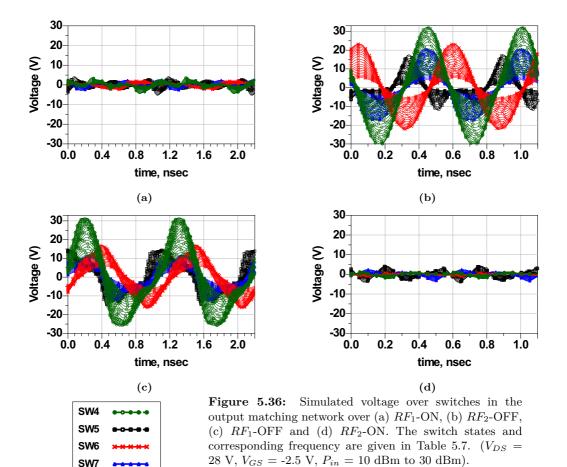

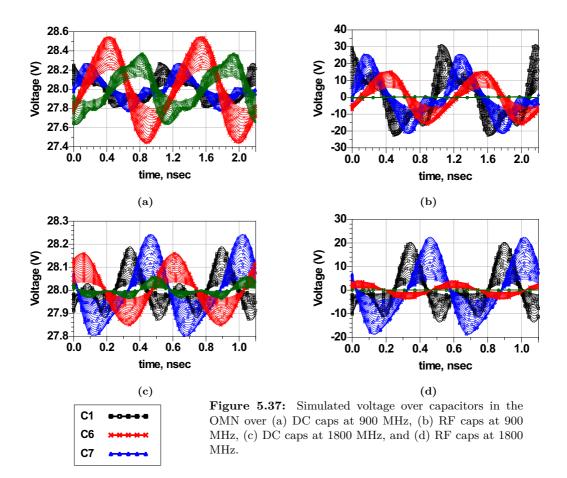

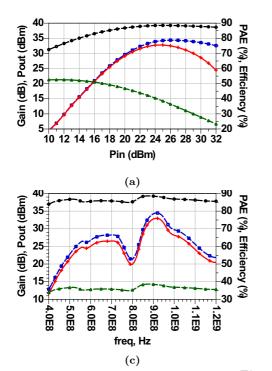

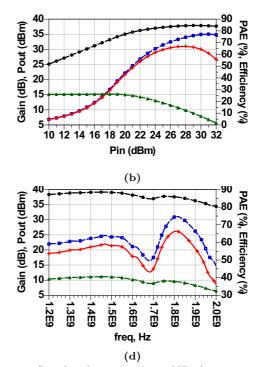

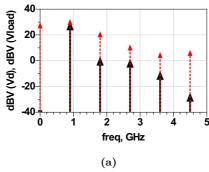

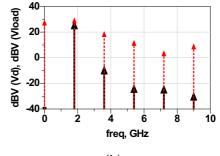

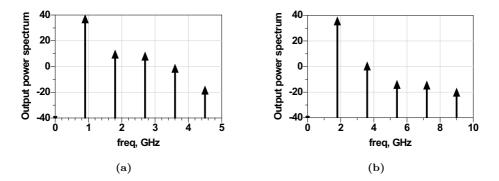

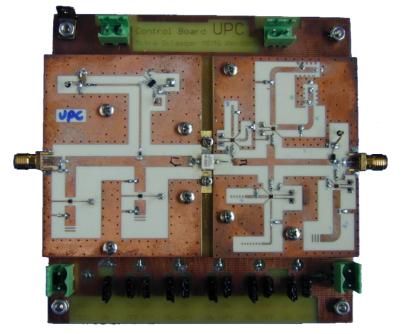

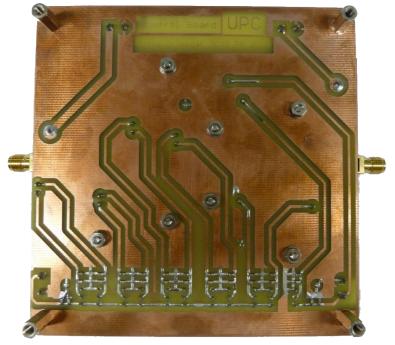

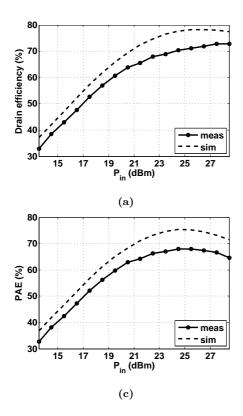

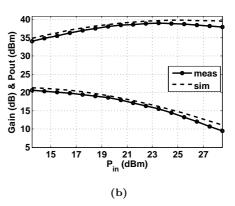

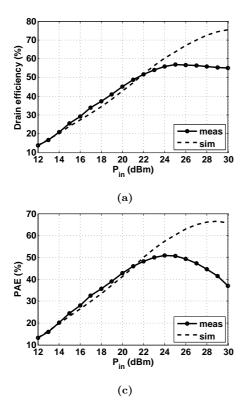

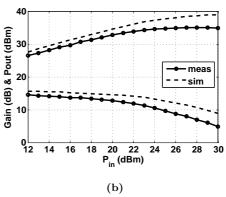

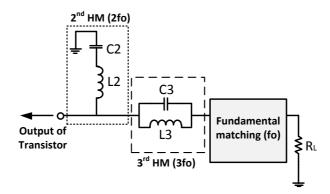

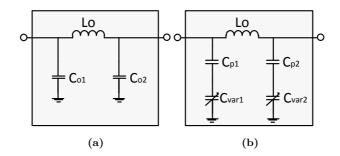

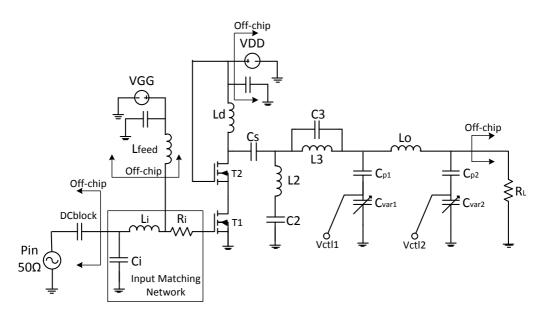

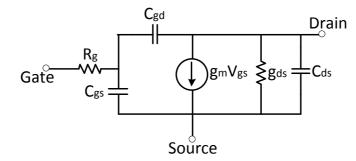

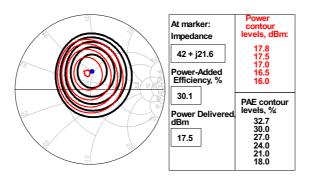

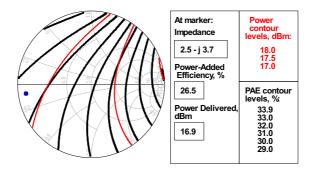

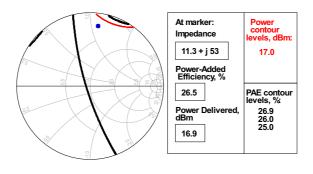

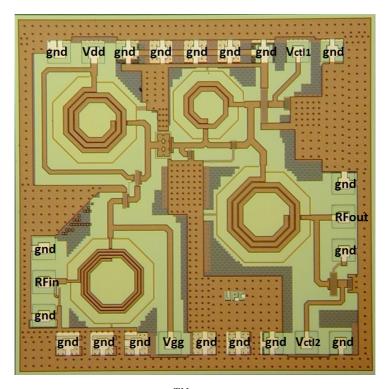

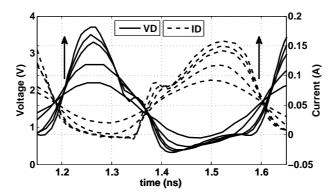

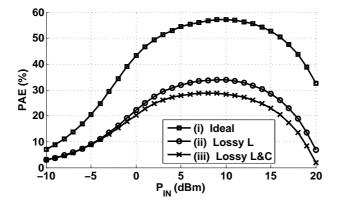

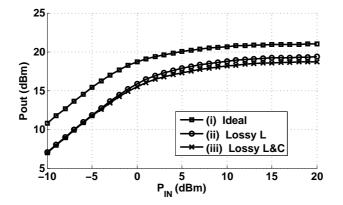

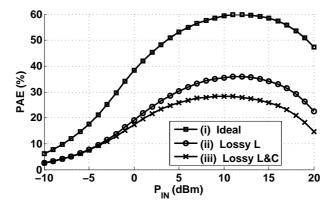

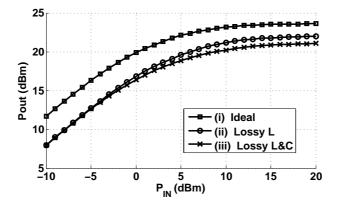

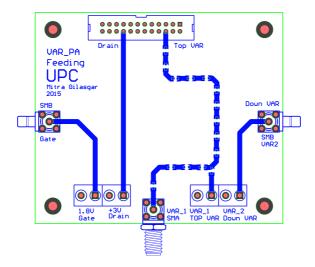

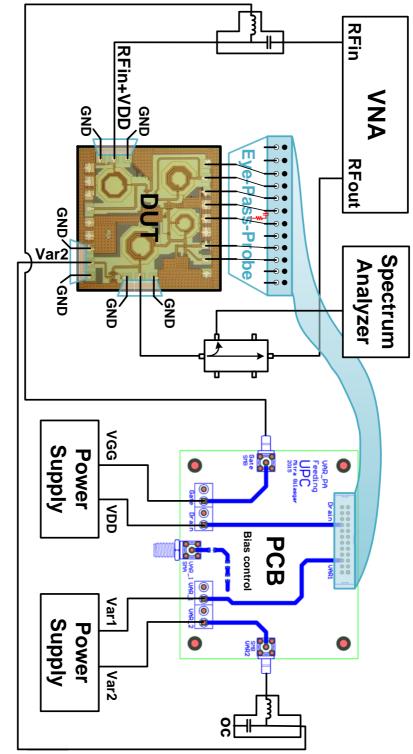

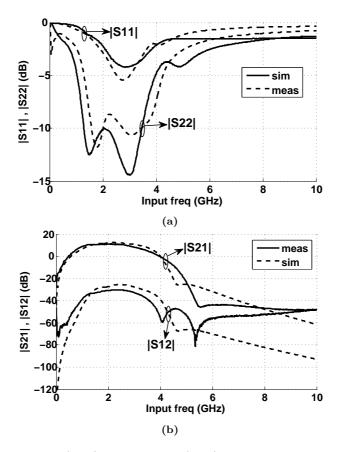

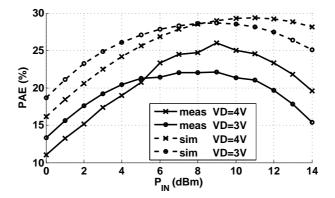

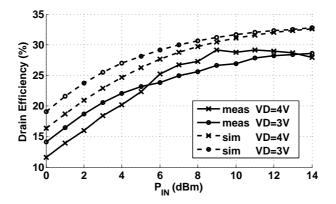

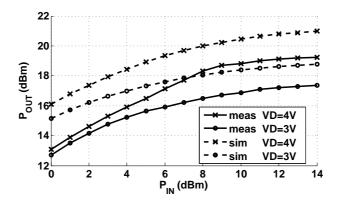

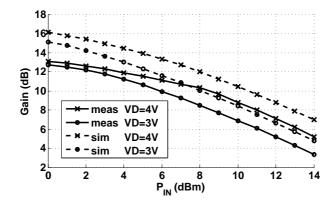

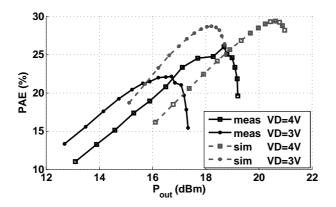

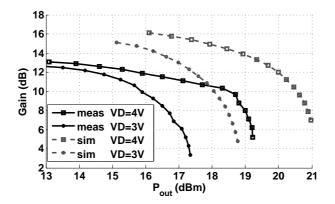

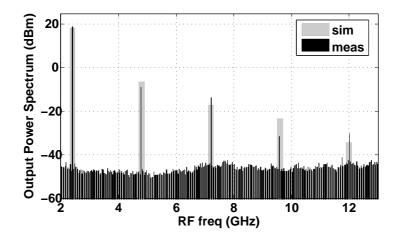

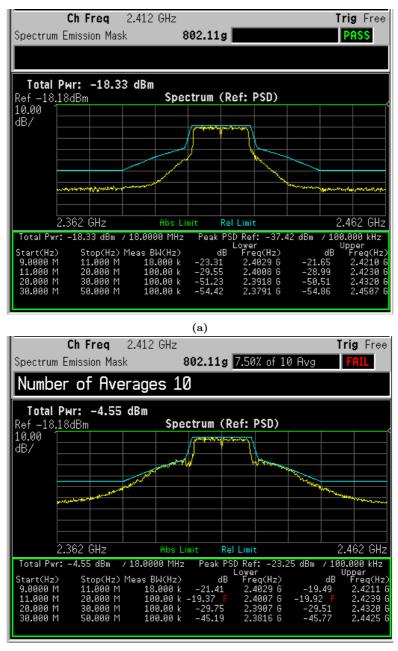

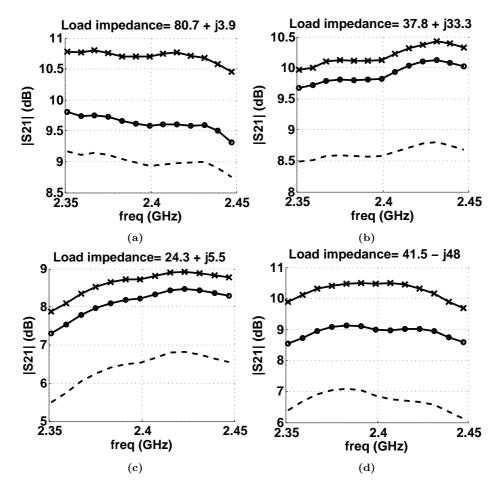

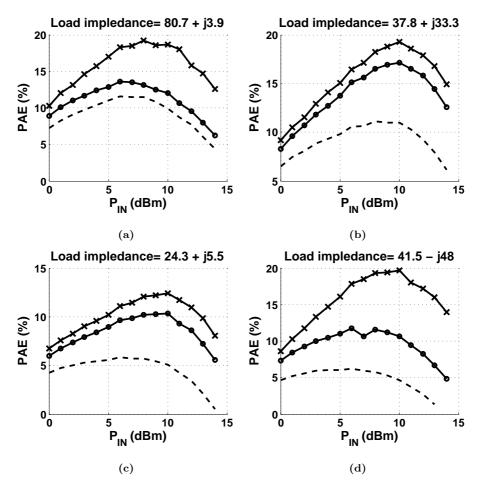

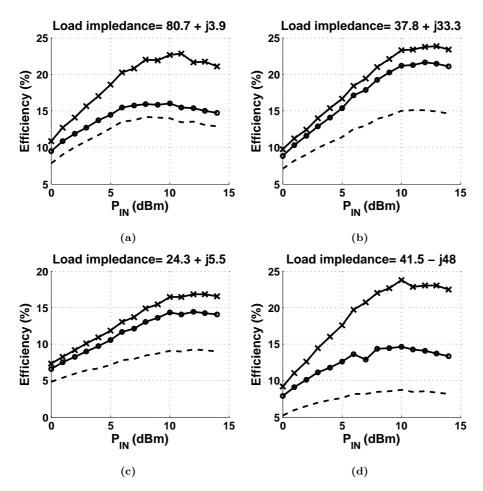

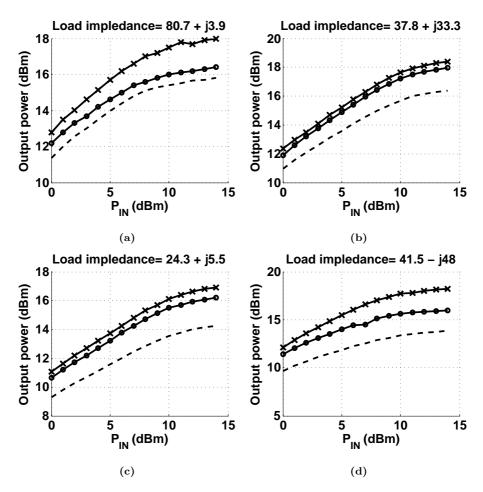

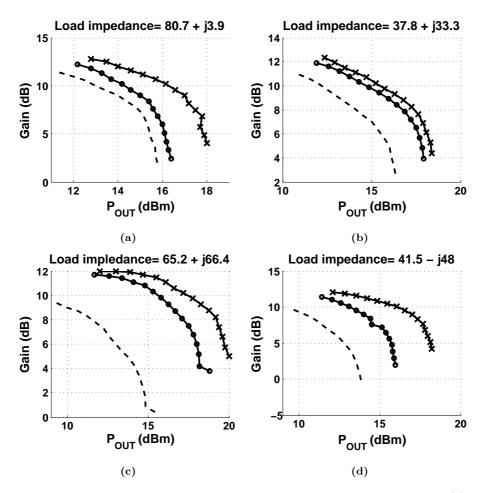

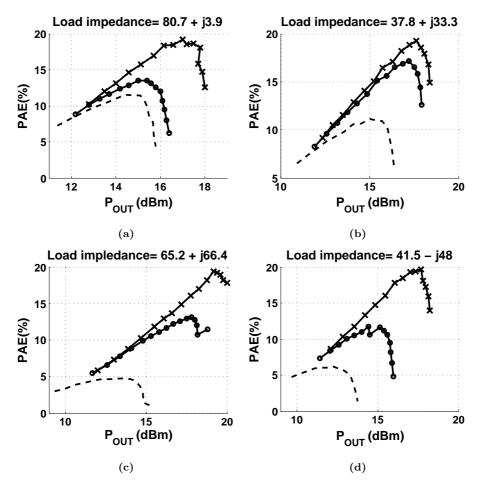

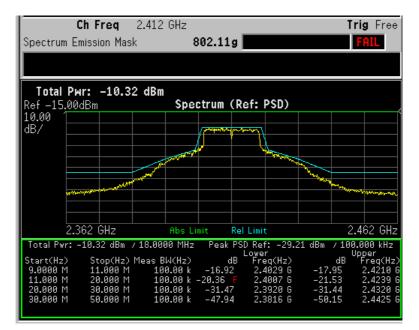

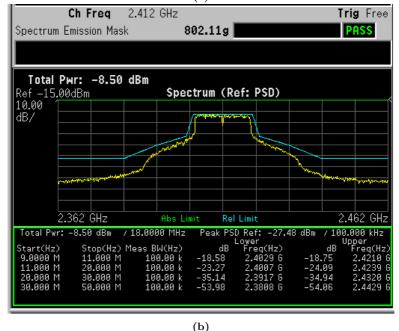

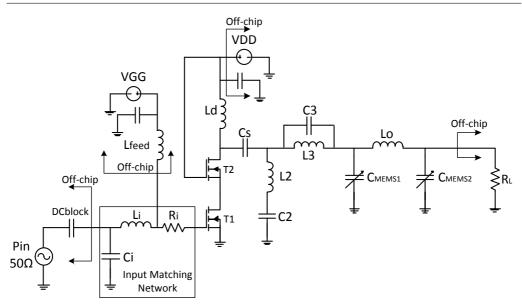

Transmission lines have unique properties that give them the advantage over lumped elements. The periodic structure of the TL reduces the complexity in the design of harmonic tuning and helps to achieve the required behavior of a class-F PA at multiple resonant frequencies. Also, a widely used concept for biasing the power amplifiers is using quarter-wave TL stub at fundamental frequency as a *biasing line*. This  $\lambda/4$  line serves a dual purpose of providing DC path from power supply to transistor gate/drain and blocks the RF at a fundamental frequency. To do so, the TL is loaded by a high-value capacitor, acting as a SC at RF, and inverted to OC at the transistor gate/drain. The open presented at the gate/drain has no effect at fundamental frequency and odd-harmonics, providing SC at second harmonic. The ability to match two complex impedances with a single TL of prescribed length and characteristic impedance is another advantage [112].