Dissertation submitted to the Combined Faculties for the Natural Sciences and for Mathematics of the Ruperto-Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

> Put forward by Dipl.-Phys. Manfred Kirchgessner born in Bad Soden, Germany

Oral Examination: December 5, 2017

Control, Readout and Commissioning of the Ultra-High Speed 1 Megapixel DSSC X-Ray Camera for the European XFEL

> Referees: Prof. Dr. Peter Fischer Prof. Dr. Udo Kebschull

#### Abstract:

The goal of this thesis was to develop the software and firmware basis to control and read out the 1-Megapixel DEPFET Sensor with Signal Compression (DSSC) detector, which is being built for the European XFEL (EuXFEL). The DSSC detector proposes single photon resolution at 0.5 keV photon energy, high dynamic range of 10000 photons at a very high frame rate of 4.5 MHz.

During this thesis, the readout chain has been implemented, which receives the average data rate of 134 GBit/s from the detector and transfers sorted image data via four QSFP+ fiber cables to the DAQ system. Additional control software and firmware has been developed for commissioning of the first 1/16th megapixel prototypes. A multifunctional measurement and data analysis framework has been created which is used for characterization of the detector, particularly of properties of the complex readout ASICs. Additional parameter trimming routines to automatically adapt gain and offset parameters of a large pixel matrix have been developed in order to generate suitable configurations which have been applied during two measurement campaigns at the Petra III synchrotron. For integration into the new Karabo framework, which is provided by XFEL for beamline control, several software devices have been implemented.

#### Zusammenfassung:

Ziel dieser Arbeit war es, die Software- und Firmwarebasis zur Steuerung und Auslese des 1 Megapixel DEPFET Sensor with Signal Compression (DSSC) Detektors zu entwickeln, der für den European XFEL (EuXFEL) gebaut wird. Der DSSC Detektor verspricht Einzelphotonenauflösung bei 0,5 keV Photonenenergie, einem hohen Dynamikbereich von 10000 Photonen bei einer sehr hohen Bildrate von 4,5 MHz. Während dieser Arbeit wurde die Auslesekette implementiert, welche die Bilddaten mit einer durchschnittlichen Datenrate von 134 GBit/s vom DSSC-Detektor empfängt, bildweise sortiert und über vier QSFP+ Glasfaserkabel zum DAQ-System überträgt. Des weiteren wurde für die Inbetriebnahme der ersten 1/16-Megapixel-Prototypen Steuerungssoftware und -firmware entwickelt. Ein multifunktionales Mess- und Datenanalyse-Framework wurde erstellt, das zur Charakterisierung des Detektors, insbesondere der Eigenschaften des komplexen Auslese-ASICs, verwendet wird. Zusätzlich wurden Parameter-Trimmroutinen für die automatische Anpassung der Verstärkungs- und Offsetparameter aller Pixel einer großen Pixelmatrix entwickelt, um geeignete Konfigurationen zu erzeugen, die bei zwei Messkampagnen am Petra III-Synchrotron eingesetzt wurden. Außerdem wurden innerhalb dieser Arbeit, für die Integration in das neue Karabo-Framework, welches von XFEL für die Steuerung der Beamline-Umgebung entwickelt wurde, mehrere Software-Devices implementiert.

### Contents

| Ι | INTRODUCTION AND PRESENTATION OF THE 1 MEGAPIXEL |                                              |    |  |  |

|---|--------------------------------------------------|----------------------------------------------|----|--|--|

|   | DS                                               | SC Camera                                    | 1  |  |  |

| 1 | Inte                                             | RODUCTION                                    | 3  |  |  |

| 2 | Background & Motivation                          |                                              |    |  |  |

|   | 2.1                                              | Principle of an X-ray Free Electron Laser    | 10 |  |  |

|   | 2.2                                              | SASE Principle                               | 15 |  |  |

|   | 2.3                                              | Experiments at 4th Generation Light Sources  | 17 |  |  |

| 3 | The European XFEL (EuXFEL)                       |                                              |    |  |  |

|   | 3.1                                              | Historical Development of the European XFEL  | 19 |  |  |

|   | 3.2                                              | Basic Parameters of the EuXFEL               | 20 |  |  |

|   | 3.3                                              | TIMING SCHEME OF THE GENERATED X-RAY PULSES  | 22 |  |  |

|   | 3.4                                              | Comparison with other SASE FELs              | 22 |  |  |

|   | 3.5                                              | Planed User Applications                     | 23 |  |  |

| 4 | Тне                                              | XFEL BEAMLINE ENVIRONMENT                    | 29 |  |  |

|   | 4.1                                              | The Clock and Control System                 | 29 |  |  |

|   | 4.2                                              | Trainbuilder                                 | 32 |  |  |

|   | 4.3                                              | Karabo - The XFEL Control Software Framework | 35 |  |  |

| 5 | Pre                                              | SENTATION OF THE DSSC DETECTOR               | 45 |  |  |

|   | 5.1                                              | Properties of the Proposed Detector          | 45 |  |  |

|   | 5.2                                              | Design Concept of the Detector System        | 46 |  |  |

|   | 5.3                                              | Sensor Technology                            | 47 |  |  |

|   | 5.4                                              | The Readout ASIC                             | 53 |  |  |

|   | 5.5                                              | Detector Layout                              | 56 |  |  |

|   | 5.6                                              | Components of the Readout Chain              | 58 |  |  |

|   | 5.7                                              | Booting and Initial Configuration            | 62 |  |  |

|   | 5.8                                              | Power-Cycling Principle                      | 63 |  |  |

|   | 5.9                                              | SAFETY CONCEPT                               | 63 |  |  |

| Contents |

|----------|

|----------|

|                     | 5.10                                                                                                   | Prototyping and Development                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| II                  | Тні                                                                                                    | E FIRMWARE OF THE DSSC DETECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67                                                                                      |

| 6                   | Desi                                                                                                   | IGN OF THE SYSTEM CONTROL FIRMWARE                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71                                                                                      |

|                     | 6.1                                                                                                    | FIRMWARE OVERVIEW AND CLOCK DISTRIBUTION                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                                                      |

|                     | 6.2                                                                                                    | REGISTER CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75                                                                                      |

|                     | 6.3                                                                                                    | MAIN STATE-MACHINES AND SYNCHRONIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78                                                                                      |

|                     | 6.4                                                                                                    | Generation of Switched Signals                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84                                                                                      |

|                     | 6.5                                                                                                    | Debug Features and Simulation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                      | 86                                                                                      |

| 7                   | Імрі                                                                                                   | ementation of the Readout Chain                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91                                                                                      |

|                     | 7.1                                                                                                    | Readout Concept of the ASIC                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92                                                                                      |

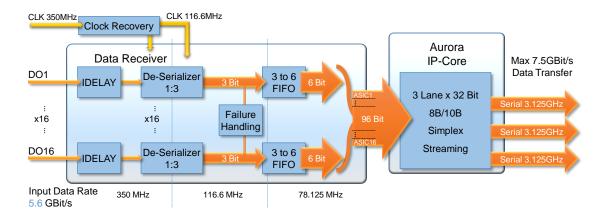

|                     | 7.2                                                                                                    | The IOB Data Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93                                                                                      |

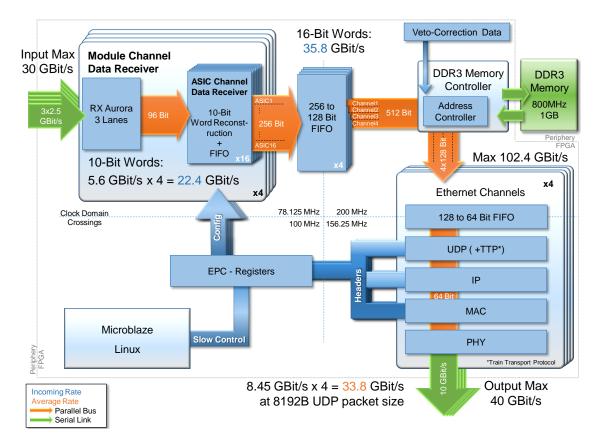

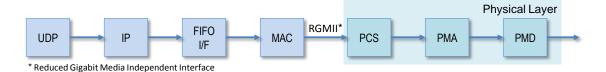

|                     | 7.3                                                                                                    | The Data Path in the PPT FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                           | 95                                                                                      |

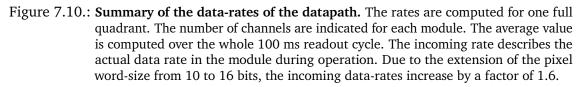

|                     | 7.4                                                                                                    | Summary of Data-Rates and Bandwidths                                                                                                                                                                                                                                                                                                                                                                                                                                    | 109                                                                                     |

| 8                   | Sele                                                                                                   | ECTED MEASUREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 113                                                                                     |

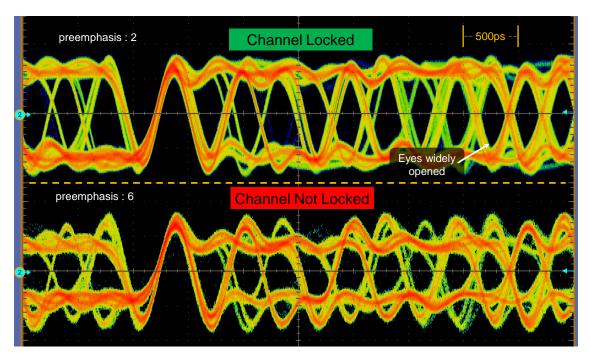

|                     | 8.1                                                                                                    | Serial Links and Transmission Quality                                                                                                                                                                                                                                                                                                                                                                                                                                   | 113                                                                                     |

|                     | 8.2                                                                                                    | FPGA UTILIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 116                                                                                     |

|                     |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

| III                 | Sof                                                                                                    | TWARE DEVELOPMENT FOR THE DSSC DETECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119                                                                                     |

| III<br>9            | _                                                                                                      | TWARE DEVELOPMENT FOR THE DSSC DETECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119<br>125                                                                              |

|                     | _                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

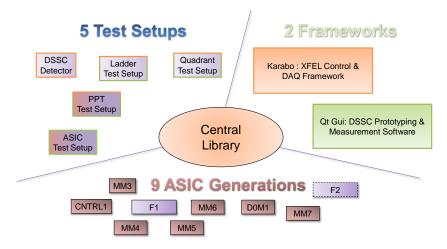

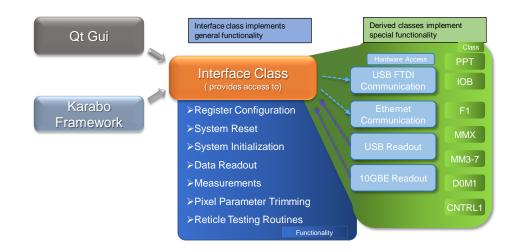

|                     | Devi                                                                                                   | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION                                                                                                                                                                                                                                                                                                                                                                                                                 | 125                                                                                     |

|                     | Devi<br>9.1                                                                                            | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>Design Approach of the Class Hierarchy                                                                                                                                                                                                                                                                                                                                                                       | 125<br>125                                                                              |

|                     | Devi<br>9.1<br>9.2<br>9.3                                                                              | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>Design Approach of the Class Hierarchy<br>Configuration Register Representation                                                                                                                                                                                                                                                                                                                              | 125<br>125<br>130                                                                       |

| 9                   | Devi<br>9.1<br>9.2<br>9.3<br>Сом                                                                       | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER                                                                                                                                                                                                                                                                                  | 125<br>125<br>130<br>135                                                                |

| 9                   | Devi<br>9.1<br>9.2<br>9.3<br>Сом<br>10.1                                                               | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING                                                                                                                                                                                                                          | 125<br>125<br>130<br>135<br>141                                                         |

| 9                   | Devi<br>9.1<br>9.2<br>9.3<br>Сом<br>10.1<br>10.2                                                       | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING<br>MEASUREMENT FRAMEWORK AND DATAANALYZER                                                                                                                                                                                | 125<br>125<br>130<br>135<br>141<br>141                                                  |

| 9                   | Devn<br>9.1<br>9.2<br>9.3<br>Сом<br>10.1<br>10.2<br>Тне                                                | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING<br>MEASUREMENT FRAMEWORK AND DATAANALYZER<br>TRIMMING ALGORITHMS                                                                                                                                                         | 125<br>125<br>130<br>135<br>141<br>141<br>146                                           |

| 9                   | Devi<br>9.1<br>9.2<br>9.3<br>Com<br>10.1<br>10.2<br>The<br>11.1                                        | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING<br>MEASUREMENT FRAMEWORK AND DATAANALYZER<br>TRIMMING ALGORITHMS<br>DSSC KARABO DEVICES                                                                                                                                  | 125<br>125<br>130<br>135<br>141<br>141<br>146<br>163                                    |

| 9                   | Devi<br>9.1<br>9.2<br>9.3<br>Сом<br>10.1<br>10.2<br>Тне<br>11.1<br>11.2                                | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING<br>MEASUREMENT FRAMEWORK AND DATAANALYZER<br>TRIMMING ALGORITHMS<br>DSSC KARABO DEVICES<br>THE KARABO::DSSCPPT CONTROL DEVICE                                                                                            | 125<br>125<br>130<br>135<br>141<br>141<br>146<br>163<br>163                             |

| 9                   | DEVI<br>9.1<br>9.2<br>9.3<br>COM<br>10.1<br>10.2<br>THE<br>11.1<br>11.2<br>11.3                        | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING<br>MEASUREMENT FRAMEWORK AND DATAANALYZER<br>TRIMMING ALGORITHMS                                                                                                                                                         | 125<br>125<br>130<br>135<br>141<br>141<br>146<br>163<br>163<br>165                      |

| 9<br>10<br>11<br>12 | DEVI<br>9.1<br>9.2<br>9.3<br>COM<br>10.1<br>10.2<br>THE<br>11.1<br>11.2<br>11.3<br>SOFT                | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING<br>MEASUREMENT FRAMEWORK AND DATAANALYZER<br>TRIMMING ALGORITHMS<br>DSSC KARABO DEVICES<br>THE KARABO ::DSSCPPT CONTROL DEVICE                                                                                           | 125<br>125<br>130<br>135<br>141<br>141<br>146<br>163<br>163<br>165<br>174               |

| 9<br>10<br>11<br>12 | DEVI<br>9.1<br>9.2<br>9.3<br>COM<br>10.1<br>10.2<br>THE<br>11.1<br>11.2<br>11.3<br>SOFT                | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION                                                                                                                                                                                                                                                                                                                                                                                                                 | 125<br>125<br>130<br>135<br>141<br>141<br>146<br>163<br>163<br>165<br>174<br>177        |

| 9<br>10<br>11<br>12 | Devi<br>9.1<br>9.2<br>9.3<br>Com<br>10.1<br>10.2<br>The<br>11.1<br>11.2<br>11.3<br>Soft<br>200<br>12.1 | ELOPMENT OF THE CENTRAL LIBRARY AND CONTROL APPLICATION<br>DESIGN APPROACH OF THE CLASS HIERARCHY<br>CONFIGURATION REGISTER REPRESENTATION<br>THE MULTITHREADED SOFTWARE DATA RECEIVER<br>PLEX METHODS FOR MEASUREMENTS AND PARAMETER TRIMMING<br>MEASUREMENT FRAMEWORK AND DATAANALYZER<br>TRIMMING ALGORITHMS<br>DSSC KARABO DEVICES<br>THE KARABO ::DSSCPPT CONTROL DEVICE<br>KARABO DEVICES FOR BEAMLINE MEASUREMENTS<br>OUTLOOK FOR QUADRANT AND MEGAPIXEL DEVICES | 125<br>125<br>130<br>135<br>141<br>141<br>146<br>163<br>163<br>165<br>174<br>177<br>179 |

#### Contents

| Cond | CLUSION                                                                                                                                                                 | 185                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 13.1 | Conclusion                                                                                                                                                              | 185                                                                         |

| 13.2 | Summary of Own Contributions                                                                                                                                            | 188                                                                         |

| 13.3 | Outlook                                                                                                                                                                 | 189                                                                         |

|      |                                                                                                                                                                         |                                                                             |

| APP  | 'ENDIX                                                                                                                                                                  | 191                                                                         |

| Appe | NDIX A: DSSC ASIC PIXEL NUMBERING                                                                                                                                       | 193                                                                         |

| DSSO | C Train Data Format                                                                                                                                                     | 195                                                                         |

| Сом  | munication Protocol and interfaces in the Ladder System                                                                                                                 | 197                                                                         |

| Code | E Example for Software Data Receiver Classes                                                                                                                            | 203                                                                         |

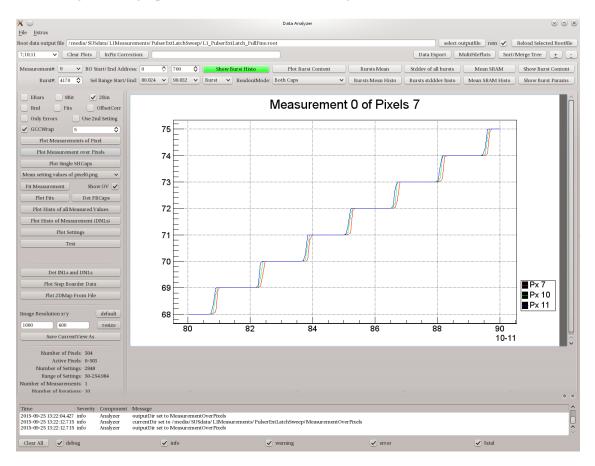

| Тне  | DATAANALYZER APPLICATION                                                                                                                                                | 207                                                                         |

| E.1  | Data Structure                                                                                                                                                          | 208                                                                         |

| E.2  | Analyzer Structure                                                                                                                                                      | 211                                                                         |

| E.3  | Burst-wise Analysis                                                                                                                                                     | 212                                                                         |

| E.4  | Analyzer Modes                                                                                                                                                          | 213                                                                         |

| E.5  | Setting-Wise Analysis                                                                                                                                                   | 214                                                                         |

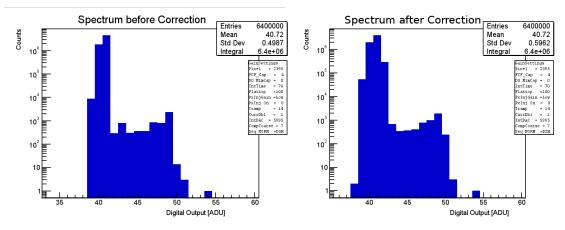

| E.6  | Systematic Corrections                                                                                                                                                  | 218                                                                         |

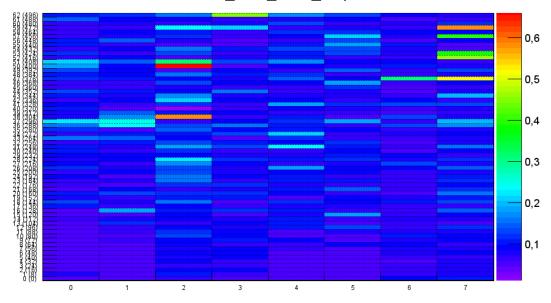

| E.7  | 2D-Color-Map Generation                                                                                                                                                 | 219                                                                         |

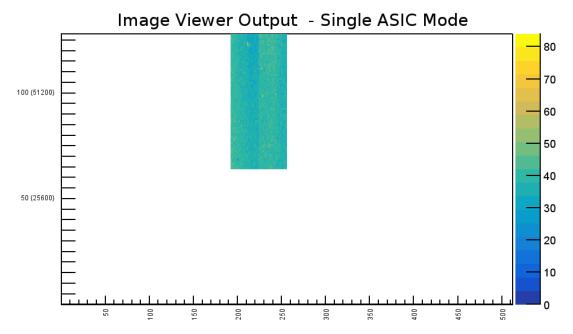

| E.8  | Image Viewer                                                                                                                                                            | 220                                                                         |

| E.9  | Data Export                                                                                                                                                             | 222                                                                         |

| E.10 | HDF5 File Import                                                                                                                                                        | 223                                                                         |

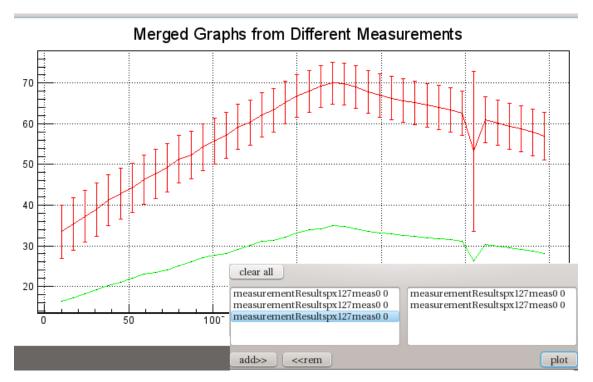

| E.11 | Multi-Measurement Plots                                                                                                                                                 | 224                                                                         |

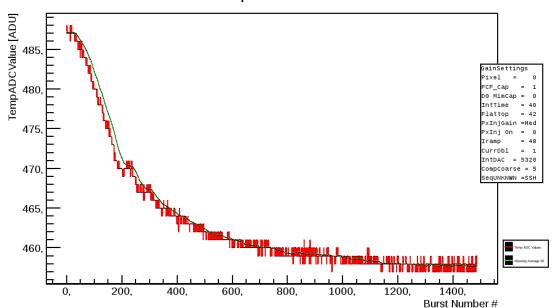

| E.12 | Plot TempADC Values                                                                                                                                                     | 224                                                                         |

|      | 13.1<br>13.2<br>13.3<br><b>APPP</b><br><b>APPPE</b><br>DSSC<br>COMP<br>THE<br>E.1<br>E.2<br>E.3<br>E.4<br>E.5<br>E.6<br>E.7<br>E.8<br>E.7<br>E.8<br>E.9<br>E.10<br>E.11 | <ul> <li>E.2 ANALYZER STRUCTURE.</li> <li>E.3 BURST-WISE ANALYSIS</li></ul> |

## Part I

# Introduction and Presentation of the 1 Megapixel DSSC Camera

### 1

#### INTRODUCTION

To enter new territories of fundamental research, one has to make enormous effort nowadays. With the EuXFEL, a two billion euro project has been launched in Hamburg (Germany) this year, which will enable completely new approaches in fundamental research and a variety of scientific fields. It will be the largest free electron laser which has ever been built: a light source of the 4th generation producing ultra short, hard X-ray pulses in the Å region with an unparalleled brilliance which will surpass the strongest 3rd generation synchrotron sources by over a billion times. This new quality of light generation is driven by a super-conducting, linear accelerator (LINAC) which has originally been proposed for the large international linear collider (ILC). But it turned out that the quality of the generated electron beam was such high that it perfectly fits to the requirements of a 4th generation light source. With a pulse generation rate of 4.5 MHz and 27000 X-ray flashes per second, the EuXFEL will also present enormous challenges to the imaging detectors and the data acquisition systems. Since no existing detector will fit the requirements of the EuXFEL, three large 2D megapixel detectors have been designed for usage in the experiments at the different beamlines. The required objective of single photon resolution combined with a large dynamic range of 10000 photons will be realized by each detector for the respective photon energy range.

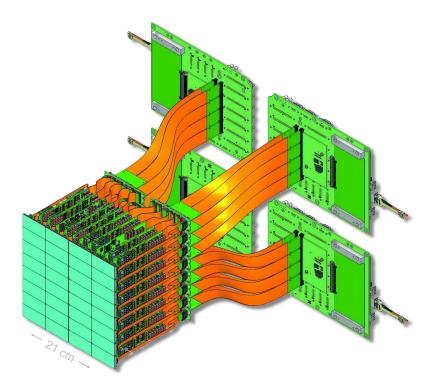

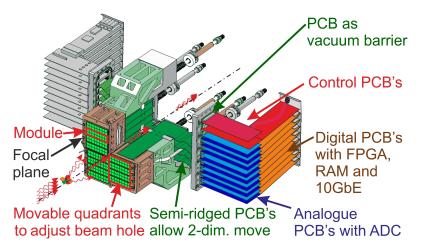

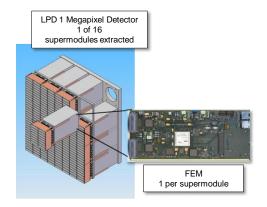

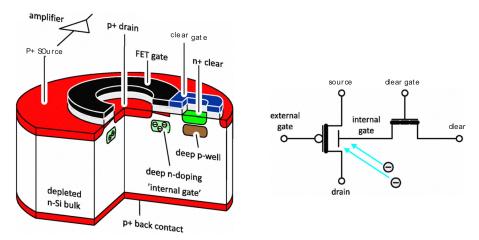

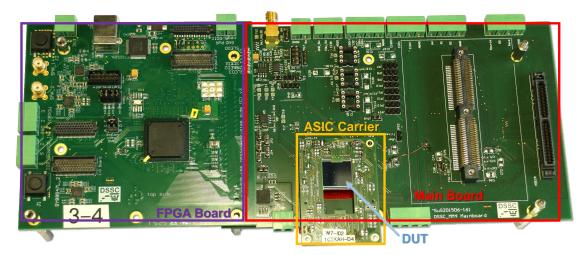

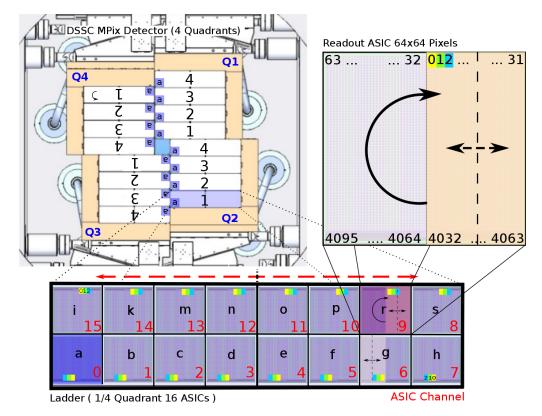

The DEPFET **S**ensor with **S**ignal **C**ompression (DSSC) detector will cover the lower energy range. It is designed and developed by a consortium of several contributors including DESY (Hamburg, Germany), Politecnico di Milano (Italy), University of Bergamo (Italy), the European XFEL GmbH (Germany) and Heidelberg University (Germany). The focal plane area of the megapixel detector as shown in figure 1.1 will fill about  $21 \times 21 \text{ cm}^2$ . By implementing high sensitive DEPFET sensors, which have already shown very good performance in low noise applications, single photon resolution of the DSSC detector will be achieved down to photon energies of 0.5 keV. By a novel design concept of the DEPFET sensor, a signal compression is introduced, leading to a non linear signal response which increases the dynamic range of the sensor to the requested 10K photons.

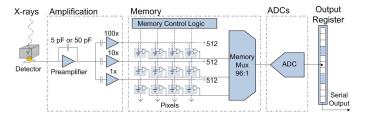

The DSSC detector implements full parallel readout of the sensor to deal with the fast event rate of 4.5 MHz. Therefore, every sensor pixel is bump bonded to a dedicated readout channel on an application specific integrated circuit (ASIC). The ASIC contains a complex signal processing chain including an integrating filter and an 8 to 9 bit ADC (analog-to-

#### 1. Introduction

Figure 1.1.: Artistic image of the DSSC megapixel detector. (Courtesy of K. Hansen, DESY)

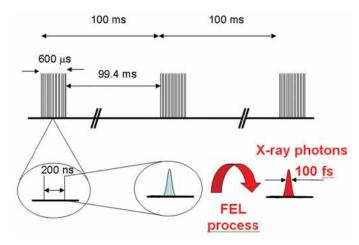

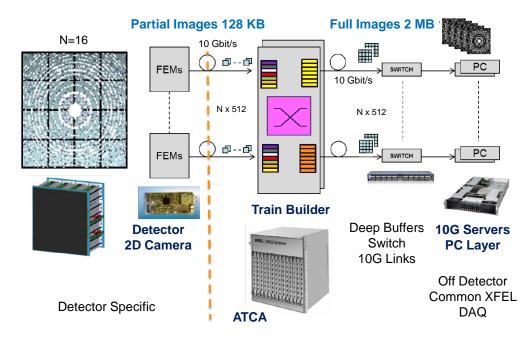

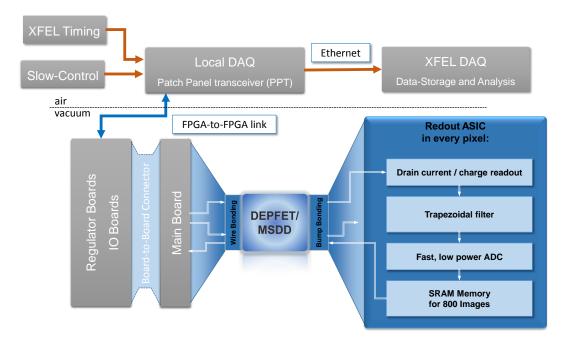

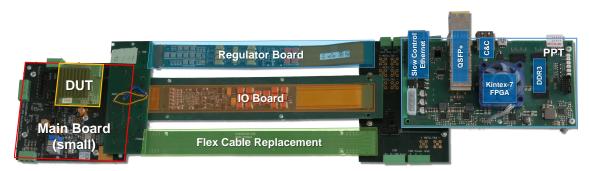

digital converter). Since the direct transfer of the pixel data is not feasible between two light flashes, the readout ASIC also contains an in-pixel SRAM memory which is used to store the digitized values for later transfer during the 99.4 ms pause that follows each X-ray pulse train. Not least because of the limited space in the readout pixels, the DSSC detector can only store 800 of the 2700 images per pulse train which remains the largest number among the other detectors. Acquiring at a repetition rate of 10 Hz, the DSSC megapixel detector generates a continuous data rate of over 134 GBit/s.

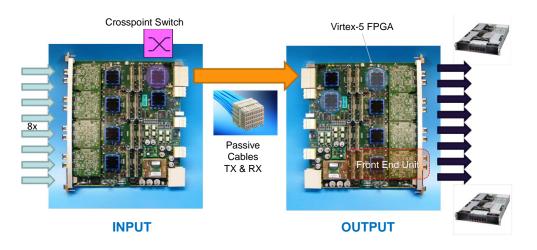

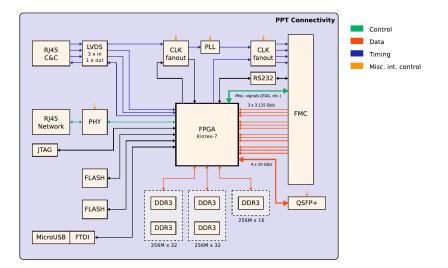

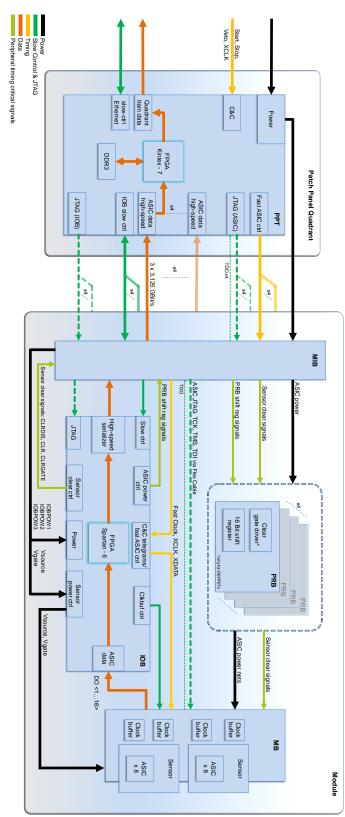

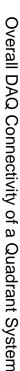

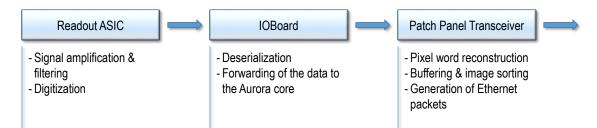

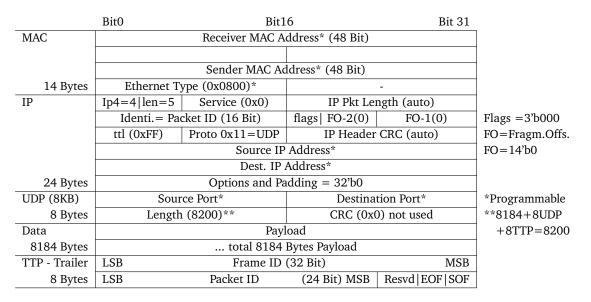

By implementing modern components, a compact design of the data acquisition (DAQ) is possible which realizes a handy transfer of the image data via only four optical QSFP+ fiber cables, each bundling four 10 Gigabit-Ethernet links. A complex readout chain transports the pixel data from the in-pixel SRAM in the ASIC to the first and second FPGA stage before the data is packed into UDP Ethernet packets and transferred out of the detector. The average utilization of the nominal 160 GBit/s data rate of the optical links thereby is round 84% which is a remarkably high value.

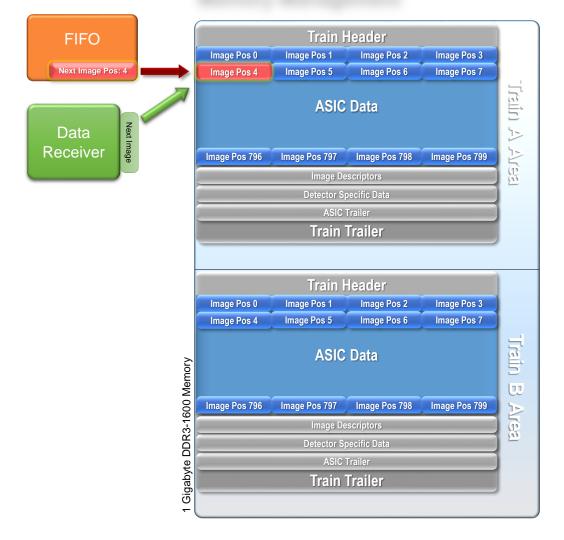

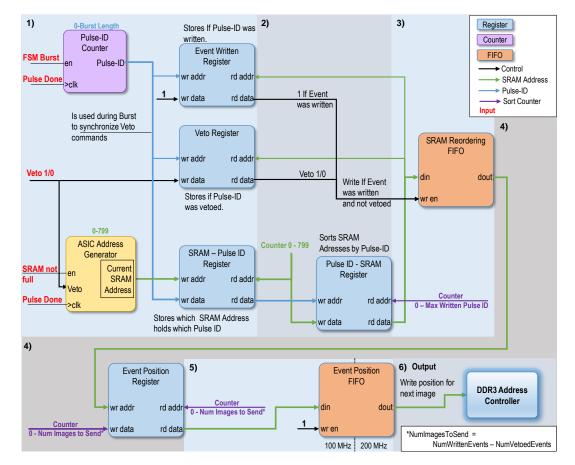

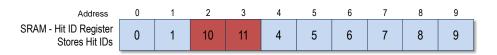

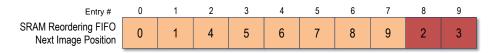

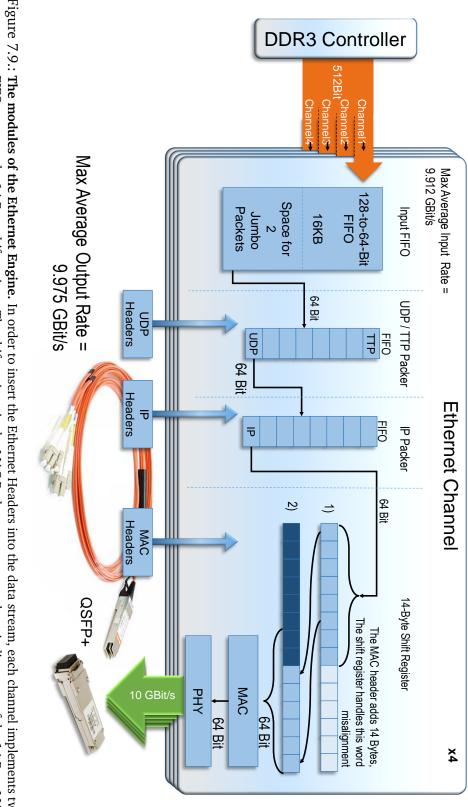

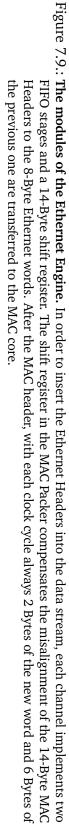

The second FPGA stage consists of four identical FPGA cards, implementing a Xilinx Kintex-7 FPGA (available since 2012). Each FPGA card combines the readout data of one quarter of the megapixel detector and generates standard Ethernet packets from the data stream before the data is sent out of the system. By implementing a 1 GB DDR3-1600 memory, which runs at 800 MHz, it is possible not only to buffer two complete data trains but also to change the order of the incoming images at full readout speed.

In this work, the major parts of the DAQ system of the DSSC detector have been developed.

As the central part, the firmware modules of the two FPGA stages of the readout chain will be described. Furthermore, the control software including the design of the central library to configure and control the whole detector system is presented in detail.

This thesis is divided into four parts. The first part comprises some basic facts about the EuXFEL and the working principle of free electron lasers. During this introduction, the DSSC detector is presented to the reader including some details about the utilized sensors of the DSSC detector as well as the hardware components of the detector system.

In the second part, the implemented firmware modules of the system FPGAs are described. This includes the configuration and synchronization modules and, as the main section of this part, the modules of the readout chain. At the end of the firmware part, some simulations and measurements are shown in order to underline the successful testing and operation of the firmware components.

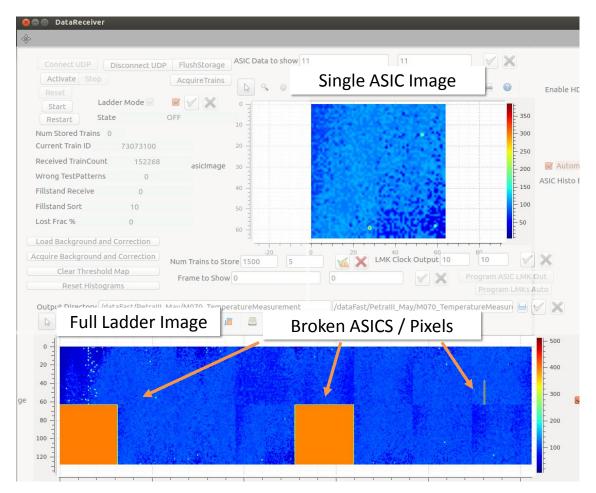

The third part includes the control and configuration software of the DSSC DAQ. This also includes the data receiver library which implements a highly optimized, multithreaded approach to enable the packet reception from the 10 Gigabit-Ethernet links at full speed and real time pixel sorting in order to directly store and visualize the image pixels as located on the focal plane. The software part includes also some aspects of the self-written measurement and data analysis framework which is frequently used by different groups of the consortium in order to characterize the system performance. The central aspect of the measurement framework is a standardized format of the data which is stored during measurements which allows to visualize and analyze the measurements automatically in an application. This turned out to be a very useful instrument to compare and exchange the measurements between the different groups and also to repeat measurements in different setups or environments.

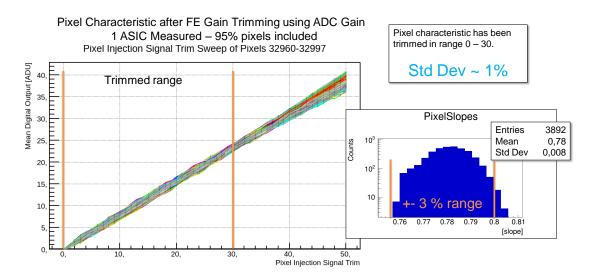

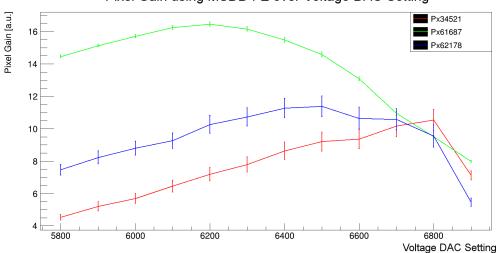

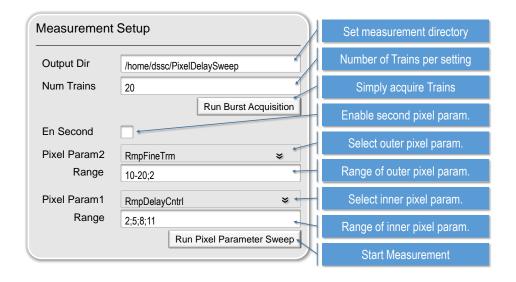

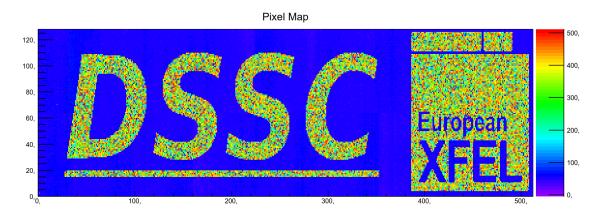

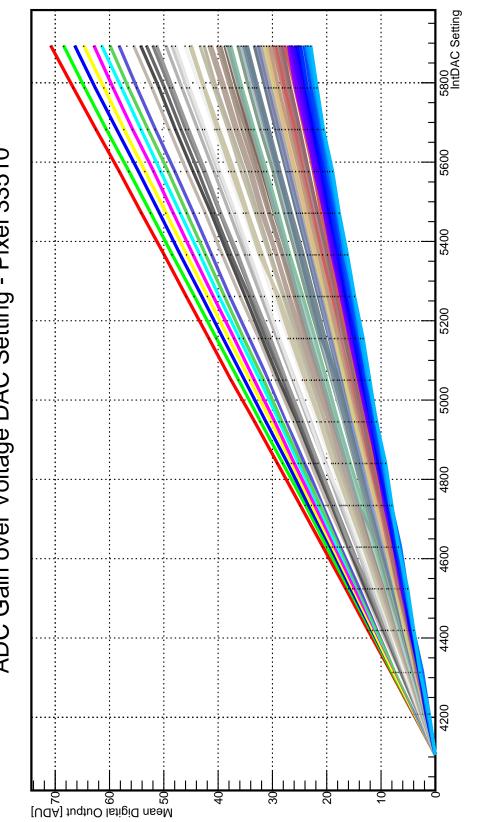

Additionally, the more complex, automated pixel parameter trimming routines are described. With a rising complexity of the test systems and a rising number of pixels, the pixel characteristics have to be tuned automatically. Therefore, automated parameter sweeps have to be measured and analyzed by software in order to optimize the pixel behavior in the whole pixel matrix. These routines have been developed during this thesis to prepare the system for calibration measurements with the first 1/16th megapixel DSSC Ladder cameras. The successful realization of these complex methods will also be presented.

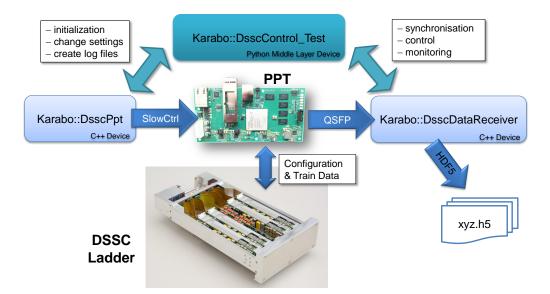

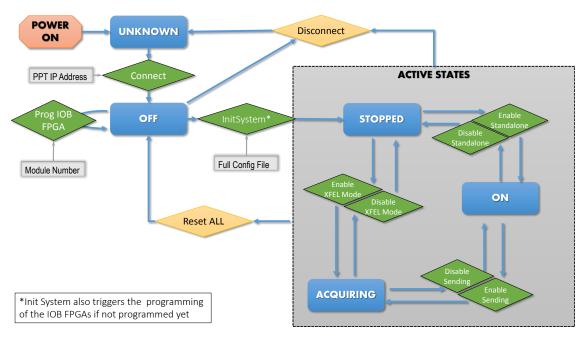

The last section of the software part includes the integration of the control software into Karabo, the new software framework, which has been developed by XFEL for beamline control, DAQ and calibration. Since this framework is the main software which will be used during experiments at XFEL, large effort has been made to realize stable and reliable control of the DSSC detector using this framework.

The last part of this thesis practically summarizes all achievements from the software and firmware part. It shows the successful implementation of the previously described components, which have been finalized shortly before the second beamline measurement campaign at the Petra III synchrotron during which important calibration measurements have been performed. The performance of the DSSC Ladder system during this campaign will be presented at the end of this thesis.

#### **BACKGROUND & MOTIVATION**

Since the discovery of X-ray radiation in 1895 by Roentgen, the radiation type has always been a fascinating and important source for new findings and technologies. With the progress of X-ray generating devices, the quality of X-ray radiation steadily increased. The short-wave radiation enables spectacular insights into the world of molecules or viruses e.g. the description of the double helix structure of the DNA molecules [1]. Simply the number of 19 handed Nobel prices, which are linked to X-ray radiation, underlines its importance in science.

With the advancement in X-ray science, new challenges and requirements have emerged. In the beginning, especially the penetrating property of X-rays attracted the most attention which allows to visualize the hidden structures in the interior of an object. Soon it became clear that in theory the small wavelength of X-rays can be utilized to image also tiniest structures down to the Å region.

But X-rays imaging procedures are much more complicated compared to an optical microscope since there are no materials which can be used for lenses or mirrors. Additionally, an X-ray microscope faces the problem that a tiny object also reflects few light and therefore the light intensity has to be very high in order to generate detectable signals from very small structures. The intensity problem could be solved by multiplying the structure in a crystal and therefore increasing the signal strength which is generated e.g. by Bragg reflections. This technique has successfully been applied to investigate the structure of a variety of crystalline materials and, due to evolving techniques in crystallization processes, also of more complicated structures like, for example, complex proteins. But this technique soon reaches its limit since not all structures can be crystallized or because the production of large crystals is very expensive.

In order to measure a comparable signal from a smaller crystal, the light intensity has to be increased. This relationship leads to the request for always stronger X-ray sources. For X-ray light sources, the intensity is measured in brilliance or spectral brightness, which is expressed in units:

$$Brilliance = \frac{N}{t \cdot A(\Delta\Omega)/(\Omega) \cdot (\Delta\lambda/\lambda)} = \frac{photons}{s \cdot mm^2 \cdot mrad^2 \cdot 0.1\% BW}$$

(2.1)

The expression 0.1% BW describes a bandwidth of  $10^{-3}$  around the central wavelength  $\lambda$

of the beam. Consequently, the brilliance is maximized, if the photon flux, i.e. the number of photons per second in a very thin wavelength region is large and the photons are emitted very densely from a small spot with little angular divergence.

With the discovery of the parasitic radiation at the General Electric 70-MeV synchrotron in 1947, a new effect has been found which enables to build very strong light sources [2].

The parasitic occurrence of synchrotron radiation is also described as light source of the 1st generation.

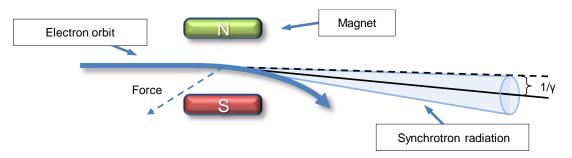

Figure 2.1.: Generation of electromagnetic radiation from a relativistic electron beam. Due to the Lorenz transformation, the emitted radiation is bundled in a narrow cone, tangential to the electron beam direction. The opening angle decreases with increasing energy  $\gamma$  of the electron beam. The power of the emitted synchrotron radiation scales with the forth power of the electron energy:  $P_{rad} \propto \gamma^4$ , where  $\gamma = E_e/m_e c^2$ .

Synchrotron radiation is generated from relativistic electrons which are deflected by a magnetic field (see figure 2.1). The induced orthogonal acceleration causes emittance of electromagnetic radiation. In case of relativistic particles, this radiation is strongly bundled in flight direction, forming a narrow cone which is directed tangential out of the machine. This type of light source provides very intense light with a continuous spectrum around the critical frequency

$$\omega_c = \frac{3c\gamma^3}{2r} \tag{2.2}$$

with the radius  $r = r(B, \gamma)$ .

The 2nd generation light sources are dedicated electron storage rings which are optimized for generation of synchrotron radiation. The introduced optimizations already cause a significant intensity increase.

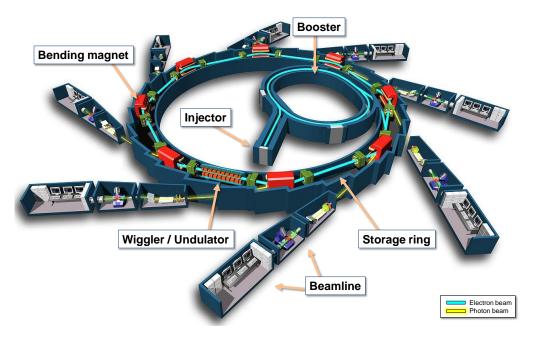

The next evolution step to the 3rd generation light source has been made, when additional devices have been integrated into straight paths of the electron beams in order to further increase the brilliance of the emitted light.

So-called wigglers or undulators<sup>1</sup> apply alternating magnetic fields with a period of typically a few centimeters [4]. In these devices, the electrons are forced on a tight slalom

<sup>&</sup>lt;sup>1</sup>A wiggler normally consists only of a few to a dozen alternating magnets, while an undulator is made up of significantly more magnets.

Figure 2.2.: Schematic setup of a 3rd generation light source synchrotron. Several beamlines, which contain the different experiments, are attached to the central electron storage ring. The electromagnetic radiation is generated in the bending magnets, wigglers or undulators [3].

path which leads to a greatly increased brilliance by four orders of magnitude, compared to the bending magnets of a synchrotron. The achieved light intensities enable to produce detectable signals from micro-crystals [5] which show only a few layers of their repetitive structure.

On the other side, the dramatically increased radiation dose introduces another problem. If the energy transfer to the sample during the imaging process becomes very high, the sample can be destroyed.

This problem can be dealt by cooling the probe down to very low temperatures which in turn has other drawbacks.

Another problem of X-ray microscopy with very small crystals is the decrease of the created interference signals. If the crystal becomes too small, the signal starts to vanish in the background. Since no lenses are available which can be used for X-ray radiation, X-rays can not be imaged like it is done in optical microscopy.

A lens works as a Fourier transformer and transfers the information from the frequency space into the real (local) space. Consequently, the diffraction patterns which are acquired in lensless X-ray diffraction imaging, contain information from Fourier space.

With Bragg reflections from periodic crystal structures, direct reconstruction is possible. But without crystallization, a reconstruction from the diffraction patterns requires phase information which is destroyed when the photon hits the detector. Nevertheless, with high computational effort and special techniques this problem can be solved.

Advanced techniques of lensless imaging require highly coherent X-ray light, as it is

generated e.g. by a LASER (Light Amplification by Stimulated Emission of Radiation). Since a synchrotron produces light with a continuous spectrum, coherent diffraction imaging (CDI) was only possible when the first light sources of the 3rd generation became available.

Consequently, X-ray microscopy faces several problems which hinder the progress towards higher spatial resolutions or the investigation of more complex molecular structures. Finally, the following lists summarizes the previously described effects:

- Small structures create only very small signals ⇒ increase of light intensity, or growing crystalline structures.

- Crystallization is expensive or not feasible with all structures.

- Smaller crystals are easier to grow but require higher light intensities.

- Very high light intensities destroy the sample during the imaging process ⇒ cooling of the sample.

- Cooling is not always feasible or changes the characteristics of the sample.

The long term goal is the imaging of single molecules and nanostructures, such as viruses, without first having to grow crystals. But the light intensities, which are necessary to achieve this goal, would destroy each molecule as soon as it is hit by the radiation. The only possibility is to compress the entire light intensity into such a short pulse, so that the light has already passed through the sample, before the parts of the molecule have begun to fly apart.

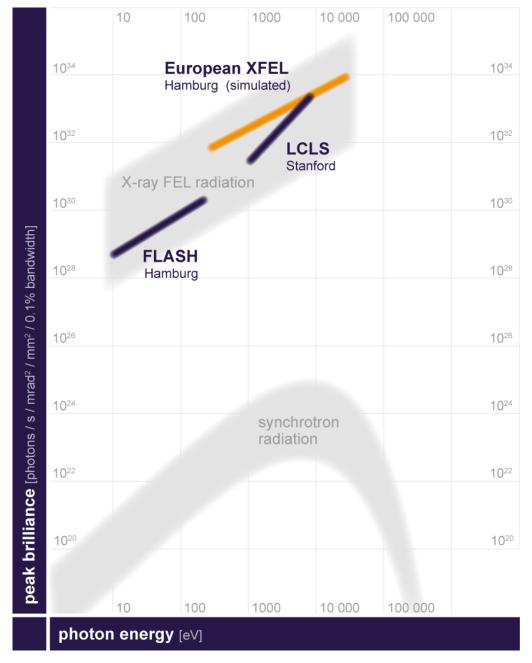

Exactly this is what the 4th generation light sources are able to provide. With the introduction of the first X-ray free electron lasers (XFELs), at the beginning of the 21st century, the first time monochromatic, highly coherent X-ray radiation of unparalleled intensity and brilliance became available. Their brilliance surpasses 3rd generation light sources by an unbelievable factor of 10 orders of magnitudes, visualized in figure 2.3. Additionally, the generated X-ray FEL pulses can be shorter than 100 fs, which is the timescale on which diffraction before destruction is possible [6].

#### 2.1 PRINCIPLE OF AN X-RAY FREE ELECTRON LASER

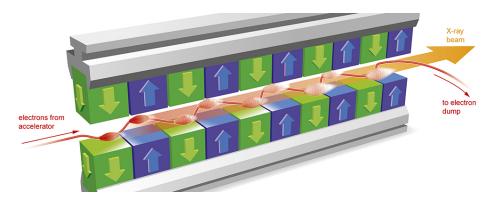

Even if the name suggests a strong relation to a quantum laser, the principle of a free electron laser is more like a very sophisticated vacuum tube. An FEL consists mainly of two major components: an electron accelerator which generates a highly relativistic electron beam and a so called undulator (see figure 2.4), in which the electron beam is injected and the radiation is generated. The undulator consists of a long row of magnets of alternating polarity. The alternating magnetic field in the undulator forces the electrons on an tight oscillating path which induces spontaneous synchrotron radiation.

Due to special effects in the undulator the spontaneous emitted radiation is highly amplified which leads to strongly coherent, laser like radiation at the output of the FEL.

The basic principle of a free electron laser including the processes which happen in the undulator, will be roughly described in the following.

Figure 2.3.: The peak brilliance of free-electron lasers compared to synchrotrons [7]. FELs exceed the brilliance of the 3rd generation synchrotron radiation sources by up to ten orders of magnitude.

Figure 2.4.: Schematic view of an undulator. The alternating magnetic field forces the electron on an tight oscillating path which induces spontaneous synchrotron radiation [8].

The origin is a bunch of highly relativistic electrons which is injected into the undulator. The transverse and longitudinal velocities of the electrons are depended from the position z in the undulator, but can be averaged over one undulator period  $\lambda_u$ :

$$\overline{v_x} = \frac{cK}{\sqrt{2\gamma}}, \overline{v_z} = c(1 - \frac{1}{2\gamma_z^2}), \gamma_z = \frac{\gamma}{\sqrt{1 + K^2/2}}, K = \frac{eB_0\lambda_u}{2\pi m_0 c^2}$$

(2.3)

Ň Where the parameter K is the undulator parameter and  $\gamma = E_e/m_ec^2$  the Lorenz factor. Since the electrons move always slower than the emitted light, a slippage occurs. After each undulator period, the delay of the electrons can be computed as:

$$\delta_z \approx (c - v_z) \frac{\lambda_u}{c} = \frac{\lambda_u}{2\gamma^2} (1 + K^2/2)$$

(2.4)

$\delta$  describes a phase advance of the electromagnetic wave. If  $\delta$  is a multiple of the emitted wave length, constructive interference occurs which finally leads to the undulator equation:

$$\lambda_r = \frac{\lambda_u}{2n\gamma^2} (1 + \frac{K^2}{2}), \qquad (2.5)$$

With *n* as an integer number. n = 1 represents the fundamental resonance and n > 1 higher harmonics. Since the resonance frequency of the FEL depends mainly on the electron energy and the undulator parameters, it can freely be chosen and the wavelength of the generated light hence tuned. The strong influence of the  $\gamma^2$  factor in the equation leads to relaxed requirements on the undulator period if very small wavelength should be generated<sup>2</sup>. This tuneability differentiates a free electron laser significantly from a quantum laser, which can radiate only at defined wavelengths.

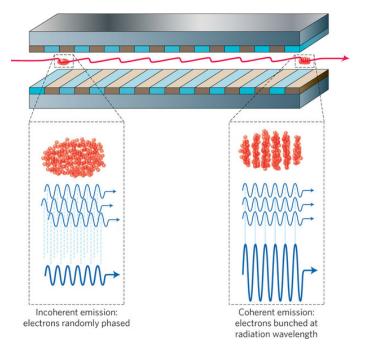

The intensity of the emitted light is strongly dependent of how the electrons are distributed along the z-axis inside the packet.

The spontaneously emitted light from randomly distributed electrons averages to an intensity which is proportional to the number of electrons of the packet ( $I \propto N$ ). If all electrons would be at the same position, forming a macro particle of charge N, the

<sup>&</sup>lt;sup>2</sup>Regarding relativistic electrons  $\gamma = E_e/510$ ,  $E_e$  in keV.

#### 2.1. Principle of an X-ray Free Electron Laser

light would be emitted fully coherent, resulting in an intensity which is proportional to N squared ( $I \propto N^2$ ). Considering a typical number of electrons in a packet of  $10^8$  to  $10^{10}$ , the difference in intensity is enormous. However, the generation of such a macro particle is technically not feasible, even with state of the art technology. But there exists a different technique which boosts the light intensity in a free electron laser.

Figure 2.5.: Bunching process in an undulator [9]. The former homogeneously distributed electrons interact with the emitted radiation. Electrons in front of the phase are slowed down and electrons after the phase of the emitted light are accelerated. Consequently, thin disks are formed. All electrons within one disk emit light synchronously while propagating through the undulator which highly amplifies the radiation intensity. This effect is proportional to the length of the undulator until saturation is reached.

During the propagation of the electrons through the undulator, frequencies near the resonance frequency  $\lambda_r$  are amplified. In this growing electromagnetic field, the electrons start to interact with the radiation as shown in figure 2.5. Besides the energy loss of the electrons to radiation, which decreases the electron velocity, some electrons gather energy from the electromagnetic field of the photons which leads to an acceleration. The effective fields from the magnetic field of the undulator in combination with the oscillating field of the electromagnetic radiation generate ponderomotive forces which lead to a modulation of the electron distribution.

The effective force accelerates electrons which are behind the field phase and decelerate the electrons which are ahead. Consequently, the electrons are bunched into thin discs while they travel along the undulator. The distance of the micro bunches is of the length of the emitted light. Since all electrons of a disk emit radiation at the same phase and, compared to the electrons of the successive disk, with a phase difference of  $2\pi$ , a similar condition to the previously described macro particle is generated. When this state is reached, all electrons emit simultaneously photons of the same phase and wavelength which results in

fully coherent radiation of extremely high intensity.

The feedback of the generated radiation to the electrons can be summarized in three steps:

- 1. The emitted radiation travels faster than the electrons and interacts with the particles ahead.

- 2. The interaction modulates the electron distribution, forming thin disks

- 3. The creation of the disks leads to higher intensity of the electromagnetic field which increases the effect of 2). If the field becomes too strong, electrons slightly behind the radiation start to gather more energy from the field. This results in a saturation of the amplification.

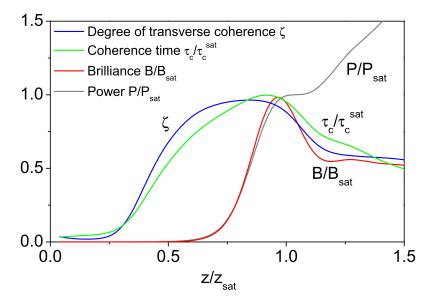

As long as the radiation emittance in direction of the undulator is larger than the loss of radiation, a gain of intensity occurs. While at the beginning of the undulator the intensity increase is linear, it grows exponentially during the bunching process until the micro bunches can not further be compressed. After the saturation length  $z_{sat}$  the bunching is at a maximum and the electrons start to gather energy from the radiation field. At this point no further amplification of the radiation is possible. The development of the gain and different basic parameters of the FEL radiation over the undulator length is drawn in figure 2.6.

Figure 2.6.: Schematic overview about the FEL properties along the undulator [10]. An FEL reaches the highest performance when the micro bunches can not be further compressed. The first saturation of an FEL in the soft X-ray region was reached in 2003 at the TESLA facility in Hamburg, Germany [11].

The bunching of the electrons requires strong electromagnetic fields from radiation. In order to start the bunching process directly at the entrance of the undulator, the process can be induced by a seed laser of the resonance wavelength. By inserting the undulator in an optical resonator, the generated radiation can be trapped for several passes through the machine which additionally accelerates the bunching process.

Oscillator FELs are often used to generate light pulses in the visible region where conventional quantum lasers for seeding are available. For shorter wavelengths, where no highly reflective mirrors exists, X-ray resonators are not feasible<sup>3</sup>. Consequently, an X-ray FEL has to generate its full intensity during a single pass of the radiation through the undulator. The principle of an X-ray FEL is described in the following.

#### 2.2 SASE Principle

The Self-Amplified Spontaneous Emission (SASE) principle is the technique which allows to generate high-intense FEL pulses in the X-ray region. Because there are no highly reflective mirrors available for X-ray radiation, the bunching process in the undulator has to be started from the spontaneously emitted radiation at the beginning of the undulator. Therefore, a very high beam quality in terms of electron emittance<sup>4</sup> and electron density in combination with very high electrical currents of several kilo Amperes have to be reached. Typically, a linear electron accelerator is required to provide a suitable electron beam.

A detailed mathematical description of the processes in a SASE FEL will go beyond the scope of this thesis. A variety of publications deal with the physics of free electron lasers and the SASE process: [14, 4, 15, 16]. A more general and well written description can be found in [9], which also includes a nice outlook in future FEL development. In [17], a comprehensive and detailed development of the mathematical model can be found.

A fundamental description of the FEL characteristics can be provided in a simplified one-dimensional approach, which already gives quite good results. Besides the former mentioned resonance wavelength  $\lambda_r$  and the undulator parameter K, the FEL or Pierce parameter  $\rho$  is used to describe some fundamental characteristics of a SASE FEL. The FEL parameter is given by [10, 18]:

$$\rho_{1D} = \frac{1}{4\gamma_0} \left[ \frac{2I}{I_A} \left( \frac{\lambda_u K A_{JJ}}{\pi \sigma_e} \right)^2 \right]^{1/3}$$

(2.6)

with the electron beam peak current I, the Alfven current  $I_A \approx 17kA$ , the undulator period  $\lambda_u$  and the Lorentz factor  $\gamma_0 = E_0/m_ec^2$ , representing the electron energy at the undulator entrance. The factor  $A_{jj}$  represents the coupling factor. For linear magnetic fields  $A_{JJ} = [J_0(Q) - J_1(Q)]$  with  $J_n$ , the Bessel function of first kind and  $Q = K^2/(2 + 2K^2)$ . The factor  $\sigma_e$  is the rms transverse size of the electron beam.

The FEL parameter gives an estimation for saturation efficiency  $\eta_{sat} \approx \rho_{1D}$  and radiation efficiency  $\eta_r \approx 1/\rho_{1D}$  in the undulator. Since  $\rho_{1D}$  is inversely dependent on the electron energy  $\gamma_0 = E_0/m_ec^2$ , high electron energies lead to small values of the FEL parameter. In a SASE FEL,  $\rho_{1D}$  is in the order of  $1/10000 \le \rho \le 1/1000$  [19]. This means a few thousand

<sup>&</sup>lt;sup>3</sup>Proposals for X-ray resonators using Bragg crystal mirrors have been published [12, 13], but not applied so far.

<sup>&</sup>lt;sup>4</sup>The beam emittance is the volume of the electron beam in phase space. A low emittance means a very dense electron packet, which does not spread during its path through the undulator.

undulator periods are required to reach saturation. The gain length of an FEL describes the travel distance during which the radiation power rises by a factor of e = 2,718:

$$L_g \approx \frac{\lambda_u}{4\pi\rho_{1D}} \tag{2.7}$$

In a SASE FEL, saturation is reached after  $\approx 20$  times the gain length  $z_{sat} \approx 20 \times L_g$ . With undulator periods of  $\lambda_u \approx 50 \, mm$ , the saturation length of an X-ray FEL can easily become over 100 meters.

In the linear approximation, the radiation power in an FEL rises exponentially with the traveled distance z:

$$P(z) \approx \frac{E_0}{3\pi} \rho_{1D}^2 \,\omega_r \exp \frac{z}{L_g} \tag{2.8}$$

Where  $\omega_r = 2\pi c/\lambda_r$  is the resonance frequency. The effective power of the shot noise is assumed as the primary value which is amplified during the SASE process. With the power gain at saturation, which can be estimated by

$$G = \frac{P_{sat}}{P_{sh}} \simeq \frac{N_c}{3} \sqrt{\pi \ln N_c},$$

(2.9)

where  $N_c = I/\omega_r e \rho_{1D}$  is the number of cooperating electrons, the effective power of shot noise is given by:

$$P_{sat} = \rho_{1D} P_0 \Leftrightarrow P_{sh} \simeq \frac{3\rho_{1D} P_0}{N_c \sqrt{\pi \ln N_c}}$$

(2.10)

with the initial electron beam power  $P_0 = \gamma_0 m_e c^2 I/e$ .

The gain of a SASE FEL is hence proportional to the peak current *I* and the inverse of the FEL parameter  $\rho_{1D}$ .

A further parameter of interest is the coherence time of the laser radiation as a function of z with  $z \leq z_{sat}$ :

$$\tau_{coh}(z) \approx \frac{\pi}{\sigma_{\omega(z)}},$$

(2.11)

with the radiation bandwidth

$$\sigma_{\omega}(z) = 3\sqrt{2}\rho_{1D}\omega_0 \sqrt{\frac{L_g}{z}}.$$

(2.12)

The coherence length also shows a maximum at  $z = z_{sat}$ .

A very central parameter is the duration of the X-ray pulse  $\tau$ . Since the velocity of the injected electrons is  $v_e \approx c$ , the length  $\delta_e$  of the electron packet gives a good approximation:

$$\tau = \delta_e/c \tag{2.13}$$

For a given maximum electron density, the length of the electron packet is always dependent on the number of electrons which are contained in the packet. Consequently, the pulse duration can not be easily reduced, due to the current strength which is required to start the SASE process. Typical lengths are of the order of a few tens of  $\mu m$  which results in pulse durations of  $\approx 100$  fs.

These formulas can only give a rough guideline to estimate the main parameters of a SASE FEL but can be used to give a basic understanding of the dependencies of different parameters.

#### 2.2.1 PROGRESS OF SASE FEL TECHNOLOGY

Since the theoretical description from John Madey in 1971 of a device which is able to amplify X-ray radiation in a periodic magnetic field [14], lots of research and development followed over two decades until the first FEL laser shot in the X-ray region could be realized. The first radiation from a SASE FEL was reached in September 2000 at the Advanced Photon Source (APS) in Argonne at the National Laboratory. The FEL reached saturation at 385 nm in the near-UV region [20]. Only one month later, the TESLA facility in Hamburg, Germany, which implements a superconducting linear electron accelerator, also reached SASE operation the first time at a wavelength of 109 nm [21]. After continuous improvements of the superconducting technology, the first soft X-ray laser pulses have been generated by the Free Electron Laser in Hamburg (FLASH), which evolved from the TESLA facility. FLASH can be regarded as a smaller, early version of the EuXFEL. The generated light pulses of this SASE FEL reached in 2006 a wavelength of 13 nm (95 eV) [22], which could be further decreased to 4.12 nm (300 eV) in 2010 [23].

Today, the world record of the shortest laser wavelength generated by a SASE FEL is held by LCLS in Stanford, California. By injecting electrons, accelerated to up to 14 GeV, into an undulator of 132 m length, this machine is able to generate X-ray flashes of a wavelength of 0.12 nm (10 keV) [24]. But it is only a question of time until the new EuXFEL in Hamburg will put a new record with wavelengths below 1 Å, after the machine started its operation in September 2017.

#### 2.3 Experiments at 4th Generation Light Sources

4th generation light sources will enable new insights into the world of molecules which have not been possible before. The enormous light intensity, which can be generated by a SASE FEL, promises to realize imaging of single viruses and complex molecules for the first time, without the need of difficult and expensive crystallization. Pulse durations of 100 fs and shorter will allow to dissolve processes on a time scale on which chemical reactions take place.

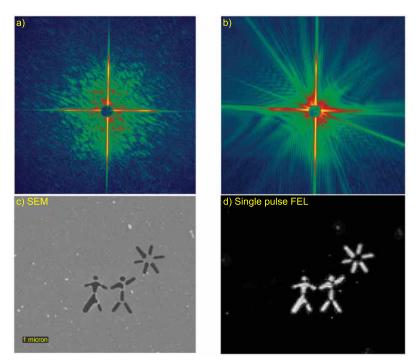

The low bandwidth and long coherence length of SASE FEL X-ray radiation enables new techniques and approaches in the field of lensless coherent diffraction imaging [25]. But reconstruction of structures from the acquired diffraction images is difficult and requires intense usage of computers. Powerful algorithms have been developed [26, 25, 27] to solve the phase problem which is needed in order to reconstruct the diffracting structure from the blurry diffraction image (see figure 2.7).

Furthermore, very special challenges are set on the experiment setup and its execution under the special conditions of an X-ray FEL beamline. Anything which is illuminated by the laser shot will immediately be destroyed because of the high radiation dose. The solution of this problem is given by the short pulse duration. As shown in experiments at FLASH [28] and LCLS [25, 29], it is possible to image complex structures with a single X-ray pulse from a SASE FEL, even if the sample is destroyed during the imaging process. The method is called 'diffraction before destruction' [30]. If the light pulse duration is in the order of 100 fs or shorter, the light has passed the sample before any movement of the exploding molecule can blur the image. The feasibility of this method has impressively been shown at FLASH with soft-X-ray radiation [28] see figure 2.7. Due to this technique, the radiation

intensity can now freely be increased since the destruction of the sample does not interfere with the resulting image. Theoretically, this enables to create and detect intense signals also from smallest structures.

Figure 2.7.: Diffraction before destruction prove of principle at FLASH [31]. c) Ground truth, before the sample has been destroyed. The ground truth has been acquired using a scanning electron microscope (SEM). a) Diffraction pattern of a single soft X-ray shot, before destruction. b) Diffraction pattern after destruction. The pattern suggests massive changes of the sample. d) Reconstructed pattern from a), the spacial resolution has been estimated to 62 nm.

Due to the destruction of the sample, sophisticated approaches to provide continuous supply of identical samples to the pulse trains are required if e.g. a video of a chemical process or a 3D model of a molecule should be acquired. One technique is, for instance, the sample injection which has been developed at LCLS and published in 2011 [29]. The goal of the experiment was to generate a 3D model of a Mimi virus, which is the largest known virus. Using a special sample injector, a very thin stream of aerosolized Mimi viruses is injected with high velocity (60 - 100 m/s) into the interaction zone of the experiment. The X-ray flashes hit the injected viruses with an arbitrary orientation. In order reconstruct the 3D model,  $10^6$  diffraction patterns had to be reconstructed and sorted by the virus orientation.

## 3

#### THE EUROPEAN XFEL (EUXFEL)

After the new free electron laser technology advances and the first machines could be driven to generate intense light flashes of shorter and shorter wavelength, the scientists started to think about the construction of the largest FEL which could generate light flashes in the hard X-ray region of unparalleled intensity.

The cornerstone of the EuXFEL was laid down in 1992 when the new TESLA (Tera Electron Volt Energy Superconducting Linear Accelerator ) technology development started. For shorter wavelengths, the beam quality had to improve. Using superconducting accelerator elements promised a great improvement in this challenge. Finally, the expectations have been fulfilled. The superconducting TESLA elements are able to generate a very thin and homogeneous electron beam which provides sufficiently high beam quality and electron currents for an advanced X-ray Free Electron Laser source of unprecedented peak brilliance<sup>1</sup> and full transverse coherence.

#### 3.1 HISTORICAL DEVELOPMENT OF THE EUROPEAN XFEL

In DESY, Hamburg, where the EuXFEL is constructed, there exists a lot of experience with constructing free electron lasers. The TESLA Test Facility for free electron experiments (TTF FEL) has been constructed in order to provide a linear accelerator with high quality electron beams. The TESLA Test Facility implemented a 100 m long linear accelerator which provides an electron beam with an electron energy of 233 MeV. Injected in an undulator, the first photon flashes have been generated by TESLA in 2000. The ultraviolet light flashes reached wavelengths down to 109 nm, a new world record at this time. By increasing the electron energy, the wavelength of the TESLA device could be further decressed down to wavelengths between 80 and 180 nm. By applying further optimizations for operation in the region between 80 nm to 120 nm, the maximum power gain of the order of  $\approx 10^7$  (saturation) could be reached over the entire wavelength range [11], [21], [32].

From this very promising device, a new test facility emerged. The Free Electron Laser in Hamburg (FLASH) was build with the goal to generate laser light of only 6 nm wavelength. The new 260 m accelerator increases the electron energy up to 1 GeV. By injecting this

<sup>&</sup>lt;sup>1</sup>Brilliance = [photons / s /  $mm^2$  /  $mrad^2$  / 0.1% bandwidth ]

#### 3. The European XFEL (EuXFEL)

high energy electron beam into the undulators of 30 m length, the FLASH device generates high intensive ultra short laser flashes of wavelengths in the ultraviolet and soft X-ray region. When FLASH became operational in 2005, the FEL already reached a wavelength of 32 nm [33] during SASE operation - a new world record. By further upgrades of the accelerator modules, the electron beam energy could be increased and therefore, the generated wavelength decreased. After the upgrade in 2007 the design goal of 6.5 nm has been reached for the first time. During the last upgrade in 2009/2010, when the electron beam energy was additionally increased to 1.25 GeV, an even shorter wavelength of 4.1 nm has been published [23]. This means a fundamental advancement, because this wavelength opens the insight into the so called water window, the wavelength range between 2.3 and 4.4 nm, in which water is nearly transparent for light. This can be used to investigate probes in liquid solutions like in vivo biological experiments.

These promising results and experiences from the TTF and FLASH systems led to the very ambitious plans to build the large EuXFEL.

#### 3.2 BASIC PARAMETERS OF THE EUXFEL

The previous achievements of X-ray FEL technology encouraged in 2007 the German government to start the development of the first superconducting X-ray FEL for ultra-short X-ray flashes and high repetition rates for life sciences and material research [34]. The construction started in 2009 in cooperation with the European Union, the state of Hamburg, Russia, Poland and 9 other contributing countries.

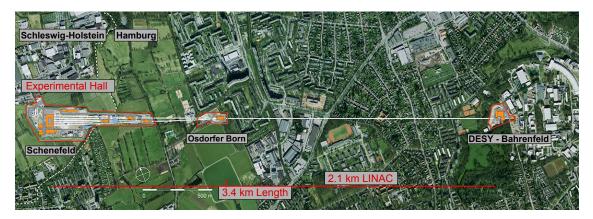

Figure 3.1.: Layout of the EuXFEL in Hamburg [8]. The machine is built in a 3.4 km long tunnel below Hamburg from DESY to the experimental hall in Schenefeld. Most of the tunnel is filled with the 2.1 km long superconducting LINAC, which accelerates the electron beam to 17.5 GeV. In Osdorfer Born, the beam is distributed and transported to the undulators, in which the X-ray radiation is generated. Finally, the X-rays are transferred to the beamlines in the experimental hall.

The main parts of the EuXFEL can be summarized as follows:

- the injector,

- the superconducting linear accelerator (LINAC),

- the beam distribution system,

- the photon beamlines,

- the 5 experimental stations.

The injector is based on a high quality radio frequency (RF) gun. Electrons are extracted from a photo cathode by a visible laser and then accelerated to 120 MeV. Beam focusing elements and diagnostic equipment is implemented to ensure the high beam quality as well as a low emittance and low energy spread.

The tunnel contains the long superconducting LINAC of 1.6 km length, which accelerates the electrons to energies of up to 20 GeV [31], while the nominal electron energy during operation is aimed at 17.5 GeV. Two stages of beam compressors shorten the electron bunches by a factor of 100 which increases the peak electron current to 5 kA. This high electron current is required to trigger the SASE process in the undulators. Further equipment is installed to align and collimate the electron beam.

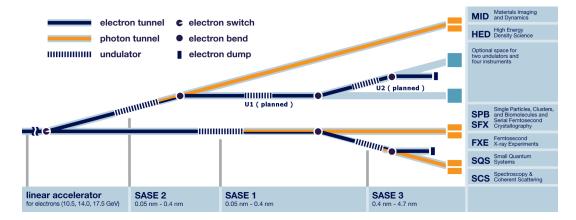

The beam distribution system at the output of the accelerator contains three very long high precision undulators. The SASE 3 undulator has a length of 100 m. SASE 1 and 2 even 200 m. Furthermore, the opening gap of each undulator can be varied providing certain tuneability of the wavelength of the generated laser pulses. Besides the three large SASE undulators, two smaller devices U1 and U2 for ultra short highly coherent X-ray radiation are planned in separate tunnels providing additional possibilities for high photon energy experiments.

Figure 3.2.: The beamlines at EuXFEL [31]. Five tunnels will provide spots for 10 different experiments. At commissioning, only three tunnels will be equipped. Each undulator is assembled from 5-meter-long segments. The strength of the magnetic fields and the distance between the magnetic rails can be changed which allows to tune the generated wavelength.

#### 3. The European XFEL (EuXFEL)

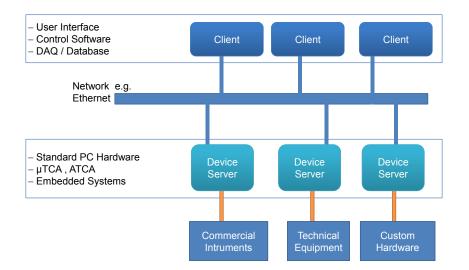

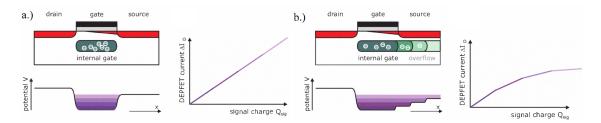

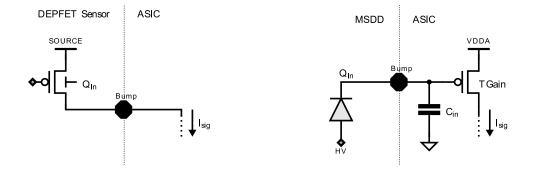

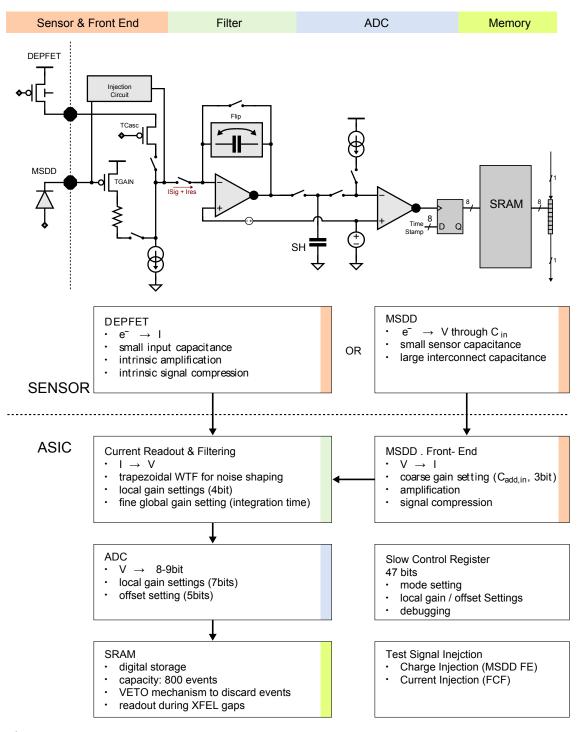

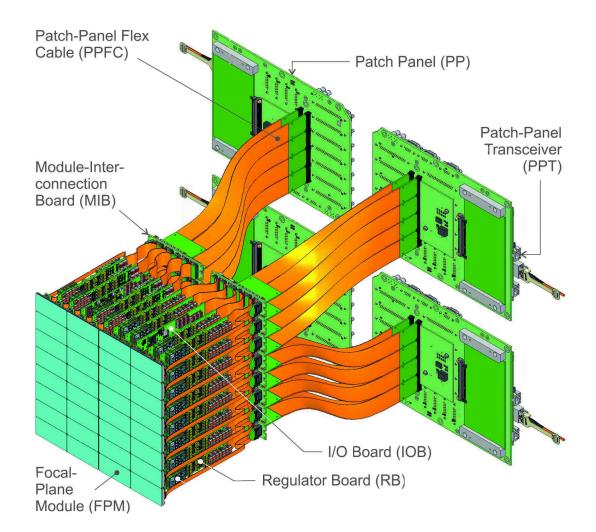

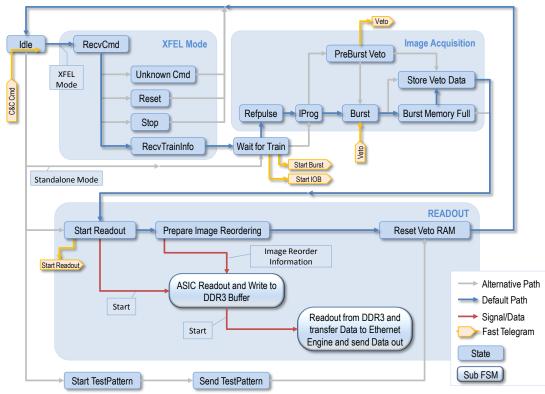

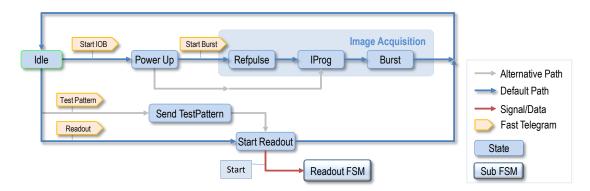

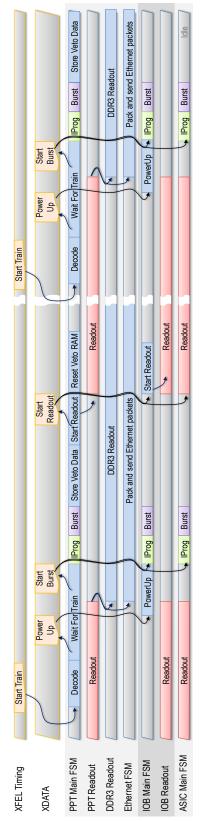

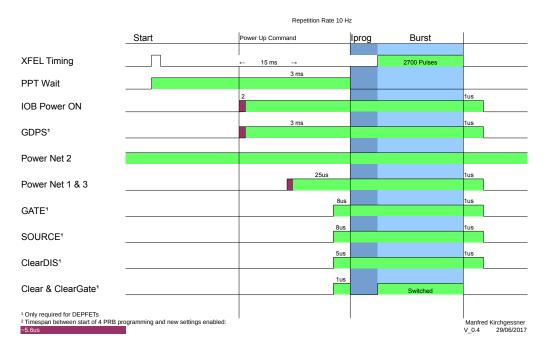

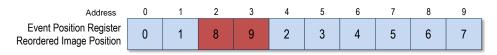

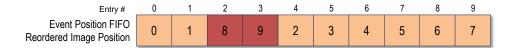

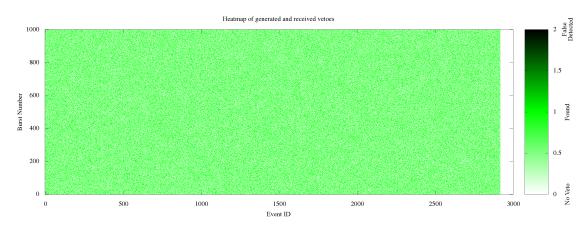

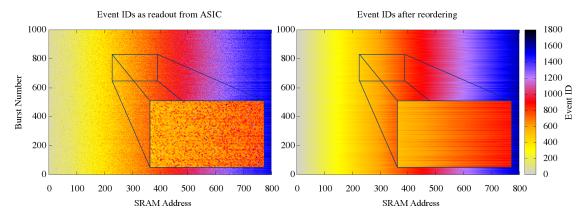

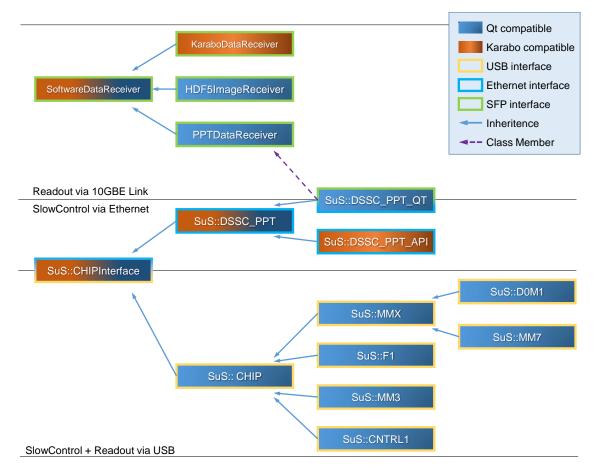

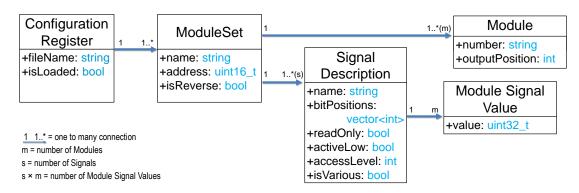

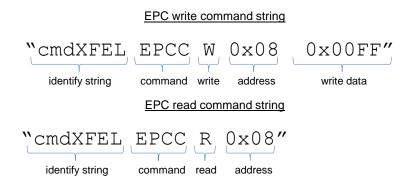

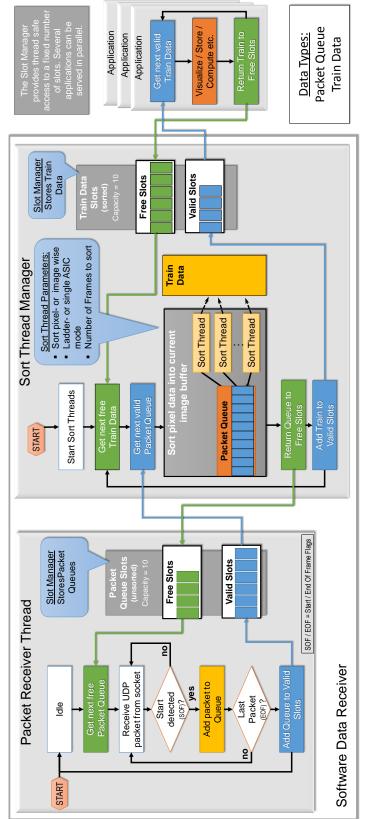

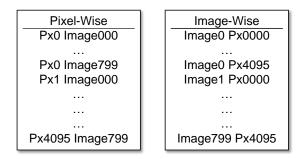

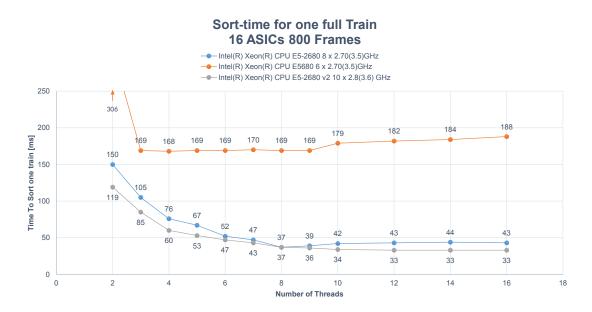

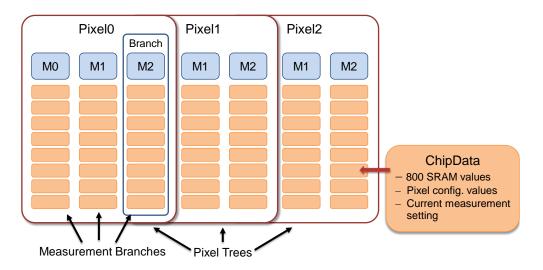

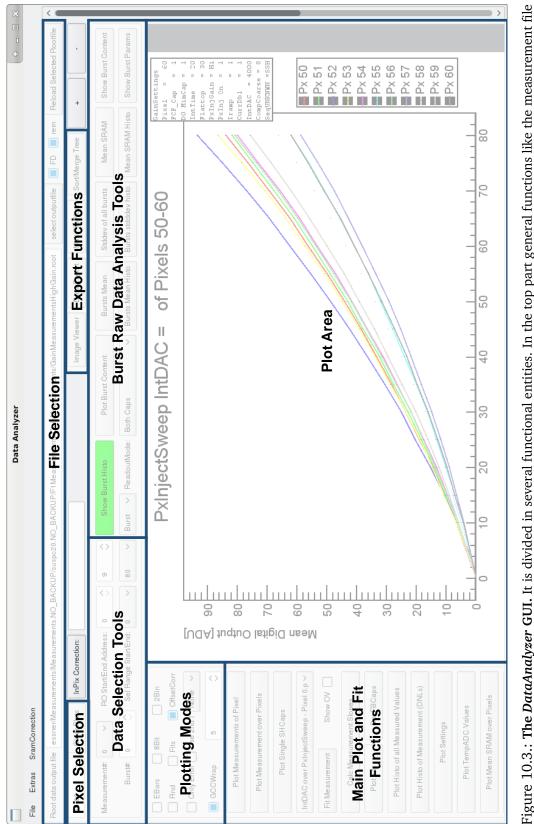

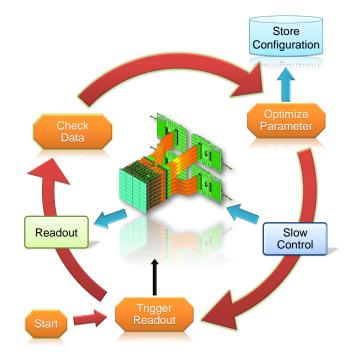

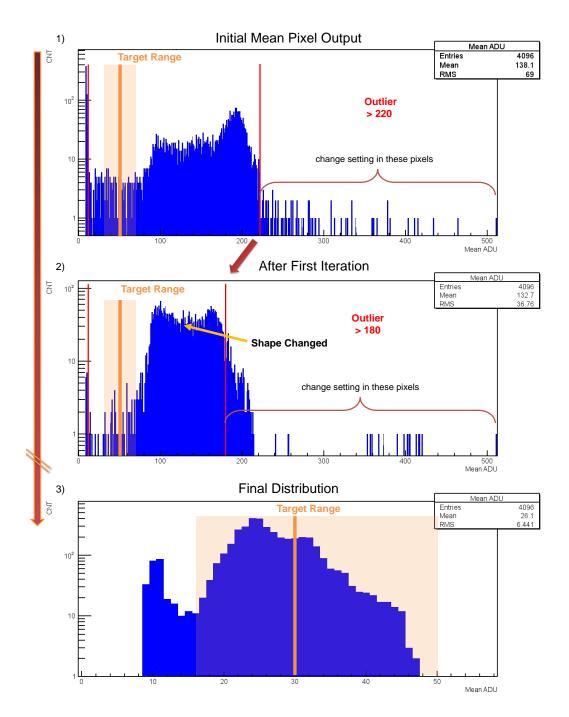

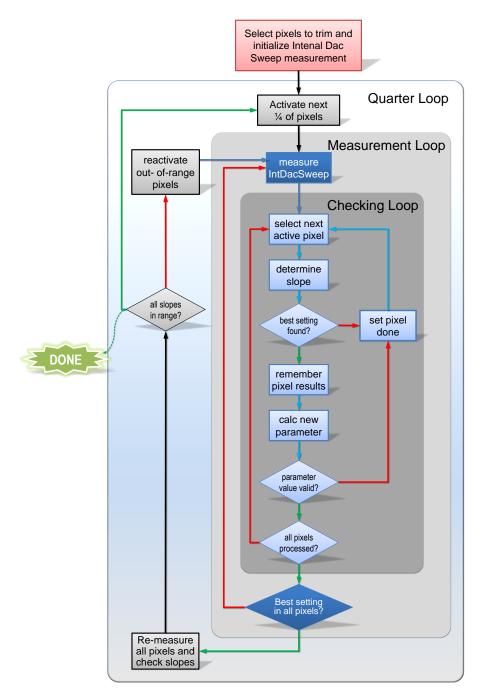

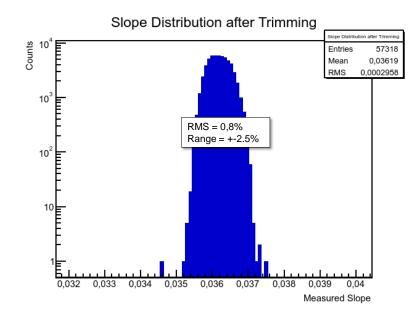

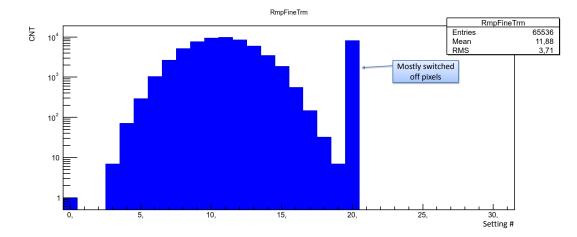

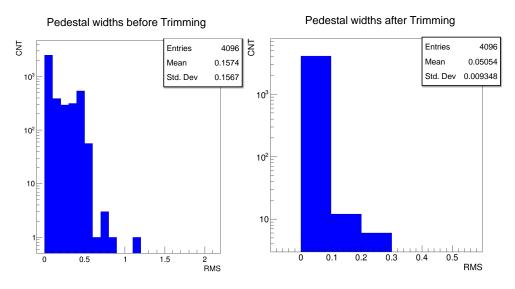

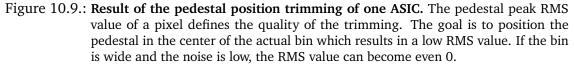

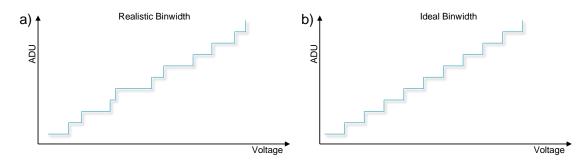

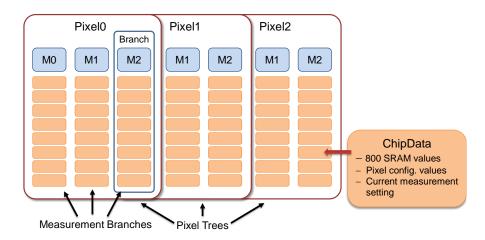

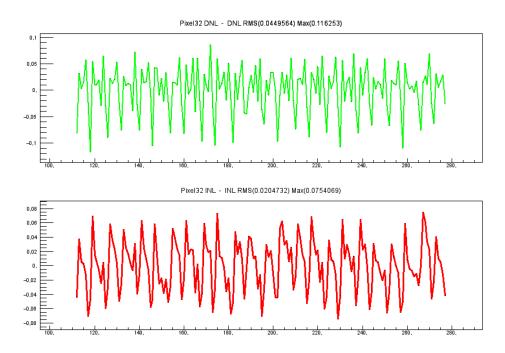

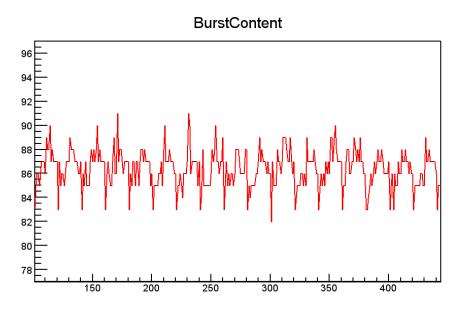

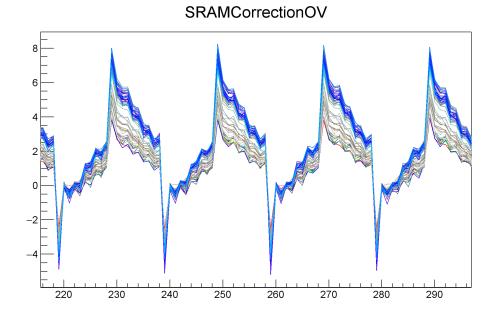

All five tunnels open out into the experimental hall. At each output, an experiment hutch provides space for 2 individual experiments.