# DISSERTATION

submitted to the

Combined Faculty of Natural Sciences and Mathematics

of the

Ruprecht–Karls University Heidelberg

for the degree of

Doctor of Natural Sciences

put forward by M.Sc. Juri Schmidt

born in Alexejewka, Kazakhstan

Mannheim, 2017

# Accelerating Checkpoint/Restart Application Performance in Large-Scale Systems with Network Attached Memory

Advisor: Professor Dr. Ulrich Brüning

Date of the oral examination: .....

To my beloved family

my parents Vera and Georg Schmidt

and my sister Ludmila Schmidt

# Abstract

Technology scaling and a continual increase in operating frequency have been the main driver of processor performance for several decades. A recent slowdown in this evolution is compensated by multi-core architectures, which challenge application developers and also increase the disparity between the processor and memory performance. The increasing core count and growing scale of computing systems furthermore turn attention to communication as a significant contributor on application run-times.

Larger systems also comprise many more components which are subject to failures. In order to mitigate the effects of these failures, fault tolerance techniques such as Checkpoint/Restart are used. These techniques often rely on message-based communication and data transport stresses the local memory interface. In order to reduce communication overhead it is desirable to either decrease the number of messages, or otherwise to accelerate the execution of commonly used global operations. Finally, power consumption of large-scale systems has become a major concern and the efficiency of such systems must considerably improve to allow future Exascale systems to operate within a reasonable power budget.

This work addresses the topics memory interface, communication, fault tolerance, and energy efficiency in large-scale systems. It presents Network Attached Memory (NAM), an FPGA-based hardware prototype that can be directly connected to a common high-performance interconnection network in large-scale systems. It provides access to the emerging memory technology Hybrid Memory Cube (HMC) as shared memory resource, tightly integrated with processing elements.

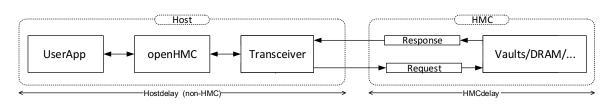

The first part introduces the HMC memory architecture and serial interface, and thoroughly evaluates it in an FPGA using a custom-developed host controller, which has become an open-source initiative.

The next part describes the hardware architecture of the NAM design and prototype, and theoretically evaluates the expected performance and bottlenecks. The NAM design

### Abstract

was fully prototyped in an FPGA and the contribution also comprises a corresponding software stack.

As a first use case NAM serves as Checkpoint/Restart target, aiming to reduce internode communication and to accelerate the creation of checkpoint parity information. Reducing checkpointing overhead improves application run-times and energy efficiency likewise.

The final part of this work evaluates the NAM performance in a 16 node test system. It shows a good read/write scaling behavior for an increasing number of nodes. For Checkpoint/Restart with a real application, a 2.1X improvement over a standard approach is a remarkable result. It proves the successful concept of a dedicated hardware component to reduce communication and fault tolerance overhead for current and future large-scale systems.

# Zusammenfassung

Der kontinuierliche Anstieg der Mikroprozessorleistung wurde über Jahrzehnte hinweg getrieben von immer feiner werdenden Halbleiterstrukturen sowie steigenden Taktraten. Die kürzlich beobachtete Verlangsamung dieser Entwicklung wird durch Multi-core Architekturen kompensiert. Diese erfordern parallelisierte Anwendungen und stellen Anwendungsentwickler und die Prozessor-Hauptspeicher Schnittstelle gleichermaßen vor große Herausforderungen. Der weiterhin fortwährende Trend zu immer größeren verteilten Systemen und die damit einhergehende Zunahme an Einzelkomponenten stellt insbesondere Anforderungen an das Verbindungsnetzwerk, sodass viele Anwendungen bereits heute viel Zeit mit reiner Kommunikation verbringen.

Größere Systeme erhöhen zugleich die Wahrscheinlichkeit für Defekte. Um deren negative Auswirkungen zu reduzieren und Defekte zu tolerieren, werden üblicherweise Checkpoint/Restart Mechanismen eingesetzt. Da diese zumeist auf Kommunikation zwischen einzelnen Knoten basieren und zusätzlich die Prozessor-Hauptspeicher Schnittstelle belasten, ist es sinnvoll entweder den Umfang der benötigten Kommunikation zu reduzieren oder deren Einfluss zu minimieren. Zu guter Letzt gewinnt auch die Leistungsaufnahme verteilter Systeme immer mehr an Bedeutung. Im Hinblick auf die Exascale-Ära ist es daher zwingend notwendig die Energieeffizienz bedeutend zu verbessern um den Leistungsverbrauch dieser Systeme in einem vertretbaren Rahmen zu halten.

Diese Arbeit geht auf die oben genannten Problematiken Speicherschnittstelle, Kommunikation, Fehlertoleranz und Energieeffizienz ein und stellt Network Attached Memory (NAM) vor. NAM ist ein Hardware Prototyp, der direkt an ein gängiges Hochleistungs-Verbindungsnetzwerk in verteilten Systemen angebunden werden kann. Es bietet Zugriff auf gemeinsamen Speicher, der durch die aufstrebende Hybrid Memory Cube (HMC) Technologie realisiert ist.

### Zusammenfassung

Der erste Beitrag umfasst die Vorstellung, Technologieanalyse und HMC Evaluation in einem FPGA mithilfe einer eigens entwickelten Zugriffseinheit, die als Open-Source Initiative frei zugänglich ist.

Der nächste Beitrag erläutert den Entwicklungsprozess und die Hardwarearchitektur des NAM Designs und Prototypen und ermittelt die Leistung theoretisch. Das NAM Design wurde hierfür vollständig in einem FPGA implementiert und durch die für den Zugriff notwendigen Softwarekomponenten ergänzt.

In einem ersten Anwendungsfall dient der NAM als Beschleuniger für Checkpoint/Restart Prozesse mit dem Ziel, Kommunikation zwischen Knoten zu verringern und die benötigte Paritätsinformation schneller zu berechnen. Dies wird sich Vorteilhaft auf Anwendungslaufzeiten und Energieeffizienz auswirken.

Der letzte Beitrag beinhaltet verschiedene Leistungsmessungen in einem realen 16 Knoten System. Diese zeigen optimale Skalierbarkeit für Lese- und Schreibzugriff. Für Checkpoint/Restart wird eine bemerkenswerte, 2.1-fache Beschleunigung erreicht. Dieses Resultat belegt das erfolgreiche NAM Konzept zur Reduktion von Kommunikation und des Berechnungsaufwands für Fehlertoleranz in aktuellen und zukünftigen Systemen.

# Contents

| 1 | Introduction |          |                                                     |   |  |  |

|---|--------------|----------|-----------------------------------------------------|---|--|--|

|   | 1.1          | Motiva   | $\operatorname{ation}$                              | 3 |  |  |

|   | 1.2          | Vision   |                                                     | 4 |  |  |

|   | 1.3          | Contri   | ibutions                                            | 5 |  |  |

|   | 1.4          | Outlin   | le                                                  | 6 |  |  |

| 2 | Stat         | te of tl | he Art                                              | 7 |  |  |

|   | 2.1          | Memo     | ry: Technologies and Interfaces                     | 7 |  |  |

|   |              | 2.1.1    | Latency                                             | 9 |  |  |

|   |              | 2.1.2    | Bandwidth                                           | 0 |  |  |

|   |              | 2.1.3    | Power                                               | 1 |  |  |

|   |              | 2.1.4    | Emerging Memory Technologies                        | 1 |  |  |

|   |              | 2.1.5    | Serial Interfaces                                   | 3 |  |  |

|   |              | 2.1.6    | Processing in Memory 13                             | 3 |  |  |

|   |              | 2.1.7    | Summary Memory                                      | 4 |  |  |

|   | 2.2          | Comm     | nunication in HPC systems                           | 4 |  |  |

|   |              | 2.2.1    | Interconnection Networks                            | 5 |  |  |

|   |              | 2.2.2    | Message Passing and Communication Characteristics 1 | 7 |  |  |

|   |              | 2.2.3    | Summary Communication                               | 9 |  |  |

|   | 2.3          | Fault    | Tolerance in HPC Systems                            | 0 |  |  |

|   |              | 2.3.1    | Failure Causes    2                                 | 1 |  |  |

|   |              | 2.3.2    | Fault Tolerance using Checkpoint/Restart            | 2 |  |  |

|   |              | 2.3.3    | SCR: Scalable Checkpoint / Restart                  | 4 |  |  |

### Contents

|   |     | 2.3.4  | Summary Fault Tolerance                                                                                                                 | 3 |

|---|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 2.4 | Summ   | ary                                                                                                                                     | 3 |

| 3 | Hyb | orid M | emory Cube 31                                                                                                                           | L |

|   | 3.1 | Introd | uction and Architecture Analysis                                                                                                        | 1 |

|   |     | 3.1.1  | Architecture                                                                                                                            | 2 |

|   |     | 3.1.2  | DRAM Organization and Performance                                                                                                       | 3 |

|   |     | 3.1.3  | Link                                                                                                                                    | 1 |

|   |     | 3.1.4  | Chaining                                                                                                                                | 5 |

|   |     | 3.1.5  | $Protocol \dots \dots$            | 3 |

|   |     | 3.1.6  | The Flow Control Barrier                                                                                                                | 7 |

|   |     | 3.1.7  | Summary HMC Architecture                                                                                                                | 1 |

|   |     | 3.1.8  | Outlook                                                                                                                                 | 2 |

|   |     | 3.1.9  | Lessons learned for an HMC host controller design                                                                                       | 3 |

|   | 3.2 | openH  | $IMC Host Controller \dots \dots$ | 1 |

|   |     | 3.2.1  | Configurations and Features                                                                                                             | 1 |

|   |     | 3.2.2  | Operating Frequencies                                                                                                                   | 3 |

|   |     | 3.2.3  | Flow Control and Performance                                                                                                            | 3 |

|   |     | 3.2.4  | Comparison with other IPs                                                                                                               | 7 |

|   |     | 3.2.5  | ASIC Implementation                                                                                                                     | 3 |

|   | 3.3 | HMC    | Performance Evaluation                                                                                                                  | 3 |

|   |     | 3.3.1  | Metrics                                                                                                                                 | ) |

|   |     | 3.3.2  | Test Setup                                                                                                                              | ) |

|   |     | 3.3.3  | Access Patterns                                                                                                                         | 1 |

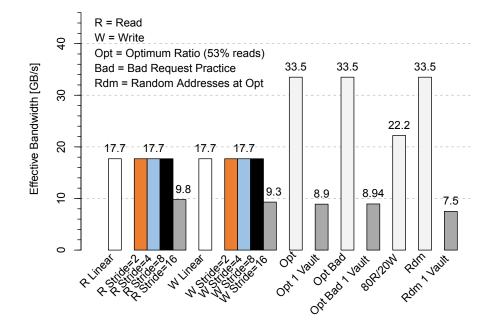

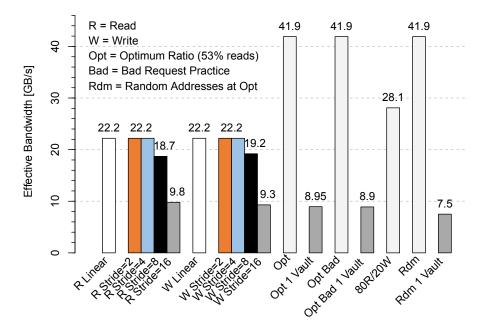

|   |     | 3.3.4  | Bandwidth $\ldots \ldots 53$          | 3 |

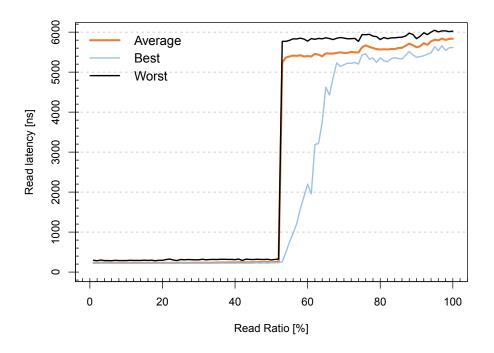

|   |     | 3.3.5  | Latency                                                                                                                                 | 3 |

|   |     | 3.3.6  | Atomic Operations                                                                                                                       | 3 |

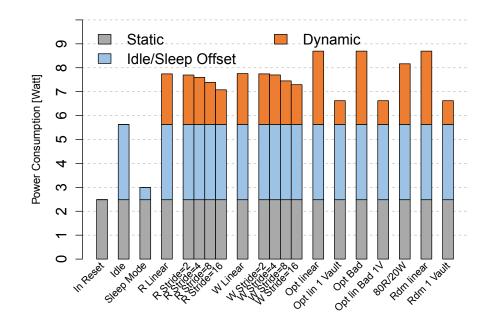

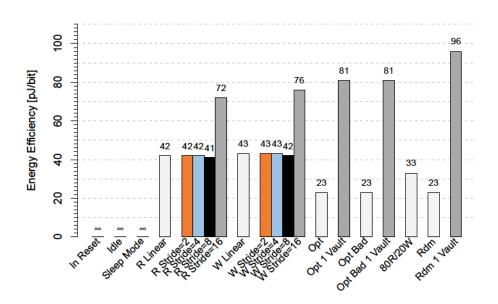

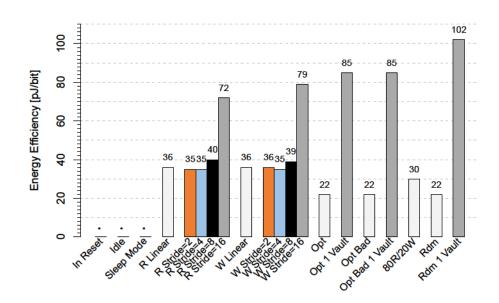

|   |     | 3.3.7  | Power Consumption and Energy Efficiency                                                                                                 | ) |

|   |     | 3.3.8  | Summary Performance Evaluation                                                                                                          | 2 |

|   | 3.4 | HMC    | Summary                                                                                                                                 | 1 |

| 4 | Net | work 4 | Attached Memory                          | 65  |

|---|-----|--------|------------------------------------------|-----|

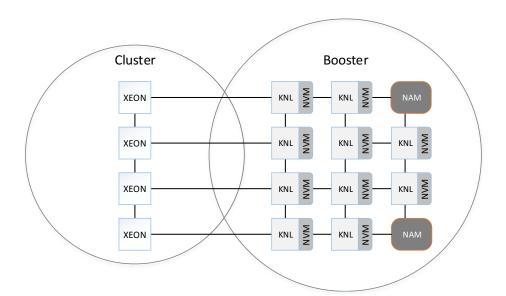

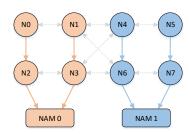

|   | 4.1 | DEEF   | P-ER Project                             | 66  |

|   | 4.2 | Backg  | round: EXTOLL                            | 66  |

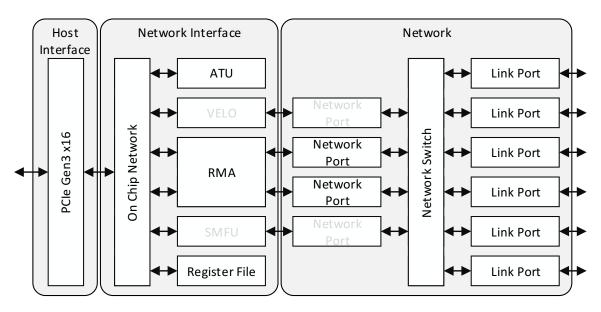

|   |     | 4.2.1  | Functional Units and Link Performance    | 68  |

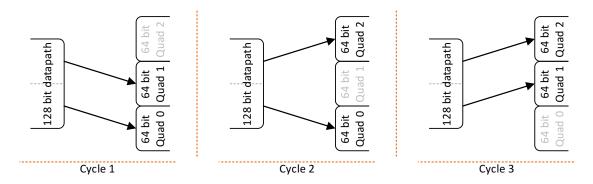

|   |     | 4.2.2  | From Software to Network Transactions    | 70  |

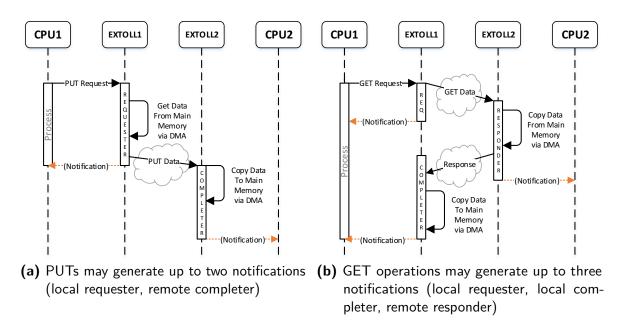

|   |     | 4.2.3  | Notification Mechanism                   | 70  |

|   |     | 4.2.4  | Network Protocol                         | 71  |

|   |     | 4.2.5  | Link Flow Control                        | 72  |

|   |     | 4.2.6  | EMP: Network Discovery and Setup         | 73  |

|   | 4.3 | NAM    | Hardware                                 | 73  |

|   |     | 4.3.1  | Requirements                             | 73  |

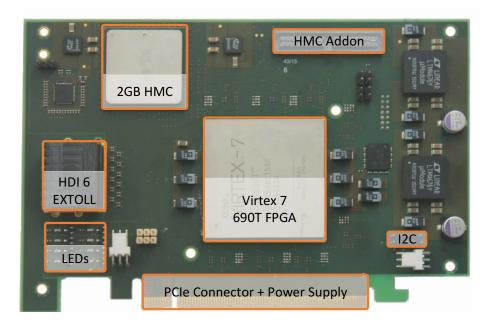

|   |     | 4.3.2  | Prototype 'Aspin-v2'                     | 75  |

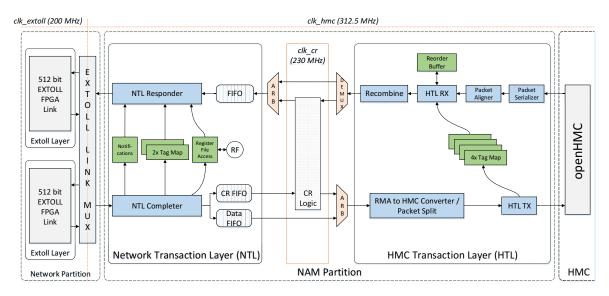

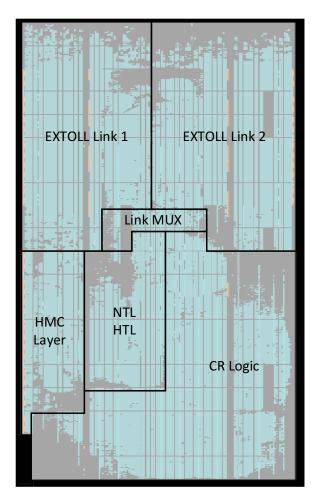

|   |     | 4.3.3  | FPGA Design Partitions                   | 77  |

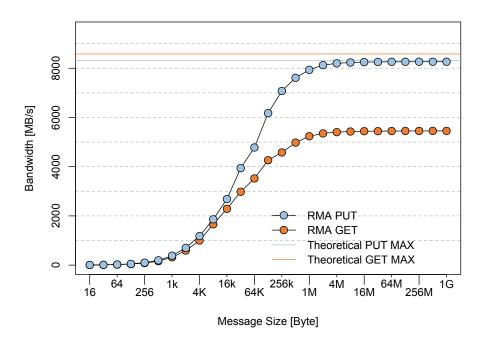

|   | 4.4 | Summ   | ary Estimated Read/Write Performance     | 92  |

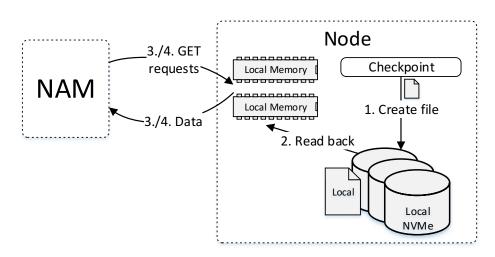

|   | 4.5 | Check  | point/Restart                            | 93  |

|   |     | 4.5.1  | Buddy Checkpointing in DEEP-ER           | 94  |

|   |     | 4.5.2  | Definitions                              | 95  |

|   |     | 4.5.3  | Design Space Exploration                 | 96  |

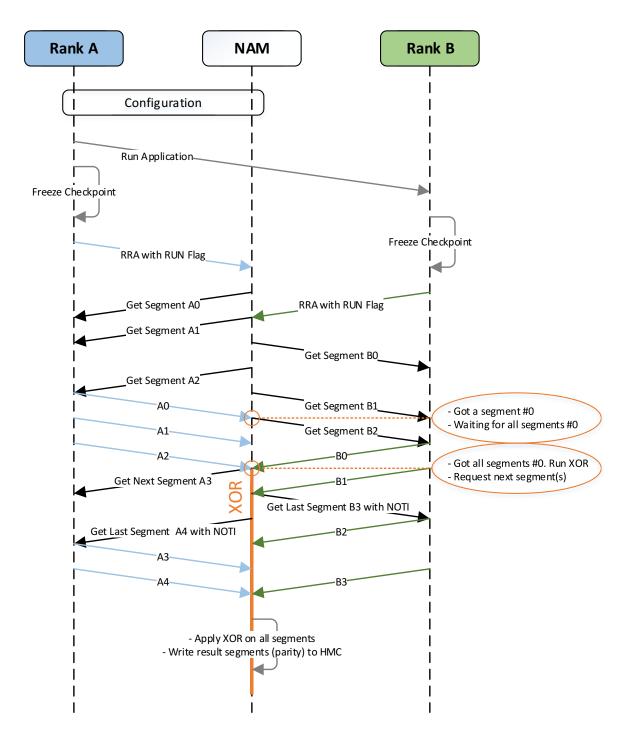

|   |     | 4.5.4  | Vision: NAM-XOR Checkpointing in DEEP-ER | 97  |

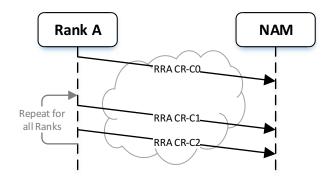

|   |     | 4.5.5  | Configuration                            | 98  |

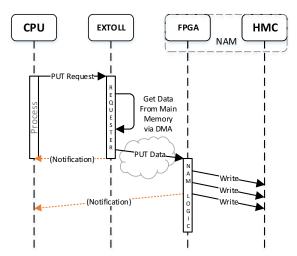

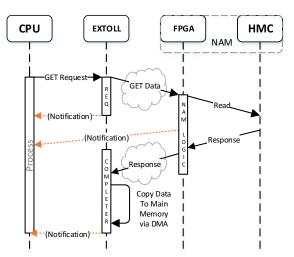

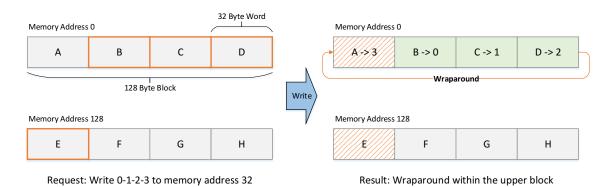

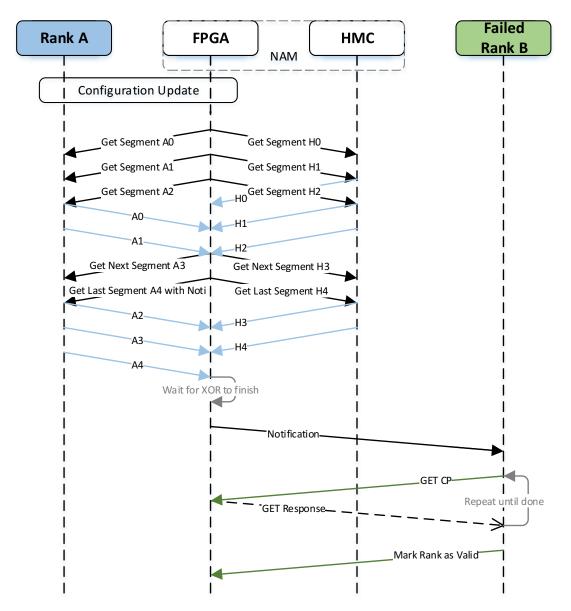

|   |     | 4.5.6  | Generating a Checkpoint                  | 99  |

|   |     | 4.5.7  | Restarting from a Checkpoint             | 99  |

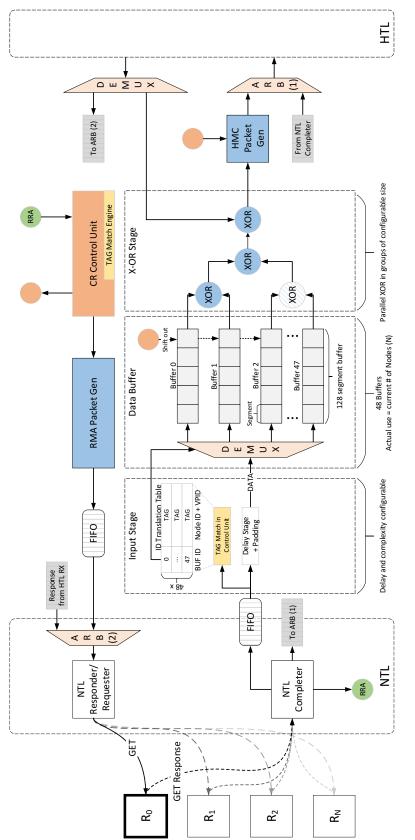

|   |     | 4.5.8  | CR Functional Unit                       | 101 |

|   |     | 4.5.9  | Estimated Performance                    | 101 |

|   | 4.6 | Imple  | mentation Results                        | 104 |

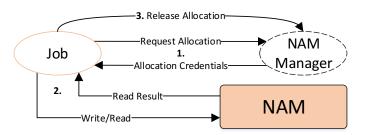

|   | 4.7 | NAM    | Software                                 | 105 |

|   |     | 4.7.1  | EMP Extension                            | 106 |

|   |     | 4.7.2  | The libNAM Library                       | 106 |

|   |     | 4.7.3  | NAM Manager                              | 108 |

|   | 4.8 | NAM    | Summary                                  | 109 |

## Contents

| <b>5</b>     | NA                    | M Per                        | formance Evaluation        | 111   |  |

|--------------|-----------------------|------------------------------|----------------------------|-------|--|

|              | 5.1                   | Write Microbenchmark Results | . 111                      |       |  |

|              |                       | 5.1.1                        | Single Link Performance    | . 112 |  |

|              |                       | 5.1.2                        | Two Link PUT/GET Bandwidth | . 115 |  |

|              |                       | 5.1.3                        | Analysis and Improvements  | . 116 |  |

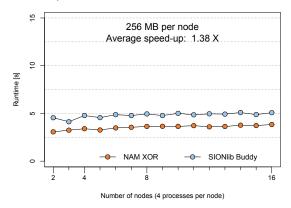

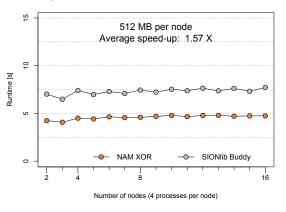

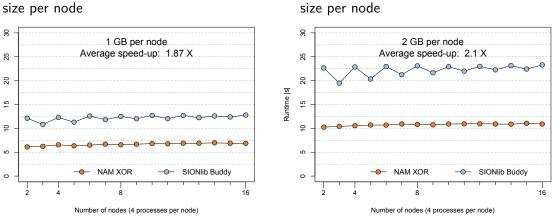

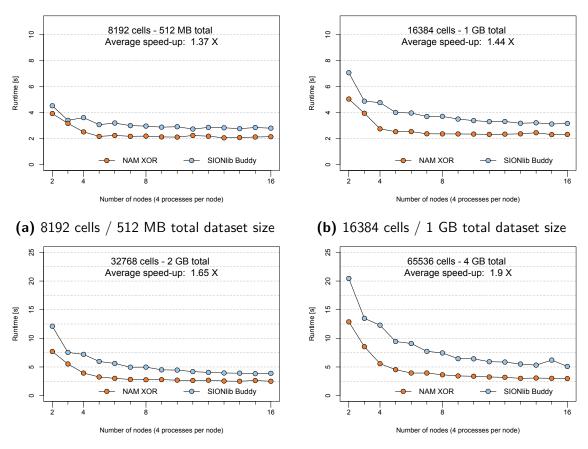

|              | 5.2                   | Check                        | point/Restart              | . 117 |  |

|              |                       | 5.2.1                        | Microbenchmark Results     | . 118 |  |

|              |                       | 5.2.2                        | Application Performance    | . 121 |  |

|              | 5.3                   | Perform                      | mance Summary              | . 125 |  |

| 6            | Con                   | clusio                       | n and Outlook              | 127   |  |

|              | 6.1                   | Improv                       | vements                    | . 129 |  |

|              | 6.2                   | Outloo                       | bk                         | . 130 |  |

| $\mathbf{A}$ | Acr                   | onyms                        |                            | 133   |  |

| в            | $\operatorname{List}$ | of figu                      | ıres                       | 137   |  |

| С            | C List of tables      |                              |                            |       |  |

| R            | Refe                  | erences                      | 5                          | 143   |  |

CHAPTER

# Introduction

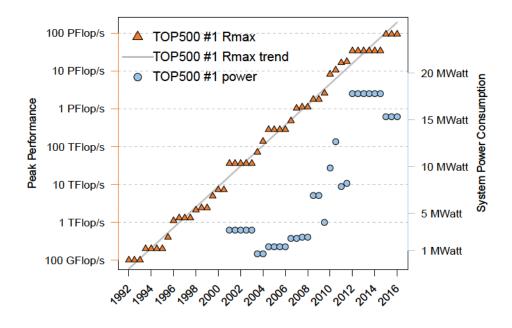

For many years, the increase in processor and system performance was driven by technology scaling which allowed to pack more transistors per area at a fixed power budget. Increasing operating frequencies supported the improvements of single thread performance accordingly. Since the early 2000's, however, this continual increase has slowed down due to excessive power dissipation, which is also caused by the leakage current of today's tiny transistor feature sizes. Multi-core architectures were developed to keep up with the traditional growth rate, and system performance was scaled by adding more and more components and nodes. Although these new architectures pose challenges to application developers as it requires carefully parallelized codes, the overall system performance kept increasing at a moderate rate. This is documented in Figure 1.1 which shows the evolution of the number 1 systems of the TOP500 list of supercomputers.

At a first glance the current trend gives no indication that there is something wrong at all, especially not with the memory system. This is because the TOP500 LINPACK benchmark in large parts is insensitive to memory performance and re-uses data that remains in registers and caches instead [1]. In reality, however, memory access times and bandwidth lag behind the historical evolution of CPU performance. This disparity is well known as the memory wall [2] and the gap is widening with the recent and ongoing increasing number of CPU cores per socket that operate on the same memory interface.

Fig. 1.1 TOP500 number 1 system performance and power development<sup>1</sup>

Despite the lag in memory evolution, large-scale systems continually achieved extraordinary performance gains. Fundamental for this development has been a steady increase in component and node count, with the current number 1 TOP500 system comprising more than 10 million cores<sup>1</sup>. Communication between two or more cores is typically realized via message passing and unless an application is perfectly parallel, inter-process communication will take place. Hence, whenever a message is sent or received across node boundaries it also involves the interconnection network. Work in [3] shows that current large-scale applications spend an average of 36% of their runtime with point-to-point communication and waiting for collective operations to complete. It will be shown that the interconnection networks for their part substantially improved over the last decade and other approaches to mitigate the overhead through inter-process communication must be developed.

One additional and underestimated drawback of system scaling is its impact on the system's error rates, or Mean Time Between Failure (MTBF). Hardware faults are among the most common causes for system crashes and every single additional component potentially decreases the average time between two failures. For an Exascale machine it is predicted that it will comprise about 260 thousand nodes (134 million cores) [4], that is about 6 times more nodes (12 times more cores) than in the current

<sup>&</sup>lt;sup>1</sup> Data collected via the TOP500 statistics sublist generator (www.top500.org/statistics/sublist).

number 1 TOP500 system. Unless the per-component MTBF will significantly drop, systems will continue to fail even more frequently in the future. In order to properly recover from failures, resilience and fault tolerance mechanisms play an important part in modern large-scale systems. These features are typically implemented by periodically storing the application's or system state to disk. The checkpoint may then be restored upon a system failure in order to reduce the amount of work lost. The obvious disadvantage is that checkpoints are created whether or not there is an actual failure. This process requires application time as well as memory and network bandwidth, and can cause applications to execute more than 10 times slower [5].

Finally, power has become a main concern of today's and future large-scale systems. Main memory in particular is one of the largest consumers with up to 40 % for a current system [6] and a projected 65 % at Exascale [7]. Inter-process communication and fault tolerance mechanisms additionally reduce the actual work that can be done within a given time period, which negatively impacts the system's energy efficiency. To allow future Exascale systems to operate within an economically and practically reasonable power budget it was suggested to limit the power consumption of such a system to 20 MWatt [7, 8]. As can be seen in Figure 1.1, the current number 1 system already consumes more than 15 MWatt at less than 100 PFLOP/s peak performance. The mandatory need for a change of the system architecture becomes clear when this system was scaled to Exascale. At 1 Exaflop per second it would consume about 150 MWatt which exceeds the 20 MWatt goal by a factor of 7.5.

In summary, the challenges on the road to Exascale machines are best described by the following quote:

> The architectural challenges for reaching Exascale are dominated by power, memory, interconnection networks, and resilience.

> > - Richard C. Murphy et. al. (2010) [9]

# 1.1 Motivation

The motivation for this work is based on the following three key observations:

#### The Processor-Memory Gap

The memory interface is one of the last parallel buses and probably the most

#### Introduction

critical bottleneck in modern computing systems. The disparity between processor and memory performance is ever increasing and the situation got worse with the introduction of multi-core architectures. Since no technological breakthroughs are expected in the near future, it is time to revisit the memory interface and evaluate alternatives.

#### Inter-Node Communication

Large-scale systems typically communicate via message passing and data must be transported between two or more nodes whenever the communicating processes are spread across distinct nodes. While some applications mainly rely on pointto-point communication, others spend a lot of time in processing and waiting for the completion of collective operations. Most often the memory interface is involved in collective operations as it holds the data elements that are placed and retrieved by processors and the interconnection network. It is desirable to either reduce the number of messages that are sent or otherwise to increase the performance of point-to-point and collective communication.

#### Fault Tolerance

With an increasing number of components in large-scale systems, and without a significant improvement in component reliability, the MTBF will continue to drop and the frequency of catastrophic failures will increase. To mitigate the effects of such failures, to reduce the amount of work lost, and to allow rapid system recovery, today's systems deploy fault tolerance techniques using Checkpoint/Restart. Unfortunately, checkpointing introduces additional overhead and can take up a large amount of the application runtimes. Parity checkpoints were introduced to lower the overhead at the expense of computation and communication, which heavily utilizes processors and the memory and storage system. It is therefore necessary to investigate in innovative approaches to reduce the overhead in order to speed-up the parity creation process.

# 1.2 Vision

As the types of hardware and interfaces in computing systems are standardized and systems are built from commercial off-the-shelf components, the only way to achieve improvements in the areas mentioned above is a dedicated hardware component. The ideal candidate avoids slow memories, offloads processors from computing collective

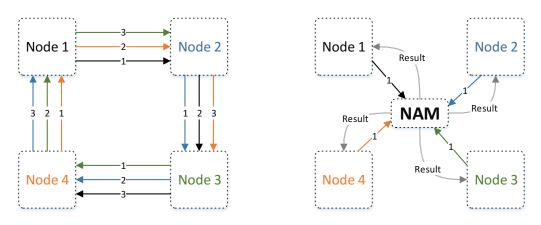

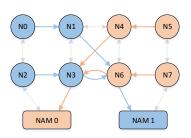

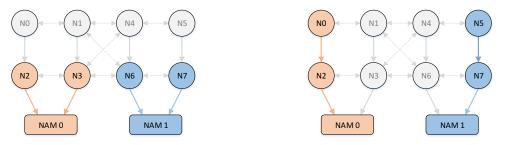

(a) Example traditional scheme: A collective(b) Envisioned scheme: NAM as central inoperation is implemented as a ringstance to execute collective operations

Fig. 1.2 NAM Vision: Reduce communication and offload processor computation

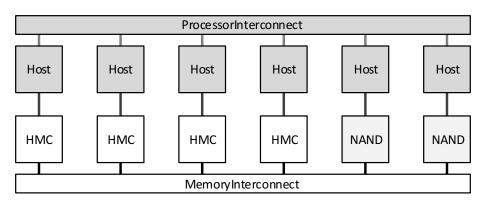

operations, reduces communication and synchronization effort, and provides sufficient bandwidth to serve as target for as many processes and nodes as possible. Figure 1.2 envisions how such a component, integrated with an existing interconnection fabric, is meant to improve collective operations by reducing inter-node communication and associated memory accesses. This general approach can be transferred to Checkpoint/Restart which in large parts relies on these patterns.

# 1.3 Contributions

This work presents the implementation of the Network Attached Memory, a dedicated component to serve as a global shared storage and to carry out collective operations in large-scale systems. It therefore employs network interfaces that provide the ability to connect it to available links within the EXTOLL high-performance interconnection network.

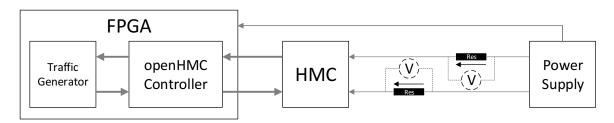

Based on the motivation to replace the current parallel memory interfaces with a flexible and serial one, the NAM prototype implements the emerging Hybrid Memory Cube memory interface. The HMC performance and power efficiency is analyzed and evaluated in an FPGA (Field Programmable Gate Array) using a custom host controller. This contribution comprises conference publications [10, 11] and the well adopted open-source initiative openHMC [12].

#### Introduction

The developed FPGA design implements links to the EXTOLL network and the HMC. It provides modules for read and write operations from remote hosts from and to the HMC memory on the NAM. A checkpointing module improves Checkpoint/Restart mechanisms that are typically deployed in today's systems. It aims to reduce the communication and synchronization overhead between participating nodes and shall offload processors from calculating the corresponding parity information. This contribution has led to news articles [13, 14] and a conference poster [15].

Finally, the performance of the NAM for reading and writing, and for the Checkpoint/Restart (CR) use case is evaluated in a 16 node test system. The results show that CR with the NAM outperforms a current approach by a factor of 2.1.

# 1.4 Outline

The remainder of this work is organized as follows: The next chapter covers the three relevant topics memory, inter-node communication, and fault tolerance. The discussion supports the need to revisit the memory interface and indicates that a dedicated hardware may be able to mitigate the excessive overhead in communication and fault tolerance. Chapter 3 presents the Hybrid Memory Cube (HMC) interface and technology in detail. Using a self-developed host controller, the HMC performance is characterized with real system measurements. Chapter 4 describes the development of the Network Attached Memory (NAM) hardware prototype. It provides network interfaces and integrates an HMC. The implemented FPGA design units are presented and the theoretical NAM performance is evaluated. As a first use case, the NAM improves the creation of parity checkpoints in the DEEP-ER (Dynamical Exascale Entry Platform - Extended Reach) project. The chapter is concluded by a description of the Checkpoint/Restart process and the developed software components. Chapter 5 evaluates the NAM in a 16 node real system setup with microbenchmarks and a DEEP-ER application mockup. The last chapter summarizes and reflects the obtained results and suggests improvements for a future NAM implementation.

CHAPTER

# State of the Art

Today's large-scale systems suffer from various limitations often caused by only very few components. As this trend is expected to intensify in the future, and in order to develop potential solutions, it is necessary to understand the reasons behind these limitations.

The first section of this chapter describes the historical evolution and current trends in the main memory development, and motivates the adoption of serial interfaces as one solution for most of the issues presented. Next, based on the prevalent software and hardware components, the communication in High Performance Computing (HPC) systems is analyzed. The third section presents currently deployed fault tolerance techniques which will gain even more importance with increasing system sizes. A final summary that puts these three topics into context concludes this chapter.

# 2.1 Memory: Technologies and Interfaces

For many years the increase in CPU (Central Processing Unit) performance was driven by Moore's law which was initially formulated in 1965 [16]. It predicts that the transistor count in microprocessors will double every 18 to 24 months, and this prediction remained true for about four decades. Although recently a slowdown can be

#### State of the Art

observed, device manufacturers found ways to keep increasing the transistor count at a moderate rate.

One processor characteristic that has stopped scaling, however, is the internal operating frequency. This is due to the reason that transistor power consumption is proportional to frequency and the power density increases as more transistors are packed per area. Also, with smaller transistors, leakage current becomes significant which causes the processor to dissipate power and heat at an increasing rate. This has led to the end of the well-known *Dennard scaling* [17] which states that power consumption remains proportional to the chip area.

To keep up with the traditional performance growth rate of CPUs, multi-core architectures were developed and current devices integrate as many as 72 cores on a single die [18].

One component that historically lags behind processor performance is the Dynamic Random-Access Memory (DRAM)-based main memory. Although it was formulated more than 20 years ago, the current situation is very well summarized by the following quote [19]:

Across the industry, today's chips are largely able to execute code faster than we can feed them with instructions and data. There are no longer performance bottlenecks in the floating point multiplier or in having only a single integer unit. The real design action is in memory subsystems—caches, buses, bandwidth, and latency. — Richard Sites: It's the Memory, Stupid! (1996)

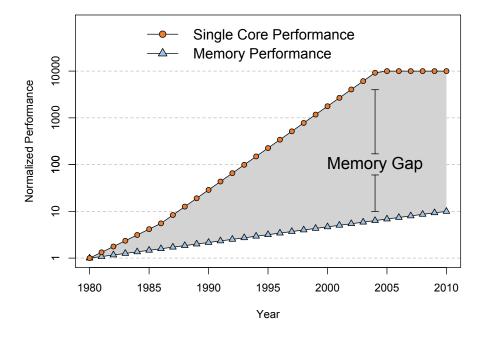

Similar to CPUs, DRAM obeyed Moore's law for a long time and only recently a slowdown in capacity growth is observed. Much more critical than the capacity, however, is the access time for a memory reference to the off-chip main memory. While the relative single core CPU performance increased by a factor of 10.000 in 30 years, the vast increase in peak memory accesses outperforms the capabilities of the memory interface. More specific, the DRAM access latency relative to the number of CPU cycles it takes to serve a memory reference only improved by a factor of eight. Within the same time period access times decreased from 250 ns in 1980 to 31 ns in 2012 [20]. Figure 2.1 illustrates this disparity in performance which is well-known as the *memory wall* [2]. Although the historical development and current trend for the performance of the number 1 system in TOP500 list of supercomputers gives only small indication that memory performance may be critical at all, it is and will remain a serious matter.

Fig. 2.1 Historical trend of the processor-memory gap [20]

The reason why in particular the TOP500 list is not suitable to discover a memory bottleneck is because of the benchmark it uses to characterize systems. The LINPACK benchmark is very insensitive to memory performance [1] which certainly does not accurately reflect the majority of HPC applications. It was also shown that future application codes will be much more memory sensitive [21].

## 2.1.1 Latency

The recognition of the memory wall led to the introduction of caches and hierarchies of caches in many variants and with various levels to hide the latency from a processor view. Caches rely on the concept of temporal (a memory reference is likely to be used more than once) and spatial locality (multiple accessed memory references are within relatively close storage locations). Hence, caching tries to avoid accessing the relatively slow physical memory interface by holding data in processor-local structures. Eventually, data still needs to be transported over the memory interface with potentially many independent processor cores competing for access. This increases the probability of cache misses and leads to additional, latency and bandwidth-wise expensive main memory accesses. And even if there was only one process to access the memory it might be limited by the interface latency if an application is not able to exploit locality for its memory references.

Although smaller and faster transistors typically help latency, the increasing number of transistors per area and additional memory chips to maximize capacity also result in longer channel distances. These longer traces and higher fan-outs naturally increase the signal latency and limit the switching speed on these lines. Also, the focus of the DRAM semiconductor process has shifted away from maximizing performance to increasing the capacity and reducing the memory cell's leakage current which is critical with today's small feature sizes. As the author in [22] states, the terms bandwidth and capacity are much easier to sell than latency marketing wise, and yet another reason why latency has been missing significant improvements.

# 2.1.2 Bandwidth

The situation with memory bandwidth is less critical than with latency although Double Data Rate (DDR) as the most commonly used main memory interface also lags behind the requirements of modern processors. For example, an Intel Core i7 CPU with four cores can generate memory references that require a peak bandwidth of 409.6 GB/s [20]. The actual requirement can be even higher as peripheral devices may also request access to main memory via Direct Memory Access (DMA). In contrast, a current DDR4 module provides 25 - 30 GB/s [20].

The main reason for this disparity is that the main memory interface has not seen meaningful changes in more than 30 years. Although each new generation of DRAM modules came with a slightly modified layout (which also required new processor generations), it is one of the last parallel interfaces in modern computing systems. Performance gains were achieved by widening the interface, increasing the pin speeds, and the introduction of DDR signaling and prefetch mechanisms. Adding more memory modules for multi-channel operation remains another viable option but its scaling behavior is limited by the excessive use of processor I/O pins, Printed Circuit Board (PCB) routing issues and a lack of physical space to place the additional components on a board.

Other approaches examined the feasibility of memory latency reduction (which correlates with a bandwidth increase) by either improving the memory access scheduling for multiple cores [23] or asynchronously reorganizing the DRAM banks within a memory chip [24]. And finally, to address the rapidly growing mobile and graphics card market, derivatives of the DDR interface were developed. These are tailored to the varying requirements of the power oriented mobile market (Low Power Double Data Rate (LPDDR) [25]) and bandwidth-hungry graphics cards (Graphics Double Data Rate (GDDR) [26]). All of these variants, however, are still limited by the memory interface bottleneck which needs to be revisited.

# 2.1.3 Power

Aside from the memory performance, power consumption of large-scale systems increasingly moves into focus and the memory system plays an important role in this observation. An analysis of a high-end IBM server in [6] showed that memory consumes as much as 40 % of the overall system power and this trend is also observed with current graphics cards [27].

To keep the power requirements of future Exascale systems within a reasonable budget it was decided that such systems should not exceed a total of 20 MWatt [7, 8]. Projections in [7] show that this goal is ambitious and challenging. The authors scale a current large-scale system to Exascale size and predict the power consumption considering technology improvements that enhance efficiency. The outcome of this experiment is that such a system would consume 70 Megawatt. More interestingly, the memory is the largest consumer with over 65 % of the total consumption.

Clearly, memory and in particular its interface will remain one of the most important targets for optimization for current and future systems. To bridge the gap until a new technology with the potential to replace DRAM as main memory hits the market, memory manufacturers recently started proposing alternative interfaces. Additionally, advances in the semiconductor manufacturing process have made layer stacking and heterogeneous stacks a viable option.

# 2.1.4 Emerging Memory Technologies

The increasing demand for memory performance and capacity, and the I/O and area scalability issues of DRAM DIMMs (Dual In-line Memory Modules) has led to vertically stacked architectures, leveraging recent developments in fabrication process. Multiple layers of DRAM can now be stacked on top of each other, linked via tiny connections called Through Silicon Vias (TSVs) [28]. The ability to pack more memory arrays

#### State of the Art

per area increases the capacity and results in shorter traces, hence reducing fan-out, latency, and power consumption for signals on the memory interface channels.

Examples for stacked memories are HBM (High Bandwidth Memory) developed by AMD and SK Hynix [29] (high-performance) and the WideIO standard [30] (low-power mobile segment). Both memory types are DRAM based and still rely on a parallel interface. Processor and memory components are typically placed and interconnected on a common silicon interposer which is packaged in 2.5D technology. This brings the two components closer to each other, thus further decreasing trace lengths and routing effort. HBM for instance is already deployed in AMD graphics cards [31] and Altera FPGAs [32].

Although these new technologies only recently entered the market and the cost is relatively high, it is expected that they will continue to gain considerable market shares as both significantly improve the memory performance and power characteristics within their market segments. It must be noted that stacking is also utilized for non-volatile storage class devices such as V-NAND from Samsung [33] as well as 3D-NAND [34] and the recently announced 3D XPoint [35] from Micron and Intel.

The second class of revolutionary packaging options is 3D integration. It benefits from the additional advantage that TSVs enable different processes such as DRAM and CMOS (Complementary Metal Oxide Semiconductor) to coexist within a single stack. 3D integration allows to shift the complexity of a memory controller into a logic layer at the bottom of a memory stack. Popular examples are Intel's Multi Channel DRAM (MCDRAM) and Microns HMC. Intel's latest KNL (Intel Knights Landing) CPUs connects multiple MCDRAM<sup>1</sup> devices via a proprietary interface in a 2.5D package [18]. An MCDRAM is a stack of multiple DRAM layers on top of a logic base that integrates the actual memory controller functions. Similarly, Micron's HMC [37] stacks up to 4 layers of DRAM on top of a logic base that fully integrates up to 16 independent memory controller. The innovative part with HMC is that the traditional parallel interface to the processor is replaced by high-speed serial links. The benefits of such an interface are described next.

$<sup>^1</sup>$   $\,$  According to [36], MCDRAM is based on HMC with a modified logic base and interface.

### 2.1.5 Serial Interfaces

Utilizing serial high-speed links to connect a memory breaks with the traditional parallel interface, and there are several good reasons to examine this approach: A serial interface

- shifts the memory controller complexity into the memory stack. It decouples the development of the memory interface from of the actual DRAM array and other memory technologies.

- 2. likely operates on packets instead of transactions. This enables the existence of potentially many outstanding requests which suits the demands of current multi-core/multi-threaded CPUs with many independent request streams.

- 3. enables the use of application-specific packets and commands to integrate processing capabilities close to the memory (see Section 2.1.6).

- 4. reduces I/O pin requirements and routing complexity. The interface itself consists of several high-speed differential lanes and a few sideband signals.

The author in [38] formulated a motivation to adapt serial interfaces and in particular highlighted the benefits of Micron's HMC as a candidate. This motivation is extended by a detailed description and evaluation of the HMC in Chapter 3.

To the best knowledge of the author, at the time of writing the only other device that stacks memory on top of a logic base with a serial interface is the SRAM (Static Random-Access Memory)-based Bandwidth Engine (BE) by Mosys [39]. Although BE provides the lowest memory access latency on the market ( $\approx 16$  ns for a full memory reference) its maximum capacity is currently 1 Gbit which makes it unusable for most applications and impractical as main memory replacement. The HBM specification similarly defines an optional interface die (e.g. with a serial interface). At the time of writing, however, there are no devices with such an interface available.

### 2.1.6 Processing in Memory

This section so far has only considered changing or improving the existing parallel memory interface. Another approach that has recently become a well discussed topic is to avoid data movement where applicable by shifting the actual processing into the memory array, or at least as close to it as possible. Among other acronyms that have emerged, the most popular is Processing In Memory (PIM).

PIM describes the tight integration of CMOS logic and memory cells within a single chip. This idea is not novel and several architectures that place combinational circuits right next to the memory were proposed already in the 1990's (e.g. [40, 41]). Their functionality, however, was limited to very basic operations and only the recent advancements in fabrication process have made PIM an interesting topic for researchers. HMC can be categorized as PIM device as it supports atomic functions that can autonomously add values to memory locations. The Active Memory Cube (AMC) [42] takes this capability to a next level. Based on the HMC memory architecture it integrates a full Instruction Set Architecture with caches and pipelines. Although AMC is still a research project and the performance projections are based on simulations, it gives a glimpse into the capabilities of PIM and how it can be used to reduce the memory interface traffic.

### 2.1.7 Summary Memory

This section highlighted the reasons for the existing and ever increasing gap between the processor and memory performance. It became clear that the main memory interface must change in order to keep up with the increasing number of cores and components that access it. Although recent developments led to performance and capacity improvements they have not significantly changed the way how memory is accessed. A technological breakthrough that is able to replace the DRAM cell is currently not foreseeable, but at the same time seems inevitable to overcome the proposed power budget of next-generation Exascale systems. To speed-up the adoption of future memory technologies, the serial memory interface was introduced. It comes with plenty benefits that have the potential to change the memory landscape. This includes the possibility to rapidly develop and integrate complex processing units within the memory stack without the need to change the interface itself.

# 2.2 Communication in HPC systems

Today's HPC systems often comprise multiple thousand nodes and projections show that this number will scale up to 260.000 nodes for Exascale machines [4]. Without a significant change in how these systems are designed, future systems will more or

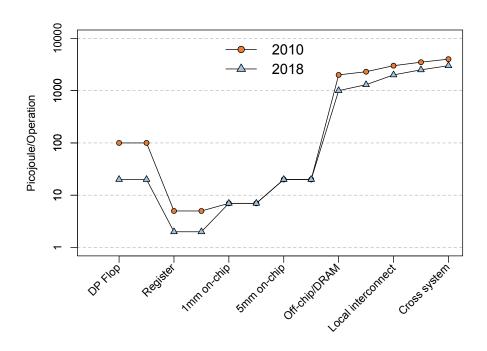

Fig. 2.2 Energy cost for data movement across different layers [7]

less rely on the current prevalent communication scheme: An application uses MPI (Message Passing Interface) to exchange messages between two or more processes. These messages are physically transported via an underlying hardware, the interconnection network (*interconnect*). This section introduces several types of commonly deployed interconnects and summarizes the communication schemes and typical patterns of current large-scale systems.

### 2.2.1 Interconnection Networks

To leverage the vast amount of processing capabilities of thousands of nodes, the jobs that run on these systems need to be partitioned and parallelized as good as possible. Unless a job (or *the problem*) is perfectly parallelized, and this often does not only depend on the programmer but the on problem itself, inter-process communication will take place. Sometimes, this communication occurs between two processes running on the same node or even the same processor. Most often, however, inter-node communication is inevitable which is expensive in terms of energy and latency. Figure 2.2 illustrates the energy cost to move data through the different possible types of the interconnect hierarchy.

#### State of the Art

It can be seen that the required energy to transport an information becomes significant when moving off-chip (e.g. to get data from local DRAM), and increases further when using the local (processor-)interconnect or crossing node boundaries. Even worse, whenever data is transported to a remote node this node is likely to be waiting for it. This additional latency results in stall states where no useful computation is performed. Hence, the interconnection network plays a vital role for the overall system performance and energy efficiency. Assuming a perfectly parallelized application the interconnect is often the most important component and a popular optimization target to keep communication overhead at a minimum.

Out of several interconnect technologies, Ethernet and Infiniband [43, 44] have emerged as the most prevalent solutions in HPC. According to the TOP500 list of supercomputers<sup>2</sup> (June 2017 edition), 208 out of 500 systems run Ethernet<sup>3</sup> (41 %) and 177 use Infiniband<sup>4</sup> (35 %). The remaining systems use proprietary interconnects such as Intel Omnipath [46] which gradually gains traction in the list since its introduction in 2015. It must be noted that currently no machine within the 10 most powerful supercomputers of the TOP500 list uses Ethernet or Infiniband. The leading spots are held by non-standard, vendor specific interconnects tailored to these machines and the LINPACK benchmark.

Most of the interconnection networks, including Ethernet and Infiniband, have in common that they come as a PCI Express (PCIe) plug-in card for the corresponding slots in today's commodity hardware. These Network Interface Controllers (NICs) provide host connectivity via PCIe and one link to the network fabric. One exception to this is Intel Omnipath which integrates the NIC with the CPU and therefore removes the often criticized PCIe connection as bottleneck.

A message that targets a remote node is first processed by the NIC and then sent to the network. Switches and hierarchies of such are used to link all nodes together. Unfortunately switches come at a price and limit the scalability as the network becomes non-uniform. Also, physical space must be preserved to place these switches in a rack.

One approach to avoid these drawbacks is the emerging interconnect EXTOLL [47, 48, 49]. Just as with the other interconnects, the EXTOLL NIC plugs into a standard PCIe slot, but it already integrates the switching functionality. Each NIC provides six network links and therefore allows to directly create topologies such as a 3D torus,

$<sup>^{2}</sup>$  The TOP500 list of supercomputers, established in 1993, is a half-yearly updated list that ranks the 500 most powerful supercomputers using the LINPACK benchmark [45].

<sup>&</sup>lt;sup>3</sup> Ethernet, 1G Ethernet, 10G Ethernet (majority), or 100G Ethernet.

$<sup>^4</sup>$  Infiniband QDR, FDR (majority), or EDR.

| Interconnect          | $\mid$ Latency [us] $\mid$ Bandwidth [GB/s] |       |  |

|-----------------------|---------------------------------------------|-------|--|

| Ethernet 1G [50]      | 47                                          | 0.112 |  |

| Ethernet $10G$ [50]   | 12                                          | 0.875 |  |

| Infiniband QDR [50]   | 1.6                                         | 3.23  |  |

| Infiniband EDR $[51]$ | 0.6                                         | 12.5  |  |

| EXTOLL [52]           | 0.6-0.8                                     | 12.5  |  |

Table 2.1 Interconnect performance comparison

maintaining scalability at all times. These are two of the main reasons why EXTOLL has been selected to evaluate the NAM. Section 4.2 will present the technology in detail.

Performance-wise, all of the interconnects mentioned above have significantly improved over the past decade. As Table 2.1 points out, Infiniband EDR and EXTOLL are superior to 1G and 10G Ethernet in bandwidth and latency. The reason why in particular 10G Ethernet is still deployed that often (195 systems in the TOP500) is because of its relatively low cost. State of the art HPC systems require thousands of NICs and hundreds of switches to fully interconnect all nodes.

Whichever interconnect is used it still remains a tool for applications to facilitate inter-process communication and the actual utilization of the interconnect depends on the communication characteristics of the application itself. It is in particular important to understand these characteristics in order to optimize the overall system performance as simply improving the interconnect bandwidth and latency might not pay off significantly in all cases.

# 2.2.2 Message Passing and Communication Characteristics

Message passing is the prevalent inter-process communication scheme in today's largescale systems and has become the de-facto standard. It abstracts the underlying data movements to a simple concept of messages that are sent and received between two processes.

The most widely used message passing standard is  $MPI^5$  (first introduced in [54]) which itself is not a library, but rather a specification that defines how message passing

$<sup>\</sup>overline{}^{5}$  The full specification of the current MPI standard version 3.0 can be found in [53].

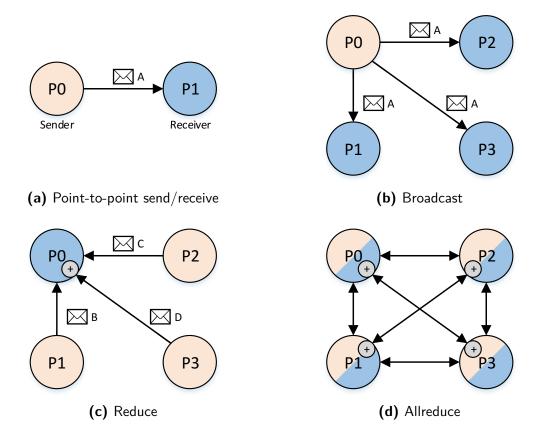

**Fig. 2.3** Example MPI operations (Legend: Orange - sender. Blue - receiver. '+': Logical operation)

libraries should operate. Out of this standard, several implementations including MVAPICH/MVAPICH2 [55] and the very popular open-source variant Open MPI [56] have evolved.

Figure 2.3 depicts four MPI operation examples. These include, but are not limited to asynchronous point-to-point messaging and collective operations such as Broadcast (distribute data from one process to other processes), Reduce (move data from other processes to one process and perform a logical operation; one process receives the result), and Allreduce (apply logical operation on data from all processes; all processes receive the result). In particular, the actual implementation of Allreduce and other similar collective operations depend on the MPI library that is used. Data exchange for such functions can be realized with all-to-all communication (Figure 2.3d) or various other logical topologies such as a binary tree or a ring.

Apart from the actual scheme that is used for collective operations, an application typically comes with predictable and well-known access patterns. It is essential to characterize applications by means of their communication behavior to determine useful system optimizations for a specific use case. Naive approaches to simply improve the performance of components such as the processors or the interconnect will not necessarily lead to substantial speed-ups if the actual bottleneck is somewhere else. For example, some applications heavily utilize point-to-point communication while others spend most of their time performing collective operations. This depends on the application itself and how it is implemented.

Recent work in [3] analyzed the MPI characteristics of application traces collected by the U.S. Department of Energy (DOE) [57]. The analyzed dataset comprises 18 different applications with 10 up to 13.000 ranks. The key finding of this work is that these applications spend 36 % on average of their time in MPI routines with a peak of up to 60 %. Interestingly, while the vast bulk of data is transported via point-to-point communication the average application spends most of its MPI time with collective operations. Although it was shown that only small amounts of data are processed with collective operations, synchronization overhead for a large number of processes becomes significant. This insight is in particular important as it highlights that for many applications the focus must be shifted to improving collective operations instead of just focusing on increasing bandwidths.

This issue has already been identified and the latest MPI-3.0 standard foresees nonblocking collective operations which allow to continue program execution while collective operations take place. However, it also brings up the question of architectural changes and encourages the use of dedicated resources to carry out these operations and to reduce synchronization overhead.

## 2.2.3 Summary Communication

Current large-scale systems and applications rely on a message-based communication schemes which send and receive messages via a physical interconnection network and it is not expected that this general approach will change in the near future.

Although the various types of interconnects as important part for inter-node communication showed substantial progress over the past decade, simply improving these components may not be sufficient. This is in particular the case for applications that spend a large amount of their execution time waiting for completion of collective operations. The resulting processor stalling negatively impacts the application's performance and energy efficiency.

#### State of the Art

Unarguably the interconnect will remain an important system component and needs to be further optimized. For many applications, however, there is an obvious need to rethink system design and a dedicated resource to mitigate existing application bottlenecks appears reasonable and tempting.

# 2.3 Fault Tolerance in HPC Systems

Resilience has become a major concern for HPC systems. As systems continue to grow in size, more and more components are added. Unfortunately, each additional component is also subject to faults (e.g. a stuck bit) which are likely to result in errors such as an incorrect value and false program execution. Errors on the other hand may lead to incorrect system states or an application crash known as failure<sup>6</sup>. Previous work in [59] showed that the number of failures per system is almost proportional to its number of processors, which correlates with the amount of memory and other components. Without an increase in component reliability the MTBF of future systems will further decrease as it is expected that Exascale systems will comprise more than 260.000 nodes [4], 6 times more than the current number 1 ranked HPC system Sunway TaihuLight<sup>7</sup>. The equation is easy: with 6 times more components at a given component reliability, a system will fail 6 times more frequently.

In fact, the single component reliability even decreases with technology scaling and design for power efficiency. Smaller transistors typically carry smaller charges and also suffer from manufacturing variances, making them more error prone. The DRAM soft error rate for example has been analyzed in two studies conducted in 2004 [60] and 2009 [61] using respective state of the art memories. A comparison of the results unveils a 25X increase in DRAM soft failure probability in only 5 years. Although ECC (Error Correction Code) technology is able to correct a bulk of such errors their occurrence will further increase.

Along with the obvious challenges caused by technology scaling, semiconductor devices also become less reliable over their lifetime. This is known as aging and it gets worse with smaller features sizes. Interestingly, the authors in [62] found a correlation between the number of component failures and the day of the week and the hour of the day. Hence, components are likely to fail more often under heavy workload.

<sup>&</sup>lt;sup>6</sup> For more information on the taxonomy see [58].

<sup>&</sup>lt;sup>7</sup> The Top500 list twice-yearly ranks the performance of the 500 fastest supercomputers in the world. See www.top500.org for more information.

2.3 Fault Tolerance in HPC Systems

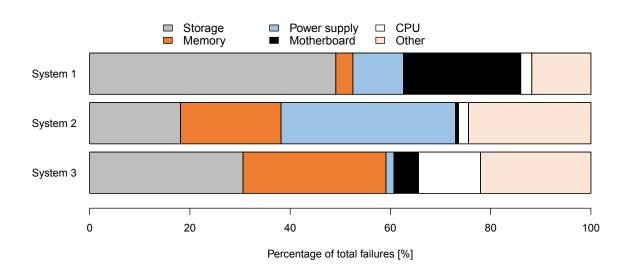

Fig. 2.4 Hardware failure breakdown by component for three different and unrelated systems [65]

| Cause      | Hardware | Software | Network | Human | Facilities | Unknown |

|------------|----------|----------|---------|-------|------------|---------|

| Percentage | 60.4~%   | 22.6~%   | 1.8~%   | 0.6~% | $1.5 \ \%$ | 13.1~%  |

Table 2.2 Causes of failures by type collected by LANL from 1996 to 2007 [66]

For today's large-scale systems, the MTBF ranges from a few hours to several days, mainly depending on the system size [63]. Researchers predicted that an Exascale system might fail in the order of every 30 minutes [64].

Fault avoidance techniques such as ECC and redundancy come at the expense of more hardware and increased power consumption. Finally, the recent IC (Integrated Circuit) development is mainly driven by cost-effective segments (e.g. mobile) that do not demand high reliability and can easily tolerate certain errors. The vast majority of available hardware focuses on these markets and high-performance systems built out of commodity hardware especially suffer from a lower MTBF.

### 2.3.1 Failure Causes

The major cause for system failures is defective hardware, and as Figure 2.4 shows it can be any component in a system. There are, however, several other possible causes for system failures which are summarized in Table 2.2. Software, for example, is ranked

#### State of the Art

on the second place and is responsible for about 23 % of all failures on the example system. With more complex hardware architectures, hierarchies, and topologies, also software increasingly becomes more complex. [59] observed that there is a relationship between the software that runs on a system and its MTBF. Although software layers are able to detect errors caused by lower layers this process can be very complex. Furthermore, this information may not necessarily be trusted since the state of the software may be corrupted. Sometimes it is even not easy to track down the cause of an error, especially whether or not it was caused by software. For example, when the job finishes but only the final result is incorrect.

Any of the failures mentioned above will likely cause an entire job to fail and fault tolerance techniques were developed to mitigate the effects of system failures. The most commonly used approach is to periodically backup the system state in order to reduce the penalty for restarting jobs after a failure. This is known as Checkpoint/Restart.

### 2.3.2 Fault Tolerance using Checkpoint/Restart

Checkpointing was introduced to avoid restarting jobs from scratch. With checkpointing, programmers define states (checkpoints) of their application the job can rollback to upon recovery from a failure. Although applications can now restart from a more advanced state, application based checkpointing has a significant characteristic: all processes will roll back to the last well-known state even if only one of many processes has failed. An additional drawback is that the checkpoints have to be stored somewhere. They require extra storage and use I/O (Input/Output) and sometimes network bandwidth to transfer the data. Traditionally, checkpoints were written to the Parallel File System (PFS) which provides only very limited bandwidth since it is most often a shared resource among multiple systems. In an extreme scenario where the time it takes to write a checkpoint is close to or exceeds the MTBF, a job would spend most of the runtime just to checkpoint its data without making progress in the actual task.

Finding the optimum time interval between two consecutive checkpoints is rather complex and subject to intense investigation [67]. It requires a deep knowledge of the system architecture and the application.

Recently exceptional effort has been put into the prediction and prevention of system failures. The results in [68] show that under certain circumstances the failure prediction recall<sup>8</sup> goes up to 50%. Proactive checkpointing [68] can then be used to back up the system state right before a failure occurs, reducing the amount of work lost. The authors also suggest spare nodes to replace other nodes that will fail soon, migrating repair time.

All these approaches come at a certain overhead and they are currently complimentary to periodic checkpointing which remains the prevalent fault tolerance technique. Checkpointing inevitably leads to longer application runtimes and it is desirable to reduce this overhead.

#### 2.3.2.1 Mitigating Checkpointing Overhead

Several options to mitigate checkpointing overhead and to reduce its negative impact on application runtimes are available:

#### Reduced checkpoint size

It is the responsibility of the programmer to identify the parts that need to be stored in order to reduce data size but still allow for correct failure recovery. Incremental checkpointing can be used to reduce the size of consecutive checkpoints by only storing data that has changed since the last checkpoint. However, current approaches such as in [69] require significant modification to operating system kernels and may not be easily deployed.

#### Reduced checkpointing frequency

It is reasonable to decrease the checkpointing frequency to lower its overhead. Since applications will lose more progress upon a failure in this case, checkpointing frequency must be seen as a trade-off between MTBF and the time it takes to store (and restore from) a checkpoint. Interestingly, the more frequent checkpoints are created and written to the storage system, the more frequent specific components such as Solid State Drives (SSDs) with limited durability will fail.

### Multilevel checkpointing

Multilevel checkpointing approaches make use of intermediate levels of storage that provide higher bandwidth than the slow PFS such as DRAM and local SSDs. The checkpoint is written to this faster storage and then asynchronously flushed to a higher storage layer via a dedicated thread [70] or an agent [71]. Meanwhile

<sup>&</sup>lt;sup>8</sup> The prediction recall is the ratio of correctly predicted errors to the number of actual detected failures.

the corresponding process can continue with its task. Typically, the last level of checkpoint storage is still the PFS and not every checkpoint stored on a faster storage will be transferred to the PFS, but instead 1 out of 10 checkpoints for example.

Multilevel checkpointing and reducing the checkpoint size both allow to increase the checkpointing frequency, which may also reduce the rollback penalty for restart. A similar form of multilevel checkpoints is accomplished with burst buffers [72, 73], which are intermediate destinations in front of the PFS but can be mounted as regular file systems. Burst buffers exploit the *bursty* characteristic of checkpoint I/O where high bandwidth is only occasionally requested, which gives enough time to forward it to the PFS as final destination in between two checkpoints. Other approaches such as In-memory checkpointing [74] rely on a memory only checkpointing scheme, avoiding the relatively slow PFS. Although checkpointing to memory undoubtedly delivers the best performance it also requires multiple copies of a single checkpoint and multiple times more memory than required by the application. Moreover, when the memory is non-volatile, a node failure such as a simple power outage will erase the checkpoint.

Multilevel checkpoints provide a good trade-off between traditional PFS-based checkpointing and the in-memory approach. It allows for frequent, fine granular checkpointing and keeps the requirement for additional memory low at a reasonable performance degradation. One example implementation which has evolved as a de-facto standard is provided by the Scalable Checkpoint / Restart (SCR) library [71, 75]. As an alternative to SCR, the Fault Tolerant Interface (FTI) library [70] provides very similar features and is also widely used. As SCR was used in the DEEP-ER project it serves as reference and will be described more in detail.

One criteria that is often unnoticed is the effect of checkpointing on power consumption. Research in [76] showed that there is only little difference between checkpointing protocols and redundancy schemes. Moreover, the power consumption of computing and checkpointing was measured to be close. Depending on the checkpointing interval and duration, creating checkpoints can significantly influence application runtimes and will increase the power footprint.

# 2.3.3 SCR: Scalable Checkpoint / Restart

The SCR library provides a multilevel checkpointing solution for MPI applications. It is based on two key observations: First, only the most recent checkpoint is required to successfully restart. Second, a system failure only disables a small portion of the system.

With these two observations SCR was designed to only store the most recent checkpoint to node-local storage, discarding any previous checkpoints. It also implements a redundancy scheme to support some node failures at reasonable network traffic and computation overhead. Storing checkpoints to node-local storage ensures system scalability since the checkpointing bandwidth scales with the number of nodes. However, even with SCR checkpoints must be occasionally written to the PFS. It is still required to recover from larger system or node-local storage failures. It must also be noted that the node-local storage may have limited endurance and frequent checkpointing to e.g. an SSD will limit its average lifetime to approximately 3 years. Additional techniques based on a hybrid DRAM/SSD approach were developed to increase the SSD lifetime [5].

Even though SCR manages checkpointing and restart by itself it is still up to the programmer to identify the parts of the code that need to be saved, and to make use of the respective function calls provided by SCR.

### 2.3.3.1 Redundancy Schemes

SCR provides three different checkpointing schemes:

**Local** Checkpoints are only written to the node-local storage. It is the fastest of the three checkpointing schemes but cannot withstand node failures.

Storage required for a checkpoint of B Bytes: B

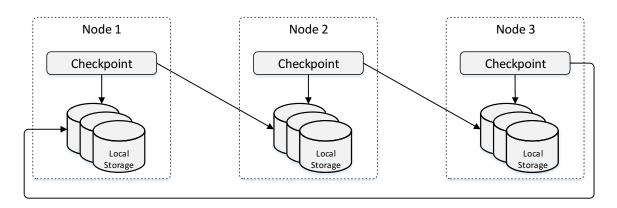

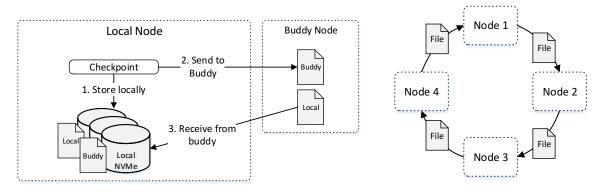

**Partner** Checkpoints are written to the node-local storage and additionally to the local storage of a remote partner node (Figure 2.5). This scheme is slower than 'Local' but can withstand node failures, and even multiple node failures as long as a node and its partner do not fail simultaneously.

Storage required for a checkpoint of B Bytes:  $2 \cdot B$

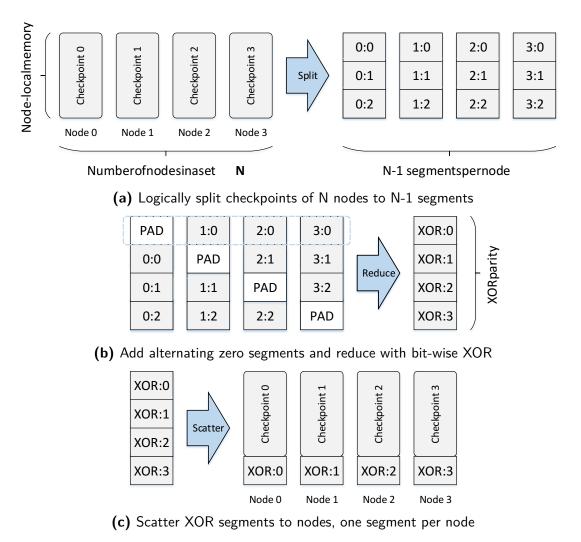

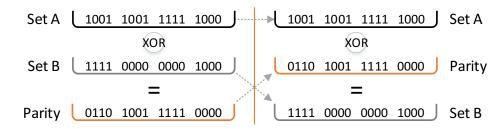

**XOR** With XOR, all available nodes are split into sets with N nodes each. Using a bit-wise XOR reduce operation, a parity information over all checkpoints in a set is calculated. Each node receives only a fraction of the parity which can then

Fig. 2.5 SCR-Partner checkpointing scheme

be used to recover from any single node failure within a set. XOR invokes more computation but requires less storage than 'Partner'. It can withstand multiple node failures as long as no more than one node within a set fails simultaneously.

Storage required for a checkpoint of B Bytes:

$$B + \frac{B}{N-1}$$

Local checkpointing is not a viable option for most systems as a single storage outage causes the scheme to fail. The Partner approach ensures the highest fault tolerance and is trivial and easy to implement but it requires the most storage space as every checkpoint is stored twice. SCR with XOR is a good trade-off in performance and storage requirements between these two approaches. It will be examined in detail next.

### 2.3.3.2 XOR Redundancy

Figure 2.6 shows how SCR generates a XOR parity. As mentioned before, SCR with XOR splits the available number of nodes into sets. In a set of N nodes, the checkpoint file of each node is logically split into N-1 segments (Figure 2.6a). In the next stage, zero-padded segments are inserted so that every checkpoint now consists of N segments. All segments with the same index are then reduced via a bit-wise XOR operation (Figure 2.6b). This process may be implemented as a typical MPI collective operation which has been described in the previous section. Finally, one XOR parity information segment is distributed (*scattered*) to every node (Figure 2.6c). SCR provides several parameters to control the size of sets and the assignments of nodes to these. The configuration in the example provides one XOR set and can only tolerate a single node

Fig. 2.6 SCR XOR checkpointing example

failure. It is the responsibility of the user to create a reasonable number of sets to allow withstanding multi-node failures.

SCR is also able to handle multiple processes per node. In this case it will automatically select and create XOR sets so that every set has no more than one process of a particular node. Also, when a process writes more than one file during execution, SCR will combine these to a single checkpoint file. Finally, checkpointing files with arbitrary sizes are managed by determining the size of the largest checkpoint in a set and padding the remaining checkpoints with zeros up to this size.

# 2.3.4 Summary Fault Tolerance

Every component in a computing system is subject to failures and the Mean Time Between Failure decreases with an increasing number of components in large-scale systems. As systems fail unexpectedly and will continue to do so, work will be lost unless the accuracy of failure prediction models and migration strategies reaches 100%. Until then, fault tolerance using periodic checkpointing is inevitable and remains the prevalent fault tolerance technique.

To mitigate the checkpointing overhead, multilevel checkpointing libraries such as SCR were developed. SCR provides multiple levels of tolerance and different redundancy schemes to account for different checkpointing strategies, and SCR with XOR has been identified as a reasonable trade-off between performance and storage requirements.

SCR with XOR, however, involves inter-node communication and computation of the XOR parity result likewise. This will keep processors busy and increase the memory references to move intermediate results to and from the memory. It is therefore desirable to have an additional device that is able to offload computation, and at the same time reduce communication among nodes. This communication overhead is identical to MPI collective operations which has been identified as a major potential performance bottleneck in the previous section.

# 2.4 Summary

This chapter highlighted the importance of the memory interface and inter-node communication in today's and future large-scale systems. It became clear that memory has been and will remain one of the most critical bottlenecks with regards to performance and power. For many applications, communication overhead is already a large part of the overall application runtimes and the situation will become worse with growing system sizes.

As future systems will comprise many more components this will also lead to more frequent soft- and hard errors, increasing the importance of fault tolerance using periodic checkpointing to reduce the penalty of such failures. Unfortunately, writing checkpoints takes application time where no actual computation is performed. Since the performance for writing checkpoints also depends on the memory interface, the interconnection network, and communication performance, it is desirable to improve these key elements.

In conclusion this chapter provided a strong motivation to develop a device that is able to mitigate the negative effects that were described above. Such a device must be able to offload computation from a host processor and simultaneously reduce inter-node communication.

CHAPTER **CHAPTER**

# Hybrid Memory Cube

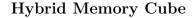

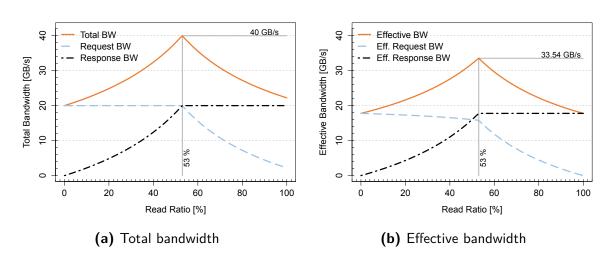

As an alternative to the DDR interface, to overcome its scalability issues (such as I/O pin, area, and load limitations), and to increase channel bandwidth, Micron recently proposed the Hybrid Memory Cube. The first section of this chapter introduces the HMC and analyzes the impact of its novel architecture on performance. Section two presents the implementation of the open-source HMC host controller openHMC. Section three evaluates HMC performance and power efficiency in a real system using the openHMC controller. A final summary concludes this chapter.

The findings of section one and three have been published in [11]. The implementation of the openHMC host controller is detailed in [10].

# 3.1 Introduction and Architecture Analysis

HMC is leveraging recent 3D fabrication processes to stack multiple layers of DRAM on top of a logic die. Its interface operates on a packet-based protocol utilizing high-speed SerDes (Serializer / Deserializer). As opposed to DDR, the HMC interface is not a JEDEC standard. Instead, Samsung Electronics and Micron Technology formed the *Hybrid Memory Cube Consortium (HMCC)* in October 2011 [37] and released the first HMC specification 1.0 in January 2013 [77]. It was later revised with the HMC specification 1.1 (HMC Gen 2 devices) which is the reference for this work. HMC

Fig. 3.1 HMC architecture overview

hardware engineering samples were available since 2013 and volume production started in June 2017 with 2 GB devices.

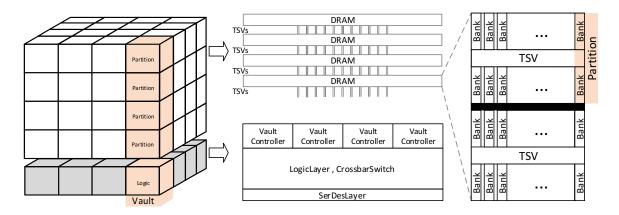

# 3.1.1 Architecture

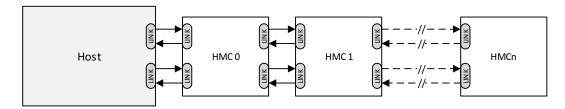

Figure 3.1 shows the basic HMC architecture. Multiple layers of DRAM are stacked on top of a CMOS based logic layer using TSVs [28]. The stack is organized in 16 independent vaults where each vault connects the upper DRAM layers with a dedicated memory controller (the vault controller) using 32 TSVs [78]. Every DRAM layer comprises 16 partitions with 2 DRAM banks each. In [78], the HMC Gen1 DRAM stack was introduced as a composition of 68 mm<sup>2</sup> 1 Gbit dies manufactured in 50 nm. Initially four layers were stacked for a total capacity of 512 MB. Current HMC Gen2 devices [79] stack four 4 Gbit DRAM dies on top of the logic base which increased the capacity to 2 GB (4 layers  $\cdot$  16 partitions  $\cdot$  2 banks = 128 banks). The capacity growth from Gen1 to Gen2 is based on denser memory arrays with a bank capacity increase from 4 MB (Gen1) to 16 MB (Gen2).

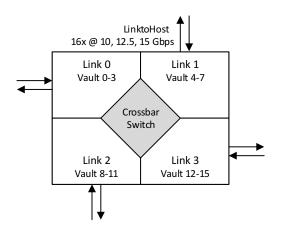

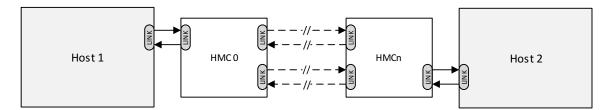

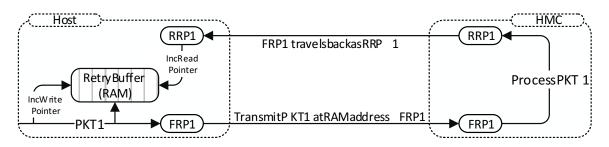

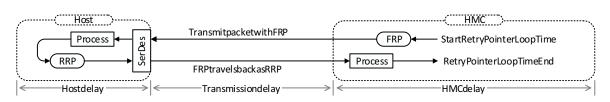

The HMC logic layer exposes four external links which can connect processors or other HMCs. Hence, multiple HMCs can be 'chained' together with varying routing options to increase the capacity (see Section 3.1.4). A single link comprises 16 bidirectional high-speed serial lanes. Every link is local to four vaults and a crossbar ensures that all links can access all vaults and other links (Figure 3.2). The 4-Link HMC comes in

Fig. 3.2 HMC logic layer top view: schematic representation

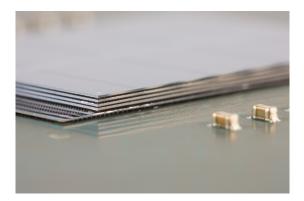

Fig. 3.3 Close-up view of an HMC stack. Image courtesy: Micron

a  $31 \times 31$  mm package (896 balls)<sup>1</sup>. Figure 3.3 shows an HMC close-up view with four DRAM layers.

# 3.1.2 DRAM Organization and Performance

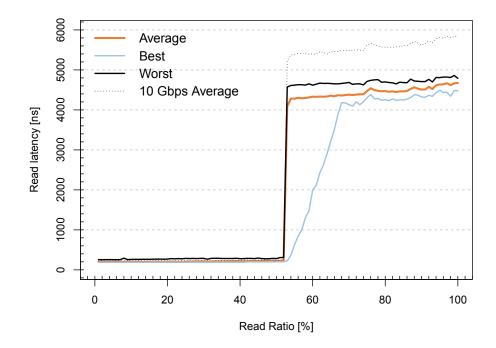

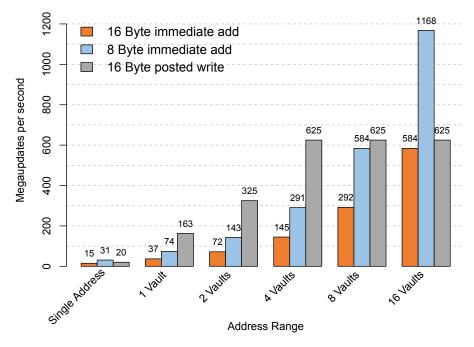

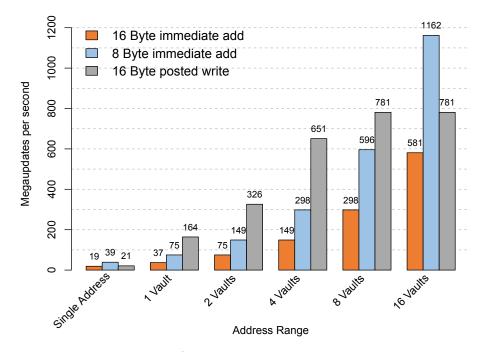

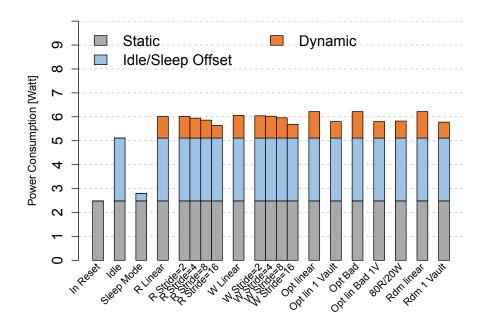

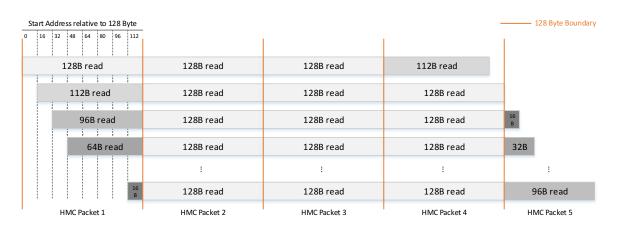

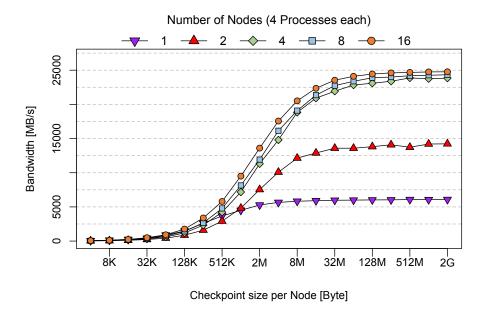

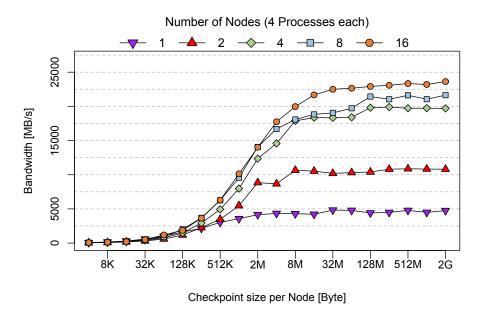

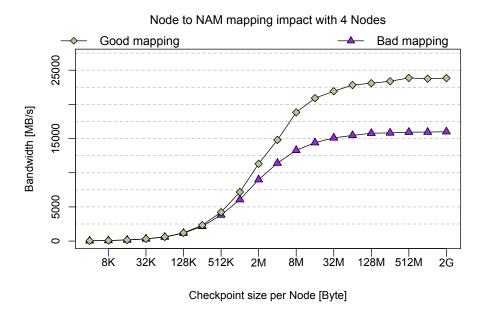

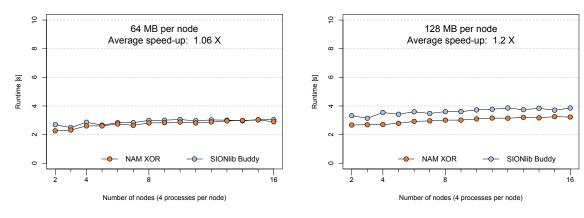

HMC implements a DRAM closed-page policy, i.e. the row buffers become inactive after each access. This is opposed to an open-page policy where a row stays active in the sense amplifiers until it times out or another row is accessed. While an open-page policy is in particular beneficial for applications with high locality (i.e. a high page  $\frac{hit}{miss}$  ratio) it also increases power consumption since the sense amplifiers stay active after a memory access. Additionally, an open-page policy introduces delay on a page miss as pre-charge of the word-line does not occur immediately after the row has been accessed. As a result, a closed-page policy theoretically performs better for random access patterns.