## Autonomic Thread Parallelism and Mapping Control for Software Transactional Memory

Naweiluo Zhou

## ▶ To cite this version:

Naweiluo Zhou. Autonomic Thread Parallelism and Mapping Control for Software Transactional Memory. Logic in Computer Science [cs.LO]. Université Grenoble Alpes, 2016. English. NNT:  $2016 \mathrm{GREAM045}$ . tel-01408450v2

HAL Id: tel-01408450

https://hal.archives-ouvertes.fr/tel-01408450v2

Submitted on 10 Jan 2018

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatics

Arrêté ministérial: 7th August 2006

Présentée par

#### Naweiluo Zhou

Thèse dirigée par **Éric Rutten, Jean-François Méhaut** et codirigée par **Gwenaël Delaval**

préparée au sein Laboratoire d'informatique de Grenoble - LIG et de École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

## **Autonomic Thread Parallelism** and **Mapping Control for Software Transactional Memory**

Thèse soutenue publiquement le **19th October 2016**, devant le jury composé de :

#### **M.Raymond Namyst**

Professeur, Université de Bordeaux, Rapporteur

#### **M.Lionel Seinturier**

Professeur, Université Lille 1, Rapporteur

#### **M.Christian Perez**

Directeur de recherche, INRIA Lyon, Examinateur

#### M.Jean-François Méhaut

Professeur, Université de Grenoble Alpes, Directeur de thèse

#### M.Éric Rutten

Chargé de recherche, INRIA Grenoble, Directeur de thèse

#### M.Gwenaël Delaval

Associate professeur, Université de Grenoble Alpes, Co-Directeur de thèse

#### M.Bogdan Robu

Associate professeur, Université de Grenoble Alpes, Invité

## GRENOBLE ALPES UNIVERSITY INRIA

## Autonomic Thread Parallelism and Mapping Control for Software Transactional Memory

# A THESIS SUBMITTED TO GRENOBLE ALPES UNIVERSITY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY (PHD)

Supervisors:

Author:

Naweiluo ZHOU

Prof. Jean-François MÉHAUT

Dr.Éric RUTTEN

Dr.Gwenaël DELAVAL

CORSE and Ctrl-A Research Teams 2016

## **Contents**

| Al | ostrac | et       |                                         | X    |

|----|--------|----------|-----------------------------------------|------|

| Re | esearc | ch Colla | aboration and Scientific Context        | xi   |

| A  | cknow  | ledgen   | nents                                   | xiii |

| 1  | Intr   | oductio  | o <b>n</b>                              | 2    |

|    | 1.1    | Contri   | butions                                 | 4    |

|    | 1.2    | Thesis   | S Outline                               | 4    |

| 2  | Bacl   | kgroun   | d                                       | 6    |

|    | 2.1    | Multi-   | core Processors                         | 6    |

|    |        | 2.1.1    | Thread affinity                         | 9    |

|    |        | 2.1.2    | Memory Affinity                         | 11   |

|    | 2.2    | Synch    | ronisation Mechanisms                   | 11   |

|    |        | 2.2.1    | Lock-based Synchronisation Techniques   | 11   |

|    |        | 2.2.2    | Other Synchronisation Techniques        | 12   |

|    | 2.3    | Transa   | actional Memory                         | 13   |

|    |        | 2.3.1    | Concepts of Transactional Memory        | 14   |

|    |        | 2.3.2    | TM Design Choices                       | 16   |

|    |        | 2.3.3    | TM Metrics                              | 18   |

|    |        | 2.3.4    | Implementation Schemes                  | 19   |

|    |        | 2.3.5    | Software Transactional Memory Platforms | 21   |

|    |        | 2.3.6    | Restrictions of STM                     | 26   |

|    | 2.4    | Bench    | marks for Evaluation of TM Systems      | 26   |

|    |        | 2.4.1    | EigenBench                              | 27   |

|    |        | 2.4.2    | STAMP                                   | 28   |

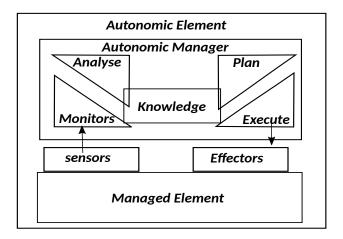

|    | 2.5    | Contro   | ol of Autonomic Computing Systems       | 31   |

ii *CONTENTS*

|   |      | 2.5.1   | Concepts of Autonomic Computing              | 31         |

|---|------|---------|----------------------------------------------|------------|

|   |      | 2.5.2   | MAPE-K Loop                                  | 32         |

|   |      | 2.5.3   | Degrees of Autonomicity                      | 34         |

|   |      | 2.5.4   | Control Theory in Self-adaptive Systems      | 34         |

|   | 2.6  | Concl   | usion Remarks                                | 35         |

| 3 | Ove  | rview o | of Algorithms and Architecture               | 38         |

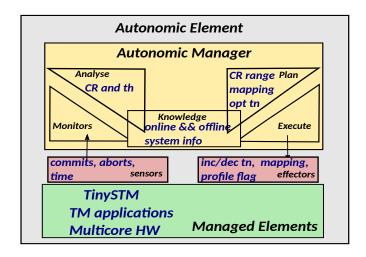

|   | 3.1  | Overv   | iew of System Architecture                   | 39         |

|   | 3.2  | Runtir  | me Profiling Approaches                      | 40         |

|   |      | 3.2.1   | General TM Profiling Concepts                | 40         |

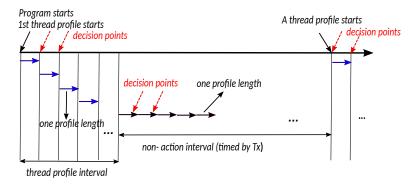

|   |      | 3.2.2   | Phase-based Profiling Algorithm              | 42         |

|   |      | 3.2.3   | Periodical Hill-Climbing Profiling Algorithm | 43         |

|   | 3.3  | Imple   | mentation                                    | <b>4</b> 4 |

|   |      | 3.3.1   | How to Collect Profile Information           | 44         |

|   |      | 3.3.2   | How to Dynamically Control Threads           | 45         |

|   | 3.4  | Concl   | usion Remarks                                | 50         |

| 4 | Auto | onomic  | Parallelism Adaptation                       | 53         |

|   | 4.1  | Introd  | uction                                       | 53         |

|   | 4.2  | Simple  | e Model for Parallelism Adaptation           | 54         |

|   |      | 4.2.1   | Overview of the Profiling Algorithm          | 54         |

|   |      | 4.2.2   | Feedback Control Loop of the Simple Model    | 54         |

|   | 4.3  | Probal  | bilistic Model for Parallelism Adaptation    | 57         |

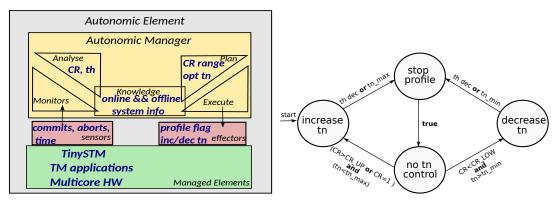

|   |      | 4.3.1   | The Autonomic Manager                        | 57         |

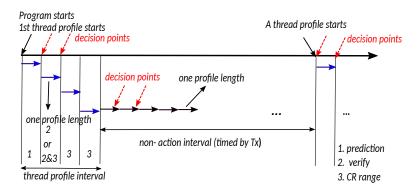

|   |      | 4.3.2   | Parallelism Prediction Decision Function     | 59         |

|   | 4.4  | Bench   | mark Setting                                 | 61         |

|   | 4.5  | Perfor  | mance Evaluation                             | 63         |

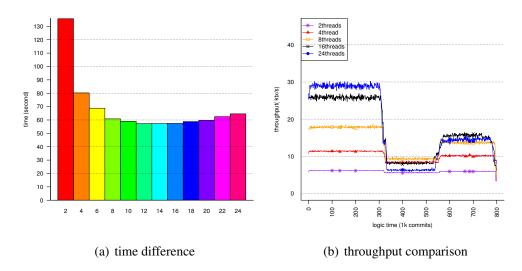

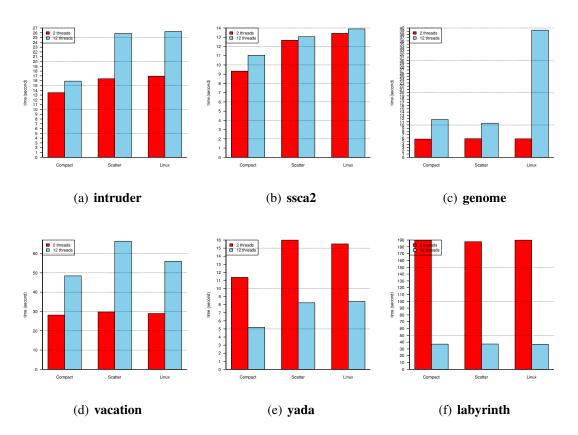

|   |      | 4.5.1   | Performance of Static Parallelism            | 64         |

|   |      | 4.5.2   | Performance Evaluation on the UMA Platform   | 66         |

|   |      | 4.5.3   | Performance Evaluation on NUMA               | 73         |

|   | 4.6  | Discus  | ssion                                        | 74         |

|   | 4.7  | Concl   | usion Remarks                                | 77         |

| 5 | Auto | onomic  | Thread Mapping Adaptation                    | 80         |

|   | 5.1  | Introd  | uction                                       | 80         |

|   | 5.2  | Dynar   | mic Thread Mapping                           | 82         |

CONTENTS

|   |      | 5.2.1    | Inputs and Outputs                                     | 83  |

|---|------|----------|--------------------------------------------------------|-----|

|   |      | 5.2.2    | Decision Functions                                     | 83  |

|   | 5.3  | Perfor   | mance Evaluation                                       | 83  |

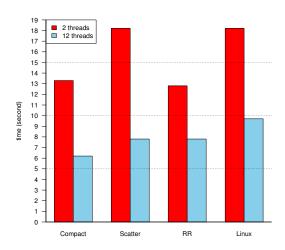

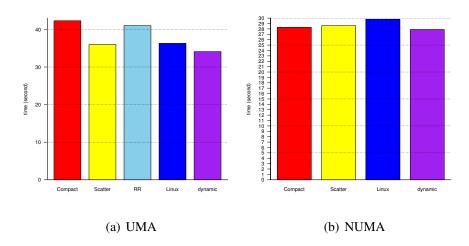

|   |      | 5.3.1    | Static Thread Mapping                                  | 83  |

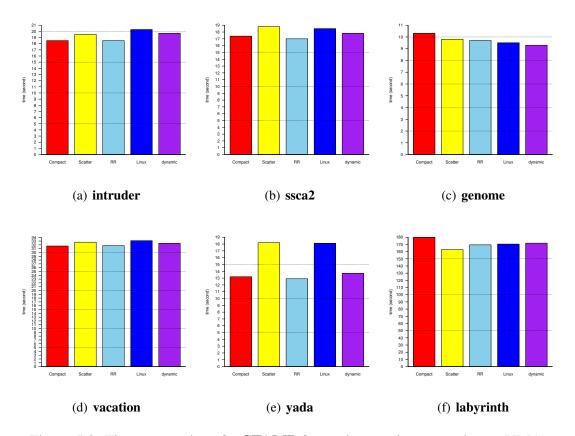

|   |      | 5.3.2    | Performance Comparison on Static and Dynamic Mapping   | 85  |

|   | 5.4  | Discus   | ssion                                                  | 88  |

|   | 5.5  | Conclu   | usion Remarks                                          | 89  |

| 6 | Coo  | rdinatio | on of Parallelism and Mapping                          | 91  |

|   | 6.1  | The C    | omplexity of Dynamic Thread Control                    | 91  |

|   |      | 6.1.1    | The Threshold of Parallelism Degree for Thread Mapping | 92  |

|   |      | 6.1.2    | The Frequency of Thread Mapping Prediction             | 92  |

|   |      | 6.1.3    | The Order of Decision Making                           | 93  |

|   | 6.2  | Overv    | iew of the Profiling Procedure                         | 93  |

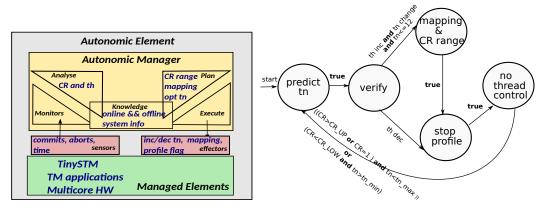

|   | 6.3  | Contro   | ol Coordination                                        | 95  |

|   |      | 6.3.1    | Inputs and Outputs                                     | 95  |

|   |      | 6.3.2    | Coordination of Control Loops                          | 95  |

|   | 6.4  | Perfor   | mance Evaluation                                       | 96  |

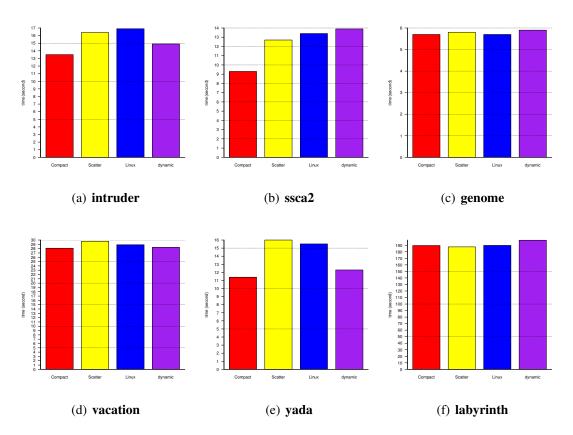

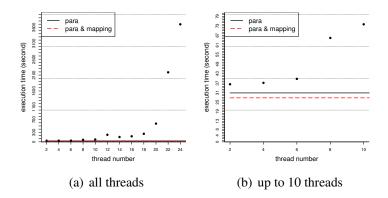

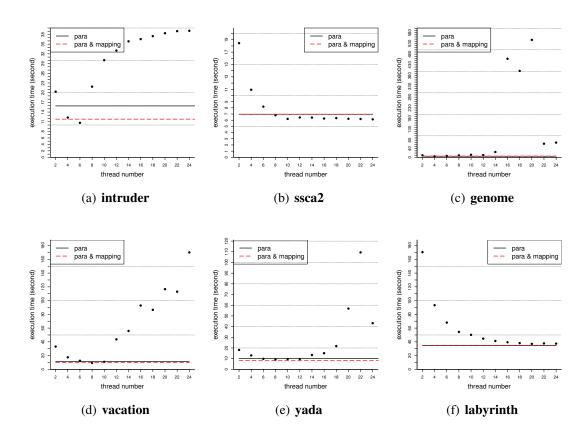

|   |      | 6.4.1    | Results on the UMA Machine                             | 97  |

|   |      | 6.4.2    | Results on the NUMA Machine                            | 104 |

|   | 6.5  | Discus   | ssion                                                  | 105 |

|   | 6.6  | Conclu   | usion Remarks                                          | 108 |

| 7 | Rela | ited Wo  | ork                                                    | 110 |

|   | 7.1  | Dynan    | mic Parallelism Adaptation on TM systems               | 110 |

|   | 7.2  | Thread   | d Mapping Adaptation                                   | 115 |

|   | 7.3  | Coord    | ination of Parallelism and Thread Mapping Adaptation   | 117 |

|   | 7.4  | Conclu   | usion Remarks                                          | 117 |

| 8 | Con  | clusion  | and Future Work                                        | 120 |

|   | 8.1  | Conclu   | usion                                                  | 120 |

|   | 8.2  | Future   | e Work                                                 | 123 |

|   |      | 8.2.1    | Thread Mapping Strategy                                | 123 |

|   |      | 8.2.2    | From STM to HTM                                        | 123 |

|   |      | 8.2.3    | Coordination of Feedback Control Loops                 | 124 |

|   |      | 8.2.4    | From STM to Other Parallel Platforms                   | 124 |

iv CONTENTS

| Bibliograpl | ny                                    | 127  |

|-------------|---------------------------------------|------|

| Glossary    |                                       | i    |

| Appendix A  | Runtime Parallelism Variation on NUMA | vi   |

| Appendix I  | Runtime Throughput Comparison on NUMA | viii |

| Appendix (  | C Résumé de Thèse en Français         | X    |

| C.1 Tit     | re de Thèse                           | xi   |

| C 2 Ré      | sumé de Thèse                         | vii  |

## **List of Figures**

| 2.1  | Examples of UMA and NUMA platforms                                    | 7  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Access latency of diverse memory levels                               | 8  |

| 2.3  | Four thread mapping strategies                                        | 10 |

| 2.4  | The basic operations of TM                                            | 14 |

| 2.5  | A simple example on usage of transaction primitives                   | 14 |

| 2.6  | An example of transaction conflicts in TM                             | 15 |

| 2.7  | EigenBench's core code                                                | 27 |

| 2.8  | Online variation of contention and throughput for <b>genome</b>       | 30 |

| 2.9  | A MAPEK control loop                                                  | 32 |

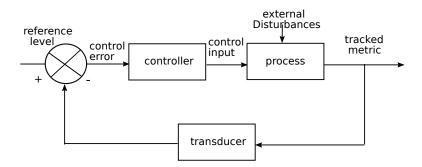

| 2.10 | The feedback control loop from control theory                         | 34 |

| 3.1  | Overview of the feedback control loop                                 | 39 |

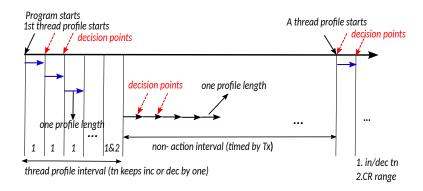

| 3.2  | The terminologies used for the profiling algorithm in the thesis      | 41 |

| 3.3  | The three entry points of the monitor and the control functions       | 47 |

| 3.4  | A snapshot of C code on thread number control                         | 48 |

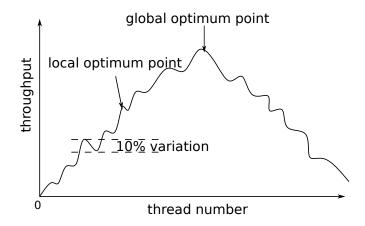

| 4.1  | An illustration of necessity for dynamic parallelism adaptation       | 54 |

| 4.2  | Profiling procedure for the simple model                              | 55 |

| 4.3  | The feedback control loop of the simple model                         | 55 |

| 4.4  | Throughput fluctuation                                                | 57 |

| 4.5  | Profiling procedure for the probabilistic model                       | 58 |

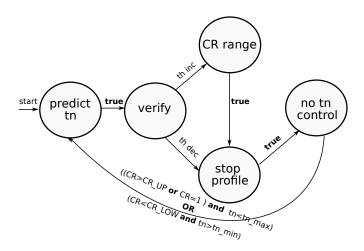

| 4.6  | The controller of the probabilistic model described as an automaton . | 58 |

| 4.7  | Inputs of EigenBench applications for 24 threads                      | 63 |

| 4.8  | The inputs of <b>STAMP</b>                                            | 63 |

| 4.9  | Time comparison of <b>EigenBench</b> for static parallelism on UMA    | 64 |

| 4.10 | Time comparison for <b>STAMP</b> for static parallelism on UMA        | 65 |

| 4.11 | Time comparison of <b>EigenBench</b> for static parallelism on NUMA   | 65 |

| 4.12 | Time comparison for <b>STAMP</b> for static parallelism on NUMA       | 66 |

vi LIST OF FIGURES

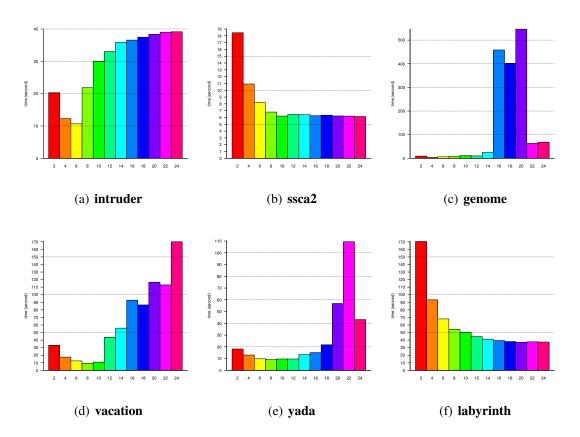

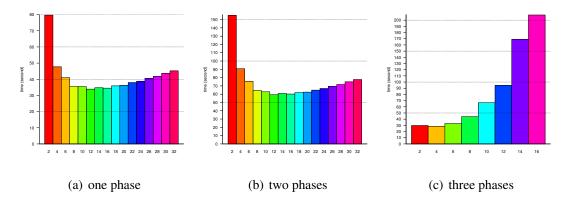

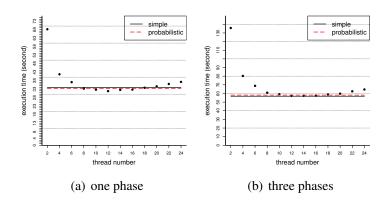

| 4.13 | Time comparison of parallelism for <b>EigenBench</b> on UMA             | 67  |

|------|-------------------------------------------------------------------------|-----|

| 4.14 | Time comparison of parallelism for <b>STAMP</b> on UMA                  | 67  |

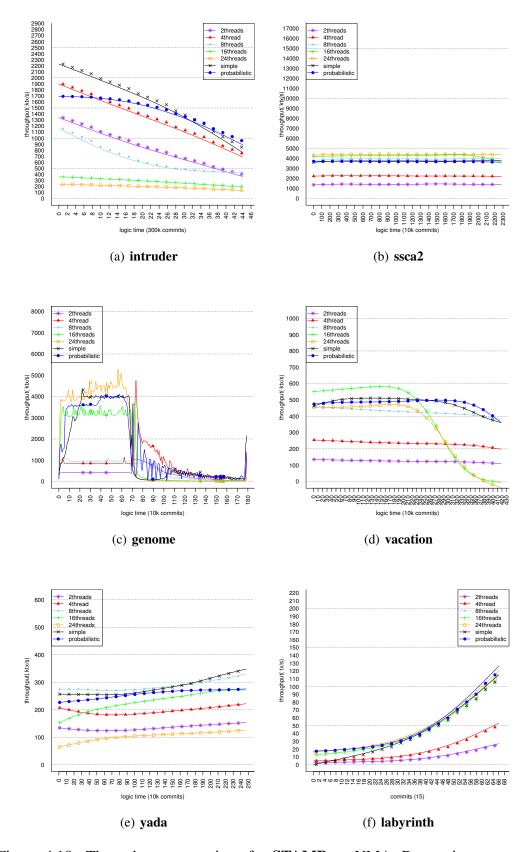

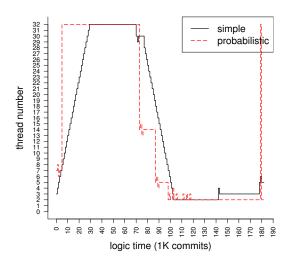

| 4.15 | Runtime parallelism variation by the two models for EigenBench on       |     |

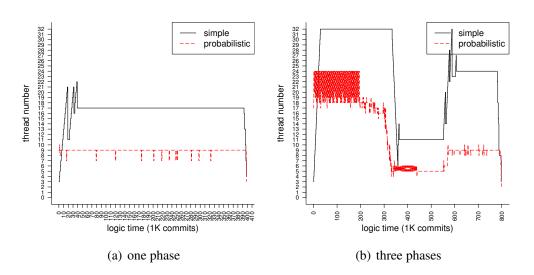

|      | UMA                                                                     | 69  |

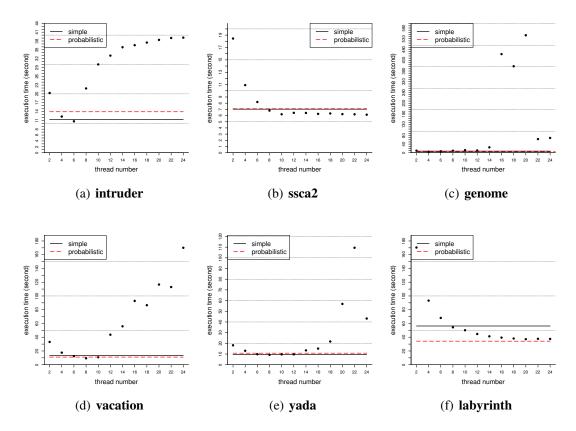

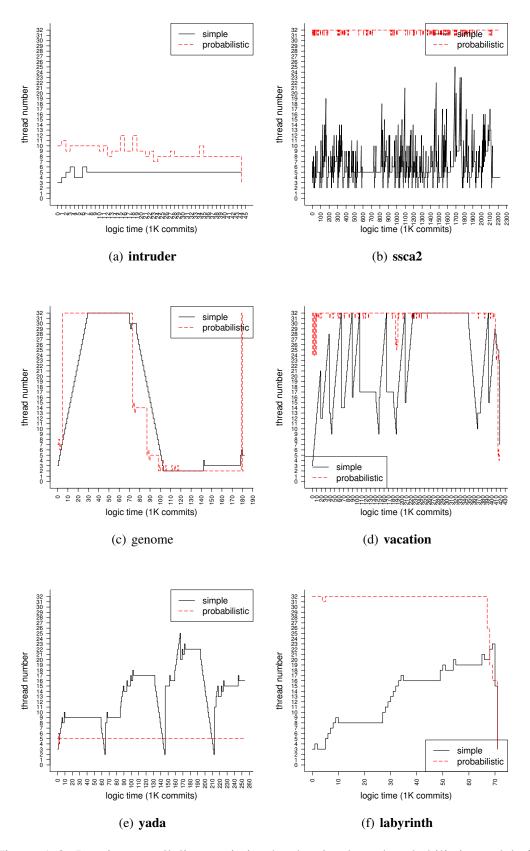

| 4.16 | Runtime parallelism variation by the two models for <b>STAMP</b> on UMA | 70  |

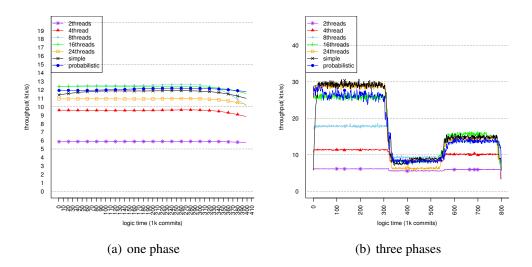

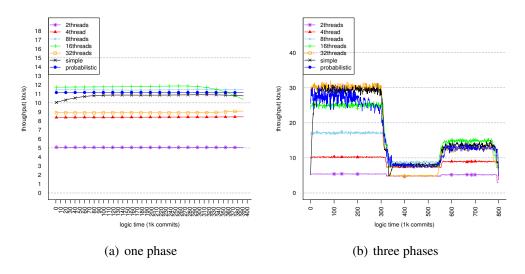

| 4.17 | Throughput comparison for <b>EigenBench</b> on UMA                      | 71  |

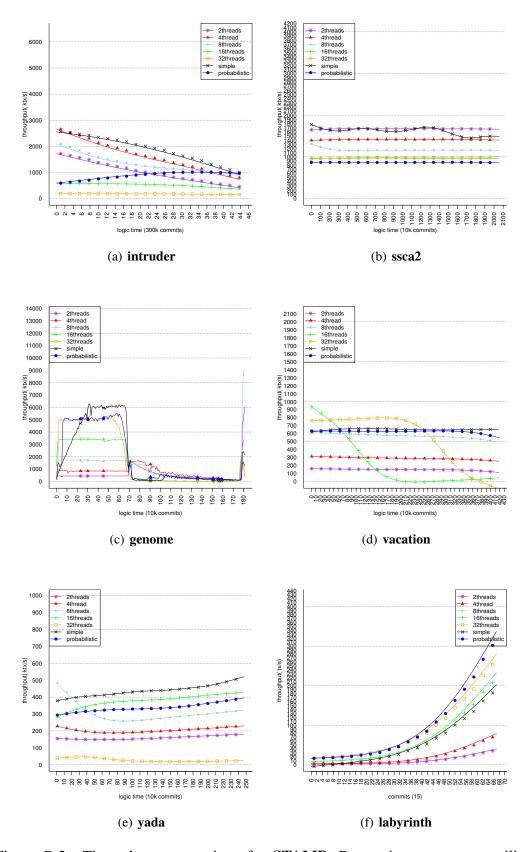

| 4.18 | Throughput comparison for <b>STAMP</b> on UMA                           | 72  |

| 4.19 | Runtime parallelism variation from dynamic parallelism control mod-     |     |

|      | els for <b>genome</b> on NUMA                                           | 75  |

| 5.1  | Time comparison for <b>yada</b> for four static mapping strategies      | 81  |

| 5.2  | Profiling the thread mapping strategy                                   | 82  |

| 5.3  | The feedback control loop for dynamic thread mapping control            | 82  |

| 5.4  | Time comparison of <b>EigenBench</b> for static mapping strategies      | 84  |

| 5.5  | Time comparison for <b>STAMP</b> for static mapping strategies on UMA   | 85  |

| 5.6  | Time comparison for <b>STAMP</b> for static mapping strategies on NUMA. | 86  |

| 5.7  | Time comparison of <b>EigenBench</b> for mapping strategies             | 87  |

| 5.8  | Time comparison for <b>STAMP</b> for static mapping strategies on UMA   | 87  |

| 5.9  | Time comparison for <b>STAMP</b> for static mapping strategies on NUMA. | 88  |

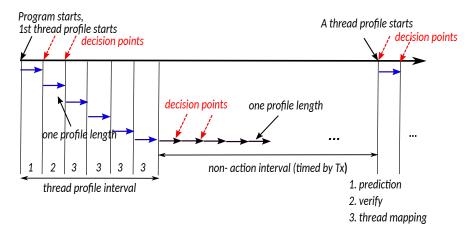

| 6.1  | Periodical profiling procedure for thread control                       | 94  |

| 6.2  | The feedback control loop for coordination                              | 95  |

| 6.3  | The implementation of the four decision functions on coordination       | 97  |

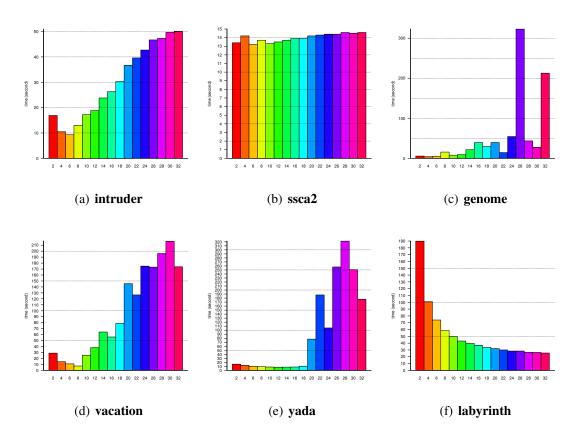

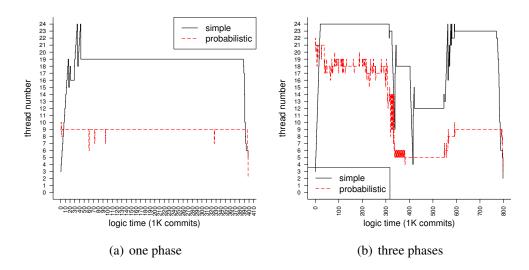

| 6.4  | Time comparison of <b>EigenBench</b> on UMA                             | 98  |

| 6.5  | Time comparison for <b>STAMP</b> on UMA                                 | 99  |

| 6.6  | Runtime variation of parallelism and mapping strategies by the two      |     |

|      | models for <b>EigenBench</b> on UMA                                     | 100 |

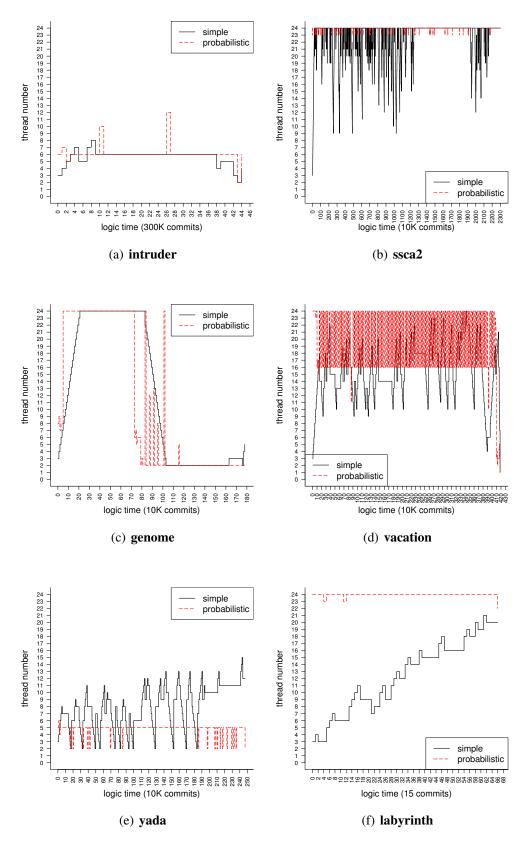

| 6.7  | Runtime variation of parallelism and mapping strategies by the two      |     |

|      | models for <b>STAMP</b> on UMA                                          | 101 |

| 6.8  | Time comparison of ${\bf EigenBench}$ for diverse parallelism on UMA $$ | 102 |

| 6.9  | Time comparison of <b>STAMP</b> for diverse parallelism on UMA          | 103 |

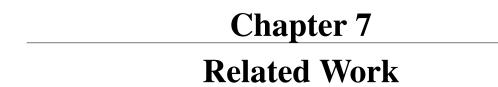

| 7.1  | Flux Concurrency Control in a feedback-driven loop                      | 111 |

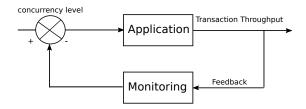

| 7.2  | System architecture of <i>Rughetti et al.</i> ' feedback control loop   | 112 |

| A.1  | Runtime parallelism variation for <b>EigenBench</b> on NUMA             | V   |

| Δ 2  | Runtime parallelism variation for STAMP on NUMA                         | 371 |

| LIST OF FIGURES | vii |

|-----------------|-----|

|-----------------|-----|

| B.1 | Throughput comparison for <b>EigenBench</b> on NUMA | viii |

|-----|-----------------------------------------------------|------|

| B.2 | Throughput comparison for <b>STAMP</b> on NUMA      | ix   |

## **List of Tables**

| 2.1 | Platform Configurations                                                    | 8   |

|-----|----------------------------------------------------------------------------|-----|

| 3.1 | The basic STM operations                                                   | 44  |

| 3.2 | Intrusiveness of the global monitor for UMA                                | 49  |

| 3.3 | The intrusiveness of the global monitor for NUMA                           | 49  |

| 3.4 | The effect of round-robin thread rotation on applications                  | 50  |

| 4.1 | Qualitative summary of each application's runtime transactional char-      |     |

|     | acteristics. The classification is based on the application with its opti- |     |

|     | mum parallelism applied on the UMA machine                                 | 62  |

| 4.2 | Performance comparison of simple model against static parallelism on       |     |

|     | applications on UMA                                                        | 68  |

| 4.3 | Performance comparison of probabilistic model against static paral-        |     |

|     | lelism on applications on UMA                                              | 68  |

| 4.4 | Performance comparison of simple model against static parallelism on       |     |

|     | applications on NUMA                                                       | 73  |

| 4.5 | Performance comparison of probabilistic model against static paral-        |     |

|     | lelism on applications on NUMA                                             | 73  |

| 6.1 | Performance comparison of different applications with the dynamic          |     |

|     | parallelism model                                                          | 99  |

| 6.2 | Performance comparison of different applications with the dynamic          |     |

|     | thread control model                                                       | 100 |

| 6.3 | Performance comparison of different applications with the dynamic          |     |

|     | parallelism model on NUMA                                                  | 105 |

| 6.4 | Performance comparison of different applications with the dynamic          |     |

|     | thread control model on NUMA                                               | 106 |

## **Abstract**

Parallel programs need to manage the trade-off between the time spent in synchronisation and computation. The trade-off is significantly affected by the number of active threads. High parallelism may decrease computing time while increase synchronisation cost. Furthermore, thread placement on different cores may impact on program performance, as the data access time can vary from one core to another due to intricacies of its underlying memory architecture. Therefore, the performance of a program can be improved by adjusting its parallelism degree and the mapping of its threads to physical cores. Alas, there is no universal rule to decide them for a program from an offline view, especially for a program with online behaviour variation. Moreover, offline tuning is less precise. This thesis presents work on dynamical management of parallelism and thread placement. It addresses multithread issues via Software Transactional Memory (STM). STM has emerged as a promising technique, which bypasses locks, to tackle synchronisation through transactions. Autonomic computing offers designers a framework of methods and techniques to build autonomic systems with wellmastered behaviours. Its key idea is to implement feedback control loops to design safe, efficient and predictable controllers, which enable monitoring and adjusting controlled systems dynamically while keeping overhead low. This dissertation proposes feedback control loops to automate management of threads at runtime and diminish program execution time.

## Research Collaboration and Scientific Context

This PhD project is a sub-program under the Grenoble Project HPES (High Performance Embedded System). This work has been partially supported by the LabEx PERSYVAL-Lab (ANR-11-LABX-0025-01) funded by the French Program Investissement d'avenir. This thesis joins work between High Performance Computing and Control Theory. It receives technique and technology support from two INRIA<sup>1</sup> research teams (CORSE and Ctrl-A) in Grenoble, France. The CORSE (Compiler optimisations and Runtime Systems ) research team works toward both execution time optimisation and energy consumption improvement for HPC and embedded processors. Ctrl-A is a research team that majors in autonomic computing with its objectives to design safe controllers for automatic, adaptive, reconfigurable computing systems. The author is affiliated to both of the research teams. This work also collaborates with the control theory department of GIPSA-lab, which is a joint research unit of CNRS<sup>2</sup>, Grenoble INP<sup>3</sup> and Grenoble Alpes University conducting theoretical and applied research in signals and systems. Thanks to the collaboration among the research teams and institutes, this work is able to show insights into the methodology of automatic control for high performance computing systems.

<sup>&</sup>lt;sup>1</sup>French Institute for Research in Computer Science and Automation.

<sup>&</sup>lt;sup>2</sup>French National Center for Scientific Research.

<sup>&</sup>lt;sup>3</sup>Grenoble Institute of Technology, France.

## Acknowledgements

The three years spent in Grenoble is one of the most joyful, peaceful time of my life. I must express my appreciation to all the people who have helped me through the years. I shall remember all the kindness.

I would like to take this opportunity to especially thank my PhD thesis supervisors Prof. Jean-François Méhaut, Dr. Éric Rutten and Dr. Gwenaël Delaval who have guided and supported me during my studies with their patience and knowledge whilst allowing me the space to work in my own way. I attribute my research to their constructive advices and efforts, without them this thesis would not have been completed otherwise.

I also would like to express my gratitude to Dr. Bogdan Robu who contributed tremendously to the development of the algorithms in my thesis and who has given all the supports to my publications.

The members of CORSE and CTRL-A research teams in INRIA have contributed immensely to my personal and professional time in Grenoble. The two groups have been a source of friendships as well as good advice and collaboration. I am especially grateful for my fun group members and friends Kevin Pouget, Brice Videau, Fabian Gruber and Christian Heinrich who have assisted me in my research and contributed greatly to proofread my dissertation. I acknowledge their solicitude and thoughtfulness.

Lastly, I offer my deepest gratitude to my parents who are always supporting me all through my life.

## **Chapter 1**

## Introduction

The last decades have seen a remarkable performance advancement of sequential processors with an annual increment rate of 40%-50% [1] in speed. This was achieved by doubling the amount of transistors on a single processor every two years to increase clock speed. However, this development is reaching an end due to physical limitations of transistors and obstacles of power dissipation among them. This hurdle promotes designs of multi-core processors. Rather than increasing clock frequency, a multi-core processor packs many cores that communicate through shared memory on one chip. Computation is accelerated by high concurrency. The performance benefits brought by multi-core processors require a program to execute in parallel and to scale when the number of cores increases. However writing a parallel application is difficult, as parallel programming encompasses all of the difficulties of sequential programming and introduces extra problems on coordination of interactions among concurrently executing tasks [1]. In addition, complex memory hierarchies are built on multi-core processors, which consist of several levels of cache to alleviate penalties of accessing the main memory. Consequently, parallel applications need to evolve to efficiently exploit potentials of their underlying multi-core platforms.

Multi-core processors boost program performance through high thread parallelism (number of simultaneously active threads). High parallelism shortens execution time, but it may also potentially increase synchronisation time. Furthermore, the complexity of the memory hierarchy causes diverse access latency from cores depending on the level of cache where data are placed. To alleviate access latency, threads can be fixed to certain cores to improve their resource usage, such as cache, main memory and interconnections. Therefore, the overall performance of a parallel application not only depends on its level of thread parallelism but also its thread localities on the cores.

The conventional way to address synchronisation is via locks. However, locks are notorious for various issues such as deadlocks as well as the vulnerability to failure and faults. Moreover, it is not straightforward to analyse interaction among concurrent operations. Transactional memory (TM) has emerged as an alternative parallel programming technique that handle synchronisation through transactions rather than locks. Access to shared data is enclosed in transactions that are executed speculatively without blocking by locks. Various TM schemes have been developed including Hardware Transactional Memory (HTM) [2], Software Transactional Memory (STM) [3] and Hybrid Transactional Memory (HyTM) [4]. This thesis presents the work on thread management under STM systems where the synchronisation time originates from transaction aborts. There are different ways to reduce the number of aborts, such as the design of contention manager policies (resolve conflicts among transactions), the way to detect conflicts (detect at early stage or later stage), the setting of version management (handles the storage policy for permanent and transient data copies) and the level of thread parallelism.

Online parallelism adaptation recently begins to receive attention. A suitable parallelism degree in a program can significantly impact on program performance. However, it is onerous to determine a parallelism degree for a program offline especially for the one with online behaviour variation. With regard to programs with online behaviour fluctuations, there is no single parallelism degree can enable its optimum performance. Therefore the natural solution consists of monitoring the program at runtime and altering its parallelism when necessary. Additionally, application performance is affected by diverse locations of threads. When the active thread number varies, locations that threads are pinned to may also need to be adjusted accordingly in order to optimise usage of the memory hierarchy. Pinning multiple threads to specific cores is called thread mapping [5] and specifying a thread to a specific core is addressed as thread affinity setting.

Furthermore, the diversity of TM applications and their supporting TM platforms together with the complexity of multi-core processor architecture make it difficult to decide the configurations of various parameters offline. Dynamical interactions among applications, TM platforms and underlying hardware can impact on system performance. All the aforementioned issues are preferred to be dealt with at runtime. Autonomic computing [6] is a technique that can automatically manage systems given high-level objectives. This thesis introduces feedback control loops into STM systems to achieve autonomic computing, more specifically, to automatically regulate thread

parallelism and mapping at runtime.

### 1.1 Contributions

This doctoral dissertation contributes to the areas of parallel systems and autonomic computing. It argues that online thread management is necessary and feasible for STM systems. It demonstrates that program performance is sensitive to thread parallelism and mapping. The contributions of this dissertation are as follows which have been partially published in [7, 8, 9, 10]:

- 1. Feedback control loops are employed to manage STM systems at runtime.

- 2. Two models are presented to detect near-optimum parallelism degrees for STM systems.

- 3. A model is proposed to coordinate adaptation of thread parallelism and mapping.

- 4. Two runtime phase detection algorithms are proposed and evaluated.

## 1.2 Thesis Outline

This thesis firstly present the relevant background in Chapter 2 to assist readers to better understand the remaining chapters. Chapter 2 begins with the description of multi-core processors and continues with the background on synchronisation mechanisms. This chapter later introduces the diverse benchmark applications utilised in this thesis for performance evaluation. Autonomic computing technique is presented lastly.

Chapter 3 proceeds to outline the overall proposed system architecture and the description of phase detection algorithms. The phase detection algorithms are utilised in the following three contribution chapters.

Chapter 4, Chapter 5 and Chapter 6 progressively detail the contributions of the thesis on thread parallelism control, thread mapping control and their coordination. Chapter 4 describes two approaches that can dynamically adjust parallelism degrees. Chapter 5 presents the method for managing thread localities. Chapter 6 gives coordination of parallelism and thread localities.

Related work is reviewed in Chapter 7 to describe the state of art and compare its significance with the contribution of this dissertation.

The last chapter (Chapter 8) gives conclusion remarks and proposes future work.

Background

## Chapter 2

## **Background**

The performance of a parallel application can be significantly affected by: its thread parallelism degree, the location of threads on cores and the synchronisation mechanisms that are used to deal with concurrent access. This chapter describes significant historical background techniques and technologies to motivate and better understand the contributions of this dissertation. This chapter is organised as follows.

To start with, Section 2.1 describes the background information on modern multicore processors which facilitates understanding of the rationales of performance impact from parallelism degree and thread affinity. Next, Section 2.2 reviews the main synchronisation mechanisms. The synchronisation techniques and technologies on Transactional Memory (TM) are described separately in the following section (Section 2.3). Then Section 2.4 introduces two benchmark suites that are widely used for performance evaluation on TM systems. Lastly, Section 2.5 outlines the necessary background on autonomic computing techniques, as autonomic computing plays a significant role in the methodologies that presented in this doctoral dissertation. Autonomic computing facilitates the Software Transactional Memory (STM) system in monitoring its runtime behaviour and responding to the changes accordingly.

### 2.1 Multi-core Processors

Moore's Law [11] (doubling of transistors on a chip every 18 months) has been a fundamental driving force of processor designs. However, since 2005, processor designers have increased core counts to exploit Moore's Law scaling, rather than focusing on single-core performance [12], as the increase in CPU clock frequency is approaching a physical end. It is intricate to continue increasing computing speed of a single-core

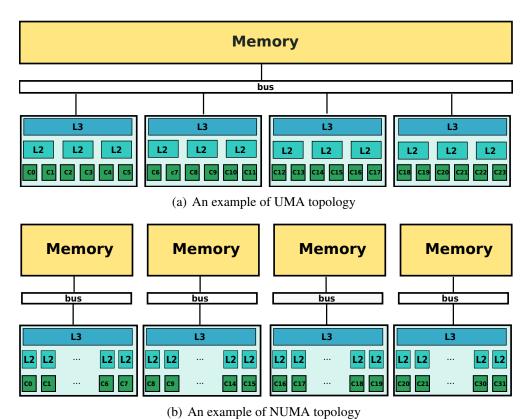

processor based on current techniques and technologies, hence an alternative way to continuously improve performance for a high-end processor is to support many cores on one processor and multiple processors on one platform. A multi-core platform outstrips a single-core platform by scheduling multiple threads (or processes) for executing programs simultaneously. This somehow relieves the demands for high CPU clock frequency. Although structures of multi-core platforms can vary from manufacturers, they mainly fall into two classes [13]: centralized shared-memory architecture and distributed memory architecture. The first group is also known as uniform memory access (UMA), as all the processors have the equal access to one single centralized memory. The second group consists of multi-processors with distributed memory, known as Non-Uniform Memory Access (NUMA). Fig. 2.1 gives examples of UMA and NUMA platforms which are the topologies of the platforms utilised for performance evaluation in this thesis. The details of the platform configurations are provided in Table 2.1.

Figure 2.1: Examples of UMA and NUMA platforms. Performance Evaluation is performed on the two machines.

Each socket of the UMA machine includes 6 cores and every two cores share a L2 cache, every 6 cores share a L3 cache and all cores share the main memory. Each

socket of the NUMA machine includes 8 cores. Each core has its own L2 cache and 8 cores share a L3 cache.

| Characteristics        | UMA              | NUMA                     |

|------------------------|------------------|--------------------------|

| Processor              | Intel Xeon X7460 | Intel Xeon Beckton X7560 |

| number of cores        | 24               | 32                       |

| number of sockets      | 4                | 4                        |

| clock (GHz)            | 2.66             | 2.27                     |

| L1 cache capacity (KB) | 32 (each)        | 32 (each)                |

| L2 cache capacity (KB) | 3072 (each)      | 256 (each)               |

| L3 cache capacity(MB)  | 16 (each)        | 24 (each)                |

| DRAM capacity (GB)     | 64               | 16 (each)                |

Table 2.1: Configurations for the UMA and NUMA platforms.

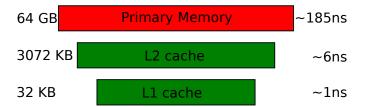

In both UMA and NUMA groups, as the distance between a core and a memory increases, the time to access data rises. More specifically, the time latency is lower to access L1 or L2 cache than that to the main memory. When it refers to a NUMA machine, the time latency is alleviated from a core to a remote memory (in contrast with its access to its local memory). The distributed memory in a NUMA machine is accessed via an *interconnect* by a core from its contiguous memory. Fig. 2.2 illustrates the access latency from the core to different memory levels<sup>1</sup>. Placing threads on the sibling cores which share all the levels of memory structure allows threads to reuse the data which already resides in the cache. This strategy can benefit the applications whose threads possess a significant amount of joint data access. Some applications showing disjoint data access may benefit from placement of distributed threads on cores, meaning that the threads do not always share the underlying memory structure, as it can alleviate potential contention.

Figure 2.2: An illustration for access latency of diverse memory levels.

Most current processors are homogeneous both in instruction set architecture and

<sup>&</sup>lt;sup>1</sup>**Lmbench** [14] is utilised to measure the latency of the UMA platform in Table 2.1. The L3 cache latency is skipped in the figured.

performance [15]. Some architecture, however, allow system software to control the clock frequency for each core individually in order to either save power or to temporarily boost single-thread performance. In contrast, heterogeneous architecture features at least two different kinds of cores that may differ in both the instruction set architecture, functionality and performance. The technique and technology on heterogeneous processors [16] are beyond the scope of the dissertation, the author is only concerned with homogeneous processors that keep clock frequency constant.

## 2.1.1 Thread affinity

Multi-core processors enhance program performance, *i.e.* reduce execution time, through high parallelism (number of simultaneous active threads). Furthermore, the complexity of modern memory hierarchies give diverse access latency from different cores, hence it becomes interesting to find the suitable tactic for thread placement in order to leverage resource usage. Applications that require significant interaction among threads, a small difference in thread management can give a non-trivial performance impact [17]. Assigning multiple threads to specific cores is called *thread mapping* [5] and fixing a thread to a specific core is called setting the *thread affinity*. In multi-core systems, there are three objectives in optimising thread placement [18]:

- **Better use of interconnects**. For instance, to reduce off-chip traffic by using intra-chip interconnects which have a higher bandwidth and lower latency.

- Reducing invalidation misses. A *invalidation miss* is when the data was already resident in the cache but is evicted by other cache lines. A common situation in shared-memory is to have one thread writing to an area of memory and another thread reading from the same location. This can cause one thread continuously to invalidate the cache lines of the other's. The objective of a thread mapping strategy is to reduce invalidation misses caused by two private caches holding the same data and continuously invalidating each other.

- Reducing compulsory misses. A *compulsory miss* (also known as *cold miss*) is caused by competition for the same cache. Threads will evict cache lines from each other if they share one cache, however, those cache lines would not be evicted if threads accessed the same group of addresses.

There are two means of tackling thread affinity [19] in most of operating systems. The first one, which is called soft affinity, relies on the traditional OS scheduler where

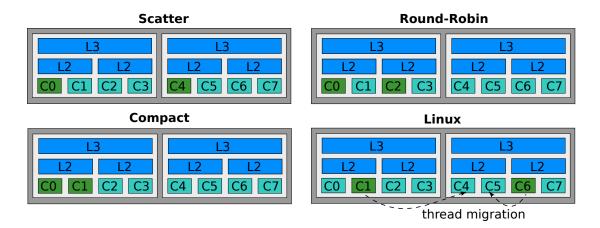

Figure 2.3: Four thread mapping strategies [5].

threads remain on the same core as long as possible. However, the OS scheduler may still migrate threads to another core or processor, possibly unnecessary, which impact on system performance. The second way of handling thread affinity is named hard affinity, meaning that allocation of threads is controlled by users. Depending on the number of cores and the memory hierarchy, there can be many different strategies to implement thread mapping. Using exhaustive search (which is utilised for optimisation on some conventional parallel program) by trying all the cases to figure out the best placement strategy is not feasible, especially when a large number of threads are involved. However if putting main memory aside, thread mapping strategies can be categorised into four main groups proposed by [5] as illustrated in Fig. 2.3:

- Compact: threads are placed on the sibling cores. This strategy is beneficial to applications in which the same amount of data is accessed by its threads. Threads sharing data but scheduled on the cores without sharing cache can result in excessive data movement and high network traffic [20].

- **Scatter**: threads are distributed across processors. Equally distributing threads is also addressed as *thread balancing* [21]. This strategy averts cache sharing among cores in order to reduce contention on the same cache. It is beneficial to applications whose thread mainly access disjoint data.

- **Round-Robin**: threads are placed on the cores where a higher level of cache (*e.g.* L3) is shared but not the lower level of cache (*e.g.* L2). This strategy can only be applied on the platforms which have more than one L3 shared cache and where the L2 cache is shared by more than one core.

• Linux: the default Linux scheduling strategy. It is based on dynamical priority-based strategy that allows threads to migrate to idle cores to balance the run queues. This mapping strategy corresponds to soft affinity, whereas the other three strategies coincide with hard affinity.

It causes thread migration to dynamically assign threads to specific cores. The most significant source of performance penalty when a thread migrates between cores is the loss of cache state [22]. The frequency of changing thread placement on cores is as important as the design of thread mapping strategies.

## 2.1.2 Memory Affinity

Memory affinity [23] is ensured when data is efficiently distributed over the machine memory. Such data distribution can either reduce the number of remote access or the memory contention. In the linux operating system, the default way to handle memory affinity is called *first-touch* [24], which places data on the node where is first accessed. In this dissertation, the author concerns little with direct manipulation of data placement in memory, but is more interested in investigating performance impact brought by thread affinity.

Multi-core processors bring parallel computing to the mainstream. Despite the potential performance boost by high concurrency, a parallel program is more difficult to write than a sequential program due to the necessity of synchronisation taking place among the concurrent tasks. There exists diverse techniques to address synchronisation issues as introduced in the following two sections.

## 2.2 Synchronisation Mechanisms

Multi-core platforms increase application performance by executing multiple threads concurrently. Threads must communicate and exchange data to complete their tasks, this is called *thread synchronisation*.

## 2.2.1 Lock-based Synchronisation Techniques

The conventional way to address synchronisation is through locks. Locks protect critical sections granting unique access by one CPU or one thread. The higher the parallelism is, the more time it may spend in contending for the lock. The time spent

in contending for the lock is called synchronisation cost. Lock-based synchronisation suffers from several limitations [25]:

- 1. **Deadlock**. This can cause the whole system to halt if circular dependencies exist where every job is stalled waiting for another job to complete.

- 2. **Long delay**. When one job which is the owner of a shared resource happens to be delayed, it causes all the other jobs which require the same resource access delayed.

- 3. **Priority inversion**. It happens when a higher priority task attempts to lock a mutex that is already locked by a lower priority task. Assuming  $P_1$ ,  $P_2$  and  $P_3$  are low, medium and high priority tasks, respectively. If  $P_1$  holds the mutex and  $P_3$  has to wait for the release of the mutex from  $P_1$ . However if  $P_2$  has been running before  $P_1$  holds the mutex,  $P_2$  will take precedence over  $P_3$ . The high priority task  $P_3$  faces un unpredicted delay before it can run and it may miss its execution deadline.

The listed pitfalls result in the advent of other techniques to handle synchronisation issues as described in Section 2.2.2 and Section 2.3.

## 2.2.2 Other Synchronisation Techniques

One way to bypass locks is to utilise atomic primitives such as *CompareAndSet*. Non-blocking synchronisation algorithms are the ones that employ atomic primitives to achieve lock-free synchronisation.

Non-blocking synchronisation has its obvious advantages over lock-based synchronisation (or sometimes called blocking synchronisation) on the isolation between processes or threads accessing a shared object. This means that several processes or threads can operate on a critical section concurrently. An algorithm [25] is a *non-blocking algorithm* (sometimes called *lock-free*) if it guarantees that at least one process can complete a task or make progress within a finite time. In the literature, non-blocking synchronisation falls into three primary classes [26]:

• *Obstruction freedom*. It provides single-thread progress guarantees in the absence of conflicting operations. It does not rule out livelocks, as the threads may repeatedly preventing each other from making progress [27].

- *Lock freedom*. It provides system-wide progress guarantees. At least one process or thread is guaranteed to complete in a finite number of steps.

- Wait freedom. Every active process or thread can complete in a finite number of steps, regardless of the execution speeds on the others. It provides fault-tolerance [28], meaning that no process or thread can be prohibited from completing an operation by unknown halting failures of others, or by arbitrary fluctuations in their speed.

On one hand, non-blocking synchronisation mechanisms rely on atomic primitives, which can only operate on one word at a time resulting in complex structure for the algorithms. On the other hand, such mechanisms introduce extra cost to ensure that an object remains in one state where progress can be made even if the current process/thread dies. An alternative mechanism to tackle synchronisation issues is transactional memory, which overcomes the aforementioned drawbacks and shifts the burden of correct synchronisation from a programmer to a transactional memory system. Strictly speaking, transactional memory can be defined as a generic non-blocking synchronisation construct that allows correct sequential objects to be converted into concurrent objects [29].

## 2.3 Transactional Memory

Transactional memory (TM) emerges as an alternative parallel programming technique, which addresses synchronisation issues through transactions. The access to the shared data is enclosed in transactions that are executed speculatively without blocking by locks. Given that actual conflicts are rare in many applications [30], the TM approach is promising as the future programming model. The original idea of transactional memory dates back to 1977, when *Lomet et al.* [31] realised that an abstraction similar to a database transaction [32] might make a good programming language mechanism to ensure the consistency of data shared among several processes. Since then various TM schemes have been developed [2, 3, 4] including Hardware Transactional Memory (HTM), Software Transactional Memory (STM) and Hybrid Transactional Memory (HyTM).

## 2.3.1 Concepts of Transactional Memory

A transaction [33, 2] is a finite sequence of machine instructions, executed by a single process, satisfying the following properties:

- **Serializability**. The steps of one transaction never interleave with the steps of another.

- Atomicity. Each transaction makes a sequence of tentative changes to shared memory. When the transaction completes, it can either *commit*, making the changes to the memory permanent, or it can *abort* causing the previous changes to be discarded.

| Tx management operations    | Data access operations                |  |  |

|-----------------------------|---------------------------------------|--|--|

| <pre>void StartTx();</pre>  | T ReadTx (T *addr);                   |  |  |

| <pre>bool CommitTx();</pre> | <pre>void WriteTx(T *addr,T v);</pre> |  |  |

| <pre>void AbortTx();</pre>  |                                       |  |  |

|                             |                                       |  |  |

Figure 2.4: The basic operations of TM

A transaction behaves as a logical unit, and its operations are either performed entirely or not performed at all. In other words, it behaves as if it were a single instruction. Failed transactions will be executed again. The stylised TM interface provides a set of operations for managing transactions and accessing data [34] without explicitly acquiring and releasing locks, as they are all handled by the TM implementation. Fig. 2.4 shows the basic operations for programming in TM. *StartTx* begins a new transaction in the current thread. So instead of acquiring a lock to access the critical section, in TM a *StartTx* instruction begins a task. *CommitTx* attempts to commit the current transaction but it may succeed or fail. Besides the commit operation, some systems also provide *AbortTx* which explicitly aborts the current transaction regardless of its conflict situation. The data access operations *ReadTx* takes the address *addr* of a value in type *T* and returns the transaction's view of the data at that address. *WriteTx*

```

do {

StartTx(); //start a new Tx

int tmp_x = ReadTx(&x); //read from x

int tmp_y = ReadTx(&y); //read from y

WriteTx(&y, tmp_x+tmp_y+1); write tmp_x+tmp_y+1 to y

} while (!CommitTx()); //commit the current transaction

```

Figure 2.5: A simple example on usage of transaction primitives [34].

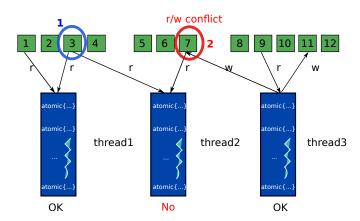

Figure 2.6: An example of transaction conflicts in TM. Object 3 and object 7 are accessing concurrently by different threads. A read and write conflict happens between thread 2 and thread 3.

takes an address *addr* and a new value *V*, writing the value to the transaction's view of that address. The data value type *T* differs from one system to another. With TM, the programmer specifies intents rather than mechanisms leading to a higher-level abstraction than locks. For instance, the programmer can concentrate on the decisions of the placement of the atomicity, in preference to the mechanisms that are used to enforce the intent [35]. Fig. 2.5 illustrates a simple example on usage of the transactional primitives of Fig. 2.4.

Conflicts can happen during a transaction execution or when it is committing. Fig. 2.6 shows an example of conflicting transactions. In the example, each thread executes a sequence of transactions. A read and write conflict happens between thread2 and thread3 when they are accessing the shared object7 concurrently. Object3 is read concurrently by two threads. Two read operations do not cause any aborts. TM employs various synchronisation mechanisms to mediate the read/write or write/write conflicts. Broadly speaking, there are two approaches for conflict control: pessimistic concurrency control and optimistic concurrency control. Pessimistic concurrency control detects and solves the conflicts at the same time when a transaction is about to access a location. This type of conflict control grants the data ownership to a transaction therefore preventing other transactions from accessing the same data. In *optimistic* concurrency control, the conflicts detection and resolution are delayed after data access therefore allowing multiple transactions to access the same data. When conflicts are frequent, the pessimistic concurrency control is favoured, as it enables a transaction to complete all of its operations once the access permission is granted. However, if the conflicts are rare, pessimistic concurrency control is inferior to optimistic concurrency

control as the later one increments the concurrency level by avoiding the locks.

TM provides serializability and atomicity. Hardware transactional memory rarely requires locking mechanisms, yet locks can not be completely removed especially for software transactional memory [36]. Since conflicts can not be avoided, different design choices have been designed aiming to diminish conflicts which are mainly based on: when to detect a conflict, how to solve a conflict and how to manage memory log.

## 2.3.2 TM Design Choices

There are four key aspects for TM designs: **granularity**, **conflict detection**, **conflict resolution** and **version management**. Every aspect includes multiple design choices which are either fixed for a TM system or can be selected by users before application execution. In some cases, it is possible to switch design choices at runtime. It is worth noting that the two approaches for conflict control (pessimistic and optimistic concurrency control) introduced in Section 2.3.1 are composed of conflict detection policies and conflict resolution policy. This section will unroll more details on that.

#### Granularity

Transaction granularity [34] is the unit of storage in which a TM system detects conflicts. The choice of granularity impacts on TM performance. Similar to the cache granularity, a fine granularity reduces false conflicts while a coarse granularity reduces overhead. HTM often uses cache-line granularity, so that the conflict is detected when a transaction is trying to change the status of a cache line. While STM operates on word or block granularity. Some TM systems employ object granularity which extends transactional protection to an entire object at once.

#### **Conflict Detection Policy**

Conflict detection [37] dictates when to check the read/write sets to detect conflicts. Two major designs are often employed, namely eager and lazy. The eager option detects conflicts for every memory access. The lazy option detects conflicts when a commit is required. The former option observes conflicts at early stage thus obviating large-size abort, but it can potentially impose high abort rate. The later option, on the other hand, delays the abort time which reduces the abort rate, however, it causes large-size aborts.

17

#### **Contention Manager**

The *contention manager* (CM) decides the actions to be taken in order to resolve conflicts. When a transaction encounters a conflict with another transactions, three possible decisions can be made [37]:

- *abort-other*: also known as *suicide*, when a transaction encounters a conflict with other transactions, it will kill the others which are in conflicts with so that its own data validation can be guaranteed.

- *abort-itself*: also known as *aggressive*, when a transaction detects conflicts with other transactions, it will kill itself to ensure the data validation of other transactions. This policy performs well on a lowly-contended application, but scales badly on highly-contended application as the aborted transactions are restarted right after the conflict is detected and are doomed to abort several times before a successful commit [5].

- *backoff*: when a transaction meets a conflict with other transactions (1) instead of aborting itself immediately, it stalls for a certain period of time and rechecks its data validation once it resumes; (2) it aborts immediately and stalls for a certain period before its re-execution.

Various conflict resolutions are proposed based on the above three schemes aiming to: minimise wasted work (aborts), avoid future conflicts and reduce the overhead of executing CM itself.

#### **Version Management**

Version management [34] handles the storage policy for permanent and transient data copies. The policy can be eager (also called write-throughput) or lazy (also known as write-back). Eager policy logs the old data and replaces the memory with the new data. Lazy policy logs new data and keeps the old data in memory. The former policy has lower commit-time overhead hence it is preferred for tackling read-after-write or write-after-write operations. The latter policy has lower abort overhead and does not require extra work to guarantee consistent reads.

## 2.3.3 TM Metrics

Different metrics in TM can be utilised to indicate the characteristics of TM applications, *Ansari et al.* [38] summarised the commonly used ones and proposed two additional new metrics as follows:

- **speedup**. This metric is intuitive. It depends on characteristics of both the application and the TM implementation.

- in transaction. It is the percentage of total time that the applications spent in transactions. Noting that non-transactional code also exists in a TM application. This metric, however, does not indicate application performance.

- wasted work. The aborted transactions. It is often calculated by dividing the total time spent in the aborted transactions by the time spent in all transactions. Or some works [39, 40, 41] are in favour of addressing wasted work as the total time spent in aborted transactions.

- **aborts per commit**. It indicates the mean aborted transactions per committed transactions.

- abort histograms. It details how abort per commit is spread among the transactions.

- **contention management time**. It is the percentage of time the mean committed transaction spends in performing contention management.

- transaction execution time histograms. It shows the spread of execution times of committed transactions. This metric is useful as it illustrates how homogeneous or heterogeneous the amount of work contained in transactions for a given application is. For instance, an application is more homogeneous with all its transaction executing the same code block, and less so when its transactions executing a group of code blocks.

- **instantaneous commit rate**. It shows the proportion of committed transactions at sample points during the execution of the application. Note that active transactions are not taken into account.

- **readset & writeset**. Size of read and write operations of a transaction. It facilitates the selection of buffer size or cache size for HTM. A *readset* of a transaction

is the set of locations read by the transaction. A *writeset* of a transaction is a set of locations accessed by the transaction.

- readset-to-writeset ratio. It indicates the mean number of reads lead to a write in a committed transaction.

- writes-to-writeset ratio. The mean number of writes to a transaction data element.

- **reads-to-readset ratio**. The mean number of reads to a transactional data element.

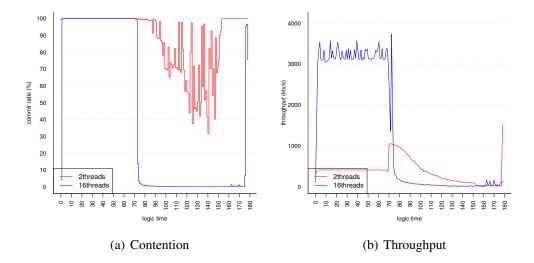

Additionally, two metrics are useful to indicate the online TM application performance, namely *commit ratio* (CR) and *throughput*. CR equals the number of commits divided by the number of commits and aborts; it measures the level of conflict or contention among the current transactions. Throughput is the number of commits in one unit of time; it directly indicates transaction progress rate. The two metrics will be discussed in more details in Chapter 3.

# 2.3.4 Implementation Schemes

Diverse implementation schemes have been developed [2, 3, 4] including Hardware Transactional Memory (HTM), Software Transactional Memory (STM) and Hybrid Transactional Memory (HyTM).

## **Software Transactional Memory**

A Software Transactional Memory (STM) system implements all its transactional semantics in software. It provides a lock-free programming interface, however, the STM system itself is not necessarily lock-free. STM requires a sequence of locks to manage concurrent access to shared data. Contrasting with a lock-protected critical section which hinders concurrent access by multiple threads, STM locks are used to indicate the ownership by certain transactions [3]. This information is used later to detect conflicts when a transaction tries to commit. A programmer neither needs to indicate where to acquire/release locks nor to identify which operations may be allowed to execute concurrently, as this responsibility is taken by the TM implementation. The old data are logged and recovered once an abort takes place. Since both the old and new data are stored, there is a high demand for memory storage. When a transaction needs

to commit, it has to traverse its previous accessed locations to ensure that the data read previously has not been changed. Implementation of such a functionality purely in software delivers a high runtime cost making STM performance-wise inefficient for general purpose parallel programs. STM systems present worse performance than locks when a small number of threads are used. In contrast, in some cases where there is a high concurrency level with rare conflicts, STM systems manifest comparable or even better performance than conventional locks [1]. As when the number of threads rises, the cost of contending for locks rises accordingly.

This dissertation is concerned with STM systems as they are flexible (*e.g.* it is easy to modify their conflict control polices and they have straightforward interfaces) and rely little on underlying specific TM hardware supports. A brief description of state-of-the-art STM systems will be given later in Section 2.3.5.

## **Hardware Transactional Memory**

Hardware Transactional Memory (HTM) implements its all transactional functionalities in hardware. A HTM system starts a transaction by executing a register checkpoint with shadow register files [42]. A *checkpoint* [43] is a program location in a transaction where control may jump during a partial abort. The cache coherence protocols of processors are modified to be compatible with transactional execution. A processor preserves two caches: one regular cache for non-transactional access and one transactional cache for transactional access. The transactional cache does not propagate the tentative writes to other processors or write to the main memory unless otherwise a transaction commits. A commit makes tentative writes visible to other processors and writes back the updates to the main memory. A conflict is detected by comparing the readsets and writesets. Once a conflict occurs, at least one of the transactions aborts and restores the values saved at the checkpoint at the start of the transaction to the registers. Meanwhile the previous tentative writes are dropped by the transactional cache.

Intel has introduced hardware support (Intel TSX) for TM in the Intel 4th Generation core <sup>TM</sup> processors [44] in 2012. L1 data cache tracks transactional states in the granularity of a cache line and detect conflicts through cache coherence protocol. Intel TSX provides developers with two software interfaces to specify the critical sections, namely hardware lock elision (HLE) and restricted transactional memory (RTM). In HLE, an abort may lead a transaction to fall back to a lock-based execution to avert successive aborts which hinders the program progress. RTM requires a programmer

to provide a software handler to tackle transaction aborts. This allows the possibility of other strategies to solve aborts rather than giving up immediately on hardware transactions [45].

HTM systems, as all the functionalities are implemented into hardware, indicate a lower overhead than STM systems thus faster execution. Just as the initial intention of TM design, HTM systems do not necessarily require locking mechanisms. Nevertheless, HTM imposes restraints on the resource capacity, such as cache capacity. Furthermore, HTM offers limited scope for contention management which plays an important role in forward progress, thus persisting aborts exist in HTM. A common solution to this restraint is to grant the transaction a lock to ensure an exclusive execution, yet acquiring a lock by a transaction causes other transactions to abort. This can lead to a chain effect known as *lemming effect* where the other aborted transactions endeavour to obtain the lock [46]. An alternative solution to gain good performance as well as flexible size of atomicity is to combine HTM with STM.

## **Hybrid Transactional Memory**

The construction of Hybrid TM (HyTM) system combines the base STM with a generic HTM system, thus removing part of high cost imposed by software data structure and also increasing the resource capacity limited by HTM. A transaction starts and progresses in the HTM mode and only enters the STM mode when a transaction aborts a certain number of times. Some tactics can be employed to reduce the abort rate reckoning on the causes of aborts [47]. An abort caused by hardware resource constraints will be executed in the STM mode as retrying in a HTM will still lead to persisting aborts. An abort due to conflicts can be re-executed in the HTM mode repeatedly.

Since both HTM and STM modes exist in one TM system, the additional complexity is added due to the intricacy of detecting the conflicts between a HTM mode transaction and a STM mode transaction [5]. *Per contra*, it is reported that HyTM can negatively affect some desirable properties of the original STM, especially the fairness of resource access [36].

# 2.3.5 Software Transactional Memory Platforms

Section 2.3.4 has briefly discussed the techniques of STM which mainly concentrates on the comparison of its difference with HTM and HyTM. This section presents implementations of different STM systems and compare their differences. Particularly,

TinySTM, which is reviewed in the end of the section, is utilised in the thesis as the STM platform. STM systems can be implemented in a library or directly into a compiler. A library-based approach relies on the programmer to convert sequential code or lock-based code into transactional code. A compiler or preprocessor can be used to enable automatic transformation. STM systems can also be classified by its programming languages (*e.g.* C, C++, Java, C#, Python, Perl, Haskell, Scala) and its granularities of data sharing (word-based or object-based). Despite the diversity, the following STM systems share some common features:

- global timestamp. It is logic timestamp, which is incremented by one per commit or write operation. The transaction checks the timestamp of its previously accessed objects upon its commit. A transaction can successfully commit if the timestamp of the previous accessed objects stay consistent.

- array of locks. Memory locations are mapped to locks based on certain functions. Locks are utilised to manage concurrent access to memory locations rather than stalling threads. The content of a lock can be either an address of an owner transaction or a timestamp (details are presented in the following sections).

## TL2

Transactional locking II (TL2) algorithm [48] is the second version of the original transactional locking (TL) proposed by *Dice et al.*. The TL2 algorithm introduces a global version-lock that is augmented by each writing transaction at commit time. Each thread has a local variable to load the current value of the global version number. Every transactional memory location is associated with a write-lock. A lock contains a bit indicating whether the lock is taken and the rest of the bits indicating a version number. The version number is the timestamp.

TL2 employs a two-phase locking scheme. A transaction first obtains the current value of the global version clock (called read version number ) and stores it in a thread local variable. Every load operation is followed by a validation operation, which checks if the location's write lock is free (to check if it is conflicting with other transactions) and has not been changed. Additionally, the lock's write version number (a version number associated by a write lock) should be no greater than the transaction's read version number. Otherwise the transaction aborts, as the memory location has been modified after the current thread performs the load operation. All the transactions are executed speculatively and conduct no change to the shared memory states

before committing. At the end of the speculative execution, all the previous performed operations of one transaction need to be revalidated. This is achieved by comparing the read version number with the lock's version number. When the version number of the write lock is greater than the read version number, the transaction is aborted. The new version number is recorded in a local variable. At commit time, the new value should be stored to the memory location and the locations locked should be released. One exception is when a read version number plus one equals a write version number, validation of the read transaction can be skipped.

To reduce the overhead the global version number is split into two parts: one part for the version number, and one part for the thread id (which records the last thread that updated it). A thread does not need to change the version number if it detects the global version number differs from its version number. A thread only performs an update (increment by one) to the global version number when its own version number equals the global one.

#### **SwissTM**

SwissTM [49] is a lock-based STM which utilises word-based granularity to map memory locations to locks. It employs a global commit counter (timestamp) which is incremented by every non-read only transaction and used for transaction validation upon commits. Every transaction starts by reading the global commit counter. When the transaction reads a memory location, it first reads the write lock. If the transaction does not own the current write lock, it reads the read lock and reads the read lock again after its reading operation. The read operation is validated if the values of the read lock at the two consecutive reads are the same. Upon the successful validation, the transaction extends its validation timestamp to the value of the current global commit counter. If validation fails, the transaction rolls back. When the transaction writes to a memory location, it also first checks if it owns the write lock. The transaction updates the value in the memory location directly if it already owns the lock, otherwise the transaction tries to obtain the write lock. Failing to obtain the write lock leads to intervention of the contention manager which decides how to resolve the conflict. Upon commit, a read-only transaction can commit immediately. A transaction with write operations has to validate all its previous read operations to guarantee their consistence with the current state of the values. Upon successful validation, the transaction updates the memory location and releases the read and write locks as well as incrementing the global commit counter.

SwissTM employs a conflict detection scheme that treat transactions differently from TL2. It detects write/write conflict eagerly to prevent transactions that are doomed to abort from further wasting resource; it detects read/write conflicts lazily to allow more parallelism. A two-phase contention manager is employed in SwissTM which incurs no overhead on read-only and short read-write transactions and allows the transactions which have performed a significant number of updates to progress. Each transaction records its write access which indicates the phase. The first phase marks the number of writes less than a threshold. A transaction aborts and restarts immediately once a conflict is met during the first phase. When exceeding this threshold, transactions are in the second phase where they abort and back-off. In addition, the transactions that abort due to write/write conflicts back-off for a period which is proportional to the number of the successive aborts.

#### **RSTM**

Rochester Software Transactional Memory (RSTM) [50] is one of the oldest open-source STM systems. RSTM is a C++ library for object-oriented transactional programming. It includes several STM algorithms that allow it to be customised to suit a given workload. The implementations of the algorithms can differ in: bookkeeping, visible reader management and memory management.

There are two major types of bookkeeping strategies, i.e. DSTM [27] and OSTM [51]. DSTM dynamically initialises and deletes the transaction locator (the shared data) which is accessed by transactions. The locator contains the information of the latest transaction which has written to it, the new data version and the old data version. The transaction utilises an object header (a pointer) to points to the locator so that the contents of the locator can be modified atomically. While in OSTM, each transaction maintains a transaction descriptor which records a list of the shared read and a list of shared write objects. The lists contain object handles which refer to the object header (a pointer which points to the current object). Each time when a transaction needs to access an object, it accesses an object header. In contrast, RSTM mixes the above two strategies, rather than utilising a locator, RSTM merges its contents into the new data object which also points to the old data object. Each transaction also owns a transaction descriptor which only contains the status of the transaction (in contrast with OSTM's descriptor, which also maintains two lists of read and write objects). When a transaction demands access to an object, it accesses an object header which points to the share objects. The object header also maintains a list of visible reads which

serves to avoid the cost of validating invisible reads. The object header and transaction descriptor of RSTM require no dynamic memory allocation.

## **TinySTM**

TinySTM [3] is a word-based (granularity) lightweight STM system which employs a shared array of locks to control concurrent access to memory and applies a shared counter as clock to indicate the global timestamp. The role of locks in TinySTM is to enable atomicity when hardware support is missing, rather than locking memory locations, therefore its locks do not intercept memory access by multiple threads.

A TinySTM lock is the size of an address with its least significant bit indicating whether the lock is owned by a transaction. If not owned, the remaining bits of the lock store the version number (timestamp) of the transaction which is the last to write to one of the memory locations covered by the lock. If it is owned, the remaining bits store an address to either the owner transaction (when using write-through version management) or to an entry in the write set of the owner transaction (write-back version management). When the least significant bit is set, a writing transaction first checks if it is the owner of the lock, if not, the transaction can write the new value directly otherwise it has to wait for a certain period or abort immediately. If the least significant bit is not set, the writing transaction tries to acquire the lock by setting this bit using an atomic operation (*e.g.* Compare and Swap). A failure indicates that another transaction has acquired the lock concurrently. A reading operation by a transaction verifies if the lock is owned or updated concurrently. A reading operation is consistent if the lock is not owned and its value has not been changed between both read operations.

At commit time, a transaction needs to verify its previous read operations. The verification process can be costly. TinySTM employs hierarchical locking to diminish the cost of validating a large chunk of memory. In addition to the shared array of locks, a smaller hierarchical array of counters (different from the global counter which is used as the timestamp) are maintained. Multiple locks are mapped to one counter using a hash function. Transactions additionally maintain a read mask and write mask specifically for the counters. A read operation sets its read mask and stores the value of the counter, and a write operation sets its write mask and increments the counter. Upon validation, the counters with corresponding read masks set are checked if: the value of the counter is equal to the stored value in the transaction, or the counter is one more than the stored value when the write mask is set. If true, the corresponding locks traverse can be skipped. Comparing the locks in TL2, TinySTM does not require

storing of the thread id and it provides an additional hierarchical locking layer to gain performance for read operation validation.

TinySTM provides memory-management functions that allow transactional code to use dynamic memory. Transactions keep track of memory allocated or freed: allocated memory is automatically disposed of upon abort, and freed memory is not disposed of until commit. Furthermore, a transaction can only free the memory locations after it has acquired all the locks covering the memory locations.

TinySTM provides interfaces allowing users to choose different parameters easily, such as conflict detection policies, version management policies and CM policies. Additionally, it also grants easy interface to user-defined functions.

## 2.3.6 Restrictions of STM

Despite of its merits, a STM system is complicated. It incorporates numerous tunable parameters such as contention manger, version management policy and so forth. Such tunable parameters are usually set prior to application execution and remain consistent during the whole program execution. Few actions from the STM can be made to adapt the system to the diversity of program runtime behaviour. Alongside the underlying multi-core processors and divergence of the applications, the intricacy is further enhanced. Manual offline tuning is arduous and less precise. *Autonomic computing* (Section 2.5) is capable of monitoring the behaviour of applications and STM systems at runtime and tuning their parameters accordingly to ameliorate performance. Before starting to investigate autonomic computing techniques, it is necessary to present several benchmark applications that are widely used to evaluate performance of TM systems in the next section.

# 2.4 Benchmarks for Evaluation of TM Systems

Since the advent of the first TM proposal, efforts have been seen to develop TM microbenchmarks and benchmarks to evaluate performance of TM implementations. This section gives a brief introduction to the benchmark suites that are utilised in the dissertation: an artificial benchmark suite (**EigenBench**) and a realistic benchmark suite (**STAMP**). There are other available TM benchmarks [52, 53, 54, 55] which are beyond the scope of the thesis.

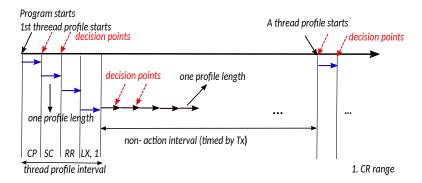

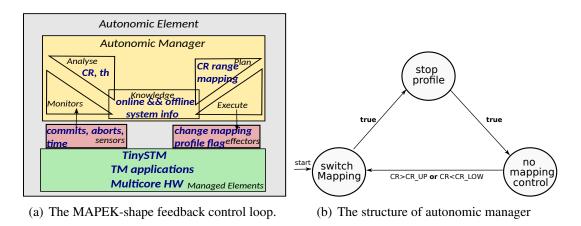

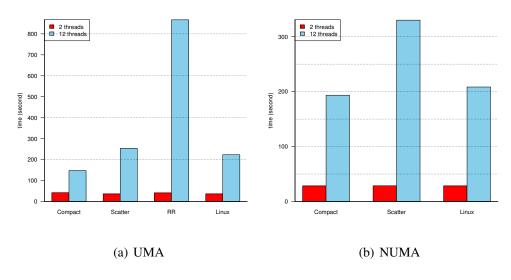

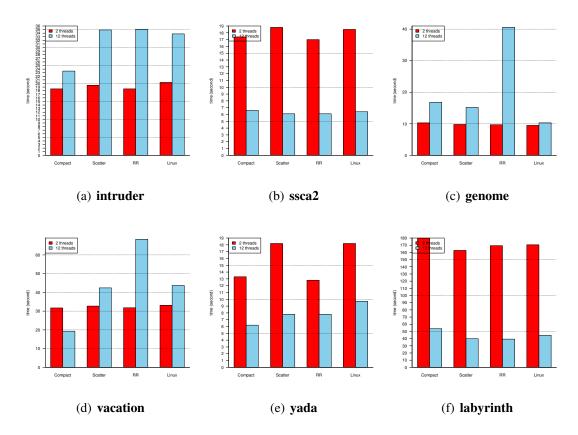

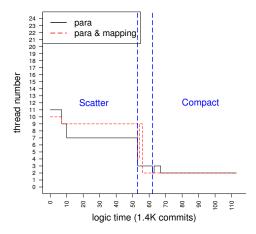

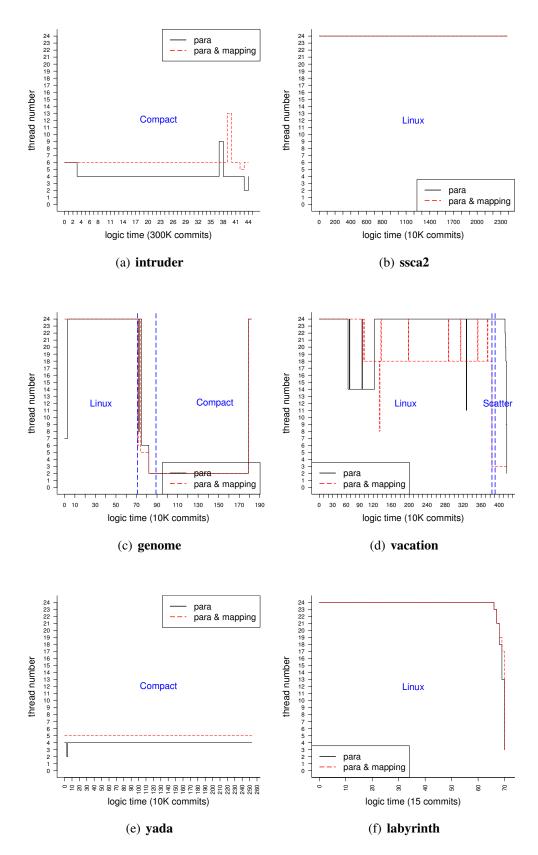

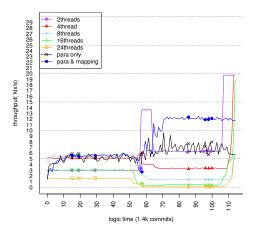

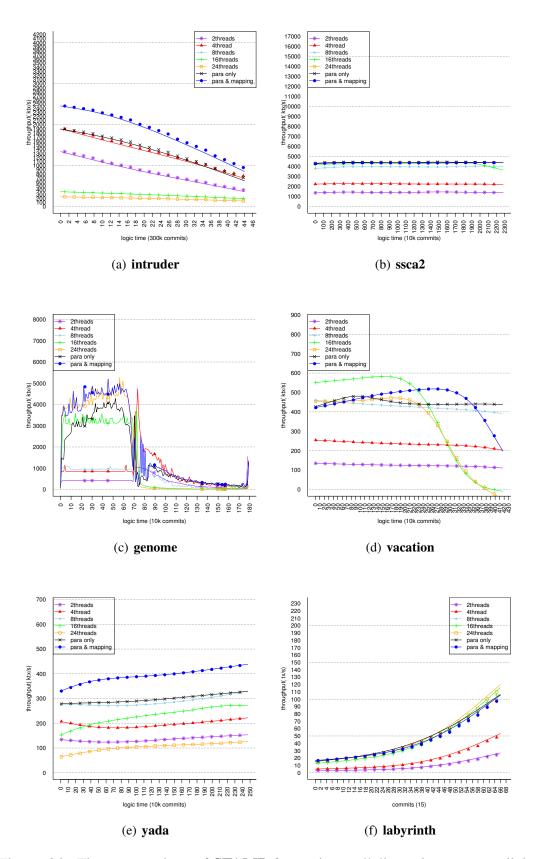

## 2.4.1 EigenBench