# **Energy-efficient Interfaces for Vibration Energy Harvesting**

#### Sijun Du

Supervisor: Prof. Ashwin A. Seshia

Advisor: Prof. Gehan A. J. Amaratunga

Department of Engineering University of Cambridge

This dissertation is submitted for the degree of Doctor of Philosophy

Queens' College

December 2017

To my wife, Peng Yi.

To my baba, Du Daozhong, and mama, Zhang Xinfeng.

#### **Declaration**

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements. This dissertation contains fewer than 65,000 words including appendices, bibliography, footnotes, tables and equations and has fewer than 150 figures.

Sijun Du December 2017

#### Acknowledgements

#### Sincere gratitude to

Prof. Ashwin Seshia for his supervision, mentoring, guidance, support and regular critical review of the research progress.; without whom, this research would have definitely undertaken many detours.

Prof. Gehan Amaratunga for his unreserved advice, support and constructive criticism.

Dr. Yu Jia for the continued support, help and fruitful discussions for novel ideas and experimental setup in research.

Prof. Sir. Mark Welland for his reference for PhD funding application.

Dr. Chun Zhao for helping construct PCB circuit designs and experiments.

Dr. Cuong Do for his help on CMOS chip fabrications.

Mr. Shao-Tuan Chen for vacuum-chamber MEMS chip tests and discussions.

Dr. Emmanuelle Arroyo for MEMS temperature tests and communicating with project cooperators.

#### **Abstract**

Ultra low power wireless sensors and sensor systems are of increasing interest in a variety of applications ranging from structural health monitoring to industrial process control. Electrochemical batteries have thus far remained the primary energy sources for such systems despite the finite associated lifetimes imposed due to limitations associated with energy density. However, certain applications (such as implantable biomedical electronic devices and tire pressure sensors) require the operation of sensors and sensor systems over significant periods of time, where battery usage may be impractical and add cost due to the requirement for periodic re-charging and/or replacement. In order to address this challenge and extend the operational lifetime of wireless sensors, there has been an emerging research interest on harvesting ambient vibration energy.

Vibration energy harvesting is a technology that generates electrical energy from ambient kinetic energy. Despite numerous research publications in this field over the past decade, low power density and variable ambient conditions remain as the key limitations of vibration energy harvesting. In terms of the piezoelectric transducers, the open-circuit voltage is usually low, which limits its power while extracted by a full-bridge rectifier. In terms of the interface circuits, most reported circuits are limited by the power efficiency, suitability to real-world vibration conditions and system volume due to large off-chip components required.

The research reported in this thesis is focused on increasing power output of piezoelectric transducers and power extraction efficiency of interface circuits. There are five main chapters describing two new design topologies of piezoelectric transducers and three novel active interface circuits implemented with CMOS technology. In order to improve the power output of a piezoelectric transducer, a series connection configuration scheme is proposed, which splits the electrode of a harvester into multiple equal regions connected in series to inherently increase the open-circuit voltage generated by the harvester. This topology passively increases the rectified power while using a full-bridge rectifier. While most of piezoelectric transducers are designed with piezoelectric layers fully covered by electrodes, this thesis proposes a new electrode design topology, which maximizes the raw AC output power of a piezoelectric harvester by finding an optimal electrode coverage.

In order to extract power from a piezoelectric harvester, three active interface circuits are proposed in this thesis. The first one improves the conventional SSHI (synchronized switch harvesting on inductor) by employing a startup circuitry to enable the system to start operating under much lower vibration excitation levels. The second one dynamically configures the connection of the two regions of a piezoelectric transducer to increase the operational range and output power under a variety of excitation levels. The third one is a novel SSH architecture which employs capacitors instead of inductors to perform synchronous voltage flip. This new architecture is named as SSHC (synchronized switch harvesting on capacitors) to distinguish from SSHI rectifiers and indicate its inductorless architecture.

# **Table of contents**

| Li | st of f | figures                                                               | X  |

|----|---------|-----------------------------------------------------------------------|----|

| Li | st of t | tables                                                                | XX |

| 1  | Intr    | oduction                                                              |    |

|    | 1.1     | Motivation and previous research                                      |    |

|    | 1.2     | Different energy harvesting solutions                                 | 3  |

|    | 1.3     | Objectives of the project                                             | 3  |

|    | 1.4     | Outline of the dissertation                                           | 3  |

| 2  | Bac     | kground on Piezoelectric Energy Harvesting Interfaces                 | 4  |

|    | 2.1     | Introduction                                                          | 4  |

|    | 2.2     | Equivalent circuit of a piezoelectric VEH                             | 6  |

|    | 2.3     | Raw AC power generated by a PT                                        | 8  |

|    | 2.4     | Full-bridge rectifier interface circuit                               | Ģ  |

|    | 2.5     | Parallel-SSHI interface                                               | 13 |

|    | 2.6     | Other circuits                                                        | 16 |

|    |         | 2.6.1 Existing issues and challenges                                  | 16 |

| 3  | A C     | onnection Configuration Scheme to Increase Operational Range and Out- | -  |

|    | put     | Power                                                                 | 19 |

|    | 3.1     | Introduction                                                          | 19 |

|    | 3.2     | Full-bridge rectifier                                                 | 20 |

|    | 3.3     | Proposed scheme                                                       | 2  |

|    | 3.4     | Modeling                                                              | 23 |

|    |         | 3.4.1 Monolithic model                                                | 24 |

|    |         | 3.4.2 N-stage series model                                            | 26 |

|    |         | 3.4.3 Performance comparison                                          | 29 |

|    | 3 5     | Experiments and discussions                                           | 30 |

**xii** Table of contents

|   | 3.6  | Concl    | usion                                                                | 35 |

|---|------|----------|----------------------------------------------------------------------|----|

| 4 | Elec | ctrode D | Design to Maximize Output Power                                      | 37 |

|   | 4.1  | Introd   | uction                                                               | 37 |

|   | 4.2  | Model    | ling of a plain cantilever                                           | 38 |

|   | 4.3  | Model    | ling of a structure with arbitrary strain distribution               | 43 |

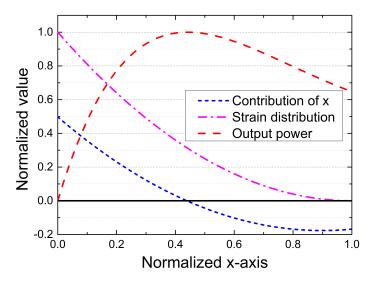

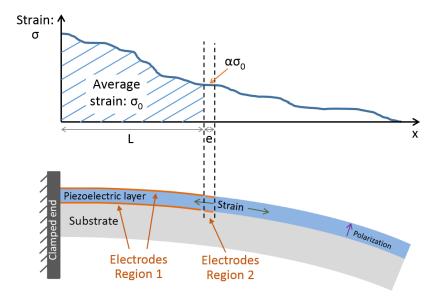

|   |      | 4.3.1    | Output power with electrode covering region 1                        | 44 |

|   |      | 4.3.2    | Output power with electrode covering regions 1+2:                    | 45 |

|   |      | 4.3.3    | Contribution analysis of additional electrode coverage in region 2 . | 46 |

|   | 4.4  | Experi   | imental Validation                                                   | 47 |

|   |      | 4.4.1    | MEMS plain cantilever                                                | 47 |

|   |      | 4.4.2    | MEMS double-clamped beam                                             | 50 |

|   |      | 4.4.3    | Discussion                                                           | 52 |

|   | 4.5  | Concl    | usion                                                                | 52 |

| 5 | An ] | Inducto  | orless Dynamically Configured Interface Circuit                      | 55 |

|   | 5.1  | Introd   | uction                                                               | 55 |

|   | 5.2  | Model    | ling of parallel and series configurations                           | 57 |

|   |      | 5.2.1    | Parallel model                                                       | 57 |

|   |      | 5.2.2    | Series model                                                         | 60 |

|   |      | 5.2.3    | Performance comparison and proposed scheme                           | 62 |

|   | 5.3  | Propos   | sed interface circuit                                                | 64 |

|   | 5.4  | Circui   | t implementations                                                    | 65 |

|   |      | 5.4.1    | Parallel-series connection switching block                           | 66 |

|   |      | 5.4.2    | Calibration block                                                    | 69 |

|   |      | 5.4.3    | Power management block                                               | 71 |

|   | 5.5  | Measu    | rement results and discussions                                       | 75 |

|   | 5.6  | Concl    | usion                                                                | 85 |

| 6 | An ] | Enhanc   | ed SSHI Interface Circuit with Auto-Startup Circuitry                | 87 |

|   | 6.1  | Introd   | uction                                                               | 87 |

|   | 6.2  | Model    | ling                                                                 | 87 |

|   | 6.3  | Propos   | sed architecture                                                     | 91 |

|   | 6.4  | Circui   | t implementation of the proposed SSHI circuit                        | 93 |

|   |      | 6.4.1    | Conventional SSHI circuit                                            | 93 |

|   |      | 6.4.2    | SSHI working monitoring block                                        | 96 |

|   |      | 6.4.3    | Excitation evaluation block                                          | 97 |

| Table of contents | xiii |

|-------------------|------|

|-------------------|------|

|     |             | 6.4.4 Pre-charging block                                              | 10 |

|-----|-------------|-----------------------------------------------------------------------|----|

|     | 6.5         | Simulation results                                                    |    |

|     | 6.6         | Measurement results and discussion                                    |    |

|     | 6.7         | Conclusion                                                            |    |

| 7   | An I        | nductorless Bias-flip Rectification Circuit                           | 1  |

|     | 7.1         | Introduction                                                          | 1  |

|     | 7.2         | Inductor-based SSHI interface                                         | 1  |

|     | 7.3         | Proposed inductor-less SSHC interface circuit                         | 1  |

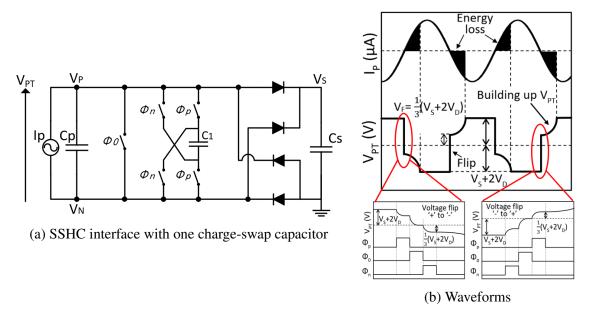

|     |             | 7.3.1 SSHC with one capacitor                                         | 1  |

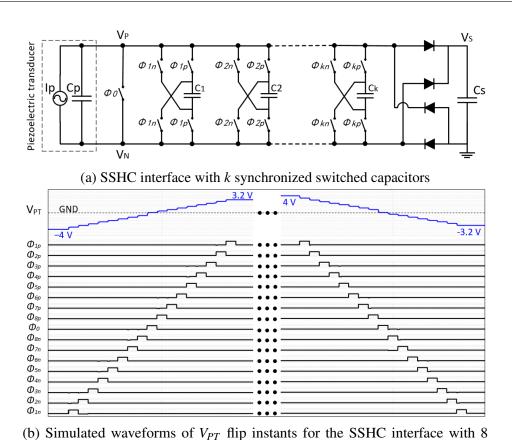

|     |             | 7.3.2 SSHC with multiple capacitors                                   | 1  |

|     |             | 7.3.3 Performance analysis                                            | 1  |

|     | 7.4         | Circuit implementation of the proposed SSHC interface                 | 1  |

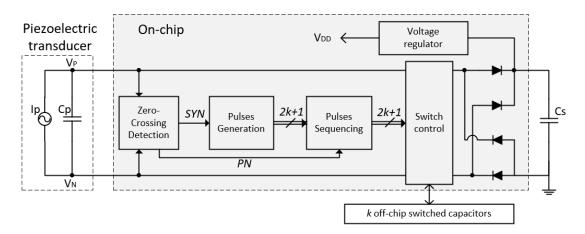

|     |             | 7.4.1 System architecture                                             | 1  |

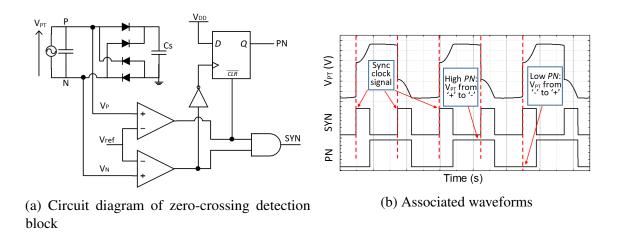

|     |             | 7.4.2 Zero-crossing detection                                         | 1  |

|     |             | 7.4.3 Pulse generation                                                | 1  |

|     |             | 7.4.4 Pulse sequencing                                                | 1  |

|     |             | 7.4.5 Switch control and voltage regulation blocks                    | 1  |

|     | 7.5         | Measurement results                                                   | 12 |

|     | 7.6         | Conclusion                                                            | 12 |

| 8   | Con         | clusions and Future Work                                              | 12 |

|     | 8.1         | Conclusion of the work                                                | 12 |

|     | 8.2         | Suggestions for future work                                           | 1. |

|     |             | 8.2.1 Fully integrated system                                         | 13 |

|     |             | 8.2.2 System cold startup                                             | 1. |

| Ref | feren       | ces                                                                   | 1. |

| Ap  | pend        | ix A Characteristics of piezoelectric transducers                     | 1: |

|     | <b>A.</b> 1 | Modeling of a resonant system                                         | 1: |

|     | A.2         | Piezoelectric materials                                               | 1: |

| Ap  | pend        | ix B MEMS piezoelectric device fabrication process                    | 1  |

| Ap  | pend        | ix C Real-world assessment of the self-startup SSHI interface circuit | 10 |

|     | C.1         | Introduction                                                          | 10 |

|     | C.2         | Measurement results                                                   | 16 |

| <b>xiv</b> Table of co          | ntents |

|---------------------------------|--------|

| C.3 Conclusion                  | . 168  |

| Appendix D List of publications | 169    |

# List of figures

| 2.1 | Schematic of energy conversion in vibration energy transducers                           | 6  |

|-----|------------------------------------------------------------------------------------------|----|

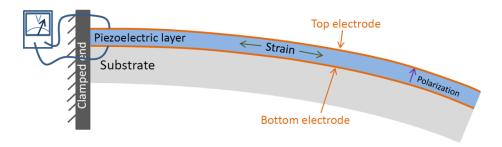

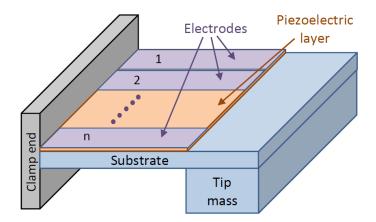

| 2.2 | Cantilevered piezoelectric harvester                                                     | 7  |

| 2.3 | Equivalent circuit of a piezoelectric harvester                                          | 7  |

| 2.4 | Load resistor connected to a monolithic PT                                               | 8  |

| 2.5 | Full-bridge rectifier interface circuit for the piezoelectric harvester and the          |    |

|     | associated waveforms                                                                     | 11 |

| 2.6 | The peak-to-peak open-circuit voltage $V_{pp(open)}$                                     | 11 |

| 2.7 | SSHI interface for piezoelectric harvester and the associated waveforms                  | 13 |

| 2.8 | Simplified system architecture of an SSHI interface circuit                              | 14 |

| 2.9 | Circuit diagram of the switch-only interface circuit                                     | 16 |

| 3.1 | Splitting a monolithic PT into <i>n</i> regions                                          | 22 |

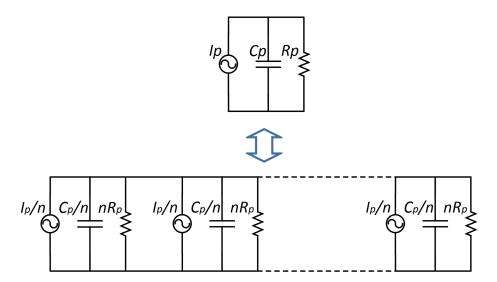

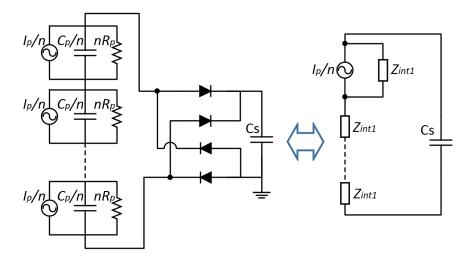

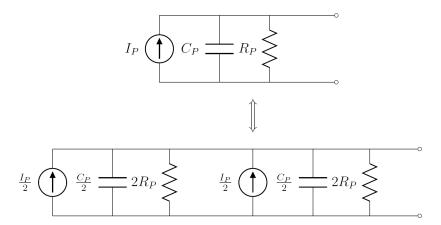

| 3.2 | Monolithic harvester (top) and <i>n</i> -region harvester connected in parallel (bottom) | 23 |

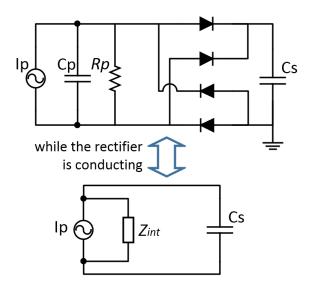

| 3.3 | Equivalent circuit while the full-bridge rectifier is conducting                         | 25 |

| 3.4 | Equivalent circuit for considering only one source in <i>n</i> -region series con-       |    |

|     | nected PTs while the rectifier is conducting                                             | 28 |

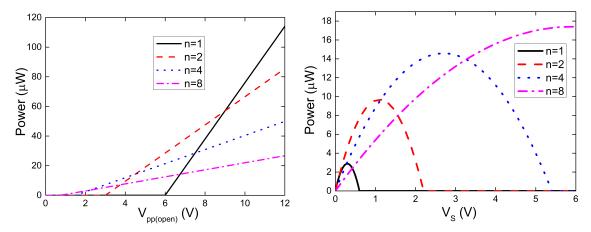

| 3.5 | Theoretical electrical power output of full-bridge rectifier for 1, 2, 4, and 8          |    |

|     | series stages                                                                            | 31 |

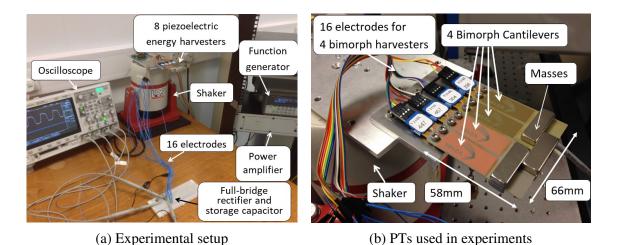

| 3.6 | Experimental setup                                                                       | 32 |

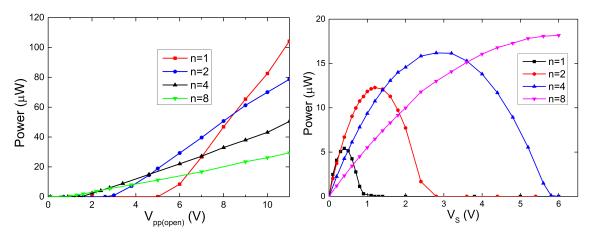

| 3.7 | Measured performance of the proposed scheme                                              | 33 |

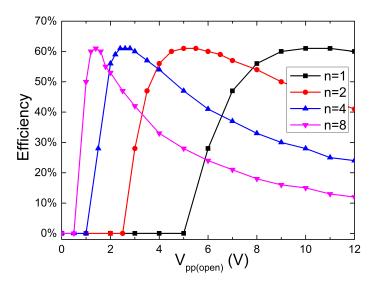

| 3.8 | Measured power efficiency while fixing $V_S = 2 V$ and varying excitation level          | 34 |

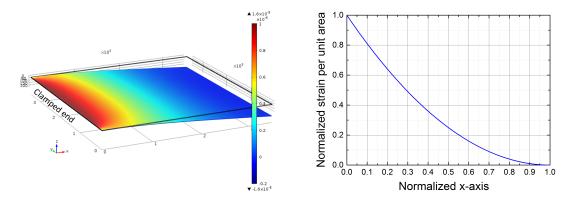

| 4.1 | COMSOL model of a plain cantilever shows the strain is high near the                     |    |

|     | clamped end and very low near the free end                                               | 38 |

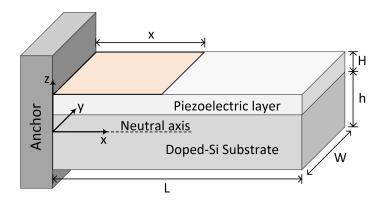

| 4.2 | Cantilevered piezoelectric harvester                                                     | 39 |

| 4.3 | Simulation results                                                                       | 43 |

**xvi** List of figures

| 4.4  | A piezoelectric vibration energy harvester with arbitrary decreasing strain along axis $x$ ( $L$ is the length of the electrode region 1 and $e$ is the length of an extract electrode region 2, where $e \ll L$ . the average strain in the region 1 is noted as $\sigma_0$ , $\alpha$ is a factor between 0 and 1 and $\alpha\sigma_0$ is the strain for the |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | small region 2)                                                                                                                                                                                                                                                                                                                                                | 44 |

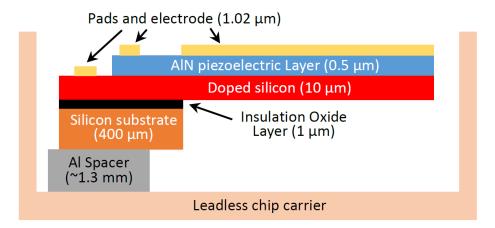

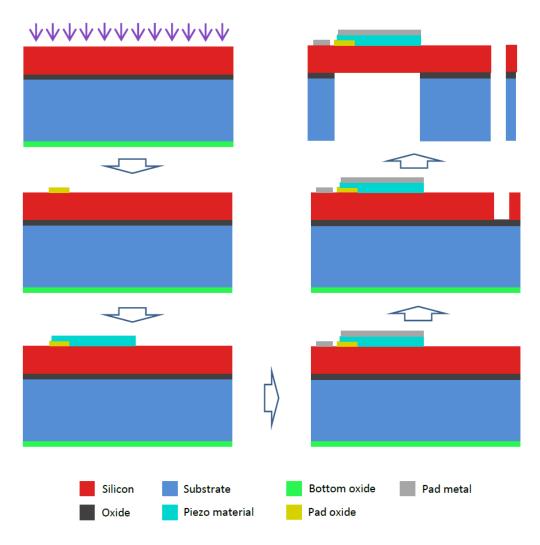

| 4.5  | MEMS device fabrication process                                                                                                                                                                                                                                                                                                                                | 47 |

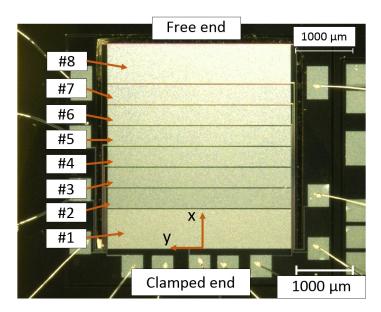

| 4.6  | Microscopic view of a MEMS plain cantilevered PVEH                                                                                                                                                                                                                                                                                                             | 48 |

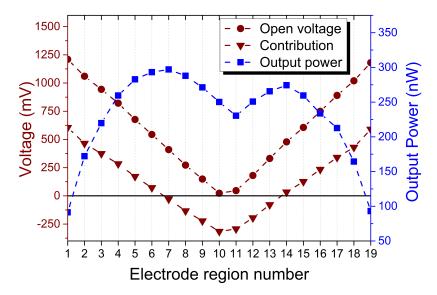

| 4.7  | Measured results for MEMS plain cantilevered PVEH                                                                                                                                                                                                                                                                                                              | 49 |

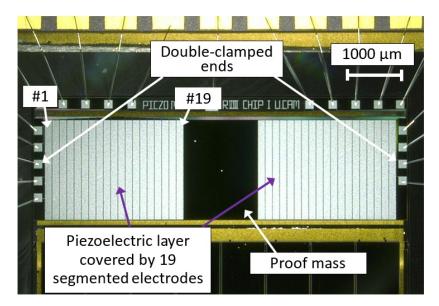

| 4.8  | Microscopic view of a MEMS double-clamped beam PVEH with a centered                                                                                                                                                                                                                                                                                            |    |

|      | proof mass                                                                                                                                                                                                                                                                                                                                                     | 50 |

| 4.9  | Measured results for MEMS double-clamped beam PVEH                                                                                                                                                                                                                                                                                                             | 52 |

| 5.1  | A monolithic PT (top) and two PTs connected in parallel (bottom)                                                                                                                                                                                                                                                                                               | 57 |

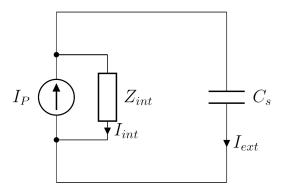

| 5.2  | Current flow in a piezoelectric generator                                                                                                                                                                                                                                                                                                                      | 58 |

| 5.3  | Current flow while charging $C_S$ - parallel model                                                                                                                                                                                                                                                                                                             | 59 |

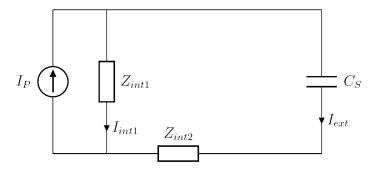

| 5.4  | Equivalent circuit for two PTs connected in series for charging $C_S$                                                                                                                                                                                                                                                                                          | 61 |

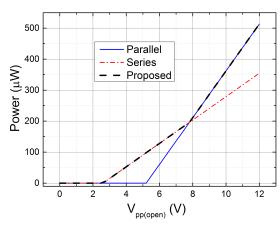

| 5.5  | Theoretical output power for parallel model, series model and proposed                                                                                                                                                                                                                                                                                         |    |

|      | model (diode voltage drop set as $V_D = 0.3 \mathrm{V}$ )                                                                                                                                                                                                                                                                                                      | 62 |

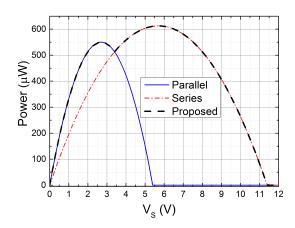

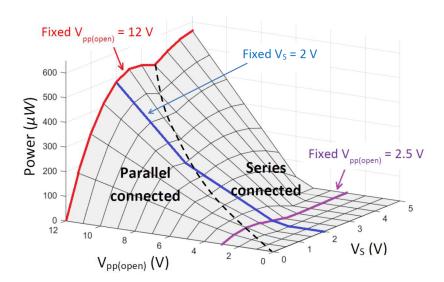

| 5.6  | 3-D surface plot of theoretical output power in function of $V_{pp(open)}$ and $V_S$ .                                                                                                                                                                                                                                                                         | 63 |

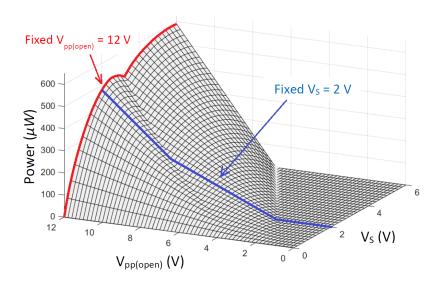

| 5.7  | Architecture of proposed interface circuit                                                                                                                                                                                                                                                                                                                     | 65 |

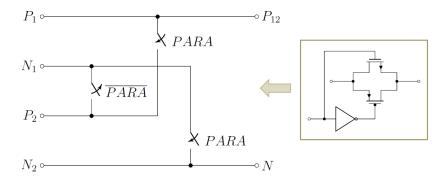

| 5.8  | Parallel-series connection switching circuitry with CMOS analogue switches.                                                                                                                                                                                                                                                                                    | 66 |

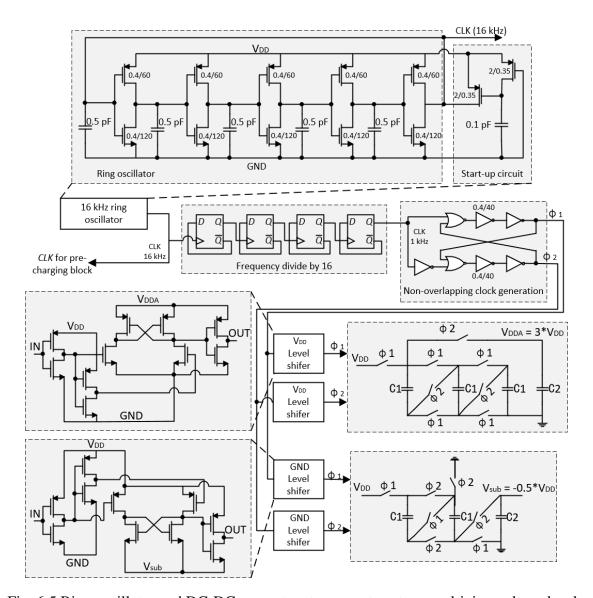

| 5.9  | Two-stage level-up shifter                                                                                                                                                                                                                                                                                                                                     | 66 |

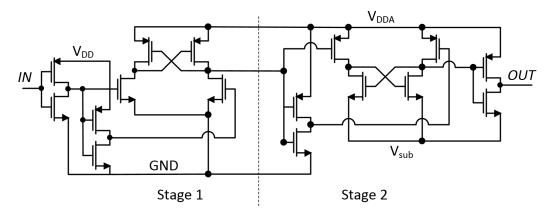

| 5.10 | Switched-capacitor (SC) converters used to generate gate overdriving voltage                                                                                                                                                                                                                                                                                   |    |

|      | levels: (a) $V_{DD} \rightarrow 3V_{DD}$ , (b) $V_{DD} \rightarrow -0.5V_{DD}$                                                                                                                                                                                                                                                                                 | 67 |

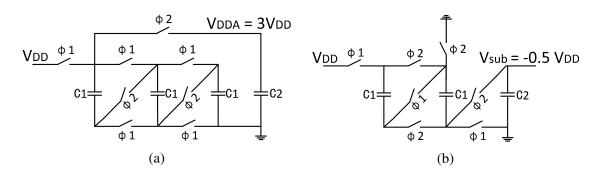

| 5.11 | Nano-watt power ring oscillator to provide digital clock for the SC converters                                                                                                                                                                                                                                                                                 |    |

|      | and power management block, including the start-up circuitry and the non-                                                                                                                                                                                                                                                                                      |    |

|      | overlapping signal generation block                                                                                                                                                                                                                                                                                                                            | 68 |

| 5.12 | Circuit diagram of the calibration block                                                                                                                                                                                                                                                                                                                       | 70 |

| 5.13 | Continuous time comparator to evaluate the input excitation level                                                                                                                                                                                                                                                                                              | 71 |

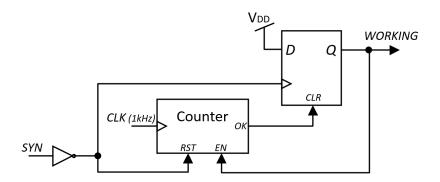

| 5.14 | Power management and parallel-series determining circuitry                                                                                                                                                                                                                                                                                                     | 72 |

|      | Simulation results of the proposed interface circuit                                                                                                                                                                                                                                                                                                           | 73 |

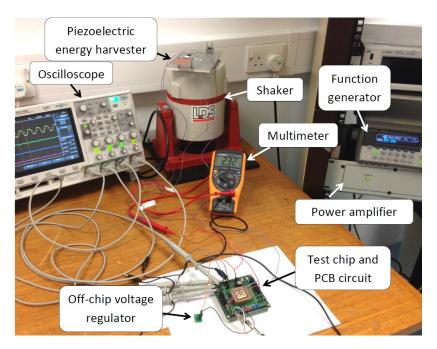

| 5.16 | Experimental setup                                                                                                                                                                                                                                                                                                                                             | 75 |

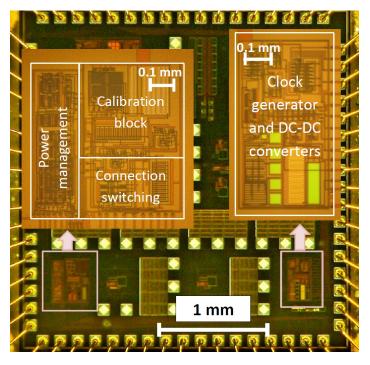

| 5.17 | Micrograph of the test chip fabricated in a 0.35 μm CMOS foundry process.                                                                                                                                                                                                                                                                                      |    |

|      | The overall die size is $2.8  \text{mm} \times 3.2  \text{mm}$ . The active area for the proposed                                                                                                                                                                                                                                                              |    |

|      | circuit is around 0.5 mm <sup>2</sup> excluding the pads and the remaining die area is                                                                                                                                                                                                                                                                         |    |

|      | occupied by circuits of other projects                                                                                                                                                                                                                                                                                                                         | 76 |

List of figures xvii

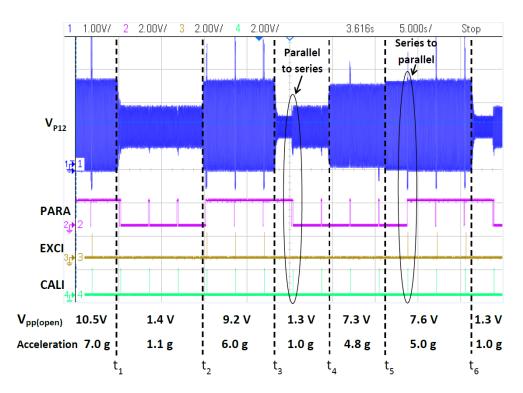

| 5.18 | Measured waveforms of signal $V_{P12}$ , $PARA$ , $EXCI$ and $CALI$ in a period of                       |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | 50 s                                                                                                     | 77  |

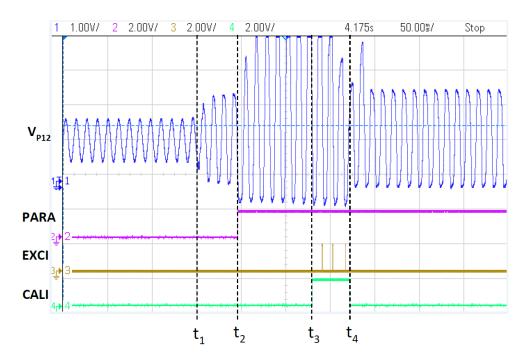

| 5.19 | Measured waveforms in 0.5 s while connection is being changed from series                                |     |

|      | to parallel                                                                                              | 79  |

| 5.20 | Output power comparison between theoretical and measured results as a                                    |     |

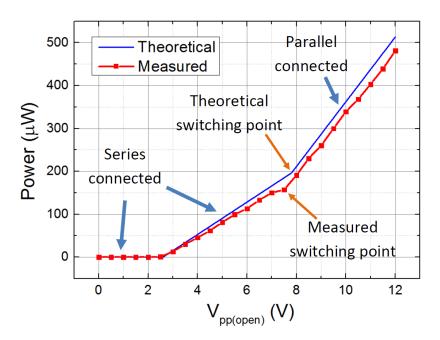

|      | function of excitation level with fixed $V_S = 2 \text{ V}$ (diode voltage drop $V_D = 0.3 \text{ V}$ ). | 80  |

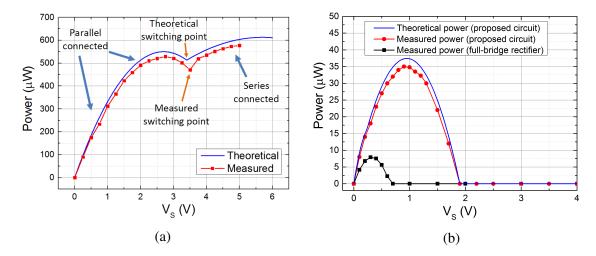

| 5.21 | Theoretical and measured output power in function $V_S$ using proposed circuit                           |     |

|      | and full-bridge rectifier under different excitation levels. (a) With a fixed                            |     |

|      | excitation level of $V_{pp(open)} = 12 \text{ V}$ (equivalent to acceleration level of 8.0 g);           |     |

|      | (b) $V_{pp(open)} = 2.5 \text{V}$ (equivalent to 1.8 g). Diode voltage drop $V_D = 0.3 \text{V}$ .       | 81  |

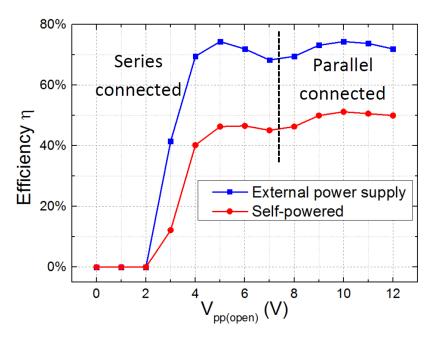

| 5.22 | 3-D surface plot of measured output power in function of $V_{pp(open)}$ and $V_S$ .                      | 82  |

| 5.23 | Measured power efficiency of the proposed interface circuit while it is exter-                           |     |

|      | nally powered and self-powered ( $V_S = 2 V$ )                                                           | 83  |

| 6.1  | Associated waveforms of SSHI interface while the circuit is operating prop-                              |     |

|      | erly and not operating.                                                                                  | 88  |

| 6.2  | Simulation waveforms showing the SSHI circuit fails to restart                                           | 90  |

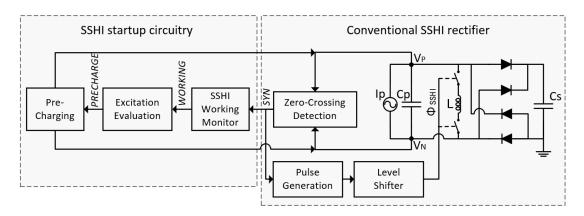

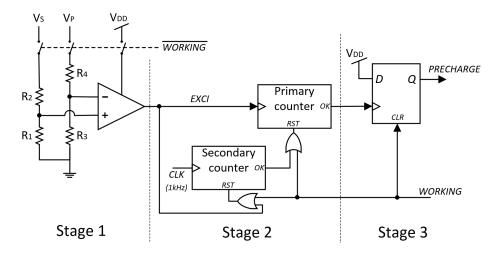

| 6.3  | System architecture of the proposed SSHI interface with self-startup circuitry.                          | 91  |

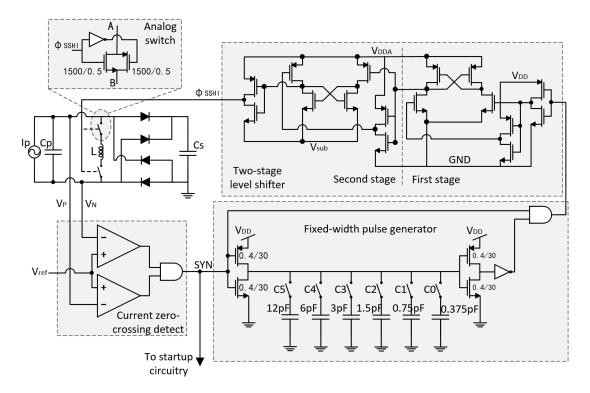

| 6.4  | Conventional SSHI rectifier.                                                                             | 92  |

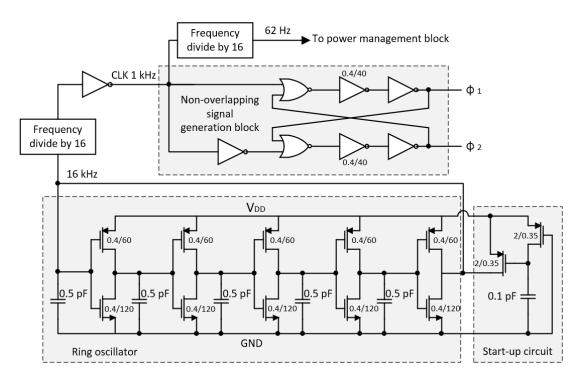

| 6.5  | Ring oscillator and DC-DC converters to generate gate over-driving voltage                               |     |

|      | levels                                                                                                   | 94  |

| 6.6  | Circuit diagram of SSHI working monitoring block                                                         | 96  |

| 6.7  | Circuit diagram of excitation evaluation block                                                           | 97  |

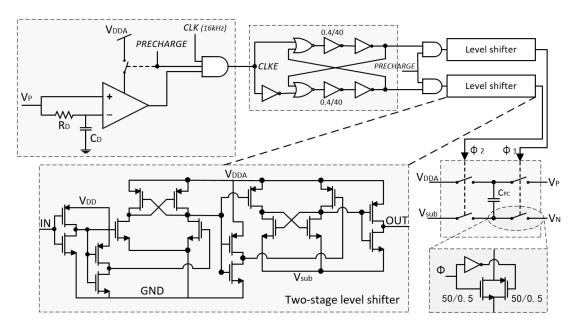

| 6.8  | Circuit diagram of the pre-charging block with on-chip $R_D = 7.5 \mathrm{M}\Omega$ and                  |     |

|      | $C_D = 30 \mathrm{pF}.$                                                                                  | 99  |

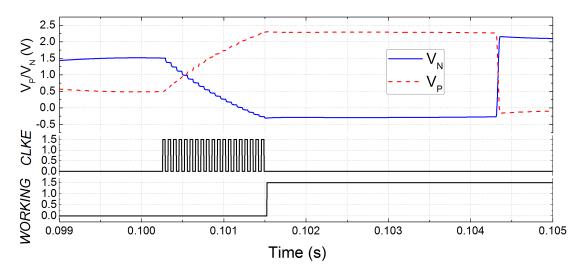

| 6.9  | Simulation waveforms of pre-charging block                                                               | 101 |

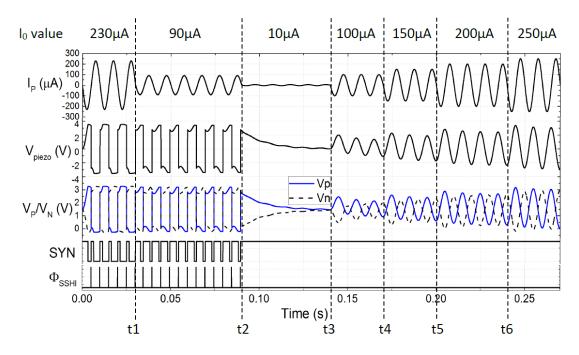

| 6.10 | Chip-level simulation waveforms                                                                          | 102 |

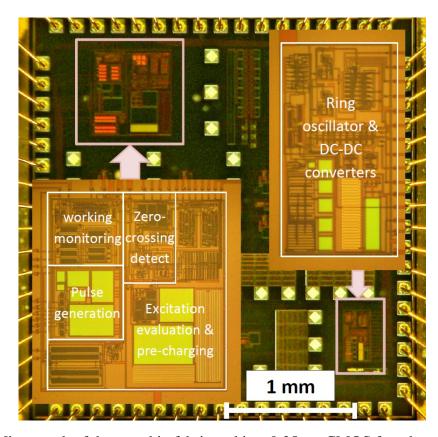

| 6.11 | Micrograph of the test chip fabricated in a 0.35 μm CMOS foundry process.                                |     |

|      | The overall die size is $2.8\text{mm} \times 3.2\text{mm}$ . The active area for the proposed            |     |

|      | circuit is around $0.6 \mathrm{mm}^2$                                                                    | 103 |

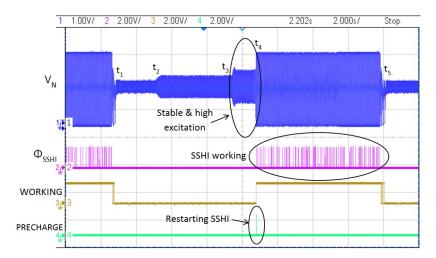

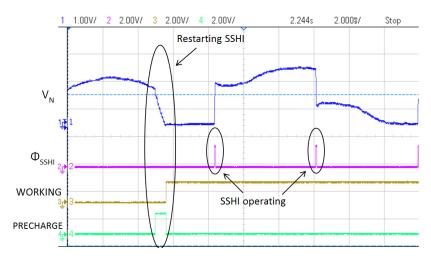

| 6.12 | Measured waveforms of signal $V_N$ , $\phi_{SSHI}$ , $WORKING$ and $PRECHARGE$                           |     |

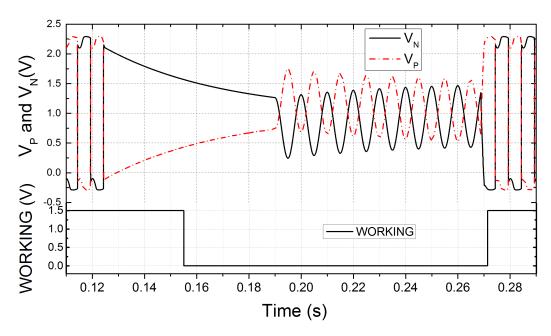

|      | in a period of 20 s                                                                                      | 105 |

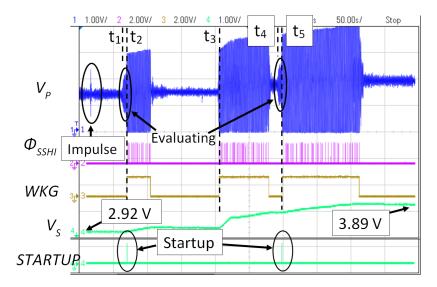

| 6.13 | Measured waveforms in a short period of time while restarting the SSHI circuit.                          | 106 |

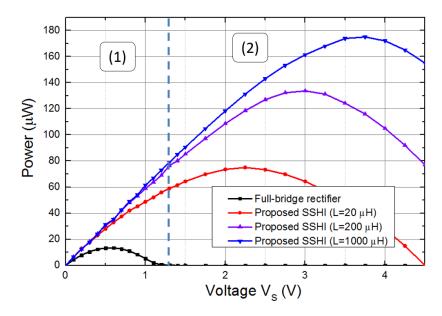

| 6.14 | Measured electrical power output of full-bridge rectifier and the proposed                               |     |

|      | SSHI rectifier with off-chip diodes ( $V_D = 0.2 \mathrm{V}$ ), where the horizontal axis $V_S$          |     |

|      | represents the voltage across the storage capacitor $C_S$ and $V_{pp(open)} = 2.8 \mathrm{V}$ .          | 106 |

xviii List of figures

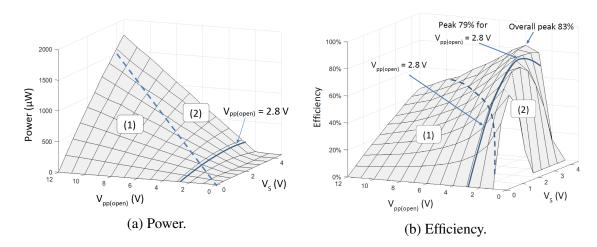

| 6.15 | 3-D surface plot of measured output electrical power and efficiency in function of $V_{pp(open)}$ and $V_S$ while the inductor is chosen at $L=1\mathrm{mH}$ (with external stable 1.5 V power supply and the conversion efficiency of voltage regulator is not considered) | 107 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

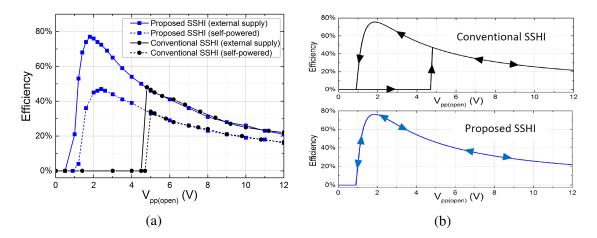

| 6.16 | (a) Measured power efficiency for the proposed SSHI with startup circuitry and the conventional SSHI without startup circuitry while the circuit is                                                                                                                         |     |

|      | externally powered and self-powered using an off-chip voltage regulator. (b) Efficiency variation while excitation level is swept in two directions                                                                                                                         | 108 |

| 7.1  | SSHI interface circuit and the associated waveforms                                                                                                                                                                                                                         | 112 |

| 7.2  | Proposed SSHC interface circuit and the associated waveforms                                                                                                                                                                                                                | 113 |

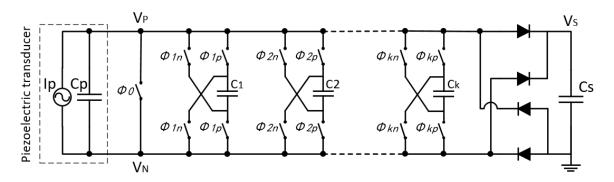

| 7.3  | Proposed SSHC interface circuit with <i>k</i> synchronized switched capacitors .                                                                                                                                                                                            | 114 |

| 7.4  | System architecture of the proposed SSHC interface circuit                                                                                                                                                                                                                  | 118 |

| 7.5  | Zero-crossing detection block                                                                                                                                                                                                                                               | 119 |

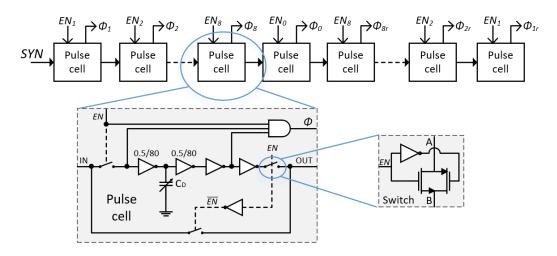

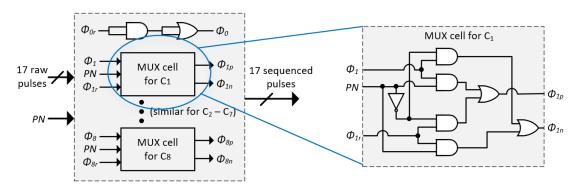

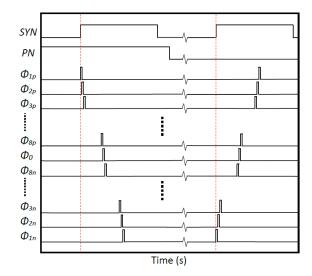

| 7.6  | Circuit diagram of the pulse generation block                                                                                                                                                                                                                               | 120 |

| 7.7  | Circuit diagram of the pulse sequencing block                                                                                                                                                                                                                               | 120 |

| 7.8  | Associated waveforms of the pulse sequencing block                                                                                                                                                                                                                          | 121 |

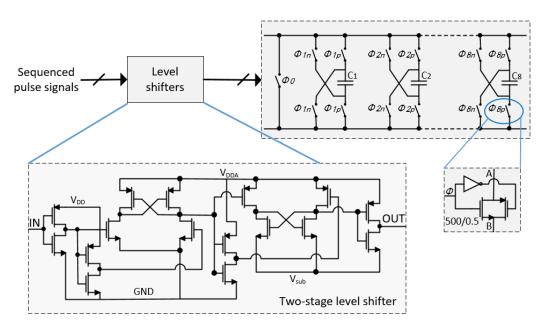

| 7.9  | Circuit diagram of the switch control block                                                                                                                                                                                                                                 | 122 |

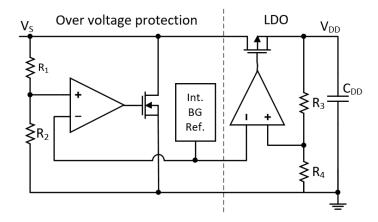

| 7.10 | Circuit diagram of the voltage regulator and over-voltage protection                                                                                                                                                                                                        | 122 |

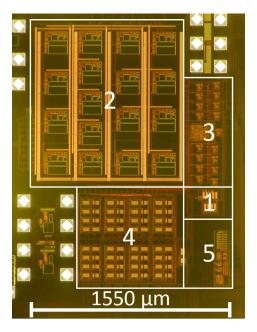

| 7.11 | Micrograph of the test chip fabricated in a $0.35\mu m$ CMOS foundry process.                                                                                                                                                                                               |     |

|      | The active area for the proposed circuit is 2.9 mm <sup>2</sup> . (1. zero-crossing, 2.                                                                                                                                                                                     |     |

|      | pulse generation, 3. pulse sequencing and level shifters, 4. switch control, 5.                                                                                                                                                                                             |     |

|      | OVP and voltage regulator)                                                                                                                                                                                                                                                  | 123 |

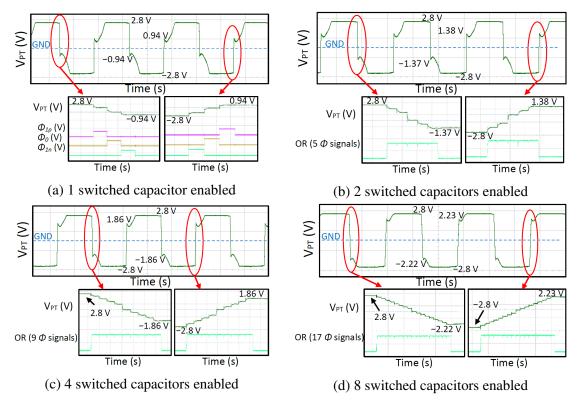

| 7.12 | Measured transient waveforms of $V_{PT}$ and switch signals (some switch                                                                                                                                                                                                    |     |

|      | signals are ORed for display due to the limited number of oscilloscope                                                                                                                                                                                                      |     |

|      | channels)                                                                                                                                                                                                                                                                   | 125 |

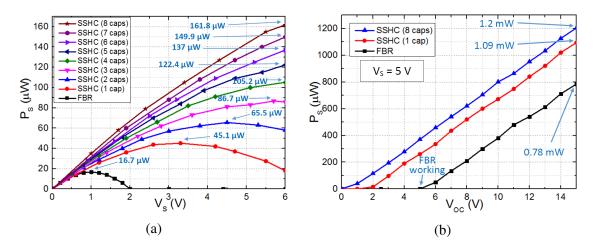

| 7.13 | Measured electrical output power of a FBR and the proposed SSHC interface                                                                                                                                                                                                   |     |

|      | circuit with up to 8 switched capacitors. (a) Output power in a range of $V_S$                                                                                                                                                                                              |     |

|      | with a fixed $V_{OC} = 2.5 \text{ V}$ (equivalent to an acceleration level 1.2 g). (b) Output                                                                                                                                                                               |     |

|      | power measured over a wide range of excitation levels (up to $V_{OC} = 15 \mathrm{V}$ ,                                                                                                                                                                                     |     |

|      | equivalent to 7.5 g) with a fixed $V_S = 5 \text{ V} \dots \dots \dots \dots \dots$                                                                                                                                                                                         | 126 |

| 8.1  | SSHC interface with $k$ synchronized switched capacitors                                                                                                                                                                                                                    | 130 |

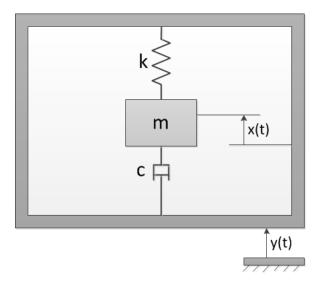

| A.1  | Equivalent spring-mass-damping system of an inertial resonator                                                                                                                                                                                                              | 154 |

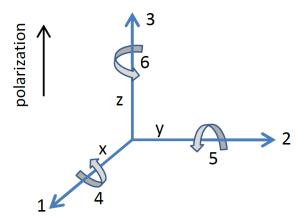

| A.2  | Directions of forces affecting a piezoelectric element                                                                                                                                                                                                                      |     |

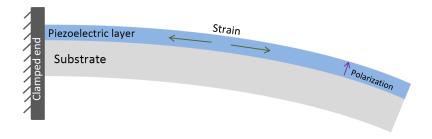

| A.3  | Strain in a vibrating unimorph piezoelectric cantilever                                                                                                                                                                                                                     |     |

| Γ ! - 4 - C C   | •   |

|-----------------|-----|

| List of figures | XIX |

|                 |     |

| B.1 | Micromachining process flow                                                 | 160 |

|-----|-----------------------------------------------------------------------------|-----|

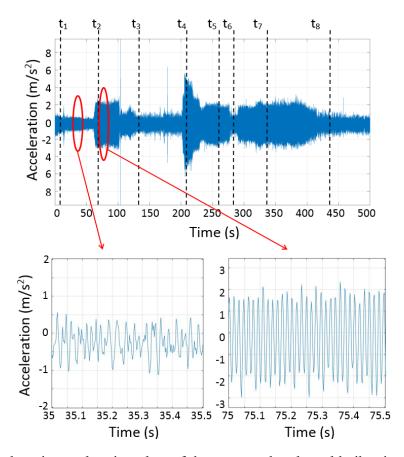

| C.1 | Time-domain acceleration plots of the measured real-world vibration data of |     |

|     | length 500 s collected from a tram in Birmingham, UK                        | 164 |

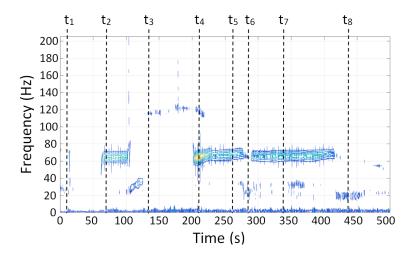

| C.2 | STFT (Short-time Fourier Transform) plot of the vibration data              | 165 |

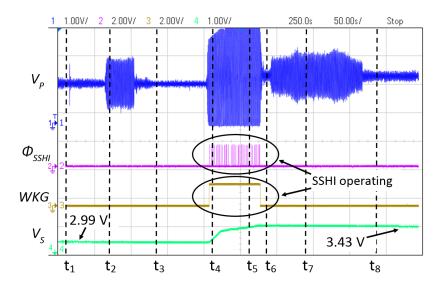

| C.3 | Waveforms of the conventional SSHI rectifier                                | 166 |

| C.4 | Waveforms of the proposed SSHI rectifier with startup circuit               | 167 |

## List of tables

| 1.1 | The output power comparison of different energy harvesting solutions                                                                              | 2   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Simulation results (symbol '-' means 'not working')                                                                                               | 30  |

| 3.2 | Performance comparison with reported active rectifiers                                                                                            | 35  |

| 4.1 | Measured open-circuit voltage and output power contribution for each region of the MEMS cantilever PVEH (frequency: 1208 Hz, acceleration: 0.5 g) | 49  |

| 4.2 | Measured open-circuit voltage and output power contribution for each re-                                                                          |     |

|     | gion of the MEMS clamped-clamped beam PVEH (frequency: 1430 Hz,                                                                                   |     |

|     | acceleration: 0.5 g)                                                                                                                              | 51  |

| 5.1 | Breakdown of the chip power loss and other power loss sources with simu-                                                                          |     |

|     | lated and measured results                                                                                                                        | 77  |

| 5.2 | Performance comparison with reported interface circuits                                                                                           | 84  |

| 6.1 | Breakdown of the chip power consumption                                                                                                           | 104 |

| 7.1 | Performance comparison between SSHI and SSHC                                                                                                      | 117 |

| 7.2 | Breakdown of the chip power consumption                                                                                                           | 124 |

| 7.3 | Performance comparison with state-of-the-art interface circuits                                                                                   | 127 |

| Δ 1 | Material properties of most common piezoelectric materials                                                                                        | 157 |

**xxii** List of tables

#### **Abbreviations and Acronyms**

MEMS Microelectromechanical systems

CMOS Complementary metal-oxide-semiconductor

IC Integrated circuit

VEH Vibration energy harvesting

PVEH Piezoelectric vibration energy harvester

PT Piezoelectric transducer

PH Piezoelectric harvester

FBR Full-bridge rectifier

SSHI Synchronized switch harvesting on inductor SSHC Synchronized switch harvesting on capacitors

SSD Synchronized switch damping

SECE Synchronous electrical charge extraction

MPP Maximum power point

MPPT Maximum power point tracking

AC Alternative current

DC Direct current

MSB Most significant bit

LSB Least significant bit

WSN Wireless sensor network

PZT Lead zirconate titanate

ZnO Zinc oxide

AlN Aluminum nitride

STFT Short-time Fourier transform

SOI Silicon on insulator

### Chapter 1

#### Introduction

#### 1.1 Motivation and previous research

The very significant advances in microelectronics engineering in the last decades have led to the development of ultra low power wireless sensors and sensor systems [1–4]. These sensor systems are of increasing interest in a variety of applications ranging from structural health monitoring to industrial process control [5, 6]. Compared to wired methodologies, wireless devices provide many advantages, such as flexibility and ease of placing the sensors in some locations that are not accessible by the wired counterparts. The systems can also be ameliorated without considering issues such as wiring and allowance for cabling.

Design consideration of ultra low power plays an important part in the design flow of electronic devices [7]. By minimizing the power consumption, researchers and engineers aim to extend the battery lifetime and to avoid replacing or recharging batteries too frequently. Electrochemical batteries have thus far remained the primary energy sources for such systems despite the finite associated lifetimes imposed due to limitations associated with energy density. However, in certain sensing contexts requiring the operation of sensors and sensor systems over a significant period of time [8, 9], including implantable biomedical electronic devices [10] and tire pressure sensors [11], battery usage may be both impractical and add extra cost due to the requirement for periodic re-charging and/or replacement [12]. In order to address this challenge and extend the operational lifetime of wireless sensors, there has been an emerging research interest to harvest energy from environmental sources [13–23].

For powering wireless nodes, vibration energy harvesters (VEH) are designed by groups in [24–44] through harvesting energy from kinetic vibration sources. Similar VEHs were also implemented in a tire pressure sensing [45]. In [46], a hybrid energy harvesting system of harvesting indoor ambient light and thermal energy is developed to power wireless sensor nodes, where a peak power of around  $700\,\mu\text{W}$  was achieved. In terms of structural health

2 Introduction

Table 1.1 The output power comparison of different energy harvesting solutions

| Solution                               | Power density in outdoor implementations                                                                                 | Power density in indoor implementation                                                                          |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Solar energy harvesting                | $15 \mathrm{mW  cm^{-2}}  [56]$                                                                                          | $100 \mu\mathrm{W}\mathrm{cm}^{-2}$ (at $10 \mathrm{W}\mathrm{cm}^{-2}$ light density [57])                     |

| Thermal energy harvesting              | 100 μW cm <sup>-2</sup> at 5 °C gradient,<br>3.5 mW cm <sup>-2</sup> at 30 °C gradient<br>[57]                           | 100 μW cm <sup>-2</sup> at 5 °C gradient,<br>3.5 mW cm <sup>-2</sup> at 30 °C gradient<br>[57]                  |

| Vibration energy harvesting            | 500 μW cm <sup>-2</sup> (piezoelectric method) [7, 58, 59]                                                               | 500 μW cm <sup>-2</sup> (piezoelectric method) [7]                                                              |

| RF energy harvesting                   | 15 mW cm <sup>-2</sup> (with a transmitted<br>power of 2-3 W at a frequency of<br>906 MHz at a distance of 30 cm<br>[59] | 15 mW cm <sup>-2</sup> (with a transmitted power of 2-3 W at a frequency of 906 MHz at a distance of 30 cm [59] |

| Air flow energy harvesting             | $3.5 \mathrm{mW  cm^{-2}}$ (wind speed of $8.4 \mathrm{m  s^{-1}}$ ) [60]                                                | $3.5 \mu\text{W cm}^{-2}$ (air flow speed is less than $1 \text{m s}^{-1}$ ) [60]                               |

| Acoustic energy harvesting             | $960 \mathrm{nW}\mathrm{cm}^{-2}$ (acoustic noise of $100 \mathrm{dB}$ ) [56]                                            | $960 \mathrm{nWcm^{-2}}$ (acoustic noise of $100 \mathrm{dB}$ ) [56]                                            |

| Electromagnetic wave energy harvesting | $0.26\mu Wcm^{-2}$ (from an electric field of $1Vm^{-1}$ ) [61]                                                          | $0.26\mu Wcm^{-2}$ (from an electric field of 1 V m <sup>-1</sup> ) [61]                                        |

| Biochemical energy harvesting          | $0.1-1 \text{ mW cm}^{-2} [62]$                                                                                          | 0.1-1 mW cm <sup>-2</sup> [62]                                                                                  |

monitoring, a self-powered pacemaker is proposed in [47] as an example of applying vibration energy harvesting technology in biomedical devices. The group of Canan Dagdeviren also tries to harvest energy from both heart and lung movements [48]. In [49], a hybrid VEH employing linearity and nonlinearity is used for powering pacemakers. Similar researches of VEH on biomedical applications are shown in [50–53]. Wind energy harvesting for structural health monitoring has also become more and more popular [54]. An approach of powering implementable biosensors by harvesting heat flow in [55] also proves the great research potential of environmental energy harvesting technology.

#### 1.2 Different energy harvesting solutions

Small energy harvesters are of increasing interest along with the development of ultra low power electronics and wireless sensor networks (WSN). Many different kinds of energy harvesters have been proposed over the past decade [63–68]. Table 1.1 shows the power densities (harvested power per unit active area) for different energy harvesting solutions.

The solar and air flow energy harvesting systems give impressive power densities in outdoor implementation but the harvested power decreases dramatically while they are implemented indoors or when the weather condition is unsuitable. Because the performance of these two solutions is greatly dependent on the weather condition and an indoor environment cannot provide enough sunlight and wind speed to make the systems work at their optimal performance. RF energy harvester provides a high power density up to 15 mW cm<sup>-2</sup> in indoor environments. However, a high-power drive of about 2-3 W at a high frequency is needed as the energy source and the transmission distance is limited to tens of centimeters. These limitations make the RF energy harvesters unsuitable for powering WSN but it facilitates remote battery recharging compared to conventional wired charging.

#### 1.3 Objectives of the project

Among all vibration energy harvesting methods, piezoelectric vibration energy harvesting (PVEH) is widely employed due to its high power density, scalability and compatibility with conventional integrated circuit technologies. This project aims to improve the PVEH systems in two directions: output power and system miniaturization. In order to increase output power, piezoelectric transducers (PT) can be improved to generate higher raw AC power and rectification circuits can be improved to increase the energy extraction efficiency. The improvements on PTs are to propose series-connected electrodes and electrode coverage optimization and the work on interface circuits is to improve the existing SSHI rectifier and to propose new system architectures. Since SSHI rectifiers employ large inductors to achieve high energy efficiency, the volume of inductors can be dominant for miniaturized energy harvesting systems. Hence, removing the inductor by achieving comparable or higher performance is another focus of this project.

#### 1.4 Outline of the dissertation

In general, this dissertation is focused on energy efficient interfaces for piezoelectric vibration energy harvesting (PVEH). In the second chapter, the background on piezoelectric energy har-

4 Introduction

vesting interfaces is introduced, where state-of-the-art interface circuits and the performance are analyzed and compared. The third chapter proposes a novel connection configuration scheme, which splits the electrode of a piezoelectric transducer (PT) into several regions connected in series and this scheme is found to be able to improve the rectified power of a PT by several times without introducing additional active circuit. In the fourth chapter, the output power of a PT is analyzed by studying the electrode coverage and the results in order to maximize the output power. The fifth chapter presents a new connection configuration interface circuit which dynamically configures the connection of two PTs to increase the rectified power. In the sixth chapter, a new SSHI rectifier is proposed, which can be restarted by an additional startup circuit under low excitation levels; hence, the energy harvesting system can operate over a large excitation range. This circuit has also been experimentally evaluated using real-world vibration data and the results are shown in Appendix B. In the seventh chapter, a novel inductorless bias-flip rectifier is proposed, which employs capacitors to synchronously flip the voltage across the PT instead of using inductors as SSHI circuits. A summary of the contributions of this thesis and a discussion of future work are provided in the last chapter.

### Chapter 2

# **Background on Piezoelectric Energy Harvesting Interfaces**

#### 2.1 Introduction

Vibration energy harvesting (VEH) has recently drawn much interest on harvesting environmental kinetic energy [69–76]. As noted in table 1.1, the output power of a vibration energy harvester is often acceptable for powering ultra-low-power wireless sensors [7, 77, 45, 55] and biomedical sensors [78, 79] under the right environmental conditions. Furthermore, VEHs can be fabricated at the MEMS-scale which enables wireless sensors to be implemented in applications where macro-scale energy harvesters cannot be employed [80].

A vibration energy harvester (VEH) is to convert kinetic vibrational energy in form of mechanical movement into electric energy [81–85]. This kind of harvester is often used in an environment with steady or frequent vibration of a specific frequency range [86–92], for example, the vibration caused by passing vehicles, engines, human gait [93–96] or heart beats [48–50]. In recent years, there has been a growing interest in VEH for realizing a decentralized on-board power solution [97–103].

In order to harvest vibration energy from motion, environmental kinetic displacement needs to be converted to electrical energy through a transduction mechanism [104–107]. The transduction mechanism should be designed to maximize the coupling between kinetic energy and electrical energy to improve the raw output power of a harvester and the characteristics of environmental vibration are the only factors that affect the performance of a harvester. A method of implementing vibration energy harvesting is to employ an electromechanical resonator which consists of an inertial mass attached to an inertial frame through a spring-equivalent structure, such as a cantilever. The environmental vibration applied on the inertial

frame is transmitted through a spring to the suspended inertial mass to produce a relative displacement between the frame and the mass. In order to increase the vibration amplitude, a resonant harvester is designed to be operated in or around the resonant frequency to produce a large displacement, hence more output power.

Fig. 2.1 Schematic of energy conversion in vibration energy transducers

A spring-mass system aims to convert vibration energy to relative displacement between the mass and the frame, hence strain in the spring. A transduction mechanism is then required to generate electricity by exploiting the displacement or strain (see figure 2.1 [108–112]). Piezoelectric materials are widely employed due to the relatively high power density and compatibility with conventional CMOS technology compared to other kinds of energy harvesters, such as electromagnetic and electrostatic harvesters [113–117].

#### 2.2 Equivalent circuit of a piezoelectric VEH

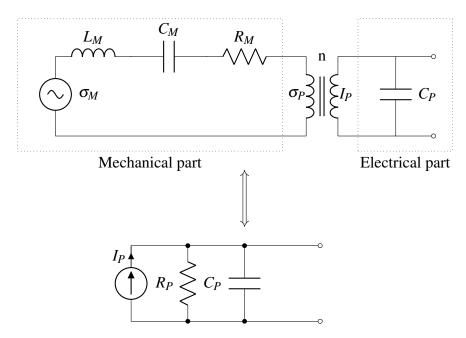

A cantilevered piezoelectric transducer (PT) generally consists of a substrate layer, a thin piezoelectric layer and two electrode layers on the both sides of the piezoelectric ceramics [12], as shown in figure 2.2 where the electrode pads are not shown in the figure. Sometimes a mass is added to the tip of the free end to increase the strain and decrease natural frequency [118–123]. Lead-Zirconate-Titanate (PZT) is commonly used for PT due to its relatively high piezoelectric charge constant ( $d_{31}$ ,  $d_{33}$  and  $d_{51}$ ); some other materials, like Zinc Oxide (ZnO) and Aluminum Nitride (AlN), are mainly used in MEMS-scale harvesters. The equivalent circuit of a piezoelectric harvester can be understood as a damped mechanical spring-mass system coupled to an electrical part, as shown in Fig. 2.3 [124, 125]. There are mechanical and electrical parts shown in the figure, where  $L_M$ ,  $C_M$  and  $R_M$  are equivalent to the mechanical mass, spring stiffness and mechanical loss respectively.  $\sigma_M$  represents the input excitation while the PT is excited. The output of the mechanical part (or the input of the transformer n), noted as  $\sigma_P$ , is the response of the PT under the excitation  $\sigma_M$ . The signal  $\sigma_P$  achieves its peak while the resonance frequency of the PT (formed by  $L_M$ ,  $C_M$  and  $R_M$ ) equals to the excitation frequency of  $\sigma_M$ .  $\sigma_P$  represents the strain (or stress) generated in the

Fig. 2.2 Cantilevered piezoelectric harvester

piezoelectric ceramics. The induced strain is then converted into electrical charge within the piezoelectric elements, resulting in a charge flow representing a current source. Hence, the input of the electrical part (or the output of the transformer n) is a current source noted as  $I_P$ . The transformer in the figure represents the work of converting strain to current and the factor n is equivalent to the charge constant of the piezoelectric material, which is  $d_{31}$  for most of PTs. More details on piezoelectric materials and widely used charge constants can be found in appendix A.2. In the electrical part, the capacitor  $C_P$  is the plate capacitor of the piezoelectric material, which is equivalent to the capacitance formed by the two parallel electrode layers.

Fig. 2.3 Equivalent circuit of a piezoelectric harvester

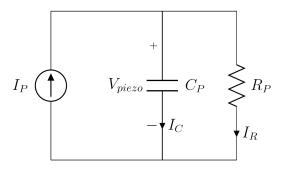

While the harvester is vibrating at or near resonance, the whole circuit can then be modeled as an equivalent current source  $I_P$  parallel with a capacitor  $C_P$  and a resistor  $R_P$  [126, 127]. The resistor can be interpreted as the charge leakage resistance between the two

Fig. 2.4 Load resistor connected to a monolithic PT.

plate of the capacitor  $C_P$ . The current source  $I_P$  directly depends on the strain variation of the mechanism of the harvester. While the harvester is excited at resonance by a sinusoidal vibration, the current source  $I_P$  can be modeled as a sinusoidal current source. The expression of  $I_P$  can be written as:

$$I_P = I_0 \sin \omega_0 t = I_0 \sin 2\pi f_0 t \tag{2.1}$$

where  $I_0$  depends on the excitation amplitude (or acceleration) and  $f_0$  is the excitation frequency. Unlike a conventional battery or other energy source, the power generated by a piezoelectric transducer (PT) can be an unstable AC output because it depends on the vibration occurrence, amplitude and frequency [128]. It can only generate power while vibration occurs and the output voltage and frequency depend directly on the input excitation. Furthermore, the high output impedance prevents effectively driving load electronics. All of these limitations make an interface circuit indispensable.

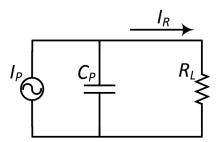

#### 2.3 Raw AC power generated by a PT

The raw output power from a piezoelectric transducer (PT) is analyzed in this section. The raw output power means the power consumed in a resistive load connected with the PT with the impedance matching. As discussed in the previous section, a PT can be modeled as a current source in parallel with a capacitor and a resistor. As the impedance of the resistor is typically much larger than that of the capacitor, the resistor is usually ignored to facilitate calculations. While the PT is excited with a sine wave excitation, the current source can be expressed as  $I_P = I_0 \sin(\omega t)$ , where  $\omega = 2\pi f_P$  and  $f_P$  is the excitation frequency. Hence, the total charge generated by the PT in a half period (T/2) can be calculated, which is expressed as:

$$Q_{total} = \int_0^{\frac{T}{2}} I_0 \sin \omega t dt = \frac{2I_0}{\omega}$$

(2.2)

Assuming the PT is operated as an open circuit, all generated charge  $Q_{total}$  flows into  $C_P$ . Therefore, the open-circuit zero-to-peak voltage amplitude is calculated as:

$$V_{OC} = \frac{1}{2} \frac{Q_{total}}{C_P} = \frac{I_0}{\omega C_P}$$

(2.3)

In order to measure the raw output power generated from a PT, a variable load resistor,  $R_L$ , is connected to the PT, as shown in Fig. 2.4. The resistance  $R_L$  is varied to match the internal impedance of the PT in order to find the peak output power consumed in the  $R_L$ . While a resistor  $R_L$  is connected to a PT, the current amplitude in  $R_L$  can be expressed as:

$$I_R(j\omega) = I_0 \frac{Z_C}{Z_C + R_L} = \frac{I_0}{1 + j\omega R_L C_P}$$

(2.4)

Hence, the output power consumed in the resistor  $R_L$  can be calculated as:

$$P_{R} = \left| \frac{1}{2} I_{R}^{2} R_{L} \right| = \frac{I_{0}^{2}}{2} \left| \frac{R_{L}}{(1 + j\omega R_{L} C_{P})^{2}} \right|$$

$$= \dots = \frac{I_{0}^{2}}{2} \frac{1}{\frac{1}{R_{L}} + \omega^{2} C_{P}^{2} R_{L}}$$

(2.5)

The output power  $P_R$  attains its peak while  $R_L = \frac{1}{\omega C_P}$ . Hence, the raw output power of a PT consumed in a matched resistive load is:

$$P_{R(max)} = \frac{I_0^2}{4\omega C_P} \tag{2.6}$$

Equation (2.6) shows the maximal AC power consumed in a matched resistive load. In order to make use of the generated power for load electronic devices, the power needs to be rectified and regulated [129–135]. Hence, interface circuits are required and the power efficiency of the circuits significantly affects the usable energy provided to the loads [136, 137].

#### 2.4 Full-bridge rectifier interface circuit

A typical MEMS piezoelectric transducer (PT) can provide an output power of up to  $500 \,\mu\text{W}$  per  $1 \,\text{cm}^2$  [95], which sets a strict constraint on designing an interface circuit for the load circuitry [138–143]. The interface circuit does not only need to consume ultra low power, but it also should be able to extract as higher power as possible from the piezoelectric harvester [144–148]. So in order to make the piezoelectric VEH system to provide a high output

power, the powering conditioning interface is as important as the harvester mechanism. This section provides an overall background on some reported interface circuits and performance analysis on these interfaces. The limitations are discussed and future design considerations are proposed.

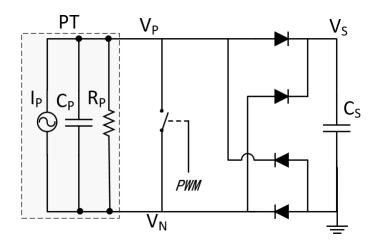

A piezoelectric vibration energy harvester vibrating at resonance can be considered equivalent to a current source  $I_P$  in parallel with a capacitor  $C_P$  and a resistor  $R_P$  [25, 149, 150]. As the resistor  $R_P$  is very large and is significantly higher than the impedance of  $C_P$ , it is usually ignored. According to the previous section, the output voltage and frequency may vary all the time according to the environmental vibration [151–153]. This unstable power source cannot be used directly to power analog or digital load circuitry, such as wireless sensors [8], pace-makers, etc. For this reason, a power conditioning circuit should be added between the piezoelectric transducer (PT) and the load circuitry in order to rectify and store the unstable AC energy into a battery [109, 154], which is usually a super capacitor with low leakage coefficient. As the output of the PT is an unstable or sinusoidal AC current, most of interface circuits use rectifiers to perform an AC-DC conversion before further power conditioning [155].

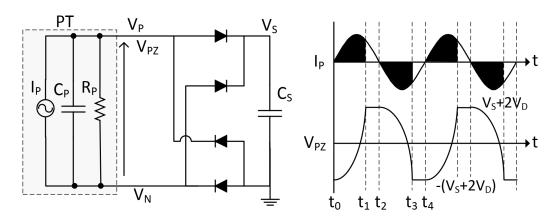

The most commonly used interface circuit for a piezoelectric vibration energy harvester is based on a full-bridge rectifier (FBR) [156–159], which employs four diodes to perform full-bridge rectification in order to do AC-DC conversion [160, 161]. Fig. 2.5 shows the circuit diagram of a FBR and the associated waveforms. The energy harvested from the output of a full-bridge rectifier is stored in a storage capacitor  $C_S$ . Usually, further voltage regulation circuitry is needed to provide a stable DC supply to loads. When the piezoelectric harvester vibrates and it is not connected to any circuit (open-circuit), there is a voltage difference between  $V_P$  and  $V_N$ , note  $V_{PZ(open)} = V_P - V_N$ . In order to charge the capacitor  $C_S$ , the voltage  $V_{PZ(open)}$  should firstly be greater than  $V_S$ ; in addition, it should also overcome the forward threshold voltages of the diodes. Hence,  $V_{PZ(open)} > V_S + 2V_D$  should be satisfied in order to make sure the PT can charge the storage capacitor  $C_S$ , where  $V_S$  is the voltage across  $C_S$  and  $V_D$  is the forward voltage drop in a diode.

At the end of a half vibration period, the voltage  $V_{PZ}$  equals  $V_S + 2V_D$  or  $-(V_S + 2V_D)$ .  $V_{PZ}$  is assumed to be equal to  $-(V_S + 2V_D)$  for the following explanation, which is labeled as the time instant  $t_0$  in Fig. 2.5. In order to charge the capacitor  $C_S$  in the next half cycle,  $V_{PZ}$  should go to  $V_S + 2V_D$ , which means the PT needs to charge its internal capacitor  $C_P$  from  $-(V_S + 2V_D)$  to  $V_S + 2V_D$  (from time  $t_0$  to time  $t_1$ ). After  $V_{PZ} = V_S + 2V_D$  satisfies, the rest of charge generated by the PT can then be able to be transferred to  $C_S$  between the time  $t_1$  and  $t_2$ . Noting the peak-to-peak open-circuit voltage of  $V_{PZ}$  as  $V_{pp(open)}$ , the condition for the FBR being able to transfer energy from the PT to  $C_S$  is given as:

Fig. 2.5 Full-bridge rectifier interface circuit for the piezoelectric harvester and the associated waveforms

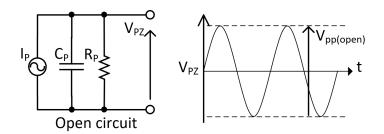

Fig. 2.6 The peak-to-peak open-circuit voltage  $V_{pp(open)}$ .

$$V_{pp(open)} > 2(V_S + 2V_D) \tag{2.7}$$

The peak-to-peak open-circuit voltage,  $V_{pp(open)}$  is illustrated in Fig. 2.6 and it is proportional to the excitation level. As shown in Fig. 2.5, the charge generated by the piezoelectric harvester between  $t_0$  and  $t_1$  is used to discharge and recharge the internal capacitor  $C_P$ , which means this amount of charge is wasted [162]. The wasted charge is illustrated as black areas in the figure. The useful charge that can be transferred to the storage capacitor is just in a small time interval between  $t_1$  and  $t_2$  for each half-cycle. Assuming the internal capacitance is  $C_P$ , the amount of charge wasted ( $Q_{wasted}$ ) between  $t_0$  and  $t_1$  for each half  $I_P$  cycle is given as:

$$Q_{loss(FBR)} = C_P(V_S + 2V_D) - C_P(-(V_S + 2V_D))$$

=  $2C_P(V_S + 2V_D)$  (2.8)

From Fig. 2.5, it can be found that the useful charge that can be transferred into  $C_S$  is the time intervals  $t_1$  to  $t_2$ ,  $t_3$  to  $t_4$ , etc. For each half cycle of  $I_P$ ,  $V_{PZ}$  needs to goes from  $V_S + 2V_D$

to  $-(V_S + 2V_D)$  or from  $-(V_S + 2V_D)$  to  $V_S + 2V_D$  before  $C_S$  can be charged. Therefore, the condition in equation 2.7 needs to be satisfied for the full-bridge rectifier to work. If this condition is not met, the full-bridge rectifier will stop operation and all the energy generated by the harvester is wasted in discharging and recharging  $C_P$ . For a  $V_{pp(open)}$  that is slightly higher than the threshold  $2(V_S + 2V_D)$ , most of the generated charge is wasted and the power efficiency is extremely low in this case.

In order to calculate the how much percentage of generated charge is wasted, the total charge generated by the harvester in a half cycle T/2 should be calculated, which can be written as:

$$Q_{total} = \int_0^{\frac{T}{2}} I_0 \sin \omega t dt = \frac{2I_0}{\omega}$$

(2.9)

Since all the generated charge flows into  $C_P$  while the PT is in an open circuit,  $V_{pp(open)}$  can be expressed as:

$$V_{pp(open)} = \frac{Q_{total}}{C_P} = \frac{2I_0}{\omega C_P}$$

(2.10)

So the percentage of the wasted charge in the total generated charge is given by:

$$\eta_{loss(FBR)} = \frac{Q_{loss(FBR)}}{Q_{total}} = \frac{\omega C_P(V_S + 2V_D)}{I_0} = \frac{2(V_S + 2V_D)}{V_{pp(open)}}$$

(2.11)

While  $V_{pp(open)} < 2(V_S + 2V_D)$ ,  $\eta_{wasted} = 100\%$  because the threshold is not attained. In order to calculate the harvested power stored in  $C_S$ , the charge flowing into  $C_S$  should first be found. The amount of total available charge flowing into  $C_S$  is the difference between the total generated charge in the PT and the wasted charge in the FBR. Hence, the amount of charge flowing into  $C_S$  is given as:

$$Q_S = Q_{total} - Q_{wasted} = 2C_P(\frac{V_{pp(open)}}{2} - V_S - 2V_D)$$

(2.12)

As a result, when the voltage increase  $\Delta V_S$  is very small, the energy transferred into  $C_S$  for half-cycle approximately equals to:

$$E_S = V_S Q_S = 2C_P V_S \left( \frac{V_{pp(open)}}{2} - V_S - 2V_D \right)$$

(2.13)

As this is the energy harvested in a half cycle, the power that can be transferred to  $C_S$  is:

$$P_S = \frac{E_S}{T/2} = 4C_P V_S f_P \left( \frac{V_{pp(open)}}{2} - V_S - 2V_D \right)$$

(2.14)

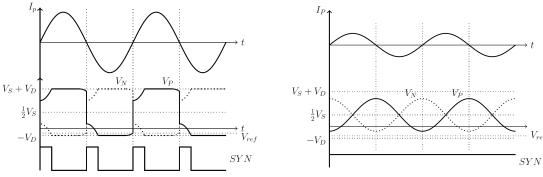

Fig. 2.7 SSHI interface for piezoelectric harvester and the associated waveforms

It can be easily found that the maximum  $P_S$  is obtained when  $V_S = \frac{V_{pp(open)}}{4} - V_D$ . The peak power transferred to  $C_S$  is:

$$P_{S(max)} = 4C_P f_P (\frac{V_{pp(open)}}{4} - V_D)^2$$

(2.15)

When ignoring the forward voltage drop of diodes  $V_D$ , the peak power can be rewritten as:

$$P_{S(maxFBR)} = \frac{1}{4} C_P f_P V_{pp(open)}^2$$

(2.16)

#### 2.5 Parallel-SSHI interface

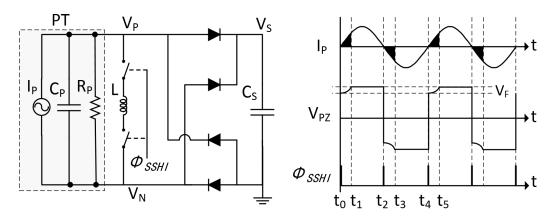

In order to minimize the wasted charge due to self-discharging and recharging internal capacitor  $C_P$  of the harvester, a scheme of employing synchronous charge inversion was proposed to enhance efficiency of piezoelectric energy harvesting devices [163], which is called "Parallel Synchronized Switch harvesting on Inductor (P-SSHI)". The circuit diagram and the associated waveforms are shown in figure 2.7.

A synchronous switch and an inductor are added in parallel with the piezoelectric transducer in order to flip the voltage. The signal  $I_P$  represents the equivalent current source of the piezoelectric harvester. At the time instant  $t_2$ , the zero-crossing of  $I_P$  is detected by a monitoring circuit and a pulse ( $\phi_{SSHI}$ ) is generated to turn ON the switch for a predetermined time to invert the voltage between  $V_P$  and  $V_N$ . The pulse width of  $\phi_{SSHI}$  should be exactly a half of the period of the RLC oscillation loop.

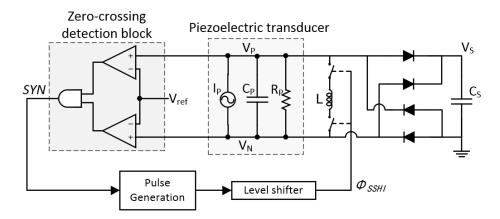

Figure 2.8 shows a simplified architecture of an SSHI rectifier, which contains a FBR, a zero-crossing detection block, a pulse generation block, a level-shifter, two analog switches

Fig. 2.8 Simplified system architecture of an SSHI interface circuit

and an inductor L. When  $I_P$  is close to zero, the diodes of the FBR are just about to turn OFF. At this moment, one of  $V_P$  and  $V_N$  begins to increase from  $-V_D$  and the other one begins to decrease from  $V_S + V_D$ . One common method to detect the zero-crossing moment of  $I_P$  is using two comparators to compare  $V_P$  and  $V_N$  with a reference voltage  $V_{ref}$ . This reference voltage is set slightly higher than  $-V_D$  and it aims to finds the moment while  $V_P$  or  $V_N$  begins to increase from  $-V_D$ . The outputs of the two comparators are ANDed and the resulting signal SYN presents a synchronous signal to control the switch. For each zero-crossing moment of  $I_P$ , a rising edge is generated in SYN and it is used to generate a pulse in the following blocks to control the inductor.

The ON resistance in the switch and any parasitic resistance in the RLC oscillation loop act as the electrical damping and it causes the loss of energy during charge inversion. This amount of energy loss forms a new threshold for the SSHI circuit to transfer charge from piezoelectric harvester to  $C_S$ , which can be written as:

$$V_{pp(open)} > V_F = (V_S + 2V_D)(1 - e^{-\frac{\pi}{\sqrt{\frac{4L}{R^2C} - 1}}}) = (V_S + 2V_D)\eta_F$$

(2.17)

where the threshold  $V_F$  is illustrated in figure 2.7, which represents the voltage loss after one flip.  $\eta_F$  is the voltage loss ratio between 0 and 1 and it is expressed as  $\eta_F = \frac{\pi}{\sqrt{\frac{4L}{R^2C}-1}}$ . The resistance R is the total resistance in the RLC loop, which consists of ON resistance in the switches, DC resistance of the inductor and all other parasitic resistance. Compared to the threshold of the FBR in equation (2.7), the SSHI circuitry decreases the threshold dramatically. Hence it significantly increases power efficiency, especially for small environmental excitations [164–166]. As  $V_F$  is the voltage loss after one flip in a half period of the vibration, the charge loss in this period can be written as:

$$Q_{loss(SSHI)} = C_P V_F \tag{2.18}$$

Hence, the amount of charge flowing into the storage capacitor  $C_S$  is:

$$Q_{S(SSHI)} = Q_{total} - Q_{loss(SSHI)} = C_P(V_{pp(open)} - V_F)$$

(2.19)

where,  $Q_{total}$  is given in equation 2.9. As a result, assuming the voltage increase in  $V_S$  is very small, the energy transferred into  $C_S$  in a half period can be expressed as:

$$E_{S(SSHI)} = V_S Q_{S(SSHI)} = C_P V_S (V_{pp(open)} - V_F)$$

(2.20)

Therefore, the extracted power stored in  $C_S$  is:

$$P_{S(SSHI)} = \frac{E_{S(SSHI)}}{T/2} = 2C_P V_S f_P(V_{pp(open)} - V_F) = 2C_P V_S f_P(V_{pp(open)} - (V_S + 2V_D)\eta_F)$$

(2.21)

The power attains its maximum value when  $V_S = \frac{V_{pp(open)}}{2\eta_F} - V_D$  and the maximum power can be calculated as:

$$P_{S(maxSSHI)} = 2C_P f_P \eta_F \left(\frac{V_{pp(open)}}{2\eta_F} - V_D\right)^2$$

(2.22)

While  $V_D$  is ignored, the peak power of using an SSHI interface circuit can be rewritten as:

$$P_{S(maxSSHI)} = \frac{1}{2\eta_F} C_P f_P V_{pp(open)}^2$$

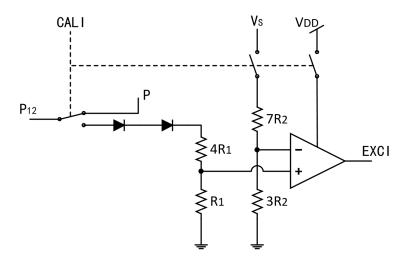

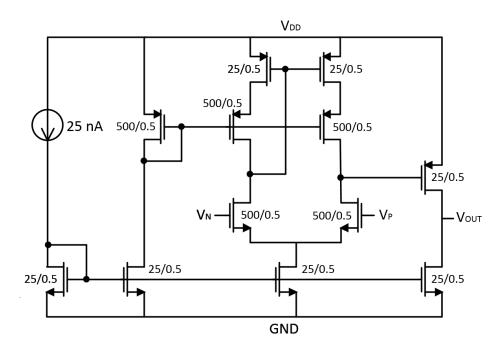

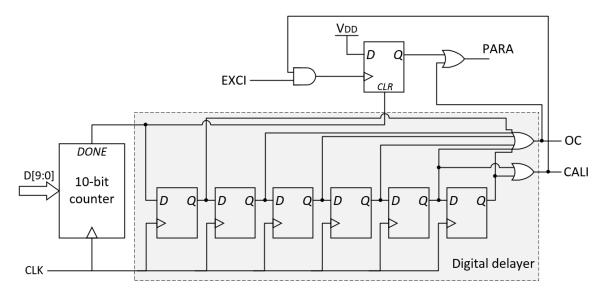

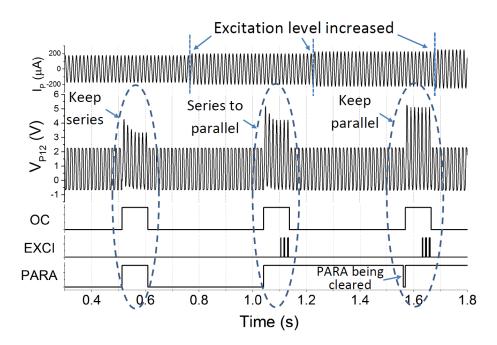

(2.23)