## An FPGA Implementation of a Power **Converter Controller**

Tero Kuusijärvi

### School of Electrical Engineering

Thesis submitted for examination for the degree of Master of Science in Technology. Espoo 13.10.2017

Thesis supervisor:

Prof. Kari Halonen

Thesis advisors:

D.Sc. (Tech.) Vlad Grigore

M.Sc. Pasi Lauronen

Aalto University School of Electrical Engineering

Author: Tero Kuusijärvi

Title: An FPGA Implementation of a Power Converter Controller

Date: 13.10.2017

Language: English

Number of pages: 7+84

Department of Electronics and Nanoengineering

Professorship: Electronic Circuit Design

Supervisor: Prof. Kari Halonen

Advisors: D.Sc. (Tech.) Vlad Grigore, M.Sc. Pasi Lauronen

High switching frequencies and control rates in switched-mode power supplies are hard to implement with microcontrollers. Very high clock frequency is required to execute complex control algorithms with high control rate. FPGA chips offer a solution with inherent parallel processing. In this thesis, the feasibility of implementing the control of a typical telecom power converter with FPGA is studied. Requirements for the control system partitioning are considered. The control of a resonant LLC converter is studied in detail and implemented in VHDL. As part of the controller, a high-resolution variable frequency PWM module and floating-point arithmetic modules are implemented. Finally, a complete VHDL simulation model is created and run in different conditions to verify the functionality of the design.

Keywords: LLC, FPGA, high frequency control, DPWM, PFM, power converter

### AALTO-YLIOPISTO SÄHKÖTEKNIIKAN KORKEAKOULU

DIPLOMITYÖN TIIVISTELMÄ

Tekijä: Tero Kuusijärvi

Työn nimi: Tehomuuntajan säädön toteutus FPGA:lla

Päivämäärä: 13.10.2017

Kieli: Englanti

Sivumäärä: 7+84

Elektroniikan ja nanotekniikan laitos

Professuuri: Electronic Circuit Design

Työn valvoja ja ohjaaja: Prof. Kari Halonen

Korkeat kytkentä- ja säätötaajuudet hakkuriteholähteissä ovat haastavia toteuttaa mikrokontrollereilla. Monimutkaiset säätöalgoritmit edellyttävät mikrokontrollereilta korkeaa kellotaajuutta. FPGA-teknologia mahdollistaa rinnakkaislaskennan, joka on etu säätösovelluksissa. Tässä työssä tutkitaan FPGA-teknologian soveltumista tyypillisen telecom-tehomuuntajan säätöön. Työssä selvitetään säätöjärjestelmän partitiointia sekä toteutetaan LLC-muuntajan ja sen säätöjärjestelmän simulaatiomalli VHDL-kielellä. Säädön osana toteutetaan korkearesoluutioinen PWM-moduuli sekä liukulukuaritmetiikkamoduuleja.

Avainsanat: LLC, FPGA, DPWM, PFM, tehomuuntaja

## Contents

| Abs | tract     |                                              | ii        |

|-----|-----------|----------------------------------------------|-----------|

| Abs | tract (in | Finnish)                                     | iii       |

| Con | tents     |                                              | iv        |

| Sym | nbols and | abbreviations                                | vi        |

| 1 I | ntroduct  | ion                                          | 1         |

| 2 ] | Theory a  | nd Background                                | 3         |

| 2   | .1 Teleco | om AC-DC Power Converter                     | . 3       |

| 2   | 2.2 Power | Factor Correction Circuit                    | . 4       |

|     | 2.2.1     | Power Factor                                 | . 4       |

|     | 2.2.2     | Structure and Operation                      | . 4       |

| 2   | LLC       | Resonant Converter                           | . 7       |

|     | 2.3.1     | Structure                                    |           |

|     | 2.3.2     | Resonant Tank Gain                           | . 8       |

|     | 2.3.3     | Operation                                    |           |

| 2   |           | Programmable Gate Array Technology           |           |

|     | 2.4.1     | Structure                                    |           |

|     | 2.4.2     | Routing, Interconnect and Clock Distribution |           |

|     | 2.4.3     | Design Flow                                  |           |

| 2   | 0         | al Control of PFC-LLC Power Converter        |           |

|     | 2.5.1     | Data acquisition                             |           |

|     | 2.5.2     | Control law generation                       |           |

|     | 2.5.3     | Digital PWM generation                       | . 20      |

|     |           | mplementation                                | <b>23</b> |

| 3   |           | ol System Partitioning                       |           |

|     | 3.1.1     | The Galvanic Isolation                       |           |

|     | 3.1.2     | Controller Requirements                      |           |

| -   | 3.1.3     | Partitioning Options                         |           |

|     |           | State Machine Structure                      |           |

| 3   |           | Width Modulation Architecture                |           |

|     | 3.3.1     | The Phase-shifting                           |           |

|     | 3.3.2     | The Counter                                  |           |

|     | 3.3.3     | The Asynchronous Output                      |           |

| 3   | -         | ronous Rectifier Control                     |           |

|     | 3.4.1     | Secondary Synchronization                    |           |

| 0   | 3.4.2     | Dynamic Range Requirement                    |           |

| 3   |           | ing-Point Arithmetic                         |           |

|     | 3.5.1     | Single-Precision Representation              |           |

|     | 3.5.2     | Number Format Conversions                    | . 39      |

3.5.3Subtraction 403.5.4423.5.5444 Simulations 46 Start-Up And Static Regulation 4.1464.2Dynamic Response 474.349Pulse Skipping 4.4Synchronous Rectifier Control 494.5504.6Floating-Point Arithmetic 514.7525 Conclusions 53References 55A PWM module 5858A.2 65A.3 Output Multiplexer 7273**B** Floating-Point Arithmetic  $\mathbf{74}$ B.1 74B.2 76B.3 80 B.4 82

# Symbols and abbreviations

## Symbols

| $b_n$           | bit of index n                                           |

|-----------------|----------------------------------------------------------|

| $C_r$           | resonant capacitance                                     |

| $D_r$           | duty cycle                                               |

| DR              | dynamic range                                            |

|                 | exponent bit of index n                                  |

| $e_n$<br>F      |                                                          |

|                 | relative switching frequency                             |

| $\int_{f}$      | frequency<br>clock frequency                             |

| $f_{clk}$       | clock frequency                                          |

| $f_{eff}$       | effective clock frequency                                |

| $f_r$           | first resonant frequency                                 |

| $f_{r2}$        | second resonant frequency                                |

| $f_s$           | switching frequency                                      |

| $I_{l,rms}$     | RMS value of total line (AC input) current               |

| $I_{l1,rms}$    | RMS value of line (AC input) current fundamental         |

| $I_p$           | transformer primary current                              |

| $I_{RMS}$       | RMS current                                              |

| $I_s$           | transformer secondary current                            |

| $L_m$           | magnetizing inductance                                   |

| $L_r$           | resonant inductance                                      |

| $m_n$           | mantissa bit of index n                                  |

| $N_p$           | number of turns in transformer primary winding           |

| $N_s$           | number of turns in transformer primary winding           |

| p               | index of most significant non-zero bit                   |

| Q               | quality factor                                           |

| $R_{AC}$        | equivalent load seen from the converter primary side     |

| $R_{load}$      | equivalent load seen from the converter secondary side   |

| S               | complex frequency                                        |

| $\frac{s_x}{-}$ | sign bit of word x                                       |

| $T_r$           | isolation transformer                                    |

| $t_{eff}$       | effective clock period                                   |

| $t_s$           | switching period                                         |

| $V_{AC}$        | AC voltage                                               |

| $V_{in}$        | input voltage                                            |

| $V_L$           | inductor voltage                                         |

| $V_{L(av)}$     | average inductor voltage                                 |

| $V_{out}$       | output voltage                                           |

| $V_p$           | transformer primary voltage                              |

| $V_{RMS}$       | RMS voltage                                              |

| $V_s$           | secondary voltage                                        |

| $\theta$        | angle between RMS voltage and RMS current in linear load |

| $\theta_1$      | angle between line voltage and line current fundamental  |

| $\Phi_m$        | magnetizing flux                                         |

| ω               | angular frequency                                        |

|                 |                                                          |

## Abbreviations

| AC            | alternating current                               |

|---------------|---------------------------------------------------|

| ADC           | analog-to-digital converter                       |

| ASIC          | application-specific integrated circuit           |

| CCM           | continuous-conduction mode                        |

| DC            | direct current                                    |

| DPWM          | digital pulse-width modulation                    |

| DSP           | digital signal processor                          |

| EMI           | electromagnetic interference                      |

| FHA           | first harmonic approximation                      |

| FPGA          | field-programmable gate array                     |

| GaN           | gallium-nitride                                   |

| HDL           | hardware description language                     |

| HIL           | hardware-in-the-loop                              |

| I/O           | input/output                                      |

| IP            | intellectual property                             |

| LSB           | least significant bit                             |

| LUT           | lookup table                                      |

| MCU           | microcontroller unit                              |

| MIPS          | million instructions per second                   |

| MOSFET        | metal-oxide-semiconductor field-effect transistor |

| MSB           | most significant bit                              |

| MSPS          | million samples per second                        |

| $\mathbf{PF}$ | power factor                                      |

| PFC           | power factor correction                           |

| PFM           | pulse-frequency modulation                        |

| PID           | proportional-integral-derivative                  |

| PLL           | phase-locked loop                                 |

| PWM           | pulse-width modulation                            |

| RAM           | random access memory                              |

| RMS           | root-mean-square                                  |

| SPI           | serial peripheral interface                       |

| SRAM          | static random access memory                       |

| VHDL          | very high speed hardware description language     |

| XOR           | exclusive or                                      |

| ZCS           | zero-current switching                            |

| ZVS           | zero-voltage switching                            |

|               |                                                   |

## 1 Introduction

The requirements for efficiency and flexibility of power converters are ever increasing. Efficient operation over wide operation conditions requires optimization schemes and special operation modes. These requirements demand more advanced control methods. As a result, the industry has turned to digitally controlled high-speed switching converters. Resonant converters are especially attractive since they can be operated in zero-voltage or zero-current-switching modes [1]. There is a drive towards smaller reactive component sizes and higher power densities, requiring ever higher switching frequencies. The maximum switching frequency in a power converter has previously been limited by the switching and conduction losses of silicon-based switching devices. With the emerging of Silicon-Carbide and Gallium-Nitride based low-loss switches, digital control has become the limiting factor for higher switching frequencies.

Digital control of switched-mode power converters is commonly implemented using a microcontroller with DSP capabilities. Special-purpose microcontrollers typically include all the necessary functionalities and peripherals to control a power converter, such as multipliers, timers, analog-to-digital converters and pulse-width modulators, enabling optimization of the total system cost. With matured integrated development environments, designing control algorithms for microcontrollers is a straightforward process. Microcontrollers are also inexpensive. The cheapest models are sold for less than a US dollar.

However, microcontrollers operate in a sequential manner. This means that the maximum instruction throughput is directly related to the system clock frequency. High control frequency requires high performance from the computation hardware itself as well as the peripherals. In one cycle control, there must be enough time in each cycle for the analog-to-digital conversions as well as the control computation. In addition, there must be some processor time reserved for other functionalities such as communication. The number of instructions in a control loop is thus limited, and this sets a limit to the complexity of the control. At the same time, the cost of power supplies is being pushed lower. These factors together make it very difficult to implement a cost-effective real-time control system for switching frequencies approaching 1 MHz with a microcontroller. This is also the reason why field-programmable gate arrays have become more attractive choice for control system implementation.

Unlike microcontrollers, FPGA chips allow for the development of parallel algorithms. The configurable logic interconnections make it possible to calculate parts of the control simultaneously at hardware level. The extra functionality of a control system, such as external communication and system level optimizations can be performed at the same time with the control. These factors remove the control complexity limit, since the control is no longer limited by the system clock frequency. Moreover, several converters can be controlled with one FPGA chip, increasing only the area and cost of the chip but not reducing the available computation time. In this work, the feasibility of using a field-programmable gate array chip in the control of a typical telecom AC-DC power converter is assessed from cost, performance, modularity and upgradability points of view. Furthermore, an efficient control topology for a PFC-LLC power converter is proposed and an LLC control algorithm capable of 1.2 MHz switching frequency is implemented in VHDL. As part of this implementation, a high-resolution, variable frequency pulse-width modulation architecture is implemented in VHDL. The implementation is verified by HDL simulation. PFC boost converter control implementation is not within the scope of this work.

## 2 Theory and Background

### 2.1 Telecom AC-DC Power Converter

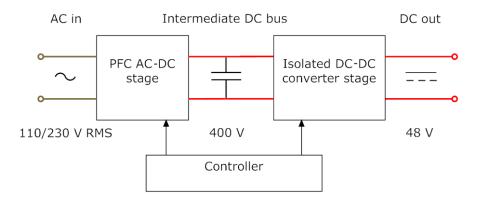

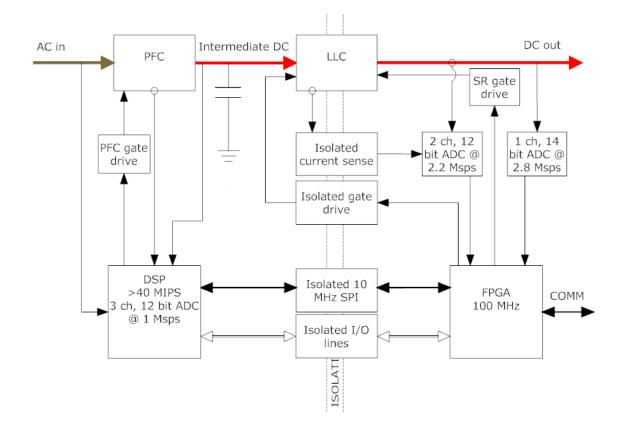

In telecommunication sector, the millions of cellular base stations distributed across the globe require high performance DC power supplies. The requirements for power density, smaller size, low harmonic distortion and range of loading conditions are increasing. The purpose of a telecom AC-DC power supply is to convert the line AC voltage of 230 or 110 volts to the DC voltage utilized by the telecom equipment, usually -48 V. The load to be powered may increase and decrease depending on the network utilization at given time. The power converter must be able to keep its output voltage regulated while supplying required amount of current. This power conversion must be achieved with the mentioned requirements taken into account. A popular solution for a switched-mode AC-DC power converter consisting of a boost PFC stage followed by a galvanically isolated DC-DC converter [2] is shown in Figure 1.

Figure 1: Simplified block diagram of a typical telecom AC-DC power converter

The purpose of the PFC stage (Power Factor Correction) is to keep the input current waveform sinusoidal and in phase with the input voltage. For this stage, a boost PFC topology is commonly employed. A benefit of such PFC stage is the ability to raise the intermediate voltage above the line voltage and also regulate it. This allows using both the 230 V and 110 V AC line inputs with the same design. After the PFC stage, there is a DC-DC stage to add galvanic isolation to the design and to create the 48 V output voltage from the intermediate DC bus voltage. Resonant LLC converter with synchronous rectification is typically used for this stage. The resonant operation allows for soft switching, resulting in highly efficient operation over wide load range. The operation of the two converter stages is governed by the controller block, shown in the bottom. It takes measurements of the various currents and voltages within the converter and generates the appropriate switching sequence for each switching device to keep the operation optimal.

### 2.2 Power Factor Correction Circuit

The PFC stage is essentially a rectifier coupled with a boost converter: its purpose is to shape the line current drawn by the power converter to sinusoidal form and keep it in phase with the input AC voltage while regulating the intermediate DC bus voltage. The sinusoidal waveform of line current minimizes its distortion. The distortion of the line current is linked to the efficiency of the whole power converter. High distortion equals high harmonic content which in turn means high reactive power and thus higher losses. Furthermore, distorted current might also distort the grid AC voltage, and that is why it should be minimized. Standards such as IEC61000-3-2 [3] regulate the maximum allowed levels of distortion in devices that are connected to the electric grid.

### 2.2.1 Power Factor

Power factor is defined as the relation of real power to apparent power in a system [4, p. 524]. It represents the efficiency of the use of real power within the system. Power factor for linear loads is given by:

$$PF = \frac{V_{RMS}I_{RMS} \cdot \cos(\theta)}{V_{RMS}I_{RMS}} = \cos(\theta), \tag{1}$$

where  $\theta$  is the angle between the RMS line voltage and RMS line current. Since the real power utilized by the system is the instantaneous product of voltage and current, high RMS values of voltage and current do not correspond to high power delivered to load, if the power factor is low. However, high RMS current does contribute to higher conductive losses, even if it is not in phase with the line voltage.

Switched-mode power supplies are not linear power systems. Rectifier bridges draw distorted currents, which degrade the power factor considerably. This is why it is not enough to keep the line current in phase with the input voltage. The general equation for the power factor is given by [4, p. 525]:

$$PF = \frac{I_{l1,rms}}{I_{l,rms}} \cdot \cos(\theta_1), \tag{2}$$

where  $I_{lI,rms}$  is the rms value of the fundamental component of the line current,  $I_{l,rms}$  is the rms value of the line current, and  $\theta_1$  the angle between the line voltage (assumed sinusoidal) and the fundamental component of the line current. Minimizing distortion implies minimizing the harmonic components of the line current to make the total rms value of line current equal to the rms value of the fundamental component. The goal is to shape the line current as close to purely sinusoidal as possible. There are passive and active means to improve the power factor. In this work, the active boost PFC topology shown in Figure 2 is used. With a boost PFC it is possible to achieve power factors higher than 98%.

#### 2.2.2 Structure and Operation

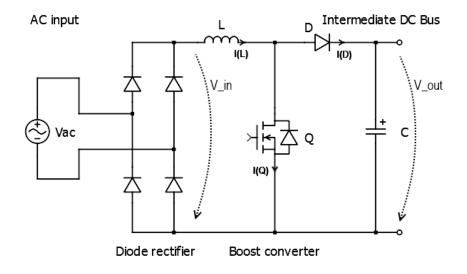

The PFC boost converter in Figure 2 consists of the input rectifier stage, boost inductor L, switch Q, boost diode D and the intermediate DC bus capacitor [4, p.

Figure 2: The PFC boost converter with a diode rectifier

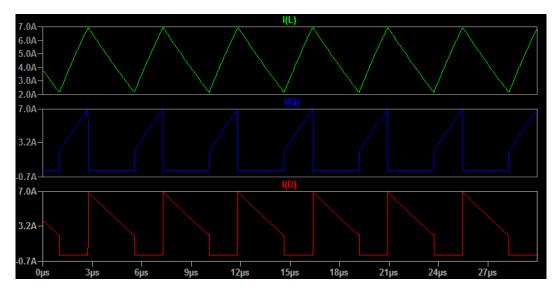

Figure 3: Current waveforms of the boost converter

528]. The boost inductor is located in the path of the input current, while the switch is connected to the boost inductor and the negative terminal of the intermediate DC bus capacitor. This configuration has advantages over buck and buck-boost type converters. When the converter operates in continuous-conduction mode (CCM), the input current is always greater than zero. It is also continuous, since it is not disrupted by the switch. The current stress of the switch is thus lower in a boost type converter. Additionally, the boost inductor smooths the input current, resulting in lower EMI generation [4, p. 529].

When the switch Q conducts, the input current flows through the boost inductor and the switch. The voltage over the inductor L is equal to the input voltage, which in this case is the rectified line voltage. The current through the inductor increases, while the load, which in this case is the LLC converter, is supplied with current from the discharging intermediate DC bus capacitor. Since the inductor corresponds to a short circuit for low frequencies, there cannot be an average non-zero voltage over the inductor. When the switch does not conduct, the input current flows through the boost inductor to the load and the intermediate DC bus capacitor. In this case, the voltage over the inductor is equal to the difference of input and intermediate DC bus voltages:

$$V_L = V_{in} - V_{out}.$$

(3)

Thus with a duty cycle D, the average inductor voltage is:

$$V_{L(av)} = 0 = D \cdot V_{in} + (1 - D) \cdot (V_{in} - V_{out})$$

(4)

$$(1-D) \cdot V_{out} = D \cdot V_{in} + (1-D) \cdot V_{in}$$

(5)

$$V_{out} = \frac{1}{1 - D} V_{in}.\tag{6}$$

As can be seen in Equation 6, the output voltage of a boost converter depends directly on the duty cycle. It is thus easy to control a boost converter, since increasing load or decreasing input voltage can both be compensated by simply increasing the duty cycle towards 1. However, in a boost PFC this is not enough. The intermediate DC bus voltage must be regulated while simultaneously keeping the line current waveform sinusoidal. This can be accomplished by appropriate control. Since the value of duty cycle corresponds to the period of time the current of the boost inductor increases, the line current can be shaped with the duty cycle. For example, when the line voltage wave reaches its peak value as its derivative is close to zero, duty cycle of 50% keeps the inductor current and equivalently the input current approximately constant. After this, the average duty cycle is decreased in phase with the sinusoidal line voltage. It is important to note here that the switching frequency is much higher than the line frequency. If the duty cycle is varied synchronously with the line voltage, the average inductor current is approximately sinusoidal within a line cycle. Varying the duty cycle results in ripple effect on the intermediate DC bus voltage.

To decrease the losses of the PFC stage, it is possible to use bridgeless design for the input rectifier. Several such implementations have been proposed [5]. The advantage of this is that some of the diodes within the path of the input current can be removed, and thus the conduction losses reduced. However, bridgeless designs require more complicated control because of greater number of controlled switches. Furthermore, bridgeless design introduces other challenges like increased commonmode noise [5].

Another technique to reduce the conduction losses of the PFC stage is to use multiple interleaved boost converters [6]. The conduction losses, directly proportional to the square of the current, are reduced to a quarter by dividing the current equally between two interleaved converters. Another benefit of this is the ability to use smaller inductors, because the current ripple in each interleaved path sums up with a 180 degree phase shift, compensating the total ripple. From the grid side, this seems like doubled switching frequency, which naturally reduces ripple. Additionally, this reduces the line current distortion and transient overshoots [7]. Interleaved PFC is best controlled digitally because of the need to keep the interleaved paths 180 degrees out of phase.

### 2.3 LLC Resonant Converter

Conventional PWM power converters operate using hard switching. This means switching where the switch device has to endure high voltage or current during the switching. Hard switching causes great stress to the power electronic components and also losses in the form of heat. The losses originate from the fact that during the switching, there is both current running through the component as well as a voltage over it. Moreover, rapidly changing currents and voltages cause increased electromagnetic interference. To overcome these problems, research efforts were focused to resonant converter topologies such as LLC converter [4, p. 410]. The general idea was to use resonant tanks to create sinusoidal voltage and current waveforms, allowing the switching to be timed to the zero-crossing points. From there come the terms zero-voltage switching (ZVS) and zero-current switching (ZCS). A characteristic of LLC converter is that it is controlled with switching frequency while the duty cycle is fixed to approximately 50%, whereas the conventional PWM converters are controlled with duty cycle while keeping the switching frequency constant.

#### 2.3.1 Structure

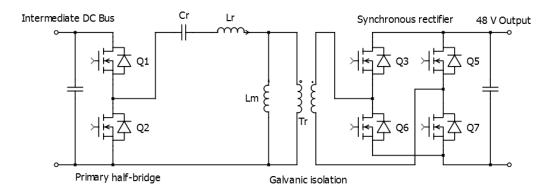

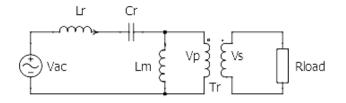

Figure 4: Circuit diagram of synchronously rectified LLC converter

There are several possibilities to arrange the reactive components of the resonant tank that result to different characteristics. One of those possibilities is the LLC converter [8]. In LLC converter the resonant tank is made of three reactive components, two inductors and a capacitor. LLC converter has advantages over the other configurations, namely efficient operation over wide load conditions and wider gain variation with narrower frequency control range [8]. Additionally, in LLC configuration it is possible to utilize the parasitic inductances of the transformer by integrating all the inductive components into the transformer. This is very beneficial from the system integration point of view. Common to all configurations is the basic operation principle: a square wave is applied to the resonant circuit by the primary bridge circuit. The bridge circuit can be of either half-bridge of full-bridge type. In this work, the half-bridge topology is used. The resonant circuit filters the applied wave, and approximately sinusoidal current flows through the windings of the isolation transformer. The current is rectified in the secondary side of the transformer, resulting in DC-DC conversion.

The secondary side rectifier could be realized with diodes. However, with passive rectification there exists a constant voltage drop over the rectification diodes. With low voltages and large currents, the resulting power loss grows too high. Synchronous rectification is a viable solution. Replacing the diodes with switches, such as the MOSFETs in Figure 4, the conduction losses can be almost eliminated. Synchronous rectification requires that the switching takes place when the current through the switch is approximately zero, in order not to introduce additional losses originating from the switching. To achieve this the phase difference between the primary switching signals and the secondary switching signals must be calculated.

The three reactive components of the resonant tank cause the converter to have two resonant frequencies, given by [9, p. 7/64]:

$$f_r = \frac{1}{2\pi\sqrt{L_r C_r}}\tag{7}$$

$$f_{r2} = \frac{1}{2\pi\sqrt{(L_r + L_m)C_r}},$$

(8)

where  $L_m$ ,  $L_r$  and  $C_r$  are the magnetizing inductor, resonant inductor and resonant capacitor respectively. The primary resonant frequency in Equation 7 is the frequency that is commonly referred to as the resonant frequency. The second resonant frequency  $f_{r2}$  is at lower frequency than the primary resonant frequency. The impedance of the resonant tank can be either inductive or capacitive, depending on the switching frequency. When the LLC converter is driven below the lower resonant frequency, the input impedance of the resonant tank is capacitive. The input impedance is inductive when the resonant tank is driven above the higher resonant frequency [9, p. 7/64]. Between the resonant frequencies, the input impedance depends on the load condition, and can be either inductive or capacitive.

#### 2.3.2 Resonant Tank Gain

The analysis of resonant switching converters is thought to be more complex than in the case of conventional PWM converters. To address this, it is assumed from here on that from the square wave input only the first fundamental harmonic component contributes to the transfer of electrical power and the rest of the harmonic content is neglected. This greatly simplifies the analysis of the converter, and allows the usage of classical AC circuit analysis to study the dynamics of the system. This is called first harmonic approximation (FHA). In addition to the LLC gain characteristics, it is used in the control algorithm of the synchronous rectifier to find the optimal switching instants for the secondary side switches.

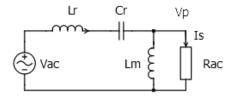

Simplified circuit consisting of the primary resonant tank, magnetizing inductance, transformer and the load is shown in Figure 5. The synchronous rectifier is combined

Figure 5: Simplified diagram of resonant tank, transformer and load.

with the actual load to a single load  $R_{load}$ , seen as an AC load from the transformer. The voltages from the dotted terminals to the undotted terminals for primary and secondary sides of the transformer are respectively the following [10, p. 137]:

$$V_p = N_p \frac{d\Phi_m}{dt} \tag{9}$$

$$V_s = N_s \frac{d\Phi_m}{dt},\tag{10}$$

where  $N_p$  and  $N_s$  is the number of turns on either side and  $\Phi_m$  is the magnetizing flux of the transformer. An ideal transformer is assumed here, and for that reason no leakage fluxes or losses are included in this analysis. Dividing Equation 9 by Equation 10 yields:

$$\frac{V_p}{V_s} = \frac{N_p}{N_s}.$$

(11)

Conservation of energy means that the input power and the output power of the transformer must be equal. This means that:

$$V_p I_p = V_s I_s \tag{12}$$

$$\rightarrow \frac{V_p}{V_s} = \frac{I_s}{I_p} = \frac{N_p}{N_s}.$$

(13)

The relationship between the primary current and the secondary current is then:

$$I_s = I_p \frac{N_p}{N_s}.$$

(14)

From Equation 14 it can be seen that the secondary current is simply the primary current scaled by the turns ratio constant. This means that the primary and secondary currents are in phase, and the circuit in Figure 5 can be further simplified by including the transformer and the load to a single AC load,  $R_{AC}$ . The simplified circuit is shown in Figure 6.

Figure 6: Further simplified resonant circuit.

Using Laplace transforms to obtain the complex impedances, we get for the complex primary voltage:

$$V_{p} = \frac{\frac{sL_{m}R_{AC}}{sL_{m}+R_{AC}}}{\frac{sL_{m}R_{AC}}{sL_{m}+R_{AC}} + sL_{r} + \frac{1}{sC_{r}}}V_{AC}$$

(15)

$$V_{p} = \frac{sL_{m}R_{AC}}{sL_{m}R_{AC} + s^{2}L_{m}L_{r} + sL_{r}R_{AC} + \frac{sL_{m} + R_{AC}}{sC_{r}}}V_{AC}$$

(16)

$$V_p = \frac{s^2 C_r L_m R_{AC}}{s^2 C_r L_m R_{AC} + s^3 C_r L_m L_r + s^2 C_r L_r R_{AC} + s L_m + R_{AC}} V_{AC}$$

(17)

$$V_p = \frac{s^2 C_r L_m R_{AC}}{s^3 C_r L_m L_r + s^2 C_r R_{AC} (L_m + Lr) + s L_m + R_{AC}} V_{AC}.$$

(18)

Substituting  $j\omega$  in place of the complex frequency s yields:

$$V_{p} = \frac{-\omega^{2}C_{r}L_{m}R_{AC}}{-j\omega^{3}C_{r}L_{m}L_{r} - \omega^{2}C_{r}R_{AC}(L_{m} + Lr) + j\omega L_{m} + R_{AC}}V_{AC}$$

(19)

$$V_{p} = \frac{-\omega^{2}C_{r}L_{m}R_{AC}}{j(\omega L_{m} - \omega^{3}C_{r}L_{m}L_{r}) - \omega^{2}C_{r}R_{AC}(L_{m} + Lr) + R_{AC}}V_{AC}.$$

(20)

Substituting switching frequency  $2\pi f_S$  in place of  $\omega$  yields:

$$V_p = \frac{-(2\pi f_s)^2 C_r L_m R_{AC}}{j((2\pi f_s)L_m(1 - (2\pi f_s)^2 C_r L_r)) - (2\pi f_s)^2 C_r R_{AC}(L_m + Lr) + R_{AC}} V_{AC}.$$

(21)

Quality factor Q and relative switching frequency F are the following:

$$Q = \frac{\sqrt{\frac{L_r}{C_r}}}{R_{AC}} \tag{22}$$

$$F = \frac{f_s}{f_r}.$$

(23)

Using quality factor and relative switching frequency instead of  $R_{AC}$  and  $f_s$  in Equation 21 results to:

$$V_{p} = \frac{-(2\pi F f_{r})^{2} C_{r} L_{m} \frac{\sqrt{\frac{L_{r}}{C_{r}}}}{Q}}{j((2\pi F f_{r}) L_{m}(1 - (2\pi F f_{r})^{2} C_{r} L_{r})) - (2\pi F f_{r})^{2} C_{r} \frac{\sqrt{\frac{L_{r}}{C_{r}}}}{Q} (L_{m} + Lr) + \frac{\sqrt{\frac{L_{r}}{C_{r}}}}{Q}}{(24)}$$

Using Equation 7, this simplifies into:

$$V_p = \frac{-F^2 L_m}{j \cdot Q L_m F(1 - F^2) - F^2 (L_m + L_r) + L_r} V_{AC}$$

(25)

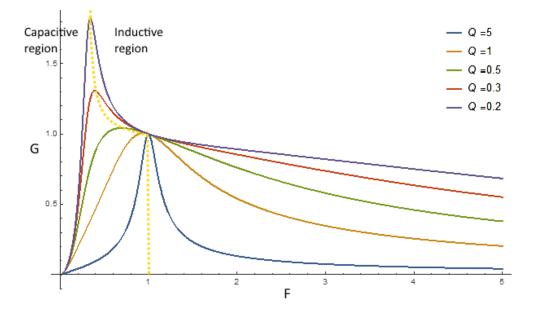

Figure 7: LLC resonant tank gain as function of relative switching frequency The equation for the resonant tank gain G(Q, F) is then:

$$G(Q,F) = \left|\frac{V_p}{V_{AC}}\right| = \frac{F^2 L_m}{\sqrt{(QL_m F(1-F^2))^2 + (L_r - F^2(L_m + L_r))^2}}.$$

(26)

As can be seen from Figure 7, the gain of the resonant tank depends on the switching frequency of the primary side bridge circuit. The LLC converter is controlled by adjusting the switching frequency near the resonant point. Zero-voltage switching requires that the resonant tank impedance is inductive [9, p. 15/64]. The switching frequency must then be limited to the inductive frequencies. Inductive impedance increases with frequency, which is why the gain of the resonant tank is lower at higher frequencies. The controller must respond to decreasing input voltage or increasing load by reducing the switching frequency. With heavy loads (corresponding to quality factor of 5 in Figure 7), the lowest allowed frequency is the resonant frequency. With lighter loads, the switching frequency can be even lower, as long as it is in the inductive region. All the gain curves coincide at the resonant frequency, where it has value of unity. This is the operation point when the load condition is at the specified nominal level. As will be shown next, it is the point of most efficient operation.

### 2.3.3 Operation

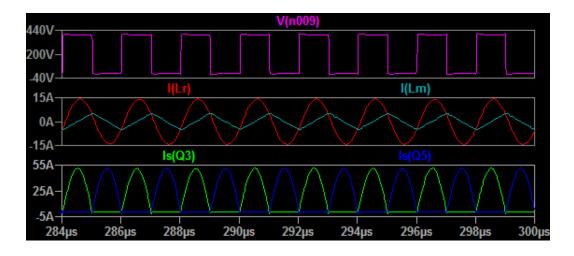

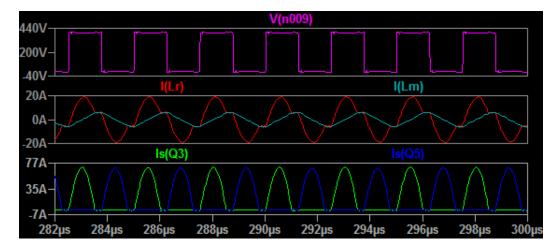

Figure 8: LLC waveforms at resonant frequency

in Figures 8 - 10, the voltage and current waveforms of the LLC converter are plotted. V(n009) refers to the voltage applied to the resonant tank by the primary switches. I(Lr), I(Lm), Is(Q3), and Is(Q5) are the resonant inductor current, magnetizing current, and source currents through secondary switches Q3 and Q5 (in Figure 4) respectively. In Figure 8 the circuit is operated at the resonant frequency. The resonant inductor current I(Lr) is approximately sinusoidal and the magnetizing current I(Lm) is triangular. The difference of these two currents flows through the windings of the transformer. On the secondary side, the current flows through the rectifier switches, which can be operated in ZCS conditions. On the primary side, ZVS conditions are achieved in turning on the switches. During turn-off, there is always some current flowing through the switches, causing turn-off losses. It should be noted here that the resonant inductor current is not at its peak during the switching, but rather has reversed its direction of change and is approaching zero. At the points

when the resonant inductor current meets the magnetizing current, the conducting primary side switch is turned off. The inductive operation region guarantees that the current will keep flowing. The only path for the current is through the body diode of the other switch. To force the current through the body diode, the voltage at the switching node is forced to increase to forward bias the body diode. After this has happened, the voltage over the switch is just the forward voltage of the body diode, allowing ZVS at the turn-on.

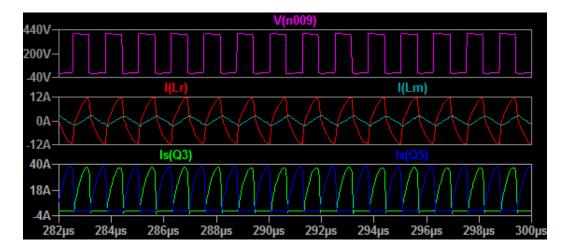

Figure 9: LLC waveforms below resonant frequency

in Figure 9, the converter is operated below resonant frequency. Now the square voltage period is longer than the resonant period of the resonant tank. The resonant inductor current I(Lr) meets the magnetizing current I(Lm) before the end of the switching half-cycle. After this point, no current flows through the primary windings of the transformer until the beginning of the next switching half-cycle. The current is simply circulated in the primary side, resulting in increased conduction losses. On the secondary side, the duty cycle of the switches must be reduced, since the duration of the current pulses are now only a portion of the primary switching cycle.

in Figure 10, the converter is operated above resonant frequency. Now the square voltage pulse is too short to allow for the resonant inductor current to complete the resonant cycle. On the primary side, this increases the turn-off losses of the switches, as the resonant inductor current is closer to its peak during the switching. On the secondary side, ZCS is no longer possible. As can be seen in the figure, the secondary current pulses are disrupted and the new half-cycle is started, resulting in inreased switching losses.

As a whole, LLC control is relatively complicated. The circuit gain is controlled with varying frequency rather than duty cycle. The control response must be different for different load conditions, as can be seen in Figure 7. The secondary duty cycle is not necessarily the same as the primary duty cycle. This is demonstrated in Figure 9. In the same figure, it can be seen that in addition to calculating the duty cycle, the switch control pulses must be slightly advanced in relation to the primary pulses to ensure zero-current switching. This advancing or delaying depends on the

Figure 10: LLC waveforms above resonant frequency

primary switching frequency. This synchronization is somewhat complicated, and it is further analyzed in section 3.4. Tight regulation of the output voltage typically requires a two-stage nested control, with output voltage and primary current being the measured quantities that are then compared to their reference values [11]. As the goal is to move to higher switching frequencies in the future to increase power density and reduce component sizes, it requires a high performance controller to run a complex control algorithm. This is why the FPGA technology is becoming more and more interesting for control implementations.

## 2.4 Field-Programmable Gate Array Technology

Field-programmable gate-array is essentially programmable logic. FPGA chips make it possible for the developer to implement logic functions in hardware. This allows implementing extremely fast algorithms and parallel processing without overhead. FPGAs can be used for most of the applications that application-specific integrated circuits (ASIC), but unlike ASICs, their logic functionality is not fixed during production but rather defined later by the developer. For this reason, using an FPGA chip instead of an ASIC is an attractive option in prototyping, low volume production and situations where it is necessary to be able to modify and update the logic within the final product on the field. While having reduced time-to-market, FPGAs are not fully customizable like ASICs and therefore cannot be as precisely designed as ASICs. An ASIC developer can draw wires in the design as desired, while FPGA designer must rely on pre-existing wiring and connections.

## 2.4.1 Structure

FPGA chip consists of two basic building blocks, logic and interconnections [12, p. 3–4]. In addition, there are number of I/O pins to connect the chip to the rest of the printed circuit board. Together these blocks form the logic fabric of the FPGA. The

logic resources are commonly realized with N-input lookup tables (LUT). LUTs are basically truth tables, which can implement any N-input combinational logic function. Lookup tables are programmed with a truth table of the implemented function. A 4-input LUT is equal to a 16-bit read only memory connected to a multiplexer. Complex combinational logic functions can be implemented with multiple lookup tables interconnected in a specific manner.

In addition to the lookup table, the other basic element in a logic slice is the register, or a flip-flop. The register is essentially a 1-bit memory element, which samples the input at a certain point of the provided clock signal and transfers the input to its output. Without memory, it would be impossible to implement state machines with an FPGA, and only combinational logic would be possible. In addition to memory, registers allow the implementation of delays and pipelines. Registers are also the root of the timing considerations of an FPGA design. To avoid metastable states and ensure correct operation, the input must be stable for a certain period of time before and after the sampling moment. These periods are called setup and hold times respectively. Using too high clock frequency for a given logic path would result in too little time for the settling of the input data of the register at the end of the path, causing its output data to be invalid at the next sampling moment. The timing requirements can be relaxed by using a lower frequency clock or inserting registers within the logic path.

Besides the LUT and the register, there is usually a multiplexer within each logic slice. With the multiplexer, output of either the LUT or the register can be chosen as the output of the block. The multiplexer is also the element that allows flexible interconnection of sequential and combinational logic.

There are usually ASIC sections, called hard intellectual property cores (IP), designed within an FPGA to allow for more flexible clock management and fast, resource efficient arithmetic operations. These blocks include phase-locked loops, delay lines, memory blocks and multiply-accumulators. These blocks can be conveniently connected to the logic fabric to improve the performance of related logic or preserve the logic resources of the chip.

#### 2.4.2 Routing, Interconnect and Clock Distribution

In a single FPGA chip, there can be thousands of individual logic slices. To map a complex logic function on the chip, the slices must be interconnected in a meaningful way. The commonly used routing architecture is the island-style architecture. In this architecture, the logic slices are arranged in a two-dimensional array with interconnections and routing in between. At the intersections of routing channels, there are switchboxes to connect the logic slices and the wiring itself in a configurable manner.

The clock signal as well as a global reset signal usually have dedicated routings, inputs and buffers to minimize skew and ensure an even distribution to the entire FPGA chip. There can be several clock domains with different frequencies on a single FPGA. Often, some of the logic running on the chip has tighter timing requirements than the rest. This allows using the minimum required clock frequency within a certain clock domain in order to save dynamic power. Care must be taken when routing signals from one clock domain to another. Since the differing clocks can be of different frequency and phase, it is possible that the register in the target domain samples the input data during a transition within the source clock domain, resulting in corrupted data. This can be avoided by using multiple buffer registers between clock domains to reduce the likelihood of unsettled input data.

### 2.4.3 Design Flow

The FPGA design flow is similar in the development environments of the major manufacturers. The steps are [13]:

- 1. HDL description

- 2. Translation and synthesis

- 3. Design implementation

- 4. Physical implementation

In the first step, a HDL description is written. Popular hardware description languages are VHDL and Verilog, derived from Ada and C respectively [12, p. 129]. At this point, the design is created as several modules, which can usually be individually simulated to ensure their functionality before interconnecting them as a larger design. Care must be taken to write the kind of description, which corresponds to the available hardware elements in some way. It is possible to write HDL code that is not synthesizable. Simulation after and during this step is called pre-synthesis simulation.

In the second step, the written description is synthesized. This means creating a netlist out of the design [13]. The netlist describes the logic gates needed to implement the design as well as the way those components are connected. Simulation after this step is call post-synthesis simulation.

In the third step, the netlist is mapped to the available FPGA resources and subsequently placed and routed on the target FPGA. The best physical locations for the functional blocks are found and routing between the blocks is calculated. The result of this step is the configuration data that can be programmed on to the FPGA chip. Simulation after this step is called post place-and-route simulation.

The data that specifies the configuration is called the configuration bitstream [12, p. 402]. In the final step, the bitstream is actually programmed into the target FPGA chip. After this step, the functionality of the design can be verified for example with a logic analyzer or a hardware-in-the-loop (HIL) simulation. As mentioned in the previous subsections, there are many elements in an FPGA that can be configured. These elements are the truth tables of LUTs, initial values of the D flip-flops, the select value of the multiplexers of the logic slices and the configurations of the switchboxes. Both the logic and the interconnect configuration bits are commonly static SRAM. The bitstream is usually stored in a non-volatile flash memory, external or internal. From there, the configuration data is loaded to the FPGA's internal SRAM memory

at the time of power-on start-up or during a manual reset at run time. SRAM is a type of volatile memory, which keeps its value only when it is powered [12, p. 17].

FPGA development allows for code reuse just like in software engineering. Because of the relatively large workload involved in creating a complex digital design from scratch, it is common to use previously designed and verified modules to speed up the development cycle. The major FPGA vendors have reusable modules, called soft IP cores, available for purchase and some for free.

## 2.5 Digital Control of PFC-LLC Power Converter

The main elements of digital switched mode power supply control system are [14, p. 6]:

- 1. Data acquisition

- 2. Control law generation

- 3. Digital PWM generation

### 2.5.1 Data acquisition

As digital controllers operate with sampled and quantized measurements, analog-todigital converters are needed to get information about the controlled process. These measurements are essentially the feedback loop of the control system. In the case of PFC-LLC power converter, we need several measurements for the control. These include:

- 1. AC input voltage

- 2. PFC phase current(s)

- 3. PFC output or intermediate voltage

- 4. LLC primary current

- 5. LLC output current

- 6. LLC output voltage

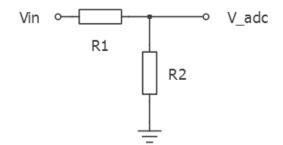

Typical ADCs have an input range of [0, 3.3] volts. However, many of the measured quantities have too large values to be directly measured with an ADC. It is necessary to scale those values down to the suitable range. Additionally, some measurements must be obtained across the isolation barrier. Different quantities require different sensing methods. For DC voltages, the scaling is done with a voltage divider. This is simply a chain of resistors in series, which scales the high voltages to lower voltages. While a resistor chain is a simple and low-cost measurement method, it does not provide isolation. A surge voltage in the input of the voltage divider can propagate past the voltage divider, possibly destroying some components. To

Figure 11: A voltage divider

make sure that the resistors themselves will not be destroyed by surges, they must be properly selected. The voltage divider is shown in Figure 11. The equation for the scaled-down voltage  $V_{adc}$  is:

$$V\_adc = Vin \cdot \frac{R2}{R1 + R2}.$$

(27)

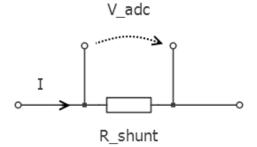

For DC currents, the most relevant options for obtaining the measurement and scaling the value are shunt resistors and Hall-effect sensors [15, p. 133]. Shunt resistor is a resistor placed in the path of the current to be measured. As the current flows through the resistor, a detectable voltage drop is formed over the resistor. The measurement scale can be adjusted by sizing the resistor properly or using an amplifier circuit. However, the resistor should be of small value, since it affects the surrounding circuit. In addition to the voltage drop over the resistor, some power is inevidently dissipated within the resistor. It should be noted that measuring current with a shunt resistor provides no isolation. The shunt resistor is shown in Figure 12. The equation for the voltage drop is:

$$V\_adc = I \cdot R\_shunt.$$

<sup>(28)</sup>

Figure 12: A shunt resistor

Instead of measuring the voltage drop in a resistor, Hall-effect sensors measure the magnetic field created by the current [15, p. 133]. This has the advantages of not affecting the measured circuit and providing electrical isolation. Hall-effect sensors are useful for measuring large currents, since those generate larger magnetic fields, leading to smaller relative error. With small currents however, factors such as the orientation of the sensor in relation to earth's magnetic field can affect the measurement considerably. Hall-effect sensors are also very sensitive to differences in distance to the measured wire as well as the wire geometrics [15, p. 134].

For AC quantities, a straightforward sensing method is to use a transformer. With proper turns ratio, the secondary winding of a voltage transformer provides a voltage which can be directly measured, as is shown in Equation 11. In case of AC current, a current is obtained from the secondary winding. If a resistor is connected to the secondary winding, voltage directly proportional to the primary current can be measured over the resistor. With proper sizing of the transformer and the resistor, negligible additional load is presented to the primary side. As an added benefit, transformers provide isolation.

The requirements for the sampling speed and bit resolution of the measurements vary, but generally the measurements that are needed within the control loops have the strictest requirements. The requirements depend on the control loop frequency as well as the dynamic and static requirements of the control. The control loop frequency means the rate at which the control algorithm is executed. The ADC's sampling speed must be at least equal to the control loop frequency, and in practice higher than that. In one-cycle control, it is necessary to have ADC sampling rate higher than the control loop frequency to leave a portion of the control period for the control law generation.

Dynamic requirements refer to the way the controlled system responds to changes in its operating conditions. Higher resolution of the ADC means that the output word of the ADC is wider in bits. This means that the measured quantity is represented by a larger integer value than with a smaller resolution ADC. When the measured quantities change their value, that change is more easily detected with a higher resolution ADC. Furthermore, when the measured quantity differs from the set reference point, the error quantity seen by the controller has a greater value. Finer precision also helps the control system to achieve more stable operation around the set reference. This requirement is usually defined as the maximum allowed ripple in a given quantity.

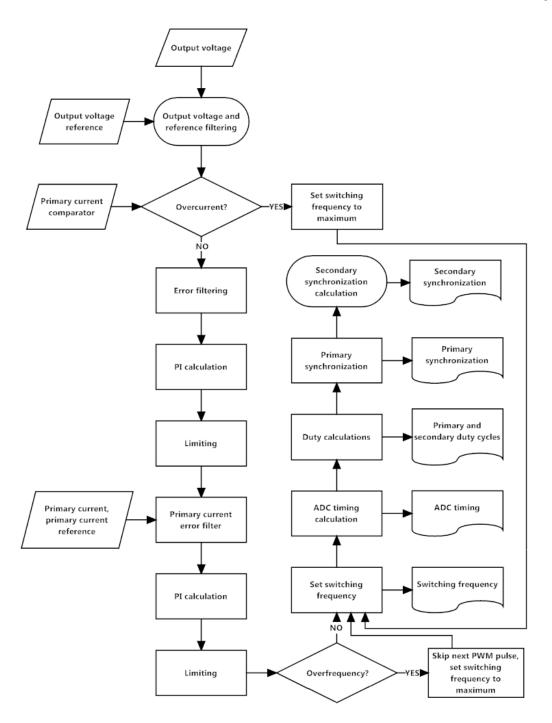

#### 2.5.2 Control law generation

The output of the controlled process, in this case currents and voltages, depend on both past and present inputs. The past inputs have caused the process to enter a certain state: its node voltages and branch currents have a certain value at a given time instant. Based on this state, certain actions must be taken to direct the process towards the desired state. As the process here is a power converter, this generally means taking appropriate actions to reach a desired output voltage. Control law means the function of process states, which determines the actions to be taken. In an LLC converter, at some instant, the output voltage might be less than the reference voltage. The control law dictates that in this situation, the action to be taken is to reduce the switching frequency of the primary side switches in order to increase the gain of the resonant tank and subsequently the output voltage. Similarly, the control law dictates that an output voltage exceeding the reference voltage should be compensated by increasing the switching frequency.

Control law also determines the magnitude of the response to a certain magnitude of error between the reference and the measured quantity. This is done using proportional-integral-derivative (PID) control structure. PID control is probably the most used control structure within industrial control. It is very robust, since it doesn't require information about the process itself. The process output is measured and subtracted from the reference to yield an error term. A control command is calculated as a sum of three terms: one directly proportional to the instantaneous error term (P), one proportional to the change, or derivative of the error term (D) and one proportional to the accumulated or integral of the error term (I). In digital control, it is sometimes good practice to use only P and I terms, since there is always noise present in measurements. From the control point of view, noise equals to abrupt changes, causing strong responses because of the derivative term. This kind of action might actually worsen the dynamic properties of the control and possibly make it unstable. This is the reason why only PI control is used in this work.

The control law is generated by a digital signal processor, a microcontroller or an FPGA chip. The FPGA or microcontroller is called a controller. The controller takes as its inputs the necessary measurements, and from them calculates the digital command word, which represents the appropriate response to a given process state at a given instant. This digital command word is then fed to an actuator, in this case a digital pulse-width-modulation unit (DPWM), which is the means by which the controller can affect the controlled process.

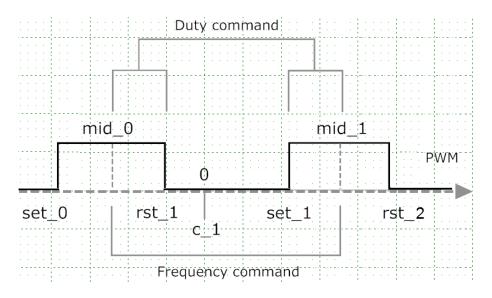

### 2.5.3 Digital PWM generation

The DPWM can be thought of as a digital-to-analog converter: it converts the digital command word to an analog signal, which has the essential information modulated in the relative width of its pulses as well as in its harmonic content. When the frequency of the modulated signal is controlled, the module is called pulse-frequency-modulator (PFM). In this work, both PWM and PFM are used. The relative width of the pulses is called the duty cycle, which is usually given as a percentage. A 0% duty cycle corresponds to a signal that is constantly zero and duty cycle of 100% corresponds to a constantly high signal. A duty cycle of 50% is equal to a square wave: the signal is at a logic high for as long period of time as it is at the logic low. This series of pulses is used to control the state of the semiconductor switches within the power converter. For example, in the LLC primary half-bridge there are two switching devices that are operated out of phase, allowing a square wave of about 400 V to be applied to the resonant tank.

Unlike analog PWM modules, the PWM output of a digital modulator is not continuous but rather has a finite number of possible output duty cycles. The width of the digital command word determines the resolution of the DPWM module. Since the command word represents a value between 0% and 100%, or [0, 1], the number

of possible values of the command word relates to the maximum precision with which the desired duty cycle percentage can be obtained. For example, an 8-bit DPWM module has 256 possibilities for the duty cycle, which means that the finest possible adjustment of the duty cycle is about 0.39 percentage points. The frequency resolution is limited by the period of time that the least significant bit (LSB) of the frequency command word corresponds to. If an LSB of the frequency command word is equal to 1 ns, and the operation frequency is initially 1 MHz, then increasing the frequency command by one LSB results in a period of:

$$t_s = 1\mu s + 1ns = 1.001\mu s \tag{29}$$

$$f_s = \frac{1}{t_s} \approx 999kHz. \tag{30}$$

The frequency resolution is then 1 kHz around the frequency of 1 MHz, or about 10 bits:

$$2^{10} = 1024 \approx \frac{1MHz}{1kHz}.$$

(31)

As can be seen from above, the frequency resolution in bits depends on the frequency around which the control system operates. The higher the control frequency, the lower is the available PWM frequency resolution in bits. The resolution is important from control point of view, since the accuracy of the control is limited by the PWM resolution. The PWM resolution must be at least higher than the ADC resolution to avoid limit cycling [16].

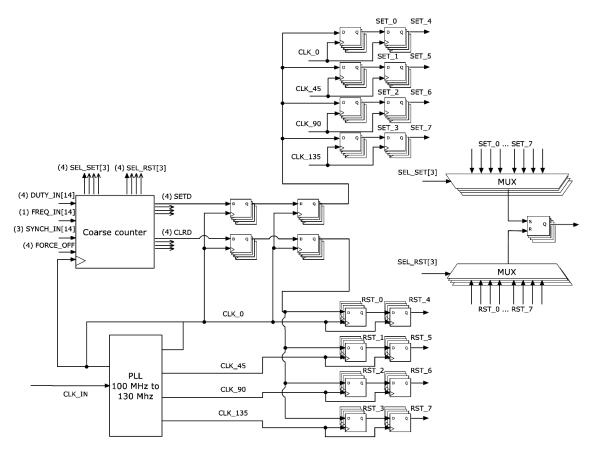

There are a couple of possible DPWM architectures for FPGAs [17] and several implementations that are based on these architectures or hybrids of them [17]-[21]. These architectures are the counter based and delay line based architectures. The counter based architecture is in principle similar to the analog PWM: The output is obtained by comparing the PWM command word to a carrier signal. In DPWM, the carrier signal is a digital counter, and the comparator is a digital comparator. The counter starts from zero, with the PWM output at logic high. The counter then increases its value at every clock cycle, until the counter value is equal to the digital command word. This is where the PWM output is reset to logic low, and is kept in that value until the counter increases to its maximum value and is set to zero again. This is a simple architecture and easy to implement with FPGA resources. The disadvantage of this architecture is that the resolution of the PWM signal is directly limited by the system clock frequency. Since the digital counter is compared to the reference once every clock cycle, the finest adjustment of the duty cycle is equal to the length of the clock cycle. For example, 14 bit duty cycle resolution around 1 MHz operation frequency requires system clock frequency of 16.38 GHz.

The delay-line architecture utilizes the propagation delays of buffers to set the duty cycle of the output. A clock input of desired frequency is fed to this modulator, and in the beginning of each clock cycle, the modulator output is set to logic high with a latch. The rising edge of the clock then propagates through series of buffers, each of which has a known delay. The delay of a single buffer corresponds to the least significant bit of the duty cycle command word. The delay must be equal in each buffer so that the duty cycle varies linearly in response to changes in the command word. The number of buffers through which the rising clock edge propagates to the reset port of the output latch is determined by the digital command word. With this architecture, the finest possible adjustment is limited only by the smallest propagation delay of available silicon resources, usually given by tens or hundreds of picoseconds. This is possible with a simple inverter gate, for example. The main disadvantage is that a large number of required buffers consumes large area of silicon or equivalently large amount of available FPGA resources. To implement a DPWM module with 10 bit resolution, there must be 1024 buffer elements in series. Other issue is that the propagation delay of logic gates depends on multiple variables, like silicon production process, junction temperature and used supply voltage. This is challenging if the final product is designed to be used in varying temperatures or if it is desired that the FPGA chip vendor is not fixed to just one.

## 3 Control Implementation

Many issues must be addressed when designing the control of a power converter. Starting from top level, the first step is the placement of the necessary devices within the physical layout of the converter. This is called control system partitioning. At the same time, a suitable way to generate the PWM control signals for the switching devices must be found, while taking into account the necessary performance as well as cost. The various measurements and their individual requirements must be considered. When the control system includes an FPGA, the required logic resource consumption of different implementations must be taken into account. This has a direct effect on the total system cost. Finally, suitable components must be chosen. In this work, the key component is the FPGA chip. Since the initial goal of the work was to find a low-cost way to implement the control, the chip selection was done in the beginning. The chosen FPGA architecture was ECP5 from Lattice Semiconductor [22], because of the price and available hardware and logic resources. The ECP5 chips include hardware digital signal processing blocks with multipliers and accumulators, and offer a relatively large number of LUTs in their price range. At the time of writing, the smallest LFE5U-12F chip with 12000 LUTs sold for less than 6\$ (minimum quantity 168) in online component distributor Digikey.com.

## 3.1 Control System Partitioning

Digital control allows multiple different configurations in the way the control system is partitioned. The optimal partitioning offers the best balance of several factors, which include total system cost, control performance, hardware and software development effort considerations, system modularity, surge robustness and the ease of upgrading the product firmware in the field. The options for control partitioning of an AC-DC power converter have been researched [2], and their advantages and disadvantages are known. However, the research has been mainly focused on using microcontrollers and not FPGA chips. A well partitioned control system takes into consideration the special properties and also the limitations of FPGAs.

### 3.1.1 The Galvanic Isolation

In DC-DC power converter, the galvanic isolation between the primary and secondary sides is beneficial for the following reasons: [10, p. 142].

- 1. To protect the user from electric shocks

- 2. To allow for more reference potentials

- 3. To avoid using components with unnecessarily high ratings

The AC mains voltage as well as the intermediate DC voltage in the primary side are dangerous to the user. This is why those should be isolated from the secondary side and the power supply chassis. The galvanic isolation in the LLC converter is in many ways the focus of the control partitioning. The power supply designer has the freedom of choosing how to place the controllers and peripherals in relation to the isolation. The isolation forms a barrier for the critical control and measurement signals within the feedback loop, and this barrier must be crossed in some way. If the signal crossing the isolation barrier is a one-channel digital control signal, it is easy to use a low-cost optocoupler for the isolation. Another simple case is AC current: a simple transformer provides the means to cross the isolation. However, the output voltage is within the LLC control loop, and for that reason it should be measured very accurately and quickly. This places limitations on the ways that the output voltage could be measured across the isolation barrier. The way the control system is partitioned greatly affects the measurements and controls.

### 3.1.2 Controller Requirements

The LLC controller is required to have higher performance than the PFC controller [2]. This can be understood in terms of the output voltage. The output voltage has the strictest accuracy and dynamic requirements and it is also within the control loop of the LLC controller. The synchronous rectifier control adds complexity to the LLC control algorithm. Using the same estimations for required microcontroller performance as in [2], 1.2 MHz control loop frequency would require a microcontroller capable of executing at least 120 million instructions per second (MIPS). With an FPGA, there is no such a performance measurement as MIPS, but it can give some reference to the necessary FPGA system clock frequency and area. If the control algorithm is not parallelized at all, then the clock frequency must be at least 120 MHz for a 120 MIPS requirement. Since the control loop often includes instructions like saving some measurement or reference values or calculating the PID control terms sequentially, its length can usually be reduced considerably. This means computing in parallel, which possibly increases the utilized FPGA area but relaxes the clock frequency requirements. With ECP5 chips, system clock frequencies up to 400 MHz are possible [22, p. 65] while frequencies up to about 100 MHz are possible without extensive timing closure efforts.

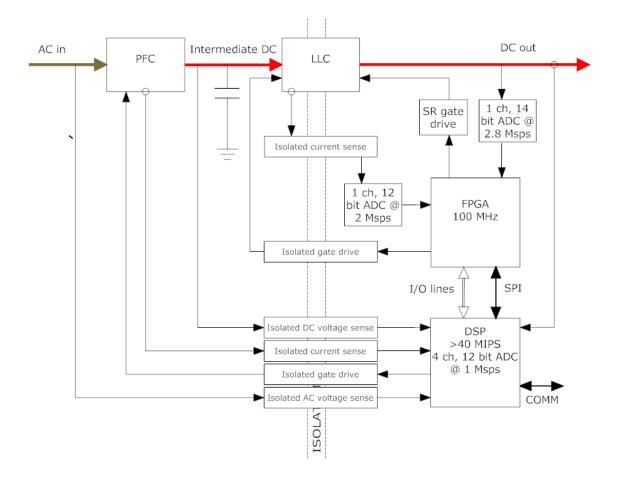

### 3.1.3 Partitioning Options

There are number of ways the partitioning can be arranged with using just one or more FPGA chips, an FPGA and a DSP, or an FPGA and an MCU. In all cases, the LLC control is handled by the FPGA. DSP in this context means a microcontroller with digital signal processing capabilities that can be used for the PFC control (> 40 MIPS [2]), communication and system supervision. It is also assumed that it includes multiple channel AD-converter. An MCU is a low performance microcontroller that is only used for communication and system level supervision and optimization tasks. The possible partitioning options are:

- 1. FPGA in primary

- 2. FPGA in secondary

- 3. FPGA in both sides

- 4. FPGA in primary, DSP in primary

- 5. FPGA in primary, DSP in secondary

- 6. FPGA in secondary, DSP in primary

- 7. FPGA in secondary, DSP in secondary

- 8. FPGA in secondary, MCU in primary

- 9. FPGA in secondary, MCU in secondary

- 10. FPGA in primary, MCU in primary

- 11. FPGA in primary, MCU in secondary

The first two options mean that a single FPGA chip would generate the control law for both LLC and PFC converters, and also perform additional computing like system level optimizations and external communication. The third option would have an FPGA in both primary and secondary, with each controlling one of the converters. One of the FPGAs would handle system optimizations and external communication. In options 4. - 7., the LLC control law is generated by the FPGA and the PFC control law by the DSP, with different placements in relation to the isolation. In options 8. - 11., The FPGA is used to generate the control laws while the communication and system optimization is handled by the MCU.

The output voltage measurement requires an external ADC in all cases. This is because of the required accuracy and speed. Even though the low-cost DSPs usually have fairly fast and accurate integrated ADCs, required speed (2.8 MSPS) and accuracy (higher than 12 bits resolution) are not available within the cheapest DSPs. Routing the measurement samples to the FPGA at 1.2 MHz rate would create overhead in the DSP firmware point of view, and this would take away a lot of processing time from the DSP. There is no considerable advantage in placing the FPGA in the primary side since the DC-DC primary current can be easily measured over the isolation with a current transformer. These reasons strongly favor placing the FPGA in the secondary side.

Using only one large FPGA chip for all tasks is attractive in system integration point of view. Runtime optimization would be easy, since all the related variables would be within one controller. Upgrading the FPGA configuration in the field would be easy, since there would be no need to keep track of matching software and FPGA configuration versions as in options 4. - 11. Nonetheless, the system supervision, external communication and power-on sequence functionality would have to be implemented as a state-machine, requiring the use of a softcore processor like Latticemico32. Latticemico32 is an IP module, which implements a processor within the logic fabric of the FPGA [23]. It allows developing software in C programming language and running that software within the FPGA. However, to implement both control loops and a softcore processor with enough program memory and RAM would require much more FPGA resources than implementing just the LLC control. All the measurements would require external ADCs, which together with a larger FPGA chip would raise the system cost too high. Because of the high volumes of DSPs, it is more expensive to use an external ADC than a DSP with an integrated ADC with similar performance. At the time of writing this work, the cheapest 1MSPS, 12 bit resolution ADCs costed approximately twice as much as the cheapest microcontroller with an integrated ADC of equal performance.

The advantages of using two FPGAs over using just one FPGA is the increased hardware modularity as well as reduction of necessary isolation crossings. The other FPGA could be replaced without changing the first one. The required FPGA resources are roughly the same for the control law generation. The communication between the chips will require some extra development effort as well as FPGA resources. Instead of isolating the ADC communications, isolation is needed for the internal communication bus. Nonetheless, this partitioning would be expensive because of the required ADCs and FPGA resources.

Since using an MCU for system optimization also requires using many external ADCs, the most attractive partitioning options from cost point of view are 6. and 7., which have an FPGA for LLC control law generation and a DSP for PFC control as well as for most of the measurements. A comparison of all the partitioning options is shown in Tables 1, 2, and 3.

| Layout                 | 1.<br>FPGA in primary                            | 2.<br>FPGA in secondary                          | 3.<br>FPGA in both sides                                                                   | 4.<br>FPGA in primary,<br>DSP in primary                             |

|------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Functions              | FPGA handles<br>controls, extra<br>functionality | FPGA handles<br>controls, extra<br>functionality | Secondary FPGA<br>controls LLC and<br>extra functionality,<br>primary FPGA<br>controls PFC | FPGA controls<br>LLC, DSP controls<br>PFC and extra<br>functionality |

| External ADCs          | All measurements                                 | All measurements                                 | All measurements                                                                           | Output voltage,<br>output current,<br>primary current                |

| Switch isolation       | Synchronous rectifier                            | LLC primary, PFC                                 | LLC primary                                                                                | Synchronous rectifier                                                |

| Isolated voltage meas. | Output                                           | Intermediate, PFC<br>bridge                      | -                                                                                          | Output                                                               |

| Isolated current meas. | Output                                           | LLC primary, PFC                                 | LLC primary                                                                                | Output                                                               |

| Int. comm. isolation   | No                                               | No                                               | Yes                                                                                        | No                                                                   |

| Ext. comm. isolation   | Yes                                              | No                                               | No                                                                                         | Yes                                                                  |

| Surge robustness       | Least                                            | Medium                                           | Most                                                                                       | Least                                                                |

| FPGA resources         | Most                                             | Most                                             | Most                                                                                       | Least                                                                |

| Field programming      | Easiest                                          | Easiest                                          | Hardest                                                                                    | Hardest                                                              |

| Runtime optimization   | Easiest                                          | Easiest                                          | Hardest                                                                                    | Hardest                                                              |

| Cost                   | Highest                                          | Highest                                          | Highest                                                                                    | Lowest                                                               |

Table 1: Partitioning options 1. - 4.

|                        | 5.                 | 6.                 | 7.                 | 8.                  |

|------------------------|--------------------|--------------------|--------------------|---------------------|

| Layout                 | FPGA in primary,   | FPGA in secondary, | FPGA in secondary, | FPGA in secondary,  |

|                        | DSP in secondary   | DSP in primary     | DSP in secondary   | MCU in primary      |

| Functions              | FPGA controls      | FPGA controls      | FPGA controls      | FPGA handles        |

|                        | LLC, DSP controls  | LLC, DSP controls  | LLC, DSP controls  | controls, MCU extra |

|                        | PFC and extra      | PFC and extra      | PFC and extra      | functionality       |

|                        | functionality      | functionality      | functionality      |                     |

| External ADCs          | Output voltage,    | Output voltage,    | Output voltage,    | All measurements    |

|                        | primary current    | output current,    | primary current    |                     |

|                        |                    | primary current    |                    |                     |

| Switch isolation       | Synchronous recti- | LLC primary        | LLC primary, PFC   | LLC primary, PFC    |

|                        | fier, PFC          |                    |                    |                     |

| Isolated voltage meas. | Output, intermedi- | -                  | Intermediate, PFC  | Intermediate, PFC   |

|                        | ate, PFC bridge    |                    | bridge             | bridge              |

| Isolated current meas. | PFC                | LLC primary        | LLC primary, PFC   | LLC primary, PFC    |

| Int. comm. isolation   | Yes                | Yes                | No                 | Yes                 |

| Ext. comm. isolation   | No                 | No                 | No                 | No                  |

| Surge robustness       | Least              | Most               | Medium             | Medium              |

| FPGA resources         | Least              | Least              | Least              | Medium              |

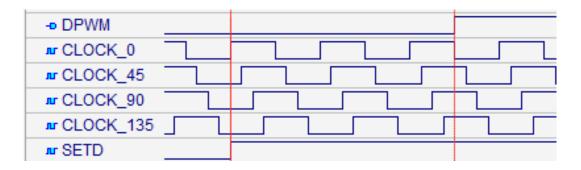

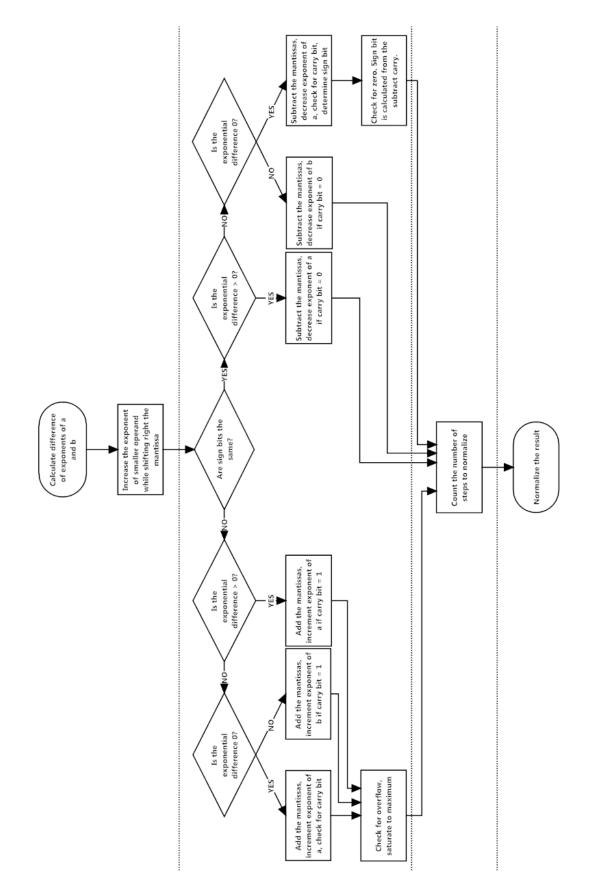

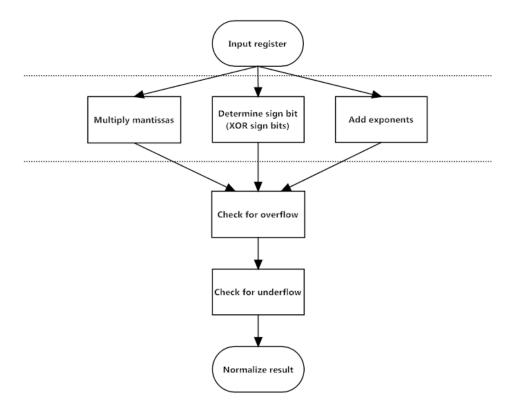

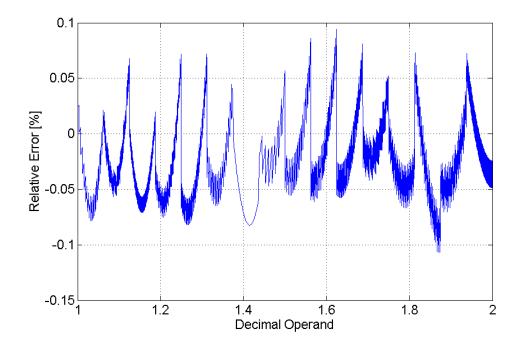

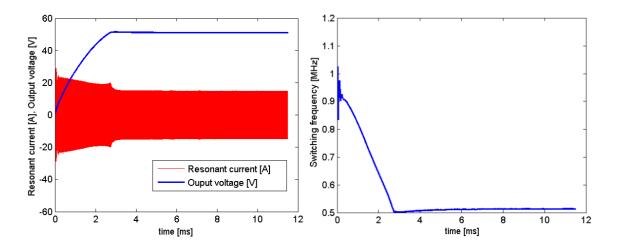

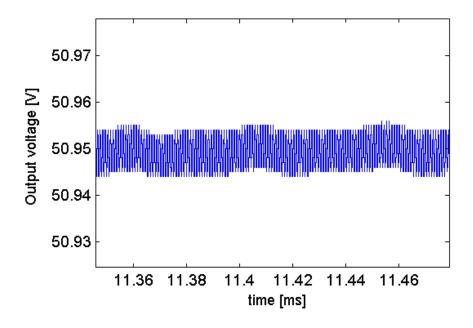

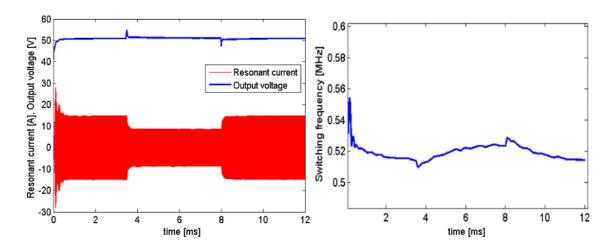

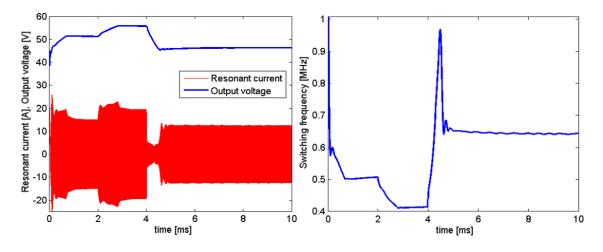

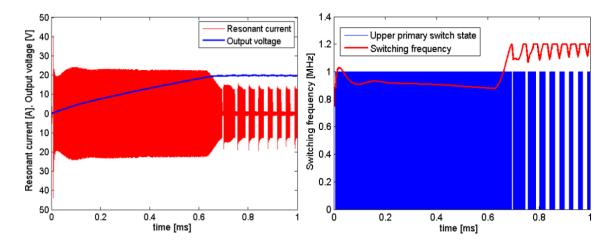

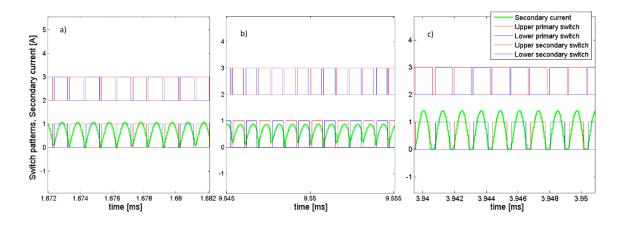

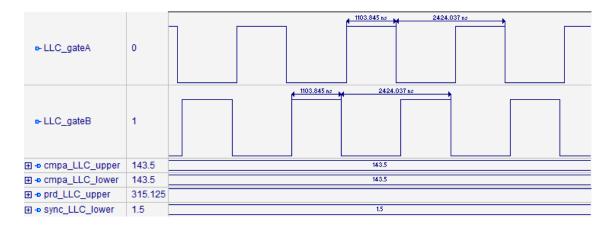

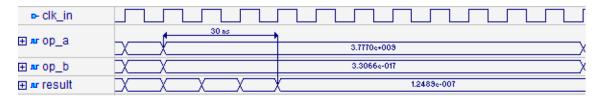

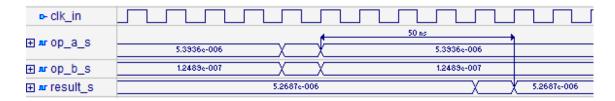

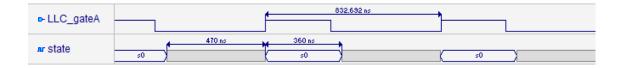

| Field programming      | Hardest            | Hardest            | Hardest            | Hardest             |