## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2017

# A Silicon Carbide Power Management Solution for High Temperature Applications

Robert Murphree University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Power and Energy Commons

## Recommended Citation

Murphree, Robert, "A Silicon Carbide Power Management Solution for High Temperature Applications" (2017). Theses and Dissertations. 2542.

http://scholarworks.uark.edu/etd/2542

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

## A Silicon Carbide Power Management Solution for High Temperature Applications

## A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

## Robert Murphree University of Arkansas Bachelor of Science in Electrical Engineering 2015

## December 2017 University of Arkansas

| This thesis is approved for recommendation | to the Graduate Council.              |

|--------------------------------------------|---------------------------------------|

| Dr. H. Alan Mantooth<br>Thesis Director    | _                                     |

| Dr. Simon Ang<br>Committee Member          | _                                     |

| Dr. A. Matthew Francis Committee Member    | Dr. Ashfaqur Rahman Ex-officio Member |

#### Abstract

The increasing demand for discrete power devices capable of operating in high temperature and high voltage applications has spurred on the research of semiconductor materials with the potential of breaking through the limitations of traditional silicon. Gallium nitride (GaN) and silicon carbide (SiC), both of which are wide bandgap materials, have garnered the attention of researchers and gradually gained market share. Although these wide bandgap power devices enable more ambitious commercial applications compared to their silicon-based counterparts, reaching their potential is contingent upon developing integrated circuits (ICs) capable of operating in similar environments.

The foundation of any electrical system is the ability to efficiently condition and supply power. The work presented in this thesis explores integrated SiC power management solutions in the form of linear regulators and switched capacitor converters. While switched-mode converters provide high efficiency, the requirement of an inductor hinders the development of a compact, integrated solution that can endure harsh operating environments.

Although the primary research motivation for wide bandgap ICs has been to provide control and protection circuitry for power devices, the circuitry designed in this work can be incorporated in stand-alone applications as well. Battery or generator powered data acquisition systems targeted towards monitoring industrial machinery is one potential usage scenario.

#### Acknowledgements

I am grateful for the opportunity Dr. Mantooth and Kacie Woodmansee have given me to work in the MSCAD laboratory. I would like to thank the members of my advisory committee – Dr. Simon Ang, Dr. Matt Francis, and Dr. Ashfaqur Rahman. The guidance from Ashfaqur and Matt during my time in the MSCAD laboratory as an undergraduate and then as a graduate student has undoubtedly helped to shape this work.

I am also thankful for the former and current students of the MSCAD IC design group including Shamim Ahmed, Matt Barlow, Affan Abbasi, Sajib Roy, Aminta Castillo, Maria Benavides, Austin Gattis, Chase Rowlett, and Kyle Addington. The project related experience they shared with me has played an instrumental role in the design work presented.

The assistance from the late Dr. Michael Glover and Michael Steger during their time at the High Density Electronics Center (HiDEC) was invaluable when packaging circuits. The time they put in, even after normal working hours, to help our entire group made this work possible.

The material presented is based upon work funded in part by the National Science Foundation grants #IIP1237816 and #EPS-1003970. Any opinions, findings, and conclusions presented do not necessarily reflect the views of the National Science Foundation.

## **Dedication**

I would like to dedicate this work to the IC design group. They've always attempted to answer any design related questions that I had, even if it wasn't specifically related to their role in a project. My hope is that this work will serve to assist them throughout the process of finishing their degrees.

## **Table of Contents**

| CHA  | PTER 1  | INTRODUCTION                                                   | 1   |

|------|---------|----------------------------------------------------------------|-----|

| 1.1  | Overv   | iew of Power Management Integrated Circuits                    | 1   |

| 1.2  | Motiv   | ation for Silicon Carbide                                      | 4   |

| 1.3  | Thesis  | Structure                                                      | 6   |

| CHAI | PTER 2  | SILICON CARBIDE INTEGRATED CIRCUITS                            | 8   |

| 2.1  | Proper  | ties of Silicon Carbide                                        | 8   |

| 2.2  | Backg   | round on SiC ICs                                               | 9   |

| 2.3  | Rayth   | eon's HiTSiC® Process                                          | 10  |

| CHAI | PTER 3  | OVERVIEW OF CIRCUITS AND SYSTEMS                               | 13  |

| 3.1  | Linear  | Regulators                                                     | 13  |

| 3    | .1.1    | Operational Amplifiers                                         | 20  |

| 3    | .1.2    | Stability Criteria and Considerations                          | 35  |

| 3.2  | Switch  | ned Capacitor Converter                                        | 37  |

| 3    | .2.1    | Efficiency Considerations                                      | 42  |

| 3    | .2.2    | Control Logic and Supporting Circuitry                         | 44  |

| CHAI | PTER 4  | DESIGN AND SIMULATION                                          | 51  |

| 4.1  | Vulca   | n II Linear Regulator: Design and Analysis                     | 51  |

| 4    | .1.1    | Vulcan II Linear Regulator: Simulation Results and Test Setups | 60  |

| 4.2  | Fully ( | On-Chip Linear Regulators                                      | 65  |

| 4    | .2.1    | Operational Amplifiers                                         | 66  |

| 4    | .2.2    | Fully On-Chip NFET Pass Transistor Based Linear Regulator      | 97  |

| 4    | .2.3    | Fully On-Chip PFET Pass Transistor Based Linear Regulator      | 110 |

| 4.3  | Switch  | ned Capacitor Converter                                        | 122 |

| 4    | .3.1    | Low Power, Fully On-Chip Pre-Regulator                         | 127 |

| 4    | .3.2    | Dickson Charge Pump                                            | 128 |

| 4    | .3.3    | Level Shifters                                                 | 130 |

| 4    | .3.4    | Voltage-Controlled Oscillator                                  | 133 |

| 4    | .3.5    | Non-Overlapping Clock Generator                                | 138 |

| 4    | .3.6    | Digital Controller                                             | 141 |

| 4.         | .3.7   | Switched Capacitor Converter: Simulation Results | 145 |

|------------|--------|--------------------------------------------------|-----|

| 4.         | .3.8   | Switched Capacitor Converter: Optimizations      | 149 |

| CHAI       | PTER S | 5 CHIP FABRICATION AND TEST RESULTS              | 150 |

| 5.1        | Chip 1 | Fabrication, Packaging, and Test Setup           |     |

| 5.2        | Test F | Results                                          | 156 |

| CHAI       | PTER ( | 6 CONCLUSION AND FUTURE WORK                     | 168 |

| 6.1        | Concl  | usions and Contributions to the State of the Art | 168 |

| 6.2        | Future | e Work                                           | 169 |

| BIBL       | IOGRA  | APHY                                             | 171 |

|            |        | APPENDIX A 178                                   |     |

| <b>A.1</b> | Pytho  | on Script #1: Automated Reliability Testing      | 178 |

# **Table of Figures**

| Fig. 1.1. A generic diagram of a linear regulator.                                           | 2  |

|----------------------------------------------------------------------------------------------|----|

| Fig. 1.2. A generic diagram of a buck converter.                                             | 3  |

| Fig. 2.1. The cross-section of Raytheon's HiTSiC® process.                                   | 10 |

| Fig. 3.1 An LDO schematic based on a PFET pass transistor.                                   | 14 |

| Fig. 3.2. The schematic of a two-stage op-amp.                                               | 21 |

| Fig. 3.3. An indirect compensation technique for the two-stage op-amp.                       | 25 |

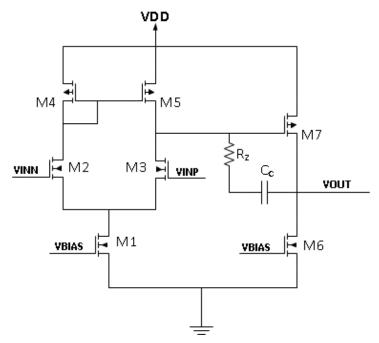

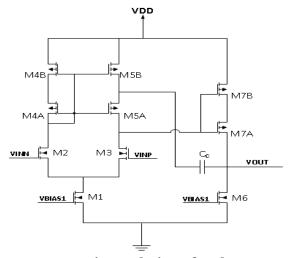

| Fig. 3.4. A rail-to-rail two-stage op-amp with indirect compensation                         | 26 |

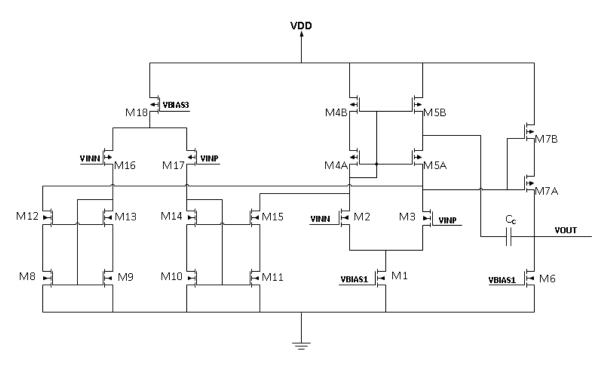

| Fig. 3.5. A conventional folded-cascode topology with an NFET input pair                     | 27 |

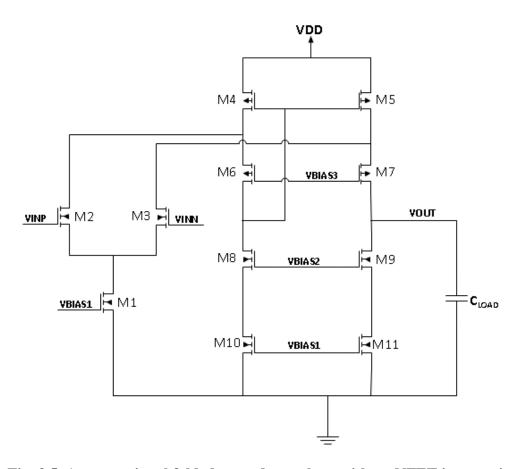

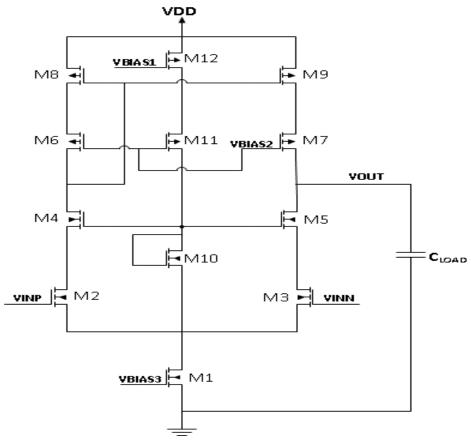

| Fig. 3.6. The schematic of a telescopic differential amplifier.                              | 31 |

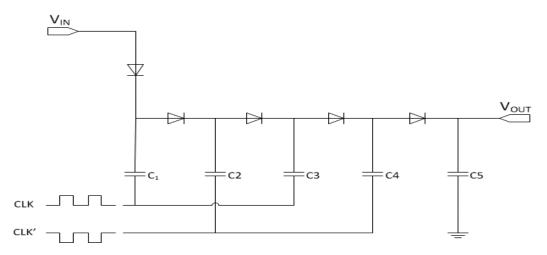

| Fig. 3.7. The schematic of a generic N-stage Dickson charge pump                             | 38 |

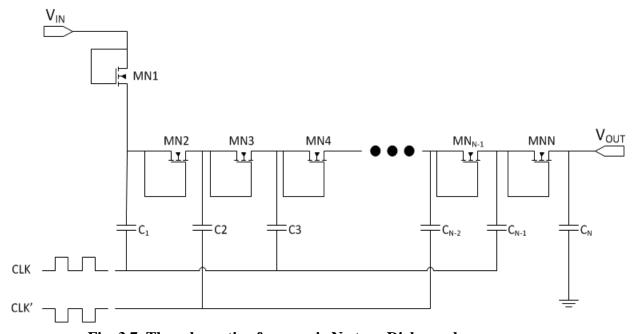

| Fig. 3.8. The schematic of a 2:1 step-down SC converter.                                     | 39 |

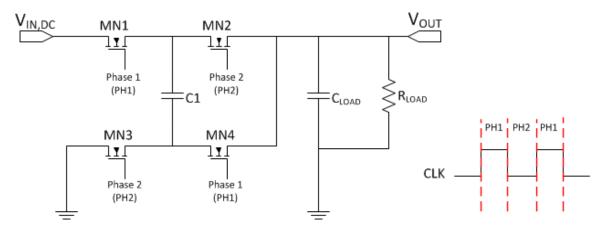

| Fig. 3.9. A schematic of a SC converter supporting 2:1 and 3:2 conversion ratios             | 41 |

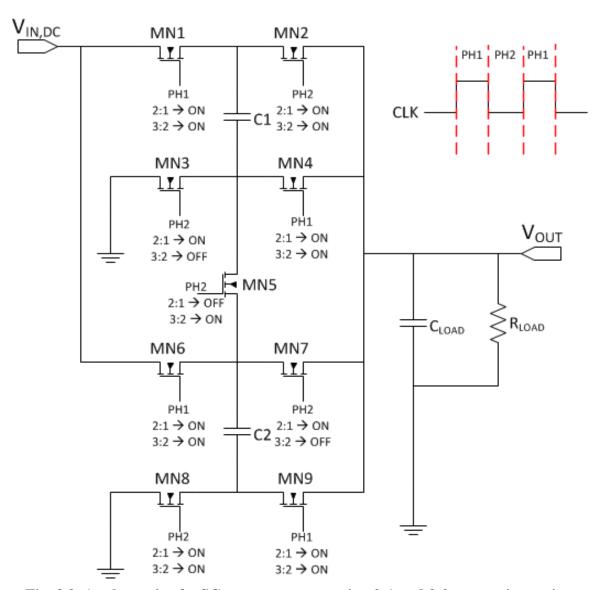

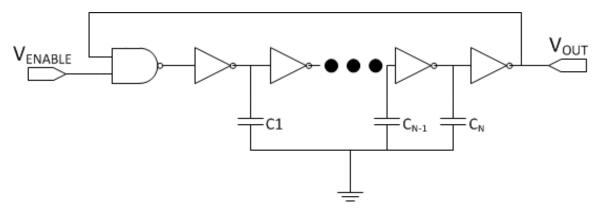

| Fig. 3.10. The schematic of the ring oscillator.                                             | 45 |

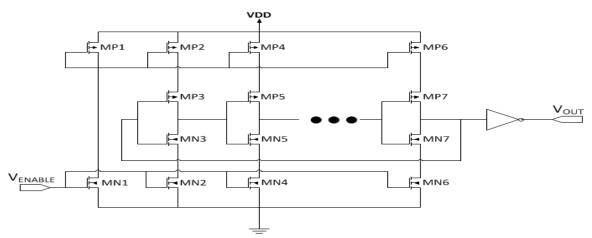

| Fig. 3.11. The schematic of the current-starved VCO.                                         | 45 |

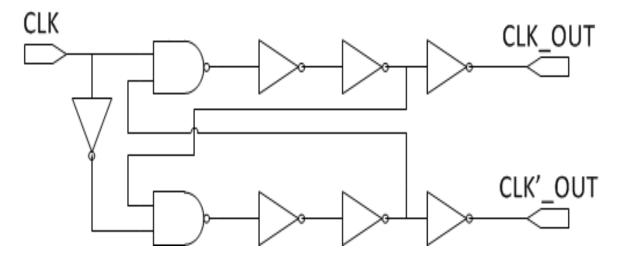

| Fig. 3.12. The schematic of the non-overlapping clock generator                              | 46 |

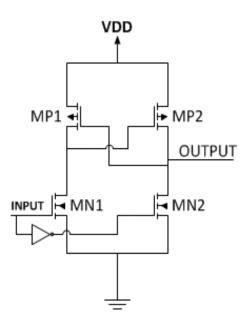

| Fig. 3.13. A schematic of a cross-coupled level shifter.                                     | 47 |

| Fig. 3.14. A level shifter utilizing a common source amplifier with an inverted input        | 48 |

| Fig. 3.15. A comparator with pre-amplification, decision, and output buffer stages           | 49 |

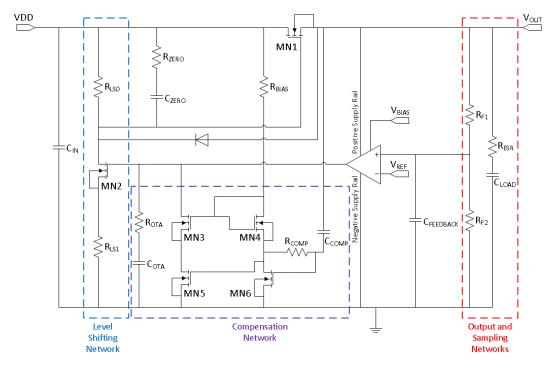

| Fig. 4.1. The schematic of the Vulcan II linear regulator.                                   | 52 |

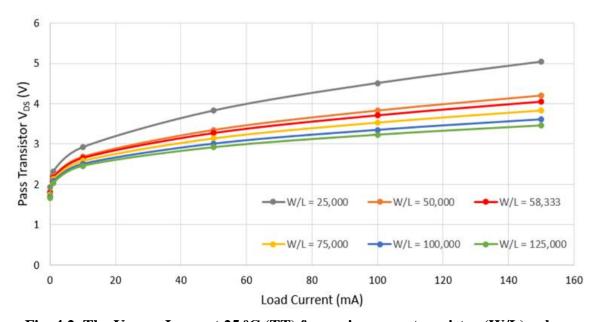

| Fig. 4.2. The $V_{DS}$ vs. $I_{LOAD}$ at 25 °C (TT) for various pass transistor (W/L) values | 54 |

| Fig. 4.3. The schematic of the two-stage op-amp used in the Vulcan II linear regulator       | 55 |

| Fig. 4.4. The AC test configuration for the Vulcan II linear regulator.                      | 62 |

| Fig. 4.5. The test configuration used to determine the Vulcan II linear regulator's power su  | pply  |

|-----------------------------------------------------------------------------------------------|-------|

| gain                                                                                          | 63    |

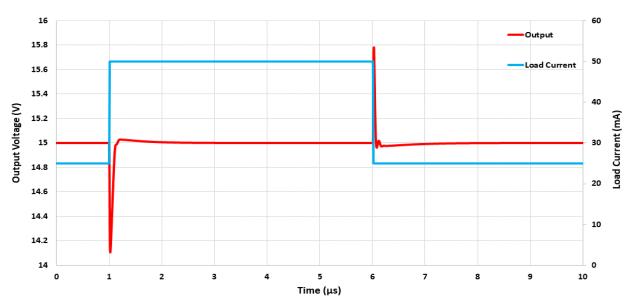

| Fig. 4.6. The PSRR simulation results of the Vulcan II linear regulator at 300 °C             | 64    |

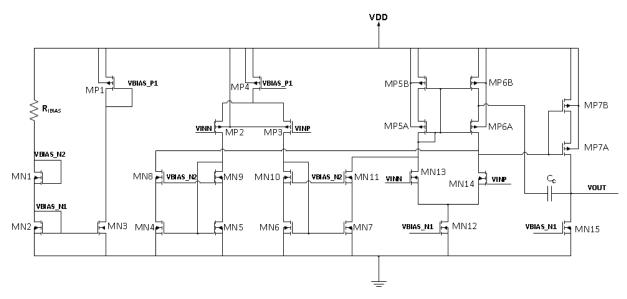

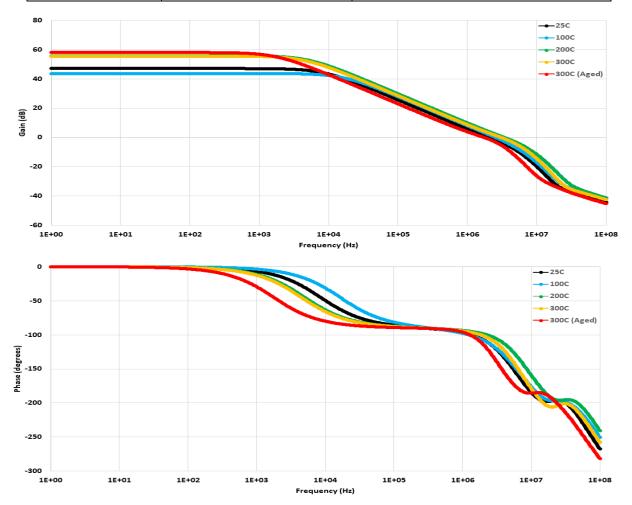

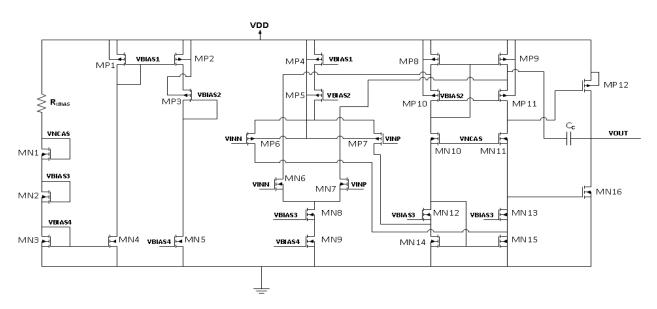

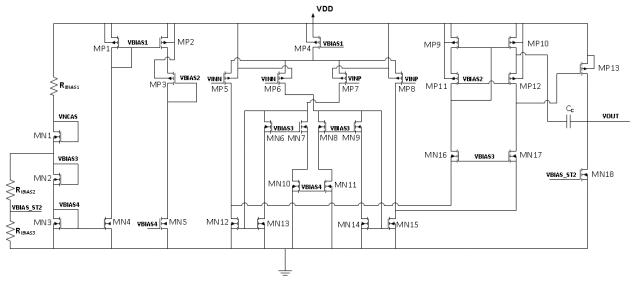

| Fig. 4.7. The rail-to-rail two-stage op-amp schematic with indirect compensation.             | 67    |

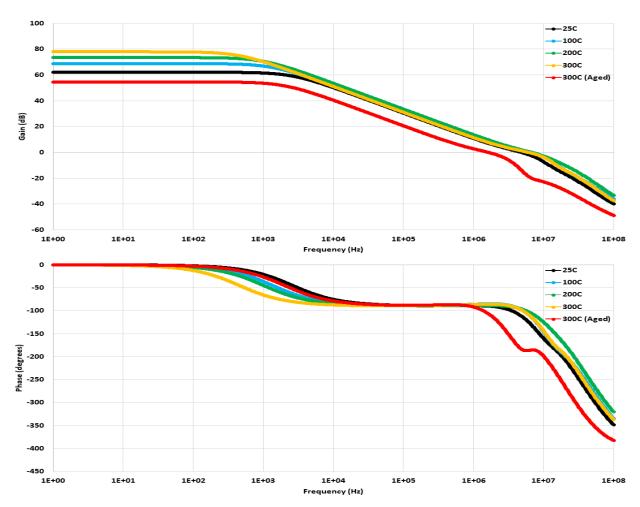

| Fig. 4.8. The frequency response of the two-stage op-amp shown in Fig. 4.7.                   | 68    |

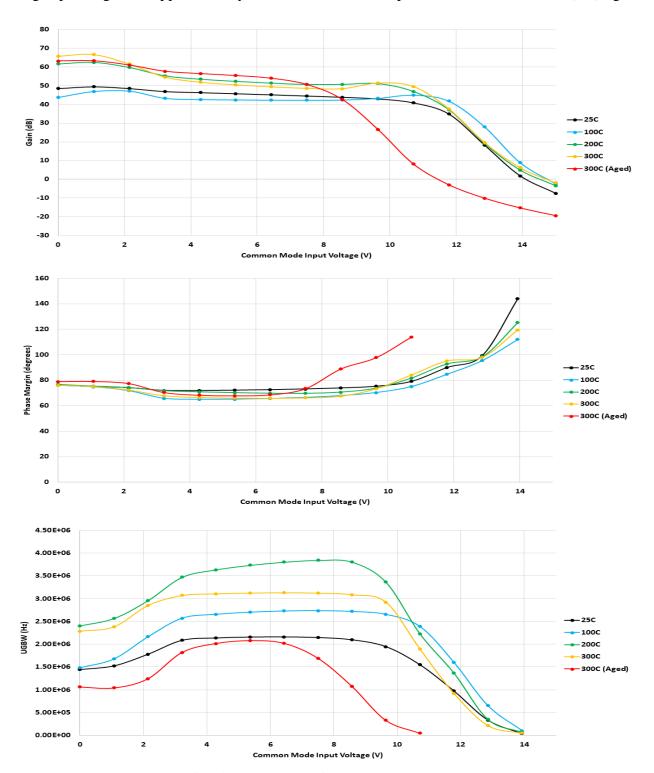

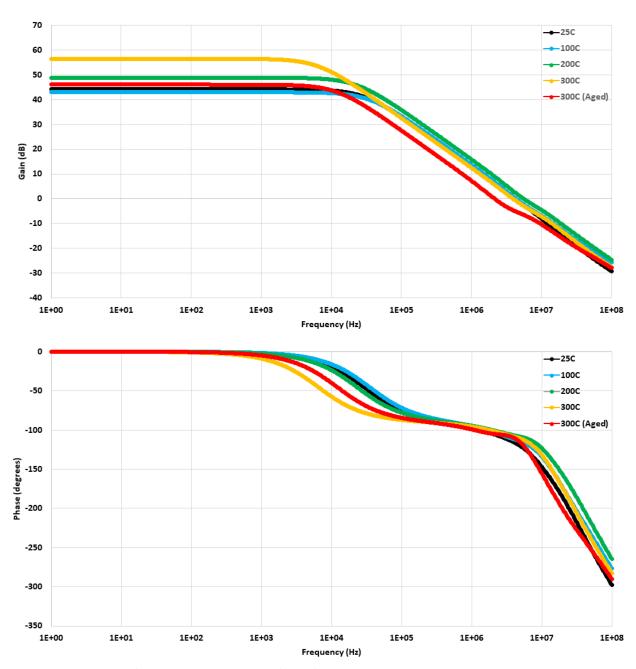

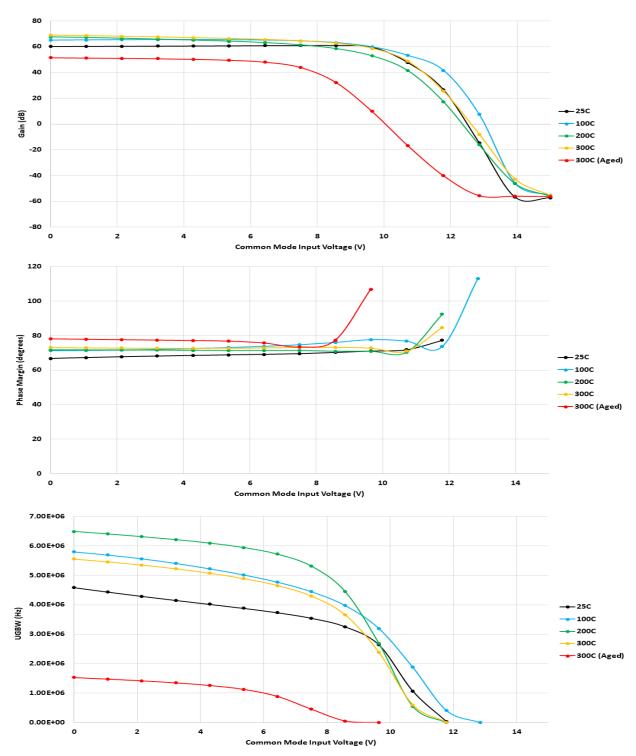

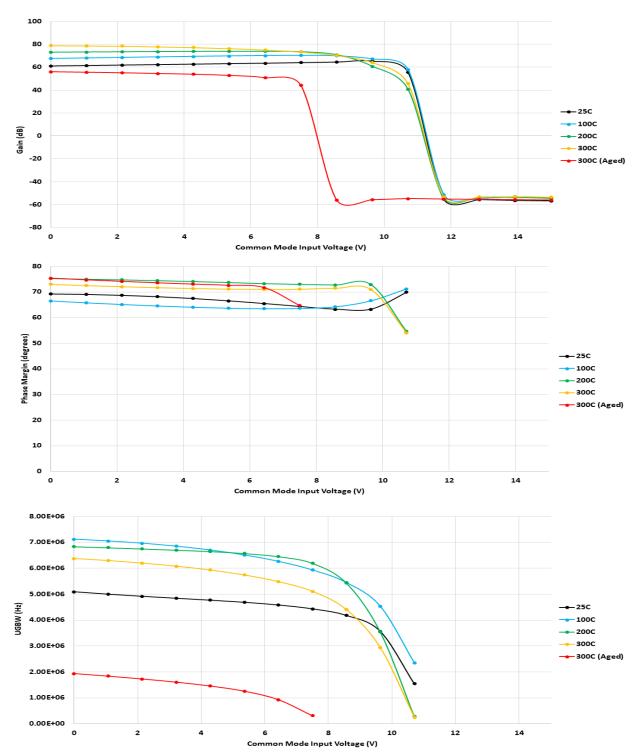

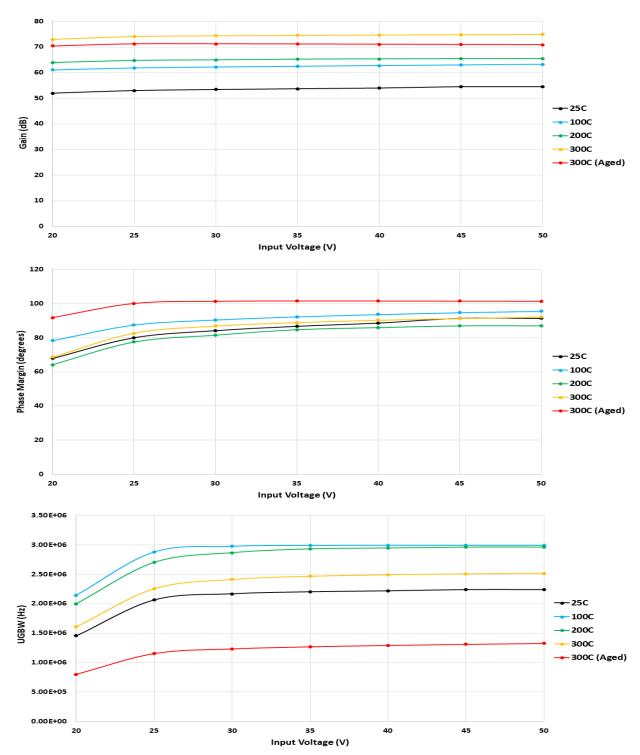

| Fig. 4.9. The open-loop DC gain, PM, and UGBW over temperature and a 0-15 V common n          | node  |

| input voltage for the two-stage op-amp with indirect compensation in Fig. 4.7.                | 69    |

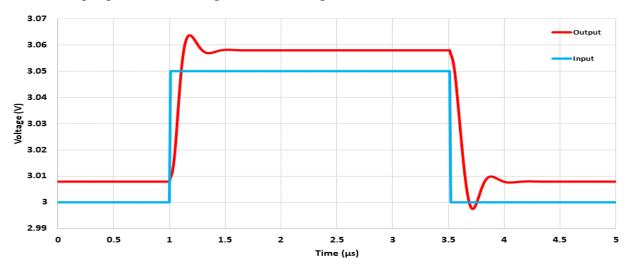

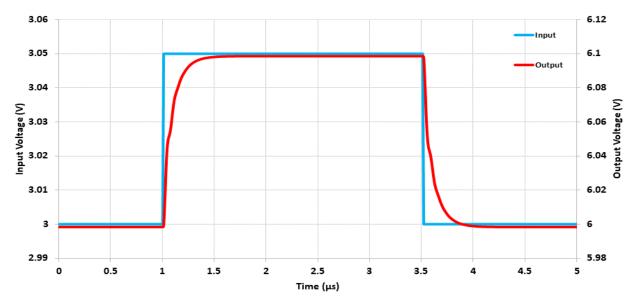

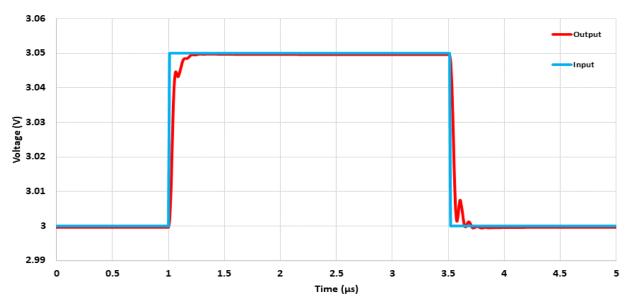

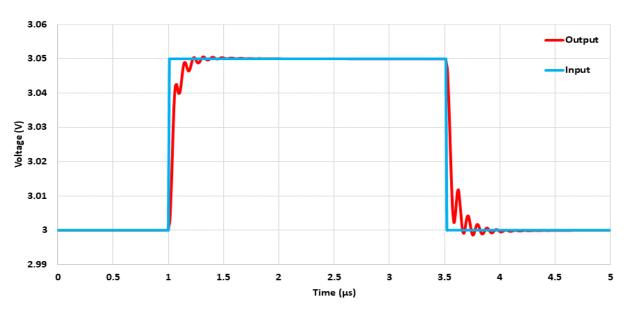

| Fig. 4.10. The transient response of the two-stage op-amp shown in Fig. 4.7 driving a 4.5 pF  | load  |

| at 300 °C (TF) for a 50 mV step input in a unity-gain configuration.                          | 70    |

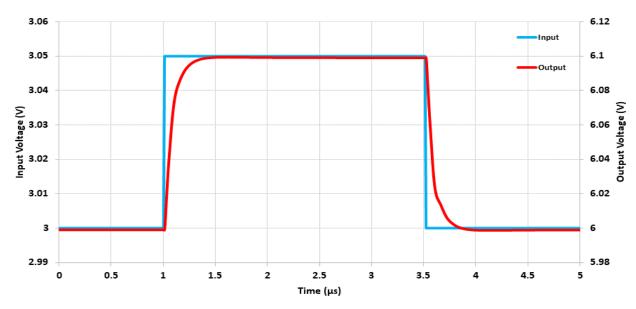

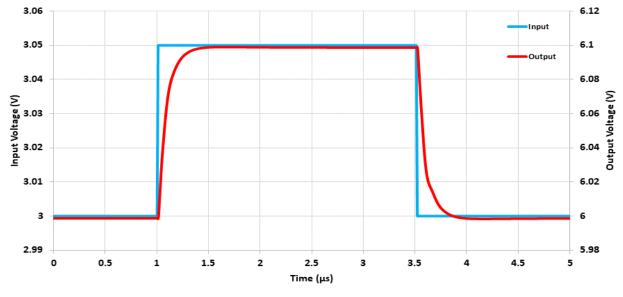

| Fig. 4.11. The transient response of the two-stage op-amp driving a 4.5 pF load at 300 °C (TF | ) for |

| a 50 mV step input in a non-inverting configuration.                                          | 72    |

| Fig. 4.12. The telescopic op-amp schematic with an output stage and indirect compensation     | 73    |

| Fig. 4.13. The frequency response of the telescopic op-amp shown in Fig. 4.12                 | 75    |

| Fig. 4.14. The open-loop DC gain, PM, and UGBW over temperature and a 0-15 V common n         | node  |

| input voltage for the telescopic op-amp with indirect compensation in Fig. 4.12               | 76    |

| Fig. 4.15. The transient response of the two-stage telescopic op-amp driving a 4.5 pF load at | 300   |

| °C (TF) for a 50 mV step input in a unity-gain configuration.                                 | 77    |

| Fig. 4.16. The transient response of the two-stage telescopic op-amp driving a 4.5 pF load at | 300   |

| °C (TF) for a 50 mV step input in a non-inverting configuration.                              | 77    |

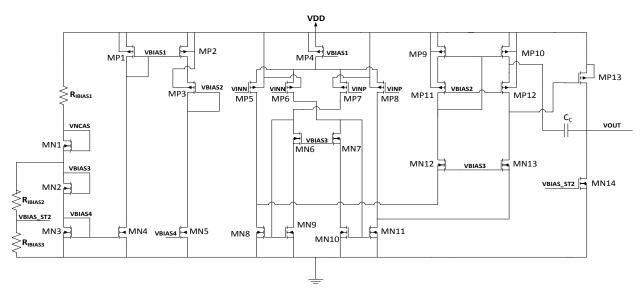

| Fig. 4.17. The modified traditional folded-cascode op-amp schematic with an output stage      | and   |

| indirect compensation.                                                                        | 78    |

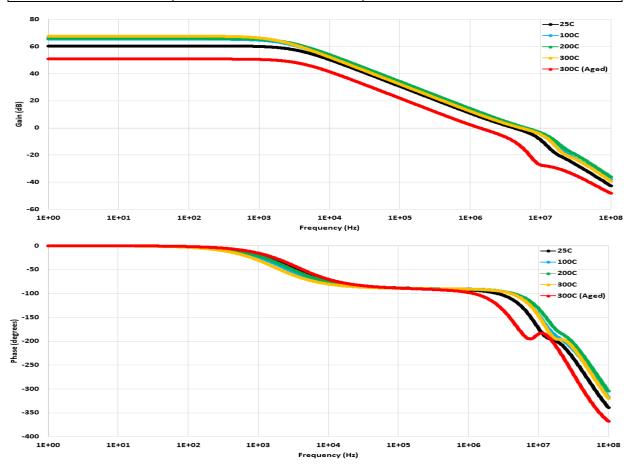

| Fig. 4.18. The frequency response of the folded-cascode op-amp shown in Fig. 4.17             | 80    |

| Fig. 4.19. The open-loop DC gain, PM, and UGBW over temperature and a 0-15 V common mode            |

|-----------------------------------------------------------------------------------------------------|

| input voltage for the folded-cascode op-amp with indirect compensation in Fig. 4.17 81              |

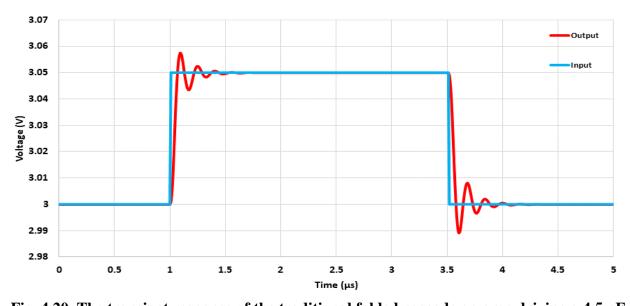

| Fig. 4.20. The transient response of the traditional folded-cascode op-amp driving a 4.5 pF load at |

| 300 °C (TF) for a 50 mV step input in a unity-gain configuration                                    |

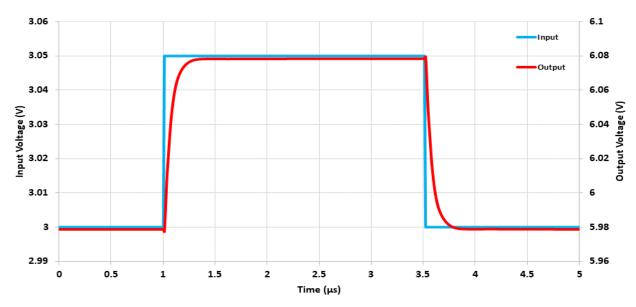

| Fig. 4.21. The transient response of the traditional folded-cascode op-amp driving a 4.5 pF load at |

| 300 °C (TF) for a 50 mV step input in a non-inverting configuration                                 |

| Fig. 4.22. The RFC op-amp schematic with an output stage and indirect compensation                  |

| Fig. 4.23. The frequency response of the recycling folded-cascode op-amp in Fig. 4.22               |

| Fig. 4.24. The open-loop DC gain, PM, and UGBW over temperature and a 0-15 V common mode            |

| input voltage for the recycling folded-cascode in Fig. 4.22                                         |

| Fig. 4.25. The transient response of the recycling folded-cascode op-amp driving a 4.5 pF load at   |

| 300 °C (TF) for a 50 mV step input in a unity-gain configuration                                    |

| Fig. 4.26. The transient response of the recycling folded-cascode op-amp driving a 4.5 pF load at   |

| 300 °C (TF) for a 50 mV step input in a non-inverting configuration                                 |

| Fig. 4.27. The multipath RFC op-amp schematic.                                                      |

| Fig. 4.28. The frequency response of the multipath RFC op-amp in Fig. 4.27                          |

| Fig. 4.29. The open-loop DC gain, PM, and UGBW over temperature and a 0-15 V common mode            |

| input voltage for the multipath RFC in Fig. 4.27                                                    |

| Fig. 4.30. The transient response of the multipath RFC driving a 4.5 pF load at 300 °C (TF) for a   |

| 50 mV step input in a unity-gain configuration. 93                                                  |

| Fig. 4.31. The transient response of the multipath RFC driving a 4.5 pF load at 300 °C (TF) for a   |

| 50 mV step input in a non-inverting configuration                                                   |

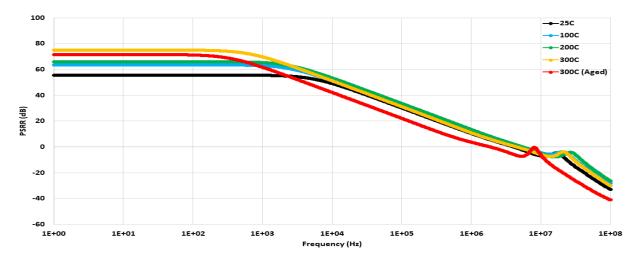

| Fig. 4.32. The PSRR of the multipath RFC over the operating temperature range96                     |

|                                                                                                     |

| Fig. 4.33. The CMRR of the multipath RFC over the operating temperature range                                     |

|-------------------------------------------------------------------------------------------------------------------|

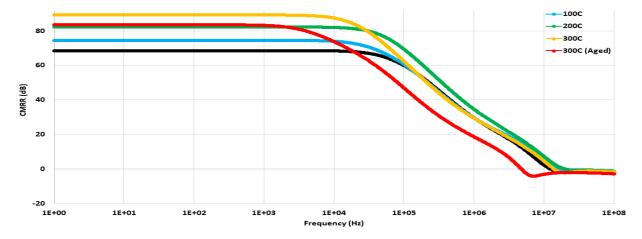

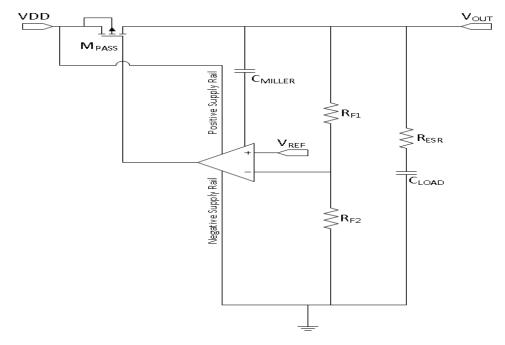

| Fig. 4.34. The schematic of the fully on-chip linear regulator with an NFET pass device 97                        |

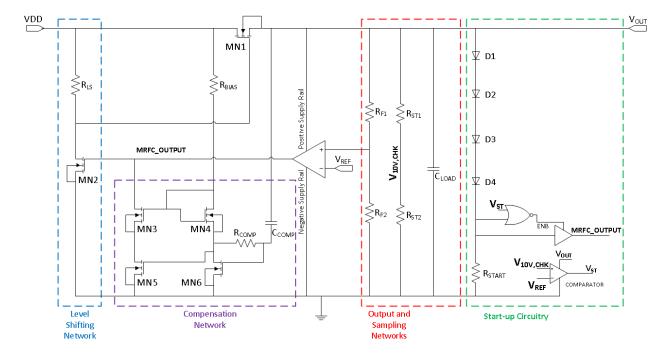

| Fig. 4.35. The frequency response of the fully on-chip NFET linear regulator for $V_{\rm IN}=20~V$ and            |

| $I_{LOAD} = 50 \text{ mA}$ across the operating temperature range                                                 |

| Fig. 4.36. The low-frequency gain, PM, and UGBW of the fully on-chip NFET linear regulator                        |

| with an $I_{LOAD} = 50$ mA across the temperature range                                                           |

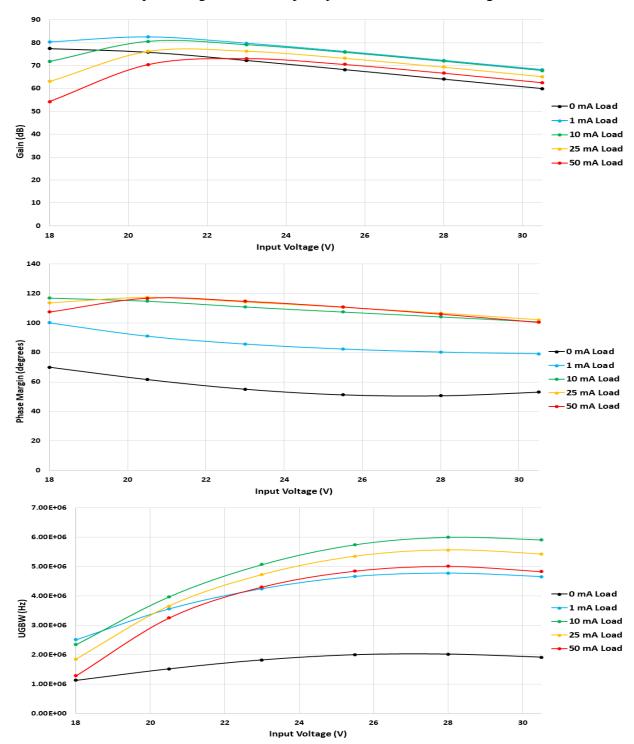

| Fig. 4.37. The low-frequency gain, PM, and UGBW of the fully on-chip NFET linear regulator for                    |

| various load currents over the input voltage range at 300 °C (TF).                                                |

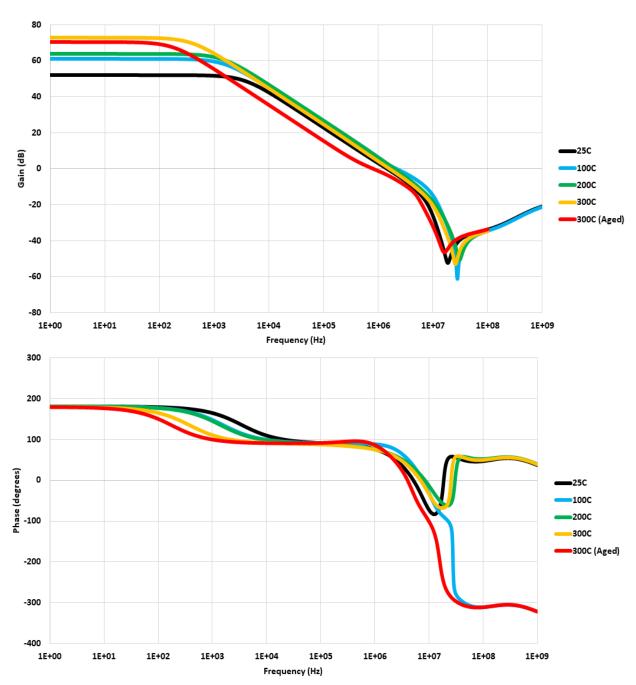

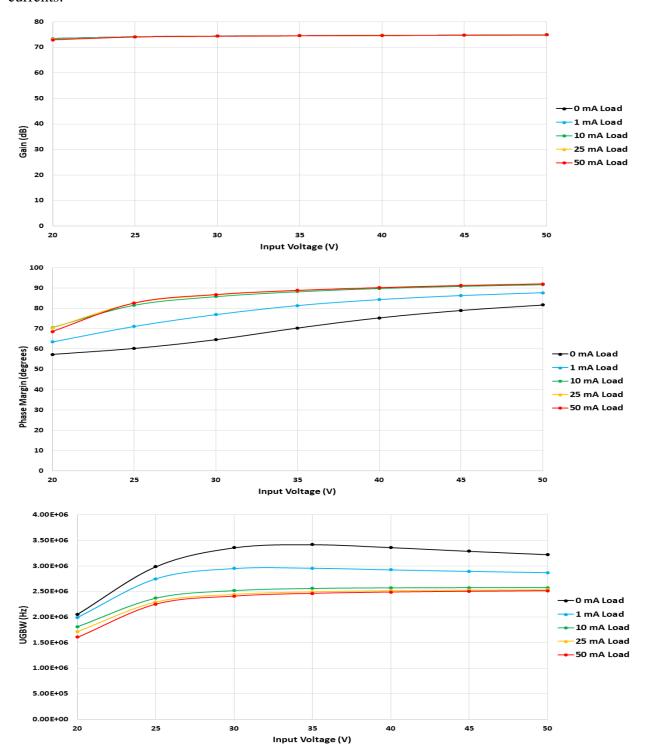

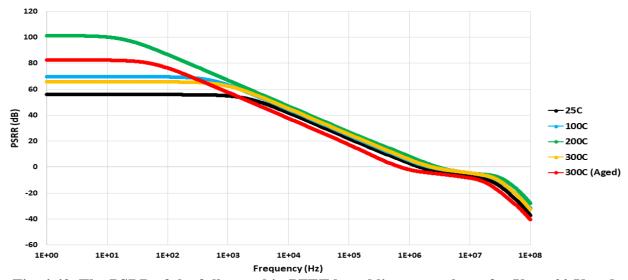

| Fig. 4.38. The PSRR of the fully-on chip linear regulator for $V_{\rm IN} = 25~V$ and $I_{\rm LOAD} = 50~mA$ over |

| the operating temperature range                                                                                   |

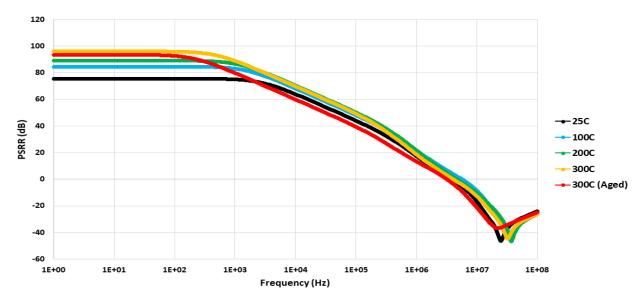

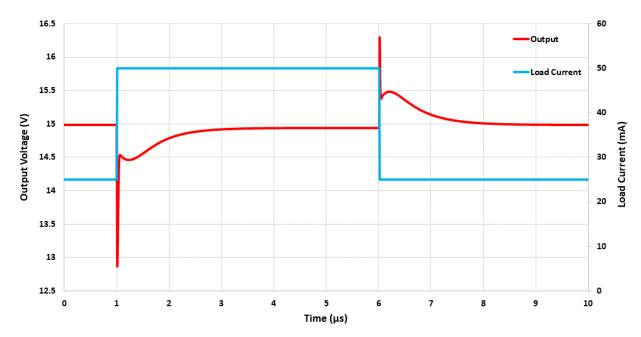

| Fig. 4.39. The transient response of the fully on-chip NFET linear regulator at 300 °C (TF) for $V_{\rm IN}$      |

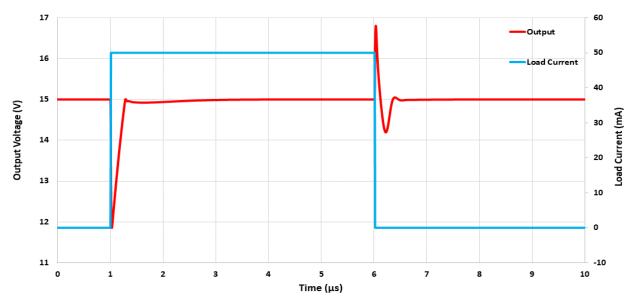

| = 25 V, a $I_{LOAD,CONT}$ = 25 mA, and a $I_{PULSE}$ = 25 mA                                                      |

| Fig. 4.40. The transient response of the fully on-chip NFET linear regulator at 300 °C (TF) for $V_{\rm IN}$      |

| = 25 V, a $I_{LOAD,CONT}$ = 0 mA, and a $I_{PULSE}$ = 50 mA                                                       |

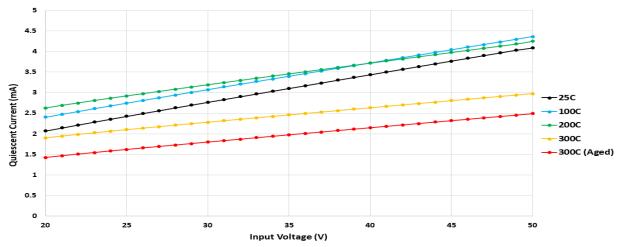

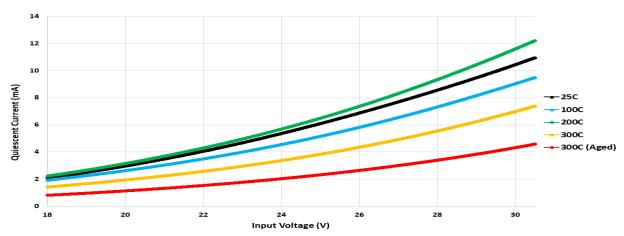

| Fig. 4.41. The quiescent current of the fully on-chip NFET based linear regulator for each operating              |

| temperature and an $I_{LOAD} = 0 \text{ mA}$                                                                      |

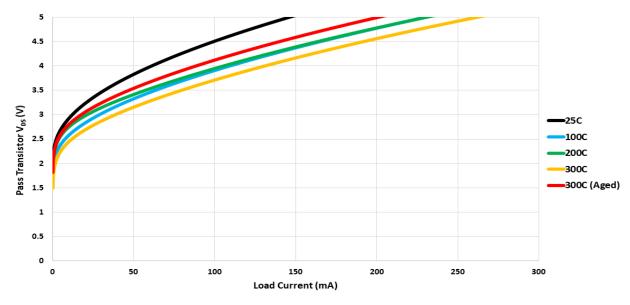

| Fig. 4.42. The dropout voltage $(V_{DS})$ of the fully on-chip linear regulator's NFET pass transistor            |

| over temperature                                                                                                  |

| Fig. 4.43. The schematic of the fully on-chip linear regulator with a PFET pass device 110                        |

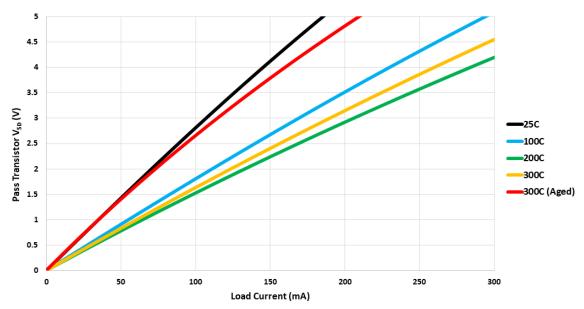

| Fig. 4.44. The dropout voltage $(V_{SD})$ of the fully on-chip linear regulator's PFET pass transistor            |

| over temperature for a W/L = 10,000 $\mu m  /  1.2 \; \mu m$                                                      |

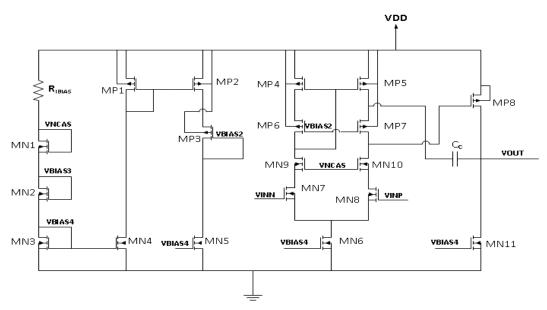

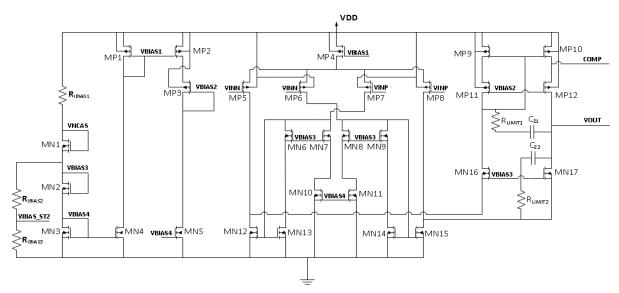

| Fig. 4.45. The multipath RFC op-amp schematic modified for the PFET linear regulator 112                          |

|                                                                                                                   |

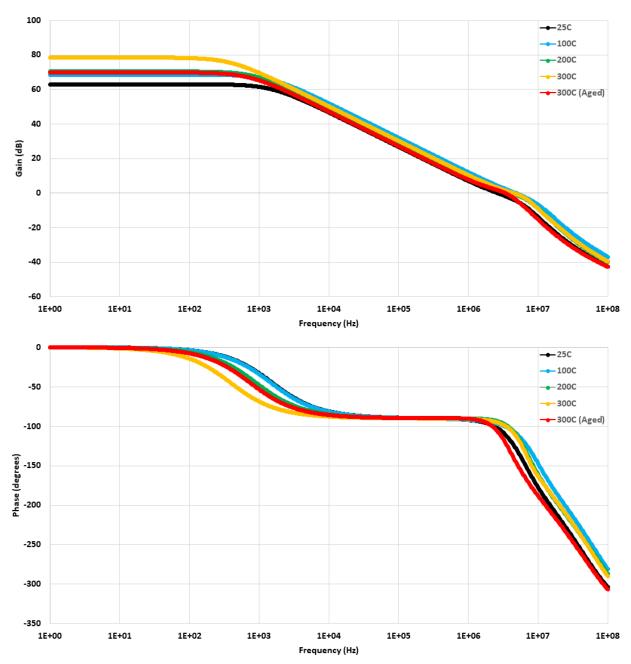

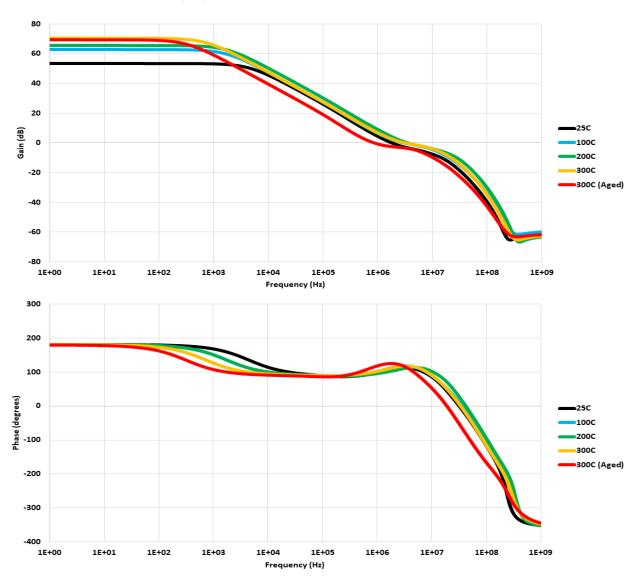

| Fig. 4.46. The frequency response of the fully on-chip PFET based linear regulator for $V_{\rm IN} = 20~V$        |

|-------------------------------------------------------------------------------------------------------------------|

| and I <sub>LOAD</sub> = 50 mA across the operating temperature range                                              |

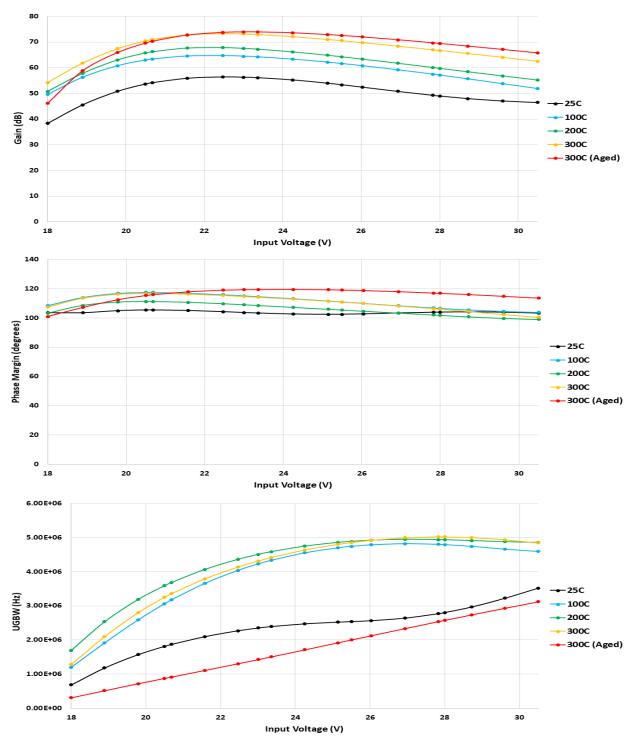

| Fig. 4.47. The low-frequency gain, PM, and UGBW of the fully on-chip PFET linear regulator                        |

| with an $I_{LOAD} = 50$ mA across the temperature range                                                           |

| Fig. 4.48. The low-frequency gain, PM, and UGBW of the fully on-chip PFET linear regulator for                    |

| various load currents over the input voltage range at 300 °C (TF)                                                 |

| Fig. 4.49. The PSRR of the fully-on chip PFET based linear regulator for $V_{IN} = 20 \text{ V}$ and $I_{LOAD} =$ |

| 50 mA over the operating temperature range                                                                        |

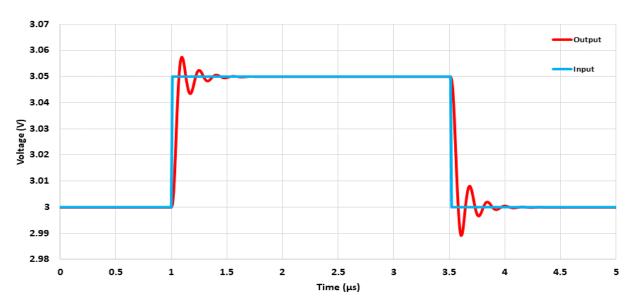

| Fig. 4.50. The transient response of the fully on-chip PFET linear regulator at 300 °C (TF) for $V_{\rm IN}$      |

| = 25 V, a I <sub>LOAD,CONT</sub> = 25 mA, and a I <sub>PULSE</sub> = 25 mA                                        |

| Fig. 4.51. The quiescent current of the fully on-chip PFET based linear regulator for each operating              |

| temperature and an $I_{LOAD} = 0$ mA. 121                                                                         |

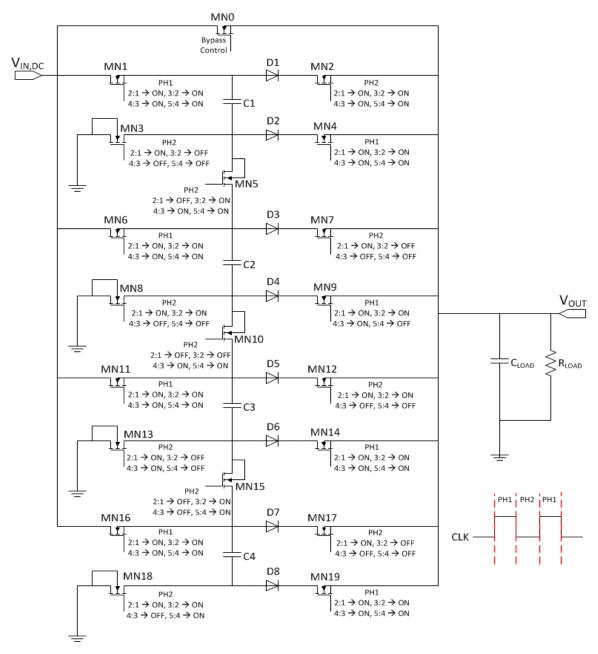

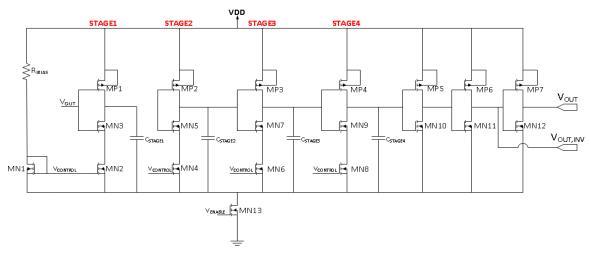

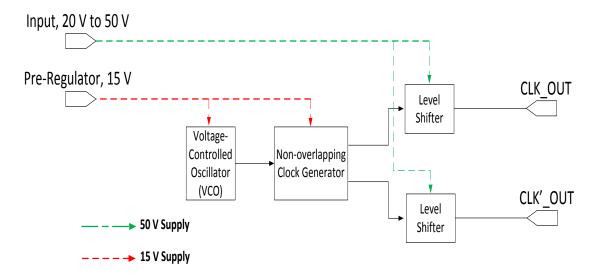

| Fig. 4.52. The top-level view of the reconfigurable switching converter                                           |

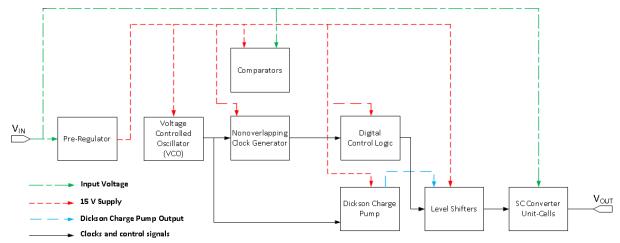

| Fig. 4.53. The block diagram of the reconfigurable SC converter                                                   |

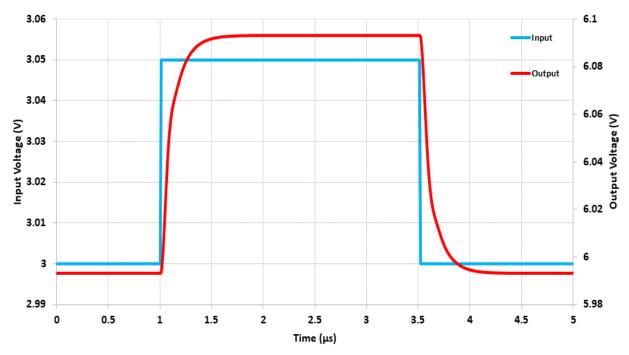

| Fig. 4.54. The pre-regulator's transient response - $I_{PULSE} = 50$ mA and $V_{IN} = 50$ V (300 °C) 127          |

| Fig. 4.55. The schematic of the 4-stage Dickson charge pump used in the SC converter 129                          |

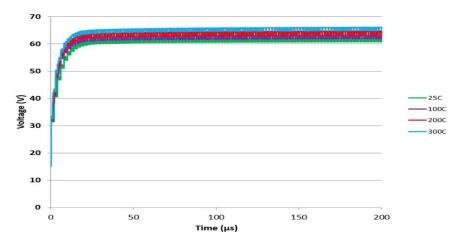

| Fig. 4.56. The simulated output voltage of the 4-stage Dickson charge pump                                        |

| Fig. 4.57. A schematic of a basic level shifter                                                                   |

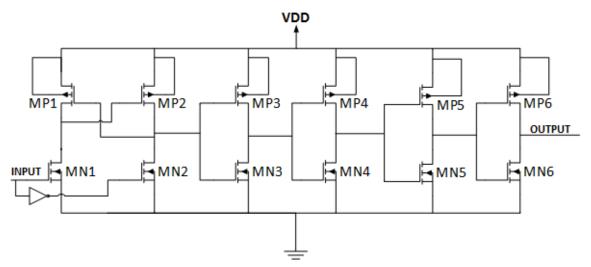

| Fig. 4.58. The level shifter used in the reconfigurable SC converter                                              |

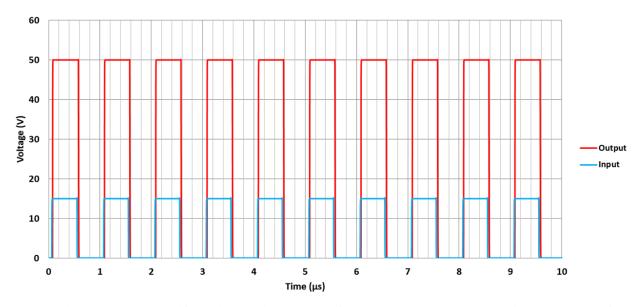

| Fig. 4.59. The level shifter simulation results for a 1 MHz square wave input at 300 °C (TF) 132                  |

| Fig. 4.60. The voltage-controlled oscillator used in the SC converter                                             |

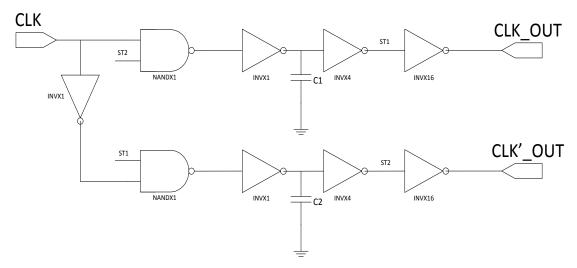

| Fig. 4.61. The schematic of the SC converter's non-overlapping clock generator                                    |

| Fig. 4.62. The test bench used for the SC converter's non-overlapping clock generator 140                         |

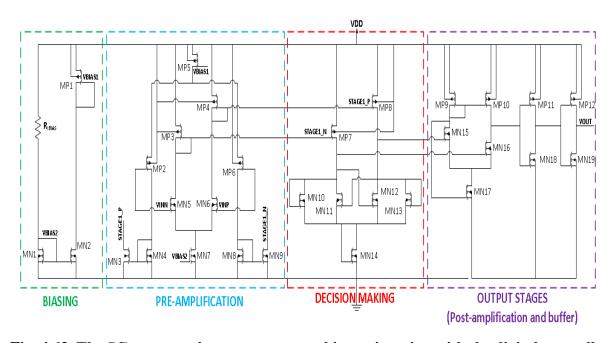

| Fig. 4.63. The SC converter's comparator used in conjunction with the digital controller 141                   |

|----------------------------------------------------------------------------------------------------------------|

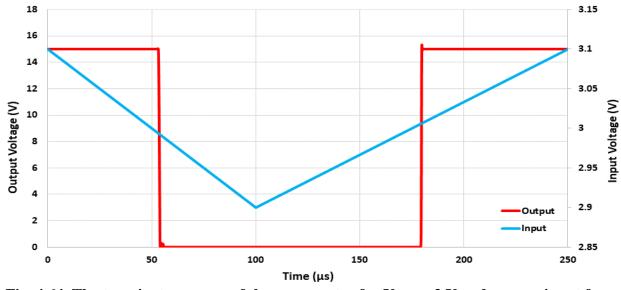

| Fig. 4.64. The transient response of the comparator for $V_{REF} = 3 \text{ V}$ and a ramp input from 2.9 V to |

| 3.1 V at 300 °C (TF)                                                                                           |

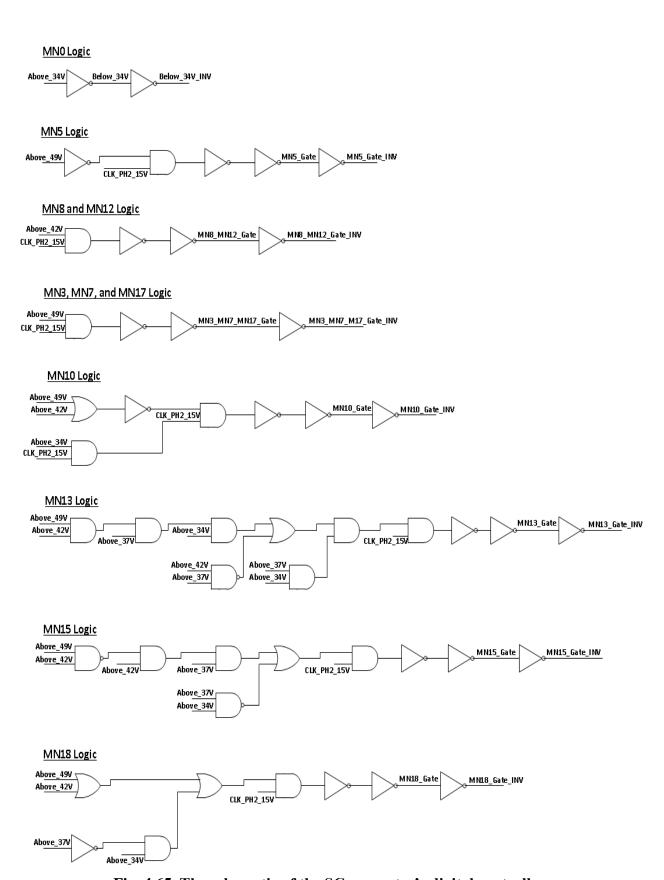

| Fig. 4.65. The schematic of the SC converter's digital controller                                              |

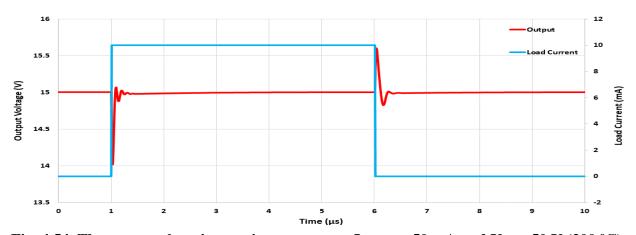

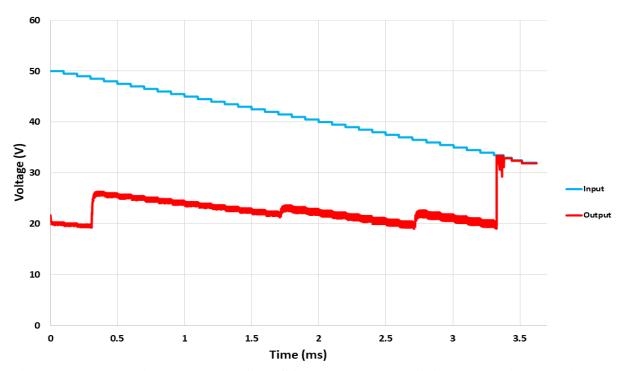

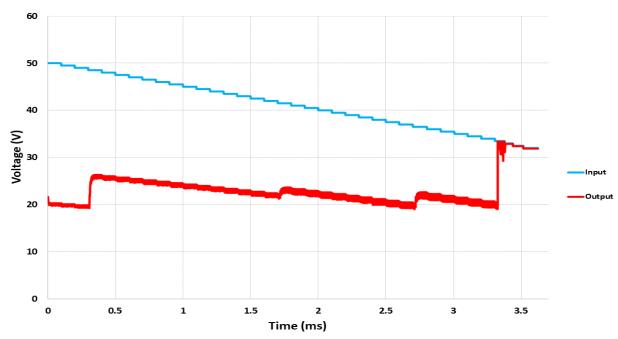

| Fig. 4.66. The transient response of the SC converter at 25 °C for NFETs in the unit-cells sized to            |

| be 20 $\mu m$ / 1.2 $\mu m$ (m = 25) and $I_{LOAD}$ = 50 mA.                                                   |

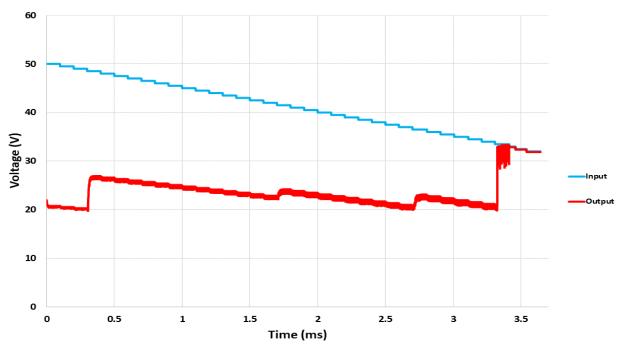

| Fig. 4.67. The transient response of the SC converter at 300 °C (TF) for NFETs in the unit-cells               |

| sized to be 20 $\mu m$ / 1.2 $\mu m$ (m = 25) and $I_{LOAD}$ = 50 mA                                           |

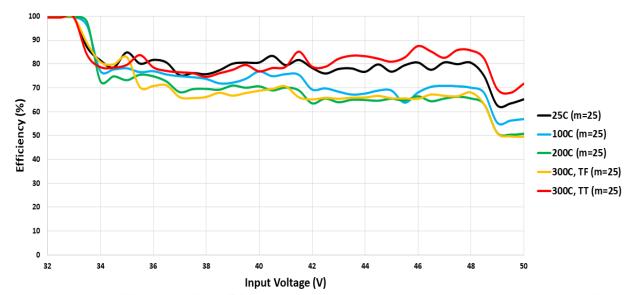

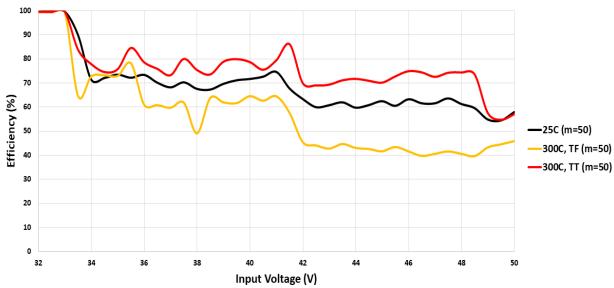

| Fig. 4.68. The efficiency of the SC converter across the operating temperature range for NFETs in              |

| the unit-cells sized to be 20 $\mu m$ / 1.2 $\mu m$ (m = 25) and $I_{LOAD}$ = 50 mA                            |

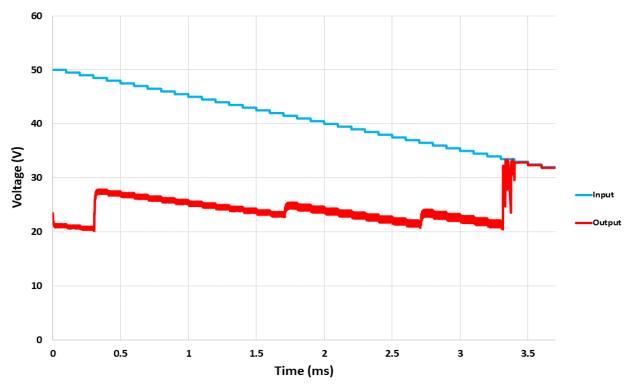

| Fig. 4.69. The transient response of the SC converter at 25 °C for NFETs in the unit-cells sized to            |

| be 20 $\mu m$ / 1.2 $\mu m$ (m = 50) and $I_{LOAD}$ = 50 mA. $\hfill 148$                                      |

| Fig. 4.70. The transient response of the SC converter at 300 °C (TF) for NFETs in the unit-cells               |

| sized to be 20 $\mu$ m / 1.2 $\mu$ m (m = 50) and $I_{LOAD}$ = 50 mA                                           |

| Fig. 4.71. The efficiency of the SC converter across the operating temperature range for NFETs in              |

| the unit-cells sized to be 20 $\mu m$ / 1.2 $\mu m$ (m = 50) and $I_{LOAD}$ = 50 mA                            |

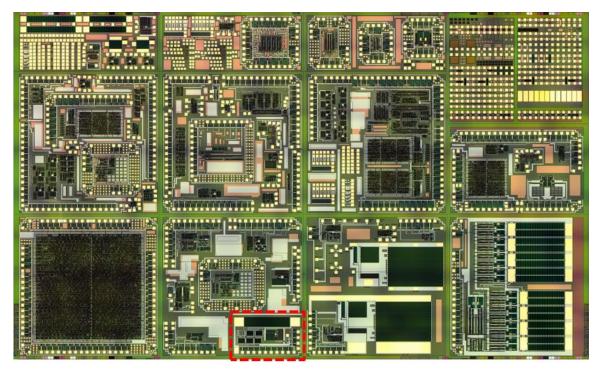

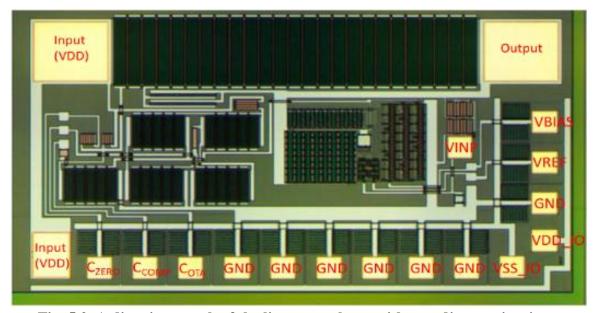

| Fig. 5.1. The complete die micrograph from the Vulcan II fabrication run. The linear regulator is              |

| highlighted in red                                                                                             |

| Fig. 5.2. A die micrograph of the linear regulator without adjacent circuitry                                  |

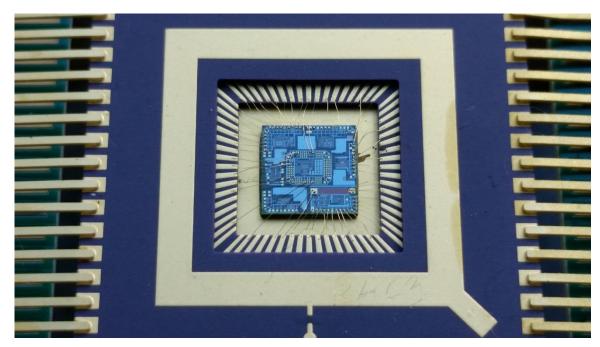

| Fig. 5.3. The diced linear regulator subsite die attached to the LDCC package with connections                 |

| formed by wirebonds                                                                                            |

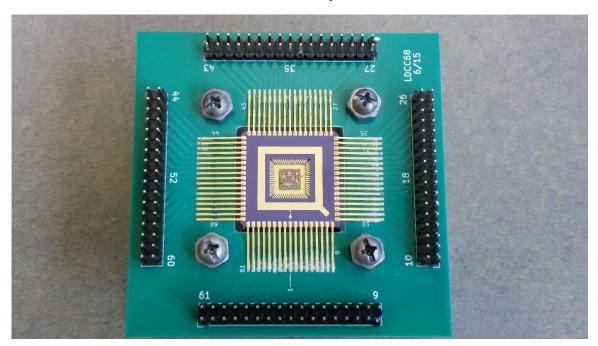

| Fig. 5.4. The LDCC package soldered onto the Rogers 4350 board                                                 |

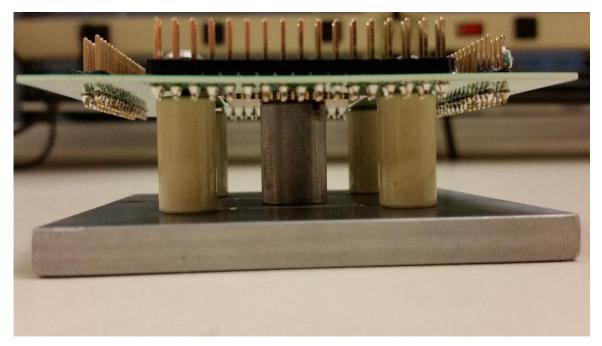

| Fig. 5.5. A side-view of the high temperature test fixture                                                     |

| Fig. 5.6. The breakout board created for characterizing the linear regulator                     |

|--------------------------------------------------------------------------------------------------|

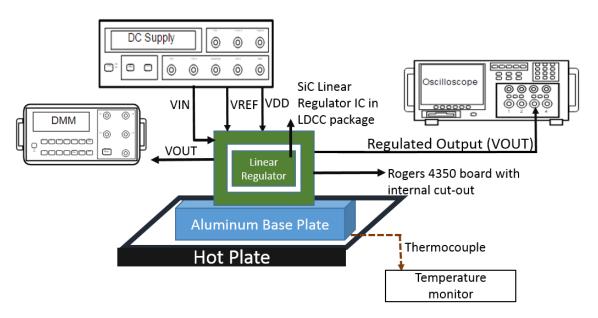

| Fig. 5.7. A block diagram for the linear regulator test setup                                    |

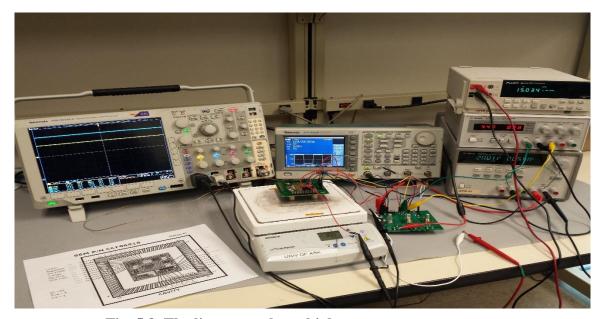

| Fig. 5.8. The linear regulator high temperature test setup                                       |

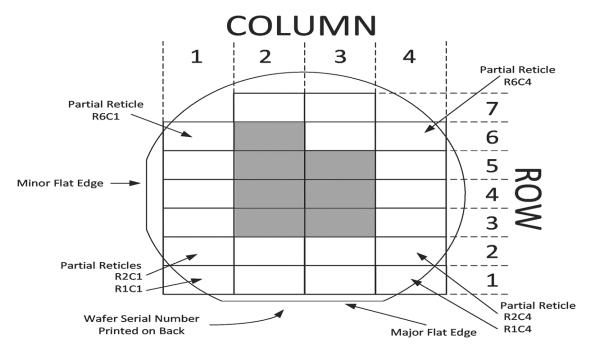

| Fig. 5.9. The wafer map with shaded cells indicating the tested reticles                         |

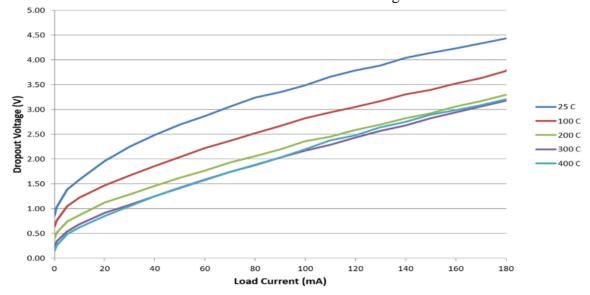

| Fig. 5.10. The dropout voltage of the linear regulator (R4C2 reticle)                            |

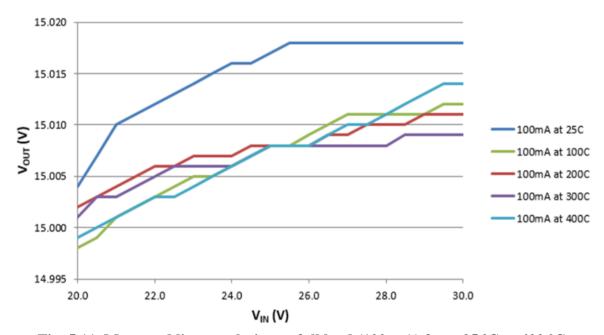

| Fig. 5.11. Measured line regulation at full load (100 mA) from 25 °C to 400 °C                   |

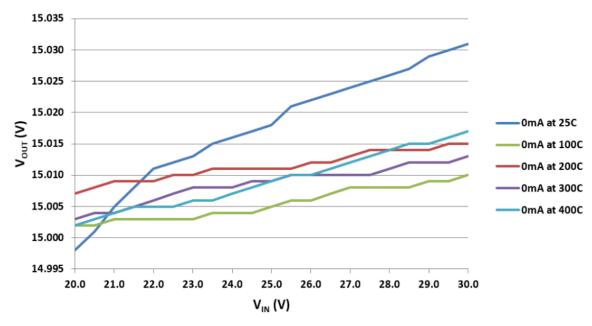

| Fig. 5.12. Measured line regulation with no load from 25 °C to 400 °C                            |

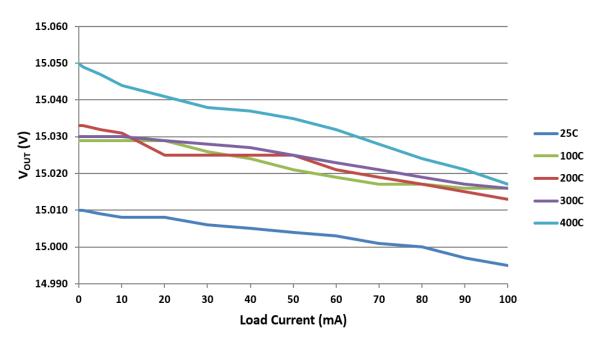

| Fig. 5.13. The measured load regulation over temperature for a 20 V input                        |

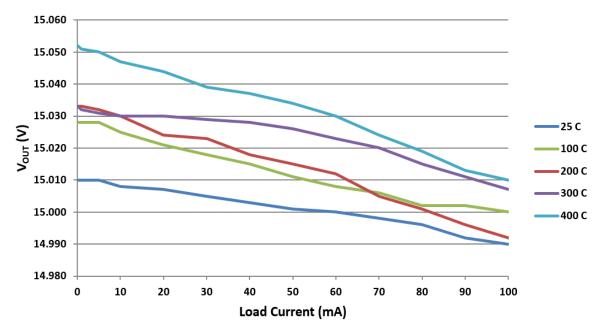

| Fig. 5.14. The measured load regulation over temperature for a 30 V input                        |

| Fig. 5.15. The measured quiescent current of the Vulcan II linear regulator over temperature and |

| input voltage                                                                                    |

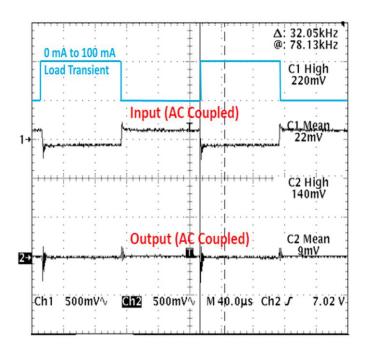

| Fig. 5.16. The 100 mA pulsed load test at 300 °C                                                 |

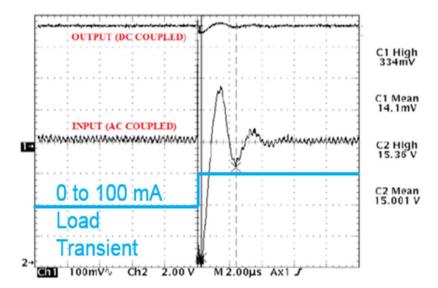

| Fig. 5.17. The 100 mA pulsed load test at 530 °C                                                 |

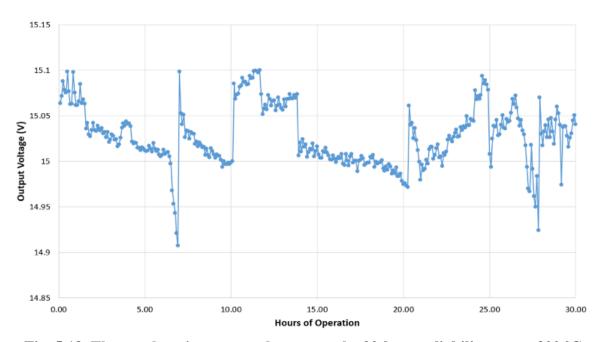

| Fig. 5.18. The regulator's output voltage over the 30-hour reliability test at 300 °C            |

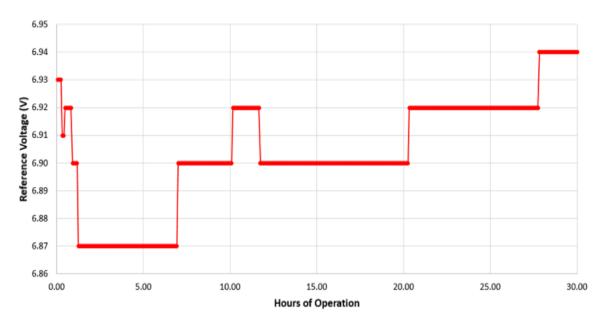

| Fig. 5.19. The reference voltage applied to the regulator throughout the reliability test 167    |

# **Table of Tables**

| Table 2.1. A comparison of silicon and wide bandgap semiconductor properties                      |

|---------------------------------------------------------------------------------------------------|

| Table 3.1. A comparison of the two-stage, folded-cascode, and telescopic topologies               |

| Table 4.1. Component sizing for the Vulcan II linear regulator                                    |

| Table 4.2. The simulation results for the Vulcan II linear regulator                              |

| Table 4.3. The device sizes for the two-stage op-amp shown in Fig. 4.7                            |

| Table 4.4. The device sizes for the telescopic op-amp shown in Fig. 4.12                          |

| Table 4.5. The device sizes for the traditional folded-cascode op-amp shown in Fig. 4.17 79       |

| Table 4.6. The devices sizes for the recycling folded-cascode schematic in Fig. 4.22              |

| Table 4.7. The devices sizes for the multipath RFC schematic in Fig. 4.27                         |

| Table 4.8. An op-amp performance comparison at 300 °C (TF)                                        |

| Table 4.9. The device sizes used in the fully on-chip NFET based linear regulator                 |

| Table 4.10. The line regulation of the fully on-chip NFET based linear regulator over temperature |

| for $V_{IN} = 20 \text{ V}$ to 50 V compared to TI's UA78L15 linear regulator                     |

| Table 4.11. The load regulation of the fully on-chip NFET based linear regulator over temperature |

| for $I_{LOAD} = 0$ mA to 50 mA compared to TI's UA78L15 linear regulator                          |

| Table 4.12. A summary of the fully on-chip NFET linear regulator and a comparison to silicon      |

| based parts                                                                                       |

| Table 4.13. The component sizes of the PFET based regulator                                       |

| Table 4.14. The load regulation of the fully on-chip PFET based linear regulator over temperature |

| for $I_{LOAD} = 0$ mA to 50 mA compared to TI's UA78L15 linear regulator                          |

| Table 4.15. The line regulation of the fully on-chip PFET based linear regulator over temperature |

| for $V_{IN} = 17.5 \text{ V}$ to 30 V compared to TI's UA78L15 linear regulator                   |

| Table 4.16. A summary of the fully on-chip PFET linear regulator and a comparison to silicon    |

|-------------------------------------------------------------------------------------------------|

| based parts                                                                                     |

| Table 4.17. The relevant device size changes made in the pre-regulator and multipath RFC 127    |

| Table 4.18. The sizes of the devices used in the level shifter presented in Fig. 4.58           |

| Table 4.19. The sizes of the devices used in the VCO presented in Fig. 4.58                     |

| Table 4.20. Simulation results of the low-frequency VCO from 25 °C to 300 °C                    |

| Table 4.21. Simulation Results of the high-frequency VCO from 25 °C to 300 °C                   |

| Table 4.22. The device sizes used in the high frequency VCO and Dickson charge pump 137         |

| Table 4.23. Device sizes for the SC converter's non-overlapping clock generator                 |

| Table 4.24. Simulation results for the non-overlapped clock generator from 25 °C to 300 °C 140  |

| Table 4.25. Device sizes for the comparator used in conjunction with the digital controller 142 |

| Table 5.1. The line regulation performance over temperature with 0 mA and 100 mA loads 160      |

| Table 5.2. A comparison of the measured and simulated values for line regulation with a 100 mA  |

| load                                                                                            |

| Table 5.3. The load regulation over temperature for input voltages of 20 V and 30 V             |

| Table 5.4. A comparison of the measured and simulated load regulation values over temperature   |

| for the 20 V case.                                                                              |

#### CHAPTER 1 INTRODUCTION

### 1.1 Overview of Power Management Integrated Circuits

Developing power management solutions to efficiently condition and regulate a power supply voltage has presented a continuing challenge to designers and researchers. The ubiquity of battery powered, portable devices such as smartphones and tablets has been a driving force behind efforts to improve power management designs. Motivating factors for the continued emphasis on power management circuitry include the demand for improving efficiency, decreasing response time to load transients, and reducing system footprint (e.g. moving to a system-on-chip solution).

Without a well-regulated supply voltage, applications with transient loads can experience undesirable performance variations or even fail to operate. In the case of smartphones, a combination of analog and digital circuitry is reliant upon a battery to supply the energy. However, a battery will not provide a consistent voltage throughout its charge/discharge cycle. Even within a relatively small time sample of this cycle, the clock dependent load transients of digital circuitry can cause a noticeable voltage swing from the battery. This is due in part to the battery chemistry and the corresponding internal resistance, which produces a voltage drop during the load transients.

The regulation of the battery voltage is accomplished with DC-DC converters, which can include a combination of linear regulators and switched-mode converters. Switched-mode converters encompass several different topologies, with the most common being the traditional buck (step-down) and boost (step-up) converters. More complex topologies include the single-ended primary-inductor converter (SEPIC) which offers the functionality of both the buck and boost converters.

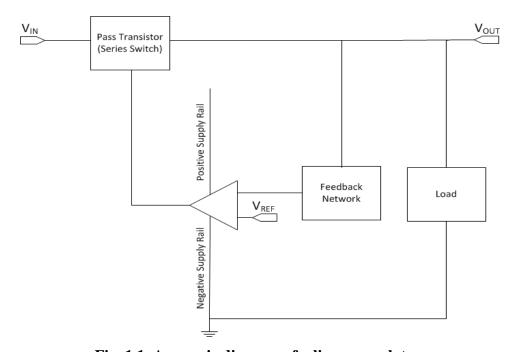

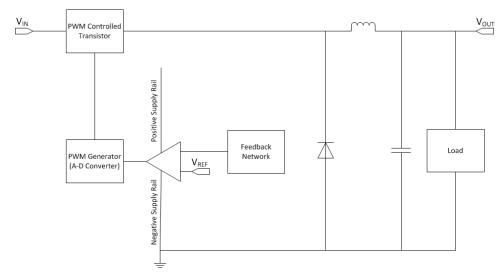

Linear regulators provide functionality similar to the buck converter by stepping down the supply voltage. The generic diagrams for a linear regulator and buck converter are illustrated in Fig. 1.1 and Fig. 1.2, respectively. One noticeable difference is the use of an inductor in the switched-mode converter. Although commonly used, an inductor is not required for all switching converter implementations. The inductor-less topologies are often referred to as "charge pumps" and while they generally do not have the same output current capabilities, a system-on-chip topology is made possible by eliminating the need for a discrete inductor.

An operational amplifier (op-amp) is used in both the linear regulator and switched-mode converter to compare the output voltage with a reference voltage. The difference between the reference and output voltages is amplified to give a control signal. The mixed-signal nature of the buck converter's feedback loop is one of the key differences between the switching converter and its linear regulator counterpart. The linear regulator functions by dynamically controlling the conductance of a series pass transistor with its feedback loop to obtain a desired output voltage.

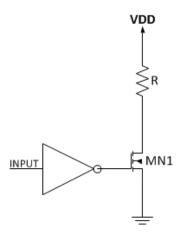

Fig. 1.1. A generic diagram of a linear regulator.

Fig. 1.2. A generic diagram of a buck converter.

On the other hand, the buck converter uses an op-amp in conjunction with a pulse-width-modulation (PWM) generator to control the switching transistor with a digital pulse-train.

Another major difference is that the buck converter can provide higher efficiency compared to the linear regulator. The linear regulator achieves a lower output voltage by dropping part of the input voltage across a pass transistor which results in wasted power proportional to the load current. A switched-mode converter stores energy in an ideally lossless inductor and capacitor during half of the switching cycle and discharges the stored energy during the other half of the cycle. Low-dropout linear regulators present a possible exception in regards to limited efficiency since the input voltage can be made close to the selected output voltage, reducing the voltage drop across the pass transistor and lowering the power loss.

Despite the potential for higher efficiency operation, there are multiple drawbacks to switched-mode operation that result in the linear regulator having inherent advantages. In addition to eliminating the need for a discrete inductor, linear regulators produce less noise and have lower response times. The reduction in noise is due to the linear regulator not having abrupt signals (i.e. a digital pulse-train) driving a power transistor which can inject noise into the output as is the case

for switch-mode converters. The slower response times of switched-mode converter topologies can be linked in part to the requirement of more components and the mixed-signal nature of the control scheme. Whereas the feedback network for a linear regulator topology consists primarily of an op-amp, switched-mode converters often require multiple mixed-signal blocks including a non-overlapping clock generator, pulse-width modulation generator, sawtooth waveform generator, and an op-amp.

The bandwidth of a switched-mode converter also limits its response times since it must be below the switching frequency. Although a higher switching frequency allows for higher bandwidth and smaller passive components, due to less energy storage requirements per cycle, the switching losses of the converter will increase. At higher switching frequencies, the high frequency noise component of the digital signals can also substantially impact the control circuitry and necessitate the use of filters. For these reasons, the switching frequency of switched-mode converters is typically between 20 kHz and 10 MHz. The feedback and compensation required to ensure stable operation further limit the regulator's bandwidth below the selected switching frequency.

#### 1.2 Motivation for Silicon Carbide

Traditional silicon process technologies have been unable to keep pace with the continued demand for increasing power density and operating temperature capabilities of commercial applications. Due to the maturity of silicon, it has become imperative to identify new semiconductor materials to allow for continued improvement. Silicon carbide's properties as a wide bandgap semiconductor material have enabled the development of power devices capable of lower switching losses along with higher temperature and voltage capabilities [1]. Although SiC power devices are commercially available, exploring their potential remains a focus within the

research community. Packaging continues to be one such area of research. While a SiC power MOSFET is theoretically capable of sustained operation at high temperatures, the materials the power module is composed of must also be fully capable of enduring the extreme operating environment. Similarly, the ability to achieve higher switching frequencies is dependent on the parasitic wiring inductances within the power module. Research teams are continuing to examine the optimal solders, wire bonding techniques, epoxies, and a host of other packaging related concerns.

Another barrier to unlocking the full potential of SiC power devices is the control and protection circuitries around the devices. The present solution is to use silicon and silicon-on-insulator (SOI) integrated circuitry, but these solutions are limited to approximately 125 °C and 250 °C before reliability concerns begin to arise [2], [3]. In order to withstand the extreme operating environments, heat sinks or cooling systems must be used with silicon based ICs. Both solutions are costly and result in larger system footprints. Given that the IC must be thermally isolated from the heat source, it also prohibits a complete module, or system-in-package, design. This ultimately becomes a detriment to the application by increasing parasitic elements due to longer wires while reducing system reliability as well as power density [4] – [6].

The demand for developing IC technology with operating temperature capabilities similar to SiC power devices has been a driving force behind current research efforts in SiC ICs. However, it is not the only motivating factor. Research efforts are currently underway to design stand-alone sensing and data acquisition ICs capable of operation beyond 300 °C. From a power management standpoint, literature has been published demonstrating the operation of linear regulators fabricated on SOI and all-NFET SiC processes at approximately 225 °C and 300 °C, respectively [7], [8]. Raytheon Systems Limited (RSL) has fabricated SiC CMOS ICs capable of operating at

temperatures exceeding 400 °C, representing a viable path towards creating more complex mixed-signal circuitry [9] – [11]. This work aims to present the design of SiC CMOS power management circuitry in the form of linear regulators and a switched capacitor converter, each of which can become a crucial building block for future mixed-signal solutions for high temperature applications.

#### 1.3 Thesis Structure

This thesis is organized into the following chapters.

- Chapter 1: Introduction A brief overview is presented for power management integrated circuits along with the motivation for silicon carbide devices and ICs.

- Chapter 2: Silicon Carbide Integrated Circuits The properties of silicon carbide are

briefly analyzed and characteristics of the Raytheon HiTSiC® CMOS process are

described. Publications detailing the successful fabrication and testing of SiC ICs are

reviewed.

- Chapter 3: Overview of Circuits and Systems A more detailed presentation of power

management integrated circuitry, specifically linear regulators and switched capacitor

converters, is given. Standard linear regulator topologies are described and the stateof-the-art switched capacitor converters are reviewed.

- Chapter 4: Design and Simulation The design process of the SiC CMOS linear regulators and switched capacitor converter is presented. Multiple operational amplifier topologies are examined for the linear regulators. The building blocks of the switched capacitor converter ranging from the digital controller to the voltage-controlled oscillator are described. The schematic and simulation results are provided for each of the circuits.

- Chapter 5: Chip Fabrication and Test Results The fabrication and test results of the

Vulcan II linear regulator are presented. Vulcan II is the codename for the University

of Arkansas's second fabrication with RSL, which is described in Chapter 2.

- Chapter 6: Conclusions and Future Work The conclusions from designing the linear regulators and switched capacitor converter are given along with recommendations for future work in integrated SiC CMOS technology.

#### CHAPTER 2 SILICON CARBIDE INTEGRATED CIRCUITS

## 2.1 Properties of Silicon Carbide

Wide bandgap semiconductor devices including GaN and SiC have inherent advantages over silicon (Si) in power electronics applications. The wide bandgap materials provide higher breakdown electric fields and greater thermal conductivity [6]. The development of power semiconductor devices using these materials has led to superior breakdown voltages, operation at higher junction temperatures, and lower switching losses.

A comparison between wide bandgap semiconductors and silicon is given in Table 2.1 [6], [12]. SiC is reported to have over 150 different polytypes, but research and commercialization has primarily focused upon 4H-SiC and 6H-SiC [6]. The breakdown, or critical, electric field of SiC is nearly 10 times that of silicon, making it an attractive solution for high voltage applications.

Table 2.1. A comparison of silicon and wide bandgap semiconductor properties.

| Material | Bandgap<br>Energy<br>Eg<br>(eV) | Intrinsic Carrier Concentration $n_i$ (cm <sup>-3</sup> ) | Relative Dielectric Constant $\epsilon_s$ | Electron<br>Mobility<br>$\mu_n$<br>$(cm^2/V*s)$ | Breakdown Electric Field E <sub>B</sub> (MV/cm) | Thermal Conductivity $\lambda$ (W/cm*K) |

|----------|---------------------------------|-----------------------------------------------------------|-------------------------------------------|-------------------------------------------------|-------------------------------------------------|-----------------------------------------|

| Si       | 1.1                             | $1.5 \times 10^{10}$                                      | 11.8                                      | 1350                                            | 0.3                                             | 1.5                                     |

| GaN      | 3.39                            | 1.9 x 10 <sup>-10</sup>                                   | 9.0                                       | 900                                             | 3.3                                             | 1.3                                     |

| 4H-SiC   | 3.26                            | 8.2 x 10 <sup>-9</sup>                                    | 9.76 <sup>a</sup><br>10.32 <sup>b</sup>   | 1020 <sup>a</sup><br>1200 <sup>b</sup>          | 2.2 <sup>a</sup><br>2.8 <sup>b</sup>            | 4.5                                     |

| 6H-SiC   | 3.02                            | 2.3 x 10 <sup>-6</sup>                                    | 9.66 <sup>a</sup><br>10.03 <sup>b</sup>   | 450 <sup>a</sup><br>100 <sup>b</sup>            | 1.7 <sup>a</sup><br>3.0 <sup>b</sup>            | 4.5                                     |

| Diamond  | 5.45                            | 1.6 x 10 <sup>-27</sup>                                   | 5.5                                       | 1900                                            | 5.6                                             | 20                                      |

Note: <sup>a</sup> – Perpendicular to c-axis, <sup>b</sup> – Parallel to c-axis.

As stated in Table 2.1, the thermal conductivity of SiC is three times greater than that of silicon. It should be noted that the thermal conductivity is reported to vary substantially across temperature in [12]. Despite the temperature dependency, SiC remains superior to Si with respect to thermal conductivity and is able to achieve higher operating temperatures.

In an application with a given voltage rating, the advantages of SiC allow power devices to be fabricated at a fraction of the size of silicon devices. The result is not only a smaller footprint with increased power density, but also the potential for lower switching losses. The material characteristics and advantages have led to the adoption of discrete SiC devices within the power electronics market. Nevertheless, the potential of SiC cannot be fully realized without the ability to place mixed-signal circuitry in the same module or package as the power device.

## 2.2 Background on SiC ICs

Driven by the motivation of developing a single module consisting of an integrated gate driver alongside the power device, research into SiC ICs began in the 1990s. The first literature reports of SiC ICs demonstrate the successful fabrication of building block analog and digital circuitry in 6H-SiC processes [13] – [16]. A gate driver was successfully designed and fabricated in 5  $\mu$ m 6H-SiC technology by 1999 [17], but manufacturing challenges ultimately led to the stagnation of research efforts in SiC IC technology while these fundamental concerns were addressed.

The manufacturing challenges pertaining to both SiC ICs and power devices are reported to be linked in part to trapped charges at the SiC/SiO<sub>2</sub> interface [18] – [20]. Literature suggests that charges become trapped in the oxide, leading to a reduction in mobility, threshold voltage instability, and ultimately performance degradation. Improvements to 4H-SiC manufacturing

techniques have lowered the change in mobility and threshold voltage by methods such as implanting nitrogen in the gate oxide prior to fabrication [21], [22].

Process improvements and production of discrete power devices as well as LEDs in 4H-SiC led to the development of Cree's 2 μm all-NFET 4H-SiC process. The successfully fabricated and tested circuits included a linear regulator and UVLO [8], [23]. General Electric has also reported operation of an all-NFET 4H-SiC technology at 500 °C [24]. Building block circuitry such as differential amplifiers and inverters have also been reported in 4H-SiC BJT, JFET, and MESFET technologies [25] – [27]. However, the inability to fabricate a 4H-SiC CMOS process with minimal defects has prevented the design of more complex and power efficient circuitry.

## 2.3 Raytheon's HiTSiC® Process

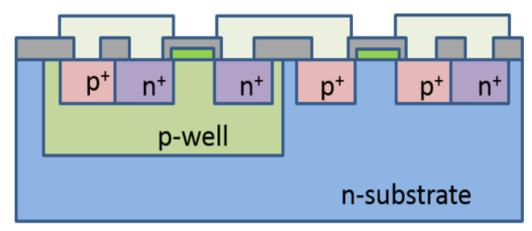

The 1.2 µm CMOS HiTSiC® process developed in 4H-SiC by Raytheon Systems Limited has provided a path towards designing more complex ICs. An n-type substrate is used in the process as shown in Fig. 2.1 [28]. NFETs are formed in isolated P-wells while PFETs are fabricated in the substrate without isolated N-wells. Due to the PFETs being fabricated in the substrate, the body connection of each PFET must be tied to the substrate. The n-type substrate must be connected to the highest voltage seen by the chip as a result of the p-n junctions between

Fig. 2.1. The cross-section of Raytheon's HiTSiC® process.

the n-type substrate, p-wells, and p+ regions for PFET drains/sources. If the n-type substrate is connected to a voltage less than the source of a PFET, then there is a risk of the formation of a forward biased diode. Another consequence of fabricating PFETs in the common n-type substrate is that body effect must be taken into consideration when cascoding PFETs.

The process utilizes a 40 nm thick gate oxide and incorporates a single metal layer for routing [28]. Two poly layers are available, both of which can be used to form resistors. One of the poly layers has a relatively low sheet resistance that makes it a possible second layer for routing. On-chip diodes and capacitors are also available in the process.

The target temperature for the HiTSiC® process was 400 °C. The initial circuits designed and fabricated by RSL were functional at 300 °C and demonstrated the potential for higher operating temperatures as the process matured [28], [29]. In cooperation with Ozark IC, the University of Arkansas Mixed-Signal Computer (MSCAD) Laboratory developed a process design kit (PDK) for the HiTSiC® process [30], [31].

During the first fabrication run with RSL, code named Vulcan I, isothermal BSIM3 models were created for 25 °C, 100 °C, 200 °C, and 275 °C using process control monitor (PCM) test structures provided by RSL. The silicon based temperature scaling built into the models necessitated making separate models at each of the selected temperatures. For each temperature, binned models were added for FET lengths of 1.2 μm, 2 μm, and 5 μm. Model corners were also provided to simulate the behavior of commonly observed process variation, described as slow, typical, and fast with respect to "typical" devices. The culmination of the effort in Vulcan I resulted in the fabrication of voltage and current references, an operational amplifier, a phase-locked-loop (PLL), as well as synchronous and asynchronous digital logic [31] – [33].

The second fabrication run, Vulcan II, coordinated between RSL and the University of Arkansas led to the fabrication of the linear regulator presented in Chapters 4 and 5 [34]. In Vulcan II, isothermal BSIM4 models replaced the use of BSIM3 models. The inability of BSIM3 models to properly characterize trapped charges at the SiC/SiO<sub>2</sub> interface and SiC based parameters such as carrier concentration were motivating factors for the transition.

Similar to Vulcan I, the BSIM4 models were binned at 25 °C, 100 °C, 200 °C, and 300 °C. Model corners were added as before to predict the effects of potential process variation and aging on performance. Slow (S), typical (T), and fast (F) corners were developed for both NFETs and PFETs at each temperature. For example, the TF model corner predicts the device performance based on typical NFETs and fast PFETs. Beyond the world's first integrated SiC CMOS linear regulator presented in this work, the circuits fabricated on Vulcan II included a comparator, a gate driver, an RS-485 transceiver, and digital circuitry [11], [35], [36].

The work presented in this thesis is designed for Raytheon's HiTSiC process using the BSIM4 models that have been developed. Additional SiC IC foundries exist and the work presented here will be applicable to those processes as well if the models and designs, specifically FET and passive sizes, are adjusted to account for different process related parameters.

#### CHAPTER 3 OVERVIEW OF CIRCUITS AND SYSTEMS

This chapter presents an overview of the circuits designed to form a power management solution in 4H-SiC. The top-level designs that will be detailed are linear regulators and a switched capacitor (SC) converter. The discussion will also extend to the lower-level circuitry required, such as operational amplifiers for linear regulators and digital control logic for switched capacitor converters.

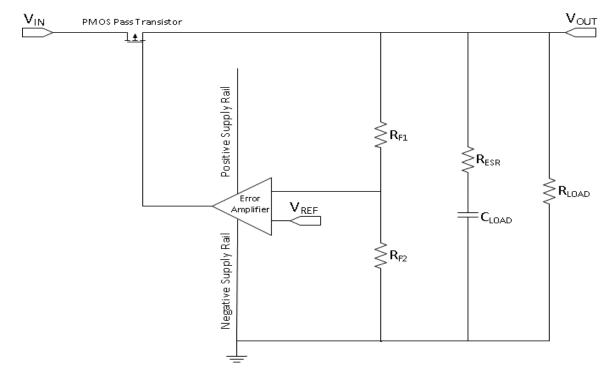

#### 3.1 Linear Regulators

The demands for eliminating the noisy output of switching converters and delivering a stable output under a variety of loading conditions while achieving a smaller footprint, particularly in system-on-chip applications, are factors behind the continued popularity of linear regulators. Linear regulators are commonly designed in a low-dropout (LDO) configuration with a PFET pass transistor to achieve greater efficiencies due to the supply voltage being closer to the selected output voltage. The dropout voltage indicates the supply voltage at which the linear regulator is no longer able to provide the output voltage target due to the minimum FET on-resistance.

The potential for improved efficiency with the LDO makes it popular in low power designs targeted towards portable, battery-powered applications. In cases where energy efficiency is less critical, high-bandwidth linear regulators with relatively high dropout voltages are alternative solutions. In either configuration, however, the efficiency is limited by the power dissipation across the pass transistor plus the regulator's quiescent current as expressed by (3.1).

$$Efficiency = \frac{P_{out}}{P_{in}} = \frac{P_{out}}{(V_{SUPPLY})(I_o + i_{LOAD})}$$

(3.1)

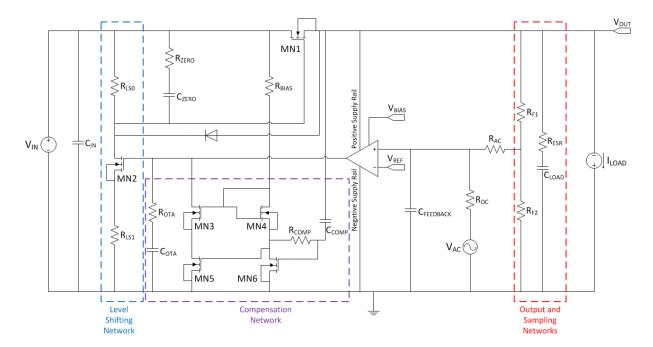

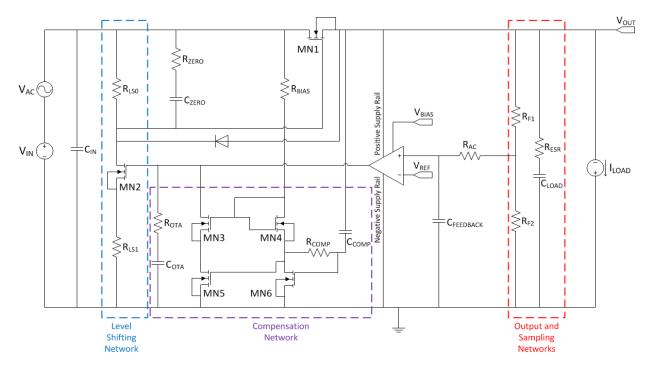

The power dissipation across the pass transistor is inherent to the linear regulator operation. The step-down voltage conversion is a result of the voltage drop across the pass transistor, which has a feedback loop dynamically controlling its channel resistance. The quiescent current,  $I_Q$ , is primarily due to the op-amp used within the feedback loop. To illustrate this more clearly, the basic schematic of an LDO is shown in Fig. 3.1. This topology has quiescent current flowing through the feedback network consisting of the feedback resistors  $R_{F1}$  and  $R_{F2}$  along with the opamp, which is commonly referred to as the error amplifier.

The feedback resistors sample the output voltage in a resistor divider and connect the sampled voltage to the error amplifier terminal. In the topology given in Fig. 3.1, the feedback voltage is connected to the non-inverting input terminal of the error amplifier while the inverting terminal is connected to the reference voltage. When the output voltage increases above a calculated threshold, the resistor divider will provide a voltage greater than the reference voltage

Fig. 3.1 An LDO schematic based on a PFET pass transistor.

to the non-inverting terminal of the error amplifier. This will cause the op-amp to provide an output voltage greater than zero, up to the positive supply rail, to the PFET pass transistor. As the  $V_{SG}$  of the pass transistor decreases, it will begin to shutoff and the output will fall back to the desired value.

Typically,  $R_{F1}$  and  $R_{F2}$  will be relatively large resistance values and will not significantly increase the quiescent current. This leaves the op-amp as the main source of quiescent current. The bandwidth of the linear regulator is heavily dependent on the op-amp's bandwidth, which increases with higher bias currents. This creates a tradeoff between the frequency response capabilities of the linear regulator and its quiescent current as well as maximum efficiency.

Due to the linear regulator's feedback loop, it is essential that the system remains stable. An open-loop phase shift of less than 180° at the frequency the linear regulator's gain crosses the 0 dB, or unity gain, point is needed for stability. Note that proper error amplifier operation also depends on the same stability criterion. Intuitively, the requirement of less than 180° of phase shift can be understood by the need to keep the system operating with negative feedback.

For example, the feedback loop will act to turn the PFET pass transistor off when the output voltage increases. If the closed-loop system has more than 180° phase shift, then an AC disturbance at the non-inverting input of the error amplifier will produce positive feedback and ultimately cause the system to oscillate. The error amplifier's output will be high during the negative half of the AC disturbance and will cause the output of the regulator to go low, which is considered positive feedback. Similarly, during the positive half of the AC disturbance the error amplifier's output will go low and increase the linear regulator's output voltage. The system is operating with positive feedback in both halves of the AC disturbance waveform, which causes the system to

continuously oscillate. When the system has negative gain, meaning it has transitioned below the 0 dB point, a phase shift of more than 180° is permissible since negative gain will negate the positive feedback.

There are two poles and one zero in the system shown in Fig. 3.1 that dictate the stability of the regulator. As will be discussed in the following sections, it is also possible to have relatively high frequency poles due to the op-amp topology selected and if a bypass capacitor is utilized. Regardless of additional poles, the potential of an unstable system exists with two poles and one zero. This is because each pole will provide a -20 dB/decade gain roll off and a phase shift of approximately -90° over two decades (starting one decade before and ending one decade after the pole location). Although not always the case, a zero is generally complementary to a pole in that it provides +20 dB/decade of gain and a phase shift of +90° over two decades. The system is therefore conditionally stable depending on the pole and zero locations since the total contribution of two poles is -180° of phase shift. To ensure stability, the zero location must be near to or lower than the second pole.

The first pole is formed by the output resistance of the PFET pass transistor along with the load capacitance and its associated equivalent series resistance (ESR). The expression for the first pole is given by (3.2) and it is typically the dominant pole in the system, although internally compensated regulators provide an exception.

$$f_{p1} = f_{3dB} = \frac{1}{2\pi(R_{o,pass} + R_{ESR})(C_{LOAD})}$$

(3.2)

The location of the second pole in the system is a function of the error amplifier's output resistance and the inherent capacitances of the pass transistor as expressed by (3.3).

$$f_{p2} = \frac{1}{2\pi (R_{0.EA})(C_{PassFET})}$$

(3.3)

Linear regulators commonly use a bypass capacitor that is generally an order of magnitude or lower than the load capacitance and has low ESR. It is placed between the output of the linear regulator and ground. The pole it forms is typically located beyond  $f_{p1}$  and  $f_{p2}$  due to  $C_{LOAD}$  being greater than  $C_{Bypass}$  and  $R_{o,EA}$  being much larger than  $R_{ESR}$ . The expression for the third pole associated with the bypass capacitor is given by (3.4).

$$f_{p3} = \frac{1}{2\pi (R_{ESR})(C_{Bypass})}$$

(3.4)

The zero is a result of the load capacitor's ESR. Although it is detrimental to the regulator's efficiency due to the power dissipation when the load capacitor is charging/discharging, it is beneficial for stability. If a bypass capacitor is used, then the zero will need to be either near the second pole or at a lower frequency. The location of the zero is determined by (3.5).

$$f_{z1} = \frac{1}{2\pi (R_{ESR})(C_{LOAD})}$$

(3.5)

Due to  $f_{p1}$  being dependent upon the output resistance of the pass transistor, there is a corresponding dependence of the pole's location on the amount of current passing through the PFET pass device. While in the saturation region, a MOSFET will have an output resistance given by (3.6).

$$r_o = \frac{1}{\lambda I_D} \tag{3.6}$$

The output resistance is therefore dependent upon the channel-length modulation parameter ( $\lambda$ ) and the current through the pass transistor. Equations (3.2) and (3.6) indicate the first pole location will be at higher frequencies when the load current is at its maximum value and at relatively low frequencies when the regulator is in the no-load condition. The value of R<sub>ESR</sub> for typical ceramic capacitors is only a few milliOhms, which allows the f<sub>p1</sub> location to extend out to

high frequencies that may be the same order of magnitude as  $f_{p2}$  or  $f_{p3}$  (if  $C_{Bypass}$  is used). It follows that the worst-case stability condition is for high load currents where  $f_{p1}$  begins to cluster around the other poles, because the gain will not start to roll off until high frequencies. The 0 dB point will extend out to higher frequencies, increasing the bandwidth of the regulator but decreasing its phase margin (i.e. the phase at the unity gain frequency) to the point of possible instability. For this reason, some applications may require the use of a discrete  $R_{ESR}$  resistor to minimize the movement of  $f_{p1}$ .

The open-loop gain of the system is the product of the gain provided by the pass transistor, the error amplifier, and the sampling network formed by  $R_{F1}$  and  $R_{F2}$ . The expression for the open-loop gain is given by (3.7), where the gain of the sampling network is given as (3.8).

$$A_{OL} = A_{PassFET} * A_{EA} * A_{Sampling}$$

(3.7)

$$A_{Sampling} = \frac{V_{REF}}{V_{OUT}} \tag{3.8}$$

Three of the fundamental linear regulator parameters that depend upon the open-loop gain are line regulation, load regulation, and power-supply rejection ratio (PSRR). Line regulation is defined as the change in output voltage for a given change in input voltage and is expressed in (3.9). This demonstrates the ability of the regulator to provide a constant output from a supply that may vary relatively slowly over time (not an AC disturbance).

$$Line Regulation = \frac{\Delta V_{OUT}}{\Delta V_{IN}}$$

(3.9)

Deriving the line regulation begins by solving for the change in output voltage as in (3.10).

$$\Delta V_{OUT} = (\Delta V_{IN}) \left( \frac{R_{LOAD}}{R_{ds,pass} + R_{LOAD}} \right) - (\Delta I_{LOAD}) \left( R_{LOAD} \right)$$

(3.10)

The expression for the change in load current is given in (3.11).

$$\Delta I_{LOAD} = (A_{PassFET})(A_{EA})(\Delta V_{OUT})(\frac{R_{F2}}{R_{E1} + R_{E2}})(\frac{1}{R_{Ougs}})$$

(3.11)

Substituting (3.11) into (3.10) results in (3.12). The expression in (3.12) can be rearranged into (3.13), then the line regulation can be approximated as in (3.14).

$$\Delta V_{OUT} = \frac{(\Delta V_{IN})(R_{LOAD})}{R_{ds,pass} + R_{LOAD}} - (A_{PassFET})(A_{EA})(\Delta V_{OUT})(\frac{R_{F2}}{R_{F1} + R_{F2}})(\frac{1}{R_{o,pass}})(R_{LOAD})$$

(3.12)

$$\Delta V_{OUT} \left[ 1 + (A_{PassFET})(A_{EA}) \left( \frac{R_{F2}}{R_{F1} + R_{F2}} \right) \left( \frac{1}{R_{o,pass}} \right) (R_{LOAD}) \right] = \frac{(\Delta V_{IN})(R_{LOAD})}{R_{ds,pass} + R_{LOAD}}$$

(3.13)

Line Regulation

$$\approx \frac{\Delta V_{OUT}}{\Delta V_{IN}} = \frac{1}{R_{ds,pass} + R_{LOAD}} * \frac{R_{o,pass}}{(A_{PassFET})(A_{EA})(\frac{R_{F2}}{R_{F1} + R_{F2}})}$$

(3.14)

Improving the line regulation performance is dependent upon increasing the system's openloop gain. It should be noted that the line regulation derivation neglects the voltage reference's drift over temperature. The voltage reference also commonly uses the unregulated input as its supply voltage and will vary slightly with a change in supply.

The regulator's load regulation is defined as the change in output voltage for a given change in output current and is expressed by (3.15).

$$Load Regulation = \frac{\Delta V_{OUT}}{\Delta I_{IOAD}}$$

(3.15)

The change in output current is determined by the system's open-loop gain and is given by (3.11). The change in output voltage given by (3.16) assumes that the feedback resistor values in the sampling network are much larger than the load resistance and that the input voltage is constant. The combination of the two expressions yields (3.17) as the load regulation.

$$\Delta V_{OUT} = (\Delta I_{LOAD})(R_{LOAD}) \tag{3.16}$$

Load Regulation =

$$\frac{\Delta V_{OUT}}{\Delta I_{LOAD}} = \frac{R_{o,pass}}{(A_{PassFET})(A_{EA})(\frac{R_{F2}}{R_{F1} + R_{F2}})}$$

(3.17)

Equation (3.17) shows improved load regulation performance with a larger open-loop gain.

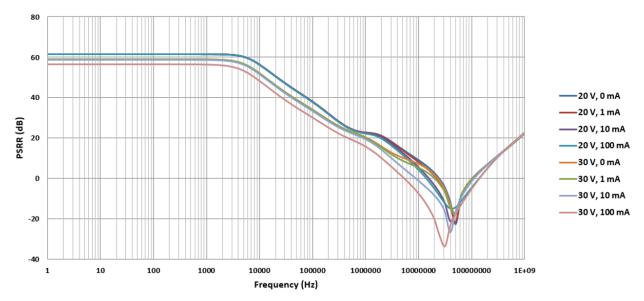

Whereas the line and load regulation are steady-state performance metrics, PSRR indicates the regulator's ability to reject supply noise (e.g. 60 Hz noise). The expression for PSRR is given in (3.18), where  $A_{OL}$  is the open-loop gain given in (3.7) for low frequencies.

$$PSRR = \frac{\Delta V_{supply}}{\Delta V_{out}} * A_{OL}(s)$$

(3.18)

PSRR is dependent upon the supply noise frequency and the regulator's gain over frequency. Commercially available linear regulators with datasheets reporting PSRR performance typically list PSRR values for multiple frequencies for a given test condition. Most linear regulators have poorer PSRR at high frequencies, beyond their bandwidths, compared to low frequencies which is a result of the characteristic gain roll off.

#### 3.1.1 Operational Amplifiers

The op-amp forms the core of the linear regulator's feedback loop and serves as a building block for a wide range of mixed signal applications. Parameters such as gain and bandwidth are vital to the op-amp's performance, particularly in closed-loop feedback systems. Additional parameters such as input common mode range, maximum output swing, power dissipation, and slew rate can also vary in degrees of importance based on the application. Outside of a general-purpose design, the application specifications and understanding of tradeoffs between parameters are essential for designing a high-performance op-amp. This section aims to provide an analysis of the common op amp topologies, describe design techniques, and compare the characteristics of each topology. Note that the analysis throughout this section will be provided based upon long-channel device characteristics.

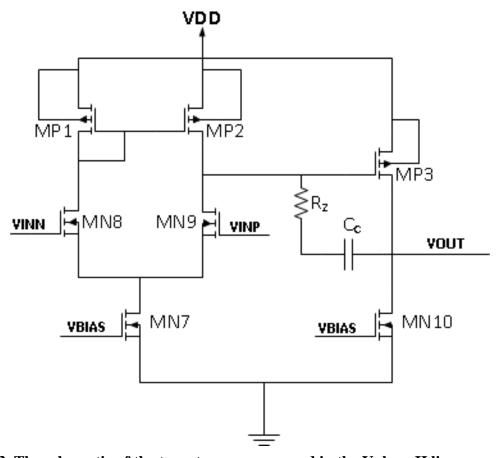

## 3.1.1.1 Two-Stage Op-Amp

The first op-amp that will be discussed is the traditional two-stage op-amp shown in Fig. 3.2. The first stage is a differential amplifier biased by M1 while the second stage is a common source amplifier formed by M7 and its biasing transistor M6. Since the op-amp has a high-impedance node at the drains of M3 and M5, which is neither the input nor the output, it is not considered an operational transconductance amplifier (OTA). The stability of the op-amp will often require the resistor R<sub>Z</sub> and capacitor C<sub>C</sub> to be used for compensation, although it will be shown why this is not always the case.

The input common mode range of the op-amp is one of the first parameters to consider. The minimum common mode voltage is determined to be (3.19) with a KVL between either of the two inputs and ground.

$$V_{CM,MIN} = V_{GS2.3} + V_{DS,SAT1} (3.19)$$

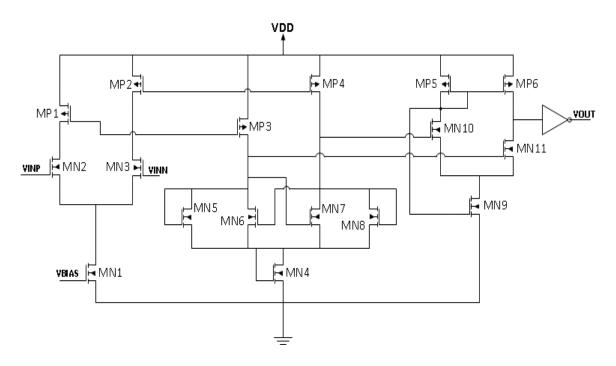

Fig. 3.2. The schematic of a two-stage op-amp.

Similarly, equation (3.20) expresses the maximum common mode voltage. To simplify this equation, it is necessary to find the drain voltage on the NFET M2 (or M3). Rearranging (3.21) to (3.22) and (3.23) shows the condition that keeps M2 or M3 in the saturation region. Plugging (3.23) into (3.20) yields (3.24).

$$V_{CM,MAX} = VDD - V_{SG4,5} - V_{DS2,3} + V_{GS2,3}$$

(3.20)

$$V_{DS} \ge V_{GS} + V_{TH} \tag{3.21}$$

$$V_D - V_G \ge V_{TH} \tag{3.22}$$

$$V_G - V_D \le V_{TH} \tag{3.23}$$

$$V_{CM,MAX} = VDD - V_{SG4,5} + V_{THN2,3}$$

(3.24)

A key takeaway from expressions (3.19) and (3.24) is that the value of  $V_{CM,MAX}$  will typically be closer to VDD than  $V_{CM,MIN}$  is to ground. The use of both an NFET and PFET input pair allows for obtaining a wider input common mode range, which can extend from below ground up to approximately VDD.

The maximum output swing of the op-amp is limited by the  $V_{SD,SAT}$  value of the output stage PFET M7 whereas the minimum output swing is limited by the current sink M6's  $V_{DS,SAT}$ . The output swing can be increased by designing M6 or M7 with a larger width. However, the tradeoffs for this design choice include an increase in power consumption, the potential for systematic offset, and a change in the frequency response of the circuit.

With respect to the types of offsets, random offset results in threshold voltage and mobility differences between devices that are intended to be matched such as the NFET pair M2 and M3 in Fig. 3.2. These mismatches can be minimized with offset cancellation schemes and with layout practices such as the common centroid layout technique. Systematic offset is a function of the design and can be seen in simulations. Systematic offset arises when FET pairs within the same

stage are not matched (e.g. M2 and M3) or a PFET/NFET branch (e.g. M6 and M7) is not matched to sink and source equal amounts of current. Systematic offset is eliminated by making a symmetrical design such that the DC bias currents satisfy the equations given in (3.25) and (3.26).

$$I_{D2} = I_{D3} = I_{D4} = I_{D5} (3.25)$$

$$I_{D6} = I_{D7} (3.26)$$

The low frequency, open-loop gain of the two-stage op-amp shown in Fig. 3.2 is a product of the gains of the differential and output stages, as given by equations (3.27) to (3.30).

$$A_{OL,DC} = A_{Stage1} * A_{Stage2} \tag{3.27}$$

$$A_{Stage1} = g_{m3}(r_{o3} // r_{o5}) \tag{3.28}$$

$$A_{Stage2} = g_{m7}(r_{o6} // r_{o7}) \tag{3.29}$$

$$A_{OL,DC} = g_{m3}g_{m7}(r_{o3} // r_{o5})(r_{o6} // r_{o7})$$

(3.30)

Based on the hybrid-pi model, the locations of the first and second poles are expressed as (3.31) and (3.32), respectively. The values of  $C_1$  and  $C_2$  in the second pole equation are determined by the inherent MOSFET capacitances as shown in equations (3.33) and (3.34).

$$f_{p1} = f_{3dB} = \frac{1}{2\pi (g_{m7})(r_{o3} // r_{o5})(r_{o6} // r_{o7})C_C}$$

(3.31)

$$f_{p2} = \frac{g_{m7}c_c}{2\pi[(c_c)(c_1) + (c_c)(c_2) + (c_1)(c_2)]}$$

(3.32)

$$C_1 = C_{gd3} + C_{gd5} + C_{sq7} (3.33)$$

$$C_2 = C_{LOAD} + C_{gd6} \tag{3.34}$$

A takeaway from the equations for the first and second poles is that the locations of the two poles will split apart with a larger  $C_C$ , a common technique referred to as pole splitting. The  $C_C$  is critical for stability since it effectively provides a large capacitance on the gate of the PFET in the second stage (i.e. M7) and a relatively small capacitance at the output of the second stage. The input and output capacitances of the second stage, provided by  $C_{gd7}$ , can be expressed as in

(3.35) and (3.36) using Miller's theorem, where  $A_V$  is the gain of the common source amplifier formed by M7.

$$C_{IN} = C_{ad7}(1 + |A_V|) \tag{3.35}$$

$$C_{OUT} = C_{gd7} (1 + \frac{1}{|A_V|}) \tag{3.36}$$

Intuitively, the input capacitance becomes effectively larger since it is charged without the gain provided by the common source amplifier. The gain of the amplifier charges the output capacitance faster and is the underlying reason for the effective decrease in output capacitance. This demonstrates the importance of pole splitting and why increasing  $C_C$  results in  $f_{p1}$  and  $f_{p2}$  moving farther apart.

However, ignoring  $R_Z$  momentarily, a larger value of  $C_C$  results in the output of the differential amplifier shorting with the output of the second stage at lower frequencies. As the output of the first stage shorts to the output of the second stage, the common source amplifier is bypassed and there is no longer an inversion. This creates a zero in the right half plane (RHP), which leads to a +20 dB/decade gain and a -45°/decade phase roll off as given by equation (3.37).

$$f_z = \frac{1}{2\pi(C_C)(\frac{1}{g_{m7}})} \tag{3.37}$$

A zero in the RHP is undesirable due to the decrease in phase. To achieve high speed operation, this zero needs to be moved to the left half plane (LHP) such that it contributes +20 dB/decade gain and +45°/decade phase. The nulling resistor  $R_Z$  is inserted in series with the compensation capacitor  $C_C$  to attenuate the feedforward current (from the  $1^{st}$  stage to  $2^{nd}$  stage) and either cancel the zero ( $R_Z = 1/g_{m7}$ ) or move the zero into the LHP ( $R_Z > 1/g_{m7}$ ). Implementing an  $R_Z$  greater than  $1/g_{m7}$  forces the feedforward current through the capacitor to be in-phase with

the output current such that it negates the effects of the output pole and recovers the phase lost. The location of the zero is then determined by the expression (3.38).

$$f_Z = \frac{1}{2\pi (C_C)(\frac{1}{g_{m7}} - R_Z)}$$

(3.38)

When the RHP zero is eliminated, the frequency response of the op-amp is that of a single pole system with a phase margin of nearly 90°. However, in practical applications it is difficult to make  $1/g_{m7}$  and  $R_Z$  equal over all process corners. A solution is to use an op-amp with an indirect compensation technique, as in Fig. 3.3, that injects  $C_C$ 's feedforward current from the  $2^{nd}$  stage output, through a low-impedance node (M5A's source), and into the high impedance node at M3's drain. The RHP zero is eliminated with this method since the feedforward path is blocked (1st to  $2^{nd}$  stage), but the output can still feed back to the input at high frequencies to reduce the gain.

This scheme improves the frequency response by moving  $f_{p2}$  to a higher frequency because M3's drain is no longer loaded by  $C_C$ . The split length devices (e.g. M4A and M4B, M5A and M5B, as well as M7A and M7B) are used to reduce the offset by keeping the PFET  $V_{DS}$  and  $V_{GS}$  values the same in both the first and second stages. A PFET based differential amplifier can be added to make the input common mode range nearly rail-to-rail, as shown in Fig. 3.4.

Fig. 3.3. An indirect compensation technique for the two-stage op-amp.

Fig. 3.4. A rail-to-rail two-stage op-amp with indirect compensation.

# 3.1.1.2 Folded-Cascode Op-Amp

The conventional folded-cascode topology shown in Fig. 3.5 offers an improvement in the low-frequency, open-loop gain compared to a single stage differential amplifier or a two-stage opamp if an output stage is included. The cascoded devices in this topology allow for a relatively high output resistance and large DC gain. One of the most notable distinctions of the folded-cascode topology compared to the two-stage op-amp is that the load capacitance plays a key role in the frequency response.

The maximum value of the input common-mode range is determined by expression (3.39). Using the long channel saturation condition equations, as in the two-stage op-amp analysis, allows for rearranging the equation into (3.40).

$$V_{CM,MAX} = VDD - V_{SD,SAT4,5} - V_{DS,SAT2,3} + V_{GS2,3}$$

(3.39)

$$V_{CM,MAX} = VDD - V_{SD,SAT4,5} + V_{THN2,3}$$

(3.40)

Fig. 3.5. A conventional folded-cascode topology with an NFET input pair.

The minimum value of the input common mode range is expressed in equation (3.41). A solution for designing a nearly rail-to-rail input common mode range for the folded-cascode is to add a PFET differential amplifier similar to the two-stage topology in Fig. 3.4.

$$V_{CM,MIN} = V_{GS2,3} + V_{THN2,3}$$

(3.41)

If a PFET input pair is added, then the drain of each PFET connects to the drain of either M10 or M11. Note that this will change the sizing of the existing FETs. In the configuration shown in Fig. 3.5, the PFETs M4 and M5 are both sourcing current to the differential amplifier and the cascode structures. To mitigate systematic offset, the DC current flowing through one branch of the differential amplifier should be the same as the corresponding branch of the cascode structure. The width of M4 and M5 should therefore be sized appropriately (i.e. twice that of M6 and M7).

With a PFET input pair added, the NFETs M10 and M11 would likewise need to have their widths doubled to account for sinking current to two different branches with equal DC currents.

The wide swing cascode current mirror configuration implemented by connecting the drain of M6 to the gate of M4 (and M5) more accurately mirrors the current through M5's branch. The operation of the current mirror can still be intuitively understood as a single gate-drain connected PFET that mirrors current. However, the goal of this approach is to bias M4's gate such that the  $V_{SD}$  of M4 places it on the edge of saturation, which closely matches with the  $V_{SD}$  of M5.

If a gate-drain connection was made with M4 and a separate gate-drain connection was made with M6, then the finite output resistances of the FETs would result in more poorly matched currents through M4 and M5. The gates of M4 and M5 would be biased to (3.42). Likewise, the gates of M6 and M7 would be set to (3.43).

$$V_{G4,5} = VDD - V_{SD4,5} - V_{THP4,5} (3.42)$$

$$V_{G6,7} = V_{G4,5} - V_{SD6,7} - V_{THP6,7} \tag{3.43}$$

From equation (3.42), the gate voltage of M4 and M5 is set to a threshold drop beyond the saturation condition. By decreasing the gate voltage to only V<sub>SD4,5</sub> below VDD, the devices can be placed on the edge of saturation. This allows for more accurately mirrored currents and it also decreases the supply voltage requirement, leading to either lower power consumption or increased speed. The wide swing cascode current mirror shown in Fig. 3.5 accomplishes this since the drains of M4 and M5 follow equation (3.44).

$$V_{D4,5} = VDD - V_{SD4,5} (3.44)$$

Similarly, the gates of M6 and M7 can now be biased to (3.45), which eliminates a second threshold drop as seen by equations (3.42) and (3.43).

$$V_{G6,7} = V_{D4,5} - V_{SD6,7} - V_{THP6,7} \tag{3.45}$$

The output swing of the folded-cascode topology shown in Fig. 3.5, regardless of whether a PFET differential pair is added, is limited to (3.46) and (3.47) for the minimum and maximum, respectively.

$$V_{OUT,MIN} = V_{DS,SAT9} + V_{DS,SAT11} \tag{3.46}$$

$$V_{OUT,MAX} = VDD - V_{SD,SAT5} - V_{SD,SAT7}$$

(3.47)

From the equations given above, it is apparent that the greatest output swing occurs when M4 - M7 and M8 - M11 are all biased to be on the edge of saturation.