## Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

8-2016

# Laser direct written silicon nanowires for electronic and sensing applications

Woongsik Nam Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations Part of the <u>Electrical and Computer Engineering Commons</u>, <u>Mechanical Engineering Commons</u>, and the <u>Nanoscience and Nanotechnology Commons</u>

#### **Recommended** Citation

Nam, Woongsik, "Laser direct written silicon nanowires for electronic and sensing applications" (2016). *Open Access Dissertations*. 821. https://docs.lib.purdue.edu/open\_access\_dissertations/821

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

#### PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

#### By Woongsik Nam

Entitled LASER DIRECT WRITTEN SILICON NANOWIRES FOR ELECTRONIC AND SENSING APPLICAITONS

For the degree of Doctor of Philosophy

Is approved by the final examining committee:

| Xianfan Xu       | Yi Xuan |

|------------------|---------|

| Chair            |         |

| Peide (Peter) Ye |         |

|                  |         |

| Minghao Qi       |         |

| Cagri Savran     |         |

To the best of my knowledge and as understood by the student in the Thesis/Dissertation Agreement, Publication Delay, and Certification Disclaimer (Graduate School Form 32), this thesis/dissertation adheres to the provisions of Purdue University's "Policy of Integrity in Research" and the use of copyright material.

Approved by Major Professor(s): Xianfan Xu

Approved by: <u>Jay</u> P. Gore

7/16/2016

Head of the Departmental Graduate Program

# LASER DIRECT WRITTEN SILICON NANOWIRES FOR ELECTRONIC AND

## SENSING APPLICATIONS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Woongsik Nam

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2016

Purdue University

West Lafayette, Indiana

# TABLE OF CONTENTS

# Page

| LIST OF TAB  | LES                                                    | iv    |

|--------------|--------------------------------------------------------|-------|

| LIST OF FIGU | JRES                                                   | v     |

| ABSTRACT     |                                                        | . vii |

| CHAPTER 1.   | INTRODUCTION                                           | 1     |

| 1.1          | Nanowires                                              | 2     |

| 1.2          | Laser Direct Writing                                   | 3     |

| 1.3          | Nanowire Field Effect Transistor Sensors               | 4     |

| 1.4          | Nanowire Transistors and Circuits                      | 6     |

| 1.5          | P-n Junction Nanowires                                 | 8     |

| 1.6          | Summary                                                | . 10  |

| 1.7          | Report Outline                                         | . 11  |

| CHAPTER 2.   | LASER DIRECT WRITING OF SILICON NANOWIRES              | . 12  |

| 2.1          | Experimental Description                               | . 12  |

| 2.1.1        | Lasers and Optical Components                          | 13    |

| 2.1.2        | CVD System                                             | 15    |

| 2.1.3        | Substrate Preparation                                  | 16    |

| 2.2          | Fresnel Zone Plates for Light Focusing                 | . 17  |

| 2.2.1        | Principle of Fresnel Zone Plates                       | 19    |

| 2.2.2        | Rayleigh-Sommerfeld Calculation of Fresnel Zone Plates | 20    |

| 2.2.3        | Focusing Analysis of Fresnel Zone Plates               | 22    |

| 2.3          | Nanowire Growth                                        |       |

| 2.3.1        | Effects of Experimental Parameters                     | 26    |

| 2.3.2        | Explanation of Nanowire Formation                      | 28    |

| 2.3.3        | Micro-structure of Silicon Nanowires                   | 32    |

| 2.4          | Summary                                                | . 34  |

| CHAPTER 3.   | SILICON NANOWIRE FIELD EFFECT TRANSISTOR SENSORS .     | . 36  |

| 3.1          | Basic Principles of FET Sensors                        | . 37  |

| 3.2          | Laser Direct Writing of Silicon Wires for FET Sensors  | . 41  |

| 3.3          | Fabrication of Silicon Nanowire FET Sensors            | . 42  |

| 3.4          | Experimental Setup for pH Sensing Tests                | . 45  |

| 3.5          | Electrical Characterization of pH Sensors              |       |

| 3.6          | Summary                                                | . 53  |

| CHAPTER 4.   | SILICON NANOWIRE FIELD EFFECT TRANSISTORS              | . 54  |

| 4.1          | Basic Principles of FETs                               |       |

| 4.2          | Laser Direct Writing of Silicon Nanowires for FETs     | . 56  |

|              |                                                        |       |

# Page

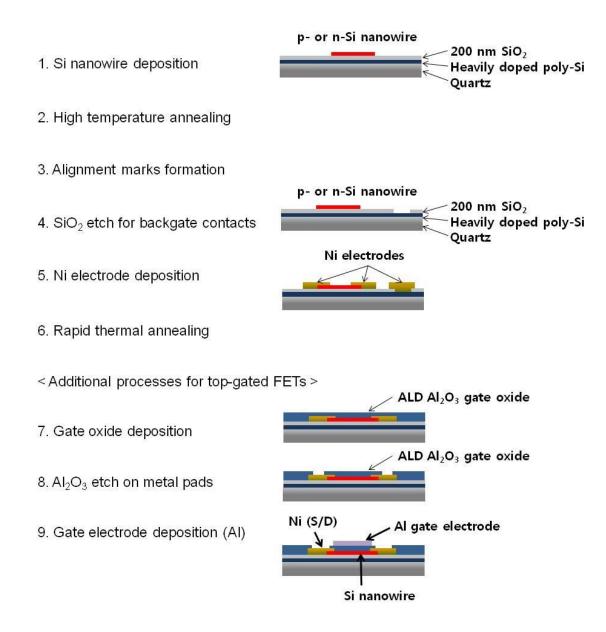

| 4.3         | Fabrication of Silicon Nanowire FETs                            | 57  |

|-------------|-----------------------------------------------------------------|-----|

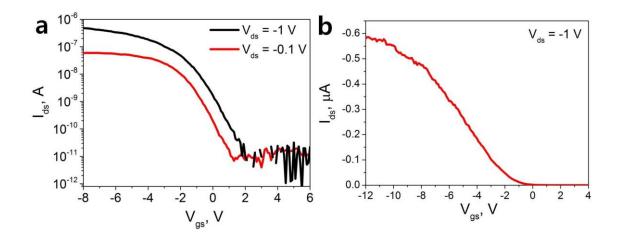

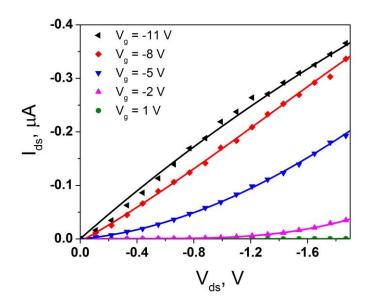

| 4.4         | Electrical Characterization of Back-Gated Silicon Nanowire FETs | 62  |

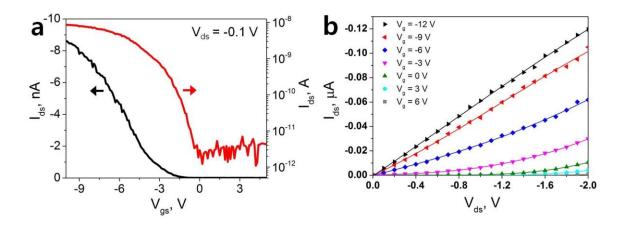

| 4.5         | Electrical Characterization of Top-Gated Silicon Nanowire FETs  | 67  |

| 4.6         | Effect of Doping Concentration on Device Performance            | 69  |

| 4.7         | Summary                                                         | 73  |

| CHAPTER 5.  | P-N JUNCTION SILICON NANOWIRES                                  | 74  |

| 5.1         | Laser Direct Writing of P-n Junction Nanowires                  | 74  |

| 5.2         | Fabrication of P-n Junction Nanowire Devices                    | 78  |

| 5.3         | Electrical Characterization of P-n Junction Nanowire Devices    | 82  |

| 5.4         | Kelvin Probe Force Microscopy of P-n Junction Nanowires         | 86  |

| 5.5         | Summary                                                         | 91  |

| CHAPTER 6.  | CONCLUSIONS AND FUTURE WORK                                     | 93  |

| 6.1         | Conclusions                                                     | 93  |

| 6.2         | Future work                                                     | 94  |

| LIST OF REF | ERENCES                                                         | 98  |

| VITA        |                                                                 | 108 |

|             |                                                                 |     |

# LIST OF TABLES

| I                                                                            | Page                                                                                                                                                                                                                |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design parameters of the phase zone plates used in the experiment            | 22                                                                                                                                                                                                                  |

| Summary of device parameters of laser-direct-written SiNW FETs               | 72                                                                                                                                                                                                                  |

| Summary of the diffusion coefficients, vacancy diffusivities, and activation |                                                                                                                                                                                                                     |

| energies used to estimate the characteristic diffusion lengths               | 80                                                                                                                                                                                                                  |

|                                                                              | Design parameters of the phase zone plates used in the experiment<br>Summary of device parameters of laser-direct-written SiNW FETs<br>Summary of the diffusion coefficients, vacancy diffusivities, and activation |

# LIST OF FIGURES

# Figure

# Page

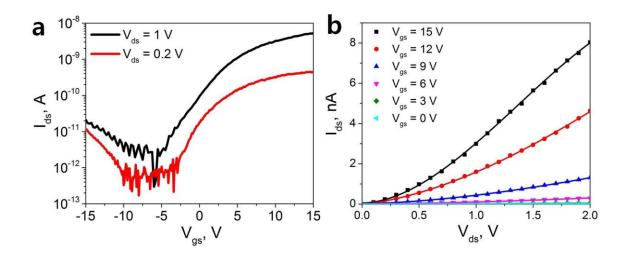

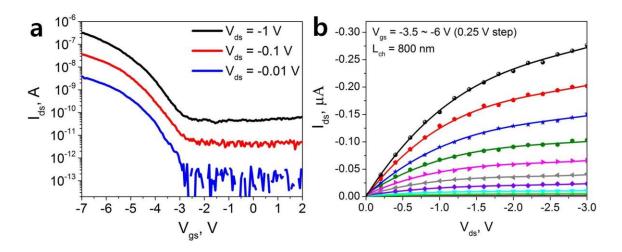

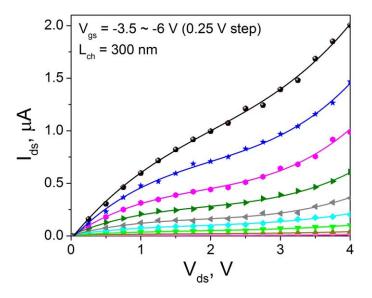

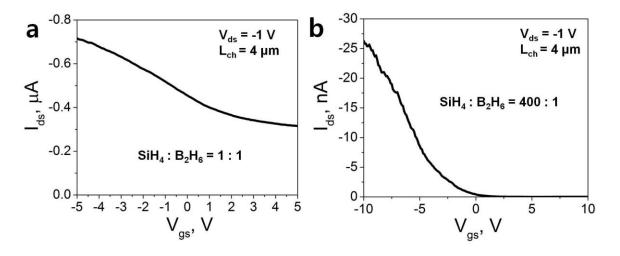

| Figure 4.9 <i>I</i> <sub>ds</sub> - <i>V</i> <sub>ds</sub> characteristics of a SiNW FET with a back gate      | 64 |

|----------------------------------------------------------------------------------------------------------------|----|

| Figure 4.10 (a) $I_{ds}$ - $V_{gs}$ and (b) $I_{ds}$ - $V_{ds}$ characteristics of a SiNW FET with a back gate | 65 |

| Figure 4.11 (a) $I_{ds}$ - $V_{gs}$ and (b) $I_{ds}$ - $V_{ds}$ characteristics of an n-type SiNW FET.         | 67 |

| Figure 4.12 (a) $I_{ds}$ - $V_{gs}$ and (b) $I_{ds}$ - $V_{ds}$ characteristics of a top-gated SiNW FET        | 68 |

| Figure 4.13 <i>I</i> <sub>ds</sub> - <i>V</i> <sub>ds</sub> characteristics of a top-gated SiNW FET.           | 69 |

| Figure 4.14 <i>I</i> <sub>ds</sub> - <i>V</i> <sub>ds</sub> characteristics of back-gated SiNW FETs            | 71 |

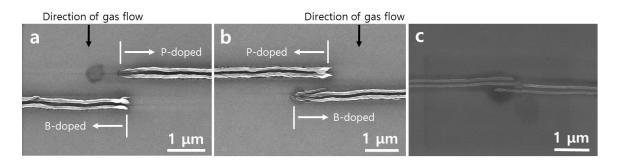

| Figure 5.1 SEM images of p-n junction nanowires with discontinuity and defects                                 | 76 |

| Figure 5.2 SEM images of continuous p-n junction nanowires                                                     | 76 |

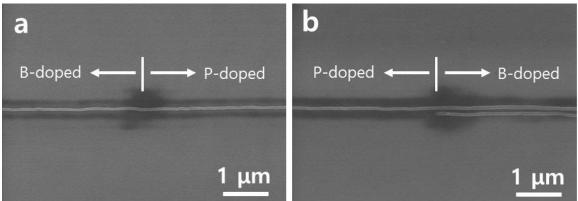

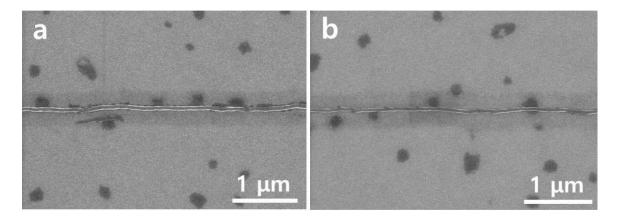

| Figure 5.3 SEM images of continuous p-n junction nanowires                                                     | 77 |

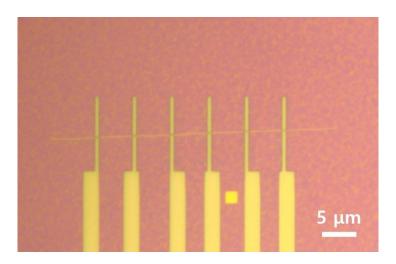

| Figure 5.4 Optical image of a multifinger device                                                               | 81 |

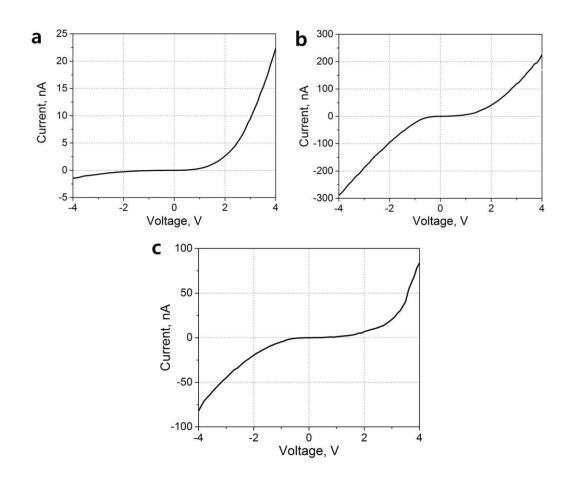

| Figure 5.5 I-V characteristics of a laser-direct-written p-n junction SiNW devices                             | 84 |

| Figure 5.6 I-V characteristics of a laser-direct-written p-n junction SiNW devices                             | 86 |

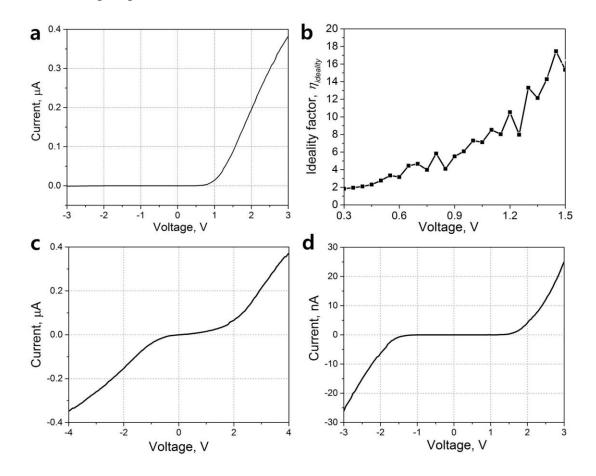

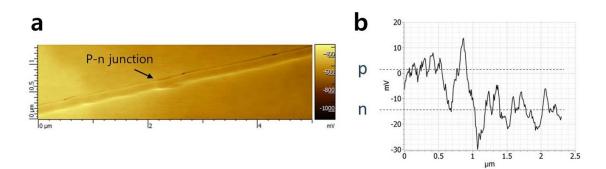

| Figure 5.7 Energy band diagram illustrating Kelvin probe physics                                               | 88 |

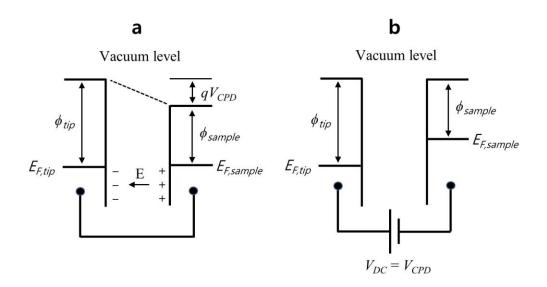

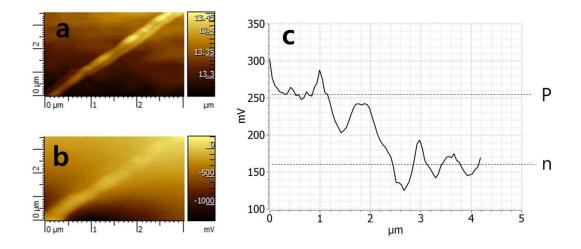

| Figure 5.8 Kelvin probe force microscope images of a p-n junction nanowire                                     | 90 |

| Figure 5.9 AFM and KPFM images of a laser-direct-written p-n junction nanowire                                 | 91 |

|                                                                                                                |    |

#### ABSTRACT

Nam, Woongsik Ph.D., Purdue University, August 2016. Laser Direct Written Silicon Nanowires for Electronic and Sensing Applications. Major Professor: Xianfan Xu, School of Mechanical Engineering.

Silicon nanowires are promising building blocks for high-performance electronics and chemical/biological sensing devices due to their ultra-small body and high surfaceto-volume ratios. However, the lack of the ability to assemble and position nanowires in a highly controlled manner still remains an obstacle to fully exploiting the substantial potential of nanowires. Here we demonstrate a one-step method to synthesize intrinsic and doped silicon nanowires for device applications. Sub-diffraction limited nanowires as thin as 60 nm are synthesized using laser direct writing in combination with chemical vapor deposition, which has the advantages of in-situ doping, catalyst-free growth, and precise control of position, orientation, and length. The synthesized nanowires have been fabricated into field effect transistors (FETs) and FET sensors. The FET sensors are employed to detect the proton concentration (pH) of an aqueous solution and highly sensitive pH sensing is demonstrated. Both top- and back-gated silicon nanowire FETs are demonstrated and electrically characterized. In addition, modulation-doped nanowires are synthesized by changing dopant gases during the nanowire growth. The axial p-n junction nanowires are electrically characterized to demonstrate the diode behavior and the transition between dopant levels are measured using Kelvin probe force microscopy.

#### CHAPTER 1. INTRODUCTION

During the past decades, semiconductor nanowires have attracted a great deal of attention due to their demonstrated potential for high-performance nanoscale devices such as transistors (Cui and Lieber, 2001), sensors (Cui et al., 2001), resonators (Feng et al., 2007), solar cells (Garnett and Yang, 2008) and thermoelectric systems (Hochbaum et al., 2008). The high surface-to-volume ratios of nanowires make them sensitive probes to chemical and biological species. The ultra-thin bodies of nanowires allow excellent electrostatic control which is required for high-performance electronic devices. However, despite their promise, complex procedures for integrating nanowires into a nanoscale device remain an obstacle for widespread applications. The bottom-up approach requires assembly of nanowires grown from chemical vapor deposition (CVD), which not only involves CMOS incompatible processes but also suffers from difficulty in precisely positioning nanowires. The top-down approaches require multiple fabrication steps for nanowire patterning, etching, and doping as well as the use of advanced optical or electron-beam lithography and silicon-on-insulator (SOI) substrates.

In this work, we demonstrate a single-step, laser-direct-write method to fabricate intrinsic and doped silicon nanowires. The synthesized nanowires are used for electronic devices and sensing applications.

#### 1.1 <u>Nanowires</u>

The vapor-liquid-solid (VLS) method has been the most successful route to produce semiconductor nanowires. In the VLS method, vapor phase precursors are dissolved into nanosized liquid droplets of a catalyst material, from which unidirectional nanowire growth proceeds. The produced nanowires have a single-crystalline structure, which is ideal for electronic and optical applications, and high-quality surfaces with fewer surface dangling bonds due to nanowire surface faceting (Garnett et al., 2009). The possible in situ doping by incorporating dopant precursors during nanowire growth eliminates the need for an additional doping procedure. Because the diameter of each nanowire is largely determined by the size of the catalytic particle, the choice of the seed particles allows control over the diameter of the nanowires produced. However, the use of the catalyst also leads to undesirable contamination of nanowires. For Si nanowires, the most commonly used catalyst is Au. Au atoms are highly diffusive in Si and act as deep level acceptors, negatively affecting device performance. There have been significant research efforts to overcome this drawback. Complementary metal-oxidesemiconductor (CMOS) compatible metals such as Al (Wang et al., 2006) and Bi (Heitsch et al., 2008) have been demonstrated as catalysts for Si nanowire growth. Catalyst-free growth of silicon nanowires was also shown to be possible (Kim et al., 2009).

A more crucial drawback of using the bottom-up nanowires for device applications is difficulty in precisely controlling the position and orientation of nanowires. Because these nanowires are produced as entangled mesh, additional fabrication procedures are required to position and align nanowires in placement required for large-scale

2

semiconductor devices. There have been a number of techniques developed to overcome this obstacle. For example, nanowires were aligned using strong electric fields (Lee et al., 2010), dielectrophoresis (Raychaudhuri et al., 2009; Freer et al., 2010), microfluidic alignment (Huang et al., 2001), lubricant-assisted contact printing (Fan et al., 2008; Yan et al., 2011), and nanocombing (Yao et al., 2013). Some of these techniques achieved a very high yield in the alignment of single nanowires to metallic pads, but none of them has demonstrated the capability to create the high density and precision required for integrated circuit manufacturing. Alternatively, large arrays of accurately placed, high density vertical nanowires were demonstrated using lithographically defined catalyst locations (Mårtensson, 2003; Borgström, 2007). Although these vertical nanowires are available for high-density device applications, a great amount of work is still required to solve fabrication issues and improve device performance.

#### 1.2 Laser Direct Writing

Laser direct writing (LDW) refers to a technique that is able to create 1D to 3D features by laser-induced deposition, modification, or subtraction of materials. LDW has some advantages over conventional patterning methods such as lithography. First, a wide range of materials including metals, ceramics, semiconductors, polymers, composites and biomaterials can be patterned or fabricated. Second, intricate 3D structures which are either impossible or impractical with conventional patterning methods can be easily made by LDW. Moreover, no need for masks or preexisting patterns adds more flexibility to LDW. Consequently, LDW is extensively used for rapid prototyping applications because designs and patterns can be changed and immediately applied to final products.

One of the LDW methods is laser chemical vapor deposition (LCVD). In this process, a laser beam is focused on a substrate and materials are deposited around the laser spot from gas precursors. Since LCVD was first demonstrated for depositing Si and W in the early 1980s (McWilliams et al., 1983), the method was used for direct writing of Al lines on various substrates (Foulon and Stuke, 1993), and also applied to create 3D structures (Lehmann and Stuke, 1994; Wanke et al., 1997). However, minimum feature sizes in these studies were much larger than the laser beam diameter.

There has been much research effort to reduce feature sizes far below the diffraction limit. The approaches to this end include multiphoton polymerization (Kawata et al., 2001; Li et al., 2009), stimulated emission depletion (STED) microscopy (Westphal and Hell, 2005), near field plasmonic approaches (Sun and Leggett, 2004; Srituravanich et al., 2008), and zone plate lithography (Smith et al., 2006). These methods have achieved sub-diffraction limit features down to tens of nanometers, but none of them was able to be directly applied to grow nanoscale materials.

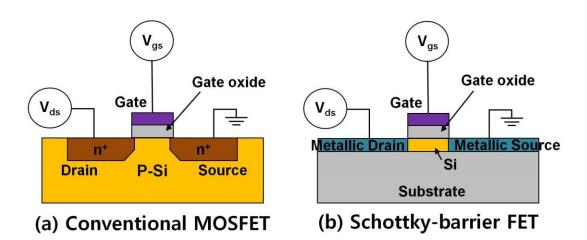

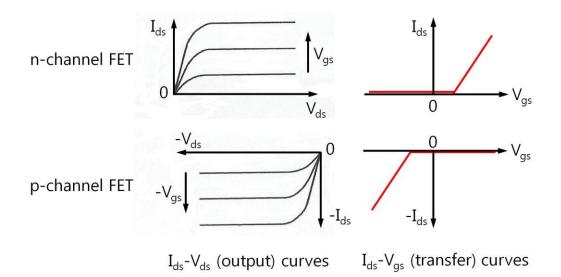

#### 1.3 <u>Nanowire Field Effect Transistor Sensors</u>

Since ion-sensitive field effect transistors (ISFETs) were first demonstrated to measure chemical quantities in 1970 (Bergveld, 1970), there has been considerable attention to use them for chemical and biological applications. The detection principle of ISFETs is based on their configuration as field effect transistors (FETs). In a standard FET, the conductance of the semiconductor channel is modulated by the electric field applied by a gate electrode. The application of a gate voltage depletes or accumulates charge carriers in the channel and thus the FET conductance directly depends on the gate voltage. In an ISFET, the binding of a charged chemical or biological species has a role analogous to that of a gate voltage. Unlike conventional FETs, the gate oxide surface of an ISFET is exposed to an external electrolyte, allowing a chemical or biological species of interest to interact with the surface. The charges of the surface-bound species create an electric field, which modulates the number of carriers in the channel in the same way as a gate voltage does, and consequently the existence and the concentration of a target species can be detected by measuring the change of the FET conductance.

One advantage of ISFETs is that there is no need for the a priori attachment of fluorescent or any other labels to target molecules. This label-free sensing makes detection quick and on site. The required specific detection can be provided by functionalizing the sensor surface with a receptor for target molecules. The direct, electrical readout of signals is another attractive feature of these sensors. The electrical signals can be directly routed to the outside world, enabling easy integration of the sensors into miniaturized systems. However, the limited sensitivity of ISFETs remained a challenge.

In 2001, the application of nanowires to FET sensors (Cui et al., 2001) demonstrated the potential of significantly improved sensitivity, triggering new research interest. Because of the one-dimensional morphology and high surface-to-volume ratio of a nanowire, a very small amount of surface-bound molecules are needed to change the conductance of the nanowire in the sensors. In subsequent research, sensitivity increased to the point sufficient to detect single particles (Patolsky, 2004). The first nanowire FET sensors were demonstrated for the detection of pH, protein, and calcium ions. Later, nanowire FET sensors were used to detect single-stranded DNA (Hahm and Lieber, 2004). Complementary single-stranded sequences of peptide nucleic acids (PNAs) were used as a receptor, and excellent selectivity between target DNA and mismatched mutant DNA was demonstrated. Cancer marker proteins down to femtomolar concentrations were also detected using nanowire FET sensors (Zheng et al., 2005). In this research, an array of distinct nanowires with different receptors were used to simultaneously detect multiple biomarkers and discriminate false positives, providing high selectivity and the information necessary for robust diagnosis of disease. Gas-phase species, such as NO<sub>2</sub>, CO, ethanol and so on, have been sensed via metal oxide nanowires, including ZnO, TiO<sub>2</sub>, SnO<sub>2</sub>, and others (Comini et al., 2002; Li et al., 2008; Joshi et al., 2009).

A persistent issue encountered in applications of nanowire FET sensors to physiological fluid samples such as blood is that the surface of nanowires can be deactivated by biofouling and non-specific binding. Also, the sensitivity of the sensors depends on solution ionic strength due to charge screening of dissolved solution counterions, that is, the Debye screening (Stern et al., 2007). To overcome these limitations, Stern et al. (2009) used a microfluidic purification chip which captures biomarkers from blood samples and thereafter releases them into a purified buffer for sensing. The approach allowed them to detect two cancer markers, PMSA and CA15.3 in whole blood.

#### 1.4 Nanowire Transistors and Circuits

Using nanowires for FETs offers some advantages over conventional planar devices. First, the ultra-thin body of nanowires allows more efficient control over charge carriers in the semiconductor channel. Moreover, the one-dimensional morphology of nanowires enables straightforward implementation of semicylindrical gate or gate-allaround architectures, reducing short channel effects and improving device performance. In addition, the single-crystalline structure and smooth surfaces of nanowires reduce carrier scattering in the FET channel and results in high carrier mobility.

One of the most commonly used structures of nanowire FETs is a back gate configuration where a nanowire is deposited on an oxide and the underlying Si substrate acts as a back gate. Metal electrodes are directly deposited on the nanowire without intentional formation of p-n junctions. In this structure, device performance is largely affected by Schottky barriers at the metal-semiconductor interfaces (Guo et al., 2003; Chen et al., 2005). In a conventional FET, metal-semiconductor interfaces are placed away from a channel by highly doped source/drain extensions and thus a gate voltage has little influence on the Schottky barriers. However, in such a nanowire FET, the application of a gate voltage alters the width of the Schottky barriers and the carrier transport through the Schottky barriers is influenced by the gate voltage, making the FET a Schottky barrier device. Schottky barriers at metal-silicon nanowire interfaces are typically positive due to Fermi level pinning by surface states (Sze and Ng, 2007). Therefore, engineering contact properties can significantly improve device performance. For example, a study of nanowire FETs showed that extrinsic field-effect mobility can be significantly improved by thermal annealing (Cui et al., 2003).

Early research on nanowire devices focused on the demonstration of individual transistors and basic devices. Duan et al. (2001) demonstrated indium phosphide nanowire FETs and crossed-wire p-n junctions. Cui and Lieber (2001) also demonstrated silicon nanowire p-n junction diodes and bipolar transistors. Huang et al. (2001)

fabricated logic gates using silicon and gallium nitride nanowires. As nanowire assembly techniques (Lee et al., 2010; Raychaudhuri et al., 2009; Freer et al., 2010; Huang et al., 2001; Fan et al., 2008; Yan et al., 2011; Yao et al., 2013) have developed, nanowire devices have been integrated into larger scale circuits. Address decoders (Zhong et al., 2003) were created using a crossbar structure where active devices were formed at the intersection points of two crossed nanowires. Programmable nanowire circuits were demonstrated using Ge/Si heterostructure nanowires (Yan et al., 2011). However, the lack of the capability to create a high density array of precisely aligned nanowires which are required for very large scale integrated (VLSI) circuit manufacturing still limits an industrial use of nanowire arrays for device applications.

#### 1.5 <u>P-n Junction Nanowires</u>

In order to make full use of the electrical properties of semiconductor nanowires, controlled doping is an important issue. For VLS nanowires, in-situ doping can be realized by adding dopants to the gas mixture used for nanowire deposition. Diborane (Cui et al., 2000) and trimethylboron (Lew et al., 2004; Vallett et al., 2010) have been used for p-type Si nanowires, and phosphine (Wang et al., 2005) and arsenic (Tang et al., 2005) for n-type Si nanowires. The growth mechanism of semiconductor nanowires also offers the possibility of straightforward fabrication of axial heterojunction structures. For example, axial modulation-doped nanowires have been demonstrated by changing the dopant source during nanowire growth (Kempa et al., 2008; Imamura et al., 2008). These axial p-n junction structures are advantageous because they do not require additional junction fabrication processes. In addition, transition lengths as short as 10 nm have been

reported (Christesen et al., 2013). The known difficulty in fabricating axial p-n junction nanowires is the radial deposition or the dopant incorporation through the nanowire surface after changing the growth conditions (Yang et al., 2005). In the case of boron in silicon nanowires, boron atoms are insufficiently incorporated into Si via metal catalysts and the majority of boron atoms come from deposition of high boron concentration layers on the side-wall of a nanowire (Imamura et al., 2008). Therefore, if a doping agent such as B<sub>2</sub>H<sub>6</sub> is introduced midway during the growth of a p-n junction nanowire, the entire nanowire is doped with boron, which severely limits the realization of axial p-n junction nanowires. A similar mechanism was also observed for boron-doped Ge nanowires and Tutuc et al. (2006) proposed a new method to synthesize p-n junction Ge nanowires where a thin boron-doped layer is deposited after fabricating a phosphorus-doped and undoped junction structure. On the other hand, when  $PH_3$  is used as an n-type doping source for Si nanowires, a similar n-type overcoating has not been observed (Kempa et al., 2008; Yang et al., 2005). The VLS grown axial p-n junction nanowires have been demonstrated for tunnel field-effect transistors (Vallett et al., 2010), photovoltaics (Kempa et al., 2008) and diodes (Tutuc et al., 2006).

Another way to create p-n junction nanowires is growing a distinct shell on a preexisting nanowire core. The outer shell is epitaxially grown on a nanowire surface and by repeating the shell growth with different reactants, core/shell or core/multi-shell radial structures can be created. The unique geometry of radial nanowire heterostructures makes them excellent candidates for photovoltaic devices (Tian et al., 2007) because a carrier collection distance can be very short and hence bulk recombination can be avoided. The outer shell of a radial nanowire heterostructure can be also used as a surrounding-gate

which provides excellent electrostatic control over the conducting channel. Lauhon et al. (2002) reported the fabrication of high-performance transistors based on core/multi-shell Si-Ge nanowires.

#### 1.6 <u>Summary</u>

Despite the demonstrated potential of nanowires for many applications and intense research for over a decade, nanowires still have few industrial applications. The main challenges include the lack of a reliable nanowire assembly technique which satisfies requirements for VLSI circuit fabrication, and metal contamination from catalysts used during the CVD growth. Although previous research has shown significant progress to overcome each of these drawbacks separately, none of them has achieved the level which can be used for industrial applications.

Laser direct writing has been widely used for research and industrial applications. The combination of laser direct writing and CVD was demonstrated decades ago, but the minimum feature sizes were much larger than the laser beam diameters. Although recent research has decreased feature sizes down to sub 100 nm resolution, these methods generally cannot be used for material synthesis.

In this work, we report a single-step approach to fabricate intrinsic and doped silicon nanowires with excellent control of nanowire position. Laser direct writing in combination with CVD created nanowires with diameters as small as 60 nm which is far below the diffraction limit. The synthesized nanowires are demonstrated for nanowire FETs and sensors. In addition, by changing dopant gases during nanowire growth, p-n junction nanowires were synthesized and characterized.

#### 1.7 <u>Report Outline</u>

This chapter has introduced previous research about nanowires, laser direct writing, nanowire FET sensors, nanowire FETs, and p-n junction nanowires. Chapter 2 discusses laser direct writing of silicon nanowires. Experimental details of the laser direct write CVD method are first provided and the resulting nanowire growth is discussed. Our experiment and HFSS simulation show that the interference between incident laser irradiation and surface scattered radiation creates periodic heating needed for the synthesis of sub-diffraction limited nanowires.

Chapter 3 demonstrates the application of the laser direct written nanowires for chemical sensors. The synthesized nanowires are fabricated into nanowire FET sensors and the sensors are employed to detect the proton concentration (pH) of an aqueous solution.

Chapter 4 focuses on the application of the laser direct written nanowires for FETs. Both top-gated and back-gated nanowire FETs are fabricated using the laser direct synthesized nanowires, and device characteristics are investigated. The effect of doping concentration on device performance is studied.

In Chapter 5, axial p-n junction nanowires are demonstrated. The p-n junction nanowires are fabricated by changing the dopant gases during the laser-assisted nanowire growth. The p-n junction nanowires are electrically tested as diode devices and the surface potential is measured using Kelvin probe force microscopy.

Chapter 6 presents a summary and future plans for synthesis of modulation-doped nanowires as well as to improve the performance of nanowire FETs and sensors.

#### CHAPTER 2. LASER DIRECT WRITING OF SILICON NANOWIRES

The laser direct writing of silicon nanowires requires a variety of equipment, including lasers, optics, a gas delivery system, and nano-positioning stages. In this chapter, the experimental system for the nanowire synthesis will be described in detail. Then, a Fresnel zone plate (FZP) which is one of the key components in the experiment will be discussed. The focusing performance of our FZPs will be analyzed using the scalar diffraction theory. Finally, we will discuss experimental parameters which critically affect the nanowire growth and provide an explanation for the formation of the nanowires based on experimental results and numerical calculations.

#### 2.1 Experimental Description

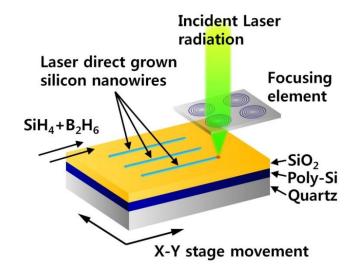

Silicon nanowires are synthesized using the combination of laser direct writing and chemical vapor deposition (CVD). Figure 2.1 shows a schematic of the laser direct write CVD method. A laser beam is focused onto a substrate using a focusing element. In our experiment, Fresnel zone plates were used as the focusing element because they give a diffraction limited spot size and are compact. This compactness of zone plates offers the potential of parallel processing by placing an array of multiple zone plates. The focused laser beam locally heats a small area on the substrate. The substrate is a 200 nm-thick silicon dioxide top layer over a 200 nm-thick polycrystalline silicon (poly-Si) layer on

quartz. The silicon dioxide top layer electrically isolates deposited Si nanowires from the substrate, and the poly-Si layer serves as a means for absorbing laser radiation. The substrate is located in a vacuum chamber with precursor gases of silane and dopant gases. Due to the thermal energy of the laser, the reactive precursors decompose on the laser spot and silicon is deposited. The choice of dopant atoms determines the doping polarity of nanowires. In the meantime, movement of the piezoelectric stage holding the substrate creates silicon nanowires in a desired pattern.

Figure 2.1. Schematic diagram of laser direct writing of silicon nanowires.

#### 2.1.1 Lasers and Optical Components

Two titanium sapphire femtosecond pulsed lasers were used for nanowire growth. The first laser was a Coherent Mira which has a wavelength of 800 nm, 150 fs pulse duration, and 76 megahertz (MHz) repetition rate. The other laser was a Coherent Micra with a wavelength of 800 nm, a minimum pulse duration of 20 femtoseconds, and 80 MHz repetition rate. The reason to choose femtosecond lasers over a continuous wave (CW) laser is the capability of creating a highly confined heated area. Because a CW laser delivers energy to the focus spot continuously, the heat dissipates around the spot and consequently the surface area with a temperature high enough to decompose silane becomes larger than the laser focus spot. In contrast, the high energy pulses of a femtosecond laser heat up the substrate in a very short time. Because temperature increases up to the point needed for silicon deposition before the heat is dissipated, the highly confined heating necessary to create a narrow silicon nanowire is possible.

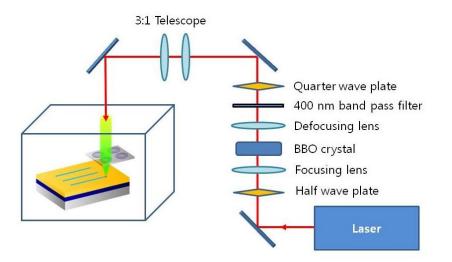

Figure 2.2. Diagram of the optical components in the experimental setup.

The laser beams were tuned to have a wavelength of 790 nm and frequency doubled to 395 nm by using a barium borate (BBO) crystal because silicon or silicon dioxide does not absorb the wavelength of 800 nm easily. Since the pulse widths of the two femtosecond lasers are different, two different thicknesses of the BBO crystal were required. A 1 mm-thick crystal was used for the Mira laser and a 100  $\mu$ m-thick crystal was used for the Micra. To control the power and the polarization of the incident laser light, a half wave plate was inserted before the BBO crystal. Changes in the polarization angle were made by rotating the crystal and the half wave plate, and a circularly polarized beam was created by adding a quarter wave plate after the crystal. The frequency doubled beam was filtered using a 400 nm band pass filter. The beam path with the optical components is shown in Figure 2.2. More details on the experimental setup and the laser direct writing method are found in the literature (Mitchell, 2010; Mitchell et al., 2011).

#### 2.1.2 CVD System

The integrated system for the laser CVD method consists of a vacuum chamber, a gas delivery system, and a mechanical positioning system. The vacuum chamber is the place where the actual CVD takes place. The chamber has a viewport on top through which the laser passes and a swinging front door which allows the substrates and other components to be placed. A mechanical roughing pump is used to pump the chamber down to a minimum pressure of less than 100 milliTorr.

In the gas delivery system, there are 6 processing gas lines, which are separately regulated by mass flow controllers (MFCs). The 6 available gases are nitrogen at 2000 standard cubic centimeters per minute (sccm) maximum flow rate, a 9:1 hydrogen silane mixture at 10 sccm, diborane at 10 sccm, silicon tetrachloride in hydrogen at 10 sccm, argon at 200 sccm, and phosphine at 10 sccm. The process gas is delivered to the substrate through a flexible metal nozzle which is positioned close to the substrate. Because silane easily reacts with oxygen in the air to form silicon dioxide, the chamber is pumped to a minimum pressure and filled to 100 Torr with nitrogen to ensure that there is as little oxygen left in the chamber as possible. This pumping and filling process is repeated 8 times before and after the experiment. The entire gas delivery system is controlled by a custom-built software.

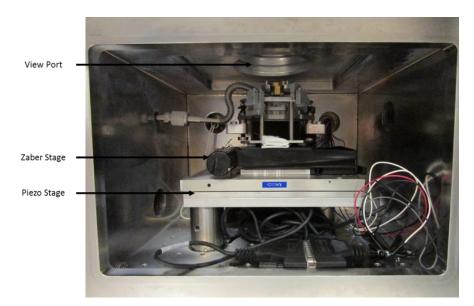

In order to write silicon nanowires in a desired pattern, the substrate needs to be moved relative to the laser beam. A Mad City Labs Nano-Align5-200 nanopositioning stage was used for the high precision movement of the substrate. The piezo-electric stage has a spatial resolution of 0.1 nm and the capability of scanning in both the x and y directions. In addition, the stage controls the separation in the z direction between the zone plates and the substrate. A Labview program was custom-written and used to control the stage. Figure 2.3 shows the inside of the CVD chamber including the zone plate holder, the piezo-electric stage, and the substrate holder.

Figure 2.3. Internal image of the vacuum chamber.

#### 2.1.3 Substrate Preparation

The substrate for nanowire growth is a quartz slide with a 200 nm-thick silicon dioxide top layer and a 200 nm-thick poly-Si layer in between. The substrate fabrication starts with standard solvent and piranha cleanings of a quartz slide. Semiconductor grade toluene, acetone, methanol and isopropanol were used for the solvent cleaning, and 96 % sulfuric acid and 30 % hydrogen peroxide were mixed in a 1:1 ratio for the piranha cleaning. Then, a 350 nm-thick amorphous silicon layer was deposited using low pressure CVD at 545 °C for 260 minutes. In order to utilize the Si layer as a backgate in backgated FET devices, phosphorus was ion-implanted into the amorphous silicon. The used implant energy was 50 keV and the implant dose was 5 x  $10^{14}$  ions/cm<sup>2</sup>. The amorphous silicon was dry-oxidized at 1100 °C in O<sub>2</sub> for 130 minutes to yield 200 nm of thermally grown silicon dioxide. The oxidation consumes some of the Si layer and the thickness of the Si layer is reduced to around 200 nm. The high temperature process also crystallizes the amorphous Si layer, turning it into poly-Si. In addition, the implanted dopant atoms diffuse in the Si layer and are electrically activated during the high temperature process.

The top silicon dioxide layer serves as an insulator which electrically isolates lasergrown nanowires from the underlying poly-Si layer. The 200 nm-thick poly-Si layer has two roles as an efficient light absorber during the nanowire growth and as a backgate in a fabricated FET device. The heat absorbed in the poly-Si layer during nanowire growth locally increases the temperature of the substrate, enabling nanowire growth with a low laser power.

#### 2.2 Fresnel Zone Plates for Light Focusing

A Fresnel zone plate (FZP) is a two dimensional focusing device consisting of a series of concentric circular gratings. Although FZPs have been known for more than 100 years, they had attracted little interest for a long time because of difficulty in fabrication and the existence of other optical elements, such as lenses and mirrors, which have functions similar to those of FZPs. Recent advances in micro-/nanotechnology triggered

FZPs to gain growing interest in various applications. Because FZPs can operate with all electromagnetic waves regardless of wavelength, they have found useful applications with x-rays and extreme ultraviolet (EUV) radiation where a refractive lens cannot be used due to strong absorption (Chao et al., 2005). Not only that, mature silicon technology resolved the difficulty in the fabrication of FZPs. With a planar geometry, FZPs can be conveniently made using standard thin film technology. The compactness of FZPs makes the integration of the optical device with other components easier. FZPs have become important optical devices in a variety of applications such as confocal microscopy, spectroscopy, and high-resolution lithography (Smith, 1996).

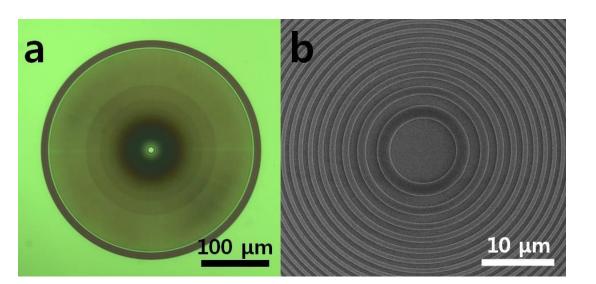

In our experiment, FZPs are used to focus the incident laser on the substrate. Because FZPs can be designed to achieve a near diffraction limit spot size at a specific wavelength and are as small as a few hundreds of µm in diameter, they are suitable for our experiment. Arrays of FZPs can be easily fabricated using standard thin film methods and used for parallel writing of nanowires. There are two types of FZPs, amplitude- and phase-zone plates. The former has alternate transparent and opaque rings. In this case, light impinging on the opaque rings is absorbed and the focusing efficiency of the FZP is low. In the case of phase-zone plates, phase-reversal zones are used instead of opaque rings. The incident radiation with the wrong phase is phase-modulated and waves passing through both open and phase-reversal zones interfere constructively at the focal point, allowing a higher efficiency of phase-zone plates. We chose to use phase-zone plates due to their higher efficiency and this allowed us to use very low laser power for nanowire growth. The FZPs were fabricated on a quartz substrate using E-beam lithography and the detailed fabrication procedure has been described previously (Srisungsitthisunti, 2011).

#### 2.2.1 Principle of Fresnel Zone Plates

Fresnel zone plates have concentric alternate transparent and opaque (or phasereversal) zones as shown in Figure 2.4. The optical path length from the boundary of each zone to the focal spot is a half wavelength different from that of an adjacent zone. In the case of having a plane wave as incident radiation, the radii of zones can be calculated using the following equation (Pedrotti et al., 2007).

$$r_n^2 = (f + \frac{n\lambda}{2})^2 - f^2 = n\lambda f + \frac{n^2\lambda^2}{4}$$

(3.1)

where *f* is the focal length of the zone plate,  $\lambda$  is the wavelength of the incident radiation, and  $r_n$  is the radius of the *n*th zone. The radius of the innermost zone is denoted as  $r_1$ . In the far-field, the focal length is much larger than the wavelength (*f* >>  $\lambda$ ) and the radii of the zones are approximately given by the following expression.

$$r_n = \sqrt{n\lambda f} \tag{3.2}$$

Figure 2.4. (a) Optical image and (b) SEM image of Fresnel zone plate.

The resolution of an FZP is largely determined by the wavelength  $\lambda$  and the outermost zone width,  $\Delta r_n = r_n - r_{n-1}$ . The Rayleigh's criterion sets the diffraction limited spatial resolution of an FZP as follows:

$$d_{FWHM} = \frac{0.61\lambda}{NA} \tag{3.3}$$

The numerical aperture of an FZP is the ratio of the outermost zone radius to the focal length, and can be expressed using the outer zone width  $\Delta r_n$  by taking the derivative of Eq. (3.2):

$$NA = \frac{r_n}{f} = \frac{\lambda}{2\Delta r_n} \tag{3.4}$$

Thus, the resolution of the zone plate depends on the outermost zone width,  $\Delta r_n$ .

$$d_{FWHM} = 1.22\Delta r_n \tag{3.5}$$

#### 2.2.2 Rayleigh-Sommerfeld Calculation of Fresnel Zone Plates

Because the final size of the focused laser spot in our experiment is ultimately determined by the Fresnel zone plates, it is important to accurately analyze the focusing performance of the FZP. Several numerical methods are available to predict the light diffraction of an FZP, including scalar diffraction theory (Cao and Jahns, 2004), beam propagation method (Srisungsitthisunti, 2009), finite element analysis (Kurokhtin and Popov, 2002), and finite-difference time domain method (Prather and Shi, 1999). Among these methods, the scalar diffraction theory is simple and fast because it includes analytical methods. Although the method is inaccurate for near-field calculation, the farfield diffraction of FZPs, which is the case in our experiment, can be accurately calculated using the method. Cao and Jahns (2004) recently evaluated the analytical solution for FZP focusing using the far-field approximation ( $f >> \lambda$ ). The Rayleigh-Sommerfeld (RS) diffraction integral modified by Cao and Jahns (2004) is used to calculate the diffraction of FZPs in this chapter.

When the wavelength of a wave field is smaller than the aperture size of an FZP used to control the wave, the Rayleigh-Sommerfeld (RS) diffraction integral can be used to calculate the light diffraction of the FZP:

$$U(R) = \sum_{n=1}^{N} U_n(R)$$

(3.6)

$$U_n(R) = \frac{1}{\lambda} \iint_{A_n} \frac{f}{\rho^2} \exp(jk\rho) r dr d\theta$$

(3.7)

where  $(r, \theta)$  are the polar coordinates at the FZP plane,  $(R, \phi)$  are the polar coordinates at the focal plane, *N* is the number of rings,  $U_n(R)$  is the individual diffracted field at the focal plane from the *n*th ring, U(R) is the total diffracted field distribution at the focal plane,  $A_n$  is the area of the *n*th ring, and  $\rho = [f^2 + R^2 + r^2 - 2Rr\cos(\theta - \phi)]^{1/2}$ . Although the RS integral is normally difficult to solve analytically, Cao and Jahns (2004) applied the far-field assumption  $(f >> \lambda)$  and evaluated an analytical solution for an FZP as follows:

$$U_n(R) = \frac{kf}{f_n^2} \exp\left[jk\left(f_n + \frac{R^2}{2f_n}\right)\right] \times \int_{a_n}^{b_n} \exp\left(jk\frac{r^2 - r_n^2}{2f_n}\right) J_0\left(\frac{kRr}{f_n}\right) r dr$$

(3.8)

where  $a_n$  and  $b_n$  are the radii of the lower and the upper edges of the *n*th ring, respectively,  $f_n = (f^2 + r_n^2)^{1/2}$ , and  $J_0$  is the zero-order Bessel function of the first kind. Equation (3.8) is used to calculate the diffraction of FZPs in this chapter.

#### 2.2.3 Focusing Analysis of Fresnel Zone Plates

The design parameters of the Fresnel zone plates used to grow nanowires are summarized in Table 2.1. The zone plates were designed for the wavelength of 395 nm and the diameter is about 300 µm. The phase-reversal zones were made of hydrogen silsesquioxane (HSQ) and the refractive index of the HSQ layer at around 400 nm wavelength was estimated to be 1.47 (Srisungsitthisunti, 2011). Because the light passing through the HSQ layer must undergo a  $\pi$  phase shift, the thickness of the layer should be 420 nm from the equation,  $t = \lambda/2(n_2 - n_1)$ .

| Wavelength           | 395 nm | # of rings             | 540       |

|----------------------|--------|------------------------|-----------|

| Focal length         | 50 µm  | Zone plate radius      | 149.88 µm |

| Outermost zone width | 211 nm | Focal spot size (FWHM) | 185 nm    |

| N.A.                 | 0.9487 | Diffraction efficiency | 15.8 %    |

Table 2.1. Design parameters of the phase zone plates used in the experiment.

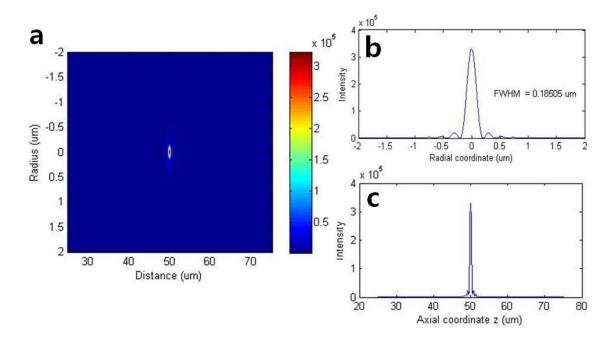

Figure 2.5 shows the light diffraction of the FZP calculated using the RS diffraction integral method. In Figure 2.5a, the x axis is the axial distance from the center of the FZP and the y axis is the radial distance from the center of the FZP. Strong light focusing is observed at  $x = 50 \mu m$  which is the focal point of the FZP. Figure 2.5b shows the intensity distribution of light at the focal plane. The full width half maximum (FWHM) at the focal spot is calculated to be 185 nm. Because the spot size of the FZP is directly related to the thickness of synthesized nanowires, achieving a small spot size is important in our experiment. The diffraction efficiency of the FZP is calculated to be 15.8 % by dividing the light intensity at the central peak by the total intensity incident on the FZP.

Figure 2.5. RS integral calculation of the FZP used to grow nanowires. (a) The intensity distribution of light diffracted by the FZP, (b) radial intensity at the focal plane, and (c) axial intensity.

The effect of fabrication errors in zone radii was also calculated. Figure 2.6a shows the intensity distribution at the focal plane when random fabrication errors between 10 and 50 nm, which are 5 – 24 % of the outermost zone width, are added to the zone radii. The FWHM increased only 2 nm from that of the ideal zone plate and the peak intensity decreased to 85.4 % of the ideal zone plate. In real fabrication processes, a more common situation is when all of the HSQ zones are either wider or narrower than the ideal zones. For example, when the HSQ layer is under-exposed or over-developed, the widths of the HSQ zones can be narrower than intended. Figure 2.6b shows when the HSQ zones become 60 nm narrower than the ideal widths. In this case, the FWHM increased only 2 nm and the peak intensity decreased to 87 % of the ideal zone plate. This indicates that the FZPs are tolerant of errors in zone widths.

Figure 2.6. Intensity distribution of diffracted light at the focal plane. Blue lines are for ideal zone plates and red lines are for (a) an FZP with random fabrication errors in zone width and (b) an FZP with narrower HSQ zone widths.

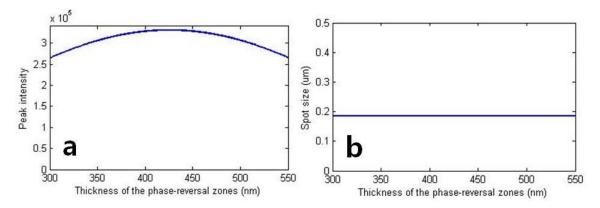

Another possible fabrication error can be variation in the thickness of the HSQ layer. Figure 2.7 shows the spot size and the peak intensity of the focused light with different thicknesses of the HSQ layer. The thickness of the phase-reversal zones has no influence on the size of the focal spot. The peak intensity at the focus has its maximum at the phase retardation of  $\pi$  and decreases with an increasing or decreasing amount of phase retardation. However, the change in the peak intensity is gradual and as small as 2.4 % with a thickness error of 43 nm which is 10 % of the ideal thickness.

Figure 2.7. (a) Peak intensity at the focal spot and (b) the size of the focal spot as a function of the thickness of the HSQ layer.

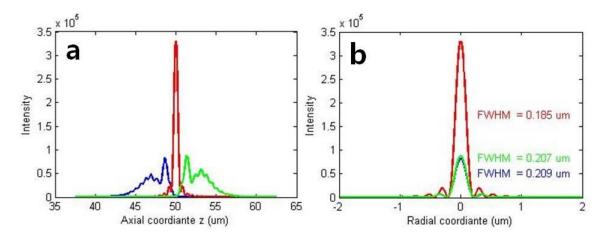

Although the FZP is tolerant of errors in zone radii and the thickness of the phasereversal zones, the FZP is sensitive to variation in the incident wavelength. Figure 2.8 shows the axial and the radial intensity distribution of diffracted light when the incident wavelength is shifted by  $\pm 5$  nm. The 5 nm wavelength shift decreases the peak intensity to about 25 % and increases the spot size by more than 20 nm. Moreover, the focal length is shifted by about 1.3 µm. This indicates that the laser wavelength needs to be carefully tuned to the correct value to get the best result in the experiment. In addition, considering that the bandwidths of our femtosecond lasers are tens of nm, a non-negligible part of the laser power will be lost in the focusing process, making the actual focusing efficiency of the FZP lower.

Figure 2.8. (a) Axial and (b) Radial intensity distribution of the light diffracted by the FZP designed for 400 nm and illuminated with 395 nm (green), 400 nm (red), and 405 nm (blue).

#### 2.3 Nanowire Growth

Silicon nanowires with widths as small as 60 nm which is far below the diffraction limit are produced using the laser CVD method. By appropriately controlling experimental parameters, nanowires with different diameters and morphology can be created. Our experimental results and numerical simulation elucidate that the interference between incident laser radiation and surface-scattered radiation plays a key role in forming high-resolution nanowires. The nanowires were synthesized by James Mitchell and the numerical calculation was performed by Nan Zhou.

#### 2.3.1 Effects of Experimental Parameters

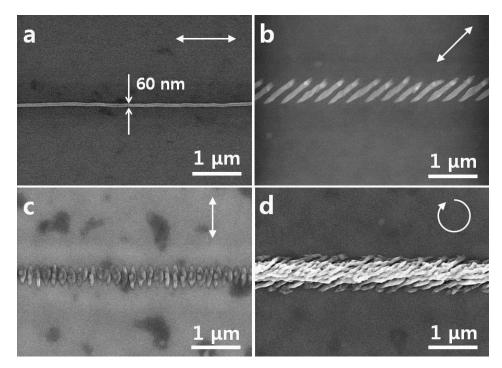

One of the key parameters in the formation of nanowires is the polarization of the incident laser. Figure 2.9 shows the dependence of the nanowire shape on the polarization direction. When the laser was horizontally polarized, a continuous, thin nanowire was created as shown in Figure 2.9a. Vertical and 45 degree diagonal polarization directions, on the other hand, resulted in discontinuous segments of nanowires in Figure 2.9b and c, respectively. As a result, nanowires were formed parallel to the polarization direction of the incident laser. All the nanowires in Figure 2.9 were written from left to right and the writing direction had no influence on nanowire shape or orientation. It is also worth noting that the width of the nanowire in Figure 2.9a is about 60 nm which is far below the diffraction limit of the 400 nm laser. A circularly polarized light resulted in a thicker wire in Figure 2.9d. The wire is essentially an agglomerate of thinner nanowires and has a rough surface.

Figure 2.9. Effect of laser polarization on nanowire formation.

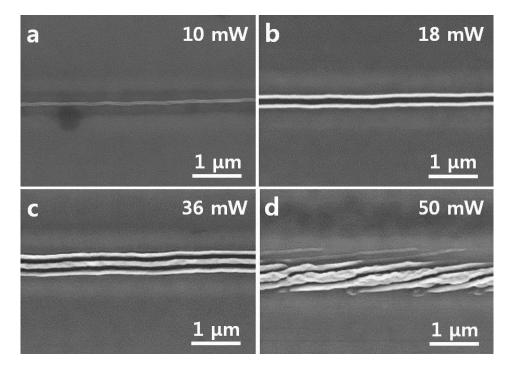

Another important parameter in the formation of nanowires is the power of the incident laser. Unlike polarization which affects the shape of nanowires, power determines the number and the thickness of nanowires which are formed simultaneously. For horizontally polarized laser irradiation, the number of simultaneously formed nanowires increases with a higher power as shown in Figure 2.10. A single nanowire is created at a low power (Figure 2.10a) and two or three nanowires are simultaneously formed by increasing the power (Figure 2.10b and c). As many as five nanowires were created in the experiment and the finite size of the laser spot kept the number of simultaneously formed nanowires from further increasing. As the power continues to increase, nanowires become thicker, touch each other, and a thick wire is formed instead of multiple thin nanowires. When multiple nanowires are formed, the gap distance between nanowires is not altered with the laser power. This is because thin nanowires are

created by periodic surface heating in the laser spot and this will be further discussed in Chapter 2.3.2. For circularly polarized laser irradiation, a thick nanowire was formed instead of multiple nanowires and the power controlled the thickness of the nanowires. More discussion on the effects of experimental parameters can be found in the literature (Mitchell et al., 2014).

Figure 2.10. Effect of laser power on nanowire formation.

## 2.3.2 Explanation of Nanowire Formation

The formation of thin nanowires in our experiment has a close relation to laser induced periodic surface structures (LIPSS, ripples) which are often observed when a linearly polarized laser beam ablates a surface of a solid. According to the ratio of the ripple period ( $\Lambda$ ) to the laser wavelength ( $\lambda$ ), LIPSS can be divided into low spatial frequency ripples ( $0.4 < \Lambda/\lambda < 1$ ) and high spatial frequency ripples ( $\Lambda/\lambda < 0.4$ ) (Huang et al., 2009). For metals and semiconductors, low spatial frequency ripples are perpendicular to laser polarization in most cases. These ripples are generally explained by interference of an incident laser beam and surface plasmons caused by the incident beam (Brueck and Ehrlich, 1982; Bonse et al., 2012). In dielectrics, low spatial frequency ripples are often parallel to laser polarization. It is widely accepted that these ripples are the result of interference between the incident radiation and surface-scattered radiation (Emmony et al., 1973; Sipe et al., 1983). It has been also reported that dielectric surfaces highly excited by high-power laser irradiation exhibit metallic behavior and formed ripples are perpendicular to the polarization direction (Huang et al, 2009). The ripple formation in this case is explained in the same way as on metal surfaces.

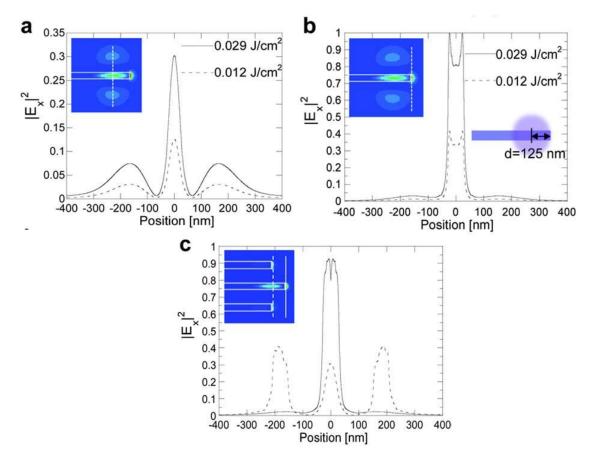

In order to explain the formation of our nanowires, numerical calculations were performed using the frequency-domain finite-element method (FEM). Figure 2.11 shows the  $|E_x|^2$  distributions right above the silicon dioxide surface along the dashed lines in the insets. The laser fluences of 0.012 and 0.029 J/cm<sup>2</sup> were calculated using the laser power used in the experiment and the zone plate efficiency of 15.8 % calculated in Chapter 2.2.3. The laser beam diameter in the simulation was 250 nm and the beam center was positioned 125 nm away from the end of the nanowire as shown in the right inset of Figure 2.11b. For all simulations, the electric field polarization of the incident laser was parallel to the nanowires. Figure 2.11a shows that the interference between the incident radiation and nanowire-scattered radiation causes a central peak and two side lobes in electric field intensity. The highest intensity of the electric field was at the end of the nanowire as shown in Figure 2.11b and this indicates that the nanowire grows at the tip. The distances between the central peak and the two side lobes are about 180 nm, which is close to the distance between simultaneously formed nanowires in the experiment. As the laser fluence increases, the field intensity at the two side lobes increases. Once the field intensity at the two side lobes becomes high enough to heat the silicon dioxide surface to the temperature required for silane decomposition, three nanowires will be simultaneously formed. Figure 2.11c shows the electric field distribution when three nanowires are formed. High intensity areas are found at the ends of the nanowires, illustrating the nanowire growth at the tip of each nanowire. The center nanowire is longer than the two side nanowires and this is also observed in the experiment (Figure 2.12).

Figure 2.11. Electric field distributions during nanowire growth (Mitchell et al., 2014).

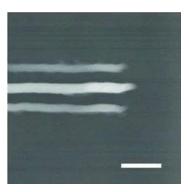

Figure 2.12. SEM image of the ends of triple nanowires. The scale bar is 400 nm (Mitchell et al., 2014).

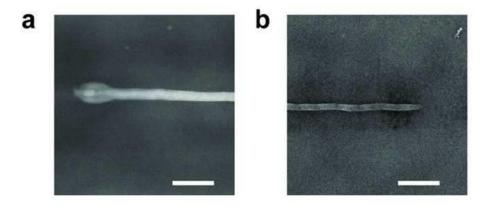

The simulation illustrates the nanowire formation when a nanowire already exists on the laser spot. However, the beginning of the nanowire formation cannot be explained by the interference effect because there is no scattering center at first. Indeed, a large initial deposition is often observed in the experiment (Figure 2.13a) because the incident radiation heats up the oxide surface without the confinement needed for sub-diffraction limited nanowires. Figure 2.13a also shows that as the scanning continues, the wire diameter quickly decreases due to the aforementioned interference. The end of the nanowire in Figure 2.13b, on the other hand, shows no sign of large deposition because the interference is already stable.

Figure 2.13. SEM images of (a) the start and (b) the end of a nanowire. The scale bars are 400 nm (Mitchell et al., 2014).

To sum up, the direct heating by the incident laser creates an unstable initial deposition of silicon. The initially deposited silicon scatters the incident laser and the interference between the incident laser beam and the scattered irradiation begins to occur. A spatially confined, periodic surface heating is generated due to the interference effect and consequently nanowires with sub-diffraction limited diameters are synthesized. It is also worth noting that the laser fluence in the experiment is far below the ablation threshold of the surface silicon oxide and therefore surface plasmons which are often mentioned as a cause of LIPSS formation plays no role in the formation of our nanowires (Mitchell et al., 2014).

#### 2.3.3 Micro-structure of Silicon Nanowires

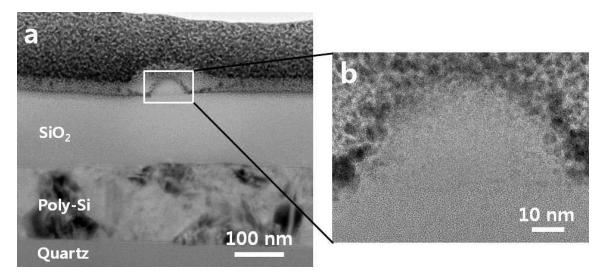

The laser direct written silicon nanowires were analyzed using transmission electron microscopy (TEM). Figure 2.14 shows the cross-section TEM images of an as-deposited nanowire. The nanowire has a semi-circular cross-section with a width of about 60 nm and a height of about 30 nm. No periodic atomic structure is observed in Figure 2.14b, indicating that the nanowire is composed of amorphous silicon. Figure 2.14a shows that the silicon oxide layer under the nanowire is completely intact, demonstrating that the laser irradiation during the nanowire formation causes no damage on the oxide surface. The image also shows the structure of the substrate with 200 nm thick silicon dioxide and 200 nm thick poly-Si layers. The platinum layers over the nanowire were deposited for TEM sample preparation.

Figure 2.14. Cross-section TEM images of an as-deposited nanowire.

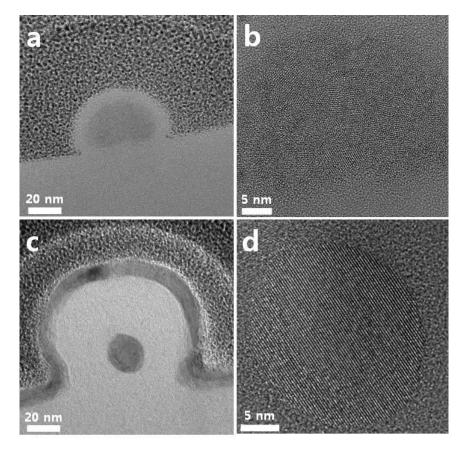

Although the amorphous silicon nanowire has usefulness for some applications such as thin-film transistors (TFTs) for displays, single-crystalline or polycrystalline silicon is preferred in most cases due to its superior electrical properties. In order to crystallize the amorphous nanowires, we annealed the nanowires and examined the micro-structure of the annealed nanowires using TEM. Figure 2.15a and b show the cross-section TEM images of a nanowire annealed at 700 °C for 12 hours. Small grains with diameters of 2-7 nm are observed in Figure 2.15b, indicating that the nanowire crystallized into polycrystalline silicon. Although the annealing was done with  $N_2$  flow, the outside of the nanowire was unintentionally oxidized due to a small amount of  $O_2$  which remained in the annealing chamber. We expect that this oxidation can be minimized by deliberately purging  $O_2$  residue from the chamber. Figure 2.15c and d show the cross-section of a nanowire annealed at 1100 °C for 2 hours. Severe oxidation is observed on the outside of the nanowire and the diameter of the central silicon is reduced to about 20 nm. Note that the diameter of the oxidized nanowire increased and the shape of the nanowire is not semi-circular any more because silicon expands 2.17 times in thickness when oxidized. The central silicon is single-crystalline in Figure. 2.15d. However, the nanowire is most likely to have multiple grains along the axial direction because the nanowire is tens of micrometers long.

Figure 2.15. TEM cross-section images of silicon nanowires annealed (a-b) at 700 °C for 12 hours and (c-d) at 1100 °C for 2 hours.

# 2.4 <u>Summary</u>

In this chapter, the laser-direct-writing method to synthesize silicon nanowires has been described. The femtosecond pulsed lasers and optical components including filters, lenses, and frequency-doubling crystals are used to provide a spatially confined heating required for silane decomposition. The CVD system was deliberately designed to deliver gases, control gas flow rates, and accurately move a substrate. The substrates were prepared to have Si and  $SiO_2$  layers on quartz.

The Fresnel zone plate is one of the most important optics in the experiment which focuses the incident laser beam into a diffraction-limited spot size. In order to analyze the focusing capacity of the zone plates, the modified Rayleigh-Sommerfeld diffraction integral was used and the spot size and the efficiency of the zone plates were calculated. It was also shown that the zone plates are tolerant of fabrication errors, but sensitive to variation in the incident wavelength.

In addition, we have discussed the experimental parameters which affect the nanowire formation. The polarization direction of the incident laser is one of the parameters which determine the shape of synthesized nanowires and the laser power mainly determines the number of simultaneously formed nanowires. The experimental results and numerical calculations have explained that the interference between the incident laser and surface-scattered radiation plays a critical role in producing sub-diffraction limited nanowires. The synthesized nanowires were amorphous silicon and could be crystallized into poly-Si.

35

## CHAPTER 3. SILICON NANOWIRE FIELD EFFECT TRANSISTOR SENSORS

Over the past decades, field effect transistor (FET) sensors, in which the surface potential of the conduction channel is modulated by charged molecules, have garnered significant research interest for chemical and biological applications. Recently, it has been shown that the use of nanoscale materials such as silicon nanowires (SiNWs) can significantly improve the sensitivity of FET sensors, allowing detection of a very low concentration of analytes (Cui et al., 2001; Stern et al., 2007). Due to the large surface-tovolume ratio, nanoscale Si FETs are expected to have excellent sensitivity (Chen et al., 2007). Label-free, direct electrical detection is another advantage of FET sensors. However, complex procedures for integrating nanowires into a nanosensor remain an obstacle for widespread applications. The "bottom up" approach requires assembly of nanowires grown from chemical vapor deposition (CVD) (Patolsky et al., 2006), which not only involves CMOS incompatible processes but also suffers from difficulty in precisely positioning nanowires. Metal contamination from catalysts used during CVD growth is another disadvantage. Alternative "top-down" methods are proposed to overcome these shortcomings, providing CMOS compatibility and precise control of nanowire position (Stern et al., 2007; Hakim et al., 2012). The "top-down" approaches require complex, multiple fabrication steps for nanowire patterning, etching, and doping.

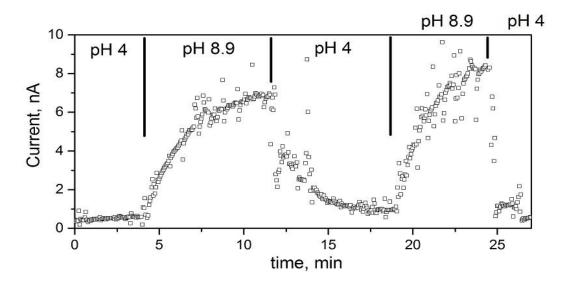

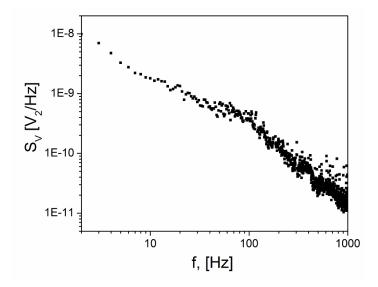

In this chapter, we describe fabricating Si FET sensors with laser direct written silicon wires which have diameters of a few hundred nm. Our laser direct writing method enables one-step nanowire fabrication, eliminating the need for nanowire positioning, etching, and doping. The unique feature of the fabricated Si wires is that they can have very rough surfaces which are beneficial for sensing applications due to their large surface area. In addition, our approach features in situ doping, catalyst-free growth, and excellent control of position, orientation, and length. Laser direct written Si FETs were employed to detect the proton concentration (pH) of an aqueous solution.

## 3.1 Basic Principles of FET Sensors

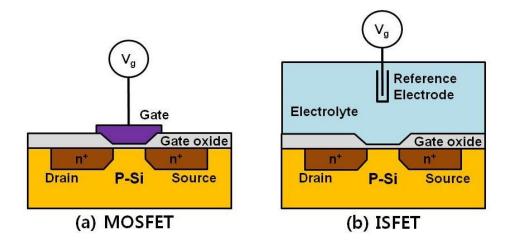

Among the different types of FET sensors, ion-sensitive field-effect transistors (ISFETs) are the most fundamental sensor devices. Most of the other FET sensors can be constructed by modifying the gate of an ISFET or coupling the surface of the gate oxide with different receptors, such as antibodies, nucleic acids, and cells. The ISFET bears a close similarity to a MOSFET. The main difference between an ISFET and a MOSFET is that there is no metal gate electrode in the ISFET. Instead, a gate voltage can be applied through a reference electrode (*e.g.*, Ag/AgCl electrode) inserted in an aqueous solution which is in contact with the gate oxide in the ISFET (Figure 3.1b).

Figure 3.1. Schematic representation of (a) a MOSFET and (b) an ISFET.

Because of the similarities between an ISFET and a MOSFET, the ISFET operational mechanism is commonly described using the theoretical expressions of a MOSFET. The drain current of the MOSFET,  $I_d$ , in the non-saturated mode is given by the following equation (Sze and Ng, 2007):

$$I_d = \mu C_{ox} \frac{W}{L} \left( V_g - V_t - \frac{1}{2} V_d \right) V_d$$

(3.1)

where  $\mu$  is the electron mobility in the channel,  $C_{ox}$  is the oxide capacitance per unit area, W and L are the width and the length of the channel,  $V_g$  is the gate voltage,  $V_t$  is the threshold voltage, and  $V_d$  is the drain-source voltage. Eq. (3.1) can be also used for an ISFET in spite of the absence of a gate electrode. In the case of an ISFET, the gate voltage,  $V_g$ , which is applied to the reference electrode creates an electric field across the electrolyte and the solution/oxide interface, and this electric field induces an inversion layer in the channel when  $V_g$  is high enough. The effects of the reference electrode and the solution/oxide interface manifest themselves in the threshold voltage,  $V_t$ . For a MOSFET, the threshold voltage,  $V_t$ , is given by

$$V_{t} = \frac{\Phi_{M} - \Phi_{Si}}{q} - \frac{Q_{ox} + Q_{ss} + Q_{B}}{C_{ox}} + 2\phi_{f}$$

(3.2)

where the first term means the work-function difference between the gate metal ( $\Phi_M$ ) and the silicon channel ( $\Phi_{Si}$ ),  $Q_{ox}$  is the oxide-trapped charge density,  $Q_{ss}$  is the charge density at the oxide-silicon interface,  $Q_B$  is the depletion charge density in the silicon channel, and  $\phi_f$  is the Fermi level of the silicon from the intrinsic Fermi level which is a function of the doping concentration of the silicon. In an ISFET, the metal work-function,  $\Phi_M$ , is replaced by the potential of the reference electrode,  $E_{ref}$ , the solution/oxide potential,  $\varphi$ , which depends on the activity of ions in the solution, and the surface dipole potential,  $\chi_{sol}$ , of the solution. Therefore, the threshold voltage of the ISFET is (Bergveld, 2003)

$$V_{t} = E_{ref} - \varphi + \chi_{sol} - \frac{\Phi_{Si}}{q} - \frac{Q_{ox} + Q_{ss} + Q_{B}}{C_{ox}} + 2\phi_{f}$$

(3.3)

Finally, the drain current of the ISFET,  $I_d$ , becomes (Schöning and Poghossian, 2002)

$$I_{d} = \mu C_{ox} \frac{W}{L} \left[ V_{g} - \left( E_{ref} - \varphi + \chi_{sol} - \frac{\Phi_{Si}}{q} - \frac{Q_{ox} + Q_{ss} + Q_{B}}{C_{ox}} + 2\phi_{f} \right) - \frac{1}{2} V_{d} \right] V_{d} \quad (3.4)$$

The interface potential,  $\varphi$ , can be changed chemically, for example, by changing the pH of the solution and this means that the threshold voltage,  $V_t$ , and correspondingly the drain current,  $I_d$ , can be altered chemically without changing the applied voltages.

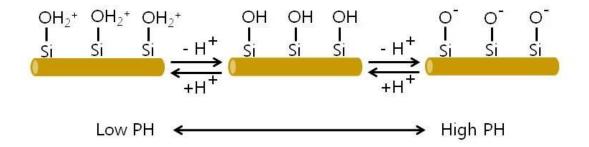

In the case of pH sensors, hydroxyl groups (-OH) on the oxide surface act as active sites which are able to bind or release hydrogen ions in an electrolyte. The hydroxyl groups can be neutral, protonized or deprotonized depending on the pH of the solution (Figure 3.2). They are positively charged when protonized to  $OH_2^+$  and negatively

charged when deprotonated to O<sup>-</sup>. Therefore, the pH of the surrounding solution changes the amount of the surface charges and consequently the solution/oxide interface potential,  $\varphi$ . The pH dependence of the interface potential,  $\varphi$ , is described by the site-binding theory (Bousse et al., 1983):

$$\varphi = 2.303 \frac{kT}{q} \frac{\beta}{\beta + 1} (pH_{px} - pH)$$

(3.5)

with *k* as the Boltzmann constant, *T* as the absolute temperature,  $\beta$  as a dimensionless sensitivity parameter which is dependent on the density of surface hydroxyl groups and the surface reactivity, and  $pH_{pzc}$  as the pH at the point of zero charge. According to Eq. (3.4) and (3.5), a change in pH induces an alteration in the channel conductance and consequently the drain current, *I<sub>d</sub>*. Thus, the pH value of the test solution can be determined by measuring the drain current of the ISFET.

Figure 3.2. Protonation and deprotonation of hydroxyl groups in an aqueous solution.

Since the ISFET is very sensitive to an electrical interaction near the gate insulator surface, the sensor device can be used to detect a chemical or biological reaction leading to a potential change near the gate insulator surface. To this end, the surface of an ISFET is, in general, functionalized with chemical or biological receptors. Depending on the type of receptors used, the mechanism of potential generation is different. For example, an antigen-antibody affinity reaction or DNA hybridization will cause a surface polarization effect which affects the surface potential, whereas potential changes are caused by a catalytic reaction product on an enzyme-modified surface. However, the basic principles for an ISFET discussed in this chapter can be applied to most FET-based sensors.

#### 3.2 Laser Direct Writing of Silicon Wires for FET Sensors

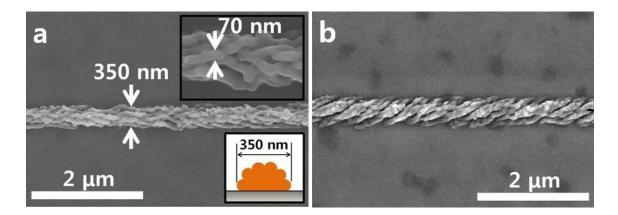

Silicon nanowires for FET sensors were synthesized using the laser direct writing method discussed in Chapter 2. The silicon nanowires were created using circularly polarized laser light at a pressure between 30 and 40 Torr with flow of 10 % silane in argon and 100 ppm diborane in hydrogen. In order to obtain a low doping concentration desirable for high sensitivity (Nair and Alam, 2007), we lightly doped the Si nanowires with a SiH<sub>4</sub>:B<sub>2</sub>H<sub>6</sub> mass flow ratio of 6,000:1. Figure 3.3 shows the SEM images of Si nanowires synthesized for FET sensors. The diameters of the nanowires are between 300 and 500 nm and they have rough surfaces which are desirable for high sensitivity due to their large surface areas. The nanowire in Figure 3.3a is an agglomerate of 70 nm-thick nanowires as shown in the upper inset of Figure 3.3a. Using the cross section in the lower inset of Figure 3.3a, we calculated the surface-to-volume ratio of the nanowire to be 1.4 times that of a smooth, cylindrical wire of the same thickness. However, if we consider the 350 nm wire consisting of strands of 70 nm wires, which is closer to what is shown in the upper inset of Figure 3.3a, the surface-to-volume ratio will be about 5 times that of the smooth nanowire. Therefore, the actual surface-to-volume ratio can be between 1.4 and 5 times that of a smooth wire.

Figure 3.3. SEM images of laser direct written silicon wires (Nam et al., 2013).

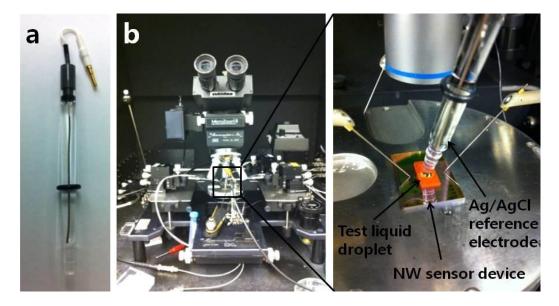

#### 3.3 Fabrication of Silicon Nanowire FET Sensors

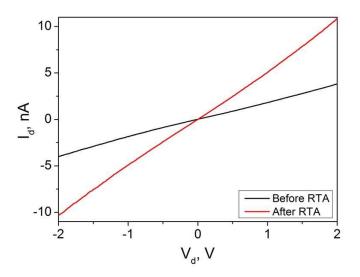

The laser direct written silicon nanowires were annealed at 1000 °C in argon for 30 minutes to crystallize and activate dopant atoms. Source/drain contacts were then patterned using photolithography. AZ1518 photoresist and a Suss MJB-3 mask aligner were used for the photolithography. The photoresist-patterned device chip was treated with  $O_2$  plasma to remove a photoresist residue in the exposed area and etched in buffered oxide etch for 5 seconds to remove native oxide on the silicon surface. Subsequently, a 100 nm-thick Ni layer was deposited using electron beam evaporation and source/drain contacts were created with a liftoff process. The metalized nanosensors were annealed using rapid thermal annealing at 400 °C in forming gas (4 % H<sub>2</sub>/ 96 % N<sub>2</sub>) for 2 minutes to form low-resistance NiSi contacts at the interfaces between the Si wires and the Ni electrodes (Patolsky et al., 2006).

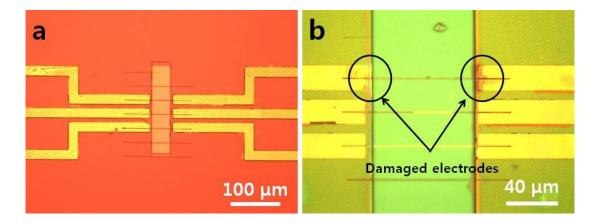

Since the sensor devices operate in contact with an aqueous solution, it is essential to have a passivation layer on the device surface which prevents Ni electrodes from undergoing electrochemical corrosion in the solution. A combination of  $Si_3N_4$  and SU8layers was first tested for the passivation layer. A pattern for a liftoff of  $Si_3N_4$  was created using AZ1518 photoresist and photolithography. Then, 100-200 nm thick Si<sub>3</sub>N<sub>4</sub> was deposited using plasma-enhanced CVD at a low temperature of 95 °C to avoid thermal deformation of the photoresist as well as to facilitate the liftoff. Finally, an SU8 layer was deposited and patterned (Figure 3.4a). Although the passivation layers of Si<sub>3</sub>N<sub>4</sub> and SU8 effectively protected most of the Ni electrodes, an electrochemical corrosion was observed near the silicon channel (Figure 3.4b), which is near the open edge of the passivation layers, after an extended operation of the device in a solution. This indicates that the Si<sub>3</sub>N<sub>4</sub> coating was not conformal and the aqueous solution leaked into the electrodes because of the poor adhesion between SU8 and the underlying layer.

Figure 3.4. Optical images of (a) a Si FET sensor device with Si<sub>3</sub>N<sub>4</sub> and SU8 passivation layers and (b) electrochemically damaged electrodes after a pH sensing experiment.

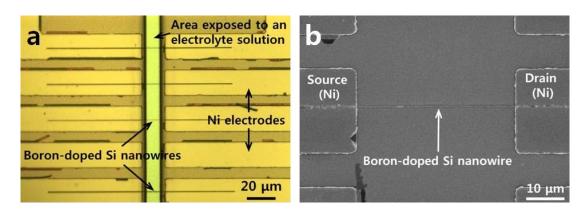

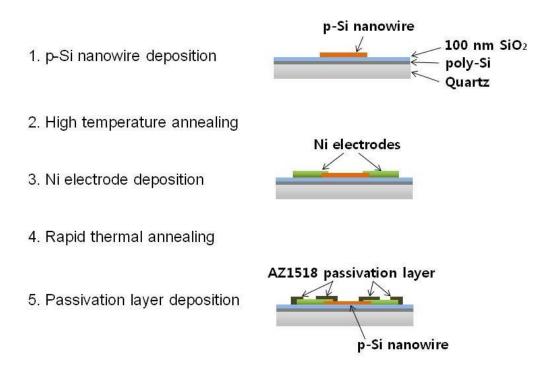

AZ1518 photoresist was also tested for the passivation layer because of its excellent adhesion to the SiO<sub>2</sub> substrate. The AZ1518 photoresist was patterned and baked at 120 °C for 30 minutes. Although an increase in gate leakage current was detected when a high gate voltage was applied to the reference electrode, the AZ1518 passivation layer kept the gate leakage current very small at a low gate voltage and suppressed the corrosion of the Ni electrodes effectively. Therefore, AZ1518 passivation was used for FET sensors in the following chapters. Figure 3.5a shows an optical image of a typical device with four Si wires aligned horizontally. In the device, the separation between source/drain contacts is 20  $\mu$ m and the width of the vertical channel exposed to an electrolyte solution in the pH sensing experiment is 10  $\mu$ m. The device fabrication procedure is illustrated in Figure 3.6.

Figure 3.5. (a) Optical image of a laser direct written Si FET sensor. (b) SEM image of a Si FET sensor without a passivation layer.

Figure 3.6. Schematic illustration of the device fabrication procedure.

#### 3.4 Experimental Setup for pH Sensing Tests

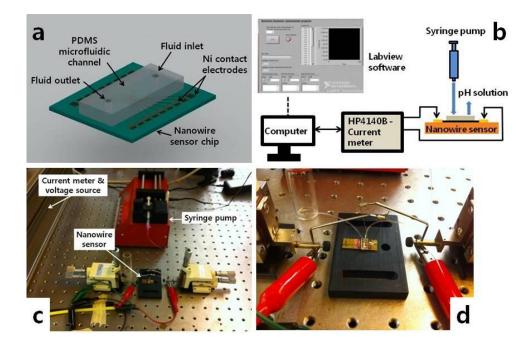

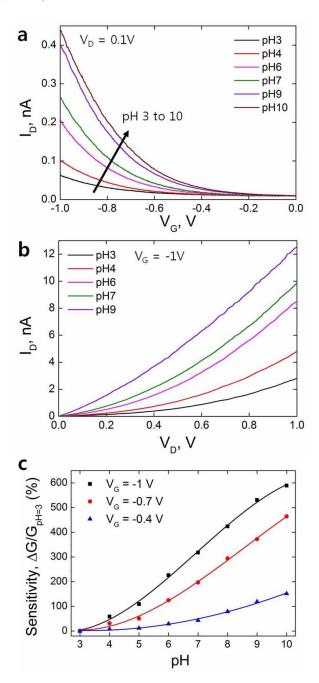

Two different experimental setups were used for the pH sensing experiment. For the real-time measurement of the drain current, an HP 4140B pA meter was used to apply a drain voltage and measure the consequent drain current. The current meter was connected to a computer and controlled by a custom-written Labview program. Standard pH buffer solutions (pH 3-10) were purchased from EMD Chemicals, Inc. and a syringe pump delivered pH solutions to an FET sensor at a constant flow rate of 50  $\mu$ L/min. A custom-made PDMS microfluidic channel with a volume of about 2  $\mu$ L was placed on the sensor surface to hold pH solutions. The measurement setup is shown in Figure 3.7.

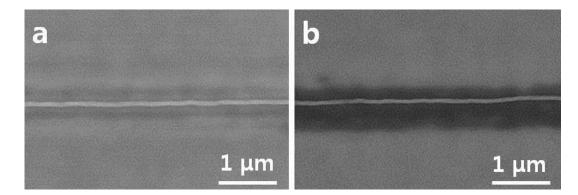

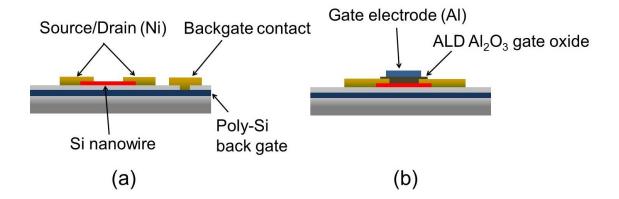

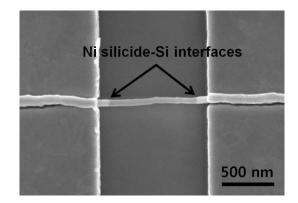

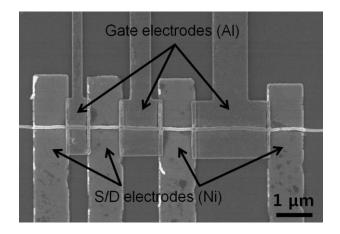

Figure 3.7. (a) Schematic of an FET sensor chip with a microfluidic channel. (b) Schematic of the experimental setup for a real-time pH sensing test. (c-d) Images of the measurement setup with a fabricated sensor device.