| 1 |   | 3 1 |     | I ( |   | V | 0 | F | 1 ( | J : | 1 | 1 | 1 1 | -1 |   | <u> </u> | <u> </u> |   |

|---|---|-----|-----|-----|---|---|---|---|-----|-----|---|---|-----|----|---|----------|----------|---|

| М | A | С   | H   | I   | N | Е | - | I | N   | D   | E | P | E   | N  | D | Е        | N        | Т |

|   |   | (   | 5 0 | D I |   | Ξ |   | G | E   | N   | E | R | A   | Т  | 0 | R        |          |   |

Thesis submitted by <u>PETER GRAHAM CLAYTON</u> in fulfilment of the requirements for the degree of <u>MASTER OF SCIENCE</u> RHODES UNIVERSITY

DECEMBER 1983

### ACKNOWLEDGEMENTS

My thanks are due to Professor Pat Terry, for help and encouragement which has extended way beyond the limits of this thesis, and for permission to make use of much of his software, and to Louisa for her support and help in preparing this report.

### ABSTRACT

As both computer languages and architectures continue to proliferate, there is a continuing need for new compilers. Researchers have attempted to ease the work of producing compilers by developing methods to automate compiler writing. While much work has been done (and considerable success achieved) in writing parsers which can handle a variety of source languages (using mainly table-driven analysis methods), less progress has been made in formalizing the code generation end of the compiler. Nevertheless, some of the more recent publications in code generation stress portability or retargetability of the resulting compiler. A number of code generator synthesisers have been developed, some of which produce code that can be compared in quality with that produced by a conventional code generator. However, because of the complexity of generalizing the mapping from source language to target machine, and the need for efficiency of various kinds, code generator large, complicated synthesisers are programs. Consequently, the person who develops a code generator using one of these tools invariably needs to be a code generation specialist himself.

Many compilers follow a pattern of having a front end which generates intermediate code, and a back end which converts intermediate code to machine code. The intermediate code is effectively machine independent, or can be designed that way.

With these points in mind, we have set out to write a system of programs which

- will allow the generation of such a back end in a reasonably short time, for a general intermediate code, and for a general machine code, and

- 2. can be used by anyone who has a sound knowledge of the target machine's architecture and associated assembler language, but is not necessarily a specialist compiler writer.

The system consists of a series of friendly, interactive programs by means of which the user sets up tables defining the architecture and assembly level instructions for the target machine, and the code templates onto which intermediate codes produced by a parser have been mapped. A general notation has been developed to represent machine instructions using the same format as the target assembler. Thus the code generator writer is able to write code sequences to perform the effects of the intermediate codes, using assembly mnemonics familiar to him. The resultant table-driven code generator simply replaces a sequence of intermediate codes by their respective codetemplates, relocating them in memory and filling in addresses known only at code-generation time.

This thesis describes the use and implementation details of this generalized code generation system. As an example, the implementation of a code generator for a CLANG <sup>[23]</sup> parser on an 8080 processor is described. The discussion also includes guide-lines on how to implement a loader and associated run-time routines for use in executing the object code.

The results of a number of bench-marks have shown, as expected, that code produced by a code generator developed in this manner is larger and slower than that from a special purpose optimizing code generator, but is still several times faster than interpreting the intermediate code. The major benefit to be gained from using this system lies in the shorter development time by a less skilled person.

## CONTENTS

| Intr | oduction                                                                 | 8        |

|------|--------------------------------------------------------------------------|----------|

| 1.1  | Compilers in Brief                                                       | 9        |

|      | 1.1.1 Lexical Analysis                                                   | 10       |

|      | 1.1.2 Syntax Analysis                                                    | 11       |

|      | 1.1.3 Semantic Analysis                                                  | 11       |

|      | 1.1.4 Code Optimization                                                  | 12       |

|      | 1.1.5 Code Generation                                                    | 13       |

| 1.2  | Automated Code Generator Writing                                         | 14       |

| 1.3  | Why another Machine-Independent Code<br>Generator ?                      | 17       |

| 1.4  | Outline of the Remainder of the Thesis                                   | 19       |

| over | view Of The Generalized Code Generator<br>The Machine Definition Program | 21<br>22 |

| 2.2  | The Code-Skeleton Definition Program                                     | 39       |

| 2.3  |                                                                          | 50       |

| 2.4  | When To Use The Programs                                                 | 50       |

|      | ample Implementation                                                     | 52       |

| 3.1  | The CLANG Compiler                                                       | 52       |

| 3.2  | The Machine Definition                                                   | 53       |

| 3.3  | Code-Skeleton Definitions                                                | 59       |

| 3.4  | The Code-Generation Driving Table                                        | 67       |

| 3.5  | A Sample Program                                                         | 69       |

|      |                                                                          |          |

-5-

PAGE

The second secon

CONTENTS -6-

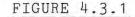

| 4. | Writing a Loader and Standard Run-time Routines  | 73 |

|----|--------------------------------------------------|----|

|    | 4.1 Implications of the Loading Process          | 74 |

|    | 4.2 Run-Time Support Packages                    | 75 |

|    | 4.3 A Sample Implementation                      | 76 |

| 5. | The Mark 3 System                                | 79 |

|    | 5.1 Memory Allocation at Code Generation<br>Time | 79 |

|    | 5.2 Improved Code-Skeleton Definitions           | 82 |

|    | 5.3 Optimization                                 | 83 |

|    | 5.4 Compiling Separate Modules                   | 88 |

| 6. | Historical Remarks and Conclusions               | 90 |

## PART 2 - A User Manual

| 7. | Usin | Using The Machine Definition Program |                                   |     |  |  |  |  |  |  |  |  |

|----|------|--------------------------------------|-----------------------------------|-----|--|--|--|--|--|--|--|--|

|    | 7.1  | Current                              | Implementation Requirements       | 93  |  |  |  |  |  |  |  |  |

|    | 7.2  | Driving                              | The Program                       | 94  |  |  |  |  |  |  |  |  |

|    |      | 7.2.1                                | Word Definition Mode              | 95  |  |  |  |  |  |  |  |  |

|    |      | 7.2.2                                | Instruction Definition Mode       | 97  |  |  |  |  |  |  |  |  |

|    |      | 7.2.3                                | Editing Word Definitions          | 107 |  |  |  |  |  |  |  |  |

|    |      | 7.2.4                                | Editing Instruction Definitions   | 111 |  |  |  |  |  |  |  |  |

|    |      | 7.2.5                                | Reading Definitions From a File   | 114 |  |  |  |  |  |  |  |  |

|    |      | 7.2.6                                | Listing Definitions To the Screen | 115 |  |  |  |  |  |  |  |  |

|    |      | 7.2.7                                | Exiting the Program               | 116 |  |  |  |  |  |  |  |  |

|    | 7.3  | Error Co                             | onditions                         | 117 |  |  |  |  |  |  |  |  |

| 8. | Usin | g The Co                             | de-Skeleton Definition Program    | 120 |  |  |  |  |  |  |  |  |

|    | 8.1  | Current                              | Implementation Requirements       | 120 |  |  |  |  |  |  |  |  |

CONTENTS -7-

| 8.2       | Driving '  | The Program                                     | 121 |

|-----------|------------|-------------------------------------------------|-----|

|           | 8.2.1      | Editing or Defining a Code-<br>Skeleton         | 123 |

|           | 8.2.2      | Editing or Defining a Run-Time<br>Subroutine    | 132 |

|           | 8.2.3      | Deleting a Code-Skeleton                        | 134 |

|           | 8.2.4      | Deleting a Run-Time Subroutine                  | 135 |

|           | 8.2.5      | Listing a Code-Skeleton to the<br>Screen        | 135 |

|           | 8.2.6      | Listing a Run-Time Subroutine<br>to the Screen  | 135 |

|           | 8.2.7      | Altering the Default Integer<br>Output Base     | 136 |

|           | 8.2.8      | Exiting the Program                             | 137 |

|           | 8.2.9      | A General Note on the Current<br>Implementation | 138 |

| 8.3       | Error Co   | nditions                                        | 139 |

| 9. Usir   | ng the Cod | e Generation Program                            | 141 |

| 9.1       | Current    | Implementation Requirements                     | 141 |

| 9.2       | The User   | 's Point of View                                | 141 |

| 9.3       | Implemen   | tor's Note                                      | 142 |

| REFERENCI | ES         |                                                 | 145 |

| APPENDIX  | A - The    | Machine Definition Program                      | 148 |

| APPENDIX  |            | Code-Skeleton Definition<br>gram                | 149 |

| APPENDIX  |            | General Code Generation<br>gram                 | 149 |

| APPENDIX  |            | Ø Monitor Routines and olute Loader             | 149 |

| APPENDIX  | E - The    | Clang Compiler                                  | 149 |

### 1. INTRODUCTION

...let's see if you can read my code:

VDDL RBT CLJKS NT PSD KLHSM ATFO

If you can read it, make it rain tomorrow so I will know.

from CHILDREN'S LETTERS TO GOD<sup>[1]</sup>

In the early days of computers, the esoteric nature of internal machine code did much to inhibit the computer revolution. While most humans find it difficult to understand the "language" of the central processing unit, most computer processors are completely devoid of conventional linguistic skills. The non-specialist was able to enjoy the use of a computer only once high-level languages had been developed.

In the last decade, many new general-purpose programming languages have emerged, along with a large number of more specialised languages. Since no major breakthrough has been achieved in "humanizing" the computer processor's communicative ability, the design and implementation of compilers for programming languages has become an essential part of systems software development. Although the construction of new compilers is being made easier by the use of various language development tools, the implementation of a compiler for a major high-level language remains a non-trivial task.

### 1.1 COMPILERS IN BRIEF

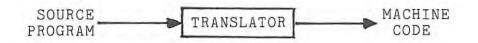

A compiler is a computer program which translates programs, written in a particular source programming language, into executable code for a target computer of a particular design.

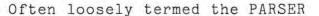

The compilation process is usually subdivided into a sequence of simpler phases. It is convenient to think of each phase as an operation which takes, as input, one representation of the source program and produces, as output, another representation. Most compilers consist of at least the following phases:

The boundries between phases are blurred. Two or more of the phases above may often be combined into one phase. The modern trend towards "intelligent" editors, has seen some of the initial stages of the compiler incorporated into complementary editors. In some interpretive systems, the compilation process may be completely transparent to the user.

A brief description of the operation of each phase appears below. More information on the historical development of compilers can be found in articles by Knuth <sup>[4]</sup>, Feldman and Gries <sup>[5]</sup> (which also includes a comprehensive bibliography up to that time) and Aho <sup>[6]</sup> and in many modern textbooks on compilers <sup>[7]-[11]</sup>.

### 1.1.1 Lexical Analysis (or scanning)

The name is derived from LEXICON [Greek] meaning DICTIONARY. This initial parsing phase sees the source program as a sequence of characters. These characters are grouped into tokens, which are substrings of the input stream which logically belong together, such as identifiers and constants. The lexical analyser is usually also responsible for recognising comments, blanks and separators in the source program. The output of the lexical analysis phase is a stream of tokens.

### 1.1.2 Syntax Analysis (or true parsing phase)

This phase groups tokens emitted by the lexical analyser into syntactic structures such as expressions and statements. It is the syntax analyser that determines whether the source program satisfies the formation rules of the programming language. If the source program is not syntactically correct, this phase must be able to produce appropriate error diagnostics, and recover from each error, so as to catch any subsequent errors that might be present.

The syntax analyser usually invokes some semantic action as each syntactic construct is recognised. The semantic action may be to enter some information into a table, emit some error diagnostics, or generate some output. The output of the syntax analyser is some intermediate language representation of the source program such as postfix Polish notation, a tree structure, quadruples or codes for a hypothetical stack machine.

### 1.1.3 Semantic Analysis

This phase has to do with the actual meaning of words and constructs. Type checking, determining that functions are called with the appropriate number of arguments, and verifying that identifiers have been declared are typical of what takes place during semantic analysis.

### 1.1.4 Code Optimization

An optimizing compiler attempts to transform an intermediate language representation of the source program into one from which a faster or smaller object program can be generated. The term "optimization" is something of a misnomer, as it is theoretically impossible for a compiler to produce the best possible object program for every source program. A more accurate term might be "code improvement" as suggested by Aho & Ullman <sup>[7]</sup>. Tradition, however, has given us the term "code optimization".

A number of optimizations can be safely performed only by knowing information gathered from the entire program. One needs to make use of a technique known as Global Data-flow Analysis <sup>[2] [3]</sup>. Other forms of optimization are static, for example the well known peephole optimization technique <sup>[7]</sup>. This attempts to improve the generated code, by viewing a small range of instructions (peephole) and trying to improve upon them. It is a characteristic of peephole optimization that each improvement may spawn opportunities for additional improvements. Thus, repeated passes over the code are necessary to get the maximum benefit. Peephole optimization can be applied at both the intermediate and final code stages.

### 1.1.5 Code Generation

The code generator is the final stage of the compiler and usually incorporates the optimization algorithms. This phase produces machine code directly, and is therefore the non-portable component of a compiler.

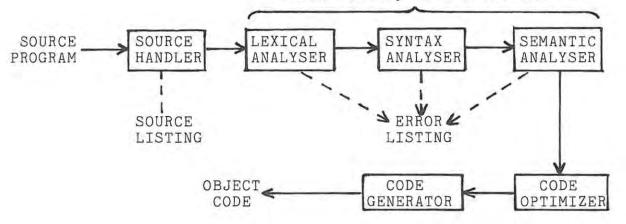

To promote portability and decrease the complexity of the translation algorithms, the code generation phase in a modern compiler is usually written as a completely separate module. Communication with the more easily transportable parts of the compiler is by means of a clearly defined set of intermediate codes.

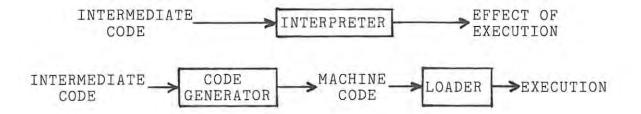

The compiler writer then has the option of either interpreting the intermediate codes, or of converting them to machine code.

### 1.2 AUTOMATED CODE GENERATOR WRITING

Recently. much interest has been shown in tools that reduce the effort needed to construct a good compiler. These go by names such as compiler-compilers, translator writing systems or compiler generators.

To date, more work has been done on automating the front end of the compiler (possibly since this can be done without regard to target machine architecture) than the code generation end (which is target machine dependent). Considerable success has been achieved, using mainly tabledriven analysis methods <sup>[7]</sup>, towards making this aspect of compiler writing not only easier, but more reliable. It is easier to check that a grammar is an accurate syntax description than it is to check the implicit description embodied in the logic of a syntax analysis program.

While less progress has been made in formalizing the code generation end of the compiler, a number of successful code generator synthesisers have been developed  $\begin{bmatrix} 14 \end{bmatrix} - \begin{bmatrix} 21 \end{bmatrix}$ . The emphasis here lies in the portability or retargetability of the resulting compiler.

In attempting to provide tools for automating code generation, most researchers have again turned to table driven methods. By using a table-driven syntax analyser, we can handle the analysis of a new language by giving a new grammar to the table building program and then providing the new table to the analyser. Similarly, by presenting a description of a new target machine to the code generator's table-building program, we can retarget the code generator to produce code for the new machine.

A portable C compiler has been developed at Bell Laboratories, Murray Hill <sup>[14]</sup>. This compiler incorporates programs such as LEX, a lexical analyser generator, and YACC (Yet Another Compiler-Compiler), which generates parsers from an input specification language that describes the desired syntax, both well known to users of the UNIX <sup>[37]</sup> system. The code generator uses a table consisting of a collection of templates. Each template contains a pattern to search for in a previously generated intermediate program form. This demands a lot of work from the implementor, who must specify each template. The portable C compiler provides code of reasonable quality, and has been retargeted successfully on over a dozen machine types.

Another table-driven code generator is under development at the University of California, Berkeley [15] [21], in which the templates are generated automatically, instead of being written by the implementor. The added generality is both a strength and a weakness. There is less work involved in developing a code generator using this tool, but it is claimed [15] that both the quality of the code generated and the speed of the code generator are significantly reduced when compared with the C compiler.

An ambitious compiler-compiler project has been undertaken by a large group of researchers at Carnegie-Mellon University <sup>[16] [19]</sup>. The goal of this project is to develop a compiler-compiler that is capable of producing highquality optimizing compilers from formal machine and language descriptions. Known as the PQCC (Production-Quality Compiler-Compiler), this enormous project boasts good code that can be compared with that of a conventional code generator.

A number of other fruitful investigations into compilerbuilding methods are being conducted at various research institutes around the world. A recently revised bibliography of the subject has been published by Ganapathi and Fisher [20].

Because of the complexity of generalizing the mapping from source language to target machine, and the need for efficiency of various kinds, code generator synthesisers are large, complicated programs. Consequently, the person who develops a code generator using one of these tools invariably needs to be a code generation specialist himself.

### 1.3 WHY ANOTHER MACHINE-INDEPENDENT CODE GENERATOR ?

All the code generator generators studied in the literature satisfy, to varying degrees, the aims of their authors. Without exception, they reduce the amount of work required in developing new compilers or transporting existing compilers to a new system. However, they are also, without exception, large programs. Very few code generator synthesisers can be run on any machine smaller than a mainframe. In addition, all the systems studied require of the implementor some knowledge of code generation and optimization techniques.

At Rhodes University, microcomputers of various manufacture are widely used. The most popular operating system is the UCSD p-System, which interprets its object programs. Since most undergraduate students spend far more time compiling their programs than running them, the slow interpreter does not prove to be a handicap. However, interpretation becomes an impeding factor if new systems programs are developed on the UCSD p-System. An example of such a systems program is the CLANG compiler <sup>[23]</sup>, developed at Rhodes University on the UCSD p-System. The entire compiler is interpreted and, since the CLANG system also interprets the codes it produces, the effect of executing object programs is accomplished by two levels of interpretation. An obvious gain in speed would be achieved if at least one (but preferably both) of the levels of interpretation was replaced by direct execution.

Since new machine architectures are acquired from time to time, a transportable compiler would also reduce the amount of effort needed by supervisors and teachers before students could write programs in familiar languages on new systems.

A project was undertaken at Rhodes University to write a system of programs which would generate code generators for both large and small computers. The resultant code generators would take their input from parsers which produce some suitable form of intermediate code. At the same time, an attempt was made to satisfy the following criteria:

- the code generator should be up and going in a reasonably short time, and

- 2. the person developing the code generator would not have to be a specialist compiler writer. In fact, a sound knowledge of the target machine's architecture and associated assembler language should be sufficient.

### 1.4 OUTLINE OF THE REMAINDER OF THE THESIS

Much of the work described in this thesis is of a highly technical nature, and it becomes difficult, if not tedious, to discern the intent from the details. Accordingly, the remainder of this report is divided into three sections. The first describes the system in fairly broad detail, gives an example of an actual system produced, and discusses briefly refinements which have been made to the system in the closing stages of the project. The second describes how the system might be used to construct further code generators, both like that described in the first section. and for other architectures. The third and most technical section has, due to its bulk, been confined to a set of appendices. This section discusses implementation details of the system, which will be of interest only to those wishing to extend its basic philosophy. Code for all programs appear with the implementation details in the appendices.

# PART 1

# INTENT AND ACCOMPLISHMENT

### 2. OVERVIEW OF THE THE GENERALIZED CODE GENERATOR

Faced with the major problem of trying to design a truly general machine representation, it was decided that code optimization would have to be sacrificed in the interests of ease of use. The most successful retargetable compilers have been those with minimal processing at the code generation stage, while the most successful optimizing compilers have been designed around a particular target machine. A general compiler can achieve both goals only if it relies on the compiler writer to provide the optimization information.

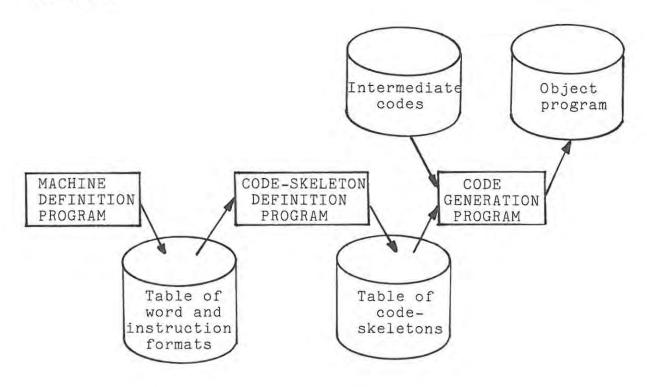

The system to be described consists of two definition programs, and a general table-driven code generation program.

This system has been written for use with any parser which produces intermediate codes which are effectively machine instructions for a hypothetical stack machine  $\begin{bmatrix} 11 \end{bmatrix} \begin{bmatrix} 12 \end{bmatrix}$  $\begin{bmatrix} 23 \end{bmatrix}$ . Two parsers of this type have been used to test the code generator. One for a relatively simple system  $\begin{bmatrix} 23 \end{bmatrix}$ , the other for a system similar to the Pascal P4 compiler  $\begin{bmatrix} 39 \end{bmatrix}$ . Other forms of intermediate codes, such as three-address codes  $\begin{bmatrix} 7 \end{bmatrix}$ , require slightly different assumptions, but the notation described below should prove effective for these codes as well without major alteration.

### 2.1 THE MACHINE DEFINITION PROGRAM

This table construction program takes as input a description of the target machine. The nature of the description differs considerably from the corresponding table construction programs of other well known compilercompilers. All table-driven code generators demand certain details of the target machine, notably the bit-patterns of instruction opcodes. Several well known products, for example the Berkeley project <sup>[15]</sup> <sup>[21]</sup>, require details of the way in which registers are designated and the selection strategy to be used in allocating registers and in choosing which ones to save and re-use if there are not enough. Since these projects attempt to reorder computations to produce a smaller object code, other parts of the machine description indicate which operators are commutative and whether frequently-used constants are given permanent register or memory storage. The code generator described in this thesis is driven by a template matching algorithm and, since the compiler-writer is required to define the templates, the criteria for using registers, constants and operands are decided by him, not by a program. In place of this information, the table construction program of this thesis collects details of assembly mnemonics which are used to write the templates.

### 2.1.1 Overview of Machine Instruction Formats

Although computer processors vary greatly in architecture, they do not disagree in their underlying principles so widely as to detract from a concept of code retargetability. In particular, all processors are capable of recognising a binary pattern as representing a particular operation, and of producing the effect of that operation.

To realise a retargetable code generator, one must be able to produce a set of instructions (the bit patterns) which the processor will recognise. This involves knowing such information as the length of each bit pattern and its value. In addition, if one is to allow non-sequential flow of control, one needs to know how many bits there are in the machine's smallest addressable unit. This enables an accurate **Program Counter** to be maintained, and consequently, jumping and looping instructions to be produced correctly.

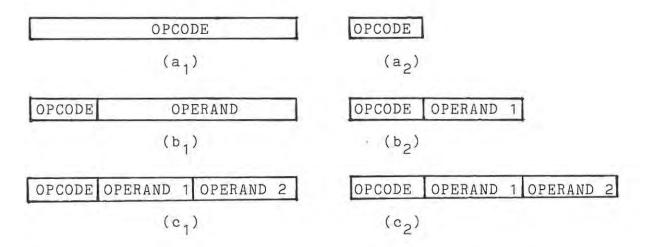

All machine level instructions must contain an operation code, or opcode for short, which indicates what action is to be performed. In addition, many instructions contain, or specify the location of, data used by the instruction. The fields used to specify data are known as operand or argument fields. These operand fields may be immediate data, the address of the data, a register name or the addressing mode which the instruction is to use.

On some machines, all instructions have the same length; on others, there may be several lengths. Moreover, instructions may be shorter, the same length as, or longer than the word (i.e. smallest addressable unit) length. Within a particular instruction length, various instruction formats may exist. Opcodes and operand fields may vary both in number and length.

In attempting to design a truly general definition for an

instruction, taking the enormous variety of possible instruction formats into account, a bit-by-bit definition appears to be the only solution.

### 2.1.2 A Notation for describing Instruction Formats

A notation has been developed for describing an instruction in terms of its length and the number and width of its fields. Each field is described by an alphabetic letter, which is repeated as many times as there are bits in the field. For example, an instruction format

| OPCODE | OPERAND | OPERANI |

|--------|---------|---------|

| <br>~  |         |         |

|        |         |         |

might be defined as

### FFFF FFFF AAAA BBBB

F represents a field which is eight bits wide. A and B represent fields which are each four bits wide. Spaces may be inserted for clarity and are ignored. The choice of alphabetic letter is completely arbitrary, but must be unique for the instruction in question.

Most processors have a small number of unique instruction formats, typically between 3 and 15. Several individual

instructions may share the same format. All the fields will agree in number and width, but the operand field will contain a different binary pattern for each instruction, representing a different operation. The size of the instruction set differs from computer to computer, typically within the range 60 to 300.

### 2.1.3 Input for the Machine Definition Program

The machine definition program allows a user to define all formats for a particular architecture (termed word formats for the purpose of this program) in the notation already described. Individual instructions may then be defined which conform to one of the word formats. This prevents unnecessary typing and reduces errors.

The aim of the machine definition program is to produce a set of instruction mnemonics which agree as closely as possible with those with which an assembler programmer of the target machine will be familiar.

Each instruction's definition must include the name, or mnemonic, by which the instruction will be known. The mnemonic is really representative of the binary patterns of the opcode fields (there may be more than one opcode field). Therefore the implementor is also required to furnish the name (this will be a character which marks the position of the field in the word format description, for example F, A or B) and value of the field (or fields) which will be representative of the instruction mnemonic.

Any remaining fields are regarded as argument (operand) fields. These fields will also eventually contain a binary pattern, but their values are only filled in when the instruction is used during the code-skeleton definition phase. In the meantime however, the program collects information about valid actual values for each argument field. The user is required to specify the valid binary range (positive binary, 2's complement or restricted range) for the field, so that errors may be trapped when the instruction is used. Alternatively, the user may choose an "unrestricted" range to indicate that no validation is to be performed on a particular field.

In the interests of making the instructions resemble an assembler format as closely as possible, the user is able to define a set of non-numeric symbols which will be used to represent numeric values in an argument field. Thus one is able to refer to a register by its name, rather than by its numeric value. Memory addresses, too, may be replaced by alphabetic names representing an address. In this way, the readability is improved for code segments which perform calls to run-time subroutines.

To emulate the assembly format even further, the user is

asked to specify valid separating characters which will precede each argument.

Finally, the user must specify the order in which the arguments are to appear in the assembly-like version of the instruction. This is important for ensuring correct validation.

2.1.4 An Example

The best explanation of this notation might be by means of an example. Let us define the 8080 assembler instruction

MVI reg, immediate value

This is a two-byte instruction of the form:

Byte 1: ØØRRR11Ø where RRR is a three-bit integer value representing one of the registers

Byte 2: an immediate value in the positive integer range  $\emptyset$  .. 255.

The definitions required to record this instruction are:

- (a) Define the word form:

Word format number: 1

Description: Immediate instruction

Format: FF RRR GGG IIII IIII

The fields are specified by distinct alphabetic

letters, one for each bit.

- (b) Define an instruction which uses the format description of (a) above:

Instruction uses word form number:1Mnemonic which will represent instruction:MVIField to associate with mnemonic:FValue of mnemonic field:ØØAnother field to associate with mnemonic:GValue of this field:110

Legal values for argument field R: Ø .. 7 where Ø is represented by the symbol B

1 is represented by the symbol C .

7 is represented by the symbol A Separator to precede argument field R: space Argument position for field R: 1

Legal values for argument field I: Ø .. 255 Separator to precede argument field I: space or comma Argument position for field I: 2 (Both definitions are required unless definition (a) has already been entered to describe a previous instruction of the same format, in which case only (b) is necessary).

In this way, target machine instructions are defined for use in later stages of the system. When an instruction such as

MVI A,25 is used,

'MVI' fills in the fields associated with the mnemonic 1. G F F R R R G G I I Ι Ι Ι Ι I Τ Ø 1 1 Ø Ø

2. 'A' fills in the field associated with the first argument (symbol A represents the value 7)

|  | - | - | - | - | ι. | u | u | u | n | 11 | n | Ľ | L. |

|--|---|---|---|---|----|---|---|---|---|----|---|---|----|

|  |   |   |   |   |    | Ø | 1 | 1 | 1 | 1  | 1 | Ø | Ø  |

|  |   |   |   |   |    | Ø | 1 | 1 | 1 | 1  | 1 | Ø | Ø  |

3. '25' fills in the field associated with the second argument

| F | F | R | R | R | G | G | G | Ι | I | Ι | I | I | I | I | Ι |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Ø | Ø | 1 | 1 | 1 | 1 | 1 | Ø | Ø | Ø | Ø | 1 | 1 | Ø | Ø | 1 |

Thus it can be seen that the machine definition program essentially provides the information for a table-driven assembler for a particular target machine.

### 2.1.5 Defining Specific Machines

The Machine Definition Program has been thoroughly tested on the Z-80 based North Star Advantage computer. The example in chapter 3 shows a machine definition for this computer using 8080 assembly mnemonics and bears witness to the fact that all aspects of the 8080 assembly language can be implemented using the current machine definition program. Implementing a compiler on the 8080 processor has the advantage of showing up a "worst case" condition. The 8080 is probably one of the simplest processors available which can still be classed as a computer and its deficiencies at the conventional machine level place extra effort on the assembly level programmer. As one moves up the scale towards more powerful computers, the effort required to implement an assembly level system decreases. Time efficient routines become less important as processors get faster, increased memory size relieves the problem of overlaying, and other additional features, such as special types of registers and floating-point hardware, take the place of soft routines. In this particular case, however, the 8080 example does have a disadvantage in that, since the 8080 language mnemonics are very simple (e.g. each opcode has only one true addressing mode), it does not show up some of the deficiencies of the notation described in this thesis. The examples below are intended to illustrate the application of the notation to other assembler languages.

In contrast to the 8080 assembly language, the PDP-11 series of computers has a highly sophisticated assembly language, called MACRO-11 <sup>[31]</sup>. Instructions are 16, 32 and 48 bits long. Although the smallest addressable unit is the byte, the word (two bytes) is addressed at all times, so that only even addresses are allowed. The PDP-11 uses an expanding opcode scheme. What appear to be 32- and 48-bit instructions are actually 16-bit instructions followed by one or two data words. What makes this assembly language so powerful are its advanced instruction formats and addressing techniques. Source and destination fields generally contain two sub-fields, one specifying the addressing mode and the other specifying the address (e.g. a register name). By way of an example, consider the MOV instruction:

16 bits

| MOV | source | source   | destination | destination |

|-----|--------|----------|-------------|-------------|

|     | mode   | register | mode        | register    |

|     | M      | R        | N           | D           |

| 4   | 3      | 3        | 3           | 3           |

The 3-bit register fields take on one of the values  $\emptyset$  to 7 to represent one of the 16-bit general registers R $\emptyset$ , R1, R2, R3, ..., R7. The 3-bit mode field also takes on a value in the range  $\emptyset$  to 7 to represent one of the following addressing modes:

### CHAPTER 2 -33-

#### MODE ADDRESS

#### Register Addressing Ø Operand is in R

- 1 Register Indirect R points to the operand

- Autoincrement 2 R is used to point to the operand and is then incremented

Autoincrement indirect 3 R is used to point to the operand address and is then incremented

4 Autodecrement R is decremented, then used load R4 from the address to point to the operand

5 Autodecrement indirect R is decremented, then used load R4 indirectly from to point to operand address the address R3 points to

- 6 Indexing operand address = contents of R + 16-bit offset in next word

- 7 Indexing & indirect pointer to operand address = contents of R + 16-bit offset in next word

EXAMPLE

Move R3 to R4 MOV R3,R4

Move memory word pointed to by R3 to R4 MOV @R3,R4

Move memory word pointed to by R3 to R4 and add 2 to R3 MOV (R3)+,R4

Move to R4 the memory word addressed by the word R3 points to; add 2 to R3 MOV @(R3)+,R4

Decrement R3 by 2, then R3 points to MOV -(R3),R4

Decrement R3 by 2, then MOV @-(R3),R4

Load R4 with the memory word at (R3) + 24MOV 24(R3),R4

Load R4 with the memory word pointed to by word (R3) + 24MOV @24(R3),R4

The word format description for this instruction is straightforward:

### FFFF MMM RRR NNN DDD

Field F will be associated with the mnemonic and will have the value 0001. The register fields, R and D, can both be defined as taking on the symbolic names of the registers.

### CHAPTER 2 -34-

However, specifying the mode fields presents a problem. Let us ignore modes 6 and 7 for the mean time, and assume we can define the mode fields using the symbolic names:

"" represents the value 000 "0" represents the value 001 "+" represents the value 010 "0+" represents the value 011 "-" represents the value 100 "0-" represents the value 101

Using our defined instruction, the examples for modes  $\emptyset$  to 5 will be written:

| Ø | MOV | R3,    | R4 |

|---|-----|--------|----|

| 1 | MOV | @ R3,  | R4 |

| 2 | MOV | + R3,  | R4 |

| 3 | MOV | @+ R3, | R4 |

| 4 | MOV | - R3,  | R4 |

| 5 | MOV | @- R3, | R4 |

|   |     |        |    |

We can make these instructions look more like the MACRO-11 originals by defining the characters "(" and ")" as the appropriate separators, so that they may also be included in our instructions. However, the problem of splitting a symbol (as mode 3 requires),  $\mathcal{Q}(R3)$ + instead of  $\mathcal{Q}+(R3)$ , cannot be solved using the current notation. In addition, the argument position must be the same for all versions of the instruction, forcing mode 2 to position the mode before the register, +(R3), instead of the more realistic (R3)+. Both these problems can be overcome by defining these nonconforming addressing modes as separate instructions. However, this would still require some unique identifying feature, e.g. using a different instruction mnemonic might allow mode 3 to read:

MOVAI @(R3)+, R4

The above mentioned problems are easily solved (at the expense of a tedious definition) by grouping the mode and register fields together as a single 6-bit field.

| MOV | SSSSSS | DDDDDD |

|-----|--------|--------|

| 4   | 6      | 6      |

where each argument field may take on one of 2<sup>6</sup> symbols:

| "RØ"    | represents | the | value | 000 | 000 |  |

|---------|------------|-----|-------|-----|-----|--|

| "R1"    | represents |     |       | ØØØ | ØØ1 |  |

| -       |            |     |       |     |     |  |

|         |            |     |       |     |     |  |

| "       | A          | L 1 |       | 000 |     |  |

| "R7"    | represents |     |       | 000 | 111 |  |

| "@RØ"   | represents | the | value | 001 | 000 |  |

|         |            |     |       |     | ÷-  |  |

|         |            |     |       |     | ÷.  |  |

|         |            |     |       |     | •   |  |

| "@R7"   | represents | the | value | ØØ1 | 111 |  |

| "(RØ)+" | represents | the | value | 010 | 000 |  |

|         |            |     |       |     |     |  |

### CHAPTER 2 -36-

|          |            |     |       | 1.5 | S. 1 |  |

|----------|------------|-----|-------|-----|------|--|

| •        |            |     |       |     |      |  |

| "@(RØ)+" | represents | the | value | Ø11 | 000  |  |

|          |            |     |       |     |      |  |

|          |            |     |       | 1.1 | ·    |  |

| "-(RØ)"  | represents | the | value | 100 | 000  |  |

| •        |            |     |       |     | •    |  |

|          |            |     |       |     |      |  |

| "@-(RØ)" | represents |     |       | 101 | 000  |  |

| "@-(R1)" | represents | the | value | 101 | 001  |  |

|          |            |     |       |     |      |  |

| •        |            |     |       |     | •    |  |

| •        |            |     |       |     |      |  |

This definition allows our defined instruction to imitate the original PDP-11 assembly language exactly.

Modes 6 and 7 call for expanding opcodes. Since the current notation is not designed to handle this feature, a solution to this problem cannot be found which matches the original assembly language instruction. Thus a separate MOV-INDEX instruction will have to be defined.

The COMPASS assembly language of the CDC CYBER series of processors [32] also presents an interesting case. The smallest addressable unit on these machines is the 60-bit word and address fields are up to 17 bits in length. The Cyber has three instruction lengths: 15, 30 and 60 bits. Thus it is possible to squeeze several instructions into a single word. This presents no problem as far as the transportable code generator is concerned, since the CDC's decoding microcodes will unpack the instructions in the

appropriate way. However, instructions may not be split across word boundries. This restriction demands that that the no-operation instruction (this 15-bit NO instruction has the octal code 46000) be used within code skeletons to pad unused bits at the end of a word. Alternatively, the code generation program could be tailored to emit padding bits where necessary.

The CDC assembly level instructions also include some unique addressing features. For example, when a memory address is put into the 18-bit register A1, the contents of that address are automatically loaded into the 60-bit register X1. However, the assembly language mnemonics for these instructions are very basic and are easily implemented using the machine definition program. For example

#### SA1 25

will set register A1 to 25, thereby loading the contents of word 25 into register X1.

Finally, the ICL 1900 assembly language, PLAN <sup>[33]</sup>, shows up the system's behaviour for instruction mnemonics which use fixed formats. A normal 24-bit ICL 1900 instruction has the format:

| XXX | FFFFFFF | MM | NNNNNNNNNNNN |

|-----|---------|----|--------------|

| 3   | 7       | 2  | 12           |

The assembly language allocates specific fields to fixed columns in the source language input line.

Columns 1 to 6 = Label field Columns 7 to 12 = Opcode field Columns 13 to 15 = Accumulator field Columns 16 to 72 = Operand field

The name of a register used for indexing (termed "modifier" in ICL jargon) may optionally follow the operand address enclosed in parentheses. For example, add to accumulator 7 the word at address [3027 + contents of index register 2]:

The order of operands as mapped onto the machine instruction is:

$$\begin{vmatrix} 1 \\ F \end{vmatrix} = \begin{vmatrix} 7 \\ X \end{vmatrix} = \begin{vmatrix} 13 \\ N(M) \end{vmatrix}$$

The machine definition program imposes a free format on the assembly language, forcing the user to declare his separation characters or use the space character as a separator. However, the basic structure of the ICL PLAN language is maintained as long as at least one space is typed between the mnemonic, accumulator and operand fields, and as long as the user declares the parentheses about the modifier field as separators. Since blanks are ignored, the user is still able to type the instructions in fixed format if he so wishes.

### 2.2 THE CODE-SKELETON DEFINITION PROGRAM

The table driven code generator of this thesis uses the template-matching idea of Bell Laboratories' portable C compiler <sup>[14]</sup>. The nature of the templates are somewhat different from those of the C compiler. The front end of the portable C compiler produces an intermediate form which is a tree structure (termed the Abstract Syntax Tree [7]). The tree structure makes it easy to distinguish operands (leaf nodes) and operators (internal nodes), and to vary the order in which the computation is performed. Temporary values (at the internal nodes) are stored in registers and register allocation algorithms are needed. The code generator uses a table containing a collection of templates. Each template contains a pattern to search for in the tree. The templates for the code generator described in this theses are far simpler. They are written in the assembler notation of section 2.1 and, since the intermediate code used in this case is very similar to machine code, simply take the place of the intermediate code. The program described in this section is a table driven assembler/editor which constructs the table of templates.

A number of compilers exist which produce assembler language as their output, notably some well known C compilers [41][42]. While certain features of the code generation system are similar in concept to this type of compiler, the output of a synthesised code generator is final machine code, and its advantage over such compilers lies in its retargetability and the absence of an assembly stage in the final compilation sequence.

### 2.2.1 Intermediate Codes

"Intermediate codes for a hypothetical stack machine" are machine-like function codes for a make-believe computer whose primary data structure is a stack. This is not to say that a machine could not be built to directly execute such codes. Certain models of Burroughs computers and the Western Digital Micro Engine (which is microcoded to execute UCSD p-Code, level 3) are examples of machines which are microcoded to do this. However, in real machine terms, intermediate codes of this type tend to be rather powerful.

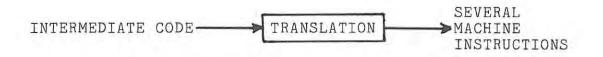

Most conventional machine level instructions specify the movement of one item of data, or a single operation on one or two items of data. Since many intermediate codes for a hypothetical machine originated for the express purpose of being interpreted (i.e. simulating the action of the machine by means of a piece of software), they incorporate fewer design constraints than their microprogram controlled or sequential logic hardware controlled counterparts. It is not difficult to write an interpreter which can perform several move and arithmetic/logic operations as a single pseudo-operation.

In addition, intermediate codes tend to be designed around the language of the source program. Thus the set of intermediate codes for a Pascal compiler might include a CALL code, which sets up a procedure stack frame entry on the stack so that recursion might be implemented before jumping to the code for that procedure; on the other hand, a set of intermediate codes for a Forth system might include a DEF code to create a dictionary entry for a new defined word. At a lower level, however, a piece of processing hardware must be designed to execute programs written in a wide range of source languages; so in the interests of generality, its machine level instructions need to be kept simple.

Although most intermediate codes take their operands from the stack, it is sometimes more convenient for an argument to be included, in much the same way as some opcodes in a conventional processor require operands. As an example, an intermediate code to perform a conditional jump

JMPF Y

might be interpreted as

<u>if</u> TOS = FALSE <u>then</u> PC := Y pop (TOS) Each intermediate code may take zero or more arguments (the current implementation allows a maximum of 2), whose values are known at code generation time.

### 2.2.2 Conversion of Intermediate Code to Machine Code

For the reasons above, a one-to-many mapping is usual when writing conventional machine code segments to produce the same effect as a single intermediate code.

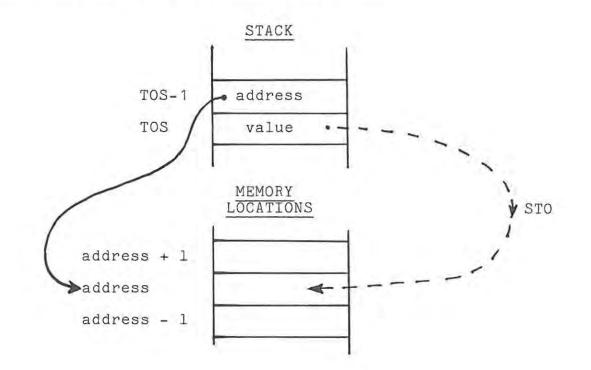

For example, suppose an intermediate code STO stores the value at the top of the stack (TOS) in the memory location whose address is at TOS-1 (next from top).

A code segment written in 8080 assembler code to produce the effect of STO might be:

| POP | D   | ; | get value             |

|-----|-----|---|-----------------------|

| POP | H   | ; | get address           |

| MOV | M,E | ; | store low order byte  |

| INX | Н   | ; | increment address     |

| MOV | M,D | ; | store high order byte |

The body of machine instructions, which produces the same effect as the intermediate code, is called a code-skeleton.

The code-skeleton definition program is the combination of an editor and an assembler. It allows the user to define a code-skeleton for each of the intermediate codes using conventional assembler mnemonics.

As each code skeleton is entered, it is checked against the table of word and instruction formats for validity. Help messages and meaningful error diagnostics are constantly available, making this an easy program to drive.

The user is able to perform the usual types of editing operations on his code skeletons. The editor is essentially a line-at-a-time editor, which performs operations on the "current" instruction. Control keys are available for listing the entire code skeleton, printing the current code skeleton, stepping through the code-skeleton either forwards or backwards, jumping to the top of the code skeleton, and deleting and inserting instructions.

### 2.2.3 Enhancements

If several code skeletons use a similar instruction sequence, then the implementor can make use of a facility which exists for writing run-time subroutines. These are really just code-skeletons which have a name associated with them. They will be included only once in the object program, and can be called from any code-skeleton, simply by including a referencing instruction with the name of the run-time subroutine as its address argument.

In addition, a number of standard run-time subroutines must be written, usually as part of the loader (see chapter 4), and included in every program. These are subroutines for performing very common operations such as input/output, arithmetic and logic operations, and standard function calls. A number of reserved names represent these run-time subroutines, and are recognised when used in the address field of a referencing instruction.

Finally, it is necessary to be able to define memory addresses relative to some other address values known at compile-time. For example, the reserved name PC represents the code-generation time address of the current instruction. Reserved names also exist to represent the values of the two arguments which an intermediate code might have. Table 8.2.1 and its associated text provide more information on this aspect.

These reserved and user-declared subroutine names are the only valid non-numeric values which may appear in an address field. They may optionally be followed by a "+" or "-" sign and a numeric value, to represent an address (or value) relative to the value represented by the given name. The numeric offset is in "smallest addressable units".

For example, the following code skeleton reads a positive integer:

| CALL<br>POP | IREAD | ; Call run-time subroutine<br>; Get result of read |

|-------------|-------|----------------------------------------------------|

|             |       |                                                    |

| PUSH        |       | ; but leave a copy on the stack                    |

| MOV         | A,D   | ; Test result < $\emptyset$                        |

| ANI         |       | ; Set zero flag if sign-bit off                    |

| JZ          | PC+6  | ; Cond jump to current PC + 6 bytes                |

| CALL        | ERR   | ; Report an error                                  |

Here IREAD is a reserved run-time subroutine name (see table 8.2.1) and ERR a user defined run-time subroutine skeleton, whose actual addresses will be filled in at code generation time. PC will be the current instruction address, not known at code-skeleton definition time, but only at code generation time.

Code-skeletons are represented in such a way that they can

be relocated to any address in memory, and are stored on a disc file for use by the code generator.

It can be seen that the user defining the code generator merely has to be able to write an assembly language code sequence to produce the desired effect of each intermediate code.

### 2.1.4 Code-Skeletons on Specific Machines

Since both the PDP-11 and the 8080 computers have built-in stack facilities, they are ideal target machines onto which to map intermediate codes for a hypothetical stack machine. However, non stack-oriented machines, such as the ICL 1900, show up some inhibiting features. This does not mean that it is impossible to write code-skeletons to produce the effects of the intermediate language codes on this machine, the implementation will just be a little more clumsy than it is on stack-oriented machines.

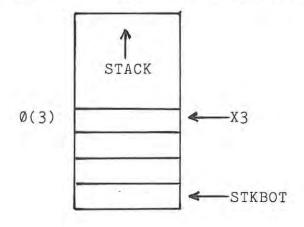

On the ICL 1900, words are 24 bits long. To implement a stack for pushing and popping single length words, one might designate one of the registers to point to the top of the stack. The most convenient method might be to set aside one of the index registers. Let us use register 3 (denoted X3), and make use of indexed addressing to refer to the stack. Assume that the stack begins at the address stored in STKBOT

(used to test for underflow) and moves upwards in memory towards higher addresses. At the start of execution, X3 should be set by the instruction LDX 3 STKBOT.

The push instruction would have to be implemented as:

| 1 | 7   | 13 | 16   |                |

|---|-----|----|------|----------------|

|   | STO | 6  | Ø(3) | [ push X6      |

|   | ADN | 3  | 1    | [ increment SP |

and the pop instruction would be:

| 11 | 17  | 13 | 16   |                |

|----|-----|----|------|----------------|

|    | LDX | 6  | Ø(3) | [ pop X6       |

|    | SBN | 3  | 1    | [ decrement SP |

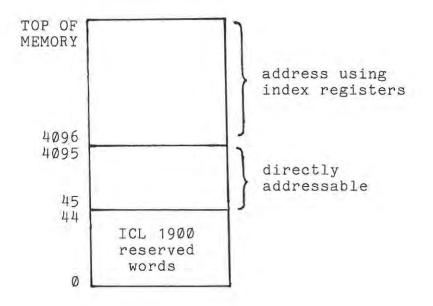

The ICL 1900 shows up another addressing feature which deserves special mention. The normal instruction form described in section 2.1.5 has a 12-bit address field.

| XXX | FFFFFFF | MM | NNNNNNNNNNNN |

|-----|---------|----|--------------|

| 3   | 7       | 2  | 12           |

This restricts the direct addressing to memory locations below address 4096 only (the first 45 of which are reserved by the ICL 1900 operating system for use as registers and work space). Higher memory locations must be addressed using index registers.

Indexed addressing turns out to be useful for implementing procedure stack frames. One simply sets an index register to the address of the bottom of the stack frame and uses an absolute offset to reference each word. For example

However, having to use some indirect addressing method to access ordinary variables can become costly.

The ICL 1900 places another restraint on the size of executable code, by the format of its branch instructions.

| XXX | FFFFFF | NNNNNNNNNNNNNNN |

|-----|--------|-----------------|

| 3   | 6      | 15              |

Since the address field of the branch instruction contains an absolute address, a 15-bit field means that the executable code should not extend beyond address 32767 (An extended branch mode is, however, available).

Whereas the generalized code generator described in this document favours a processor which can address all memory locations with equal ease, a more efficient run-time system could be produced for the ICL 1900 series if data were stored below address 4096, code below address 32768, and procedure stack frames in high memory. It should be stressed that a viable code generator could be developed for an ICL 1900 computer using the code generator synthesiser, but it would not be able to match the efficiency of a tailor-made compiler. Fortunately, most modern computers are able to address all their memory (within reasonable limits) with equal ease.

### CHAPTER 2 -50-

#### 2.3 THE CODE GENERATION PROGRAM

This program simply replaces a sequence of intermediate codes by their respective code skeletons, relocating the skeletons in memory, and filling in addresses known only at code generation time. Because this is a relatively simple process, the code generation time is short.

A few simple optimizations are included at present, but for the reasons already mentioned, these are not extensive.

### 2.4 WHEN TO USE THE PROGRAMS

To implement any compiler using the machine-independent code generator, one has to run the machine definition program first. It should only be necessary to run this program once for a new computer. Subsequent runs might be necessary to debug the instruction definition table or to add new definitions to the table. Since some machine instructions have more obscure uses than others, one might initially use only a subset of the target machine's instruction set to implement a new compiler.

### CHAPTER 2 -51-

Once the machine definition table has been established, the implementor will run the code-skeleton definition table once for each compiler he wishes to implement on the target computer. Again, subsequent runs might be necessary to debug the code-skeleton table or add new code-skeletons to the table.

Whereas the previous two programs are run only once for a particular compiler implementation, the general table-driven code generator (and its associated parser) is run every time a program is compiled. The output is a machine representation of the particular source program.

### 3. A SAMPLE IMPLEMENTATION

This chapter describes the implementation of a code generator for the CLANG parser on an 8080 processor using the automated code generation system. Some knowledge of the CLANG intermediate language codes <sup>[23]</sup> and the assembly language and architecture of the 8080 processor <sup>[24]</sup> - <sup>[28]</sup> is assumed. Readers not familiar with these topics are advised to consult the references listed.

### 3.1 THE CLANG LANGUAGE

The CLANG language is a Pascal-like one used at Rhodes University as the basis of a course in compiler writing, and for testing the principles of concurrent programming. It exists as a set of subsets, of increasing complexity. The subset used here allows simple control structures (if-thenelse, while) nested procedure declarations, recursion, simple parameter passing by reference and by value, but supports integers, and arrays of integers, as its only data type. The higher facilities for data abstraction <sup>[23]</sup> have not been included at this stage. A sample program is given below in section 3.5.

A CLANG Parser/Interpreter system has been written in Pascal and implemented on various machines, notably using UCSD Pascal, by P.D. Terry. The system was adapted to run under Pascal MT+ by the author, and a listing of the parser and interpreter sections of this appears in full in Appendix E.

# 3.2 THE MACHINE DEFINITION

The following subset of the 8080 assembly instructions is required to produce the effect of the CLANG intermediate codes.

| ADC r<br>DCR r | ADD r SBB<br>INR r                                                        |                                                                                                                                |

|----------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| DCX rp         | INX rp DAD                                                                | rp                                                                                                                             |

| CALL addr      | RET                                                                       | PCHL                                                                                                                           |

| JMP addr       | JZ addr                                                                   | JNZ addr                                                                                                                       |

| ANA r          | ANI i                                                                     | ORA r                                                                                                                          |

| MOV r,r        | MVI r,i                                                                   | LXI rp,i                                                                                                                       |

| LHLD addr      | SHLD addr                                                                 | XCHG                                                                                                                           |

| PUSH rp        | POP rp                                                                    | SPHL                                                                                                                           |

|                | DCR r<br>DCX rp<br>CALL addr<br>JMP addr<br>ANA r<br>MOV r,r<br>LHLD addr | DCR r INR r<br>DCX rp INX rp DAD<br>CALL addr RET<br>JMP addr JZ addr<br>ANA r ANI i<br>MOV r,r MVI r,i<br>LHLD addr SHLD addr |

Miscellaneous: NOP

where "r" is a register (A,B,C,D,E,H,L,M), "rp" is a register pair (B,D,H,PSW), "i" is an immediate value and "addr" a 2-byte address.

The word and instruction definitions for these instructions are shown below (and more fully in the example of Appendix A5). Since the assembler mode of the skeleton definition program has no directive for setting aside a word of store for use as data, the instruction, ASCII, has been defined as an 8-bit word which has the first bit always zero and subsequent bits variable. This enables the implementor to set aside a byte of memory and initialise it to the value of an ASCII character code.

# e.g. ASCII 65 for the character "A".

ASCII is not used in the example below, but proved to be useful when implementing a code generator on the 8080 processor for the enhanced Pascal-s <sup>[39]</sup> compiler (see chapter 6). Setting aside other areas of data within a code skeleton can be achieved using similar clumsy definitions. Assembler directives would be an obvious future enhancement to the system.

## Word Definitions

| 1.  | 8-bit register form | FFFF F RRR                     |

|-----|---------------------|--------------------------------|

| 2.  | 8-bit move form     | FF RRR SSS                     |

| 3.  | Immediate move      | FF RRR GGG IIII IIII           |

| 4.  | 8-bit immediate     | FFFF FFFF IIII IIII            |

| 5.  | 3-BYTE form         | FFFF FFFF AAAA AAAA AAAA AAAA  |

| 6.  | Double-reg form     | FF DD GGGG                     |

| 7.  | Inr-dcr form        | FF RRR GGG                     |

| 8.  | No-operand form     | FFFF FFFF                      |

| 9.  | 3-BYTE double-reg   | FF DD GGGG AAAA AAAA AAAA AAAA |

| 10. | ASCII byte fiddle   | 0 CCCC CCC                     |

# CHAPTER 3 -55-

# Instruction Definitions

| 1. | ADC | Machine format:<br>Assembler format:<br>Arg 1. field R: | 10001 RRR<br>ADC R<br>B (0,000)<br>C (1,001)<br>D (2,010)<br>E (3,011)<br>H (4,100)<br>L (5,101)<br>M (6,110)<br>A (7,111)            |

|----|-----|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 2. | ADD | Machine format:<br>Assembler format:<br>Arg 1. field R: | 10000 RRR<br>ADD R<br>B (0,000)<br>C (1,001)<br>D (2,010)<br>E (3,011)<br>H (4,100)<br>L (5,101)<br>M (6,110)<br>A (7,111)            |

| 3. | ANA | Machine format:<br>Assembler format:<br>Arg 1. field R: | 10100 RRR<br>ANA R<br>B (0,000)<br>C (1,001)<br>D (2,010)<br>E (3,011)<br>H (4,100)<br>L (5,101)<br>M (6,110)<br>A (7,111)            |

| 4. | MOV | Machine format:<br>Assembler format:<br>Arg 1. field R: | Ø1 RRR SSS<br>MOV R,S<br>B (Ø, ØØØ)<br>C (1, ØØ1)<br>D (2, Ø10)<br>E (3, Ø11)<br>H (4, 100)<br>L (5, 101)<br>M (6, 110)<br>A (7, 111) |

|    |     | Arg 2. field S:                                         | B ( Ø , ØØØ )<br>C ( 1 , ØØ1 )<br>D ( 2 , Ø1Ø )<br>E ( 3 , Ø11 )<br>H ( 4 , 10Ø )<br>L ( 5 , 1Ø1 )<br>M ( 6 , 11Ø )<br>A ( 7 , 111 )  |

# CHAPTER 3 -56-

| 5.  | ANI   | Machine format:<br>Assembler format: | ANI I                                   |

|-----|-------|--------------------------------------|-----------------------------------------|

|     |       | Arg 1. field I:                      | 0255 (000000001111111                   |

| 6.  | CALL  |                                      | 11001101 ΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑ           |

|     |       | Assembler format:<br>Arg 1. field A: | CALL A<br>NO ARGUMENT CHECKS (width=16) |

| 7.  | JMP   | Machine format:<br>Assembler format: | 11000011 AAAAAAAAAAAAAAAAAAAAAAAAAAAAAA |

|     |       | Arg 1. field A:                      | NO ARGUMENT CHECKS (width=16)           |

| 8.  | JZ    | Machine format:<br>Assembler format: | 11001010 ΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑ |

|     |       | Arg 1. field A:                      | NO ARGUMENT CHECKS (width=16)           |

| 9.  | JNZ   | Machine format:<br>Assembler format: | 11000010 AAAAAAAAAAAAAAAAAAAAAAAAAAAAAA |

|     |       |                                      | NO ARGUMENT CHECKS (width=16)           |

| 10. | DAD   | Machine format:<br>Assembler format: | 00 DD 1001<br>DAD D                     |

|     |       | Arg 1. field D:                      | B (Ø, ØØØ)                              |

|     |       |                                      | D (1,001)                               |

|     |       |                                      | D (1,001)<br>H (2,010)<br>SP (3,011)    |

|     |       |                                      | SP (3,011)                              |

| 11. | INX   | Machine format:<br>Assembler format: | 00 DD 0011<br>INX D                     |

|     |       | Arg 1. field D:                      | B (Ø, 000)                              |

|     |       |                                      | D (1,001)                               |

|     |       |                                      | H (2,010)                               |

|     |       |                                      | SP (3,011)                              |

| 12. | DCX   | Machine format:<br>Assembler format: | 00 DD 1011<br>DCX D                     |

|     |       | Arg 1. field D:                      | B (Ø,ØØØ)                               |

|     |       |                                      | D (1,001)                               |

|     |       |                                      | H (2,010)<br>SP (3,011)                 |

|     |       |                                      | SP (3,011)                              |

| 13. | LHLD  | Machine format:                      | ØØ101010 ΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑ            |

|     |       | Assembler format:<br>Arg 1. field A: | LHLD A<br>NO ARGUMENT CHECKS (width=16) |

|     | OTT D | Machine format:                      | 00100010 ΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑΑ             |

| 14. | SHLD  | Assembler format:                    | SHLD A                                  |

# CHAPTER 3 -57-

| 15. | DCR  | Machine format:<br>Assembler format:<br>Arg 1. field R: | ØØ RRR 101         DCR R         B       (Ø, ØØØ)         C       (1, ØØ1)         D       (2, Ø10)         E       (3, Ø11)         H       (4, 100)         L       (5, 101)         M       (6, 110)         A       (7, 111) |

|-----|------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16. | INR  | Machine format:<br>Assembler format:<br>Arg 1. field R: | ØØ RRR 100         INR R         B       (Ø, 000)         C       (1, 001)         D       (2, 010)         E       (3, 011)         H       (4, 100)         L       (5, 101)         M       (6, 110)         A       (7, 111) |

| 17. | ORA  | Machine format:<br>Assembler format:<br>Arg 1. field R: | 10110 RRR<br>ORA R<br>B (0,000)<br>C (1,001)<br>D (2,010)<br>E (3,011)<br>H (4,100)<br>L (5,101)<br>M (6,110)<br>A (7,111)                                                                                                       |

| 18. | NOP  | Machine format:<br>Assembler format:                    | ØØØØØØØØ<br>NOP                                                                                                                                                                                                                  |

| 19. | PCHL | Machine format:<br>Assembler format:                    |                                                                                                                                                                                                                                  |

| 20. | POP  | Machine format:<br>Assembler format:<br>Arg 1. field D: | 11 DD 0001<br>POP D<br>B (0,000)<br>D (1,001)<br>H (2,010)<br>PSW (3,011)                                                                                                                                                        |

| 21. | PUSH | Machine format:<br>Assembler format:<br>Arg 1. field D: | 11 DD 0101<br>PUSH D<br>B ( 0 , 000 )<br>D ( 1 , 001 )<br>H ( 2 , 010 )<br>PSW ( 3 , 011 )                                                                                                                                       |

| 22. | RET  | Machine format:<br>Assembler format:                    | 11001001<br>RET                                                                                                                                                                                                                  |

1

# CHAPTER 3 -58-

| 23 | . SPHL  | Machine format:<br>Assembler format:                                       | 11111001<br>SPHL                                                                                                                                                 |

|----|---------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24 | . XCHG  | Machine format:<br>Assembler format:                                       | 11101011<br>XCHG                                                                                                                                                 |

| 25 | . SBB   | Machine format:<br>Assembler format:<br>Arg 1. field R:                    | 10011 RRR<br>SBB R<br>B ( 0 , 000 )<br>C ( 1 , 001 )<br>D ( 2 , 010 )<br>E ( 3 , 011 )<br>H ( 4 , 100 )<br>L ( 5 , 101 )<br>M ( 6 , 110 )<br>A ( 7 , 111 )       |

| 26 | . SUB   | Machine fomat:<br>Assembler format:<br>Arg 1. field R:                     | 10010 RRR<br>SUB R<br>B (0,000)<br>C (1,001)<br>D (2,010)<br>E (3,011)<br>H (4,100)<br>L (5,101)<br>M (6,110)<br>A (7,111)                                       |

| 27 | . MVI   | Machine format:<br>Assembler format:<br>Arg 1. field R:<br>Arg 2. field I: | 00 RRR 110 IIIIIII<br>MVI R,I<br>B (0,000)<br>C (1,001)<br>D (2,010)<br>E (3,011)<br>H (4,100)<br>L (5,101)<br>M (6,110)<br>A (7,111)<br>0255 (0000000011111111) |

| 28 | . LXI   | Machine format:<br>Assembler format:<br>Arg 1. field D:<br>Arg 2. field A: | 00 DD 0001 AAAAAAAAAAAAAAAAAAA<br>LXI D,A<br>B (0,000)<br>D (1,001)<br>H (2,010)<br>SP (3,011)<br>NO ARGUMENT CHECKS (width=16)                                  |

| 29 | . ASCII | Machine format:<br>Assembler format:<br>Arg 1 field C:                     | Ø CCCCCCC<br>ASCII C<br>Ø127 (ØØØØØØ01111111)                                                                                                                    |

### CHAPTER 3 -59-

### 3.3 CODE-SKELETON DEFINITIONS

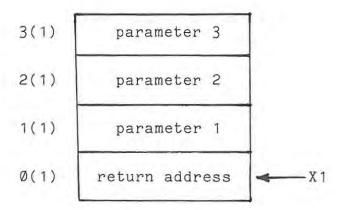

The level 2 CLANG parser generates 27 intermediate language codes, one of which is not used by the code generator (STK is used only in aiding students to understand the stack frame concept). Codes take zero, one or two arguments. The current Code-Skeleton definition program allows a maximum of two arguments per code, called X and Y. CLANG generally uses the first argument to indicate the level at which a declaration was made, and the second to indicate an address or offset.

The CLANG pseudo-machine has a set of "display" registers, used to point to the most deeply nested procedure stack frame for a particular declaration level (useful in handling variable addressing) and a "base register", pointing to the base of the top stack frame on the stack. The most convenient method of implementing these pointers in the target program would undoubtedly be to use the processor's own registers. Unfortunately, the 8080 does not have enough register pairs for the implementor to dedicate some of them permanently to a particular task, so memory locations have to be used instead. In order to be able to refer to these memory locations by name, they are "defined" as run-time subroutines (simply a block of memory which has a name). Run-time subroutine BASERE is a 2-byte pointer.

BASERE: NOP NOP

Run-time subroutine DISPLA allows a maximum declaration nesting of 5 (i.e. five 2-byte pointers).

DISPLA: NOP NOP DISPLA+2: NOP NOP DISPLA+4: NOP NOP DISPLA+6: NOP NOP DISPLA+8: NOP NOP

Four more run-time subroutines are defined to be called from code-skeletons.

GETDIS is called with a value X in the H-L register pair to return the value of the  $X^{th}$  display register in the D-E pair.

GETDIS: DAD H ; X \* 2 for 16-bit addressing LXI B,DISPLA DAD B ; + DISPLA MOV E,M ; get value from INX H ; DISPLA + (2\*X) MOV D,M RET ADDRCD is called after a call to GETDIS to use the display value in D-E and a displacement in H-L to calculate the address of a local variable.

| ADDRCD: | DAD | H | ; * 2 for 16-bit addressing |

|---------|-----|---|-----------------------------|

|         | DAD | D | ; + base address            |

|         | RET |   | ; address in H-L            |

STORE is a subroutine to store TOS (top of stack) value at TOS-1 address.

| POP  | В   | ; return address         |

|------|-----|--------------------------|

| POP  | D   | ; get value              |

| POP  | H   | ; get address            |

| MOV  | M,E | ; store low order byte   |

| INX  | H   | ; increment address      |

| MOV  | M,D | ; store high order byte  |

| PUSH | В   | ; restore return address |

| RET  |     | ·                        |

The last run-time subroutine, START, has a special initialization status. It stores the stack's first word in DISPLA[1] and BASERE.

| LXI  | D,-2   | ; | D,E  | =  | -2  |   |

|------|--------|---|------|----|-----|---|

| LXI  | H,Ø    | ÷ |      |    |     |   |

| DAD  | SP     | ; | H,L  | =  | SP  |   |

| DAD  | D      | ; | subt | ra | act | 2 |

| SHLD | DISPLA |   |      |    |     |   |