# HARDWARE EVOLUTION OF A DIGITAL CIRCUIT USING A CUSTOM VLSI ARCHITECTURE

SUBMITTED IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### MASTER OF ENGINEERING IN MECHATRONICS

IN THE FACULTY OF ENGINEERING, THE BUILT ENVIRONMENT AND INFORMATION TECHNOLOGY AT THE NELSON MANDELA METROPOLITAN UNIVERSITY

#### **ALLAN EDWARD VAN DEN BERG**

UNDER THE SUPERVISION OF DR FAROUK SMITH

PORT ELIZABETH, SOUTH AFRICA DECEMBER 2013

# HARDWARE EVOLUTION OF A DIGITAL CIRCUIT USING A CUSTOM VLSI ARCHITECTURE

Submitted in fulfilment of the requirements for the degree of

#### **Master of Engineering in Mechatronics**

in the Faculty of Engineering, The Built Environment and Information Technology at the Nelson Mandela Metropolitan University

#### Allan Edward van den Berg

Under the supervision of Dr Farouk Smith

Department of Mechatronics Port Elizabeth, South Africa December 2013

## **DOCUMENT INFORMATION**

**Author:** Allan Edward van den Berg

Author's Student Number: 208033000

**Supervisor:** Dr Farouk Smith

**Institution:** Nelson Mandela Metropolitan University

Faculty: Engineering, the Built Environment and Information Technology

School: Engineering

**Department:** Mechatronics

**Degree:** Master of Engineering in Mechatronics

Degree Code: 75001

**NQF Level** 9 (Masters Degree)

Pages: 125 (Excluding Appendices)

Word Count: 32696

**Date Printed:** 10/04/2014 11:05:00

**Last Saved:** 10/04/2014 11:01:00

Revision Number: 164

File Name: WorkingMasters

## **ABSTRACT**

Keywords: Control Circuit, Critical-Path Circuits, Evolutionary Hardware, Evolved Hardware, Field-

Programmable Gate Array, Finite-State Machine, Modular Evolution, Portability, Real-

World Applications, Two-Bit Multiplier, Virtual Reconfigurable Circuit, Scalability

This research investigates three solutions to overcoming portability and scalability concerns in the Evolutionary Hardware (EHW) field.

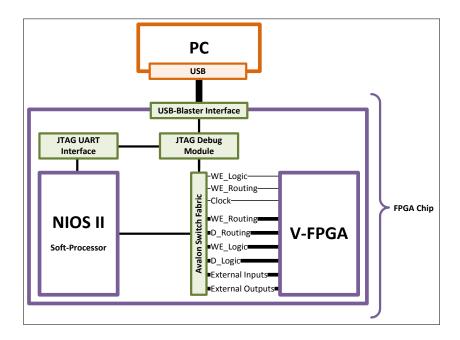

Firstly, the study explores if the V-FPGA—a new, portable Virtual-Reconfigurable-Circuit architecture—is a practical and viable evolution platform.

Secondly, the research looks into two possible ways of making EHW systems more scalable: by optimising the system's genetic algorithm; and by decomposing the solution circuit into smaller, evolvable sub-circuits or modules.

GA optimisation is done is by: omitting a canonical GA's crossover operator (i.e. by using an  $1 + \lambda$  algorithm); applying evolution constraints; and optimising the fitness function. The circuit decomposition is done in order to demonstrate modular evolution.

Three two-bit multiplier circuits and two sub-circuits of a simple, but real-world control circuit are evolved.

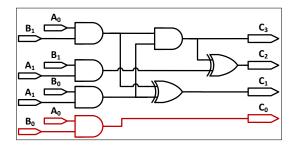

The results show that the evolved multiplier circuits, when compared to a conventional multiplier, are either equal or more efficient. All the evolved circuits improve two of the four critical paths, and all are unique. Thus, it is experimentally shown that the V-FPGA is a viable hardware-platform on which hardware evolution can be implemented; and how hardware evolution is able to synthesise novel, optimised versions of conventional circuits.

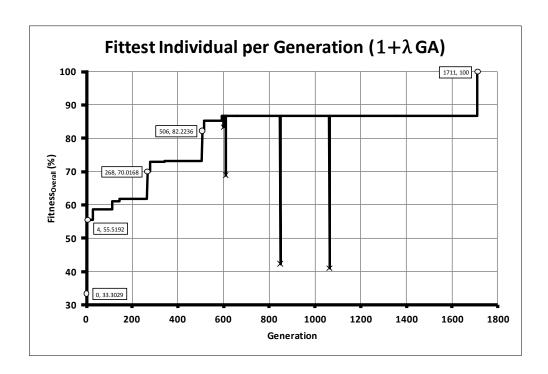

By comparing the  $1 + \lambda$  and canonical GAs, the results verify that optimised GAs can find solutions quicker, and with fewer attempts. Part of the optimisation also includes a comprehensive critical-path analysis, where the findings show that the identification of dependent critical paths is vital in enhancing a GA's efficiency.

Finally, by demonstrating the modular evolution of a finite-state machine's control circuit, it is found that although the control circuit as a whole makes use of more than double the available hardware resources on the V-FPGA and is therefore not evolvable, the evolution of each state's sub-circuit is possible. Thus, modular evolution is shown to be a successful tool when dealing with scalability.

## **ACKNOWLEDGEMENTS**

Firstly, I wish to express my gratitude to my supervisor, Dr Farouk Smith, who introduced me to the field of Evolutionary Hardware, assisted me in obtaining financial support, spent many hours proof-reading my documentation and pushed me to submit my findings for review at an academic conference. Your constant concern and patience throughout this process is appreciated; and your knowledge and passion for the FPGA field enabled me to remain enthusiastic throughout my research.

Secondly, the financial assistance of the National Research Foundation (NRF) towards this research is hereby also acknowledged. Opinions expressed and conclusions arrived at are my own and are not necessarily to be attributed to the NRF.

## PREVIOUSLY PUBLISHED WORK

A major portion of the work in this dissertation has been previously published (see (van den Berg & Smith, 2013)), and has also been presented at the Annual Research Conference of the South African Institute for Computer Scientists and Information Technologists, held in East London during October 2013. The publication includes the implementation of the V-FPGA and the evolution of the trial two-bit multiplier.

## **DECLARATION**

I, Allan Edward van den Berg, student number 208033000, in accordance with Rule G4.6.3, hereby declare that this dissertation for Master of Engineering in Mechatronics is my own original work, and that it has not previously been submitted for assessment or completion of any postgraduate qualification to another university or for another qualification.

# TABLE OF CONTENTS

| Chapter 1 INTRODUCTION                                         | 1  |

|----------------------------------------------------------------|----|

| 1.1 Background                                                 | 1  |

| 1.2 Evolutionary Hardware                                      | 2  |

| 1.2.1 Overview of Evolutionary Algorithms                      | 3  |

| 1.2.2 Using Evolutionary Algorithms to Evolve Hardware         | 4  |

| 1.2.3 Hardware Evolution Platforms                             | 6  |

| 1.3 Evolving a Finite-State Machine                            | 7  |

| 1.4 Problem Statement                                          | 8  |

| 1.4.1 The Virtual Reconfigurable Architecture                  | 8  |

| 1.4.2 Optimising Genetic Operators for use on the Virtual-FPGA | 10 |

| 1.4.3 Scalability                                              | 11 |

| 1.5 Statement of Objectives                                    | 12 |

| 1.5.1 Major Objectives                                         | 12 |

| 1.5.2 Minor Objectives                                         | 13 |

| 1.6 Methodology                                                | 13 |

| 1.7 Paper Structure                                            | 14 |

| Chapter 2 LITERATURE REVIEW                                    | 15 |

| 2.1 A History Driven by Target Platforms                       | 15 |

| 2.1.1 The Early Years                                          | 15 |

| 2.1.2 The Virtual-Reconfigurable-Circuit Era                   | 16 |

| 2.1.3 Future Platforms                                         | 17 |

| 2.2 Factors Delaying Real-World Applications                   | 18 |

| 2.2.1 Performance, Cost and Time                   | 19 |

|----------------------------------------------------|----|

| 2.2.2 Scalability and Chromosome Length            | 19 |

| 2.2.3 Variety of Research                          | 21 |

| 2.3 Chapter Summary                                | 22 |

| Chapter 3 THE VIRTUAL-FPGA                         | 23 |

| 3.1 Introduction                                   | 23 |

| 3.2 The V-FPGA's Logic Elements                    | 24 |

| 3.2.1 Programming the Logic Configuration Memory   | 26 |

| 3.3 The V-FPGA's Routing Architecture              | 27 |

| 3.3.1 The Routing Matrix                           | 27 |

| 3.3.2 Programming the Routing Configuration Memory | 29 |

| 3.4 V-FPGA Simulation                              | 30 |

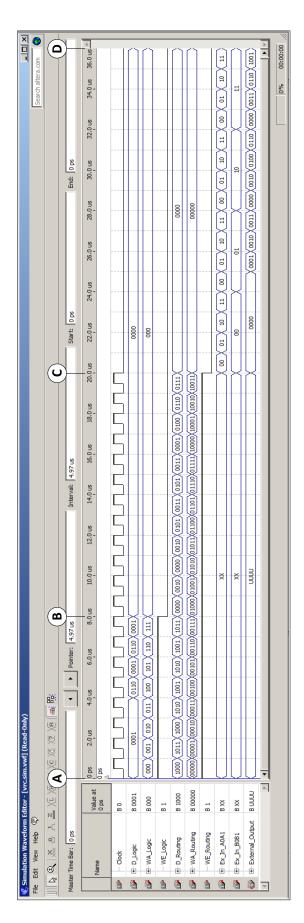

| 3.4.1 Simulation Results                           | 32 |

| Chapter 4 EVOLVING A TWO-BIT MULTIPLIER CIRCUIT    | 35 |

| 4.1 Introduction                                   | 35 |

| 4.2 Hardware and V-FPGA Setup                      | 36 |

| 4.2.1 Hardware Components                          | 36 |

| 4.2.2 Creating a 20-LE VHDL-Based V-FPGA File      | 39 |

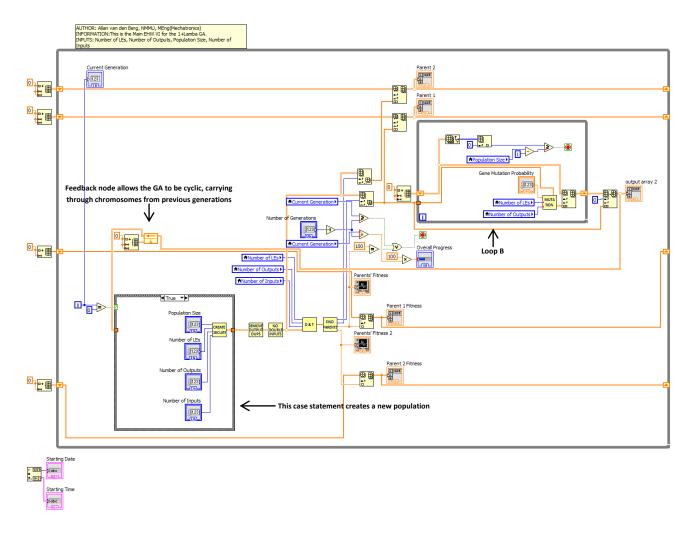

| 4.3 Implementing the LabVIEW Genetic Algorithms    | 42 |

| 4.3.1 The Canonical Genetic Algorithm              | 42 |

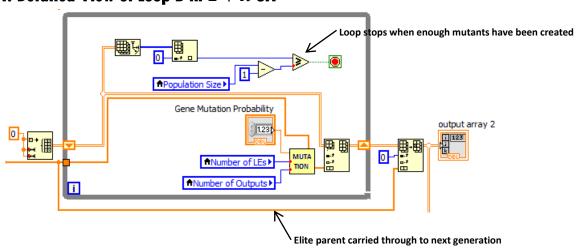

| 4.3.2 The $1+\lambda$ Genetic Algorithm            | 44 |

| 4.3.3 Genetic Operators                            | 45 |

| 4.3.4 Genotype-Phenotype Mapping                   | 46 |

| 4.3.5 Evolution Constraints                        | 48 |

| 4.3.6 Downloading a Genotyne                       | 50 |

| 4.3.7 Evaluating a Phenotype                                | 51 |

|-------------------------------------------------------------|----|

| 4.3.8 The Fitness Function                                  | 52 |

| 4.4 Results                                                 | 56 |

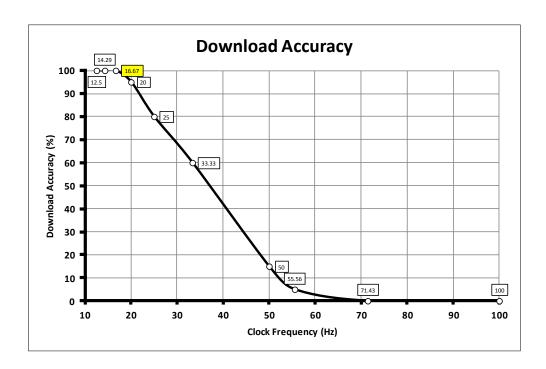

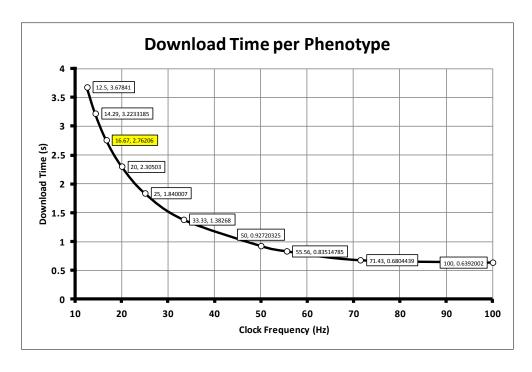

| 4.4.1 Clock Frequency                                       | 56 |

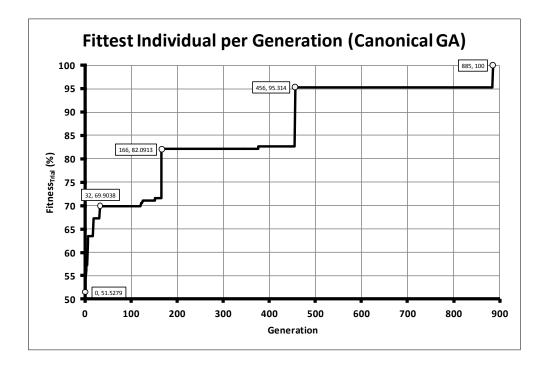

| 4.4.2 Canonical Evolution                                   | 58 |

| 4.4.3 $1 + \boldsymbol{\lambda}$ Evolution                  | 62 |

| 4.5 Discussion                                              | 64 |

| 4.5.1 The V-FPGA and Hardware Setup                         | 64 |

| 4.5.2 The Genetic Algorithms                                | 65 |

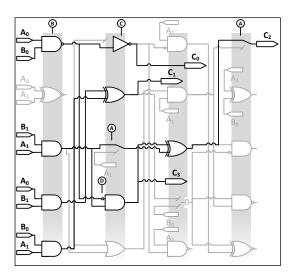

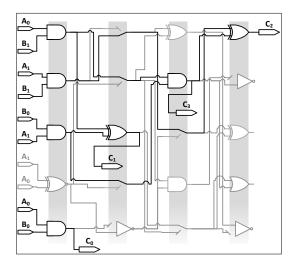

| 4.5.3 The Evolved Phenotypes                                | 67 |

| 4.5.4 Repeatability                                         | 69 |

| Chapter 5 THE MODULAR EVOLUTION OF A FINITE-STATE MACHINE   | 73 |

| 5.1 Introduction                                            | 73 |

| 5.2 System Components                                       | 74 |

| 5.3 System Operation and Analysis                           | 75 |

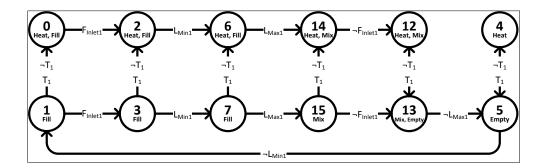

| 5.3.1 State One: The Mixing Tank                            | 75 |

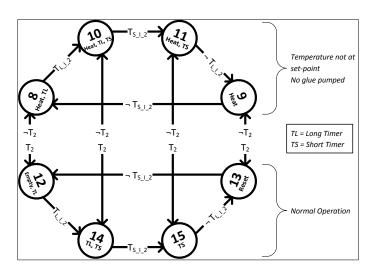

| 5.3.2 State Two: The Holding Tank                           | 77 |

| 5.4 Modelling the Finite-State Machine                      | 79 |

| 5.4.1 State Diagram                                         | 79 |

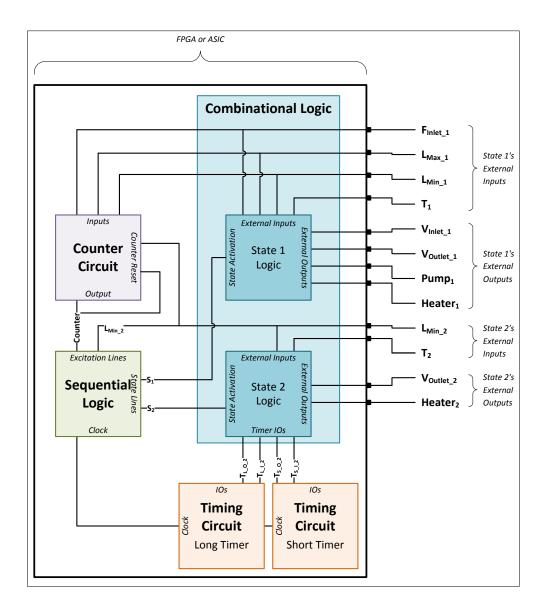

| 5.4.2 Block Diagram                                         | 80 |

| 5.5 Evolving the Finite-State Machine's Combinational Logic | 82 |

| 5.5.1 The States' Combinational Logic                       | 82 |

| 5.6 Results                                                 | 86 |

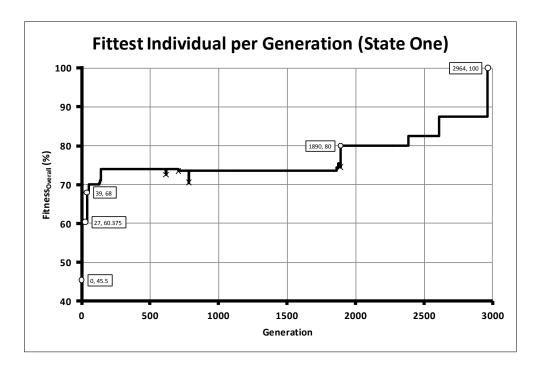

| 5.6.1 State One                                             | 86 |

| 5.6.2 State Two                                             | 87 |

| 5.7 Discussion                                                | 89  |

|---------------------------------------------------------------|-----|

| 5.7.1 The Evolved Critical Paths                              | 89  |

| 5.7.2 Modular Evolution and Scalability                       | 90  |

| 5.7.3 The Distribution of Logic Elements and External Outputs | 92  |

| Chapter 6 CONCLUSION                                          | 95  |

| 6.1 Introduction                                              | 95  |

| 6.2 Contributions                                             | 95  |

| 6.3 The Way Forward: Future Work                              | 97  |

| BIBLIOGRAPHY                                                  | 99  |

| APPENDICES                                                    | 107 |

# LIST OF FIGURES

| Figure 1.1 Overview of the Hardware Evolution process using a Genetic Algorithm             | 5  |

|---------------------------------------------------------------------------------------------|----|

| Figure 1.2 A general FSM's circuit implemented as a sequential circuit                      | 7  |

| Figure 1.3 Overview of an FPGA with a virtual reconfigurable layer                          | 9  |

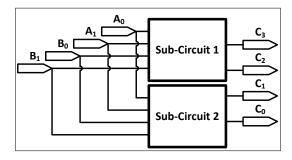

| Figure 2.1 Output decomposition of a four-output circuit.                                   | 20 |

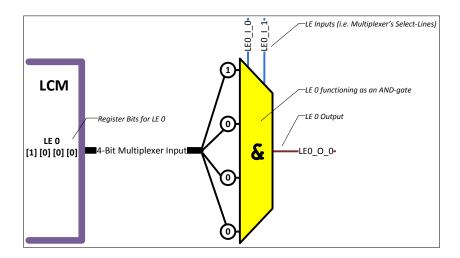

| Figure 3.1 AND-gate implementation using a multiplexer                                      | 24 |

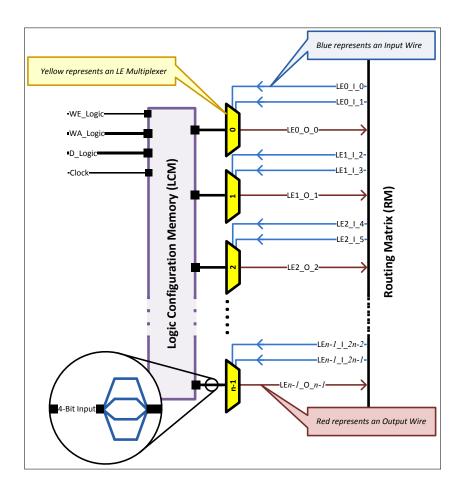

| Figure 3.2 Logic Configuration Memory and Routing Matrix connected to the LE multiplexers   | 26 |

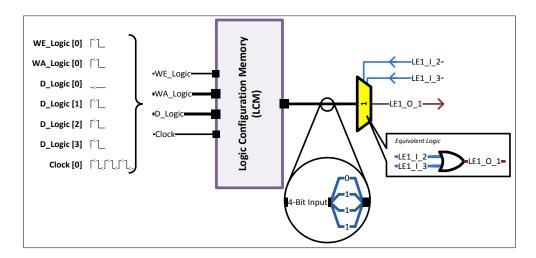

| Figure 3.3 An example implementation of an OR-gate using the LCM and multiplexer 1          | 27 |

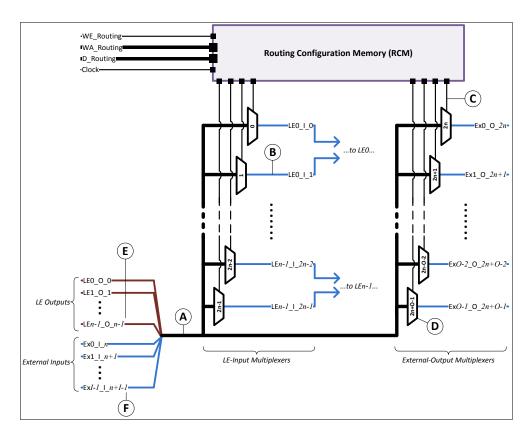

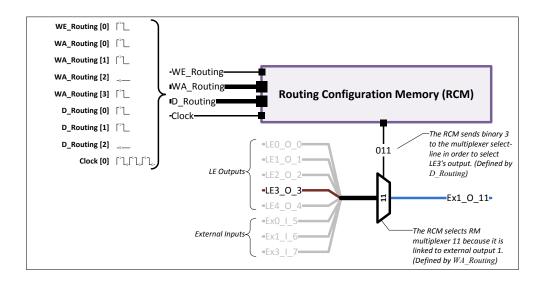

| Figure 3.4 The Routing Matrix's multiplexers linked to the Routing Configuration Memory     | 28 |

| Figure 3.5 Example implementation of a RM multiplexer                                       | 30 |

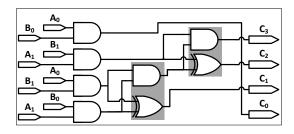

| Figure 3.6 A conventional two-bit multiplier                                                | 30 |

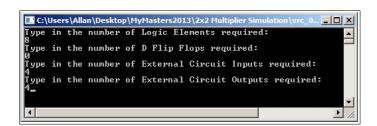

| Figure 3.7 C-code variable-prompt which configures the V-FPGA's size                        | 31 |

| Figure 3.8 Simulation results                                                               | 33 |

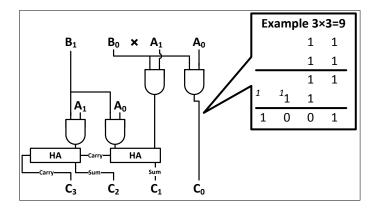

| Figure 4.1 A two-bit multiplier using half-adders (HA) to sum the partial products          | 35 |

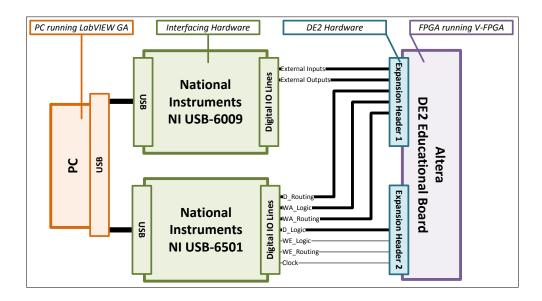

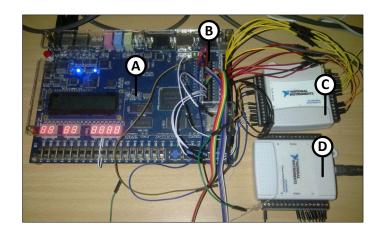

| Figure 4.2 Schematic of the hardware components used in the experimental setup              | 37 |

| Figure 4.3 Actual hardware setup                                                            | 38 |

| Figure 4.4 NI USB-6501 DAQ card (National Instruments, 2012)                                | 38 |

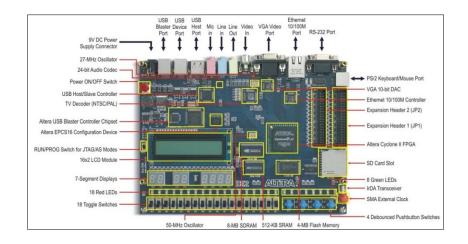

| Figure 4.5 The DE2 Board (Altera, 2006)                                                     | 39 |

| Figure 4.6 C-code variable-prompt used to configure a 20-LE V-FPGA                          | 40 |

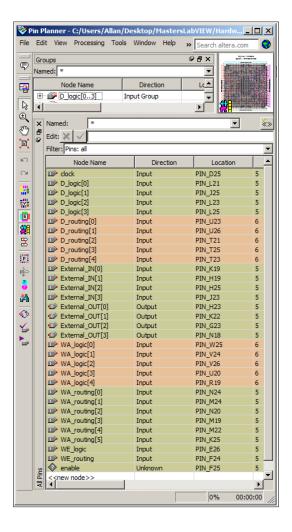

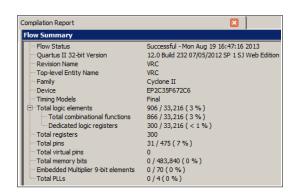

| Figure 4.7 Quartus II Pin Planner screen dump                                               | 41 |

| Figure 4.8 Compilation report                                                               | 41 |

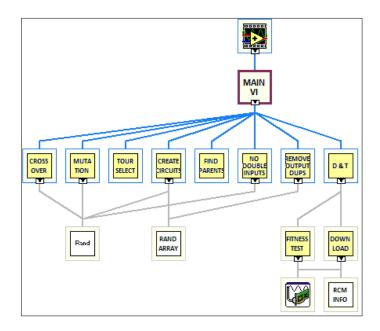

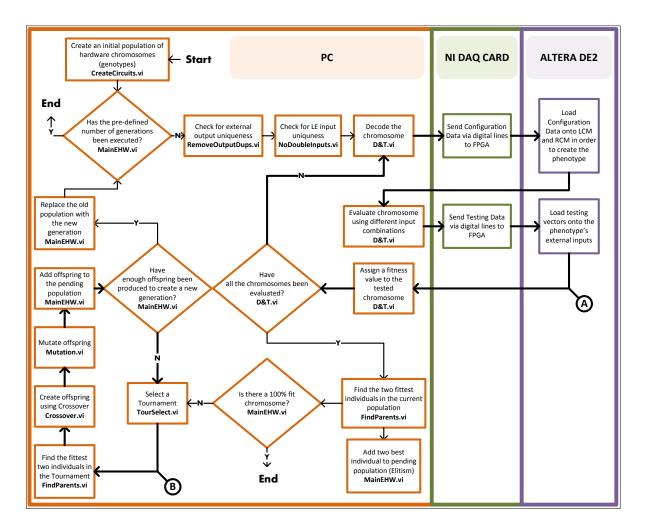

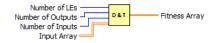

| Figure 4.9 Hierarchical structure of the LabVIEW VIs                                        | 42 |

| Figure 4.10 Flowchart of the LabVIEW GA with the applicable VIs highlighted using hold text | 43 |

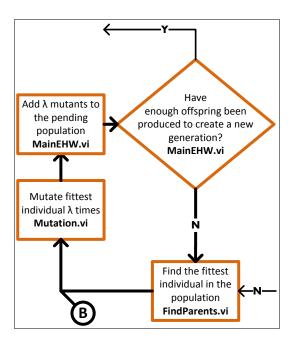

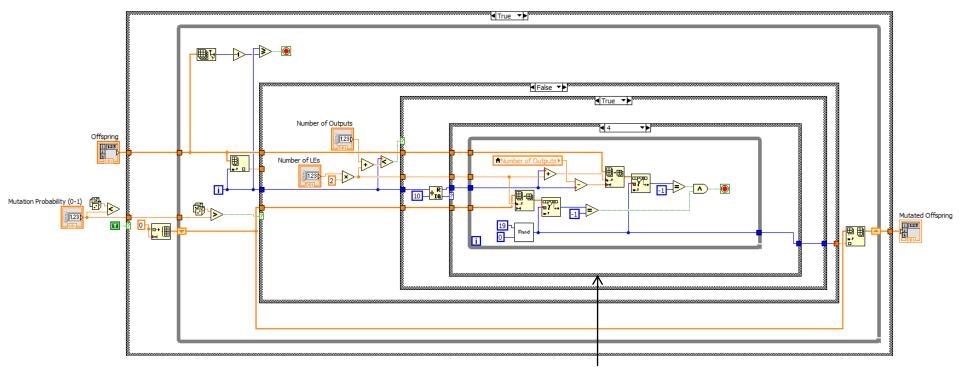

| Figure 4.11 $1+\lambda$ mutation loop                                                                 | 44 |

|-------------------------------------------------------------------------------------------------------|----|

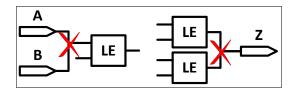

| Figure 4.12 Illegal configurations                                                                    | 47 |

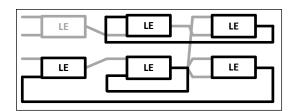

| Figure 4.13 CGP layout of LEs used to permit only feed-forward circuits                               | 50 |

| Figure 4.14 A CGP LE array with prohibited feedback loops                                             | 50 |

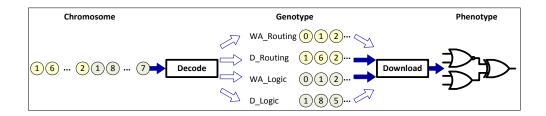

| Figure 4.15 Decoding and downloading procedure                                                        | 51 |

| Figure 4.16 General truth table                                                                       | 51 |

| Figure 4.17 Test vector with corresponding output vector                                              | 52 |

| Figure 4.18 Conventional multiplier circuit (right) comprising of four smaller CP circuits (left)     | 52 |

| Figure 4.19 Analysis of a 2-bit multiplier's truth table                                              | 53 |

| Figure 4.20 Logic-low circuit                                                                         | 55 |

| Figure 4.21 Download accuracy vs. clock frequency                                                     | 57 |

| Figure 4.22 Download time vs. clock frequency                                                         | 57 |

| Figure 4.23 The results of the successful trial                                                       | 59 |

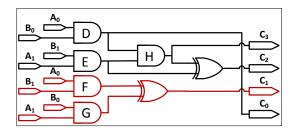

| Figure 4.24 Evolved trial phenotype                                                                   | 60 |

| Figure 4.25 Simplified trial phenotype (A red outline indicates an independent CP)                    | 60 |

| Figure 4.26 Results of the final-canonical GA                                                         | 61 |

| Figure 4.27 Canonical phenotype                                                                       | 62 |

| Figure 4.28 Simplified canonical phenotype (A red outline indicates an independent CP)                | 62 |

| Figure 4.29 Results of the $1+\lambda$ GA                                                             | 63 |

| Figure 4.30 $1 + \boldsymbol{\lambda}$ phenotype                                                      | 63 |

| Figure 4.31 Simplified $1+\boldsymbol{\lambda}$ phenotype (A red outline indicates an independent CP) | 64 |

| Figure 4.32 Future EHW SOPC                                                                           | 65 |

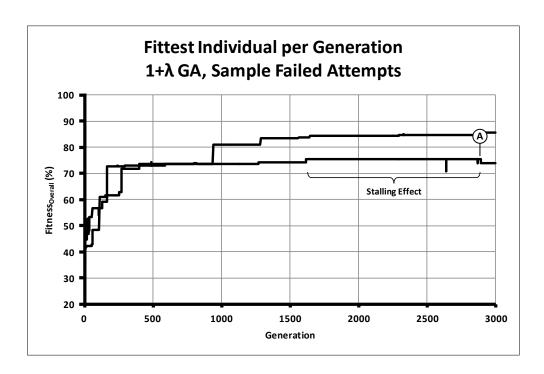

| Figure 4.33 Sample failed attempts showing the Stalling Effect.                                       | 70 |

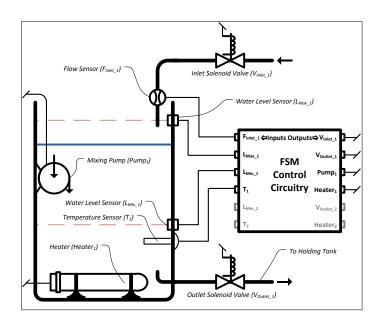

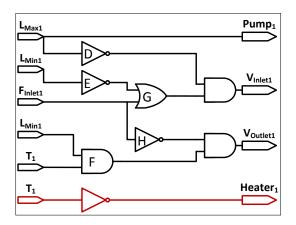

| Figure 5.1 Mixing-tank components                                                                     | 74 |

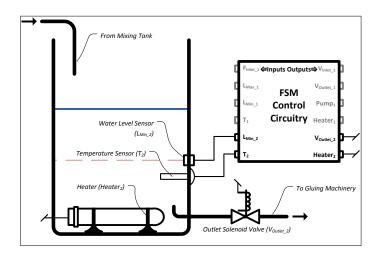

| Figure 5.2 Holding-tank components                                                                    | 74 |

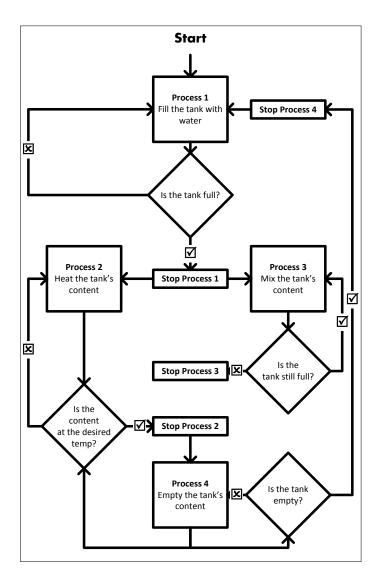

| Figure 5.3 Logic flowchart of the mixing tank              | 76 |

|------------------------------------------------------------|----|

| Figure 5.4 Schematic of mixing-tank processes              | 77 |

| Figure 5.5 Logic flowchart of the holding tank             | 78 |

| Figure 5.6 Schematic of two holding-tank processes         | 79 |

| Figure 5.7 State diagram of the tank system                | 79 |

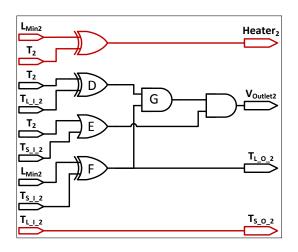

| Figure 5.8 Block diagram of the system's control circuitry | 81 |

| Figure 5.9 State one's input-combination diagram           | 84 |

| Figure 5.10 State two's input-combination diagram          | 85 |

| Figure 5.11 Results of state one's evolution               | 86 |

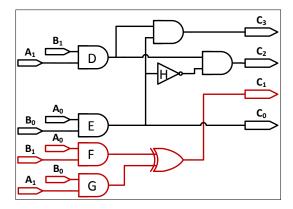

| Figure 5.12 State one's final phenotype                    | 87 |

| Figure 5.13 State one's simplified phenotype               | 87 |

| Figure 5.14 Results of state two's evolution               | 88 |

| Figure 5.15 State two's final phenotype                    | 89 |

| Figure 5.16 State two's simplified phenotype               | 89 |

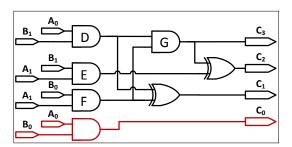

| Figure 5.17 Complete combinational-logic of the FSM        | 91 |

| Figure 5.18 Proposed pyramid layout of LEs                 | 93 |

# LIST OF TABLES

| Table 2.1 Overview of FPGA and ASIC-based EHW applications, found in literature                      | 21 |

|------------------------------------------------------------------------------------------------------|----|

| Table 3.1 V-FPGA logic-gates                                                                         | 25 |

| Table 3.2 Two-bit multiplier truth table                                                             | 30 |

| Table 4.1 Number of pins used                                                                        | 40 |

| Table 4.2 An example hardware-chromosome (shaded grey)                                               | 46 |

| Table 4.3 LE summary of the simplified phenotypes                                                    | 67 |

| Table 4.4 Summary of the net number-of-LEs evolved by each CP (Red text indicates an independent CP) | 68 |

| Table 5.1 Overview of the mixing-tank variables                                                      | 75 |

| Table 5.2 Overview of the holding-tank variables                                                     | 75 |

| Table 5.3 Possible transition-variable combinations                                                  | 80 |

| Table 5.4 State one's truth table                                                                    | 82 |

| Table 5.5 Next-possible-input-combination table for state one                                        | 83 |

| Table 5.6 State two's truth table                                                                    | 84 |

| Table 5.7 Next-possible-input-combination table for state two                                        | 85 |

| Table 5.8 Summary of the net number-of-LEs evolved by each CP                                        | 90 |

| Table 5.9 The distribution-of-external-outputs and used-LEs per CGP column                           | 92 |

# LIST OF EQUATIONS

| Equation 3.1 Maximum number of LE multiplexers       | 25 |

|------------------------------------------------------|----|

| Equation 3.2 Maximum number of RM multiplexers       | 28 |

| Equation 4.1 Fitness function of the output vectors  | 53 |

| Equation 4.2 Fitness function of the output elements | 54 |

| Equation 4.3 Fitness function of the CPs             | 54 |

| Equation 4.4 Fitness function of the partial CPs     | 54 |

| Equation 4.5 Overall fitness function                | 55 |

| Equation 4.6 Trial fitness function                  | 58 |

## **DEFINITIONS**

$(\mu + \lambda)$ -Selection A selection scheme which selects  $\mu$  best individuals from a population, and

creates  $\lambda$  mutants from these best individuals (Engelbrecht, 2007, p. 139).

Cartesian Genetic Programming Invented by Miller & Thomson (2000), CGP is a method of arranging the

nodes of a circuit using the Cartesian coordinate system.

CP Vector The collective logic responses of one particular external output when

evaluated using all the sets of test vectors.

Critical Path An output's critical path includes only the relevant circuitry required for

that output to function. Thus, it is the direct path linking certain external

inputs to a particular external output.

**Crossover** Process of combining two individuals' genes in order to create new

offspring.

**Decomposition** Kalganova (2000, p. 2) defines decomposition as "breaking a large logic

circuit into several relatively smaller ones."

**Divide and Conquer** The process of dividing a problem into two or more sub-problems until the

sub-problems become simple enough to solve. The solved sub-problems

can then be recombined to offer a solution for the original problem.

Elitism The process of ensuring the best individual survives from one generation to

the next.

**Evolvability** The ability for an EHW system to produce individuals fitter than those

found in previous generations (Altenberg, 1994).

Field-Programmable Gate Array An IC specifically designed to be reconfigured and programmed by a

designer after manufacturing.

Finite-State Machine A simple computational model containing finite number of states.

According to the received inputs, the machine transitions from one state to another (Daciuk, 1998). FSM are used as tools to design both computer

programs and sequential logic circuits.

Fitness Function The fitness function is a mathematical formula that is used to assess an

individual's ability. An individual is said to be fit if it successful fulfils the

requirements of a predefined objective function.

Fitness Landscape A fitness landscape is a visual metaphor used to describe the fitness of all

the possible solutions within the search space. There are peaks and valleys

within the landscape, with the highest peaks representing the fittest

solutions (Hubert, n.d.). Peaks can be grouped together, or scattered.

Genetic Operator The programming syntax used to add genetic diversity to population.

Examples include selection, mutation, elitism and crossover.

Genotype The string of integers that represent the necessary logic and routing data

needed to implement a particular digital circuit.

Genotype-Phenotype Mapping The process of encoding a digital circuit, or phenotype, into a genotype

(Vassilev & Miller, 2000).

**Mutation** The process of randomly changing random genes within a chromosome.

On-Chip Evolution An evolutionary setup which incorporates the evolutionary algorithm on a

separate processor incorporated into the same chip containing the target

EHW (Torresen, 2004, p. 6).

Output Element The logic response of a single external output when evaluated using a

single test vector.

Output Vector The collective logic responses of all external outputs when evaluated using

a single test vector.

**Phenotype** The genotype's circuit

**Portability** The ability of a system to be implemented on different target platforms.

**Scalability** Refers to an EHW problem being unsolvable due to the scale of the desired

solution. The complexity of a circuit greatly impacts the GA's search space. As a result, complex circuits become exponentially difficult to evolve. Scalability becomes more prominent if: the EHW system uses too few LEs—the desired circuit cannot be evolved due to a lack of resources; or too

many LEs—the search space is too large.

**Search Space** The set of all the potential solutions.

Soft-Processor A microprocessor core that is implemented using the programmable logic

of semiconductor devices.

**Stalling Effect** The fitness of a population does not increase over a substantial number of

generations.

System on a Programmable Chip Mead (2001) defines an SOPC as "a set of functional blocks built on a

programmable devices, with at least one computing engine." The programmable device is usually an FPGA, while the computing engine is

usually a soft-processor.

**Test Vector** A combination of logic high and low signals sent to the V-FPGA's external

inputs in order to evaluate a phenotype's response.

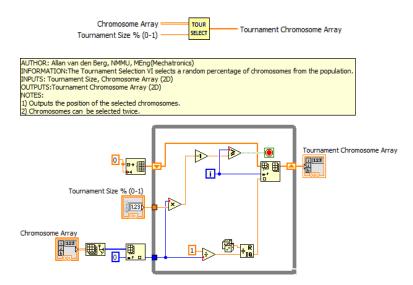

**Tournament Selection** A selection scheme which selects a group of n random individuals from a

population of p individuals, where n < p (Engelbrecht, 2007, p. 137).

Very-Large-Scale Integration An IC architecture which combines thousands of transistors onto a single

chip.

# **NOMENCLATURE**

| .vi           | LabVIEW VI file-extension          | HDL    | Hardware Description Language |

|---------------|------------------------------------|--------|-------------------------------|

| ANN           | Artificial Neural Network          | IC     | Integrated Circuit            |

| API           | Application-Program Interface      | Ю      | Input or Output               |

| ASIC          | Application-Specific Integrated    | LCM    | Logic Configuration Memory    |

|               | Circuit                            | LE     | Logic Element                 |

| CGP           | Cartesian Genetic Programming      | LUT    | Look-up Table                 |

| Clock         | Clock line used by the LCM and RCM | MOSFET | Metal-Oxide-Semiconductor     |

|               |                                    |        | Field-Effect Transistor       |

| СР            | Critical Path                      | NI     | National Instruments          |

| CPLD          | Complex Programmable Logic Device  | NQF    | National Qualifications       |

|               |                                    |        | Framework                     |

| DAQ           | Data Acquisition                   | NRF    | National Research Foundation  |

| DSM           | Dynamic State Machine              | PC     | Personal Computer             |

| $D_{Logic}$   | Data line used by the LCM          | PIG    | Processing Integrated Grid    |

| $D_{Routing}$ | Data line used by the RCM          | PLA    | Programmable Logic Array      |

| EDA           | Electronic Design Automation       | RAM    | Random-Access Memory          |

| EHW           | Evolutionary Hardware              | RCM    | Routing Configuration Memory  |

| EA            | Evolutionary Algorithm             | RM     | Routing Matrix                |

| FPGA          | Field-Programmable Gate Array      | soc    | System on Chip                |

| FSM           | Finite-State Machine               | SOPC   | System on a Programmable Chip |

| GA            | Genetic Algorithm                  | V-FPGA | Virtual Field-Programmable-   |

| GDD           | Generalised Disjunction            |        | Gate-Array                    |

|               | Decomposition                      |        |                               |

| НА            | Half Adder                         |        |                               |

| VHDL         | Very-high-speed Integrated     | $WA_{Routing}$ | Write-address line used by the |

|--------------|--------------------------------|----------------|--------------------------------|

|              | Circuit Hardware Description   |                | RCM                            |

|              | Language                       | $WE_{Logic}$   | Write-enable line used by the  |

| VI           | Virtual Instrument (LabVIEW    |                | LCM                            |

|              | routine)                       | $WE_{Routing}$ | Write-enable line used by the  |

| VLSI         | Very-Large-Scale Integration   |                | RCM                            |

| VRC          | Virtual Reconfigurable Circuit | XOR            | Exclusive OR                   |

| $WA_{Logic}$ | Write-address line used by the |                |                                |

|              | LCM                            |                |                                |

### INTRODUCTION

This chapter introduces the field of Evolutionary Hardware and its significance in the context of modern VLSI microelectronics. Evolutionary Hardware makes use of special nature-inspired search algorithms. The chapter discusses these algorithms as well as identifies challenges surrounding the research field, and why it has not yet been widely implemented in industry. Finally, the key objectives for this research are noted, and a paper structure is outlined.

#### 1.1 Background

The development of microelectronics has boomed over the last four decades. Initially, in the sixties, integrated circuits (ICs) only hosted about 10 to 100 transistors (EngineersGarage, 2012). This was known as the Small- to Medium-Scale Integration era. During this era, IC developments were largely funded by the United States government for use in the military and space fields (Schnee, 1978). It was only later, in the seventies, that the manufacturing costs of ICs fell, allowing private firms to start penetrating industrial and consumer markets. By the mid-eighties, the transistor count on ICs well exceeded the 1000 range, thereby marking the Very-Large-Scale Integration (VLSI) age. Common examples of VLSI chips include microprocessors and Field-Programmable Gate Arrays (FPGAs). Today, ICs can typically contain millions of transistors, with programmable-logic device manufacturer Xilinx setting an industry record for 6.8 billion transistors on an FPGA chip (Yannou, 2011).

This rapid growth of technology was first observed by Intel's co-founder, Gordon Moore, when in 1965 he predicted that the number of transistors on ICs would double approximately every two years (Moore, 1965). However, as the transistors count increases, there has been a desire to make computer hardware more complex and physically smaller.

Consequently, this is causing a bottleneck in the development of circuit designs. Enhancements in hardware design have been achieved by improving hardware-fabrication processes and using better-designed components, rather than optimising conventional circuits to make them more efficient.

Traditional circuit-design methodologies "rely on rules that have been developed over many decades" and require more human expertise for increasingly complex designs, which may be costly (Gordon & Bentley, 2002, p. 1). Complex designs are often tackled using powerful design tools, such as Electronic Design

Automation (EDA), high-level abstraction design-techniques and advanced IP-core libraries. However, the design-productivity gap is still increasing (Cancare, et al., 2011).

One solution to this design problem is Evolutionary Hardware (EHW). EHW is a combination of three disciplines: Computer Science, Electronics Engineering and Biology (Stomeo, et al., 2005, p. 1). Through modelling biological and natural intelligence, engineers and scientists have been able to mimic natural evolution in software for use in hardware design.

EHW has had a growing interest from many institutes across the world. Conferences, such as the Institute of Electrical and Electronics Engineers' International Conference on Evolvable Systems (IEEE ICES), allow researchers to share ideas and solutions in this research area. The IEEE (2013) describes the conference as "the leading conference in the field of evolvable hardware and systems." The conference's domain now covers a large array of research topics, including circuit diagnostics, self-repairing systems, evolutionary hardware design, real-world applications of evolvable hardware and evolutionary robotics. (See Thompson (1995), Higuchi et al. (1999), Hauschildt (n.d.), Barlow & Edwards (2001) and Moreno et al. (1998) as examples)

Despite the increased research and resources in the field, EHW systems remain largely unusable in real-world applications (Keymeulen, et al., 2003). Only a few engineering applications have shown promise (Higuchi, et al., 1999) (Mataric & Cliff, 1996), even though early pioneers claiming that evolution will soon be applied to large-scale machines (de Garis, et al., 1997). Researchers have raised a number of issues that have retarded the growth of EHW applications. These include the difficulties in configuring EHW platforms, scalability (Bedi, 2009), evolution time and problem complexity (Krohling, et al., 2002).

#### 1.2 Evolutionary Hardware

EHW can be categorized into two main areas (Greenwood & Tyrrell, 2006, p. 9), namely Evolvable Hardware and Evolved Hardware:

- 1. Evolvable Hardware, or open-ended evolution, refers to hardware devices that can autonomously adapt to dynamic environments (artificially-intelligent systems), or automatically recover from hardware failures (fault-tolerant systems) (Sekanina & Freidl, 2005). Thus, open-ended evolution continuously evolves solution according to the environmental stimuli, while the best solution found so far is executed (Cancare, et al., 2011). Examples include temperature and radiation tolerant electronics (Keymeulen, et al., 2004) (Stocia, et al., 2004), robot controllers (Nolfi & Floreano, 2000) and image filters (Sekanina, 2002).

- 2. Evolved Hardware, or complete evolution, refers to the automatic synthesis of novel hardware circuits. Once a solution is found, the evolution is stopped. Evolved hardware is often more efficient—uses less hardware components—than conventional circuits (Miller & Job, 1999).

An example of this efficiency was demonstrated by in 2003, when Koza et al. (2003) examined six different circuit patents, filed between 2000 and 2001, which were issued to universities or

commercial enterprises. Koza et al. (2003) used EHW to automatically synthesize new circuits that duplicated the patented circuits' functionality. It was found that only one of the six evolved circuits infringed on the original circuits' patents. This example clearly highlights the power of EHW, since Koza et al. (2003) only had to identify the desired outcome of the synthesized circuits; and had minimal knowledge on how the circuitry worked.

This research will concentrate on the advantages and downfalls of Evolved Hardware—in particular, how it can be applied when creating control circuitry. But first, in order to understand Evolved Hardware, one needs to examine the two fundamental parts that all EHW systems make use of: an Evolutionary Algorithm (EA) and an evolution platform.

#### 1.2.1 Overview of Evolutionary Algorithms

Natural evolution is a process, taken by organisms or systems, with the aim of optimising the survival rate of the species within a dynamically changing environment (Engelbrecht, 2007). Darwin (1859) first coined the term "natural selection", which became the theoretical foundation of biological evolution. The Darwinian theory of evolution, as summarised by Engelbrecht (2007, p. 127), states:

In a world with limited resources and stable **populations**, each **individual** competes with others for survival. Those individuals with the "best" characteristics or traits are more likely to survive and to reproduce, and those characteristics will be passed on to their offspring. These desirable characteristics are inherited by the following generations, and over time become dominant among the population.

The second part of the summary states:

During the production of a child organism, random events cause **random changes** to the child organism's characteristics. If these new characteristics are of benefit to the organism, then the chances of survival for that organism are increased.

Taking cues from biology, computer scientists have been able to code various search algorithms that mimic evolution, which are collectively known as EAs. EAs and biological evolution share many commonalities, which have been highlighted using bold text in the quotations above, and are discussed further below:

- A population with individuals: An initial population is established in which all the individuals represent potential solutions to the computer problem.

- Selection and survival of the best individuals: Individuals are first evaluated using a problemspecific fitness function. A fitness function is a function that evaluates how closely an individual is to

achieving the desired objective. Fitness is often represented as a percentage, where a 100%-fit individual would be considered completely fit. Once fitness is established, a selection operator is applied to the population. Many selection operators exist, but fundamentally, they all select one or more of the fittest individuals from the population, usually with a degree of randomness. Then, these selected individuals become the parents that produce offspring.

- Reproduction to produce offspring: The selected parents reproduce using a crossover operator.

Crossover recombines two parents in such a way as to allow the best characteristics of each parent to be passed to the offspring.

- Random Changes: A randomised mutation operator is applied to each offspring, thereby making each offspring unique. This allows diversity to be introduced into the new population. The above crossover and mutation procedures are repeated until a completely new population of offspring is produced—called a generation.

#### 1.2.2 Using Evolutionary Algorithms to Evolve Hardware

When EAs are applied to digital logic, either at gate-level (by using gates such as AND, OR, XOR-gates), or function-level (by using micro-circuits such as adders, multipliers, multiplexers), they can be used to automatically design and synthesise complex circuits. This is essentially how most EHW systems are implemented. The level at which the evolution is performed is called "granularity", with gate-level evolution being fine, and function-level evolution being course (Cancare, et al., 2011, p. 2).

Various forms of EAs have been used to solve EHW problems. Examples of EAs include Cartesian Genetic Programming (CGP) (Miller & Thomson, 2000), Adaptive Genetic Algorithms (Ko, et al., 1997), Parallel Genetic Algorithms (Wang, et al., 2007) and Particle Swarm Optimisation (Eberhart & Kennedy, 1995). One of the more researched EAs used in EHW is the Genetic Algorithm (GA) (used by Gordon (2005), Sekanina & Friedl (2005), Martin & Poli (2002)).

Rustem (2012) claims that from 1990 to 2010, over 80 000 GA<sup>1</sup> journal papers have been published by Springer. In 2010 alone, approximately 12 200 papers were published. The trend seems to be increasing, showing that the GA-research field is still in its infancy.

GAs are often referred to as search algorithms because they search, in a structured manner, for a solution that possesses the correct combination of parameters. "The set of all possible combinations of parameter values" is known as the GA's search space (Gordon, 2005, p. 17). Thus, since there are millions of combinations of circuits a GA has to search through, GAs typically have large search spaces from which a solution needs to be found.

\_

<sup>&</sup>lt;sup>1</sup> To clarify—"80 000 GA journal papers" includes all GAs relating to the computer-science field, and not necessarily GAs relating to only EHW.

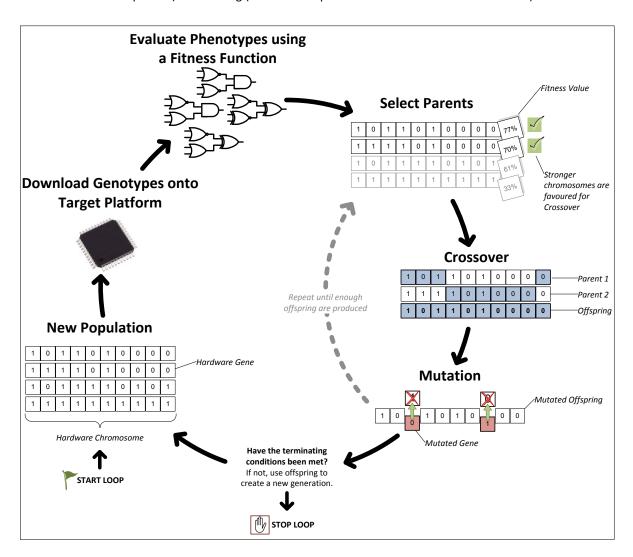

Figure 1.1 shows an overview of an EHW system using a GA. The GA is executed using a continuous loop. Every iteration of the loop produces a new generation of individuals.

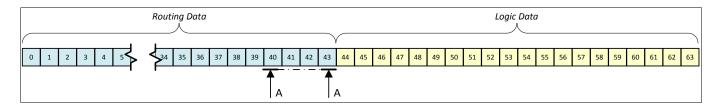

In EHW, each individual is represented using a hardware chromosome—also called the genotype. A hardware chromosome is a string of integers that represents a certain circuit configuration when decoded. Each single integer in the hardware chromosome is referred to as a hardware gene.

The decoded circuit is known as the phenotype. Phenotypes are configured in terms of functionality (the function of each component) and routing (how the components are connected to one another).

Figure 1.1 Overview of the Hardware Evolution process using a Genetic Algorithm

The Figure 1.1's loop starts by creating an initial population of hardware chromosomes using random values, with each hardware chromosome representing a circuit and a potential solution. The chromosome are then decoded into the phenotypes and downloaded onto the EHW platform. The phenotypes are evaluated using a fitness function in order to establish which circuits have the most desirable characteristics. This is done by either implementing and testing the phenotypes using a simulated software model, or loading the circuits

onto reconfigurable hardware. There are many different types of reconfigurable hardware testing platforms, which are discussed in the next section.

Once evaluation is complete, the GA operators are applied to the chromosomes, namely: selection, crossover and mutation. These genetic operators are used to maintain genetic diversity in the population.

The above process is iterated until either a perfectly fit individual is found, or a predefined number of generations are executed.

#### 1.2.3 Hardware Evolution Platforms

To explore the different platforms<sup>2</sup> on which evolved circuits can be evaluated, we need to first consider the rate at which modern circuits and components are advancing. The field of EHW is very reliant on the underlying platform technology it is based on. The idea of implementing evolutionary characteristics into hardware and software systems has been around since the 1950s (Rustem, 2012), but it is only since the early 1990s that the hardware platforms have not constrained EHW systems (Iwata, et al., 1996). In addition, more recently, in the field of microelectronics, the feature size of components has decreased from 2-3 $\mu$ m in 2002 to 0.09 $\mu$ m in 2004 (Greenwood & Tyrrell, 2006), allowing for faster EHW systems to be implemented and thus allowing greater advancements to be made in the EHW field.

There are four major digital hardware platforms on which EHW has been tested (Lambert, et al., 2009):

- 1. Application-Specific Integrated Circuits (ASICs): These application-specific ICs are designed to execute EHW within very specific parameters. The chips are custom made according to the designer's EHW needs. ASICs are considered to be the least flexible hardware platform; and because of their uniqueness, are expensive to manufacture.

- 2. Programmable Logic Arrays (PLAs): A PLA chip provides limited flexibility in that it can only implement circuits consisting of AND and/or OR-gates. They are considered cheap devices.

- **3. Complex Programmable Logic Devices (CPLDs):** Similarly to PLAs, CPLDs also have limited flexibility—they can implement circuits using AND, OR and/or XOR-gates.

- **4. Field-Programmable Gate Arrays (FPGAs):** These devices are very flexible (allows for the reconfiguration of a circuit's routing and functionality), readily available and competitively priced when compared to ASICs.

Due to point four above, FPGA's have become the preferable choice for many EHW researchers (see (Moreno, et al., 1998) (Lambert, et al., 2009) (Sekanina & Freidl, 2005) (Smith, 2010) as examples), and thus this research will make use of the FPGA platform to evolve a control circuit. However, before exploring FPGAs further, it is first necessary to discuss the design of a control circuit using a finite-state machine.

-

<sup>&</sup>lt;sup>2</sup> "Platform" in this case refers to the target hardware (i.e. board, IC, or chip) on which the evolved circuits (phenotypes) are implemented.

#### 1.3 Evolving a Finite-State Machine

In the previous sections, the EHW field was broadly introduced. We will now describe, in the section below, the opportunity EHW presents when synthesising the control circuitry of a finite-state machine (FSM).

State machines are one of the oldest and most used ways of modelling the behaviour of systems (Wright, 2005). They are actively used in systems of: hardware design; biology; genetic; processing and retrieval of text information; and verification (Kryvyi, 2011). All state machines, regardless of their application, make use of the following fundamental principles:

- The whole system is described using a set of states

- The machine can only be in one state at a time

- To change to another state, a triggering event has to be initiated

A FSM, which is simply a state machine with a predefined finite number of states, can be used to help aid the design of a sequential-logic control system. FSMs consist of a set of states, an initial state, a set of finite inputs/outputs and a finite number of triggering events (Black, 2008).

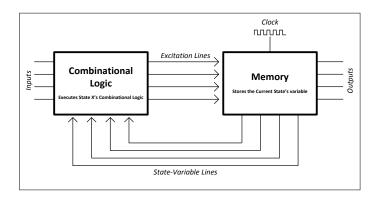

Consider the following example of a FSM, being implemented in hardware as a sequential circuit, as explained by Floyd (2009, p. 436). A general FSM's circuitry, as shown in Figure 1.2, consists of a combinational-logic and memory section. The memory, which is often implemented using flip-flops, stores the state variable, i.e. current state's number. At any given time, the memory is in a state called the *current state*, and transitions to the next state on a clock pulse according to the conditions on the excitation lines. The combinational logic controls the system's excitation lines according the system's inputs.

Figure 1.2 A general FSM's circuit implemented as a sequential circuit

Now, consider the combinational logic. In order to advance to the next state, a triggering or input condition needs to be met. If met, the relevant excitation lines are activated, thereby initiating the next state-variable in memory. The state variable is communicated to the combinational logic via the state-variable lines.

Most FSM are cyclic in nature, and execute unconditionally. There are many examples of FSM circuits used as cyclic control systems. Examples include counters, traffic lights, wristwatches, turnstiles and elevators (see (Floyd, 2009) (Harel, 1986) (Wright, 2005) for examples).

In evolved hardware, much emphasis has been placed on evolving simple, functional circuits, as opposed to evolving real-world FSM circuits. The functional circuits include multipliers, adders, filters and oscillators (see (Vassilev, et al., 1999), (Sekanina & Freidl, 2005), (Sekanina, 2002), (Thompson, 1995) for examples). These simple circuits have been popular because they are small and practical enough to evolve, while still allowing the researcher the ability to test and adjust new EHW platforms, GAs and architectures.

Nevertheless, Rustem (2012) did manage to evolve a complex six-state, four-input/four-output FSM. Two key points, taken from Rustem's (2012) research, include:

- 1. The FSM was evolved using a software simulation, i.e. it was not evolved using a hardware platform

- 2. The final circuit was tested on a CPLD and not an FPGA

These two points are significant, as even though this research will also aim to evolve a four-input/four-output FSM, it will differ to previous research by not simulating the evolution and not using a CPLD. Instead, the FSM will be evolved and implemented on an FPGA platform.

#### 1.4 Problem Statement

There are three main problems addressed in this study:

- 1. The difficulty of configuring modern FPGAs to implement EHW

- 2. The influence of different genetic operators on the efficiency of EHW GAs

- 3. Using modular evolution to address scalability issues when evolving FSMs

#### 1.4.1 The Virtual Reconfigurable Architecture

Altera (2013) describes FPGAs as "semiconductor devices that can be programmed after manufacturing." This is a particularly vital advantage in that an FPGA allows the designer to reconfigure the hardware architecture according to the designer's EHW needs.

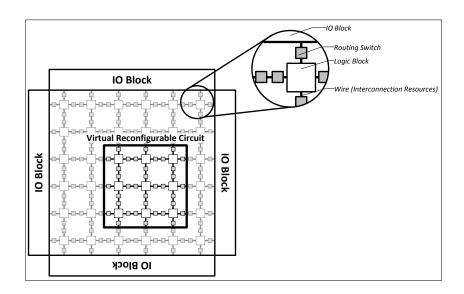

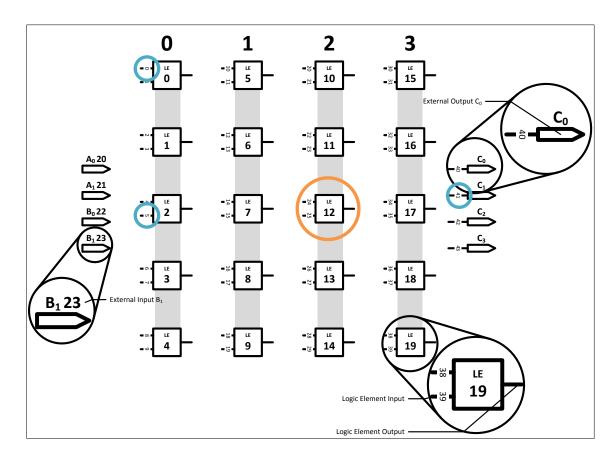

In order to understand this reconfiguration, first consider the simplified internal structure of an FPGA, shown in Figure 1.3, consisting of IO blocks, logic blocks, routing switches and wires. FPGAs use thousands of basic programmable logic blocks which are arranged in a row/column matrix formation and connected via reconfigurable interconnections. By allowing the logic blocks to communicate to one another and to external hardware via the IO blocks, complex combinational logic and sequential logic operations can be performed. This allows the user to implement any hardware circuit on the FPGA by simply reprogramming the chip's configuration.

Figure 1.3 Overview of an FPGA with a virtual reconfigurable layer

When programming an FPGA, the designer makes use of the FPGA vendor's software, which loads the circuit's configuration data onto the FPGA using a configuration bitstream. The bitstream is a sequence of bits which describes all the necessary data needed to implement the user-defined circuit, and is stored in the FPGA's configuration memory. In the case of EHW, the hardware genotypes would be decoded into an FPGA bitstream in order to implement the phenotype circuit.

The initial FPGAs used for EHW, such as the Xilinx 6200 used by Thompson (1996) and Gers, et al. (1998), offered many evolutionary-friendly features, including partial reconfigurations, access to single logic blocks, an open architecture and protection against illegal configurations (Haddow & Tufte, 2001). However, the Xilinx 6200 FPGA is now obsolete and most modern FPGAs have become less EHW-friendly.

FPGA manufactures have prohibited the modification of the configuration memory or bitstreams, claiming that it is "intellectual property" or "proprietary to the vendor" (Bedi, 2009, p. 2) (Majzoobi, et al., 2012, p. 200). The only FPGA devices capable of performing bitstream configurations are the "Xilinx 4000" and the "Xilinx Virtex series" (Smith, 2010, p. 1) (Bedi, 2009, p. 1). Still, even though these FPGAs can be used, few evolution features, found on the original Xilinx 6200, have been retained.

To overcome this problem, Xilinx introduced JBits. JBits is a set of Java classes that allow the designer access the FPGA's bitstream via an application-program interface (API) (Guccione & Levi, 1999). This, in turn, gives the designer the capability of designing, modifying and dynamically modifying circuits on JBits-enabled FPGA devices.

However, JBits has shortcomings: larger EHW chromosomes can be cumbersome to dynamically decode into bitstreams; JBits can only be used on Xilinx FPGAs; JBits can only be configured using external hardware attached to configuration ports.

In light of the above-mentioned problems, a more promising solution, used in this research, is the virtual-reconfigurable-circuit (VRC) architecture. A VRC, as shown in Figure 1.3, is a virtual reconfigurable layer residing on top of the FPGA hardware layer. The VRC allows the designer access to its virtual configuration memory (i.e. a set of registers) and bitstream (i.e. the chromosome), thus allowing run-time configuration of the FPGA to be performed.

Notice, in Figure 1.3, that the VRC only makes use of a portion of the FPGA's available logic blocks. This is because VRCs maintain complete encapsulation during evolution. Designers thus have the opportunity to utilise the remaining logic blocks for other digital functions, such as implementing a soft-processor.

There is no standard for VRCs—each VRC is unique, and thus VRCs are made to the exact requirements of a given EHW application. Different designers may create different virtual architectures that perform similarly, but utilise different methodologies.

In 2010, Smith presented a VRC architecture called the Virtual-FPGA (V-FPGA). It was shown, through software simulation, that the V-FPGA was successfully configured to implement a clock-divider circuit. However, the V-FPGA also presented a drawback. Smith (2010, p. 2) noted that any reconfigurable architecture, which is built on top of an FPGA architecture, creates inevitable "inefficient resource utilisation". This disadvantage, however, is negligible for prototyping EHW applications. Most VRC architectures have shown promise in the EHW field (Sekanina & Freidl, 2005).

#### 1.4.2 Optimising Genetic Operators for use on the Virtual-FPGA

Variations in GAs—such as changing the population size, crossover, selection and mutation—may a have vast impact on the performance of the algorithm. From the literature, GA operators are usually optimised for each EHW system according to the makeup of the evolutionary platform and architecture, the complexity of the circuit being evolved, the fitness function and the representation of the hardware chromosome. Thus, every GA is unique to the specific application.

Vassilev et al. (1999) tested the effectiveness of the crossover and mutation operators in a GA configured to evolve a two-bit multiplier. They did this by examining the GA's fitness landscape<sup>3</sup>. The setup made use of a VRC which could reconfigure 16 LEs according to their function and routing. Each cell could function as either a two-input logic gate or a 2-1 multiplexer. Restrictions were also applied to the circuits' outputs: Outputs could only be connected to a select number of cells.

Vassilev et al. concluded that uniform crossover was not a favourable operator for evolving the functionality and internal connectivity of the evolved multiplier. Furthermore, Vassilev et al. states, "the mutation landscapes appear to be relatively smooth, and therefore, it is feasible for an evolutionary search." Although

-

<sup>&</sup>lt;sup>3</sup> Fitness Landscape: A collective term for the fitness values of all the possible solutions within the search space.

many EHW researchers have, and still do, obtain success using crossover (see (University of Heidelberg, 2011) (Miller & Thomson, 1998)), Vassilev et al. suggests that by omitting crossover and using mutation only, the GA may be optimised.

The above findings were successfully demonstrated by both Vassilev & Miller (2000) and Selanina & Freidl (2005). The latter evolved both an adder and multiplier circuit by omitting crossover, constraining the LEs' functionality and using effective fitness functions.

It is important to note that all the sources, used in this section, have implemented different EHW architectures, platforms, cell restrictions and GAs. Thus, because each EHW system is unique, it would be advantageous to investigate the outcome of optimising the EHW GA—as done by Selanina & Freidl (2005)—to evolve a two-bit multiplier on the V-FPGA.

Evolving a multiplier circuit is a good starting point when experimenting with a new EHW architecture and setup. Multipliers have been well researched (Miller & Thomson (1998), Vassilev et al. (1999) and Selanina & Freidl (2005)), are mathematically useful and are relatively uncomplicated.

#### 1.4.3 Scalability

Since EHW makes use of search algorithms that need to explore large search spaces, the intricacy and sheer scale of finding a solution becomes more apparent as the solution circuit becomes more complex. Many researchers have recognised that scalability is a hindrance in the successful implementation of EHW in real-world applications (Gordon & Bentley, 2005) (Vassilev & Miller, 2000).

Scalability, in this context, refers to the difficulty of finding a satisfactory solution for large, complex problems—those found in real-world applications—due to the GA's search space being too large, or the solution being too complex to be implemented on the EHW system. To put scalability in context, remember that EHW systems have to evolve circuitry by placing logic gates—often thousands of logic gates in larger systems—in very specific configurations. In addition, as the complexity of the circuit increases, so the genotype length and the time required to calculate the fitness of each phenotype also increases. This results in there being billions of potential solutions which are cumbersome and time-consuming to explore, even with evolutionary techniques.

One suggested solution to scalability is function-level evolution, which uses micro-circuits as the building blocks for larger complex circuits (Higuchi, et al., 1997) (Antola, et al., 2007). However, function-level evolution merely moves the problem: A designer is still needed to successfully identify the suitable function-level circuits. Also, function-level evolution is inheritably inefficient due to the evolution not being performed at the lowest gate-level. For instance, a three-bit multiplier requires only 23 LEs using gate-level evolution (Vassilev & Miller, 2000); compared to 14 LEs and 7 three-input binary multipliers (Miller, et al., 2000).

A more reasonable approach, which follows on from function-level evolution, is modular evolution. (Some literature refers to *modular evolution* as *incremental evolution*.) Modular evolution simplifies an EA's search space by decomposing the desired circuit into smaller modules, and then re-assembling the smaller modules once evolved. This process of circuit decomposition-and-assembly is inspired by the divide-and-conquer principle, which has been observed in biological systems (Torresen, 1998) (Wang, et al., 2007).

Since each module, or sub-circuit, can be independently evolved using gate-level components, the evolution allows for fine-granularity (Gordon, 2005). Gordon (2005, p. 16) goes on to further state that modularisation in evolutionary designs have "proved useful in many respects", however have still not caught up with the modular evolution used in "biological organisms". For example, mammals are modular, comprising of sub-components such as organs and tissue. Each sub-component has been specifically evolved in order for the mammal to thrive in its natural environment.

Modular evolution is not a new concept. Torresen (1998) showed, through experimentation, that the number of generations required, when using smaller sub-systems, "can be substantially reduced when compared to direct evolution." Similar results are concluded by Vassilev & Miller (2000): "To evolve digital circuits using modules is faster, since the building blocks of the circuit are sub-circuits rather than two-input gates."

This research will demonstrate that by modularising EHW problems, EHW systems are able to synthesise larger, complex circuits that are typically not directly evolvable due to scalability. In particular, unlike the previous research, the modular evolution will be applied to a FSM's circuitry.

#### 1.5 Statement of Objectives

#### 1.5.1 Major Objectives

With the above background considered, there are three major objectives addressed in this research:

- 1. This research will form a continuation of the research done on the V-FPGA architecture designed by Smith (2010). Smith (2010) first introduced the V-FPGA in his paper entitled, "A Virtual VLSI Architecture for Computer Hardware Evolution". The paper's objective was to "provide and method to facilitate hardware evolution" and "not to demonstrate hardware evolution." It thus follows that this study will aim to show, by successfully implementing and demonstrating evolved hardware on an FPGA, that practically the V-FPGA is a viable evolution platform.

- 2. Following Vassilev et al. (1999) and Selanina & Freidl's (2005) research, this study will explore the effectiveness of optimising the EHW GA for use on the V-FPGA by omitting the crossover operator, applying evolution constraints and optimising the fitness function. The GA will be used to evolve smaller circuits, such as a two-bit multiplier, in order to provide a viable means of studying major EHW issues, such as: scalability, evolution time, circuit efficiency and the V-FPGA configuration.

3. Finally, once the V-FPGA and GA are optimised, modular evolution will be demonstrated by evolving the circuitry required for a simple, but real-world FSM. This will aim to show that larger control circuits may be scalable if the evolution process is constrained.

#### 1.5.2 Minor Objectives

In order to achieve the major objectives, the following minor milestones have to be attained:

- The V-FPGA architecture has to be verified through simulation.

- A genotype representation of the phenotype has to be devised, i.e. a standard by which all the phenotypes' data can be represented and modified in software.

- A software procedure for decoding the genotypes into phenotypes has to be programmed.

- An effective fitness function, which correctly evaluates the outcome of each phenotype, must be developed.

- The size of the GA's search space needs to be investigated.

- A critical-path analysis of each circuit needs to be completed in order to understand the manner in

which the circuits are evolved. With this knowledge, better fitness functions and operators can be

developed to further enhance the EHW system's efficiency.

#### 1.6 Methodology

The research methodology is outlined as follows:

- 1. Create a V-FPGA VHDL file and simulate a two-bit multiplier using software.

- 2. Create a larger V-FPGA, and download the VHDL file onto an FPGA chip.

- 3. Create a LabVIEW GA which can evolve a two-bit multiplier.

- 4. Optimise the GA, through experimentation, by adjusting different operators.

- 5. Use the optimised GA to evolve the combinational circuits used in a FSM.

To create a V-FPGA VHDL-based file, the following parameters have to be defined: the number of logic elements (LEs); the number external inputs and the number of external outputs. Initially, the V-FPGA will be configured to use four external inputs, eight LEs and four external outputs. This configuration will be adequate to implement a two-bit multiplier on the V-FPGA. Through software simulation, the conventional two-bit multiplier will then be tested, thereby validating if V-FPGA architecture works correctly.

Once the simulation is successful, a larger V-FPGA will be configured using four external inputs, twenty LEs and four external outputs. This V-FPGA configuration will be used, in conjunction with the GA, to evolve the control and multiplier circuits. To do this, V-FPGA will be downloaded onto an FPGA chip.

The GA will be programmed using LabVIEW software on a PC. Since the GA and V-FPGA will not be executed on the same processor, this research will demonstrate off-chip evolution. Off-chip evolution occurs when the

evolutionary algorithm is performed on a separate processor not incorporated into the chip containing the target EHW (Torresen, 2004).

A two-bit multiplier will first be evolved using different GAs operators, constraints and fitness functions. For the successfully implemented GA, the number of generations, fittest parent per generation, phenotype and evolution time will be recorded. Appropriate statistical and design comparisons will be made between the evolved phenotype and the conventional multiplier circuit.

Finally, an example eight-variable FSM case study will be also be evolved. This case study will demonstrate the modular evolution of a FSM's state circuits. Since the V-FPGA and GA will be constrained to only evolve forward-feed circuits, only the combinational section of the FSM will be evolved. Similar to the evolved two-bit multiplier, the evolution time, number of generations and final phenotype will also be recorded.

#### 1.7 Paper Structure

The dissertation will continue with a literature review in Chapter 2. The chapter will begin with a brief history of the EHW field; and will conclude by identifying several difficulties hindering the implementation of real-world applications.

Chapter 3 will discuss the V-FPGA architecture. The chapter will be presented in twofold: first, how to configure a circuit's LEs within the V-FPGA; second, how to configure a circuit's routing structure using a specialised Routing Matrix. The chapter will close with the simulation of a two-bit multiplier.

Chapter 4 will illustrate the evolution of a two-bit multiplier using the V-FPGA architecture. The chapter will start by describing the experimental hardware setup. Part of the setup will include configuring and compiling the V-FPGA on an FPGA chip. Once configured, the effectiveness of two different GAs will be investigated. Finally, the chapter will end with an account of three evolved multiplier phenotypes as well as a discussion on the arising evolution difficulties, the possible causes and solutions.

Chapter 5 will be to demonstrate a means of overcoming scalability by using modular evolution. The chapter will starts by introducing a case study and a real-world FSM. Then, the FSM will be modelled using a state and block diagram. Finally, each state's combinational sub-circuit in the FSM will be is independently evolved. The chapter will end with a discussion.

The final chapter will conclude the research by reviewing the study's contributions, and presenting considerations for future work.

## LITERATURE REVIEW

This chapter surveys the benefits and shortcomings of previous EWH systems. The chapter starts with a brief history of the EHW field, which was primarily driven by the development of reconfigurable FPGAs. Then, from the literature, several difficulties of implementing real-world applications are identified. In particular, scalability is addressed in detail, with a number of solutions being proposed.

#### 2.1 A History Driven by Target Platforms

#### 2.1.1 The Early Years

EHW can first be traced back to 1993, when de Garis (1993) published a paper on "Darwin Machines". It was proposed that Darwin Machines would use EHW to evolve artificial nervous systems, which would be used to control artificial creatures and/or robots. de Garis believed that "software configurable hardware", in particular FPGAs, would allow the Darwin Machines to be realised "within a year or two".

However, this was not to be. In 1995 Xilinx introduced the XC6200 FPGA device-family—the first reconfigurable FPGAs (Lazzaro, 2010). It was only after the introduction of the XC6200 that the first research on implemented EHW was published. The research, conducted by Thompson (1996) over a three week period, showed how an EHW system managed to evolve a frequency discriminator able to distinguish between 1kHz and 10kHz square waves. The XC6216 FPGA allowed Thompson to directly reconfigure the FPGA's logic blocks by manipulating the configuration bitstream.

Thompson's work can be considered an important milestone in EHW, since it was the first publication to demonstrate the advantages of EHW through bitstream manipulation.

However, in addition to the evolution, Thompson's experimentation revealed that the evolved discriminator was susceptible to external conditions, such as temperature, and was device-dependent, i.e. the evolved discriminator malfunctioned when implemented on different FPGAs. These factors made the evolution volatile.

To address this volatility, Thompson turned his attention to the EHW system's "robustness". Robustness, as defined by Thompson (1998, p. 1), means "to be able to maintain satisfactory operation when certain variations in the circuit's environment or implementation occur." To increase robustness, Thompson created

an "Evolvatron" tool to simultaneously test the evolved circuits in different conditions and on different devices. By testing the circuits in all conditions, a more precise fitness function could be used to accurately award fitness values (Thompson, 1999). The Evolvatron proved to be a success.

Besides Thompson, other notable research done before 2000 was conducted by Torresen (1999), Higuchi, et al. (1999) and Macias (1999).

Torresen and Thompson's research have similarities: Both used the Xilinx 6200 FPGA and both initially lacked robustness. Torresen managed to evolve a character recognition system which performed as expected, however lacked "noise robustness". His paper also highlighted some reasons as to why EHW had not yet been widely applied—mostly due to scalability.

Higuchi, et al.'s research, in contrast to Torresen and Thompson, investigated an ASIC, which was named the "GRD chip", to dynamically reconfigure gates within the chip. The GRD chip, which made use of a RISC processor, evolved the hardware using an Artificial Neural Network (ANN) algorithm. The aim of the study was to introduce an EHW chip capable of solving a variety of real-world problems, such as robot navigation and the control of a prosthetic hand.

Similarly, Macias also created an EHW ASIC, called the "Processing Integrated Grid", or simply PIG, consisting of a reconfigurable-element grid which allowed the implementation any large digital circuit. What made the PIG architecture unique is that it was capable of parallel reconfiguration. Hence, different elements within the circuit could be evolved simultaneously.

#### 2.1.2 The Virtual-Reconfigurable-Circuit Era

Besides specialised ASIC chips, most FPGA-based EHW research before 2000 was performed on a Xilinx XC6200 device. Cancare, et al. (2011) and Hollingworth, et al. (2000) highlight some of the XC6200 features:

- Safe Reconfiguration: The FPGA could not be physically damaged through implementing illegal bitstream configurations that created short circuits.

- Partial Reconfiguration: Selected portions of the FPGA could be reconfigured independently.

- **Fast Reconfiguration:** The FPGA used a parallel interface, allowing faster configurations compared to previous devices.

- Static Random-Access Memory (RAM): The FPGA made use of static RAM that could be swiftly

accessed and rewritten through standard interfaces.

- **Known Data Format**: The well-known bitstream format allowed the designer to alter individual parts of the configuration.

In 1998, Xilinx withdrew the XC6200 device-family from further development, thereby indirectly halting any EHW research done using direct bitstream-manipulations (Lazzaro, 2010). The reasoning behind the

discontinuation, as Cancare, et al (2011, p. 3) explains, is that "the open bitstream format was allowing the reverse engineering of proprietary-hardware intellectual-property cores."

Later in 1998, Xilinx released the Virtex FPGA family to replace the XC6200. It retained most of the XC6200 features, but had drawbacks: Virtex FPGAs did not allow the designer direct access to the FPGA's bitstream or static RAM. In addition, the Virtex series allowed multi-directional routing, thus allowing unsafe and potentially damaging routing configurations (Hollingworth, et al., 2000).

Subsequently, the discontinuation was a major turning point. To combat the Virtex shortfalls, many designers attempted direct bitstream-manipulation by means of well defined APIs such as JBits (as discussed in Chapter 1) (Hollingworth, et al., 2000). However, although successful, JBits was limited and clumsy, and there was a need to find a more universal and standardised EHW approach—one which did not rely purely on Virtex FPGAs. As such, researchers proposed VRCs.

VRC-based solutions, such as those designed by Slorach & Sharman (2000), Sekanina & Azeddien (2000), Sekanina & Freidl (2005) and Smith (2010), generally always consisted of:

- Logic Elements (LEs): Programmable elements, sometimes called cells

- Programmable Interconnection Network: Connected the LEs and external IOs

- Configuration Memory: Stored the VRC's virtual bitstream so that the desired circuit could be implemented

To create a VRC, the above components would first be modelled at a higher level of abstraction, using either C++ or C. Thereafter, an executable file would be generated to produce the required Hardware-Description-Language (HDL) code needed to deploy the VRC on a target FPGA.

VRC architectures were able to make EHW systems portable by providing a standardised, device-independent means of configuring circuits on FPGAs through virtual bitstreams. Thus, VRCs provided a major advantage over specialised direct-bitstream-FPGA and ASIC systems.

#### 2.1.3 Future Platforms

The latest research done by Dobai & Sekanina (2013) investigated two new potential target platforms: Xilinx's latest EHW offering—a stand-alone programmable system-on-chip (SOC) called Zynq-7000; and a hybrid-VRC architecture.

The Zynq-7000 integrates programmable logic with a dual-core ARM processor. The main difference between the Zynq and previous FPGAs is that FPGAs are typically built around the programmable logic, with on-chip processors being an extension, i.e. part of the programmable logic is configured into a soft-processor. On the contrary, the Zynq-7000 is an FPGA platform built around its hard-processor (Dobai & Sekanina, 2013). Thus, the processor and programmable logic are independent, and can be accessed and configured independently.

For example, the configuration bitstream can be downloaded from memory onto the programmable logic without utilising the processor.

Hybrid VRCs make use of both direct-bitstream and VRC architectures, and can thus only be used on specific Xilinx FPGAs. Essentially, a hybrid VRC uses the direct-bitstream approach to program the LEs' functionality, and the VRC architecture to route the LEs. In this way, hybrids are able to take advantage of VRCs' faster reconfigurations, while lowering the hardware resources needed to implement the VRC.

Finally, Dobai & Sekanina (2013, p. 7) concluded that "the hybrid approach represent computationally equal power to the pure VRCs." However, VRCs still present device-independent advantages. In addition, although the Zynq platform is promising, further work is needed to "exploit all the features and advantages of this platform."

## 2.2 Factors Delaying Real-World Applications

There has been extended research, with some success, into VRCs and target platforms to improve the portability of EHW systems. Thus, systems are becoming less device and application specific. However, there are additional factors which are delaying the field's progress.

Many researchers agree that real-world applications of EHW systems, such as the control circuitry on robots, have been, and still are, a major challenge (Higuchi, et al., 1999) (Cancare, et al., 2011) (Wang, et al., 2007) (Sekanina, 2003). From the literature, the following key areas have been identified as troublesome:

- 1. **Performance:** Conventional circuit-design methods currently outperform EHW. For example, only basic adder and multiplier circuits have been evolved.

- 2. **Cost:** Designing and manufacturing an EHW ASIC, or using the latest FPGAs, is costly.

- 3. **Time:** For intrinsic evolution, testing each chromosome becomes increasingly time-consuming as the number of external IOs increase.

- 4. **Scalability:** Digital circuits generally do not scale proportionally. For example, a two-bit multiplier can be evolved within 5000 generations, whereas a 3-bit multiplier could take as much as three million generations to evolve (Miller, et al., 1999).

- 5. **Chromosome Length:** Most EHW chromosomes use one-to-one mapping, where one gene configures either a single LE or a routing node. Thus, to evolve larger circuits, the length of the chromosome can be cumbersome and computationally taxing.

- 6. Variety of Research: Because the research field is varied (with each system using different target platforms, EAs and being designed for different applications) the research is scattered with each researcher's work tending to be isolated. Also, most literature only describes the EHW system and/or relevant results. Little technical detail such as coding and exact architecture implementation is included.

It is vital for designers to consider all the above factors holistically when designing EHW systems, as they all interlink. The factors are now discussed further in the subsections below.

## 2.2.1 Performance, Cost and Time

On both the Xilinx (2013) and Altera (2013) websites, the FPGA manufacturers state that FPGAs provide faster time-to-market and no non-recurring engineering costs—the costs of developing, designing and testing an IC—when compared to ASICs. Xilinx (2013) further states that FPGA devices do not require "complex and time-consuming floor-planning, place-and-route, timing-analysis and mask stages." Thus, FPGAs provide a clear advantage over ASICs when considering costs and flexibility—which are two important points considered by EHW researchers.

However, as discussed in Section 2.1.2, FPGAs can be limiting, and as FPGA vendor's release newer models, procuring the latest technology, such as the Zynq platform, can also be costly.

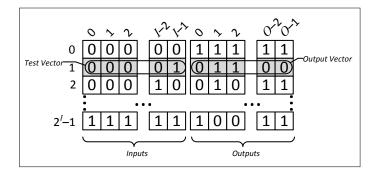

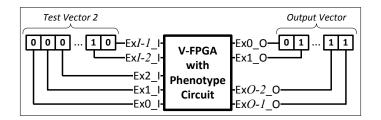

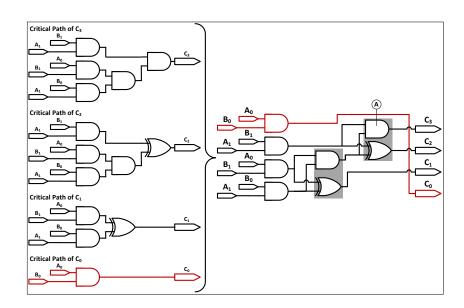

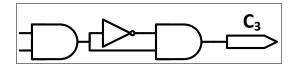

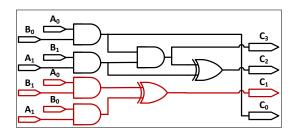

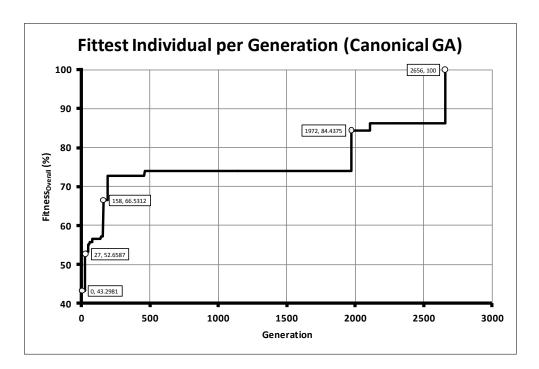

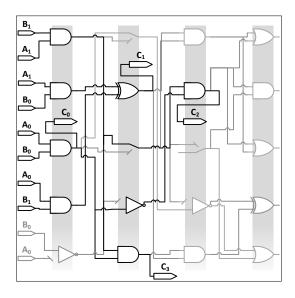

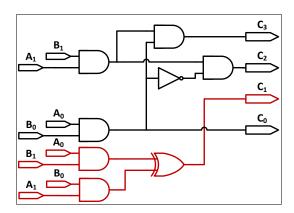

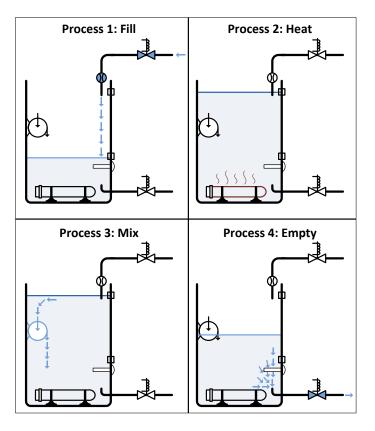

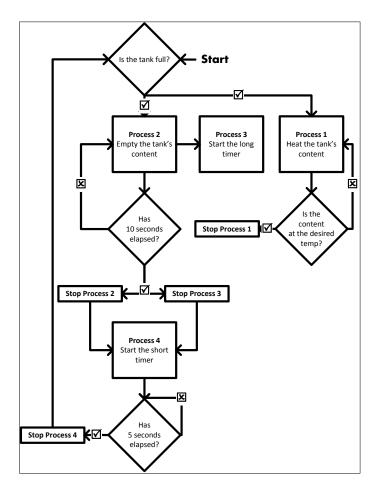

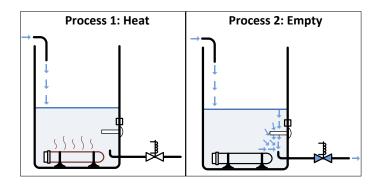

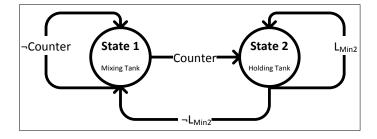

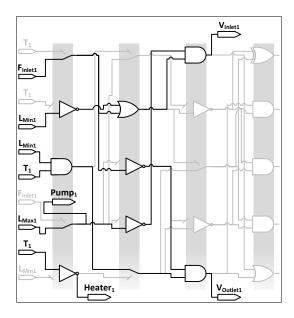

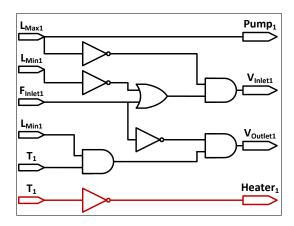

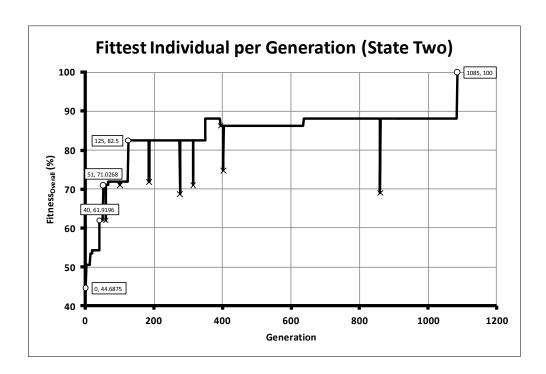

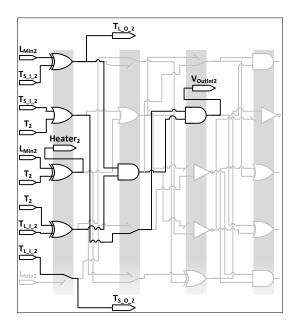

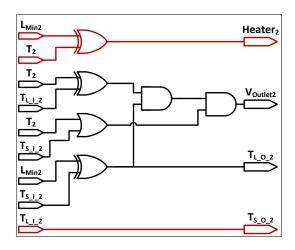

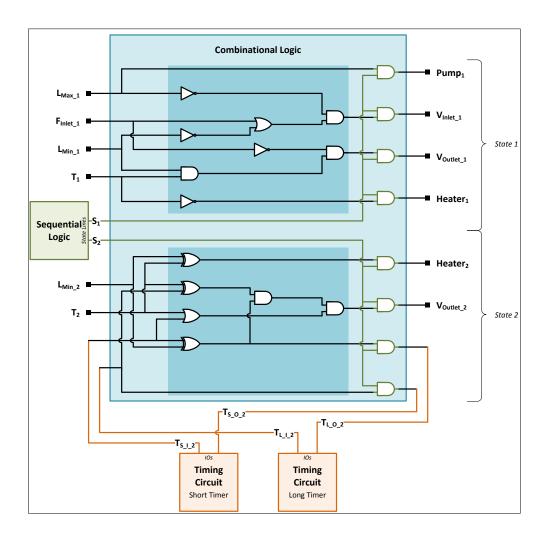

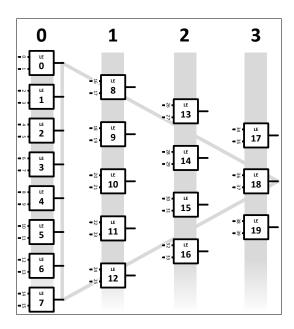

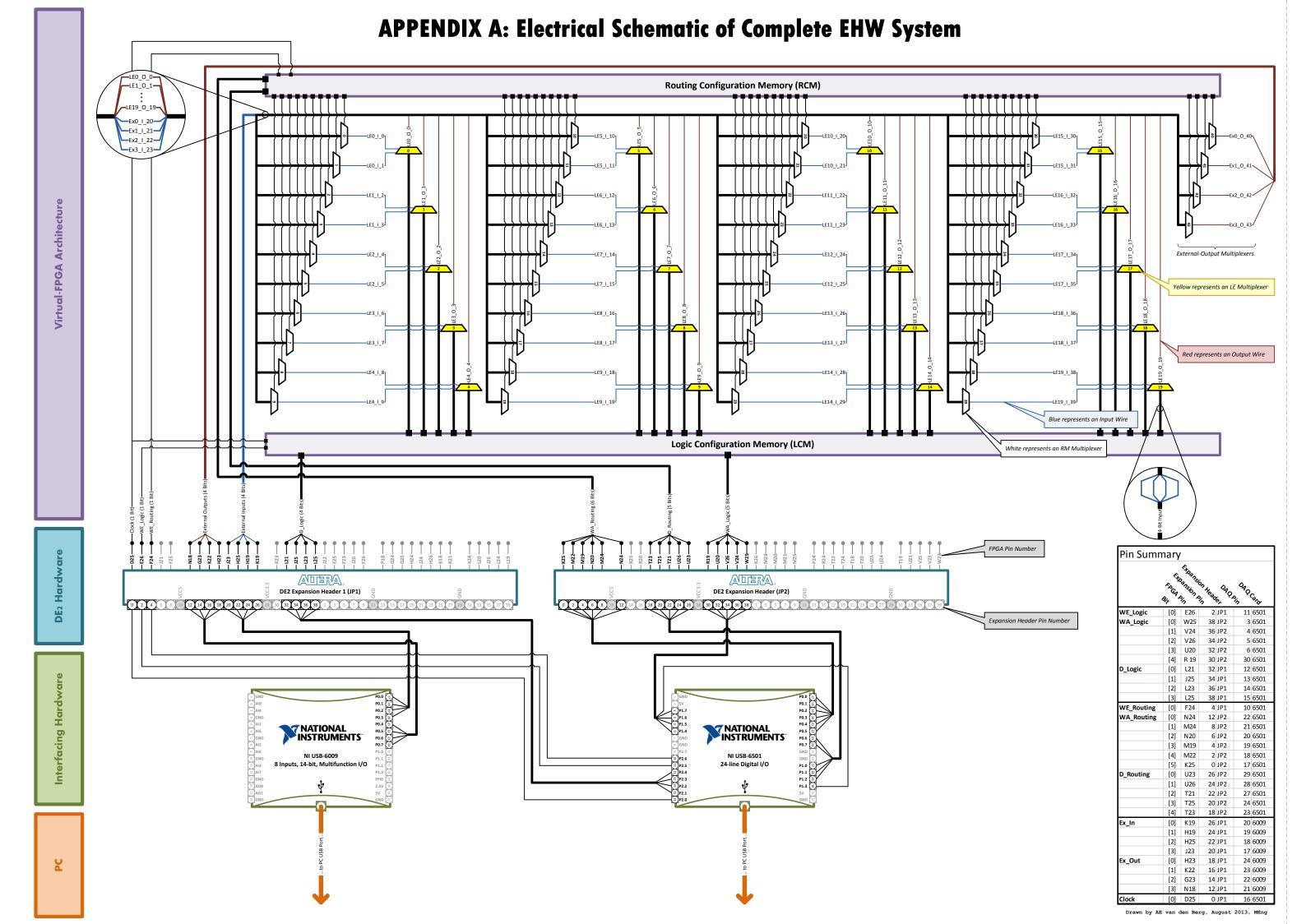

Generally, VRCs do help to minimise FPGA costs, since they have no special hardware requirements. But, even so, designers should be aware that although cheaper, VRCs do compromise on performance. This is because VRCs, by their very nature, are secondary configurable layers, which make use of FPGA logic blocks configured as multiplexers and registers to implement logic. Direct-bitstream evolution, on the other hand, does not require additional hardware resources. Thus, the evolution can be performed at higher frequencies with the evaluation of individuals being faster (Dobai & Sekanina, 2013).