## Computer control of an HF chirp radar

### THESIS

Submitted in fulfilment of the requirements for the degree of MASTER OF SCIENCE (ELECTRONICS) of Rhodes University

by

DESMOND BRYAN GRIGGS

December 1990 (Revised March 1991)

## Abstract

This thesis describes the interfacing of an IBM compatible microcomputer to a BR Communications chirp sounder. The need for this is twofold: Firstly for *control* of the sounder including automatic scheduling of operations, and secondly for *data capture*.

A signal processing card inside the computer performs a Fast Fourier Transform on the sampled data from two phase matched receivers. The transformed data is then transferred to the host computer for further processing, display and storage on hard disk or magnetic tape, all in *real time*.

Critical timing functions are provided by another card in the microcomputer, the timing controller. Built by the author, the design and operation of this sub-system is discussed in detail. Additional circuitry is required to perform antenna and filter switching, and a possible design thereof is also presented by the author.

The completed system, comprising the chirp sounder, the PC environment, and the signal switching circuitry, has a dual purpose. It can operate as either a meteor radar, using a fixed frequency (currently 27,99 MHz), or as an advanced chirp ionosonde allowing frequency sweeps from 1,6 to 30 MHz. In the latter case fixed frequency doppler soundings are also possible. Examples of data recorded in the various modes are given.

## Declaration

I declare the contents of this thesis to be my own unaided work, with the exception of the following software routines:

TMS320 FFT - Delanco Spry

DSP16 assembler driver routines - Ariel

TMS320 ionosonde routines - BT Bonnevie

Pascal DCS and Tape driver - BT Bonnevie

In addition all the processed meteor data results presented here were produced by Prof G Poole.

This thesis is being submitted for the degree of Master of Science in Electronics at Rhodes University, Grahamstown. It has not been submitted before for any degree or examination at any other university.

DB Griggs

689G4433

On this the 31'st day of December 1990

# Acknowledgements

Firstly thanks must go to my supervisor Dr Allon Poole for proposing and funding the project.

Secondly to my other supervisor Prof Graham Poole for the use of his equipment and for tolerating my interference with his meteor research programme.

To Mr Andries Delport and Mr Ronnie Seeber of Mikomtek, for the use of their sounder and signal processing card, and general interest expressed by them in the project.

To all the staff in the Physics department and Electronic Services at Rhodes, particularly the late Mr Barry Guthrie, for their advice and expertise.

Prof Pat Terry from the Computer Science department for his assistance during my software evaluation.

Mr Andy Soper for the loan of his PCMOS operating system for evaluation purposes.

Finally many thanks to Mr Bo Bonnevie for his much needed advice and encouragement.

# Contents

| A | bstra | act                                      | ii  |

|---|-------|------------------------------------------|-----|

| D | eclar | ation                                    | iii |

| A | ckno  | wledgements                              | iv  |

| 1 | Inti  | roduction                                | 1   |

|   | 1.1   | Ionospheric research                     | 1   |

|   | 1.2   | Meteor Research                          | 2   |

|   | 1.3   | Project requirements                     | 3   |

| 2 | Cor   | ntroller requirements                    | 5   |

|   | 2.1   | Existing equipment                       | 5   |

|   |       | 2.1.1 VIS-1                              | 5   |

|   |       | 2.1.2 VOS-1                              | 8   |

|   |       | 2.1.3 BR-9034                            | 11  |

|   | 2.2   | Upgrading the BR-9034                    | 13  |

|   | 2.3   | Rationalisation of ionosondes            | 17  |

|   | 2.4   | Man - machine interface                  | 17  |

| 3 | Des   | cription of additional hardware          | 20  |

|   | 3.1   | Digital Signal Processing board (DSP-16) | 20  |

|   | 3.2   | Serial link                              | 21  |

|   | 3.3   | Timing controller (TC)                   | 21  |

|   | 3.4   | Signal Switching (SS)                    | 28  |

|   |       | 3 4 1 Antanna switching                  | 28  |

|   |      | 3.4.2 Base-band signal and filter switching                       |  |

|---|------|-------------------------------------------------------------------|--|

|   |      | 3.4.3 Synchronisation of the external sample rate timer           |  |

|   | 3.5  | Film Recording System (FRS)                                       |  |

| 4 | Soft | vare 34                                                           |  |

|   | 4.1  | Data capture and preliminary signal processing                    |  |

|   |      | 4.1.1 Ionosonde mode                                              |  |

|   |      | 4.1.2 Meteor mode                                                 |  |

|   |      | 4.1.3 General information                                         |  |

|   | 4.2  | Operating system                                                  |  |

|   | 4.3  | Choice of high level language                                     |  |

|   |      | 4.3.1 Language options                                            |  |

|   |      | 4.3.2 Turbo C                                                     |  |

|   |      | 4.3.3 Turbo Pascal                                                |  |

|   |      | 4.3.4 TopSpeed Modula-2                                           |  |

|   |      | 4.3.5 Speed comparisons                                           |  |

|   |      | 4.3.6 Language decision                                           |  |

|   | 4.4  | User Interface                                                    |  |

|   |      | 4.4.1 Storage of system operations                                |  |

|   |      | 1.4.2 Data storage to disk                                        |  |

|   | 4.5  | Software description                                              |  |

|   |      | 4.5.1 Using units                                                 |  |

|   |      | 4.5.2 System initialisation                                       |  |

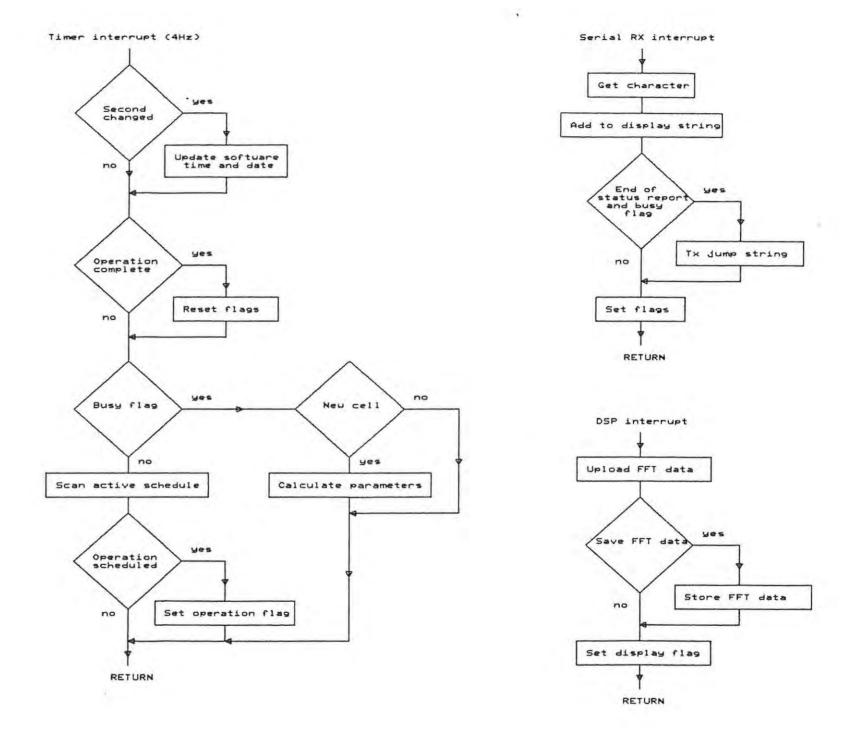

|   |      | 4.5.3 Handling interrupts                                         |  |

|   |      | 4.5.4 Programing the Timing Controller                            |  |

|   |      | 4.5.5 Controlling the sounder                                     |  |

| 5 | Sys  | em Testing 63                                                     |  |

|   | 5.1  | Phantom meteor echoes                                             |  |

|   | 5.2  | Comparison of data from the old and new meteor logging systems 65 |  |

|   | 5 3  | Performance of the RP 0034 as an ionesenda 75                     |  |

| 6  | Cor                                     | nclusion                                    | 82  |  |  |  |  |  |  |  |  |  |  |  |  |

|----|-----------------------------------------|---------------------------------------------|-----|--|--|--|--|--|--|--|--|--|--|--|--|

|    | 6.1                                     | Meeting the initial project specifications  | 82  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 6.2                                     | Future development of the system            | 83  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | 6.3                                     | The ionosonde rationalisation programme     | 84  |  |  |  |  |  |  |  |  |  |  |  |  |

| Re | efere                                   | nces                                        | 86  |  |  |  |  |  |  |  |  |  |  |  |  |

| G  | lossa                                   | ry                                          | 89  |  |  |  |  |  |  |  |  |  |  |  |  |

| A  | Advanced chirpsounding basic principles |                                             |     |  |  |  |  |  |  |  |  |  |  |  |  |

|    | A.1                                     | A cell                                      | 93  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | A.2                                     | A sounding                                  | 94  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | A.3                                     | An ionogram                                 | 95  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | A.4                                     | A stationary ionogram                       | 96  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | A.5                                     | A doppler sounding                          | 96  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | A.6                                     | Basic equations                             | 97  |  |  |  |  |  |  |  |  |  |  |  |  |

|    | A.7                                     | Windowing                                   | 98  |  |  |  |  |  |  |  |  |  |  |  |  |

| В  | Bac                                     | kground to the meteor programme             | 100 |  |  |  |  |  |  |  |  |  |  |  |  |

| В  | B.1                                     | Observation techniques                      | 101 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | B.2                                     | The Grahamstown meteor radar                | 101 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | B.3                                     | Shortcomings of the old data logging system | 103 |  |  |  |  |  |  |  |  |  |  |  |  |

| C  | Rev                                     | rision of the Fast Fourier Transform        | 104 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | C.1                                     | Discrete Fourier transform                  | 104 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | C.2                                     | Fast Fourier transform                      | 108 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | C.3                                     | Practical implications of the FFT           | 110 |  |  |  |  |  |  |  |  |  |  |  |  |

| D  | Pas                                     | cal, C & Modula-2 test programs             | 112 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | D.1                                     | Graphics routines                           | 112 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | D.2                                     | Integer computations                        | 114 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | D.3                                     | Floating point computations                 | 115 |  |  |  |  |  |  |  |  |  |  |  |  |

| E  | Mo                                      | difications to the 9034 chirpsounder        | 117 |  |  |  |  |  |  |  |  |  |  |  |  |

|    | E.1                                     | Remote selection of the T/R waveform        | 117 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | E.2  | Power on indicator                         | 118 |

|---|------|--------------------------------------------|-----|

|   | E.3  | Gain weighting of external receivers       | 118 |

| F | DSI  | P-16 Overview                              | 119 |

|   | F.1  | Hardware description                       | 119 |

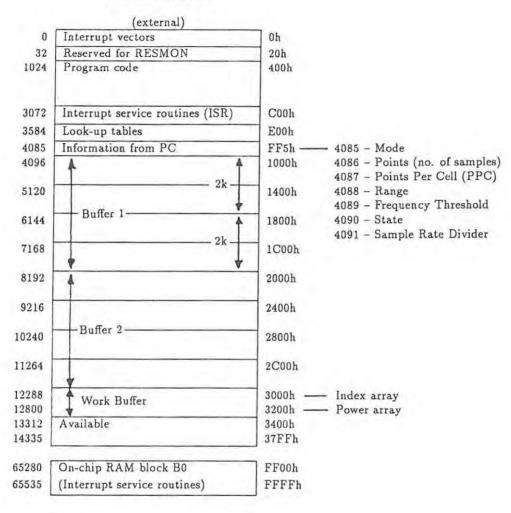

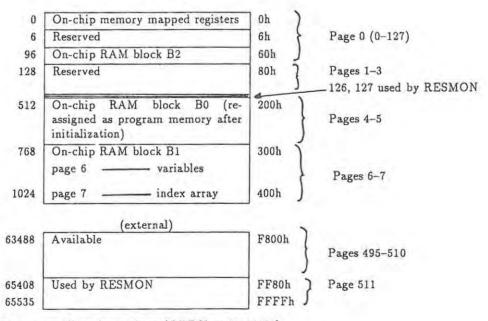

|   | F.2  | Memory map                                 | 120 |

|   | F.3  | Internal timing diagrams                   | 123 |

|   | F.4  | Analog connectors                          | 126 |

|   | F.5  | Driver software                            | 126 |

|   | F.6  | Hardware configuration                     | 128 |

|   |      | F.6.1 I/O ports                            | 128 |

|   |      | F.6.2 Memory space                         | 128 |

|   |      | F.6.3 Interrupts                           | 129 |

|   | F.7  | DSP-16 Plus                                | 130 |

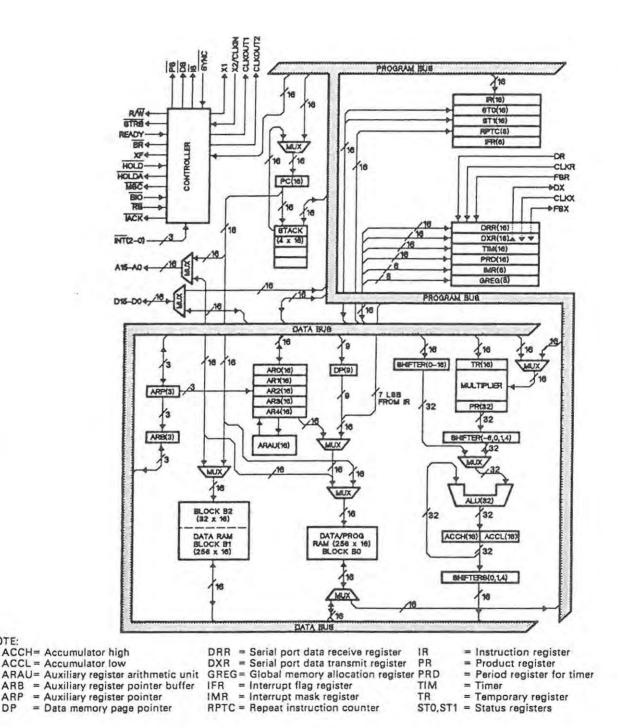

| G | TM   | S32020 overview                            | 131 |

|   | G.1  | Architecture                               | 131 |

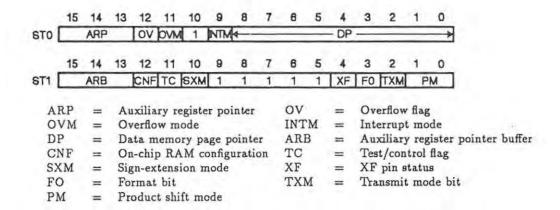

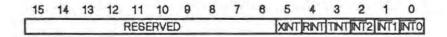

|   | G.2  | Registers, I/O ports and interrupts        | 133 |

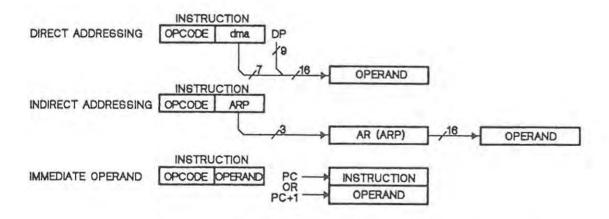

|   |      | Addressing modes                           | 135 |

|   |      | Instruction set                            | 136 |

| Н | DSF  | P-16 software flow diagrams                | 137 |

| I | PC   | memory map, I/O and interrupt vector table | 142 |

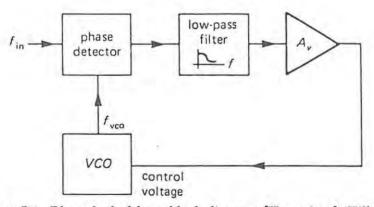

| J | Pha  | se-locked loops                            | 146 |

|   | J.1  | Comparison of types                        | 146 |

|   | J.2  |                                            | 148 |

| K | Circ | cuit descriptions                          | 149 |

|   | K.1  |                                            | 149 |

|   |      | K.1.1 Clock frequency generator            | 152 |

|   |      |                                            | 155 |

|   |      | K.1.3 Connectors                           | 157 |

|   |      | K.1.4    | Power requirements .    |  |   | • |     | • | •  | ÷  |   | ٠ |   |   | • |    | ÷ | 9 |   |   | • |    | 158 |

|---|------|----------|-------------------------|--|---|---|-----|---|----|----|---|---|---|---|---|----|---|---|---|---|---|----|-----|

|   |      | K.1.5    | Register addressing     |  | į |   | . : |   |    | ŀ  |   |   | ÷ | è |   | ÷  | ě | • | • |   |   |    | 159 |

|   | K.2  | Signal   | Switching unit (SS)     |  |   | • |     |   | •  |    |   | ٠ |   |   |   |    |   | • | • |   | • | •  | 160 |

| L | Circ | cuit dia | agrams                  |  |   |   |     |   |    |    |   |   |   |   |   |    |   |   |   |   |   |    | 163 |

| M | Par  | ts list  |                         |  |   |   |     |   |    |    |   |   |   |   |   |    |   |   |   |   |   |    | 171 |

| N | Syst | tem in   | stallation              |  |   |   |     |   |    |    |   |   |   |   |   |    |   |   |   |   |   |    | 175 |

|   | N.1  | PC ad    | dressing and interrupts |  |   |   | e i | - | 14 | œ. | , |   | ٠ | ٠ |   |    | ٠ | ٠ |   | ě |   | Ý. | 175 |

|   | N.2  | System   | n interconnections      |  |   |   |     |   |    | ī  |   | 4 |   |   |   | į. |   |   |   |   |   |    | 176 |

# List of Figures

| 2-1  | Block diagram of the VIS-1 chirp sounder [Barry Research 1972]                 | 6  |  |

|------|--------------------------------------------------------------------------------|----|--|

| 2-2  | Block diagram of the VOS-1 chirp sounder system [Evans GP 1984]                | 9  |  |

| 2-3  | Block diagram of the BR-9034 chirp sounder [BR Communications 1984] .          | 12 |  |

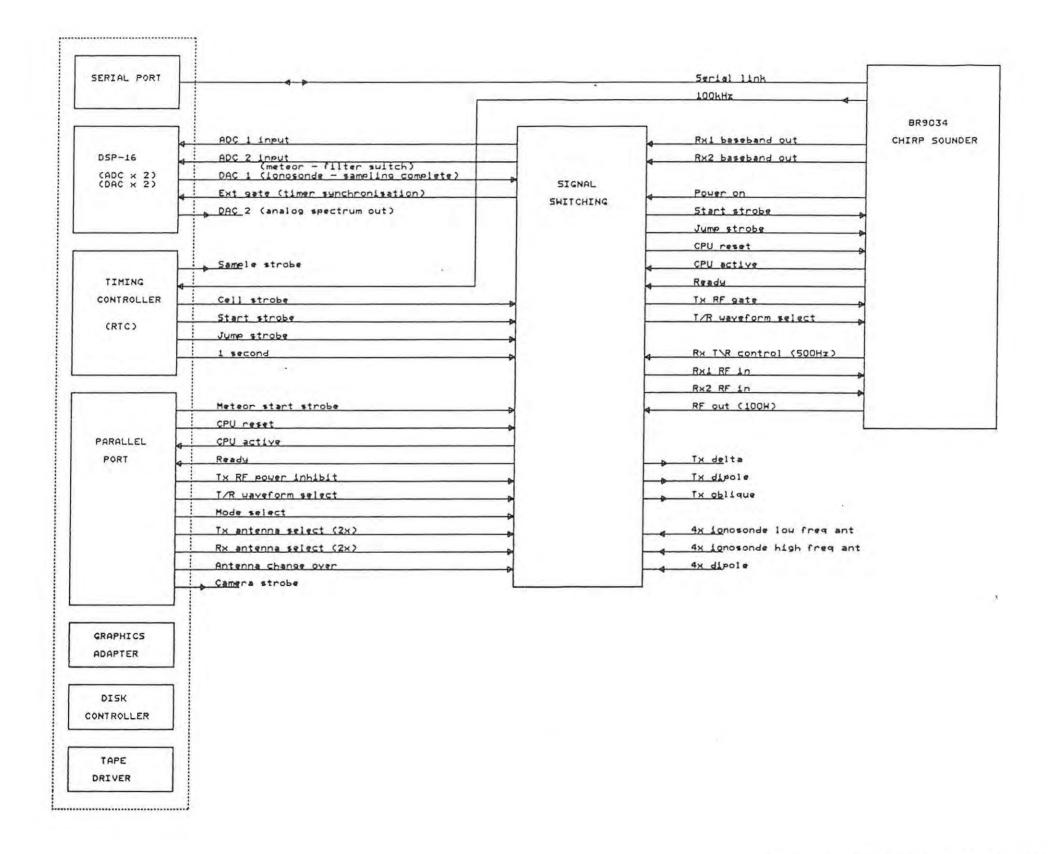

| 2-4  | Block diagram of the upgraded BR-9034 system                                   | 14 |  |

| 2-5  | Block diagram of the rationalised VOS-1 system (IA/VOS-1 interface in-         |    |  |

|      | complete)                                                                      | 15 |  |

| 2-6  | The functional blocks from Vertchirp controller that would be retained by      |    |  |

|      | the Interface Adapter                                                          | 16 |  |

| 2-7  | DOS and BIOS systems software as a control and interface layer [Borland        |    |  |

|      | (assembler) 1988]                                                              | 18 |  |

| 3-1  | Serial transmission format                                                     | 21 |  |

| 3-2  | Graphical illustration of effecting timing shifts by adjusting the 5 MHz input | 22 |  |

| 3-3  | Timing shifts effected by adjusting the basic rate                             | 22 |  |

| 3-4  | Implementation of timing shifts by adjusting the jump strobe                   | 23 |  |

| 3-5  | Graphical representation of software frequency jumps to effect 'smooth'        |    |  |

|      | timing shifts                                                                  | 24 |  |

| 3-6  | Comparison of frequency spectra for: (a) the hardware shift methods and        |    |  |

|      | (b) the software shift methods                                                 | 25 |  |

| 3-7  | Signal synchronisation using (a) timing and (b) frequency shifts               | 26 |  |

| 3-8  | Timing controller block diagram                                                | 27 |  |

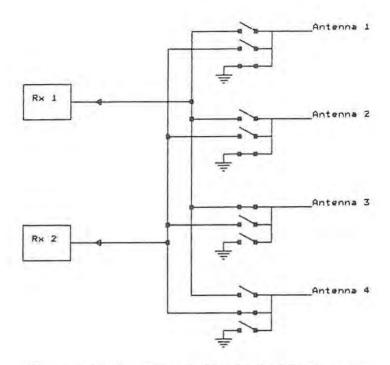

| 3-9  | RF switch                                                                      | 28 |  |

| 3-10 | Antenna switching in the VOS-1 system                                          | 29 |  |

| 3-11 | RF signal path in ionosonde mode, showing all possible antenna orienta-        |    |  |

|      | tions, and a sample 3 cell sounding structure (Mr BT Bonnevie) $\dots$         | 30 |  |

|      |                                                                                |    |  |

| 3-12 | Effective signal path in ionosonde mode                                                  | 31 |

|------|------------------------------------------------------------------------------------------|----|

| 3-13 | Effective signal path in meteor mode                                                     | 31 |

| 3-14 | Synchronisation of the sample rate timer on the DSP-16                                   | 32 |

| 4-1  | DSP-16 to PC data transfer format                                                        | 35 |

| 4-2  | Graphical representation of data storage in ionosonde mode                               | 36 |

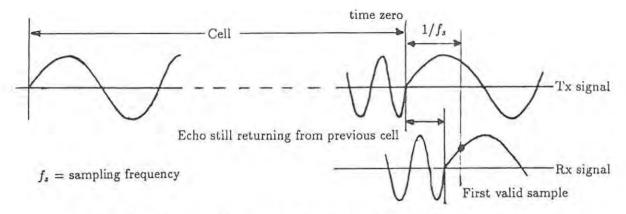

| 4-3  | Transmit and received signals at cell boundaries in 'chirp' mode                         | 37 |

| 4-4  | Sampling error                                                                           | 37 |

| 4-5  | Storage of samples in meteor mode                                                        | 38 |

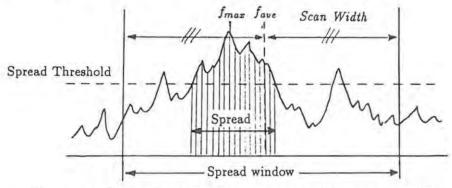

| 4-6  | Determination of frequency spread in meteor mode                                         | 39 |

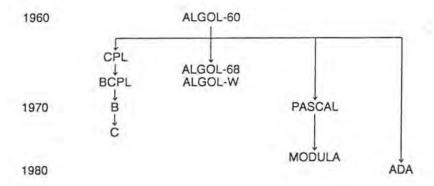

| 4-7  | Schematic genealogy for members of the Algol family of programming lan-                  |    |

|      | guages [Brown DL 1985]                                                                   | 42 |

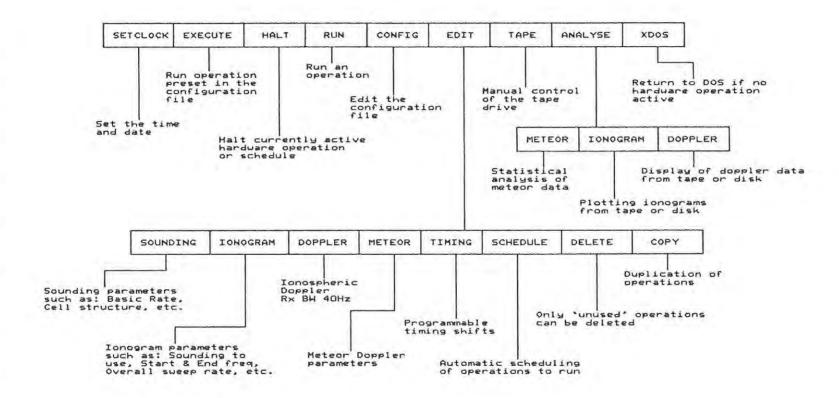

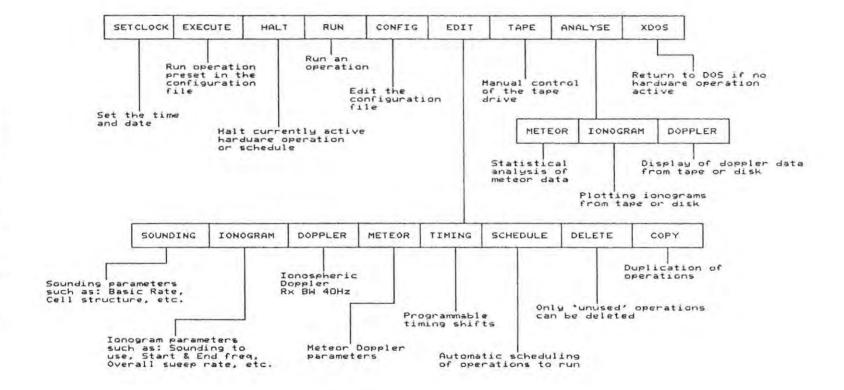

| 4-8  | The hierarchial software menu structure                                                  | 50 |

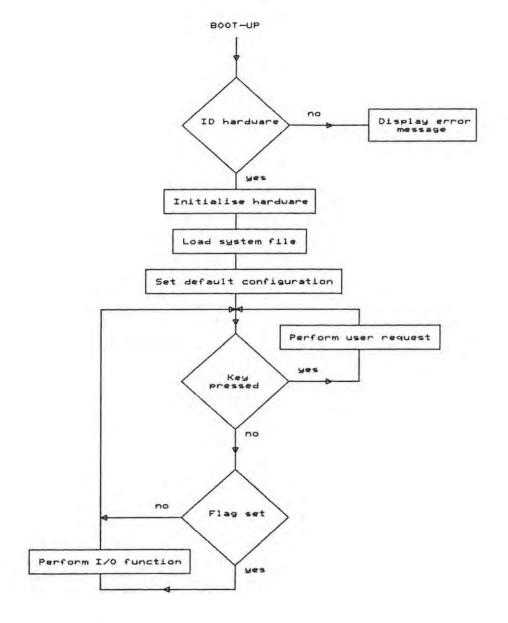

| 4-9  | Simplified flow diagram of the controller software                                       | 58 |

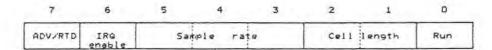

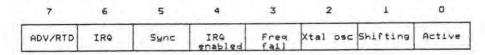

| 4-10 | TC control register                                                                      | 60 |

| 4-11 | TC status register                                                                       | 60 |

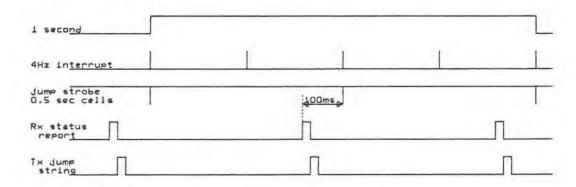

| 4-12 | Timing diagram for transmission of the jump command string to the BR-9034 $$             | 61 |

| 5-1  | DSP-16 digital filter                                                                    | 63 |

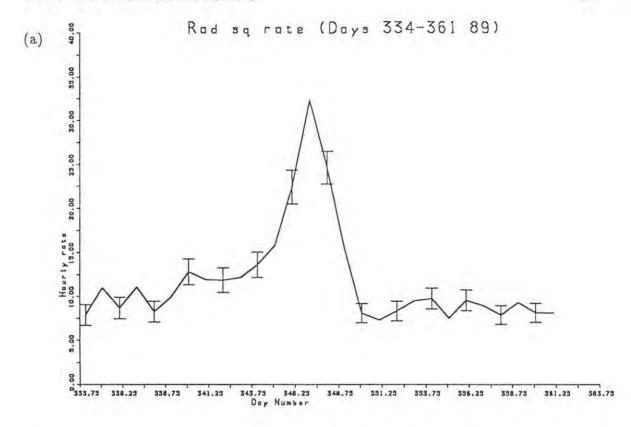

| 5-2  | Meteor rates for the $10^{\circ}$ by $10^{\circ}$ region of sky about the Geminid shower |    |

|      | radiant as recorded by (a) the old and (b) the new meteor logging systems                |    |

|      | (Prof G Poole)                                                                           | 66 |

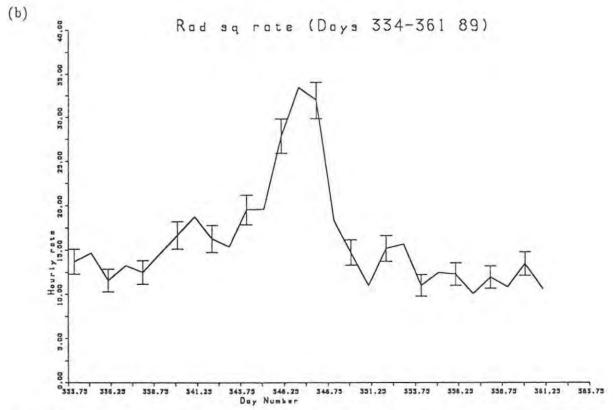

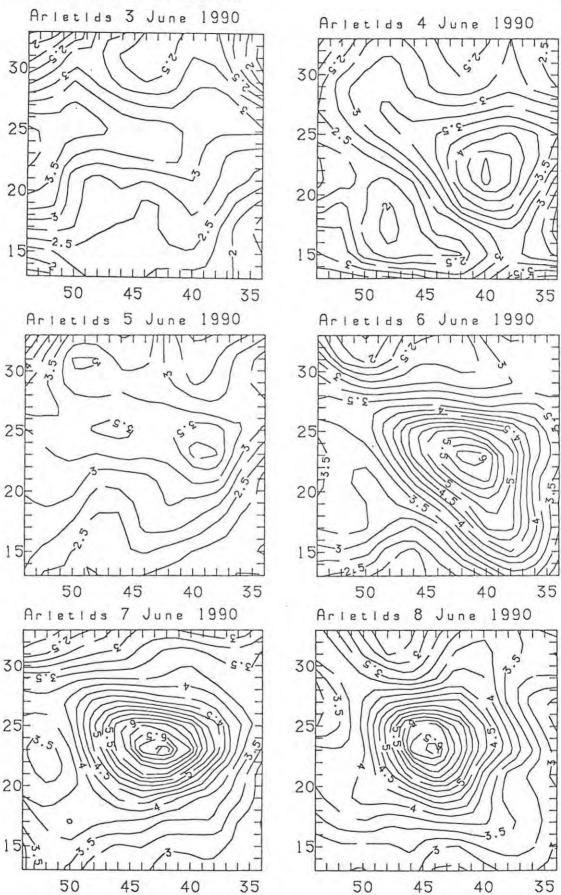

| 5-3  | Contour map of the Geminid shower radiant as given by (a) the old and                    |    |

|      | (b) the new meteor logging systems (Prof G Poole)                                        | 67 |

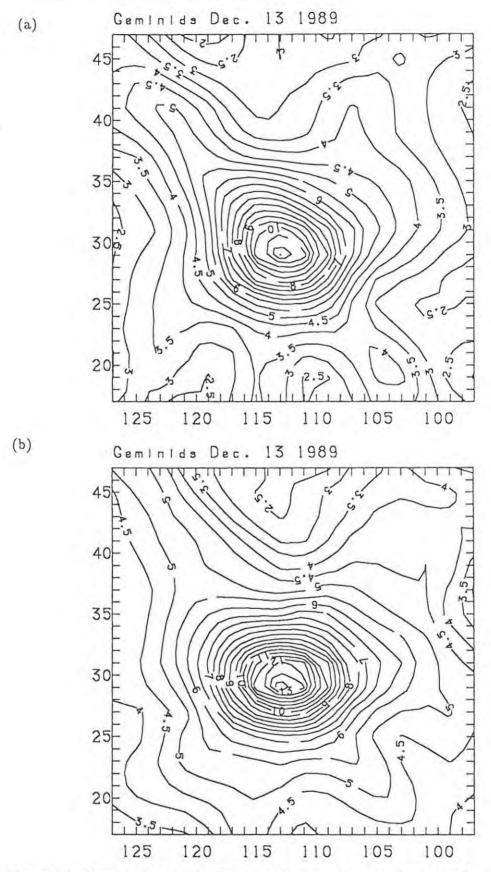

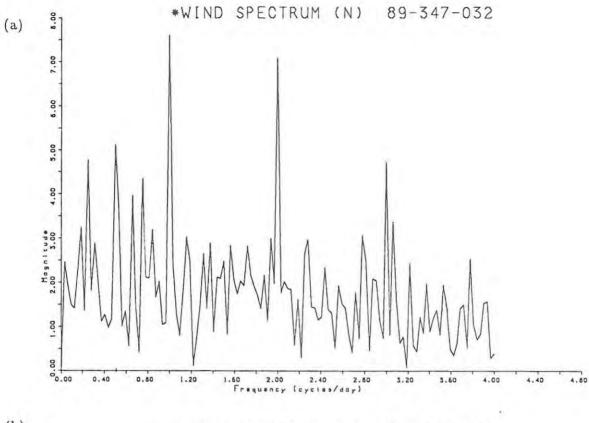

| 5-4  | Comparison of upper atmosphere wind data (E - W) recorded by (a) the                     |    |

|      | old and (b) the new meteor logging systems (Prof G Poole)                                | 68 |

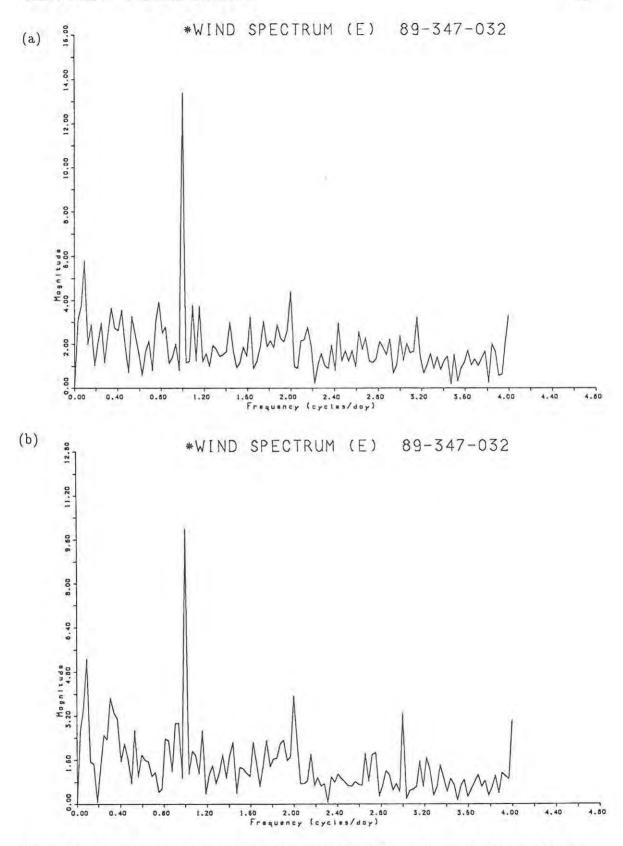

| 5-5  | Comparison of upper atmosphere wind data (N - S) recorded by (a) the                     |    |

|      | old and (b) the new meteor logging systems (Prof G Poole)                                | 69 |

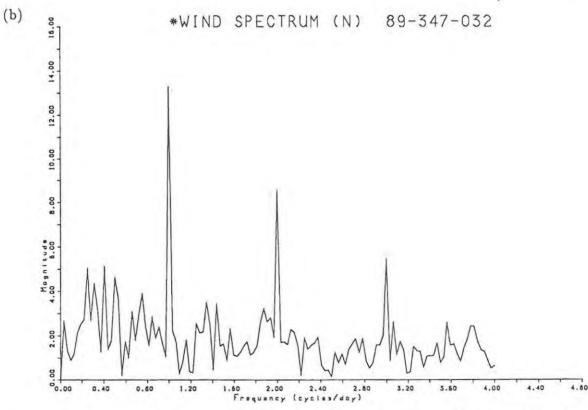

| 5-6  | Contour map of the Delta-Aquarids shower radiant as given by (a) the old                 |    |

|      | and (b) the new meteor logging systems (Prof G Poole)                                    | 70 |

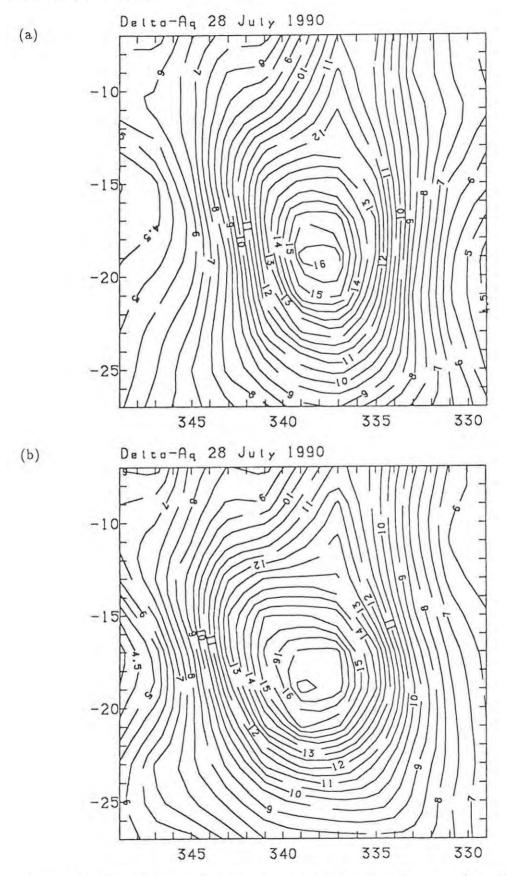

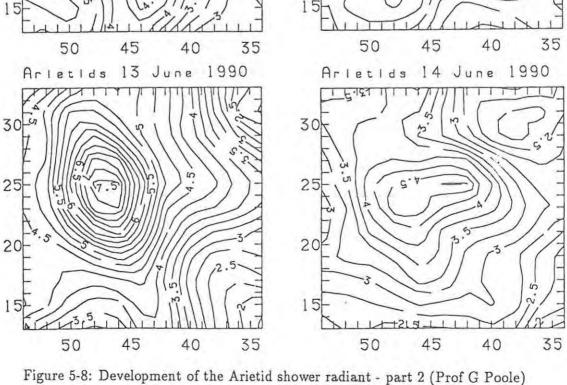

| 5-7  | Development of the Arietid shower radiant - part 1 (Prof G Poole)                        | 72 |

| 5-8  | Development of the Arietid shower radiant - part 2 (Prof G Poole)                        | 73 |

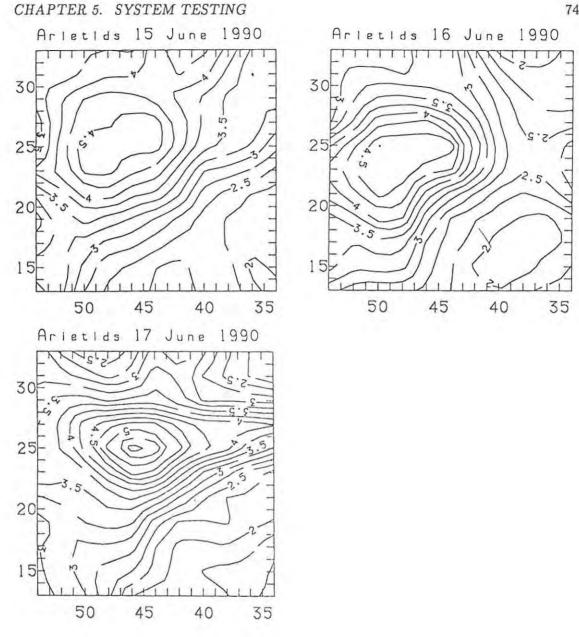

| 5-9  | Development of the Arietid shower radiant - part 3 (Prof G Poole)                        | 74 |

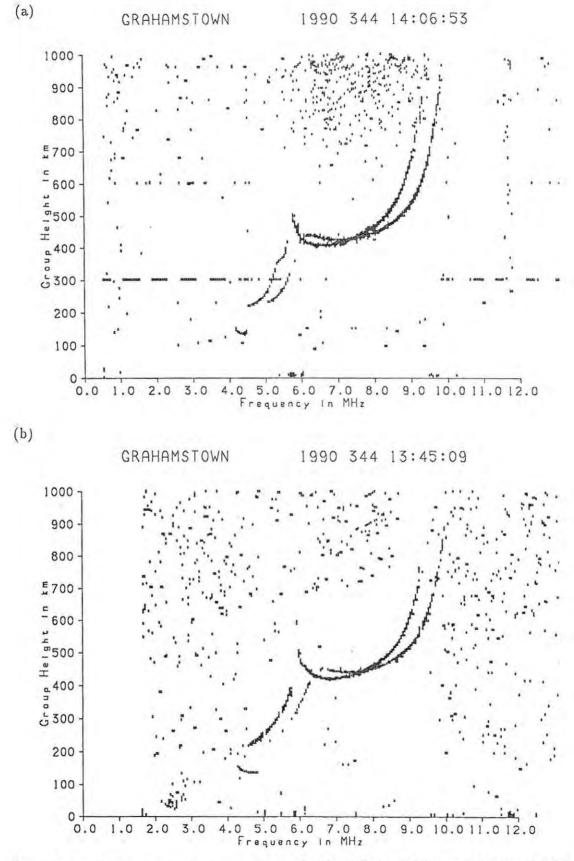

| 5-10 | Comparison of ionograms recorded by (a) the VOS-1 and (b) the BR-9034       |     |

|------|-----------------------------------------------------------------------------|-----|

|      | ionosondes (Dr A Poole)                                                     | 76  |

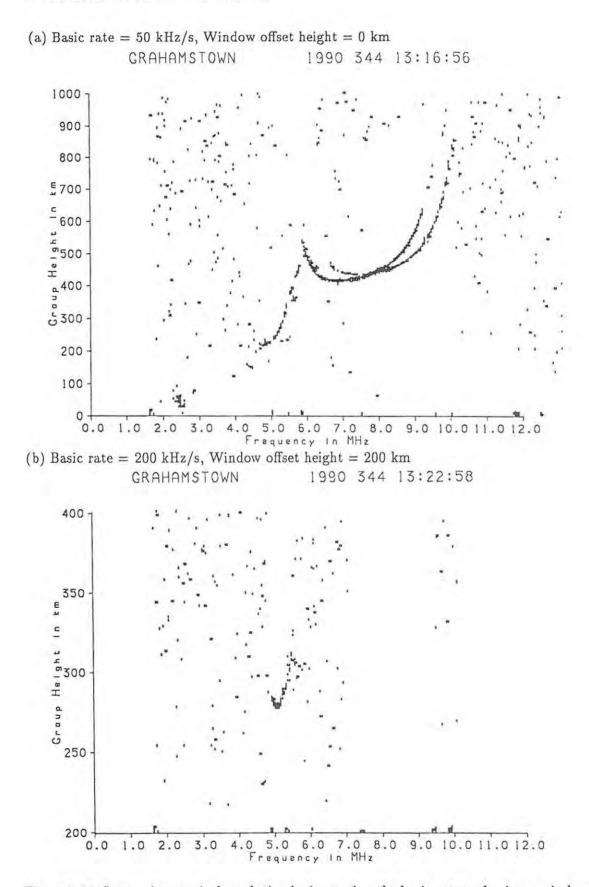

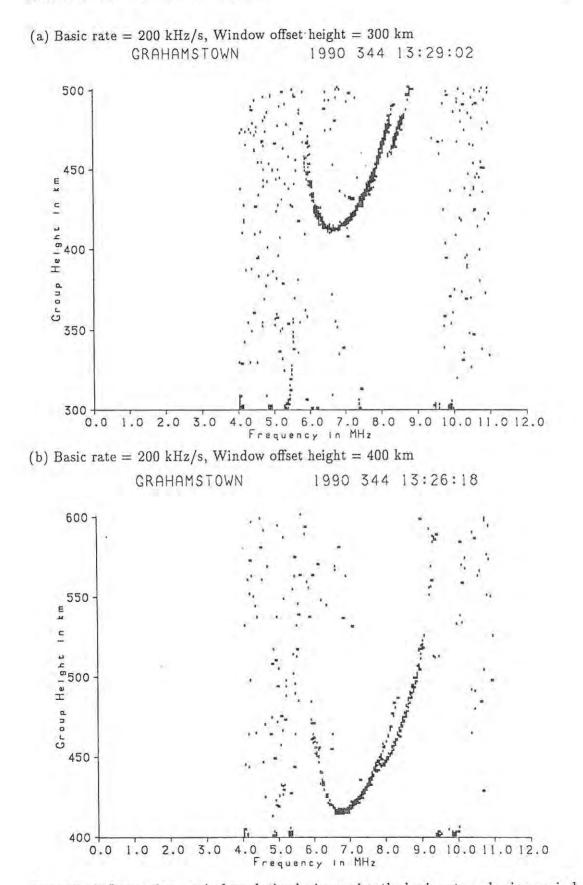

| 5-11 | Improving vertical resolution by increasing the basic rate and using a win- |     |

|      | dow offset - part 1 (Dr A Poole)                                            | 77  |

| 5-12 | Improving vertical resolution by increasing the basic rate and using a win- |     |

|      | dow offset - part 2 (Dr A Poole)                                            | 78  |

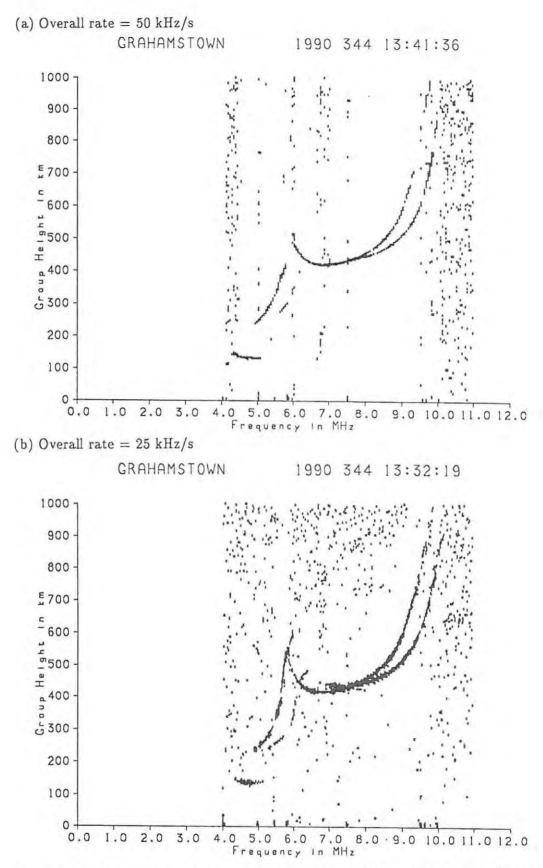

| 5-13 | Comparison of ionograms recorded using different linear overall sweep rates |     |

|      | (Dr A Poole)                                                                | 79  |

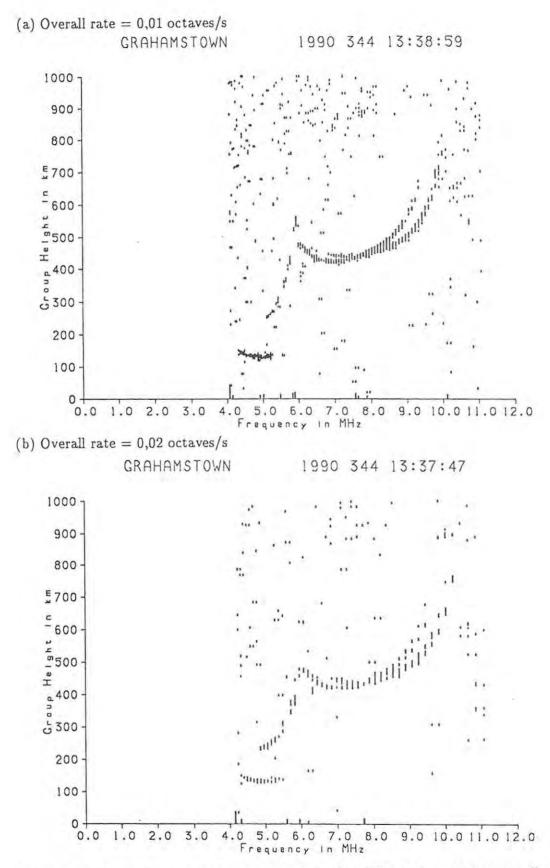

| 5-14 | Comparison of ionograms recorded using different logarithmic overall sweep  |     |

|      | rates (Dr A Poole)                                                          | 80  |

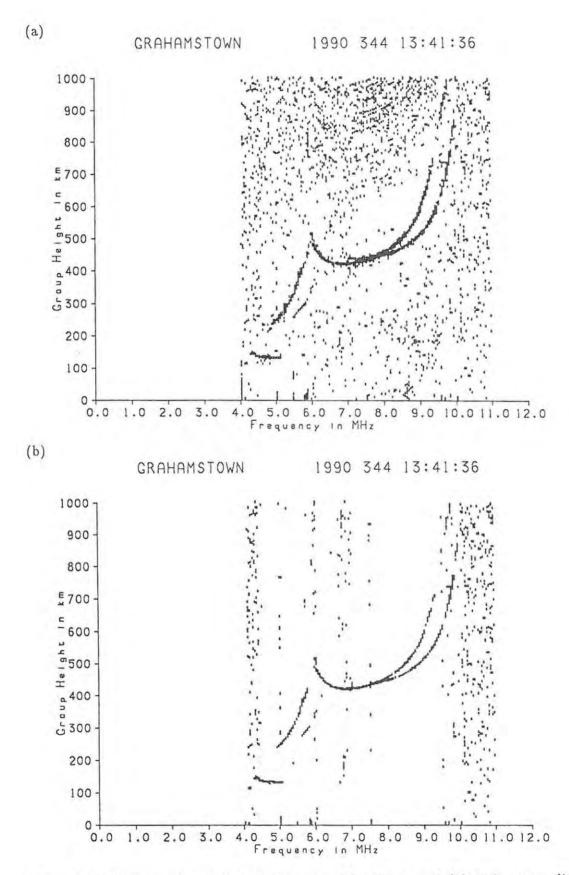

| 5-15 | Results of recording an ionogram (a) without and (b) with an amplitude      |     |

|      | threshold criterion (Dr A Poole)                                            | 81  |

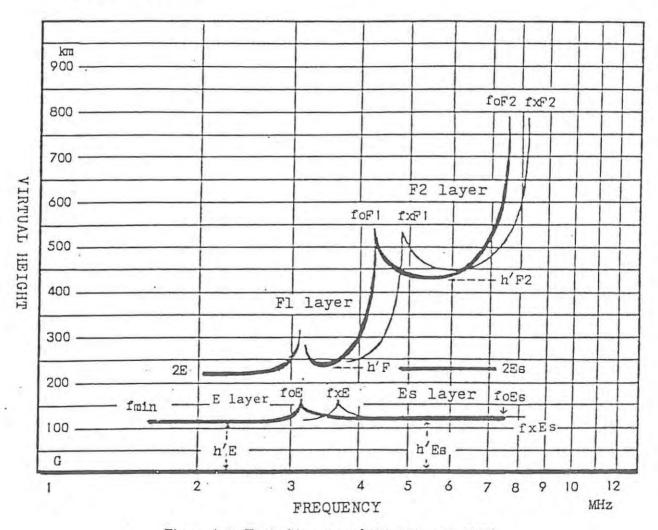

| A-1  | Typical ionogram [Wakai N et al 1978]                                       | 91  |

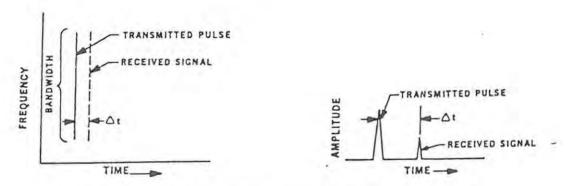

| A-2  | Pulse ionosonde [Barry Research 1972]                                       | 92  |

| A-3  | Chirp Ionosonde [Barry Research 1972]                                       | 92  |

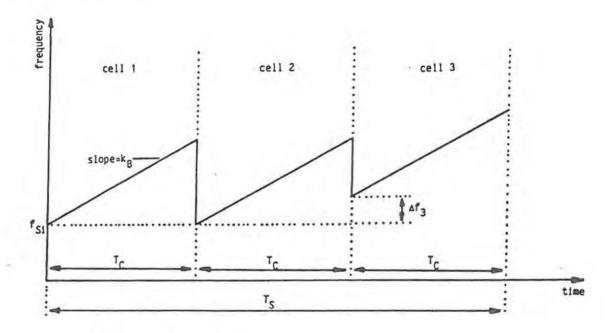

| A-4  | A cell [Evans GP 1984]                                                      | 93  |

| A-5  | A 3 cell sounding [Evans GP 1984]                                           | 94  |

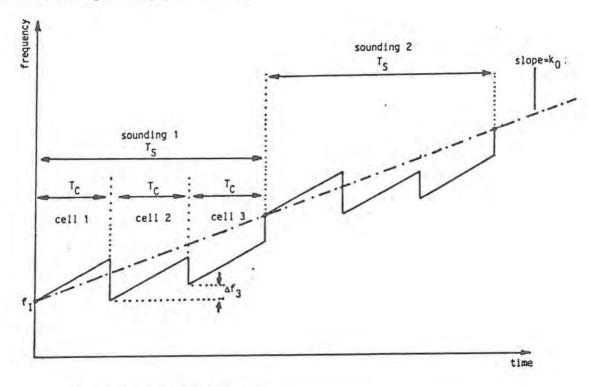

| A-6  | Digital ionogram structure [Evans GP 1984]                                  | 95  |

| A-7  | Logarithmic sweep [Evans GP 1984]                                           | 96  |

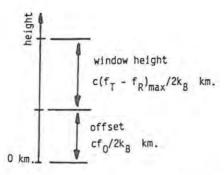

| A-8  | Graphical representation of windowing. [Evans GP 1984]                      | 98  |

| A-9  | Window offset and window height. [Evans GP 1984]                            | 99  |

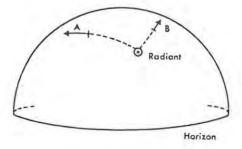

| B-1  | The meteor path as projected on the celestial sphere by two spaced ob-      |     |

|      | servers. [Hawkins GS]                                                       | 100 |

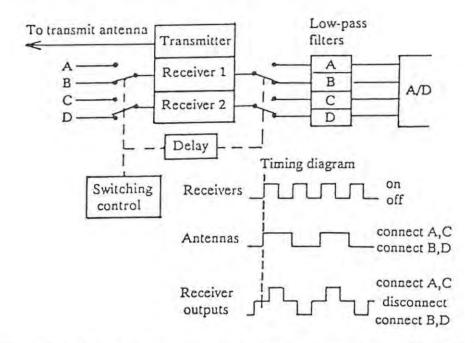

| B-2  | Schematic of meteor operation antenna switching. [Poole LMG 1988]           | 102 |

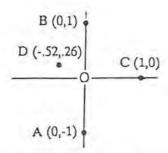

| B-3  | Receive antenna array with co-ordinates given in wavelengths relative to    |     |

|      | the origin. [Poole LMG 1988]                                                | 103 |

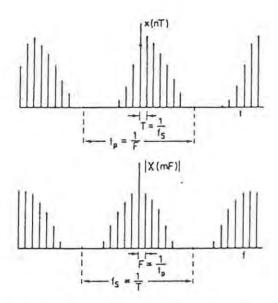

| C-1  | A periodic, discrete time function and its Fourier transform                | 105 |

| C-2  | Illustration of some of the properties of the DFT [Stanley WD 1982]         | 106 |

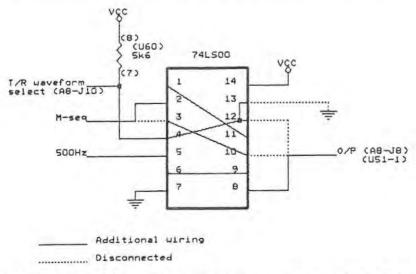

| E-1  | Wiring modifications to enable remote selection of the T/R waveform         | 117 |

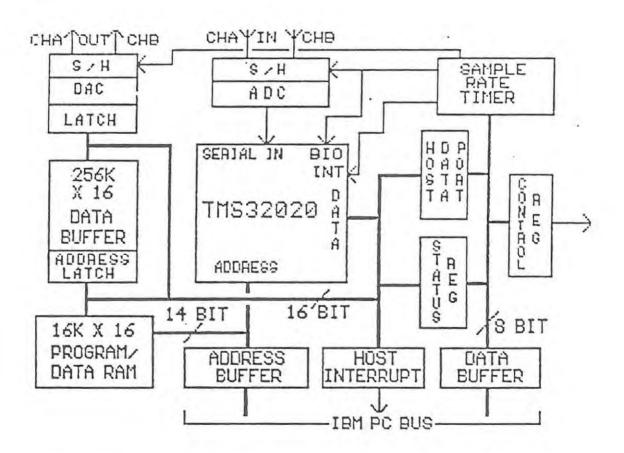

| F-1  | Block diagram of the DSP-16 signal processing board. [Ariel 1987]           | 119 |

|------|-----------------------------------------------------------------------------|-----|

| F-2  | Memory map of the DSP-16                                                    | 121 |

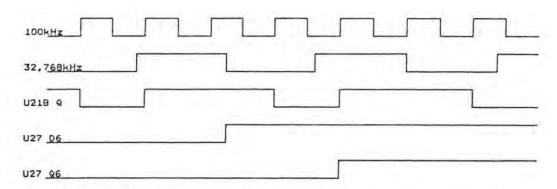

| F-3  | Derived timing diagram for DSP-16 interupts in conjunction with the ex-     |     |

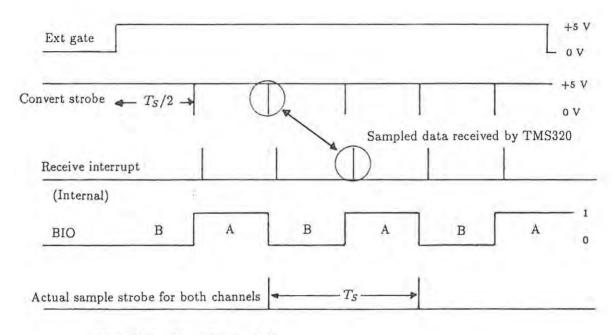

|      | ternal gate                                                                 | 123 |

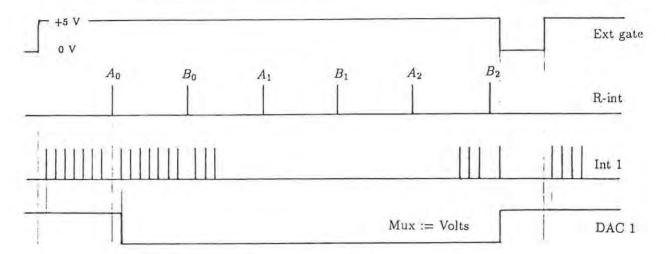

| F-4  | Synchronisation of the sample rate timer in ionosonde mode via the external |     |

|      | gate (simplified timing diagram)                                            | 124 |

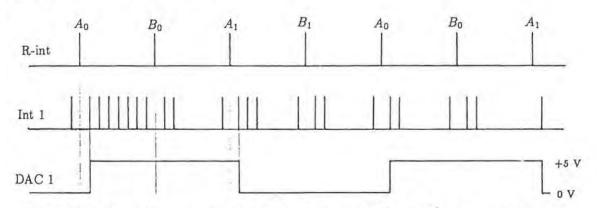

| F-5  | Dual channel multiplexing in meteor mode (simplified timing diagram)        | 124 |

| F-6  | Analog spectrum from the DSP-16's DAC 2 output to an oscilloscope $$        | 125 |

| F-7  | Analog connectors on the backplane of the DSP-16 card [Ariel 1987]          | 126 |

| F-8  | DSP-16 external gate circuitry                                              | 126 |

| F-9  | DSP-16 switch locations [Ariel 1987]                                        | 128 |

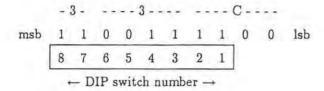

| F-10 | DSP-16 I/O address switch with with default setting of 33Ch [Ariel 1987]    | 128 |

| F-11 | DSP-16 interrupt jumper switch J3 [Ariel 1987]                              | 129 |

| G-1  | Block diagram of the TMS32020 Digital Signal Processor [TI 1986]            | 132 |

| G-2  | TMS320 status registers [TI 1986]                                           | 134 |

| G-3  | TMS320 interrupt mask register [TI 1986]                                    | 134 |

| G-4  | TMS320 addressing modes [TI 1986]                                           | 135 |

| G-5  | Summary of the TMS32020 instruction set [TI 1986]                           | 136 |

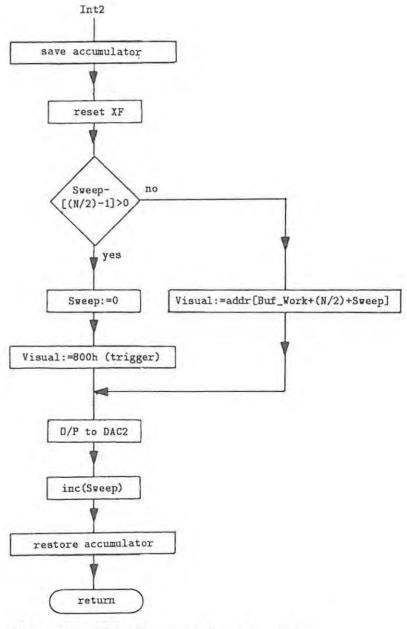

| H-1  | DSP-16 interrupt 2 service routine                                          | 137 |

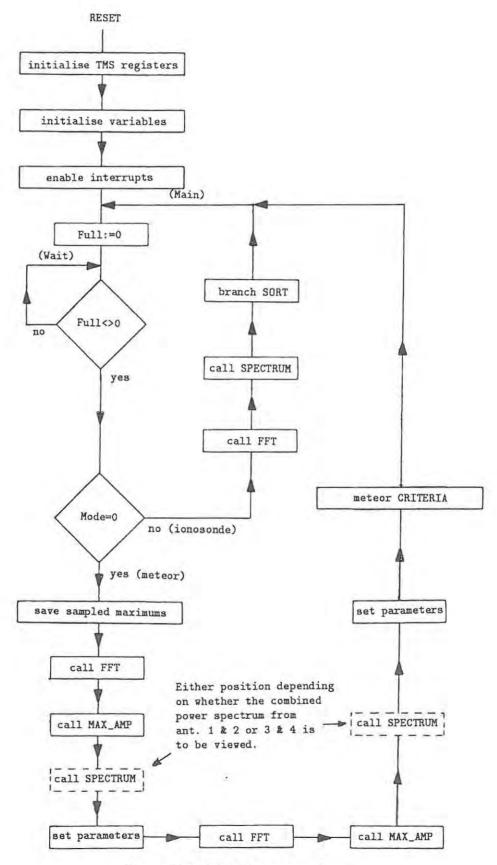

| H-2  | DSP-16 program flow                                                         | 138 |

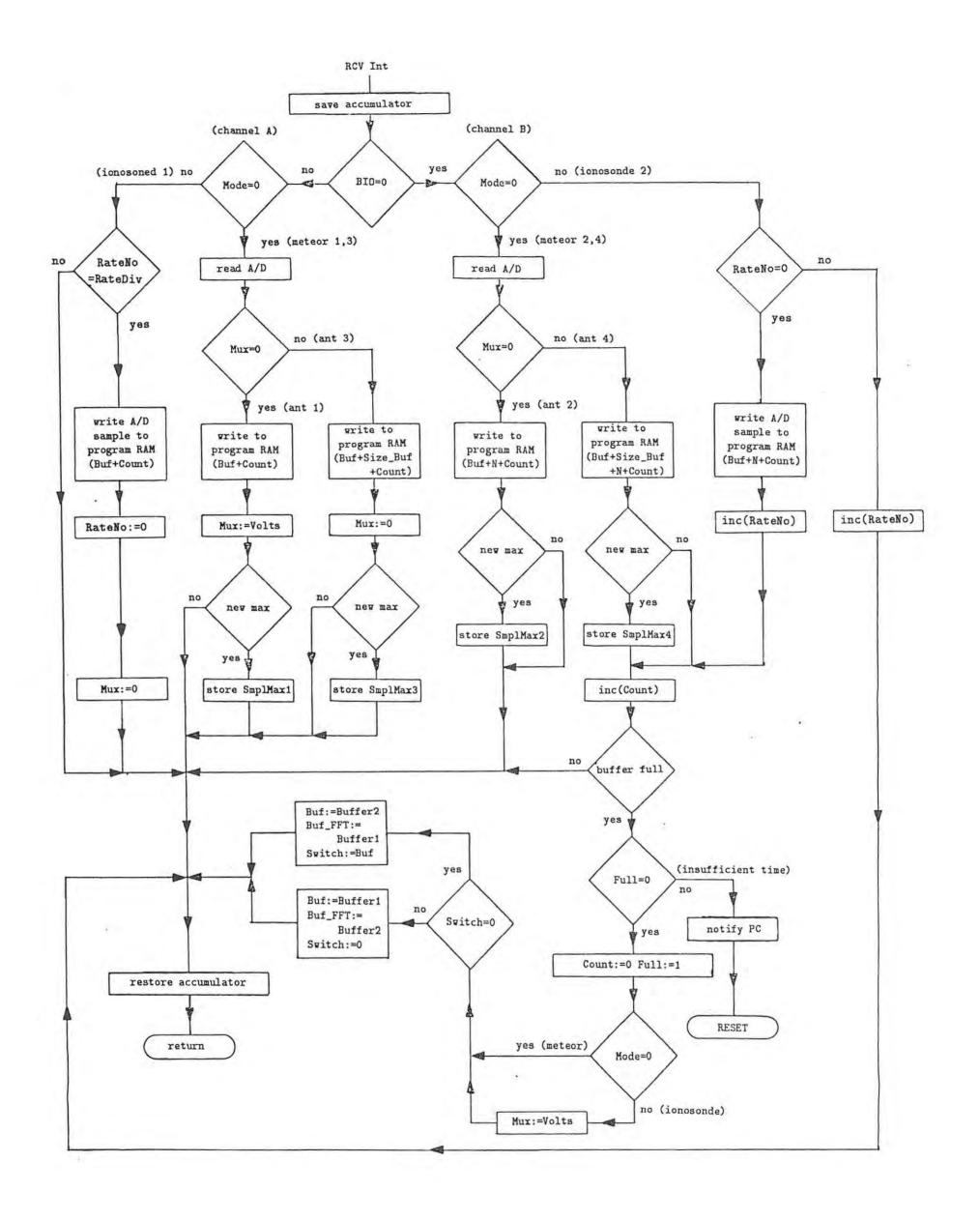

| H-3  | DSP-16 ADC interrupt service routine                                        | 139 |

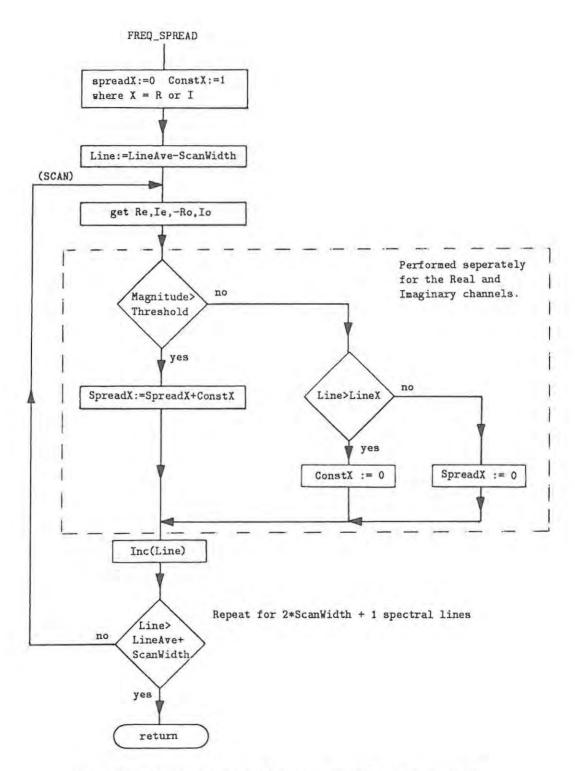

| H-4  | Determination of frequency spread in meteor mode                            | 140 |

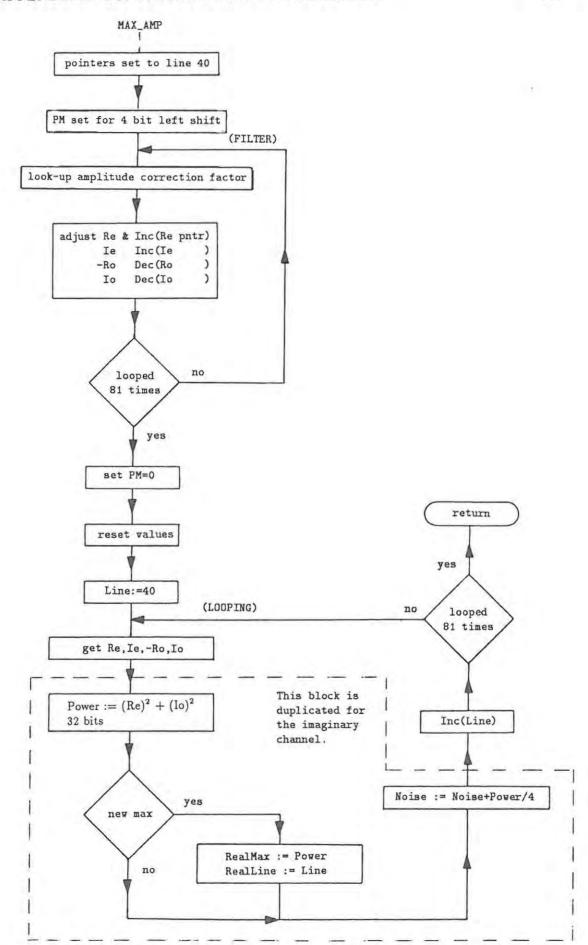

| H-5  | Digital filter and determination of the maximum frequency component         | 141 |

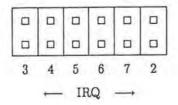

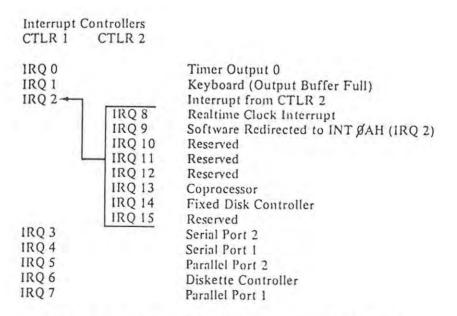

| I-1  | IBM AT interrupt request lines [IBM 1983]                                   | 142 |

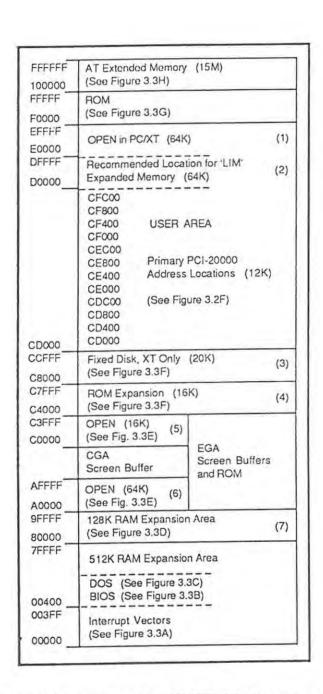

| I-2  | Memory map for PC/XT/AT [Burr-Brown 1987]                                   | 143 |

| I-3  | The interrupt vector table [Burr-Brown 1987]                                | 144 |

| I-4  | IBM AT I/O map [Burr-Brown 1987]                                            | 145 |

| I-5  | CRT screen buffers [Burr-Brown 1987]                                        | 145 |

| J-1  | Phase-locked loop block diagram [Horowitz & Hill 1984]                      | 146 |

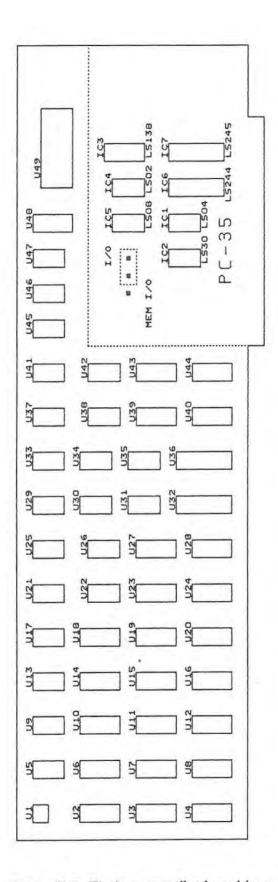

| K-1  | Detailed block diagram of the timing controller                           | 150 |

|------|---------------------------------------------------------------------------|-----|

| K-2  | Timing controller board layout                                            | 151 |

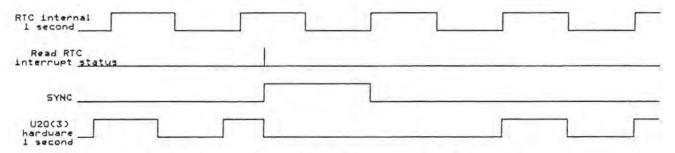

| K-3  | Synchronisation of the hardware with the RTC                              | 152 |

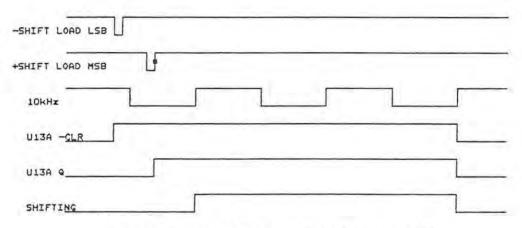

| K-4  | Timing diagram for a 0.2 ms time shift                                    | 153 |

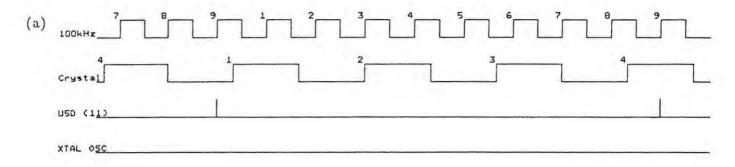

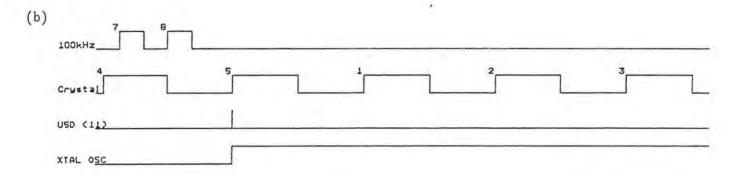

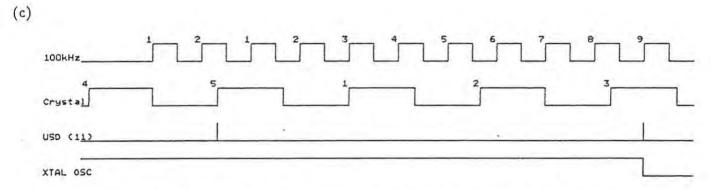

| K-5  | Timing diagrams for the input frequency detector :- (a) normal operation, |     |

|      | (b) frequency failure, (c) input re-established                           | 154 |

| K-6  | Synchronisation of strobes with the frequency standard                    | 155 |

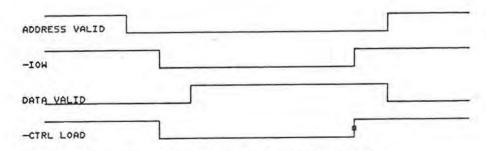

| K-7  | Writing to the control register                                           | 155 |

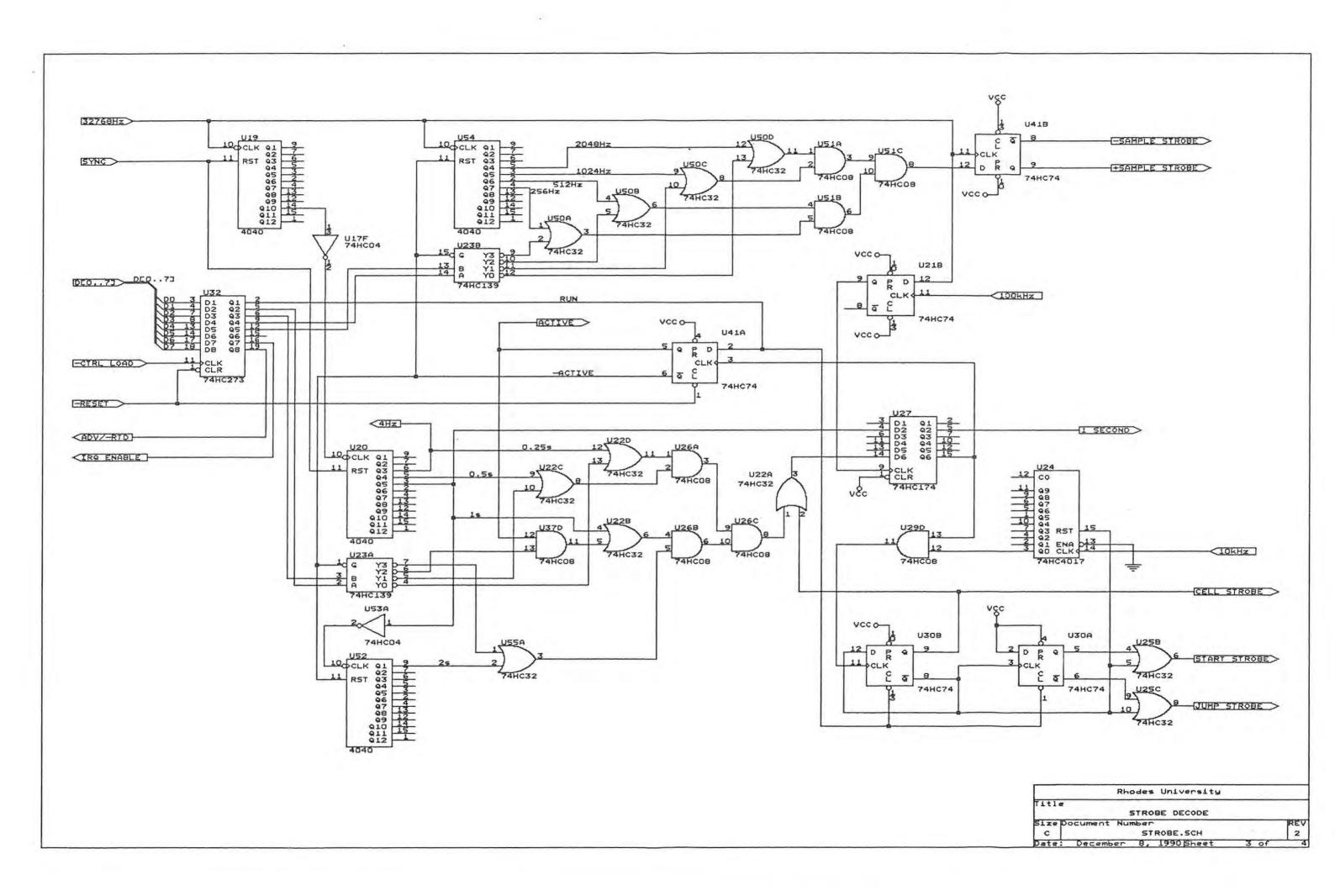

| K-8  | Timing controller strobe decoding timing diagram                          | 156 |

| K-9  | Timing controller sample strobe timing diagram                            | 156 |

| K-10 | Strobe decode timing diagram on reset                                     | 157 |

| K-11 | Block diagram of the Signal Switching unit                                | 161 |

| K-12 | RF signal path                                                            | 162 |

| L-1  | Timing controller circuit diagram                                         | 164 |

| L-2  | Clock frequency generator circuit diagram                                 | 165 |

| L-3  | Strobe decode circuit diagram                                             | 166 |

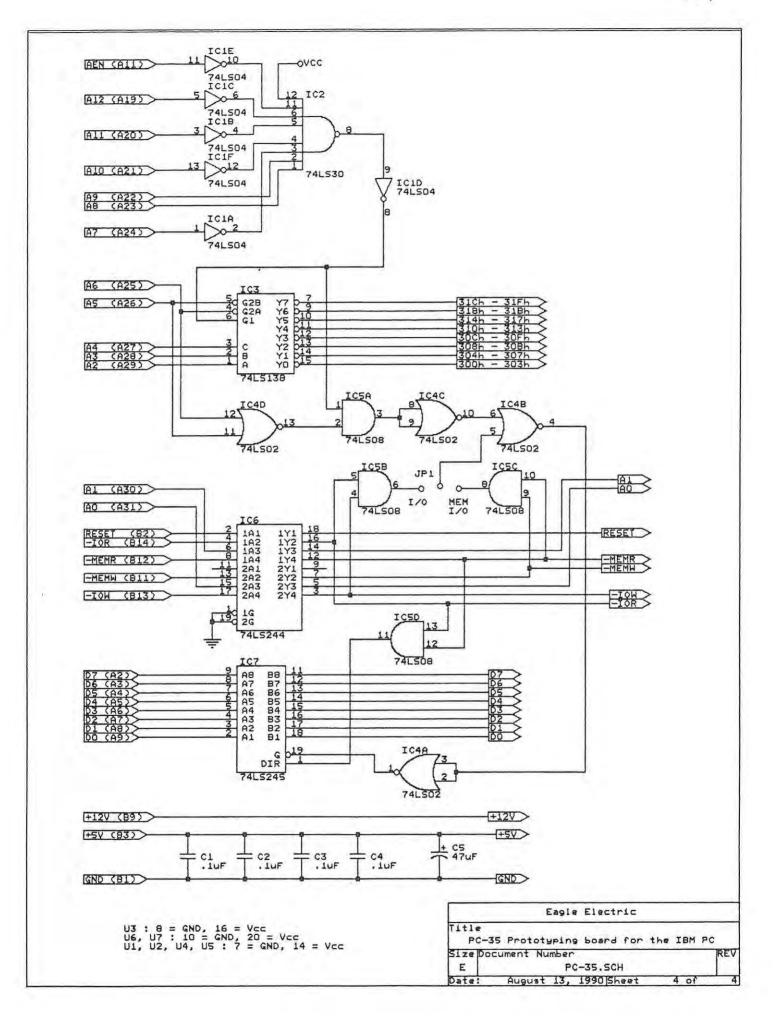

| L-4  | PC-35 circuit diagram [Eagle Electric]                                    | 167 |

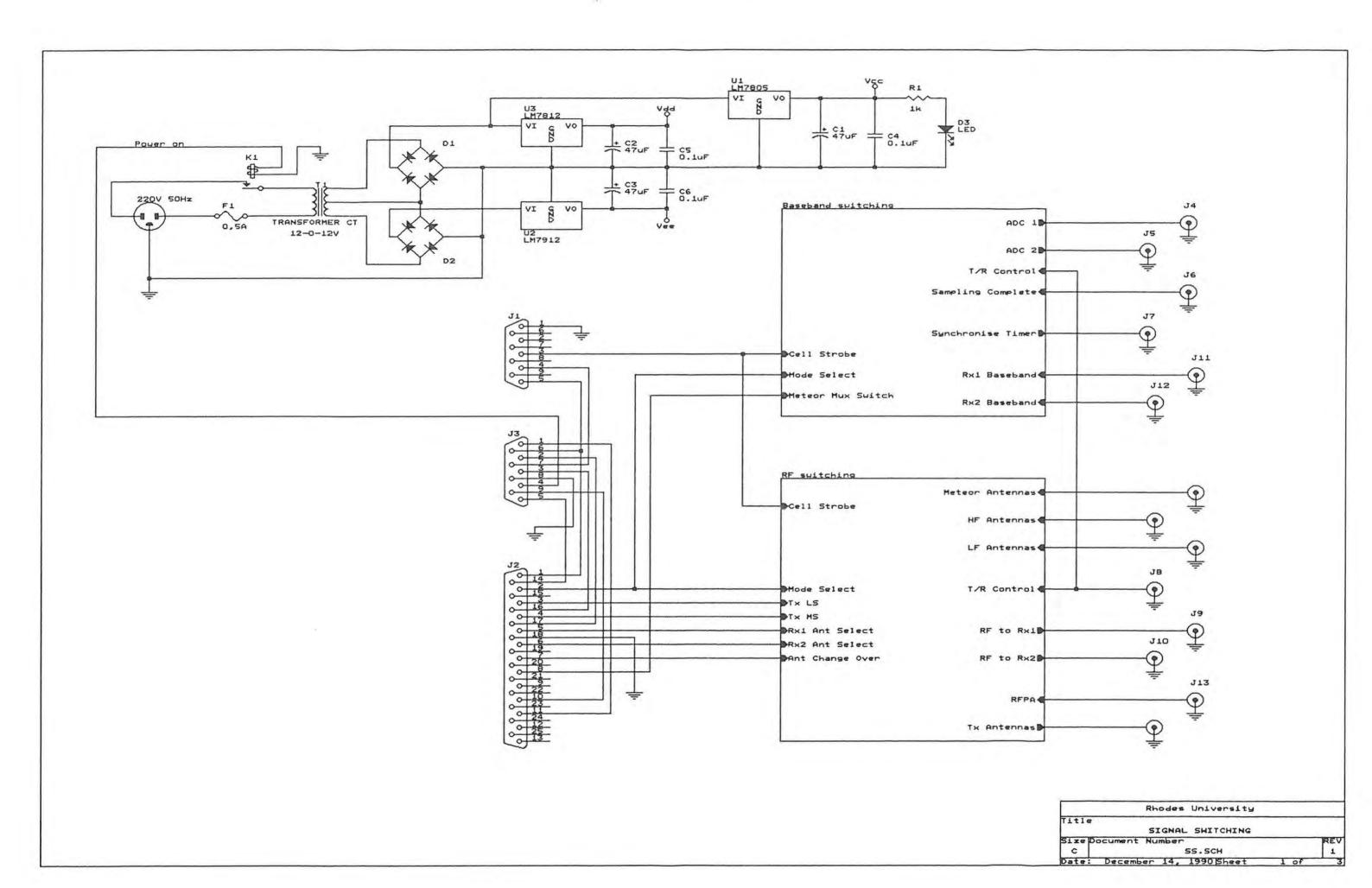

| L-5  | Signal Switching unit circuit diagram                                     | 168 |

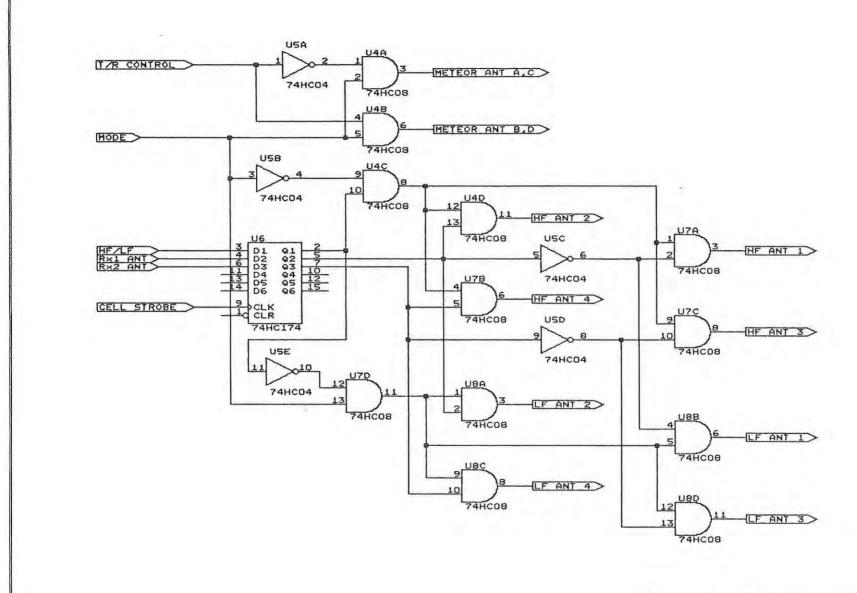

| L-6  | RF signal switching circuit diagram                                       | 169 |

| L-7  | Baseband signal switching circuit diagram                                 | 170 |

| N-1  | Wiring the RS-232 link                                                    | 176 |

| N-2  | Connecting the PC's parallel port to the Signal Switching unit            | 176 |

| N-3  | Connecting the Timing Controller to the Signal Switching unit             | 177 |

| N-4  | Connecting the BR-9034 to the Signal Switching unit                       | 177 |

| N-5  | System wiring diagram                                                     | 178 |

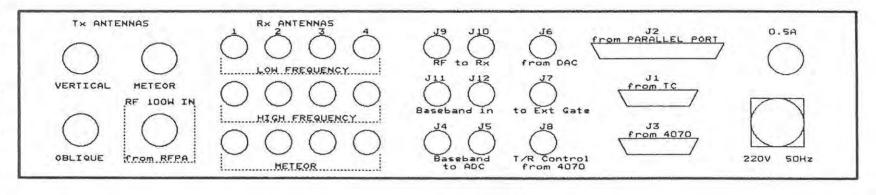

| N-6  | The Signal Switching unit rear panel                                      | 179 |

# List of Tables

| 4-1 | Time (in seconds) required to address an entire 'hi-res' graphics screen pixel |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | by pixel                                                                       | 46  |

| 4-2 | Comparison of times for integer computations (in seconds)                      | 47  |

| 4-3 | Comparison of times for floating point computations (in seconds)               | 47  |

| C-1 | Comparison of Fourier transform pairs [Stanley WD 1982]                        | 104 |

| C-2 | Even and odd properties of the DFT [Stanley WD 1982]                           | 107 |

| C-3 | Properties of $W_N$ [Stanley WD 1982]                                          | 108 |

| C-4 | Comparison of times for the DFT and FFT [Stanley WD 1982]                      | 109 |

| C-5 | Effects of FFT size and sampling frequency on frequency resolution and         |     |

|     | separation of points on the frequency spectrum                                 | 111 |

| F-1 | DSP-16 memory address switch options [Ariel 1987]                              | 129 |

| G-1 | TMS320 global memory allocation register (GREG) as used by the DSP-16          | 133 |

| G-2 | TMS320 memory mapped registers [TI 1986]                                       | 133 |

| G-3 | I/O ports of the TMS320 used by the DSP-16 [Ariel 1987]                        | 134 |

| G-4 | TMS320 Interrupts [TI 1986]                                                    | 135 |

| J-1 | Comparison of the two types of phase detectors [Horowitz & Hill 1984]          | 147 |

| K-1 | Timing controller power requirements                                           | 158 |

| K-2 | TC port address allocation                                                     | 159 |

| K-3 | Significance of TC status register bits                                        | 159 |

| K-4 | Programing the TC control register                                             | 160 |

| N-1 | Memory and port addresses required by system hardware                          | 175 |

| N-2 | Allocation of | f Interrupt | Request | (IRQ) | lines |  |  |  | 8 |  |  |  |  |  |  |  |  |  |  |  |  | 1' | 7 |  |

|-----|---------------|-------------|---------|-------|-------|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|--|----|---|--|

|-----|---------------|-------------|---------|-------|-------|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|--|----|---|--|

## Chapter 1

## Introduction

An ionosonde is a piece of equipment that is used to probe the upper atmosphere and is a type of variable frequency radar. Ionisation of the neutral gas in the ionosphere, which extends from approximately 60 km upwards, affords this region the characteristic property of refracting and reflecting radio waves propagating through it. Long distance shortwave radio communications is possible as a result of this, and the reliability of these communications was originally the main driving force behind investigation of the ionosphere.

Traditionally ionosondes measure only the virtual height of the reflecting layer at different frequencies, and from this electron density profiles can be calculated. Two broad types of ionosondes are in use. The first uses pulsed sounding techniques, and the second uses frequency modulated continuous wave (FMCW) or 'chirp' sounding. The ionosondes under consideration here fall into the second category [Poole AWV 1983, Evans GP 1984].

## 1.1 Ionospheric research

In the absence of an accurate model of the ionosphere, predictions of optimum frequencies for radio transmissions have been based on the large data-base collected mainly over the last 50 to 60 years. Modern investigation of the ionosphere requires parameters other than just the virtual height. Digital or advanced sounders have been developed over approximately the past 20 years (less for advanced chirpsounders). Parameters which can be measured with such a sounder include Doppler velocity of the reflecting layer, angle of arrival of the received signal, determination of polarisation mode, and vernier group height

from phase information. It also allows for quantitative evaluation of the amplitude, as well as, numerical rather than 'graphical' recording of the data. This requires a special type of segmented frequency sweep, as well as continual switching between pairs of spatially separated antennas. To achieve this, advanced sounders are under microprocessor control, and digital data are stored on magnetic storage media as opposed to the traditional recording of ionograms on photographic film [Evans GP 1984, Reinisch BW 1986]. The basic principles of chirpsounder operation are outlined in Appendix A, and an explanation is given of the terms cell, sounding and ionogram.

Of particular interest to the Hermann Ohlthaver Institute for Aeronomy is the ability to perform oblique digital sounding, using two chirpsounder systems some distance apart. This requires precise timing synchronization of the two systems.

Ionisation due to solar radiation and other sources may produce several distinct layers in the ionosphere which vary according to many factors such as time of day, season, solar cycle and unusual solar activity. The maximum plasma frequency of a given layer is called the layer's critical frequency and its maximum for the ionosphere is called the penetration frequency (see Figure [A-1]). Above this frequency vertically incident radio waves are not reflected, though they may be scattered [URSI 1978]. The penetration frequency for the region of the ionosphere directly above Grahamstown rarely exceeds 15 MHz.

## 1.2 Meteor Research

Ionisation of the ionosphere, though due mainly to incident solar energy, may also be caused by *meteoroids* as they 'burn up' on entry into the earth's atmosphere. The resulting phenomenon, which is marked by a visible streak of light and an ionisation trail along its path, is known as a *meteor* [McKinley DWR 1961].

Ionisation due to meteors is localised and extremely intense, though short lived, and can reflect frequencies well above the penetration frequency of the ionosphere. The chirpsounder at a suitably high fixed frequency (in this instance 27,99 MHz), provides an accurate and efficient facility for logging meteors which, for the most part, is independent of weather conditions and time of day.

Maximum heating of the meteoroid, and thus maximum ionisation, occurs at a height of approximately 100 to 110 km. See Appendix B for a background to the meteor pro-

gramme.

## 1.3 Project requirements

At the time this project was started the Hermann Ohlthaver Institute for Aeronomy had in its possession three chirp sounders, one with no digital capabilities, one advanced chirpsounder, and the newest of the three possessing potential digital capabilities but lacking external command and timing control. The latter sounder (a BR Communications 9034) was at the time being used solely for meteor research and it was decided to complete this system, to allow for both meteor and ionosonde operation, by linking it to an IBM AT compatible PC for control purposes. It is this project with which this thesis concerns itself.

The following initial requirements were of primary concern:

- Upgrading the existing meteor data logging routine to allow for validation of echoes in 'real time' and compression of the stored data.

- Connection of an IBM AT for system control allowing for specification of sweep structure, antenna selection and real time data processing, as well as automatic scheduling of operations to be run.

- Development of the controller software and user interface in a suitable 'high level' language.

- 4. Design and construction of a timing controller, allowing for accurate timing adjustment, even during the execution of system operations (particularly important for oblique ionosonde operation as allowance has to be made for synchronization of two independent sounders).

- 5. The design and construction of antenna switching circuitry.

- Design of compatible software for ultimate inclusion of the data capture system (DCS) developed by BT Bonnevie.

- 7. Inclusion of a device driver for a future film recording system (FRS).

- 8. Implementation of the above with the minimum of interference with the existing meteor and ionosonde programmes.

- 9. Finally, the overall system design was to take into account the existing hardware, structure and requirements of the older two ionosondes, so as to maintain compatibility between all three as far as possible. This would assist in the future rationalization of all three systems.

# Chapter 2

# Controller requirements

## 2.1 Existing equipment

At the time of commencement of this project the institute had in its possession three Barry Research / BR Communications 'chirp' ionosondes. The VIS-1, the eldest of the three, having been purchased around 1971.

#### 2.1.1 VIS-1

The VIS-1 (Vertical Incidence Sounder) has over the past twenty years undergone minimal modification and consists of two 19" racks containing the following units:

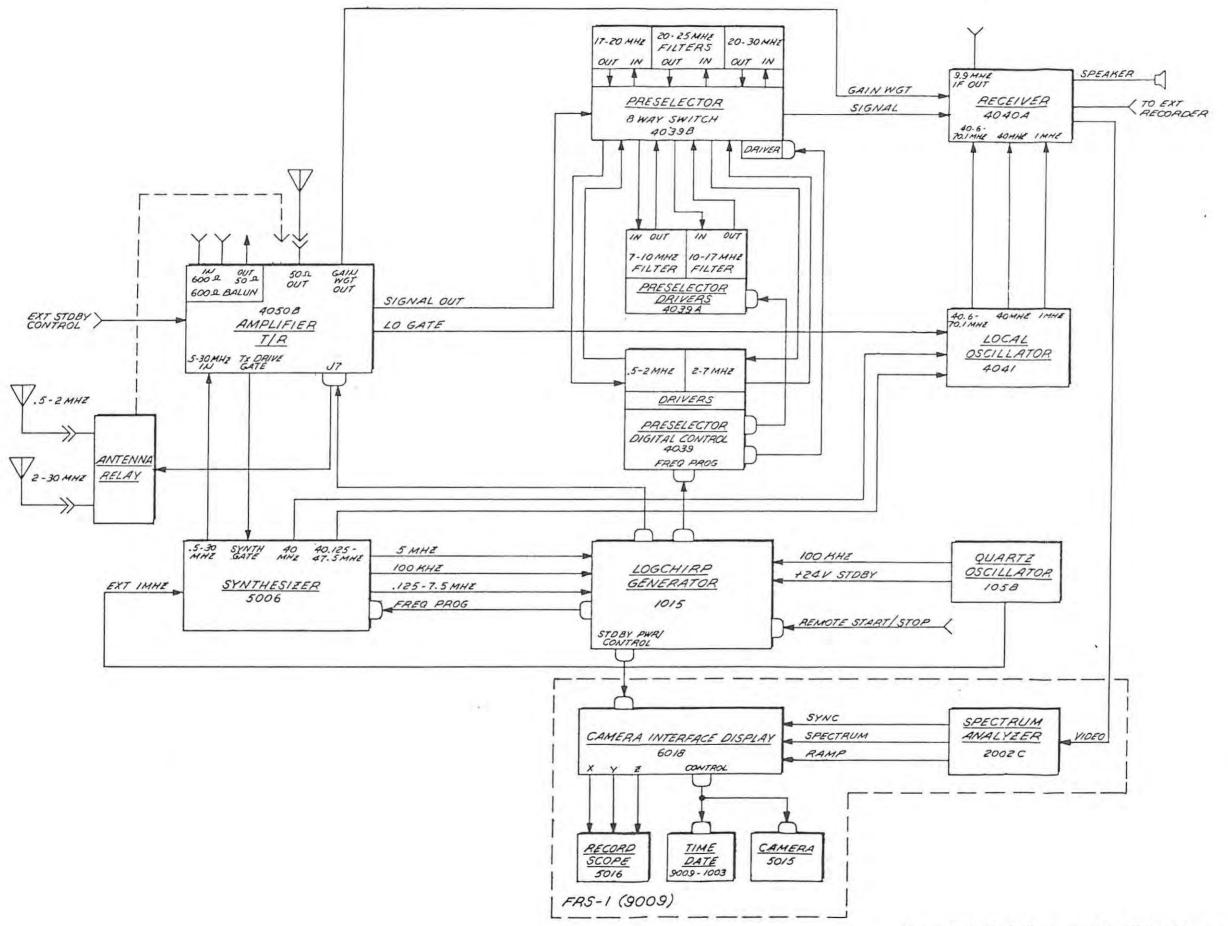

Logchirp Control (1015) – This performs the overall control functions. These include setting of the vertical and oblique sweep rates, sweep limits, sweep formats (log or linear) in vertical mode, frequency mark generation and sounding interval. Ionogram records may be initiated manually, automatically at 5 minute intervals, or remotely. All options are selectable via front panel controls.

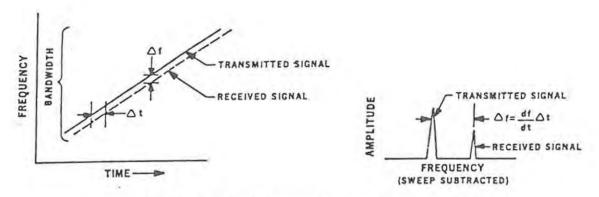

Frequency synthesizer (5006) - To produce the vertical incidence mode linear and logarithmic sweep rates the Logchirp Control unit programs the synthesizer through 1/2 sec (25 kHz) segments of a 50 kHz/s sweep. This basic rate determines the relationship between the sounder height range (1000 km) and the sounder receiver bandwidth (500 Hz). See Appendix A for a detailed discussion of chirpsounder principles and operation. The two oblique incidence sweep rates, 50 kHz/s and 100 kHz/s, are continuous linear frequency ramps.

Figure 2-1: Block diagram of the VIS-1 chirp sounder [Barry Research 1972]

- Amplifier-T/R (4050B) Signals between 0.5 and 30 MHz generated by the synthesizer are amplified to approximately 8 W (peak) by the amplifier-T/R unit in vertical or oblique transmit mode. A T/R switch and its associated timing circuitry enables the use of a single antenna for both transmitting and receiving. The T/R rate used was a 'warbled' function which partially eliminated blind height ranges but produced considerable interference with other HF equipment. This has since been replaced by an M-sequence function.

- Preselectors (4039) The received RF signal originally passed through one of three preselectors, which consisted of digitally tuned filters. As these filters were switched by mechanical relays, they proved unreliable for the limited increase in performance and have since been removed from circuit.

- Receiver (4040A) At the input of the receiver a variable gain amplifier (under the control of the amplifier-T/R) is used to gain weight the received signals in vertical incidence mode. The receiver baseband output is in the frequency range 0-500 Hz and an audio monitor is also provided.

Local oscillator (4041) - Generates all the necessary mixer frequencies.

Spectrum analyser (2002) - Produces a frequency spectrum for film records.

- Film recording system (FRS-1) This includes the Camera interface (6018), monitor and record oscilloscopes, and camera, and produces a 35 mm film record of each ionogram. Record identification was originally achieved with a mechanical time/date unit but this has been replaced by an electronic, microprocessor controlled T/D unit.

- Quartz oscillator (HP 105B) A stable, temperature controlled, battery backed up, quartz oscillator provides the necessary 1 MHz and 100 kHz signals to the system.

There is an additional unused 5 MHz output.

#### 2.1.2 VOS-1

This sounder, being only a year younger than its predecessor, had the same basic units. The only marked difference between the two was the inclusion of circuitry in the camera interface to display the time and date on the two oscilloscope screens, thus doing away with the need for a separate time/date unit.

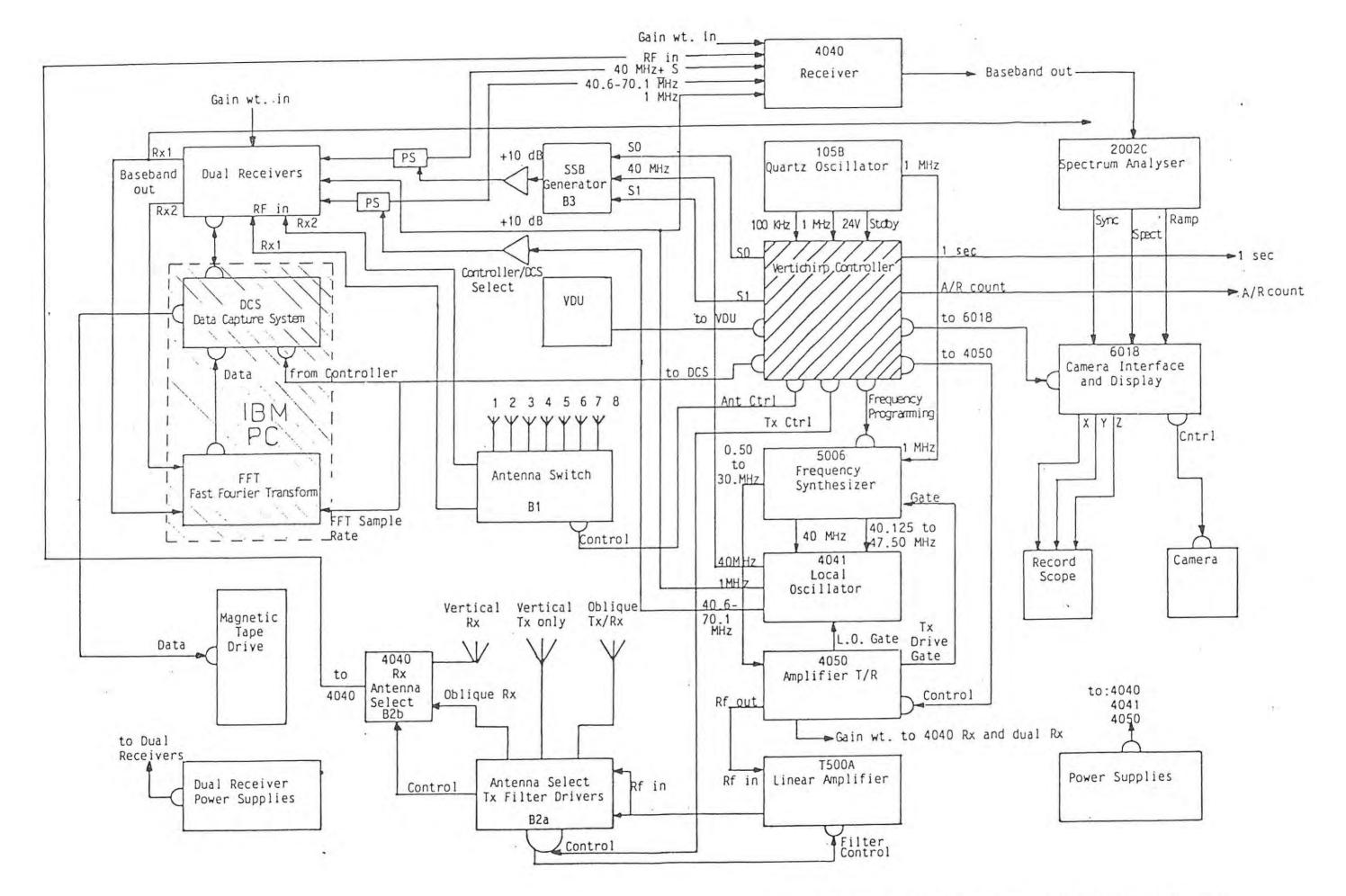

However, in the early 1980's the VOS-1 underwent extensive modifications, with the replacement of Logchirp Control by a microprocessor based controller. In addition the single receiver was replaced by two phase matched receivers, and an array of antenna switching circuitry was added. A RF power amplifier was also used with the system for the first time.

The result of these modifications was the ability to perform complex structured frequency sweeps, and the digital storage of data on magnetic tape. This was achieved through the use of a hardware FFT box [Fisher JS 1979] and a 6800 based data capture system (DCS) [Poole AWV 1983]. These latter two units have since been replaced and it suffices to say here that the principle of operation of the new DCS remains the same. The VOS-1 thus includes the following new units:

Vertichirp controller – This replaces Logchirp Control, but the two are interchangeble with only a few minor modifications. The Vertichirp controller is based on a South West Techniques Corporation 6809 microprocessor system. In addition to the processor board, two 32 k memory boards containing both EPROM and RAM, and a calculator board are used. Communication with the controller is via an RS-232 link from a dumb terminal. The majority of the software is written in the language Forth, and stored in EPROM.

All system timing circuitry and RAM are on battery backup. System functions (operations) such as *ionograms* and *timing* shifts can be defined completely from the dumb terminal, and scheduled to run at any time.

Phase matched receivers - A pair of phase matched receivers are required for phase comparisons which allows for the measurement of such parameters as angle of arrival.

Remote control of the AGC is possible with the receiver gain being reported.

RF power amplifier (T500A) - Maximum of 70W in, into 50Ω. Nominal 10 dB gain.

Figure 2-2: Block diagram of the VOS-1 chirp sounder system [Evans GP 1984]

Remote switching of filters is required as well as power blanking.

Antenna switching – The transmit RF power out can be switched to one of two antennas, generally either a vertical or oblique antenna, at the start of an ionogram.

Mechanical relays are used and 100 W can be switched.

The two receivers can be switched to any pair of a possible eight receive antennas (four LF and four HF). All unused antenna inputs are grounded. Switching is again performed via mechanical relays, and while this has the advantage that the RF signal is not attenuated, the relays have a finite life expectancy, and a fault may not be readily identifiable. Remember that the receive antennas may be required to switch every cell.

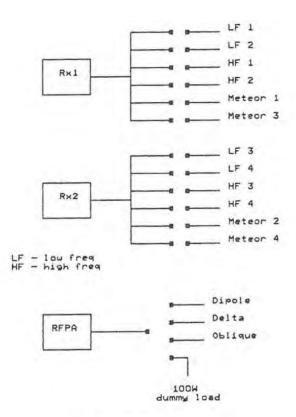

Digital signal processor – A Delanco Spry, TMS32010 based signal processing card is used to perform the real time transformations from the time to the frequency domain, as well as computation of the power spectrum. The power spectrum is then indexed in descending order of magnitude to a preselectable number of points per cell (PPC), scaled to retain all significant bits, and the processed data transferred to the PC. The card has an onboard analog to digital converter (ADC) and digital to analog converter (DAC) which are not used.

IBM PC - An IBM PC compatible is used to perform all the data capture functions. It contains two 12 bit ADC cards (PC-26), each connected to a receiver output, and these cards are strobed by the external sample strobe. After every sample one of these cards interrupts the PC, which then services the two cards and writes the samples to an appropriate area in memory. At the end of a cell the processed data are retrieved from the signal processing card and the raw data down-loaded to the card. After further processing of the transformed data, it is plotted to a graphics screen and if required, written to magnetic tape. All necessary information as regards the ionogram, such as cell length, sample rate, etc, is obtained from the Vertichirp Controller via a link through a parallel port.

Magnetic tape drive - Data can be stored to magnetic tape. The present tape format used is 1/2 inch, 9 track, PE, 1600 bpi.

#### 2.1.3 BR-9034

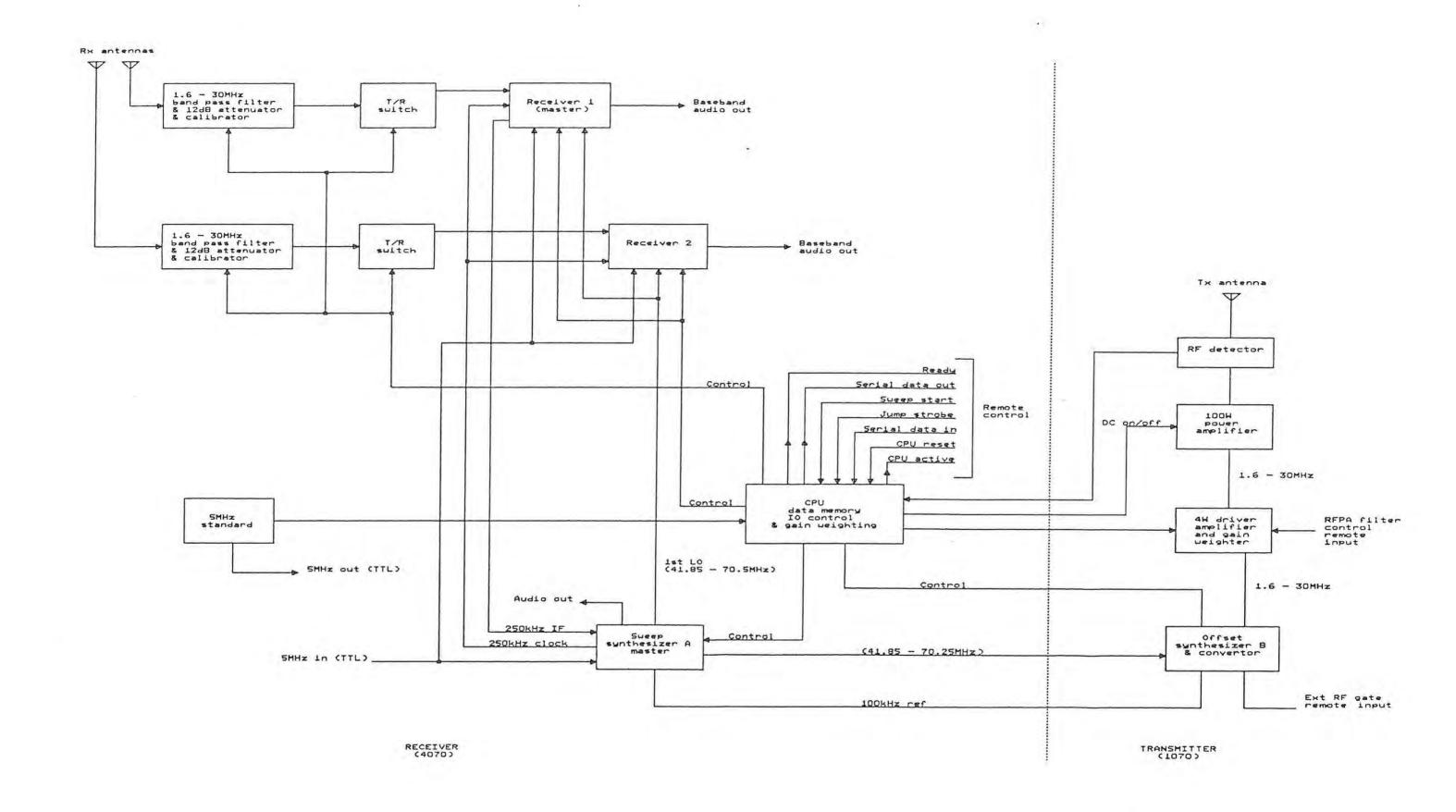

The 9034 was purchased in 1985 and consists of three units:

Transmit exciter (1070) – This emits a continuous wave signal at a fixed frequency or is swept in an upward linear ramp starting at any frequency in the range 1.6 to 30 MHz. Four basic rates are available; 25, 50, 100 and 200 kHz/s. The transmit frequency can be offset from the receive frequency by up to ±10 kHz in 1 Hz steps. The transmit exciter also contains an RF power detector to warn of RFPA failure.

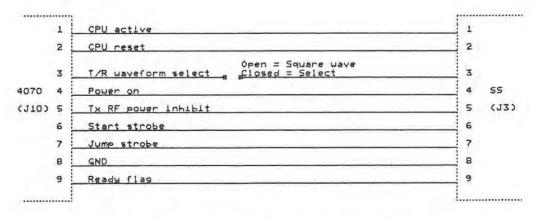

Dual channel receiver (4070) – This contains two phase matched receivers, the receive frequency synthesizer, 5 MHz oscillator, and a microprocessor for control purposes. All system operating parameters such as tuned frequency, sweep rate, bandwidth, gain, etc. are digitally controlled and remotely programmed via an RS-232C serial data port. The internal 5 MHz signal may be replaced by an external source via rear panel BNC J22. Start and jump strobing is possible, via rear panel connectors J10 to J14.

Power amplifier (5018) – Nominal 100 W is fed back to the transmit exciter where it passes through a final T/R switch ('dark' switch) before being fed to the antenna. Input to the RFPA is 0 dBm and a 10 W output is available as well. All inputs and outputs are matched to  $50\Omega$ .

Control of the 9034 system was, at the start of this project, achieved through the use of a dumb terminal for programming and a push button switch to provide the start strobe. This is adequate for continuous, fixed frequency operation as required for meteor research, but operation as an ionosonde is not at all possible.

The T/R switching function was interchangeable between a 500 Hz square wave and an M-sequence, via the reversal of a jumper on the interface board in the dual channel receiver. For meteor research the 500 Hz square wave option is used, but ionosonde operation requires the M-sequence.

Figure 2-3: Block diagram of the BR-9034 chirp sounder [BR Communications 1984]

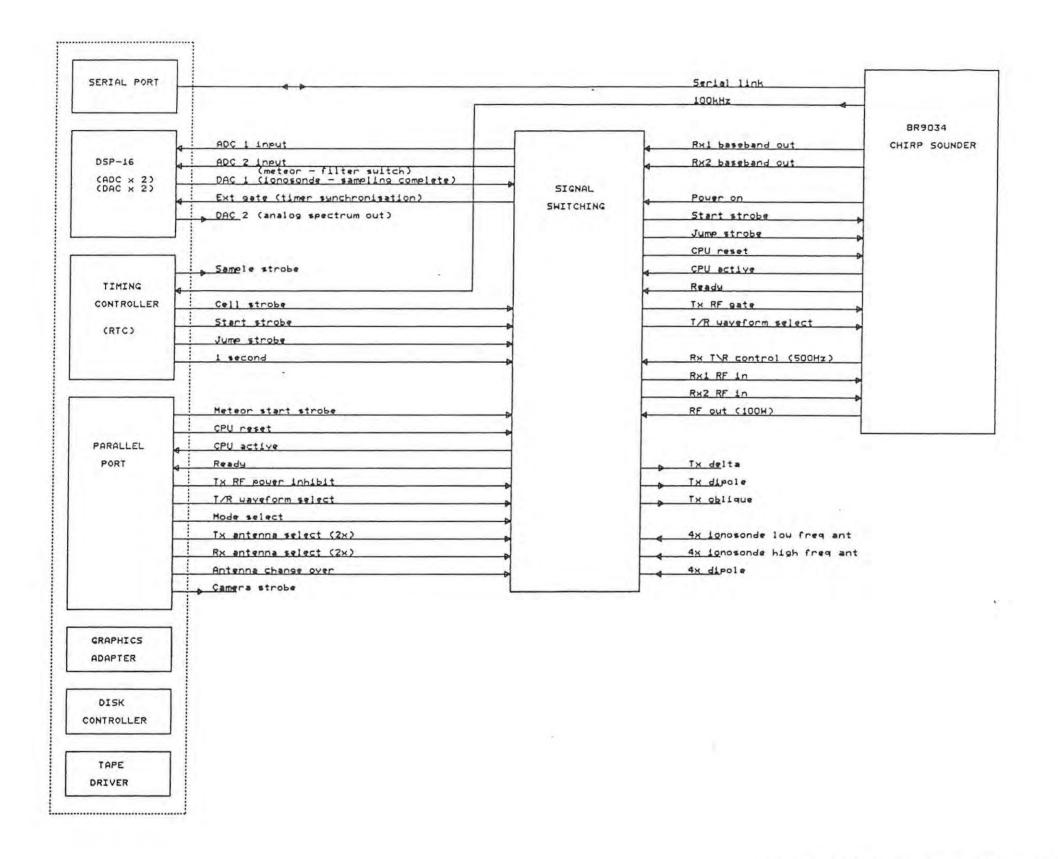

## 2.2 Upgrading the BR-9034

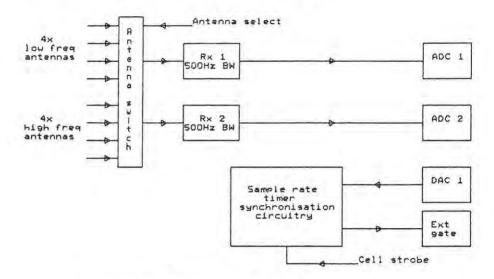

It was decided to use an IBM AT compatible to perform the necessary control functions, as well as simultaneously doubling as the data capture system. This imposed certain speed (time) requirements on the system which initially the author was unsure could be met.

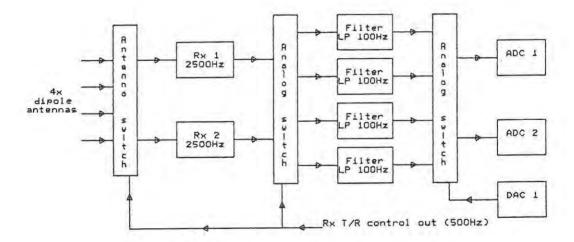

An Ariel DSP-16 digital signal processing card is used to perform the 'front end' data capture. It contains two analog to digital converters and the sampled data is transformed to the frequency domain. After some additional processing the resultant data are uploaded to the host computer for display and storage.

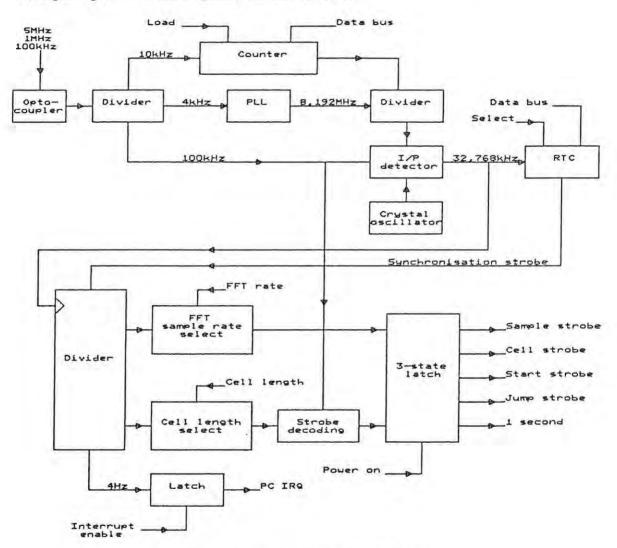

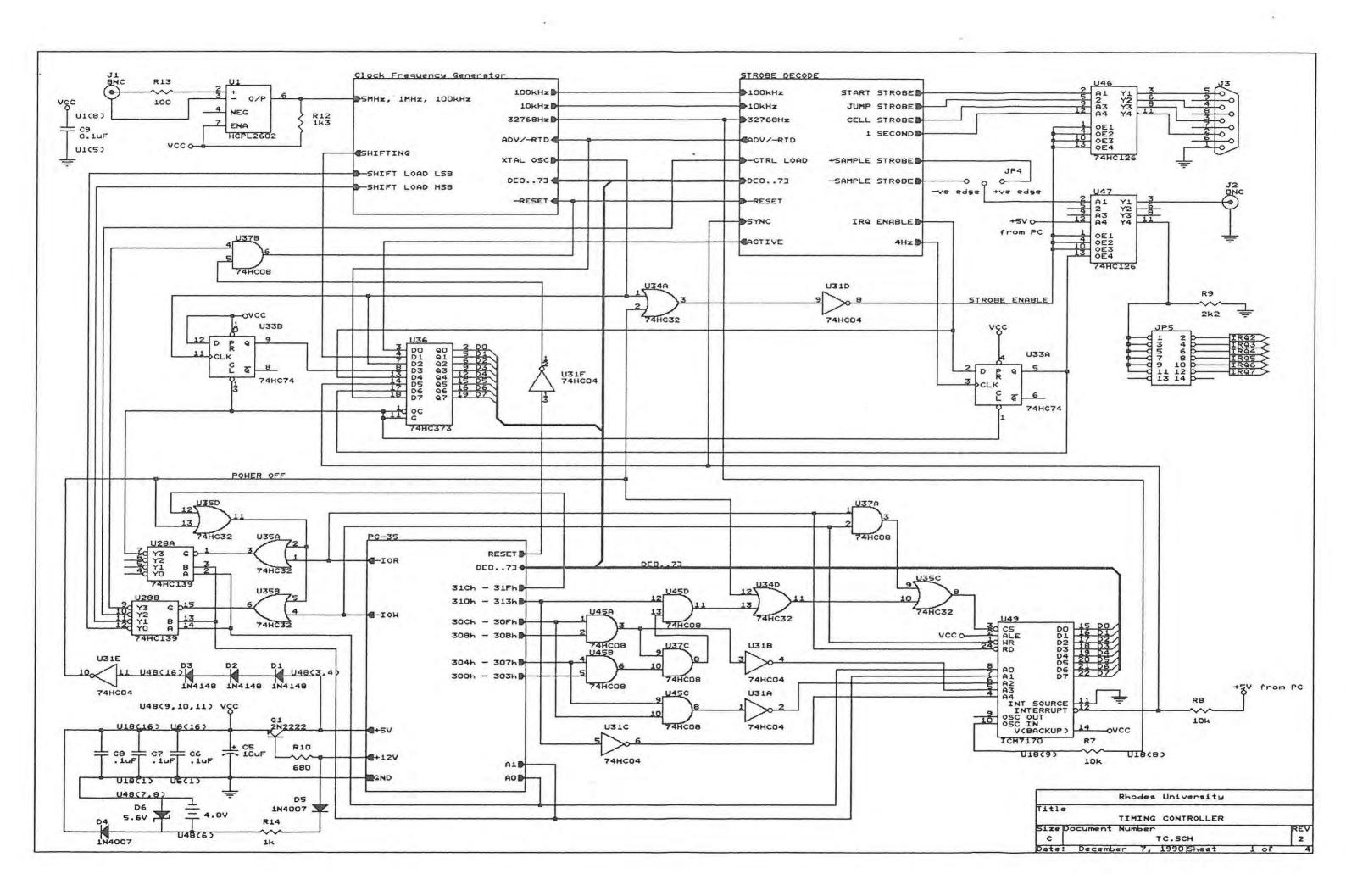

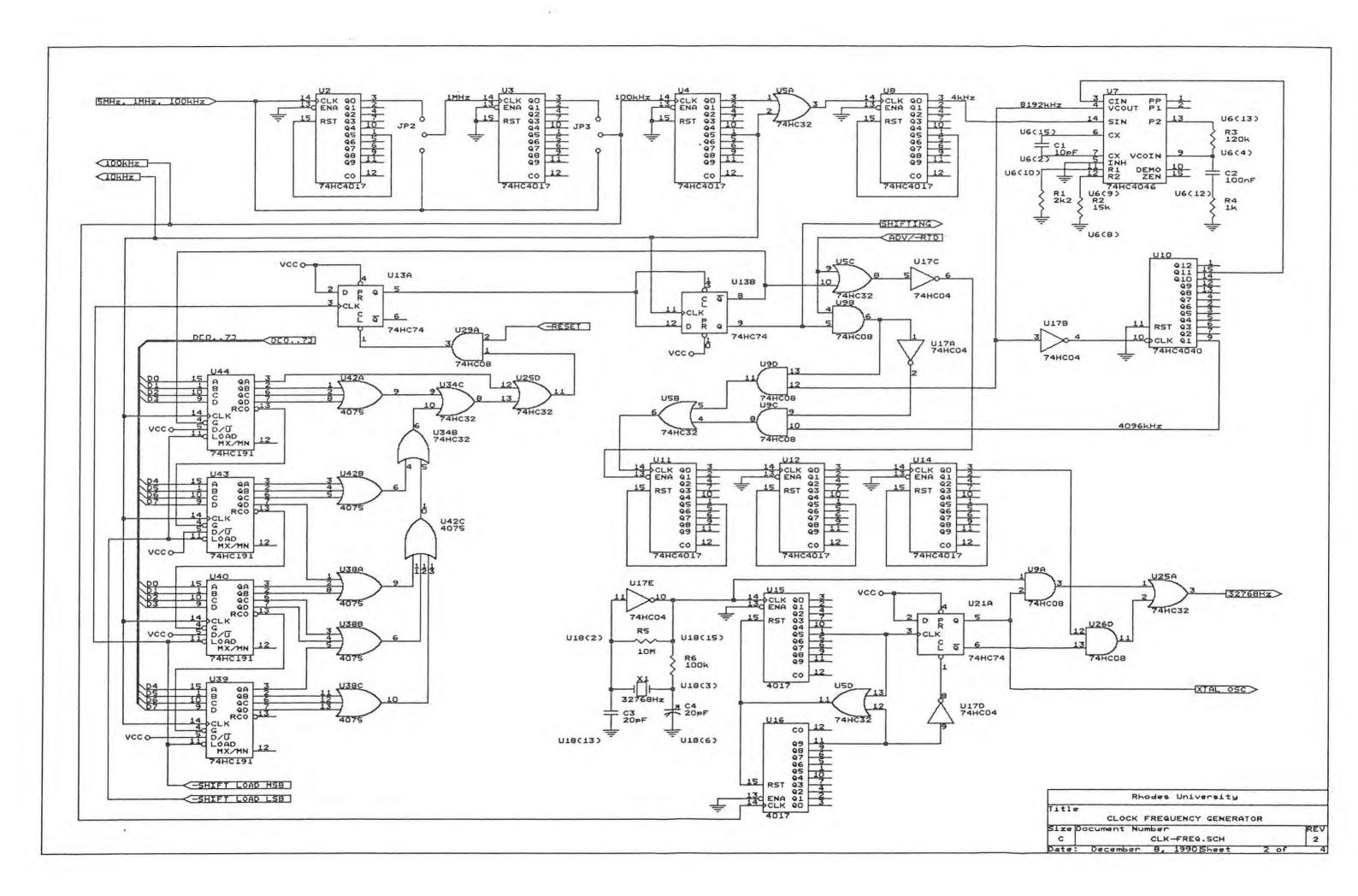

The timing controller (TC) provides all timing and strobe inputs to the ionosonde. It was decided to develop this as a plug in card for the IBM PC<sup>1</sup> so that accurate timing control of the PC could be achieved as well. This also allows rapid data transfer to and from the card. The TC requires battery backup so as not to lose system timing during power failures. In addition the TC has to allow for system timing to be advanced and retarded by small amounts, even while the sounder is sweeping.

It was decided to use a Real Time Clock chip (RTC) to provide time and date information to the PC. The reason the PC's RTC was not used is simply the necessity for the clock to remain in phase with the system frequency standard. The use of a RTC chip substantially reduced the amount of circuitry that would have otherwise been required to implement this function. The only drawback is that the clock input frequencies to these devices are not readily obtainable from a 5 MHz signal.

One forced modification to the 9034 was that to enable remote selection of the T/R waveform (500 Hz square wave or M-sequence) required for operation as both an ionosonde and meteor radar. A small additional amount of circuitry was added to the interface card in the dual channel receiver, and a control line added to the rear panel connector J10 (see Appendix E).

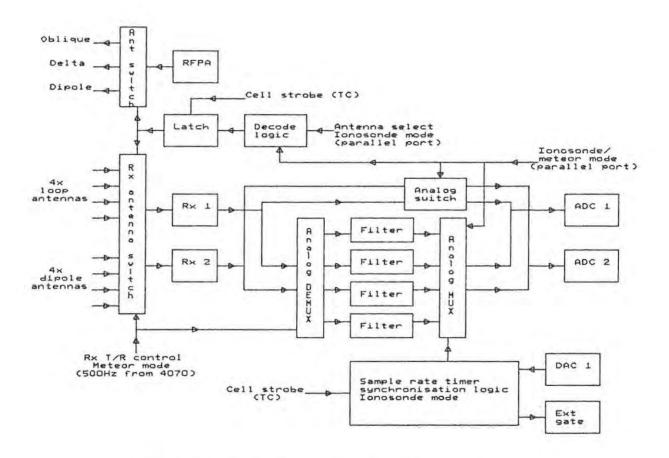

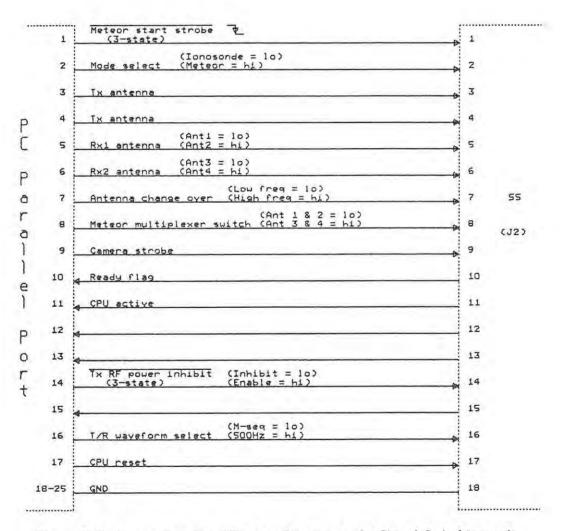

An additional standard 19" rack module, the Signal Switching unit (SS), is required and contains all the antenna, RF, baseband, and filter switching circuitry. The signal path followed varies depending on whether the sounder is operating as an ionosonde or

<sup>&</sup>lt;sup>1</sup>It will in future be taken as understood that PC refers to an IBM AT compatible unless otherwise stated.

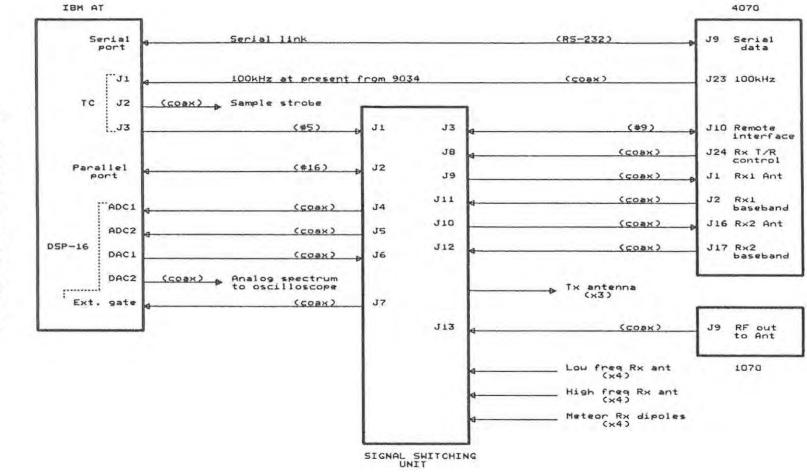

Figure 2-4: Block diagram of the upgraded BR-9034 system

Figure 2-4: Block diagram of the upgraded BR-9034 system

a meteor radar. Control of the SS is largely via the parallel port on the PC. With the exception of the serial link (and internal frequency standard if used), all input and output signals associated with the 9034 connect to the outside world via the SS.

The SS also contains the circuitry necessary for synchronising the sample rate timer on the DSP16 at the start of each cell. The need for this will be described in detail in section 3.4.3.

## 2.3 Rationalisation of ionosondes

Figure [2-4] gives a block diagram of the overall 9034 system showing all control lines, signal lines, etc. The rationalisation programme is intended to introduce some compatibility between the three chirpsounder systems, both on a software and a hardware level. The outermost 'shell' of the system, the man - machine interface, will, within the bounds of any hardware constraints, remain the same on all three systems.

Figure [2-5] is a block diagram of the rationalised VOS-1/VIS-1 sounder systems. The Interface Adapter (IA) will replace the vertichirp controller in the present VOS-1 system. The IA will be substantially simpler in design than vertichirp control and Figure [2-6] shows the functional blocks that will be retained from this controller. A microprocessor is still required to interpret the serial string from the PC and program the frequency synthesizer. The IA will also have to retrieve the IF gain from the receivers and return this to the PC serially.

### 2.4 Man - machine interface

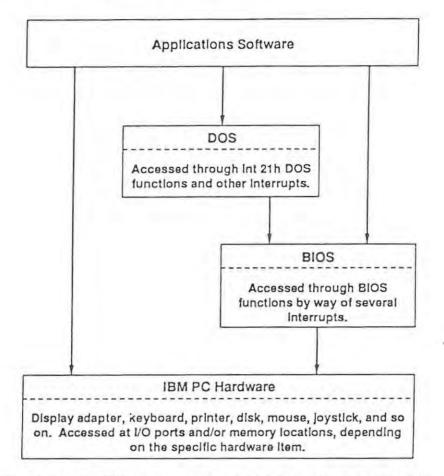

The architecture of the IBM PC is shown in Figure [2-7]. The BIOS<sup>2</sup> is stored in ROM on the motherboard. It gains immediate control of the system on power-up and is responsible for system checks, hardware identification and all low level hardware operations. If the application software makes numerous BIOS calls, then the BIOS can be loaded into 'shadow' RAM for increased speed.

DOS3 is the operating system and affords control of the hardware at a higher level

<sup>&</sup>lt;sup>2</sup>Basic Input Output System

<sup>&</sup>lt;sup>3</sup>Disk Operating System

Figure 2-7: DOS and BIOS systems software as a control and interface layer [Borland (assembler) 1988]

than the BIOS. It is consequently easier to use and a single DOS function call may make use of a number of BIOS routines.

If all hardware operations are performed solely via the above two systems software layers, then the exact hardware configuration will be invisible to the applications software. However, if specific control of the hardware is required, or a non-standard device is being used, then these interface layers can be bypassed. DOS allows access to BIOS calls through software interrupt 21h. For additional information consult the DOS programmers guide [Microsoft 1984].

The applications layer itself may consist of a number of levels. We require that at the highest level, the user interface, the hardware configuration be invisible. Ideally this means that the user need not know what ionosonde, signal processing card, magnetic tape unit, etc. are configured in any particular system in order to operate it. The software driver routines for the sounder itself and signal processing card will obviously vary for the three systems. However, if these routines can be placed in separate libraries then all that is required will be to recompile the main program with the appropriate libraries. This requires that the libraries have a common, predefined interface or declaration section. The 'high level' language chosen for software development must allow for this.

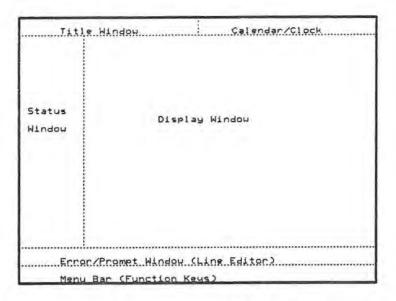

The user interface must be such that the program is easy to use. This requires a menu-driven approach with as much relevant information as possible being displayed on the screen. All user input must be validated before being accepted. Parameters associated with a particular mode of operation are to be stored on disk in a file of system operations. This will avoid problems during power failures. In addition system files could be transferred from one ionosonde system to the next, allowing for immediate duplication of system operation, scheduling, etc. These modes of operation must be rationalised, and more clearly defined than those used by the VOS-1 system.

## Chapter 3

# Description of additional hardware

## 3.1 Digital Signal Processing board (DSP-16)

The DSP-16 is a general purpose signal processing card (based upon the TMS32020 digital signal processor) which interfaces as a slave processor to an IBM PC. It forms a self-contained subsystem, with on-board RAM, two analog input and two analog output channels, and a programmable sample rate timer [Ariel 1987].

Communication is via four consecutive I/O ports in the host PC (switch selectable). The DSP-16 also interrupts the PC with the interrupt request line being jumper selectable. A 64 kbyte page in the PC's memory is required to accommodate the DSP-16's dual ported RAM (see Appendix I for available locations).

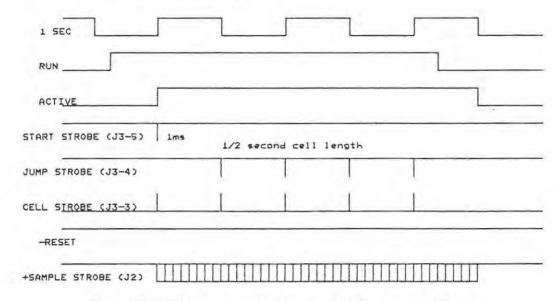

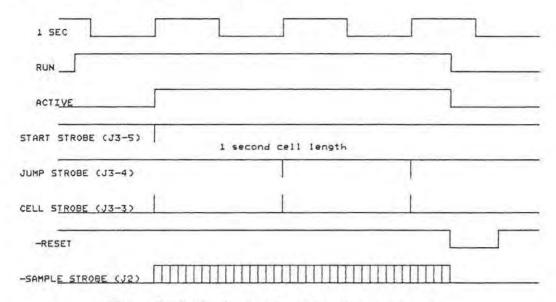

Control of the on-board sample rate timer is possible via an external gate, allowing hardware synchronisation of sampling between cells. A *cell* is the period of time over which the data for a single FFT was collected. In ionosonde mode this cell length corresponds to a linear chirp segment of the sounder sweep as described in Appendix A. A detailed overview of the DSP-16 is given in Appendices F & G.

#### 3.2 Serial link

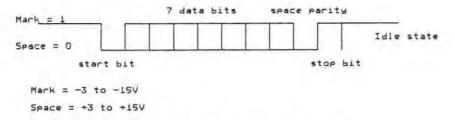

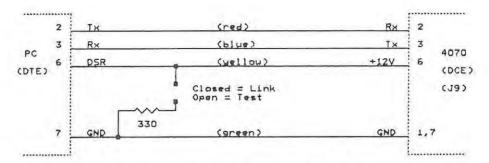

Serial communications between the PC and the BR-9034 is via an RS-232C link at 9600 baud. The transmission format is shown in Figure [3-1]. Parity is switch selectable (on the BR-9034 interface board) between none and space parity. It was left at space parity to allow for operation of the link by the existing dumb terminal instead of the PC, particularly while testing the system.

Figure 3-1: Serial transmission format

Serial port 1 on the PC is used (COM 1), and is configured during the controller software initialization routine. The PC is connected as Data Terminal Equipment (DTE) and the BR-9034 as Data Communications Equipment (DCE). Transmit, receive, ground and Data Set Ready (DSR) are the only lines used. DSR is held at +12 V when the BR-9034 is powered on and is used by the PC to check that the sounder is 'on-line'. If the link is disconnected then this check can be bypassed by a switch on the connector to the PC. This switch allows DSR to float to +12 V by disconnecting it from the  $100\Omega$  pull-down resistor. The connector wiring diagram is given in Appendix J. The serial card is configured to interrupt the PC whenever it receives a character or is ready to transmit the next character. [IBM 1983, BR Communications 1984, Nathanson P 1987]

## 3.3 Timing controller (TC)

A number of alternatives presented themselves for effecting advance/retard timing shifts. Firstly, the actual 5 MHz signal to the BR-9034 could be increased/decreased in frequency. This results in a smooth time adjustment even during sounder operation, as all the sounder frequencies are adjusted accordingly. With the VOS-1 a simple technique of pulse insertion and deletion is employed to produce a modified signal from the standard frequency of 100 kHz. The insertion of a pulse is in effect a doubling of the frequency over that

period. A similar technique could not be used with the 5 MHz signal however, as this is running close to the frequency limit of CMOS logic firstly, and secondly would almost certainly cause problems with the internal timing of the 9034, as it uses phase locked loops which have a limited input frequency range. Instead a small but continuous frequency adjustment would be necessary to effect these changes (4.5 – 5.5 MHz).

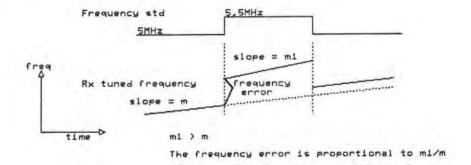

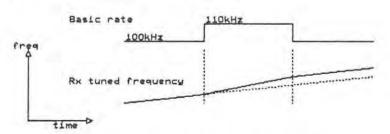

This was the approach first adopted by the author and was pursued to the stage of wire wrapping the proto-type. However, it can be seen (by the author now as well) that as all the receiver mixer frequencies are locked to the 5 MHz standard, a 10% change in the 5 MHz signal will produce a corresponding 10% change in the receiver tuned frequency (shown graphically in Figure [3-2]). This fundamental oversight proved to be a costly mistake time wise.

Figure 3-2: Graphical illustration of effecting timing shifts by adjusting the 5 MHz input

A modification on the above approach would be to effect a burst adjustment of the 5 MHz signal over say 10% of the cell duration. For the remaining 90% of the time the receiver would tune to the correct frequency. However, to produce suitably high shift rates would require adjustment of the input frequency by an order of magnitude. This is again unacceptable.

Figure 3-3: Timing shifts effected by adjusting the basic rate

An elegant solution would be to adjust the basic rate alone (see Figure [3-3]). This is

the technique currently used with the VOS-1, and if the timing controller could produce an adjusted 100 kHz signal compatibility with the VOS-1 system would be maintained, which complements the rationalisation programme. However, this signal is not readily accessible on the 9034 system and the potential for synchronisation problems if this signal was modified, were just too high to have pursued this approach even on an experimental basis. It would also have required numerous modifications to the 9034 in conflict with the authors philosophy of effecting the minimum number of changes.

From a software point of view the above approaches are relatively straight forward as no adjustment of programmed cell frequency jumps is required. In fact the timing shift is invisible to the software, apart from monitoring the size of the time shift.

Figure 3-4: Implementation of timing shifts by adjusting the jump strobe

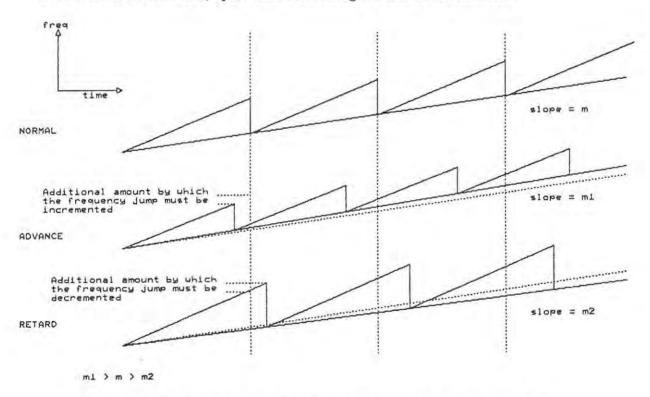

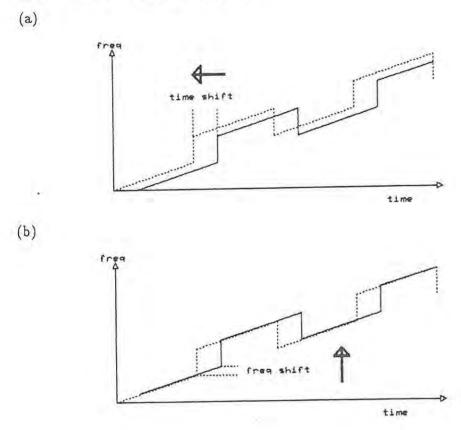

An entirely different approach would be not to modify any of the signals used internally by the 9034, which would avoid many of the timing problems. Cell start times are defined by either a cell start or jump strobe. Cell end times are not defined except by the reception of a jump strobe. Thus the timing could effectively be adjusted during operation by advancing or delaying these strobes.

This requires a software modification to the jump frequency programmed in the serial

string during timing shifts. Different jump offsets would be required for different timing advance/retard rates. Adjustment to the system timing would only become apparent at the start of the next cell. That is timing shifts would not appear smooth and continuous during sounder operation. Timing shifts could also only be implemented in fixed, relatively large steps. This method involves complex synchronisation of the software with the TC hardware.

Figure 3-5: Graphical representation of software frequency jumps to effect 'smooth' timing shifts

All of the above approaches have the distinct advantage of providing a direct method of adjusting the Real Time Clock (RTC) by simply deriving its clock input from the adjusted output frequency. The RTC cannot be set with sufficient accuracy from the PC and changing its clock input frequency proved to be the only solution to adjusting the RTC by small amounts.

A disadvantage of the above methods is that they all effect the cell length. Adjusting the cell length would interfere with re-synchronisation of the external sample rate timer on the DSP16 (see section 3.4.3). This is not a problem if separate ADC cards are being used which require an external sample strobe, as this strobe could be suitably adjusted.

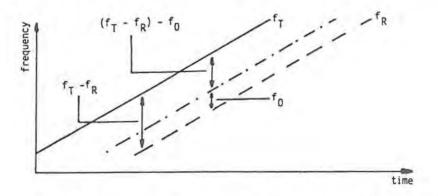

A final solution was to effect all timing shifts during sounder operation purely in software. In other words no adjustment is made of any of the input frequencies to the 9034, nor any of the strobe inputs. Consequently the cell length remains unchanged and all timing and synchronisation problems, both with the 9034 and sample rate timer on the DSP16, are avoided. Timing shifts are effected by adjusting the programmed jump frequency to the 9034. As with the previous method, timing shifts can only be performed in fixed jumps. The size of these jumps is however greatly variable. In addition it is possible to effect a number of small frequency increments at regular intervals during each cell, by using software jump 'strobes', instead of a single jump at the end of the cell (Figure [3-4]). This means that time shifts could be controlled more finely with prompt response to operator commands.

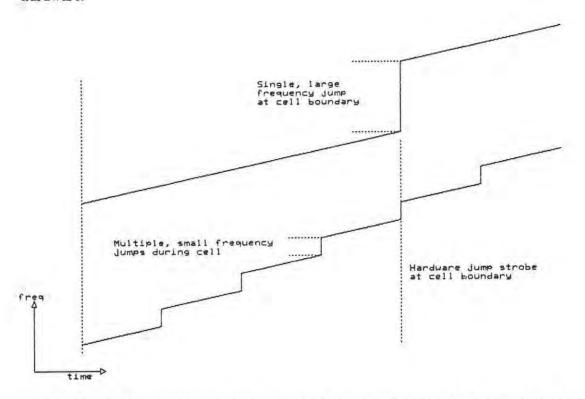

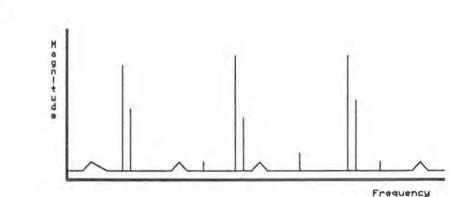

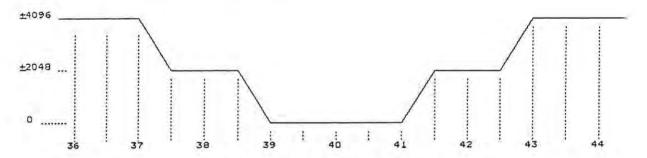

Figure 3-6: Comparison of frequency spectra for: (a) the hardware shift methods and (b) the software shift methods

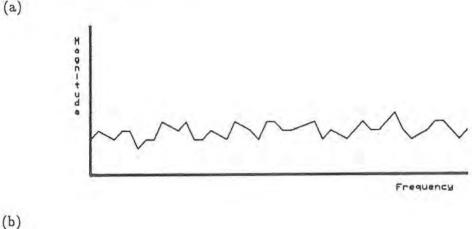

As FFT's are performed on a cell by cell basis, a series of spikes will be observed as the receiver 'steps' through the signal being searched for. With the majority of the

other methods discussed no useful data could be expected from the FFT as the signal would sweep through the whole frequency band of the receiver. Figure [3-6] compares the expected FFT output for these cases.

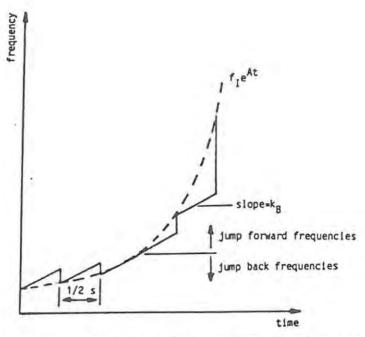

This was the method finally implemented. It is completely effective for linear sweeps where the basic rate and overall rate are equal. A linear sweep where these two rates differ, or a structured cellular sweep where local frequency offsets are used within cells, will produce no results if the timing error is of the order of the cell length. The problem is illustrated in Figure [3-7]. Logarithmic sweeps could be used but would require involved calculations of frequency jumps taking into account the frequency offset. These limitations can for the most part be disregarded.

Figure 3-7: Signal synchronisation by (a) effecting a hardware timing shift and (b) synthesizing a timing shift by a frequency shift, illustrating the problems associated with a structured cellular sweep.

A block diagram of the timing controller is given in Figure [3-8]. From speed and power considerations the TC has been constructed largely from high speed CMOS devices.

Circuit descriptions are given in Appendix K and circuit diagrams in Appendix L. Note: The actual TC hardware and RTC are only adjusted at the end of a sweep. Timing shifts of up to  $\pm 1$  second are possible in 0,1 ms steps. The rate of adjustment is such that to effect a hardware shift of 1 second in either direction takes 1 second to complete.

An onboard crystal oscillator is provided to maintain approximate system timing if the input signal from the frequency standard is lost.

Figure 3-8: Timing controller block diagram

# 3.4 Signal Switching (SS)

### 3.4.1 Antenna switching

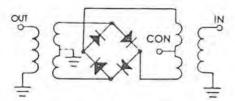

In ionosonde mode four spacially located antennas are needed for determination of angle of arrival, doppler velocity, etc (Appendix A). Antenna switching occurs between cells, ie at a maximum rate of 4 Hz. If mechanical relays were used to achieve this, then signal attenuation would be negligible but reliability questionable. Even if the programme schedule were only a simple synoptic consisting of a single 5 minute ionogram every hour, the majority of these devices could only guarantee 1 year of reliable operation. A malfunction might not be readily detectable by the operator either. So, some type of solid state switching device is required. The CMOS analog switches that will be discussed in section 3.4.2 would not be suitable as attenuation would be too high for such small signals. BR Communications use two baluns and some diodes to perform RF switching. Single package devices (PAS-3) are available in this configuration (Figure [3-9]), and are in fact the devices that are used by the meteor system as will be described shortly.

Figure 3-9: RF switch

For maximum flexibility any of the four ionosonde receive antennas should be able to connect to either or both the receivers. In addition it may or may not be desirable to ground unused antenna inputs as done presently in the VOS-1 system (see Figure [3-10]). In the authors opinion this is likely to degrade system performance, but this would have to be determined empirically.

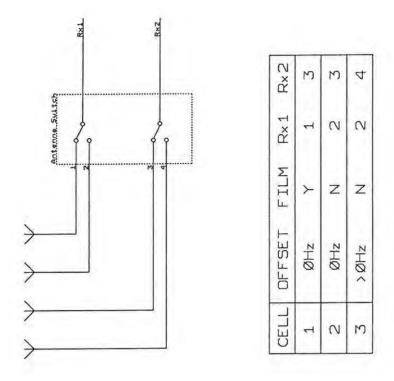

An alternative design for antenna switching in ionosonde mode, suggested by the author and Mr BT Bonnevie, is shown in Figure [3-11]. This approach simplifies the required hardware substantially, while sacrificing minimal system flexibility. Requirements on antenna orientation are more rigid, and the exact configuration will have to be taken into consideration during post analysis of recorded data. Programming of multi-cell soundings will also be simplified, as antenna allocation will be independent of station location. It is

Figure 3-10: Antenna switching in the VOS-1 system

important that in the physical construction of the SS all RF signal paths be kept equal in length. Antenna selection is via the parallel port on the PC and some decoding logic in the SS itself.

In meteor mode pairs of receive antennas are switched to the receivers at 250 Hz (Appendix B). The circuitry to perform this was designed by Prof G Poole and uses four PAS-3 switches. The switching signal is provided by the 4070 dual channel receiver, Rx T/R control out (Appendix E).

Depending on whether the system is operating in ionosonde or meteor mode, one bank of antennas will be disabled. This control line comes directly from the parallel port.

The PAS-3 switches were very expensive but no suitable alternative could be found. The author has thus provided a rough circuit diagram (Appendix L) of the RF switching circuitry, but this will have to be constructed at some future date when the devices can be purchased.

The RF power out can be connected to one of three transmit antennas or a 50  $\Omega$  dummy load. Should the SS unit lose power or the antenna select input, the transmitter output will be switched into the dummy load.

Figure 3-11: RF signal path in ionosonde mode, showing all possible antenna orientations, and a sample 3 cell sounding structure (Mr BT Bonnevie)

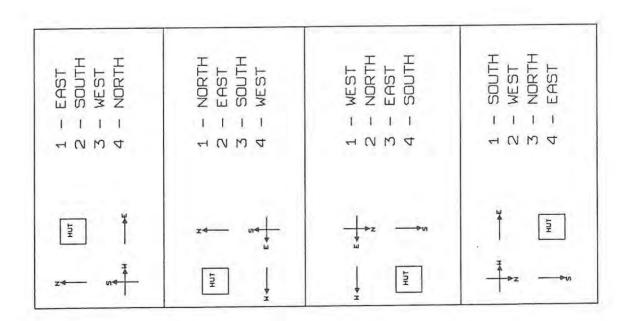

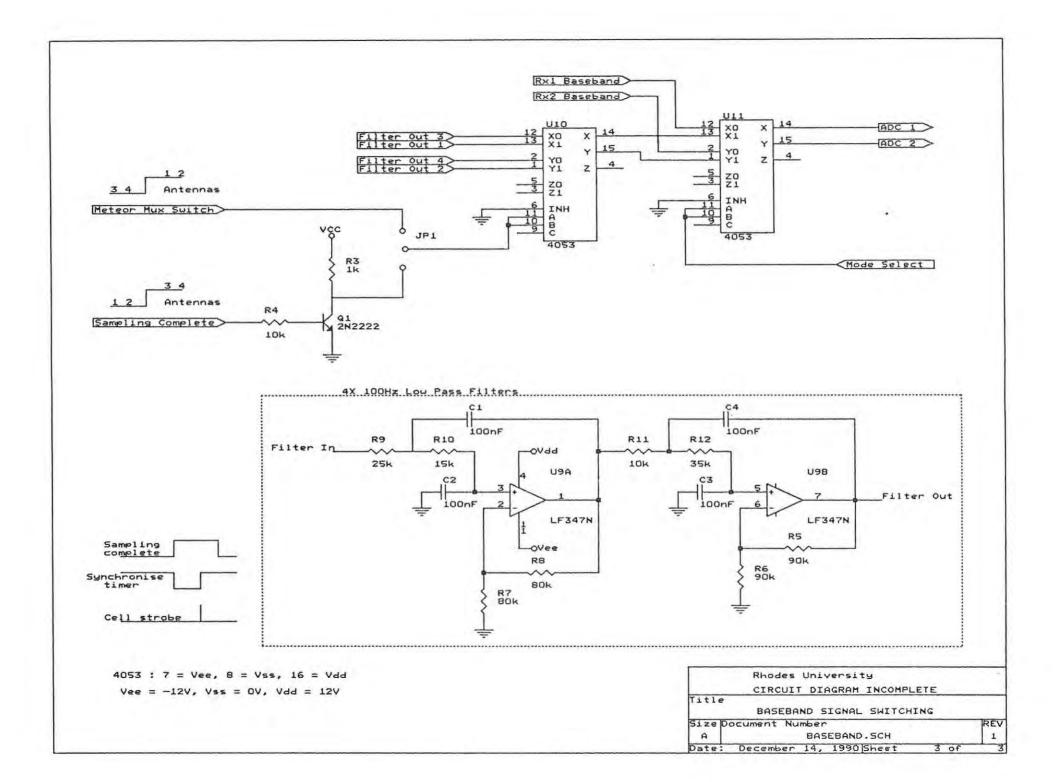

# 3.4.2 Base-band signal and filter switching

Figure 3-12: Effective signal path in ionosonde mode

Figure 3-13: Effective signal path in meteor mode

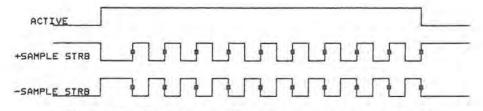

In ionosonde mode, receiver outputs are sampled directly by the ADC's (Figure [3-12]). In meteor mode the receiver bandwidth is 2500 Hz and the receiver outputs pass through 100 Hz low pass filters before being sampled. An analog demultiplexer switches each receiver output between a pair of these filters. Switching is synchronous with the RF section, with allowance for transmission delay through the receivers (Appendix B). Pairs of filter outputs are then switched to the ADC's by an analog multiplexer as shown in Figure [3-13]. Control of this multiplexer is provided by the DAC 1 on the signal processing card (or the parallel port if separate ADC cards are being used). A timing

diagram of multiplexer operation is given in Figure [F-5]. Signal switching is done using CMOS analog switches (type 4053 & 4066). An additional switch is used to bypass these low pass filters in ionosonde mode.

### 3.4.3 Synchronisation of the external sample rate timer

Two approaches to sampling the receiver outputs exist. Either the ADC card(s) use an external sample strobe, provided by the timing controller, or alternatively the card may use an onboard sample rate timer, in which case synchronisation of the timer with the cell strobe is required.

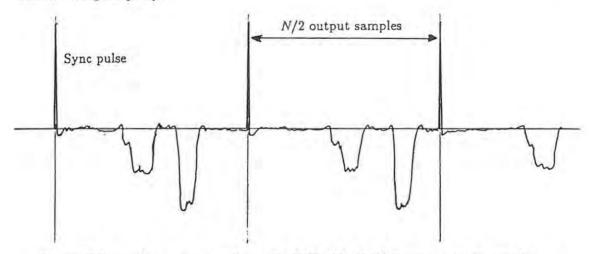

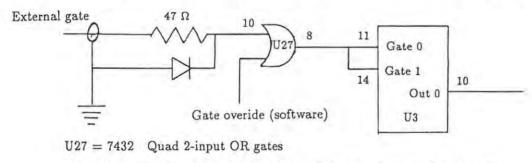

The second alternative is applicable to the DSP-16 and synchronisation is performed at the start of every cell. This is achieved by using a slightly higher sample rate (1024,6 Hz) so that the last sample will be taken before the end of the cell. Immediately after this sample the sampling complete line (DAC 1) to the signal switching unit is raised hi. This positive edge clocks a flip flop which then disables the sample rate timer via an external gate on the DSP-16 card as shown in Figure [3-14]. This gate holds the timer reset until it is released by the next cell strobe from the TC. A fundamental requirement of this approach is that the time interval between enabling the timer and first sample being taken, remain contstant. A detailed timing diagram is given in Figure [F-4].

Figure 3-14: Synchronisation of the sample rate timer on the DSP-16

# 3.5 Film Recording System (FRS)

The VOS-1 system produces ionogram records by 'dragging' the film across a viewing slit on an oscilloscope screen. This is a cumbersome approach and is fraught with mechanical and electronic problems. The intention is to replace this with a system whereby the ionogram is first plotted on a graphics screen and then photographed using a camera

with a motor-drive. A single control line has been made available on the parallel port to provide the necessary strobe to the camera.

Ideally a second monitor is needed, that could be set up in a dark cabinet and used purely for this purpose. To produce ionograms of suitable quality a graphics screen (EGA<sup>1</sup> or VGA<sup>2</sup>) would be needed. This poses a problem however as every monitor requires a driver card in the PC and the memory location of the various cards has been predefined by IBM and is used by DOS and the ROM BIOS. It is theoretically possible to simultaneously operate a CGA<sup>3</sup> and monochrome monitor if both are running in text mode. However only one adapter can be installed if graphics mode is to be used due to over-lapping of memory addresses as a result of the additional memory requirements (see Figure [I-5] for CRT memory locations).

The final possibility is to use two similar monitors in parallel. This would require either installing two identical graphics adapter cards, or driving both monitors from one card. The first is not possible as the PC requires acknowledge signals from the adapter cards, and this would cause bus contention as the timing on the two cards could never be exactly the same. The second would almost certainly require additional buffering of one of the monitors.

The author has, where possible, allowed for the future inclusion of the FRS with the present software.

<sup>&</sup>lt;sup>1</sup>Enhanced Graphics Adapter

<sup>&</sup>lt;sup>2</sup>Video Graphics Array

<sup>&</sup>lt;sup>3</sup>Colour Graphics Adapter

# Chapter 4

# Software

The PC performs two distinct functions. Firstly it has overall <u>control</u> of the complete sounder system, and is responsible for the programming of the ionosonde as well as automatic scheduling of operations. Secondly it is responsible for <u>data capture</u>, processing and data display, and finally storage to some mass storage medium. The software that performs the above two functions is contained in the file CONTROLEXE.

System timing is derived from the timing controller, a card which plugs into the PC and is programmable by the PC. The PC also plays host to the digital signal processing card (and analogue to digital converter cards) which performs initial data capture and processing.

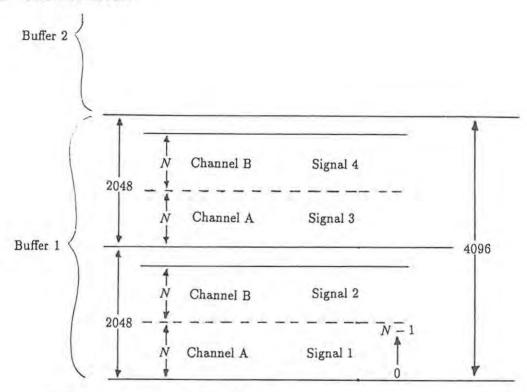

# 4.1 Data capture and preliminary signal processing

This is performed using the Ariel Corporations, TMS32020 based, DSP-16. The two on-board 16 bit analog to digital converters (ADC) are used to sample the two input channels simultaneously. Hardware sample rates of approximately 1024 or 2048 Hz are used. Lower sample rates can be achieved by discarding samples in software. Samples from consecutive cells are stored in two separate buffers with one buffer being processed while the other is being filled (Figure [F-2]). The DSP-16 software is written such that it has two modes of operation, described as follows.

# Data upload format

Total: 2661 words

#### Meteor mode

| Spectral    | $f_{max}1$    |  |  |

|-------------|---------------|--|--|

| maxima      | $f_{max}2$    |  |  |

| frequencies | $f_{max}3$    |  |  |

|             | fmax4         |  |  |

|             | R1 (at fave)  |  |  |

|             | I1            |  |  |

|             | R2            |  |  |

|             | 12            |  |  |

|             | R3            |  |  |

|             | I3            |  |  |

|             | R4            |  |  |

| (4)         | I4            |  |  |

| 1.0         | Freq spread 1 |  |  |

|             | Freq spread 2 |  |  |

|             | Freq spread 3 |  |  |

|             | Freq spread 4 |  |  |

|             | Sample max 1  |  |  |

|             | Sample max 2  |  |  |

|             | Sample max 3  |  |  |

|             | Sample max 4  |  |  |

|             | Noise Hi      |  |  |

|             | Noise Lo      |  |  |

|             |               |  |  |

Total: 22 words

# Control data download format

|     | Mode              |

|-----|-------------------|

| No. | samples / channel |

| Po  | ints / cell (PPC) |

| Ec  | ho criterion (Hz) |

| S   | pread threshold   |

|     | State             |

| Sa  | mple rate divider |

Total: 7 words

Mode = 0 Meteor operation  $Mode \neq 0$  Ionosonde mode

State = 0 Data output to PC (interrupt PC)

State > 0 Analogue spectrum only

Sample rate = Hardware rate / 2Rate divider

Figure 4-1: DSP-16 to PC data transfer format

#### 4.1.1 Ionosonde mode

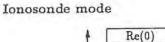

In ionosonde mode a 1024 point complex FFT simultaneously transforms data from both input channels into the frequency domain. If 1024 points per channel have not been sampled, as for example in the case of half and quarter second cells, the remainder of the buffer is filled with zeros. This has the effect of extending the period of time over which the signal is sampled in the time domain (see Appendix C). The FFT uses an in-place, scrambled input – natural output algorithm and was adapted from the one supplied by Delanco Spry with the model 10 DSP board [Langman D 1986].

The real and imaginary components, corresponding to channels A and B respectively, are separated using an unscrambling routine based on Equations [C-6] & [C-7]). A combined power spectrum of the two channels is then calculated, scaled to retain as many significant bits as possible, and indexed in descending order of magnitude to a preselectable number of points per cell (PPC). Finally all of the above information is transferred to the host PC, in the format shown in Figure [4-1], by consecutively writing each word to the host data port. The DSP-16 interrupts the PC when it is ready to upload data. The above routines were adapted from those written by Mr BT Bonnevie for the model 10. Compatibility of the two sets of code has been maintained as far as possible.

Figure 4-2: Graphical representation of data storage in ionosonde mode.

Re-synchronisation of the sample rate timer is required at the start of each cell in order to maintain phase relationships for cell comparisons. The external gate is used to disable the interrupt timer at the end of each cell until the next start cell strobe. This gate is disabled via one of two digital to analog converters which outputs a positive pulse after the required number of samples have been captured. The gate is reset by the next start cell strobe. The relevent timing diagram is shown in Figure [F-4]. [Ariel 1987]

The first valid sample is stored in position 1 of the respective channel buffer. The value stored in position 0 is conceptually the sample from time zero, and is set to zero in ionosonde mode before computing the FFT (see Figure [4-2]). This is unimportant as

there will be no valid data to sample at that time anyway if the ionosonde is 'chirping' (Figure [4-3]).

Figure 4-3: Transmit and received signals at cell boundaries in 'chirp' mode.

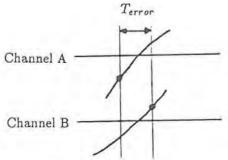

The error allowed in the sampling time of the two channels must not exceed 1% of the shortest period in the signal out of the receiver (500 Hz in ionosonde mode).

$$T_{min}=1/f_{max}=1/(500Hz)=2~ms$$

$$1\% \longrightarrow T_{error}=20~\mu s$$

The DSP-16 samples to within 1 ns, ie simultaneously for our application. Similarly the error allowed between appropriate samples in different cells must meet this criterion, ie. be less than 20  $\mu s$ .

Figure 4-4: Sampling error

#### 4.1.2 Meteor mode

N may have a maximum size of 1024

Figure 4-5: Storage of samples in meteor mode