# Real-Time Audio Spectrum Analyser

Research, Design, Development and Implementation using the 32-bit ARM® Cortex-M4 Microcontroller

A dissertation submitted in fulfilment of the requirement for the degree of

Master of Science in Electronics

of

**Rhodes University**

by

Stefan Antonio Just

May 2016

## **Abstract**

This thesis describes the design and testing of a low-cost hand-held real-time audio analyser (RTAA). This includes the design of an embedded system, the development of the firmware executed by the embedded system, and the implementation of a real-time signal processing algorithms.

One of the objectives of this project was to design an alternative low-cost audio analyser to the current commercially available solutions. The device was tested with the audio standard test signal (pink noise) and was compared to the expected flat-spectrum response corresponding to a balanced audio system. The design makes use of an 32-bit Reduced Instruction Set Computer (RISC) processor core (ARM Cortex-M4), namely the STM32F4 family of microcontrollers. Due to the pin compatibility of the microcontroller (designed and manufactured by STMicroelectronics), the new development board can also be upgraded with the newly released Cortex-M7 microcontroller, namely the STM32F7 family of microcontrollers. Moreover, the low-cost hardware design features 256kB Random Access Memory (RAM); on-board Micro-Electro-Mechanical System (MEMS) microphone; on-chip 12-bit Analogue-to-Digital (A/D) and Digital-to-Analogue (D/A) Converters; 3.2" Thin-Film-Transistor Liquid-Crystal Display (TFT-LCD) with a resistive touch screen sensor and SD-Card Socket.

Furthermore, two additional expansion modules were designed and can extend the functionality of the designed real-time audio analyser. Firstly, an audio/video module featuring a professional 24-bit 192kHz sampling rate audio CODEC; balanced audio microphone input; unbalanced line output; three MEMS microphone inputs; headphone output; and a Video Graphics Array (VGA) controller allowing the display of the analysed audio spectrum on either a projector or monitor. The second expansion module features two external memories: 1MB Static Random Access Memory (SRAM) and 16MB Synchronous Dynamic Random Access Memory (SDRAM). While the two additional expansion modules were not completely utilised by the firmware presented in this thesis, upgrades of the real-time audio analyser firmware in future revisions will provide a higher performing and more accurate analysis of the audio spectrum.

The full research and design process for the real-time audio analyser is discussed and both Problems and pitfalls with the final implemented design are highlighted and possible resolutions were investigated. The development costs (excluding labour) are given in the form of a bill of materials (BOM) with the total costs averaging around R1000. Moreover, the additional VGA controller could further decrease the overall costs with the removal of the TFT-LCD screen from the audio analyser and provided the external display was not included in the BOM.

# **Declaration**

I hereby declare that this thesis has not been submitted, either in the same or different form, to this or any other university for a degree and that it represents my own work. I know the meaning of plagiarism and declare that all of the work in the thesis, save for that which is properly acknowledged, is my own.

Stefan Antonio Just May 2016

# **Acknowledgements**

I would like to acknowledge a selected few individuals. Without your help this research project would not have been possible.

- Mr Anthony Sullivan For supervising this research project, providing guidance and endless patience with me and my need to over complicate the simplest of tasks. Moreover, for allowing me to use, abuse and finally kill your old CRT monitor. R.I.P.

- Mr Andy Youthed For helping create a backup server which contained all the code, schematic and circuit designs as well as all the resources used for this research. Additionally, for teaching me the process of etching small printed circuit boards for prototyping.

- Mr Dino Giovannoni For providing your thoughts, opinions and guidance in writing this thesis. Additionally, for your infinite wisdom, knowledge and aid in navigating the intricacies of LaTeX.

- Family For providing the funding of the first year of this research project, without the financial aid none of this research would be possible. Thank you for your support, sound opinions and suitable suggestions, all were considered.

- Department of Physics and Electronics For the use of the *Tektronix MSO 2024B Mixed Signal Oscilloscope*, the *Tektronix AFG310 Arbitrary Function Generator* and a work space within the department.

- Microtronix Manufacturing For aiding in fabricating and populating the printed circuit boards.

- National Research Foundation (NRF) For funding the second year of this research project. The financial assistance of the National Research Foundation (NRF) towards this research is hereby acknowledged. Opinions expressed and conclusions arrived at, are those of the author and are not necessarily to be attributed to the NRF.

"Craftsmanship is a direct expression of character." - Don Davis

# **Contents**

| $\mathbf{C}$ | onter        | nts     |                                                  | V    |

|--------------|--------------|---------|--------------------------------------------------|------|

| Li           | st of        | Figure  | es                                               | ix   |

| Li           | st of        | Tables  | 5                                                | xii  |

| 1            | Intr         | oducti  | on                                               | 1    |

|              | 1.1          | What    | are Audio Analysers and How are They Used        | . 1  |

|              | 1.2          | Motiva  | ations for the Research Project                  | . 1  |

|              | 1.3          | Resear  | rch Goal and Objectives                          | . 2  |

|              | 1.4          | Resear  | rch Approach                                     | . 3  |

|              |              | 1.4.1   | Phase 1 - Research, Theory and Literature Review | . 3  |

|              |              | 1.4.2   | Phase 2 - Design of Hardware                     | . 3  |

|              |              | 1.4.3   | Phase 3 - Development of Firmware                | . 4  |

|              |              | 1.4.4   | Phase 4 - Implementation of the RTAA             | . 4  |

|              |              | 1.4.5   | Phase 5 - Investigate Possible Improvements      | . 4  |

|              | 1.5          | Thesis  | Structure                                        | . 4  |

| <b>2</b>     | $Th\epsilon$ | eory an | nd Literature Review                             | 5    |

|              | 2.1          | Audio   | Signals and Systems                              | . 5  |

|              |              | 2.1.1   | Types of Audio Signals                           | . 5  |

|              |              | 2.1.2   | White Noise                                      | . 7  |

|              |              | 2.1.3   | Pink Noise                                       | . 7  |

|              |              | 2.1.4   | Black Noise                                      | . 8  |

|              |              | 2.1.5   | Audio Equalization                               | . 8  |

|              |              | 2.1.6   | The Human Auditory System                        | . 10 |

|              |              | 2.1.7   | Equivalent Sound Level Addition                  | . 11 |

|              | 2.2          | Fourie  | r Transformations                                | . 13 |

Contents vi

|   |     | 2.2.1   | Continuous-Time Fourier Transform (CTFT)                                  | 13        |

|---|-----|---------|---------------------------------------------------------------------------|-----------|

|   |     | 2.2.2   | Discrete-Time Fourier Transform (DTFT)                                    | 13        |

|   |     | 2.2.3   | Discrete Fourier Transform (DFT)                                          | 14        |

|   | 2.3 | Filters | 5                                                                         | 15        |

|   |     | 2.3.1   | Digital Signal Processing Windows                                         | 15        |

|   |     | 2.3.2   | Audio Weighting Filters                                                   | 19        |

|   | 2.4 | Simult  | aneous Real-Valued Fast-Fourier Transform (FFT)                           | 23        |

|   | 2.5 | The D   | ecibel $(dB)$                                                             | 27        |

|   |     | 2.5.1   | The Decibel in Electronics                                                | 27        |

|   |     | 2.5.2   | The Decibel in Acoustics $(L_I, L_W, L_P)$                                | 28        |

|   |     | 2.5.3   | The Decibel in Audio Electronics (dBV, dBu, dBW ,dBm, dBFS) $\ . \ . \ .$ | 28        |

|   |     | 2.5.4   | Adding Decibels and Combining Voltages                                    | 32        |

|   |     | 2.5.5   | Microphone Sensitivity $(S_V)$ and Open-Circuit voltage $(V_O)$           | 34        |

|   | 2.6 | The S'  | TM32F4 Series of ARM® Cortex-M4 Microcontrollers                          | 35        |

|   |     | 2.6.1   | STM32F407 Microcontroller (Foundation Line)                               | 35        |

|   |     | 2.6.2   | STM32F429 Microcontroller (Advanced Line)                                 | 35        |

| 3 | Ovo | rviou   | of the Real-Time Audio Analyser                                           | 37        |

| J | 3.1 |         | v                                                                         | 37        |

|   | 5.1 | 3.1.1   |                                                                           | 38        |

|   | 3.2 |         | ·                                                                         | 39        |

|   | 5.2 | Specin  | cations and Capabilities of the Real-Time Addio Analyset                  | 99        |

| 4 | The |         | v                                                                         | <b>40</b> |

|   | 4.1 |         |                                                                           | 40        |

|   | 4.2 |         | al Oscillator                                                             |           |

|   | 4.3 |         | 2F4 Microcontroller                                                       |           |

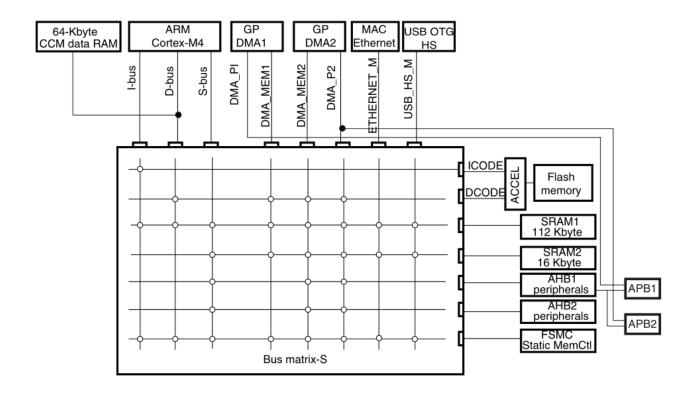

|   |     | 4.3.1   | Memory and System Bus Architecture                                        |           |

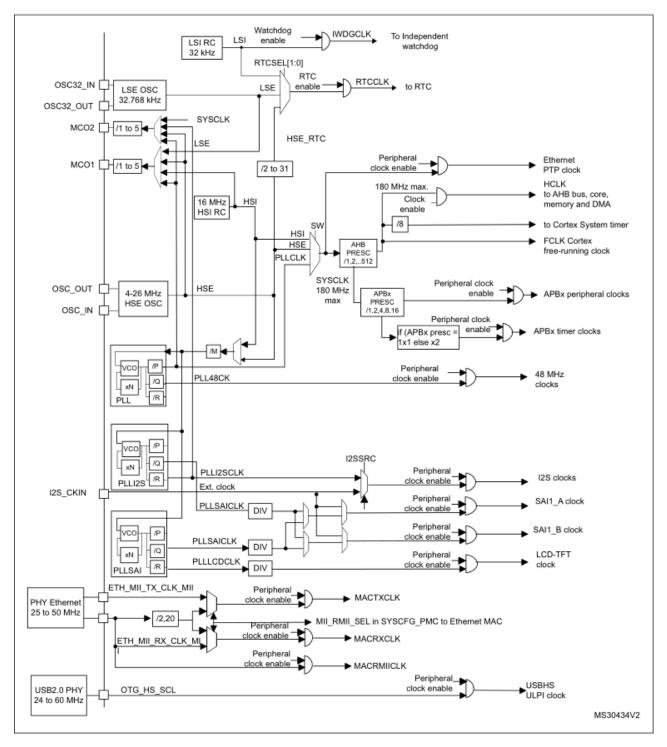

|   |     | 4.3.2   | Reset and Clock Controller (RCC)                                          |           |

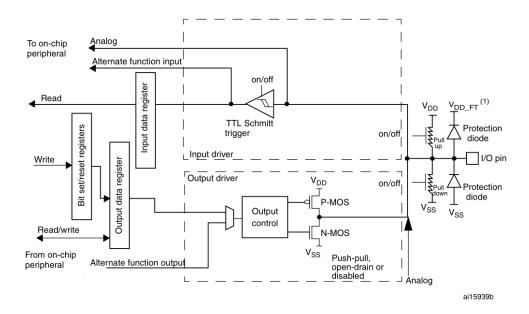

|   |     | 4.3.3   | General Purpose Input/Output (GPIO) Controller                            | 48        |

|   |     | 4.3.4   | Nested Vectored Interrupt Controller (NVIC)                               | 49        |

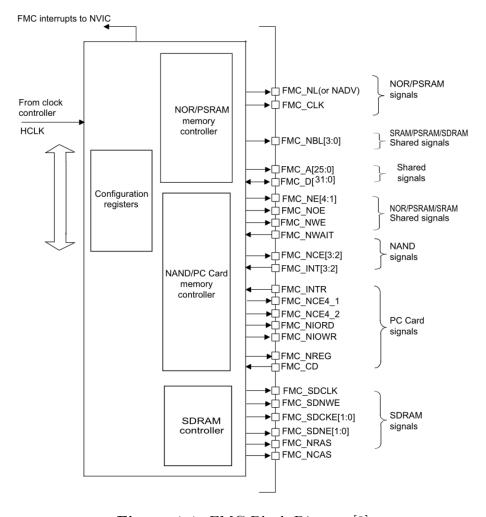

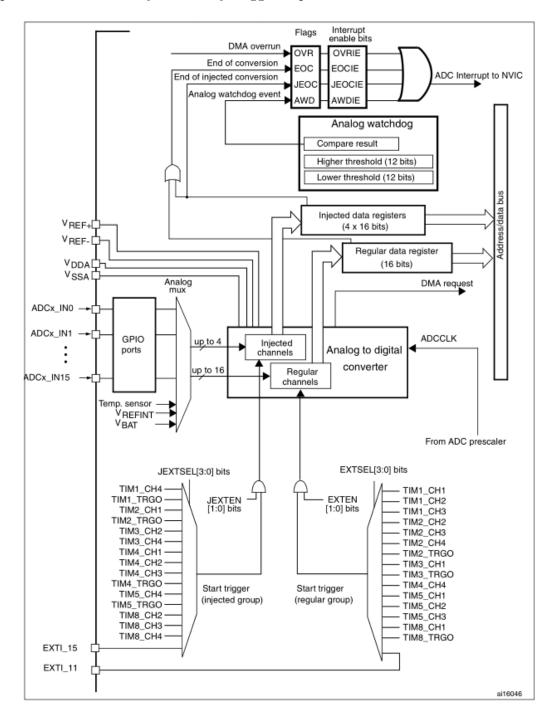

|   |     | 4.3.5   |                                                                           | 49        |

|   |     | 4.3.6   |                                                                           | 51        |

|   |     | 4.3.7   |                                                                           | 52        |

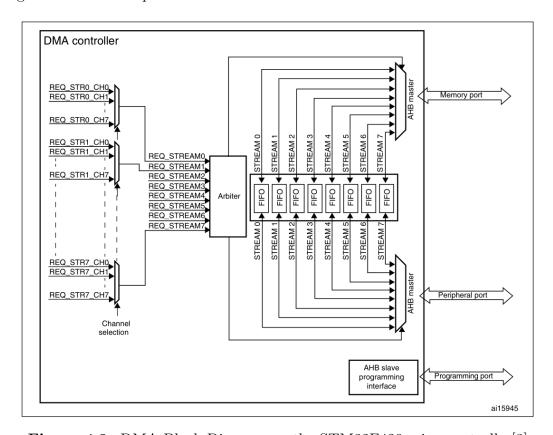

|   |     | 4.3.8   | Direct Memory Access (DMA)                                                | 54        |

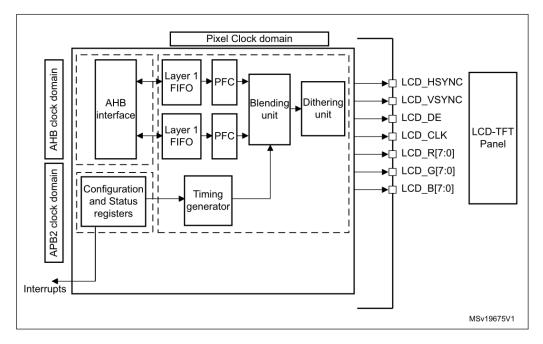

|   |     | 4.3.9   | LCD-TFT Display Controller (LTDC)                                         | 54        |

|   | 4.4 | Debug   | ging LEDs, Switches and Jumpers                                           | 55        |

|   |     | 4.4.1   | Debugging LEDs                                                            | 55        |

|   |     | 4.4.2   | Reset and DFU Bootloader Switches                                         | 56        |

|   |     |         |                                                                           |           |

|   |     | 4.4.3   | Mode Selection Jumpers                                                    | 56        |

|   | 4.5 |         | · · · · · · · · · · · · · · · · · · ·                                     | 56<br>56  |

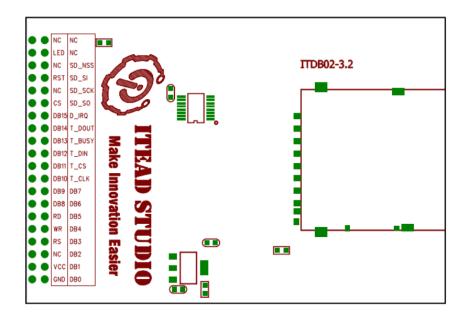

|   | 4.5 |         | LCD Screen, Touch Screen Controller and SD Card Socket                    |           |

Contents vii

|              | 4.6 | External Memory                                  |

|--------------|-----|--------------------------------------------------|

|              |     | 4.6.1 AS6C8016 SRAM                              |

|              |     | 4.6.2 AS4C8M16S SDRAM                            |

|              | 4.7 | Audio Data Converters                            |

|              |     | 4.7.1 Internal STM32F429 ADC                     |

|              |     | 4.7.2 External CS4272 CODEC                      |

|              | 4.8 | External and Internal Microphones                |

|              |     | 4.8.1 Internal Microphone                        |

|              |     | 4.8.2 External Microphone                        |

|              | 4.9 | Video Graphics Array (VGA) Controller            |

|              |     | 4.9.1 Video Digital-to-Analogue Converters (DAC) |

| 5            | The | Real-Time Audio Analyser Firmware 75             |

|              | 5.1 | Programming the STM32F4 Microcontroller          |

|              | 5.2 | CMSIS-DSP Software Library                       |

|              | 5.3 | The Real-Time Audio Analyser Files               |

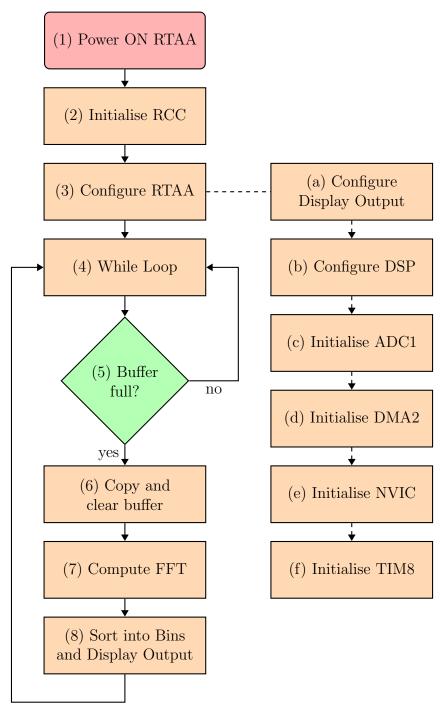

|              | 5.4 | The Real-Time Audio Analyser Algorithm           |

|              |     | 5.4.1 Powering up the Real-Time Audio Analyser   |

|              |     | 5.4.2 Initialise RCC                             |

|              |     | 5.4.3 Configure the Real-Time Audio Analyser     |

|              |     | 5.4.4 Endless While Loop and DSP Processing      |

|              | 5.5 | Some Final Words                                 |

| 6            | Tes | ting and Discussion 91                           |

|              | 6.1 | Performance Comparison to Commercial Solutions   |

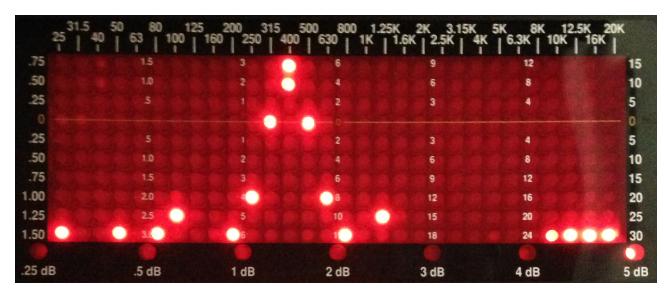

|              |     | 6.1.1 Pure Audio Tone Signal Results             |

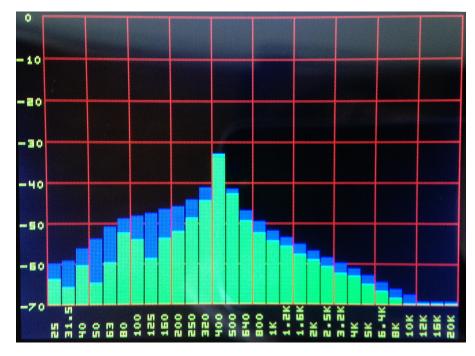

|              |     | 6.1.2 Pink Noise Audio Signal Results            |

|              |     | 6.1.3 Final Deliberation                         |

| 7            | Fut | ure Work                                         |

| 8            | Cor | aclusion 99                                      |

| $\mathbf{A}$ | Sch | ematics, PCB Designs and BOM 101                 |

|              | A.1 | DAD Schematics and PCB Designs                   |

|              |     | A.1.1 DAD MCU Board                              |

|              |     | A.1.2 DAD External Memory Board                  |

|              |     | A.1.3 DAD Audio and Video Board                  |

|              |     | A.1.4 DAD Pinout Board                           |

|              |     | A.1.5 Internal MEMS Microphone Breakout Boards   |

| В            | STI | M32F4 Peripheral Registers 119                   |

|              | B.1 | Reset and Clock Controller (RCC)                 |

Contents viii

| B.2 General Purpose Input/Output (GPIO) Controller        | 20  |

|-----------------------------------------------------------|-----|

| B.3 Nested Interrupt Controller (NVIC)                    | 21  |

| B.4 Advanced Timer 8 (TIM8)                               | 21  |

| B.5 Flexible Memory Controller (FMC)                      | 22  |

| B.6 Analogue-to-Digital Converter (ADC)                   | 23  |

| B.7 Direct Memory Access (DMA) Controllers                | 23  |

| B.8 LCD-TFT Display Controller (LTDC)                     | 24  |

| B.9 Inter-Integrated Circuit (I <sup>2</sup> C) Interface | 25  |

| B.10 Serial Peripheral Interface (SPI)                    | 25  |

| B.11 Inter-IC Sound (I <sup>2</sup> S) Interface          | 26  |

| Bibliography 1                                            | .27 |

| List of Electronic Vendors 1                              | .32 |

| Acronyms 1                                                | .34 |

# **List of Figures**

| 2.1  | Periodic 100Hz test tone signal calculated and plotted using Matrix Laboratory             |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | (MATLAB)                                                                                   | 6  |

| 2.2  | Non-periodic random noise signal calculated and plotted using MATLAB                       | 6  |

| 2.3  | Front view of DN360 $\frac{1}{3}$ octave graphic equaliser[1]                              | 8  |

| 2.4  | Addition of correlated audio sources[2]                                                    | 11 |

| 2.5  | Addition of uncorrelated audio sources $[2]$                                               | 12 |

| 2.6  | Rectangle window function for 4096 data points calculated and plotted with MATLAB $$       | 16 |

| 2.7  | Hanning window function for 4096 data points calculated and plotted with MATLAB            | 16 |

| 2.8  | Hamming window function for 4096 data points calculated and plotted with MATLAB            | 17 |

| 2.9  | Welch window function for 4096 data points calculated and plotted with MATLAB              | 17 |

| 2.10 | Bartlett window function for 4096 data points calculated and plotted with MATLAB           | 18 |

| 2.11 | Blackman window function for 4096 data points calculated and plotted with MATLAB           | 18 |

| 2.12 | Audio weighting functions for 30 bands of $\frac{1}{3}$ octave spaced steps calculated and |    |

|      | plotted using MATLAB                                                                       | 23 |

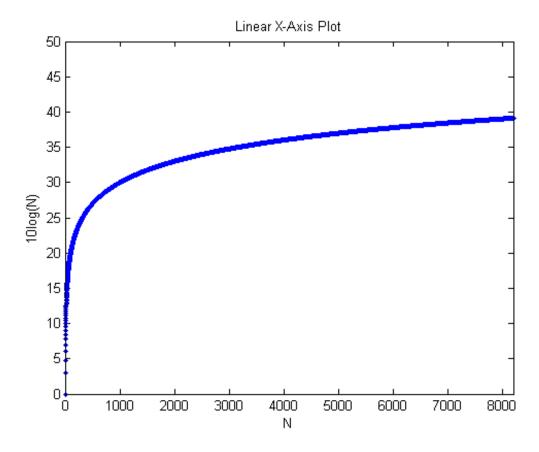

| 2.13 | Difference between correlated and uncorrelated decibel addition for N sources each         |    |

|      | with level L calculated and plotted using MATLAB                                           | 33 |

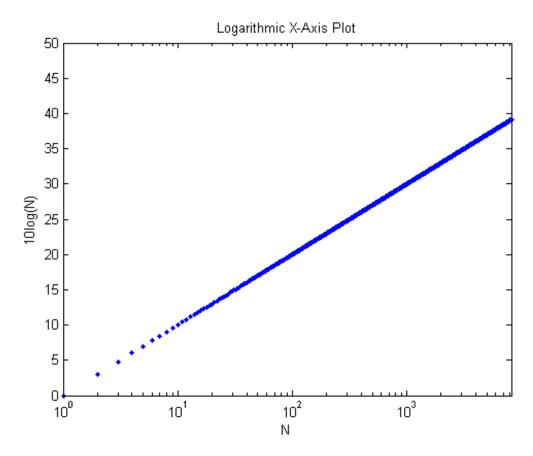

| 2.14 | Difference between correlated and uncorrelated decibel addition for N sources each         |    |

|      | with level L calculated and plotted using MATLAB                                           | 34 |

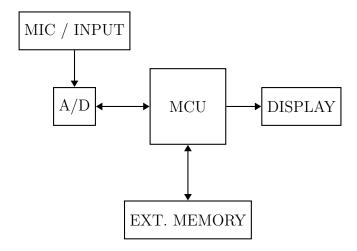

| 3.1  | Simplified Real-Time Audio Analyser System Overview                                        | 37 |

| 4.1  | System Bus Architecture on the STM32F429 microcontroller[3]                                | 44 |

| 4.2  | Clock Tree on STM32F429 microcontroller[3] $\dots \dots \dots \dots \dots \dots$           | 45 |

| 4.3  | GPIO port bit basic structure[3]                                                           | 48 |

| 4.4  | FMC Block Diagram[3]                                                                       | 50 |

| 4.5  | FMC Memory Banks[3]                                                                        | 51 |

| 4.6  | Timers Features Comparison[3]                                                              | 52 |

| 4.7  | Single ADC Block Diagram on the STM32F429 microcontroller[3]                               | 53 |

List of Figures x

| 4.8  | DMA Block Diagram on the STM32F429 microcontroller[3]                                                                                                    | 54 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | LTDC Block Diagram on the STM32F429 microcontroller<br>[3] $\ \ldots \ \ldots \ \ldots \ \ldots$                                                         | 55 |

| 4.10 | $ITDB02-3.2S\ TFT-LCD\ Module\ from\ ITead\ Studio[4]\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$                                                                  | 57 |

| 4.11 | thm:tom:tom:tom:tom:tom:tom:tom:tom:tom:to                                                                                                               | 57 |

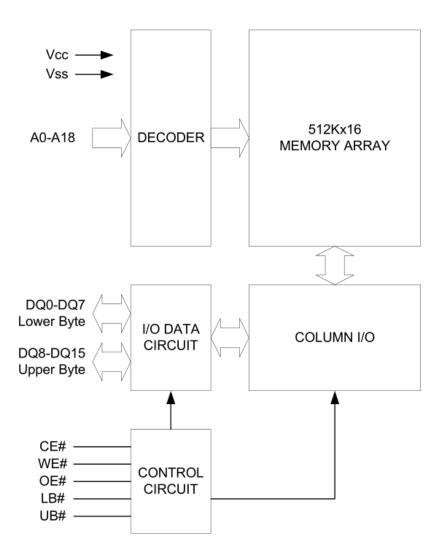

| 4.12 | SRAM Block Diagram[5]                                                                                                                                    | 60 |

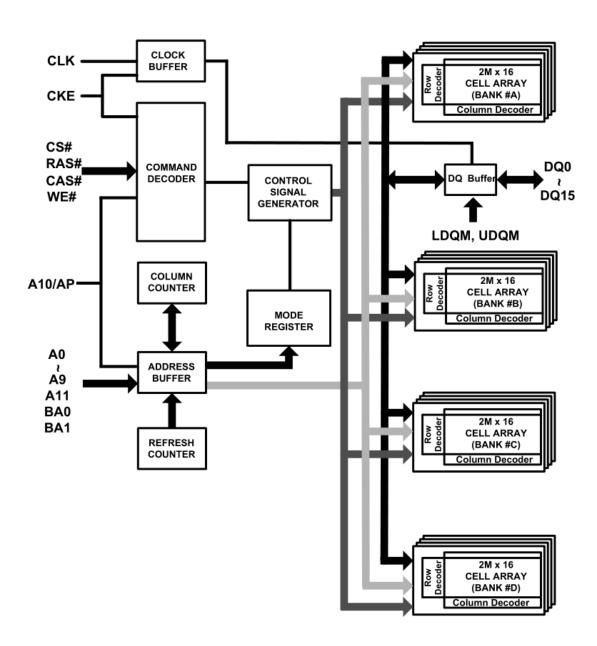

| 4.13 | SDRAM Block Diagram[6]                                                                                                                                   | 62 |

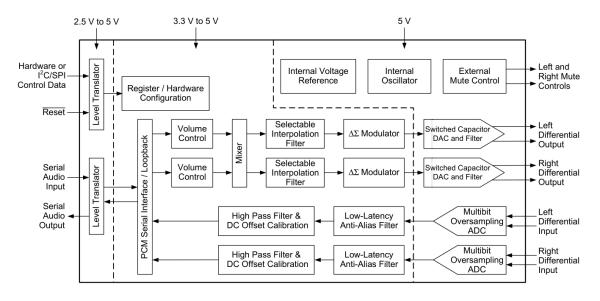

| 4.14 | CS4272 Block Diagram[7]                                                                                                                                  | 64 |

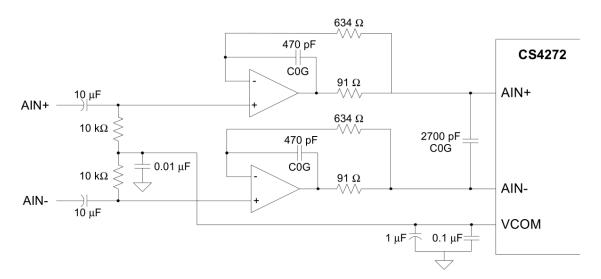

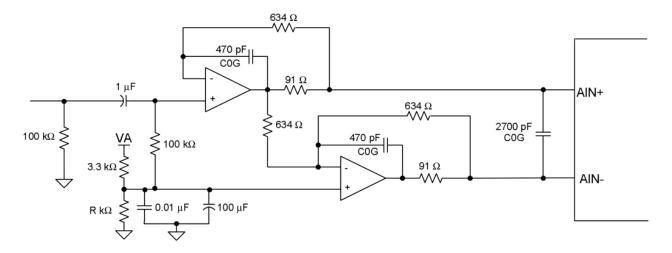

| 4.15 | Fully Differential Input Buffer Circuit[7]                                                                                                               | 66 |

| 4.16 | Single-Ended Input Buffer Circuit[8] $\dots \dots \dots$ | 67 |

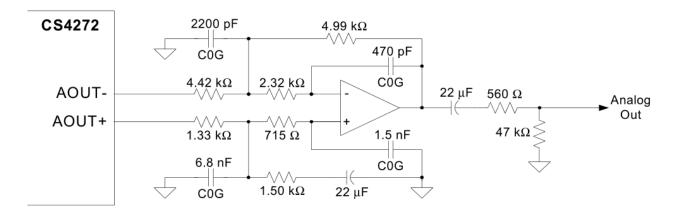

| 4.17 | Differential to Single-Ended Output Buffer[7]                                                                                                            | 68 |

| 4.18 | ADMP401 MEMS microphone break-out board[9]                                                                                                               | 69 |

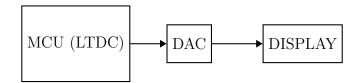

| 4.19 | Overview of designed VGA hardware                                                                                                                        | 71 |

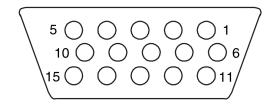

| 4.20 | VGA 15-Pin D-SUB Female Connector[10]                                                                                                                    | 71 |

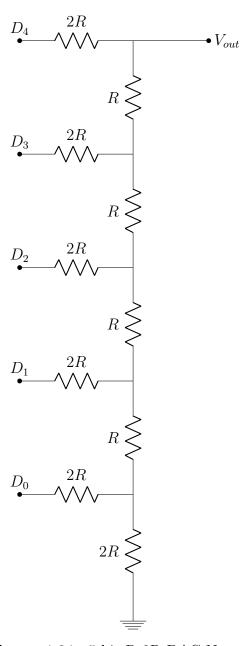

| 4.21 | 5-bit R-2R DAC Network                                                                                                                                   | 73 |

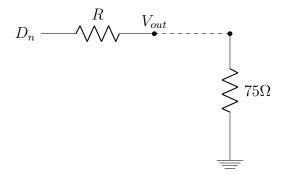

| 4.22 | Reduced Equivalent R-2R DAC connected to $75\Omega$ display monitor                                                                                      | 74 |

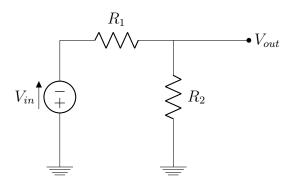

| 4.23 | Potential Divider Circuit                                                                                                                                | 74 |

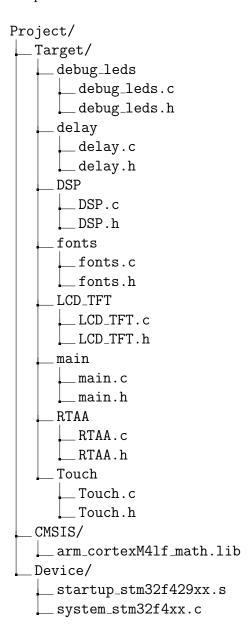

| 5.1  | Real-Time Audio Analyser Firmware Project Directory                                                                                                      | 77 |

| 5.2  |                                                                                                                                                          | 78 |

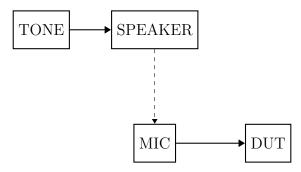

| 6.1  | Audio Test System Overview                                                                                                                               | 92 |

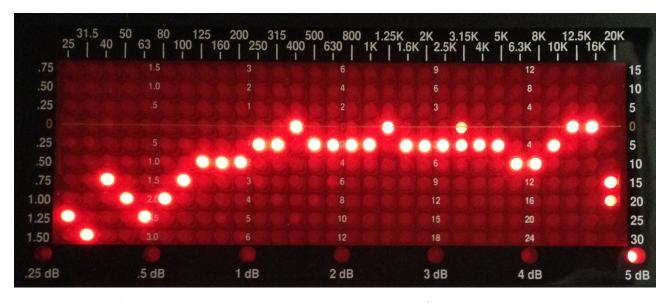

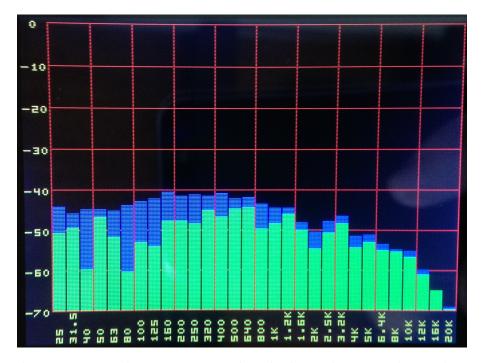

| 6.2  |                                                                                                                                                          | 94 |

| 6.3  | v                                                                                                                                                        | 94 |

| 6.4  | · · · · · · · · · · · · · · · · · · ·                                                                                                                    | 95 |

| 6.5  |                                                                                                                                                          | 96 |

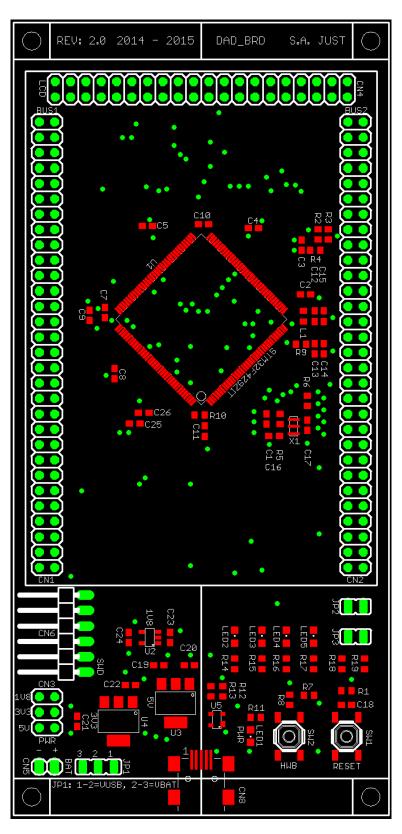

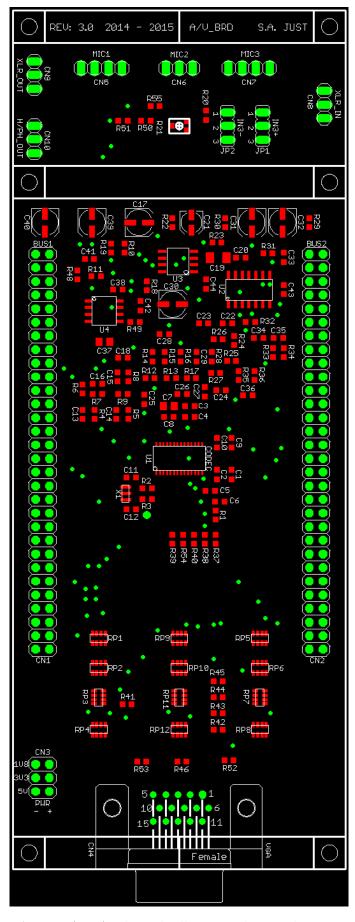

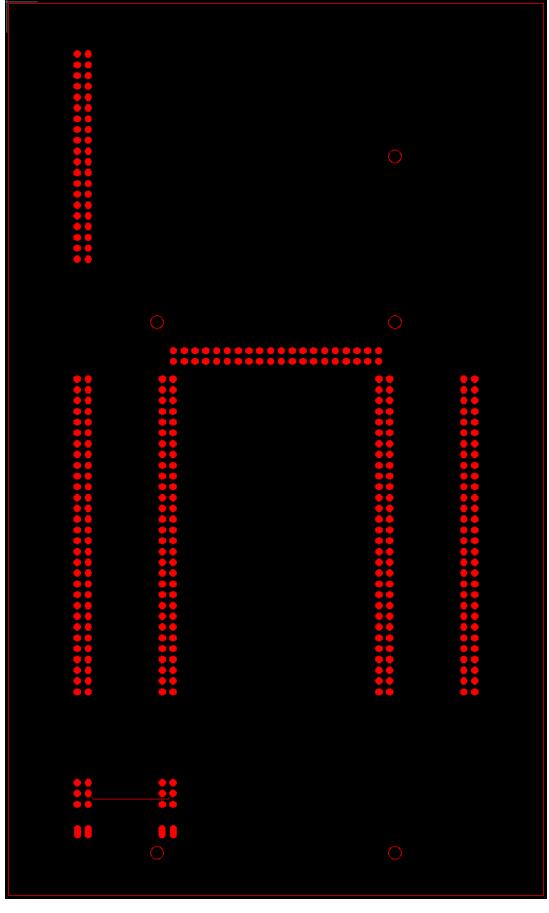

| A.1  | DAD Microcontroller board silkscreen designed using Easily Applicable Graphical                                                                          |    |

|      | Layout Editor (EAGLE)                                                                                                                                    | 02 |

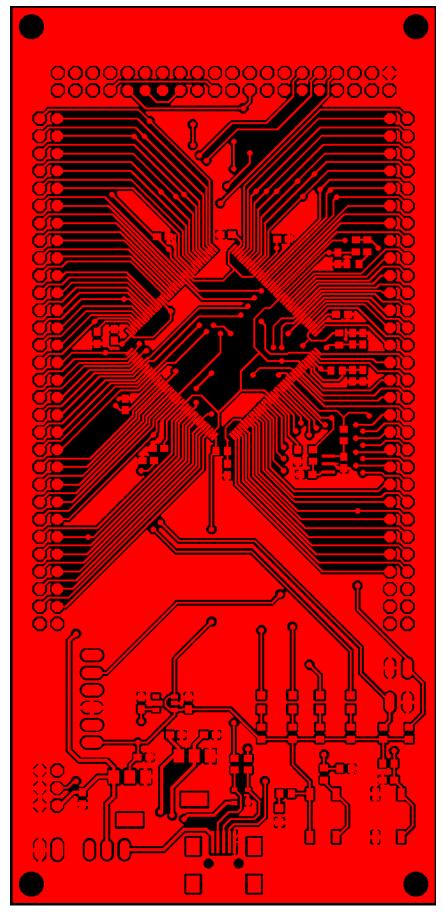

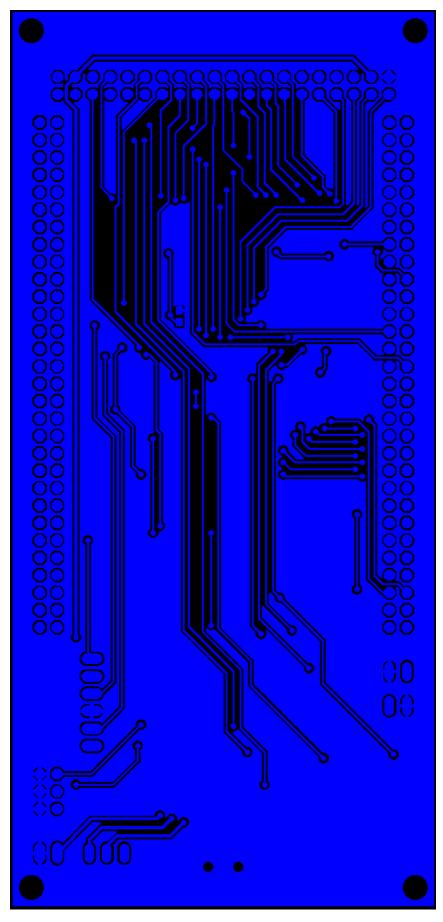

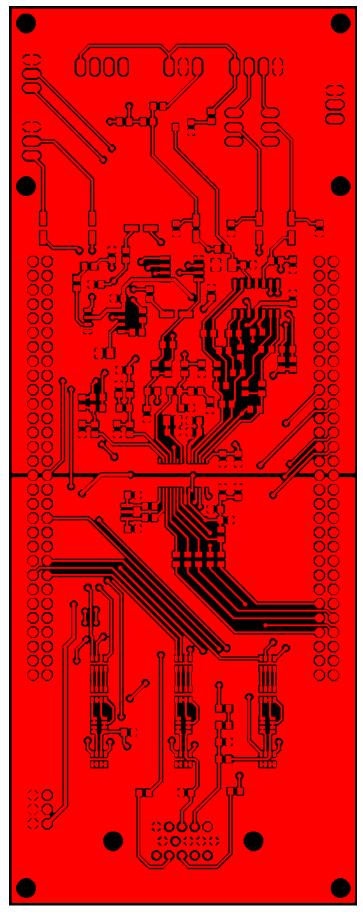

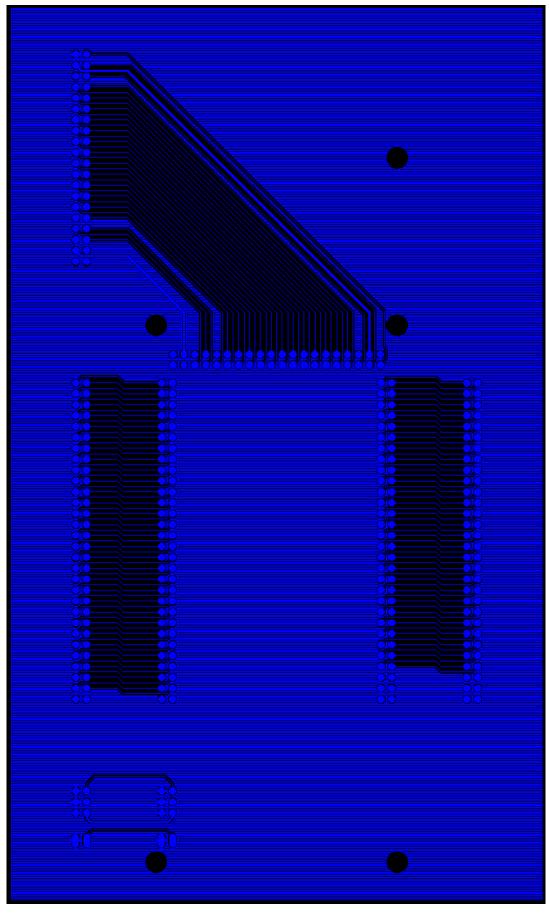

| A.2  | DAD Microcontroller board top layer designed using EAGLE                                                                                                 |    |

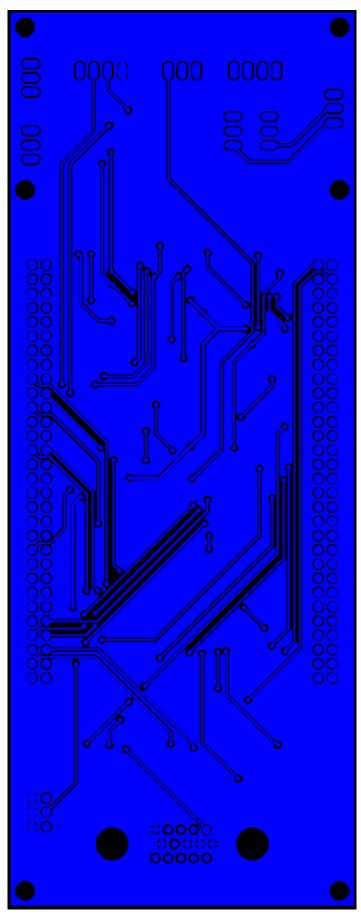

|      | DAD Microcontroller board bottom layer designed using EAGLE                                                                                              |    |

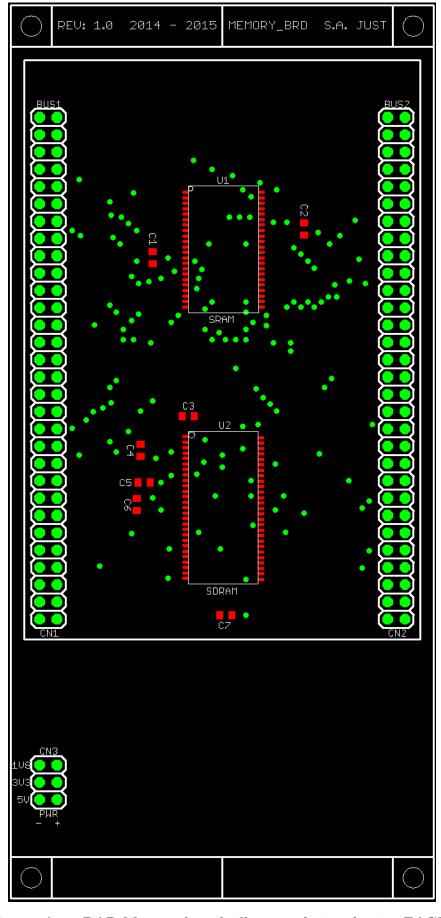

|      | DAD Memory board silkscreen designed using EAGLE                                                                                                         |    |

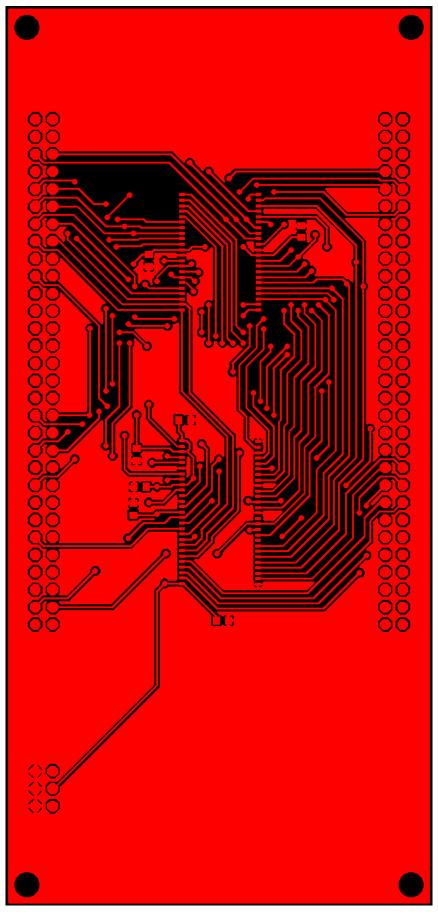

|      | DAD Memory board top layer designed using EAGLE                                                                                                          |    |

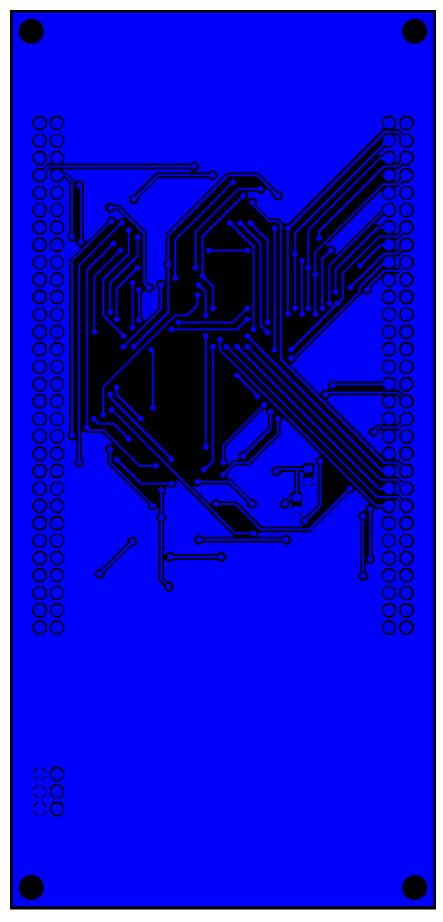

| A.6  | DAD Memory board bottom layer designed using EAGLE                                                                                                       |    |

| A.7  | DAD AV board silkscreen designed using EAGLE                                                                                                             |    |

|      | DAD AV board top layer designed using EAGLE                                                                                                              |    |

|      | DAD AV board bottom layer designed using EAGLE                                                                                                           |    |

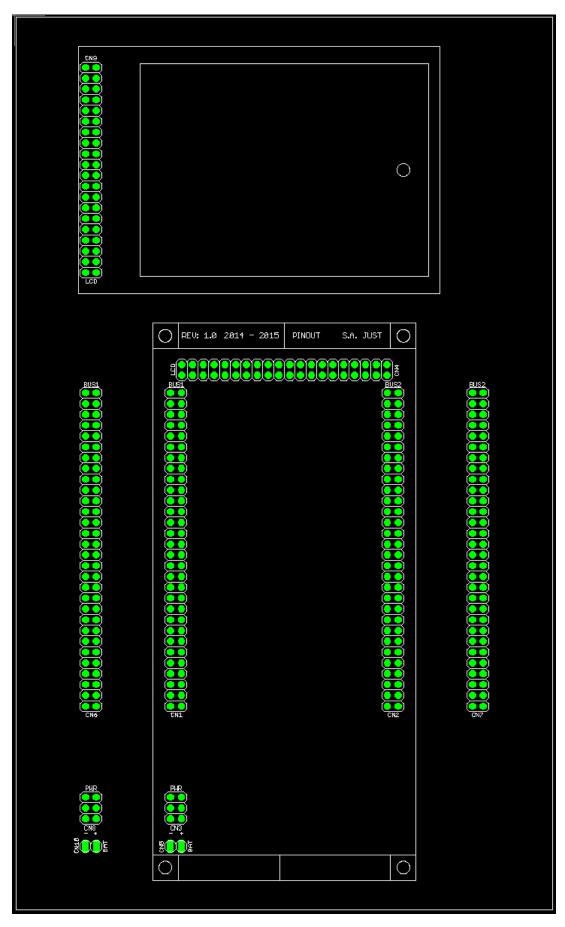

|      | DAD PINOUT board silkscreen designed using EAGLE                                                                                                         |    |

|      | DAD PINOUT board top layer designed using EAGLE                                                                                                          |    |

|      | DAD PINOUT board bottom layer designed using EAGLE                                                                                                       |    |

|      | C928A board silkscreen designed using EAGLE                                                                                                              |    |

|      | C928A board top layer designed using EAGLE                                                                                                               |    |

|      | C928A board bottom layer designed using EAGLE                                                                                                            |    |

|      | MP34DT01 board silkscreen designed using EAGLE                                                                                                           |    |

| _    |                                                                                                                                                          |    |

| List of Figures | X |

|-----------------|---|

|                 |   |

| A.17 MP34DT01 board top layer designed using EAGLE    | . 1 | 18 |

|-------------------------------------------------------|-----|----|

| A.18 MP34DT01 board bottom layer designed using EAGLE | . 1 | 18 |

# **List of Tables**

| 1.1  | Real-Time Audio Analyser System Requirements                                                 | 2   |

|------|----------------------------------------------------------------------------------------------|-----|

| 2.1  | 30 Bands of $\frac{1}{3}$ octave spaced steps calculated using the STM32F429 microcontroller | 10  |

| 2.2  | Types of Fourier Transforms[11]                                                              | 14  |

| 2.3  | Audio Weighting functions for 30 bands of $\frac{1}{3}$ octave spaced steps calculated using |     |

|      | the STM32F429 microcontroller                                                                | 22  |

| 2.4  | Quantization Values for a 12-bit Converter with $3.3V_{FS}$                                  | 31  |

| 2.5  | Quantization Values for a 24-bit Converter with $3.3V_{FS}$                                  | 31  |

| 2.6  | Comparison between the STM32F407 and STM32F429 microcontrollers<br>[12][13]                  | 36  |

| 4.1  | Peripheral Address Organization                                                              | 42  |

| 4.2  | Clock Frequencies used by the Real-Time Audio Analyser                                       | 47  |

| 4.3  | Debugging LEDs on the DAD-MCU-BRD                                                            | 55  |

| 4.4  | SSD1289 Control and Data Pins                                                                | 58  |

| 4.5  | XPT2046 Control and Data Pins                                                                | 59  |

| 4.6  | XPT2046 Control and Data Pins                                                                | 59  |

| 4.7  | AS6C8016 Control and Data Pins                                                               | 61  |

| 4.8  | AS4C8M16S Control and Data Pins                                                              | 63  |

| 4.9  | Internal ADC on DAD-MCU-BRD                                                                  | 64  |

| 4.10 | CS4272 Control Pins                                                                          | 65  |

| 4.11 | CS4272 Serial Audio Data and Clocks                                                          | 65  |

| 4.12 | VGA Connection Pins[10]                                                                      | 71  |

| 4.13 | Liquid-TFT Display Controller (LTDC) RGB565 Digital Video Output $\ \ldots \ \ldots$         | 72  |

| 6.1  | Comparison between the ADMP401 and 6051 microphones<br>[14][15] $\ \ldots \ \ldots \ \ldots$ | 92  |

| A.1  | Bill of Materials for DAD Microcontroller Board                                              |     |

| A.2  | Bill of Materials for DAD MEM Board                                                          | 109 |

| A 3  | Bill of Materials for DAD AV Board                                                           | 113 |

| A.4 | Bill of Materials for DAD PINOUT Board |  |  |  |  |  |  |  |  |  | 117 |

|-----|----------------------------------------|--|--|--|--|--|--|--|--|--|-----|

## Introduction

# 1.1 What are Audio Analysers and How are They Used

An audio analyser is an electronic measurement tool commonly used by acoustic and sound engineers. Audio analysers provide sound engineers with performance measurements of a sound reinforcement system operating within a specific acoustic environment, such as a concert hall, chapel, amphitheatre or sports stadium. A real-time audio analyser is used to view on a display screen the spectrum or frequency response of the individual sound intensities at selected frequencies within the audible frequency range, namely 20Hz - 20kHz. With the aid of a real-time audio analyser the sound engineer can identity common audio related problems such as over-powering low frequencies, or the detection of high frequency feedback from microphones. The spectrum displayed by the real-time audio analyser allows the sound engineer to obtain the best audio frequency response for the environment by either physically repositioning the loudspeakers of the sound system or through the application of signal processing techniques to the audio signal such as equalization. Ultimately the sound engineer should strive to provide a listener with the best possible audio experience for a sound system operating in a given environment and the real-time audio analyser is the go-to tool for many sound engineers.

## 1.2 Motivations for the Research Project

A real-time audio analyser is an essential measurement tool used to assess the sound levels at selected frequencies within the audio frequency range of a sound reinforcement system operating within an environment. The cost of a real-time audio analyser corresponds directly to the quality of the audio analysis. Professional hardware audio analysers cost between \$1000 and \$5000 (Gold Line DSP30[16], Meyer Sound Laboratories SIM 3[17], and Klark Teknik

DN6000[15]). Cheaper yet less sophisticated software implementations can be purchased as software applications ("apps") for smart phones (Apple iPhone, Samsung Galaxy) for a few dollars (\$10 - \$50). While the cheaper software implementations provide a quick and on-the-go analysis, they lack the professional audio signal chain (professional audio converters, suitable analysis microphones and correctly displayed outputs) found primarily in commercial analysers. Hence, professional audio analysers are not a financially viable option for students, academics and undergraduate sound engineers that wish to study and understand the audio spectrum of a signal or sound system.

## 1.3 Research Goal and Objectives

The primary objective of this research project is the design of a low-cost hand-held real-time audio analyser capable of displaying the measured audio spectrum of an audio environment to the user. The audio analyser must accept the audio signal to be analysed using an external microphone level input, a line level input, or a high-quality build-in microphone.

A secondary goal of this research project is to review and remove any non-essential hardware costs. The costly LCD screen could be removed and an alternative output viewing display could be developed such as the common Video Graphics Array (VGA) interface. The removal of non-essential hardware costs may allow other hardware features to be incorporated into the audio analyser such as professional 24-bit audio data converters, additional external memory, and/or environment sensors.

The final goal of this project to provide sound educators, audio technicians and engineers with an alternative low-cost real-time audio analysis solution to the currently commercially audio analysis solutions.

In summary, the system requirements are shown in Table 1.1:

| System Parameter     | Requirement            |

|----------------------|------------------------|

| Real Data Input Rate | $\geq 48 \text{ kHz}$  |

| Number of Input Bits | $\geq 12 \text{ bits}$ |

| Product Size         | Small (Hand-held)      |

| Power Supply         | Low (1.8V-5V)          |

| Cost                 | Low                    |

| Input Source         | Analogue (Microphone)  |

| Output Display       | Digital (LCD/VGA)      |

**Table 1.1:** Real-Time Audio Analyser System Requirements

It should be noted that there is no clear cut rule or definition as how both the product size and costs are quantified - at least for the purpose of this research project. There is a sense in vagueness which could be open for interpretation as how one can quantify and measure a product cost or product size. Nevertheless, the aim of the designed real-time audio analyser is to be minimal in size and to reduce as much as possible the costs of the product.

## 1.4 Research Approach

This thesis addresses the development of a low-cost real-time audio analyser in five phases. The five separate phases highlight a developmental plan followed for the implementation of an inexpensive yet dependable real-time audio analysis tool.

- Phase 1 Research, Theory, and Literature Review

- Phase 2 Design of Hardware

- Phase 3 Development of Firmware

- Phase 4 Implementation of the Real-Time Audio Analyser (RTAA)

- Phase 5 Investigation and Implementation of Possible Improvements

Each phase provides a clear overview of the path followed by the author in this research project and a full schedule followed by the author during this research project can be obtained upon request.

#### 1.4.1 Phase 1 - Research, Theory and Literature Review

Electronic device manufacturers are often reluctant to reveal the complete inner circuits, workings and schematics of their implemented designs. The first phase is developing an understanding of problem by reviewing previously developed algorithms, techniques and implementations of measuring an audio signal and displaying the correct and desired audio spectrum. Research into the various specifications and features of previously successful implemented audio analyser designs provided an insight into the requirements of a correctly displayed audio spectrum output.

#### 1.4.2 Phase 2 - Design of Hardware

The second phase in the development of a real-time audio analyser is the review of the hard-ware guidelines from the microcontroller manufacturer and research into the additional external peripheral components such as analogue-to-digital converters (ADC), external memory implementations and different output display options.

The three additional external memory devices that are of interest are:

- Secure Digital Card (SD-Card)

- Static Random Access Memory (SRAM)

- Synchronous Dynamic Random Access Memory (SDRAM)

The two output display devices that are of interest are:

- Thin-Film Transistor Liquid-Crystal Display (TFT-LCD)

- Video Graphics Array (VGA)

#### 1.4.3 Phase 3 - Development of Firmware

The third phase is the development of a suitable digital signal processing algorithm capable of processing an input audio signal from the designed hardware. Once the hardware has buffered and digitised the analogue audio signal, the microcontroller will process the sampled audio signal and output the correctly formatted audio spectrum to the selected display device for interpretation by the user.

### 1.4.4 Phase 4 - Implementation of the RTAA

The fourth phase combines the designed hardware with the developed firmware algorithms and implements a working prototype for analysing an audio signal such as test audio tones and signals. The implemented real-time audio analyser will also be compared to a commercially available solution using a standard pure tone audio signal and a pink noise audio signal.

#### 1.4.5 Phase 5 - Investigate Possible Improvements

The fifth and final phase discusses both pitfalls and improvements for the designed, developed, and implemented real-time audio analyser. In an ideal world the design, development and implementation of an electronic device such as a real-time audio analyser would undergo several hardware and firmware revisions prior to being made available on the market. Ideally the final electronic device should provide a complete fault-free and bug-free solution to the customer or client.

#### 1.5 Thesis Structure

This thesis is structured in a similar - yet not completely identical - manner to the problem approach with each chapter closely linking each phase. Included in this thesis are several appendices that provide additional background on the digital communication protocols, digital signal processing techniques as well as the final designed schematics, printed circuit boards, and developed firmware code. Moreover, various electronic component datasheets, audio technical manuals, digital signal processing text-books, articles and technical standards are included in a single reference list. A list of both international and local electronic vendors used to complete this research project is provided. Finally, a list of acronyms used in this thesis is included.

# Theory and Literature Review

The objective of this chapter is to give the reader some insight into the required background knowledge of the underlying audio theory, research into signal processing algorithms and investigation of electronic hardware. While all attempts have been made to keep this chapter as simple and as concise as possible, the less subtle and more mathematical aspects of the calculations can be obtained from the author upon request.

## 2.1 Audio Signals and Systems

The properties of sound and the propagation of sound waves through different mediums and environments are well studied in undergraduate physics or applied mathematics. The theory of longitudinal and transverse waves, vibrational physics and even fluid mechanics all provide the framework, theory and models of the fundamental transfer of vibrational energy or rather information through a medium. The analogue representation of an audio signal consisting of currents, voltages, powers and intensities have been explored and experimented for over a century. The digital representation of an audio signal consisting of digital clocks, sampled and binary logic data has been leading the professional audio industry as a new standard in the last few decades.

## 2.1.1 Types of Audio Signals

An analogue audio signal is measured with a transducer such as a microphone which converts the changes in sound pressure level into an electrical voltage. An audio signal sound pressure level is described as a function over the independent continuous-time variable t and is denoted x(t). A digital audio signal is expressed over the independent time discrete-time variable n and is denoted x[n]. Moreover, for a digital signal both the independent variables and the dependent variables are discrete, i.e. both time and amplitude [18].

There are two main types of audio signals:

- Periodic Signals

- Non-Periodic Signals (Random Signals)

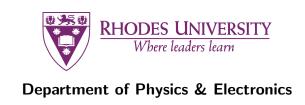

As an example, a pure test tone is a periodic signal and is given in Figure 2.1.

Figure 2.1: Periodic 100Hz test tone signal calculated and plotted using MATLAB

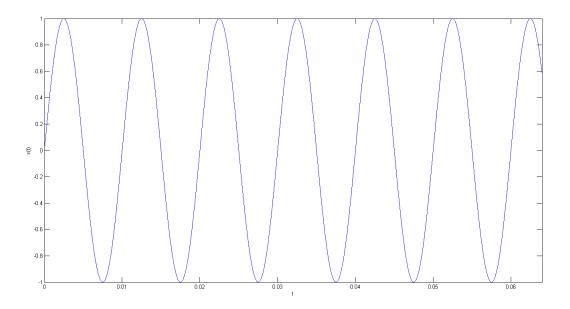

An example of a non-periodic random noise signal is given in Figure 2.2.

Figure 2.2: Non-periodic random noise signal calculated and plotted using MATLAB

Audio engineers are concerned with three main types of noise and each are attributed to a colour: White, Pink, and Black. The power of a noise signal can be expressed as a homogeneous power-law with a frequency dependence and is given by [19]:

$$P_{noise} \propto f^{-\beta}$$

(2.1)

where  $P_{noise}$  is the power of the noise signal, f is the frequency, and  $\beta$  is a constant.

#### 2.1.2 White Noise

White noise consists of constant and equal energy per frequency bandwidth[20]. The power spectrum of white noise is constant or 0dB/octave (0dB/decade) on a linear scale and therefore when analysed with a constant-Q audio analyser the display exhibits an increase by 3dB/octave (10dB/decade)[20].

The power of white noise can be expressed with the power law relation where  $\beta = 0$  and is given by [19]:

$$P_{whitenoise} \propto f^{-\beta}$$

(2.2)

$$\propto f^{-0} \tag{2.3}$$

$$\propto 1$$

(2.4)

### 2.1.3 Pink Noise

Pink noise consists of constant and equal energy per octave [20]. The power spectrum of pink noise decreases by 3dB/octave (10dB/decade) on a linear scale and therefore when analysed with a constant-Q audio analyser the display exhibits a flat spectrum [20].

The power of pink noise can be expressed with the power law relation where  $\beta = 1$  and is given by [19]:

$$P_{pinknoise} \propto f^{-\beta}$$

(2.5)

$$\propto f^{-1} \tag{2.6}$$

$$\propto \frac{1}{f}$$

(2.7)

Pink noise can be generated by passing white noise through a filter that has a transfer function given by [21]:

$$H(s) = \frac{K}{\sqrt{s}} \tag{2.8}$$

where K is an arbitrary constant.

The frequency response function for Pink noise is given by [21]:

$$H(j\omega) = \frac{K}{\sqrt{j\omega}} \tag{2.9}$$

$$=\frac{K}{\sqrt{\omega}}e^{-j\frac{\pi}{4}}\tag{2.10}$$

where K is an arbitrary constant.

#### 2.1.4 Black Noise

Black noise is often neglected and overlooked in the family of noise colours. Black noise is quite simply silence [20] and consists of zero energy per frequency.

The power of black noise can be expressed with the power relation where  $\beta > 2[19]$ . As an example, the power of black noise can be expressed with the power law relation where  $\beta = 3$  and is given by [19]:

$$P_{blacknoise} \propto f^{-\beta}$$

(2.11)

$$\propto f^{-3} \tag{2.12}$$

$$\propto \frac{1}{f^3} \tag{2.13}$$

#### 2.1.5 Audio Equalization

Audio equalization is a process used to alter the frequency response of an audio signal with the use of signal processing techniques such as passing an audio signal through a system of linear filters.

A graphic equalizer allows the sound engineer to add (boost) and/or remove (cut) frequency bands from an input audio signal. A graphic equalizer can be modelled as bank of bandpass filters spread across a logarithmically spaced audio frequency range with a centre frequency  $f_0$ , and a bandwidth B. The relationship between the bandwidth B, the range of applicable frequencies,  $f_1$  and  $f_2$ , and the centre frequency  $f_0$  is termed the quality factor, Q. The quality factor is given by the following equation:

$$Q = \frac{f_0}{B} \tag{2.14}$$

$$=\frac{f_0}{f_2-f_1}\tag{2.15}$$

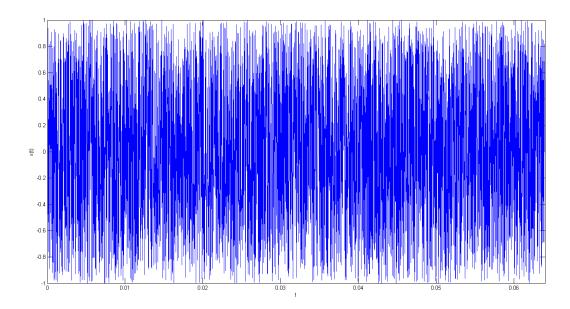

An example of an audio graphic equalizer is the DN360 manufactured by Klark Teknik and is shown in Figure 2.3. The DN360 audio graphic equalizer is a dual channel, 30 band equalizer featuring up to 12dB of cut/boost for frequencies between 25Hz and 20kHz in  $\frac{1}{3}$  octave steps[1].

**Figure 2.3:** Front view of DN360  $\frac{1}{3}$  octave graphic equaliser[1]

The frequency spacing is non-linear yet repetitive with a constant quality factor for each bandpass filter. The centre frequencies for the 30 bands of  $\frac{1}{3}$  octave spaced frequency steps are determined according to an international standard. For the purposes of this academic research project a series of out-dated standards were viewed and are referenced appropriately.

The relationship between the centre frequency  $f_{cent}$ , the higher  $f_{high}$ , and lower  $f_{low}$  boundary or bandedge frequencies is given by the ANSI S1.11-2004: Specification for Octave-Band and Fractional-Octave-Band Analog and Digital Filters[22]. There are two octave ratio's specified in the ANSI S1.11-2004 document, namely, the base-10 ratio:

$$G_{10} = 10^{\frac{3}{10}} \approx 1.9953 \tag{2.16}$$

and the base-2 ratio:

$$G_2 = 2 \tag{2.17}$$

The base-10 system is preferred[22]. Once a system base ratio has been chosen the centre frequency,  $f_{cent}$ , and bandedge frequencies,  $f_{low}$  and  $f_{high}$ , can be calculated for a reference frequency,  $f_{ref}$ , with the fraction of an octave band defined by the bandwidth designator,  $\frac{1}{B}$ .

For a reference frequency  $f_{ref} = 1000kHz$ , the band centre frequency  $f_{cent}$  and the bandedge frequencies can be calculated for each band, x, with a  $\frac{1}{3}$  bandwidth designator by[22]:

$$f_{cent}(x) = (G^{\frac{x-16}{B}})f_{ref}$$

(2.18)

$$f_{low}(x) = (G^{-\frac{1}{2B}})(f_{cent}(x))$$

(2.19)

$$f_{high}(x) = (G^{+\frac{1}{2B}})(f_{cent}(x))$$

(2.20)

where  $0 \le x < 10 \times B$  and B = 3.

The 30 band  $\frac{1}{3}$  octave spaced centre frequencies with bandedge frequencies are given in Table 2.1.

| $\mathbf{n}$ | Low Freq (Hz) | Centre Freq (Hz) | High Freq (Hz) | Bandwidth (Hz) | Q    |

|--------------|---------------|------------------|----------------|----------------|------|

| 0            | 22.10         | 24.80            | 27.84          | 5.74           | 4.32 |

| 1            | 27.84         | 31.25            | 35.08          | 7.24           | 4.32 |

| 2            | 35.08         | 39.37            | 44.19          | 9.12           | 4.32 |

| 3            | 44.19         | 49.61            | 55.68          | 11.49          | 4.32 |

| 4            | 55.68         | 61.50            | 70.15          | 14.47          | 4.32 |

| 5            | 70.15         | 78.75            | 88.39          | 18.23          | 4.32 |

| 6            | 88.39         | 99.213           | 111.36         | 22.97          | 4.32 |

| 7            | 111.36        | 125.00           | 140.31         | 28.95          | 4.32 |

| 8            | 140.31        | 157.49           | 176.78         | 36.47          | 4.32 |

| 9            | 176.78        | 198.43           | 222.72         | 45.95          | 4.32 |

| 10           | 222.72        | 250.00           | 280.62         | 57.89          | 4.32 |

| 11           | 280.62        | 314.98           | 353.55         | 72.94          | 4.32 |

| 12           | 353.55        | 396.85           | 445.45         | 91.90          | 4.32 |

| 13           | 445.45        | 500.00           | 561.23         | 115.78         | 4.32 |

| 14           | 561.23        | 629.96           | 707.11         | 145.88         | 4.32 |

| 15           | 707.11        | 793.70           | 891.00         | 183.79         | 4.32 |

| 16           | 891.00        | 1000.00          | 1122.46        | 231.56         | 4.32 |

| 17           | 1122.46       | 1259.92          | 1414.21        | 291.75         | 4.32 |

| 18           | 1414.21       | 1587.40          | 1781.80        | 367.58         | 4.32 |

| 19           | 1781.80       | 2000.00          | 2244.92        | 463.13         | 4.32 |

| 20           | 2244.92       | 2519.84          | 2828.43        | 583.50         | 4.32 |

| 21           | 2828.43       | 3174.80          | 3563.59        | 735.17         | 4.32 |

| 22           | 3563.59       | 4000.00          | 4489.85        | 926.25         | 4.32 |

| 23           | 4489.85       | 5039.68          | 5656.85        | 1167.01        | 4.32 |

| 24           | 5656.85       | 6349.60          | 7127.19        | 1470.34        | 4.32 |

| 25           | 7127.19       | 8000.00          | 8979.70        | 1852.51        | 4.32 |

| 26           | 8979.70       | 10079.37         | 11313.71       | 2334.01        | 4.32 |

| 27           | 11313.71      | 12699.21         | 14254.38       | 2940.67        | 4.32 |

| 28           | 14254.38      | 16000.00         | 17959.39       | 3705.01        | 4.32 |

| 29           | 17959.39      | 20158.74         | 22627.42       | 4668.02        | 4.32 |

**Table 2.1:** 30 Bands of  $\frac{1}{3}$  octave spaced steps calculated using the STM32F429 microcontroller

#### 2.1.6 The Human Auditory System

The human hearing system provides a pathway from the external body world through a system of membrane tissues (outer ear), mechanical bone levers (middle ear) and auditory nerve transducer (inner ear) to the brain. The separation of the human hearing system into three distinct different functions provides additional insight into the complex mechanisms with which a listener hears an incoming audio signal from the external environment. Each stage of the human auditory system analyses the audio signal for specific audio properties such as the location of the incoming audio source, the distinct frequency components and the perceived loudness of the audio sound. The complex audio processing by the human hearing system provides the often misguided view that the frequency components are analysed in linearly spaced frequency bands and at equally perceived loudness over the audio spectrum (20Hz - 20kHz).

#### 2.1.7 Equivalent Sound Level Addition

In the ideal scenario, an incoming sound wave does not reflect and interact with objects within the environment and arrives at the listener as a single correlated audio source. In the practical scenario, an incoming sound wave reflects and interacts with objects within the environment resulting in a natural reverberation audio effect on the sound signal which may be interpreted by the human hearing system as a single uncorrelated source. The two different ways of adding and interpreting audio levels from separate sound sources are termed as coherent or correlated level addition, and incoherent or uncorrelated level addition.

#### 2.1.7.1 Coherent and Correlated Audio Sources

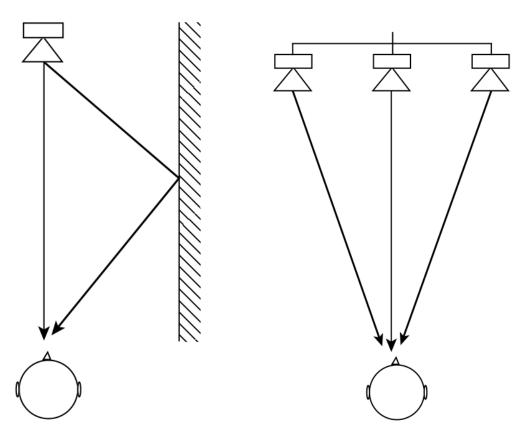

An audio source is termed **coherent** or **correlated** with other audio sources if there is either a negligible timing difference between the sources or if the point of origination for each audio source is singular[23]. Figure 2.4 illustrates a coherent or correlated audio source. An audio wave produced by a single source reflects and interacts with the environment producing a negligible time delay or reverberation effect. Moreover, a single audio source which is then split into multiple audio sources such as a public address system or live sound reinforcement system is also considered to be correlated[2].

- (a) Correlation due to reflection

- (b) Correlation due to multiple sources

Figure 2.4: Addition of correlated audio sources[2]

A set of coherent or correlated audio sources can be very crudely considered to be a set of very

much the same source with identical frequencies and phase differences. The sum or addition of several coherent or correlated audio sources,  $L_{corr}$ , is given by:

$$L_{corr} = L_1 + \dots + L_N \tag{2.21}$$

All the individual coherent or correlated sources have the same frequency and a minimal phase difference to other audio sources. A special case of coherent or correlated audio sources exists if each source is of the same level L. The equation for coherent or correlated addition simplifies as follows:

$$L_{corr} = L_1 + \dots + L_N \tag{2.22}$$

$$= L + \dots + L \qquad (N \text{ times}) \tag{2.23}$$

$$= L \times N \tag{2.24}$$

#### 2.1.7.2 Incoherent and Uncorrelated Audio Sources

An audio source is termed **incoherent** or **uncorrelated** with other audio sources if there is either a significant timing difference between the audio sources or if the point of origination for each audio source is non-singular[23]. Figure 2.5 illustrates an incoherent or uncorrelated audio source. An audio wave produced by a single source reflects and interacts with the environment producing a significant time delay or reverberation effect. Moreover, a set of multiple audio sources consisting of set of distinct audio waves such as a choir or musical instruments arriving at a singular point is also considered to be uncorrelated[2].

- (a) Uncorrelated reflection due to long delay

- (b) Uncorrelated multiple sources

Figure 2.5: Addition of uncorrelated audio sources[2]

A set of incoherent or uncorrelated audio sources can be very crudely considered to be a set of distinct or unrelated audio sources with different frequencies and phase differences. The sum or addition of several incoherent or uncorrelated audio sources,  $L_{uncorr}$ , is given by:

$$L_{uncorr} = \sqrt{\left((L_1)^2 + \dots + (L_N)^2\right)}$$

(2.25)

All the individual incoherent or uncorrelated sources have different frequencies and phase differences to other audio sources. A special case of incoherent or uncorrelated audio sources exists if each source is of the same level L. The equation for incoherent or uncorrelated addition simplifies as follows:

$$L_{uncorr} = \sqrt{(L_1)^2 + \dots + (L_N)^2}$$

(2.26)

$$= \sqrt{(L)^2 + \dots + (L)^2} \tag{2.27}$$

$$= \sqrt{L^2 \times N} \qquad (N \text{ times}) \tag{2.28}$$

$$=L\sqrt{N}\tag{2.29}$$

#### 2.2 Fourier Transformations

The Fourier Transformations presented here are by no means the only mathematical transformations that were investigated during the research in audio signal processing techniques. Two examples of such transformations are the Hartley Transform and the Constant-Q Transform, both very similar yet very different to the presented Fourier Transforms. Moreover, the Fourier Transforms are primarily useful for quasi-static or stationary signals. Therefore, the analysis of a chirp signal using the Fourier Transforms directly provides very little information on the change in frequency of the signal over a time duration. Alternative techniques such as time-frequency transformations were briefly explored however additional future research will be required to implement a time-frequency display such as an audio spectrogram or waterfall spectrum.

### 2.2.1 Continuous-Time Fourier Transform (CTFT)

The Continuous-Time Fourier Transform (CTFT) is the formal mathematical description for the continuous frequency-domain spectrum of a continuous-time signal x(t).

The CTFT of the continuous-time signal  $x_c(t)$  is defined as follows[11]:

$$X_c(j\omega) = \int_{-\infty}^{+\infty} x_c(t)e^{-j\omega t} dt$$

(2.30)

## 2.2.2 Discrete-Time Fourier Transform (DTFT)

The Discrete-Time Fourier Transform (DTFT) is a continuous frequency-domain representation of the discrete-time signal x[n].

The DTFT of the discrete-time signal x[n] is defined by [11]:

$$X(e^{j\hat{\omega}}) = \sum_{n=-\infty}^{+\infty} x[n]e^{-j\hat{\omega}n}$$

(2.31)

where  $\hat{\omega}$  is a continuous-frequency variable and  $X(e^{j\hat{\omega}})$  is periodic with period  $2\pi$ .

The discrete-time sequence x[n] can be obtained by sampling a continuous-time signal  $x_c(t)$  with a sampling period  $T_s$  by:

$$x[n] = x_c(nT_s) (2.32)$$

## 2.2.3 Discrete Fourier Transform (DFT)

The Discrete Fourier Transform (DFT) is a discrete frequency-domain representation of the discrete-time sequence x[n].

The DFT of the discrete-time finite-duration sequence x[n] is defined as follows[11]:

$$X[k] = \sum_{n=0}^{N-1} x[n]e^{-\frac{2\pi nk}{N}}$$

(2.33)

where  $0 \le k \le N - 1$ .

Alternatively, the DFT of the discrete-time finite-duration sequence x[n] can be defined by:

$$X[k] = \sum_{n=0}^{N-1} x[n]W_N^{nk}$$

(2.34)

where  $W_N^{nk}=e^{-\frac{j2\pi nk}{N}}=\cos\left(\frac{2\pi nk}{N}\right)-j\sin\left(\frac{2\pi nk}{N}\right)$  and  $0\leq k\leq N-1$ .

It should be noted that the frequency domain for the result of an N-point DFT applied to a sampled discrete-time finite-duration sequence can be determined by:

$$f_i = \frac{Sample\ Rate}{Sample\ Size} \times i \tag{2.35}$$

Thus, the frequency divisions are dependent on both the rate of the sampled data and the total number of data samples.

Table 2.2 illustrates the differences between the Fourier Transformations, namely the Continuous-Time Transform (CTFT), Discrete-Time Fourier Transform (DTFT), and the Discrete Fourier Transform (DFT).

|                      | Discrete-Time                | Continuous-Time           |

|----------------------|------------------------------|---------------------------|

| Discrete-Frequency   | DFT, $X[k]$                  | Fourier Series, $\{a_k\}$ |

| Continuous-Frequency | DTFT, $X(e^{j\hat{\omega}})$ | CTFT, $X_c(j\omega)$      |

**Table 2.2:** Types of Fourier Transforms[11]

### 2.3 Filters

The filters presented here have been coded appropriately and are features of the implemented real-time audio analyser. Data windowing functions are commonly studied in digital signal processing courses and are a necessity when analysing digitally sampled signals. Audio weighting filters are found in many audio analysing devices such as an audio analyser and are a necessity when analysing a audio signals.

#### 2.3.1 Digital Signal Processing Windows

A digital signal processing window w[n] is a weighting function that is multiplied with an input digital signal x[n] prior to computing the discrete fourier transform (DFT) of the windowed input signal  $x_w[n]$ .

$$x_w[n] = x[n] \times w[n] \tag{2.36}$$

where  $0 \le x \le N - 1$ .

The application a window to the input sample results in the reduction of the side-lobes and a widening of the main lobe without altering the centre frequency of each DFT filter[24]. Extensive research has been done on various types and flavours of digital windowing functions[25] and those featured on the implemented real-time audio analyser are discussed in more detail.

It should be noted that the digital window functions are used as a mechanism to smooth the audio signal before performing the audio analysis. The digital audio signal is analysed in short time intervals which is governed by the sampling rate frequency of the analogue to digital converter. The application of a window function to the sampled audio signal results in the suppression of the distant samples and highlights the central samples in the short time interval.

#### 2.3.1.1 Rectangular Window

The most fundamental window is the rectangular (or boxcar) window which does not alter the windowed input signal in any manner. The rectangular window is given by:

$$w[n] = 1 \tag{2.37}$$

where  $0 \le n \le N - 1[24]$ .

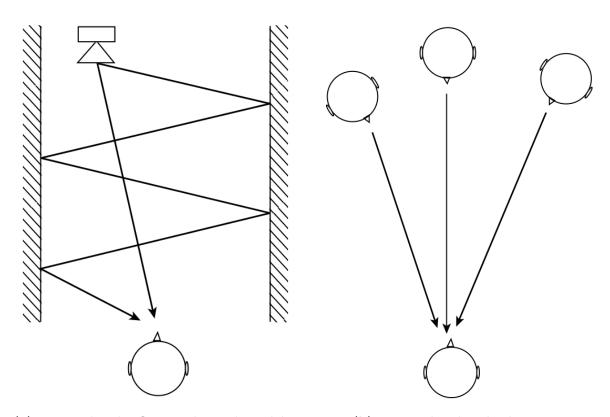

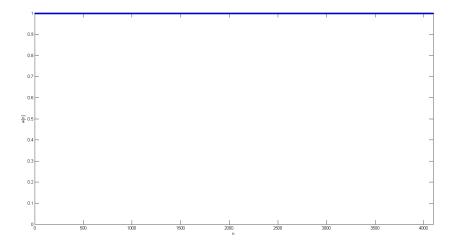

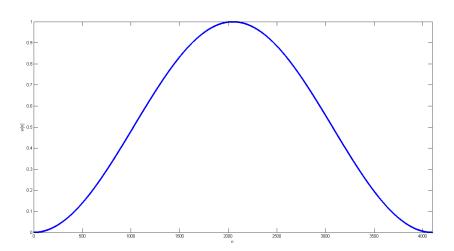

The rectangular window is given in Figure 2.6 for 4096 data points.

**Figure 2.6:** Rectangle window function for 4096 data points calculated and plotted with MATLAB

#### 2.3.1.2 Hanning Window

The Hanning window is given by:

$$w[n] = \frac{1}{2} \left( 1 - \cos\left(\frac{2n\pi}{N}\right) \right) \tag{2.38}$$

where  $0 \le n \le N - 1[24]$ .

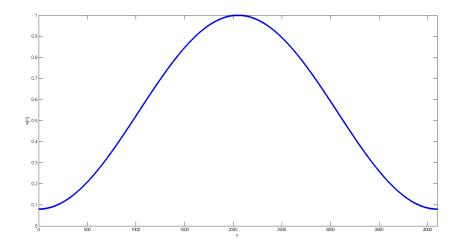

The Hanning window is given in Figure 2.7 for 4096 data points.

**Figure 2.7:** Hanning window function for 4096 data points calculated and plotted with MAT-LAB

#### 2.3.1.3 Hamming Window

The Hamming window is given by:

$$w[n] = 0.54 - 0.46\cos\left(\frac{2n\pi}{N}\right) \tag{2.39}$$

where  $0 \le n \le N - 1[24]$ .

The Hamming window is given in Figure 2.8 for 4096 data points.

**Figure 2.8:** Hamming window function for 4096 data points calculated and plotted with MATLAB

#### 2.3.1.4 Welch Window

The Welch window is given by:

$$w[n] = 1 - \left(\frac{n - \frac{N}{2}}{\frac{N}{2}}\right)^2 \tag{2.40}$$

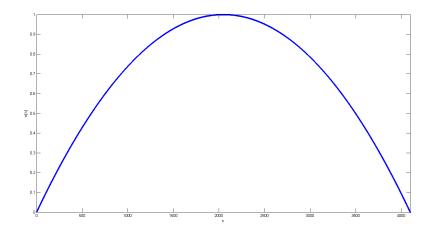

where  $0 \le n \le N - 1[26]$ .

The Welch window function is given in Figure 2.9 for 4096 data points.

Figure 2.9: Welch window function for 4096 data points calculated and plotted with MATLAB

#### 2.3.1.5 Bartlett Window

The Bartlett window is given by:

$$w[n] = 1 - \left| \frac{n - \frac{N}{2}}{\frac{N}{2}} \right| \tag{2.41}$$

where  $0 \le n \le N - 1[26]$ .

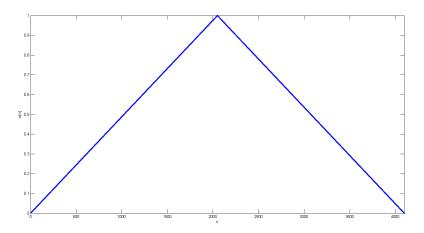

The Bartlett window is given in Figure 2.10 for 4096 data points.

**Figure 2.10:** Bartlett window function for 4096 data points calculated and plotted with MATLAB

#### 2.3.1.6 Blackman Window

The Blackman window is given by:

$$w[n] = 0.42 - 0.50 \left(\cos\left(\frac{2\pi n}{N}\right)\right) + 0.08 \left(\cos\left(\frac{4\pi n}{N}\right)\right)$$

(2.42)

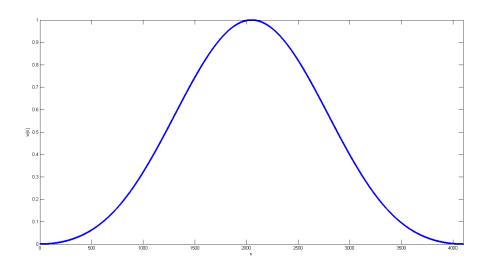

where  $0 \le n \le N - 1[24]$ .

The Blackman window is given in Figure 2.11 for 4096 data points.

**Figure 2.11:** Blackman window function for 4096 data points calculated and plotted with MATLAB

It should be noted that while only six data windowing functions have been presented here, there are many others types such as Gaussian, Kasier, and Dolph-Chebyshev. The Rectangle, Hanning, Hamming, Welch, Bartlett and Blackman windows are the most common data windowing functions found in digital signal analysers as well as being the most common studied by students in a digital signal precessing course.

#### 2.3.2 Audio Weighting Filters

Ultimately the listener will use their ears - the human auditory system - to hear an audio signal or source. Audio measuring devices such as a real-time audio analyser are often designed with the underlying principle of providing a linear frequency response. As a result, an additional weighting filter is commonly applied to the results of an audio analysis which in turn compensates for the non-linearity of the human auditory system. The audio signal is first passed through an appropriate weighting-filter before the root mean square (RMS) or peak value is calculated[27].

From a signal processing point of view, a Linear Time-Invariant (LTI) system or filter can be characterised by its Transfer Function (TF) in the the analogue s-domain or corresponding digital z-domain. The transfer function for each weighting filter can be determined from the contents of the logarithm in the filter weighting level equation and by expressing the frequency f as an angular frequency  $\omega = 2\pi f$  and units rad/s.

Each weighting filter has a characteristic pole-zero graphical representation, also called a complex plane pole-zero plot. The pole-zero plot for each weighting filter can be viewed as a flat rubber sheet spanning infinitely on the flat 2-D plane. The flat rubber sheet is initially raised in the z-axis by a fixed constant value:  $K_A$ ,  $K_B$ ,  $K_C$ . A pole placed at a particular point underneath the flat rubber sheet will cause the previously flat transfer function to be altered and attenuate certain frequencies:  $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$ ,  $f_5$ . A zero placed at a particular point fixes or nails the flat rubber sheet to remain unaltered while points around the zero are free to be altered by any neighbouring poles.

#### 2.3.2.1 A-Weighting

The most common audio frequency weighting filter is the A-weighting filter and is given by [28]:

$$W_A(f) = 20 \log \left( \frac{f_4^2 f^4}{(f^2 + f_1^2)(f^2 + f_2^2)^{\frac{1}{2}} (f^2 + f_3^2)^{\frac{1}{2}} (f^2 + f_4^2)} \right) + K_A$$

(2.43)

where  $K_A = 1.9997$ ,  $f_1 = 20.598997 Hz$ ,  $f_2 = 107.65265 Hz$ ,  $f_3 = 737.86223 Hz$ , and  $f_4 = 12194.22 Hz$ .

The transfer function for the A-weighting filter is given by [29]:

$$H_A(s) = \frac{\omega_4^2 s^4}{(s + \omega_1)^2 (s + \omega_2)(s + \omega_3)(s + \omega_4)^2}$$

(2.44)

where  $s = j2\pi f$ ,  $\omega_1 = 129.43 \ rad/s$ ,  $\omega_2 = 676.40 \ rad/s$ ,  $\omega_3 = 4636.13 \ rad/s$ , and  $\omega_4 = 76618.54 \ rad/s$ .

Moreover, the transfer function for the A-weighting filter can be expanded and viewed as three cascaded filters:

$$H_A(s) = \frac{\omega_4^2 s^4}{(s + \omega_1)^2 (s + \omega_2) (s + \omega_3) (s + \omega_4)^2}$$

$$= \frac{\omega_4 s}{(s + \omega_1)^2} \times \frac{s}{(s + \omega_2)} \times \frac{s}{(s + \omega_3)} \times \frac{\omega_4 s}{(s + \omega_4)^2}$$

(2.45)

$$= \frac{\omega_4 s}{(s+\omega_1)^2} \times \frac{s}{(s+\omega_2)} \times \frac{s}{(s+\omega_3)} \times \frac{\omega_4 s}{(s+\omega_4)^2}$$

(2.46)

Hence, a digital implementation of the A-weighting filter could be achieved with the aid of the bilinear transform and its relation to a digital biquad filter with poles and zeros located at frequencies  $f_0$ ,  $f_1$ ,  $f_2$ ,  $f_3$ , and  $f_4$ :

- 4 zeros at  $f_0 = 0Hz$

- 2 poles at  $f_1 = 20.598997 Hz$

- 1 pole at  $f_2 = 107.65265 Hz$

- 1 pole at  $f_3 = 737.86223 Hz$

- 2 poles at  $f_4 = 12194.22 \, Hz$

#### 2.3.2.2 B-Weighting

The B-weighting filter is given by [28]:

$$W_B(f) = 20 \log \left( \frac{f_4^2 f^3}{(f^2 + f_1^2)(f^2 + f_4^2)(f^2 + f_5^2)^{\frac{1}{2}}} \right) + K_B$$

(2.47)

where  $K_B = 0.1696$ ,  $f_1 = 20.598997 Hz$ ,  $f_4 = 12194.22 Hz$ , and  $f_5 = 158.48932 Hz$ .

The transfer function for the B-weighting filter in the s-domain is given by [29]:

$$H_B(s) = \frac{\omega_4^2 s^3}{(s + \omega_1)^2 (s + \omega_4)^2 (s + \omega_5)}$$

(2.48)

where  $s = j2\pi f$ ,  $\omega_1 = 129.43 \ rad/s$ ,  $\omega_4 = 76618.54 \ rad/s$ , and  $\omega_5 = 995.82 \ rad/s$ .

Again, the transfer function for the B-weighting filter can be expanded and viewed as three cascaded filters:

$$H_B(s) = \frac{\omega_4^2 s^3}{(s + \omega_1)^2 (s + \omega_4)^2 (s + \omega_5)}$$

(2.49)

$$= \frac{\omega_4 s}{(s+\omega_1)^2} \times \frac{\omega_4 s}{(s+\omega_4)^2} \times \frac{s}{(s+\omega_5)}$$

(2.50)

Hence, a digital implementation of the B-weighting filter could be obtained with the aid of the bilinear transform and its relation to a digital biquad filter with poles and zeros located at frequencies  $f_0$ ,  $f_1$ ,  $f_4$ , and  $f_5$ :

- 3 zeros at  $f_0 = 0Hz$

- 2 poles at  $f_1 = 20.598997 Hz$

- 1 pole at  $f_5 = 158.48932 Hz$

- 2 poles at  $f_4 = 12194.22 Hz$

#### 2.3.2.3 C-Weighting

The C-weighting filter is given by:

$$W_C(f) = 20 \log \left( \frac{f_4^2 f^2}{(f^2 + f_1^2)(f^2 + f_4^2)} \right) + K_C$$

(2.51)

where  $K_C = 0.0619$ ,  $f_1 = 20.598997 Hz$ , and  $f_4 = 12194.22 Hz[28]$ .

The transfer function for the C-weighting filter in the s-domain is given by [29]:

$$H_C(s) = \frac{\omega_4^2 s^2}{(s + \omega_1)^2 (s + \omega_4)^2}$$

(2.52)

where  $s = j2\pi f$ ,  $\omega_1 = 129.43 \ rad/s$ , and  $\omega_4 = 76618.54 \ rad/s$ .

Again, the transfer function for the C-weighting filter can be expanded and viewed as two cascaded filters:

$$H_C(s) = \frac{\omega_4^2 s^2}{(s + \omega_1)^2 (s + \omega_4)^2}$$

(2.53)

$$= \frac{\omega_4 s}{(s+\omega_1)^2} \times \frac{\omega_4 s}{(s+\omega_4)^2} \tag{2.54}$$

Hence, a digital implementation of the C-weighting filter could be obtained with the aid of the bilinear transform and its relation to the digital biquad filter with poles and zeros located at frequencies  $f_0$ ,  $f_1$ , and  $f_4$ :

- 2 zeros at  $f_0 = 0Hz$

- 2 poles at  $f_1 = 20.598997Hz$

- 2 poles at  $f_4 = 12194.22Hz$

#### 2.3.2.4 Z-Weighting

The Z-weighting filter is sometimes excluded from the family of audio weighing filters commonly found on audio analysing and measuring devices. The Z-weighting is a flat frequency response filter and is sometimes referred to as the zero frequency weighting or flat weighting [30].

The Z-weighting filter is given by:

$$W_Z(f) = 0 (2.55)$$

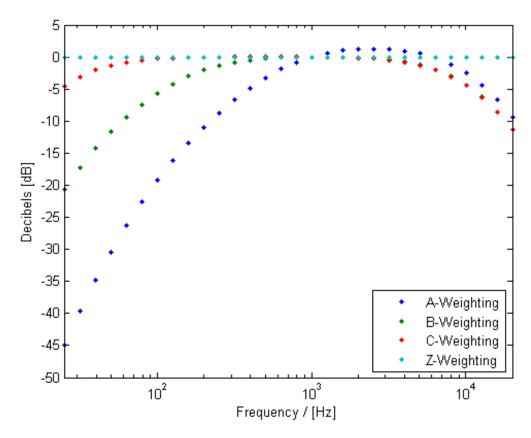

#### 2.3.2.5 Comparison between the A-, B-, C-, Z-Weighting Filters

The audio attenuation level for each of the audio weighting filter discussed in sections 2.3.2.1, 2.3.2.2, 2.3.2.3, 2.3.2.4 can be computed with the 30 band  $\frac{1}{3}$  centre frequencies given in Table 2.1. Table 2.3 shows the audio weighting filter attenuation values in decibels calculated on the STM32F429 microcontroller using equations 2.43, 2.47, 2.51, 2.55.

| n  | Freq [Hz] | A-Weight [dB] | B-Weight [dB] | C-Weight [dB] | Z-Weight [dB] |

|----|-----------|---------------|---------------|---------------|---------------|

| 0  | 24.80     | -45.01        | -20.60        | -4.49         | 0.00          |

| 1  | 31.25     | -39.70        | -17.23        | -3.07         | 0.00          |

| 2  | 39.37     | -34.85        | -14.29        | -2.04         | 0.00          |

| 3  | 49.61     | -30.42        | -11.71        | -1.32         | 0.00          |

| 4  | 61.50     | -26.35        | -9.44         | -0.83         | 0.00          |

| 5  | 78.75     | -22.64        | -7.44         | -0.51         | 0.00          |

| 6  | 99.213    | -19.25        | -5.70         | -0.31         | 0.00          |

| 7  | 125.00    | -16.19        | -4.23         | -0.17         | 0.00          |

| 8  | 157.49    | -13.42        | -3.02         | -0.09         | 0.00          |

| 9  | 198.43    | -10.93        | -2.07         | -0.03         | 0.00          |

| 10 | 250.00    | -8.67         | -1.36         | 0.00          | 0.00          |

| 11 | 314.98    | -6.64         | -0.85         | 0.02          | 0.00          |

| 12 | 396.85    | -4.83         | -0.51         | 0.03          | 0.00          |

| 13 | 500.00    | -3.25         | -0.28         | 0.03          | 0.00          |

| 14 | 629.96    | -1.91         | -0.13         | 0.03          | 0.00          |

| 15 | 793.70    | -0.83         | -0.04         | 0.02          | 0.00          |

| 16 | 1000.00   | 0.00          | 0.00          | 0.00          | 0.00          |

| 17 | 1259.92   | 0.59          | 0.01          | -0.03         | 0.00          |

| 18 | 1587.40   | 0.98          | -0.02         | -0.09         | 0.00          |

| 19 | 2000.00   | 1.20          | -0.09         | -0.17         | 0.00          |

| 20 | 2519.84   | 1.27          | -0.21         | -0.30         | 0.00          |

| 21 | 3174.80   | 1.20          | -0.41         | -0.51         | 0.00          |

| 22 | 4000.00   | 0.96          | -0.73         | -0.83         | 0.00          |

| 23 | 5039.68   | 0.54          | -1.20         | -1.31         | 0.00          |

| 24 | 6349.60   | -0.14         | -1.92         | -2.02         | 0.00          |

| 25 | 8000.00   | -1.15         | -2.94         | -3.05         | 0.00          |

| 26 | 10079.37  | -2.55         | -4.35         | -4.46         | 0.00          |

| 27 | 12699.21  | -4.40         | -6.21         | -6.32         | 0.00          |

| 28 | 16000.00  | -6.71         | -8.53         | -8.63         | 0.00          |

| 29 | 20158.74  | -9.45         | -11.27        | -11.38        | 0.00          |

**Table 2.3:** Audio Weighting functions for 30 bands of  $\frac{1}{3}$  octave spaced steps calculated using the STM32F429 microcontroller

Figure 2.12 is a plot of the audio weighting filter attenuation values in decibels calculated and plotted with MATLAB using equations 2.43, 2.47, 2.51, 2.55.

**Figure 2.12:** Audio weighting functions for 30 bands of  $\frac{1}{3}$  octave spaced steps calculated and plotted using MATLAB

Table 2.3 and Figure 2.12 illustrate the audio attenuation levels for each of the audio weighting filters discussed in sections 2.3.2.1, 2.3.2.2, 2.3.2.3, and 2.3.2.4.

# 2.4 Simultaneous Real-Valued Fast-Fourier Transform (FFT)

This section discusses the underlying mathematical calculations for the audio signal processing algorithm. The developed audio signal processing algorithm is also discussed from a coding point of view in Chapter 5.

Since the input samples are real-valued and not inherently complex-valued, the imaginary part of the complex number is often equated to zero before computing the DFT with an appropriate FFT algorithm. This results in the output of the FFT being mirrored across the frequency domain, and often half of the FFT results are discarded. This method of computing the DFT of a real-valued input may be an option if computing time, memory space and power are not limiting factors of the hardware. An alternative method for determining the FFT of input samples that are real-valued is implemented by the designed real-time audio analyser presented in this research thesis. The algorithm for computing the simultaneous real-valued FFT of sampled data with size 2N is discussed in several referenced sources[24], [26], [31], [32], [33].

Consider g[n], a single real-valued sample of data with a sample size of 2N. The single real-valued sample of data g[n] can be split into  $x_1[n]$  and  $x_2[n]$ , two separate real-valued samples of size N to form the complex-valued input sample x[n] of size N.

The two real-valued samples,  $x_1[n]$  and  $x_2[n]$  each with sample size N, are defined by the following two equations:

$$x_1[n] = g[2n] (2.56)$$

$$x_2[n] = g[2n+1] (2.57)$$

where  $0 \le n \le N - 1$ .

Therefore the complex-valued input x[n] is given by:

$$x[n] = x_1[n] + jx_2[n] (2.58)$$

$$= g[2n] + jg[2n+1] \tag{2.59}$$

where  $0 \le n \le N - 1$ .

The DFT of the complex-valued input x[n] is given by:

$$X[k] = \sum_{n=0}^{N-1} x[n]W_N^{nk}$$

(2.60)

$$= \sum_{n=0}^{N-1} (x_1[n] + jx_2[n]) W_N^{nk}$$

(2.61)

$$= \sum_{n=0}^{N-1} (x_1[n]W_N^{nk}) + j \sum_{n=0}^{N-1} (x_2[n]W_N^{nk})$$

(2.62)

$$= X_1[k] + jX_2[k] (2.63)$$

where  $0 \le k \le N - 1$ .

The separate components of X[k] are given by:

$$X_1[k] = \frac{1}{2}(X[k] + X^*[N-k])$$

(2.64)

$$X_2[k] = \frac{1}{2i}(X[k]) - X^*[N-k])$$

(2.65)

Now applying the DFT operator directly to the real-valued input sample g[n] with sample size

2N results in:

$$G[k] = DFT(g[n]) (2.66)$$

$$=\sum_{n=0}^{2N-1}g[n]W_{2N}^{nk} \tag{2.67}$$

$$= \sum_{n=0}^{N-1} g[2n]W_{2N}^{2nk} + \sum_{n=0}^{N-1} g[2n+1]W_{2N}^{(2n+1)k}$$

(2.68)

$$= \sum_{n=0}^{N-1} g[2n]W_{2N}^{2nk} + \sum_{n=0}^{N-1} g[2n+1]W_{2N}^{2nk}W_{2N}^{k}$$

(2.69)

$$= \sum_{n=0}^{N-1} x_1[n] W_N^{nk} + W_{2N}^k \sum_{n=0}^{N-1} x_2[n] W_N^{nk}$$

(2.70)

$$= X_1[k] + W_{2N}^k X_2[k] (2.71)$$

where  $0 \le k \le N - 1$ .

Substituting the separate components for  $X_1[k]$  and  $X_2[k]$  from equations 2.64 and 2.65 results in:

$$G[k] = X_1[k] + W_{2N}^k X_2[k] (2.72)$$

$$= \frac{1}{2} (X[k] + X^*[N-k]) + W_{2N}^k \frac{1}{2i} (X[k] - X^*[N-k])$$

(2.73)

$$= \frac{1}{2} \Big( (X[k] + X^*[N-k]) - jW_{2N}^k (X[k] - X^*[N-k]) \Big)$$

(2.74)

$$= \frac{1}{2} \left( X[k] + X^*[N-k] + \sin\left(\frac{k\pi}{N}\right) \left( X^*[N-k] - X[k] \right) + j\left(\cos\left(\frac{k\pi}{N}\right) \left( X^*[N-k] - X[k] \right) \right) \right)$$

(2.75)

where  $0 \le k \le N - 1$ .

The real and imaginary components for G[k] in terms of X[k] can be determined as:

$$Re(G[k]) = \frac{1}{2} \left( X[k] + X^*[N-k] + \sin\left(\frac{k\pi}{N}\right) \left( X^*[N-k] - X[k] \right) \right)$$

(2.76)

$$\operatorname{Im}(G[k]) = \frac{1}{2} \left( \cos\left(\frac{k\pi}{N}\right) \left(X^*[N-k] - X[k]\right) \right) \tag{2.77}$$

The power of G[k] in terms of X[k] can be determined by:

$$|G[k]|^2 = \left(\text{Re}(G[k])\right)^2 + \left(\text{Im}(G[k])\right)^2$$

(2.78)

$$= X[k]^{2} \left(1 - \frac{1}{2} \sin\left(\frac{k\pi}{N}\right)\right) + X^{*}[N-k]^{2} \left(1 + \frac{1}{2} \sin\left(\frac{k\pi}{N}\right)\right)$$

(2.79)

$$= X[k]^{2}A[k] + X^{*}[N-k]^{2}B[k]$$

(2.80)

where  $A[k] = \left(1 - \frac{1}{2}\sin\left(\frac{k\pi}{N}\right)\right)$ ,  $B[k] = \left(1 + \frac{1}{2}\sin\left(\frac{k\pi}{N}\right)\right)$ , and  $0 \le k \le N - 1$ .

Now, recall:

$$X[k] = X_1[k] + jX_2[k] (2.81)$$

$$X[N-k] = X_1[N-k] + jX_2[N-k]$$

(2.82)

$$X^*[N-k] = X_1[N-k] - jX_2[N-k]$$

(2.83)

Substituting equations 2.81, 2.82, and 2.83 into 2.75 results in:

$$G[k] = \frac{1}{2} \left( X[k] + X^*[N - k] + \sin\left(\frac{k\pi}{N}\right) \left( X^*[N - k] - X[k] \right) + j\left(\cos\left(\frac{k\pi}{N}\right) \left( X^*[N - k] - X[k] \right) \right) \right)$$

$$= \frac{1}{2} \left( A[k] + \cos\left(\frac{k\pi}{N}\right) B[k] - \sin\left(\frac{k\pi}{N}\right) C[k] + j(D[k] - \cos\left(\frac{k\pi}{N}\right) C[k] - \sin\left(\frac{k\pi}{N}\right) B[k] \right) \right)$$

(2.85)

where

$$A[k] = X_1[k] + X_1[N-k]$$

,  $B[k] = X_2[k] + X_2[N-k]$ ,  $C[k] = X_1[k] - X_1[N-k]$ ,  $D[k] = X_2[k] - X_2[N-k]$ , and  $0 \le k \le N-1$ .