TOTAL IONIZING DOSE AND SINGLE EVENT UPSET TESTING

OF FLASH BASED FIELD PROGRAMMABLE GATE ARRAYS

By

Stefan van Aardt

Submitted in fulfilment of the requirements for

the degree of Masters of Engineering in Mechatronics (Research) in the

Faculty of Engineering, the Built Environment and Information Technology

at the Nelson Mandela Metropolitan University

December 2014

Supervisor: Dr Farouk Smith

## **Acknowledgements**

Completing this project would not have been possible without the support and assistance of a number of organizations and people for which I am very grateful.

I would like to specially thank my supervisor Dr Farouk Smith, for all of the guidance and assistance throughout the project.

The National Research Foundation for the generous support during the duration of the project as well as making the staff and test facilities available at the iTemba LABS to perform the radiation experiments.

Drs Retief Neveling, Rudolph Nchodu and Ricky Smit for all of their time and assistance at the iTemba LABS.

JP Potgieter for his encouragement and support as my fellow student.

My family and friends, for all of their moral support and encouragement during this project.

Christine Olivier, for her encouragement, assistance and patience during this project.

## **Table of Contents**

| Αc  | knowledgei     | ments                          | i   |

|-----|----------------|--------------------------------|-----|

| Lis | st of Figures  |                                | vi  |

| Lis | st of Tables.  |                                | x   |

| Lis | st of Equation | ons                            | xi  |

| ΑŁ  | stract         |                                | xii |

| Κe  | y Words        |                                | xiv |

| 1.  | Introduct      | tion                           | 1   |

|     | 1.1 Ove        | rview                          | 1   |

|     | 1.2 Out        | line of the thesis             | 3   |

|     | 1.2.1          | Chapter 2                      | 3   |

|     | 1.2.2          | Chapter 3                      | 3   |

|     | 1.2.3          | Chapter 4                      | 4   |

|     | 1.2.4          | Chapter 5                      | 4   |

|     | 1.2.5          | Chapter 6                      | 5   |

| 2   | Theoretic      | cal Background                 | ε   |

|     | 2.1 Fun        | damental Concepts              | ε   |

|     | 2.1.1          | Energy                         | ε   |

|     | 2.1.2          | Radiation Dose                 | ε   |

|     | 2.1.3          | Flux                           | 7   |

|     | 2.1.4          | Fluence                        | 7   |

|     | 2.1.5          | Linear Energy Transfer         | 7   |

|     | 2.2 Orb        | its                            | 8   |

|     | 2.2.1          | High Earth Altitude and ground | 8   |

|     | 2.2.2          | Low Earth Orbit                | g   |

|     | 2.2.3          | Medium Earth Orbit             | g   |

|     | 2.2.4          | Geostationary Orbit            | 10  |

|     | 2.2.5          | High Earth Orbit               | 10  |

|     | 2.3 Space      | ce Radiation Environment       | 11  |

|     | 2.3.1          | Vacuum                         | 11  |

|     | 2.3.2          | Temperature                    | 11  |

|     | 2.3.3          | Radiation                      | 12  |

|     |                |                                |     |

|   | 2.4   | Rad   | iation Sources                                   | 12 |

|---|-------|-------|--------------------------------------------------|----|

|   | 2.4.  | 1     | Galactic Cosmic Rays                             | 13 |

|   | 2.4.2 |       | Trapped Radiation                                | 16 |

|   | 2.4.3 |       | Solar Particle Events                            | 18 |

|   | 2.4.  | 4     | Atmospheric ionizing radiation                   | 19 |

|   | 2.4.  | 5     | Dose Levels in space orbits                      | 19 |

|   | 2.4.  | 6     | Testing Facility Sources                         | 20 |

|   | 2.5   | Nat   | ural shielding                                   | 20 |

|   | 2.5.  | 1     | Magnetosphere                                    | 20 |

|   | 2.5.  | 2     | Geomagnetic shielding                            | 21 |

|   | 2.6   | Rad   | iation interactions with matter                  | 22 |

|   | 2.6.  | 1     | Charged particles (direct ionizing)              | 22 |

|   | 2.7   | Con   | nmon Space Radiation Effects on Microelectronics | 25 |

|   | 2.8   | Con   | nplementary Metal Oxide Semiconductor (CMOS)     | 25 |

|   | 2.9   | Met   | tal Oxide Semiconductors Field Effect Transistor | 26 |

|   | 2.10  | Арр   | lication Specific Integrated Circuits            | 27 |

|   | 2.11  | Fiel  | d Programmable Gate Arrays                       | 28 |

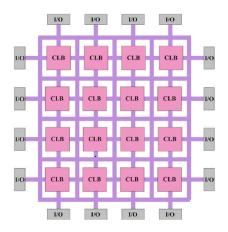

|   | 2.13  | 1.1   | Architecture                                     | 29 |

|   | 2.12  | Sing  | le Event Effects                                 | 30 |

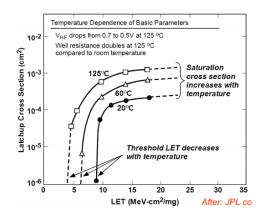

|   | 2.12  | 2.1   | Single Event Latchup                             | 31 |

|   | 2.12  | 2.2   | Single Event Functional Interrupt                | 32 |

|   | 2.12  | 2.3   | Single Event Transient                           | 32 |

|   | 2.12  | 2.4   | Single Event Upsets                              | 33 |

|   | 2.13  | Tota  | al Ionizing Dose                                 | 35 |

|   | 2.14  | SRA   | M vs. FLASH testing                              | 36 |

|   | 2.14  | 4.1   | Effects on SRAM cells:                           | 36 |

|   | 2.14  | 4.2   | Effects on FLASH cells:                          | 36 |

| 3 | Res   | earch | ı Rationale                                      | 38 |

|   | 3.1   | Res   | earch Motivation                                 | 38 |

|   | 3.2   | Rea   | l World Radiation Effects                        | 39 |

|   | 3.3   | Cur   | rent Shortcomings                                | 40 |

|   | 3.4   | Con   | nmercial off the Shelf Components                | 41 |

|   | 3.5   | Rad   | iation Hardened Devices                          | 42 |

|   |       |       |                                                  |    |

|   | 3.5.  | .1 Physical hardening                       | 42  |

|---|-------|---------------------------------------------|-----|

|   | 3.5.2 | .2 Mitigation Schemes                       | 43  |

| 4 | Rese  | search Set-up and Procedure                 | 47  |

|   | 4.1   | Primary Objectives                          | 47  |

|   | 4.2   | ProASIC3 A3P 1000 PQ208 Architecture        | 48  |

|   | 4.3   | Testing Circuits                            | 49  |

|   | 4.3.  | S.1 Single Event Upsets                     | 50  |

|   | 4.3.2 | 2.2 Circuit Comparing and Duplication       | 50  |

|   | 4.3.3 | Standard mitigation techniques              | 51  |

|   | 4.3.4 | S.4 Serial Peripheral Interface             | 58  |

|   | 4.3.  | Inter Integrated Circuit (I2C)              | 62  |

|   | 4.3.6 | Universal Asynchronous Receiver/Transmitted | 66  |

|   | 4.3.  | 5.7 DC Motor                                | 68  |

|   | 4.3.8 | 8.8 Servo Motor                             | 70  |

|   | 4.3.9 | 9.9 Stepper Motor                           | 71  |

|   | 4.3.  | .10 Control Board Circuit                   | 72  |

|   | 4.4   | Data Acquisition                            | 73  |

|   | 4.5   | Experimental Setup - Total Ionizing Dose    | 73  |

|   | 4.5.  | Electrical Design                           | 74  |

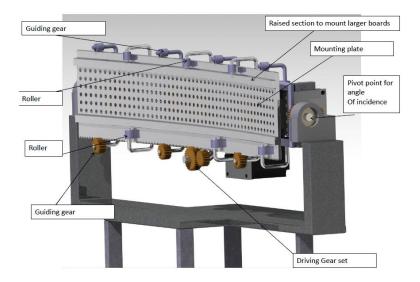

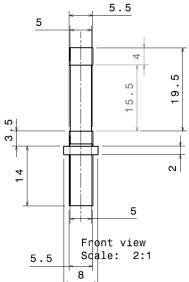

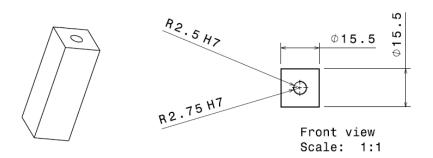

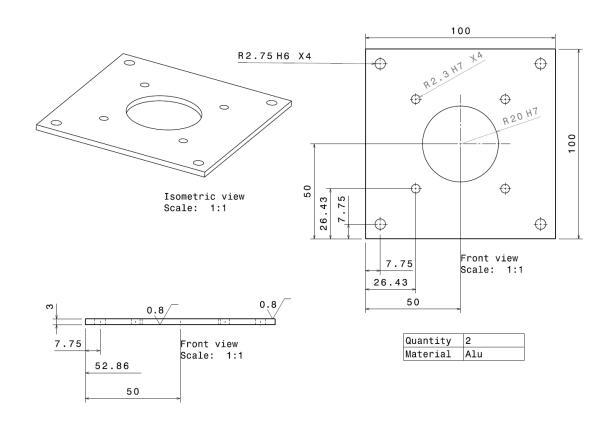

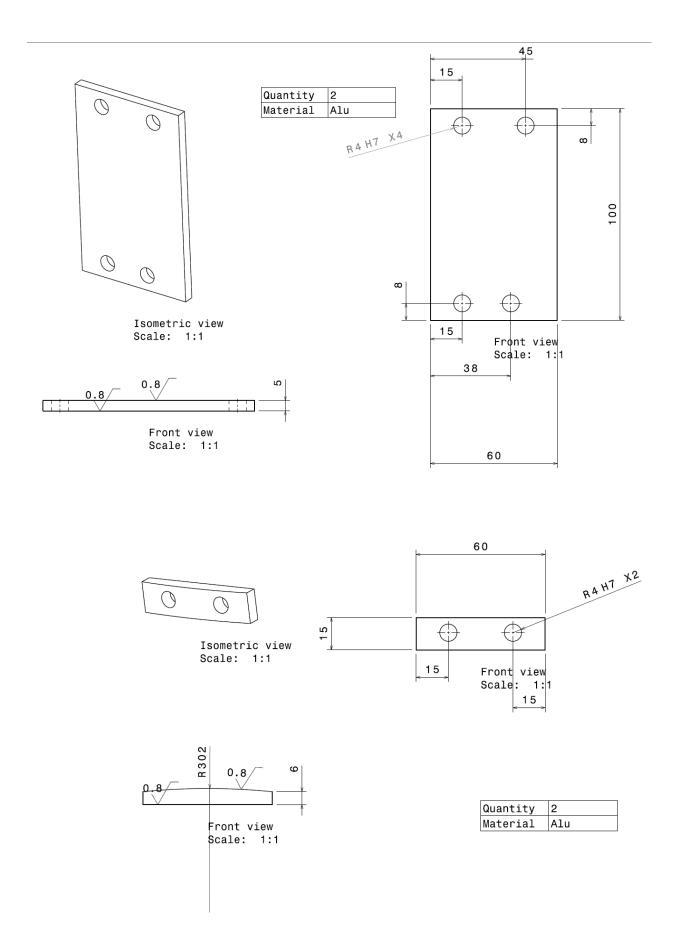

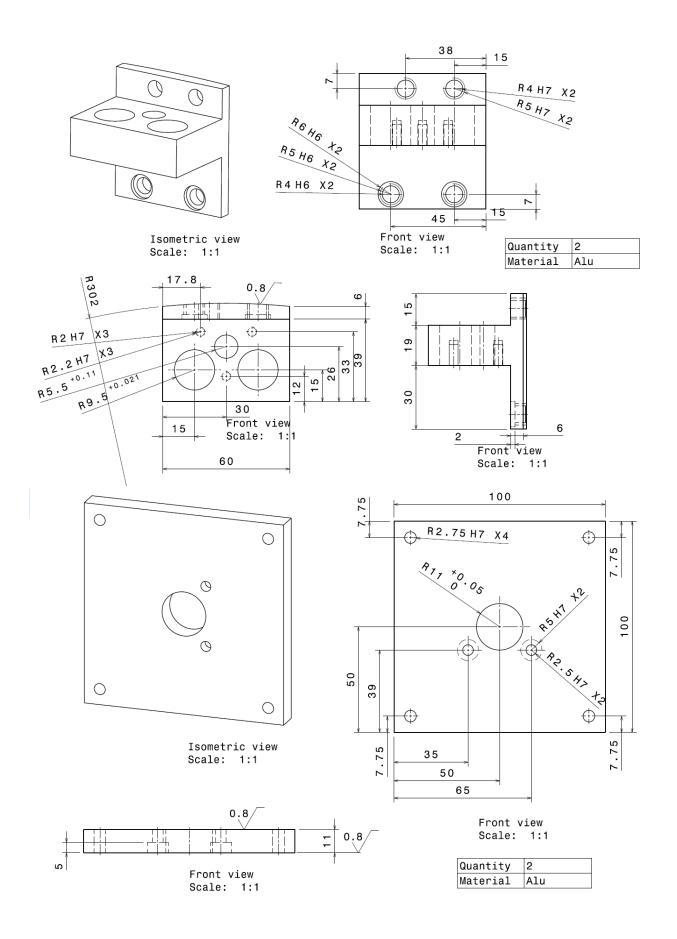

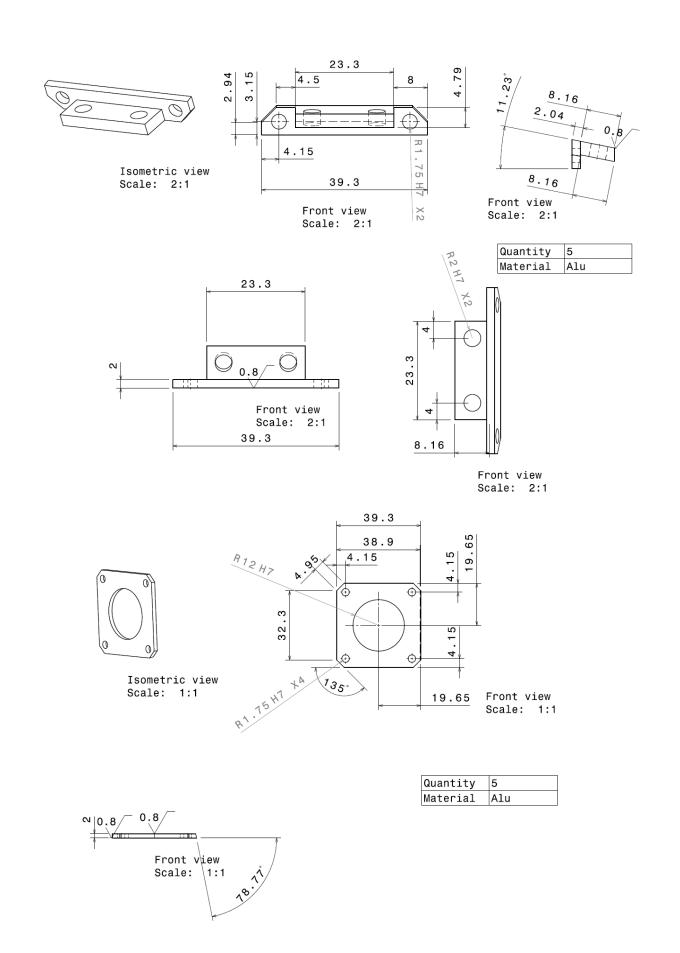

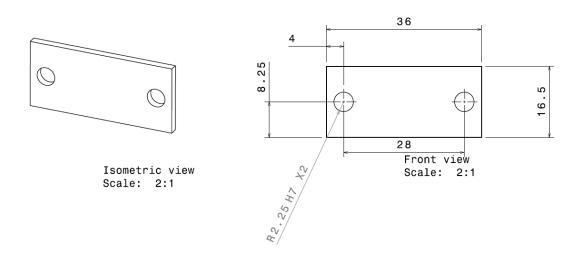

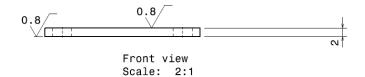

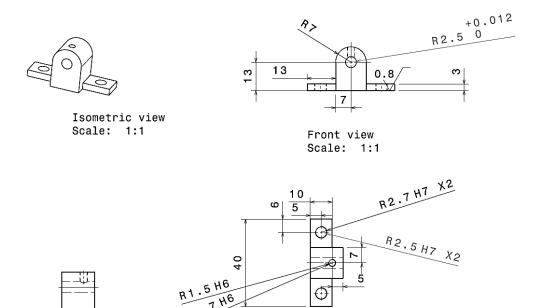

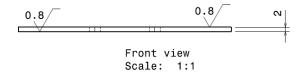

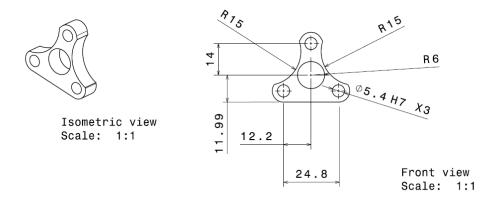

|   | 4.5.2 | .2 Mechanical Design                        | 75  |

|   | 4.5.3 | .3 Test Procedure                           | 76  |

|   | 4.5.4 | .4 Monitoring and Recording of Data         | 76  |

|   | 4.5.  | Data Analysis                               | 78  |

|   | 4.6   | Experimental Setup - Single Event Upset     | 78  |

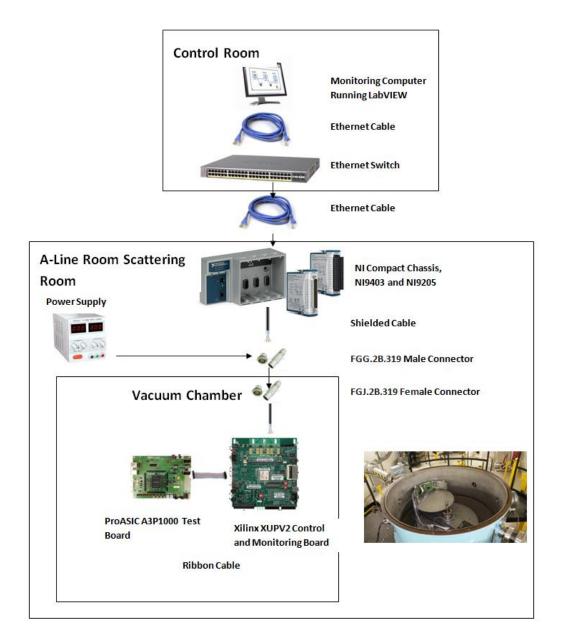

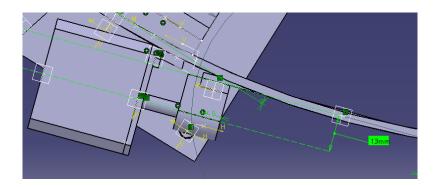

|   | 4.6.  | Testing Configuration                       | 79  |

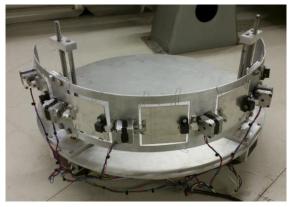

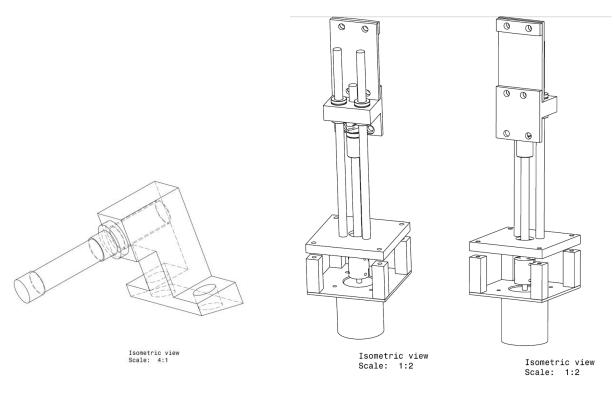

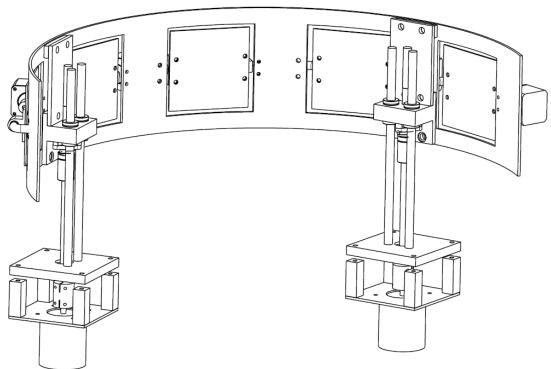

|   | 4.6.2 | Mechanical                                  | 80  |

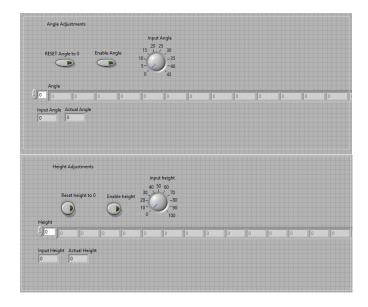

|   | 4.6.3 | Control                                     | 95  |

|   | 4.6.4 | 5.4 Electrical Design                       | 96  |

|   | 4.6.  | 5.5 Test Procedure                          | 97  |

|   | 4.6.6 | 5.6 Data Analysis                           | 98  |

|   | 4.7   | Testing Installation                        | 99  |

|   | 4.7.  | 7.1 Total Ionizing Dose                     | 99  |

|   | 4.7.2 | 7.2 Single Event Upset                      | 100 |

|   | 4.8    | Deca   | apsulation                   | .104 |

|---|--------|--------|------------------------------|------|

| 5 | Exp    | erime  | ental Results and Discussion | .105 |

|   | 5.1    | Sing   | le Event Upset               | .105 |

|   | 5.1.   | 1      | Test 1                       | .105 |

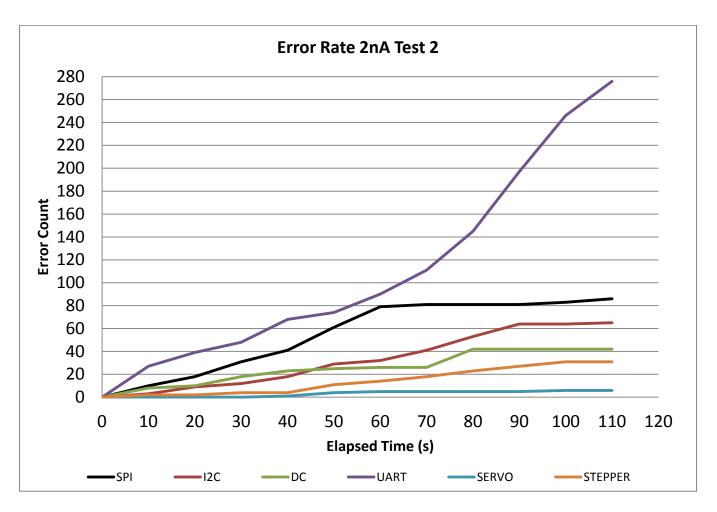

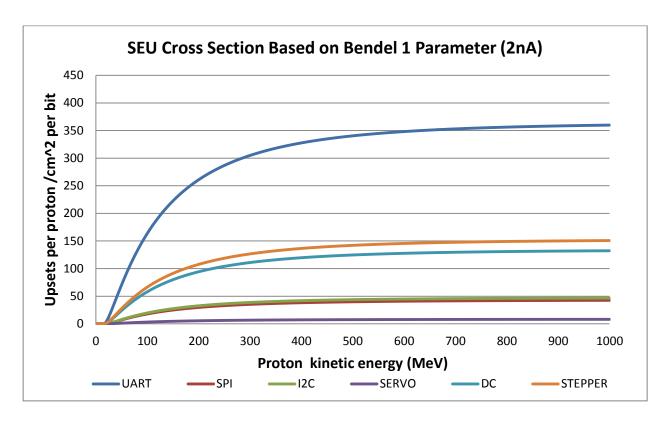

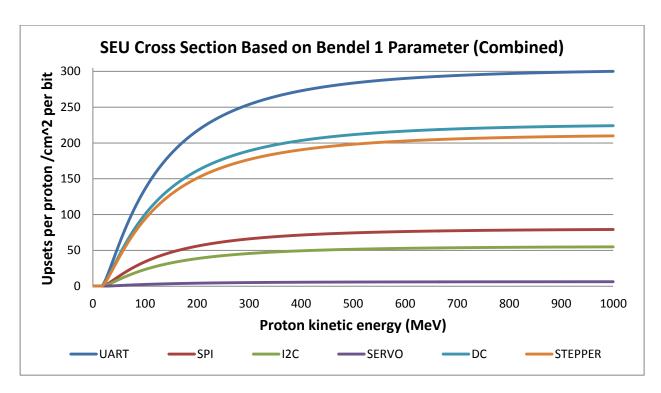

|   | 5.1.   | 2      | Test 2                       | .115 |

|   | 5.1.   | 3      | Post Radiation Tests         | .130 |

|   | 5.1.   | 4      | Mechanical Design            | .130 |

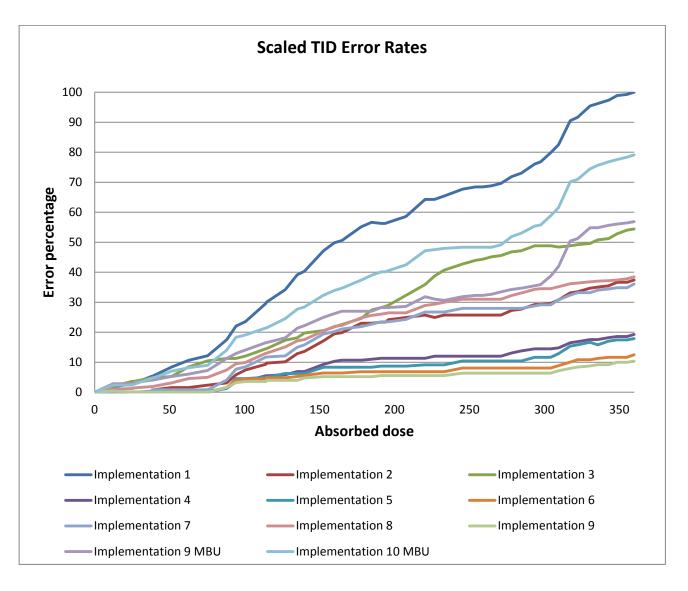

|   | 5.2    | Tota   | al Ionizing Dose             | .131 |

|   | 5.2.   | 1      | Output Error Rate            | .131 |

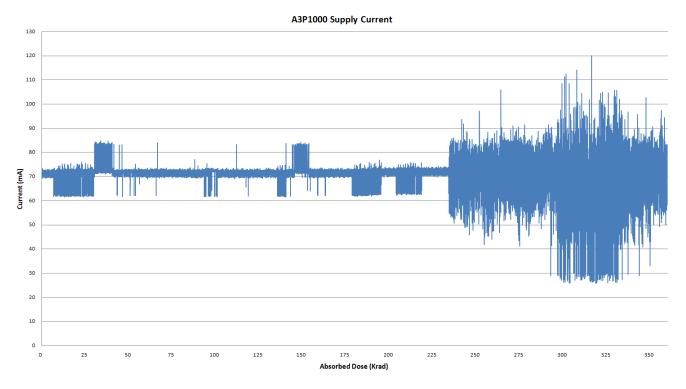

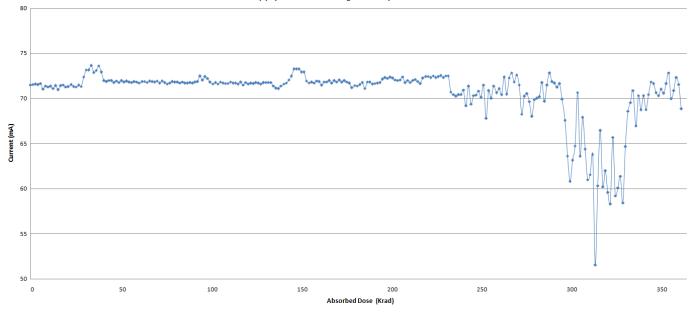

|   | 5.2.   | 2      | Supply Current               | .136 |

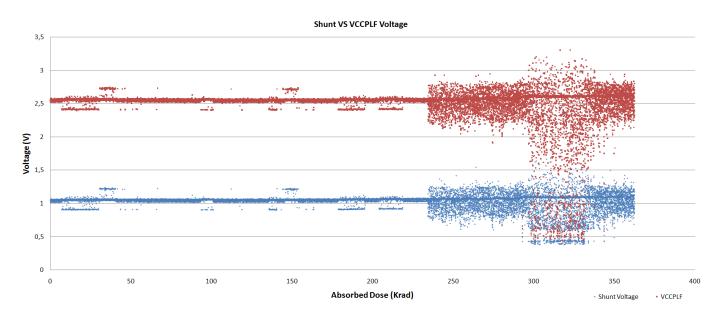

|   | 5.2.   | 3      | Voltage                      | .138 |

| 6 | Con    | clusic | on                           | .140 |

|   | 6.1    | Ove    | rview                        | .140 |

|   | 6.2    | Reco   | ommendations                 | .145 |

| 7 |        |        | es                           |      |

| Α | ppendi | x A    |                              | .157 |

# **List of Figures**

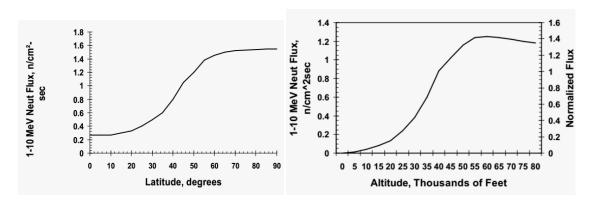

| Figure 1: Flux at varying latitudes [26]                                                                   | 9   |

|------------------------------------------------------------------------------------------------------------|-----|

| Figure 2: Flux at various altitudes [26]                                                                   | 8   |

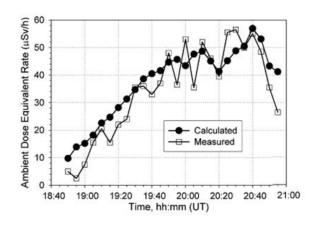

| Figure 3: Dose rate on board a Concorde flight [25]                                                        | 9   |

| Figure 4: Dose rates on-board an A310-300 flight [25]                                                      | 9   |

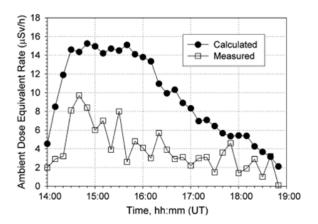

| Figure 5: Basic orbit layout [32]                                                                          | 10  |

| Figure 6: Principal space radiation sources [29]                                                           | 13  |

| Figure 7: GCR energy spectra for protons, helium, oxygen and iron [41]                                     | 15  |

| Figure 8: In the Earth's radiation bands, three types of motion can be seen for charged particles, namely; |     |

| cyclotron motion, bouncing motion and drift motion [29, 39]                                                | 16  |

| Figure 9: Iso-Flux curves for 9.4MeV protons [29]                                                          | 17  |

| Figure 10: Iso-Flux curves for 560keV electrons [29]                                                       | 17  |

| Figure 11: Earth's magnetosphere [46]                                                                      | 21  |

| Figure 12: Energy required to penetrate the magnetosphere                                                  | 22  |

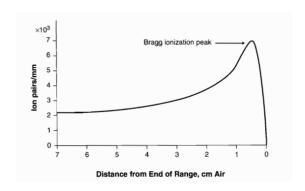

| Figure 13: Path of charged particle in air [23]                                                            | 24  |

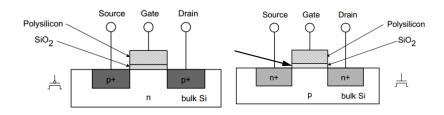

| Figure 14: N and P type CMOS                                                                               |     |

| Figure 15: Cross section and circuit symbol of n-type MOSFET [52]                                          | 26  |

| Figure 16: FPGA architecture                                                                               | 29  |

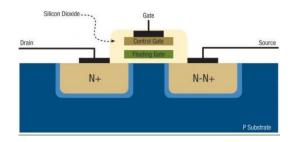

| Figure 17: Floating gate flash structure [25]                                                              | 30  |

| Figure 18: Temperature dependence of latchup cross section vs. LET [62]                                    | 32  |

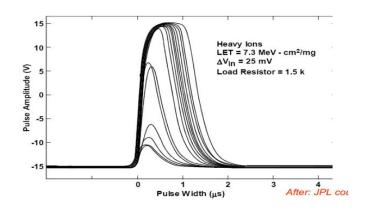

| Figure 19: SET pulse width and amplitude [62]                                                              | 33  |

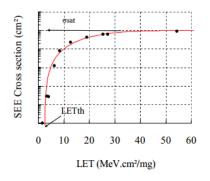

| Figure 20: Cross section vs. LET                                                                           | 34  |

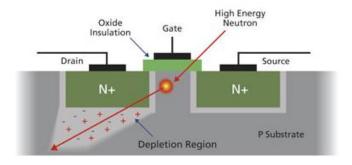

| Figure 21: High energy particle collision with MOS                                                         | 34  |

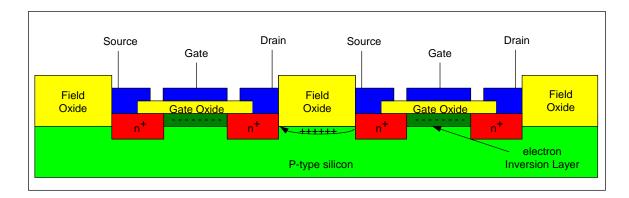

| Figure 22: TID                                                                                             | 36  |

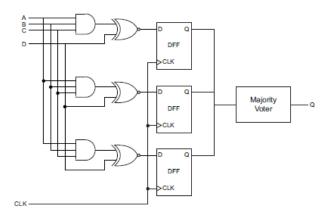

| Figure 23: TMR Mitigation                                                                                  | 44  |

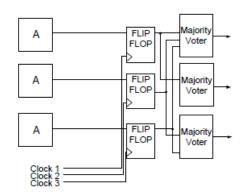

| Figure 24: Full global TMR                                                                                 | 44  |

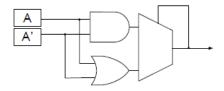

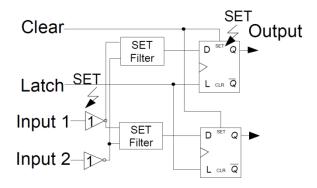

| Figure 25: DMR SET filter [15]                                                                             | 45  |

| Figure 26: Delay element SET filter [15]                                                                   | 45  |

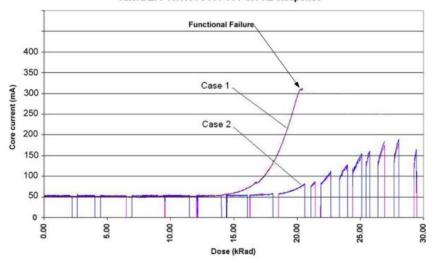

| Figure 27: TID mitigation comparison between unmitigated (Case 1) and mitigated (case 2) methods for the   | e   |

| Altera SRAM FPGA [11]                                                                                      | 46  |

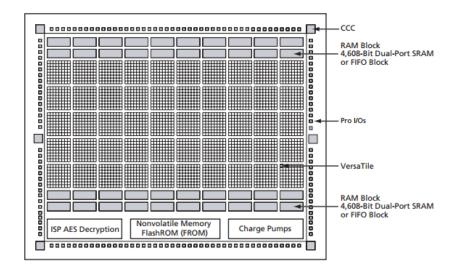

| Figure 28: ProASIC3E architecture                                                                          | 49  |

| Figure 29: A number of the sensors and motors tested with the circuits                                     | 50  |

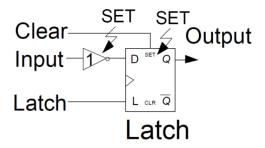

| Figure 30: Implementation 1                                                                                | 52  |

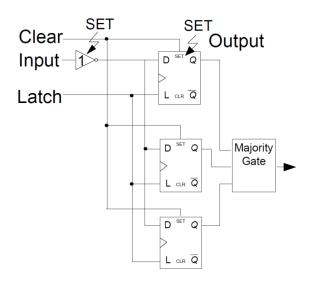

| Figure 31: Implementation 2                                                                                | 53  |

| Figure 32: Implementation 3                                                                                | 53  |

| Figure 33: Implementation 4                                                                                | 54  |

| Figure 34: Implementation 5                                                                                | 55  |

| Figure 35: Implementation 6                                                                                | 55  |

| Figure 36: Implementation 7                                                                                | 56  |

| Figure 37: Implementation8                                                                                 | 56  |

| Figure 38: Implementation 9                                                                                | 57  |

| Figure 39: Implementation 9 MBU                                                                            | 57  |

|                                                                                                            | vii |

| Figure 40: Implementation 10 MBU                   | 58   |

|----------------------------------------------------|------|

| Figure 41: Typical SPI operating modes [79]        | 59   |

| Figure 42: Multiple slave SPI mode [79]            | 60   |

| Figure 43: Required Communication procedure [80]   | 61   |

| Figure 44: SPI MISO test signal                    | 61   |

| Figure 45: SPI MOSI test signal                    | 62   |

| Figure 46: SPI clock signal                        | 62   |

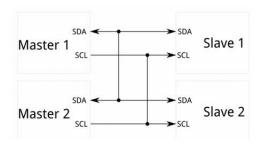

| Figure 47: Multi master and slave I2C set up       | 63   |

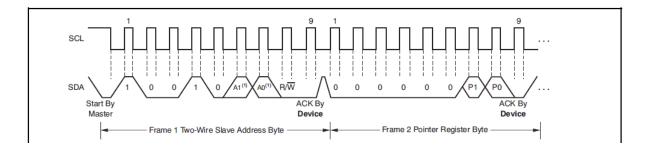

| Figure 48: TMP102 communication protocol [89]      | 64   |

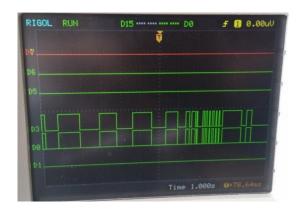

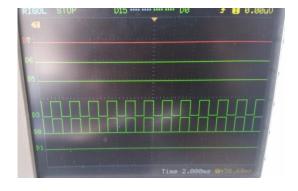

| Figure 49: I2C SDA signal                          |      |

| Figure 50: I2C SCL signal                          | 65   |

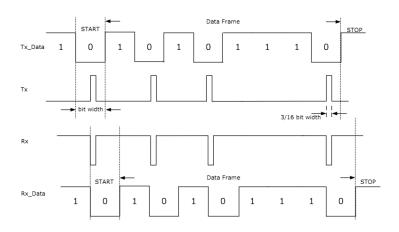

| Figure 51: UART communication protocol [92]        |      |

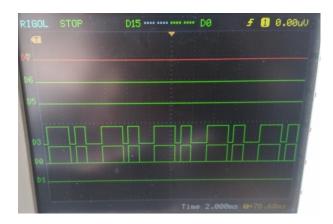

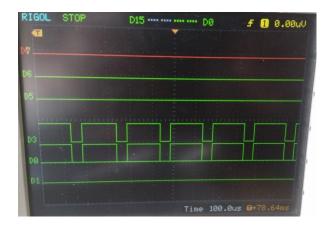

| Figure 52: UART TX signal                          | 68   |

| Figure 53: UART TX signal                          | 68   |

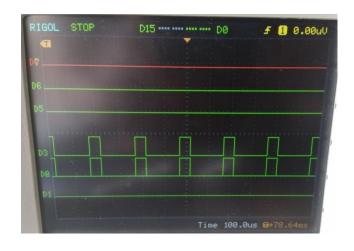

| Figure 54: High speed DC output signal             | 69   |

| Figure 55: Low speed DC output signal              | 70   |

| Figure 56: Servo motor PWM signal                  | 71   |

| Figure 57: Stepper motor output signal             | 72   |

| Figure 58: Stepper motor winding outputs           |      |

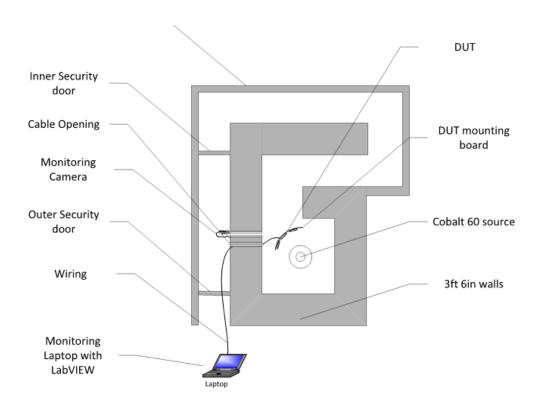

| Figure 59: Facility Layout                         | 74   |

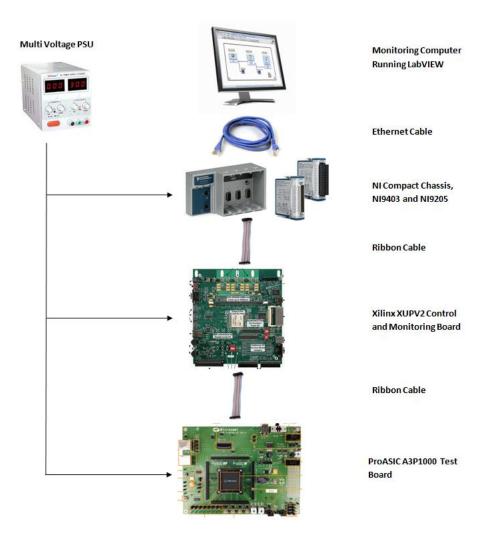

| Figure 60: TID test configuration                  | 75   |

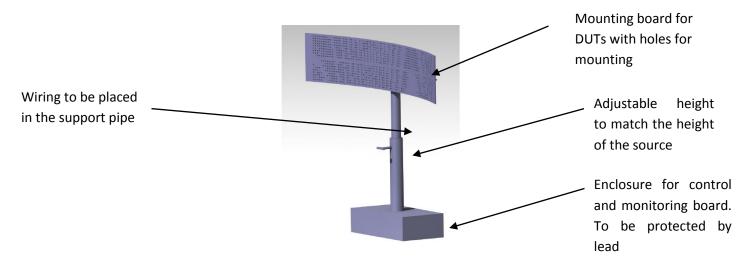

| Figure 61: Proposed mechanical set up              |      |

| Figure 62: LabVIEW user interface                  | 77   |

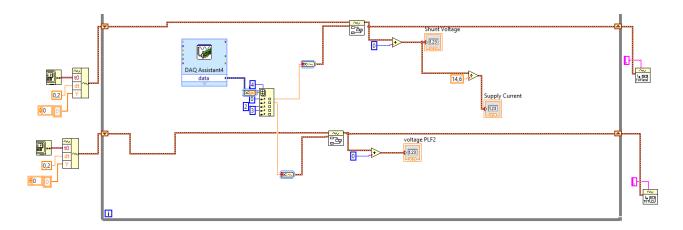

| Figure 63: Current and voltage measurement method  | 77   |

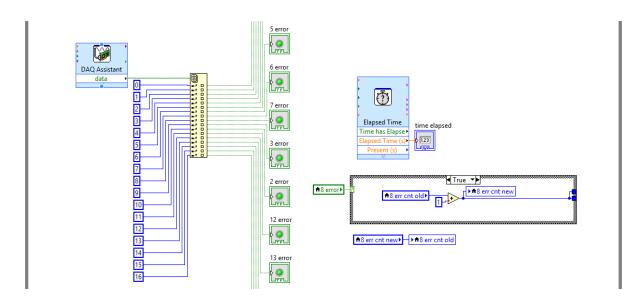

| Figure 64: Section of LabVIEW code counting errors |      |

| Figure 65: SEU test configuration                  | 80   |

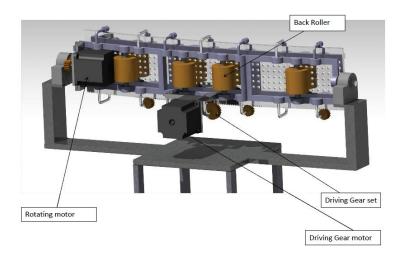

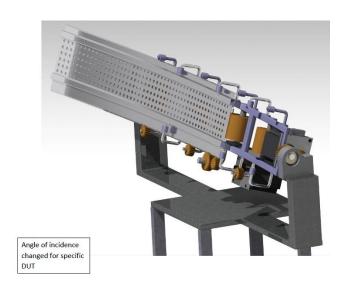

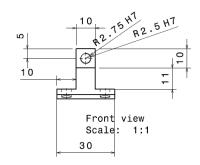

| Figure 66: Concept Front                           | 81   |

| Figure 67: Concept Rear                            |      |

| Figure 68: Concept DUT Selected Position           |      |

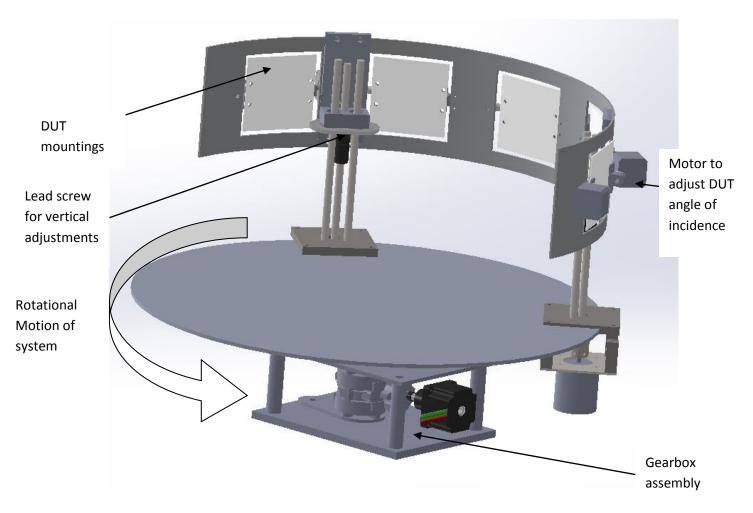

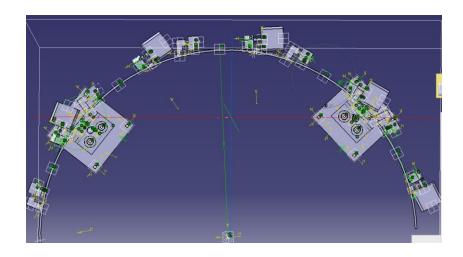

| Figure 69: Final design                            |      |

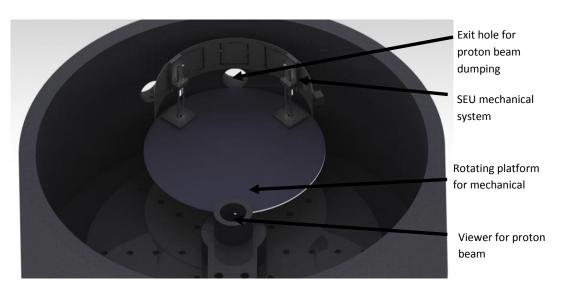

| Figure 70: SEU mechanical in vacuum chamber        |      |

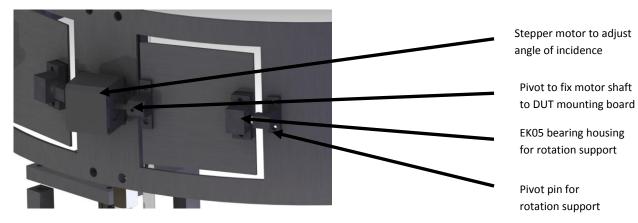

| Figure 71: Reverse of SEU mechanical               | 84   |

| Figure 72: Front of SEU mechanical system          |      |

| Figure 73: Reverse DUT mounting plate              |      |

| Figure 74: SEU mechanical system                   | 84   |

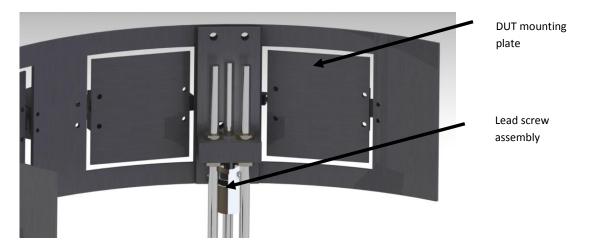

| Figure 75: Front of SEU mechanical DUT plates      | 85   |

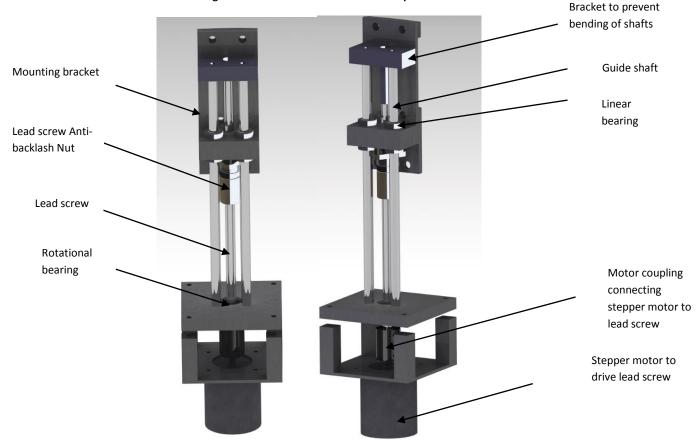

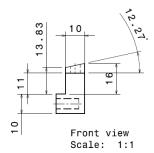

| Figure 76: Lead screw assembly                     |      |

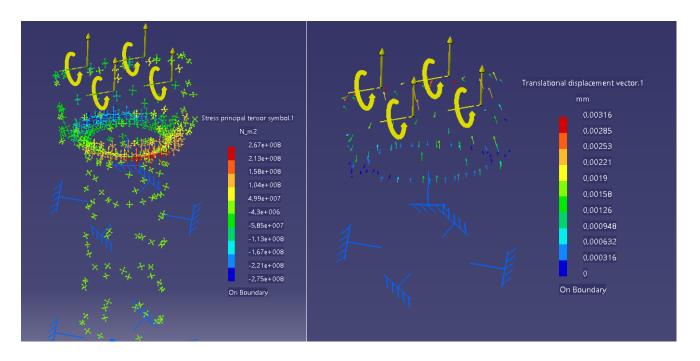

| Figure 77: Centre of gravity                       | 89   |

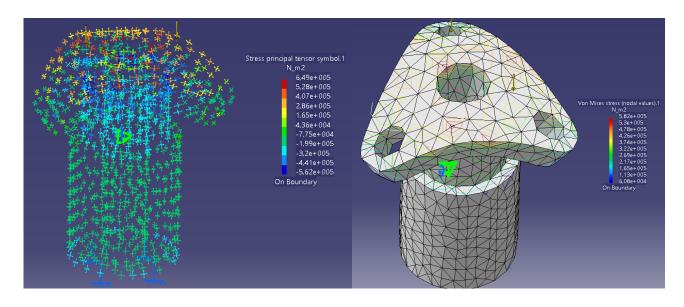

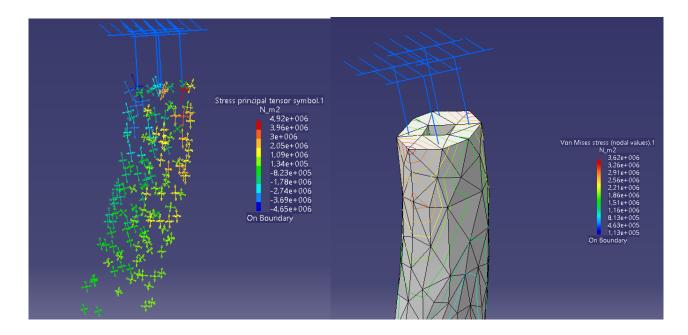

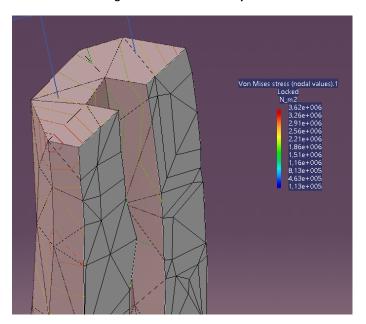

| Figure 78: Lead screw nut analysis                 | 89   |

| Figure 79: Lead screw nut analysis                 |      |

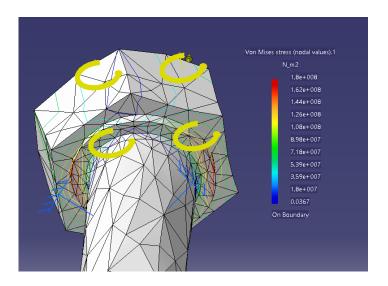

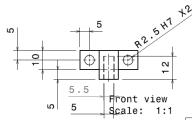

| Figure 80: Bolt head analysis                      |      |

| Figure 81: Bolt head analysis                      |      |

| Figure 82: Bolt head analysis                      |      |

| Figure 83: Bolt head analysis                      |      |

|                                                    | viii |

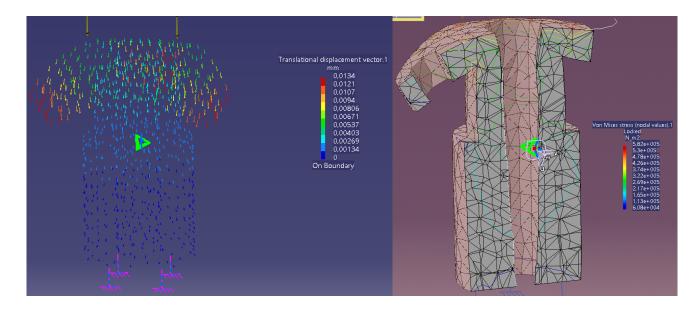

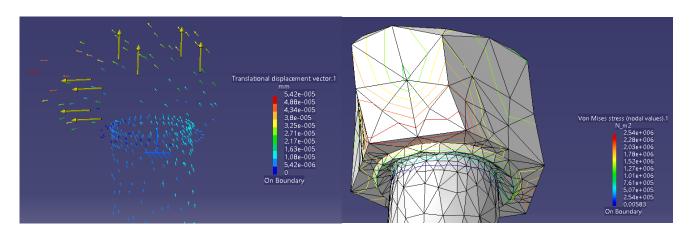

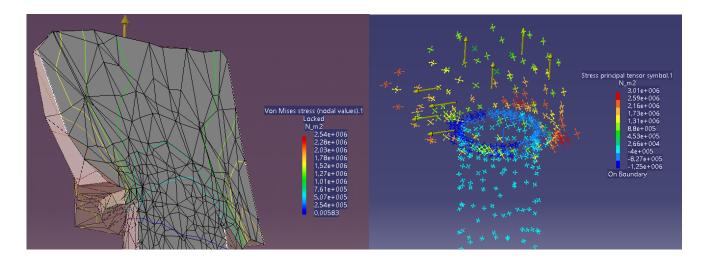

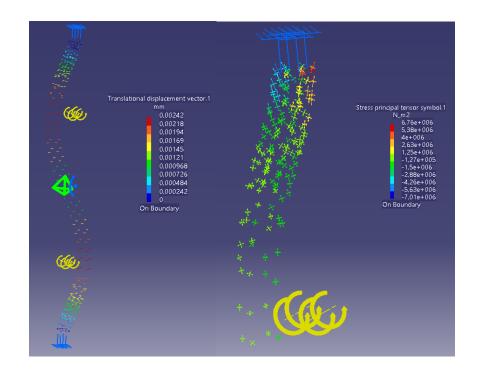

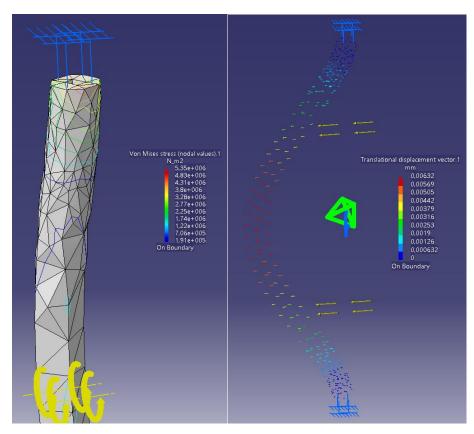

| Figure 84: Guide shaft analysis                                                                         | 93  |

|---------------------------------------------------------------------------------------------------------|-----|

| Figure 85: Guide shaft analysis                                                                         | 93  |

| Figure 86: Guide shaft analysis                                                                         | 94  |

| Figure 87: Guide shaft analysis                                                                         |     |

| Figure 88: Mounting plate torque                                                                        | 95  |

| Figure 89: LabVIEW interface for angle of incidence and height control                                  | 96  |

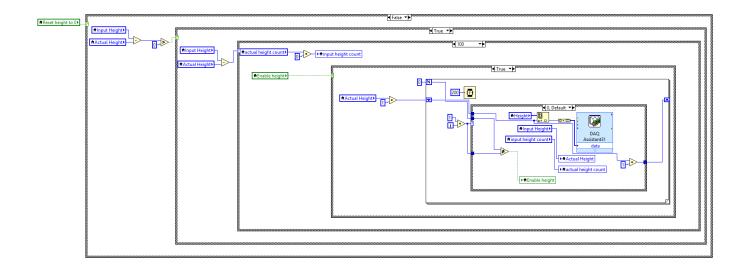

| Figure 90: LabVIEW code for motor control for height                                                    | 96  |

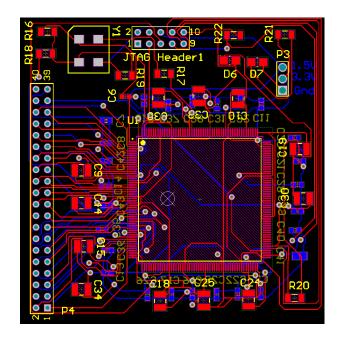

| Figure 91: Designed PCB intended to test                                                                | 97  |

| Figure 92: MicroSemi ProASIC3 A3P1000 chip and development board                                        | 99  |

| Figure 93: XIlinx Xup2developmentboard                                                                  | 99  |

| Figure 94: FruitFly Africa Co-60 source                                                                 | 100 |

| Figure 95: TID testing set up                                                                           | 100 |

| Figure 96: A-Line scattering chamber                                                                    | 101 |

| Figure 97: Vacuum chamber with test equipment installed                                                 | 101 |

| Figure 98: FGG.2B.319 male vacuum connectors                                                            | 102 |

| Figure 99: FGJ.2B.319 female vacuum connectors                                                          | 102 |

| Figure 100 :A3P1000 test board and Xilinx control board in chamber                                      | 102 |

| Figure 101: NI DAQ and chassis                                                                          |     |

| Figure 102: A3P1000 test board                                                                          | 102 |

| Figure 103: Control room at iTemba LABS facility                                                        | 102 |

| Figure 104: Image of proton beam striking the viewer                                                    | 103 |

| Figure 105: SEU mechanical fixture                                                                      | 103 |

| Figure 106: SEU mechanical fixture                                                                      | 103 |

| Figure 107: Rotating motor and gearbox                                                                  | 103 |

| Figure 108: ProASIC A3P1000 PQ208 FPGA with exposed die                                                 | 104 |

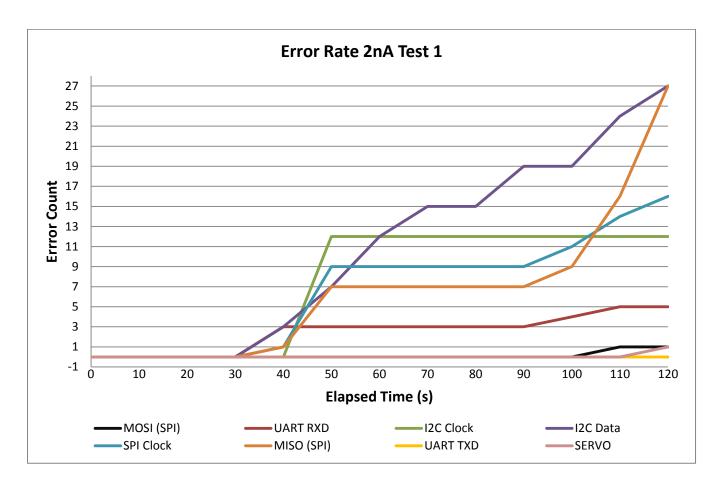

| Figure 109: Test 1 error rate results at 2nA                                                            | 107 |

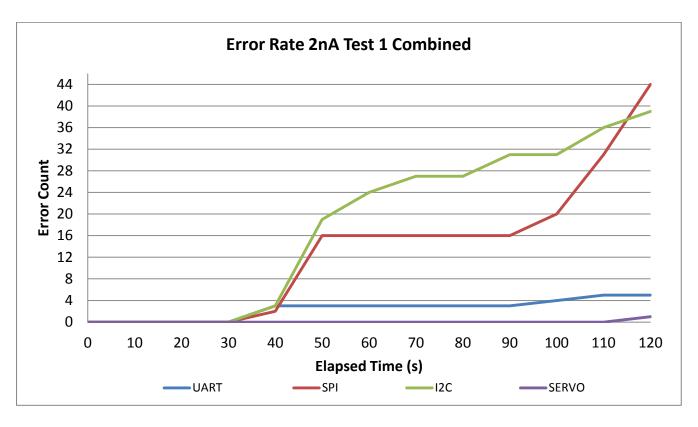

| Figure 110: Test 1 combined error rate results at 2nA                                                   | 108 |

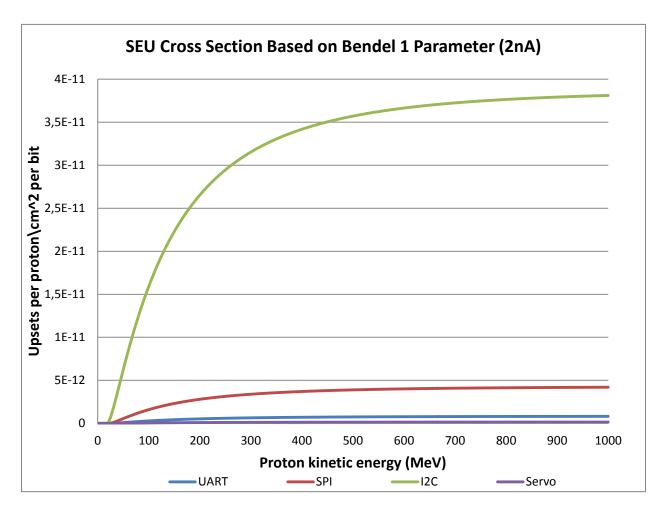

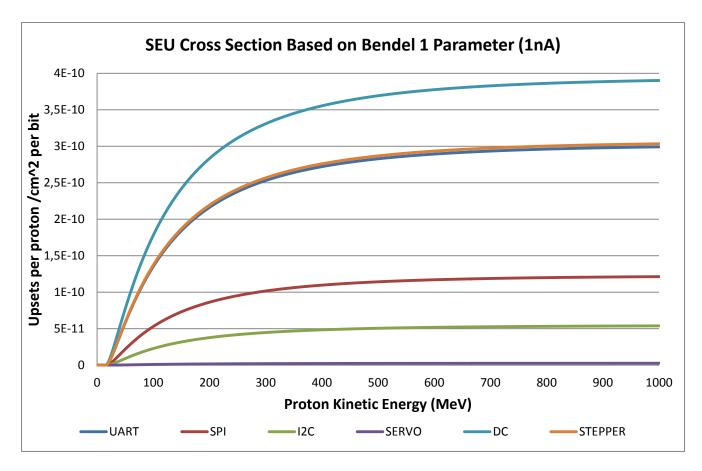

| Figure 111: SEU cross section for test circuits at 2nA from, Bendel 1 parameter equation                | 110 |

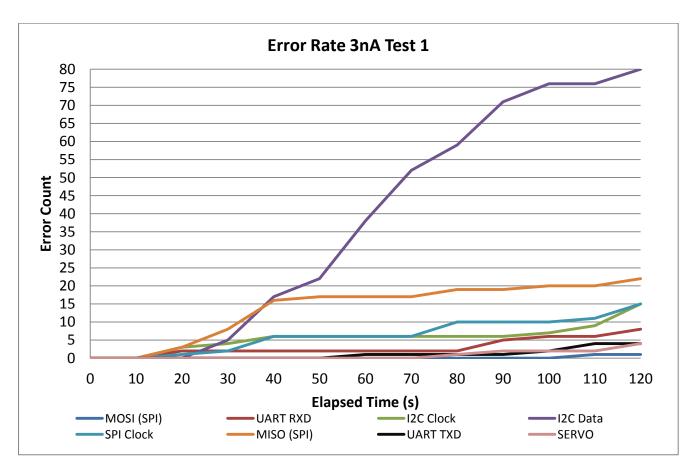

| Figure 112: Test 1 error rate results 3nA                                                               | 111 |

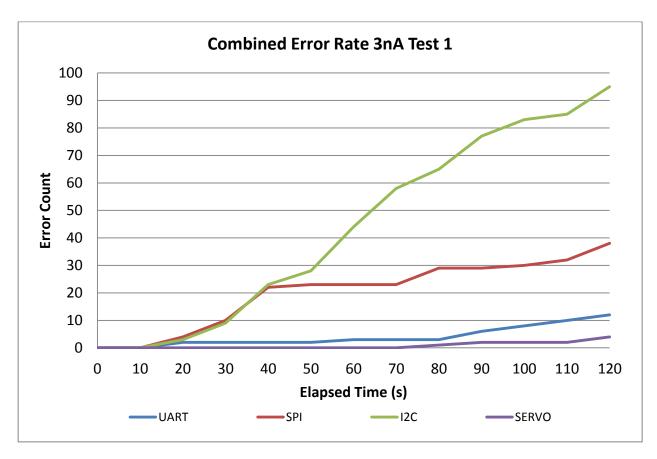

| Figure 113: Test 1 error rate results combined 3nA                                                      | 112 |

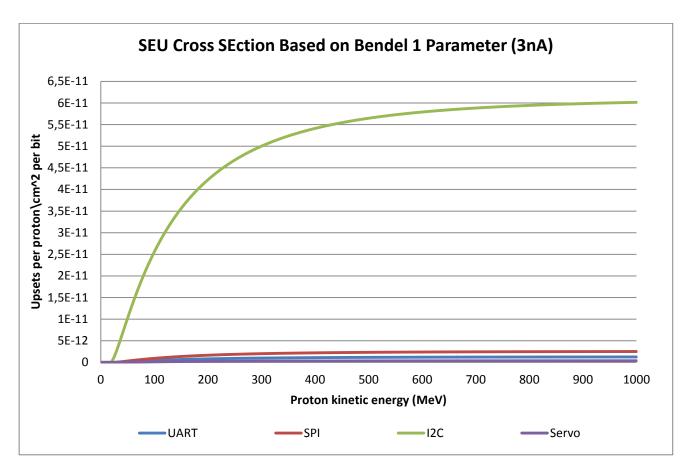

| Figure 114: SEU cross section for test circuits at 3nA, from Bendel 1 parameter equation                | 114 |

| Figure 115: SEU cross section for test circuits at 3nA, from Bendel 1 parameter equation for combined r | uns |

|                                                                                                         | 115 |

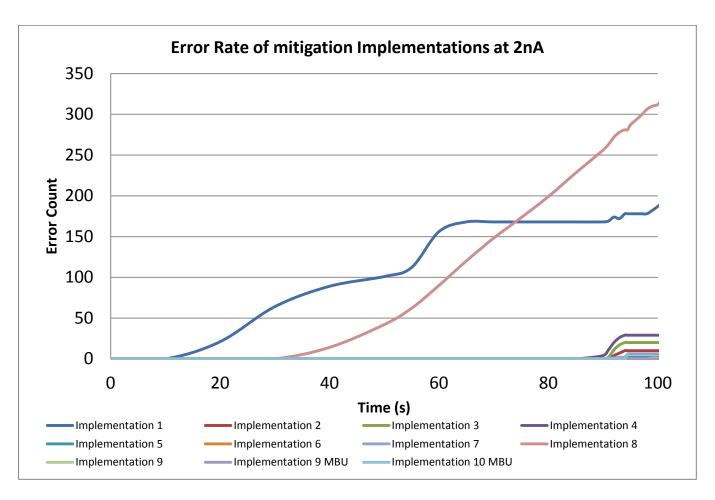

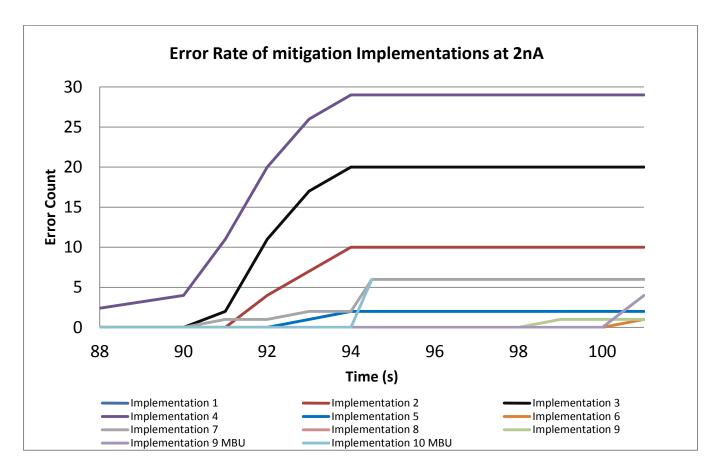

| Figure 116: Error rate for implemented mitigation schemes at 2nA                                        | 116 |

| Figure 117: Scaled SEU error rate of Figure 116                                                         | 119 |

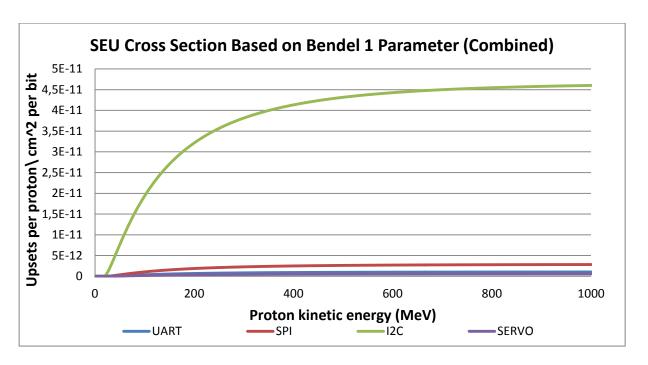

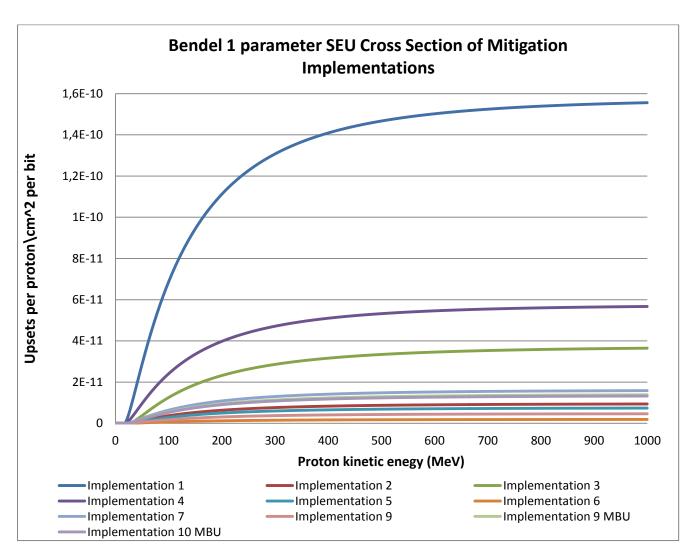

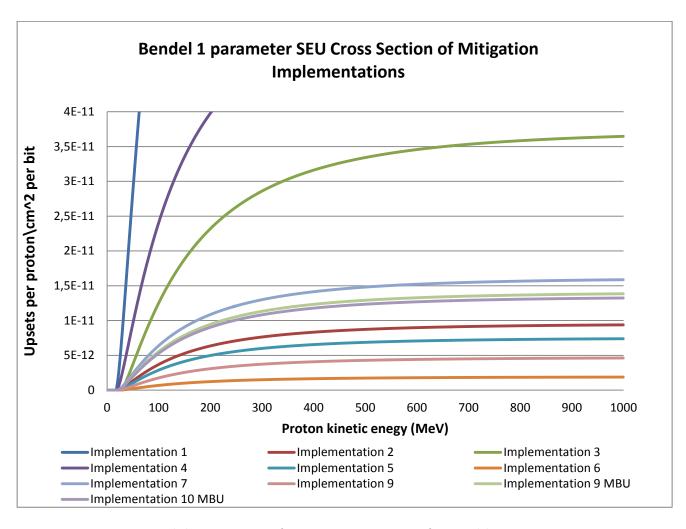

| Figure 118: SEU cross section for mitigation circuits at 2nA, from Bendel 1 parameter equation          | 121 |

| Figure 119: rescaled SEU cross section for mitigation circuits at 2nA, from Bendel 1 parameter equation | 122 |

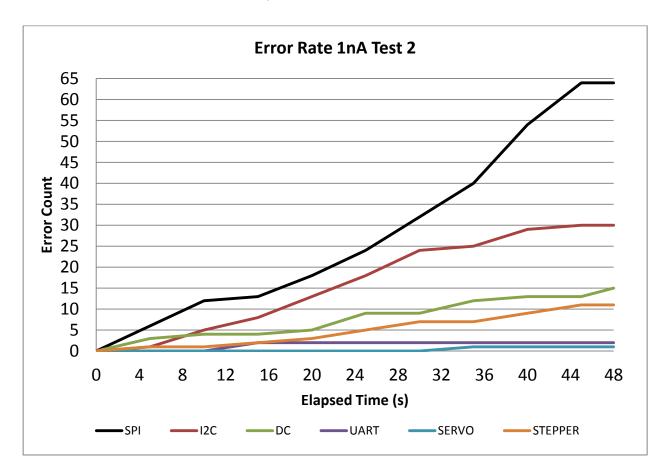

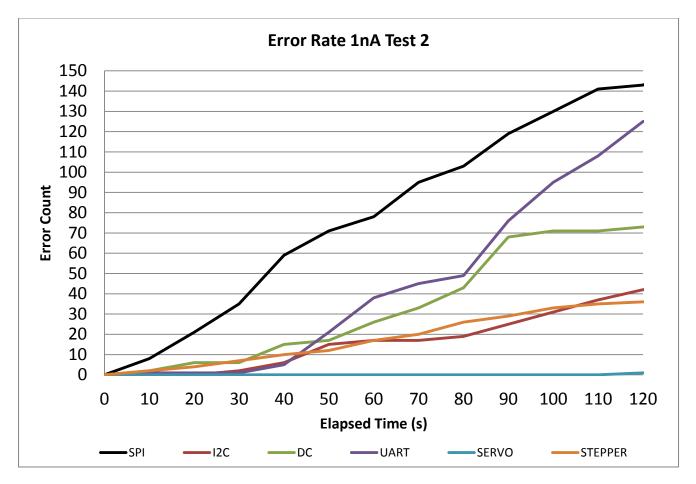

| Figure 120: Test 2 error rate results 1nA (run 1)                                                       | 123 |

| Figure 121: Test 2 error rate results 1nA (run 2)                                                       | 124 |

| Figure 122: SEU cross section for mitigation circuits at 1nA, from Bendel 1 parameter equation          | 126 |

| Figure 123: Test 2 error rate results 2nA                                                               |     |

| Figure 124: SEU cross section for mitigation circuits at 2nA, from Bendel 1 parameter equation          |     |

| Figure 125: SEU cross section for mitigation circuits for combined runs, from Bendel 1 parameter equati |     |

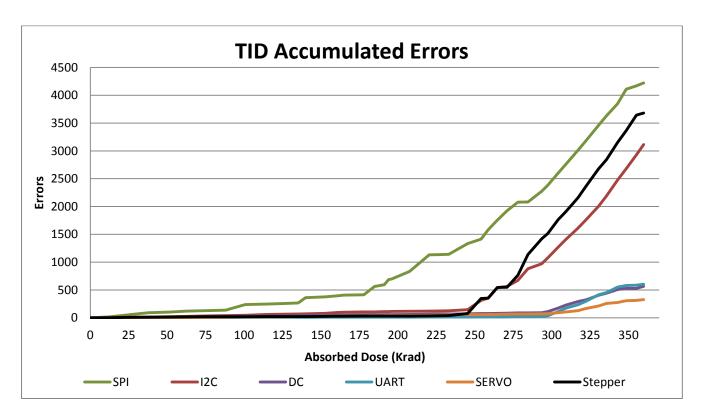

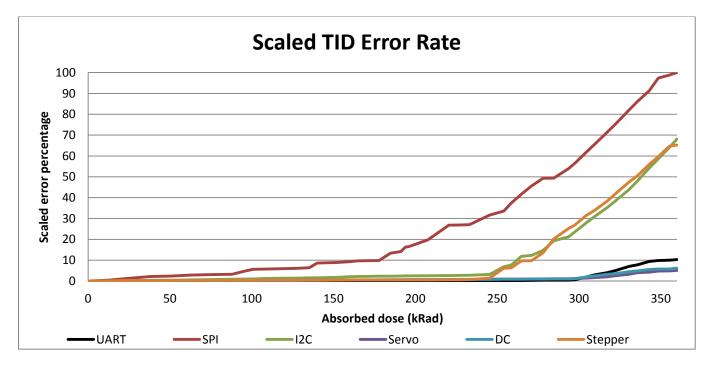

| Figure 126: TID error rate for test circuits                                                            | 132 |

|                                                                                                         |     |

| Figure 127: Rescaled TID error rate for test circuits       | 133 |

|-------------------------------------------------------------|-----|

| Figure 128: TID error rate scaled according to circuit size | 133 |

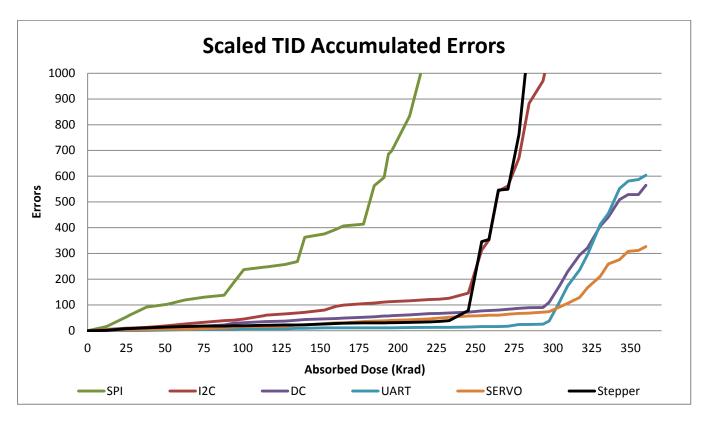

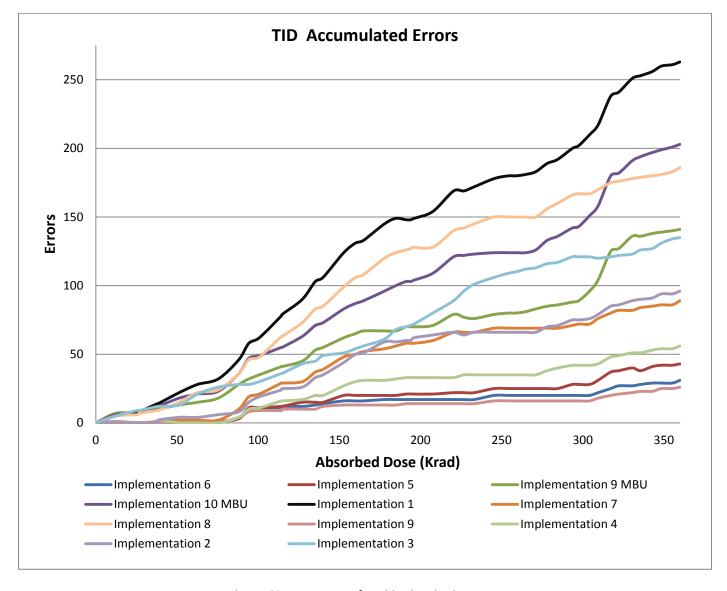

| Figure 129: TID error rate for mitigation circuits          | 135 |

| Figure 130: Scaled TID error rates                          | 136 |

| Figure 131: Supply current vs. absorbed dose                | 137 |

| Figure 132: Averaged supply current over 100 second periods | 138 |

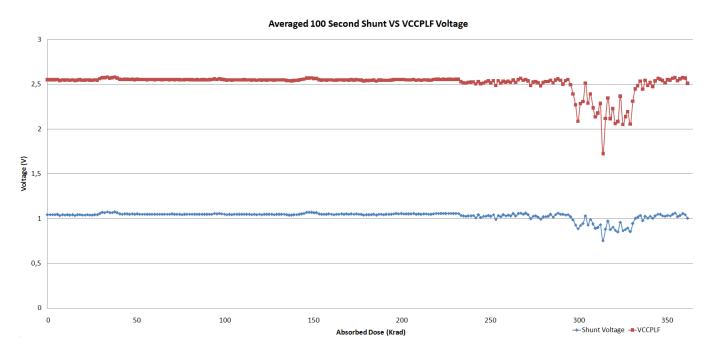

| Figure 133: Shunt and VCCPLF voltage vs. absorbed dose      | 138 |

| Figure 134: Averaged shunt resistor and VCCPLF voltages     | 139 |

## **List of Tables**

| Table 1: Solar flare dose with shielding in geostationary orbit                | 14  |

|--------------------------------------------------------------------------------|-----|

| Table 2: Characteristics of galactic cosmic rays [40]                          | 15  |

| Table 3: Daily dose for 500km/60 degree orbit during solar minimum [39]        |     |

| Table 4: Characteristics of SPEs [41]                                          | 19  |

| Table 5: Material specifications [101, 105]                                    | 88  |

| Table 6 : Beam and target parameters at 2nA                                    | 108 |

| Table 7: Circuit mapping of A3P1000                                            | 109 |

| Table 8: Cross section results for implemented circuits at 2nA                 | 109 |

| Table 9: Beam and target parameters at 3nA                                     | 112 |

| Table 10: Cross section results for implemented circuits test 1 at 3nA         | 113 |

| Table 11 : Cross section results for implemented circuits of combined runs     | 114 |

| Table 12: Circuit mapping of various implementation methods in A3P1000         | 119 |

| Table 13: Beam and test parameters at 2nA                                      | 120 |

| Table 14: SEU cross section results for implemented mitigation schemes at 2nA  | 120 |

| Table 15: Circuit mapping of various implementation methods in A3P1000         | 125 |

| Table 16: Beam and test parameters at 1nA                                      | 125 |

| Table 17: SEU cross section results for implemented circuits at 1nA            | 125 |

| Table 18: Beam and test parameters at 2nA                                      | 127 |

| Table 19: SEU cross section results for implemented circuits at 2nA            | 127 |

| Table 20: SEU cross section results for implemented circuits for combined runs | 128 |

| Table 21: TID test summary                                                     | 131 |

| Table 22: TID test summary for mitigation methods                              | 134 |

# **List of Equations**

| Equation 1  |   |

|-------------|---|

| Equation 2  |   |

| Equation 3  |   |

| Equation 4  | 8 |

| Equation 5  |   |

| Equation 6  |   |

| Equation 7  |   |

| Equation 8  |   |

| Equation 9  |   |

| Equation 10 |   |

| Equation 11 |   |

| Equation 12 |   |

| Equation 13 |   |

| Equation 14 |   |

| Equation 15 |   |

| Equation 16 |   |

## **Abstract**

The effectiveness of implementing field programmable gate arrays (FPGAs) in communication, military, space and high radiation environment applications, coupled with the increased accessibility of private individuals and researchers to launch satellites, has led to an increased interest in commercial off the shelf components. The metal oxide semiconductor (MOS) structures of FPGAs however, are sensitive to radiation effects which can lead to decreased reliability of the device.

In order to successfully implement a FPGA based system in a radiation environment, such as on-board a satellite, the single event upset (SEU) and total ionizing dose (TID) characteristics of the device must first be established. This research experimentally determines a research procedure which could accurately determine the SEU cross sections and TID characteristics of various mitigation techniques as well as control circuits implemented in a ProASIC3 A3P1000 FPGA.

To gain an understanding of the SEU effects of the implemented circuits, the test FPGA was irradiated by a 66MeV proton beam at the iTemba LABS facility. Through means of irradiation, the SEU cross section of various communication, motor control and mitigation schemes circuits, induced by high energy proton strikes was investigated. The implementation of a full global triple modular redundancy (TMR) and a combination of TMR and a AND-OR multiplexer filter was found to most effectively mitigate SEUs in comparison to the other techniques. When comparing the communication and motor control circuits, the high frequency I2C and SPI circuits experienced a higher number of upsets when compared to a low frequency servo motor control circuit.

To gain a better understanding of the absorbed dose effects, experimental TID testing was conducted by irradiating the test FPGA with a cobalt-60 (Co-60) source. An accumulated absorbed dose resulted in the fluctuation of the device supply current and operating voltages as well as resulted in output errors. The TMR and TMR filtering combination mitigation techniques again were found to be the most effective methods of mitigation

## **Key Words**

FPGA - Field Programmable Gate Array

ASIC - Application Specific Integrated Circuit

COTS - Commercial Off The Shelf

SEE - Single Event Effect

SEU - Single Event Upset

TID - Total Ionizing Dose

SET - Single Event Transient

## 1. Introduction

### 1.1 Overview

With the designed operational lifespan of modern satellites exceeding 10 years [1], in-field reprogrammability has become requirement in the design. Variations in the objectives, design or operational parameters could result in inadequate performance of the satellite system which may lead to partial or complete failure of the system. The implementation of reliable, long term and fully reprogrammable satellites will allow for adaptations to be made to the system due to developments of the objectives. Satellites will be able to perform both multiple interchangeable tasks and adapt to new requirements, increasing the effective lifespan.

Field programmable gate arrays (FPGAs) have been utilized in space applications for more than 10 years with varying results [2]. Only in recent years, have they gained popularity over the conventional application specific integrated circuits (ASICs). As a result of their high flexibility, together with high performance, complexity and the ability to feature more than one million system gates [2], FPGAs have become an ideal component of space applications.

The implementation of FPGAs in a radiation environment unfortunately poses a number of disadvantages. Total Ionizing Dose (TID) effects, caused by an accumulative dose of radiation, can induce a degradation of performance characteristics in, or result in failure of the FPGA. TID effects in FPGAs lead to the increase in computational times, increased leakage current, shifts in the device threshold voltages and permanent functional failure [3]. In addition to the permanent effects, temporary soft errors can also be experienced, resulting in bit flips in the memory elements of the device propagating through the circuitry and producing an error on the output of the circuit.

FPGAs are also susceptible to single event effects (SEEs) caused by heavy ion or ionized high energy particle strikes, depositing a charge in the device [4]. If the deposited charge surpasses the critical charge of the device, a resulting bit flip could be induced in the form of a single event transient (SET) [4]. This SET propagates throughout the circuitry of the device and, if latched into a memory element, results in a single event upset (SEU). This consequently results in the affected circuitry outputting an error. In addition to SEUs and other soft errors, permanent SEEs can also be induced, resulting in temporary failure, or at worst, permanent failure of the FPGA.

A large amount of research into the effects of space radiation has been conducted in order to better understand and mitigate the effects of an accumulation of dose and high energy particle strikes can be seen in [5, 6, 7, 8]. A large number of advanced radiation hardened devices have been developed by many of the FPGA manufacturing companies for applications in high radiation environments [9, 10]. However, these devices are available at very high costs in terms of capital, computational speeds, physical dimensions and the amount of resources available in the device. In most cases, radiation hardened FPGAs at the available cost, fail to minimize the effects which radiation imposes on the device. As a result, a growing interest in the feasibility of utilizing commercial off the shelf (COTS) FPGAs in these space based applications has emerged [2]. Consequently, numerous tests have been conducted to determine the SEU cross section, TID characteristics and expected operating life span of numerous commercially available FPGAs [7, 11, 12, 13].

In an attempt to mitigate space radiation effects, various mitigation schemes have been invented and patented. An example of a TID mitigation scheme which aims to extend the operational life span of the device can be seen in [11]. A growing number of mitigation schemes, aimed at reducing the effects of SEEs due to high energy particle strikes in FPGAs, been developed as a response to the increased interest in implementing FPGAs in space applications.

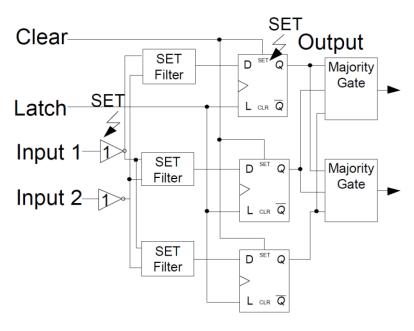

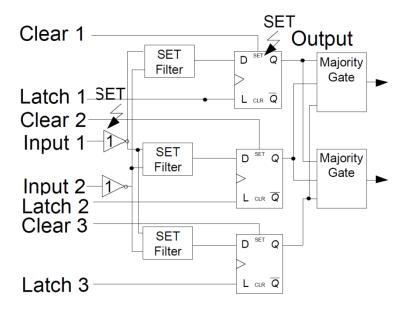

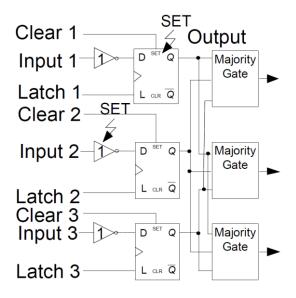

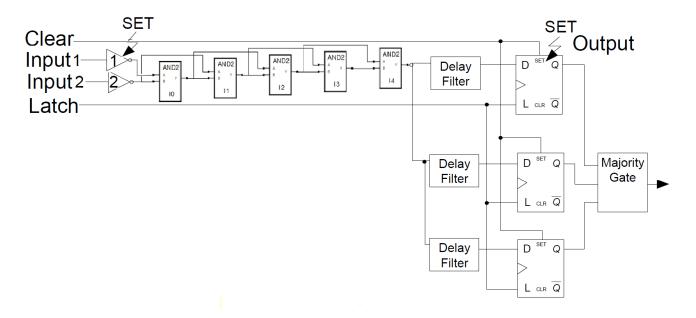

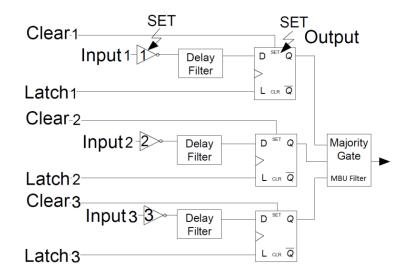

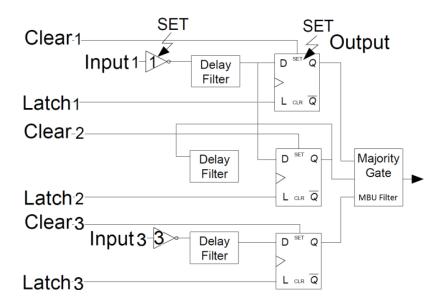

The most common of these, triple modular redundancy (TMR), is based on a principle that implements a series of three flip-flops or latches, as oppose to one, followed by a majority voter, which determines the state of the output by considering all three. TMR may be applied locally to memory elements alone or globally to the user logic, global signals and memory elements [14]. Although global TMR has been proven to mitigate SEUs effectively, it requires at least triple the amount of additional overhead resources [15]. An alternative mitigation approach can be seen in [16, 17] where three identical FPGAs have been programmed, with the outputs voted externally, to the devices in order to detect any errors in the device. The FPGA from which the error originates is reprogrammed to restore the internal state of the device's configuration memory (SRAM device). A specialized mitigation technique described in [18] enables the identification and classification of errors as either being due to permanent faults or transients, as well as identifying if the error affects a replicating module, user voter or the mitigation scheme itself [19]. This self-checking capability allows for the origin of the internal fault to be identified and corrected. This mitigation scheme has been implemented in the Xilinx XC4000 FPGA.

SEU protection insertion discussed in [20] utilizes a tool which implements SEU protection mechanisms for both the FPGA memory elements and registers automatically. The protection is implemented in the VHDL code and is based on Hamming coding and two dimensional parity arrays.

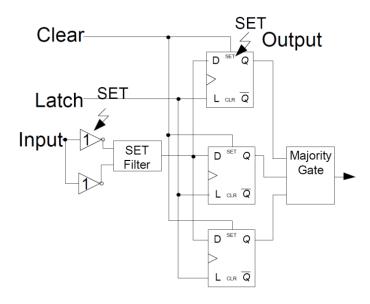

The guard-gate mitigation scheme seen in [21] makes use of a SET filter, consisting of an inverter string which delays the signal along a path. All signals with a pulse width shorter than the delay are filtered out, in essence filtering out the transient and preventing it from being latched into memory.

The AND-OR multiplexer SET filter described in [15] mitigates SEUs by filtering out single event transients. The mitigation technique offers two variations for implementation in circuits where single or double input lines are available. The mitigation scheme can be seen to be combined with TMR to ensure effective mitigation.

The main contribution of this thesis was to develop an experimental procedure to experimentally determine the single event upset and total ionizing dose effects of the ProASIC3 A3P1000 flash based FPGA in a space radiation environment. The research presented aimed to examine the SEU cross section and TID effects of various mitigation schemes and control circuits implemented in the A3P1000. It also aimed to determine the effectiveness of the implemented mitigation schemes in order to draw comparisons between them.

#### 1.2 Outline of the thesis

#### 1.2.1 Chapter 2

Chapter 2 covers the theoretical background topics related to the single event upset and total ionizing dose testing. A summary of the space orbits and environment in which satellites operate in presented, followed by the common radiation sources found in space. This chapter also provides a brief description of CMOS, MOSFET, ASIC and FPGA devices and discusses the single event effects and total ionizing dose effects on FPGAs, which forms the basis of testing during this research.

#### 1.2.2 Chapter 3

Chapter 3 discusses the research motivation for this project, as well as the real world effects of radiation. The shortcomings of current solutions to the radiation effects faced in a space based

applications are then discussed, together with a new focus on the use of commercial off the shelf components in these space applications. Radiation hardened FPGAs and current mitigation schemes are then discussed which aim to reduce and even eliminate the effects which radiation plays on the device. This chapter aims to provide an overview of the current issues faced and proposed solutions suggested when considering the implementation of a FPGA in a space based application.

#### 1.2.3 Chapter 4

In chapter 4 the research procedure is described in detail. The primary objectives of the experimental tests conducted are described, together with a description of the ProASIC3 A3P1000 device used during testing. The SPI, I2C, UART communication protocols, in addition to the DC, stepper and servo motor control circuits implemented in the FPGA during testing, are described in detail in order to gain a better understanding of the implemented code which was tested. The various mitigation techniques implemented are also described in this chapter, outlining the structure of each such that a clear comparison can be made between them. The data acquisition device and method of capturing and monitoring data is described together with the experimental set-up for both the SEU and TID testing conducted. Furthermore, the design of the mechanical system implemented at the iTemba LABS facility can be seen in this chapter. This chapter also illustrates the detailed design schematics and strength analyses required to design and implement the mechanical platform. The LabVIEW code written for the control of the mechanical system, as well as for the data monitoring, can be found in this chapter. Photographs of the experimental set up and equipment at both the TID and SEU testing facilities are also included in this chapter.

#### 1.2.4 Chapter 5

Chapter 5 presents the results obtained from both the high energy proton SEU testing and the absorbed dose response TID testing. The SEU results from the two testing sessions, each consisting of multiple tests, will be presented and discussed to describe the error rate observations as well as the SEU cross sections of the test circuits implemented in the FPGA. The TID results obtained from the testing conducted at the FruitFLY facility are also presented in this chapter. The error rate of each of the implemented circuits as well as the device current and voltage characteristics will be presented and discussed.

## 1.2.5 Chapter 6

Chapter 6 discusses the data presented in chapter 5 and draws conclusions from the experiments conducted. The findings thereof are presented, together with recommendations for related future work and improvements which would prove to be beneficial if similar testing were to be conducted.

## 2 Theoretical Background

Space is a harsh environment characterised by the presence of various sources and levels of radiation, vast ranges of temperatures, virtually no gravity effects, very low density of matter and an almost perfect vacuum. When implementing an electrical, mechanical or control system in a space environment, it is essential to consider these factors, especially the extreme temperatures and the radiation and vacuum effects of space on the components to be used. Either one of these variables could result in the malfunctioning of components or systems, in turn, resulting in the failure of the mission. The following sections will introduce a basic theoretical background to certain aspects of the space environment and related concepts.

## 2.1 Fundamental Concepts

#### **2.1.1** Energy

Radiation energy is generally defined in terms of the Electron Volt (eV). The electron volt is not a SI unit, but rather a value that must be experimentally determined. The electron volt is a unit of energy approximately equal to  $1.60217657 \times 10^{-19}$  joules and is defined as the amount of kinetic energy gained by a single unbound electron as it is accelerated through an electric potential difference of one volt [22]. The Electron volt was defined as a standard as a result of the usefulness in electrostatic particle accelerator sciences as a particle with charge q has an energy of E=qV once passed through a potential V [22].

#### 2.1.2 Radiation Dose

Radiation can be measured and described in two units. The first is a measure of the rate of exposure experienced. The second is a measure of the total amount of radiation accumulated over a specific time period. Radiation dose is a measurement of the energy deposited by a source of ionizing radiation per unit mass of a specific material. The SI unit of the absorbed radiation dose is joules per kilogram, named gray (Gy), and the non-SI unit being the rad. The relationship between the rad and gray can be seen in equation 1 [23].

1 rad = 1 Ergs/g

1 Gy = 1 J/kg

$$Dose = \frac{\Delta E}{\Delta m}$$

and  $1Gy = 1\frac{J}{kg} = 100 \ rads = 10^4 \ Ergs/g$

#### Equation 1

The absorbed dose is defined as the amount of energy ( $\Delta E$ ) deposited by the ionizing radiation per unit mass of material ( $\Delta m$ ) [24]:

#### 2.1.3 Flux

The flux can be defined as the number of particles passing through a 1 cm<sup>2</sup> area during a 1 second interval. The unit is thus particle/cm<sup>-2</sup>s<sup>-1</sup>.

$$\Phi = \frac{\dot{Photons}}{Area\ Time}$$

## **Equation 2**

## 2.1.4 Fluence

The fluence is obtained by integrating the flux over the time giving the unit particles/cm<sup>-2</sup>.

$$\Phi = \frac{Photons}{Area}$$

#### **Equation 3**

#### 2.1.5 Linear Energy Transfer

The linear energy transfer (LET) is defined as the amount of energy deposited per unit length and is represented in units of eV/cm [24]. The LET of a charged particle is known to be proportional to the square of the charge and inversely proportional to the kinetic energy of the particle defined as:  $Q^2/E_k$ . The LET is also a product of specific ionization and the average energy deposited per ion pair [24].

The LET has the unit MeV/(g/cm2) and is defined by the following equation:

$$LET = \frac{1}{\rho} \frac{dE}{dx}$$

#### **Equation 4**

Where  $\rho$  is the density of the material, E is the energy loss through the material and x is the distance.

#### 2.2 Orbits

The orbit or region of space in which the designed system will operate in will be of great importance when designing the electrical and mechanical subsystems. The orbit in which the space platform will operate will determine the instantaneous energy and total dose of the radiation experienced by the platform. When considering the amount of radiation which will be present in the desired operating region of space, the operating characteristics and expected operating life cycle of the system can be estimated. Satellite orbits can be broadly classified into the low earth orbit, medium earth orbit and high hearth orbit.

#### 2.2.1 High Earth Altitude and ground

The high earth altitudes occupied by commercial and military aircrafts range from of 30 000 feet (9.144km) to 60 000 feet (18.288km) [25, 26, 27]. Sensitive electronics on board these aircrafts will experience high energy particle strikes from galactic cosmic rays, as well as total ionizing dose accumulation. The GCR flux exposure is approximately doubled for each 6000 feet increase in altitude, reaching a maximum at 60 000 feet. SEE are of greater importance at these altitudes than TID. The amount of absorbed radiation in a 20 year life cycle of an avionic system would be in the region of 110 rad, a large factor less than required to induce any errors [25, 26, 27]. Only SEEs are considered at ground level as the amount of absorbed radiation will have no impact on electronics. Figures 1 and 2 show the various flux measurements at varying altitudes and latitudes.

Figure 1: Flux at varying latitudes [26]

Figure 2: Flux at various altitudes [26]

Figures 3 and 4 [25] illustrates the measured and calculated dose rate on board two different flights.

Figure 3: Dose rate on board a Concorde flight [25]

Figure 4: Dose rates on-board an A310-300 flight [25]

#### 2.2.2 Low Earth Orbit

Low earth orbit is characterized by an approximate distance of 160 to 1 400 kilometres away from the surface of the earth [28]. The majority of scientific research, weather monitoring, satellite phone and military satellites are found in this orbit.

Low earth orbit satellites primarily experience ionizing radiation from sources such as galactic cosmic rays (GCRs), energetic electrons and protons trapped in the geomagnetic field and the earth's natural radiation belts and solar particle events (SPEs) [29].

#### 2.2.3 Medium Earth Orbit

Medium earth orbits are classified as being a distance of 6 000 to 27 000 kilometres from the earth's surface and is primarily used by global positioning system (GPS), observation, weather and spy satellites [30]. Medium earth orbits include a semi-synchronous orbit which allows a satellite to constantly cross over the same position on the equator each day. This also includes the Molniya orbit, which allows a satellite to access and communicate with in the far northern and southern areas of the earth's surface as oppose to the geostationary satellites [30].

The primary source of radiation found in the medium earth orbit originates from the Van Allen radiation belts [31]. Additional radiation sources also include galactic cosmic rays and solar particle events.

### 2.2.4 Geostationary Orbit

This orbit is defined by a distance of approximately 36 000 kilometres from the surface of the earth. The most common satellites found in this orbit include weather, television, long distance communication, internet and GPS satellites. Geostationary satellites at a distance of approximately 36 000 kilometres have a constant velocity of 11080 km/h about the equator and follow the earth's rotation as a result. The geostationary satellites are able to maintain their relative position over a longitude, but may drift north or south. These satellites have little capabilities to monitor the northern or southern areas of the earth. [28, 30].

The primary source of ionizing radiation in the geostationary orbit originates from the outer electron belt of the earth's trapped radiation belts. Additional sources include radiation from solar particle events and galactic cosmic rays.

#### 2.2.5 High Earth Orbit

High earth orbits are classified as being more than 36 000 kilometres above the surface of the earth and are commonly occupied by space observation and weather observation satellites [32]. Space systems found in the high earth orbit have no protection from the earth's magnetic field and thus are vulnerable to galactic cosmic rays and solar particle events. Figure 5 illustrates the basic Earth orbit layout.

Figure 5: Basic orbit layout [32]

## 2.3 Space Radiation Environment

#### 2.3.1 Vacuum

In addition to the presence of radiation, the space environment can also be characterized by a lack of matter (vacuum) and atmosphere. Only a few hydrogen and helium atoms can be found per square meter, and additionally, due to the gravitational pull of larger bodies in space such as planets, the atoms are found closer to these bodies [33, 34]. The lack of air in space prevents the transfer of heat from components such as motors or voltage regulators into the atmosphere, preventing the components from being able to dissipate heat at the required rate. Another consideration to take into account when designing the electrical or mechanical system is the physical properties of the component. An electrical component which contains trapped air will result in a pressure difference between the outer space environment, this internal structure will then result in the failure of the component. The pressure difference between, for example, the trapped air and the vacuum will lead to the physical failure of the device.

The same applies to motors and bearings which are manufactured in such a manner that trapped air cannot escape. In addition to the previously stated design considerations, lubrication is not able to function correctly in a vacuum or non-gravity environment. The lubrication substance will leak from its original position and spread to other unintended locations. In applications where lubrication is essential, such as high revolution bearings, it will be required to make the correct design choices when considering components which will experience large amounts of motion [33, 34].

## 2.3.2 Temperature

The temperature of components in space is determined by the presence or lack of sunlight shining onto the component. A piece of metal exposed to sunlight for example, can reach temperatures of 260 degrees Celsius and, when in shade, can drop to far below -100 degrees Celsius [35]. A special coating may be applied to the surface of exposed metals, resulting in a temperature range of the materials between 120 to -129 degrees Celsius [36]. Precautions must be taken as to the specified operating temperatures of any mechanical or electrical components implemented on board a space platform.

#### 2.3.3 Radiation

The measuring and quantifying of the radiation environment in space has long been an area of interest for many scientists and companies. The space environment typically consists of a large variety of primary particles of varying ranges of energies and secondary particles created by a number of different nuclear interactions [29]. Even though the large numbers of particles have a wide range of energies, their flux is often low. Occurrences such as solar flares are often the only times at which the flux levels are dramatically higher. This variation in energy and flux levels requires the components, which are implemented in a space system, to be robust.

Naturally occurring radiation in space comprises of protons, electrons and heavy ions of elements from the periodic table [37] as well as secondary neutrons created by interactions of solar particles with the atmosphere and materials. Radiation can be defined as energy in motion in the form of high speed particles or electromagnetic waves [38] and can further be classified as being either ionizing or non-ionizing radiation.

lonizing Radiation has adequate energy to remove electrons from atoms, thus creating charged particles. Due to the high energy of the radiation, electrons from inner orbits are able to be removed creating a highly unstable atom. Sources of high energy ionizing radiation include protons and gamma rays.

Non-ionizing radiation does not have sufficient energy to remove electrons from atoms and thus are not considered to negatively impact any part of electronic space operations. Sources of non-ionizing radiation include radio waves and microwaves [38].

## 2.4 Radiation Sources

FPGAs in the space environment will mainly be implemented on board satellites and data collecting space craft systems, the more common being satellites. Most satellites are found in low, medium and high earth orbits where radiation source typically include plasma radiation, trapped radiation, cosmic rays and solar flares [39]. Any space system in operation will be exposed to radiation originating from a number of sources characterized by varying energy and magnitudes of flux. The

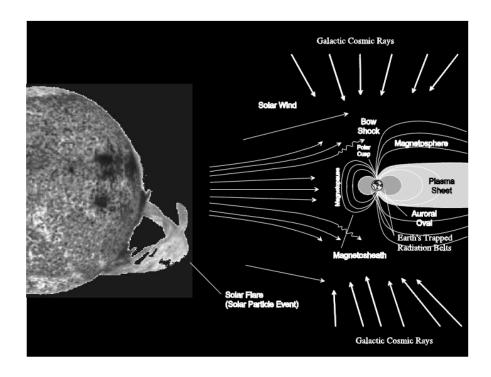

three principal sources of space radiation are; galactic cosmic rays, trapped radiation and solar particle events. Figure 6 demonstrates the principal space radiation sources.

Figure 6: Principal space radiation sources [29]

### 2.4.1 Galactic Cosmic Rays

Galactic cosmic rays consist of high energy particles, the majority of which are protons, originating from space. The main contributing particles for electronics include neutrons and protons.

#### 2.4.1.1 Ionizing Radiation Dose

The ionizing radiation dose originating from GCRs can be seen as insignificant compared to that of trapped radiation. Flux originating from GCRs are affected and attenuated by the geomagnetic field which prevents penetration of low orbits of low inclinations [39]. The main variable is the inclination of the orbit, as seen in the example of a 500 km 30 degree inclination orbit, there is almost no penetration, but for a 500 km 57 degree inclination orbit, where penetration occurs and for polar orbits the exposure is high at any altitude [39].

Despite the fact that geomagnetic shielding is ineffective for GEO, the average dose for ordinary events with a spherical shielding of 2 gram/square centimetre is approximately 18 rad (Si)/year. For an anomalously large flare and the same shielding as mentioned above, the dose would be as high as 600 rad(Si)/event [39].

Table 1 shows solar flare shielded doses for 1 anomalously large event for the geostationary orbit [39].

Table 1: Solar flare dose with shielding in geostationary orbit

| MAGNETOSPHERICALLY MAGNETOSPHERICALLY MAGNETOSPHERICALLY |              |              |           |                       |           |               |  |  |

|----------------------------------------------------------|--------------|--------------|-----------|-----------------------|-----------|---------------|--|--|

|                                                          | UNATTENUATED |              |           | ATTENUATED TO 70DEG W |           | D TO 160DEG W |  |  |

| S                                                        | SLAB(4PI)    | SOLID SPHERE | SLAB(4PI) | SOLID SPHERE          | SLAB(4PI) | SOLID SPHERE  |  |  |

| (GM/SQCM)                                                | (RADS-S1)    | (RADS-SI)    | (RADS-SI) | (RADS-SI)             | (RADS-SI) | (RADS-SI)     |  |  |

|                                                          |              |              |           |                       |           | 1 1           |  |  |

| 0.01                                                     | 4.690E+03    | 4.597E+03    | 4.796E+02 | 4.782E+02             | 2.680E+02 | 2.675E+02     |  |  |

| 0.02                                                     | 4.762E+03    | 4.645E+03    | 4.810E+02 | 4.781E+02             | 2.686E+02 | 2.674E+02     |  |  |

| 0.03                                                     | 4.812E+03    | 4.688E+03    | 4.824E+02 | 4.782E+02             | 2.692E+02 | 2.675E+02     |  |  |

| 0.04                                                     | 4.846E+03    | 4.737E+03    | 4.838E+02 | 4.784E+02             | 2.696E+02 | 2.675E+02     |  |  |

| 0.05                                                     | 4.868E+03    | 4.788E+03    | 4.850E+02 | 4.786E+02             | 2.702E+02 | 2.676E+02     |  |  |

| 0.06                                                     | 4.878E+03    | 4.850E+03    | 4.862E+02 | 4.788E+02             | 2.708E+02 | 2.676E+02     |  |  |

| 0.08                                                     | 4.872E+03    | 4.950E+03    | 4.886E+02 | 4.794E+02             | 2.718E+02 | 2.678E+02     |  |  |

| 0.10                                                     | 4.828E+03    | 5.221E+03    | 4.910E+02 | 4.802E+02             | 2.728E+02 | 2.680E+02     |  |  |

| 0.20                                                     | 4.004E+03    | 5.875E+03    | 5.000E+02 | 4.849E+02             | 2.768E+02 | 2.696E+02     |  |  |

| 0.30                                                     | 3.202E+03    | 5.117E+03    | 5.062E+02 | 4.902E+02             | 2.802E+02 | 2.716E+02     |  |  |

| 0.40                                                     | 2.680E+03    | 4.429E+03    | 5.110E+02 | 4.950E+02             | 2.826E+02 | 2.737E+02     |  |  |

| 0.50                                                     | 2.298E+03    | 3.957E+03    | 5.144E+02 | 4.998E+02             | 2.846E+02 | 2.758E+02     |  |  |

| 0.60                                                     | 2.004E+03    | 3.553E+03    | 5.168E+02 | 5.051E+02             | 2.862E+02 | 2.776E+02     |  |  |

| 0.70                                                     | 1.774E+03    | 3.216E+03    | 5.182E+02 | 5.108E+02             | 2.874E+02 | 2.794E+02     |  |  |

| 0.80                                                     | 1.587E+03    | 2.966E+03    | 5.190E+02 | 5.168E+02             | 2.884E+02 | 2.814E+02     |  |  |

| 0.90                                                     | 1.428E+03    | 2.727E+03    | 5.188E+02 | 5.232E+02             | 2.892E+02 | 2.836E+02     |  |  |

| 1.00                                                     | 1.296E+03    | 2.512E+03    | 5.180E+02 | 5.297E+02             | 2.898E+02 | 2.860E+02     |  |  |

| 1.25                                                     | 1.038E+03    | 2.134E+03    | 5.130E+02 | 5.488E+02             | 2.900E+02 | 2.921E+02     |  |  |

| 1.50                                                     | 8.504E+02    | 1.795E+03    | 5.038E+02 | 5.690E+02             | 2.890E+02 | 2.988E+02     |  |  |

| 1.75                                                     | 7.120E+02    | 1.592E+03    | 4.908E+02 | 6.002E+02             | 2.868E+02 | 3.061E+02     |  |  |

| 2.00                                                     | 5.978E+02    | 1.402E+03    | 4.736E+02 | 6.153E+02             | 2.834E+02 | 3.144E+02     |  |  |

| 2.50                                                     | 4.430E+02    | 1.037E+03    | 4.244E+02 | 7.829E+02             | 2.736E+02 | 3.334E+02     |  |  |

| 3.00                                                     | 3.424E+02    | 8.769E+02    | 3.406E+02 | 8.544E+02             | 2.592E+02 | 3.626E+02     |  |  |

| 3.50                                                     | 2.654E+02    | 7.021E+02    | 2.654E+02 | 6.989E+02             | 2.394E+02 | 3.929E+02     |  |  |

| 4.00                                                     | 2.136E+02    | 5.719E+02    | 2.136E+02 | 5.725E+02             | 2.118E+02 | 4.972E+02     |  |  |

| 4.50                                                     | 1.733E+02    | 4.956E+02    | 1.733E+02 | 4.954E+02             | 1.733E+02 | 5.004E+02     |  |  |

| 5.00                                                     | 1.418E+02    | 4.160E+02    | 1.418E+02 | 4.161E+02             | 1.418E+02 | 4.147E+02     |  |  |

| 6.00                                                     | 9.860E+01    | 3.047E+02    | 9.860E+01 | 3.047E+02             | 9.860E+01 | 3.050E+02     |  |  |

| 8.00                                                     | 5.120E+01    | 1.759E+02    | 5.120E+01 | 1.759E+02             | 5.120E+01 | 1.759E+02     |  |  |

| 10.00                                                    | 2.870E+01    | 1.094E+02    | 2.870E+01 | 1.094E+02             | 2.870E+01 | 1.094E+02     |  |  |

| 15.00                                                    | 7.984E+00    | 3.464E+01    | 7.984E+00 | 3.464E+01             | 7.984E+00 | 3.464E+01     |  |  |

| 20.00                                                    | 2.558E+00    | 1.580E+01    | 2.558E+00 | 1.580E+01             | 2.558E+00 | 1.580E+01     |  |  |

| 30.00                                                    | 1.104E-01    | 1.250E+00    | 1.104E-01 | 1.250E+00             | 1.104E-01 | 1.250E+00     |  |  |

## 2.4.1.2 Single Event Effects

Galactic cosmic rays and anomalously large events for transitioning protons are the most likely sources to cause SEEs. Cosmic ray induced SEEs are much more common than proton induced SEEs at altitudes below 1000 km and above 4000 km for 60 degree circular orbits [39]. The earth's magnetic field shields low inclination orbits from cosmic rays, resulting in a decrease as oppose to the proton upset rates. Higher inclination orbits thus experience higher upset rates due to cosmic radiation.

Galactic cosmic rays (GCRs) originate from outside of our solar system and are speculated to be isotropic throughout space. GCRs particles in our solar system have been measured to have energies of between tens up to 10<sup>12</sup> MeV (10 GeV) nucleon<sup>-1</sup> and have the highest penetrating capabilities of

the ionizing radiation types [40]. Sources of GCRs mainly include supernovae and neutron starts within our galaxy and partially from our sun. The magnetic field of the sun, as well as solar winds, modulate the flux of ions with energies of 10 GeV or less and a large attenuation of the flux is experienced during the high activity solar maximum periods. [41].

Table 2: Characteristics of galactic cosmic rays [40]

| Hadron<br>Composition [11]                   | Energies                       | Flux                                     | Radiation<br>Effects | Metric |

|----------------------------------------------|--------------------------------|------------------------------------------|----------------------|--------|

| 87% protons<br>12% alphas<br>1% heavier ions | Up to ~10 <sup>11</sup><br>GeV | 1 to 10 cm <sup>-2</sup> s <sup>-1</sup> | SEE                  | LET    |

The GCR spectrum comprises of 98% protons and heavy ions (baryon component) and 2% electrons and positrons (lepton component) and the baryon component consists of 87% protons, 12% helium ions (alpha particles) and 1% heavy ions [40] as seen in Table 2. The high energy heavy ions are of great importance in single event effects (SEE) testing and have high linear energy transfer (LET) and penetrating characteristics. The flux of the GCR is usually in the range of 1 to  $10 \text{cm}^{-2} \text{s}^{-1}$  and dependent on solar cycles [41].

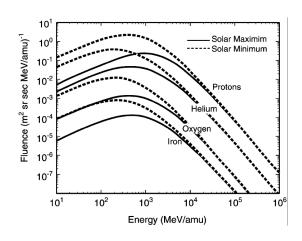

Figure 7 illustrates the typical GCR energy spectrum of a few elements during a solar minimum and maximum [41].

Figure 7: GCR energy spectra for protons, helium, oxygen and iron [41]

Due to the particle composition of GCRs, low energy particles readily lose their energy once they penetrate the magnetosphere and due to the earth's magnetic field as well as are deflected away

from the earth at the equator as a result of the geomagnetic field lines being parallel to the earth's surface, but the protection has no effect in the geosynchronous orbit (36 000km) where the earth's magnetic field is weak. The geomagnetic filed lines at the poles are directed towards the earth at the poles, resulting in GCR particles being funnelled towards the high altitudes [23, 29].

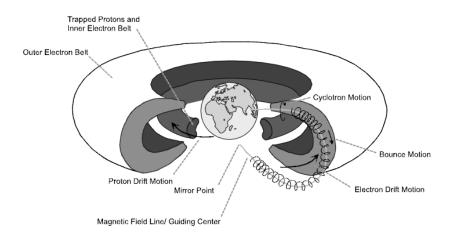

#### 2.4.2 Trapped Radiation

The radiation environment around the earth can be described as a high concentration of energetic ionizing electrons and protons together with small amounts of low energy heavy ions [39] which are trapped within two toroidal shaped radiation belts called the Van Allen Belts, found in the earth's magnetosphere [29, 40]. The inner radiation belt (IRB) is theorized to extend from approximately 0.1 to 2.4 earth radii and comprises of electrons of energies up to 5 to 10MeV and protons of energies up to approximately 700 MeV. The majority of trapped protons have energies of between 150 and 250 MeV and these energies and abundance decrease with the distance from the earth. The outer radiation belt (ORB), which extends from between approximately 2.8 to 4 earth radii, to between approximately 10 to 12 earth radii consists of electrons with energies below a maximum of 10MeV and no significant number of protons [29, 40]. The level flux found in the IRB is much lower than that found in the ORB resulting in higher dose rates for humans and electronics in this belt [41, 42]. Figure 8 illustrates the three types of motion of charged particles in the Earth's radiation bands.

Figure 8: In the Earth's radiation bands, three types of motion can be seen for charged particles, namely; cyclotron motion, bouncing motion and drift motion [29, 39]

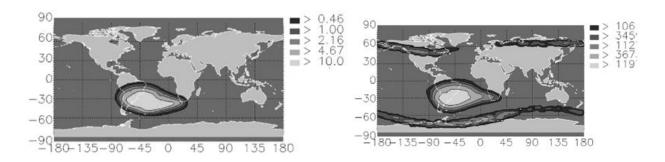

Due to the earth's axis of rotation and magnetic field axis being misaligned, a region known as the South Atlantic Anomaly (SAA) has been an important area of research and concern for low orbiting

space crafts. This area experiences high levels of trapped protons due to the intersection of the trapped proton belt with orbiting space crafts. Research has discovered that "for the 51.56° inclination, 400 km altitude orbit of the ISS, about half the ionizing radiation dose is due to trapped protons in the SAA and half originates from GCR at higher altitudes" [29]. Figures 8 and 9 show the flux curves over the SAA.

Figure 9: Iso-Flux curves for 9.4MeV protons [29]

Figure 10: Iso-Flux curves for 560keV electrons [29]

The movement of the trapped particles can be defined as circling around and bouncing along magnetic field lines, while also being reflected back and forth between mirror points in opposite hemispheres, as shown in Figure 8. [29, 39] Additional movement of particles include the longitudinal drift of electrons to the east and protons to the west [23].

At the geostationary orbit protons have energies between 100 keV and 1MeV, while electrons have energies of between 100keV and a few MeV [41].

## 2.4.2.1 Ionizing Radiation Dose

The calculated daily dose for LEO and GEO for an orbit altitude of 500km and inclination of 60 degrees [39] can be seen in Table 3.

Table 3: Daily dose for 500km/60 degree orbit during solar minimum [39]

| s       | т     | T       | ELEC      | BREM      | PROTON    | TOTAL     |

|---------|-------|---------|-----------|-----------|-----------|-----------|

| GM/SQCM | MM    | MILS    | RADS-AL   | RADS-AL   | RADS-AL   | RADS-AL   |

| 0.01    | 0.04  | 1.00    | 4.304E+02 | 1.679E-01 | 6.493E+01 | 4.955E+02 |

| 0.02    | 0.07  | 3.00    | 2.406E+02 | 1.187E-01 | 2.498E+01 | 2.657E+02 |

| 0.03    | 0.11  | 4.00    | 1.539E+02 | 9.230E-02 | 1.545E+01 | 1.694E+02 |

| 0.04    | 0.15  | 6.00    | 1.076E+02 | 7.633E-02 | 1.071E+01 | 1.184E+02 |

| 0.05    | 0.19  | 7.00    | 7.992E+01 | 6.540E-02 | 7.814E+00 | 8.780E+01 |

| 0.06    | 0.22  | 9.00    | 6.208E+01 | 5.710E-02 | 6.268E+00 | 6.841E+01 |

| 0.07    | 0.26  | 10.00   | 4.989E+01 | 5.060E-02 | 5.159E+00 | 5.510E+01 |

| 0.08    | 0.30  | 12.00   | 4.115E+01 | 4.537E-02 | 4.395E+00 | 4.559E+01 |

| 0.09    | 0.33  | 13.00   | 3.468E+01 | 4.110E-02 | 3.844E+00 | 3.857E+01 |

| 0.10    | 0.37  | 15.00   | 2.967E+01 | 3.756E-02 | 3.389E+00 | 3.310E+01 |

| 0.20    | 0.74  | 29.00   | 1.090E+01 | 2.170E-02 | 1.675E+00 | 1.260E+01 |

| 0.30    | 1.11  | 44.00   | 6.208E+00 | 1.625E-02 | 1.164E+00 | 7.389E+00 |

| 0.40    | 1.48  | 58.00   | 4.088E+00 | 1.316E-02 | 9.099E-01 | 5.011E+00 |

| 0.50    | 1.85  | 73.00   | 2.833E+00 | 1.104E-02 | 7.575E-01 | 3.601E+00 |

| 0.60    | 2.22  | 87.00   | 2.008E+00 | 9.501E-03 | 6.737E-01 | 2.691E+00 |

| 0.80    | 2.96  | 117.00  | 1.056E+00 | 7.438E-03 | 5.723E-01 | 1.636E+00 |

| 1.00    | 3.70  | 146.00  | 5.778E-01 | 6.156E-03 | 5.052E-01 | 1.089E+00 |

| 1.25    | 4.63  | 182.00  | 2.756E-01 | 5.123E-03 | 4.589E-01 | 7.396E-01 |

| 1.50    | 5.56  | 219.00  | 1.309E-01 | 4.425E-03 | 4.216E-01 | 5.570E-01 |

| 1.75    | 6.48  | 255.00  | 6.178E-02 | 3.921E-03 | 3.964E-01 | 4.621E-01 |

| 2.00    | 7.41  | 292.00  | 2.811E-02 | 3.540E-03 | 3.764E-01 | 4.081E-01 |

| 2.50    | 9.26  | 365.00  | 4.293E-03 | 3.016E-03 | 3.411E-01 | 3.484E-01 |

| 3.00    | 11.11 | 437.00  | 4.175E-04 | 2.677E-03 | 3.140E-01 | 3.171E-01 |

| 3.50    | 12.96 | 510.00  | 8.088E-06 | 2.436E-03 | 2.882E-01 | 2.907E-01 |

| 4.00    | 14.81 | 583.00  | 0.000E+00 | 2.251E-03 | 2.689E-01 | 2.711E-01 |

| 4.50    | 16.67 | 656.00  | 0.000E+00 | 2.099E-03 | 2.524E-01 | 2.545E-01 |

| 5.00    | 18.52 | 729.00  | 0.000E+00 | 1.970E-03 | 2.364E-01 | 2.384E-01 |

| 6.00    | 22.22 | 875.00  | 0.000E+00 | 1.756E-03 | 2.098E-01 | 2.116E-01 |

| 8.00    | 29.63 | 1167.00 | 0.000E+00 | 1.453E-03 | 1.706E-01 | 1.721E-01 |

| 10.00   | 37.04 | 1458.00 | 0.000E+00 | 1.233E-03 | 1.421E-01 | 1.433E-01 |

#### 2.4.2.2 Single Event Effects

The high energy protons trapped in the space environment are able to cause single event effects in semiconductor electronics. At an altitude of 2600 km and inclination of 60 degrees, the maximum upset rate occurs, with a single event upset rate of 0.1 upsets/bit-day for susceptible electronics with typical shielding [39]. The upset rate of protons at low altitude orbits and a low inclination are generally determined by the South Atlantic Anomaly.

#### 2.4.3 Solar Particle Events

The main source of solar energetic particles (SEPs) includes solar flares and sporadic eruptions of the sun's chromospheres [40]. The flux emitted contains protons, and heavy charged particles and electrons. The most important of these being protons, due to their abundance and high energy levels. Solar particle events are considered to be rare and are generally limited to the 11 year solar cycle. During this cycle of 11 years, 7 are high activity years and 4 years are of low activity [41].

Two generally accepted indications of the solar cycle include the number of sunspots and solar 10.7cm radio flux (F10.7) [41]. More emphasis has been put on forecasting and predicting solar cycle activity in recent years. It is known that during the declining phase of the solar maximum, the larger

solar particle events are likely to occur more regularly. It is also know that electron flux will be larger during the declining phase and the proton flux will be at a maximum during the solar minimum phase [41].

A solar particle events is defined as an event with a total proton fluence of >30 MeV of  $10^6$ , 3 X $10^6$  and  $10^7$  cm<sup>-2</sup>, which generally has proton energies in the region of 20 to 80 MeV. Approximately 50 of these events can occur during a solar cycle [29, 40].

The manner in which SPEs are produced allows SPEs to be defined as either those which are produced by impulsive flares or those which are produced by coronal mass ejections (CMEs) [29]. SPEs which result from impulsive solar flares have short durations, usually only lasting a few hours. These SPEs also have large fluxes of electrons, with a total fluence of between 10<sup>7</sup> and 10<sup>8</sup> cm<sup>-2</sup>, which is relatively small. These SPEs are limited to a 30 to 45 degree angle in solar latitude [29]. SPEs as a result of CMEs have a longer duration in the order of days and also have higher proton fluxes of which the total fluence can be larger than 10<sup>9</sup> cm<sup>-2</sup>. The solar latitude angle extends from 60 to as much as 180 degrees.

Table 4: Characteristics of SPEs [41]

| Hadron<br>Composition                         | Energies        | Integral Fluence<br>(>10MeV/nuc.)        | Peak Flux<br>(>10MeV/nuc.)                       | Radiation<br>Effects |

|-----------------------------------------------|-----------------|------------------------------------------|--------------------------------------------------|----------------------|

| 96.4% protons<br>3.5% alphas<br>~0.1% heavier | Up to ~GeV/nuc. | Up to ~10 <sup>10</sup> cm <sup>-2</sup> | Up to $\sim 10^5 \text{ cm}^{-2} \text{ s}^{-1}$ | TID<br>DD<br>SEE     |

#### 2.4.4 Atmospheric ionizing radiation

This secondary form of radiation occurs as a result of the primary GCR particles interacting with the earth's atmosphere. The intensity and energies of the primary GCR and secondary particles are dependent on the altitude, location in the geomagnetic field and the solar cycle stage [40].

#### 2.4.5 Dose Levels in space orbits

The dose rates for various orbits in space are of importance for total ionizing dose effects on microelectronics. The following are the dose rates for specific orbits [23, 24]:

Low Earth Orbit 0.1 kRads/year

Medium Earth Orbit 100 kRads/year

Geostationary Earth Orbit 10 kRads/year

#### 2.4.6 Testing Facility Sources

## 2.4.6.1 Total ionizing dose

The facility available for the experiment is the Agricultural Council Facilities in Stellenbosch which allows the tests to be performed with a Colbat-60 (Co-60) source. The Co-60 source produces Gamma rays with energies close to 1.3MeV and a radiation dose of 845.08 rad/minute. The source will allow for good long term characterization of exposing a FPGA to a radiation source.

### 2.4.6.2 Single Event Upset

The SEU testing will be conducted at the iThemba Laboratories in Cape Town. This research facility is able to produce protons with energies of up to 66MeV for regular testing and 200MeV if the request for a higher energy is approved. The dose rate is not of interest for SEE testing.

#### 2.5 Natural shielding

### 2.5.1 Magnetosphere

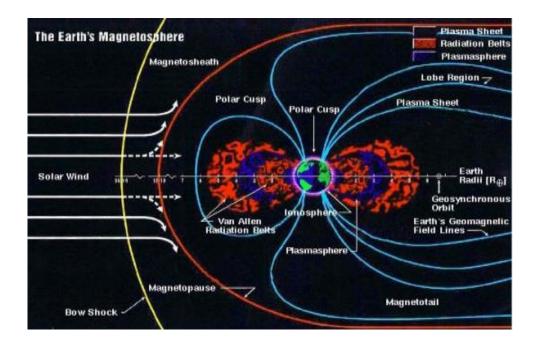

A magnetosphere is generated when a constant stream of charged particles interact with, and is deflected by, the intrinsic magnetic field of a planet [43]. The shape of the magnetosphere is characterized by the earth's magnetic field, solar winds and interplanetary magnetic fields (IMF) [44]. The physical shape of the magnetosphere is non-spherical and extends to approximately 70 000km (10-12 Earth radii) on the sun's side. The tail side of the magnetosphere, on the night side of the earth, is shaped like a cylinder with a radius of approximately 20-25 radii with the magnetotail extending to over 200 earth radii [44].

The Earth's magnetosphere deflects solar wind, cosmic rays and high energy charged particles originating from outside of the solar system. The charged particles which enter the magnetosphere spiral around filed lines, moving back and forth between the poles several times per second [45].

The interaction between solar winds and the earth's geomagnetic field produces energy, stored as potential energy in the magneto tail, this causes a magnetic substorm and, as a result, auroral activity in the upper atmosphere occurs. This occurrence can cause the surfaces of spacecraft to

become highly charged, causing a discharge in the form of electrical arching [23, 24]. Figure 11 illustrates the Earth's magnetosphere and radiation sources.

Figure 11: Earth's magnetosphere [46]

#### 2.5.2 Geomagnetic shielding

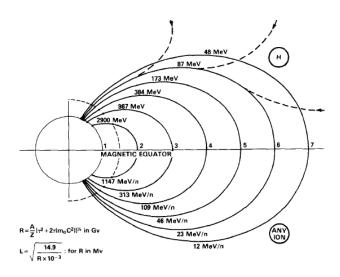

The earth's magnetosphere deflects most of the charged particles originating from outside of the magnetosphere and prevents the particles from entering. The charged particles are deflected away via the Lorentz force, but this force is opposed by the particles' own momentum. The ability of a charged particle to penetrate a geomagnetic field is dependent on the particle's magnetic rigidity defined in equation 5 [47]:

$$p = \frac{pc}{Ze}$$

## **Equation 5**

Where p = relativistic momentum expressed in units of eV/c, c = velocity of light, 2.998X  $10^8$  ms<sup>-1</sup>, e = elementary charge, 1.602 X  $10^{-19}$  c and Z = atomic number. Figure 12 demonstrates the method of calculating the required energy to penetrate the magnetosphere.

Figure 12: Energy required to penetrate the magnetosphere

#### 2.6 Radiation interactions with matter

The interaction and energy loss of radiation particles can be classified into two categories, namely (direct) ionizing and (indirect ionizing) non-ionizing radiation. The first, ionizing radiation includes; Alpha particles, electrons, protons, positrons and beta particles. The interaction of charged particles with matter is described as electric (coulomb) forces which dispose of their energy as ionization and excitation [23, 24].

The second category, uncharged (indirect ionizing) particles which include neutrons and y-quantums is the radiation of particles with no charge. These particles can transfer energy to the absorbing matter by transferring energy to charge particles, nuclei and atom electrons as a result of nuclear or electromagnetic interactions. [23, 24].

#### 2.6.1 Charged particles (direct ionizing)

#### 2.6.1.1 Alpha particles

Alpha particles have strong interactions with matter due to being relatively heavy in addition to having charge. During an interaction, a large number of ions per unit length are produced, resulting in less penetration. Alpha particles are able to interact with both orbiting electrons and the nuclei in any absorbing material [23, 24]. Alpha particles passing close to a nucleus can be deflected away

with no change in energy (Rutherford scattering), deflected away with a small change in energy or absorbed by the nucleus, resulting in nuclear transformation [23, 24].

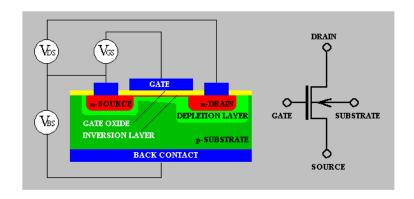

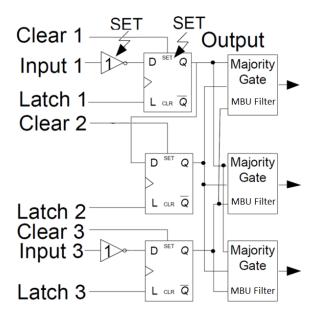

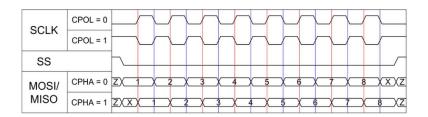

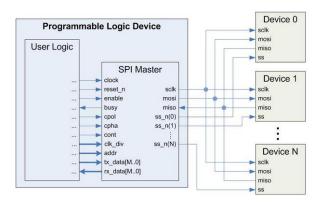

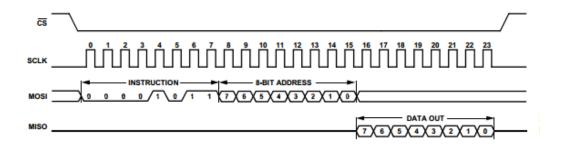

The most commonly found process which occurs during the absorption of alpha particles is the excitation and ionization of orbital electrons. During excitement, the incident particle transfers an amount of its energy into the electrons of the absorbing material by pulling (attracting) the electron towards it and out of its belt. This energy "excites" the electron and the gained energy promotes the electron to a further orbit. However, after excitation the transferred energy is not sufficient to surpass the binding energy of the electron, resulting in the electron returning to its original, lower energy, orbit. During the de-excitation phase, the electron will emit the excitation energy in the as electromagnetic radiation [23]. If the amount of energy transferred surpasses the binding energy of the electron, an ion pair will be created during an ionization effect. The ion pair will comprise of an ejected electron and positively charged atom [23, 24].