### UNIVERSITY OF TARTU

Faculty of Mathematics and Computer Science

Institute of Computer Science

Chair of Cryptography

## Emilia Käsper

# Complexity Analysis of Hardware-Assisted Attacks on ${\sf A5/1}$

Master's Thesis

Supervisor: Prof. Helger Lipmaa

# Acknowledgements

This Master's thesis was written as part of the GO-SEC project at Helsinki University of Technology. The project was financed by the National Technology Agency of Finland and several Finnish telecommunication companies. I thank the partners of GO-SEC, the Laboratory for Theoretical Computer Science and the Signal Processing Laboratory at Helsinki University of Technology for supporting this research and providing me with an excellent working environment for the duration of the project.

I am grateful to my supervisor Helger Lipmaa for his numerous suggestions and remarks, and especially for his contributions to optimising the software implementation. I would also like to thank Kaisa Nyberg, Jan Villemson and Sven Laur for their helpful comments, and Kimmo Järvinen for giving me insight into the hardware world.

# Contents

| 1 | Intr | oduct           | ion                                                       | 6  |

|---|------|-----------------|-----------------------------------------------------------|----|

| 2 | Intr | oduct           | ion to GSM Security                                       | 8  |

|   | 2.1  | GSM             | Speech Transmission                                       | 8  |

|   | 2.2  | Securi          | ity in the GSM System                                     | 11 |

| 3 | The  | $\mathbf{A5/1}$ | Encryption Algorithm                                      | 13 |

|   | 3.1  | The A           | A5 Family of Stream Ciphers                               | 13 |

|   | 3.2  | The A           | A5/1 Stream Cipher                                        | 14 |

|   | 3.3  |                 | analysis of the A5/1 Stream Cipher: Generic Ideas $\dots$ | 16 |

| 4 | Gue  | ess-An          | d-Determine Attacks                                       | 20 |

|   | 4.1  | Ander           | rson-Keller-Seitz Attack                                  | 20 |

|   |      | 4.1.1           | Key Ideas of the Attack                                   | 21 |

|   |      | 4.1.2           | Average-Case Complexity of the Attack                     | 26 |

|   |      | 4.1.3           | Discussion on a Previous Complexity Analysis              | 36 |

|   |      | 4.1.4           | Implementations                                           | 37 |

|   | 4.2  | Bihan           | n-Dunkelman Attack                                        | 41 |

|   |      | 4.2.1           | Key Ideas of the Attack                                   | 42 |

|   |      | 4.2.2           | A Trade-Off Between Computational and Plaintext Com-      |    |

|   |      |                 | plexity                                                   | 44 |

|   |      | 4.2.3           | Possibilities for Hardware Implementation                 | 47 |

|   | 4.3  | Golić           | Attack                                                    | 48 |

|   |      | 4.3.1           | Key Ideas of the Golić Attack                             | 48 |

|   |      | 4.3.2           | Implementations                                           | 51 |

| 5 | Oth  | er Att          | acks on A5/1                                              | 53 |

|   | 5.1  | Time-           | Memory Trade-Off Attacks                                  | 53 |

|   |      | 5.1.1           | Key Ideas of A Time-Memory Trade-Off Attack               | 53 |

|   |      | 5.1.2           | Biased Birthday Attack                                    | 55 |

|   |      | 5.1.3           | Random Subgraph Attack                                    | 59 |

|    |       | 5.1.4   | Possibilities for Hardware Implementation | 61         |

|----|-------|---------|-------------------------------------------|------------|

|    | 5.2   | Ekdah   | l-Johansson Correlation Attack            | 62         |

|    |       | 5.2.1   | Key Ideas of the Attack                   | 62         |

|    |       | 5.2.2   | An Improvement of the Attack              | 65         |

|    |       | 5.2.3   | Possibilities for Hardware Implementation | 67         |

|    | 5.3   | Cipher  | rtext-Only Attacks                        | 68         |

| _  |       |         |                                           |            |

| 6  | A C   | Compai  | rison of the Attacks                      | 71         |

| 7  | Con   | clusio  | n                                         | 74         |

| R  | esüm  | ee (ees | sti keeles)                               | <b>7</b> 6 |

| Bi | bliog | graphy  |                                           | 77         |

# Chapter 1

## Introduction

The A5/1 stream cipher is an encryption algorithm used in the GSM standard of mobile communications. The standard originally incorporated two ciphers: A5/1 was used mainly in Europe, whereas A5/2, an intentionally weaker version of the A5 algorithm was created for export. Recent cryptanalytic attacks against A5/2 have caused 3GPP (3rd Generation Partnership Project, [3GP]), who is currently responsible for maintaining and developing GSM technical specifications, to withdraw A5/2 from the standard. According to [GSM04], there were over 1.7 billion GSM subscribers as of March 2006. With 3G networks still under development and A5/2 in removal, a vast majority of those users will rely on A5/1 to protect the confidentiality of their voice communications during the coming years.

The history of GSM dates back to the 1980s and the A5/1 encryption algorithm was developed already at the end of the same decade. The first initiative to create a pan-European mobile communications network was met in 1982, when the Groupe Spéciale Mobile was established and development of the new digital cellular standard begun. This was also the birth of the GSM acronym: only later was the original French acronym changed to Global System for Mobile Communications. In 1989, the responsibility for specification development passed to the newly created European Telecommunications Standards Institute (ETSI); during the next year, most of the GSM specifications were published. However, the encryption algorithms were initially kept secret in hope to increase security. The "security through obscurity" principle did not prove a very good idea: the general design of GSM ciphering algorithms leaked in 1994, and by 1999, both A5/2 and A5/1 algorithms had been reverse-engineered.

The subject of this work is the cryptanalysis of A5/1, with special focus on attacks that could benefit from hardware assistance. Special-purpose hardware has proved useful for example in cracking the DES block cipher [Fou98].

The goal of this Master's thesis is to analyse whether it is also possible to speed up the cryptanalysis of the A5/1 stream cipher with the aid of hardware, in particular, field programmable gate arrays (FPGAs). The nature of the thesis is theoretical: descriptions of attack algorithms and estimates on their time and memory complexity are meant to help a hardware specialist in selecting the method most suitable for hardware implementation. Also, we are aware of one previous hardware implementation of a cryptanalytic attack against A5/1, which we cover in Section 4.1.4.

The thesis is organised as follows: Chapter 2 introduces the reader to the general architecture of GSM security and gives necessary background about other aspects of GSM voice transmission. The first part of Chapter 3 describes the A5/1 encryption algorithm. The second part summarises some general concepts in the cryptanalysis of stream ciphers. This concludes the introductory part.

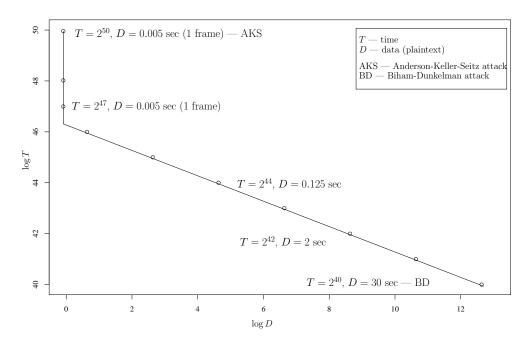

The major part of our original work is presented in Chapter 4. In this chapter, we analyse three different attacks against A5/1, belonging to a generic class of attacks known as guess-and-determine attacks. Apart from reviewing work done by other authors, our own contribution is the following. First, in Section 4.1, we give a detailed complexity analysis for the Anderson-Keller-Seitz attack presented in this section. Keller and Seitz have attempted such analysis in [KS01], however, we have found that their analysis is imprecise, and present our exact results. Second, we have also implemented the attack in software. The implementation enables us to verify our theoretical results as well as to give an estimate on the time complexity of the attack on a PC. Implementation results are presented in the end of the section.

Next, we also use our results from Section 4.1 to give a precise estimate on the complexity of the Biham-Dunkelman attack, presented in Section 4.2. Also, as a smaller original contribution, we generalise the Biham-Dunkelman attack by proposing a trade-off curve between the amount of required plaintext and computational complexity.

Chapter 5 proceeds with reviewing other known attacks against A5/1. In each section of this chapter, we describe the key ideas of one attack and provide implementation details, where available. We conclude each section by discussing possibilities for hardware implementation. Finally, in Chapter 6, we give a comparison table of the parameters for all of the presented attacks.

# Chapter 2

# Introduction to GSM Security

This chapter gives a general introduction to the GSM system. We start by giving information about speech encoding, error correction coding and speech transmission in GSM. In the next section, we move on to the more specific field of security in the GSM system. This chapter is meant to give necessary background information for understanding the security of the A5/1 encryption algorithm. We do not analyse the security of the GSM system as a whole and all security claims that we make later in this thesis will only concern the cryptographic strength of the A5/1 cipher.

## 2.1 GSM Speech Transmission

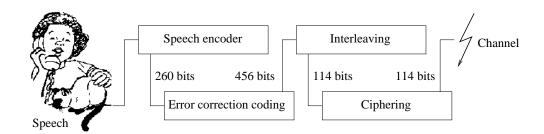

Speech in GSM is digitally coded at a rate of 13 kbps, so-called full-rate speech coding. The speech signal is divided into 20 millisecond samples, so one block of the GSM speech codec output is 260 bits long. Each block is then protected from errors, using cyclic and convolutional encoding, and the output size of the encoder is 456 bits. Before transmission, this data is encrypted, using a bitwise exclusive-or (XOR) operation with a pseudorandom bit sequence generated by the encryption algorithm. The fact that the encrypted data is redundant—260 bits of actual data are expanded into 456 bits by the encoder—has been exploited to mount a ciphertext-only attack on the encryption algorithm. For more details on GSM error-correction coding, we refer the reader to the relevant standard [ETSa].

The GSM system uses Time Division Multiple Access (TDMA) to allow several users to share the same channel. The time unit of the TDMA system is a burst, which lasts 3/5200 seconds (approximately 0.577 ms). One burst is capable of carrying 114 data bits, and so the size of a burst is 25% of the size of an error correction coded block, or equivalently 5 ms of conversation.

| 0 |   | 8  |    | 16 |    | 24 |    |  | 448 |     | burst N   |

|---|---|----|----|----|----|----|----|--|-----|-----|-----------|

| 1 |   | 9  |    | 17 |    | 25 |    |  | 449 |     | burst N+1 |

| 2 |   | 10 |    | 18 |    | 26 |    |  | 450 |     | burst N+2 |

| 3 |   | 11 |    | 19 |    | 27 |    |  | 451 |     | burst N+3 |

|   | 4 |    | 12 |    | 20 |    | 28 |  |     | 452 | burst N+4 |

|   | 5 |    | 13 |    | 21 |    | 29 |  |     | 453 | burst N+5 |

|   | 6 |    | 14 |    | 22 |    | 30 |  |     | 454 | burst N+6 |

|   | 7 |    | 15 |    | 23 |    | 31 |  |     | 455 | burst N+7 |

Figure 2.1: The block diagonal interleaver of the GSM system

However, the division of a block into bursts is slightly more complicated.

While error correction codes employed in the GSM system make it possible to detect and correct bit errors, they cannot guard against disturbances causing a large number of consecutive erroneous bits—a situation common to the radio interface. To further protect against such errors, each 456-bit speech sample is interleaved before transmission. First, the 456 bits are divided into 8 blocks of 57 bits each: bits  $0, 8, \ldots, 448$  form block I, bits  $1, 9, \ldots, 449$  form block II etc, until the last block of 57 bits (block VIII) will then contain the bits numbered  $7, 15, \ldots, 455$ . The first four blocks of 57 bits are then placed in the even-numbered bits of four consecutive bursts. The other four blocks of 57 bits are placed in the odd-numbered bits of the next four bursts. This type of interleaver is called the block diagonal interleaver (see Figure 2.1).

Since a burst can carry 114 data bits, each burst carries blocks from two consecutive samples, and one sample is distributed over eight bursts. This means that even if an entire burst is lost during transmission, the loss for a sample block is only 12.5% of the total number of bits.

A burst also contains some fixed bits to control modulation, so the total length of one burst is 156.25 bits. However, only the 114 data bits are encrypted before transmission. Encryption takes place as a final step after interleaving and before modulation; decryption is carried out symmetrically after demodulation. The steps of speech processing before modulation are depicted in Figure 2.2.

In addition to digitally encoded speech, the mobile and the network also exchange signalling data during the set-up phase of a call, and also during the call itself, e.g., to report signal strength. While speech data is exchanged on traffic channels, signalling data is sent on dedicated control channels. Both types of channels are bidirectional, i.e., data is sent and received simultaneously. Signalling data is protected from errors with similar error correction

Figure 2.2: Speech coding in the GSM system

methods, but the input to the encoder is now a message of fixed length 184 bits and the output block size is again 456 bits. Interleaving is done in a slightly different manner. Namely, the first four blocks of 57 bits are again placed in the even-numbered bits of four consecutive bursts, but the other four blocks are placed in the odd-numbered bits of the *same* four bursts. Hence, a burst of signalling data carries data from only one signalling message. This type of interleaver is called the block rectangular interleaver. Finally, the 114 significant bits of a signalling data burst are encrypted in exactly the same way as bits of speech data.

Bursts in GSM are sent in frames. One TDMA frame contains eight bursts from eight different users and consecutively lasts approximately 4.62 milliseconds. The difference between the frame length and the corresponding length of conversation (5 ms) is compensated by the fact that not all frames carry speech data. Of each 26 consecutive TDMA frames, 24 are reserved for traffic channels, one frame is used for signalling data on the Slow Associated Control Channel (SACCH) and the last frame is an idle frame, i.e., nothing is transmitted at all.

This structure is called the TDMA 26-Multiframe. In this multiframe structure, there are separate channels for uplink and downlink information, so the total number of information bits transmitted on a channel within each frame is  $2 \cdot 114 = 228$  bits per user. Now, for each user, 26 frames carry 24 blocks of (uplink and downlink) speech data of 114 bits, or equivalently,  $24 \cdot 5 = 120$  milliseconds of conversation. We see that the total duration of the 26 frames, together with the data frame and the idle frame, is also 120 milliseconds, as expected.

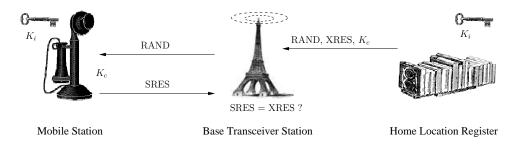

Figure 2.3: User authentication in the GSM system

## 2.2 Security in the GSM System

For each user i in the GSM network, there exists a permanent 128-bit secret key  $K_i$  that is stored in two locations: the user's Subscriber Identity Module (SIM) card and the Authentication Centre (AuC) of the network. The key is never supposed to leave either of these locations. Checking whether the user has access to his key  $K_i$  (and is hence, hopefully, a legitimate user) is done by challenging the SIM card to do a computation that can only be done with the correct key  $K_i$ . The base transceiver station (BTS) can do this without obtaining knowledge of the secret key  $K_i$  in the following way.

When a mobile station (MS)—a user—logs on to the network, the BTS requests an authentication triplet from the AuC of the user's Home Location Register (HLR). The HLR/AuC first selects a 128-bit random value RAND. It then computes an authentication value XRES (eXpected RESponse) and the session key  $K_c$  from RAND and the user's permanent secret key  $K_i$  (recall that the AuC is the only other party in possession of the key  $K_i$ ).

The three values—the 128-bit RAND, the response value XRES and the 64-bit session key  $K_c$ —form the authentication triplet that the HLR/AuC sends to the BTS. The BTS forwards RAND to the MS. The MS performs the same computations as the HLR/AuC did before. It obtains two values: the session key  $K_c$  and the authentication value SRES (Signed RESponse), and sends the latter to the BTS. If the MS is in possession of the correct secret key  $K_i$ , the value of SRES will match the expected value XRES. Vice versa, it should be the case that if the value of SRES matches the expected value XRES, then the MS is indeed in possession of the correct key. If the values match, authentication succeeds and the key  $K_c$ , now known by both the user and the BTS, is used for encryption until the next authentication occurs (see Figure 2.3).

The response value and the session key are generated by the HLR and the MS with two one-way functions A3 and A8, respectively. Neither of these algorithms is specified in the GSM specifications; rather, they are left for

the service provider to implement. In practice, they are usually implemented together as COMP128, a "reference implementation" from the GSM specifications, or one of its later, improved versions. An overview of security issues related to COMP128 can be found at [COM].

Authentication in GSM systems is one-way: the user is authenticated to the base station, but not vice versa. This opens up possibilities for active attacks with a fake base station.

After the session key  $K_c$  has been generated and the encryption process has been initialised, ciphering takes place at both the mobile station and the base station. The encryption algorithm of GSM is called A5. Each frame, the A5 algorithm produces the same pseudorandom sequence of  $2 \times 114$  bits at both ends. Encryption is achieved by simple bitwise XOR with the plaintext block; the decryption operation is obviously identical to encryption. The first 114-bit block output by the algorithm is now used to encrypt data on the network side and, once received, to decrypt it on the mobile station side. The second block is used analogously to encrypt data transmitted from the mobile station to the base station.

As explained above, encryption of calls in the GSM system is not end-to-end. Radio traffic between the end user and the nearest base station is encrypted; however, base stations have access to plaintext, and on (landline) links between network stations, data is sent in the clear. Moreover, control data, including the session key used for ciphering, is sent to the base station unencrypted. This is one of the most criticised properties of GSM security. Also, session key setup, which is triggered by the authentication procedure, may occur as often—or as rarely—as the network operator wishes. In practice, the same key may be in use for days. As we shall see from some of the attacks, a large amount of data encrypted with the same key increases the vulnerability of the cipher.

The ciphering procedure described above applies to GSM security. GPRS connections are secured using a different encryption algorithm (GEA), which is not publicly known. Readers interested in other aspects of GPRS security may read [eK01].

# Chapter 3

# The A5/1 Encryption Algorithm

In this chapter, we describe the A5/1 encryption algorithm. The description was first obtained by methods of reverse engineering and can be found at [And94], together with a reference software implementation in C programming language [BGW99]. According to [BSW01], the GSM organisation has confirmed the correctness of the algorithm. We end this chapter by introducing the general concept of the cryptanalysis of stream ciphers.

## 3.1 The A5 Family of Stream Ciphers

There are multiple versions of the encryption algorithm referred to as A5:

- A5/0 is a dummy cipher that provides no encryption;

- A5/1 (the subject of this Master's thesis) is the original A5 algorithm used in Europe but also in North America and increasingly all over the world;

- A5/2 is an intentionally weaker encryption algorithm created for export;

- A5/3 is a strong encryption algorithm created as part of the 3rd Generation Partnership Project (3GPP).

Following the principle of "security through obscurity", the designs of A5/2 and A5/1 were initially kept secret. Sketchy designs leaked in 1994 and the exact designs were reverse engineered in 1999. A recent ciphertext-only attack on A5/2 by Barkan, Biham and Keller [BBK03] requires less

than 5.5 hours of one-time precomputation and recovers the session key in less than a second on a regular PC. Attacking A5/1 still requires notably more time and memory resources. The development of A5/3 has been public from the start and there are no known security problems with the algorithm, which is based on the KASUMI block cipher.

A5/2 was designed intentionally weak due to export limitations. Following the publication of the Barkan-Biham-Keller attack, the 3GPP organisation recently withdrew A5/2 from its standard. Export limitations have been removed and 3GPP is encouraging networks to remove A5/2 support at the earliest opportunity [3GP04]. Since support for A5/3 version is present only in Third Generation networks, and Second Generation networks are gradually dismissing the weak A5/2 version, A5/1 will be the prevailing algorithm of GSM encryption almost all over the world during the coming years. Moreover, 3G networks will have to ensure backwards compatibility with A5/1 until old handsets are no longer used, so the cryptanalysis of A5/1 is still an important topic of research.

## 3.2 The A5/1 Stream Cipher

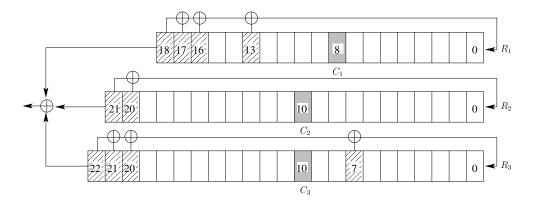

A5/1 is a generic (as opposed to block cipher based) synchronous stream cipher. Three linear feedback shift registers (LFSRs)  $R_1$ ,  $R_2$  and  $R_3$  of lengths 19, 22 and 23 bits, respectively, are used as its main building blocks. Table 3.1 shows the primitive (i.e., maximal length) feedback polynomials of the registers.

| Register | Feedback polynomial                                 | tap positions  | period       |

|----------|-----------------------------------------------------|----------------|--------------|

| $R_1$    | $x^{19} \oplus x^5 \oplus x^2 \oplus x \oplus 1$    | 18, 17, 16, 13 | $2^{19} - 1$ |

| $R_2$    | $x^{22} \oplus x \oplus 1$                          | 21, 20         | $2^{22}-1$   |

| $R_3$    | $x^{23} \oplus x^{15} \oplus x^2 \oplus x \oplus 1$ | 22, 21, 20, 7  | $2^{23}-1$   |

Table 3.1: Feedback polynomials of the LFSRs in the A5/1 construction

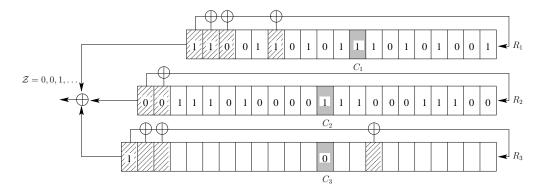

A schematic description of the A5/1 cipher is given in Figure 3.1. Throughout this thesis, we refer to bits 18, 21 and 22—leftmost bits in the figure—of registers  $R_1$ ,  $R_2$  and  $R_3$ , respectively, as the most significant bits of the respective registers. Conversely, the bits at position 0—rightmost in the figure—are referred to as the least significant bits.

When a register is clocked, the bits at its tap positions are XORed together and stored in the least significant bit of the register, after its bits have been shifted one position to the left. The most significant bit of each register

Figure 3.1: The three LFSRs of the A5/1 stream cipher

is its output bit. The output of the A5/1 generator is at each clocking cycle obtained by XORing the output bits of the three registers.

The algorithm takes as input two parameters: a 64-bit secret session key  $K_c$  and a 22-bit counter  $F_n$ , derived from the publicly known TDMA frame number. During the operation of the cipher, the contents of the three registers are re-initialised with a new counter before the encryption/decryption of each frame.

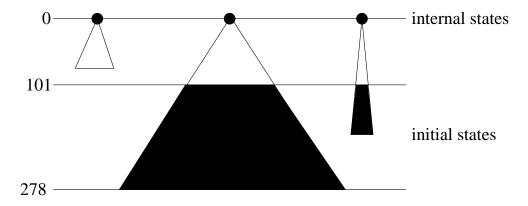

In the initialisation phase, all registers are clocked regularly at each cycle. During the first 64 clockings, the 64 bits of the session key  $K_c$ —from least significant bit (lsb) to most significant bit (msb)—are XORed into the lsb of each of the registers in parallel. During the next 22 cycles, the frame number  $F_n$  is mixed into the registers analogously. In the key setup phase, the cipher produces no output. The state of the three registers after key setup is called the *initial state* of frame n. Due to the way the contents of the registers are initialised, the initial state is a linear combination of the publicly known frame counter  $F_n$  and the secret session key  $K_c$ . Hence, when the initial state of any given frame is known, the secret key is revealed.

After initialisation, an irregular clocking rule is introduced. The middle bits of the three registers—bits 8, 10 and 10, denoted by  $C_1$ ,  $C_2$  and  $C_3$ , respectively—are the clocking bits used to determine the stop/go clocking. At each step, the majority of the three bits is calculated and only those registers for which the clocking bit agrees with the majority are clocked. Hence, if  $C_1 = C_2 = C_3$ , all registers are clocked; if  $C_1 = C_2 = C_3 \oplus 1$ , registers  $R_1$  and  $R_2$  are clocked, and so on. The probability for an individual LFSR to be clocked is 3/4 and the majority clocking rule guarantees that at least two of the three registers are clocked at each cycle.

With the stop/go clocking started, the registers are first clocked for 100

clock cycles without producing any output. Finally, the registers are stop/go clocked for 228 cycles and an output bit is produced after each clock cycle. Hence, the first output bit is produced after the registers have been clocked irregularly for 101 clock cycles. Half of the produced 228 bits are then used to encrypt uplink traffic, while the remaining bits are used to decrypt downlink traffic in the current frame. The amount of discarded bits is crucial in correlation attacks against the cipher (c.f. Chapter 5, Section 5.2).

One more observation should be made about encryption. Namely, the GSM protocol is implemented in such a way that if one of the conversation parties is silent, transmission from that side is cut. In this case, only half of the 228 bits are actually used in encryption; the other half is just discarded. For the cryptanalyst, this brings bad news, since it reduces the amount of available ciphertext and plaintext. In all complexity estimates throughout this thesis, we assume that from each time frame during the conversation all 228 bits of keystream can be extracted.

At any moment during the operation of the cipher, the contents of the three registers form the *internal state* of the cipher. Note that the internal state size of A5/1 is equal to the secret key length. In modern stream ciphers (e.g., SNOW 2.0), the state size is usually at least twice the key size. This requirement is also pointed out in the ECRYPT Call for Stream Cipher Primitives, published in November 2004, as a prevention measure for time-memory trade-off attacks [ECR]. All known attacks against A5/1 are internal state recovery attacks, followed by initial state reconstruction and session key recovery.

# 3.3 Cryptanalysis of the A5/1 Stream Cipher: Generic Ideas

Cryptanalysis of a stream cipher is usually based on the **known plaintext** assumption. This means that the attacker has access to a certain amount of corresponding pairs of plaintext and ciphertext. Assume that the attacker holds a chunk of plaintext  $X = (x_0, x_1, \ldots, x_n)$  and a corresponding chunk of ciphertext  $Y = (y_0, y_1, \ldots, y_n)$  (where  $x_i$  and  $y_i$  are bits,  $0 \le i \le n$ ). The encryption operation of a stream cipher is typically—and also in the case of A5/1—simple bitwise exclusive-or of the plaintext  $X = (x_0, x_1, \ldots, x_n)$  and keystream  $Z = (z_0, z_1, \ldots, z_n)$ :

$$(y_0, y_1, \dots, y_n) = (x_0, x_1, \dots, x_n) \oplus (z_0, z_1, \dots, z_n)$$

=  $(x_0 \oplus z_0, x_1 \oplus z_1, \dots, x_n \oplus z_n)$ ,

or briefly,

$$Y = X \oplus Z . (3.1)$$

This means that the attacker can immediately deduce the keystream produced by the cipher by rewriting (3.1) as

$$Z = X \oplus Y$$

,

i.e.,

$$(z_0, z_1, \ldots, z_n) = (x_0 \oplus y_0, x_1 \oplus y_1, \ldots, x_n \oplus y_n) .$$

The task of the attacker is now to find the key that was used to produce this output. In the following sections, we use the terms known plaintext and known keystream as synonyms, since knowledge of one reveals the other.

In the case of the A5/1 cipher, access to known plaintext then means either direct access to the keystream generator or access to the output of the speech codec (or signalling data). Some ideas for obtaining plaintext are presented in Chapter 5, Section 5.3.

If an attack is mounted without any knowledge of the plaintext, only using the encrypted data, it is called a ciphertext-only attack. In the case of the A5/1 cipher, such an attack would require only passive eavesdropping on radio channels to obtain encrypted data and would hence be very powerful. On the other hand, a ciphertext-only attack still requires some (statistical) knowledge of the plaintext. If nothing about the plaintext is known, then in (3.1), Z can be any keystream produced with a valid key and X can be anything. Hence, any keystream will yield a valid plaintext and there is no way to decide which of the keys was actually used for encryption.

In real-life settings, plaintext is never "anything". In the case of A5/1 in the GSM setting, plaintext is digitally encoded speech or signalling data. Moreover, as was described in Section 2.1 of Chapter 2, all data is expanded by employing error-correction coding. This means that although output from the speech codec is compressed, input to the encryption algorithm is redundant. In Section 5.3, we describe how the redundancy can be exploited to mount a ciphertext-only attack on the cipher.

In the following chapters, several types of attacks against the A5/1 cipher are described. When comparing these attacks from the viewpoint of efficiency and practical threat to security, the following four parameters should be considered:

• Data complexity. In the common known plaintext model, data complexity means known plaintext requirement—the amount of plaintext-ciphertext pairs needed to complete the attack with a given

success probability. In the case of a ciphertext-only attack, data complexity simply means the amount of ciphertext needed. In practical settings, there is usually an upper limit to the amount of plaintext encrypted using the same key. In the case of A5/1, we know that the amount of plaintext encrypted, using the same session key and frame number combination, is 228 bits. The amount of conversation encrypted, using the same session key but different frame numbers depends on the frequency of authentication. In any case, obtaining seconds of known plaintext or minutes of known ciphertext might be feasible, whereas re-authentication makes obtaining hours of conversation from one session an impossible task.

• Time complexity. In the theory of cryptanalysis, time complexity is usually given as a number of operations needed to complete the attack. The worst-case time complexity of an exhaustive search is equivalent to the size of the keyspace—2<sup>64</sup> in the case of A5/1—and the efficiency of any other attack can be compared to this measure. If an attack succeeds in finding the key in less than 2<sup>64</sup> time, the cipher is said to be broken.

In practical settings, we are of course interested in the actual wall clock time needed to carry out the attack. The attack time then depends on the type of operations referred to in the theoretical calculations, and an attack requiring  $2^{40}$  cipher clockings is in practice somewhat faster than an attack requiring  $2^{40}$  steps of "solving a system of linear equations".

The time needed to complete an attack can be divided into **precomputational complexity** and **attack-time complexity**. Precomputations are usually done only once, before the attack is launched, so time requirements are slightly more relaxed. An attack requiring a month of one-time precomputations, but thereafter finding the key in seconds during actual attack time is more feasible than an attack requiring a month of computations each time a new key is attacked.

Finally, we distinguish worst-case complexity and average-case complexity. Worst-case complexity is the time after which the attack is bound to finish, whereas average-case complexity refers to the time after which the attack is expected to finish. For example, in the case of an exhaustive search over  $2^{64}$  possible keys, the right key will definitely be found after  $2^{64}$  tests, but it is expected to be found after half of the tests, i.e., in time  $2^{63}$ .

• Memory complexity. The required amount of memory needed to

perform the attack is most often crucial if the attack has a precomputation stage. Memory complexity is directly related to precomputation time complexity: large memory requirement infers long precomputation time.

• Success probability. We consider two types of attacks. Deterministic attacks are guaranteed to succeed within time T, given an amount D of plaintext, using M memory. Probabilistic attacks, on the contrary, have success probability p < 1 for fixed parameters T, M and D.

# Chapter 4

## Guess-And-Determine Attacks

This chapter, which forms the core of the thesis, deals with a certain class of attacks against stream ciphers in general and the A5/1 cipher in particular, namely, guess-and-determine attacks. Guess-and-determine attacks were the first attacks proposed against A5/1; they are also probably the easiest to understand. Later, several other attacks with significantly lower computational complexity have been found. However, guess-and-determine attacks still prevail in one area—the amount of known plaintext required. We believe that in the real world, obtaining known plaintext may be more difficult than obtaining a sufficient amount of computation power, and so guess-and-determine attacks are still worth investigating, despite their relatively high computational complexity.

### 4.1 Anderson-Keller-Seitz Attack

In this section, we discuss the first proposed guess-and-determine attack against the A5/1 stream cipher. The core of a guess-and-determine attack lies in guessing part of the cipher's internal state and deriving the remaining unknown state bits from known keystream. Thus, this attack is a known plaintext attack. The proposed attack requires only one or two frames of known plaintext, no precomputation and, correspondingly, no notable amount of memory. On the other hand, the computational complexity of such an attack is quite high—over  $2^{50}$  A5/1 clock cycles, which amounts to over two years of computation time on our test platform PC.

The next three sections focus on theoretical attack models and their complexity. Section 4.1.1 introduces the main concept of the attack, which was first mentioned by Anderson [And94]. In Section 4.1.1, we analyse a concrete attack model that was used in a hardware implementation by Keller

and Seitz [KS01]. From now on, we refer to this attack as the Anderson-Keller-Seitz (AKS) attack. Section 4.1.1 contains original theoretical results on the computational complexity of the attack. A previous attempt at complexity analysis by Keller and Seitz is discussed in Section 4.1.3—we show that their case study is incomplete and, as a consequence, they underestimate the complexity of the attack over 4 times.

In the final section, we compare two implementations of the AKS attack. First, we describe our own implementation of the attack in software. We include some notes on implementation and a time complexity estimate. Then, we discuss the hardware implementation by Keller and Seitz and compare the efficiency of the two implementations.

### 4.1.1 Key Ideas of the Attack

Even before the exact design of the A5/1 algorithm was reverse engineered, first attacks against the cipher were published. When the sketchy design leaked, Anderson immediately pointed out that a trivial guess-and-determine attack, where the contents of two linear feedback shift registers are guessed and the content of the last register is then derived from known keystream, has computational complexity of about  $2^{40}$  tests.

(Un)fortunately, the complexity estimate given by Anderson is too optimistic. Namely, the contents of two registers are not sufficient to derive the contents of the third register in a straightforward manner, since it is not possible to determine, which registers are being clocked each cycle, without knowing the clocking bit of the third register. A rough approach would be to additionally guess the 11 less significant bits of the third register. This would reveal the clocking sequence and would allow to determine the remaining 12 bits of the internal state. Since the combined length of the two shortest LF-SRs is 41 bits, the worst-case complexity of the attack would now increase to 2<sup>52</sup> tests, where each test consists of deriving the remaining 12 bits of the third register and further checking the solution against known keystream to eliminate false possibilities. The average-case complexity of the same attack is then 2<sup>51</sup> tests, since we can expect to examine half of the possibilities before we find the right state.

This attack can be slightly improved by noting that some of the 2<sup>11</sup> possibilities for the less significant bits of the third register lead to an early contradiction with the known keystream even before all the remaining unknown bits have been recovered. Keller and Seitz have taken advantage of this improvement and implemented the attack in hardware. In the next section, we proceed to describe the attack in more detail and present a detailed complexity analysis for both hardware and software implementations.

We stress that the internal state of the cipher recovered by this attack does not directly reveal the secret session key. The attack recovers the state of the registers at the moment when the cipher starts producing output, i.e., after 100 bits of discarded output. Techniques for reversing the algorithm for 101 cycles to recover the initial state and derive the session key were first proposed by Golić and are discussed in the end of Section 4.1.2.

### An Improvement of the Attack

We shall now present a concrete attack model from [KS01] and give a theoretical complexity analysis of the model. First, we present the stages of the attack step-by-step. Then, we compute the average-case complexity of the attack in high-level operations. Finally, we give two implementation-specific complexity estimates in A5/1 clock cycles.

Our computations throughout this thesis will be based on the assumption that the LFSR sequences are mutually independent and uniformly random. Although this is not the case, the randomness assumption is reasonable, since the individual LFSR sequences of A5/1 are maximum-length sequences with good statistical pseudo-random properties. In particular, it is known that the output sequence of a maximum-length LFSR satisfies a set of properties known as Golomb's randomness postulates. Also, it should be noted that the output function of A5/1—a ternary exclusive-or with inputs from the outputs of its three registers—is maximum-order correlation immune. Recall that an n-ary Boolean function is maximum order correlation immune if its output is statistically independent of any n-1 inputs to the function, and exclusive-or clearly satisfies this property. A nice explanation of both Golomb's postulates and correlation immunity can be found in e.g. [MvOV96]. Furthermore, the results of our practical simulations, discussed in Section 4.1.4 also support the reasonableness of such assumptions.

#### The Precise Attack Model

We start by giving some notations. Let our time unit be an A5/1 clock cycle and let the time when the first output bit is produced be t = 0. Denote the (unknown) most significant bits of registers  $R_1$ ,  $R_2$  and  $R_3$  at time t by  $O_1(t)$ ,  $O_2(t)$  and  $O_3(t)$ , respectively. Denote the clocking bits of the registers at time t by  $C_1(t)$ ,  $C_2(t)$  and  $C_3(t)$ , respectively. Finally, suppose that we are given the known keystream sequence  $\mathcal{Z}(t) = Z(0), Z(1), \ldots, Z(227)$  from one frame. Our task is then to determine the internal state of the cipher that generates this sequence. Note that at each cycle, the following relation

holds:

$$Z(t) = O_1(t) \oplus O_2(t) \oplus O_3(t)$$

(4.1)

We proceed as follows. First, we guess the contents of registers  $R_1$  and  $R_2$  at time t = 0. Equation (4.1) can then be rewritten as

$$O_3(t) = Z(t) \oplus O_1(t) \oplus O_2(t)$$

, (4.2)

where the right-hand-side is now known, provided that the clocking sequence is known. In particular, we can immediately determine the unknown bit  $O_3(0)$  from the first known output bit Z(0) and the guessed bits  $O_1(0)$  and  $O_2(0)$ . In general, every time the third register is clocked, the next output bit of  $R_3$  is determined by known keystream. Finally, when the entire state of register  $R_3$  has been derived, we can continue to clock the registers and compare the output against known keystream to eliminate false possibilities for the internal states of registers  $R_1$  and  $R_2$ .

The difficulty here lies in the fact that the clocking sequence of the registers depends not only on the guessed states of  $R_1$  and  $R_2$ , but also on the 11 less significant bits (bits 0 to 10) of  $R_3$ . Hence, we would need to guess 11 more bits, yielding the aforementioned worst-case complexity of  $2^{52}$  tests.

Fortunately, it turns out that we can do a little better. Namely, some of the  $2^{52}$  partial internal states cannot be completed to a full 64-bit state that produces the required keystream. Therefore, we proceed to derive the contents of the third register bit-by-bit. As we shall soon see, this enables us to eliminate inconsistent guesses early on in the search.

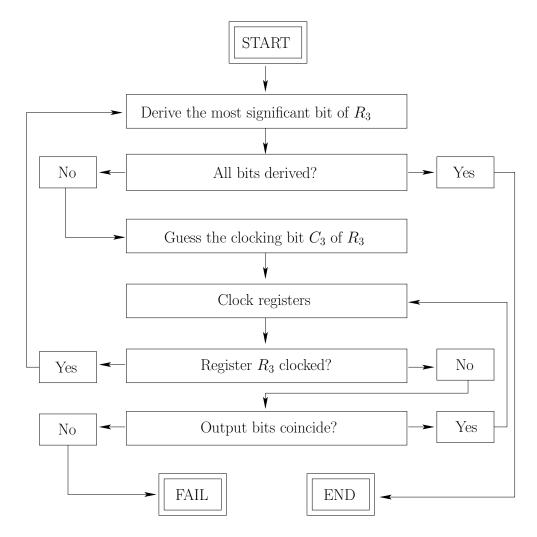

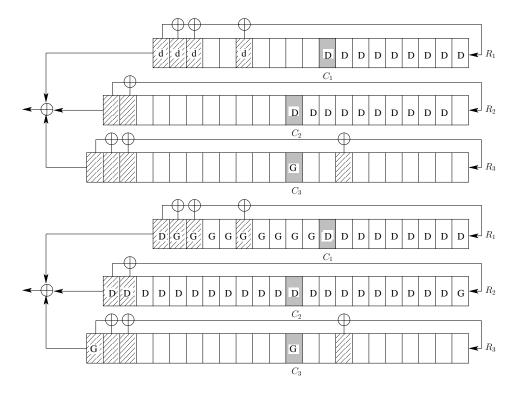

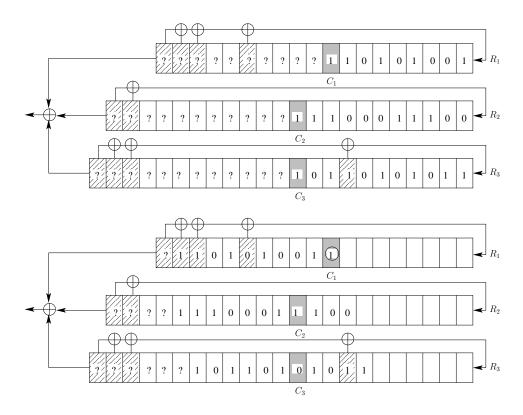

The search, depicted in Figure 4.1 goes as follows. First, since Z(0),  $O_1(0)$  and  $O_2(0)$  are known, bit  $O_3(0)$  can immediately be derived from (4.2). Next, we guess the clocking bit  $C_3(0)$  and clock the registers according to the majority rule.

At any time t, when guessing bit  $C_3(t)$ , there are two possible cases. First, assume that the clocking bits  $C_1(t)$  and  $C_2(t)$  of registers  $R_1$  and  $R_2$  are different. In this case,  $C_3(t)$  agrees with either  $C_1(t)$  or  $C_2(t)$  and, due to the majority rule, register  $R_3$  is definitely clocked. There are two possibilities for the clocking bit  $C_3(t)$  and we need to check both of them. Either case leads us back to the beginning of the loop depicted in Figure 4.1 and we proceed to derive the next output bit of  $R_3$ .

Second, suppose that registers  $R_1$  and  $R_2$  have identical clocking bits at some time t, i.e.,  $C_1(t) = C_2(t)$ . Then these registers are both clocked. Now, consider the guess  $C_3(t) = C_1(t) \oplus 1$ , i.e., assume that the clocking bit  $C_3(t)$  disagrees with the majority and, consequently, the third register is not clocked. Then the most significant bit of  $R_3$  remains the same during the next clock cycle, i.e.,  $O_3(t+1) = O_3(t)$ . The next keystream bit Z(t+1)

can then be compared to the XOR of the most significant bits of  $R_1$ ,  $R_2$  and  $R_3$ . If these bits differ, the guessed internal state does not produce correct keystream, so the option  $C_3(t) = C_1(t) \oplus 1$  can be eliminated. In other words, it has to be that  $C_3(t) = C_1(t) = C_2(t)$  and register  $R_3$  is clocked. Now, the clocking bit  $C_3(t)$  is uniquely determined. The probability that a random guess for  $C_3(t)$  leads to such a contradiction in one clock cycle is thus

$$\begin{aligned} \Pr[\mathsf{fail}(1)] &= & \Pr[C_1(t) = C_2(t) \neq C_3(t)] \cdot \\ & & \Pr[Z(t+1) \neq O_1(t+1) \oplus O_2(t+1) \oplus O_3(t)] \\ &= & \frac{1}{2} \cdot \frac{1}{2} \cdot \frac{1}{2} = \frac{1}{8} \ . \end{aligned}$$

Here, the probability is taken over all possible values for bits  $C_1(t)$ ,  $C_2(t)$ ,  $C_3(t)$ ,  $O_1(t+1)$ ,  $O_2(t+1)$  and  $O_3(t) = Z(t) \oplus O_1(t) \oplus O_2(t)$ , assuming that the LFSR sequences of  $R_1$  and  $R_2$  are mutually independent and uniformly random.

Observe that at most one of the two guesses for  $C_3(t)$  leads to a contradiction. Thus, by mutual exclusivity, the probability that either of the two guesses for  $C_3(t)$  leads to a contradiction (so that  $C_3(t)$  is uniquely determined) is 1/4. Therefore, the average number of possibilities that we need to consider is at most  $(1 \cdot 1/4 + 2 \cdot 3/4)^{11} = (7/4)^{11} \approx 471$ , so the heuristic reduces the number of tests approximately 4 times.

However, we can refine this search a bit further. Namely, what if  $R_3$  is not clocked at cycle t but the keystream bit and the XOR bit are identical, so that we do not get a contradiction? Then, the clocking bit of  $R_3$  remains the same during the next cycle, so we can look one step further. If  $R_3$  is clocked at cycle t+1, we cannot determine whether our initial guess  $C_3(t) = C_1(t) \oplus 1$  was right or not. If  $R_3$  is not clocked, we can again perform the output bit check. Continuing analogously, one of the two things is bound <sup>1</sup> to happen: either  $R_3$  is clocked or we get a contradiction in the output bit check. In the latter case, we know that  $R_3$  had to be clocked at cycle t, so we have reduced the possibilities for the clocking bit  $C_3(t)$  from two to one. In the former case, we cannot outrule either guess for the clocking bit of  $R_3$  at cycle t, so we must keep both possibilities.

Figure 4.1 gives a schematic description for the search. The search has two end states: FAIL means that our last guess for  $C_3(t)$  is inconsistent with

<sup>&</sup>lt;sup>1</sup>Unless registers  $R_1$  and  $R_2$  are both in the constant all-zero state, register  $R_3$  will definitely be clocked after a finite number of cycles. If it indeed happens that registers  $R_1$  and  $R_2$  are both in the all-zero state, then for a certain (constant) keystream the test will "hang" until we run out of available keystream. However, our test will finish with very high probability and avoiding the contrary is just a simple matter of implementation.

Figure 4.1: A schematic description of the improved guess-and-determine search

the output keystream, hence, the algorithm must return to the point where the last assumption about the clocking bit  $C_3(t)$  was made. END means that we have found a complete candidate internal state for the three registers and continue to check the solution. We shall call these internal states candidate solutions.

In Figure 4.2, an example of a contradictory guess is given. If the output sequence is  $\mathcal{Z} = 0, 0, 1, \ldots$ , the most significant bit of  $R_3$  must be 1. Now, the clocking bit  $C_3(t)$  is uniquely determined:  $C_3(t) = 1$ . Indeed, if we set  $C_3(t) = 0$ , then register  $R_3$  is not clocked for two consecutive cycles and the output produced is  $\mathcal{Z}' = 0, 0, 0, \ldots$ , so the second clock cycle yields a contradiction.

Figure 4.2: A contradictory state for the output sequence  $\mathcal{Z} = 0, 0, 1, \dots$

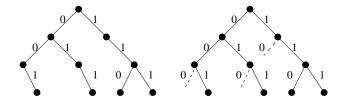

Figure 4.3: A binary solution tree for n = 3. Here, (001), (011), (110) and (111) are valid solutions, whereas (000), (010) and (10) lead to a contradiction.

### 4.1.2 Average-Case Complexity of the Attack

In the following, we shall use a binary solution tree to model our search algorithm. Obviously, for each guess of registers  $R_1$  and  $R_2$ , we can use a full binary tree of depth 11 to represent all possible choices for the 11 clocking bits of register  $R_3$ . In our search, we then start from the root and step down one level in the tree every time register  $R_3$  is clocked. If we did not eliminate contradictions on the fly, our search algorithm would need to go through the entire binary tree  $2^{41}$  times, once for every guess of registers  $R_1$  and  $R_2$ .

Now, in order to model contradictions, we need to build a tree of *consistent* solutions. Such a tree can be obtained by pruning the full binary tree at the nodes where a contradiction is found. A toy example of such a pruned tree is given in Figure 4.3: the tree on the left is a pruned solution tree; the tree on the right also contains deleted edges. It should be noted that we always prune at most one of the two subtrees of a node, since at most one guess for the clocking bit of register  $R_3$  can lead to a contradiction. Hence, in our binary solution tree, all leaves are located at level 11. Each path to a leaf (or shortly, each leaf) corresponds to one consistent choice for the 11 bits of register  $R_3$ , and vice versa.

In order to calculate the complexity of the AKS attack, we need to find the average number of leaves in a solution tree. For this, we first find the average number of children of a non-leaf node. As stated above, all computations in this chapter will be based on the (essentially false but practically reasonable) assumption that the output sequences produced by the three LFSRs are mutually independent and uniformly random. For example, when we make a random guess for the 19 bits of  $R_1$  at t = 0, we assume that  $R_1$  produces random bits even for  $t \geq 19$  (while, in reality, each bit is a linear combination of previous bits). We are now ready to formulate and prove the first result.

**Proposition 4.1.** Assume that the bits entering the clock control of registers  $R_1$  and  $R_2$  and the output bits produced by registers  $R_1$  and  $R_2$  are mutually independent and uniformly random for all  $t \geq 0$ . A non-leaf node in a binary solution tree then has 12/7 children on average, where the average is taken over all solution trees defined by the known keystream  $\mathcal{Z}(t)$  and all possible bit combinations for  $R_1$  and  $R_2$ .

*Proof.* We need to count the average number of edges leaving a non-leaf node. Thus, we need to determine the probability of a contradiction, i.e., the probability that an edge is deleted. The probability that we run into a contradiction during the first cycle is

$$\begin{split} \Pr[\mathsf{fail}(1)] &= & \Pr[C_1(t) = C_2(t) \neq C_3(t)] \cdot \\ & & \Pr[Z(t+1) \neq O_1(t+1) \oplus O_2(t+1) \oplus O_3(t)] = \frac{1}{8} \ . \end{split}$$

The probability that we run into a contradiction during the second cycle is

$$\begin{split} \Pr[\mathsf{fail}(2)] &= & \Pr[C_1(t) = C_2(t) \neq C_3(t)] \cdot \\ & \Pr[Z(t+1) = O_1(t+1) \oplus O_2(t+1) \oplus O_3(t)] \cdot \\ & \Pr[C_1(t+1) = C_2(t+1) \neq C_3(t)] \cdot \\ & \Pr[Z(t+2) \neq O_1(t+2) \oplus O_2(t+2) \oplus O_3(t)] \\ &= & \frac{1}{4} \cdot \frac{1}{2} \cdot \frac{1}{4} \cdot \frac{1}{2} = \frac{1}{8^2} \; . \end{split}$$

Analogously, a contradiction takes place during the *i*th cycle if (a) register  $R_3$  is not clocked for *i* cycles; (b) no contradiction is found for i-1 cycles; and (c) a contradiction is found during the *i*th cycle, so

$$\Pr[\mathsf{fail}(i)] = \frac{1}{4^i} \cdot \frac{1}{2^{i-1}} \cdot \frac{1}{2} = \frac{1}{8^i} \ . \tag{4.3}$$

The overall probability of a contradiction is then

$$\Pr[\mathsf{fail}] = \sum_{i=1}^{\infty} \Pr[\mathsf{fail}(i)] = \sum_{i=1}^{\infty} \frac{1}{8^i} = \frac{1}{7}$$

(4.4)

Here, working under the randomness assumption means, amongst other things, that our computations do not take into account the upper bound for the number of cycles that register  $R_3$  can remain unclocked, but the difference in probabilities is clearly very small.

Now, since the probability of deleting an edge is 1/7, we delete one of the two edges of a non-leaf node with probability 2/7. Indeed, we always prune at most one of the two subtrees, so the two events corresponding to deleting the two edges are mutually exclusive.

We conclude that a non-leaf node of a solution tree has  $1 \cdot 2/7 + 2 \cdot 5/7 = 12/7$  children on average.

As an easy consequence, we can now state the main result of the complexity analysis.

Corollary 4.2. Assume that the conditions of Proposition 4.1 hold. Assume also that all  $2^{64}$  internal states occur with equal probability  $2^{-64}$ . The average-case complexity of the AKS attack is then approximately  $2^{48.6}$  tests.

*Proof.* From Proposition 4.1, it follows that a binary solution tree has on average  $(12/7)^n$  nodes at depth n. Since the number of candidate solutions is equal to the number of leaves in the tree, we conclude that we get on average

$$\mathbf{E}[\mathsf{solns}] = \left(\frac{12}{7}\right)^{11} \approx 376 \tag{4.5}$$

candidate solutions for each of the  $2^{41}$  tests. We can expect to perform half of the tests before we find the right internal state, which gives us a complexity estimate

$$\mathbf{E}[\mathsf{T}] = 2^{41} \cdot \mathbf{E}[\mathsf{solns}] \cdot \frac{1}{2} \approx 2^{48.6} \ .$$

In other words, we have shown that the effective key length of the A5/1 cipher is reduced from 64 bits to less than 50 bits.

This result is different from the complexity analysis of the same attack model by Keller and Seitz [KS01]. In Section 4.1.3, we discuss their analysis and point out the corrections we have made. We have also verified our results in a practical implementation; our theoretical and simulation results agree completely.

### A Complexity Estimate in A5/1 Clock Cycles

When we turn our interest to implementations, we are more interested in finding the time complexity of the attack in low-level operations. In the current case, a natural choice for the operation is one A5/1 cipher clock cycle. The term "clock cycle" should be handled with care here—during the attack, each cycle involves other operations than just shifting the three registers. Nevertheless, for a hardware implementation, an estimate in clock cycles gives a direct relation between the implementation clock frequency and the total expected complexity in wall clock time. In a software implementation, an A5/1 clock cycle is more vague, since one A5/1 clock cycle involves several CPU clock cycles. Still, these estimates are helpful when planning an implementation strategy. We shall give two different complexity estimates that correspond to a typical software and hardware implementation, respectively.

We shall again use the solution tree model to explain the results. Recall that a binary solution tree represents the search corresponding to one choice for the 41 bits of registers  $R_1$  and  $R_2$ : non-leaf nodes correspond to intermediate internal states of the cipher; edges mark consecutive guesses for the bits of  $R_3$ ; and leaves correspond to candidate solutions. The tree has been pruned in such a way that if a guess is contradictory, the corresponding edge (together with the whole subtree) has been deleted. However, since we are counting clock cycles, we must also take into account the time spent on finding contradictions. Therefore, we use the tree model with deleted edges (see Figure 4.3, right).

We divide the attack into three phases. Phase 1 consists of finding candidate solutions. Phase 2 consists of eliminating false solutions by comparing the output generated by a candidate internal state against further known keystream. When a candidate solution passes Phase 2, its correctness should be verified by rewinding the algorithm to the initial state and comparing against another frame—this is Phase 3. The time complexity of Phase 1 is estimated in the following section. Phase 2 is inspected in Section 4.1.2. Techniques for Phase 3 are also briefly discussed in the same section, although the time complexity is in this case notably smaller.

### Software-Oriented Strategy

Suppose first that the implementation is a simple depth-first traversal of the tree, and the intermediate states of the registers are kept in memory, as it is feasible in a software implementation. Then, each edge in the tree is traversed once and the time required to complete one of the 2<sup>41</sup> tests is proportional to the number of edges in the tree. Let us start with some simple facts.

**Proposition 4.3.** Assume that the bits entering the clock control of registers  $R_1$  and  $R_2$  and the output bits produced by registers  $R_1$  and  $R_2$  are mutually independent and uniformly random for all  $t \geq 0$ . A binary solution tree then has approximately 525 non-leaf nodes and approximately 1050 edges on average, where deleted edges are included in the count and the average is taken over all solution trees defined by the known keystream  $\mathcal{Z}(t)$  and all possible bit combinations for  $R_1$  and  $R_2$ .

*Proof.* Since a non-leaf node was shown to have 12/7 children on average, and all leaf nodes are located at level 11, the average number of non-leaf nodes is

$$\mathbf{E}[\mathsf{nl} - \mathsf{nodes}] = \sum_{i=0}^{10} \left(\frac{12}{7}\right)^i \approx 525,$$

as desired. Furthermore, each non-leaf node has exactly two outgoing edges, provided that we count deleted edges. Thus, the average number of edges in a tree is  $\mathbf{E}[\mathsf{edges}] \approx 1050$ .

Consider now a non-leaf node in a tree and the corresponding internal state of the registers. We will find the average number of cycles needed to process a guess for the next clocking bit of  $R_3$ , i.e., the average number of cycles spent before register  $R_3$  is clocked. In solution tree terms, we are evaluating the average number of cycles required to traverse an edge, counting also for the deleted edges leading to a contradiction. Multiplying the result with the number of edges will give us the desired complexity estimate.

**Proposition 4.4.** Assume that the bits entering the clock control of registers  $R_1$  and  $R_2$  and the output bits produced by registers  $R_1$  and  $R_2$  are mutually independent and uniformly random for all  $t \geq 0$ . Also, assume that each edge in a solution tree is traversed exactly once. Traversing one edge in a solution tree with deleted edges then takes 8/7 A5/1 clock cycles on average, where the average is taken over all solution trees defined by the known keystream  $\mathcal{Z}(t)$  and all possible bit combinations for  $R_1$  and  $R_2$ .

*Proof.* Let cycles be the number of cycles required to traverse an edge. Processing a guess for the next clocking bit of  $R_3$  always takes at least one clock cycle, so  $\Pr[\text{cycles} \geq 1] = 1$ . Next, processing a guess takes at least two clock cycles if and only if the following events take place: (a) register  $R_3$  stops for the first clock cycle, i.e.,  $C_1(t) = C_2(t) \neq C_3(t)$ ; and (b) no contradiction is found after the first clock cycle, i.e.,  $Z_3(t+1) = O_1(t+1) + O_2(t+1) + O_3(t)$ .

Since  $R_3$  stops with probability 1/4 and the output bit check fails with probability 1/2, we conclude that

$$\begin{split} \Pr[\mathsf{cycles} \geq 2] &= \Pr[C_1(t) = C_2(t) \neq C_3(t)] \cdot \\ &\quad \Pr[Z_3(t+1) = O_1(t+1) + O_2(t+1) + O_3(t)] \\ &= \frac{1}{4} \cdot \frac{1}{2} = \frac{1}{8} \ . \end{split}$$

In general, traversing an edge takes at least i cycles if (a) register  $R_3$  is not clocked for i-1 cycles; and (b) no contradiction is found for i-1 consecutive checks. Therefore, the probability that traversing an edge takes at least i cycles is

$$\Pr[\mathsf{cycles} \ge i] = \frac{1}{4^{i-1}} \cdot \frac{1}{2^{i-1}} = \frac{1}{8^{i-1}} , \qquad (4.6)$$

where the first term in the product corresponds to event (a) and the second to event (b). Conclusively, traversing an edge takes

$$\mathbf{E}[\mathsf{cycles}] = \sum_{i=1}^{\infty} \Pr[\mathsf{cycles} \ge i] = \sum_{i=1}^{\infty} \frac{1}{8^{i-1}} = \frac{8}{7}$$

cycles on average.

Therefore, the average time required to traverse a solution tree is

$$\mathbf{E}[\mathsf{tree}] = \mathbf{E}[\mathsf{cycles}] \cdot \mathbf{E}[\mathsf{edges}] \approx 1199$$

A5/1 clock cycles. It is now straightforward to give a complexity estimate in A5/1 clock cycles for a typical software implementation.

Corollary 4.5. Assume that the conditions of Propositions 4.3 and 4.4 hold. Assume also that all  $2^{64}$  internal states occur with equal probability  $2^{-64}$ . The average-case time complexity of Phase 1 in a software-oriented attack is then  $2^{50.2}$  A5/1 clock cycles.

*Proof.* We can expect to perform half of the tests before we find the right internal state. Multiplying the number of tests, the average number of edges in a tree, the average number of clock cycles required to traverse an edge and dividing the result by 2 yields

$$\mathbf{E}[\mathsf{T}_1^{\mathsf{soft}}] = 2^{41} \cdot \mathbf{E}[\mathsf{tree}] \cdot \frac{1}{2} \approx 2^{50.2} \ .$$

Finally, we remark that on average 3.2 clock cycles are spent on finding each candidate solution.

### Hardware-Oriented Strategy

In the depth-first search used in the software-oriented strategy, we need to store in memory the internal states of registers  $R_1$  and  $R_2$  for each level in the tree, in order to be able to backtrack to the last branching point. Since the efficiency of a hardware implementation depends on the area used up by the test, a different strategy might prove useful for a hardware implementation. Namely, instead of keeping up to 11 backtracking points, it is possible to keep a simple 11-bit counter to record which 11-bit combinations for the bits of  $R_3$  have already been checked. The state of the counter then represents 11 consecutive guesses for the bits of  $R_3$ : every time we reach a leaf node in the tree (i.e., we find a candidate solution), registers  $R_1$  and  $R_2$ are re-initialised and the counter is increased by 1. That is, each check is started over from the root node. For example, assume that the 11 consecutive guesses (00101010111) yield a candidate solution. Then we would proceed by setting the clocking bits of  $R_3$  to (00101011000) for the next check. Contradictions can be processed analogously: suppose that the counter is set to (00101010111), but at level 5 we encounter a contradiction, so that (00101) cannot be completed to a full solution. Then, the remaining guesses beginning with the contradictory prefix (00101) should be skipped and the counter should be set to (00110000000) for the next check.

We proceed to compute the time complexity of the attack in A5/1 clock cycles. Note that while in case of a software-oriented strategy, each edge is traversed once, in case of the current strategy, each *path* is traversed once. This means that edges closer to the root are traversed more often. Thus, we need to recompute the expected number of cycles required to traverse an edge, taking into account the weights of the edges.

**Proposition 4.6.** Assume that the bits entering the clock control of registers  $R_1$  and  $R_2$  and the output bits produced by registers  $R_1$  and  $R_2$  are mutually independent and uniformly random for all  $t \geq 0$ . Also, assume that each path in a solution tree is traversed exactly once. Traversing a solution tree with deleted edges then takes approximately 6374 A5/1 clock cycles on average, where the average is taken over all solution trees defined by the known keystream  $\mathcal{Z}(t)$  and all possible bit combinations for  $R_1$  and  $R_2$ .

*Proof.* First, we show that the average number of cycles required to traverse an edge is independent of the fact whether the edge is a deleted edge (i.e., one leading to a contradiction) or not. According to (4.4), the probability of

an edge being deleted is Pr[fail] = 1/7. Analogously, according to (4.3),

$$\begin{split} \Pr[\mathsf{cycles} \geq i \,\&\, \mathsf{fail}] &= \sum_{j=i}^{\infty} \Pr[\mathsf{fail}(j)] = \sum_{j=i}^{\infty} \frac{1}{8^i} = \frac{1}{8^{i-1}} \cdot \frac{1}{7} \\ &= \Pr[\mathsf{cycles} \geq i] \cdot \Pr[\mathsf{fail}] \enspace, \end{split}$$

where the last equality is obtained from (4.6). Thus,

$$\mathbf{E}[\mathsf{cycles}|\mathsf{fail}] = \mathbf{E}[\mathsf{cycles}] = \frac{8}{7}$$

.

Next, note that each deleted edge is traversed exactly once. For all other edges, the number of times an edge is traversed equals the number of leaves in the subtree hanging from that edge. The average number of such leaves, in turn, depends only on the level the edge is located at. Thus, the weighted average for the number of clock cycles required to traverse an edge is still  $\mathbf{E}[\mathsf{cycles}] = 8/7$ .

Finally, we count the total number of edge traversals  $\mathbf{E}[\text{trav}]$ . There are two types of paths: paths of length 11 ending with a leaf and paths of various lengths ending with a deleted edge. The average number of paths of length 11 equals the average number of leaves in a tree, that is,  $(12/7)^{11} \approx 376$ . The average number of paths of length i ending with a deleted edge equals the average number of one-child nodes at depth i-1, that is,  $(12/7)^{i-1} \cdot 2/7$ . Summing up the traversals, we get

$$\mathbf{E}[\mathsf{trav}] = 11 \cdot \left(\frac{12}{7}\right)^{11} + \sum_{i=1}^{11} i \cdot \frac{2}{7} \cdot \left(\frac{12}{7}\right)^{i-1} \approx 5577 \ .$$

We conclude that the average time required to traverse a solution tree is

$$\mathbf{E}[\mathsf{tree}] = \mathbf{E}[\mathsf{cycles}] \cdot \mathbf{E}[\mathsf{trav}] \approx 6374$$

.

We have also verified this result by doing an implementation of the hardware-oriented strategy in software. Over 100 000 000 simulations, the average time required to traverse a tree was 6373.83 cycles (theoretical estimate 6373.60). We also remark that on average,  $\mathbf{E}[\mathsf{tree}]/\mathbf{E}[\mathsf{solns}] \approx 17$  clock cycles are spent on each solution. Again, it is now straightforward to compute the total time complexity.

Corollary 4.7. Assume that the conditions of Proposition 4.6 hold. Assume also that all  $2^{64}$  internal states occur with equal probability  $2^{-64}$ . The average-case complexity of Phase 1 in a hardware-oriented attack is then approximately  $2^{52.6}$  A5/1 clock cycles.

*Proof.* As usual, we can expect to perform half of the tests before we find the right internal state. Multiplying the number of tests, the average number of cycles per test and dividing the result by 2 yields

$$\mathbf{E}[\mathsf{T}_1^{\mathsf{hard}}] = 2^{41} \cdot \mathbf{E}[\mathsf{tree}] \cdot \frac{1}{2} \approx 2^{52.6} \ .$$

### **Eliminating False Solutions**

After a search branch has been completed and a candidate solution has been found, it also needs to be compared against further known keystream bits to check whether the candidate internal state indeed generates the expected sequence. Our final result shows that this can be done in two clock cycles on average.

**Proposition 4.8.** Assume that the output sequence produced by an incorrect candidate internal state is uniformly random. Discarding an incorrect solution then takes 2 clock cycles on average, where the average is taken over all possible output sequences.

Proof. Under the assumption that the output sequence generated by an internal state is uniformly random, we can expect this sequence to differ from the remaining known keystream already in the first bit with probability 1/2. The probability that the sequences coincide in the first bit, but differ in the second bit, is then 1/4, and, generally, the probability that the sequences first differ in the nth bit is  $2^{-n}$ . Thus, the number of steps required to eliminate a false candidate solution is a geometric random variable with parameter p = 1/2 and expectation 1/p = 2.

In practice, one would want to set an upper limit for the total number of compared bits. Since there are  $2^{64}$  possible internal states, 64 bits might be a suitable threshold.

We conclude the complexity analysis by comparing the total average time required to complete Phases 1 and 2 of the AKS attack using softwareoriented and hardware-oriented strategies.

Corollary 4.9. Assume that the conditions of Proposition 4.8 and Corollaries 4.5 and 4.7 hold. The overall average-case complexity of the AKS attack is then 2<sup>50.9</sup> A5/1 clock cycles in the software-oriented case and 2<sup>52.8</sup> A5/1 clock cycles in the hardware-oriented case.

*Proof.* The average time spent on Phase 2 is in both cases

$$\mathbf{E}[\mathsf{T}_2] = 2^{41} \cdot 2 \cdot \mathbf{E}[\mathsf{solns}] \cdot \frac{1}{2} = 2^{41} \cdot \left(\frac{12}{7}\right)^{11} \approx 2^{49.6}$$

clock cycles. The overall average-case complexity of the attack is now

$$\mathbf{E}[\mathsf{T}^{\mathsf{soft}}] = \mathbf{E}[\mathsf{T}_{\mathsf{1}}^{\mathsf{soft}}] + \mathbf{E}[\mathsf{T}_{\mathsf{2}}] \approx 2^{50.9}$$

A5/1 clock cycles in the software-oriented case and

$$\mathbf{E}[\mathsf{T}^{\mathsf{hard}}] = \mathbf{E}[\mathsf{T}_1^{\mathsf{hard}}] + \mathbf{E}[\mathsf{T}_2] \approx 2^{52.8} \tag{4.7}$$

A5/1 clock cycles in the hardware-oriented case.

It remains to invert the algorithm to extract the secret session key (Phase 3), however, Phases 1 and 2 will dominate in the overall complexity of the attack. Strategies for completing Phase 3 will be discussed next.

#### **Initial State Reversion**

Previously, we have described attack models for reconstructing the internal state of the cipher at the time when the cipher produces its first output bit, i.e., 100+1 clock cycles after initialisation. In order to successfully complete the attack, it is also necessary to reverse the internal state and find the initial state of the cipher after the initialisation phase.

Suppose that the attacker succeeds in finding the initial state. Since the frame counter is publicly known, the algorithm can then be reversed to find the state after the mixing of the session key but before the mixing of the frame counter, i.e., 64 cycles after the start of initialisation. This reversal is straightforward, since during initialisation, registers are clocked in a regular fashion, without the stop/go clocking rule. After the effect of the frame counter has been eliminated, there is actually no need to derive the session key. The state after the input of the session key is common to all frames and can be used directly in decryption.

Denote the initial state, i.e., the state after the initialisation has been completed by S(0). We are interested in recovering this unknown state from the now known internal state S(101). This can be done by guessing individually for each of the three registers the number of times it has been clocked. For each such guess, the registers can first be reverted to their corresponding states in S(0). Next, the A5/1 algorithm can be run forward for 101 cycles to test whether the state after 101 stop/go-clocked steps is indeed S(101).

Even if we do not take into account any of the mutual clocking constraints, we know that each of the registers was clocked between 0 and 101 times. This gives us  $102^3 \approx 2^{20}$  states to test. Since backwards clocking is an independent process for each register, it can be done by e.g. table look-up. Running the cipher forward with irregular clocking to obtain S(101) from S(0) will take 101 clock cycles. Altogether, even in the worst case and with the most naive implementation, it will take less than  $2^{30}$  A5/1 clock cycles to find the initial state.

The search can further be made much more efficient by taking into account that at each step, each register is clocked with probability 3/4, and therefore, the expected number of clocks is  $(3/4) \cdot 101 \approx 76$ . Starting the search from the most probable values for each LFSR will clearly make finding a solution much more efficient.

However, it can happen that several initial states produce the same internal state S(101)—whereas only one of them is the correct S(0) that reveals the session key after eliminating the effect of the frame counter. If one wants to take into account this possibility, then one has to perform an exhaustive search over all possible clockings. Still, due to the majority rule in clocking, there is no need to go over all possible  $102^3$  values. One can simply take into account that since at each cycle at least two registers are clocked, during 101 cycles the three LFSRs have to be clocked at least 202 times.

In any case, the complexity of this part of the attack is insignificant compared to that of deriving the internal state S(101).

### 4.1.3 Discussion on a Previous Complexity Analysis

In this section, we discuss the complexity analysis of the Anderson-Keller-Seitz attack given by Keller and Seitz. First, we review their estimate on the average number of candidate solutions. Citing the analysis of [KS01]:

If the clock bits of R1 and R2 are identical, then both registers are clocked. If we assume the clock bit of R3 to be different, then R3 will not be clocked, and its most significant bit in the next cycle will remain the same. The output bit generated by an exclusive-or operation of the most significant bits can then be compared to the bit of the output sequence  $\mathcal{O}$ . If they differ, then this possibility was a false one and the clock bits must be equal. If the output bit produced and the bit from the output sequence are identical, we pursue this possibility. Thus, in one half of the situations (R1 and R2 having identical clock bits) on the average,

we reduce the number of possibilities from two to one and have to check  $(3/2)^{11} \approx 85$  cases.

These results are different from the results presented above, where the average number of cases is approximately 376. According to our analysis, this argumentation is not correct. Namely, if the exclusive-or of the most significant bits and the bit of the output sequence differ, then we can indeed decide that all clock bits must be equal. However, if the bits are identical, we cannot decide anything—we still need to consider both cases. This analysis therefore excludes some candidate solutions and an implementation according to this strategy may fail to find the key. According to (4.5) (c.f. Section 4.1.2), the correct value for the number of candidate solutions is 376.

Keller and Seitz state that each check inspects 14 output bits on average. Although not explained in the paper, this implies that they follow the hardware-oriented strategy, i.e., each check is started from the beginning. Since the number of inspected output bits is equivalent to the number of A5/1 clock cycles spent, they claim to spend 14 clock cycles per solution. This value is different from our theoretical estimate, which is approximately 17 clock cycles. One reason to this difference could be that we have taken into account also those cycles that lead to a contradiction and thus never yield a full solution. Simulating the attack in software, we have also found that our practical results agree with our theoretical estimate, however, we admit that there may be differences in implementations that we are not aware of.

As to the extraction of the right solution from the set of candidate solutions, Keller and Seitz state that "false possibilities can be eliminated fast". We have shown above that it takes on average 2 clock cycles to eliminate false candidates. Taking this into account, the number of clock cycles spent on each candidate solution in the hardware-oriented strategy is now 19.5 according to our analysis, or 16 according to the claims of Keller and Seitz.

# 4.1.4 Implementations

In this section, we compare two implementations of the Anderson-Keller-Seitz guess-and-determine attack. The first is our own implementation in software, whereas the second is an FPGA implementation by Keller and Seitz. The first attack is implemented by using software-oriented strategy; for the FPGA attack, we do not know the implementation details, but the computations of the authors imply that hardware-oriented strategy was followed (c.f. Section 4.1.2). We compare our theoretical results on the attack complexity with statistics from simulations and estimate the wall clock time

complexity of our implementation on our test platform. We also give an estimate for the time requirement of the hardware implementation, however, these results should be considered less precise, since the implementation is not our own and its full details are not known to us.

#### A Software Implementation of the Attack

We have implemented the Anderson-Keller-Seitz guess-and-determine attack in software, using the first strategy, i.e., doing a depth-first search, while keeping the intermediate states in memory. All the following statistics are averaged over 100 million test runs with pseudorandom selections of the states of registers  $R_1$  and  $R_2$ , and of the output keystream. The simulations were run on a PC with the following parameters:

| CPU:              | Intel Celeron M, 1300MHz, Banias-512 core           |

|-------------------|-----------------------------------------------------|

| Memory:           | 256 MB                                              |

| Operating system: | Windows XP Home Edition SP 1                        |

| Compiler:         | GCC v.3.3.3 (cygwin special), optimisation level O4 |

Table 4.1: Test platform for the AKS attack in software