Chandrasekar, H., Bhat, K. N., Rangarajan, M., Raghavan, S., & Bhat, N. (2017). Thickness Dependent Parasitic Channel Formation at AlN/Si Interfaces. *Scientific Reports*, 7(1), 15749. https://doi.org/10.1038/s41598-017-16114-w

Publisher's PDF, also known as Version of record

License (if available):

CC BY

Link to published version (if available): 10.1038/s41598-017-16114-w

Link to publication record in Explore Bristol Research PDF-document

## **University of Bristol - Explore Bristol Research** General rights

This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/pure/about/ebr-terms

Received: 15 August 2017 Accepted: 7 November 2017

Published online: 16 November 2017

# **OPEN** Thickness Dependent Parasitic Channel Formation at AIN/Si **Interfaces**

Hareesh Chandrasekar 61,2,4, K. N. Bhat1, Muralidharan Rangarajan1, Srinivasan Raghavan1,2 & Navakanta Bhat<sup>1,3</sup>

The performance of GaN-on-Silicon electronic devices is severely degraded by the presence of a parasitic conduction pathway at the nitride-substrate interface which contributes to switching losses and lower breakdown voltages. The physical nature of such a parasitic channel and its properties are however, not well understood. We report on a pronounced thickness dependence of the parasitic channel formation at AIN/Si interfaces due to increased surface acceptor densities at the interface in silicon. The origin of these surface acceptors is analyzed using secondary ion mass spectroscopy measurements and traced to thermal acceptor formation due to Si-O-N complexes. Low-temperature (5 K) magneto-resistance (MR) data reveals a transition from positive to negative MR with increasing AIN film thickness indicating the presence of an inversion layer of electrons which also contributes to parasitic channel formation but whose contribution is secondary at room temperatures.

The availability of large area silicon substrates at low cost, allied with the development of CMOS-compatible process flows for GaN device fabrication are rapidly enhancing the commercial viability of GaN-on-silicon electronics, making such devices cost-competitive with traditional Si-based solutions for high-power, high-frequency applications<sup>1-7</sup>. GaN-on-Si discrete power devices such as high electron mobility transistors (HEMTs) and diodes are expected to have a major impact in terms of switching efficiency and size (form-factor) in the 200-1200 V application ranges8. For RF applications, GaN HEMTs on SiC deliver the best performance at a higher cost, with GaN-on-Si expected to have more of an impact on price-sensitive markets such as wireless base station amplifiers, satellite communication and cable television(CATVs)<sup>9,10</sup>. In view of the potential held out by GaN-on-Si electronics, a thorough understanding and control of all aspects affecting their device performance is timely and of utmost importance. One such issue is the presence of a parasitic channel at the epitaxial nitride-silicon interface. Substrate losses are a major concern for RF applications due to eddy currents induced by capacitive coupling between the substrate and channel at such high frequencies (2.4 GHz in wireless base stations, for instance), which is the reason GaN-on-Si HEMTs for high-frequency operation are manufactured on high resistivity  $(>10,000~\Omega$ -cm HR-Si) substrates. Hence, the presence of a parasitic conduction pathway at the nitride-silicon interface is detrimental in terms of the switching efficiency and reduces the output power that can be extracted from these devices<sup>7,11,12</sup>. GaN power transistors on silicon, on the other hand, switch at more modest frequencies (~1 MHz) which reduces the impact of substrate switching losses and are commonly fabricated on low resistivity Si substrates. However, the presence of a parasitic channel in power devices has been shown to contribute to higher leakage currents and lead to accelerated breakdown, effectively reducing the off-state blocking voltages of these devices<sup>13–16</sup>. Substrate parasitic channel formation is therefore a pressing technological issue affecting the performance and reliable operation of GaN-on-Si transistors for both RF and power device applications. In the following sections, we first examine the possible sources of the parasitic substrate channel and follow it up with our experimental results, discussions and conclusions.

<sup>1</sup>Centre for Nano Science and Engineering, Indian Institute of Science, Bangalore, 560012, India. <sup>2</sup>Materials Research Centre, Indian Institute of Science, Bangalore, 560012, India. 3 Department of Electrical Communication Engineering, Indian Institute of Science, Bangalore, 560012, India. <sup>4</sup>Present address: Centre for Device Thermography and Reliability, HH Wills Physics Laboratory, University of Bristol, Bristol, BS81TL, UK. Correspondence and requests for materials should be addressed to H.C. (email: hareeshc2408@gmail.com) or N.B. (email: navakant@iisc.ac.in)

#### On the Origin of the Parasitic Substrate Channel

The physical origin of the parasitic substrate channel can be traced back to the growth of III-nitride stacks on silicon. The epitaxy of GaN on Si universally begins with an AlN nucleation layer due to the melt-back etching observed for direct growth of GaN on Si<sup>17-19</sup>. This is followed by the introduction of stress-mitigating transition layers for defect and stress management and subsequently, the GaN buffer and the active device layers including the AlGaN/GaN heterojunction which constitute the HEMT<sup>20</sup>. AlGaN/GaN interfaces demonstrate extremely high two-dimensional electron gas (2DEG) densities (~10<sup>13</sup> cm<sup>-2</sup>) due to the difference in spontaneous and piezoelectric polarization between these two materials<sup>21</sup>, while the source of these electrons is widely attributed to donor-like surface states which populate the potential well<sup>22</sup>. In this context, it is well worth pointing out that nitride growth on silicon inherently gives rise to a dissimilar semiconductor-semiconductor hetero-interface at the AlN/Si junction. AlN is a wide band gap semiconductor and possesses the highest value of spontaneous and piezoelectric polarization among the family of group III-A nitrides and hence leads to a very large "polarization step" at the interface with non-polar Si substrates. Typically, MOCVD growth of AlN on Si gives rise to Al-polar material which leads to a positive fixed charge density at the interface. The magnitude of spontaneous polarization in single crystalline AlN is  $0.081 \, \text{C/m}^2$ , corresponding to an interfacial charge density of  $5 \times 10^{13} \, \text{cm}^{-2}$  for the case of an ideal defect-free interface<sup>23</sup>. We note that for good quality material, the nature of such an interface is clean and abrupt, devoid of any amorphous interfacial layers<sup>19,24</sup>. Furthermore, AlN films are strained in tension during growth on Si and hence any piezoelectric polarization field is expected to add to the existing spontaneous polarization component 12,21,25. However, the severe lattice and thermal mismatches between AlN and Si give rise to c-axis oriented AlN domains of 50-100 nm which then coalesce to form a defective AlN film, with a dislocation density of 1013 cm<sup>-2</sup> typically observed in these layers<sup>25,26</sup>. These defective regions could reduce the magnitude of polarization charge at the interface by disrupting the epitaxial registry of nitride films. The presence of an interfacial fixed positive charge due to polarization differences will lead to an inversion layer of electrons in the Si substrate even for no applied bias. However, the mobility of these mobile interfacial carriers is expected to be poor due to defects and imperfections at the interface acting as trap states in silicon. An inversion layer of electrons at the AlN/Si interface, attributed to the polarization in AlN, with surface donors contributing these electrons has been inferred previously in literature, with Yacoub et al. extracting an electron density of  $3 \times 10^{13}$  cm<sup>-3</sup> without freeze-out at temperatures down to 77 K<sup>14</sup>, while Luong et al. have measured a higher RF transmission line loss for thicker AlN films on HR-Si as compared to thinner ones, attributed to higher interfacial electron densities.

On the other hand, the growth of III-nitrides also involves the introduction of Al and Ga containing precursors into the reaction chamber at extremely high temperatures ( $>900\,^{\circ}$ C for MOCVD layers) which could lead to auto-doping of the exposed silicon surface by Al/Ga atoms, which are acceptors in Si and hence dope the substrate p-type. The presence of significant stresses in these films ( $>1\,\mathrm{GPa}$ )<sup>26,27</sup> and extended line defects such as dislocations could also serve as localized pathways for the diffusion and segregation of Al and Ga from nitride films to the substrate. Contrary to the inversion layer of electrons discussed before, this mechanism would give rise to mobile holes and immobile ionized acceptors in Si. Such a parasitic channel due to Ga (and to a lesser extent Al) diffusion into the Si with a surface concentration  $>10^{17}\,\mathrm{cm}^{-3}$  and their effect on RF transmission line losses has also been reported<sup>11</sup>.

We thus have two plausible but entirely distinct mechanisms for parasitic channel formation, both of which have been experimentally observed, and which can operate either individually or together contributing to observed RF and power performance degradation. Additional factors such as the diffusion of other growth species during the epitaxy of nitride films into silicon (N, C and O to name a few), and contributions from dopant re-distribution in Si substrates themselves during the high growth temperatures, can also affect parasitic channel formation. But the effects of these other factors have not hitherto been observed or explored.

From the above discussion, we see that the exact mechanisms underlying the formation of the substrate parasitic conduction channel are quite involved and need careful and systematic investigation to unravel. As a first step in this direction, this paper focuses solely on the role of AlN nucleation layers in parasitic channel formation for MOCVD grown epitaxial nitride stacks on Si. Using a combination of C-V and conductance spectroscopy we show that the parasitic channel formed at the AlN/Si interface is due to increased acceptor density at the surface of the substrate and it demonstrates a rather striking dependence on the thickness of the AlN films grown. Thicker AlN films display both a higher acceptor density in Si and a higher trap density at the AlN/Si interface. Secondary-ion mass spectrometry (SIMS) results are presented and correlated with electrical measurements, which show that the formation of thermal acceptor complexes in silicon are the proximate cause for parasitic channel formation at these AlN/Si interfaces. Additionally, low-temperature magnetoresistance measurements reveal a transition from positive to negative magneto-resistance with increasing AlN thickness, with a square dependence at low magnetic fields indicative of two-dimensional carrier confinement due to an inversion layer of electrons at the interface.

### **Results and Discussion**

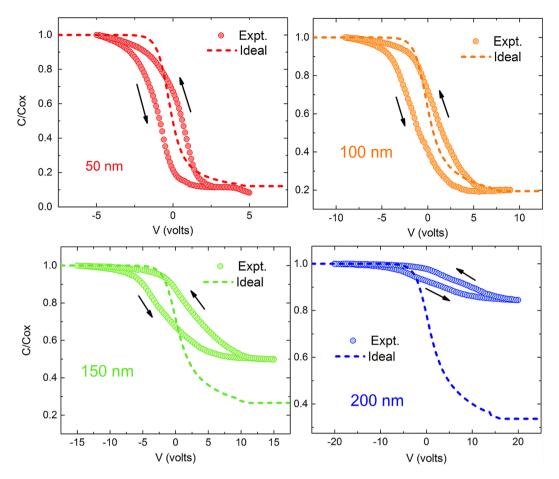

Capacitance-Voltage Measurements of AlN/Si Interfaces. Capacitance measurements are one of the most versatile methods to characterize semiconductor interfaces and have been extensively applied to nitride thin films  $^{28,29}$ . Since the use of HR-Si substrates makes CV measurements challenging due to additional substrate capacitance contribution, p-Si substrates (~5  $\Omega$ .cm) were used for these experiments. Al/AlN/p-Si capacitors were fabricated with four different AlN film thicknesses - 50, 100, 150 and 200 nm $^{30}$ . The measured high frequency C-V curves (1 MHz) for all four AlN thicknesses normalized to their dielectric capacitances are as shown in Fig. 1. Also plotted alongside are the ideal high-frequency MOSCAP C-V curves, calculated for p-type Si samples of the same doping density used in the experiments  $^{28}$ . The three notable features that can be observed from these C-V curves are the following:

**Figure 1.** Normalized 1 MHz C-V curves of AlN/p-Si capacitors for the four AlN thicknesses - 50, 100, 150 and 200 nm - investigated in this study. Also shown are the ideal high-frequency C-V curves for each thickness for comparison. The 150 nm and 200 nm capacitances show significant deviations from the ideal behavior at positive bias voltages for reasons discussed in the text.

- Hysteresis between forward and reverse voltage sweeps.

- Stretch out of the measured C-V as compared to the ideal case.

- The deviations in depletion and inversion capacitance from the ideal case observed for the 150 nm and 200 nm AlN samples.

Both the anti-clockwise hysteresis loops and the stretch-out in the CV indicate the presence of trap states at the interface. An estimate of the interface trap density from the hysteresis can be obtained by estimating the shift in the flat-band voltages for the forward and reverse sweeps i.e  $N_{it} = C_{ox} \Delta V_{FB}/q$ , where  $N_{it}$  is the interface trap density in cm<sup>-2</sup>,  $C_{ox}$  the dielectric capacitance at accumulation and  $\Delta V_{FB}$  the shift in flat-band voltage.

The presence of interface traps can be further quantified by the stretch out in the measured 1 MHz C-V curves when compared to ideal high frequency C-V characteristics. The interface trap density can be extracted from the high-frequency C-V curves by employing Terman's method i.e,

$$D_{it} = \frac{C_{ox}}{q} \left[ \left( \frac{d\psi_s}{dV} \right)^{-1} - 1 \right] - \frac{C_D}{q} \tag{1}$$

where  $C_{ox}$  stands for the dielectric capacitance,  $C_D$  the depletion capacitance, and  $\psi_s$  the surface potential<sup>28</sup>. The interface trap densities for the different AlN thicknesses as extracted from the hysteresis and Terman's method are summarized in Table 1. We see that these magnitudes compare favorably with reported values for high-k/Si interfaces. The large deviations of the measured capacitance from the ideal values at inversion for the 150 and 200 nm films prevent the accurate estimation of trap densities.

Lastly, the thicker samples clearly show deviations from the ideal C-V case, in the form of much higher capacitances in the depletion and inversion region. While this effect is absent in case of the 50 and 100 nm samples, it begins to manifest in the 150 nm case. In case of the 200 nm, the capacitance in the inversion region is much higher than even the expected flat band capacitance for this sample. This feature cannot be explained merely by the presence of an inversion layer of electrons at this interface. Two possible reasons for such an increase in capacitance are the presence of a very high density of interfacial traps or increased p-type doping of the Si close

| AlN film<br>thickness (nm) | Trap Density from Hysteresis $C_{ox}\Delta V_{FB}/q$ (cm <sup>-2</sup> ) | Trap Density at midgap from Terman's method (cm <sup>-2</sup> ) |

|----------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|

| 50                         | $1.26 \times 10^{12}$                                                    | $1.74 \times 10^{12}$                                           |

| 100                        | $1.22 \times 10^{12}$                                                    | $2.07 \times 10^{12}$                                           |

| 150                        | $1.33 \times 10^{12}$                                                    | _                                                               |

| 200                        | _                                                                        | _                                                               |

**Table 1.** Interface trap densities, for the four different AlN thicknesses, as extracted from the hysteretic shift in flat band voltage and Terman's method. Trap densities for the thicker samples cannot be extracted as the inversion capacitance deviates significantly from its expected value as discussed in the text, and in the 200 nm case, observed  $C_{\min} > C_{\text{FB}}$ .

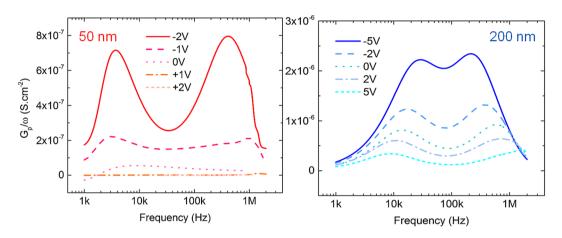

**Figure 2.** Normalized conductance  $(G_p/\omega)$  as a function of frequency for the 50 nm (left) and 200 nm (right) thick AlN films on p-Si, swept from depletion into weak inversion. Both samples show two distinct traps corresponding to slow and fast trap states with the 200 nm sample having ~3x the trap densities as the 50 nm AlN film.

to the AlN/Si interface. However, given the estimates for trap densities extracted above and a <5% dispersion in  $C_{max}$  and  $C_{min}$  observed over a 1 kHz-1MHz frequency range, it is unlikely that trap states are the cause of this feature. Trap densities extracted from a conductance technique on these samples also reveal that the interfacial density does not increase significantly to justify such as assertion and will be discussed next. This suggests that the increased acceptor concentration at the surface of Si, which would lead to a narrower maximum depletion width and increased  $C_{min}$ , is the cause of the observed deviation from the expected CV curves for thicker AlN samples. Assuming that the up-shift in  $C_{min}$  is due to increased surface p-type doping, the extent of such doping is estimated to be  $5.07\times10^{17}\,\rm cm^{-3}$  from the value of the minimum capacitance, while the doping density of the starting Si substrate used was  $2.8\times10^{15}\,\rm cm^{-3}$ . The interface trap density ( $D_{it}$ ) value for the 200 nm film can now be estimated using Terman's method with this increased doping density and is found to be  $3\times10^{12}\,\rm cm^{-2}$  at midgap. This is larger than the trap densities observed for the thinner films, but not significantly high enough to increase  $C_{min}$  by itself, and again points to increased surface p-type doping in Si.

Conductance Spectroscopy Measurements of AlN/Si Interfaces. To further elucidate the electrical properties of the AlN/Si interface and their thickness dependence, conductance spectroscopy was used to quantify the interfacial trap densities and their characteristic time constants of these samples. The normalized conductance  $(G_p/\omega)$  is related to the measured capacitance  $(C_m)$  and conductance  $(G_m)$  as

$$\frac{G_p}{\omega} = \frac{\omega G_m C_{ox}^2}{G_m^2 + \omega^2 (C_{ox} - C_m)^2}$$

(2)

where  $\omega$  and  $C_{ox}$  are the angular measurement frequency and capacitance of the gate dielectric respectively. In case of a continuous distribution of interface states in energy throughout the band gap, the normalized conductance is in turn related to the interface trap density  $D_{it}$  as

$$\frac{G_p}{\omega} = \frac{qD_{it}}{2\omega\tau_{it}}\ln[1 + (\omega\tau_{it})^2]$$

(3)

where  $\tau$  it is the interface trap time constant  $(R_{it} * C_{it})$ . The expression for  $D_{it}$  can further be approximated in terms of conductance maxima as  $D_{it} = 2.5/q * (G_p/\omega)^{31}$ . For the sake of brevity, we restrict our discussions to the conductance spectra of the 50 nm and 200 nm samples, which are as shown in Fig. 2.

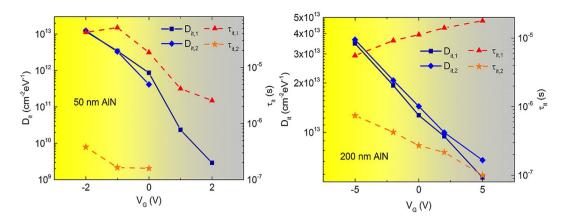

**Figure 3.** Evolution of  $D_{it}$  and  $\tau_{it}$  in the depletion region with gate voltage for 50 nm (left) and 200 nm (right) AlN/p-Si capacitors. Slow and fast traps are denoted by suffixes 1 and 2 respectively. Higher trap densities are observed in the case of the thicker AlN film while the time constants remain similar.

We see that two distinct slow and fast trap states are observed for both film thicknesses, having similar time constants that vary with applied gate bias, which indicates that increasing the AlN film thickness does not give rise to additional traps. However, the density of existing traps is exacerbated as can be observed from the higher  $G_n/\omega$  values for the 200 nm thick films compared to the 50 nm sample. Figure 3 plots the trap densities and characteristic time constants as a function of applied bias for the 50 and 200 nm AlN films. For the 50 nm AlN films, the slow traps (denoted by  $\tau_{it,1}, D_{it,1}$ ) have a maximum time constant of  $4.23 \times 10^{-5}$  s with a zero bias  $D_{it}$  of  $8.6 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> while the minimum time constant and zero bias  $D_{it}$  for the fast traps  $(\tau_{it,2}, D_{it,2})$  are  $3.77 \times 10^{-7}$  s and  $4.1 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>. The trap response time of the fast traps shifts outside the measurement frequency range for  $V_G > 0$  V and hence cannot be further quantified. Similarly, the slow traps in the 200 nm AlN films exhibit a maximum time constant of  $6.2 \times 10^{-6}$  s and a  $D_{it}$  of  $1.27 \times 10^{13}$  cm $^{-2}$ eV $^{-1}$  at zero applied bias and fast traps have a minimum time constant of  $7.5\times10^{-7}s$  and a zero bias  $D_{it}$  of  $1.44\times10^{13}\,cm^{-2}eV^{-1}$ . We also see that the defect density as estimated from Terman's method earlier provides but a lower limit for  $D_{ij}$  as only the trap states capable of responding at the C-V measurement frequency of 1 MHz contribute to the stretch-out whereas the conductance method profiles the trap density both as a function of frequency and applied bias. These results represent the first actual characterization of trap states at the AlN/Si interface, which are expected to impact high-frequency device performance<sup>32</sup> and reliability of AlGaN/GaN HEMTs, and indicate that passivation schemes, either *in-situ* or *ex-situ*, need to be explored to reduce the trap densities at this interface.

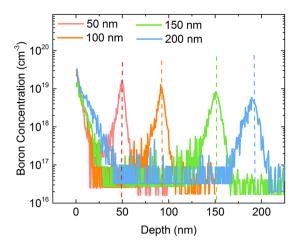

The Physical Origin of Increased Surface Acceptor Concentration. We now address the origin of increased acceptor densities at the surface of the Si substrate for thicker AlN films. Two possible reasons which have already been mentioned are auto-doping of Si substrate with Al-containing species either during growth or from the AlN film and dopant pile-up at AlN/Si interfaces from the acceptors in the p-Si substrate itself (boron, in this case). In case of GaN growth on AlN nucleation layers, the diffusion of Ga into Si is another factor that needs to be accounted for. Additionally, the presence of nitrogen, carbon, and oxygen (in trace amounts from reactants and in the Czochralski-grown Si substrates) which are invariably present during MOCVD growth of nitride films also get incorporated in Si when subject to the high growth temperatures. The AlN films thus grown are significantly strained in tension with growth stresses >1GPa<sup>19,25</sup> and an increase in AlN thickness hence increases the strain energy built up in these films. This increased strain energy could potentially create new defects at the interface which in turn can act as sinks for boron pile-up from the bulk silicon substrate, as has been observed in literature for ion-implantation induced damage in p-Si<sup>33-35</sup>. Also, the dislocation density in AlN nucleation layers is ~10<sup>13</sup> cm<sup>-2</sup>, which can act as diffusion pathways for the migration of Al or N species from the AlN film to the substrate<sup>36</sup>. In order to distinguish between these possible explanations of the increased surface acceptor densities, secondary ion mass spectroscopy (SIMS) was performed on the AlN/p-Si films. Figure 4 shows the depth profile of the concentration of boron atoms as measured from the top of the AlN/p-Si samples. We see that the concentration of boron, originating from the uniformly doped substrate, peaks at the AlN/Si interface and the magnitude of this peak reduces with increasing AlN thickness. This occurs due to boron diffusion into thicker AlN films due to their exposure to higher temperatures for longer durations needed to grow thicker films. Peak boron concentrations observed can reach almost  $10^{19}\,\mathrm{cm}^{-3}$  as compared to the starting substrate doping density of  $< 3 \times 10^{16} \, \rm cm^{-3}$ . The thinner AlN films have a slightly higher boron concentration near the Si surface, both in terms of peak boron concentrations and the integrated areal density of boron in Si. While thicker films are exposed to the higher growth temperature for longer times (300 seconds of additional exposure duration at 1050 °C for the 200 nm AlN sample compared to the 50 nm sample), prior reports on the activation of ion-implanted boron in crystalline Si indicates that such a time difference is insufficient to significantly impact the activation of boron atoms at this temperature<sup>37–40</sup>. Hence the presence of higher surface boron concentrations cannot be the reason for the higher surface acceptor concentration observed for thicker films. Furthermore, the fact that segregation of boron to the AlN/Si interface for thinner samples does not manifest in their capacitance

**Figure 4.** SIMS profile of boron concentration as a function of depth for the four different AlN film thicknesses. The dotted lines indicate AlN/p-Si interfaces. The peak concentrations and the integrated areal density of boron atoms in Si are higher for thinner films as diffusion into AlN itself increases with film thickness.

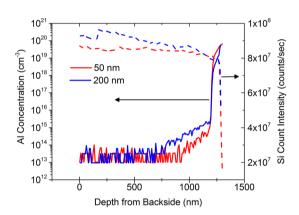

**Figure 5.** SIMS profile of aluminum concentration as a function of depth from the backside of 50 and 200 nm thick AlN/p-Si samples. The dotted lines indicate Si SIMS count intensity which shows the transition from Si to AlN. The peak concentrations and the integrated areal density of aluminum atoms in Si are slightly higher for the 50 nm films.

profiles indicates that they are electrically inactive due to their non-substitutional nature and the formation of clusters/complexes<sup>41</sup>.

Al diffusion into Si during the growth of AlN could be another reason for the increased acceptor concentration. Figure 5 show the SIMS profile for Al concentration for the 50 and 200 nm AlN films measured through the backside of the sample after thinning the silicon substrate. The observed concentration of Al is also  $>10^{18}\,\rm cm^{-3}$  and a higher tail concentration of Al can be seen into Si. However, no significant difference in the Al concentration between 50 and 200 nm films are observed in terms of peak and areal Al densities in Si which makes it unlikely that auto-doping of Si with Al-containing species is the reason for the observed capacitance effects, analogous to the case of the boron discussed above.

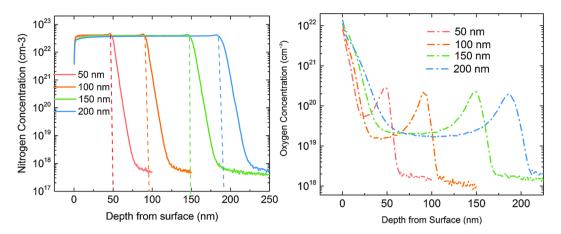

Given the similar concentrations of boron and Al in the thinner and thicker films, it is clear that the source of increased acceptor doping lies elsewhere. Figure 6 shows the SIMS profile of the other two pre-dominant atomic species during the growth of nitrides, viz; nitrogen and oxygen. Indeed, the observed peak nitrogen concentrations in Si for all the AlN films is at least an order of magnitude higher than any other dopant species, followed by the oxygen concentration in silicon.

Once again, we see that the peak concentrations and integrated areal densities of these species are comparable to each other for the four AlN thicknesses considered here. The behaviour of nitrogen complexes in silicon is quite involved with many nitrogen-interstitial and vacancy complexes predicted to be deep donors and acceptors  $^{42}$ . Experimentally, however, nitrogen is known to transition from being a donor in Si with <1% activation at low annealing temperatures to being electrically inactive for annealing temperatures  $>850\,^{\circ}\mathrm{C}^{43}$ , which should be the case for MOCVD grown AlN films ( $1050\,^{\circ}\mathrm{C}$  in our case, for instance). However, the simultaneous presence of high concentrations of oxygen and nitrogen atoms in the top surface of silicon indicates the possibility of forming Si-O-N complexes which can act as thermal acceptors  $^{44}$ . Thermal acceptor concentration has been reported in implanted Si samples to first increase with annealing times until it reaches a steady state concentration after a few

**Figure 6.** SIMS profile of nitrogen (left) and oxygen (right) concentration as a function of depth for four different AlN film thicknesses with peak concentrations occurring at the AlN/p-Si interface. Both the peak concentrations and integrated areal densities are comparable for all four film thicknesses.

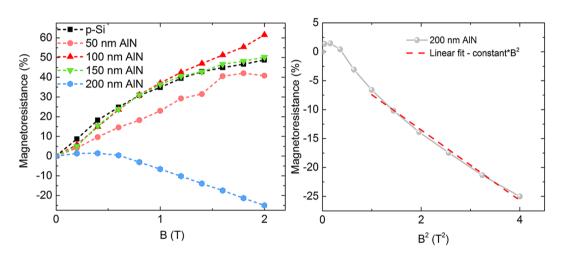

**Figure 7.** (left) Magnetoresistance of four different AlN film thicknesses on Si at 5 K as a function of applied magnetic field (B). Also shown for comparison is the MR of a bare p-Si sample having the same doping density as the substrates. (right) Negative MR of the 200 nm AlN sample as a function of square of applied magnetic field ( $B^2$ ). Dotted line indicates a linear fit to  $B^2$  for comparison.

hours of annealing at high temperatures. Even though the actual oxygen and nitrogen concentrations are not too different in the case of thinner and thicker AlN films, the difference in growth times (300 s in case of 200 nm vs 50 nm film) means that the thicker samples are exposed to higher temperatures for longer durations, thus increasing the concentration of thermal acceptor complex formation and correspond to the time scales reported by Yang et al. for increased thermal acceptor formation 44. We note that even a 0.02% activation of N-containing complexes thus formed is enough to account for the increased acceptor concentrations observed in the capacitance profiles. Such thermal acceptor formation is expected to be exacerbated during the growth of a complete GaN HEMT stack due to the higher growth times (typical growth rates ~1  $\mu$ m/hr), while the effects of Ga-diffusion from the stack into silicon would also need to be accounted for.

**Low-temperature Magnetoresistance Behavior with AIN Film Thickness.** The preceding discussion makes it clear that the pre-dominant thickness dependent parasitic channel effects observed at AIN/Si interfaces are due to thermal acceptor complexes formed in Si during film growth. However, the presence of an inversion layer of electrons close to the interface, which is swamped out by the effect of the increased acceptor concentration, is still a possibility. Such an inversion layer, if it exists, is expected to persist down to low temperatures while the acceptor contribution to the parasitic channel are expected to be frozen out. In order to investigate this possibility, samples were fabricated in van der Pauw Hall geometry using Indium contacts and were subjected to low temperature magnetoresistance measurements.

The magnetoresistance (MR =  $\Delta R_{xx}/R_{xx}$  in %) as a function of magnetic field (B) at 5 K for a reference p-Si sample of the same doping density and the four AlN samples under investigation are as shown in Fig. 7. We observe

that the standard p-Si with no AlN and p-Si deposited with AlN films of thicknesses 50, 100 and 150 nm exhibit large positive MR with applied magnetic fields, which has been attributed in literature to space-charge injection of carriers through the contacts<sup>45</sup>. In contrast, the 200 nm sample shows a high negative magnetoresistance (NMR) of 25% at 2 T. The magnetic field dependence due to weak localization in a 2D-confined carrier system is proportional to B<sup>2</sup> at low magnetic fields<sup>46</sup>, and such a dependence is also observed for the 200 nm samples as shown in Fig. 7. The transition from positive to negative NMR with increasing AlN thickness is further indicative of a transition from 3D to 2D carrier confinement for these samples and such an observation has also been reported for in-plane magneto-resistance changes in LAO/STO hetero-junctions, where the transition from a 3D to a 2D electron gas engenders a change from positive to negative MR due to the stronger localization effects with reduced dimensionality<sup>47</sup>. These features are suggestive of two-dimensional confinement at the AlN/Si interface in case of the 200 nm samples and they support the possibility of the formation of an inversion channel of electrons at the AlN/Si interface for the thicker samples, due to the polarization discontinuity at AlN/Si and contribution from surface donors as reported by Luong *et al.*<sup>12</sup>. Further investigation of magneto-transport at AlN/Si interfaces is necessary to conclusively demonstrate such confinement effects and offers an interesting topic for future studies.

In conclusion, thickness-dependent parasitic channel formation at AlN/Si interfaces is shown to be composed of both electron and hole contributions, from the polarization difference at AlN/Si and surface donors, and increased thermal acceptor formation due to Si-O-N complexes at Si surface respectively. At room temperatures, the effect of the surface acceptors completely dominates the characteristics of the interface and manifests in the thickness dependent change in capacitance of these samples. SIMS analysis reveals that thermal acceptor formation due to Si-O-N complexes is responsible for the increased surface acceptor densities for the thicker films, which also demonstrate higher interfacial trap densities as compared to thinner films. Low temperature magnetoresistance measurements at 5 K, well below the acceptor freeze-out temperature reveal a transition from positive to negative MR for thicker samples, with a B² dependence for NMR, indicative of two-dimensional confinement due to an inversion layer of electrons at the AlN/Si interface. The use of thinner AlN layers is expected to help suppress both effects, but its effect on the properties of the rest of the layers constituting the HEMT stack needs to be considered as well.

#### Methodo

MOCVD growth of AlN and device fabrication. AlN films were grown on p-Si substrates (1–10  $\Omega$ .cm, 2" prime wafers) using an AIX 200/4 RF-S MOCVD system with trimethyl aluminum and ammonia as precursors, after a HF pre-treatment<sup>19</sup>, with a growth rate of 25 nm/min and a V/III ratio of 434. 50, 100, 150 and 200 nm AlN films were grown and film thickness was monitored *in-situ* at the centre of the wafer to ensure accurate thicknesses. Ellipsometry of these four films post-growth indicated average film thickness to be 54 nm, 97 nm, 159 nm and 202 nm respectively with a 5% variation in thickness across the 2" wafer<sup>30</sup>. AlN/p-Si MOSCAP fabrication involved deposition of circular Al electrodes of 300 μm diameter using thermal evaporation of the top-side with a blanket Al metallization of the bottom forming the back electrode. The samples were then annealed in forming gas at 400 °C, 15 min for post-metallization annealing. For the magnetoresistance measurements, van der Pauw squares of ~1 cm were used with Indium contacts soldered onto the four corners at 400 °C.

**Electrical and SIMS characterization.** AlN/Si MOSCAPs were then characterized using an Agilent 4941 Impedance Analyzer for capacitance and conductance measurements over a frequency range of 1 kHz to 2 MHz with an a.c. excitation of 30 mV. A frequency dispersion of ~5% was observed from 1 kHz to 1 MHz with the dissipation factors less than 0.1. Magnetoresistance measurements were performed using a Lakeshore CRX-VF closed cycle He-cryostat at 5 K with a superconducting magnet of maximum field 2 T perpendicular to the sample plane. SIMS measurements, both front-side and back-side with substrate polished down to ~1  $\mu$ m, were performed at Evans Analytical Group Inc., USA.

#### References

- 1. Marcon, D., Saripalli, Y. N. & Decoutere, S. 200 mm GaN-on-Si Epitaxy and e-mode DeviceTechnology (Invited), *Electron Devices Meeting*, 2015 IEEE International (IEDM). Washington DC, USA, https://doi.org/10.1109/IEDM.2015.7409709 IEEE (2015 December 7–9).

- 2. Bhat, T. N. *et al.* Structural and optical properties of AlxGa1-xN/GaN high electron mobility transistor structures grown on 200 mm diameter Si(111) substrates. *Journal of Vacuum Science & Technology B* 32, 021206, https://doi.org/10.1116/1.4866429 (2014).

- 3. Krost, A. & Dadgar, A. GaN-Based Devices on Si. *Physica status solidi (a)* **194**, 361–375, https://doi.org/10.1002/1521-396x(200212)194:2<361::aid-pssa361>3.0.co;2-r (2002).

- 4. Van Hove, M. et al. CMOS process-compatible high-power low-leakage AlGaN/GaN MISHEMT on silicon. IEEE Electron Device Letters 33, 667–669 (2012).

- 5. Moens, P. et al. An industrial process for 650V rated GaN-on-Si power devices using in-situ SiN as a gate dielectric, Power Semiconductor Devices & IC's (ISPSD), 2014 IEEE 26th International Symposium on. Waikola, HI, USA, https://doi.org/10.1109/ISPSD.2014.6856054, IEEE (2014 June 15–19).

- 6. Medjdoub, F. et al. Low-noise microwave performance of AlN/GaN HEMTs grown on silicon substrate. IEEE Electron Device Letters 32, 1230–1232 (2011).

- 7. Medjdoub, F., Zegaoui, M. & Rolland, N. Beyond 100 ghz aln/gan hemts on silicon substrate. Electronics letters 47, 1345-1346 (2011).

- Lidow, A. GaN as a displacement technology for silicon in power management. Energy Conversion Congress and Exposition (ECCE), 2011 IEEE. Phoenix, AZ, USA, https://doi.org/10.1109/ECCE.2011.6063741, IEEE (2011 Sept 17–22).

Takenaka, I. et al. Low Distortion CATV Power Amplifier Using GaAs HJFET andGaN FET Cascode Distortion Cancellation

- Takenaka, I. et al. Low Distortion CATV Power Amplifier Using GaAs HJFET and GaN FET Cascode Distortion Cancellation Technique, Compound Semiconductor Integrated Circuit Symposium (CSICS), 2013 IEEE. Monterey, CA, USA, https://doi. org/10.1109/CSICS.2013.6659236, IEEE(2013 Oct 13–16).

- Brown, J. et al. Performance of AlGaN/GaN HFETs fabricated on 100 mm silicon substrates for wireless basestation applications. Microwave Symposium Digest, 2004 IEEE MTT-S International. Fort Worth, TX, USA, https://doi.org/10.1109/MWSYM.2004.1339095, IEEE (2004 June 6–11).

- 11. Hanson, A. W., Roberts, J. C., Piner, E. L. & Rajagopal, P. III-nitride material structures including silicon substrates, US Patent 7,247,889 (2007).

- 12. Luong, T. T. et al. RF loss mechanisms in GaN-based high-electron-mobility-transistor on silicon: Role of an inversion channel at the AlN/Si interface. *Physica status solidi (a)* (2017).

- 13. Umeda, H. et al. Blocking-voltage boosting technology for GaN transistors by widening depletion layer in Si substrates. Electron Devices Meeting (IEDM), 2010 IEEE International. San Francisco, CA, USA, https://doi.org/10.1109/IEDM.2010.5703400, IEEE (2010 Dec 6–8).

- 14. Yacoub, H. et al. The effect of the inversion channel at the AlN/Si interface on the vertical breakdown characteristics of GaN-based devices. Semiconductor Science and Technology 29, 115012 (2014).

- Tang, C., Sheng, K. & Xie, G. Buffer leakage induced pre-breakdown mechanism for AlGaN/GaN HEMTs on Si. Communications, Circuits and Systems (ICCCAS), 2013 International Conference on. Chengdu, China, https://doi.org/10.1109/ICCCAS.2013.6765355, IEEE (2013 Nov 15–17).

- Visalli, D. et al. Experimental and simulation study of breakdown voltage enhancement of AlGaN/GaN heterostructures by Si substrate removal. Applied Physics Letters 97, 113501, https://doi.org/10.1063/1.3488024 (2010).

- 17. Watanabe, A. et al. The growth of single crystalline GaN on a Si substrate using AIN as an intermediate layer. Journal of crystal growth 128, 391–396 (1993).

- Ishikawa, H. et al. Thermal stability of GaN on (1 1 1) Si substrate. Journal of Crystal Growth 189–190, 178–182, https://doi.org/10.1016/ S0022-0248(98)00223-1 (1998).

- 19. Chandrasekar, H. *et al.* An early *in-situ* stress signature of the AlN-Si pre-growth interface for successful integration of nitrides with (111) Si. *Applied Physics Letters* **103**, 211902, https://doi.org/10.1063/1.4831968 (2013).

- Mohan, N., Soman, R. & Raghavan, S. Integrating AlGaN/GaN high electron mobility transistor with Si: A comparative study of integration schemes. *Journal of Applied Physics* 118, 135302 (2015).

- 21. Ambacher, O. et al. Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N-and Gaface AlGaN/GaN heterostructures. *Journal of applied physics* 85, 3222–3233 (1999).

- Ibbetson, J. et al. Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors.

Applied Physics Letters 77, 250–252 (2000).

- 23. Bernardini, F. & Fiorentini, V. Spontaneous vs. piezoelectric polarization in III-V nitrides: conceptual aspects and practical consequences. *Physica status solidi* (b) **216**, 391–398, https://doi.org/10.1002/(SICI)1521-3951(199911)216:1<391::AID-PSSB391>3.0.CO;2-K (1999).

- 24. Liu, R., Ponce, F. A., Dadgar, A. & Krost, A. Atomic arrangement at the AlN/Si (111) interface. Applied Physics Letters 83, 860–862, https://doi.org/10.1063/1.1597749 (2003).

- Raghavan, S. & Redwing, J. M. In situ stress measurements during the MOCVD growth of AlN buffer layers on (111) Si substrates. Journal of crystal growth 261, 294–300 (2004).

- 26. Raghavan, S. & Redwing, J. M. Group III-A nitrides on Si: stress and microstructural evolution. (Boca Raton, FL: CRC Press, 2011).

- Krost, A., Dadgar, A., Strassburger, G. & Clos, R. GaN-based epitaxy on silicon: stress measurements. Physica status solidi (a) 200, 26–35 (2003).

- 28. Sze, S. M. & Ng, K. K. Physics of semiconductor devices. (John wiley & sons, 2006).

- Chandrasekar, H., Singh, M., Raghavan, S. & Bhat, N. Estimation of background carrier concentration in fully depleted GaN films. Semiconductor Science and Technology 30, 115018, https://doi.org/10.1088/0268-1242/30/11/115018 (2015).

- Chandrasekar, H. et al. Spotting 2D atomic layers on aluminum nitride thin films. Nanotechnology 26, 425202, https://doi. org/10.1088/0957-4484/26/42/425202 (2015).

- 31. Schroder, D. K. Semiconductor material and device characterization. (John Wiley & Sons, 2006).

- 32. Neve, C. R. et al. Effect of temperature on advanced Si-based substrates performance for RF passive integration. *Microelectronic Engineering* 120, 205–209 (2014).

- 33. Duffy, R. et al. Boron uphill diffusion during ultrashallow junction formation. Applied Physics Letters 82, 3647–3649, https://doi.org/10.1063/1.1578512 (2003).

- 34. Jung, M. Y. L., Gunawan, R., Braatz, R. D. & Seebauer, E. G. Effect of near-surface band bending on dopant profiles in ion-implanted silicon. *Journal of Applied Physics* 95, 1134–1140, https://doi.org/10.1063/1.1638621 (2004).

- 35. Rafferty, C. S. et al. Explanation of reverse short channel effect by defect gradients. Electron Devices Meeting, 1993. IEDM '93. Technical Digest., International Washington DC, USA https://doi.org/10.1109/IEDM.1993.347345, IEEE (1993 Dec 5–8).

- 36. Kuball, M., Ťapajna, M., Simms, R. J. T., Faqir, M. & Mishra, U. K. AlGaN/GaN HEMT device reliability and degradation evolution: Importance of diffusion processes. *Microelectronics Reliability* 51, 195–200, https://doi.org/10.1016/j.microrel.2010.08.014 (2011).

- 37. Höfler, A. *et al.* A technology oriented model for transient diffusion and activation of boron in silicon. *Journal of applied physics* **78**, 3671–3679 (1995).

- 38. Aboy, M. et al. Atomistic analysis of the evolution of boron activation during annealing in crystalline and preamorphized silicon. *Journal of Applied Physics* **97**, 103520, https://doi.org/10.1063/1.1904159 (2005).

- 39. Seidel, T. & Mac Rae, A. The isothermal annealing of boron implanted silicon. Radiation Effects 7, 1-6 (1971).

- 40. Cohen, S., Norton, J., Koch, E. & Weisel, G. Shallow boron-doped junctions in silicon. Journal of applied physics 57, 1200-1213 (1985).

- 41. Hofker, W. K., Werner, H. W., Oosthoek, D. P. & Koeman, N. J. Boron implantations in silicon: A comparison of charge carrier and boron concentration profiles. *Applied physics* 4, 125–133, https://doi.org/10.1007/bf00884267 (1974).

- 42. Goss, J., Hahn, I., Jones, R., Briddon, P. & Öberg, S. Vibrational modes and electronic properties of nitrogen defects in silicon. *Physical Review B* 67, 045206 (2003).

- 43. Mitchell, J. B., Shewchun, J., Thompson, D. A. & Davies, J. A. Nitrogen—implanted silicon. II. *Electrical properties. Journal of Applied Physics* 46, 335–343, https://doi.org/10.1063/1.321340 (1975).

- 44. Yang, D., Lu, J., Li, L., Yao, H. & Que, D. Thermal acceptor formation in nitrogen-doped silicon. *Applied Physics Letters* 59, 1227–1229, https://doi.org/10.1063/1.105511 (1991).

- 45. Delmo, M. P., Yamamoto, S., Kasai, S., Ono, T. & Kobayashi, K. Large positive magnetoresistive effect in silicon induced by the space-charge effect. *Nature* 457, 1112–1115 (2009).

- 46. Arapov, Y. G., Harus, G. I., Neverov, V. N., Shelushinina, N. G. & Kuznetsov, O. A. Parabolic negative magnetoresistance in p-Ge/Ge1-xSix heterostructures. Semiconductors 33, 978–980, https://doi.org/10.1134/1.1187817 (1999).

- 47. Wang, X. et al. Magnetoresistance of two-dimensional and three-dimensional electron gas in LaAlO 3/SrTiO 3 heterostructures: Influence of magnetic ordering, interface scattering, and dimensionality. Physical Review B 84, 075312 (2011).

#### Acknowledgements

We acknowledge the Ministry of Defence, Government of India through sanction number TD-2008/SPL-147 and the Minsitry of Electronics and IT Government of India thorugh Centre of Excellence in Nanoelectronics project for funding to carry out this research, the National Nano Fabrication Centre (NNFC) and the Micro and Nano Characterization Facility (MNCF) of the Centre for Nano Science and Engineering, Indian Institute of Science for providing access to the fabrication and characterization facilities. H.C. wishes to thank Prof. V Venkataraman, Department of Physics, IISc, Bangalore for helpful discussions.

#### **Author Contributions**

N.B., H.C. and S.R. conceived the experiments. H.C. performed the MOCVD growth, device fabrication and characterization, and wrote the paper. N.B. and K.N.B. supervised the electrical characterization and analysis, and R.M. the magnetoresistance measurements. All authors discussed and analyzed the results and interpretation and reviewed the paper.

#### **Additional Information**

**Competing Interests:** The authors declare that they have no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2017