Ong, Jia Jan (2016) Hardware realization of discrete wavelet transform cauchy Reed Solomon minimal instruction set computer architecture for wireless visual sensor networks. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/32583/1/%5BONG%20JIA%20JAN%5D%20HARDWARE %20REALIZATION%200F%20DISCRETE%20WAVELET%20TRANSFORM%20CAUCHY %20REED%20SOLOMON%20MINIMAL%20INSTRUCTION%20SET%20COMPUTER %20ARCHITECTURE%20FOR%20WIRELESS%20VISUAL%20SENSOR %20NETWORKS.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

# HARDWARE REALIZATION OF DISCRETE WAVELET TRANSFORM CAUCHY REED SOLOMON MINIMAL INSTRUCTION SET COMPUTER ARCHITECTURE FOR WIRELESS VISUAL SENSOR NETWORKS

ONG JIA JAN, MEng (Hons.)

# THESIS SUBMITTED TO THE UNIVERSITY OF NOTTINGHAM FOR THE DEGREE OF DOCTOR OF PHILOSOPHY JULY 2016

#### ABSTRACT

Large amount of image data transmitting across the Wireless Visual Sensor Networks (WVSNs) increases the data transmission rate thus increases the power transmission. This would inevitably decreases the operating lifespan of the sensor nodes and affecting the overall operation of WVSNs. Limiting power consumption to prolong battery lifespan is one of the most important goals in WVSNs. To achieve this goal, this thesis presents a novel low complexity Discrete Wavelet Transform (DWT) Cauchy Reed Solomon (CRS) Minimal Instruction Set Computer (MISC) architecture that performs data compression and data encoding (encryption) in a single architecture. There are four different programme instructions were developed to programme the MISC processor, which are Subtract and Branch if Negative (SBN), Galois Field Multiplier (GF MULT), XOR and 11TO8 instructions. With the use of these programme instructions, the developed DWT CRS MISC were programmed to perform DWT image compression to reduce the image size and then encode the DWT coefficients with CRS code to ensure data security and reliability. Both compression and CRS encoding were performed by a single architecture rather than in two separate modules which require a lot of hardware resources (logic slices). By reducing the number of logic slices, the power consumption can be subsequently reduced. Results show that the proposed new DWT CRS MISC architecture implementation requires 142 Slices (Xilinx Virtex-II), 129 slices (Xilinx Spartan-3E), 144 Slices (Xilinx Spartan-3L) and 66 Slices (Xilinx Spartan-6). The developed DWT CRS MISC architecture has lower hardware complexity as compared to other existing systems, such as Crypto-Processor in Xilinx Spartan-6 (4828 Slices), Low-Density Parity-Check in Xilinx Virtex-II (870 slices) and ECBC in Xilinx Spartan-3E (1691 Slices). With the use of RC10 development board, the developed DWT CRS MISC architecture can be implemented onto the Xilinx Spartan-3L FPGA to simulate an actual visual sensor node. This is to verify the feasibility of developing a joint compression, encryption and error correction processing framework in WVSNs.

## LIST OF ASSOCIATED PUBLICATIONS

### **Published Papers**

#### Journal:

Jia Jan Ong, L.-M. Ang, and K.P. Seng, "Selective Secure Error Correction on SPIHT Coefficients for Pervasive Wireless Visual Network," International Journal of Ad Hoc and Ubiquitous Computing, vol. 13, pp. 73-82, 2013.

#### **Book Chapter:**

Jia Jan Ong, L.-M. Ang and K. P. Seng, "Lifting Scheme DWT Implementation in a Wireless Vision Sensor Network", Visual Informatics: Bridging Research and Practice, Lecture Notes in Computer Science, Vol. 5857/2009, pp. 627-635, 2009.

Jia Hao Kong, Jia Jan Ong, L.-M. Ang, and K. P. Seng, "Low Complexity Processor Designs for Energy-Efficient Security and Error Correction in Wireless Sensor Networks", Wireless Sensor Networks and Energy Efficiency: Protocols, Routing and Management, pp. 350-368, January 2012.

#### Conference Paper:

Jia Jan Ong, Jia Hao Kong, L.-M. Ang, and K. P. Seng, "Implementation of the One Instruction Set Computer (OISC) on FPGA using Handel-C", The International Conference on Embedded Systems and Intelligent Technology ICESIT 2010 Proceedings, February 2010.

Jia Jan Ong, L.-M. Ang, and K. P. Seng, "Implementation of (255,223) Reed Solomon Minimal Instruction Set Computing using Handel-C," 3rd IEEE International Conference on Computer Science and Information Technology (ICSIT) 2010, Vol. 5, pp. 49-54, July 2010.

Jia Jan Ong, L.-M. Ang, and K.P. Seng, "Implementation of (15, 9) Reed Solomon Minimal Instruction Set Computing on FPGA using Handel-C," 2010 International Conference on Computer Applications and Industrial Electronics (ICCAIE), pp. 356-361, December 2010.

Jia Jan Ong, L.-M. Ang, K.P. Seng, and Fong Tien Ong , "Implementation of (255, 251) Reed Solomon Minimal Instruction Set Computing using Handel-C," 2011 International Conference on Information Networking (ICOIN), pp. 429-434, January 2011

Jia Jan Ong, L. -M. Ang, and K.P Seng, "FPGA Implementation Reed Solomon Encoder for Visual Sensor Networks," the 2011 International Conference on Telecom Technology and Applications (ICTTA 2011), Proc. of CSIT, Vol 5, pp. 88-92, 2011

Jia Jan Ong, L.-M Ang, K.P.Seng, and Ong Fong Tien, "Implementation of Selective Error Protection on SPHIT coefficients for wireless visual network", Proceedings of the 3rd International Conference on Software Technology and Engineering, pp. 383-388, 2011.

## ACKNOWLEDGEMENT

First and foremost, I would express my greatest gratitude to my supervisor Dr. Kenneth Ang Li-Minn for his guidance in my PhD studies. His creative thoughts and wide knowledge in the relevant field have greatly motivated me to put my best effort in completing this study. Nevertheless, his never ceasing patience in giving guidance for this study has gained my utmost respects.

At the same time, I would like to thank my interim supervisor Dr. Wong Yee Wan who has given me guidance, encouragement and support during difficulties time. I would like to thank my co-supervisor Prof. Dr. Jasmine Seng Kah Phooi, my family members and peers for their strong moral support, giving me the courage and strength during the duration of research. They have encouraged me to continue working on the problems when I encountered obstacles. With these efforts and words of encouragement, I strived to continue on the research work even when I meet with difficulties. Once again I would like to express my sincere appreciation for those who have directly and indirectly contributed to this piece of writing and research.

# **TABLE OF CONTENT**

| ABST   | RACT    |                                                                 | Ι    |

|--------|---------|-----------------------------------------------------------------|------|

| LIST ( | OF ASSO | OCIATED PUBLICATIONS                                            | II   |

| ACKN   | OWLE    | DGEMENT                                                         | IV   |

| TABL   | E OF CO | ONTENT                                                          | v    |

| LIST ( | OF FIGU | JRES                                                            | x    |

| LIST ( | OF TAB  | LES                                                             | XIII |

| LIST ( | OF ACR  | ONYMS                                                           | XIV  |

| 1.0 IN | TRODU   | UCTION                                                          | 1    |

| 1.1    | PROB    | BLEM STATEMENT                                                  | 2    |

| 1.2    | SYST    | EM OVERVIEW                                                     | 4    |

| 1.3    | RESE    | ARCH AIM AND OBJECTIVES                                         | 5    |

| 1.4    | SIGN    | IFICANCE OF RESEARCH                                            | 6    |

| 1.5    | THES    | IS ORGANISATION                                                 | 8    |

| 2.0 LI | TERAT   | URE REVIEW                                                      | 10   |

| 2.1    | DISC    | RETE WAVELET TRANSFORM                                          | 10   |

|        | 2.1.1   | Recent DWT and CWT Research Works                               | 11   |

|        | 2.1.2   | DWT and CWT Comparison                                          | 14   |

| 2.2    | REDU    | JCED INSTRUCTION SET COMPUTER                                   | 17   |

|        | 2.2.1   | Ultimate Reduced Instruction Set Computer                       | 17   |

|        | 2.2.2   | Summary                                                         | 19   |

| 2.3    | WIRE    | CLESS VISUAL SENSOR NETWORK                                     | 20   |

|        | 2.3.1   | Existing WVSN Platforms                                         | 21   |

|        | 2.3.2   | Summary                                                         | 23   |

| 2.4    | COM     | PRESSION IN WSN                                                 | 24   |

|        | 2.4.1   | S-LZW Compression for Energy-Constrained WSNs                   | 24   |

|        | 2.4.2   | Lapped Biorthognal Transform for WSNs                           | 24   |

|        | 2.4.3   | SPHIT MIPS Processor for WVSNs                                  | 25   |

|        | 2.4.4   | JPEG FPGA-Based Wireless Vision Sensor Node                     | 27   |

|        | 2.4.5   | Low Power Wavelet Transform for WSNs                            | 27   |

|        | 2.4.6   | DWT Selective Retransmission for Wireless Image Sensor Networks | 27   |

|        | 2.4.7   | CL-DCT for Wireless Camera Sensor Networks                      | 28   |

|     |     | 2.4.8  | Summary                                                              | 28 |

|-----|-----|--------|----------------------------------------------------------------------|----|

|     | 2.5 | FORW   | ARD ERROR CORRECTION IN WSN                                          | 29 |

|     |     | 2.5.1  | Old-Weight-Column Code in Wireless Sensor Network                    | 31 |

|     |     | 2.5.2  | Reed Solomon Code in WSNs                                            | 32 |

|     |     | 2.5.3  | Turbo Codes in WSNs                                                  | 35 |

|     |     | 2.5.4  | Cauchy Reed Solomon in WSNs                                          | 37 |

|     |     | 2.5.5  | Hybrid ARQ/FEC Error Control in WSNs                                 | 37 |

|     |     | 2.5.6  | Hamming Code in WSNs                                                 | 38 |

|     |     | 2.5.7  | Error Concealment for Robust Image Transmission over WSNs            | 39 |

|     |     | 2.5.8  | LDPC Coding in WSNs                                                  | 39 |

|     |     | 2.5.9  | Summary                                                              | 40 |

|     | 2.6 | ENCR   | YPTION IN WSN                                                        | 41 |

|     |     | 2.6.1  | SPINS: Security Protocols for Sensor Networks                        | 41 |

|     |     | 2.6.2  | TinySec Security Architecture for WSNs                               | 42 |

|     |     | 2.6.3  | Advanced Encryption Standard for WSNs                                | 42 |

|     |     | 2.6.4  | HIGHT Block Cipher for Low-Resource Device                           | 43 |

|     |     | 2.6.5  | MiniSec Architecture for Secure WSNs                                 | 44 |

|     |     | 2.6.6  | TinyECC: Elliptic Curve Cryptography in WSNs                         | 44 |

|     |     | 2.6.7  | CURUPIRA Block Cipher for WSNs                                       | 45 |

|     |     | 2.6.8  | Broadcast Encryption Scheme in WSNs                                  | 46 |

|     |     | 2.6.9  | Authenticated-Encryption Schemes in WSNs                             | 46 |

|     |     | 2.6.10 | Crypto-Processor Encryption Algorithms for WSNs                      | 46 |

|     |     | 2.6.11 | Summary                                                              | 47 |

|     | 2.7 | JOINT  | SCHEMES                                                              | 48 |

|     |     | 2.7.1  | Joint Source Channel Coding and Power Control for WSNs               | 48 |

|     |     | 2.7.2  | Video Compression BCH Code in Wireless Video-Surveillance Networks   | 48 |

|     |     | 2.7.3  | SAC and Multiple-Input Turbo Code for WSNs                           | 49 |

|     |     | 2.7.4  | Robust Encryption for Secure Image Transmission in Wireless Channels | 49 |

|     |     | 2.7.5  | FPGA Image Compression Encryption Scheme                             | 50 |

|     |     | 2.7.6  | Error-Correcting Cipher for Wireless Networks                        | 50 |

|     |     | 2.7.7  | MVMP Secure and Reliable Data Transmission in WSNs                   | 50 |

|     |     | 2.7.8  | ContikiSec in WSN                                                    | 51 |

|     |     | 2.7.9  | Joint AES-LDPCC-CPFSK Schemes in WSN                                 | 51 |

|     |     | 2.7.10 | Secure and Reliable Distributed Data Storage in Unattended WSNs      | 52 |

|     |     | 2.7.11 | Reliable and Secure Distributed In-Network Data Storage in WSNs      | 52 |

|     |     | 2.7.12 | Error Correction-Based Cipher in WSN                                 | 53 |

|     |     | 2.7.13 | Multipath Routing Approach for Secure and Reliable Data in WSNs      | 54 |

|     |     | 2.7.14 | Compressed Sensing System for WSNs with Reliability                  | 54 |

|     |     | 2.7.15 | Summary                                                              | 55 |

| 3.0 | DEV | VELOP  | PED DWT CRS MISC                                                     | 56 |

|     | 3.1 | GALO   | IS FIELD                                                             | 56 |

|     |     | 3.1.1  | Galois Field GF(2)                                                   | 57 |

|     |     | 3.1.2  | Extension Galois Field GF(2 <sup>8</sup> )                           | 57 |

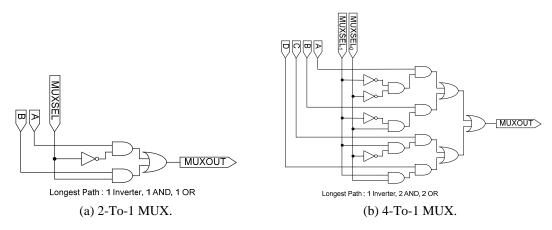

|     | 3.2 | PROP   | OSED DWT CRS MISC ARCHITECTURE                                       | 59 |

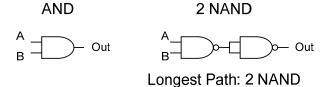

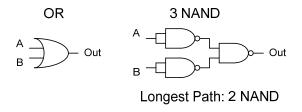

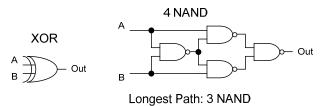

|     |     | 3.2.1  | NAND Gate Representations                                            | 61 |

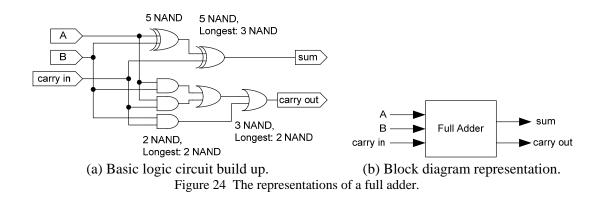

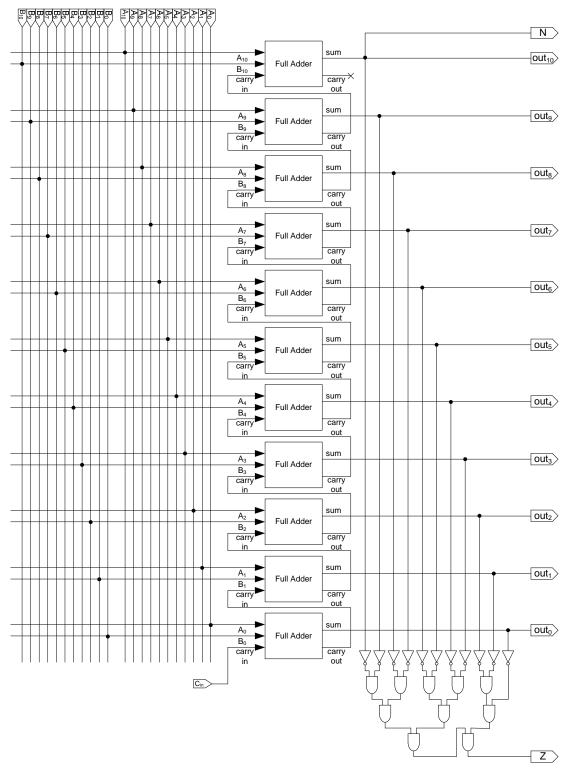

|     |     | 3.2.2  | ADDER Block                                                          | 62 |

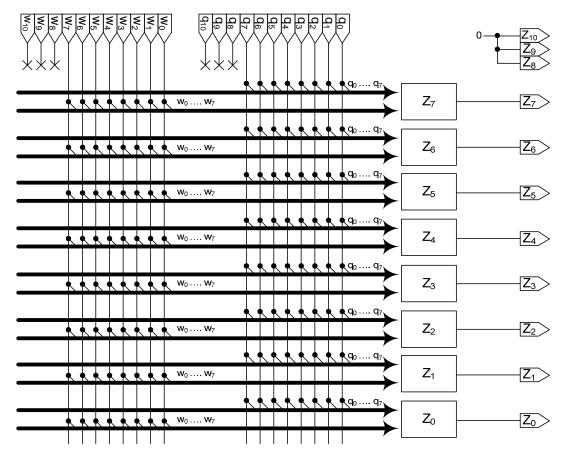

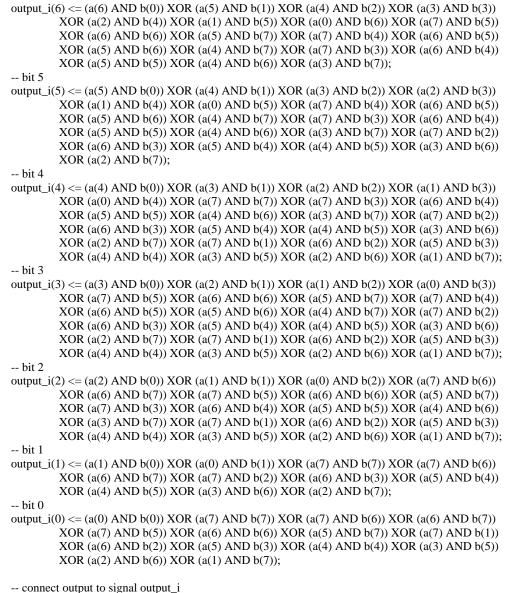

|     |     | 3.2.3  | GF(2 <sup>8</sup> ) MULT Block                                       | 65 |

|     |     |        |                                                                      | vi |

|     |     | 3.2.4 | XOR Block                                                   | 73  |

|-----|-----|-------|-------------------------------------------------------------|-----|

|     |     | 3.2.5 | 11TO8 Block                                                 | 74  |

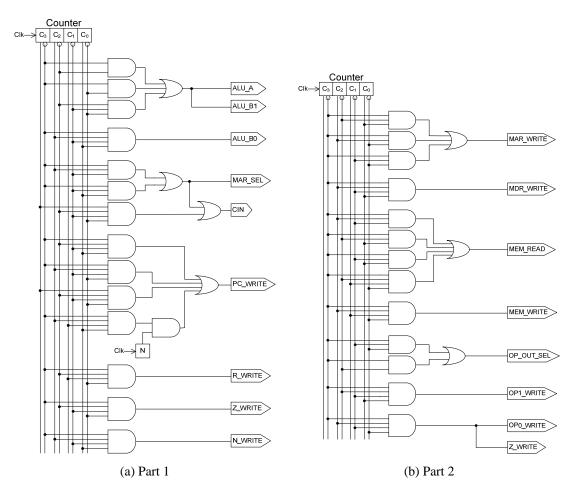

|     | 3.3 | DWT   | CRS MISC CONTROL SIGNALS                                    | 75  |

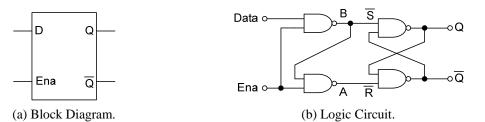

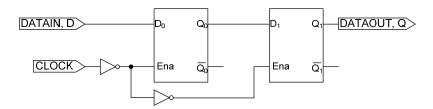

|     |     | 3.3.1 | D-Latch                                                     | 78  |

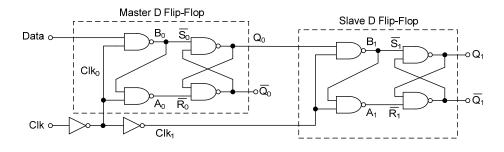

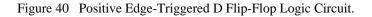

|     |     | 3.3.2 | Edge-Triggered D Flip-Flop                                  | 78  |

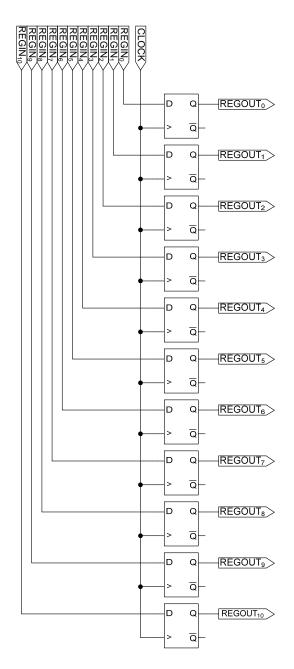

|     |     | 3.3.3 | Registers                                                   | 80  |

|     |     | 3.3.4 | 4-Bit Counter for Control Signals                           | 81  |

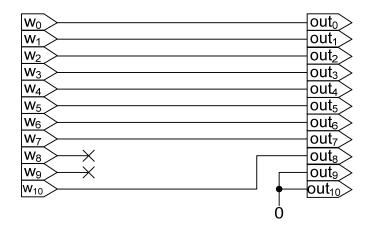

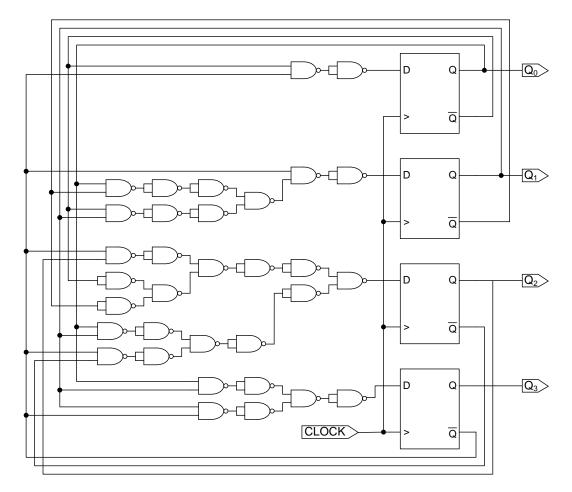

|     |     | 3.3.5 | Multiplexer and De-Multiplexer                              | 82  |

|     |     | 3.3.6 | Estimated Longest Logic Gates Delays                        | 87  |

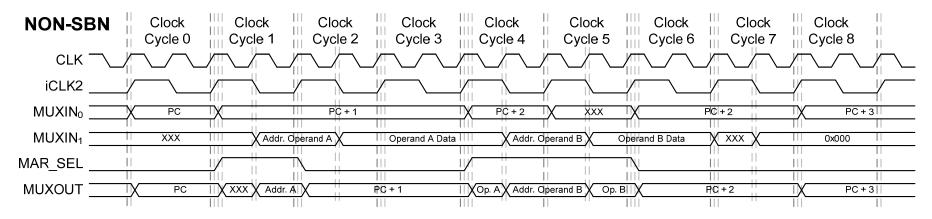

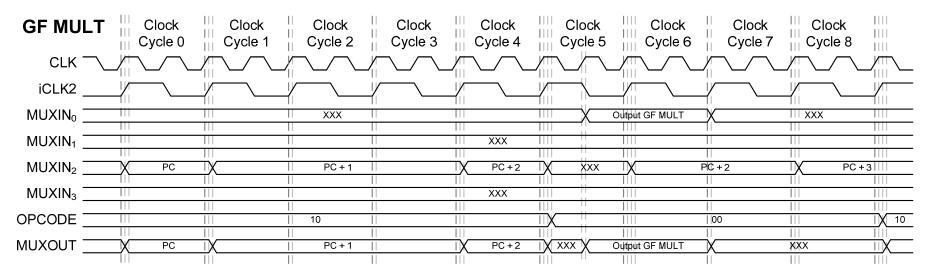

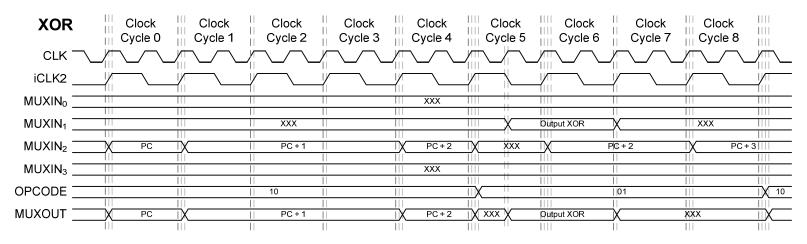

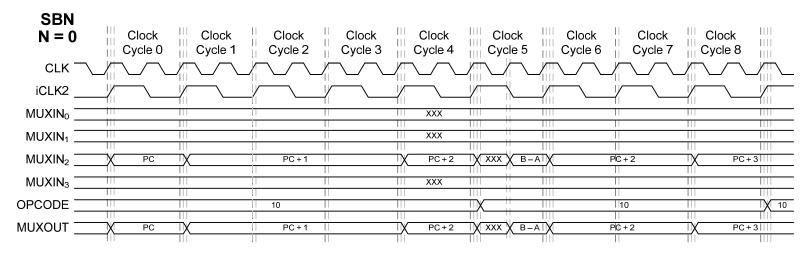

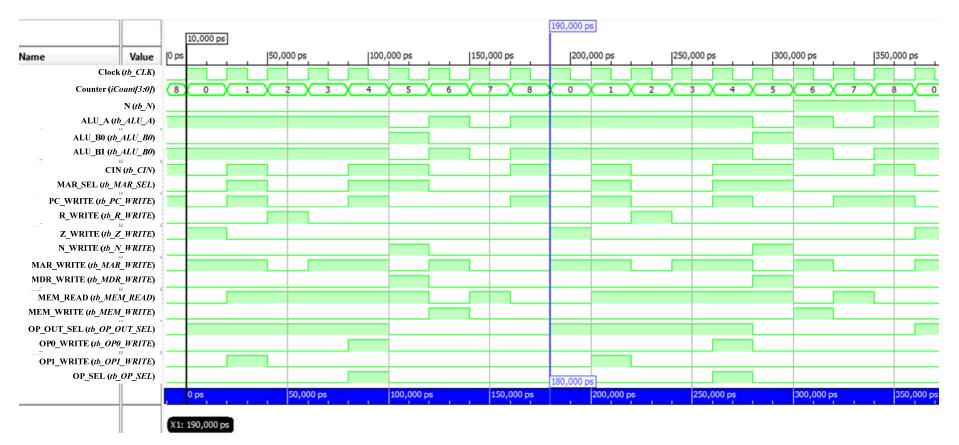

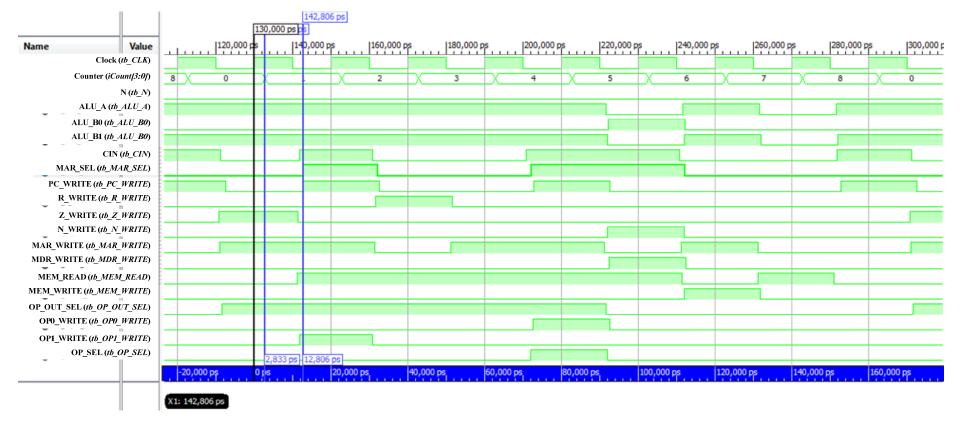

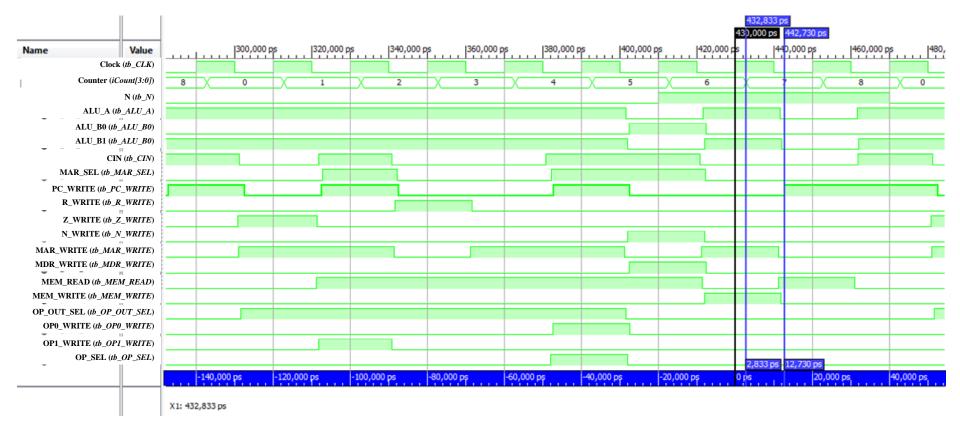

|     |     | 3.3.7 | Control Signals Timing Waveforms                            | 88  |

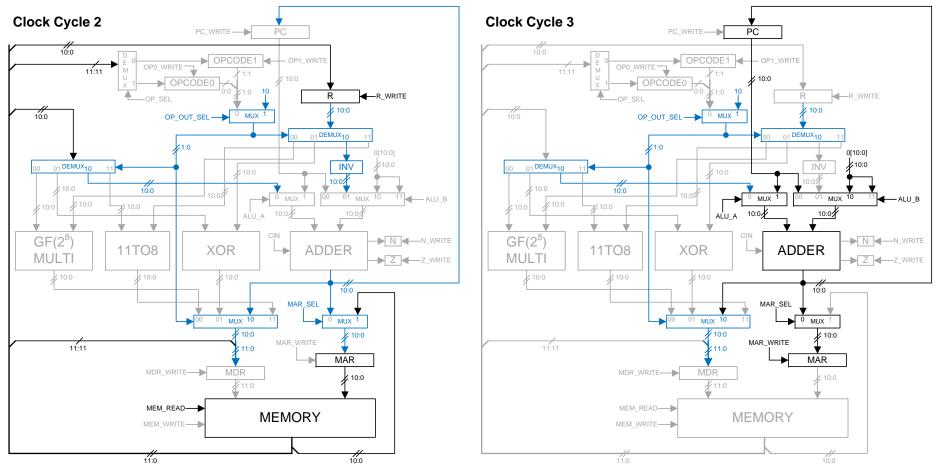

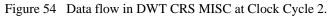

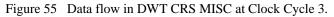

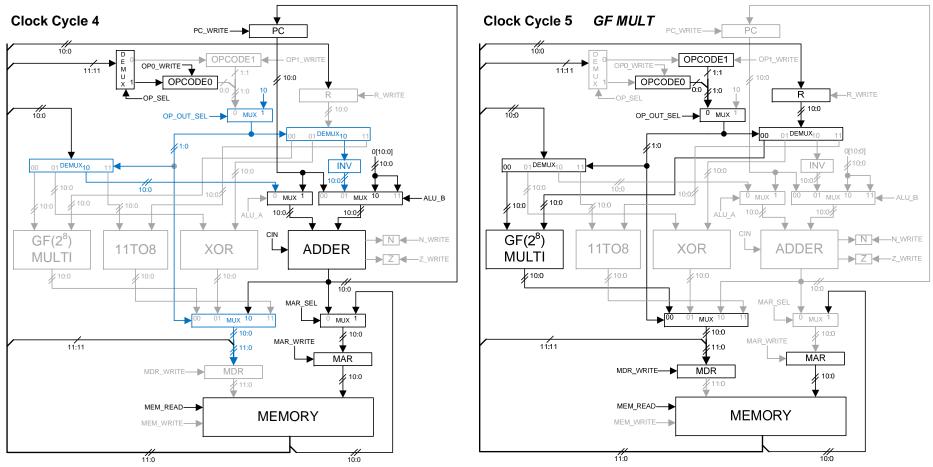

|     |     | 3.3.8 | Data Flow in DWT CRS MISC Architecture                      | 89  |

|     |     | 3.3.9 | Timing Diagram                                              | 99  |

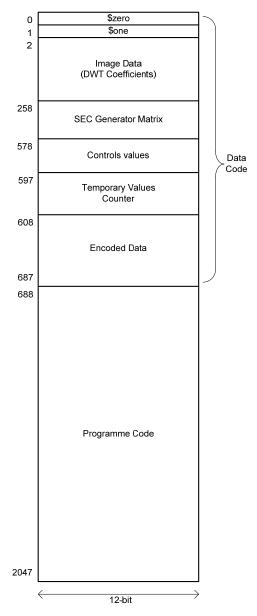

|     | 3.4 | DWT   | CRS MISC MEMORY                                             | 122 |

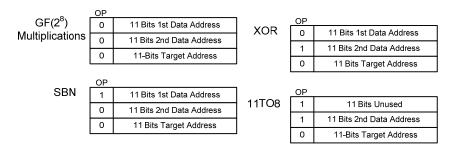

|     | 3.5 | PROG  | GRAMME INSTRUCTIONS FORMAT                                  | 123 |

|     | 3.6 | DWT   | CRS ALGORITHM                                               | 127 |

|     |     | 3.6.1 | Lifting Scheme Discrete Wavelet Transform                   | 127 |

|     |     | 3.6.2 | DWT Image Compression Algorithm                             | 128 |

|     |     | 3.6.3 | Cauchy Reed Solomon Coding Scheme                           | 135 |

|     |     | 3.6.4 | CRS Encoding Algorithm                                      | 139 |

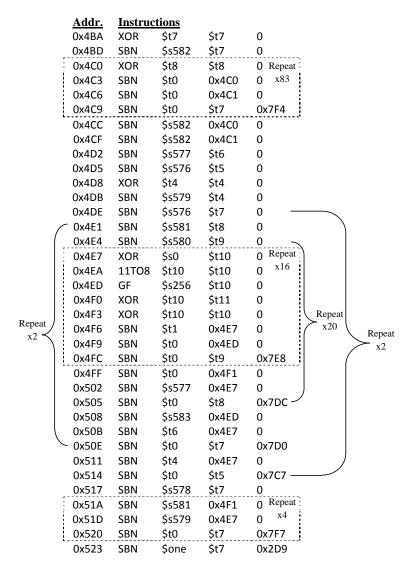

|     | 3.7 | PROG  | GRAMME INSTRUCTIONS/CLOCK CYCLES                            | 141 |

|     |     | 3.7.1 | Level 1 Lifting Scheme DWT Programme                        | 141 |

|     |     | 3.7.2 | Level 2 Lifting Scheme DWT Programme                        | 145 |

|     |     | 3.7.3 | Cauchy Reed Solomon Encoding Programme                      | 148 |

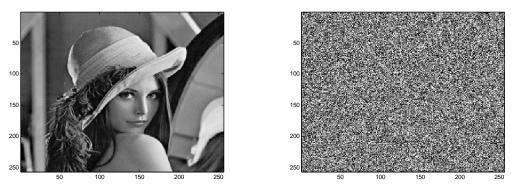

|     |     | 3.7.4 | Clock Cycles of Complete DWT CRS MISC Programme             | 150 |

|     | 3.8 | SUMN  | MARY                                                        | 151 |

| 4.0 | RES | SULTS | AND DISCUSSIONS                                             | 153 |

|     | 4.1 | CONT  | FROL SIGNALS WAVEFORMS                                      | 153 |

|     |     | 4.1.1 | Control Signals: Behavioral Simulation Waveforms            | 154 |

|     |     | 4.1.2 | Control Signals: Post and Route Simulation Waveforms        | 154 |

|     | 4.2 | PROG  | GRAMME INSTRUCTIONS WAVEFORMS                               | 161 |

|     |     | 4.2.1 | Programme Instructions: Behavioral Simulation Waveforms     | 161 |

|     |     | 4.2.2 | Programme Instructions: Post and Route Simulation Waveforms | 168 |

|     | 4.3 | DWT   | CRS MISC HARDWARE UTILISATION                               | 176 |

|     |     | 4.3.1 | DWT CRS MISC in FPGA                                        | 176 |

|     |     | 4.3.2 | DWT CRS MISC: Further Improvements                          | 179 |

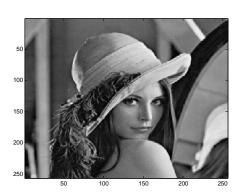

|     | 4.4 | DWT   | RECONSTRUCTED IMAGE QUALITY                                 | 181 |

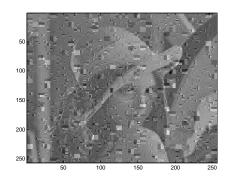

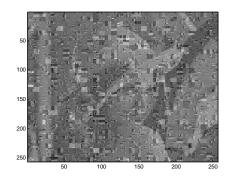

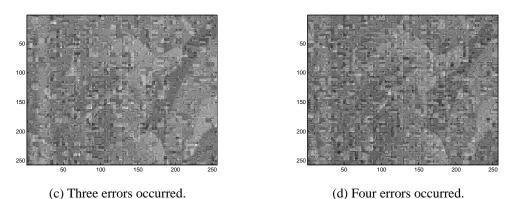

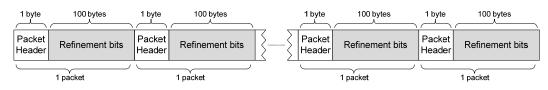

|     | 4.5 | ERRC  | ORS ON DWT COEFFICIENTS                                     | 183 |

|     | 4.6 | CRS ( | CODING SCHEME CONFIGURATION                                 | 185 |

|     | 4.7 | SUMN  | MARY                                                        | 188 |

vii

| 5.0 | HA  | RDWAR    | E IMPLEMENTATIONS                                                             | 189        |

|-----|-----|----------|-------------------------------------------------------------------------------|------------|

|     | 5.1 | SELECT   | TIVE SEC ON SPIHT COEFFICIENTS FOR WVSN                                       | 190        |

|     |     | 5.1.1 \$ | System Overview: Selective SEC on SPIHT Coefficients                          | 190        |

|     |     | 5.1.2 \$ | SPHIT Reconstructed Image Quality                                             | 192        |

|     |     | 5.1.3 I  | Hardware Utilisations: Selective SEC on SPIHT Coefficients                    | 195        |

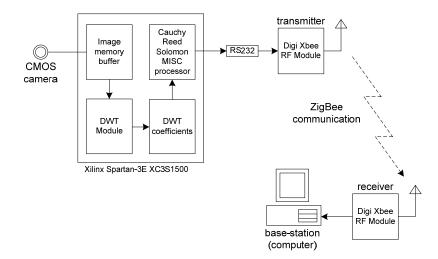

|     | 5.2 | LIFTIN   | G SCHEME DWT FILTER CRS MISC FOR WVSN                                         | 196        |

|     |     | 5.2.1 \$ | System Overview: Lifting Scheme DWT Filter CRS MISC                           | 197        |

|     |     | 5.2.2 I  | Hardware Utilisations: Lifting Scheme DWT Filter CRS MISC                     | 198        |

|     | 5.3 | DWT CF   | RS MISC FOR WVSN                                                              | 200        |

|     |     | 5.3.1    | System Overview: DWT CRS MISC                                                 | 201        |

|     |     | 5.3.2    | Hardware Utilisations: DWT CRS MISC                                           | 202        |

|     | 5.4 | SUMMA    | RY                                                                            | 206        |

| 6.0 | CO  | NCLUSI   | ONS AND FUTURE WORKS                                                          | 208        |

|     | (1  |          |                                                                               | 200        |

|     | 6.1 | FUIURI   | E WORKS                                                                       | 209        |

| RE  | FER | ENCES    |                                                                               | 211        |

| A.  | APF | PENDICH  | ES                                                                            | 219        |

|     | A.1 | DWT CF   | RS MISC ARCHITECTURE IN VHDL                                                  | 219        |

|     |     | A.1.1 (  | Control Signals Combinational Circuit Testbench - tb_Control.vhd              | 219        |

|     |     | A.1.2 (  | Control Signals Combinational Circuit - controls.vhd                          | 221        |

|     |     | A.1.3 I  | DWT CRS MISC Architecture Testbench - tb_DWTCRSMISC.vhd                       | 222        |

|     |     |          | Top Level DWT CRS MISC Architecture - DWTCRSMISC.vhd                          | 227        |

|     |     |          | 11-Bit Programme Counter Register - REGPC.vhd                                 | 237        |

|     |     |          | 11-Bit Register - REG.vhd                                                     | 237        |

|     |     |          | 1-Bit Register - REG1BIT.vhd                                                  | 238        |

|     |     |          | 2-Bit 2-To-1 Multiplexer - MUX22.vhd                                          | 239        |

|     |     |          | 1-Bit 1-To-2 Multiplexer - MUX11.vhd                                          | 240        |

|     |     |          | 11-Bit 1-To-4 Multiplexer - MUX114.vhd                                        | 240        |

|     |     |          | 11-Bit 4-To-1 Multiplexer - MUX411.vhd<br>Functional Block 11TO8 - C11TO8.vhd | 241<br>242 |

|     |     |          | Functional Block GF(28) Multiplier - GF28.vhd                                 | 242        |

|     |     |          | Functional Block 11-Bit XOR - GF211Add.vhd                                    | 242        |

|     |     |          | Functional Block SBN - SBN.vhd                                                | 244        |

|     |     |          | 11-Bit 2-To-1 Multiplexer - MUX211.vhd                                        | 245        |

|     |     |          | 12-Bit Register - REG12BIT.vhd                                                | 246        |

|     |     | A.1.18 I | LED 7-Segment Display - D4to7.vhd                                             | 246        |

|     | A.2 | DWT CF   | RS MISC PROCESSING SYSTEM IN HANDEL-C                                         | 247        |

|     | A.3 |          | SC ARCHITECTURE IN VHDL                                                       | 260        |

|     |     |          | Top Level CRS MISC Architecture - CRSMISC.vhd                                 | 260        |

|     |     |          | Control Signals Combinational Circuit - controls.vhd                          | 268        |

|     |     |          | 9-Bit Programme Counter Register - REGPC.vhd                                  | 270        |

|     |     |          | 9-Bit Register - REG.vhd                                                      | 271        |

|     |     | A.3.5    | 1-Bit Register - REG1BIT.vhd                                                  | 272        |

viii

|     | A.3.6  | 2-Bit 2-To-1 Multiplexer - MUX22.vhd                 | 272 |

|-----|--------|------------------------------------------------------|-----|

|     | A.3.7  | 1-Bit 1-To-2 Multiplexer - MUX11.vhd                 | 273 |

|     | A.3.8  | 9-Bit 1-To-3 Multiplexer - MUX94.vhd                 | 274 |

|     | A.3.9  | 9-Bit 3-To-1 Multiplexer - MUX49.vhd                 | 274 |

|     | A.3.10 | Functional Block GF(28) Multiplier - GF28.vhd        | 275 |

|     | A.3.11 | Functional Block 8-Bit XOR - GF28Add.vhd             | 276 |

|     | A.3.12 | Functional Block SBN - SBN.vhd                       | 277 |

|     | A.3.13 | 9-Bit 2-To-1 Multiplexer - MUX29.vhd                 | 278 |

|     | A.3.14 | 10-Bit Register - REG10BIT.vhd                       | 278 |

|     | A.3.15 | LED 7-Segment Display - D4to7.vhd                    | 279 |

| A.4 | RS MI  | SC ARCHITECTURE IN VHDL                              | 280 |

|     | A.4.1  | Top Level RS MISC Architecture - RSMISC.vhd          | 280 |

|     | A.4.2  | Control Signals Combinational Circuit - controls.vhd | 289 |

|     | A.4.3  | 9-Bit Programme Counter Register - REGPC.vhd         | 290 |

|     | A.4.4  | 9-Bit Register - REG.vhd                             | 291 |

|     | A.4.5  | 1-Bit Register - REG1BIT.vhd                         | 292 |

|     | A.4.6  | 2-Bit 2-To-1 Multiplexer - MUX22.vhd                 | 293 |

|     | A.4.7  | 1-Bit 1-To-2 Multiplexer - MUX11.vhd                 | 293 |

|     | A.4.8  | 10-Bit 1-To-3 Multiplexer - MUX104.vhd               | 294 |

|     | A.4.9  | 10-Bit 3-To-1 Multiplexer - MUX410.vhd               | 295 |

|     | A.4.10 | Functional Block GF(28) Multiplier - GF28.vhd        | 295 |

|     | A.4.11 | Functional Block 8-Bit XOR - GF28Add.vhd             | 297 |

|     | A.4.12 | Functional Block SBN - SBN.vhd                       | 297 |

|     | A.4.13 | 10-Bit 2-To-1 Multiplexer - MUX210.vhd               | 298 |

|     | A.4.14 | 11-Bit Register - REG11BIT.vhd                       | 299 |

|     | A.4.15 | 7-Segment LED Display - D4to7.vhd                    | 299 |

|     |        |                                                      |     |

# LIST OF FIGURES

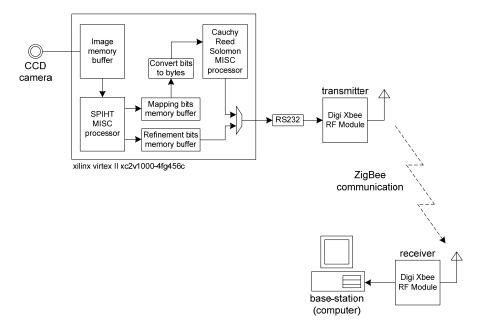

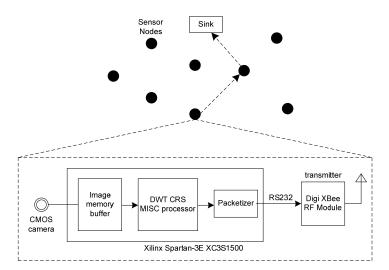

| FIGURE 1  | DEVELOPED IMAGE PROCESSING SYSTEM WITH DWT CRS MISC.                                        | 4    |

|-----------|---------------------------------------------------------------------------------------------|------|

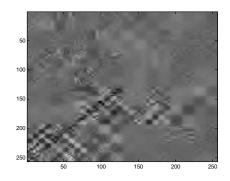

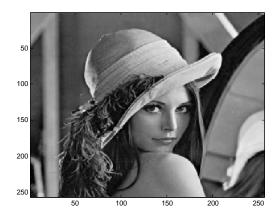

| FIGURE 2  | REPRODUCED COMPRESSED IMAGE USING CWT IN MATLAB SIMULATION.                                 | . 15 |

| FIGURE 3  | REPRODUCED COMPRESSED IMAGE USING DWT IN MATLAB SIMULATION                                  | .16  |

|           | MOVE PROCESSOR ARCHITECTURE [18]                                                            |      |

|           | BASIC HALF ADDER ELEMENT [44].                                                              |      |

| FIGURE 6  | MESH CONNECTED HALF ADDER ELEMENTS [44].                                                    | . 18 |

|           | SBN INSTRUCTION FORMAT.                                                                     |      |

|           | INFORMATION FLOWS IN TRADITIONAL BROADCASTING APPLICATION [5].                              |      |

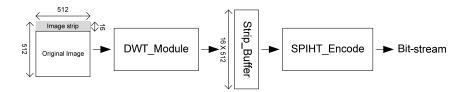

| FIGURE 9  | BLOCK DIAGRAM OF STRIP-BASED COMPRESSION [64].                                              | . 25 |

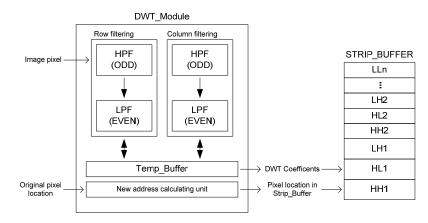

| FIGURE 10 | DWT_MODULE ARCHITECTURE [65].                                                               | .26  |

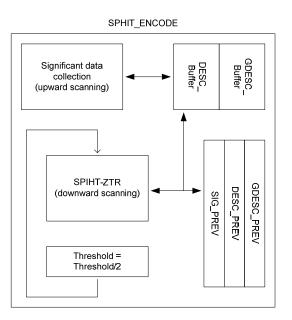

| FIGURE 11 | SPIHT_ENCODER ARCHITECTURE [65]                                                             | .26  |

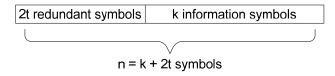

|           | ONE CODEWORD OF REED SOLOMON.                                                               |      |

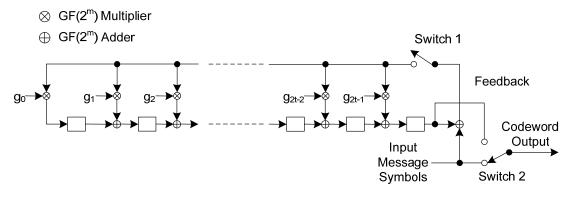

| FIGURE 13 | RS(N,K) ENCODER IN LFSR CIRCUIT CONFIGURATION [17]                                          | . 34 |

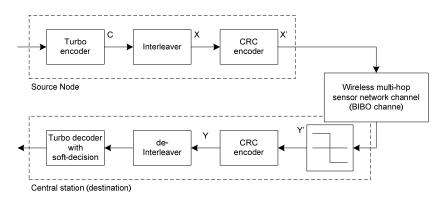

| FIGURE 14 | SIMPLIFIED MULTI-HOP CHANNEL MODEL OF WSN [88].                                             | .36  |

| FIGURE 15 | REGENERATIVE REPEATING PROCESS AT INTERMEDIATE NODE [88]                                    | .36  |

| FIGURE 16 | SIMPLIFIED SYSTEM MODEL WITHOUT REGENERATIVE REPEATING PROCESS [88]                         | .36  |

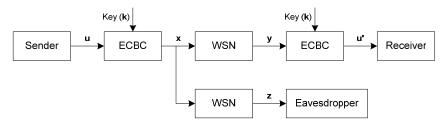

| FIGURE 17 | CONVENTIONAL SECURE COMMUNICATION SYSTEM MODEL [21].                                        | . 53 |

|           | SECURE COMMUNICATION SYSTEM USING ECBC MODEL [21].                                          |      |

| FIGURE 19 | PROPOSED NEW DWT CRS MISC ARCHITECTURE.                                                     | .60  |

| FIGURE 20 | NAND GATE REPRESENTATION OF INVERTER.                                                       | . 62 |

| FIGURE 21 | NAND GATES REPRESENTATION OF AND GATE.                                                      | . 62 |

| FIGURE 22 | NAND GATES REPRESENTATION OF OR GATE.                                                       | . 62 |

| FIGURE 23 | NAND GATES REPRESENTATION OF XOR GATE.                                                      | . 62 |

| FIGURE 24 | • THE REPRESENTATIONS OF A FULL ADDER.                                                      | .63  |

|           | THE ADDER BLOCK CONSISTING OF 11 FULL ADDER                                                 |      |

|           | THE COMPLETE GF(2 <sup>8</sup> ) MULTIPLIER BLOCK FOR DWT CRS MISC ARCHITECTURE             |      |

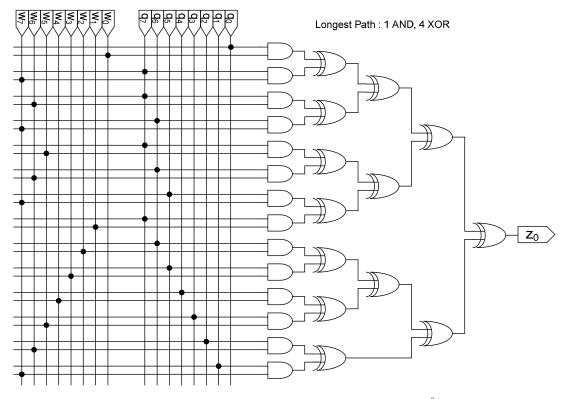

|           | BLOCK $Z_0$ (Bit 0) INTERNAL LOGIC CIRCUIT BLOCK FOR THE GF(2 <sup>8</sup> ) MULTIPLIER     |      |

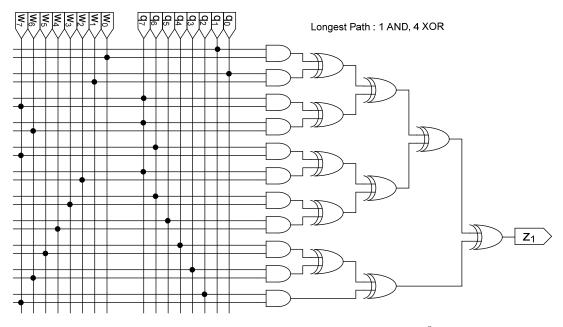

| FIGURE 28 | BLOCK $Z_1$ (BIT 1) INTERNAL LOGIC CIRCUIT BLOCK FOR THE $GF(2^8)$ MULTIPLIER               | . 68 |

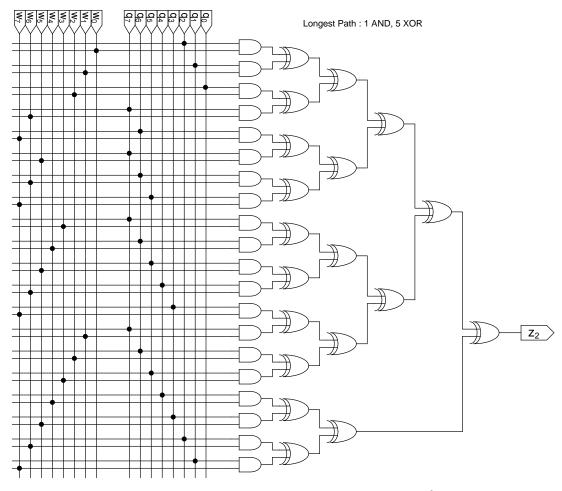

| FIGURE 29 | BLOCK $Z_2$ (BIT 2) INTERNAL LOGIC CIRCUIT BLOCK FOR THE $GF(2^8)$ MULTIPLIER               | . 68 |

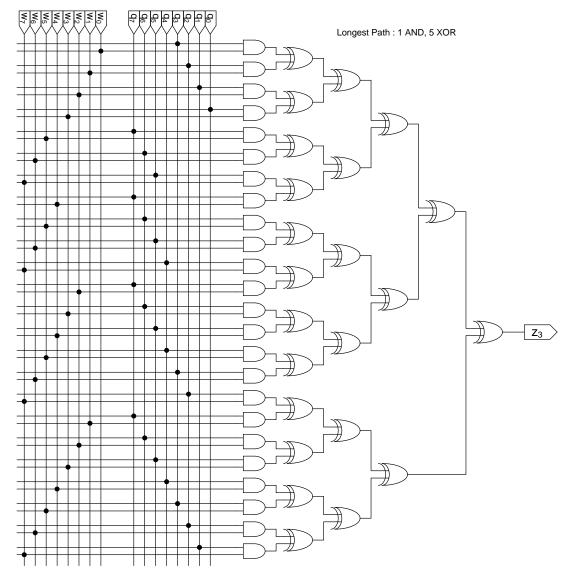

| FIGURE 30 | BLOCK $Z_3$ (Bit 3) INTERNAL LOGIC CIRCUIT BLOCK FOR THE $GF(2^8)$ Multiplier               | . 69 |

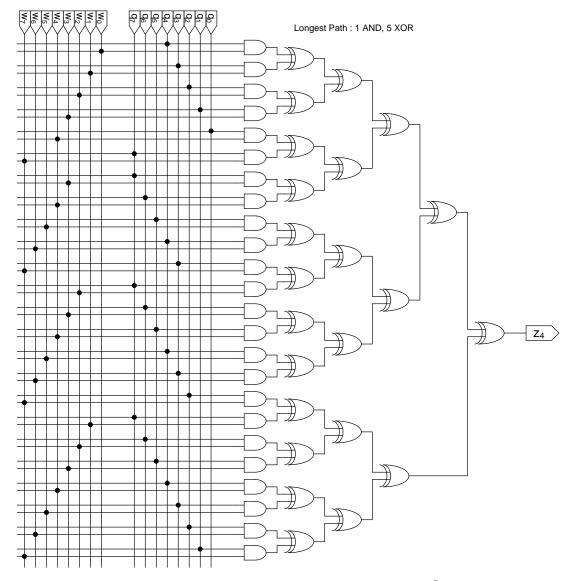

| FIGURE 31 | BLOCK $Z_4$ (BIT 4) INTERNAL LOGIC CIRCUIT BLOCK FOR THE $GF(2^8)$ MULTIPLIER               | .70  |

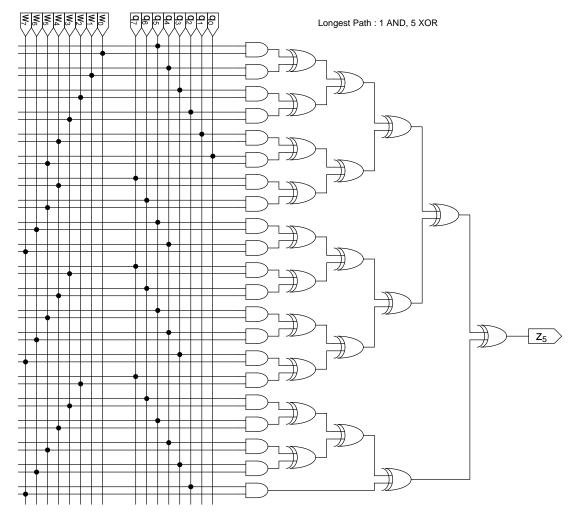

|           | BLOCK $Z_5$ (BIT 5) INTERNAL LOGIC CIRCUIT BLOCK FOR THE $GF(2^8)$ MULTIPLIER               |      |

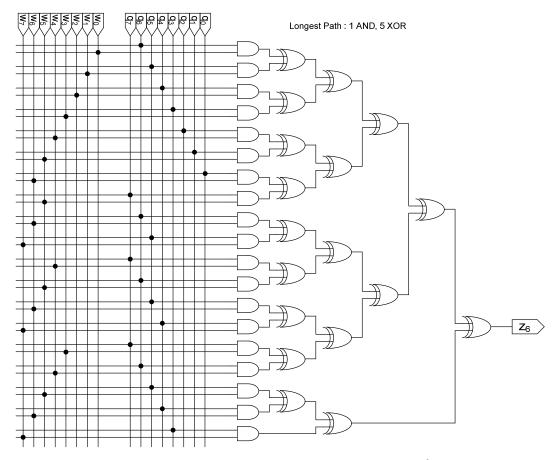

|           | BLOCK $Z_6$ (BIT 6) INTERNAL LOGIC CIRCUIT BLOCK FOR THE $GF(2^8)$ MULTIPLIER               |      |

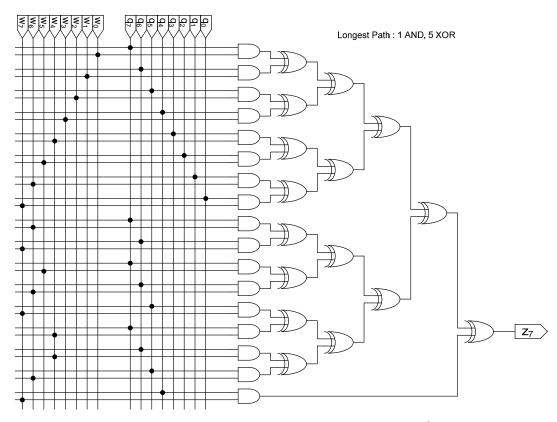

|           | BLOCK $Z_7$ (BIT 7) INTERNAL LOGIC CIRCUIT BLOCK FOR THE $GF(2^8)$ MULTIPLIER               |      |

|           | 11-BIT XOR BLOCK THAT PERFORMS $GF(2^8)$ Additions, Data Copying and Clearing               |      |

|           | Дата                                                                                        |      |

| FIGURE 36 | 11TO8 BLOCK INTERNAL LOGIC CIRCUIT.                                                         |      |

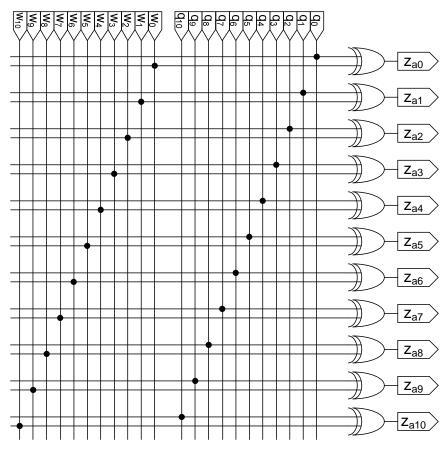

|           | COMBINATIONAL LOGIC CIRCUIT FOR MISC ARCHITECTURE CONTROL SIGNALS.                          |      |

|           | THE BLOCK DIAGRAM REPRESENTATIONS AND LOGIC CIRCUIT OF A TYPICAL D-LATCH                    |      |

|           | OUTPUT WAVEFORMS OF A TYPICAL D-LATCH WITH DELAYS                                           |      |

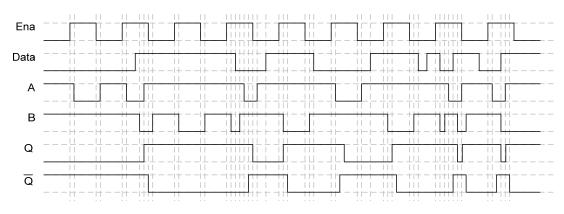

|           | POSITIVE EDGE-TRIGGERED D FLIP-FLOP LOGIC CIRCUIT                                           |      |

|           | BLOCK DIAGRAM OF D FLIP-FLOP CONSTRUCTED WITH 2 D-LATCHES                                   |      |

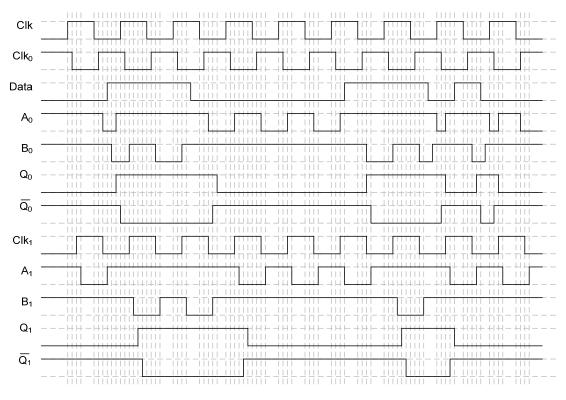

|           | FUNCTIONAL BEHAVIOUR WAVEFORM OF A POSITIVE EDGE-TRIGGERED D FLIP-FLOP                      |      |

|           | D FLIP-FLOPS ARRANGEMENTS TO FORM A 11-BIT REGISTERS.                                       |      |

|           | • A 4-BIT COUNTER THAT COUNTS FROM 0 TO 8.                                                  |      |

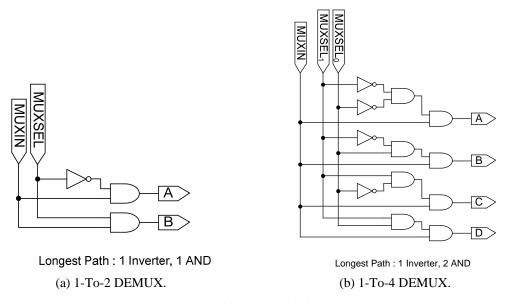

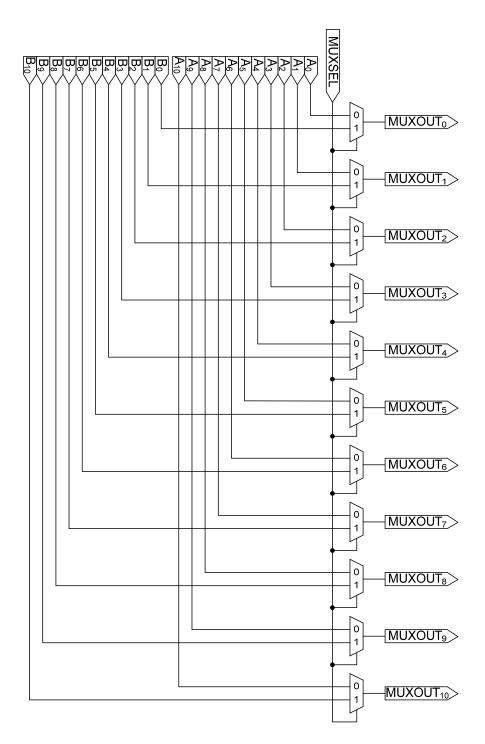

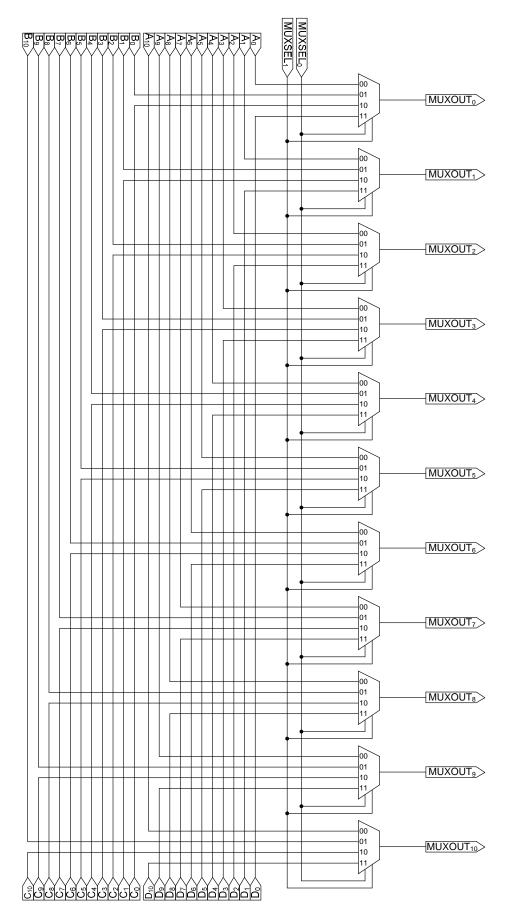

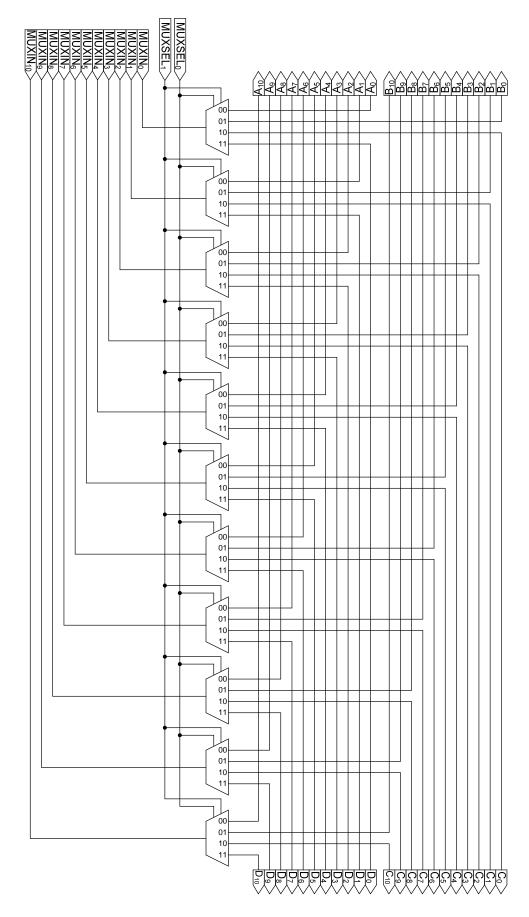

|           | MULTIPLEXER LOGIC CIRCUIT DIAGRAM.                                                          |      |

|           | DE-MULTIPLEXER LOGIC CIRCUIT DIAGRAM.                                                       |      |

|           | 2-TO-1 11-BIT MULTIPLEXER LOGIC BLOCK DIAGRAM                                               |      |

|           | 4-To-1 INPUTS 11-BIT MULTIPLEXER LOGIC BLOCK DIAGRAM.                                       |      |

|           | 1-TO-1 IN 013 H-BH WOLTH LEAR LOOIC BLOCK DIAGRAM.                                          |      |

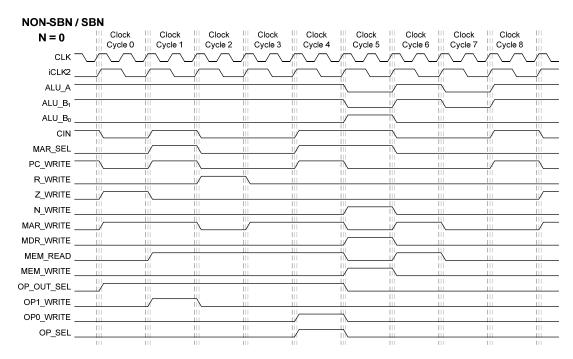

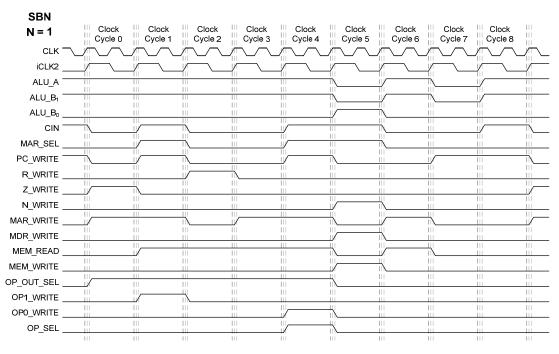

|           | CONTROL SIGNALS GENERATED AT PARTICULAR CLOCK CYCLE, NON-SBN / N=0 (SBN).                   |      |

|           | CONTROL SIGNALS GENERATED AT PARTICULAR CLOCK CYCLE, NON-SDIV/ N=0 (SBIV).                  |      |

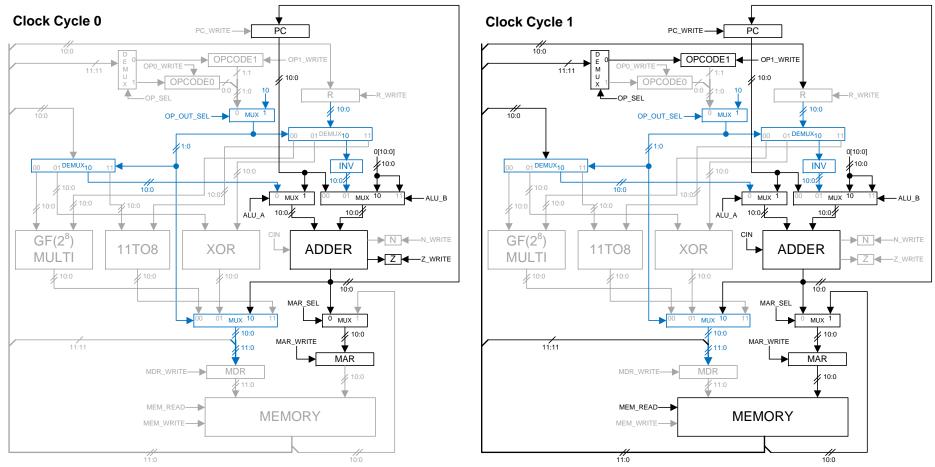

|           | DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 0.                                                 |      |

|           | DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 0.                                                 |      |

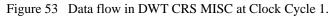

|           | DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 1.     DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 2. |      |

| 100100 07 |                                                                                             |      |

|                                                                              | 0.0    |

|------------------------------------------------------------------------------|--------|

| FIGURE 55 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 3.                        |        |

| FIGURE 56 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 4.                        |        |

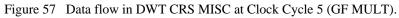

| FIGURE 57 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 5 (GF MULT)               |        |

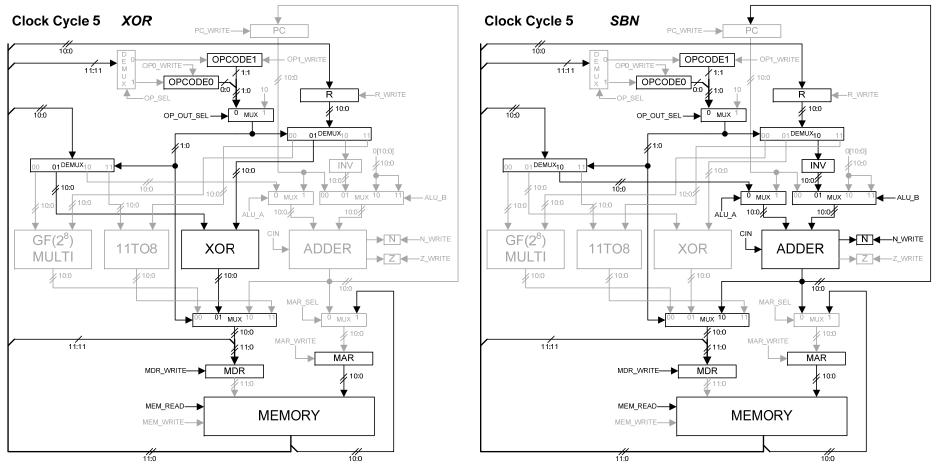

| FIGURE 58 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 5 (XOR).                  |        |

| FIGURE 59 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 5 (SBN).                  |        |

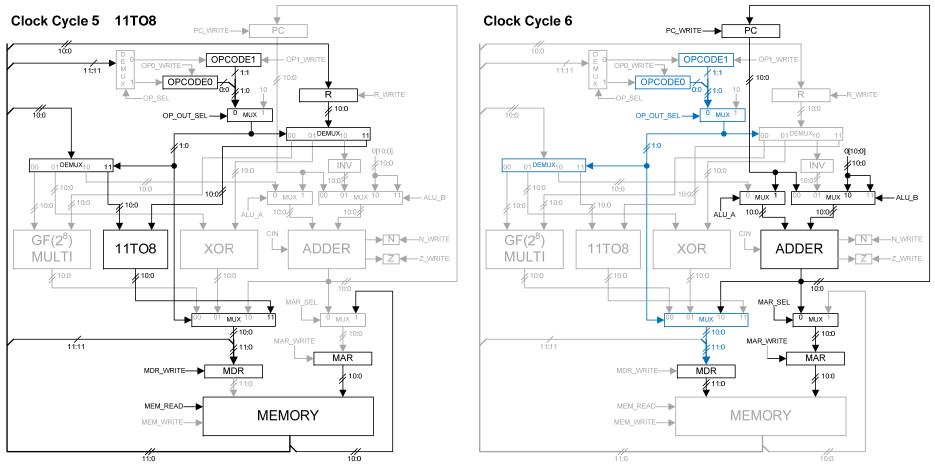

| FIGURE 60 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 5 (11TO8).                |        |

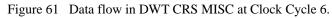

| FIGURE 61 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 6.                        |        |

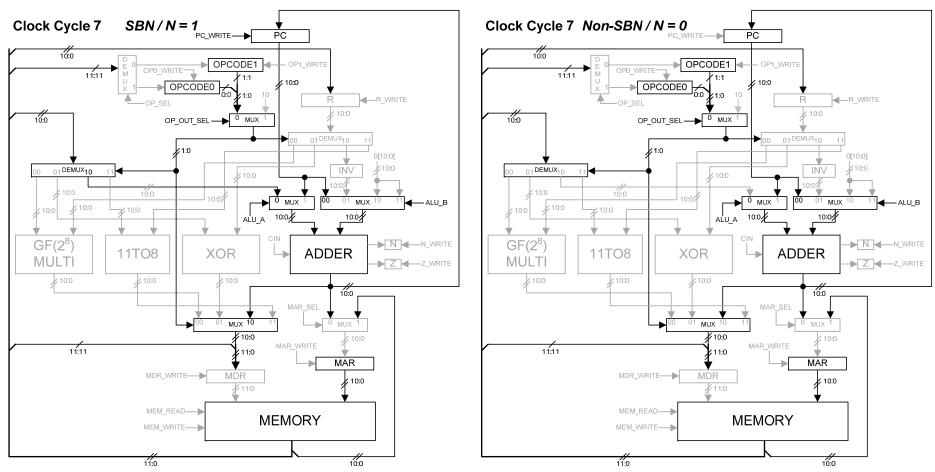

| FIGURE 62 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 7 (N = 1).                |        |

| FIGURE 63 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 7 (Non-SBN/N = 0)         |        |

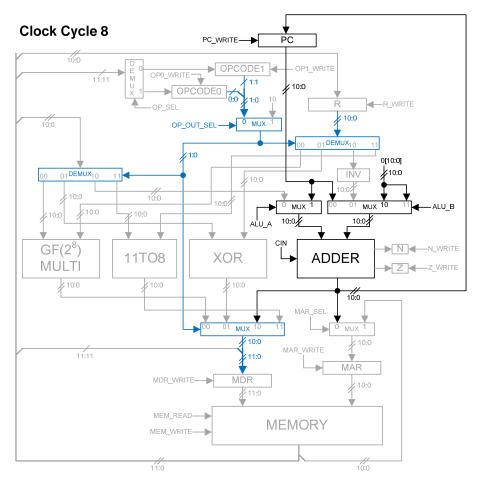

| FIGURE 64 DATA FLOW IN DWT CRS MISC AT CLOCK CYCLE 8.                        |        |

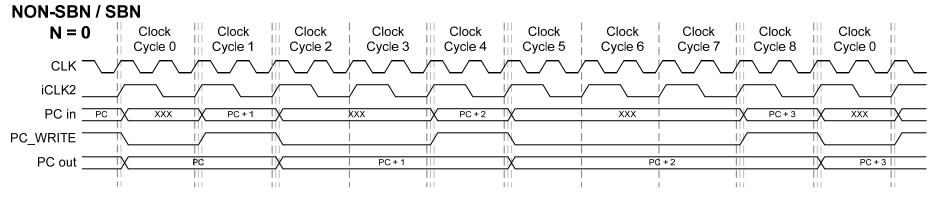

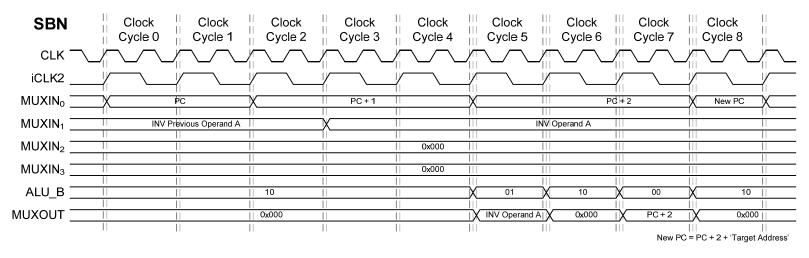

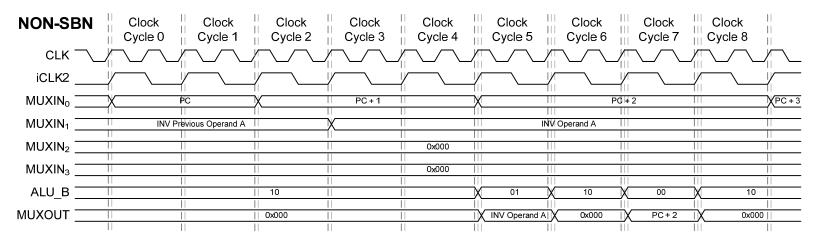

| FIGURE 65 PC REGISTER TIMING DIAGRAM FOR $N = 0$ (SBN / NON-SBN)             |        |

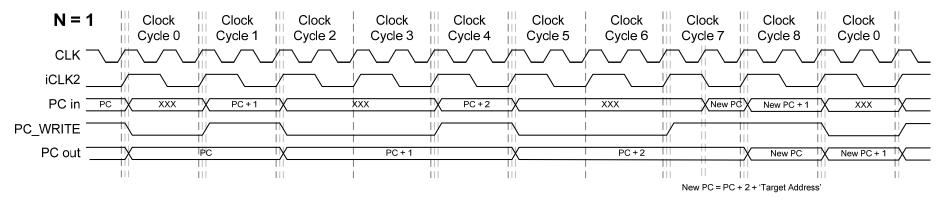

| Figure 66 PC register timing diagram for $N = 1$ (SBN).                      |        |

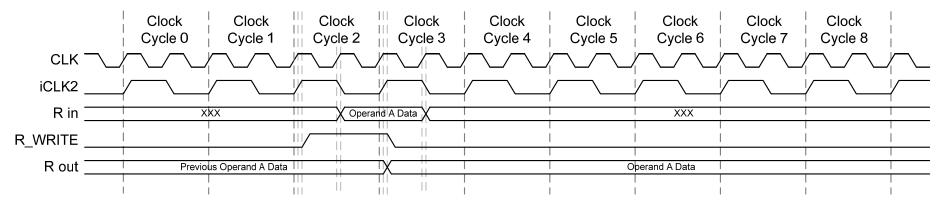

| FIGURE 67 R REGISTER TIMING DIAGRAM.                                         |        |

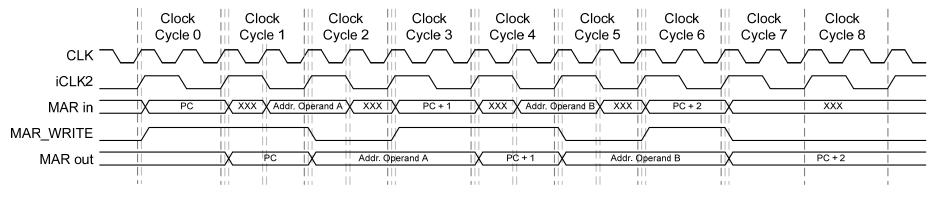

| FIGURE 68 MAR REGISTER TIMING DIAGRAM.                                       |        |

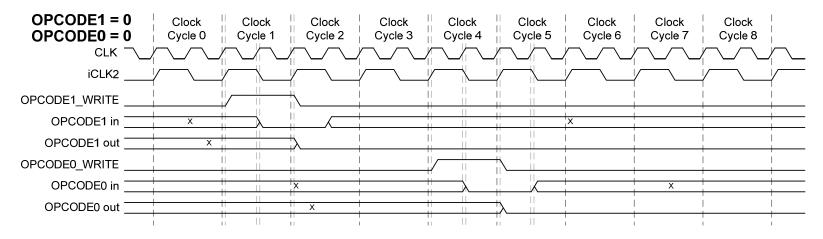

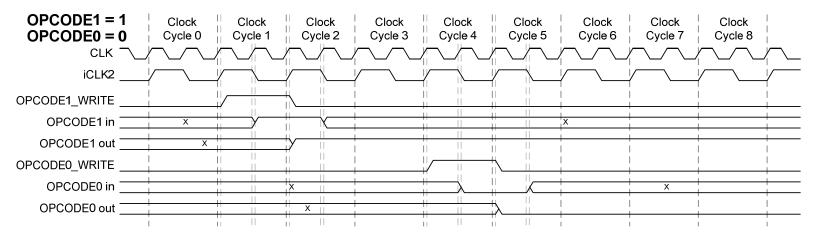

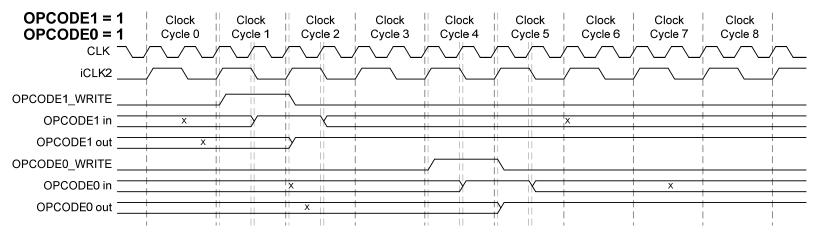

| FIGURE 69 OPCODE1 AND OPCODE0 REGISTERS TIMING DIAGRAM FOR GF MULT           |        |

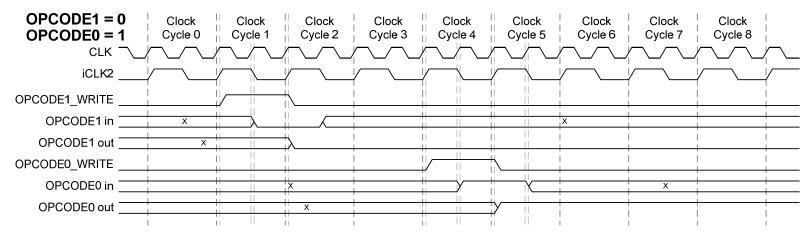

| FIGURE 70 OPCODE1 AND OPCODE0 REGISTERS TIMING DIAGRAM FOR XOR.              |        |

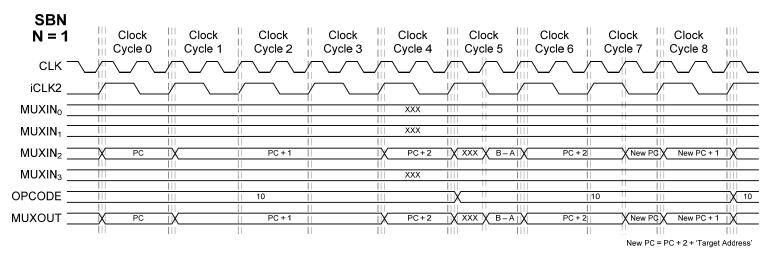

| FIGURE 71 OPCODE1 AND OPCODE0 REGISTERS TIMING DIAGRAM FOR SBN.              |        |

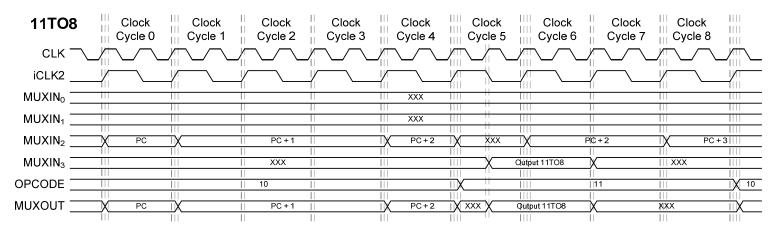

| FIGURE 72 OPCODE1 AND OPCODE0 REGISTERS TIMING DIAGRAM FOR 11TO8.            |        |

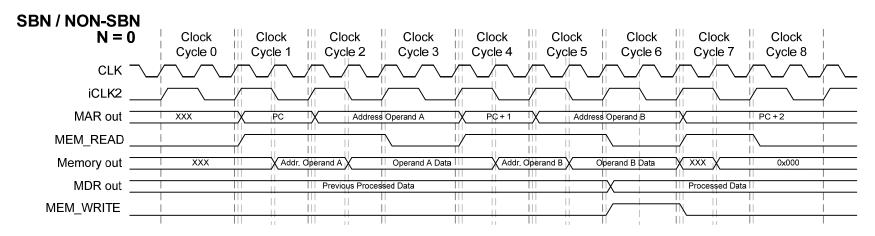

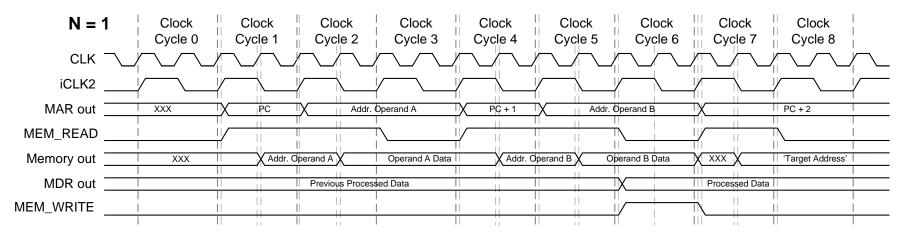

| FIGURE 73 MEMORY OUTPUT AND INPUT TIMING DIAGRAM FOR NON-SBN / N=0           |        |

| FIGURE 74 MEMORY OUTPUT AND INPUT TIMING DIAGRAM FOR $N=1$                   |        |

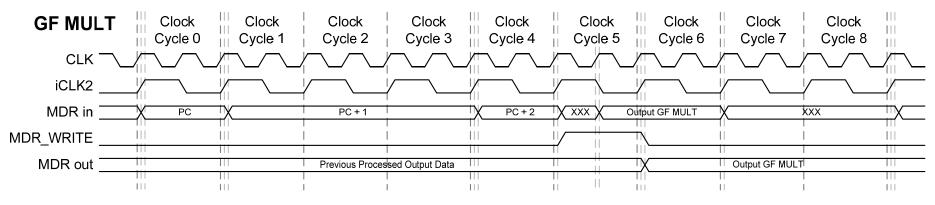

| FIGURE 75 MDR REGISTER TIMING DIAGRAM FOR GF MULT INSTRUCTION                |        |

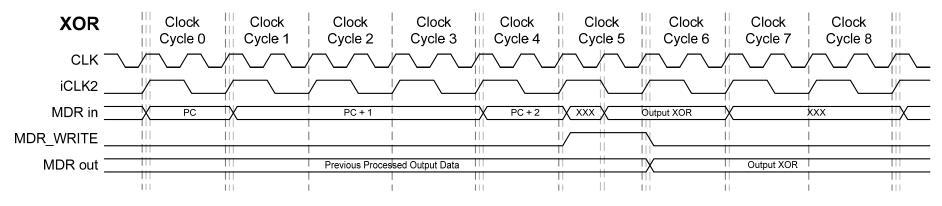

| FIGURE 76 MDR REGISTER TIMING DIAGRAM FOR XOR INSTRUCTION.                   |        |

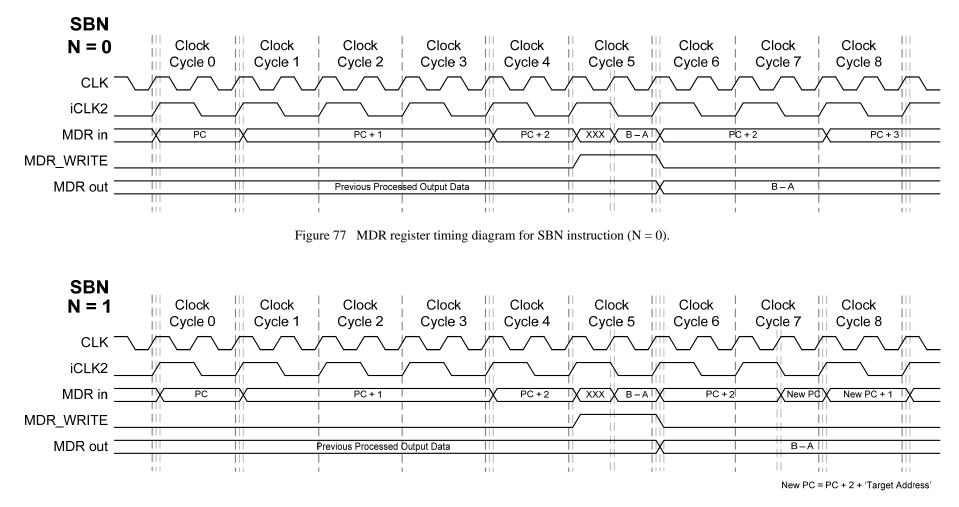

| FIGURE 77 MDR REGISTER TIMING DIAGRAM FOR SBN INSTRUCTION (N = 0)            |        |

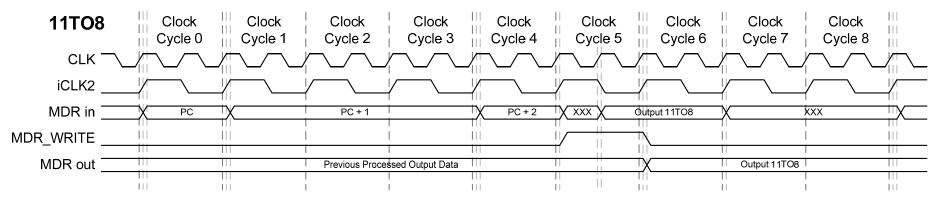

| FIGURE 78 MDR REGISTER TIMING DIAGRAM FOR SBN INSTRUCTION (N = 1)            |        |

| FIGURE 79 MDR REGISTER TIMING DIAGRAM FOR 11TO8 INSTRUCTION.                 |        |

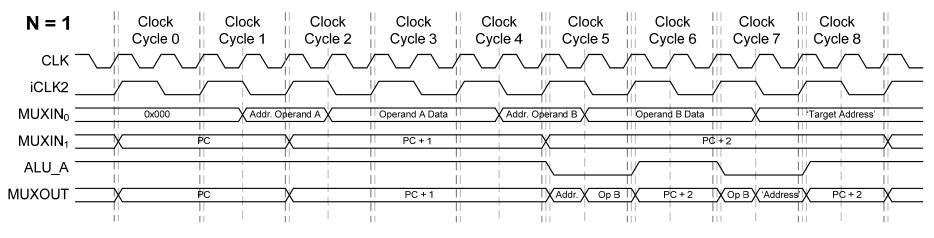

| FIGURE 80 ALU_A MUX TIMING DIAGRAM FOR SBN INSTRUCTION (N = 1)               |        |

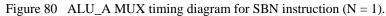

| FIGURE 81 ALU_A MUX TIMING DIAGRAM FOR SBN INSTRUCTION (N = 0)               |        |

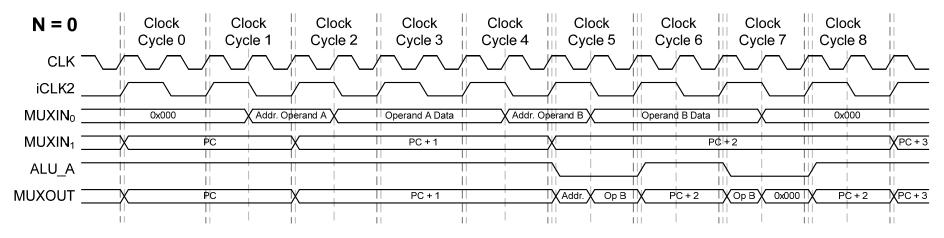

| FIGURE 82 ALU_A MUX TIMING DIAGRAM FOR NON-SBN INSTRUCTION.                  |        |

| FIGURE 83 ALU_B MUX TIMING DIAGRAM FOR SBN INSTRUCTION.                      |        |

| FIGURE 84 ALU_B MUX TIMING DIAGRAM FOR NON-SBN INSTRUCTION.                  |        |

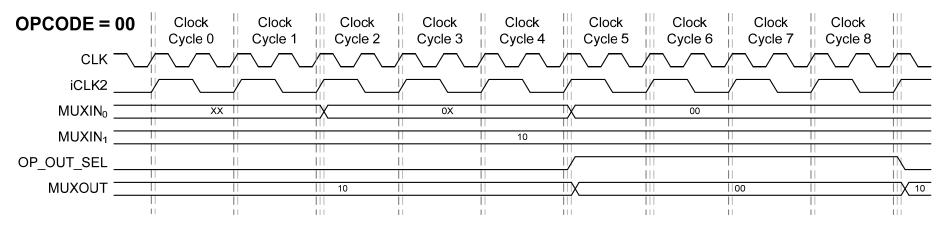

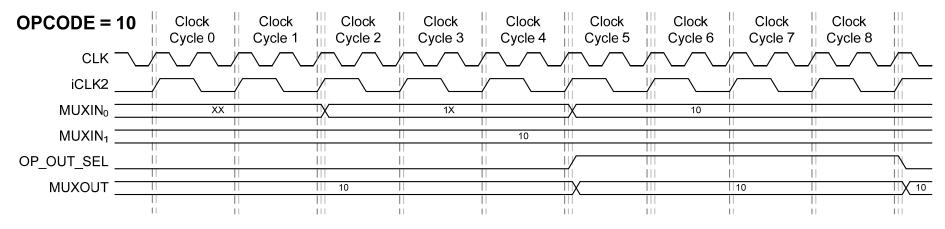

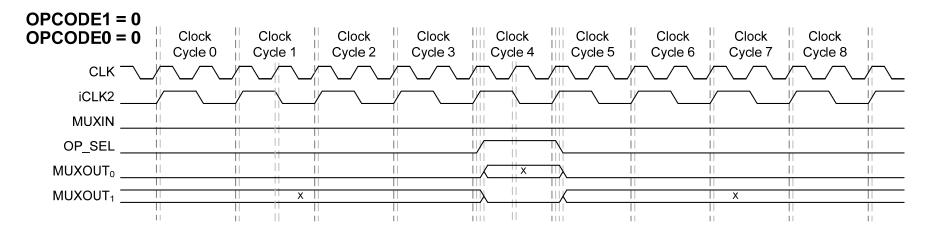

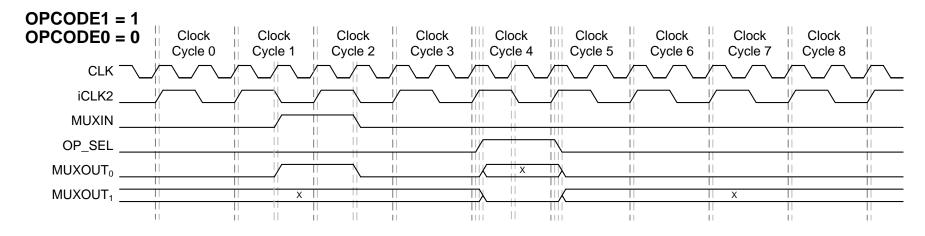

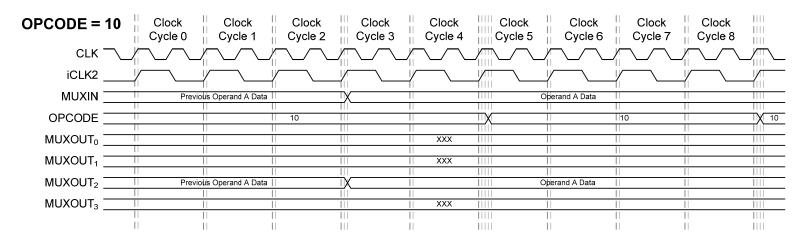

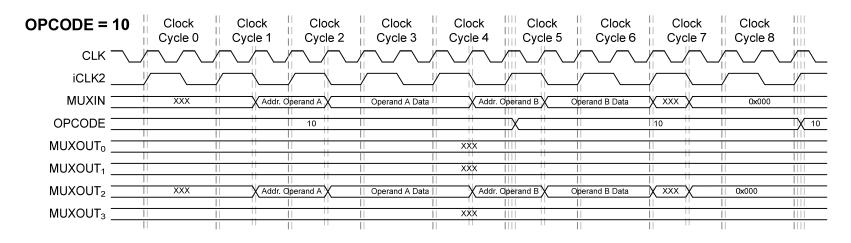

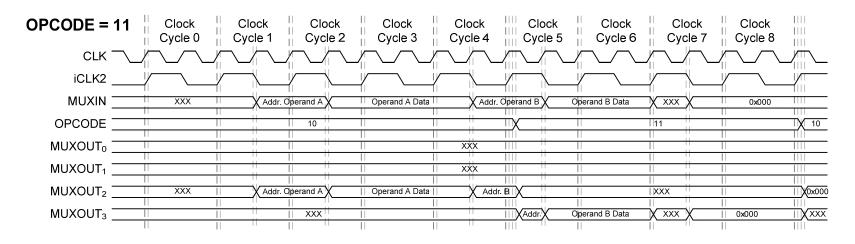

| FIGURE 85 OP_OUT MUX TIMING DIAGRAM FOR GF MULT INSTRUCTION (OPCODE=00)      |        |

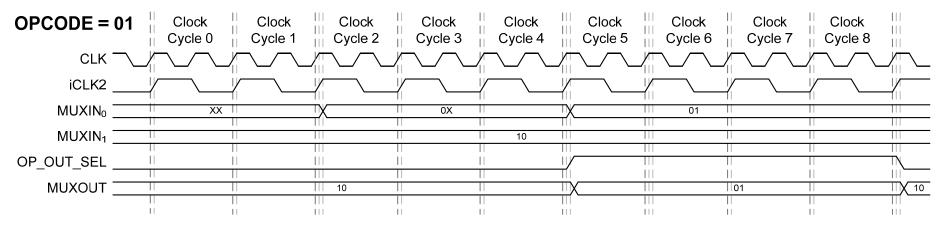

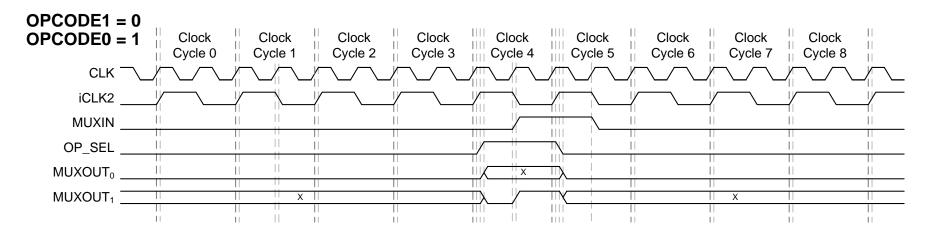

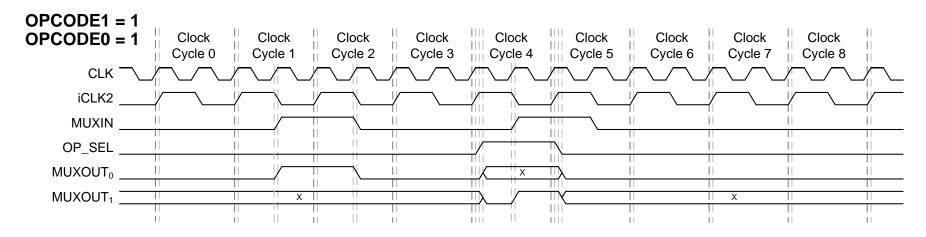

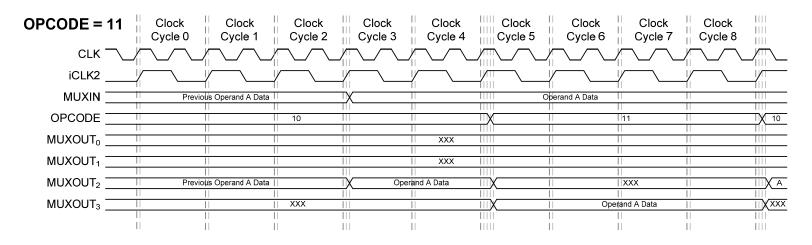

| FIGURE 86 OP_OUT MUX TIMING DIAGRAM FOR XOR INSTRUCTION (OPCODE=01)          |        |

| FIGURE 87 OP_OUT MUX TIMING DIAGRAM FOR SBN INSTRUCTION (OPCODE=10).         |        |

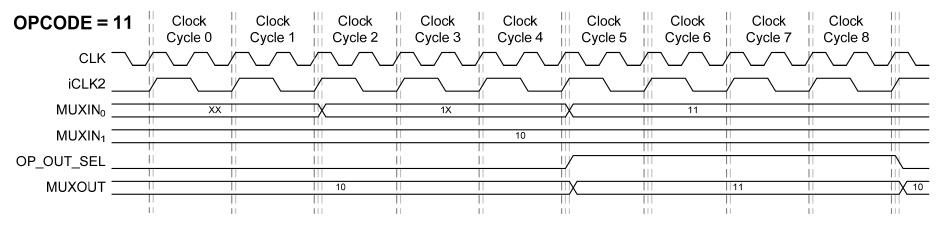

| FIGURE 88 OP_OUT MUX TIMING DIAGRAM FOR 11TO8 INSTRUCTION (OPCODE=11)        |        |

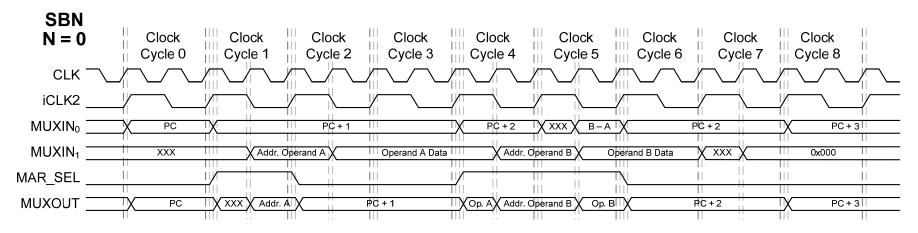

| FIGURE 89 MAR_IN MUX TIMING DIAGRAM FOR SBN INSTRUCTION (N = 0)              |        |

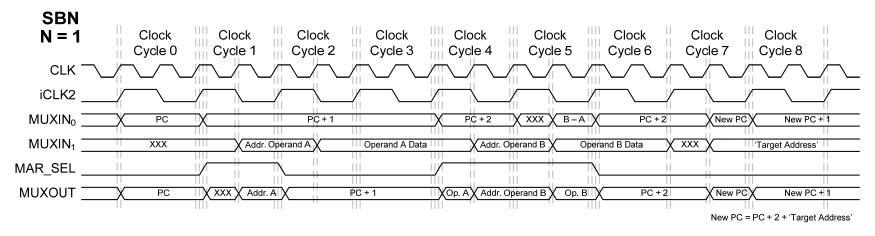

| FIGURE 90 MAR_IN MUX TIMING DIAGRAM FOR SBN INSTRUCTION (N = 1)              |        |

| FIGURE 91 MAR_IN MUX TIMING DIAGRAM FOR NON-SBN INSTRUCTION.                 |        |

| FIGURE 92 MDR_IN MUX TIMING DIAGRAM FOR GF MULT INSTRUCTION.                 |        |

| FIGURE 93 MDR_IN MUX TIMING DIAGRAM FOR XOR INSTRUCTION.                     |        |

| FIGURE 94 MDR_IN MUX TIMING DIAGRAM FOR SBN INSTRUCTION (N = 0)              |        |

| FIGURE 95 MDR_IN MUX TIMING DIAGRAM FOR SBN INSTRUCTION (N = 1)              |        |

| FIGURE 96 MDR_IN MUX TIMING DIAGRAM FOR 11TO8 INSTRUCTION.                   |        |

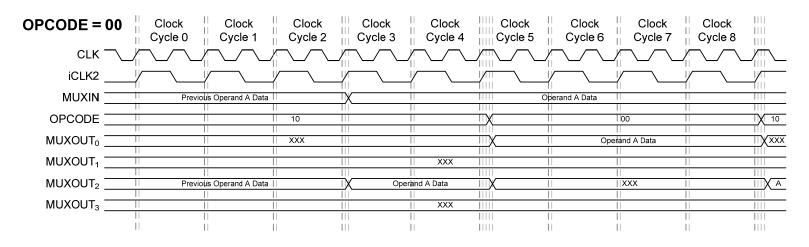

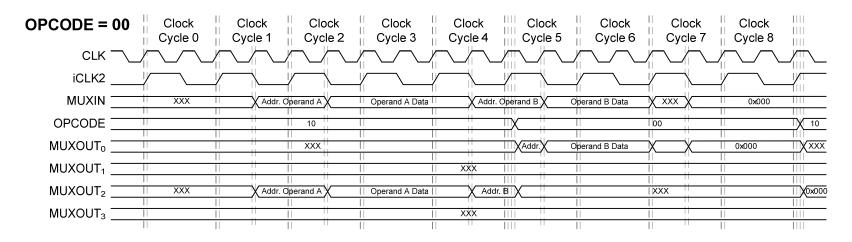

| FIGURE 97 OP_SEL DEMUX TIMING DIAGRAM FOR GF MULT INSTRUCTION (OPCODE=00)    |        |

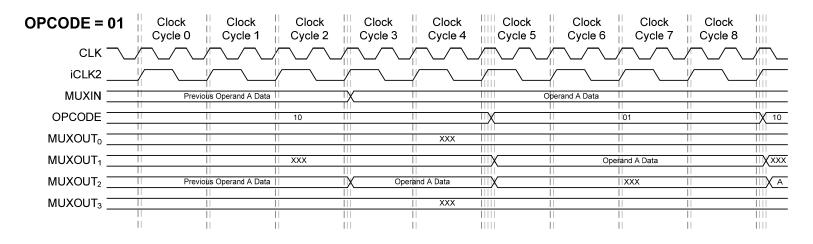

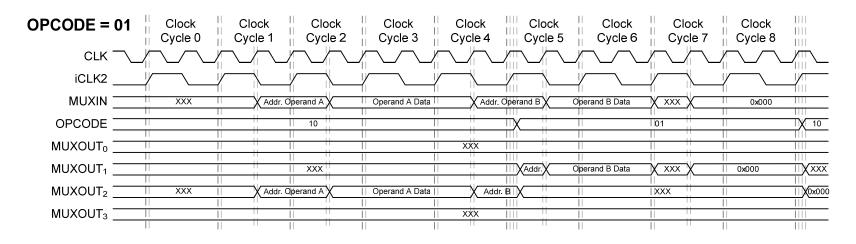

| FIGURE 98 OP_SEL DEMUX TIMING DIAGRAM FOR XOR INSTRUCTION (OPCODE=01)        |        |

| FIGURE 99 OP_SEL DEMUX TIMING DIAGRAM FOR SBN INSTRUCTION (OPCODE=10)        |        |

| FIGURE 100 OP_SEL DEMUX TIMING DIAGRAM FOR 11TO8 INSTRUCTION (OPCODE=11)     |        |

| FIGURE 101 R_OUT DEMUX TIMING DIAGRAM FOR GF MULT INSTRUCTION (OPCODE=00)    | 118    |

| FIGURE 102 R_OUT DEMUX TIMING DIAGRAM FOR XOR INSTRUCTION (OPCODE=01)        |        |

| FIGURE 103 R_OUT DEMUX TIMING DIAGRAM FOR SBN INSTRUCTION (OPCODE=10)        | 119    |

| FIGURE 104 R_OUT DEMUX TIMING DIAGRAM FOR 11TO8 INSTRUCTION (OPCODE=11)      | 119    |

| FIGURE 105 MEM_OUT DEMUX TIMING DIAGRAM FOR GF MULT INSTRUCTION (OPCODE=00   | ). 120 |

| FIGURE 106 MEM_OUT DEMUX TIMING DIAGRAM FOR XOR INSTRUCTION (OPCODE=01)      |        |

| FIGURE 107 MEM_OUT DEMUX TIMING DIAGRAM FOR SBN INSTRUCTION (OPCODE=10)      |        |

| FIGURE 108 MEM_OUT DEMUX TIMING DIAGRAM FOR 11TO8 INSTRUCTION (OPCODE=11)    | 121    |

| FIGURE 109 DWT CRS MISC MEMORY LOCATION                                      |        |

| FIGURE 110 PROGRAM INSTRUCTIONS FOR DWT CRS MISC ARCHITECTURE.               |        |

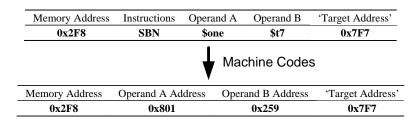

| FIGURE 111 WRITTEN PROGRAMME INSTRUCTION AND ITS CORRESPONDING MACHINE CODES |        |

| FIGURE 112 SETTING THE 'TARGET ADDRESS' FOR SBN (N = 1)                      | 125    |

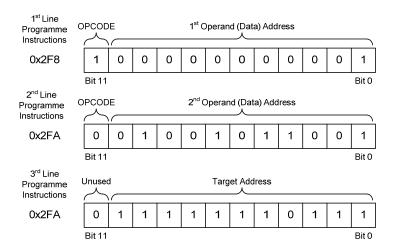

| FIGURE 113 MACHINE CODE OF SBN INSTRUCTION IN PROGRAMME MEMORY.              |        |

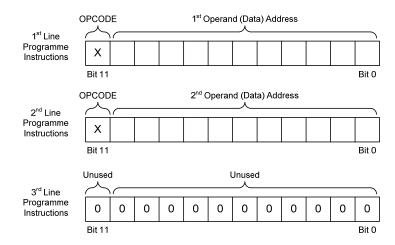

| FIGURE 114 MACHINE CODE OF NON-SBN INSTRUCTION IN PROGRAMME MEMORY           | 126    |

|                                                                              |        |

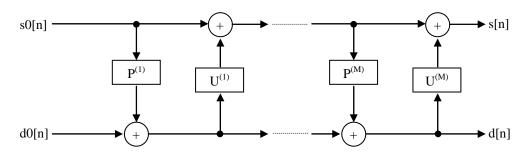

| FIGURE 115 | LIFTING SCHEME DISCRETE WAVELET TRANSFORM FILTER BANK [143].             | 127 |

|------------|--------------------------------------------------------------------------|-----|

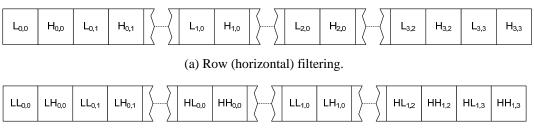

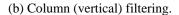

| FIGURE 116 | LEVEL 1 DWT COEFFICIENTS ARRANGEMENT IN 2D.                              | 128 |

| FIGURE 117 | ACTUAL LEVEL 1 DWT COEFFICIENTS ARRANGEMENT IN MEMORY.                   | 128 |

| FIGURE 118 | LEVEL 2 DWT COEFFICIENTS ARRANGEMENT IN 2D.                              | 132 |

| FIGURE 119 | ACTUAL LEVEL 2 DWT COEFFICIENTS ARRANGEMENT IN MEMORY.                   | 132 |

| FIGURE 120 | DWT CRS MISC CONTROL SIGNALS BEHAVIORAL WAVEFORMS.                       | 157 |

| FIGURE 121 | DWT CRS MISC CONTROL SIGNALS POST & ROUTE WAVEFORMS WITH N = 0           | 158 |

| FIGURE 122 | DWT CRS MISC CONTROL SIGNALS POST & ROUTE WAVEFORMS WITH N = 1           | 159 |

| FIGURE 123 | BEHAVIORAL SIMULATION WAVEFORMS SBN INSTRUCTION FOR DWT CRS MISC         | 164 |

| FIGURE 124 | BEHAVIORAL SIMULATION WAVEFORMS GF MULT INSTRUCTION FOR DWT CRS MISC     | 2.  |

|            |                                                                          | 165 |

| FIGURE 125 | BEHAVIORAL SIMULATION WAVEFORMS XOR INSTRUCTION FOR DWT CRS MISC         | 166 |

| FIGURE 126 | BEHAVIORAL SIMULATION WAVEFORMS 11TO8 INSTRUCTION FOR DWT CRS MISC 7     | 167 |

| FIGURE 127 | POST & ROUTE SIMULATION WAVEFORMS SBN INSTRUCTION FOR DWT CRS MISC       | 172 |

| FIGURE 128 | POST & ROUTE SIMULATION WAVEFORMS GF MULT INSTRUCTION FOR DWT CRS MIS    | SC. |

|            |                                                                          | 173 |

| FIGURE 129 | POST & ROUTE SIMULATION WAVEFORMS XOR INSTRUCTION FOR DWT CRS MISC 7     | 174 |

| FIGURE 130 | POST & ROUTE SIMULATION WAVEFORMS 11TO8 INSTRUCTION FOR DWT CRS MISC.    | 175 |

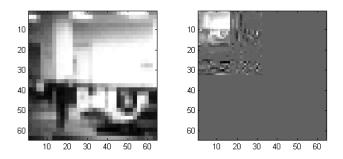

|            | DWT HAAR ON 'LENA1.TIF' IMAGE                                            |     |

| FIGURE 132 | ERRORS OCCURRED ON EACH PACKET OF DWT COEFFICIENTS.                      | 185 |

| FIGURE 133 | RECONSTRUCTED CRS ENCODED COMPRESSED IMAGE DATA WITH 4 ERRORS ON EACH    |     |

|            | PACKET.                                                                  | 185 |

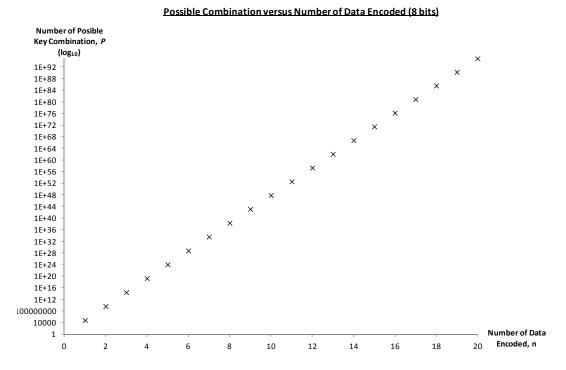

|            | POSSIBLE COMBINATION VERSUS THE NUMBER OF DATA ENCODED                   |     |

| FIGURE 135 | CRS CODING SCHEME PERFORMED ONTO LENA IMAGE.                             | 187 |

| FIGURE 136 | CRS PROTECTED MAPPING BYTES (BITS) IN PACKETS FOR WIRELESS TRANSMISSION  | 191 |

|            | REFINEMENT BYTES (BITS) IN PACKETS FOR WIRELESS TRANSMISSION.            |     |

| FIGURE 138 | SELECTIVE SEC CODING ON SPIHT COEFFICIENTS IN WVSNs                      | 192 |

| FIGURE 139 | RECONSTRUCTED IMAGE WITH 4 ERRORS ON MAPPING BYTES.                      | 194 |

| FIGURE 140 | RECONSTRUCTED IMAGE WITH 4 ERRORS ON REFINEMENT BYTES                    | 194 |

|            | RECONSTRUCTED COMPRESS IMAGE WITHOUT ERRORS                              |     |

| FIGURE 142 | PROPOSED DWT MODULE COMBINED CRS MISC IMAGE PROCESSING SYSTEM FOR WVS    |     |

|            |                                                                          |     |

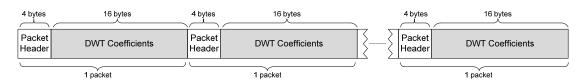

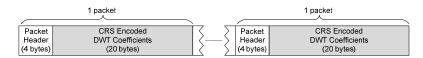

|            | PACKET ARRANGEMENTS OF DWT COEFFICIENTS WITHOUT CRS CODING               |     |

| FIGURE 144 | PACKET ARRANGEMENTS OF CRS ENCODED DWT COEFFICIENTS.                     | 198 |

| FIGURE 145 | SINGLE HOP HARDWARE SIMULATION ON THE PROPOSED SYSTEM.                   | 200 |

| FIGURE 146 | RECONSTRUCTED ORIGINAL IMAGE CAPTURED AT SENSOR NODE.                    | 200 |

|            | PROPOSED SYSTEM WITH DWT CRS MISC ARCHITECTURE FOR WVSNs                 |     |

| FIGURE 148 | TRANSMISSION OF PACKET FOR DWT CRS MISC PROCESSOR ENCODED IMAGE DATA     | 202 |

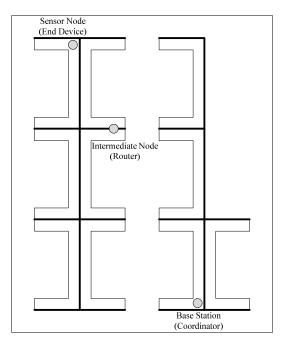

| FIGURE 149 | ARRANGEMENTS OF SENSOR NODE, INTERMEDIATE NODE AND BASE STATION INSIDE A |     |

|            | ROOM                                                                     | 203 |

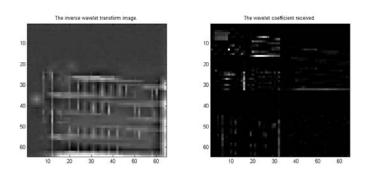

| FIGURE 150 | HARDWARE SIMULATION FOR THE PROPOSED SYSTEM WITH DWT CRS MISC            |     |

|            | ARCHITECTURE.                                                            |     |

| FIGURE 151 | RECONSTRUCTED IMAGE WITH LEVEL 2 DWT COEFFICIENTS.                       | 205 |

# LIST OF TABLES

| TABLE 1 I | LIST OF RECENT RESEARCH WORKS RELATED TO DWT AND CWT FOR IMAGE/SIGNAL        |      |

|-----------|------------------------------------------------------------------------------|------|

| F         | PROCESSING.                                                                  | . 13 |

| TABLE 2 N | MATLAB SIMULATION RESULTS FOR IMAGE COMPRESSION PERFORMED USING CWT AND      |      |

| Ι         | DWT                                                                          | . 15 |

| TABLE 3 ( | GATES DELAYS OF THE GF MULT BLOCK                                            | . 66 |

|           | FRUTH TABLE OF DWT CRS MISC CONTROL SIGNALS                                  |      |

|           | SEQUENCE OF LOGIC COMPONENTS IN LONGEST DELAY PATH                           |      |

| TABLE 6 N | NUMBER OF PROGRAMME INSTRUCTIONS EXECUTED FOR DWT CRS MISC.                  | 151  |

| TABLE 7 7 | TIME DELAYS OF CONTROL SIGNALS GENERATED FOR CASE INPUT SIGNAL, N = 0        | 160  |

|           | TIME DELAYS OF CONTROL SIGNALS GENERATED FOR CASE INPUT SIGNAL, N = 1        |      |

|           | DWT CRS MISC Architecture SBN Instruction delays                             |      |

|           | DWT CRS MISC ARCHITECTURE GF MULT INSTRUCTION DELAYS.                        |      |

|           | DWT CRS MISC ARCHITECTURE XOR INSTRUCTION DELAYS                             |      |

|           | DWT CRS MISC ARCHITECTURE 11TO8 INSTRUCTION DELAYS.                          |      |

| TABLE 13  | HARDWARE UTILISATION OF DWT CRS MISC ARCHITECTURE IN SPARTAN-3L FPGA 1       | 177  |

| TABLE 14  | HARDWARE UTILISATIONS OF DEVELOPED AND EXISTING METHOD USED IN SIMILAR FPGA  |      |

|           | TECHNOLOGY (SPARTAN-3, VIRTEX-II) FOR WVSNs/WSNs.                            | 178  |

|           | HARDWARE UTILISATION OF DWT CRS MISC ARCHITECTURE IN SPARTAN-6 FPGA          |      |

| TABLE 16  | XILINX XPOWER ESTIMATED POWER CONSUMPTION OF DWT CRS MISC ARCHITECTURE.      | 180  |

| TABLE 17  | HARDWARE UTILISATIONS OF DEVELOPED AND EXISTING METHOD IN SPARTAN-6 FPGA FC  |      |

|           | WVSNs/WSNs.                                                                  |      |

| TABLE 18  | IMAGE QUALITY, TRANSMISSION TIME AND ENERGY FOR DIFFERENT AMOUNT OF DWT (HA  | AR)  |

|           | COEFFICIENTS TRANSFERRED.                                                    |      |

|           | QUALITY OF 10 RECONSTRUCTED IMAGE WITH ERRORS ON $DWT$ coefficients          |      |

|           | NUMBER OF POSSIBLE TRIALS, P FOR DIFFERENT CRS CODING SCHEME CONFIGURATIONS. |      |

|           | RECONSTRUCTED IMAGE QUALITY WITH ERRORS ON MAPPING BYTES                     |      |

| TABLE 22  | RECONSTRUCTED IMAGE QUALITY WITH ERRORS ON REFINEMENT BYTES                  | 193  |

|           | HARDWARE UTILISATION OF COMBINED SPIHT MIPS AND CRS MISC ARCHITECTURE 7      | 196  |

| TABLE 24  | HARDWARE UTILISATION OF THE PROPOSED DWT MODULE AND CRS MISC SYSTEM FOR      |      |

|           | WVSNs.                                                                       |      |

|           | HARDWARE UTILISATION OF THE PROPOSED SYSTEM WITH DWT CRS MISC FOR WVSNS2     |      |

| TABLE 26  | HARDWARE UTILISATIONS OF THE DEVELOPED SYSTEMS FOR WVSNs                     | 207  |

# LIST OF ACRONYMS

| ADC     | Analogue-to-Digital Converter                       |

|---------|-----------------------------------------------------|

| AES     | Advanced Encryption Standard                        |

| ARQ     | Automatic Request for Retransmission                |

| AWGN    | Additive White Gaussian Noise                       |

| BCH     | Bose, Chaudhuri, and Hocquenghem                    |

| BER     | Bit Error Rate                                      |

| BIBO    | Binary-Input and Binary-Output                      |

| CCD     | Charge Coupled Device                               |

| CISC    | Complex Instruction Set Computer                    |

| CL-DCT  | Cordic Loeffler Discrete Cosine Transform           |

| CMOS    | Complementary Metal-Oxide Semiconductor             |

| CPLD    | Complex Programmable Logic Device                   |

| CPU     | Computer Processing Unit                            |

| CRC     | Cyclic Redundancy Check                             |

| CRS     | Cauchy Reed Solomon                                 |

| CS      | Compressed Sensing                                  |

| CWT     | Continuous Wavelet Transform                        |

| DES     | Data Encryption Standard                            |

| DWT     | Discrete Wavelet Transform                          |

| ECBC    | Error Correction-Based Cipher                       |

| ECC     | Elliptic Curve Cryptography                         |

| ECC     | Error-Correction Code                               |

| ECDH    | Elliptic Curve Diffie-Hellman                       |

| ECDSA   | Elliptic Curve Digital Signature Algorithm          |

| ECIES   | Elliptic Curve Integrated Encryption Scheme         |

| EEPROM  | Electrically Erasable Programmable Read-Only Memory |

| FEC     | Forward Error Correction                            |

| FPGA    | Field Programmable Gated Array                      |

| GF      | Galois Field                                        |

| GF MULT | Galois Field Multiplier                             |

| HARQ  | Hybrid ARQ/FEC                                     |

|-------|----------------------------------------------------|

| HD    | High Diffusion                                     |

| HEX   | Hexadecimal                                        |

| IBBSC | Identity-Based Broadcast Signcryption Scheme       |

| IBE   | Identity-Based Encryption                          |

| ICES  | Image Compression Encryption Scheme (ICES)         |

| IPJ   | Information Per Joule                              |

| JPEG  | Joint Photographic Experts Group                   |

| LBT   | Lapped Biorthognal Transform                       |

| LDPC  | Low-Density Parity-Check                           |

| LFSR  | Linear Feedback Shift Register                     |

| LSB   | Least Significant Bit                              |

| LUT   | Look-Up-Table                                      |

| LZW   | Lempel-Ziv-Welch                                   |

| MAR   | Memory Address Register                            |

| MDR   | Memory Data Register                               |

| MIMO  | Multiple Input Multiple Output                     |

| MIPS  | Microprocessor without Interlocked Pipeline Stages |

| MISC  | Minimal Instruction Set Computer                   |

| MIT   | Multiple-Input Turbo                               |

| MSB   | Most Significant Bit                               |

| MUX   | Multiplexer                                        |

| MVMP  | Multi-Version Multi-Path                           |

| NIST  | National Institute of Standards and Technology     |

| OISC  | One Instruction Set Computer                       |

| PC    | Programme Counter                                  |

| PCCC  | Parallel Concatenated Convolutional Code           |

| РКС   | Public-Key Cryptography                            |

| PKE   | Public-Key Encryption                              |

| PSNR  | Peak Signal-to-Noise Ratio                         |

| RAM   | Random Access Memory                               |

| RF    | Radio Frequency                                    |

| RFID  | Radio-Frequency Identification                     |

| RISC   | Reduced Instruction Set Computer                 |

|--------|--------------------------------------------------|

| RS     | Reed Solomon                                     |

| SBN    | Subtract and Branch if Negative                  |

| SEC    | Secure Erasure Coding                            |

| SECDED | Single-bit Error and Detect Double-bit Errors    |

| SKC    | Secret-Key Cryptography                          |

| SLCCA  | Significance-Linked Connected Component Analysis |

| SNEP   | Secure Network Encryption Protocol               |

| SNR    | Signal-to-Noise Ratio                            |

| SOT    | Spatial Orientation Tree                         |

| SPIHT  | Set Partitioning In Hierarchical Trees           |

| SPINS  | Security Protocols for Sensor Networks           |

| SRAM   | Static Random-Access Memory                      |

| UMC    | United Microelectronics Corporation              |

| URISC  | Ultimate Reduced Instruction Set Computer        |

| VHDL   | VHSIC Hardware Description Language              |

| VHSIC  | Very High Speed Integrated Circuit               |

| WISN   | Wireless Image Sensor Network                    |

| WMSN   | Wireless Multimedia Sensor Network               |

| WSN    | Wireless Sensor Network                          |

| WVSN   | Wireless Visual Sensor Network                   |

| XOR    | Exclusive-OR                                     |

|        |                                                  |

# CHAPTER 1 INTRODUCTION

Wireless Sensor Networks (WSNs) consists of many tiny sensor nodes that are capable of sensing the environment conditions, process the sensed data and send the data to the sink. At the sink, the received data will be displayed and analyzed either by computer(s) or human being(s). With these capabilities, the WSNs has a wide range of applications such as health, military and security [1]. The rapid deployment, self-organisation and fault tolerance characteristic of sensor networks, make them very important in military command, control, communications, reconnaissance and targeting systems [2].

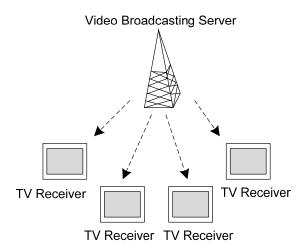

With advances of image sensor technology, many products are now embedded with low-powered image sensors, such as cellular phones, computers, toys and robots. At the same time, recent development in WSNs and distributed processing have promoted the use of image sensors for the network that resulted the development of Wireless Visual Sensor Networks (WVSNs) [3], where sometimes it is referred to as Visual Sensor Networks (VSNs) [4]. The WVSNs provides a broad range of applications such as remote and distributed video-based surveillance systems that collect visual data from a network with smart distributed image sensor nodes. These systems can be connected to the Internet which allow authorized Internet users to do remote visiting interesting locations (i.e. virtual reality), monitoring the environment, surveillance of sensitive headquarters and industrial process control [5] [6].

However, most of the WSNs applications have low bandwidth demands with delay tolerant and they measure the physical environment conditions such as pressure, humidity, and temperature. Once the sensor nodes are deployed, they are usually battery driven and operated with sacred energy source [7]. Furthermore, these sensor nodes are required to operate for months or years since battery replacement is not recommended for networks with thousands of distributed physically embedded nodes. The introduction of image sensors to WSNs generates large amount of image data into the widely distributed visual sensor nodes. Consequently, this requires larger network bandwidth usage thus higher energy consumption is required for transmitting the large amount of image data [3].

The thesis presents a novel low complexity Discrete Wavelet Transform (DWT) Cauchy Reed Solomon (CRS) Minimal Instruction Set Computer (MISC) architecture that performs data compression, data encryption and data correction in a single architecture. The developed DWT CRS MISC processor was programmed to perform DWT image compression to decrease the image data thus subsequently reduces the network bandwidth. Later on, the programmed MISC processor performs the CRS coding scheme onto the reduced image data to provide secure and reliable data transmission. With the CRS encoded data, the base-station can correct a small number of errors occurred onto the received image data thus it requires less number of retransmission. The developed new DWT CRS MISC architecture was implemented into a Field Programmable Gate Array (FPGA) to demonstrate its feasibility for use in the WVSNs.

## **1.1 PROBLEM STATEMENT**

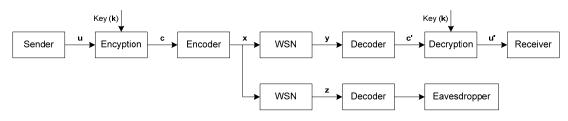

Transmitting large amount of image data requires longer transmission time that increases the power consumption of transceiver thus reduces the life span of sensor nodes [8]. Therefore, introducing compression scheme into the WVSNs to reduce the amount image data to be transmitted has a great potential in reducing communication energy costs and thus increasing the sensor nodes operating lifespan [9]. Meanwhile, image data transmitted across the wireless communication channel are prone to security threat such as eavesdropping [10]. Adversary can intercept the unencrypted data transmission in the WVSNs and learn any important information from the intercepted data. In the meantime, it requires high retransmission rate when the WVSNs operates in noisy environment, whereby the base-station often requests the

sensor nodes to retransmit the received error image data. Consequently, this increases the power consumption of the transceiver which may reduce the operating lifetime of the sensor nodes [5]. As a result, there is a need to develop a low complexity image processing system to address the aforementioned issues in the resource constrained WVSNs.

The first issue to be addressed is to have an image processing system that reduces large amount of image data produced by visual sensor, before transmitting the data across the WVSNs. The cost of transmitting 1kB data (in terms of energy) is comparable to the same amount of energy used by a general-purpose processor executes 3 million instructions [11]. As a result, this provides improvement by reducing the power consumption for transmitting lower amount of image data [12].

Second issue to be resolved is the security protection on the image data that are to be transmitted across wireless channel. Sensitive data such as surveillance image that are used for military purposes, especially in providing information on vital battlefield telemetry or monitoring [13], are exposed to security threats across the wireless communication channel. These image data transmitted across the WVSNs are prone to adversary attacks and eavesdrops on the wireless communication network [14].

Lastly, the compressed and encrypted image data are usually prone to error while transmitting the data across the noisy wireless communication channel. Although the WVSNs do have error correction capabilities at the link layer [15], it is still not sufficient because unreliable data transmission will results in incorrect encrypted data received by the base-station (sink) or by remote user through the Internet. Thus decrypting correct plaintext is not possible with the use of these corrupted ciphertext (encrypted data). With these three aforementioned issues, there is a need to develop a novel solution (architecture) that could resolve the issues. The novel architecture need to be of low hardware utilisation, such that low power consumption is achieved.

#### **1.2 SYSTEM OVERVIEW**

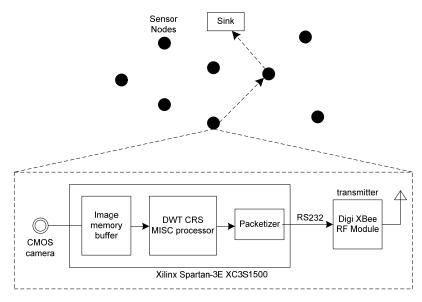

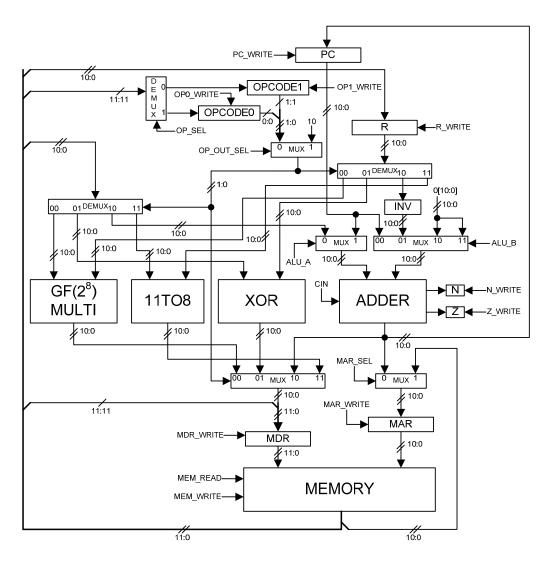

An image processing system for WVSNs was developed to resolve the aforementioned issues in Section 1.1. As shown in Figure 1, the final developed image processing system consists of a novel DWT CRS MISC architecture. The proposed MISC architecture has the capability of reducing the large amount of image data, and at the same time provides data security and reliable data transmission in a single architecture.

Figure 1 Developed image processing system with DWT CRS MISC.

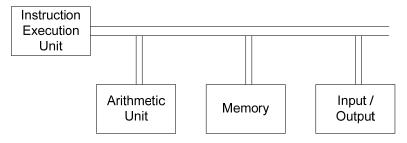

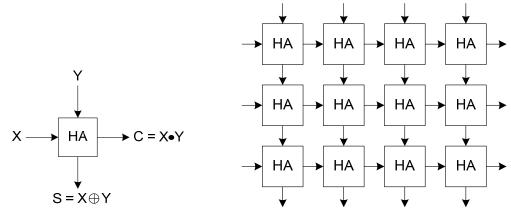

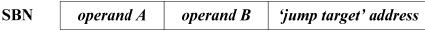

Modifications were made onto the Subtract and Branch if Negative (SBN) architecture [16] such that it can be further developed into DWT CRS MISC architecture. The additional functional blocks were added into the modified SBN architecture, which are Galois Field (GF) [17] Multiplier (MULT) block, XOR block and 11TO8 block. By adding these functional blocks, the SBN (i.e. One Instruction Set Computer [18]) was developed into a MISC architecture that consists of a minimal number of instructions.

The developed DWT CRS MISC architecture consists 4 programme instructions, which are SBN, GF MULT, XOR and 11TO8 instructions. Based on these programme instructions, the DWT CRS MISC was programmed to perform Lifting Scheme DWT image compression [19] to reduce the image data and CRS encoding (encryption) [20] onto the selected DWT coefficients to provide secure and reliable data transmission. Therefore, the developed system reduces the amount of image data that are required to be transferred across the WVSNs and thus decreases the network bandwidth. At the same time, the compressed image data were encoded using the CRS coding scheme [20] to provide Forward Error Correction (FEC) capability such that the base-station can correct the errors that occurred onto the received image data. This reduces the number of request for retransmission of incorrect received data by the base-station. Thus less amount of energy is consumed by the sensor nodes since lower data retransmission rate is required. Besides, the CRS encoded image data are also encrypted such that any adversary cannot eavesdrop and extract information from the intercepted the data.

## **1.3 RESEARCH AIM AND OBJECTIVES**

The aim of research works presented in this thesis is to develop a low complexity joint compression, forward error correction and encryption processing framework for resource constrained WVSNs. The main objectives of the research works are listed as follows:

- Develop an alternative processing approach for the Reed Solomon (RS) encoding scheme to be used in the WVSNs such that the base station can correct the errors that occurred onto the RS encoded image data. Therefore, less retransmission of image data are required from the sensor nodes when incorrect data are received.

- Further improvement on the RS processing approach such that the CRS encoding scheme can be integrated into the WVSNs. The CRS processing approach allows encryption and FEC to be performed onto the image data transmitted from the sensor nodes.

- 3. Develop a new processing approach for combined DWT filtering and CRS encoding scheme to be used in the WVSNs such that image compression, encryption and FEC can be performed onto the image data transmitted from the sensor nodes.

- 4. Design of a custom visual sensor platform with the DWT CRS MISC architecture onto a reconfigurable hardware to verify the feasibility of implementing the developed low complexity joint compression, encryption and FEC image processing system for image data transmitted from the sensor nodes.

## **1.4 SIGNIFICANCE OF RESEARCH**

A new low complexity RS MISC architecture was developed for use in WVSNs to provide reliable data transmission. The developed RS MISC architecture has lower hardware utilisations (61.2% less Slices) as compared to the traditional RS Linear Feedback Shift Register (LFSR) encoder circuit [17]. Both the RS MISC and RS LFSR encoder were implemented in the Xilinx Spartan-3L FPGA. Meanwhile, the power consumption of developed RS MISC architecture is also reduced by 17.4%. Because the developed RS MISC architecture has only one GF Multiplier block. The RS MISC does not encode the data as fast as the RS LFSR, which has many parallel GF Multiplier blocks. However, for WVSNs application, the interval between image transmissions to sink may be in hours, days, weeks or months. Therefore, the use of RS MISC in the WVSNs is justifiable as achieving low power consumption is of the utmost importance. With RS MISC, it provides error protections onto the image data such that less request for retransmission is required. With lower retransmission rate, less amount of energy is consumed by the sensor nodes.

Further improvement was made to the RS MISC architecture, whereby a CRS MISC architecture was developed to provide both data security and data reliability. With the CRS MISC, the encoded image data are protected from any eavesdropping and errors while the data are transmitted across the wireless communication network.

In comparison to the existing ECBC method [21], which were used to provide security and reliable data transmission, the CRS MISC architecture requires less than 90.8% of the hardware utilisations that were required by the ECBC. The existing ECBC method was developed in Xilinx Spartan-3E FPGA, whereby the Spartan-3E FPGA builds on the Spartan-3 family of FPGA [22]. The contents of this part of research forms part of the work published in [23].

Further development was made onto the CRS MISC architecture such that image compression capability was incorporated in the architecture. Therefore, a DWT CRS MISC architecture was developed and proposed for use in WVSNs to reduce size of the image data, provide data security and data reliability. With the DWT CRS MISC, the DWT image compression is performed first and followed by CRS coding scheme that encodes (encrypt) the compressed image data. To the knowledge of the author, the DWT CRS MISC architecture was the only jointed compression, encryption and error correction scheme processing framework for WVSNs that was ever developed. In comparison to the literature in [24], an existing simulation study was performed to show the feasibility of using the existing SAC (jointed compression and encryption techniques) combined with Multiple-Input Turbo (MIT) error correcting coding technique for WSNs. However, the SAC combined with MIT code technique only process scalar data (eg. temperature) that allowed occasional losses of sensor measurements and this technique is impractical for WVSNs that has larger data traffic [5].

By considering existing methods, with the lowest hardware utilisations, both CL-DCT compression [25] and ECBC [21] requires 1060 Slices (Xilinx Spartan-3L) and 1,691 Slices (Xilinx Spartan-3E) respectively. The developed DWT CRS MISC architecture only requires 144 Slices (Xilinx Spartan-3L) and 129 Slices (Xilinx Spartan-3E) respectively, which is comparatively a very low amount of hardware utilisations. Note that the CL-DCT, ECBC and DWT CRS MISC were implemented in the Xilinx Spartan-3 family of FPGA. Therefore, the developed DWT CRS MISC performs both DWT image compression and CRS encoding in a single architecture such that low hardware complexity of the proposed image processing system was achieved.

## **1.5 THESIS ORGANISATION**

This thesis presents the concepts, approaches and methods that are involved to develop the new low complexity joint compression, FEC and encryption processing approach for WVSNs with adhere to the constrained hardware resources. The thesis organisations are as follow:

#### **Chapter 1 – Introduction**

For this chapter, it gives the introduction on the related area of research and provides the motivations of this research. From the problem statements, the listed problems were addressed by the proposed image processing system stated in this chapter.

#### **Chapter 2 – Literature Review**

This chapter reviews on the existing image processing system in WVSNs. The reviewed image processing systems are those that provide data compression, data encryption and data reliability. The chapter also provides the necessary details on the Galois Field, Lifting Scheme DWT and CRS coding scheme that are required by the MISC architectures developed.

#### **Chapter 3 – DWT CRS Minimal Instruction Set Computer Architecture**

The chapter explains the process of developing the new DWT CRS MISC architecture. The detail explanations on the DWT CRS MISC architecture are presented in this chapter. Besides, the algorithm to perform the joint processing schemes framework is discussed. As such, the written programme instructions are listed out and the number of clock cycles required to run these instructions are estimated.

#### **Chapter 4 – Results and Discussions**

The results and simulation waveforms for the developed DWT CRS MISC architecture are discussed in this chapter. Analysis shows the improvement of data transmission time, reconstructed image quality for errors occurred on compress image data and security level of the encoded image data are presented in this chapter.

#### **Chapter 5 – Hardware Implementations**

The focus in this chapter is to develop a custom Wireless Visual Sensor Platform. This is done by integrating the proposed DWT CRS MISC architecture with a wireless transceiver such that to verify its feasibility for use in the WVSNs.

#### **Chapter 6 – Conclusions and Future Works**

The last chapter of the thesis provides conclusion on the research works and offers suggestions on future works that can be performed through the use of the newly developed DWT CRS MISC architecture discussed from previous chapters.

# **CHAPTER 2**

# LITERATURE REVIEW

Chapter 2 reviews related existing research works that were performed by the research community. First, a brief introduction on the DWT was given in Section 2.1. This includes the reason of using DWT over CWT are also discussed. Secondly, Section 2.2 provides a brief introduction on the Reduced Instruction Set Computer (RISC) architecture. The DWT CRS MISC architecture was developed based on the Subtract and Branch if Negative (SBN) architecture. Section 2.3 discusses on the Wireless Visual Sensor Networks (WVSN) and the existing WVSN platforms that are available in the literature. Section 2.4 reviews the existing compression techniques that were used in Wireless Sensor Networks (WSNs). Section 2.5 discusses on the available proposed FEC encoding scheme for WSNs. Section 2.6 reviews on the existing security schemes for WSNs. Section 2.7 reviews on the combined schemes that provides data compression, secure and reliable data transmissions in WSNs.

## 2.1 DISCRETE WAVELET TRANSFORM

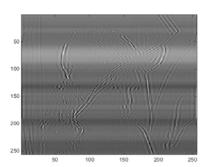

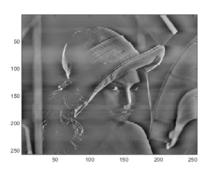

Discrete Wavelet Transform (DWT) is known to be a wavelet transform that processes and represents a continuous-time signal [26]. The DWT is also used as a means to extract relevant features from signals [27], images [28] and video [29]. In contrast to the DWT, the Continuous Wavelet Transform (CWT) compares the analysed signals (images) with many shifted and stretched (scaled) wavelet. The CWT uses only 1 filter and produces a large amount of wavelet coefficients. As a result, the CWT is considered to produce more redundant wavelet coefficients [30] and this does

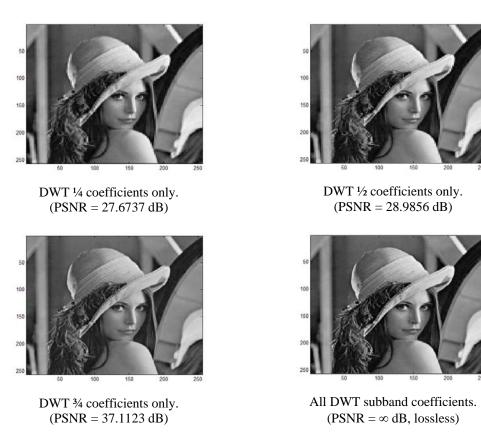

not reduce the amount of data representing the signals (mainly used in signal processing). Whereas for the DWT, it uses both high pass filter and low pass filter to analyse the signals (images), with each filter's outputs are down-sampled by 2 [31]. As a result of down-sampling, the DWT high pass filter produces Detail DWT coefficients and the DWT low pass filter produces Approximate DWT coefficients, with each of these DWT coefficients are half the length of the original signals. The Detail DWT coefficients represent the high frequency of the signals (or represent the edges in images) and the Approximate DWT coefficients represent the Low frequency of the signals (or represent an approximation of the images). With half the amount of data to represent the original signals (images), reconstruction of signals (images) is made possible with the use of Approximate DWT coefficients only. To reduce the amount of data representing the signals (images), the DWT was used for image compression because it has the advantages which overcome the wavelet redundancy issues encountered in CWT [32]. There are two different approaches of DWT, one is through the use of traditional filter bank [26] and another will be lifting scheme [19] [33].

#### 2.1.1 Recent DWT and CWT Research Works

In [34], image compression integrated with selective encryption was introduced. The authors proposed the use of combined Embedded Zerotrees of Wavelet (EZW) transforms [35] and random shuffle or permute the wavelet Spatial Orientation Trees (SOTs). The DWT is used to decompose the image data and then a randomized key is used to shuffle the wavelet trees (SOTs). Later, it was found that this proposed method, when used as the only security mechanism, is insure against a chosen plaintext attack [36]. With the knowledge on wavelet trees configurations, an adversary would be able to predict the correct size of image and number level of decompositions. The intercepted cipher-text will leak information on the randomized key used to shuffle the SOTs. Therefore, this allows the adversary to decipher the encrypted compressed image data.

Later on, both CWT and DWT were used for analyzing non-stationary and quick changing Partial Discharge (PDs) signals [37]. The PDs measurement is a method to diagnose the insulating system condition of High Voltage (HV) electrical equipment. With the use of CWT, it calculates the wavelet coefficients at every

possible scale and along every time instant. This result in having a wavelet details coefficients distribution throughout the entire time-scale view. For the de-noising process, a model-based DWT simulator is used to filter the corrupted PDs signals. With noise disturbance has been thinned out, the unchanged waveform of PDs can then be extracted [37].

A study and analysis on the usage of these techniques - Principle Component Analysis (PCA), Discrete Cosine Transform (DCT) and DWT, to perform the image fusion (processing) [38]. Image fusion is used to improve the quality of information from a set of images. From this study, the authors found that the use of DWT technique itself in fusing the images, does provide a significant fused image quality of 78.9555 dB. Compared to both PCA and DCT techniques, the fused image quality obtained were only 30.7729 dB and 30.9663 dB respectively.

The used of CWT for power limited wearable Electroencephalography (EEG) was introduced by the literature [39]. The EEG is a device that measures the voltage of electrodes placed between the scalp. Usually the voltages recorded are in between peak-to-peak voltage of 1 -  $150\mu$ V over a bandwidth frequency of 1-70 Hz. In this research work, the CWT will be used to perform physiological (analogue) signal processing. As a result, a low power g<sub>m</sub>C Low Power CWT (LPCWT) filter was developed using 0.35µm CMOS technology process. The developed LPCWT filter is capable in reducing analogue domain signals, such that it lowers the total system power consumption of EEG [39].

Meanwhile, the surface Electrocardiogram (ECG) is a non-invasive tool for diagnosis of many heart diseases. In order to detect abnormal cardiac events, continuous electrical recording of heart behaviour is performed. In order to extract the relevant information from ECG signal, the literature [40] proposed a method in segmenting and analyzing the waveforms of ECG signal. For segmentation, multiscale CWT is used to detect different ECG waveforms. Later on, the PCA is used in detecting and locating defects. It is done by modelling the behaviour of the biological process in a normal state. Then the PCA compares the observed behaviour with the normal state behaviour. This is used to detect any defects that may occur [40]. Next, the authors in [41] had proposed and designed a CWT-based multi-functional processor. The CWT-based processor is suitable for long-term real-time ECG signal analysis and abnormal cardiac event detection. Based on reported results, it was concluded that the proposed architecture is feasible to use in continuous ECG monitoring system [41].

Table 1 summarizes the recent DWT and CWT research works that were mentioned in this section. It can be seen that the CWT transform was mainly used in signal processing. As mentioned in [42], the main usage of CWT is for analysis of signals (images). For images, the CWT is usually used to detect specific features hierarchical structure, edges, contours etc. The CWT are very efficient in detecting specific features in signals or images [42]. As oppose to CWT, the DWT is mainly used when data compression is considered to be essential. The DWT produces impressive data compression rates that are very useful in image processing [42].

| Authors                                               | Year | Research<br>Works                                                           | Type of<br>Wavelet | Summary                                                                                                                                               | Applications         |  |

|-------------------------------------------------------|------|-----------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Salama, Paul;<br>King, Brian [34]                     | 2005 | Efficient Secure<br>Image<br>Transmission                                   | EZW<br>(DWT)       | DWT image compression                                                                                                                                 | Image<br>Processing  |  |

| Candela, R.;<br>Romano, E.;<br>Romano, P. [37]        | 2009 | Combined CWT-<br>DWT Method<br>using Model-based<br>Design Simulator        | CWT /<br>DWT       | Filtering onto online<br>partial discharges signals<br>measurement systems,<br>after analysis CWT<br>coefficient, with model-<br>based DWT simulator. | Signal<br>Processing |  |

| Assegie, Samuel;<br>Salama, Paul;<br>King, Brian [36] | 2010 | Shuffling DWT v                                                             |                    | Proved that the research<br>work [34] is not strong<br>against plaintext attack.                                                                      | Image<br>Processing  |  |

| Casson, A. J.;<br>Rodriguez-<br>Villegas, E. [39]     | 2011 | 60pW <i>g<sub>m</sub>C</i> CWT<br>Circuit                                   | CWT                | Portable EEG systems<br>with 7 <sup>th</sup> order CWT band<br>pass filter for analogue<br>physiological signals                                      | Signal<br>Processing |  |