# Single-Photon Avalanche Diodes in a 0.16 $\mu$ m BCD Technology With Sharp Timing Response and Red-Enhanced Sensitivity

Mirko Sanzaro, *Member, IEEE*, Paolo Gattari, Federica Villa, *Member, IEEE*, Alberto Tosi, *Member, IEEE*, Giuseppe Croce, *Member, IEEE*, and Franco Zappa, *Senior Member, IEEE*

Abstract—CMOS single-photon avalanche diodes (SPADs) have recently become an emerging imaging technology for applications requiring high sensitivity and high frame-rate in the visible and near-infrared range. However, a higher photon detection efficiency (PDE), particularly in the 700–950 nm range, is highly desirable for many growing markets, such as eye-safe three-dimensional imaging (LIDAR). In this paper, we report the design and characterization of SPADs fabricated in a 0.16  $\mu m$  BCD (Bipolar-CMOS-DMOS) technology. The overall detection performance is among the best reported in the literature: 1) PDE of 60% at 500 nm wavelength and still 12% at 800 nm; 2) very low dark count rate of <0.2 cps/ $\mu m^2$  (in counts per second per unit area); 3) <1% afterpulsing probability with 50 ns dead-time; and 4) temporal response with 30 ps full width at half-maximum and less than 50 ps diffusion tail time constant.

*Index Terms*—Photon counting, photon timing, single-photon avalanche diodes (SPADs), time-correlated single-photon counting (TCSPC), LIDAR, three-dimensional (3-D) ranging, FLIM.

# I. INTRODUCTION

SILICON Single-Photon Avalanche Diodes (SPADs) fabricated with custom epitaxial technologies [1], [2] provide best-in-class performance in terms of photon detection efficiency (PDE), dark-count rate (DCR) and timing response. However, custom fabrication technologies are expensive and, owing to their inherently limited system integrability, are best suited for small (up to hundreds of pixels [3]) SPAD arrays. As a consequence, the increasing demand for large SPAD arrays in many applications, such as fluorescence lifetime imaging microscopy (FLIM) [4]–[9] and 3-D ranging and imaging (LIDAR) [10]–[16], has driven the research toward the fabrication of SPADs in conventional CMOS processes, aiming at producing reliable single-chip detection systems at low cost and with high reproducibility.

The breakthrough occurred in early 2000's, when SPADs were successfully demonstrated using a high-voltage 0.8-μm CMOS technology [17], [18]. This paved the way for the fabrication of large ( $>10^4$  pixels [19]–[21]) SPAD imagers. However, the trend toward deep-submicron (DSM) CMOS technologies to attain either higher system integration, higher spatial resolution or higher fill factor (i.e., the active-to-total area ratio of a single pixel) is hindered [22]. A major concern with DSM technologies is that MOSFET scaling leads to higher doping levels and curtailed annealing steps, which in turn give rise to thinner depletion layers and higher defects concentration [3]. An attracting alternative to enhance the device performance is given by smart power technologies, such as BCD (Bipolar-CMOS-DMOS), since technological features required by high-voltage devices are also favorable to high-performance SPADs [1], [22]. Furthermore, smart power technologies are based on the concept of modularity [23], [24], i.e., additional implants for optional devices can be added to a basic process flow-chart.

In this paper, we present the design criteria and the experimental characterization of the SPADs we developed in the 0.16- $\mu$ m STMicroelectronics' BCD8sP technology [25]. These BCD SPADs show enhanced PDE in the near-infrared (NIR) compared to standard CMOS SPADs, coupled with state-of-theart DCRs and timing response, and maintains full compatibility with Bipolar, CMOS and DMOS on-chip circuitry, thus being suitable for SPAD imaging arrays.

## II. DEVICE DESCRIPTION

A constraint in SPAD arrays is the need to isolate SPAD detectors from CMOS circuitry and to limit the collection of minority carriers from the neutral volume below their space charge region. This is usually achieved by enclosing the SPAD in an n-well diffused through the p-type substrate and reverse-biasing the resulting (cathode-substrate) p-n junction. A low-doped ( $<10^{17}$  cm  $^3$ ) and deep n-type well is fundamental to achieve good photon-counting performance, i.e., high PDE and low DCR. The reason being that a wide space charge region (1–2  $\mu$ m) increases the quantum efficiency, reduces field-enhanced carrier generation [26] and avoids band-to-band tunneling [27].

For reducing the diffusion tail, the n-well neutral region underneath the space charge should be thin and lightly doped [28].

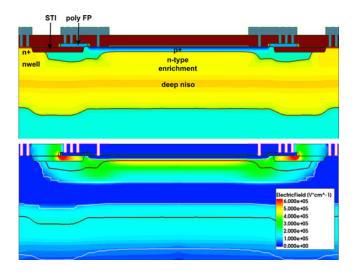

Fig. 1. Cross section of a 'shallow' BCD SPAD from wafer A with simulated net doping concentration (top) and electric field distribution at 5 V excess bias (bottom).

On the other hand, as demonstrated in [29], for achieving a narrow timing response full-width at half maximum (FWHM) the n-well doping should be high enough to guarantee a low resistivity path to the side cathode contact.

In order to attain low doping concentration within the space charge region coupled with a thin ( $\sim 1~\mu m$ ) and low-resistivity ( $< 0.1~\Omega \cdot cm$ ) buried layer, we designed a retrograde custom implant, referred in the following as *deep n-iso*. The SPAD junction is enclosed in a pocket delimited underneath by the deep n-iso and laterally by a heavily doped BCD8sP n-well, which overlaps the deep n-iso and provides a low resistance path to the side cathode contact. We sized such a double n-type well pocket to guarantee 50 V isolation toward the substrate.

## A. 'Shallow' SPADs

Fig. 1 shows the simulated cross-section of a p<sup>+</sup>/n junction BCD SPAD. In this 'virtual' guard ring structure, a dedicated Phosphorus implant, referred in the following as *enrichment*, is employed to define the avalanche region. Indeed, a fully depleted p-type guard ring is formed implicitly, owing to the residual epitaxial layer doping. The p<sup>+</sup> anode and active masks extend laterally 1–2  $\mu$ m beyond the enrichment mask, thus leaving a gap between the shallow trench isolation (STI) and the avalanche region edge. Being two order of magnitude higher than the mean free path of carriers, the gap prevents the interface states at the SiO<sub>2</sub>-silicon boundary from affecting DCR and afterpulsing [30]. The resulting annular space is used as the silicidized anode ohmic contact, while a salicide (self-aligned silicide) blocking mask prevents salicidation in the SPAD avalanche region and forms a pinhole shielding the guard ring from light. Finally, a polysilicon field-plate, kept at the same anode potential, avoids edge breakdown.

Through the custom tailoring of the enrichment doping profile, a suitable shaping of the electric field in the space charge region can be achieved. However, a few iterations may be needed to identify the best electric field distribution to attain the desired

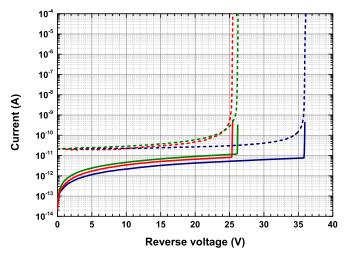

Fig. 2. Typical dark and illuminated I-V characteristics of 30- $\mu$ m BCD SPADs from wafer A, B and C at 300 K. The absence of any dark current multiplication up to breakdown suggests that perimeter leakage dominates the dark current.

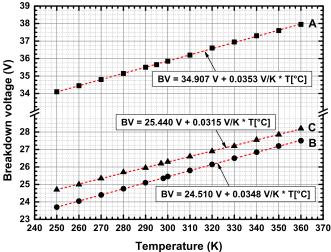

trade-off between device properties. In this work we present two designs, a first one (wafer A) with a breakdown voltage of 35.8 V at room temperature (see Fig. 2) and a second split lot (wafer B) with a 25.4 V breakdown, as a result of the higher dose and lower energy of the enrichment implant. According to simulations, performed with the Synopsys Sentaurus TCAD suite [31], [32] and STMicroelectronics process calibration data, for a given excess bias voltage (i.e., the voltage above breakdown) the electric field distribution has a ( $\sim$ 10%) lower and broader peak in wafer A, while the space charge width differs by less than 100 nm, since the deep n-iso stops the electric field.

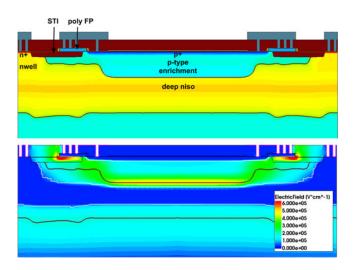

#### B. 'Deep' SPADs

An intrinsic limitation of CMOS SPADs, which are typically one-sided p+/n junctions, arises from the fact that NIR photons are primarily absorbed in the n-type side of the depletion layer. Therefore, avalanches are primarily initiated by holes [1], which have a lower avalanche triggering probability compared to electrons in Silicon [33].

A promising solution is to implant high energy Boron ions instead of low energy Phosphorus ones into the enrichment mask opening, as shown in Fig. 3, thus creating a 'deep' p/n+ junction. This way, the avalanche is primarily initiated by minority electrons moving toward the buried multiplication region, leading to a higher PDE [34].

For the split lot C, we sized a Boron enrichment implant for achieving nearly the same electric field peak and depletion layer width as in wafer B, thus making relative performance comparison straightforward.

#### III. PHOTON DETECTION EFFICIENCY

For measuring the PDE, i.e., the probability of detecting an incoming photon, we monitored the light from a broadband and stable Quartz Tungsten Halogen (QTH) lamp, attenuated by means of optical neutral density filters and passed through a monochromator, by means of a large-diameter (>1 cm)

Fig. 3. TCAD process (top) and device (bottom) simulation of a "deep" BCD SPAD (wafer C) at 5 V excess bias.

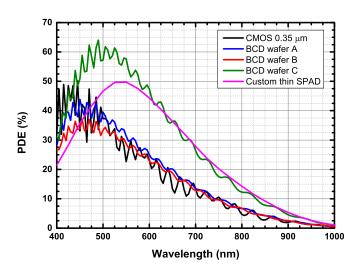

Fig. 4. PDE versus wavelength (at 5 nm steps) of 30  $\mu$ m-diameter BCD SPAD devices, operated at 5 V excess bias, compared to a 0.35  $\mu$ m CMOS SPAD [35] and of a custom Silicon SPAD [36], in the same setup.

calibrated photodiode. The light from the monochromator is fed to an integrating sphere to obtain a spatially uniform photon flux over the SPAD. The PDE is calculated as the rate of net photon detections (i.e., after subtracting the DCR), divided by the photon arrival rate through the SPAD avalanche region, i.e., the area defined by the enrichment implant.

Fig. 4 shows the PDE as a function of wavelength of all the split lots described so far. All detectors were held at room temperature (300 K) and biased 5 V above their breakdown voltage. The PDE of the state-of-the-art 0.35  $\mu$ m CMOS SPAD of Ref. [35] and the Silicon SPAD of [36], fabricated using a fully custom planar technology, have been measured with the same setup and are reported in Fig. 4 as benchmarks.

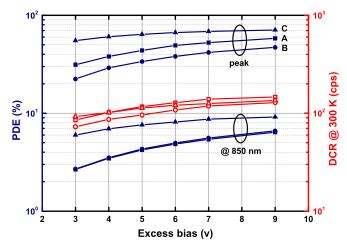

Shallow SPADs from wafers A and B reach PDE values that are comparable to the device of [35] in the 500–1000 nm range, but lower than those achievable with a fully custom SPAD. The PDE peaks are 36% and 43% at 450 nm and the PDE is 7% at 800 nm. The interference ringing, due to the multiple dielectric

Fig. 5. PDE and DCR as a function of the excess bias for 'shallow' (wafers A and B) and 'deep' (wafer C) BCD SPADs of 30  $\mu$ m-diameter.

interfaces in the back end of line (BEoL), is significantly lower than that of [35], thanks to the passivation that was selectively thinned over the SPADs avalanche region.

As expected, deep SPADs (wafer C) outperform the shallow ones (wafers A and B), owing to the higher avalanche triggering probability of electrons with respect to holes. The PDE peak shifts from 450 nm to 490 nm and is above 60%. The PDE is very good in the NIR, being approximately 12% at 800 nm, 8% at 850 nm and still 4% at 900 nm, and even better than custom SPADs in the 400–600 nm range. The reason being that most high-energy photons are absorbed in the upper neutral region of custom SPADs, and photo-generated holes (collected by diffusion) trigger the avalanche [34]. On the other hand, in wafer C SPADs the avalanche is primarily triggered by electrons regardless of the wavelength, leading to a higher PDE at short wavelengths.

Fig. 5 shows the PDE and DCR (see Section IV) dependence on excess bias of 30  $\mu$ m-diameter SPADs at 300 K. At 9 V excess bias the PDE of the deep SPAD is 71% at 490 nm wavelength and 9% at 850 nm.

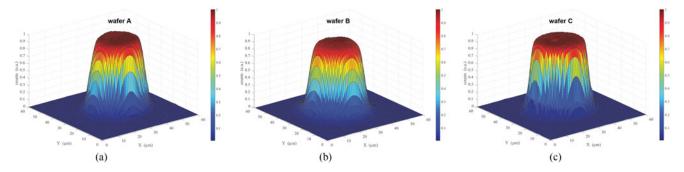

An important issue in SPAD fabrication is the electric field uniformity that leads to uniform PDE and jitter. In order to assess such uniformities, we focused an 850-nm laser into a small spot ( $\sim$ 5  $\mu$ m-diameter), we performed an x-y scan at 1  $\mu$ m steps across the detector, and measured the avalanches ignition rate at each position. After checking the laser power stability, we obtained the relative PDE maps shown in Fig. 6. The PDE is quite uniform over the sensitive area and it correctly drops outside its edges, with no detectable premature edge breakdown. The FWHM of the PDE map is 29, 30 and 31  $\mu$ m for wafer A, B and C, respectively. The normalized PDE drops from 0.9 to 0.1 over a length of 6 and 7 and 3  $\mu$ m for wafer A, B and C respectively. The reason of the sharper drop of the deep SPAD is twofold: i) the avalanche triggering probability of electrons increases faster with the electric field and is closer to saturation at 5 V excess bias (see Fig. 5); ii) the polysilicon field plate that avoids edge breakdown smooths the electric field transitions of shallow SPADs.

Fig. 6. Normalized PDE maps of a 30  $\mu$ m SPAD from wafers A, B and C operated at 5 V excess bias, measured by scanning a light spot (850 nm wavelength,  $\sim$ 5  $\mu$ m-diameter) across the detector with 1  $\mu$ m steps. The measured FWHM is 29, 30 and 31  $\mu$ m for wafer A, B and C, respectively.

Fig. 7. Temperature dependence of DCR for  $30\,\mu\mathrm{m}\text{-}\mathrm{diameter}$  SPADs operated at 5 V excess bias.

Fig. 8. Breakdown voltage vs. temperature: experimental data and linear fitting for 'shallow' (wafers A and B) and 'deep' (wafer C) SPADs.

#### IV. DARK COUNT RATE

The generation of carriers within the space charge region, due to either Shockley-Read-Hall processes [26] or trap-assisted tunneling (TAT) [27], gives rise to the DCR, i.e., the average avalanche ignition rate in the absence of illumination, whose Poissonian fluctuations represents the primary noise source of SPADs. The electric field distribution of all the split lots was designed to reduce the weight of the tunneling contribution. As shown in Fig. 5, the DCR dependence on the excess bias tracks the increase and saturation of the avalanche triggering probability (as the PDE does) up to  $V_{\rm EX}=9$  V, demonstrating that field-assisted carrier generation mechanisms are negligible at 300 K for all detectors.

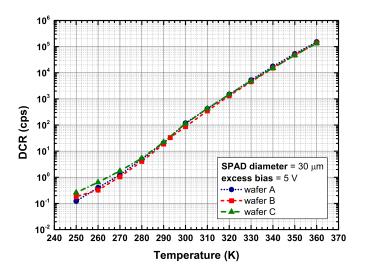

Fig. 7 shows the temperature dependence of DCR of 30  $\mu$ m-diameter SPADs. All SPADs were operated by a monolithically integrated quenching circuit having the same topology described in [37]. Measurements were performed at a constant excess bias voltage 5 V adjusting the cathode bias for compensating the breakdown drift over temperature (see Fig. 8). In order to rule out afterpulsing (see Section V) a dead-time of approximately 0.25  $\mu$ s was enforced by the active quenching circuit after each avalanche ignition.

For all the wafers, the DCR increases from 1 to  $10^5$  cps over the temperature range from 0 to 90 °C. The DCR is almost the same among the three wafers, as a direct consequence of the BCD8sP high reproducibility. The deep SPAD (wafer C) exhibits a change in the slope of the curve at about 0 °C. Conversely, tunneling generation is negligible for the shallow SPAD from wafer A and is barely visible at -20 °C for the shallow SPAD from wafer B.

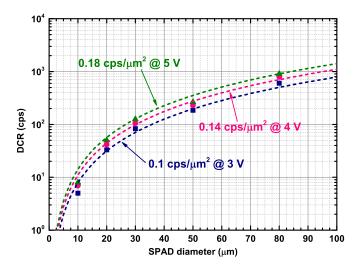

Fig. 9 shows the DCR at room temperature vs. SPAD diameter at 3 V, 4 V and 5 V excess bias, respectively; SPAD samples are from wafer A. The linear dependence of DCR with the SPAD area (i.e., the quadratic dependence on diameter) is a clear signature that interface states at STI SiO<sub>2</sub>–silicon boundary do not significantly affect the DCR [30].

## V. AFTERPULSING

During an avalanche, few carriers may get trapped by deep levels and released with a statistical delay, eventually igniting a correlated 'afterpulse' when the SPAD is re-armed. Since each afterpulse is correlated to the avalanche ignition that populated the deep levels, afterpulses have a strong correlation to the signal as well, thus causing non-linear distortion in photon-counting

Fig. 9. Room temperature DCR vs. SPAD diameter at different excess bias, for wafer A, together with a quadratic fitting. The DCR per unit area is 0.1 cps/ $\mu$ m<sup>2</sup> at  $V_{\rm EX}=3\,V$ , 0.14 cps/ $\mu$ m<sup>2</sup> at 4 V and 0.18 cps/ $\mu$ m<sup>2</sup> at 5 V.

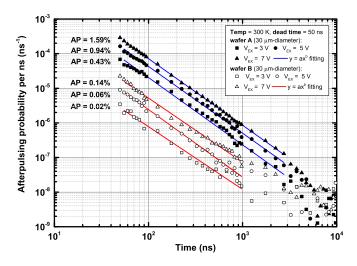

Fig. 10. Afterpulsing probability density for 30  $\mu$ m-diameter SPADs from wafers A and B, operated by an integrated active quencing circuit (AQC) with 50 ns hold-off at 3, 5 and 7 V of excess bias.

measurements. As a result, the afterpulsing probability has to be kept small, down to 1% or even lower, by enforcing a sufficiently long dead-time to allow nearly all trapped carriers to be emitted and swept from the multiplication region.

Figs. 10 and 11 show the afterpulsing probability density measured at room temperature on 30  $\mu$ m-diameter SPADs by using the time-correlated carrier counting (TCCC) technique [38]. Such a technique requires to measure the time intervals between two successive avalanche ignitions and to collect a histogram of a statistically significant number of repetitions (about  $10^7$  events in our measurements). The content of each histogram cell is normalized to the total number of repetitions and then is divided by the time-bin width in order to result in the probability distribution that describes the time between consecutive avalanche ignitions. Eventually, the afterpulsing probability density is obtained by subtracting the exponential decay due to the intrinsic DCR (measured at very long time-delays) from the distribution.

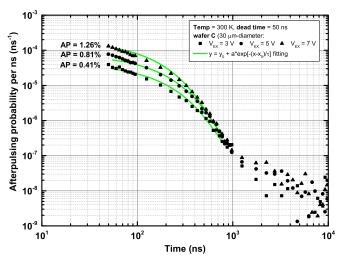

Fig. 11. Afterpulsing probability density for 30  $\mu$ m-diameter SPADs from wafers C, operated by an integrated active quenching circuit (AQC) with 50 ns hold-off at 3, 5 and 7 V of excess bias.

For the shallow SPADs shown in Fig. 10, the afterpulsing probability density decay is fitted quite well by a power-law temporal dependence, as recently proposed in [39] for InGaAs/InP SPADs. This is a clear signature that there is a broad and dense spectrum of trap levels, contrary to the common belief that just a few defect families are dominant. Conversely, measurements on wafer C with deep multiplication region shown in Fig. 11 clearly exhibit a dominant exponential decay. We believe that defect types and concentrations are similar in all processed wafers. However, in deep SPADs, traps capturing electrons (and not holes) are those primarily effective in triggering afterpulses. We can conclude that there is a dominant donor trap and many acceptor traps with close energies.

Figs. 10 and 11 also report the total afterpulsing probability, i.e., the integral of each afterpulsing probability density curve. As can be seen, at room temperature and with 50 ns dead-time, the afterpulsing probability is approximately 1% for 30  $\mu$ m-diameter SPADs from wafer A and C, and below 0.1% for wafer B SPADs, probably due to the higher electric field. These excellent results (see also Table I) are due to both the high cleanness of the BCD8sP STMicroelectronics foundry and the fast avalanche quenching performed by the monolithically integrated quenching circuit.

## VI. TIMING JITTER

In time-correlated single-photon counting (TCSPC) measurements, e.g., in FLIM and time-of-flight LiDAR, each photon is timed with respect to an exciting laser pulse. Hence, another important SPAD performance metric is the uncertainty in the identification of the photon arrival time, i.e., its timing jitter.

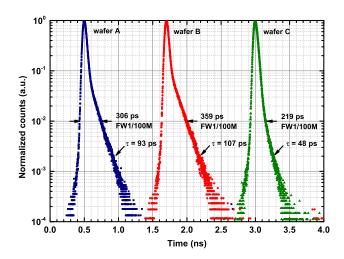

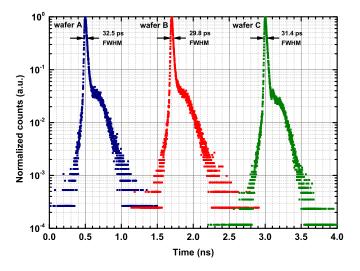

Fig. 12 shows, on a log scale and after amplitude normalization, the pulse of a gain-switching laser at 850 nm, which uniformly illuminates the entire SPAD area, acquired with the BCD SPADs described so far and a standard TCSPC setup. The laser has been attenuated so that the mean number of photons per pulse reaching the avalanche region is lower than 0.05.

TABLE I PERFORMANCE COMPARISON

|                 | Technology (nm) | Diameter (µm) | V <sub>EX</sub> /V <sub>BD</sub> (V) | Peak PDE (%)<br>@λ (nm) | PDE (%)<br>@850 nm | DCR/unit area (cps/ \(\mu\mathrm{m}^2\) | AP<br>(%)              | Jitter<br>(ps)          | Diffusion<br>tail (ps)     |

|-----------------|-----------------|---------------|--------------------------------------|-------------------------|--------------------|-----------------------------------------|------------------------|-------------------------|----------------------------|

| Ghioni [1]      | custom thin     | 50-200        | 5-10/30-35                           | 52-68 @ 550             | 12-15              | 0.4-1.6 <sup>a</sup>                    | 2 <sup>b</sup>         | 35 <sup>c</sup>         | 280-110 <sup>c</sup>       |

| Gulinatti [2]   | custom RE       | 50            | 20/45-55                             | 58 @ 650                | 28                 | $0.3^{d}$                               | N/A                    | 93 <sup>c</sup>         | $\sim 400^{\circ}$         |

| Villa [35]      | 350             | 10-500        | 2-6/25                               | 37-53 @ 450             | 2-4.5              | $0.05^{a}$                              | $\sim 1^{\rm e}$       | $\sim 90^{\mathrm{f}}$  | N/A <sup>f</sup>           |

| Leitner [45]    | 180             | 10            | 1-3.3/21                             | 35-47 @ 450             | N/A <sup>g</sup>   | 0.3-1.8 <sup>a</sup>                    | N/A                    | N/A                     | N/A                        |

| Veerappan [44]  | 180             | 12            | 2-10/23.5                            | 24-48 @ 480             | 3-8                | 0.16-176 <sup>a</sup>                   | 0.03-0.3 <sup>h</sup>  | 112-88 <sup>i</sup>     | $\sim \! 170^{\mathrm{i}}$ |

| Veerappan [46]  | 180             | 12            | 1-4/14                               | 23-47 @ 480             | 4-7                | 0.28-16 <sup>d</sup>                    | $0.2^{j}$              | 161-141 <sup>i</sup>    | $\sim 430^{i}$             |

| Veerappan [47]  | 180             | 12            | 1-12/25                              | 18-47@ 520              | 2-8                | $0.2-6^{d}$                             | 7.2 <sup>k</sup>       | 139-101 <sup>i</sup>    | N/A                        |

| Xu [48]         | 150             | 10            | 2-5/19                               | 24-32 @ 450             | 2-3.5              | 0.1-1                                   | 1-13 <sup>1</sup>      | 42 <sup>m</sup>         | $\sim 430^{m}$             |

| Lee [49]        | 140 (SOI)       | 12            | 0.5-3/11                             | 10-25 @ 500             | 2.5-7              | 0.9-260                                 | 1.7 <sup>n</sup>       | 65°                     | N/A                        |

| Richardson [50] | 130             | 8             | 0.6-1.4/14                           | 18-28 @ 500             | 3-5                | $0.24-0.6^{a}$                          | $0.02^{p}$             | $\sim 200^{\mathrm{q}}$ | N/A                        |

| Richardson [51] | 130             | 8             | 0.2-1.2/12-18                        | 18-33 @ 450             | 2-5                | 0.4-0.8                                 | $0.02^{r}$             | 237-184 <sup>s</sup>    | N/A <sup>s</sup>           |

| Niclass [52]    | 130             | 10            | 1-3.5/10                             | 34-41 @ 450             | 3                  | 120-1300 <sup>d</sup>                   | N/A                    | 144 <sup>i</sup>        | N/Ai                       |

| Gersbach [53]   | 130             | 4.3           | 1-2/9                                | 18-30 @ 480             | 3.5-5              | 1.5-11.5                                | $<1^{t}$               | 125 <sup>i</sup>        | $\sim$ 720 <sup>i</sup>    |

| Charbon [54]    | 65              | 8             | 0.05-0.4/9                           | 2-5.5 @ 420             | 0.2-0.4            | 340-15.6k <sup>a</sup>                  | $<1^{\mathrm{u}}$      | 235 <sup>i</sup>        | N/A                        |

| this work (A)   | 160             | 10-80         | 3-9/36                               | 31-58 @ 450             | 2.5-6.5            | $0.12 - 0.2^{v}$                        | 0.43-1.59 <sup>w</sup> | 39-28 <sup>c</sup>      | 93 <sup>x</sup>            |

| this work (B)   | 160             | 10-80         | 3-9/25                               | 22-47 @ 450             | 2.5-6.5            | $0.1 - 0.18^{v}$                        | $0.02 - 0.14^{w}$      | 36-28 <sup>c</sup>      | 107 <sup>x</sup>           |

| this work (C)   | 160             | 10-80         | 3-9/26                               | 55-71 @ 490             | 6-9                | $0.13 \text{-} 0.19^{\text{v}}$         | 0.41-1.26 <sup>w</sup> | 41-28 <sup>c</sup>      | 48 <sup>x</sup>            |

$^a$ At 20°C.  $^b$ 200  $\mu$ m-diameter, at 25°C, 80 ns dead time,  $V_{\rm EX}=5$  V.  $^c$ 820 nm wavelength  $^d$ At 25°C.  $^e$ 30  $\mu$ m-diameter, at 25°C, 40 ns dead time,  $V_{\rm EX}=5$  V, integrated AQC.  $^f$ A time resolution of 28-37 ps FWHM and a diffusion tail of 160-340 ps were demonstrated in Ref. [42] using the substrate bias as a trade-off parameter between jitter and diffusion tail.  $^a$ PDE = 10-13% at 800 nm.  $^b$ 300 ns dead time,  $V_{\rm EX}=2$ -10 V.  $^i$ 637 nm wavelength.  $^j$ 300 ns dead time,  $V_{\rm EX}=4$  V.  $^k$ 300 ns dead time,  $V_{\rm EX}=1$  1 V.  $^i$ 50 ns dead time,  $V_{\rm EX}=1$  1 V.  $^i$ 50 ns dead time,  $V_{\rm EX}=1$  1 V.  $^i$ 50 ns dead time,  $V_{\rm EX}=1$  1 V.  $^i$ 50 ns dead time,  $V_{\rm EX}=1$  1 V.  $^i$ 50 ns dead time.  $^i$ 6470 nm wavelength.  $^i$ 180 ns dead time.  $^i$ 50 ns dead time.  $^i$ 741 300 K.  $^i$ 750 ns dead time.  $^i$ 750 ns dead time.

Fig. 12. Timing response of 30  $\mu$ m SPADs belonging to wafer A, B, and C to a narrow ( $\sim$ 50 ps) laser pulse at 850 nm. The excess bias voltage is 5 V. All curves show a narrow peak with less than 60 ps FWHM and a very clean and short exponential diffusion tail. Note that the Full-Widths at 1/100 of the Maximum (and not the FWHM) are reported in the plots.

Pile-up corrections to the acquired histogram are not required, since the probability of having more than one photon per pulse is negligible. The SPADs are operated at room temperature by using a monolithically integrated AQC. The timing signals are generated at the cathode by employing the current pickup network described in [40], [41] (with  $\sim$ 500 ps differentiating time constant) that feeds a fast comparator. With a threshold voltage of 5 mV, the avalanche is sensed at approximately  $100~\mu\text{A}$ , when it is still confined within a small area around the seed point, in order to avoid degradation of the photon-timing performances due to the statistical phenomena involved in the avalanche

lateral spread [29]. The Full-Width at Half Maximum (FWHM) of the responses of the three SPADs is always about 60 ps, limited by the intrinsic laser pulse width.

The so-called 'diffusion tail', which is due to minority carriers photogenerated in the deep n-iso neutral region and diffusing toward the space charge is minimized, appearing more than one decade below the peak and being purely exponential (see Fig. 12). The lifetime fit parameters are just 93 ps and 107 ps for wafer A and B, respectively, and 48 ps for wafer C, with a standard error of about 1 ps. These extremely sharp timing responses lead to less than 400 ps FW1/100M (at 1/100 from the peak), and less than 1 ns even down four decades (FW1/10,000M) from the peak, thus being attractive for applications requiring high-resolution measurements of fast optical signals with wide dynamic range.

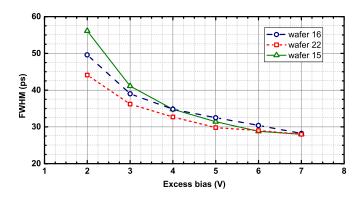

In order to ascertain the intrinsic FWHM timing jitter, we characterized the BCD SPAD responses to a narrower (FWHM  $\sim\!15$  ps) 820 nm pulsed laser (Antel MPL-820 laser module). Fig. 13 shows the measurements. Thanks to the very short diffusion tails, very weak features on the laser pulse waveform can be observed, such as the residual optical oscillation after the main peak, which is likely due to a ringing in the fast driving current pulse. The measured FWHM timing resolution is approximately 30 ps. Fig. 14 shows the peak FWHM dependence on excess bias voltage. The higher the excess bias voltage, the narrower is the measured FWHM, because of the faster avalanche current build-up. By quadratically subtracting the laser pulse FWHM, the actual time resolution of the BCD SPADs is better than 24 ps FWHM at  $V_{\rm EX}=7~\rm V$  for all detectors.

These outstanding results have been achieved thanks to the tailored electric field in the avalanche region and to the deep n-iso implant. Specifically, the low resistivity path towards the

Fig. 13. Timing response to a very narrow ( $\sim$ 15 ps) laser pulse at 820 nm. The excess bias voltage is 5 V.

Fig. 14. Measured timing jitter as a function of excess bias. The laser pulse ( $\sim$ 15 ps FWHM) has not been quadratically subtracted.

side ohmic cathode established by the deep n-iso high doping relaxes the well-known trade-off between time resolution FWHM and diffusion tail time constant of CMOS SPADs [35], [42].

The achieved state-of-the-art performance enables applications requiring single-photon detection of extremely fast and sharp visible and NIR optical signals, with wide dynamics. For example, to detect transparent objects just behind strongly reflecting targets in 3D time-of-flight LIDAR systems (e.g., a second opaque object with a factor 10 000 in reflectivity just 1 ns, i.e., 15 cm, beyond a first highly reflecting object); in time-resolved near-infrared spectroscopy (NIRS) for the study of the functional activation of human cerebral cortex, even with non-contact optical sensing [43].

# VII. STATE-OF-THE-ART COMPARISON

Table I compares the performance of the BCD SPADs presented in this work with other state-of-the-art devices suitable for arrays (i.e., isolated from the chip substrate [44]) fabricated in either custom or CMOS technologies.

Among CMOS SPADs, those developed in 0.35- $\mu$ m [35] and 0.18- $\mu$ m technologies [44]–[47] resulted in higher PDE, since the higher doping level of 150-130 nm technologies limits the PDE peak to about 30%. Veerappan et al. [44] attained the best PDE spectral response: peak PDE of 47.6% at 480 nm and >40% from 440 to 620 nm at 10 V excess bias. However, the authors claim that the integration of circuitry for reliable operation at 10 V excess bias is not straightforward. The PDE drops considerably at 4 V excess bias, but the overall spectral response remains among the best CMOS SPADs reported in the literature. In [46], the same authors attained at 4 V excess bias nearly the same PDE spectral response they reported in [44] at 10 V. Specifically, they designed a narrower depletion region and a relatively wider neutral region, from which holes are collected by diffusion. The drawback of this approach is a relatively slow diffusion tail ( $\sim$ 400 ps lifetime) in the timing response.

To the best of our knowledge the performance achieved by the wafer C SPAD presented in this work is superior to any other substrate isolated CMOS SPAD reported in the literature. At 5 V excess bias the peak PDE is 60% at 490 nm. It is worth noting that the PDE spectral response of our 'deep' SPAD and the state-of-the-art device of [46] become nearly identical in the 650–850 nm wavelength range. However, the BCD deep SPAD is a better candidate for photon timing application at red and NIR wavelengths, owing to its much faster diffusion tail (<50 ps lifetime).

Table I also shows that the achieved DCR per unit area ( $<0.2~{\rm Hz/\mu m^2}$ ) is better than most CMOS SPADs. Only the 0.35- $\mu$ m low-noise SPAD reported in [35] attains better noise performance (0.05  ${\rm Hz/\mu m^2}$ ). As shown in Fig. 5, the excess bias voltages can be increased up to 9 V with little impact on DCR. Conversely, for most CMOS SPADs in Table I, the DCR exhibits a strong dependence on the excess bias voltage.

It is harder to make a fair afterpulsing comparison between different SPAD designs and CMOS technologies. The reason being that each research group performed measurements in different experimental conditions (e.g., SPAD diameter, excess bias, dead time, quenching circuit, etc.).

Finally, to the best of our knowledge, the achieved timing response is the new state-of-the-art among CMOS [42] and custom SPADs [1] so far reported in the literature.

### VIII. CONCLUSION

We have reported the design criteria and experimental characterization of the first SPADs ever fabricated in a BCD technology, which exploit the high modularity of the STMicroelectronics BCD8sP process to achieve enhanced PDE, low DCR and state-of-the-art timing resolution. To the best of the author's knowledge the overall detection performance surpasses the very best CMOS SPADs with substrate isolation. We are currently fabricating a  $32 \times 32$  time-resolved SPAD imager to fully characterize the performance uniformity over a statistically significant number of BCD SPADs as in [55], [56].

#### REFERENCES

- M. Ghioni, A. Gulinatti, I. Rech, F. Zappa, and S. Cova, "Progress in silicon single-photon avalanche diodes," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, pp. 852–862, Jul. 2007.

- [2] A. Gulinatti et al., "New silicon SPAD technology for enhanced redsensitivity, high-resolution timing and system integration," J. Mod. Opt., vol. 59, no. 17, pp. 1489–1499, Oct. 2012.

- [3] X. Michalet et al., "Silicon photon-counting avalanche diodes for single-molecule fluorescence spectroscopy," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 248–267, Nov. 2014.

- [4] D. E. Schwartz, E. Charbon, and K. L. Shepard, "A single-photon avalanche diode array for fluorescence lifetime imaging microscopy," *IEEE J. Solid-State Circuits*, vol. 43, no. 11, pp. 2546–2557, Nov. 2008

- [5] D.-U. Li et al., "Real-time fluorescence lifetime imaging system with a 32 × 32 0.13 μm CMOS low dark-count single-photon avalanche diode array," Opt. Express, vol. 18, no. 10, May 2010, Art. no. 10257.

- [6] Y. Maruyama and E. Charbon, "An all-digital, time-gated 128 × 128 SPAD array for on-chip, filter-less fluorescence detection," in *Proc.* 2011 16th Int. Solid-State Sensors, Actuators Microsyst. Conf., 2011, pp. 1180–1183.

- [7] M. Vitali et al., "A single-photon avalanche camera for fluorescence lifetime imaging microscopy and correlation spectroscopy," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 344–353, Nov. 2014.

- [8] R. M. Field, S. Realov and K. L. Shepard, "A 100 fps, time-correlated single-photon-counting-based fluorescence-lifetime imager in 130 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 49, no. 4, pp. 867–880, Apr. 2014

- [9] M. Perenzoni, N. Massari, D. Perenzoni, L. Gasparini, and D. Stoppa, "A 160 × 120 pixel analog-counting single-photon imager with time-gating and self-referenced column-parallel A/D conversion for fluorescence lifetime imaging," *IEEE J. Solid-State Circuits*, vol. 51, no. 1, pp. 155–167, Jan. 2016.

- [10] B. F. Aull et al., "Geiger-mode avalanche photodiodes for threedimensional imaging," LINCOLN Lab. J., vol. 13, no. 2, pp. 335–350, 2002

- [11] C. Niclass, A. Rochas, P.-A. Besse, and E. Charbon, "Design and characterization of a CMOS 3-D image sensor based on single photon avalanche diodes," *IEEE J. Solid-State Circuits*, vol. 40, no. 9, pp. 1847–1854, Sep. 2005

- [12] C. Niclass, C. Favi, T. Kluter, M. Gersbach, and E. Charbon, "A 128 x 128 single-photon image sensor with column-level 10-Bit time-to-digital converter array," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2977– 2989, Dec. 2008.

- [13] C. Niclass et al., "Design and characterization of a 256 × 64-pixel single-photon imager in CMOS for a MEMS-based laser scanning time-of-flight sensor," Opt. Exp., vol. 20, no. 11, p. 11863, May 2012.

- [14] C. Niclass, M. Soga, H. Matsubara, S. Kato, and M. Kagami, "A 100-m range 10-frame/s 340x96-pixel time-of-flight depth sensor in 0.18μm CMOS," *IEEE J. Solid-State Circuits*, vol. 48, no. 2, pp. 559–572, Feb. 2013.

- [15] D. Bronzi et al., "100 000 frames/s 64 × 32 single-photon detector array for 2-D imaging and 3-D ranging," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 354–363, Nov. 2014.

- [16] F. Villa et al., "CMOS Imager with 1024 SPADs and TDCs for single-photon timing and 3-D time-of-flight," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 364–373, Nov. 2014.

- [17] A. Rochas et al., "Single photon detector fabricated in a complementary metal-oxide-semiconductor high-voltage technology," Rev. Sci. Instrum., vol. 74, pp. 3263–3270, Jul. 2003.

- [18] C. Niclass, A. Rochas, P.-A. Besse, and E. Charbon, "Toward a 3-D camera based on single photon avalanche diodes," *IEEE J. Sel. Topics Quantum Electron.*, vol. 10, no. 4, pp. 796–802, Jul. 2004.

- [19] C. Veerappan et al., "A 160 × 128 single-photon image sensor with on-pixel 55ps 10b time-to-digital converter," in Proc. 2011 IEEE Int. Solid-State Circuits Conf., 2011, pp. 312–314.

- [20] S. Burri et al., "Architecture and applications of a high resolution gated SPAD image sensor," Opt. Express, vol. 22, no. 14, Jul. 2014, Art. no. 17573.

- [21] N. A. W. Dutton et al., "A SPAD-Based QVGA image sensor for single-photon counting and quanta imaging," IEEE Trans. Electron Devices, vol. 63, no. 1, pp. 189–196, Jan. 2016.

- [22] S. D. Cova and M. Ghioni, "Single-photon counting detectors," *IEEE Photon. J.*, vol. 3, no. 2, pp. 274–277, Apr. 2011.

- [23] B. Murari, F. Bertotti, and G. A. Vignola (Eds.), Smart Power ICs: Technologies and Applications (Springer Series in Advanced Microelectronics). Berlin, Germany: Springer-Verlag, 2002.

- [24] C. Contiero, A. Andreini, and P. Galbiati, "Roadmap differentiation and emerging trends in BCD technology," in *Proc. 32nd Eur. Solid-State De*vice Res. Conf., 2002, pp. 275–282.

- [25] R. Roggero et al., "BCD8sP: an advanced 0.16 μm technology platform with state of the art power devices," Proc. 2013 25th Int. Symp. Power Semiconductor Devices & IC's, Kanazawa, 2013, pp. 361–364.

- [26] A. Schenk, "A Model for the field and temperature dependence of shockley-read-hall lifetimes in silicon," *Solid-State Electron.*, vol. 35, no. 11, pp. 1585–1596, 1992.

- [27] G. A. M. Hurkx, D. B. M. Klaassen, and M. P. G. Knuvers, "A new recombination model for device simulation including tunneling," *IEEE Trans. Electron Devices*, vol. 39, no. 2, pp. 331–338, Feb. 1992.

- [28] A. Lacaita, M. Ghioni, and S. Cova, "Double epitaxy improves single-photon avalanche diode performance," *Electron. Lett.*, vol. 25, no. 13, pp. 841–843, 1989.

- [29] M. Assanelli, A. Ingargiola, I. Rech, A. Gulinatti and M. Ghioni, "Photon-timing jitter dependence on injection position in single-photon avalanche diodes," *IEEE J. Quantum Electron.*, vol. 47, no. 2, pp. 151–159, Feb. 2011.

- [30] M. J. Hsu, H. Finkelstein and S. C. Esener, "A CMOS STI-bound single-photon avalanche diode with 27-ps timing resolution and a reduced diffusion tail," *IEEE Electron Device Lett.*, vol. 30, no. 6, pp. 641–643, Jun. 2009.

- [31] Sentaurus Process User Guide, Synopsys, Mountain View, CA, USA, Sep. 2014.

- [32] Sentaurus Device User Guide, Synopsys, Mountain View, CA, USA, Sep. 2014

- [33] W. O. Oldham, R. R. Samuelson, and P. Antognetti, "Triggering phenomena in avalanche diodes," *IEEE Trans. Electron Devices*, vol. ED-19, no. 6, pp. 1056–1060, Sep. 1972.

- [34] A. Gulinatti, I. Rech, M. Assanelli, M. Ghioni, and S. Cova, "A physically based model for evaluating the photon detection efficiency and the temporal response of SPAD detectors," *J. Mod. Opt.*, vol. 58, no. 3–4, pp. 210–224, Feb. 2011.

- [35] F. Villa et al., CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm," J. Mod. Opt., vol. 61, no. 2, pp. 102–115, Jan. 2014.

- [36] A. Giudice et al., High-rate photon counting and picosecond timing with silicon-SPAD based compact detector modules," J. Mod. Opt., vol. 54, no. 2–3, pp. 225–237, Jan. 2007.

- [37] D. Bronzi, S. Tisa, F. A. Villa, S. Bellisai, A. Tosi, and F. Zappa, "Fast sensing and quenching of CMOS SPADs for minimal afterpulsing effects," *IEEE Photon. Technol. Lett.*, vol. 25, no. 8, pp. 776–779, Apr. 15, 2013.

- [38] S. Cova, A. Lacaita, and G. Ripamonti, "Trapping phenomena in avalanche photodiodes on nanoseconds scale," *IEEE Electron Device Lett.*, vol. 12, no. 12, pp. 685–687, Dec. 1991.

- [39] M. A. Itzler, X. Jiang, and M. Entwistle, "Power law temporal dependence of InGaAs/InP SPAD afterpulsing," J. Mod. Opt., vol. 59, no. 17, pp. 1472– 1480, Oct. 2012.

- [40] A. Gulinatti, P. Maccagnani, I. Rech, M. Ghioni, and S. Cova, "35 ps time resolution at room temperature with large area single photon avalanche diodes," *Electron. Lett.*, vol. 41, no. 5, pp. 272–274, Mar. 2005.

- [41] S. Cova, M. Ghioni, and F. Zappa, "Circuit for high precision detection of the time of arrival of photons falling on single photon avalanche diodes," US patent6,384,663 B2, May 7, 2002.

- [42] M. Buttafava, G. Boso, A. Ruggeri, A. Dalla Mora, and A. Tosi, "Time-gated single-photon detection module with 110 ps transition time and up to 80 MHz repetition rate," *Rev. Sci. Instrum.*, vol. 85, no. 8, Aug. 2014, Art. no. 83114.

- [43] M. Mazurenka et al., "Non-contact time-resolved diffuse reflectance imaging at null source-detector separation," Opt. Express, vol. 20, no. 1, pp. 283–290, 2012.

- [44] C. Veerappan and E. Charbon, "A substrate isolated CMOS SPAD enabling wide spectral response and low electrical crosstalk," *IEEE J. Sel. Topics Quantum Electron.*, vol. 20, no. 6, pp. 299–305, Nov. 2014.

- [45] T. Leitner et al., "Measurements and simulations of low dark count rate single photon avalanche diode device in a low voltage 180-nm CMOS image sensor technology," *IEEE Trans. Electron Devices*, vol. 60, no. 6, pp. 1982–1988, Jun. 2013.

- [46] C. Veerappan and E. Charbon, "CMOS SPAD based on photo-carrier diffusion achieving PDP >40% from 440 to 580 nm at 4 V excess bias," *IEEE Photon. Technol. Lett.*, vol. 27, no. 23, pp. 2445–2448, Dec. 2015.

- [47] C. Veerappan and E. Charbon, "A low dark count p-i-n diode based SPAD in CMOS technology," *IEEE Trans. Electron Devices*, vol. 63, no. 1, pp. 65–71, Jan. 2016.

- [48] H. Xu, L. Pancheri, G.-F. D. Betta, and D. Stoppa, "Design and characterization of a p+/n-well SPAD array in 150nm CMOS process," *Opt. Express*, vol. 25, no. 11, May 2017, Art. no. 12765.

- [49] M.-J. Lee, P. Sun, and E. Charbon, "A first single-photon avalanche diode fabricated in standard SOI CMOS technology with a full characterization of the device," Opt. Exp., vol. 23, no. 10, May 2015, Art. no. 13200.

- [50] J. A. Richardson, L. A. Grant, and R. K. Henderson, "Low dark count single-photon avalanche diode structure compatible with standard nanometer scale CMOS technology," *IEEE Photon. Technol. Lett.*, vol. 21, no. 14, pp. 1020–1022, Jul. 2009.

- [51] J. A. Richardson, E. A. G. Webster, L. A. Grant, and R. K. Henderson, "Scaleable single-photon avalanche diode structures in nanometer CMOS technology," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2028–2035, Jul. 2011.

- [52] C. Niclass, M. Gersbach, R. Henderson, L. Grant, and E. Charbon, "A single photon avalanche diode implemented in 130-nm CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 863–869, Jul./Aug. 2007.

- [53] M. Gersbach et al., "A single photon detector implemented in a 130 nm CMOS imaging process," in Proc. 38th Eur. Solid-State Device Res. Conf., 2008, pp. 270–273.

- [54] E. Charbon, H.-J. Yoon, and Y. Maruyama, "A Geiger mode APD fabricated in standard 65nm CMOS technology," in *Proc. 2013 IEEE Int. Electron Devices Meeting*, 2013, pp. 27.5.1–27.5.4.

- [55] C. Veerappan et al., "Characterization of large-scale non-uniformities in a 20 k TDC/SPAD array integrated in a 130 nm CMOS process," in Proc. 2011 Eur. Solid-State Device Res. Conf., 2011, pp. 331–334.

- [56] I. M. Antolovic, S. Burri, C. Bruschini, R. Hoebe, and E. Charbon, "Nonuniformity analysis of a 65-kpixel CMOS SPAD imager," *IEEE Trans. Electron Devices*, vol. 63, no. 1, pp. 57–64, Jan. 2016.

Mirko Sanzaro (M'17) was born in Avola, Italy, in 1988. He received the M.Sc. degree (summa cum laude) in electronic engineering and the Ph.D. degree (summa cum laude) in information technology engineering from Politecnico di Milano, Milan, Italy, in 2013 and 2017, respectively. He is a currently a Postdoctoral Researcher at Politecnico di Milano. His research interests include the design, development, and characterization of visible and near-infrared single-photon avalanche diodes (SPADs) in both Silicon and InGaAs/InP semiconductors.

**Paolo Gattari** was born in Milano, Italy, in 1976. He received the Master's degree in physics at Università Statale di Milano, Milan, Italy. In 2004, he joined STMicroelectronics, Agrate Brianza, Italy, where he has been involved in the development of smart power BCD technologies.

**Federica Villa** (M'15) was born in Milano, Italy, in 1986. She received the B.Sc. degree in biomedical engineering in 2008, the M.Sc. degree (*summa cum laude*) in electronic engineering in 2010 and the Ph.D. degree in information and communication technology in 2014, from Politecnico di Milano, Milan, Italy. Since 2015, she has been an Assistant Professor at Politecnico di Milano. She is coauthor of 72 papers. Her current research interests include the design and development of CMOS SPAD imagers for 2-D imaging via single-photon counting and 3-D ranging through direct time-of-flight photon timing.

**Alberto Tosi** (M'07) was born in Borgomanero, Italy, in 1975. He received the Master's degree in electronics engineering and the Ph.D. degree in information technology engineering from the Politecnico di Milano, Milan, Italy, in 2001 and 2005, respectively. He was an Assistant Professor from 2006 to 2014.

He has been an Associate Professor of Electronics with the Politecnico di Milano since 2014. In 2004, he was a student with the IBM T. J. Watson Research Center, Yorktown Heights, NY, USA, working on optical testing of CMOS circuits. He currently works on silicon and InGaAs/InP single-photon avalanche diodes (SPADs). His research interests include arrays of silicon SPADs for 2-D and 3-D applications and time-correlated single-photon counting electronics.

**Giuseppe Croce** (M'07) was born in Messina, Italy, in 1969. He received the M.Sc. degree (*summa cum laude*) in electronic engineering from Pisa University, Pisa, Italy, in 1994.

In 1995, he joined STMicroeletronics, Agrate Brianza, Italy, where he is currently working as Technology Line Manager in Smart Power Technology R&D organizations. He has worked on the design and development of BCD (Bipolar CMOS DMOS) technology platform for consumer, industrial, and automotive applications. He is coauthor of more than ten papers and several patents.

Franco Zappa (SM'12) was born in Milano, Italy, in 1965. He received the Master's degree in electronics engineering and the Ph.D. degree in communication technology from Politecnico di Milano, Milan, Italy, in 1989 and 1993, respectively, where he has been a Full Professor of electronics since 2011. He is coauthor of more than 220 papers, published in peer-reviewed journals and in conference proceedings, and eight text books on electronic design, electronic systems, and microcontrollers. His research interests include microelectronic circuitry for single-photon detectors (SPAD) and CMOS and BCD SPAD imagers, for high-sensitivity time-resolved optical measurements, 2-D imaging, and 3-D depth ranging via single-photons' time of flight. In 2004, he cofounded "Micro Photon Devices" focused on the production of SPAD modules and cameras for single photon-counting and photon-timing.