ISSN 0005-1144 ATKAFF 51(1), 41–54(2010)

Lin Xu, Yang Han, Chen Chen, Jun-Min Pan, Gang Yao, Li-Dan Zhou, M. M. Khan

# Modeling, Control and Experimental Investigation of a Novel DSTATCOM Based on Cascaded H-bridge Multilevel Inverter

UDK 621.316.072.8 IFAC 5.5.4; 4.0.1

Original scientific paper

A novel static synchronous compensator for reactive power compensation of distribution system (DSTATCOM) is proposed, based on the cascaded H-bridge multilevel inverter configuration. The mathematical formulation of the multilevel DSTATCOM is presented using state-space representations. A new software phase-locked loop (SPLL) is presented for grid synchronization and the obtained phase angle of the fundamental component of the grid voltage is utilized for deriving the active and reactive power balancing equations of the multilevel DSTATCOM. The proportional-resonant (PR) controller scheme is adopted for the current tracking control of the inverter, and the average dc-link voltage is controlled using a proportional-integral (PI) controller to regulate the active power flow of the DSTATCOM. Besides, the voltage balancing (VB) control among individual H-bridges is achieved by using separate PI regulators to control the difference voltage between the individual dc-link voltage and the average dc-link voltage. The validity of the proposed multilevel DSTATCOM and its control strategies is substantially confirmed by the extensive simulation results and the experimental results from the prototype system.

Key words: Multilevel, Cascaded H-bridge, DSTATCOM, Phase-locked loop (PLL), Voltage balancing

Modeliranje, upravljanje i eksperimentalno istraživanje novoga raspodijeljenog statičkog kompenzatora jalove snage zasnovanog na višestupanjskom pretvaraču s ulančenim H-mostovima. Predložen je novi statički sinkroni kompenzator za kompenzaciju jalove snage distribucijskog sustava (DSTATCOM) zasnovan na konfiguraciji višestupanjskog pretvarača s ulančenim H-mostovima. Matematički model višerazinskog DSTATCOM-a prikazan je u prostoru stanja. Predstavljena je nova programski izvedena petlja sa zaključanom fazom namijenjena sinkronizaciji s mrežom, a dobiveni fazni kut osnovne komponente mrežnog napona koristi se za izvod jednadžbi ravnoteže aktivne i jalove snage višerazinskog DSTATCOM-a. Usvojen je koncept proporcionalno-rezonantnog regulatora za slijeđenje trajektorije struje pretvarača, a srednji napon istosmjernog međukruga upravlja se korištenjem proporcionalno-integracijskog (PI) regulatora u svrhu regulacije toka radne snage DSTATCOM-a. Osim toga, upravljanje uravnoteženjem napona među pojedinim H-mostovima ostvareno je korištenjem odvojenih PI regulatora za upravljanje razlikom napona među pojedinim istosmjernim međukrugovima te srednjim naponom istosmjernih međukrugova. Valjanost predloženog višestupanjskog DSTATCOM-a i primijenjenih upravljačkih strategija potvrđena je brojnim simulacijskim i eksperimentalnim rezultatima na prototipskoj izvedbi ovog sustava.

Ključne riječi: višestupanjski, ulančeni H-most, DSTATCOM, petlja sa zaključanom fazom (PLL), uravnoteženje napona

# **1 INTRODUCTION**

In recent decades, the electric distribution systems are suffering from significant power quality (PQ) problems, which are characterized by low power factor, poor voltage profile, voltage fluctuations, voltage sag/swell, load unbalancing, and supply interruptions. These power quality issues have attracted attention to the researchers from both academy and industry. As a result, many power quality standards were proposed, such as the IEEE 519-1992, IEEE Std.141-1993, IEEE Std.1159-1995 and IEC 1000-3-2, etc. [1–4]. Among all forms of the power quality issues, the voltage fluctuations or sag/swell problems were recognized as the most costly events in the modern assembly lines and commercial offices [5–8]. On the other hand, the increasing power quality problems have stimulated a great potential for the industry to devise the power quality mitigation and compensation devices. For instance, the static synchronous compensator for the distribution system (DSTATCOM) was proposed in [5] to solve the voltage sag and flicker problems. In [6–8], new compensation schemes for the voltage flicker problem were presented and the combined compensation scheme based on the active power filter (APF) and switching capacitors was implemented in a typical electrical distribution system for the automobile industry.

The DSTATCOMs and APFs share the same powerstage topologies, but differ in the control strategies and reference current generation schemes, as reported in [8–12]. Generally, the DSTATCOMs are designed to compensate fundamental frequency reactive power while the APFs compensate a wider spectrum which contains both fundamental reactive power and the harmonic components. Moreover, DSTATCOMs also have the capability for voltage regulation for the grid voltage at the common coupling point (PCC) by injecting or absorbing a certain amount of reactive power. Hence the DSTATCOMs received considerable attention due to the urgent requirement for tackling the voltage fluctuation problems [9–11].

To meet the requirement of the reactive compensation for high-power, medium-voltage electric distributions systems, the conventional three-phase three-wire or four-wire DSTATCOM topologies have evolved into the multilevel and multi-cell topologies [13-16]. In [13], the dc-link voltage equalization for the diode-clamped multilevel DSTAT-COM was reported. The diode-clamped multilevel topology, however, shows poor capability for modular fabrication and the capacitor voltage balancing is rating complex. Moreover, it has deficiency for redundant operation of the power electronic switches. The cascaded H-bridge multilevel topology, on the other hand, shows much better modular capability, simple layout, excellent redundant operation ability and it can be extended to higher voltage levels by adding new H-bridge modules [14-16]. However, the dc-link voltage stabilization across the dc-link capacitors is not trivial due to the unequal power losses for the individual H-bridges and the limited precision for the gating signals. Therefore, this paper is aiming to present a detailed elaboration of the DSTATCOM based on the cascaded Hbridge multilevel inverter, which includes the mathematical formulation, grid-synchronization, current tracking and the dc-link voltage balancing schemes.

This paper is organized as follows: The mathematical formulation of the multilevel DSTATCOM is presented in Section 2. The control strategies are presented in Section 3, where a novel software phase-locked loop (SPLL), the current tracking schemes and the dc-link voltage balancing scheme will be discussed in detail. In Section 4 the simulation results are presented to test the performance of the proposed system. In Section 5 the extensive experimental results obtained from the laboratory prototype system are presented to validate the theoretical analysis and the simulation results. Finally, Section 6 concludes this paper.

# 2 MATHEMATICAL MODELLING

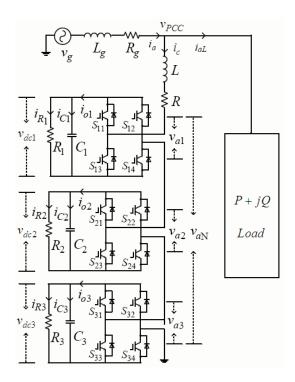

Figure 1 shows the circuit diagram of the seven-level cascaded multilevel DSTATCOM based on three H-bridge

Fig. 1. The schematic of the proposed DSTATCOM based on cascaded H-bridge multilevel inverter

modules. It can be observed that each H-bridge includes four IGBT switches with anti-parallel diodes and a dc-link capacitor. The output voltages of the cascaded H-bridge inverter can be derived as [12]:

$$v_{aN} = v_{a1} + v_{a2} + v_{a3}.$$

(1)

Assuming  $v_{dc1} = v_{dc2} = v_{dc3} = V_{dc}$  in the steady state conditions and the unipolar modulation scheme is adopted in the PWM process, then each H-bridge module can produce three different voltage levels:  $-V_{dc}$ , 0,  $V_{dc}$ . With reference to the upper bridge, it is possible to set  $v_{a1} = +V_{dc}$ by turning on power switches  $S_{11}$  and  $S_{14}$  and  $v_{a1} = -V_{dc}$ by turning on power switches  $S_{12}$  and  $S_{13}$ . Moreover, it is possible to set  $v_{a1} = 0$  by turning on either  $S_{11}$  and  $S_{12}$  or  $S_{13}$  and  $S_{14}$ , the lower bridge operates in a similar manner. Therefore, seven distinct voltage levels can be synthesized at the ac terminals. It should be noted that the switching states of  $S_{x1}$ ,  $S_{x2}$  (x = 1, 2, 3) must be complementary to those of  $S_{x3}$ ,  $S_{x4}$  (x = 1, 2, 3) in order to avoid short circuit of the H-bridge. To derive the state-space equations for the multilevel DSTATCOM, the switching functions are defined for individual H-bridges, as denoted by:

$$\begin{cases}

f_1 = S_{11} \cdot S_{14} - S_{12} \cdot S_{13}, \\

f_2 = S_{21} \cdot S_{24} - S_{22} \cdot S_{23}, \\

f_3 = S_{31} \cdot S_{34} - S_{32} \cdot S_{33}.

\end{cases}$$

(2)

The value of  $f_x$  (x = 1, 2, 3) indicates the dynamic process of charging and discharging between the dc-link capacitors  $C_1$ ,  $C_2$  and  $C_3$ . Supposing the DSTATCOM current  $i_c$  is positive, then the capacitor  $C_x$  (x = 1, 2, 3) is charging if  $f_x = 1$ , discharging if  $f_x = -1$ , and not undergoing any of these processes if  $f_x = 0$ . Complementary phenomenon appears if the inverter current is negative. The following assumptions are made for deriving the mathematical model of the cascaded H-bridge inverters.

- a) The grid is assumed to be AC current source;

- b) The power losses of the whole system are categorized as series loss and parallel loss. The series loss and interfacing inductor loss are represented as equivalent series resistance (ESR). Parallel losses are represented as shunt connected resistances across the dclink capacitors, corresponding to the active power loss of the H-bridge, including blocking loss, capacitor loss and absorbing circuit loss, etc.

The differential equation describing the dynamics of the coupling inductor between the cascaded H-bridge inverter and the grid can be derived as:

$$v_{PCC} = Ri_c + L\frac{di_c}{dt} + f_1 v_{dc1} + f_2 v_{dc2} + f_3 v_{dc3}, \quad (3)$$

where the variable  $v_{PCC}$  represents grid voltage at the point of common coupling (PCC), L represents the inductance of the coupling inductor and R represents the equivalent series resistance (ESR). The variables  $v_{dc1}$ ,  $v_{dc2}$  and  $v_{dc3}$  are actual voltages across the dc-link capacitors of the cascaded H-bridge inverter, which may not equal to the reference voltage  $V_{dc}$  during dynamic process. According to the Kirchhoff's law, the currents flowing into the dc-link capacitors  $C_1$ ,  $C_2$  and  $C_3$  can be expressed as:

$$\begin{cases} i_{c1} = C_1 \frac{dv_{dc1}}{dt} = i_{o1} - i_{R1} = f_1 i_c - \frac{v_{dc1}}{R_1}, \\ i_{c2} = C_2 \frac{dv_{dc2}}{dt} = i_{o2} - i_{R2} = f_2 i_c - \frac{v_{dc2}}{R_2}, \\ i_{c3} = C_3 \frac{dv_{dc3}}{dt} = i_{o3} - i_{R3} = f_3 i_c - \frac{v_{dc3}}{R_3}, \end{cases}$$

(4)

where  $R_1$ ,  $R_2$  and  $R_3$  are the equivalent resistance of each H-bridges, representing the parallel losses. The variables  $i_{o1}$ ,  $i_{o2}$  and  $i_{o3}$  represent the total dc-link current and  $i_{R1}$ ,  $i_{R2}$  and  $i_{R3}$  represent the current in the dc-link resistance of the individual H-bridge module. The Eqs.(3)-(4) can be

rearranged as:

$$\begin{cases} \frac{di_c}{dt} = \frac{v_{PCC}}{L} - \frac{R}{L}i_c - \frac{f_1v_{dc1}}{L} - \frac{f_2v_{dc2}}{L} - \frac{f_3v_{dc3}}{L}, \\ \frac{dv_{dc1}}{dt} = \frac{f_1i_c}{C_1} - \frac{v_{dc1}}{R_1C_1}, \\ \frac{dv_{dc2}}{dt} = \frac{f_2i_c}{C_2} - \frac{v_{dc2}}{R_2C_2}, \\ \frac{dv_{dc3}}{dt} = \frac{f_3i_c}{C_3} - \frac{v_{dc3}}{R_3C_3}. \end{cases}$$

(5)

Let the vector of state variables be denoted with  $X_3 = [i_c \ v_{dc1} \ v_{dc2} \ v_{dc3}]^{\top}$  and the input vector with  $U_3 = [v_{PCC} \ 0 \ 0 \ 0]^{\top}$ . Then (5) can be expressed in compact matrix form:

$$\dot{X}_3 = A_3 X_3 + B_3 U_3. \tag{6}$$

The matrices  $A_3$  and  $B_3$  can be simply derived as:

#### **3 CONTROL STRATEGIES**

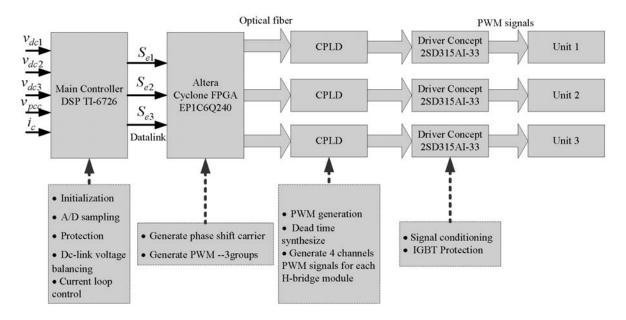

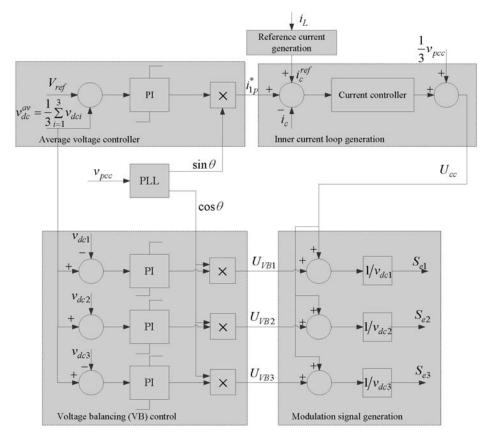

Figure 2 shows the controller architecture for the proposed multilevel DSTATCOM, which is based on the floating-point digital signal processor (DSP) and the field programmable gate array (FPGA) hardware platforms. A detailed discussion of this hardware architecture will be delivered in Section 5. This section briefly outlines the control strategies of the multilevel DSTATCOM, which includes the grid-synchronization using the software phaselocked loop (SPLL), the current tracking scheme and the voltage balancing (VB) control strategies, as illustrated in Fig. 3.

#### 3.1 Software phase-locked loop (SPLL)

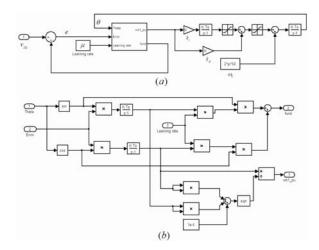

Accurate synchronization of the multilevel DSTAT-COM to the grid is of vital importance to ensure its stable operation since the phase angle of the grid voltage is used to derive the active and reactive power balancing equations for the DSTATCOM. Figure 4 shows the schematic of the proposed software phase-locked loop (SPLL) for grid synchronization based on the least-mean square (LMS) estimation algorithm [17]. Here the mathematical formulation of the SPLL is briefly outlined. An arbitrary grid voltage can be represented as:

$$v_{sa}(t) = V_1 \sin(\omega_0 t + \phi_1) + \sum_{n=2}^{N} V_n \sin(n\omega_0 t + \phi_n),$$

(7)

Fig. 2. Proposed controller architecture for the multilevel DSTATCOM

Fig. 3. Control strategies for the DSTATCOM implemented in the digital signal processor (DSP)

Fig. 4. Diagram of the single-phase software phase-locked loop (SPLL) for grid synchronization

where  $\varphi_1$  and  $\varphi_n$  are the initial phase angle of the fundamental and the *n*th order harmonic component, respectively. Here the DC offset is neglected for the sake of brevity. The phase angle of the fundamental component voltage can be expressed as:

$$\phi_1 = \Delta \theta_1 + \theta_1, \tag{8}$$

where  $\theta_1$  and  $\Delta \theta_1$  represent the estimated phase angle of the fundamental grid voltage and the estimation error, respectively, obtained from the SPLL. Therefore, substituting (8) back to (7), we get:

$$v_{sa}(t) = V_1 \cos(\Delta \theta_1) \sin(\omega_0 t + \theta_1) + V_1 \sin(\Delta \theta_1) \cos(\omega_0 t + \theta_1) + \sum_{n=2}^N V_n \sin(n\omega_0 t + \phi_n).$$

(9)

From Equation (9), it can be deduced that the fundamental component of the original signal can be regenerated by adjusting coefficients  $V_1 \cos(\Delta \theta_1)$ ,  $V_1 \sin(\Delta \theta_1)$ , even though the phase angle of the original signal is unknown. The objective of the proposed SPLL is to reconstruct the phase angle of the fundamental grid voltage  $\varphi_1$  using the least mean square (LMS) algorithm [17–19]. Therefore, the fundamental grid voltage can be expressed by the inner product of two vectors, namely, the vector of trigonometric functions and the vector of weights in the LMS-based weights updating algorithm [17, 19]. The weight vector W denotes the coefficients of the corresponding trigonometric functions. From the aforementioned definition, the fundamental grid voltage can be expressed as:

$$\hat{Y} = W^T X, \tag{10}$$

where  $\hat{Y}$  is the estimated output of the fundamental grid voltage by using the LMS-based weights estimation

L. Xu, Y. Han, C. Chen, J. Pan, G. Yao, L. Zhou, M. M. Khan

scheme. The vector W and X corresponding to the weight vector and the input vector, respectively, are represented as:

$$\begin{cases} W = [V_1 \cos(\Delta \theta_1), V_1 \sin(\Delta \theta_1)] = [\omega_{a1}, \omega_{b1}], \\ X = [\sin(\omega_0 t + \theta_1), \cos(\omega_0 t + \theta_1)]^T. \end{cases}$$

(11)

The weights updating process of the proposed SPLL is similar to the adaptive linear neural network (ADALINE) in [18, 19], which was based on the recursively searching the optimal point of the quadratic cost function, defined by the least-mean square (LMS) error of the harmonic estimation algorithm. It is worth noting that the salient difference between the ADALINE scheme and the proposed SPLL algorithm is that, the frequency and phase angle signals utilized in the LMS weights updating process were assumed to be constant. However, in case of the SPLL, the frequency and phase angle of the fundamental grid voltage is recursively updated by the loop filter (LF) and voltage controlled oscillator (VCO) of the PLL, denoted by the proportional-integral (PI) controller and the discrete integrator in Fig. 4a, respectively. In other words, the LMSbased weights updating procedure is utilized as the phase detector (PD) for the PLL, denoted in Fig. 4b, which generate the error signal to drive the loop filter (LF) and voltage controlled oscillator (VCO), according to the initial definition of PLL. The graphical interpretation of the proposed SPLL is shown in Fig. 4. It can be observed that the proposed SPLL resembles the existing PLLs in terms of loop filter (LF) and voltage controlled oscillator (VCO) structures. However, the phase detector (PD) section of the conventional PLL is replaced by the LMS recursive weights updating algorithm of the grid voltage, as shown in Fig. 4b.

### 3.2 Current-loop control scheme

The system equation across the coupling inductance can be derived as:

$$v_{PCC} = v_{aN} + R \cdot i_c + L \cdot \frac{di_c}{dt}.$$

(12)

Applying Laplace transformation (s-domain transform) to (12), assuming  $v_{dr} = v_{PCC} - v_{aN}$ , the following equation can be obtained:

$$\frac{I_c(s)}{V_{dr}(s)} = \frac{1}{R + L \cdot s}.$$

(13)

Similar to the analysis adopted in [17], the inner current loop is depicted in Fig. 5. The open-loop transfer function for the current loop controller can be represented as:

$$G_{open}(s) = G_{cc}(s) \cdot \frac{1}{1 + T_d \cdot s} \cdot \frac{1}{R + L \cdot s}, \qquad (14)$$

Fig. 5. Simplified block diagram for the current loop controller

where  $T_d$  denotes the control delay, and  $G_{cc}(s)$  represents the transfer function of the current controller, which can be a proportional controller, proportional-integral (PI) controller, or proportional-resonant controller. The closedloop transfer function for the current tracking control can be denoted as:

$$G_{close}(s) = \frac{G_{open}(s)}{1 + G_{open}(s)}.$$

(15)

Next, the current tracking performance is studied for the different regulators, namely, the P, PI and PR regulators.

The proportional controller provides a simple solution for current tracking, assuming the control gain is  $K_{cc}$ , then the closed-loop transfer function for the P controller is derived as:

$$G_{close}^{P}(s) = \frac{K_{cc}}{(T_{d} \cdot L) \cdot s + (T_{d} \cdot R + L) + (R + K_{cc})}.$$

(16)

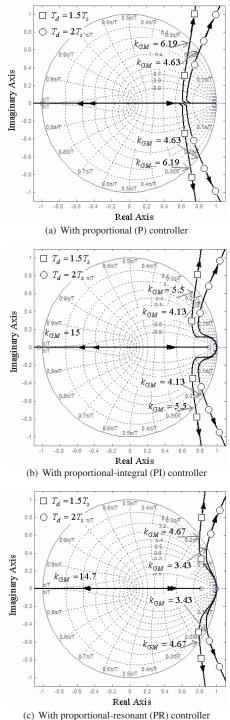

Figure 6 shows the closed-loop root locus of the currentloop controller under different regulators, namely, the P, PI and PR controllers. It can be observed from Fig. 6a that, when the proportional controller is used for current reference tracking, the maximum controller gains  $k_{GM}$  are 6.19 and 4.63 when  $T_d = 1.5T_s$  and  $T_d = 2T_s$ , respectively. The critical gains in Fig. 6a impose the upper limit for the current loop regulator to ensure the closed-loop stability. Normally, a higher controller gain implies a faster dynamic response under transient disturbance of the current reference, but at the tradeoff of reduced stability margin. Therefore, if the P controller is selected for the multilevel DSTATCOM, a tradeoff must be reached between the dynamic response and closed-loop stability. For instance, the controller gain corresponding to the damping ratio  $\xi = 0.707$  can be used for the practical system. It can also be observed from Fig. 6a that the control delay deteriorates the stability margin. Hence the delay due to the A/D sampling, computation of the control algorithm and PWM generation should be minimized to enhance the stability margin.

(c) with proportional-resonant (FK) controller

Fig. 6. Root locus analysis of the current-loop control scheme

The proportional-integral (PI) is a well-known regulator which is widely utilized for error tracking in grid-tie converter applications. Similar to the analysis of the P controller, the closed-loop transfer function for the current tracking control under the proportional-integral (PI) control is derived as:

$$G_{close}^{PI}(s) = \frac{K_{cc}(\tau s + 1)}{\{(\tau T_d L)s^3 + (T_d R + L)\tau s^2 + +(R + K_{cc})\tau s + K_{cc}\}}.$$

(17)

where the transfer function of the proportional-integral (PI) is represented as:

$$G_{PI}(s) = K_{cc}(1 + \frac{1}{\tau s}).$$

(18)

The parameter  $\tau$  represents time constant for the integrator of the PI regulator. Fig. 6b shows the root locus plot of the closed-loop current tracking scheme using PI regulator when the time constant is selected as  $\tau = 10T_s$ . It can be observed that the critical controller gains are 5.5 and 4.13, when the control delays are  $T_d = 1.5T_s$  and  $T_d = 2T_s$ , respectively. Similar to the case of the P controller, the control delay also deteriorates the stability margin. The time constant  $(\tau)$  of the PI regulator also shows a significant impact on the critical gains, smaller time constant implies faster integration, but at the tradeoff of reduced stability margin. On the other hand, higher time constant would result in sluggish integration, which relaxes the gain margin. The critical gains of the PI regulator under different time constants are listed in Table 1. It is worth noting that with the increase of the integration time constant, the critical gain also increases. Moreover, for the same integration time constant, longer control delays implies smaller stability margin.

The PI regulator shows unsatisfactory performance for current tracking in case of alternating reference signal,

Table 1. The critical gains  $(K_{GM})$  obtained from the root locus analysis for the proportional-integral (PI) controller and proportional-resonant (PR) controller under different control delays  $(T_d)$

| Time<br>constant | PI Controller  |              | PR Controller  |            |

|------------------|----------------|--------------|----------------|------------|

| $(\tau)$         | $T_d = 1.5T_s$ | $T_d = 2T_s$ | $T_d = 1.5T_s$ | $T_d=2T_s$ |

| $5T_s$           | 4.77           | 3.37         | 2.19           | 0.68       |

| $8T_s$           | 5.42           | 3.96         | 4.35           | 2.83       |

| $10T_s$          | 5.5            | 4.13         | 4.67           | 3.43       |

| $20T_s$          | 5.97           | 4.39         | 5.54           | 4.03       |

| $30T_s$          | 6.05           | 4.69         | 6.03           | 4.41       |

| $50T_s$          | 6.22           | 4.58         | 6.04           | 4.46       |

| $100T_{s}$       | 6.23           | 4.56         | 6.05           | 4.55       |

Note:  $T_s$  represents the sampling time of the A/D channels.

which results in remarkable phase and amplitude tracking errors. The proportional resonant (PR) current controller, on the other hand, achieves perfect tracking performance for the alternating reference signal, which mimics the PI regulator implemented in the synchronous rotating reference frame with the following transfer function:

$$G_{PR}(s) = K_{cc} \left[1 + \frac{1}{\tau} \cdot \frac{2s}{(s^2 + \omega_0^2)}\right],$$

(19)

where the parameter  $\tau$  is also defined as the time constant for the resonant controller, and  $\omega_0$  denotes the angular frequency of fundamental grid voltage. Hence the PR regulator achieves zero steady-state error for the alternating signal at  $\omega_0$  due to the infinite open-loop gain introduced by the PR current regulator. Substituting the equation (19) into the transfer function of the closed-loop current tracking scheme, we get:

$$\begin{aligned} G_{close}^{PR}(s) &= \\ \frac{\tau K_{cc} s^2 + 2K_{cc} s + \tau K_{cc} \omega_0^2}{\{(\tau T_d L) s^4 + (T_d R + L) \tau s^3 + [(R + K_{cc}) \tau + T_d L \omega_0] s^2 + [(T_d R + L) \tau \omega_0^2 + 2K_{cc}] s + \tau \omega_0^2 (R + K_{cc}) \}} \end{aligned}$$

(20)

Fig. 6c shows the root locus plot of the closed-loop current tracking scheme using PR regulator when the time constant is selected as  $\tau = 10T_s$ . It can be observed that the critical controller gains are 4.67 and 3.43, when the control delays are  $T_d = 1.5T_s$  and  $T_d = 2T_s$ , respectively. The same effect of the reduced stability margin to control delay can be noticed for the PR regulator, as shown in Table 1. Moreover, it is found that the time constant  $\tau$  also shows similar impact on the stability margin as compared to the case of PI regulator.

#### 3.3 Dc-link voltage balancing (VB) control strategy

In the previous section, the current tracking control scheme has been analyzed using root locus plots of the closed-loop transfer function. Another importance aspect for ensuring stable operation of the proposed multilevel DSTATCOM is the dc-link voltage balancing control strategy. It is well-know that the active and reactive power flow between the inverter and the grid depends on the magnitude and phase of the synthesized multilevel voltage  $v_{aN}$  with respect to the grid voltage  $v_{PCC}$ . The multilevel voltage  $v_{aN}$  is the sum of the output voltage of the individual H-bridge modules (Fig. 1). To better illustrate power flow of the multilevel inverter, the average output voltage for each H-bridge modules is denoted as:

$$v_{av} = \frac{1}{3} \sum_{i=1}^{3} v_{ai} = \frac{1}{3} v_{aN}.$$

(21)

Figure 7 shows the phasor representation of the output voltage waveform of each H-bridge module. The phase

Fig. 7. Phasor representation of the individual H-bridge voltage with respect to its injection current

displacement of the grid voltage and the reactive current  $i_c$  is also illustrated. The active and reactive power delivered by the *i*th H-bridge to the grid can be represented as:

$$\begin{cases} P_i = V_{ai} \cdot I_c \cdot \cos \phi_i, \\ Q_i = V_{ai} \cdot I_c \cdot \sin \phi_i, \end{cases}$$

(22)

where  $\varphi_i$  represents the phase angle between the multilevel DSTATCOM current and the output voltage of each H-bridge module. It can be observed from the phasor diagram in Fig. 7a that the active and reactive power delivered by each module is proportional to the in-phase and orthogonal component of its output voltage with respect to the current. Fig. 7b shows the fictitious *d-q* reference frame which depicts the active and reactive component of the output voltage, denoted by the *d*- and *q*-axis component, respectively, which is a projection of the individual output voltage to the two axes. Hence the active and reactive powers loaded by the *i*th H-bridge module can be derived by:

$$\begin{cases}

P_i = V_{ai}^d \cdot I_c, \\

Q_i = V_{ai}^q \cdot I_c.

\end{cases}$$

(23)

It can be noticed from the above equation, that in order to equally distribute the reactive power among each Hbridge modules, the q-axis component of the output voltage  $v_{ai}$  (i = 1, 2, 3) should be same. Nevertheless, the active power absorption by each H-bridge modules may not be identical to each other due to non-ideal dc-link parameters, such as IGBT or diodes conduction losses, which is reflected by the unequal d-axis projection of the output voltage  $v_{ai}$ . Therefore, the actual active power absorption by the *i*th H-bridge module can be rewritten in terms of the average output voltage  $v_{av}$ , as:

$$P_i = V_{ai}^d \cdot I_c = (V_{av}^d + \Delta V_{av}^d) \cdot I_c = P_{av} + \Delta P_i, \quad (24)$$

where  $P_{av}$  represents the average active power absorption of the H-bridge modules, and  $\Delta P_i$  represents the difference between the individual active power and the average L. Xu, Y. Han, C. Chen, J. Pan, G. Yao, L. Zhou, M. M. Khan

active power absorption. In order to achieve active power balance among the modules, the summation of the *d*-axis projections of output voltage of each H-bridge modules should be zero. In other words, once the total active power absorption of the multilevel DSTATCOM is obtained, the dc-link voltage balancing control scheme serves the purpose of equally distributing the reactive power among individual H-bridge modules by dynamically interchanging the active power among each modules. Followed by this principle, the control scheme is devised as shown in Fig. 3. It shows that the total active power absorption of the DSTAT-COM is balanced by regulating the average dc-link voltage using a proportional-integral (PI) controller, and the output of the PI regulator is multiplied by a sine function synchronized with the grid using software phase-locked loop (SPLL), which is completely same as that of the conventional grid-connected converters. The voltage balancing (VB), on the other hand, is achieved by regulating individual dc-link voltage with respect to the average dc-link voltage in order to regulate the active power distribution among the H-bridge modules. The proportional-integral (PI) regulators are also used and the output of the PI regulators are multiplied with a cosine function synchronized with the grid voltage, which projects the control error to the orthogonal axis with respect to the grid voltage, i.e., the *d*-axis denoted by Fig. 7.

Once again referring to Fig. 3, it is worth noting that the PI regulators for the voltage balancing signals, denoted by  $U_{VB1}$ ,  $U_{VB2}$ ,  $U_{VB3}$ , can be simplified by substituting  $U_{VB3} = -(U_{VB1} + U_{VB2})$  to reduce the computational load. After the voltage balancing signals are obtained, the total synthesized modulation signals can be derived as:

$$S_{ei} = \frac{1}{v_{dci}} (U_{VBi} + U_{cc}), \quad i = 1, 2, 3,$$

(25)

where  $U_{cc}$  represents the output signal of the current loop controller.

#### **4 SIMULATION RESULTS**

This section reports the simulation results of the proposed multilevel DSTATCOM under various operating conditions. The parameters of the power-stage and the controllers are listed in Tables 2 and 3, respectively. The sim-

Table 2. The specifications of the multilevel DSTATCOM

| Coupling inductor ( <i>L</i> )         | $500 \ \mu H$  |

|----------------------------------------|----------------|

| Dc-link Capacitor ( <i>Cdc</i> )       | $2000 \ \mu F$ |

| Switching frequency of IGBT $(f_{sw})$ | 2.5 kHz        |

| Sampling frequency (fsample)           | 15 kHz         |

| Grid voltage at PCC (vPCC)             | 100 V (RMS)    |

| Dc-link voltage reference (Vdc)        | 50 V           |

| 2.5    |             |

|--------|-------------|

|        | $10T_s$     |

| 1018   |             |

| 0.6    |             |

|        | $1000T_{s}$ |

| 0.2    |             |

|        | $2000T_{s}$ |

| 200018 |             |

|        |             |

Table 3. The controller parameters for the multilevel

DSTATCOM

ulation results under ideal H-bridge modules and non-ideal modules are investigated. In case of the ideal H-bridge module scenarios, the same dc-link capacitors and equivalent power losses are assumed across the individual H-bridges. Besides, in case of non-ideal H-bridge modules, the 20% difference is considered for the dc-link capacitors and equivalent power losses are considered, i.e., the dc-link capacitors are 2000  $\mu$ F, 2400  $\mu$ F and 1600  $\mu$ F for each module, respectively. In order to further investigate the performance of the multilevel DSTATCOM, the simulation results under different modulation indices are also provided.

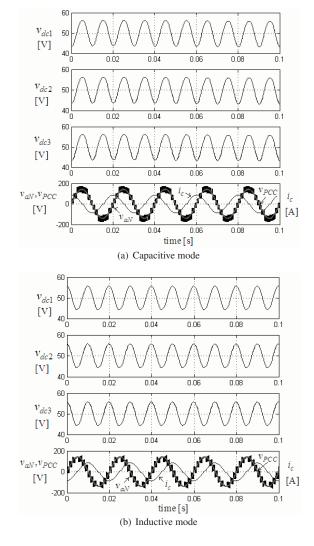

Figure 8 shows the simulation results of the DSTAT-COM for the capacitive and inductive operational modes under ideal H-bridge scenarios. Fig. 8a shows the simulation results of capacitive operation mode, i.e., the DSTAT-COM generates leading reactive current with respect to the grid voltage at the point of common coupling. The individual dc-link voltages, the synthesized multilevel output voltage and the injection current of the DSTATOM are depicted in Fig. 8a.

It can be observed that the dc-link voltages are controlled to track the reference voltage, with a ripple of double fundamental frequency due to the reactive current generated by the system. The amplitude of the voltage ripples can be reduced if the higher value dc-link capacitors are adopted, or if the reference dc-link voltage is increased to higher voltage levels. Moreover, the synthesized output voltage  $v_{aN}$  shows excellent seven-level wave shape, as predicted in the theoretical analysis. The PCC voltage  $v_{PCC}$ , as denoted by the gray color in Fig. 8a, is almost in phase with the synthesized multilevel output voltage. Since the active power exchange between the multilevel DSTATCOM with the grid is determined by the phase angle difference between  $v_{PCC}$  and the fundamental component of the multilevel voltage, hence it can be noticed from Fig. 8a that the active power consumption of the DSTAT-

Fig. 8. Simulation results of the multilevel DSTATCOM under ideal H-bridge modules

COM is very small. The compensating current  $i_c$ , is amplified by a factor of 5 for better illustration, and it shows an 90 degree leading the phase angle of the PCC voltage  $v_{PCC}$ .

Figure 8b shows the simulation results when the multilevel DSTATCOM generates lagging reactive current. The dc-link voltages are almost same as the case of generating leading reactive current (Fig. 8a). Whereas, it can be observed that the voltage ripples across the dc-link capacitors in Fig. 8b show opposite phase angles compared to Fig. 8a, which result in a different wave shape for the synthesized multilevel voltage. It is worth noting that the fundamental component of the multilevel output voltage is almost in phase with the grid voltage ( $v_{PCC}$ ). Therefore, it can be concluded from Fig. 8 that the proposed multilevel DSTATCOM can be used to generate leading or lagging reactive current, and the dc-link stabilization can be easily achieved.

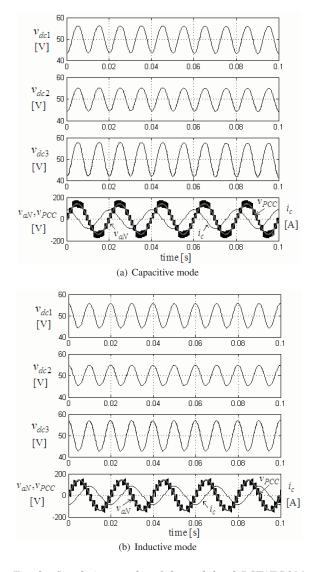

Figure 9 shows the simulation results of the DSTAT-COM under non-ideal H-bridge module scenarios by changing the dc-link capacitors of the second and third modules to 2400  $\mu$ F and 1600  $\mu$ F, respectively. The dc-link capacitor across the first H-bridge remains to be 2000  $\mu$ F. It is depicted in Fig. 9 that the dc-link with a higher value capacitance shows lower voltage ripple in magnitude, and the third unit shows the largest voltage fluctuations among

the three H-bridges. The dc-link voltage waveforms under capacitive and inductive operation mode show similar characteristics compared to Fig. 8. It is verified that the dclink voltage stabilization can also be achieved under nonideal H-bridge module scenarios.

To further test the performance of the DSTATCOM, the effect of the modulation index is studied by changing the grid voltage  $v_{PCC}$ . Figure 10 shows the simulation results of the system when the modulation index (*m*) is changed to 0.56, and both the capacitive and inductive operation modes are reported. It can be noticed from Fig. 10 that the dc-link voltages shows similar waveforms compared to the case in Fig. 8. Nevertheless, the synthesized multilevel

Fig. 9. Simulation results of the multilevel DSTATCOM under non-ideal H-bridge modules

Fig. 10. Simulation results of the multilevel DSTATCOM when the modulation index m=0.56

voltage  $v_{aN}$  reduced to five levels, which implies that the quality of the synthesized voltage degrades. Moreover, the simulation results in Fig. 10 also imply that, for the practical applications, the modulation index (m) should be properly selected to ensure the quality of the output multilevel voltage.

In other words, when the grid voltage is determined, the selection of dc-link voltage is directly associated with the modulation index (m), which influences the output multilevel voltage. For the N-block multilevel inverter with equal dc-link voltages, 2N + 1 level output voltage can be synthesized [14, 15]. Hence the filtering inductance would be minimized to reduce the cost, weight and volume of the system. Excessive small modulation index (Fig. 10), would not violate the closed-loop stability, but the performance of the multilevel DSTATCOM degrades.

## **5 EXPERIMENTAL RESULTS**

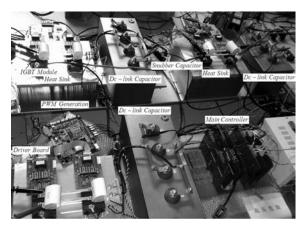

To verify the validity and effectiveness of the proposed multilevel DSTATCOM and its control strategies, a prototype system is built as shown in Fig. 11. The parameters of the power stage and the controller parameters are listed in Tables 2 and 3, which is consistent with the simulation section.

Fig. 11. A photo of the experimental setup

As depicted in Fig. 2, the proposed multilevel DSTAT-COM is implemented using the digital signal processor (DSP) from Texas Instruments, where the sampled dclink voltages, the grid voltage and the inverter current are processed using the devised control algorithm. The DSP is responsible for initialization, A/D sampling, overcurrent/voltage protection, dc-link voltage balancing control as well as the current loop tracking control algorithms. The obtained modulation signals, denoted by  $S_{e1}$ ,  $S_{e2}$  and  $S_{e3}$  in Fig. 2 are sent to the field programmable gate array (FPGA), which is utilized to generate phase-shifted carriers of 2.5 kHz, and these carriers are compared with the modulation signal  $S_{e1}$ ,  $S_{e2}$  and  $S_{e3}$  to generate switching signals for each H-bridge modules.

It is worth noting that the unipolar PWM scheme is adopted for each H-bridge hence only two switching signals, or gating signals, are generated by the comparison logic, which denote the PWM signals for the left-side and right-side arm of the individual H-bridge unit. The generated gating signals are sent to the bottom level controller, denoted by "PWM Generation" in Fig. 11, to synthesize four channel PWM signals for each H-bridge. Moreover, to avoid direct conducting between the upper and lower IG-BTs across each H-bridge, the dead-time of 4  $\mu$ s is added in the bottom controller. Then these gating signals are sent to the driver circuit (2SD315AI-33) to drive the IGBTs. A detailed flowchart of the function blocks of the hardware is also illustrated in Fig. 2.

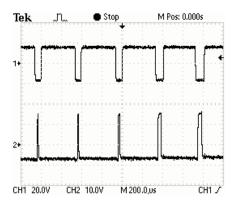

Figure 12 shows the gating signals for the left-side arm of the first H-bridge module. It can be observed that the

*Fig. 12. The gating signals for the left-side arm of the first H-bridge module*

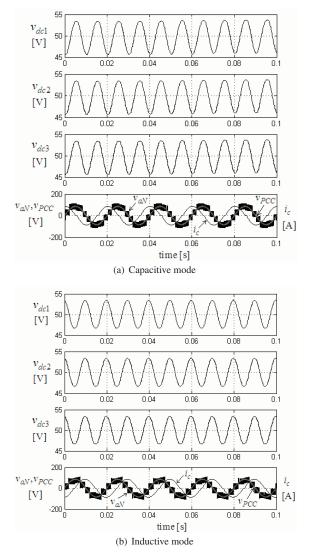

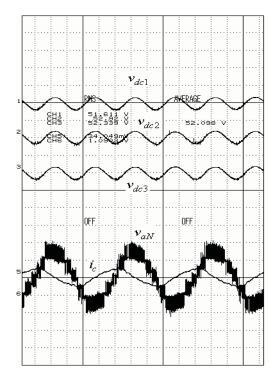

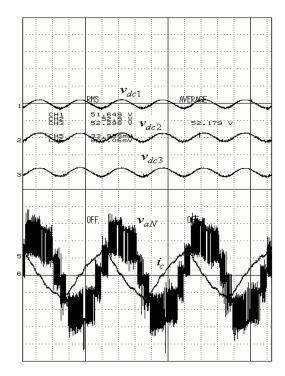

upper and lower IGBTs conduct interchangeably and the dead-time can also be observed. Figure 13 shows the experimental results of the multilevel DSTACOM when it generates leading reactive current. It is worth noting that the circuit parameters and the controller parameters are consistent with simulation section. The excellent dc-link voltage waveforms are obtained, which perfectly matches the theoretical analysis and the simulation results. Besides, the synthesized multilevel output voltage  $v_{aN}$  and the inverter current  $i_c$  are also depicted in Fig. 13. It shows that the seven level output voltage waveform is obtained and the inverter injection current is almost 90 degrees leading the synthesized multilevel voltage.

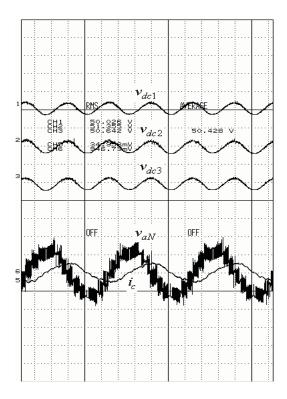

Figure 14 shows the experimental results of the multilevel DSTATCOM when it generates lagging reactive current. The dc-link voltage stabilization is also achieved and

Fig. 13. Experimental results of the multilevel DSTATCOM for the leading reactive current

the direction of the voltage fluctuation is out of the phase compared to the case of leading reactive current generation in Fig. 13. The synthesized multilevel output voltage and the injection current depicted in Fig. 14 matches the simulation results perfectly.

To test the performance of the multilevel DSTACOM under low modulation index scenario, the grid voltage at PCC is reduced to 75 V (RMS) while the reference voltage for the dc-link is also set as 50 V. As shown in Fig. 15, the lower modulation index indeed shows remarkable influence on the synthesized output voltage, which verifies the simulation results in the previous section. It can also be noticed that the dc-link voltage stabilization and reactive current generation is also achieved. Nevertheless, the synthesized multilevel voltage reduces to five levels, which is consistent with the theoretical analysis. One should be noted that for the practical multilevel DSTATCOM applications, the modulation index should be selected higher than 0.85 to ensure preferred multilevel voltage profile, i.e., the 2N + 1 level voltage for the N-block multilevel inverter system.

# 6 CONCLUSIONS

This paper proposes a novel static synchronous compensator for distribution system applications (DSTATCOM)

Fig. 14. Experimental results of the multilevel DSTATCOM for the lagging reactive current

based on the cascaded H-bridge multilevel inverter, which can be used for dynamic reactive power compensation for medium voltage electric power systems. The mathematical formulation of the DSTATCOM is presented using statespace representations. The control strategies are presented, which includes a new software phase-locked loop (SPLL) for grid synchronization, the proportional-resonant current controller and the voltage balancing algorithm. Extensive simulation results are provided to study the performance of the multilevel DSTACOM and a laboratory prototype system is also built for verification. The experimental results match the theoretical analysis and the simulation results perfectly, which validated the validity and effectiveness of the proposed system and its control strategies.

Fig. 15. Experimental results of the multilevel DSTATCOM when the modulation index m=0.56

#### REFERENCES

- [1] IEEE, IEEE Recommended Practice for Electric Power Systems in Commercial Buildings, 1990. IEEE Std-241.

- [2] IEEE, IEEE Recommended Practice for Electric Distribution for Industrial Plants, 1993. IEEE Std-141.

- [3] IEEE, IEEE Recommended Practice for Monitoring Electric Power Quality, 1995. IEEE Std-1159.

- [4] IEC, Electromagnetic Compatibility (EMC)-Part 3: Limits-Section 2: Limits for Harmonic Current Emissions (Equipment Input Current <16A per phase), 1995. IEC1000-3-2 Document.

- [5] A. Elnady and M. Salama, "Unified approach for mitigation voltage sag and voltage flicker using the dstatcom," *IEEE Transactions on Power Delivery*, vol. 20, no. 1, pp. 992– 1000, 2005.

- [6] Y. Han, L. Xu, G. Yao, L. Zhou, M. Khan, and C. Chen, "Flicker mitigation of arc furnace load using modified pq-r method," *Przeglad Elektrotechniczny*, vol. 85, no. 1, pp. 225–229, 2009.

- [7] Y. Han, L. Xu, W. Yun, G. Yao, L. Zhou, M. Khan, and C. Chen, "Power quality enhancement for automobile factory electrical distribution system-strategies and field practice," *Przeglad Elektrotechniczny*, vol. 85, no. 6, pp. 159– 163, 2009.

- [8] Y. Han, M. Khan, L. Xu, and G. Yao, "A new scheme for power factor correction and active filtering for six-

pulse converters loads," *Bulletin of the Polish Academy of Sciences-Technical Sciences*, vol. 57, no. 2, pp. 157–169, 2009.

- [9] R. Segundo, A. Medina, A. Ghosh, and G. Ledwich, "Stability analysis based on bifurcation theory of the dstatcom operating in current control mode," *IEEE Transactions on Power Delivery*, vol. 24, no. 3, pp. 1670–1678, 2009.

- [10] B. Singh and J. Solanki, "A comparison of control algorithms for dstatcom," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 7, pp. 2738–2745, 2009.

- [11] B. Singh, P. Jayaprakash, T. Somayajulu, and D. Kothari, "Reduced rating vsc with a zig-zag transformer for current compensation in a three-phase four-wire distribution system," *IEEE Transactions on Power Delivery*, vol. 24, no. 1, pp. 249–259, 2009.

- [12] Y. Han, L. Xu, G. Yao, L. Zhou, M. Khan, and C. Chen, "A novel modulation scheme for dc-voltage balancing control of cascaded h-bridge multilevel apf," *Przeglad Elektrotechniczny*, vol. 85, no. 5, pp. 81–85, 2009.

- [13] A. Shukla, A. Ghosh, and A. Joshi, "Control schemes for dc capacitor voltages equalization in diode-clamped multilevel inverter-based dstatcom," *IEEE Transactions on Power Delivery*, vol. 23, no. 2, pp. 1139–1149, 2008.

- [14] R. Gupta, A. Ghosh, and A. Joshi, "Switching characterization of cascaded multilevel-inverter-controlled systems," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 3, pp. 1047–1058, 2009.

- [15] M. Hagiwara and H. Akagi, "Control and experiment of pulsewidth modulated modulator multilevel converters," *IEEE Transactions on Power Electronics*, vol. 24, no. 7, pp. 1737–1746, 2009.

- [16] P. Lezana and G. Ortiz, "Extended operation of multicell converters under fault condition," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 7, pp. 2697–2703, 2009.

- [17] Y. Han, L. Xu, M. Khan, L. Zhou, G. Yao, and C. Chen, "A novel synchronization scheme for grid-connected converters by using adaptive linear optimal filter based pll (alofpll)," *Simulation Modelling Practice and Theory*, vol. 17, no. 8, pp. 1299–1345, 2009.

- [18] Y. Han, M. Khan, G. Yao, L. Zhou, and C. Chen, "A novel harmonic-free power factor corrector based on t-type apf with adaptive linear neural network (adaline) control," *Simulation Modelling Practice and Theory*, vol. 16, no. 9, pp. 1215–1238, 2008.

- [19] Y. Han, M. Khan, L. Xu, L. Zhou, G. Yao, and C. Chen, "A novel control strategy for active power filter using synchronous reference frame adalines," *International Review of Electrical Engineering (IREE)*, vol. 3, no. 4, pp. 629–645, 2008.

Lin Xu received the B. E. degree in electrical engineering from University of Electronic Science and Technology of China, Chengdu, China, in 2006, and is currently working toward the Ph.D. degree in power system and its automation at Shanghai JiaoTong University, Shanghai, China. Her research interests include power system automation, power quality, highperformance power converters, voltage source inverters, dynamic voltage restorer and active power filters.

Gang Yao received the B. E. degree in electrical engineering from China University of Mining and Technology, Xu Zhou, China, in 2002, and received the Ph. D. degree in electrical engineering from Shanghai JiaoTong University (SJTU), Shanghai, China, in 2006. He joined the faculty of electrical engineering of SJTU in 2006. His research interests include power electronics, power system automation, high-performance power converters, such as static var compensators

and active power filters. Currently he is a lecturer in electrical engineering within the faculty of electrical engineering, SJTU.

Yang Han received the B. E. degree in electrical engineering from University of Electronic Science and Technology of China (UESTC), Chengdu, P. R. China, in 2004, and joined the Faculty of the School of Mechatronics Engineering, UESTC in 2004. Now, he is working toward the Ph. D. degree in "power system and its automation" at Shanghai JiaoTong University, Shanghai, P. R. China. He is a student member of IEEE, and a member of IEEE Industrial Electronics society and IEEE power electronics soci-

ety. He has published several high-quality papers in ISI-indexed journals and IEEE conferences. He won the "National Excellent Student" scholarship in 2007. In 2008, he got the "Excellent Paper Award" in the "Fourth International Power Quality Forum", Yangzhou, Jiangshu Province, P. R. China. He won the first prize in the National DSP contest sponsored by Texas Instrument in 2008. In 2009, he won the second prize in "National Energy-Efficiency Contest" sponsored by the Schneider Electric Inc. His research interests include power system automation, power quality, highperformance power converters, voltage source inverters and multilevel converters for static var compensations as well as active power filters applications.

**Chen Chen** received the M. S. degree in electrical engineering from Tsinghua University, Bei-Jing, China, in 1966 and the Ph. D. degree in electrical engineering from Purdue University, West Lafayette, IN, in 1984. Currently, she is a full Professor of Electrical Engineering, Shanghai JiaoTong University, Shanghai, China. Her research interests include power system stability analysis, flexible ac transmission systems, application of artificial neural networks in power syst

tem and power electronic systems. She has published more than 100 technical papers in various conferences and international journals and is a senior member of IEEE since 1997.

Jun-Min Pan received the B. E. degree in electrical engineering from Shanghai JiaoTong University in 1970. He was a visiting scholar in Maryland University during 1984-1987. He became a full professor in 1994, and a Ph.D supervisor in 1996. His research areas include brushless dc motors, maximum power point tracking algorithms for photovoltaic systems, current source inverter and three-dimension tracking systems, etc. He is a senior member of IEEE.

Li-Dan Zhou received M. E. degree in electrical engineering from Xi'an University of Technology, Xi'an, China, in 1999, worked with the Hunan Institute of Engineering from 1999 to 2002, received the Ph. D. degree in electrical engineering from Shanghai JiaoTong University (SJTU), Shanghai, China, in 2006 and joined the faculty of electrical engineering of SJTU in 2006. Her research interests include power electronics, power system automation, high-performance power converters, such as static var compensators

and active power filters. Currently she is a lecturer in electrical engineering within the faculty of electrical engineering, SJTU.

**M. M. Khan** received the Ph. D. degree from Shanghai JiaoTong University (SJTU), Shanghai, China, in 2002, worked as post-doctoral in SJTU from 2002 to 2005, and then joined the faculty of electrical engineering of SJTU. His research interests include power electronics, dc-dc converters, static var compensation and active filtering. He gives lectures to the graduate students in the area of power electronics and power system automation. He has published lots of high quality papers in international journals. Currently he is an associate professor in electrical engineering within the department of electrical engineering, SJTU.

#### **AUTHORS' ADDRESSES**

Lin Xu<sup>1</sup>, B.Sc.E.E. Yang Han<sup>1,2</sup>, Ph.D.E.E. Prof. Chen Chen<sup>1</sup>, Ph.D.E.E. Jun-Min Pan<sup>1</sup>, Ph.D.E.E. Gang Yao<sup>1</sup>, Ph.D.E.E. Li-Dan Zhou<sup>1</sup>, Ph.D.E.E. Assoc. Prof. M. M. Khan<sup>1</sup>, Ph.D.E.E. <sup>1</sup>Department of Electrical Engineering. Shanghai JiaoTong University, #800 DongChuan Road, Shanghai, 200240, P. R. China, <sup>2</sup>School of Mechatronics Engineering, University of Electronic Science and Technology of China, North JianShe Road, Chengdu, 610054, P. R. China contact address: Yang Han, Room 601, No.7 Dormitory, XuHui Campus, Shanghai JiaoTong University, #1954 HuaShan Road, Shanghai, 200030, P. R. China, e-mails: hanyang\_facts@hotmail.com (Yang Han), xingxuepiaoling@gmail.com (Lin Xu)

> Received: 2009-09-09 Accepted: 2010-01-06