# Symmetry Reduction and Compositional Verification on Timed Automata

by

## Hoang Linh Nguyen

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Mathematics in Computer Science

Waterloo, Ontario, Canada, 2017

© Hoang Linh Nguyen 2017

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### Abstract

This thesis is about techniques for the analysis of concurrent and real-time systems.

As the first contribution, we describe a technique that incorporates automatic symmetry detection and symmetry reduction in the analysis of systems modeled by timed automata. First, our approach detects structural symmetries arising from process templates of real-time systems, requiring no additional input from the user. Then, the technique involves finding all variables of type *process identifier* and computing a set of generators that forms a group of automorphisms. Our technique is fully automatic, and not restricted to fully symmetric systems.

The second contribution of this thesis is that we combine elements of compositional proof, abstraction and local symmetry to decide whether a safety property holds for every process instance in a parameterized family of real-time process networks. Analysis is performed on a small cut-off network; that is, a small instance whose compositional proof generalizes to the entire parametric family. Our results show that verification is decidable in time polynomial in the state space of the "cut-off" instance. Then we apply these ideas to analyze Fischer's protocol, CSMA/CD protocol and Train-Bridge protocol.

#### Acknowledgements

First of all I want to thank my supervisor, Prof Richard Trefler. This thesis would never be completed without his guiding and support. I have learnt a lot about formal method and verification during two years we have worked together and I hope that one day I will be a good researcher as he is. I would like to thank all current and former members of the PAT group at National University of Singapore (NUS), especially Dr Khanh Nguyen and Prof Sun Jun. I am also grateful to my colleague, Joe Scott, for fruitful discussions.

Also I would like to thank everyone at David R. Cheriton School of Computer Science for making the department such an enjoyable environment.

# **Table of Contents**

| List of Tables ix |       |        |                                               |   |

|-------------------|-------|--------|-----------------------------------------------|---|

| Li                | st of | Figure | es<br>S                                       | x |

| 1                 | Intr  | oducti | on                                            | 1 |

|                   | 1.1   | Backgr | round and Motivation                          | 1 |

|                   | 1.2   | Summ   | ary of Contributions                          | 3 |

|                   | 1.3   | Thesis | Outline and Overview                          | 3 |

|                   | 1.4   | Relate | d Work                                        | 4 |

|                   |       | 1.4.1  | Partial-order Reduction                       | 4 |

|                   |       | 1.4.2  | Symmetry Reduction                            | 4 |

|                   |       | 1.4.3  | Symbolic Model-checking                       | 5 |

|                   |       | 1.4.4  | Approximation Methods                         | 5 |

|                   |       | 1.4.5  | Efficient Representation of Clock Constraints | 5 |

|                   |       | 1.4.6  | Symmetry Detection                            | 5 |

|                   | 1.5   | Public | ation from The Thesis                         | 6 |

| 2                 | Bac   | kgrour | nd                                            | 7 |

|                   | 2.1   | Timed  | Automata                                      | 7 |

|                   |       | 2.1.1  | A Brief Introduction to Timed Automata        | 7 |

|                   |       | 2.1.2  | Semantics of Timed Automata                   | 9 |

|   | 2.2            | Zone and Difference Bound Matrices                   |              | 14 |

|---|----------------|------------------------------------------------------|--------------|----|

|   |                | 2.2.1 Canonical DBMs                                 |              | 14 |

|   |                | 2.2.2 Operations on DBMs                             |              | 15 |

|   | 2.3            | Basics of Model Checking in Timed Auton              | ata          | 17 |

|   | 2.4            | System Modeling                                      |              | 18 |

|   | 2.5            | CSMA / CD Protocol                                   |              | 20 |

| 3 | $\mathbf{Syn}$ | mmetry Reduction in Timed Automata                   |              | 23 |

|   | 3.1            | A Theory of Symmetry                                 |              | 23 |

|   | 3.2            | 2 Symmetry Reduction                                 |              | 25 |

|   | 3.3            | Representative Function                              |              | 27 |

|   | 3.4            | Fischer's Protocol                                   |              | 29 |

|   | 3.5            | Extraction of Automorphisms                          |              | 30 |

|   |                | 3.5.1 State Swap $\ldots$ $\ldots$ $\ldots$ $\ldots$ |              | 30 |

|   |                | 3.5.2 Action of State Swap on Process Te             | emplate      | 32 |

|   |                | 3.5.3 Automorphisms $\ldots$ $\ldots$ $\ldots$       |              | 33 |

|   |                | 3.5.4 Group of Automorphisms                         |              | 33 |

| 4 | Syn            | mmetry Reduction Package in PAT                      |              | 35 |

|   | 4.1            | Dining Philosopher                                   |              | 35 |

|   | 4.2            | 2 Symmetry Detection In The Specification            |              | 37 |

|   |                | 4.2.1 Step 1: Detection of <i>pid</i> Variables      |              | 37 |

|   |                | 4.2.2 Step 2: Compute a Set of Possible              | Permutations | 39 |

|   |                | 4.2.3 Step 3: Compute a Set of Generato              | rs           | 40 |

|   | 4.3            | Generate The Symmetry-reduced State Sp               | ace          | 42 |

|   |                |                                                      |              |    |

| 5 | Par | ameterized Compositional Model Checking in Timed Automata | 44 |

|---|-----|-----------------------------------------------------------|----|

|   | 5.1 | Preliminaries                                             | 45 |

|   |     | 5.1.1 Process                                             | 45 |

|   |     | 5.1.2 Internal State                                      | 45 |

|   |     | 5.1.3 Neighborhood                                        | 46 |

|   |     | 5.1.4 Local State                                         | 46 |

|   |     | 5.1.5 Inductive Invariant                                 | 46 |

|   |     | 5.1.6 Interleaved Composition of Processes                | 46 |

|   |     | 5.1.7 Compositional Invariants                            | 47 |

|   |     | 5.1.8 Parameterized Compositional Invariants              | 47 |

|   |     | 5.1.9 Compositional Cutoff                                | 47 |

|   | 5.2 | Local Symmetry                                            | 48 |

|   | 5.3 | Parameterized Network Families                            | 49 |

| 6 | Ver | ification for Fischer's Protocol                          | 51 |

|   | 6.1 | Modeling Process Behavior                                 | 51 |

|   | 6.2 | Modeling Fischer's Protocol                               | 52 |

|   | 6.3 | Verification Properties                                   | 52 |

|   | 6.4 | Symmetry Detection                                        | 53 |

|   | 6.5 | Symmetry Reduction and Experimental Results               | 54 |

|   | 6.6 | Compositional Verification                                | 55 |

| 7 | Ver | ification for CSMA / CD Protocol                          | 57 |

|   | 7.1 | Model For CSMA/CD Protocol                                | 57 |

|   |     | 7.1.1 Modeling Sender Behavior                            | 60 |

|   |     | 7.1.2 Modeling Bus Behavior                               | 60 |

|   |     |                                                           |    |

|   |     | 7.1.3 Modeling CSMA/CD Protocol                           | 62 |

|   | 7.3   | Symmetry Detection                   | 62 |

|---|-------|--------------------------------------|----|

|   | 7.4   | Experimental Results                 | 63 |

|   | 7.5   | Compositional Verification           | 64 |

| 8 | Ver   | ification for Train-Bridge Protocol  | 66 |

|   | 8.1   | Model For Train-Bridge Protocol      | 66 |

|   |       | 8.1.1 Modeling Train Behavior        | 67 |

|   |       | 8.1.2 Modeling Bridge Behavior       | 68 |

|   |       | 8.1.3 Modeling Train-Bridge Protocol | 68 |

|   | 8.2   | Verification Properties              | 69 |

|   | 8.3   | Symmetry Detection                   | 70 |

|   | 8.4   | Experimental Results                 | 71 |

|   | 8.5   | Compositional Verification           | 72 |

| R | efere | nces                                 | 77 |

### viii

# List of Tables

| 6.1 | Experimental Results for Fischer's Protocol    | 55 |

|-----|------------------------------------------------|----|

| 7.1 | Experimental Results for CSMA/CD Protocol      | 64 |

| 8.1 | Experimental Results for Train-Bridge Protocol | 71 |

# List of Figures

| 2.1  | A Timed Automaton.                                                 | 8  |

|------|--------------------------------------------------------------------|----|

| 2.2  | A Timed Safety Automaton                                           | 9  |

| 2.3  | Network of Timed Automata. [7]                                     | 10 |

| 2.4  | Combined Automaton for The Network in Figure 2.3. [7]              | 10 |

| 2.5  | Regions for a System with Two Clocks. [7]                          | 11 |

| 2.6  | A Timed Automaton and The Corresponding Zone Graph. [9] $\ldots$ . | 12 |

| 2.7  | A Timed Automaton with an Infinite Zone Graph. [9]                 | 13 |

| 2.8  | Normalized Zone Graph for The Automaton in Figure 2.7. [9]         | 13 |

| 2.9  | Graph Interpretation of The Zone and Its Closed Form. $[7]$        | 15 |

| 2.10 | All DBM operations applied to the same zone. [9]                   | 16 |

| 2.11 | CSP# Modeling Language.                                            | 19 |

| 2.12 | Model for a Sender $i$ [48]                                        | 21 |

| 2.13 | Model for the Bus [48]                                             | 22 |

| 3.1  | The process template for Fischer's protocol                        | 30 |

| 4.1  | Dining Philosophers Example                                        | 36 |

| 4.2  | The state space of the dining philosopher.                         | 42 |

| 6.1  | The process template for Fischer's protocol                        | 52 |

| 7.1  | An Overview of CSMA/CD Protocol                                    | 58 |

| 7.2 | Components of CSMA/CD Protocol | 59 |

|-----|--------------------------------|----|

| 7.3 | Model for a Sender $i$ [48]    | 60 |

| 7.4 | Model for the Bus [48]         | 61 |

| 7.5 | Model for the BroadcastCD [48] | 61 |

| 8.1 | Model for the Train            | 68 |

| 8.2 | The template for the Bridge    | 69 |

## Chapter 1

## Introduction

## 1.1 Background and Motivation

Today's world runs on computers and in fact every aspect of our life involves computers in some form or fashion. Actually computers affect how we live, work and entertain ourselves. However, there are many reasons why computers fail to work as expected, which may lead to catastrophic consequences. If one server is suddenly down, it may cause an economical damage. But what happens if an aircraft computer system does not function properly? It even leads to loss of human lives. Thus, it is very important to verify such systems whether they have fulfilled specified requirements. This is so-called *System Verification*.

System Verification is a set of actions used to check the correctness of any element, such as a system, a system component, a service, a task, etc. Traditionally, System Verification has been accomplished by methods like reviewing of design documents, source code or empirical testing. However, those methods have two drawbacks: 1) it is time-consuming and 2) it only provides statistical measures of correctness. Many novel approaches have been proposed in the literature. They are mostly common in the sense that the verification is done by providing a formal proof on a mathematical rigorous model of a complex system. They are so-called formal methods.

Note that in formal methods, there is a tradeoff between the need for rigor and the ability to model all behaviors. Therefore, applying formal methods on real-life systems is considered too difficult. In contrast to formal methods, *model checking* is fully automatic. Given a model of a system, *model checking* checks whether this model meets a given specification

without manual interaction.

Although model checking has an obvious advantage over formal methods, it must cope with the *state space explosion* - the state space can grow exponentially since the number of components in a system increases. For example, the number of valid solutions for the 9x9 Sudoku grid is roughly 6,670,903,752,021,072,936,960. It means that a model checker must visit at most all possible valid solutions to check for a certain property  $\phi$ . Many concurrent systems, however, consist of many replicated processes and they clearly exhibit symmetry of the underlying state space. For those cases, the exploitation of structural symmetries can gain a considerable reduction in processing time and memory consumption, by a factorial magnitude. These techniques are so-called *Symmetry Reduction*.

Symmetry Reduction detects structural symmetries statically and then use these knowledge to construct a *smaller* quotient structure. Since a given property  $\phi$  is invariant under the symmetry, checking over the quotient structure is sufficient for verifying an input system. Therefore, the use of quotient graph can speed up the model-checking process.

However, statically extracting symmetry information from a model is challenging. In fact, existing solutions require the user to manually specify symmetry to be exploited, either directly or by using additional keywords. This approach has two clear drawbacks: 1) It is error-prone and 2) a modeler must have in-depth background knowledge of symmetry reduction. Moreover, they are also limited to fully-symmetric systems whose components are identical up to permutation of identifiers. This situation, however, only arises in practice for very simple systems.

For systems that clearly exhibit symmetry, we can obtain significant savings in processing time and memory consumption. However, verification is still non-scalable for systems with an unbound number of processes. It also becomes important, therefore, to consider the question of determining "once and for all" if the entire unbounded family of instances satisfies a specification. This problem is, however, generally undecidable.

Since time plays a crucial role in the operation of nowadays computer systems, in this thesis, first we study and develop techniques for real-time model-checking tools to cope with the *state space explosion* and automatic symmetry detection. Then, we explore a new and different form of parameterized verification. Specifically, we ask whether a parameterized family has a compositional proof that the specification is met for all instances.

### **1.2 Summary of Contributions**

The main results of this thesis are summarized as follows:

- We propose to extend the real-time model checker PAT [50] with symmetry reduction. Our work is based on the *state swap* technique [26]. We provide a method to detect structural symmetries arising from parameterized process templates of real-time systems that requires no additional input from a modeler. The method results in a set of generators that forms a group of automorphisms. We even support detecting partial symmetry and rotational symmetry. We have run experiments on Fischer's protocol [1], CSMA/CD protocol [55] and Train-Bridge protocol [54]. As a result, we gain a considerable reduction in the cost of analysis, by a factor exponential in the number of processes.

- State space explosion limits model checking to small protocol instances, however, it becomes important to know whether the entire unbounded family of instances satisfies a specification. Thus, we propose a technique to determine whether a property holds for every instance of a parameterized family of real-time process networks. Our technique incorporates elements of symmetry reduction, compositional reasoning and abstraction. While symmetry reduction partitions network nodes into equivalence classes, compositional reasoning analyzes each representative node of an equivalence class separately, along with an abstraction of its neighboring processes. In certain families of process networks that satisfy the conditions of local symmetry, verification is decidable and relatively effective. We show that verification is decidable in time polynomial in the state space of the smallest verified, "cut-off", instance for networks of Fischer's protocol, CSMA/CD protocol and Train-Bridge protocol.

## **1.3** Thesis Outline and Overview

In this section, we briefly present the outline of the thesis and overview of each chapter:

- Chapter 2 contains the preliminary knowledge for this thesis.

- Chapter 3 presents the theory of symmetry reduction in Timed Automata.

- Chapter 4 discusses the symmetry reduction package in PAT.

- Chapter 5 applies the parameterized compositional model checking to Timed Automata.

- Chapter 6, 7 and 8 illustrate the method through 3 examples: Fischer's protocol, CSMA/CD protocol and Train-Bridge protocol.

- Chapter 9 gives conclusions and future works.

## 1.4 Related Work

Many model-checkers have been developed in the last few years for different application areas, such as SPIN [32] for communication protocols, Mur [18] for concurrent and reactive systems, HYTECH [28] for hybrid systems, and especially UPPAAL [35] for real-time systems. These tools have been successfully applied to real cases in practice e.g. [2], [25], [39], [49], [42]. In this section we briefly summarize the well-known techniques in these tools to speed up the verification process.

### **1.4.1** Partial-order Reduction

In many systems, the ordering of events does not affect the verification process. Based on this observation, all equivalent orderings can be represented by only one single ordering. This technique is so-called *partial-order reduction* [24][51][46]. Pagani first introduces an approach to apply partial-order reduction on timed automata, which is based on globaltimed semantics [45]. However, it only limits to transitions that occur at exactly the same time. There is another approach basing on local-time semantics [8]. In [41], Minea extends results given in [8] for reachability analysis to LTL model-checking.

### 1.4.2 Symmetry Reduction

Symmetry reduction [33] is a method for exploiting structural symmetries in a model of a system with many replicated processes. Symmetry reduction statically detects structural symmetries and then use these knowledge to construct a smaller quotient structure. Since a property  $\phi$  to be checked is invariant under the symmetry, the model-checking algorithm is then applied to the quotient structure rather than the entire Kripke structure. Symmetry reduction has been implemented in the real-time model checker UPPAAL [27].

### 1.4.3 Symbolic Model-checking

Symbolic model-checking is based on the idea that sets of states can be represented and manipulated in terms of logical formulae. Specifically for timed automata, sets of clock-values are represented and manipulated in term of zones [30][3] - the solution set of clock constraints. Symbolic model-checking will be covered later in this thesis.

### 1.4.4 Approximation Methods

Approximation methods are aimed at systems whose sizes are too large. In timed automata, we are interested in *over-approximations* - one type of approximation methods where non-reachable states may be considered reachable. *over-approximation* is applied to verification of timed automata in [6] and in [53]. While in [6], the authors focus on the approximate union of two time-zones, Wong-Toi presents techniques for refining the combined results obtained from forwards and backwards analysis [53].

### 1.4.5 Efficient Representation of Clock Constraints

To cope with *state space explosion*, it is necessary to not only reduce the number of states to visit but also minimize memory spent on storing clock constraints. There are a number of novel techniques addressing this problem. In [16] live-range analysis is used to reduce the number of clocks in a model. In [36], the author presents an algorithm to compute the minimal set of constraints for a given DBM since DBM often contains redundant information.

### 1.4.6 Symmetry Detection

In order to make model checking feasible for verification of real-life systems, model checkers should be able to statically extract symmetry information from any system (fully symmetric or not). UPPAAL requires a user to manually specify symmetry via *scalarset* [27]. This method not only is error-prone but also requires a modeler to have in-depth background knowledge. Moreover, it is only applicable to fully-symmetric systems.

In [19], the authors introduce a new specification language, *Promela-Lite*, to the model checker SPIN [32]. Then they show how they can detect symmetry from specifications defined in *Promela-Lite*. However, they still need to explicitly define a special datatype

named *process identifier* (pid) in a language to facilitate the process. Moreover, their technique is not applicable to real-time systems.

## 1.5 Publication from The Thesis

The work presented in this thesis incorporates the work in University of Waterloo technical report [CS-04-2017].

## Chapter 2

## Background

In this chapter, we cover background material of timed automata, model checking and concepts related to this thesis.

## 2.1 Timed Automata

Timed automata is a well-known formalism for describing the timing behavior of concurrent systems. Through this section, we provide background on timed automata [9] with a focus on the semantics and algorithms based on which PAT is developed.

### 2.1.1 A Brief Introduction to Timed Automata

A timed automaton is a finite automaton extended by a set of real valued clocks [9]. All clocks start with the value of 0 and time progresses with the same rate. Clock constraints (guards) labeled on the transitions (edges) restrict the behavior of the automaton in the sense that a transition is only enabled when the clocks values satisfy the guard.

A clock constraint is a formula in the form of  $x \sim n$  or  $x - y \sim n$  where  $\sim \in \{=, \leq, <, >, \geq\}$ ,  $n \in \mathbb{R}_+$  and  $x, y \in \mathbb{C}$  – a set of clocks. The automaton can reset a subset of the clocks to 0 when a transition is taken.

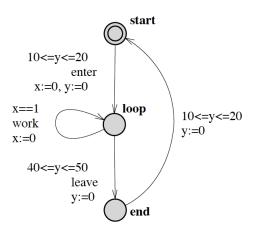

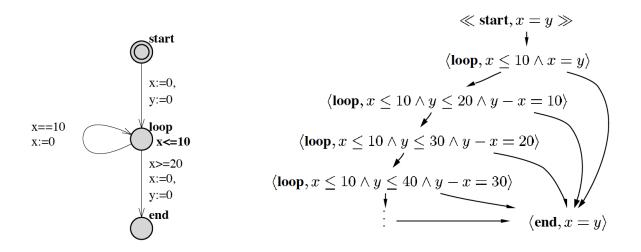

Figure 2.1 shows one example of a timed automaton, where x and y are two real-valued clocks. At first, the automaton is at the *start* location. It leaves *start* when the value of

Figure 2.1: A Timed Automaton.

y is between 10 and 20, making a transition from *start* to *loop* and reseting both clocks to 0. At the *loop* location, the automaton makes the self-loop until the value of y is between 40 and 50, the automaton may go from *loop* to *end*. Staying at the *end* location from 10 to 20 time units, the automaton may return back to *start* and restart the process.

In this example, the automaton may get stuck forever in any location since the guards are only enabling conditions, they cannot force a transition to be taken. Alur and Dill [3] solves this problem by introducing *Timed Buchi Automata*. In *Timed Buchi Automata*, some of the locations are marked as *accept* and valid executions must pass through *accept* locations infinitely often.

Back to the example above, assume that the *end* location is marked as *accept*. This implies that all executions of the system enter *end* infinitely often. Consequently, the automaton must leave *start* when the value of y is at most 20. Similarly, it can only stay at the *loop* location at most 50 time units. However, *Timed Buchi Automata* is inconvenient for system modeling and analysis [29].

In [29], the authors introduce *Timed Safety Automata*, which replaces *accepted* locations by *location invariants* - clock constraints in each location. More clearly, the automaton must leave a current location after the invariant condition is violated. Figure 2.2 shows a timed safety automaton that corresponds to the one given in Figure 2.1.

Figure 2.2: A Timed Safety Automaton.

A time automaton A is a tuple of  $\langle L, l_0, E, I \rangle$  where:

- L is a finite set of locations.

- $l_0 \in L$  is the initial location.

- $E \subseteq L \ge B(\mathbb{C}) \ge \Sigma \ge 2^{\mathbb{C}} \ge L$  is the set of edges.

- $I: L \to B(\mathbb{C})$  is the set of location invariants.

Where we use  $B(\mathbb{C})$  to denote a set of clock constraints.

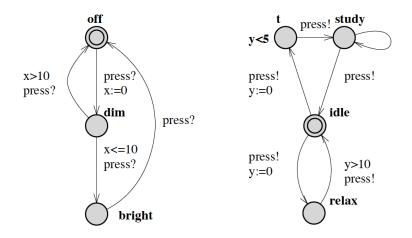

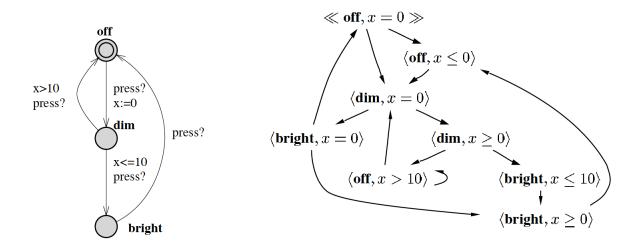

To model concurrent systems, PAT extends the concept of timed automata with parallel composition [40] as well as pair-wise synchronization between processes. Figure 2.3 models a light-switch (left) and its user (right). Two processes synchronize their actions via the *press* label. Figure 2.4 shows the state-space of the combined automaton.

### 2.1.2 Semantics of Timed Automata

Let v denote the clock assignment that maps all clocks  $\in \mathbb{C}$  to their values,  $v \in g$  denote that the clock values satisfy the guard g. The semantics of a timed automaton is defined

Figure 2.3: Network of Timed Automata. [7]

Figure 2.4: Combined Automaton for The Network in Figure 2.3. [7]

Figure 2.5: Regions for a System with Two Clocks. [7]

as a transition system. A state is a pair  $\langle l, v \rangle$  where l is a location and v is a vector of clock values. A transition is either a delay transition or an action transition, which are defined by the following rules:

Delay Transition:  $\langle l, v \rangle \xrightarrow{d} \langle l, v+d \rangle$  if  $v \in I(l), v+d \in I(l)$  and  $d \in \mathbb{R}_+$  is the elapsed time. Action Transition:  $\langle l, v \rangle \xrightarrow{a} \langle l', v' \rangle$  if  $l \xrightarrow{g,a,r} l'$  when  $\langle l, g, a, r, l' \rangle \in E, v \in g$  and  $v' \in I(l')$ .

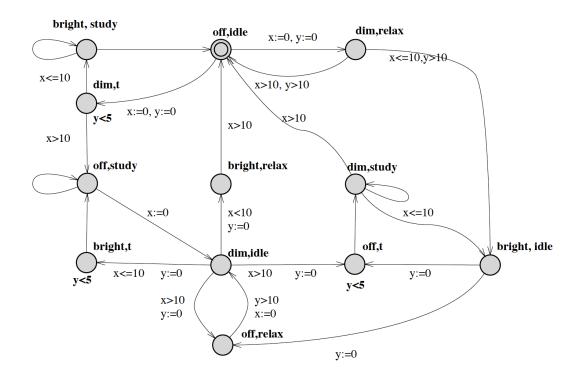

Because clocks are real-valued, the semantics has the infinite state-space and is inappropriate for automated verification. Many techniques have been developed by attempts to finitely partition the state-space into symbolic states. One technique is to construct a region graph [4]. Consider Figure 2.5, where each line segment, each intersection and each area defines one region. The number of possible regions is 60, assuming that  $x \leq k = 3$  and  $y \leq g = 2$ . It means that the region graph, however, may grow exponentially when we increase either the number of clocks or upper bounds (k, g).

Another approach is based on the notion of zone and zone-graph [17]. By definition, a *zone* is the solution set of clock constraints. Figure 2.6 (a) shows a timed automaton and Figure 2.6(b) shows its corresponding zone-graph, which has only eight states. The region-graph for that example has over fifty states.

The symbolic semantics of a timed automaton is defined as a symbolic transition system. A symbolic state is a pair  $\langle l, D \rangle$  where l is a location and D is a zone. Therefore, a symbolic state represents a set of states. Symbolic transition relations over symbolic states

Figure 2.6: A Timed Automaton and The Corresponding Zone Graph. [9]

are defined by the following rules:

Delay Transition:

$$\langle l, D \rangle \xrightarrow{d} \langle l, D^{\uparrow} \wedge I(l) \rangle$$

where  $D^{\uparrow} = \{v + d \mid v \in D, d \in \mathbb{R}_{+}\}.$

Action Transition:  $\langle l, D \rangle \xrightarrow{a} \langle l', D' \wedge I(l') \rangle$  where  $D' = reset(D)$ .

where reset(D) is one operation on zones that resets selected clock values to zero.

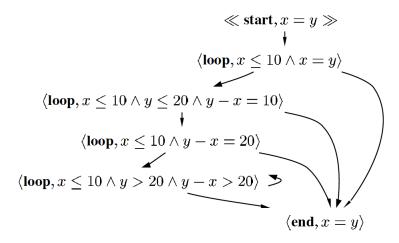

However, the zone-graph may be also infinite. Consider the model in Figure 2.7, where the values of clocks drift away unboundedly, giving an infinite graph. The solution is to transform zones into their normalized representatives to guarantee termination. In the original theory of timed automata, difference constraints  $x - y \sim n$  are not allowed to appear in the guards g. Such automata whose guards contains only atomic constraints in the form of  $x \sim n$  are known as diagonal-free automata. For diagonal-free automata, one popular zone-normalization procedure is so-called *k*-normalization [47]. Once the value of a clock x is larger than the maximum constant k, it is no longer significant for the automaton to know its precise value, only that  $x \geq k$ . Figure 2.8 depicts the *k*-normalized zone-graph of the automaton given in Figure 2.7.

Figure 2.7: A Timed Automaton with an Infinite Zone Graph. [9]

Figure 2.8: Normalized Zone Graph for The Automaton in Figure 2.7. [9]

### 2.2 Zone and Difference Bound Matrices

A *zone* is the solution set of clock constraints. Since a zone is a part of a symbolic state, how to represent a zone effectively is a major issue. In many verification tools including PAT, such sets are represented as Difference Bound Matrices (DBMs).

Recall that a clock constraint is a formula in the form of  $x \sim n$  or  $x - y \sim n$  where  $\sim \in (=, \leq, <, >, \geq)$ ,  $n \in \mathbb{N}$  and  $x, y \in \mathbb{C}$  – a set of clocks. To have a unified form for clock constraints, we introduce a reference clock **0** with the constant value 0 such that  $\mathbb{C}_0 = \mathbb{C} \cup \mathbf{0}$ . Therefore, any clock constraint can be written in the form of  $x - y \sim n$  where  $\sim \in (=, \leq, <, >, \geq)$ ,  $n \in \mathbb{N}$  and  $x, y \in \mathbb{C}_0$ .

DBM representation for a zone D is the matrix, which each row stores lower bounds on the difference between one clock and all other clocks. We denote all clocks in  $\mathbb{C}_0$  as  $x_0, x_1, ..., x_N$ . We use  $D_{i,j}$  to denote element (i, j) in the DBM. The matrix elements are then computed as follows:

- $D_{ij} = (k, \leq)$  presents the constraint  $x_i x_j \leq k$ .

- $D_{ij} = \infty$  if  $x_i x_j$  is unbounded.

- $D_{ij} = 0$  if i = j.

- $D_{ij} = 0$  for the difference between clock **0** and other clocks.

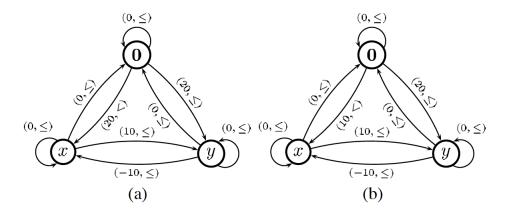

Consider the zone  $D = x - 0 < 20 \land y - 0 \le 20 \land y - x \le 10 \land x - y \le -10 \land 0 - z < 5$ , where 0, x, y, z are clocks and we denote as  $x_0, x_1, x_2, x_3$ . DBM representation for D should be:

$$D = \begin{bmatrix} 0 & 0 & 0 & 5\\ 20 & 0 & -10 & \infty\\ 20 & 10 & 0 & \infty\\ \infty & \infty & \infty & 0 \end{bmatrix}$$

### 2.2.1 Canonical DBMs

Although an infinite number of zones share the same solution set, among them there is a unique zone where no atomic constraint can be strengthened without losing solutions [36]. We call it as the canonical representation of an entire family of zones, denoted as Rep(D).

Figure 2.9: Graph Interpretation of The Zone and Its Closed Form. [7]

Rep(D) is derived from a zone D by computing the tightest constraint on each clock difference in D. We can imagine that zone is a weighted graph where clocks are nodes and clock constraints are edges.

As an example, consider the zone  $D = x - 0 < 20 \land y - 0 \le 20 \land y - x \le 10 \land x - y \le -10$ . By combining the atomic constraints  $y - 0 \le 20 \land y - x \le 10$ , we derive  $x - 0 \le 10$ , i.e. the bound x - 0 on can be strengthened. Figure 2.9(a) presents the graph interpretation of D while Figure 2.9(b) presents the representative Rep(D) after x - 0 is strengthened.

The problem of computing the canonical representation of a given zone is equivalent to finding the shortest path between every pair of nodes in the graph interpretation of the zone [9].

### 2.2.2 Operations on DBMs

We briefly list out all operations on DBMs, which are divided into three different classes:

- Property-Checking Operations in this class include checking if a DBM is consistent (consistent(D), checking inclusion between zones (relation(D, D')), and checking whether a zone satisfies a given atomic constraint (satisfied(D,  $x_i x_i \leq m$ )).

- Transformation Operations in this class include computing the strongest post condition of a zone D with respect to delay (**up**(**D**)), computes the weakest precondi-

Figure 2.10: All DBM operations applied to the same zone. [9]

tion of D with respect to delay  $(\mathbf{down}(\mathbf{D}))$ , adding a constraint to a zone  $(\mathbf{and}(\mathbf{D}, x_i - x_j \leq b))$ , removes all constraints on a given clock  $(\mathbf{free}(\mathbf{D}, \mathbf{x}))$ , setting a clock to specific values  $(\mathbf{reset}(\mathbf{D}, x \coloneqq m))$ , copying the value of one clock to another  $(\mathbf{copy}(\mathbf{D}, x \coloneqq y))$ , adding or subtracting a clock with an integer value  $(\mathbf{shift}(\mathbf{D}, x \coloneqq x + m))$ .

• Normalization Operations in this class include k-normalization.

### 2.3 Basics of Model Checking in Timed Automata

Model Checking [13][11] is one of the most successful approaches for verifying specifications of hardware and software systems. Model-checking uses reachability analysis to verify effectively systems on safety properties.

In timed automata, reachability analysis consists of two steps: 1) compute the normalized zone-graph *on-the-fly* and 2) check if a current state contradicts or satisfies given properties. In comparison to pre-computing, computing the zone-graph *on-the-fly* has an obvious advantage. Specifically, only the part of the state-space needed to prove the property is generated [9]. In most cases, the generated state-space is smaller than the entire state-space. Note that, the method, however, still generates the entire state-space to prove invariant properties.

Algorithm 1 describes the forward reachability analysis algorithm in PAT. Let  $\langle l_0, D_0 \rangle$  be

Algorithm 1 Forward Reachability Analysis Algorithm 1: Visited =  $\emptyset$ 2:  $\langle l_f, D_f \rangle$  = Violated States 3: Next =  $\langle l_0, D_0 \rangle$ 4: while Next  $\neq \emptyset$  do remove  $\langle l, D \rangle$  from Next 5:if  $l = l_f$  and  $D \cap D_f \neq \emptyset$  then return YES 6: if  $D \not\subseteq D'$  for all  $\langle l, D' \rangle \in$  Visited then 7: add  $\langle l, D \rangle$  to Visited 8: for  $\langle l', D' \rangle$  such that  $\langle l, D \rangle \rightarrow \langle l', D' \rangle$  do 9: add  $\langle l', D' \rangle$  to Next 10:11: return NO

a set of initial states and a set of bad states is given as  $\langle l_f, D_f \rangle$  respectively. Algorithm 1 computes the normalized zone-graph of the automaton on-the-fly and checks if  $\langle l_0, D_0 \rangle$  may evolve to any state whose location is  $l_f$  and whose clock assignment satisfies  $D_f$ . At each step, the algorithm stores next symbolic states in Next and checks if the reached zones intersect with  $D_f$ . Normalized zone-graph is finite [47] and the algorithm is guaranteed to terminate.

Despite model checkers have an obvious advantage over theorem proving, their applica-

tions are limited since there are some main reasons as follows:

- *Scalability.* Model checkers must cope with the *state space explosion.* The state space can grow exponentially when the number of components in a system increases.

- Accessibility. In fact, model checkers are mostly academic tools whose interfaces are not user-friendly, and they also lack of detailed documentation. Moreover, a modeler is required to have background in formal method to build models.

## 2.4 System Modeling

The section focuses on the modeling language used in PAT. PAT uses CSP# as its primary modeling language to define processes and computational logic in a process. CSP# is a timed extension of Communication Sequence Process (CSP) [31]. Its grammar is given in Figure 2.11, where P and Q are processes,  $e \in \Sigma$  is an observable event, b is a boolean expression, X is a set of event names and d is an integer constant.

To be more detailed:

- *Stop* denotes deadlock, where the process does nothing but idling.

- *Skip* states termination.

- $e \to P$  performs event e first and then behaves as P. Notice that e is either an abstract event or a data operation, e.g.

- [b]P denotes a guard process. If b is true, then it behaves as P. Otherwise, it does nothing but waits until b becomes true.

- *if b then P else Q* performs a conditional choice. Specifically, if *b* is true, then it behaves as *P*, otherwise it behaves as *Q*.

- $P \square Q$  denotes an unconditional choice. Which process it should behave as depends on upcoming events.

- $P \parallel Q$  denotes parallel composition. Two processes communicate via global variables or passing messages on channels.

| $P = Stop \mid Skip$<br>$\mid e \rightarrow P$<br>$\mid [b]P$<br>$\mid if \ b \ then \ P \ else \ Q$<br>$\mid P \Box \ Q$<br>$\mid P \parallel Q$<br>$\mid P; \ Q$<br>$\mid P \setminus X$<br>$\mid P \cong Q$<br>$\mid Wait[d]$<br>$\mid P \ interrupt[d] \ Q$<br>$\mid P \ within[d]$ | <ul> <li>primitives</li> <li>event prefixing</li> <li>state guard</li> <li>if-then-else</li> <li>general choice</li> <li>parallel composition</li> <li>sequential composition</li> <li>hiding</li> <li>process referencing</li> <li>delay</li> <li>timeout</li> <li>timed interrupt</li> <li>react within some time</li> </ul> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P interrupt $[d]$ $Q$                                                                                                                                                                                                                                                                   | - timed interrupt                                                                                                                                                                                                                                                                                                              |

| P waituntil[d]<br>  P deadline[d]                                                                                                                                                                                                                                                       | – wait until<br>– deadline                                                                                                                                                                                                                                                                                                     |

Figure 2.11: CSP# Modeling Language.

- P; Q denotes a sequential execution. The process behaves as P until P terminates and then immediately behaves as Q.

- $P \setminus X$  makes all occurrences of events in X not to be observed or controlled by the process environment.

- $P \equiv Q$  defines P to be exactly the same as Q.

- Wait[d] delays the system execution d time units and then it terminates.

- *P timeout*[*d*] *Q* behaves as *Q* after *d* time units have elapsed unless the first observable event of *P* occurs before that.

- P interrupt[d] Q only behaves as P within d time units and then behaves as Q.

- P waituntil/d/ denotes that P executes for at least d time units.

- P deadline[d] states that P must terminate within d time units.

Although Timed Automata proves its popularity for modeling real-time systems with explicit clock variables, it has certain drawbacks. Specifically, Timed Automata is not suitable for designing compositional models. However, in industry, high-level requirements for real-time systems are often stated in terms of *deadline, time out, and timed interrupt* [34]. As a result, if users define their models in Timed Automata, they need to manually cast those terms into a set of clock variables with carefully calculated clock constraints, which is tedious and error-prone [48].

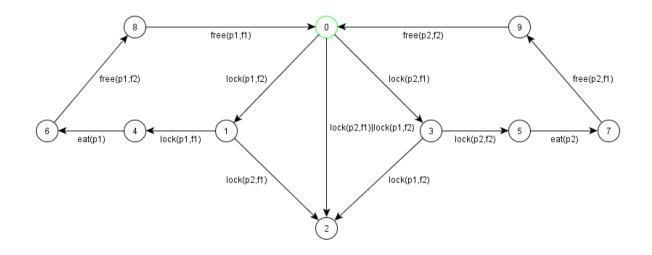

## 2.5 CSMA / CD Protocol

The Carrier Sense, Multiple Access with Collision Detection (CSMA/CD) protocol describes one solution to the problem in Ethernet network, when several agents compete for a single bus. The research group in PAT has successfully done modeling and verification on CSMA/CD protocol [48]. In this section, we show how CSMA/CD protocol is modeled using the CSP# modeling language in PAT.

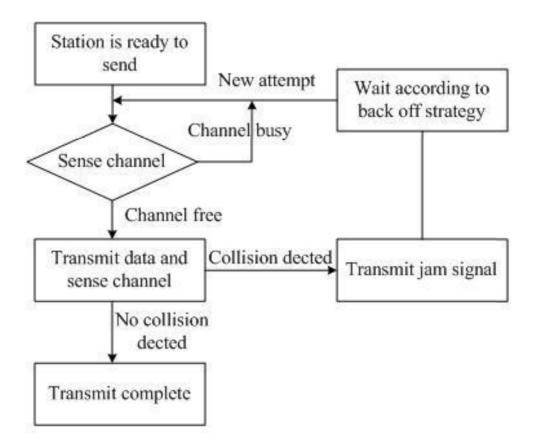

CSMA/CD protocol consists of two components, namely *Sender* and *Bus*. Two components communicate by pair-wise synchronization channels. Roughly speaking, a *Sender* must first listen to the *Bus*. If the *Bus* is idle, the *Sender* begins to transmit. Otherwise, it must wait and retry later. However, collision may occur when more than one *Sender* are sending message via the *Bus*. Then the *Bus* informs all *Senders* of this collision, and abort their transmission immediately. Therefore, all transmitting messages are discarded.

### Modeling Sender Behavior

The behavior of component *Sender* is defined in Figure 2.12. Initially, the *Sender* is in WaitFor location. When there is a message to send, if the *Bus* is idle, the *Sender* goes to *Trans* location. Otherwise, if the *Bus* is busy or a collision is detected, it moves to *Retry*. If a collision occurs while no message is arrived, the *Sender* remains in *WaitFor* location.

In *Trans* location, the *Sender* has two transitions. If a collision is detected within 52 time units, the *Sender* goes to *Retry*. Otherwise, it terminates sending the message after exactly 808 time units, then it goes to *WaitFor*.

In Retry location, if the Bus is idle, the Sender moves back to Trans within 52 time units. Otherwise, it remains in Retry location.

$$\begin{split} \text{WaitFor}(i) &= (cd?i \rightarrow \text{WaitFor}(i)) \\ &\square (newMess!i \rightarrow ((begin!i \rightarrow Trans(i))) \\ &\square (busy?i \rightarrow Retry(i)) \\ &\square (cd?i \rightarrow Retry(i)))); \\ Trans(i) &= (cd?i \rightarrow Retry(i)within[0, 52]) \\ &\square (atomic \{end!i \rightarrow Skip\}within[808, 808]; \\ & WaitFor(i)); \\ Retry(i) &= (newMess!i \rightarrow ((begin!i \rightarrow Trans(i)within[0, 52])) \\ &\square (busy?i \rightarrow Retry(i)within[0, 52]) \\ &\square (cd?i \rightarrow Retry(i)within[0, 52]))); \end{split}$$

Figure 2.12: Model for a Sender i [48]

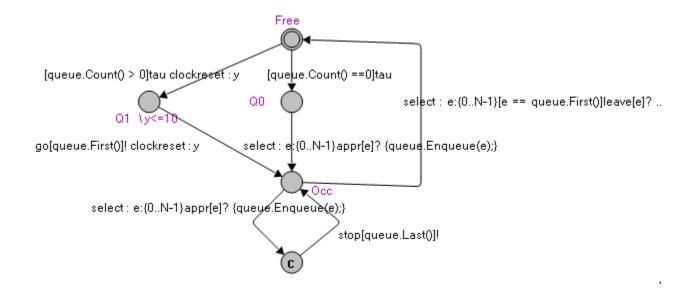

#### Modeling Bus Behavior

The behavior of component Bus is showed in Figure 2.13. Initially, the Bus is in Idle location. The transition from Idle to Active is enabled when one Sender begins to transmit.

In Active location, there are three possible transitions. If the Sender completes sending, the Bus goes back to the initial location. If another Sender starts sending messages within 26 time units, the Bus moves to Collision. Otherwise, after at least 26 time units have elapsed, the Bus replies busy signal to any new attempt, then it moves to Active1 location.

In Active1 location, the Bus takes at most 26 time units to inform all Senders of this collision, using BroadcastCD [48]. After that, the Bus moves to Idle.

In *Collision* location, the *Bus* replies busy signal to any *Sender* that attempts to send message until the active *Sender* completes transmitting, then the *Bus* moves to *Idle*.

#### Modeling CSMA/CD Protocol

The whole protocol consists of one Bus and N Senders interleaving with each other. In PAT, we model this as follows:

$CSMA = (||| i : \{0, ..., N - 1\} @ Sender(i)) ||| Bus$

$$\begin{split} Idle &= newMess?i \rightarrow begin?i \rightarrow Active; \\ Active &= (end?i \rightarrow Idle) \\ &\square (newMess?i \rightarrow ((begin?i \rightarrow Collision) timeout[26] \\ &\square (busy!i \rightarrow Active1))); \\ Active1 &= (end?i \rightarrow Idle) \\ &\square (newMess?i \rightarrow busy!i \rightarrow Active1); \\ Collision &= atomic \{BroadcastCD(0)\} within[0, 26]; Idle; \end{split}$$

Figure 2.13: Model for the Bus [48].

## Chapter 3

# Symmetry Reduction in Timed Automata

State-space explosion is the main obstacle to the scalability of model checking. Indeed, it is known that symmetry reduction techniques can be used to combat this problem for networks of replicated components. In this chapter, first we will summarize a theory of symmetry and then explain how to apply symmetry reduction into real-time systems modeled by timed automata.

## 3.1 A Theory of Symmetry

Consider state graphs, which are tuples containing a set of states S, a set  $S_0 \subseteq S$  of initial states and a transition relation  $\Delta \subseteq S \ge S$ .

A state  $s \in S$  is *reachable* if a sequence  $s_0, s_1, ..., s_{n-1}$  exists, such that:

- $s_0 \in S_0$ .

- $s = s_{n-1}$ .

- $s_i \in S$  for all  $0 \le i < n$ .

- $(s_i, s_{i+1}) \in \Delta$  for all  $0 \le i < n-1$ .

Let s be a reachable state and  $\phi$  be a safety property to verify. We denote  $s \models \phi$  if the property  $\phi$  is true in state s. Algorithm 2 depicts a standard forward exploration algorithm to check if a given system satisfies  $\phi$ .

Algorithm 2 Standard Forward Reachability Analysis Algorithm

```

1: passed = \emptyset

2: waiting = S_0

3: while waiting \neq \emptyset do

4: remove s from waiting

5: if s \models \phi then return YES

6: else if s \notin passed then

7: add s to passed

8: waiting = waiting \cup succ(s)

9: return NO

```

Initially, the set *waiting* only contains the initial states  $S_0$ . In each while-loop, the algorithm pops out a state s from *waiting* and processes in the following way:

- The algorithm returns YES if state s satisfies the property  $\phi$ .

- If property  $\phi$  is false in state s and if state s has been visited before, then the algorithm discards s and repeats the loop.

- Otherwise, s is added to the set *passed* and all of its successors are added to *waiting*.

If the state space is finite, this algorithm halts. Otherwise, it may not halt. In fact, verification with this algorithm is either undecidable for infinite-state systems or expensive for finite-state systems with a large number of components.

Symmetry reduction exploits structural properties of transition systems to speed up Algorithm 2. Authors in [3][21] define symmetry within a state graph as a graph automorphism.

**Definition 3.1 (Automorphism)** An automorphism [33], which is used to characterize symmetry in a state graph, is a bijection  $h: S \to S$  such that:

- $s \in S_0$  if and only if  $h(s) \in S_0$ .

- If  $(s, s') \in \Delta$  if and only if  $(h(s), h(s')) \in \Delta$  for all  $s, s' \in S$ .

Let M be a state graph, Aut(M) be a group of graph automorphisms, and H be a set of graph automorphisms that forms a sub-group under composition of mappings. Then any subgroup G of Aut(M) induces an equivalence relation  $\equiv_G$  on the states of M such that:

$$s \equiv_G t$$

iff  $s = \alpha(t)$

for some  $\alpha \in G$ . We say that s and t are equivalent and they belong to the same equivalence class. The equivalence class under  $\equiv_G$  of a state  $s \in S$ , denoted [s], can be used to construct a *quotient* Kripke structure  $Quot(M) = (S', S'_0, \Delta')$ .

**Definition 3.2 (Quotient Graph)** Let  $M = (S, S_0, \Delta)$  be a state graph and let Aut(M) be a group of automorphisms. The quotient graph of M, denoted as Quot(M) and induced by Aut(M), is the graph  $(S', S'_0, \Delta')$ , where:

- $S' = \{ [s] \mid s \in S \}.$

- $S'_0 = \{ [s] \mid s \in S_0 \}.$

- $\Delta' = \{([s], [k]) \mid (s, k) \in \Delta\}.$

**Theorem 1.** Let M be a state graph, G be a subgroup of Aut(M) and  $\phi$  be a safety property. If  $\phi$  is invariant under the group G then:

$$M, s \models \phi \Leftrightarrow Quot(M), [s] \models \phi$$

Therefore, in most cases, Quot(M) is a smaller structure than M and hence, the use of the quotient graph can speed up the verification process. If we can statically detect structural symmetries from the system description and compute a group of automorphisms Aut(M) in advance, then a quotient structure can be constructed. Finally, the model checking tool checks a property  $\phi$  over the quotient graph. We call this process as Symmetry Reduction.

### 3.2 Symmetry Reduction

Symmetry reduction is a technique to tackling state space explosion. For concurrent systems with many replicated processes such as Fischer's protocol or CSMA/CD protocol, the exploitation of structural symmetries in a model can gain a considerable reduction in processing time and memory usage, by a factorial magnitude.

Symmetry reduction in model checking involves replacing a set of equivalent states in a state graph M by a single representative, rep(s), from each equivalence class. It results in a *quotient graph Quot*(M). Providing a property  $\phi$  is invariant under the symmetry used:

$$M \models \phi$$

if and only if  $Quot(M) \models \phi$

The idea is to build the quotient structure on-the-fly using knowledge of a group of automorphisms Aut(M). Instead of backtracking only when a current state s has been reached previously, we now backtrack if rep(s) has been reached previously.

Consequently, we may improve Algorithm 2 to store and explore only a single representative rep(s) of each equivalence class. Algorithm 3 presents the modified reachability analysis algorithm. Initially, the set *waiting* still contains the initial states  $S_0$ . However, in each while-loop, now the modified algorithm processes in the following way:

- The algorithm returns YES if state s satisfies state property  $\phi$ .

- If property  $\phi$  is false in state s and if state s has been visited before, then the algorithm discards s and repeats the loop.

- Otherwise, s is added to the set *passed* and only representative states of its successors are added to *waiting*.

Since many equivalent states are projected onto the same representative rep(s), the number of visited states may decrease dramatically.

#### Algorithm 3 Adding Symmetry To The Forward Reachability Analysis.

```

1: passed = \emptyset

2: waiting = rep(S_0)

3: while waiting \neq \emptyset do

4: remove s from waiting

5: if s \models \phi then return YES

6: else if s \notin passed then

7: add s to passed

8: waiting = waiting \cup rep(succ(s))

9: return NO

```

Similarly, we extend the concept of Algorithm 3 to timed automata. Algorithm 4 below describes the modified reachability analysis algorithm for timed automata, which improves Algorithm 1 to store and explore only a single representative rep(s) of each equivalence class.

Algorithm 4 Modified Forward Reachability Analysis Algorithm

1: Visited =  $\emptyset$ 2:  $\langle l_f, D_f \rangle$  = Violated States 3: Next =  $rep(\langle l_0, D_0 \rangle)$ 4: while Next  $\neq \emptyset$  do remove  $\langle l, D \rangle$  from Next 5: if  $l = l_f$  and  $D \cap D_f \neq \emptyset$  then return YES 6: 7: if  $D \not\subseteq D'$  for all  $\langle l, D' \rangle \in$  Visited then add  $\langle l, D \rangle$  to Visited 8: for  $\langle l', D' \rangle$  such that  $\langle l, D \rangle \rightarrow \langle l', D' \rangle$  do 9: add  $rep(\langle l', D' \rangle)$  to Next 10:

11: return NO

However, there are two challenging problems in the actual implementation of symmetry reduction:

- How to statically detect symmetries from the system description. Then the corresponding symmetry group induces the quotient graph as discussed above.

- Find out optimal solutions to compute rep(s) for any state s.

Moreover, proposed solutions should be computationally inexpensive to protect the gain of using the quotient graph. To cope with the first problem, we propose a technique to detect symmetries automatically from the system description in the next chapter. The second problem is called *orbit problem*. Generally, it is as difficult as testing for graph-isomorphism [10]. Since there is no polynomial algorithms for this problem, in the section we discuss one sub-optimal solution to the orbit-problem in timed automata.

## 3.3 Representative Function

Given a group of automorphisms, the solution is to convert all explored states to a so-called *normal form*, which represents the equivalence class of the state. The idea is that if two

states have the same normal form, then they belong to the same equivalence class.

Let  $\theta$  be a proposed representative function, then:

$$\theta(s) = \theta(s') \to [s] = [s'] \text{ for } \forall s, s' \in S$$

In [26], the authors prove that the orbit problem is even more difficult when the state involves timing. To protect the gain with respect to both time and memory consumption, they revert to the sub-optimal solution, which is adopted in our work.

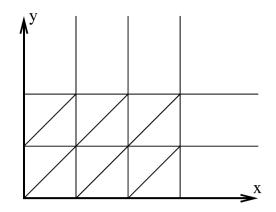

The idea is to sort states lexicographically within an equivalence class and the representative rep(s) of a state s is defined as the minimal element. Since a symbolic state is a tuple of (L, V, D) - where L and V are sequences of numbers, the problem left is how we sort lexicographically the *zone* attribute.

Let  $\mathbb{A}$  be a timed automaton whose local clocks are x and y.  $\mathbb{A}$  only performs the operation *reset* on zones. Under these assumptions, there are three possible relations between x and y as follows:

$$x \leq_D y \iff v(x) \leq v(y)$$

$$x \approx_D y \iff v(x) = v(y)$$

$$x <_D y \iff x \leq_D y \land \neg (x \approx_D y)$$

where v(x) returns a value of clock x. This is called *diagonal property*.

**Lemma 1 (Diagonal Property).** [26] Assume that a timed automaton only performs *reset* on zones. For all states and for all clocks x and y, it holds that either  $x <_D y$ , or  $x \approx_D y$  or  $y <_D x$ .

Let X be a set of clocks. Assume that the equivalence relation  $\approx_D$  partitions X into N finite sets =  $\{X_1, X_2, ..., X_n\}$ , such that:

$$X_i \le X_j \iff x \le_D y \ \forall x \in X_i, y \in X_j$$

Clearly the code of  $X_i$ , denoted by  $C^*(X_i)$ , is the lexicographically sorted sequence of the indices of the clocks in  $X_i$ . The zone code of D, denoted by C(D), is the sequence  $(C^*(X_1), C^*(X_2), \dots, C^*(X_n))$ .

Note that, every zone has exactly one zone code. Instead of sorting *zones*, we can rather

lexicographically sort zone codes since zone codes are sequences of numbers.

We define (L, V, D) and (L', V', D') as two symbolic states, we say that (L, V, D) is "smaller" than (L', V', D') if and only if:

$$(L, V, D) < (L', V', D')$$

$$\iff$$

$$(L < L') \lor (L = L' \land V < V') \lor (L = L' \land V = V' \land C(D) < C(D'))$$

This principle is used to sort states lexicographically within an equivalence class effectively. The lexicographically minimum element is selected as the representative.

In the next chapter, we will discuss in detail how to actually "minimize" the state using a group of detected automorphisms.

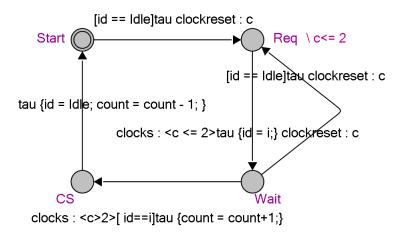

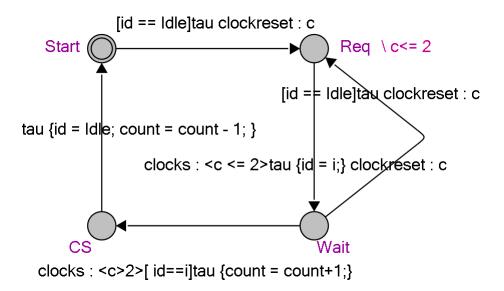

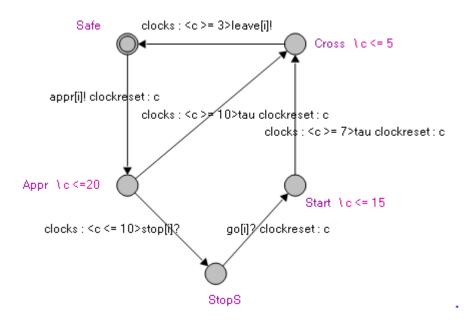

# 3.4 Fischer's Protocol

Fischer's protocol ensures mutual exclusion of access to commonly used resources via a shared variable **id**. The protocol relies on location invariants and suitable updates of the variable **id**. We model Fischer's protocol by the real-time system module in PAT. Many examples below in this chapter refer to Fischer's protocol.

Processes of the protocol are instances of a template depicted in Figure 3.1. The template has one local clock  $\mathbf{c}$  and no local variables.

Initially, a process is in location *Start*. The default value of **id** is *Idle* and clock **c** is set to 0. The transition from *Start* to *Req* is always enabled.

In location Req, the process sets **id** to its process identifier and then goes to *Wait* before 2 time units have elapsed.

In location Wait, the process waits for at least 2 time units and then reads id again. If id has kept the old value, the process may enter its critical section CS. Otherwise, the attempt has failed and the process must go back to Req.

In CS location, the process is in its critical section. The transition from CS to Start is always enabled.

Figure 3.1: The process template for Fischer's protocol

## **3.5** Extraction of Automorphisms

In this section, first we define the so-called *state-swap* functions, and second, we define which *state-swap* functions are automorphisms.

#### 3.5.1 State Swap

Based on the concept of *state swap* [26], we define permutations on the state graph, in our case, a PAT model. In a model of a concurrent system with many replicated processes, we restrict attention to automorphisms given by permutations of process identifiers. The state consists of local contributions of various components in the model. Therefore, we use processes which are instantiated from the same template to permute the state.

Let P(i) and P(j) be processes of the system P that originate from the same template T. Therefore, a *state-swap*  $swap_{i,j}$ :  $(L, V, D) \rightarrow (L', V', D')$  is defined as follows:

- Process Swap: swaps the contributions to the state given by a pair of (P(i), P(j)). Swapping a pair of (P(i), P(j)) operates in two steps: 1) interchange the current locations and 2) interchange the values of the local variables and clocks.

- Data Swap: swaps array entries i and j of all dimensions that are indexed by variables of type pid. Moreover, it swaps the value i with the value j for all variables of type

pid.

*Process Swap* is trivial since the processes originate from the same template while in order to perform *Data Swap*, first the tool needs to statically recognize all entities of type *pid* in the model.

Let *Fischer* be an instance of Fischer's protocol with N processes. Processes are instantiated from the process template T given in Figure 3.1. Then *Fischer* is defined in PAT as follows:

$$Fischer = ||| i : \{0, ..., N - 1\} @ T(i)$$

A state of *Fischer* is a tuple (L, V, D), where L is a N-component location vector, V is a set of variable valuations and D is a set of clock valuations.

*Example 1:* Assume N = 3 and also the tool recognizes that id has type of *pid*, now we consider the following state *s*:

- L:  $l_0 = Start, l_1 = Wait, l_2 = CS.$

- V: id = 2.

- D:  $c_0 = 4, c_1 = 3, c_2 = 2$ .

When we apply  $swap_{0,2}$  into this state, it results a new state s' by interchanging  $l_0$  with  $l_2$  and  $c_0$  with  $c_2$  (Process Swap), and setting *id* to 0 (Data Swap). s' is given as follows:

- L:  $l_0 = CS, l_1 = Wait, l_2 = Start.$

- V: id = 0.

- D:  $c_0 = 2, c_1 = 3, c_2 = 4.$

Similarly applying  $swap_{1,2}$  to s' gives the following state:

- L:  $l_0 = CS, l_1 = Start, l_2 = Wait.$

- V: id = 0.

- D:  $c_0 = 2, c_1 = 4, c_2 = 3.$

#### 3.5.2 Action of State Swap on Process Template

When a permutation is applied to a state, it permutes the outgoing actions of the state. Permutation of an action a returns the new action a' with permuted process parameters. Therefore, we define swap functions on the syntax of our models.

A process template in PAT is given in the following syntax:

$$T(x_0, x_1, \dots, x_{n-1}) = \{Body\}$$

where T is the template name,  $(x_0, ..., x_{n-1})$  is an optional list of template parameters and *Body* determines the computational logic of the process. *Body* consists of local variables v, guards g, updates u and program statements ps over variables and channels [50].

Let T be a process template and  $\pi$  be a state-swap. Applying  $\pi$  to T results in a new template  $\pi(T)$ , where a guard g, an update u and a program statement ps of T is replaced by  $\pi(g)$ ,  $\pi(u)$  and  $\pi(ps)$  respectively. Finally,  $\pi(T)$  is the same as T, except that:

- Any assignment statement x = val is replaced by  $x = \pi(val)$ , where type(x) = pid and val is a value.

- Any boolean expression  $x \sim val$  is replaced by  $x \sim \pi(val)$ , where  $\sim \in (==, \neq)$ , type(x) = pid and val is a value.

In other words, *state-swap* is also a syntactic operation on the template T. There is no guarantee that  $\pi(T)$  and T are syntactically equivalent.

*Example 2*: Assume that the system *Fischer* given in *Example 1* does not allow T(2) to enter its critical section. This is achieved by modifying the template T given in Figure 3.1. A guard g on an edge from location *Wait* to location *CS* is now given as:

$$id == i \text{ and } i \neq 2$$

By applying  $swap_{0,2}$  into T, it results in a new guard  $swap_{0,2}(g)$ :

$$id == i$$

and  $i \neq 0$

It is clear that  $swap_{0,2}(T)$  is not identical to T since T(2) is now enabled to enter its critical section in the template  $swap_{0,2}(T)$ .

#### 3.5.3 Automorphisms

A state-swap  $\pi$  is called an automorphism of a system, P, if it satisfies the following three properties:

- It preserves the types of the processes. On other words, it only swaps two processes that are instantiated from the same template.

- It preserves the associations of the processes it maps. It means that given the process associations in P, if a *state-swap* is applied to P, the resulting system  $\pi(P)$  should be valid with respect to the given associations.

- It preserves the transition relation of the system such that if there exists a transition between two states s and t in P, then there should be a transition between the states  $\pi(s)$  and  $\pi(t)$  in  $\pi(P)$ . On other words, P and  $\pi(P)$  must be syntactically equivalent.

Let P be a parameterized system with N processes instantiated from the same template T, where  $0 \le i < N$ . We define Swap(P) as a set of possible *state-swaps*, which consists of all permutations of the set of process identifiers  $\{0, 1, ..., N-1\}$ .

We say that  $\pi \in Swap(P)$  is valid if it satisfies three properties above. Let ValidSwap(P) be the set of valid *state-swap* functions.

Theorem 2 (Soundness) [26]. Every valid state swap is an automorphism.

#### 3.5.4 Group of Automorphisms

Let G be a group, and let  $\alpha_1, \alpha_2, ..., \alpha_n \in G$ . The smallest subgroup of G containing the elements  $\alpha_1, \alpha_2, ..., \alpha_n$  is denoted  $\langle \alpha_1, \alpha_2, ..., \alpha_n \rangle$ , and is called the subgroup generated by  $\alpha_1, \alpha_2, ..., \alpha_n$ . The elements  $\alpha_i$   $(1 \le i \le n)$  are called *generators* for this subgroup. Let X =  $\{\alpha_1, \alpha_2, ..., \alpha_n\}$  be a finite subset of G. Then we use  $\langle X \rangle$  to denote  $\langle \alpha_1, \alpha_2, ..., \alpha_n \rangle$ , the subgroup generated by X.

Let *H* be a subgroup of *G*, and let  $\alpha \in G$ . The set  $H\alpha = \{\beta\alpha : \beta \in H\}$  is called a right coset of *H* in *G*. The set of all right cosets of *H* in *G* partitions *G* into disjoint equivalence classes. In particular, for  $\alpha \in H$ , we have  $H\alpha = H$ .

ValidSwap(P) is a set of valid automorphisms, denoted as  $\{\pi_1, \pi_2, ..., \pi_n\}$ . Under composition of mappings and group theory above, ValidSwap(P) forms a group of automorphims

$\langle ValidSwap(P) \rangle = \langle \pi_1, \pi_2, ..., \pi_n \rangle$ . This means that,  $\langle ValidSwap(P) \rangle$  had an identity element  $\pi$  that maps a process p onto itself or  $\pi(p) = p$ . Also, every other permutation  $\pi_i$  has an inverse element  $\pi_i^{-1}$  such that  $\pi_i^{-1}\pi_i(p) = p$ .

The next chapter focuses on how we actually implement the symmetry reduction package in PAT.

# Chapter 4

# Symmetry Reduction Package in PAT

We target systems that are composed of several sub-systems. In each sub-system, processes are instances that are instantiated from the same template. Being motivated by many examples such as Fischer's protocol or CSMA/CD protocol that clearly exhibit structural symmetries, we have extended the real-time model checker PAT with symmetry reduction. It operates in two stages:

- Detect symmetries from the system description. It results in all graph automorphisms that are sound with respect to reachability properties: an automorphism  $\alpha$  performs certain permutations on a state s and if a state s has been visited before, then all states  $\alpha(s)$  which are obtainable by applying these permutations to s have been also visited.

- Given a group of automorphisms, we generate the symmetry-reduced state space on-the-fly and check for a property  $\phi$  using Algorithm 4.

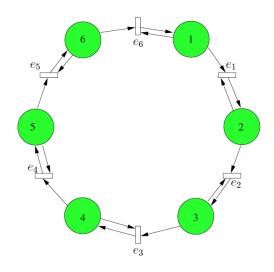

## 4.1 Dining Philosopher

We illustrate the method through the Dining Philosophers example. There are several philosophers who sit around a table with bowls of spaghetti. Forks are placed between every pair of philosophers and a philosopher can only start eating if he acquires both his left fork and the right fork. Figure 4.1 describes the Dining Philosophers example with 6 philosophers and 6 forks, where every edge on the model a shared fork.

Figure 4.1: Dining Philosophers Example

The philosopher process goes through the internal states T (thinking), H-1 (hungry-1), H-2 (hungry-2), E (eating), R-1 (release-1) and R-2(release-2):

- A transition from T to H-1 is always enabled.

- In state H-1, the philosopher tries to acquire the left fork. If the left fork is "busy", it retries in 52 time units. A transition from H-1 to H-2 is enabled after the philosopher has acquired the left fork.

- In state H-2, the philosopher tries to acquire the right fork. If the fork is "busy", it retries in 52 time units. A transition from H-2 to E is enabled after the philosopher has acquired the right fork.

- A transition from E to R-1 is enabled after 52 time units.

- In state R-1, the philosopher releases the left fork. A transition from R-1 to R-2 is always enabled.

- In state R-2, the philosopher releases the right fork. A transition from R-2 to T is always enabled.

The model has N philosophers instantiated from the template Phil and N forks instantiated from the template Fork below respectively. We define a high-level CSP definition of Dining Philosophers in PAT below:

$$Phil(i) = think.i \rightarrow get.i.(i+1)\%N \rightarrow get.i.i \rightarrow eat.i \rightarrow put.i.(i+1)\%N \rightarrow put.i.i \rightarrow Phil(i)$$

$$Fork(i) = get.i.i \rightarrow put.i.i \rightarrow Fork(i) \ \Box \ get.i.(i+1)\%N \rightarrow put.i.(i+1)\%N \rightarrow Fork(i)$$

$$P = ||| i : \{0, ..., N - 1\} @ (Phil(i) ||| Fork(i))$$

# 4.2 Symmetry Detection In The Specification

In this section, we introduce a technique to automatically detect structural symmetries arising from input process templates. Let P be a parameterized system with N processes instantiated from the same template T, the approach operates in three stages as follows:

- Recognize all valid variables of type *pid* used in *T*.

- Compute a set of all possible *state-swaps*, denoted Swap(P).

- Then each element  $\pi \in Swap(P)$  is checked for validity and finally results in a set of generators ValidSwap(P) that induces a group of automorphisms.

#### 4.2.1 Step 1: Detection of *pid* Variables

As mentioned in the previous chapter, a system composes of a set of process instances and *state-swap* performs certain permutations on a state *s*, which produces a rearrangement in the following manner: *process-swap* and *data-swap*.

While *process-swap* is trivial since processes originate from the same template, *data-swap* involves swapping variables and array entries of type *pid*. Unlike UPPAAL that a user needs to manually specify entities of type *pid* using the concept of *scalarset*, our method requires no additional information from a modeler.

To do so, we introduce *pid rules*, which allow variables of type *pid* to be used in certain ways as follows:

- (1) The process identifier i has type pid by default.

- (2) Given a variable x, type(x) = pid if and only if it is assigned to or compared for equality with another variable var, such that  $x \sim var$  where type(var) = pid and  $\sim \in [=, \neq, ==]$ .

- (3) It is not allowed to perform any arithmetical operations on variables of type *pid*.

- (4) Variable x of type *pid* is only allowed to used in the form of  $x \sim v$  where v is either a variable or value and  $\sim \in [=, \neq, ==]$ .

- (5) A[N] is an array of N elements of type *pid* if and only if type(A[i]) = pid.

Given these restrictions, Algorithm 5 presents the *pid*-type inference algorithm in PAT. Algorithm 5 runs on the template T. In PAT, T is stored as the syntax tree. Each whileloop iteration involves one pass over the syntax tree. Let *Next* be a set of *pid* variables to be analyzed and *Visited* be a set of analyzed *pid* variables. Initially, *Next* has at most one element - the process identifier *i*.

Inside a loop, first the model checker extracts a variable x from Next. Then the tool visits each guard g, each update u and each program statement ps to verify whether x is used inappropriately (violates any *pid rules*). Otherwise, x is added to ValidPids - the set of valid variables of type *pid*. The algorithm also adds any new variable y, which is related to x by the second pid rule, to Next. The algorithm only halts when Next is empty.

For any template T whose variables of type pid are used inappropriately, T is **invalid**. Currently, we do not support processes instantiated from invalid process templates to run with symmetry reduction.

Clearly, for systems that consist of N sub-systems (means that the system description has N input process templates), **Algorithm 5** will run N times.

Let P be a case of Dining Philosophers with just two philosophers  $(phil_1, phil_2)$  and the two forks  $(fork_1, fork_2)$ , which contains deadlock. First **Algorithm 5** runs on the template Phil. The template parameter *i* has type of *pid* by default and is added to Next. In the first loop, the tool extracts i from Next and goes through the computation logic of the template *Phil*. Since i does not violate or break *pid rules*, i is added to *ValidPids*. Since there is no variable that is related to i in the form defined in (2), **Algorithm 5** halts. Similarly, **Algorithm 5** runs on the template *Fork*. Since there is no invalid *pid* variable used in those templates, we say that P is valid to run with symmetry reduction.

#### Algorithm 5 *pid*-type Inference Algorithm

```

1: ValidPids = \emptyset

2: Visited = \emptyset

3: Next = \{i\}

4: isInvalidTemplate = false

5: while Next \neq \emptyset do

remove x from Next

6:

for each guard g / statement ps / update u in T do

7:

if g / ps / u contains x then

8:

if q / ps / u is in the form defined in (4) then

9:

if q / ps / u contains a variable y then

10:

if (y \text{ not} \in Visited) and (y \text{ not} \in Next) then

11:

add y to Next

12:

else

13:

isInvalidTemplate = true

14:

break

15:

if is Invalid Template == false then

16:

add x to ValidPids

17:

add x to Visited

18:

19: return FINISHED

```

#### 4.2.2 Step 2: Compute a Set of Possible Permutations

Once all valid variables of type *pid* have been recognized, the next step is to compute a set of all possible *state-swap* from the system description.

In the Dining Philosophers problem considered, assuming  $phil_1, phil_2$  are assigned indices of 1, 2 and  $fork_1, fork_2$  are assigned indices 3, 4 respectively. We define Swap(P) as a set, which consists of all permutations of the set of process identifiers  $\{1, 2, 3, 4\}$ . It results in a set of 24 elements to check for validity since only certain permutations are sound with respect to reachability properties.

#### 4.2.3 Step 3: Compute a Set of Generators

A state-swap  $\pi$  is called an automorphism of a system, if it satisfies the following three properties:

- It preserves the types of the processes.

- It preserves the associations of the processes it maps.

- It preserves the transition relation of the system.

For a given system P, the set of all possible *state-swap*, Swap(P), is computed from the previous step. For each element in this set, the algorithm checks if it is a valid permutation which means that it satisfies three properties above.

Back to the Dining Philosophers problem considered. The first property means that two processes must be instantiated from the same template. After checking for the first property and eliminating all permutations that map a philosopher to a fork and vice versa, we are left with 4 permutations namely:

$$\{1, 2, 3, 4\}, \{2, 1, 3, 4\}, \{1, 2, 4, 3\}, \{2, 1, 4, 3\}$$

The second property says that if a *state-swap*,  $\pi$ , maps  $phil_i$  to  $phil_j$  then the permutations of all forks associated with  $phil_i$  are now the forks associated with  $phil_j$  in the new system. These associations must be consistent with the original system description otherwise  $\pi$  is not an automorphism. In our example, the second property is violated by

$$\{2, 1, 3, 4\}, \{1, 2, 4, 3\}$$

Specifically, in  $\{2, 1, 3, 4\}$ , *phil*<sub>2</sub> will have *fork*<sub>2</sub> on the right and *fork*<sub>1</sub> on the left which violates the original system description. Algorithm 6 describes how a *state-swap* is checked for the second property.

| Algorithm 6 Implement CheckAssociation                                  |  |  |  |  |  |

|-------------------------------------------------------------------------|--|--|--|--|--|

| 1: if processes associated with $p_i = \{p_1, p_2,\}$ then              |  |  |  |  |  |

| 2: processes associated with $p_j = \{\pi(p_1), \pi(p_2),\}$            |  |  |  |  |  |

| 3: if $\{\pi(p_1), \pi(p_2),\}$ consistent with equations of $p_j$ then |  |  |  |  |  |

| 4: return true;                                                         |  |  |  |  |  |

|                                                                         |  |  |  |  |  |

Although processes are obtained as instances of a same parameterized process template, they are not necessarily identical up to renaming. The third property indicates that after the permutation, the new system must be equivalent to the original system. On other words, P and  $\pi(P)$  must be syntactically equivalent. This happens in **Algorithm 7**. In PAT, process templates are stored as syntax trees. **Algorithm 7** performs a depth-firstsearch on both trees and checks for their equivalence.

#### Algorithm 7 Implement CheckEquivalence

1: TreeNode A = P2: TreeNode  $B = \pi(P)$ 3: public boolean isEquivalent(TreeNode A, TreeNode B): 4: if isEquivalent(A.left, B.left) then 5: if isEquivalent(A.right, B.right) then 6: if A is equal to B then 7: return true; 8: return false:

Finally, given a set of all permutations Swap(P), Algorithm 8 shows how to compute a set of generators ValidSwap(P) that forms a group of automorphisms.

# Algorithm 8 Compute ValidSwap(P)1: Compute Swap(P)2: $ValidSwap(P) = \emptyset$ 3: for each $\pi \in Swap(P)$ do4: if $Type(p_i) == Type(p_j)$ then5: if $CheckAssociation(p_i, p_j)$ then6: if $CheckEquivalence(p_i, p_j)$ then7: add $\pi$ to ValidSwap(P).8: return ValidSwap(P)

ValidSwap(P) forms a group of automorphims Aut(P) under functional composition. This means that, Aut(P) had an identity element  $\pi$  that maps a process p onto itself or  $\pi(p) = p$ . Also, every other permutation  $\pi_i$  has an inverse element  $\pi_i^{-1}$  such that  $\pi_i^{-1}\pi_i(p) = p$ . In our example,  $\pi_1 = \{1, 2, 3, 4\}$  has an inverse element as  $\pi_2 = \{2, 1, 4, 3\}$ .

Figure 4.2: The state space of the dining philosopher.

## 4.3 Generate The Symmetry-reduced State Space

Once symmetry detection has been performed, **Symmetry Reduction** is performed to generate the symmetry-reduced state space on-the-fly using **Algorithm 4**.