# Development of Tunable RF Integrated Passive Devices

by

Ka Wai Wong

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2017

© Ka Wai Wong 2017

## **Examining Committee Membership**

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

External Examiner Aly Fathy

Professor

Supervisor(s) Raafat R. Mansour

Professor

Internal Member Safieddin Safavi-Naeini

Professor

Internal Member Siva Sivoththaman

Professor

Internal-external Member Eihab Abdel-Rahman

**Associate Professor**

## **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Radio frequency (RF) lumped elements are crucial building blocks for designing any type of passives circuits for RF front-end applications in mobile devices. In particular, high-quality (Q) factor lumped elements are desirable for improving both insertion loss and noise performance. Integrated passive devices (IPD) technology is a platform that can provide miniature inductors, and capacitors with high-Q values that are unattainable with traditional CMOS technologies. Over the past several years, IPD technology has been used to implement devices such as filters, couplers and impedance-matching networks for a wide range of system-in-package applications. However, most of the IPD circuits do not yet have any tunable/reconfigurable functions for use in frequency agile applications.

The objective of this research is to develop tunable integrated passive devices (IPDs) using barium strontium titanate (BST) and micro-electrical-mechanical-systems (MEMS) technologies. Another objective is to develop a fabrication process for monolithic integration of MEMS switches and IPD devices. A 4-mask IPD glass/alumina-based fabrication process is developed at the University of Waterloo for the first time. Details of the modeling and characterization of high-Q lumped elements, L and C, are investigated. The RF performance of these elements is compared with that of similar designs fabricated in a commercial IPD foundry. To highlight the benefits of the IPD process, lumped element bandpass filters are designed, fabricated, and tested.

BST varactors are integrated with IPD circuits to demonstrate a highly miniaturized tunable impedance matching network featuring a wide impedance coverage from 2-3 GHz and an insertion loss of approximately 1 dB. The network promises to be useful in a broad range of wireless applications. A high performance tunable IPD/BST bandstop filter with a wideband balun as a multichip module is also proposed. Reconfigurable IPD/BST bandpass filters with tunable transmission zeros are presented and investigated experimentally for operation under high power levels. Intermodulation test results are presented for the integrated IPD/BST devices.

Making use of the fact that the IPD fabrication process is amenable to the realization of MEMS devices, the IPD process originally developed for realizing passive circuits is further expanded to accommodate monolithic integration of MEMS switches with IPD circuits. Contact-type MEMS switches are developed, fabricated and tested. Also, a monolithically integrated IPD/MEMS 3-bit high resolution true-time delay network and high-Q switched-capacitor bank are fabricated and tested to demonstrate the benefits of integrating MEMS technology with the IPD technology.

## **Acknowledgements**

First and foremost, I would like to express my sincere gratitude to my advisor, Professor Raafat Mansour, for his ceaseless support throughout the years of my PhD studies. It is indeed my great honor and privilege to be his student. I deeply appreciate all of his patient guidance and discussions, which tremendously motivated me to do the best that I could in the world of research.

I am also grateful to have Prof. Safieddin Safavi-Naeini, Prof. Siva Sivoththaman and Prof. Eihab Abdel-Rahman as members of my PhD committee, and Prof. Aly Fathy from The University of Tennessee for taking the time to serve as my external examiner, all of whom contributed insightful feedback to my research.

In addition, I am grateful to be a part of the wonderful research team at the Centre for Integrated RF Engineering (CIRFE). I would like to thank our previous lab manager, Bill Jolley, who has shared his professional experience and has been a tremendous help in my research projects. I will never forget our jazz music discussions on top of our research discussions. My sincere gratitude also goes to my good officemate and friend, Scott Chen, who I talked, shared, and laughed with throughout the entire PhD journey. I would also like to thank our CIRFE members, too, including Kevin Yang, Raisa Pesel, Ahmed Aziz, Mostafa Azizi, Sara Attar, Arash Fomani, Frank Jiang, Siamak Fouladi, Saman Nazari, Johnny Jiang, Salam Gabran, Desireh Shojaei-Asanjan, Sormeh Setoodeh, Neil Sarkar, Geoff Lee, Farzad Yazdani, Chris Schroeder and other new members as well. Additionally, I wish to thank our industrial partner, Gareth Weale (ON Semiconductor), who worked very closely with us and supported our research.

No words can fully express how grateful I am to you, my dear mum, for constantly supporting me throughout this special research journey. You set a role model for me to follow, and your love and spiritual support are my driving force to work hard. I would like to also thank my sisters and other family members who always bring a lot of fun, humor, and continuous long-distance support to shape me who I am today. A special thanks goes to my church communities in Waterloo, Hong Kong and Toronto, and to the people I grew up with. Your continuous support and deep friendships have been a blessing to me. Every one of you has contributed to and enlightened my life. Last but not least, I thank my Lord, Jesus Christ, for giving me a chance to discover something he has created for us all.

Laus Deo

Oliver Ka Wai WONG, Waterloo, NOV 2016.

## **Table of Contents**

| Examining Committee Membership                                                       | ii  |

|--------------------------------------------------------------------------------------|-----|

| Author's Declaration                                                                 | iii |

| Abstract                                                                             | iv  |

| Acknowledgements                                                                     | v   |

| List of Figures                                                                      | ix  |

| List of Table                                                                        | ixv |

| Chapter 1 Introduction                                                               | 1   |

| Chapter 2 Literature Review                                                          | 8   |

| 2.1 Thin-film Integrated Passive Device (IPD) Platform                               | 8   |

| 2.1.1 IPD RF Bandpass Filter                                                         | 9   |

| 2.1.2 IPD RF Lowpass Filter                                                          | 11  |

| 2.1.3 RF Diplexer                                                                    | 12  |

| 2.2 RF MEMS Tunable Filters                                                          | 13  |

| 2.2.1 Tunable Filter with MEMS Capacitive Membrane Switch                            | 14  |

| 2.2.2 Tunable Filter with MEMS Capacitive Membrane Switch on an Inductor             | 15  |

| 2.2.3 Tunable Filter with MEMS Varactor                                              | 16  |

| Chapter 3 Development of the Integrated Passive Device (IPD) Fabrication Process and |     |

| Its Components                                                                       | 19  |

| 3.1 Introduction                                                                     | 19  |

| 3.2 Integrated Passive Device (IPD) Fabrication Considerations                       | 20  |

| 3.3 Integrated Passive Devices Process                                               | 23  |

| 3.4 Modeling and Characteristics of IPD Inductor                                     | 28  |

| Series Inductance                                                                    | 29  |

| Series Resistance                                                                    | 32  |

| Series Capacitance                                                                   | 34  |

| Q-factor of an Inductor                                                              | 35  |

| 3.5 Inductor Design Considerations                                                   | 36  |

| Metal Width (W)                                                                      | 38  |

| Number of Turns (N)                                                                  | 40  |

| Thickness of Copper (t)                                                              | 41  |

| 3.6 Modeling and the Characteristics of the IPD Capacitor                                 | 42     |

|-------------------------------------------------------------------------------------------|--------|

| 3.7 Modified Third-order Chebyshev Bandpass Filter                                        | 45     |

| 3.8 Impedance Tuner                                                                       | 53     |

| 3.8.1 Design of Impedance Tuner Using Alumina-based IPD Process                           | 55     |

| 3.8.2 Measurement Results                                                                 | 56     |

| 3.9 Summary                                                                               | 59     |

| Chapter 4 Reconfigurable/Tunable Integrated Passive Devices (IPD) Bandstop and Bandpass l | Filter |

| with Wideband Balun Using Barium Strontium Titanate (BST) Varactors                       | 60     |

| 4.1 Introduction                                                                          | 60     |

| 4.2 Barium Strontium Titanate (BST) Varactor                                              | 63     |

| 4.3 Compact Tunable Bandstop Filter Using BST Varactors                                   | 65     |

| 4.3.1 Design Structure and Operation                                                      | 65     |

| 4.3.2 Simulated and Measurement Results                                                   | 68     |

| 4.3.3 Linearity of the Tunable Bandstop Filter and its Performance with the IPD           |        |

| Wideband Balun                                                                            | 71     |

| 4.4 IPD Wideband Balun                                                                    | 75     |

| 4.4.1 Design Structure and Operation                                                      | 75     |

| 4.5 Reconfigurable IPD-based Bandpass Filters                                             | 85     |

| 4.6 Summary                                                                               | 91     |

| Chapter 5 Monolithic IPD-MEMS Technology and Its Applications to Delay-line Networks ar   | nd     |

| Switched Capacitor Banks                                                                  | 92     |

| 5.1 Introduction                                                                          | 92     |

| 5.2 Proposed Alumina-based IPD-MEMS Technology                                            | 94     |

| 5.3 DC-contact MEMS Switch Using IPD-MEMS Technology                                      | 95     |

| 5.4 True-time Delay Network Design                                                        | 99     |

| 5.4.1 Multi-bit Lumped-element Delay-line Network                                         | 100    |

| 5.4.2 Three-bit Digital True Time Delay (TTD) Network Using MEMS Switches                 | 103    |

| 5.4.3 Three-bit Continuous Tuning TTD Network Using MEMS and BST Technology               | 112    |

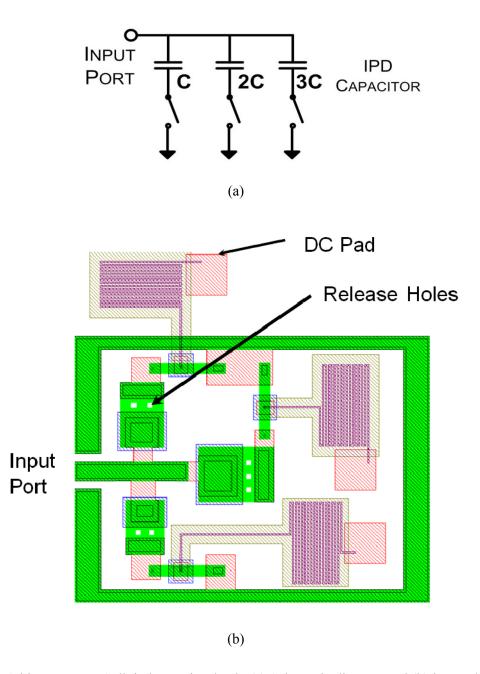

| 5.5 IPD-MEMS Digital Capacitor Bank                                                       | 117    |

| 5.6 Possible Applications for High-Q Varactors                                            | 121    |

| 5.7 Summary                                                                               | 124    |

| Chapter 6 Conclusions                                                                     | 125    |

| 6.1 Contributions | . 125 |

|-------------------|-------|

| 6.2 Future Work   | . 126 |

| References        | . 127 |

| Appendix A        | . 135 |

| Appendix B        | . 140 |

| Appendix C        | . 145 |

## **List of Figures**

| Figure 1.1 | Circuit board of the Blackberry Bold                                                   | 2    |

|------------|----------------------------------------------------------------------------------------|------|

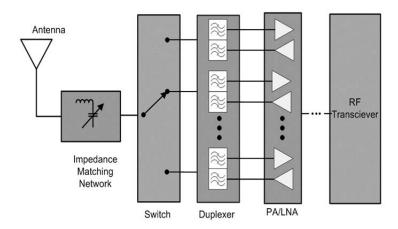

| Figure 1.2 | A typical multi-band transceiver configuration.                                        | 5    |

| Figure 2.1 | A typical geometry of IPD process                                                      | 9    |

| Figure 2.2 | Ultra-wideband (UWB) bandpass filter using silicon IPD technology by STATS             |      |

|            | ChipPAC Inc. (a) Thin-film IPD structure. (b) Schematic of the filter. (c) Layout of   |      |

|            | the UWB filter and (d) frequency response of the UWB bandpass filter [15]              | . 10 |

| Figure 2.3 | IPD GSM lowpass filter. (a) Layout of the lowpass filter and (b) frequency response of |      |

|            | the lowpass filter [17].                                                               | . 11 |

| Figure 2.4 | 900/1800 MHz diplexer by KAIST. (a) Layout of the filter. (b) IPD structure from       |      |

|            | KAIST on aluminum substrate and (c) frequency response of the duplexer [18]            | . 13 |

| Figure 2.5 | Tunable bandpass filter by using capacitive membrane switch. (a) RF MEMS               |      |

|            | capacitive membrane switch. (b) 4-bit variable capacitor. (c) Tunable capacitor        |      |

|            | with inductor network (size: 3.5 mm×14 mm) and (d) 5-pole frequency response [19]      | . 15 |

| Figure 2.6 | Bandpass filter using the tunable short-circuit inductor (a) Layout of the tunable     |      |

|            | bandpass filter. (b) Schematic of the bandpass filter and (c) the frequency response   |      |

|            | for different actuation of the switch [20]                                             | . 16 |

| Figure 2.7 | Bandpass filter using the MEMS varactor (a) Layout of MEMS varactors. (b) Layout       |      |

|            | of the bandpass filter and (c) the frequency response for different actuations of the  |      |

|            | switch [21].                                                                           | . 17 |

| Figure 2.8 | A two-pole, 850-1750 MHz tunable filter built using the off-chip air coil inductor     | . 18 |

| Figure 3.1 | Characterization of the 10 µm thick positive photoresist AZ-9260.                      | . 21 |

| Figure 3.2 | Proposed 4-mask IPD fabrication process flow.                                          | . 25 |

| Figure 3.3 | Fabrication picture in steps (e) and (f) in Figure 3.2.                                | . 26 |

| Figure 3.4 | Fabrication picture in step (g) in Figure 3.2 before depositing the seed layer         | . 26 |

| Figure 3.5 | Final fabrication: (a) Capacitor, (b) Inductor and (c) 1st preliminary wafer and       |      |

|            | (d) completely successful IPD wafer.                                                   | . 27 |

| Figure 3.6 | Geometry of the thick copper inductor.                                                 | . 28 |

| Figure 3.7 | Physical lumped model of a spiral inductor on glass substrate [13].                    | . 29 |

| Figure 3.8 | Current flow in the inductor.                                                          | . 30 |

| Figure 3.9 | Different implementations of inductor (a) square, (b) octagonal, (c) hexagonal and     |      |

|            | (d) circular.                                                                          | .31  |

| Figure 3.10 | Effective metal thickness for different frequencies.                                       | . 34 |

|-------------|--------------------------------------------------------------------------------------------|------|

| Figure 3.11 | One-turn inductor (w: 50 µm and din=500 µm)                                                | . 36 |

| Figure 3.12 | 2 (a) Measured and simulated Q-factor and inductance vs. frequency (5um thick              |      |

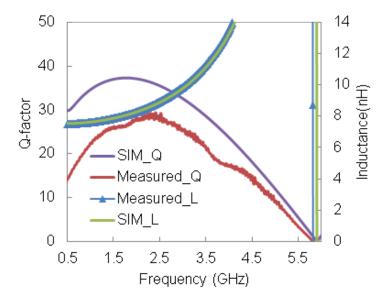

|             | copper) and (b) its Smith chart.                                                           | 37   |

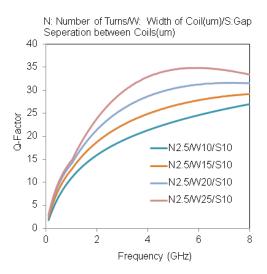

| Figure 3.13 | Simulated Q-factor vs width of the coil                                                    | . 38 |

| Figure 3.14 | The self-resonant frequency decreases as the of the width of the coil increases            | 38   |

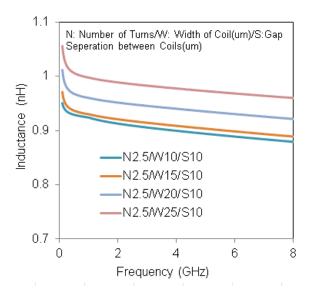

| Figure 3.15 | 5 Change in inductance as the width of the coil increases for 2.5 turns.                   | . 39 |

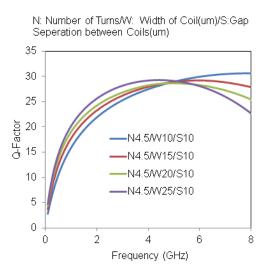

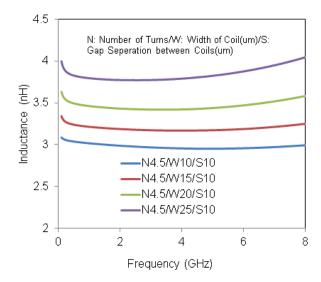

| Figure 3.16 | 6 Change in inductance as the width of the coil increases for 4.5 turns.                   | 39   |

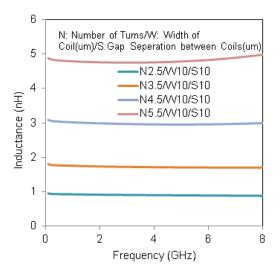

| Figure 3.17 | 7 Inductance versus number of turns.                                                       | . 40 |

| Figure 3.18 | 3 Measured and simulated Q-factor and inductance vs frequency (3.5 turns)                  | . 40 |

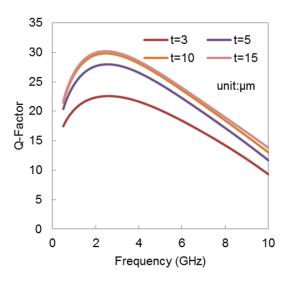

| Figure 3.19 | 9 Simulated Q-factor vs copper thickness (N=2.5, din =160 μm)                              | . 41 |

| Figure 3.20 | Geometry of the capacitor with an area of 120 μm <sup>2</sup>                              | . 42 |

| Figure 3.21 | Equivalent model of the capacitor.                                                         | 42   |

| Figure 3.22 | 2 Simplified model of the IPD capacitor (ignoring the loss in the glass substrate)         | . 42 |

| Figure 3.23 | 3 Frequency response of a 120 μm² capacitor (after correcting the dielectric constant)     | . 44 |

| Figure 3.24 | Corrected frequency response of a 120 µm <sup>2</sup> capacitor (with consideration of the |      |

|             | copper oxide)                                                                              | . 44 |

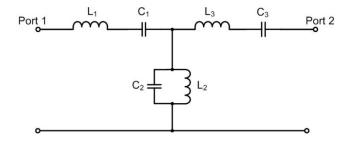

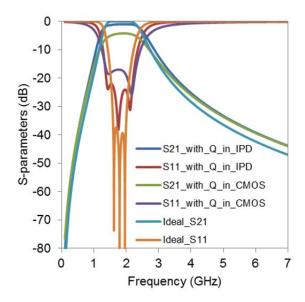

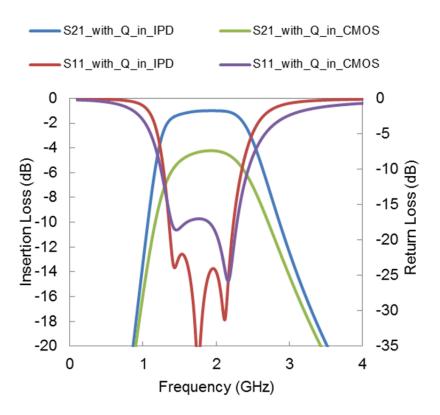

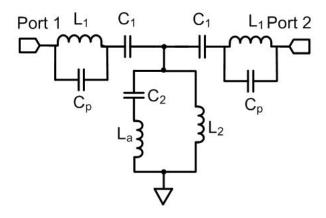

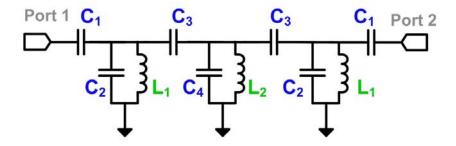

| Figure 3.25 | Schematic diagram of the third-order Chebyshev bandpass filter                             | . 46 |

| Figure 3.26 | 6 Frequency response of the third-order Chebyshev filter, with comparisons of the          |      |

|             | lumped elements in ideal, IPD and CMOS platforms.                                          | 46   |

| Figure 3.27 | Comparison of the insertion loss between high-Q L-C elements in IPD (blue) and             |      |

|             | SOI CMOS 65nm process (green)                                                              | 47   |

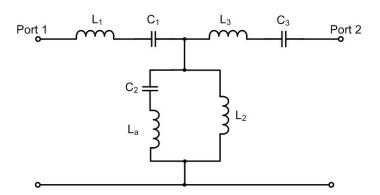

| Figure 3.28 | 3 Schematic of the modified third-order Chebyshev bandpass filter, with an extra indu      | ctor |

|             | (La) at the shunt resonator.                                                               | . 47 |

| Figure 3.29 | Frequency response after adding the small inductor.                                        | 48   |

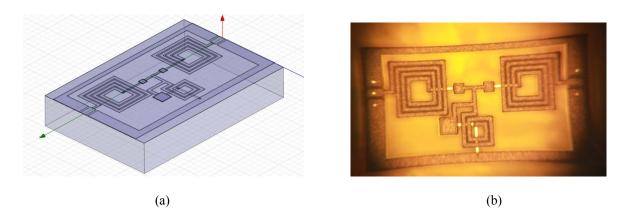

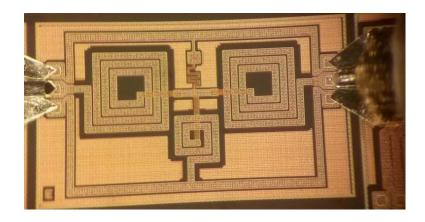

| Figure 3.30 | Layout of proposed IPD bandpass filter. (a) 3D structure in EM simulation. (b)             |      |

|             | Final modified third-order Chebyshev bandpass filter developed in CIRFE at                 |      |

|             | the University of Waterloo.                                                                | . 48 |

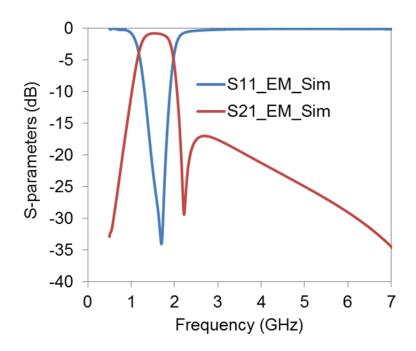

| Figure 3.31 | EM-simulated frequency response of bandpass filter (S21: ~ -1dB)                           | 49   |

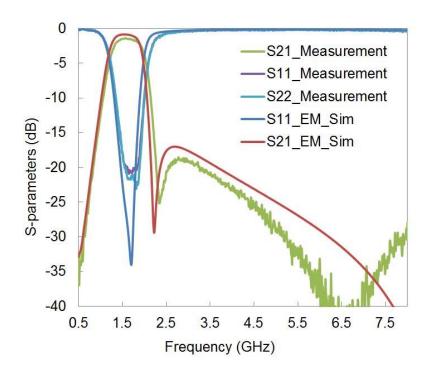

| Figure 3.32 | 2 Measured and simulated results of modified third-order Chebyshev bandpass filter         | 49   |

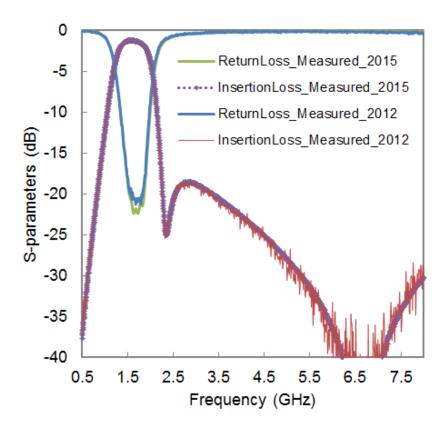

| Figure 3.33 | Measured results comparison of our proposed IPD bandpass filter between the year           |      |

|             | of 2012 and 2015                                                                           | . 50 |

| Figure 3.34 Schematic of third-order bandpass filter with an extra inductor at the shunt resonator | 51       |

|----------------------------------------------------------------------------------------------------|----------|

| Figure 3.35 Picture of modified third-order Chebyshev bandpass filter fabricated by                |          |

| ON Semiconductor.                                                                                  | 51       |

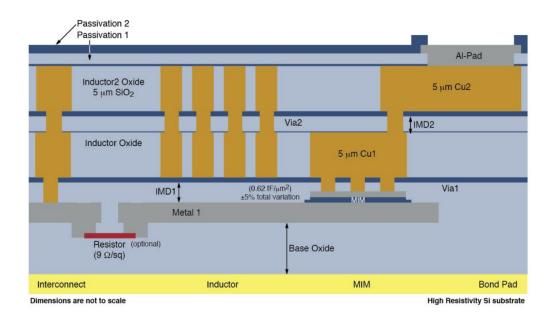

| Figure 3.36 Picture of an 8-inch IPD wafer fabricated by ON Semiconductor                          | 52       |

| Figure 3.37 IPD layer process diagram from ON Semiconductor.                                       | 52       |

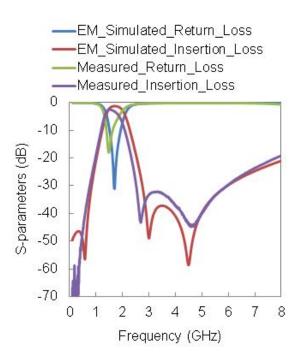

| Figure 3.38 Frequency performance of EM simulated and measured results.                            | 53       |

| Figure 3.39 Possible RF front-end configuration.                                                   | 54       |

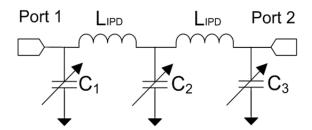

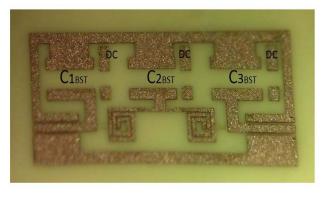

| Figure 3.40 Schematic of the proposed impedance tuner with our developed IPD process and           |          |

| BST varactors.                                                                                     | 55       |

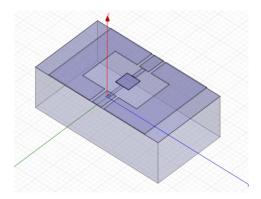

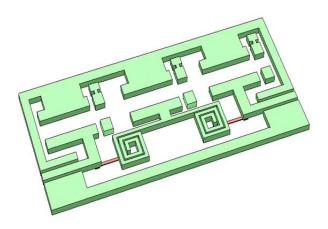

| Figure 3.41 3-D diagram for EM simulation. *z-dimension not to scale.                              | 56       |

| Figure 3.42 Proposed IPD impedance tuner (a) without BST varactors and (b) with BST                |          |

| varactors. *size: 3.8 mm x 1.88 mm (with DC pads).                                                 | 57       |

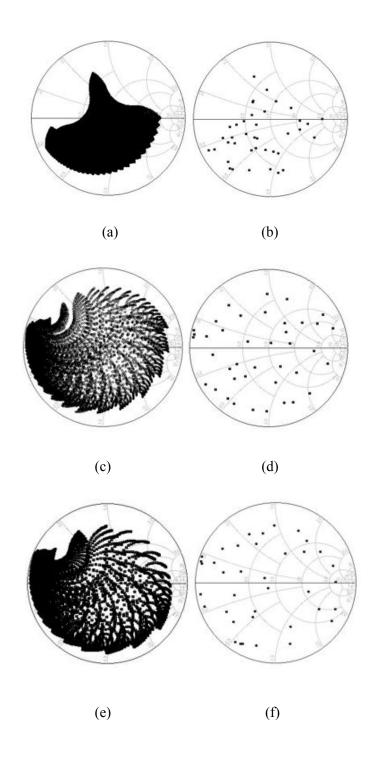

| Figure 3.43 Simulated and measured impedance coverage at different frequencies. (a) Simulated      |          |

| and (b) measured results at 2 GHz. (c) Simulated and (d) measured results at 2.7 GHz               | <b>.</b> |

| (e) Simulated and (f) measured results at 3 GHz                                                    | 58       |

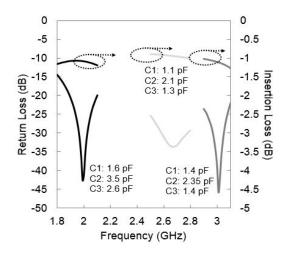

| Figure 3.44 Measured insertion loss and return loss when it is terminated at 50-ohm at both ports  |          |

| at different frequencies.                                                                          | 59       |

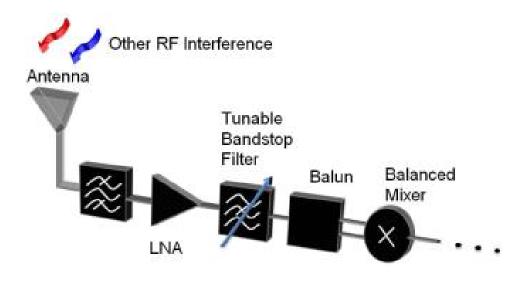

| Figure 4.1 Block diagram of a possible RF front-end configuration.                                 | 61       |

| Figure 4.2 ON Semiconductor IPD process.                                                           | 63       |

| Figure 4.3 BST varactor from ON Semiconductor.                                                     | 64       |

| Figure 4.4 Tunable bandstop filter. (a) A traditional tunable BSF using 90-degree transmission     |          |

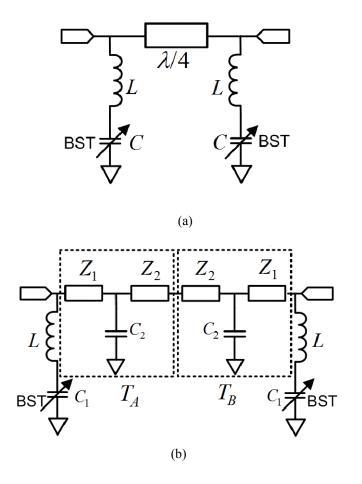

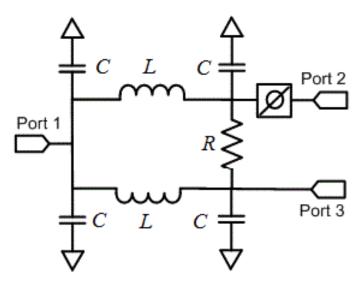

| line. (b) Proposed miniaturized IPD BSF using distributed and lumped elements                      | 65       |

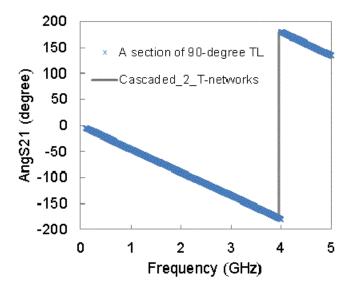

| Figure 4.5 Simulated phase response between the two cascaded T-networks and one section of a       |          |

| 90-degree transmission line.                                                                       | 67       |

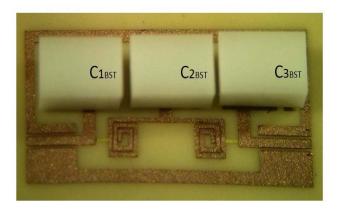

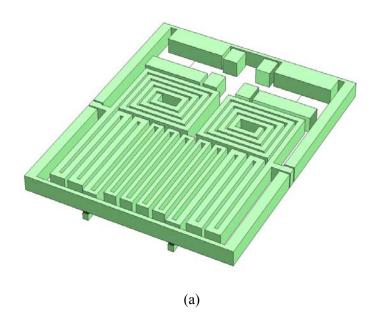

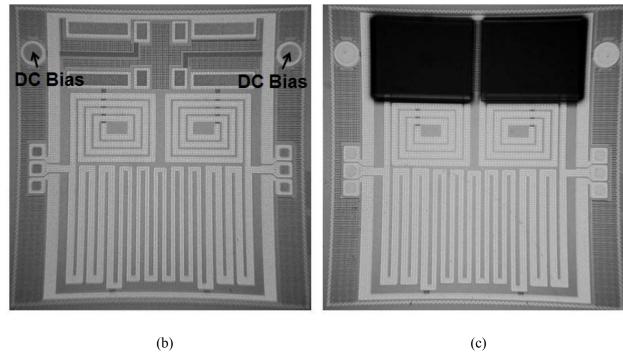

| Figure 4.6 Picture of tunable IPD bandstop filter. (a) 3D- structure* (b) layout without BST       |          |

| (c) layout with flip-chip BST (size: 2.6 mm x 2.6 mm). *not to scale in z-direction                | 68       |

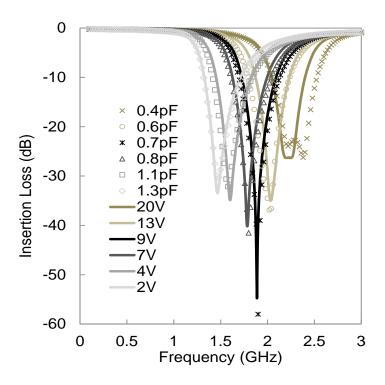

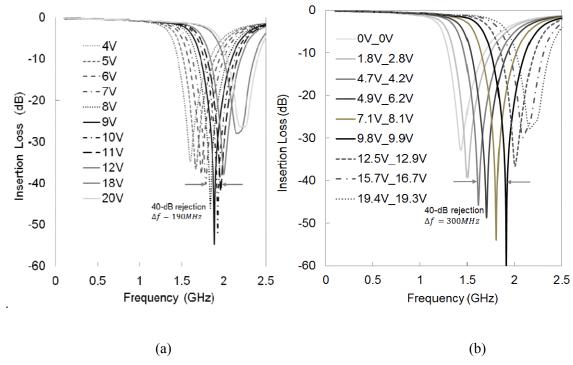

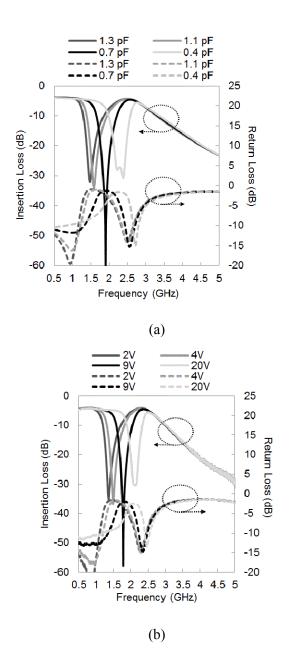

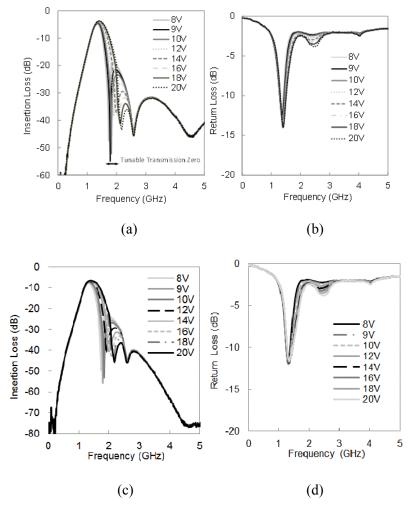

| Figure 4.7 The EM-simulated (dots) and measured (solid lines) results.                             | 69       |

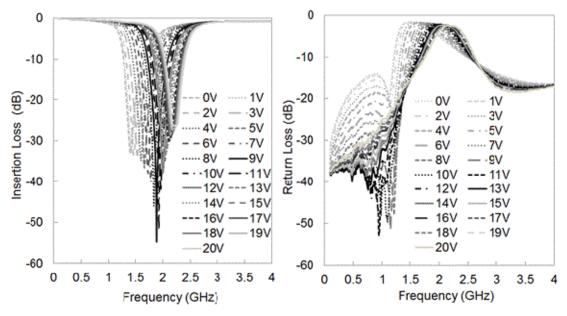

| Figure 4.8 Measured insertion loss and return loss of the continuously tunable IPD bandstop        |          |

| filter with synchronous DC bias.                                                                   | 70       |

| Figure 4.9 Measured tuning bandwidth with 40-dB rejection of the continuously tunable              |          |

| IPD bandstop filter with (a) synchronous DC bias and (b) asynchronous DC bias                      | 70       |

| Figure 4.10 Measured 20-dB fractional bandwidth                                                    | 71       |

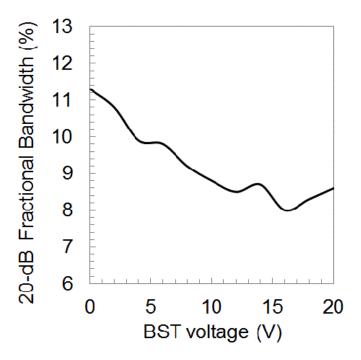

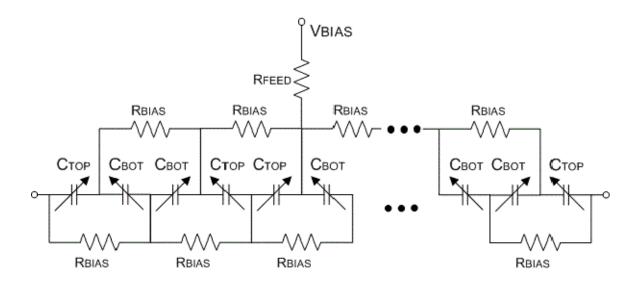

| Figure 4.11 Internal structure of S24 tunable BST varactor.                                     | 72 |

|-------------------------------------------------------------------------------------------------|----|

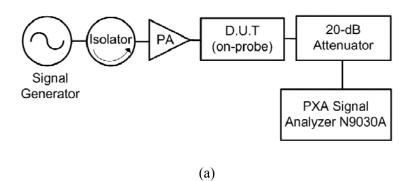

| Figure 4.12 Experiment set-up for IP <sub>3</sub> measurement.                                  | 73 |

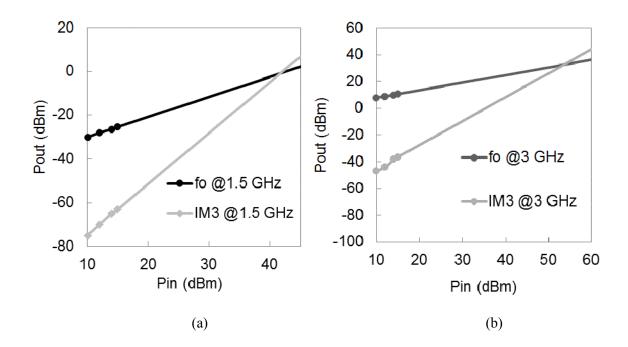

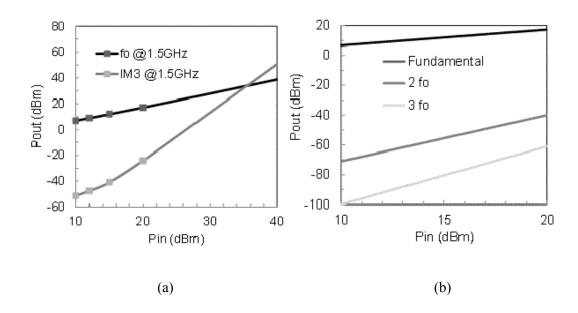

| Figure 4.13 IP <sub>3</sub> test performance for the tunable BSF (a) stopband and (b) passband  | 73 |

| Figure 4.14 Schematic of the IPD wideband balun for RF front ends.                              | 75 |

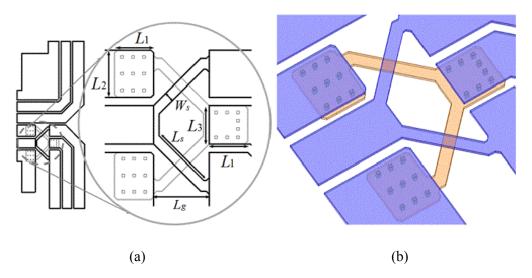

| Figure 4.15 Structure of the IPD phase inverter terminated by 50-ohm CPW line. (a) Dimensions   |    |

| of the phase inverter from top view in Table 4.5. (b) 3-D view including the via                |    |

| locations (not to scale in z-direction).                                                        | 77 |

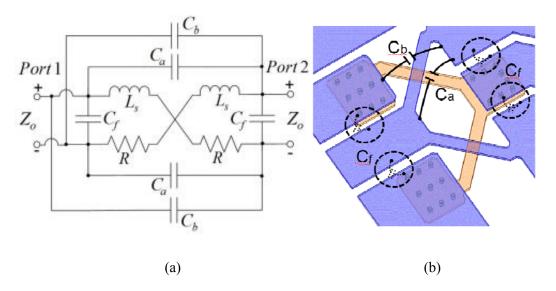

| Figure 4.16 (a) Equivalent circuit model of the IPD phase inverter. (b)Parasitics in 3D diagram |    |

| (not to scale in z-direction).                                                                  | 78 |

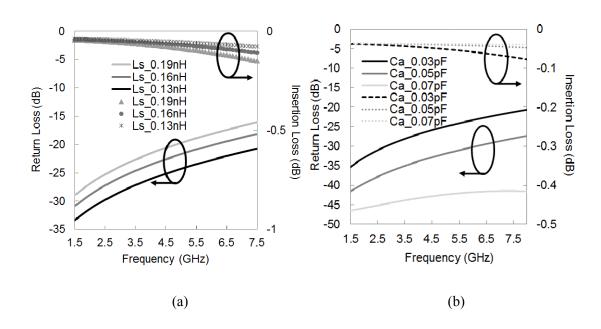

| Figure 4.17 The effect of strip line inductance $(L_s)$ and coupling capacitance $(C_a)$ of the |    |

| phase inverter. (a) $L_s$ vs. insertion/return Loss. (b) $C_a$ vs. insertion/return Loss.       |    |

| (c) $L_s$ vs. phase difference. (d) $C_a$ vs. phase difference                                  | 79 |

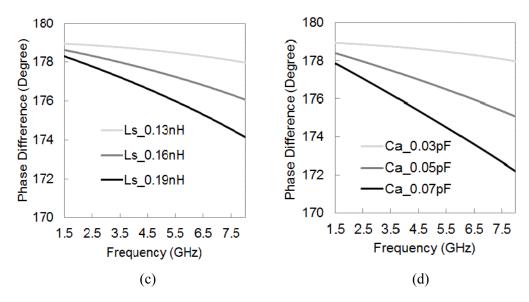

| Figure 4.18 Picture of the phase inverter (left) and a section of transmission line (right)     | 79 |

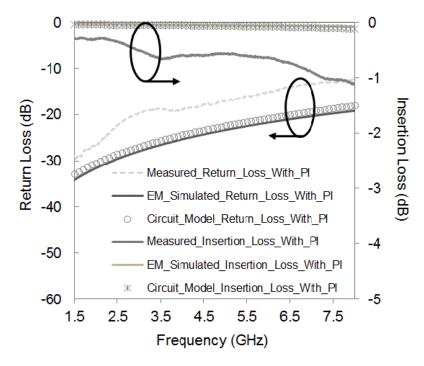

| Figure 4.19 The circuit-simulated, EM-simulated and measured results of the phase inverter      | 80 |

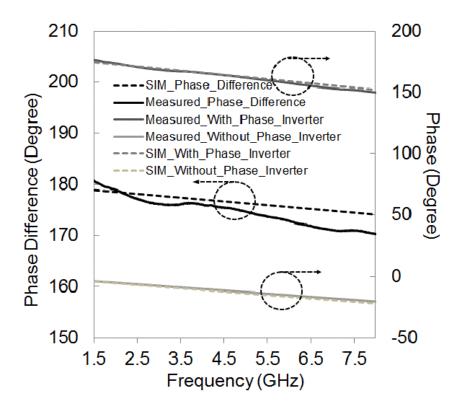

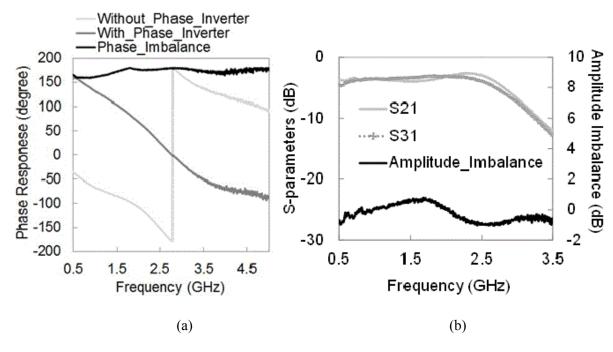

| Figure 4.20 Simulated and measured phase differences with and without phase inverter            | 81 |

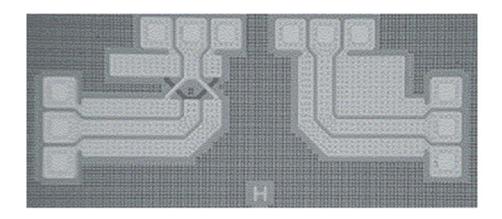

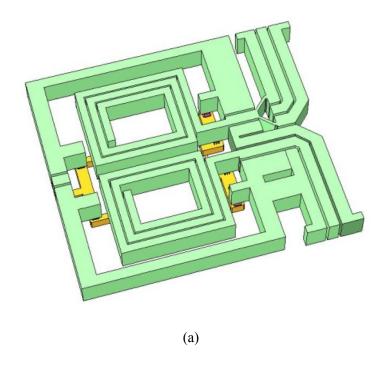

| Figure 4.21 Picture of wideband balun. (a) 3D structure* (b) circuit layout                     |    |

| (size: 2 mm x 1.9 mm). *not to scale in z-direction.                                            | 82 |

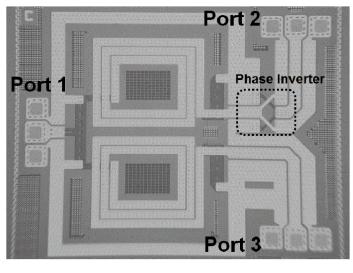

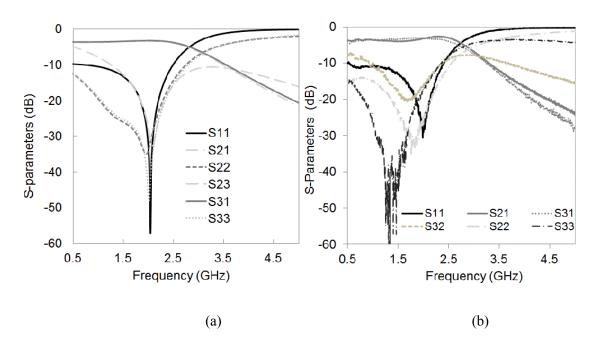

| Figure 4.22 (a) EM-Simulated and (b) measured S-parameters of the wideband IPD balun            | 83 |

| Figure 4.23 Measured (a) phase and (b) amplitude imbalance of the wideband IPD balun            | 83 |

| Figure 4.24 (a) Simulated and (b) measured tunable BSF cascaded with the IPD balun.             | 84 |

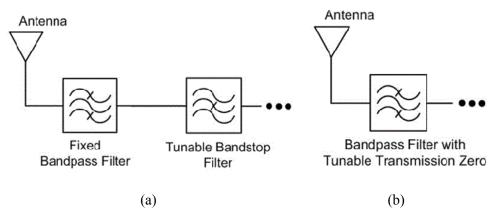

| Figure 4.25 Possible configuration of a bandpass filter with tunable zero functionality.        |    |

| (a) A fixed bandpass filter cascaded with a tunable bandstop filter. (b) A bandpass             |    |

| filter with transmission zero function.                                                         | 85 |

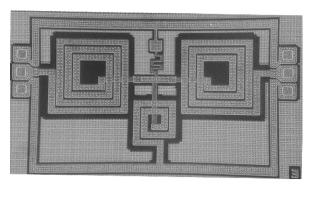

| Figure 4.26 Third-order modified Chebyshev IPD bandpass filter with two transmission zeros.     |    |

| (a) Schematic of the bandpass filter. (b) Picture of the bandpass filter                        |    |

| (size: 2.6 mm × 1.5 mm).                                                                        | 86 |

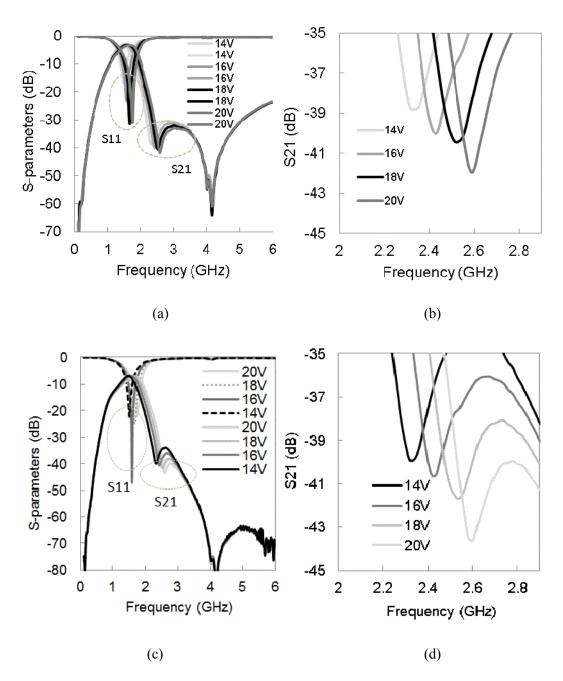

| Figure 4.27 Measured insertion loss and return loss of the IPD bandpass filter cascaded with    |    |

| the tunable IPD bandstop filter using synchronous DC bias, without balun (a) and                |    |

| (b), and with balun (c) and (d).                                                                | 87 |

| Figure 4.28 IPD bandpass filter with built-in tunable transmission zero. (a) Schematic          |    |

| (b) Layout without BST and (c) layout with BST (size: 2.6 mm× 2.5 mm)                           | 88 |

| Figure 4.29 Measured response of the IPD bandpass filter with built-in tunable transmission             |            |

|---------------------------------------------------------------------------------------------------------|------------|

| zeros. Without balun: (a) insertion and return loss (b) rejection level at around                       |            |

| 2.4 GHz. With balun: (c) insertion and return loss (d) rejection level at                               |            |

| around 2.4 GHz.                                                                                         | 90         |

| Figure 4.30 Measured (a) IP <sub>3</sub> performance: 10 MHz tone spacing and (b) harmonics performance |            |

| of the IPD bandpass filter with built-in transmission zero without balun.                               | 91         |

| Figure 5.1 Proposed alumina-based IPD-MEMS fabrication process.                                         | 95         |

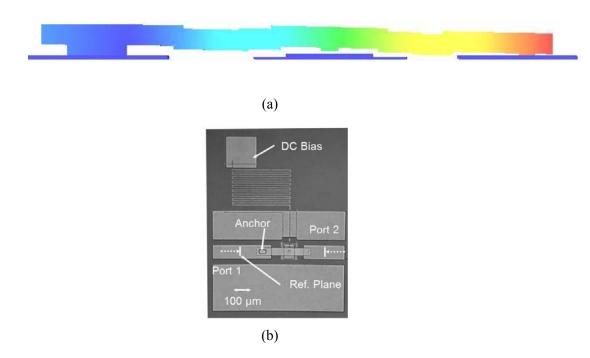

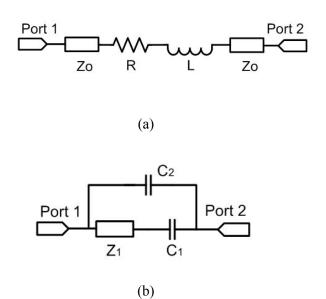

| Figure 5.2 DC-contact cantilever MEMS switch (a) side view of the membrane * not to scale               |            |

| (b) MEMS switch terminated by a 50-ohm CPW line.                                                        | 96         |

| Figure 5.3 Simplified circuit model when the series MEMS switch is (a) ON and (b) OFF                   | 97         |

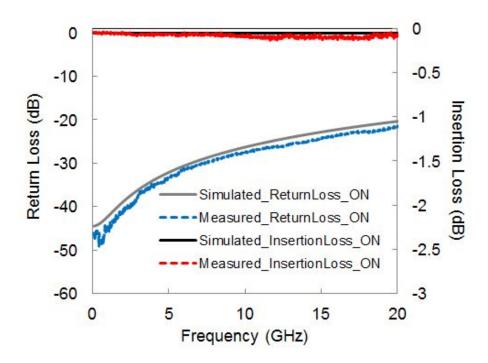

| Figure 5.4 Simulated (fitted model) and measured results for MEMS switch in the ON-state                | 98         |

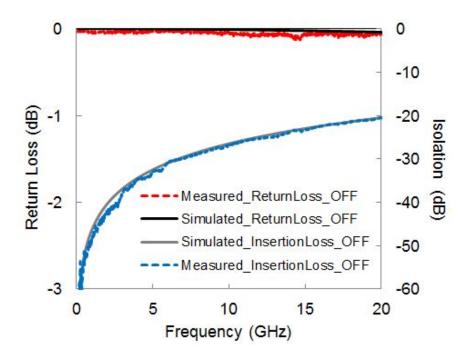

| Figure 5.5 Simulated (fitted model) and measured results for MEMS switch in the OFF-state               | 98         |

| Figure 5.6 Ideal lumped element 3-bit delay-line network using ideal switches.                          | 00         |

| Figure 5.7 Phase change for the ideal 3-bit delay-line network shown in Figure 5.6                      | 01         |

| Figure 5.8 Group delay for the ideal 3-bit delay-line network shown in Figure 5.6.                      | 02         |

| Figure 5.9 S-parameters for the ideal 3-bit delay-line network shown in Figure 5.6                      | 02         |

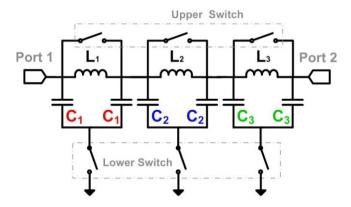

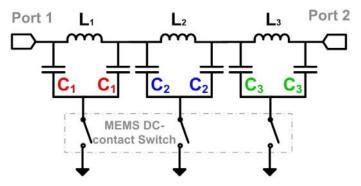

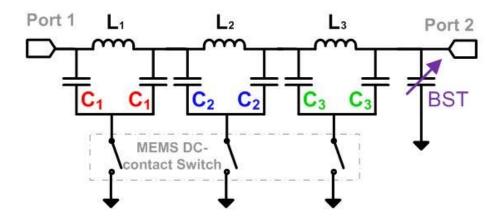

| Figure 5.10 Schematic diagram of the proposed 3-bit IPD-MEMS true-time delay network                    | 03         |

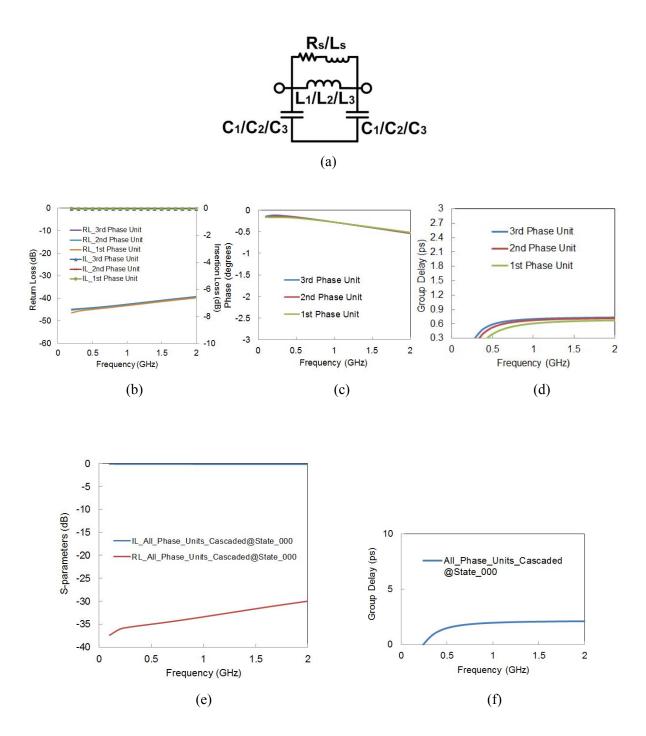

| Figure 5.11 Simulated results with upper switch when lower switch is OFF. (a) Schematic of a            |            |

| one-bit configuration without the lower switch (b) S-parameters of the individual unit.                 |            |

| (c) Phase shift of the individual unit. (d) Group delay of the individual unit.                         |            |

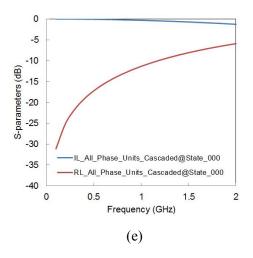

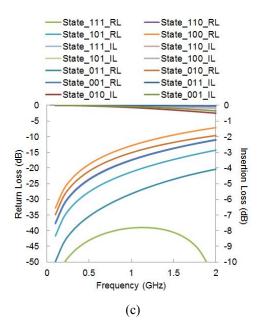

| *Rs= $0.6 \Omega$ , Ls= $0.077 \text{ nH}$ . (e) S-parameters of the cascaded three phase units at      |            |

| state 000. (f) Group delay of the cascaded three phase units at state 000                               | 04         |

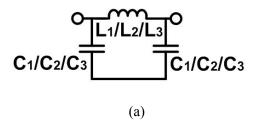

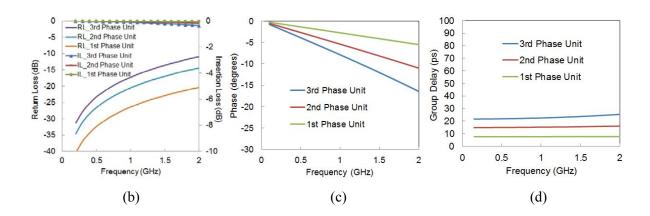

| Figure 5.12 Simulated results without upper switch when lower switch is OFF. (a) S-parameters           |            |

| of the individual unit. (b) Phase shift of the individual unit. (c) Group delay of                      |            |

| the individual unit. (e) S-parameters of the cascaded three phase units at state 000.                   |            |

| (f) Group delay of the cascaded three phase units at state 000                                          | 06         |

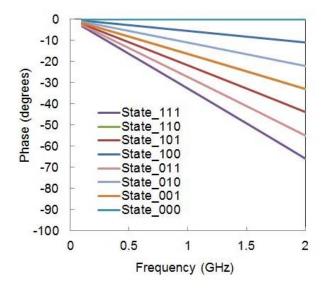

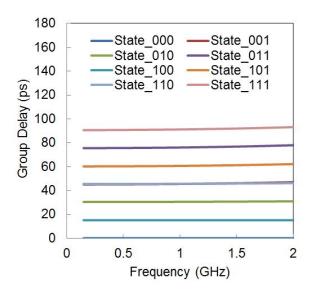

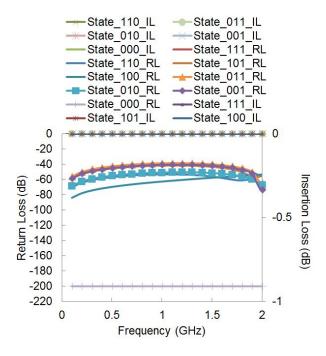

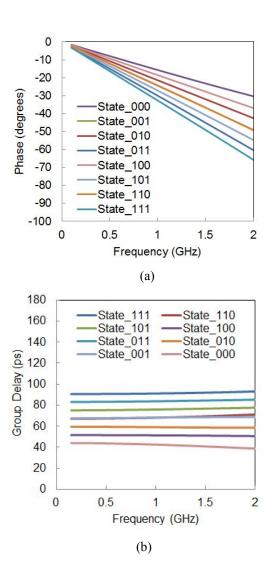

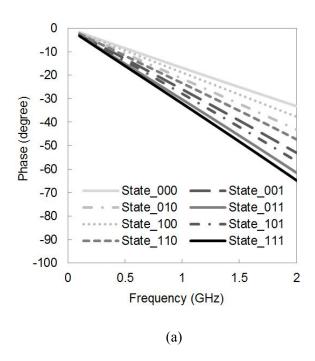

| Figure 5.13 Circuit simulations for the schematic shown in Figure 5.8. (a) Phase shift with 3-bit       |            |

| ideal switches. (b) Group delay with 3-bit ideal switches. (c) S-parameters with                        |            |

| 3-bit ideal switches.                                                                                   | 08         |

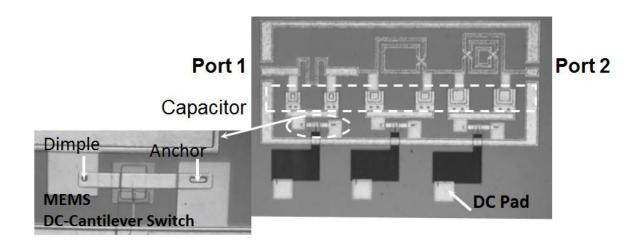

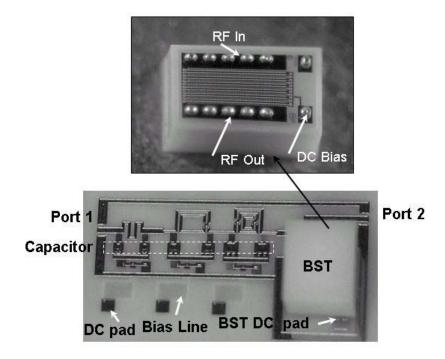

| Figure 5.14 Picture of the proposed IPD-MEMS TTD network (right)* and DC cantilever                     |            |

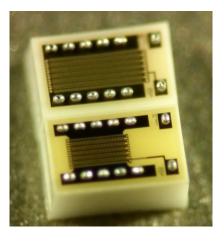

| contact switch (left) *chin size: 2 mm × 1.3 mm                                                         | <b>0</b> 9 |

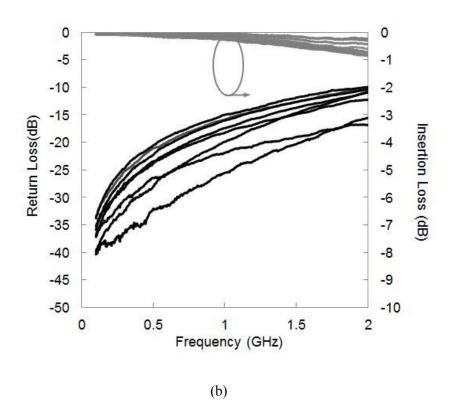

| Figure 5.15 EM-simulated performance for all 8 states. (a) Phase shift. (b) Group delay.        |       |

|-------------------------------------------------------------------------------------------------|-------|

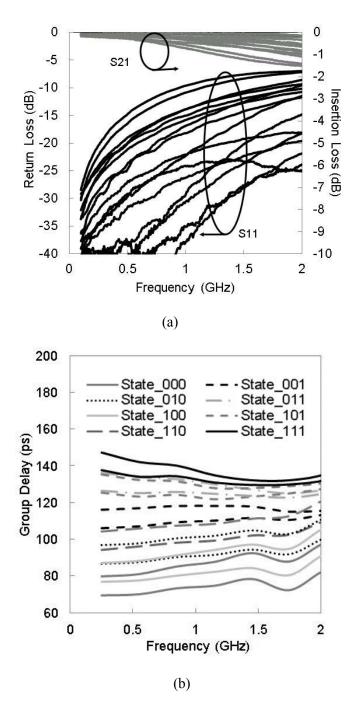

| (c) Return loss and insertion loss.                                                             | . 110 |

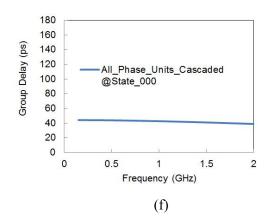

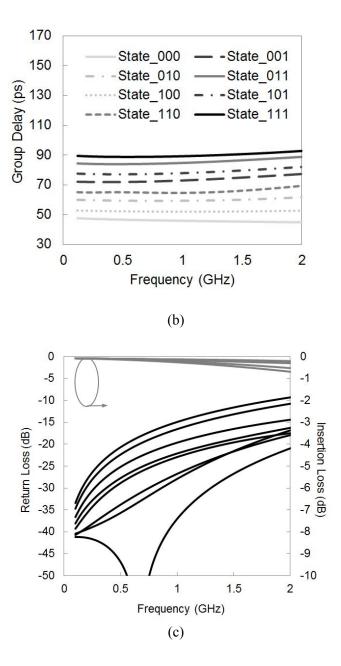

| Figure 5.16 Measured performance for all 8-state pull-in voltage: 120 V. (a) Group delay of the |       |

| TTD network. (b) Return loss and insertion loss.                                                | . 112 |

| Figure 5.17 Schematic diagram of the proposed IPD-MEMS phase shifter loaded with BST for        |       |

| phase correction.                                                                               | . 113 |

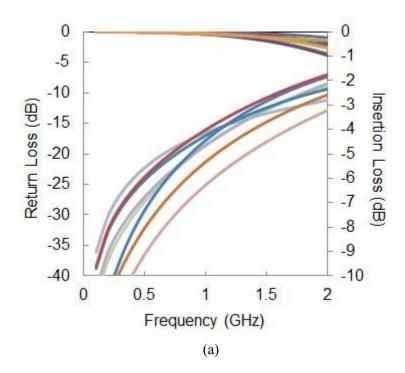

| Figure 5.18 Simulated performance for 16 states* with the lumped model for MEMS switches        |       |

| (a) return loss and insertion loss. (b) Phase shift. *Only 0.5 pF (lower boundary)              |       |

| and 0.9 pF (upper boundary) are plotted.                                                        | . 114 |

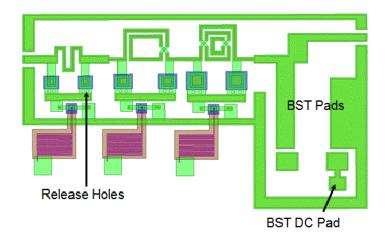

| Figure 5.19 Layout of the IPD-MEMS phase shifter loaded with a BST varactor.                    | . 115 |

| Figure 5.20 Photo of the proposed IPD-MEMS true-time-delay network loaded with a BST            |       |

| varactor. *chip size: 2.9 mm × 1.6 mm, with the back side picture of the BST varactor           | r     |

| in WLCSP package.                                                                               | . 115 |

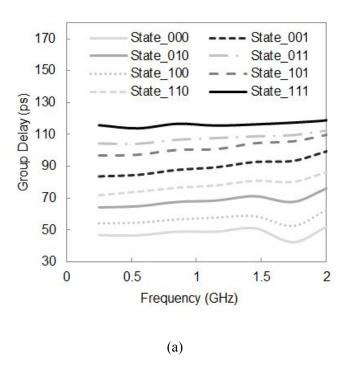

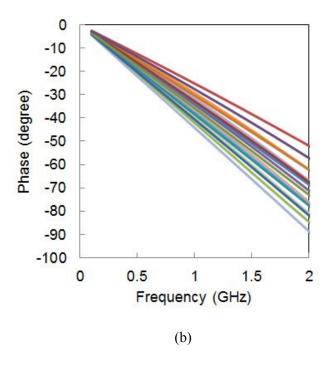

| Figure 5.21Measured performance for 16 states* (a) return loss and insertion loss.              |       |

| (b) True-time group delay. *Only 0.5 pF (lower boundary) and 0.9 pF (upper                      |       |

| boundary) are plotted at each single state using the same color and pattern of the line.        | 116   |

| Figure 5.22 3-bit IPD-MEMS digital capacitor bank. (a) Schematic diagram and (b) layout         |       |

| *chip size: 1.3 mm × 1.3 mm (including DC bias pads)                                            | . 118 |

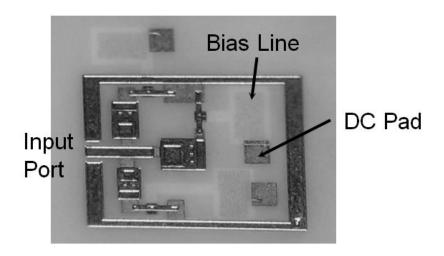

| Figure 5.23 Photo of the proposed IPD-MEMS digital capacitor bank.                              | . 119 |

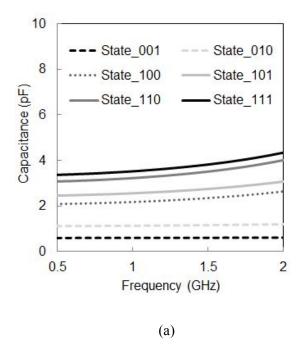

| Figure 5.24 Capacitance change for the IPD-MEMS capacitor bank. (a) Simulated capacitance.      |       |

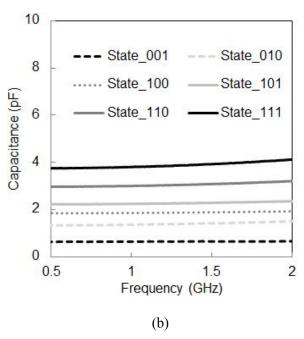

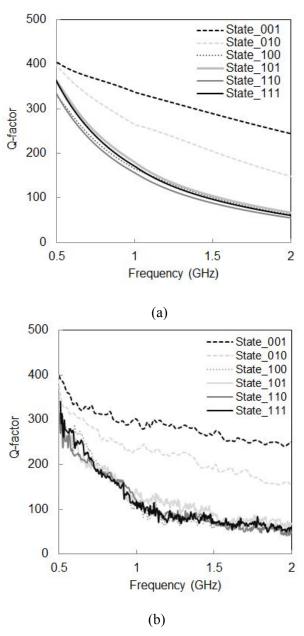

| (b) Measured capacitance                                                                        | . 120 |

| Figure 5.25 Simulated and measured quality factor for the IPD-MEMS capacitor bank.              | . 121 |

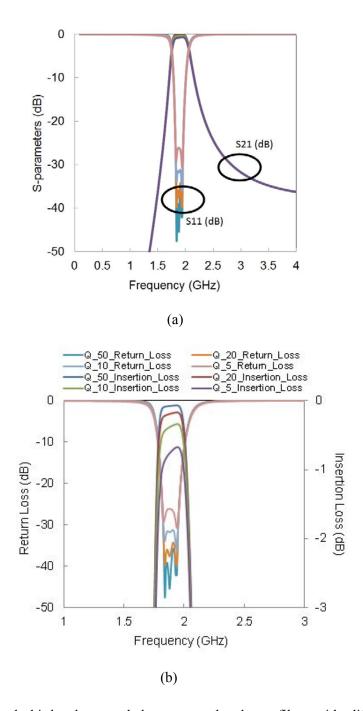

| Figure 5.26 Schematic diagram of the third-order coupled resonator bandpass filter with values  |       |

| shown in Table 5.4.                                                                             | . 122 |

| Figure 5.27 Simulated third-order coupled resonator bandpass filter with different Q-factor     |       |

| of varactors.                                                                                   | . 123 |

## **List of Tables**

| TABLE 1.1 PERFORMANCE COMPARISONS OF DIFFERENT TECHNOLOGIES                    | . 4 |

|--------------------------------------------------------------------------------|-----|

| TABLE 2.1 COMPARISONS OF DIFFERENT TUNING METHODS FOR RF TUNABLE FILTER1       | 14  |

| TABLE 3.1 COMPARISONS OF ELECTRICAL AND MECHANICAL PROPERTIES OF DIFFERENT     |     |

| Metals 2                                                                       | 20  |

| TABLE 3.2 COMPARISONS OF DIFFERENT SUBSTRATE MATERIAL 2                        | 23  |

| TABLE 3.3 COEFFICIENTS FOR DATA-FITTED MONOMIAL EXPRESSION                     | 31  |

| TABLE 4.1 COMPARISON OF TUNABLE RF ELEMENTS6                                   | 64  |

| TABLE 4.2 Design Parameters for IPD Tunable Bandstop Filter6                   | 67  |

| TABLE 4.3 COMPARISON OF TUNABLE BANDSTOP FILTER BELOW 4 GHZ                    | 74  |

| TABLE 4.4 EQUIVALENT LUMPED ELEMENT VALUE FOR IPD WILKINSON POWER DIVIDER 7    | 76  |

| TABLE 4.5 PHYSICAL DIMENSIONS FOR PHASE INVERTER                               | 78  |

| TABLE 4.6 EQUIVALENT LUMPED ELEMENT VALUE FOR PHASE INVERTER                   | 79  |

| TABLE 4.7 Design Parameters for IPD Bandpass Filter with Two Transmission      |     |

| Zero                                                                           | 86  |

| TABLE 4.8 Design Parameters for IPD Bandpass Filter With Built-in Tunable      |     |

| Transmission Zero                                                              | 89  |

| TABLE 5.1 SWITCH CONFIGURATIONS FOR LUMPED ELEMENT PHASE SHIFTER AS SHOWN IN   |     |

| FIGURE 5.6                                                                     | 01  |

| TABLE 5.2 LUMPED ELEMENTS FOR 3-BIT TTD NETWORK                                | 02  |

| TABLE 5.3 COMPARISONS OF DIFFERENT TTD NETWORKS AT 1GHZ                        | 17  |

| TABLE 5.4 LUMPED ELEMENTS FOR THIRD-ORDER COUPLED RESONATOR BANDPASS FILTER 12 | 22  |

## **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Motivations

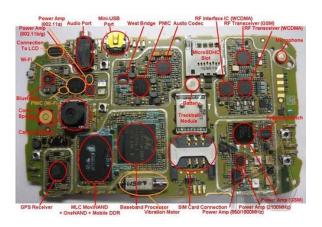

There has been a strong market-driven demand recently to increase the amount of functionality in compact wireless devices and combine it with low production cost. Multifunctional handheld devices, such as cellular phones, laptops and Internet of things (IoTs) are the main driving forces that require high performance and small-scale passive chipsets. Passive components are indispensable elements in RF communication systems. For example, in a typical cellular phone, passive components account for almost 40% of the size [1], as shown in Figure 1.1. They are used for filtering, decoupling or dividing energy, and are crucial for building L-C tanks and matching networks.

In order to fulfill the requirements of multi-wireless systems such as LTE, GSM, GPS and CDMA in small portable devices, small-form factor multi-band passive components are needed. With the help of advanced technologies, this need can be satisfied with passive surface mount devices (SMDs) or components. However, off-chip inductors, capacitors,

Figure 1.1 Circuit board of the Blackberry Bold

varactor diodes and ceramic filters still suffer performance degradation and increase overall device size.

There has been intensive research on investigating system-on-chip (SOC) passive components that would enable active RFIC devices can be built with passive devices on the same wafer. It may help reduce the cost and offer further size reductions. While it may help in reducing the cost and size, the typical quality factor (Q-factor) of an on-chip inductor for CMOS technologies is around 10 [2]-[3]. Such a low Q-factor inductor results in significantly poor performance in RF building blocks, such as low gain/power ratio of the low-noise amplifier (LNA) [4], high phase noise of the voltage-controlled oscillator (VCO) [5]-[6], and poor matching and degradation of noise figure [7].

Some techniques are proposed to boost the Q-factor of the on-chip inductors, such as using proton implantation [8] and ground shielding [9]-[10], which mainly alter the substrate impedance or diminish the substrate capacitance under the inductor so that the eddy current in the substrate can be minimized. Releasing the inductors on the back-side etching can eliminate the substrate loss and increase the Q-factor, but problems could arise during

packaging, since these inductors are relatively fragile. Also, some of the techniques cannot be easily implemented.

LTCC (low-temperature co-fired ceramic) is a popular technology for designing passive components because it provides a reasonable-cost, low-loss solution for RF applications. L and C elements can be built using aligned and laminated sheets and co-fired around 900 °C. LTCC tape thickness can be made as thin as 12.5 µm, but it is difficult to achieve an accurate thickness resolution. Although it is possible to have several layers interconnecting the L and C elements, there are several disadvantages of using LTCC technology in such applications. Since the ceramic tape film is quite thick, it results in very low density capacitors (<50 pF/mm²). Furthermore, to achieve high capacitance, these capacitors are usually very large in size which significantly increases the overall costs of the circuits. A high dielectric constant of the thick ceramic tape can be used in LTCC, but it induces a large underpass capacitance in the inductors and limits the operating frequency range of the inductors to below 4 GHz.

Over the past decade, researchers have started to develop a high-Q thin film integrated passive device (IPD) technology for realizing passive components including different transmission lines, R, L and C [11]-[12].

TABLE 1.1 Performance Comparisons of Different Technologies

|                  | Inductor                                  | Capacitor                                          | MEMS<br>Integration | Form Factor/Device<br>Precision |

|------------------|-------------------------------------------|----------------------------------------------------|---------------------|---------------------------------|

| LTCC             | Moderate Q-Factor<br>Low SRF*             | Medium Q-factor  Low Density  (<50pF/mm²)          | No                  | Medium/Moderate                 |

| Standard<br>CMOS | Poor Q-Factor                             | Low Q-Factor<br>Medium Density                     | Yes                 | Small/Good                      |

| IPD              | Moderate to High<br>Q-Factor<br>High SRF* | High Q-Factor High Density >600pF/ mm <sup>2</sup> | Yes                 | Small/Good                      |

#### \*SRF-self resonating frequency

Table 1.1 summarizes the benefits of IPD compared with LTCC and CMOS technologies in RF performance. One of the highlights of this technology is the metal layer (thick copper) which can be used to realize the high-Q values. Another highlight is that a high resistivity substrate is used so that the eddy current can be reduced and less power is dissipated in the substrate effects [13]. Also capacitor density and its Q-factor can be greatly enhanced with very thin high-dielectric constant material and thick copper, respectively.

In addition to these, the electrical performance and overall size of the circuit can be improved since it is easy to integrate several passive components to design a reconfigurable passive device, such as a differential duplexer with the L-C network. This helps reduce the extra number of passive components in the RF front-end, for instance, the balun. Furthermore, building all high-Q passive components on a single chip can, when compared to the discrete off-chip passive components, greatly reduce the unpredictable parasitic inductance of the leads and soldering. This passive loss reduction can greatly increase the battery life of a wireless device.

More importantly, the IPD thin film fabrication involves processes with sputtering, chemical vapor deposition (CVD) and e-beam evaporation, all of which are similar to the current IC technology and, the thermal budget is much lower compared with the ceramic

technology. As a result, it is advantageous to combine IPD and radio frequency microelectromechanical systems (RF MEMS) process monolithically, as well as IPD with BST technology in a hybrid fashion to obtain the goal of tunable IPD.

Research on RF MEMS began in the early 1990's. Since then, many companies and research groups have tried to employ MEMS in the RF front-end modules (FEMs) because of their excellent linearity performance, low insertion loss, low dc power consumption and high isolation [14]. Tunability in RF MEMS circuits is one of the major features in creating various tunable devices such as varactors, switching networks, phased arrays and impedance matching networks for different active and passive devices.

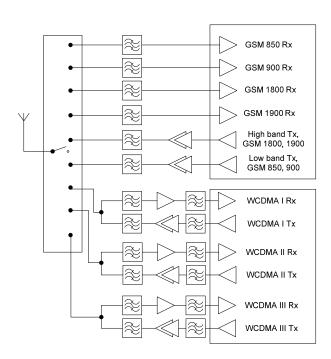

RF filter is one of the most crucial elements in microwave communication systems. These communication systems are multi-band and require a large number of filters. Figure 1.2 shows a block diagram of a multiband transceiver. A large area is occupied when individual fixed bandpass filters are employed. The problem can be circumvented by using reconfigurable/tunable devices.

Figure 1.2 A typical multi-band transceiver configuration.

## 1.2 Objectives

The motivation for this research is to develop a tunable/reconfigurable IPD platform for designing bandpass and bandstop filters, as well as other passive components, using the BST-based, MEMS integrated with the high-Q integrated passive device (IPD) platform. The MEMS integration is of particular interest since the same the IPD process, with some modifications, can be employed to realize MEMS-based tunable IPD devices. The IPD process on its own has a huge market volume, and will be in a widespread use in RF applications and, can be applied in the system in package (SiP) technologies or multi-chip modules (MCMs) integration to help develop passive devices for the next generation of communication systems.

The main objectives of this proposed project are:

- Development of a glass-based, and alumina-based integrated passive device (A/G-IPD) fabrication process, at the University of Waterloo, that can be used to fabricate high-Q RF passive lumped elements such as inductors and capacitors

- Development and demonstration of several tunable IPD devices through hybrid integration with BST technology, such as tunable impedance matching networks and tunable bandstop, and reconfigurable bandpass filters.

- Development of a monolithic IPD-MEMS process that is a compact, low-loss and reconfigurable/tunable such as high-Q switched capacitor banks and high-resolution low-loss true-time delay networks.

#### 1.3 Thesis Outline

In Chapter 1, the motivation and objectives of the overall research project are described. Chapter 2 presents a literature review of IPD devices and tunable devices using MEMS technology. Chapter 3 covers the development efforts of the new glass-based IPD process at

the University of Waterloo. Some fabrication challenges for thick metal and the corresponding solutions are addressed in detail. Measured results and modeling characterizations of high-Q passive elements such as inductors, capacitors and bandpass filters are also presented in this chapter. Chapter 3 also illustrates the design and performance of a tunable impedance network using BST varactors in an alumina-based IPD process. Chapter 4 elaborates on the reconfigurable/tunable bandstop and bandpass filter with wideband balun using the commercial IPD technology offered by ON Semiconductor for frequency agile applications. Results comparisons between the proposed process and the commercial process are presented. Chapter 5 presents a novel monolithic IPD-MEMS process, which features a low loss and high resolution true-time delay network. A high-Q IPD-MEMS digital capacitor bank is also presented. Finally, Chapter 6 provides a brief summary of the contributions of the thesis, along with possible future proposed research directions.

## CHAPTER 2

## LITERATURE REVIEW

## 2.1 Thin-film Integrated Passive Device (IPD) Platform

A thin film integrated passive device (IPD) is a general term for multiple thin-film passive elements such as resistors, capacitors and inductors that share the same substrate and packaging. Thick metal is one of the key features in this technology. Because of its small form factor and high-quality, this platform is well-suited for the future trend of the RF system-in-package (SiP) which is an excellent alternative to system-on-chip (SoC). SoC has several performance constraints in designing passive devices, so the loss of the RF systems is quite high, which is unfavorable to the future wireless systems. In contrast, SiP provides a platform to place multiple chips without performance trade-off, thus satisfying the overall requirements of the system design.

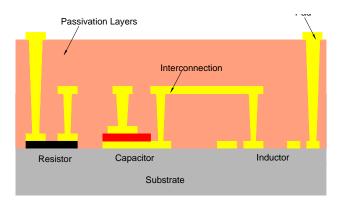

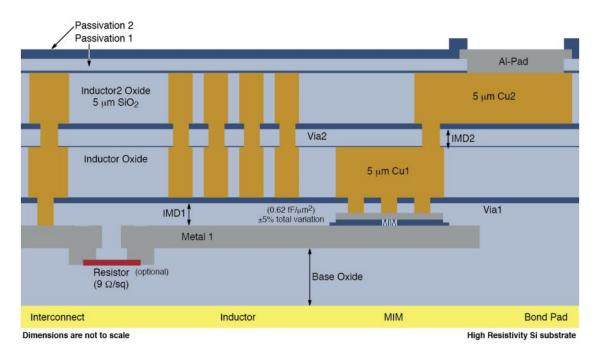

Figure 2.1 shows a typical IPD process geometry consisting of three main parts - resistor, capacitor and inductor – which are interconnected by metal via holes. A passivation layer is deposited to protect the components from air and acts as an isolation dielectric

Figure 2.1 A typical geometry of IPD process

among all the interlayer components. Pads are usually placed on top of the geometry to provide access between the IPD and the circuits outside.

#### 2.1.1 IPD RF Bandpass Filter

RF bandpass filters are one of the most crucial components in the RF-front end for a variety of wireless applications such as WiMax, WLAN and cellular phone networks. These filters can help enhance wanted signal reception, reduce harmonic effects among different active devices and improve the linearity and noise figure of the overall RF system. By using the IPD process, a low-loss and small-scale band-pass filter can be achieved. Furthermore, its flexibility is a great advantage, enabling integration of the IPD chip with other active CMOS chips by stacking.

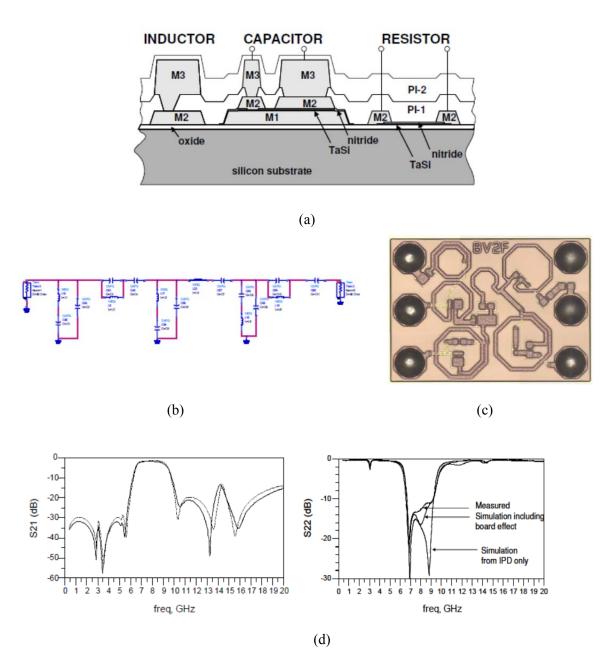

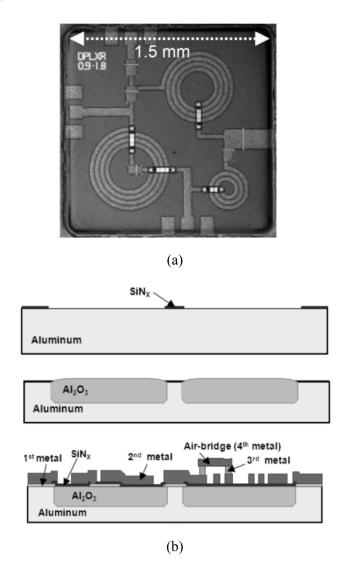

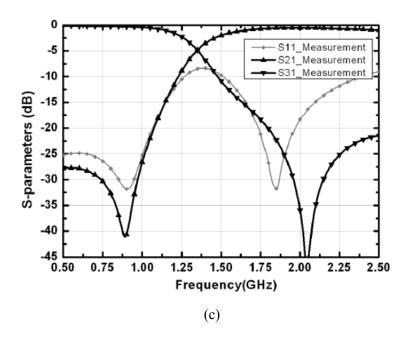

Figure 2.2 (a) shows the IPD structure by STATS ChipPAC Inc. The schematic and layout of a miniaturized ultra-wideband (UWB) bandpass filter using the silicon IPD technology is shown in Figure 2.2 (b) and (c) [15]. Three metals layers and two dielectric layers are used. The thicknesses of metal 1 (M1) to metal 3 (M3) are 1  $\mu$ m, 3  $\mu$ m and 8  $\mu$ m respectively. The capacitance density of this process is 330pF/mm<sup>2</sup> and the quality factor of the inductor is between 25 and 45, depending on the operating frequency and inductance value. As shown

in Figure 2.2(d), the passband frequency of the filter is from 7 GHz to 9 GHz, and its insertion loss is within 2.5 dB. A similar approach can also be found in [16].

Figure 2.2 Ultra-wideband (UWB) bandpass filter using silicon IPD technology by STATS ChipPAC Inc. (a) Thin-film IPD structure. (b) Schematic of the filter. (c) Layout of the UWB filter and (d) frequency response of the UWB bandpass filter [15].

### 2.1.2 IPD RF Lowpass Filter

Lowpass filters are useful for suppressing harmonics, oscillation feedback signals towards the main desired signal, and spurious responses from the active devices such as voltage-controlled oscillators (VCOs), amplifiers and mixers. The filters also help lower the possibility of receiving other frequency band signals. In [17], STMicroelectronics demonstrates the IPD lowpass filter in silicon-on-insulator (SOI) CMOS technology for GSM applications. The chip size is around 450  $\mu$ m  $\times$  700  $\mu$ m. Its layout and the frequency responses are shown in Figure 2.3 (a) and (b), respectively. It can be shown that the insertion loss is around 1.5 dB and a wideband rejection is achieved.

Figure 2.3 IPD GSM lowpass filter. (a) Layout of the lowpass filter and (b) frequency response of the lowpass filter [17].

### 2.1.3 RF Diplexer

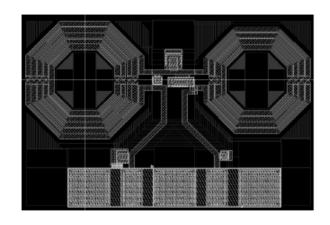

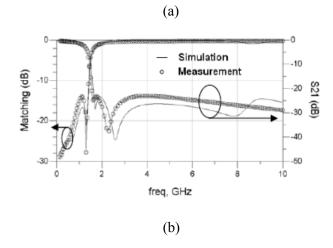

A diplexer is one of the important devices in a multi-band system. It consists of two filters coupled to a common output which has a lowpass and a highpass stage, respectively. Figure 2.4 (a) shows a 900/1800 MHz diplexer by KAIST, Korea [18]. In this design, an alumina substrate is used to replace a popular high-resistivity silicon substrate to decrease costs. Also, it brings a better thermal conductivity. The process and frequency response of the filter are shown in Figure 2.4 (b) and (c). The overall insertion loss is around 0.5 dB and the isolation is between 20-40 dB.

Figure 2.4 900/1800 MHz diplexer by KAIST. (a) Layout of the filter. (b) IPD structure from KAIST on aluminum substrate and (c) frequency response of the duplexer [18].

#### 2.2 RF MEMS Tunable Filters

Different wireless applications are allocated to different ISM frequency bands. The latest portable handheld devices even have to operate at multi-frequency bands, but many devices still have multiple single-band filters installed to function at the corresponding frequency. Tunable filters can change the cutoff frequency of the passband/stopband adaptively. It not only reduces the complexity of the systems, but also minimizes the size of the overall circuit resulting in low-cost production. Tuning methods can be generally divided into three main groups: (i) electronic, (ii) mechanical, and (iii) material. Table I shows the most popular method for the current tunable filter technology.

TABLE 2.1 COMPARISONS OF DIFFERENT TUNING METHODS FOR RF TUNABLE FILTER

| Tuning Technology | Electronic Tuning |          |                  | Mechanical Tuning |               | Material Property Tuning |        |

|-------------------|-------------------|----------|------------------|-------------------|---------------|--------------------------|--------|

|                   | PIN Diode         | Varactor | Active<br>Device | MEMS              | Piezoelectric | YIG                      | BST    |

| Tuning Speed      | ns                | ns       | ns               | μs to ns          | ms            | ms                       | ns     |

| Power Handling    | High              | Low      | Low              | High              | High          | Medium                   | Medium |

| Power Consumption | Medium            | 0        | Medium           | 0                 | Low           | Very High                | 0      |

| Q-factor          | $R_s=1\Omega$     | Low      | Low              | High              | High          | Very High                | Low    |

| Size              | Small             | Medium   | Small            | Small             | Small         | Big                      | Small  |

By comparing all the aspects in terms of tuning speed, power handling, power consumption, Q-factor and size, MEMS has the highest potential to develop a good quality tunable filter with a small size and low loss. Hence, in the following sections, various RF MEMS tunable filters are discussed.

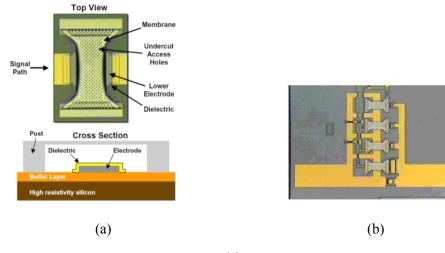

## 2.2.1 Tunable Filter with MEMS Capacitive Membrane Switch

Figure 2.5 shows one of the first tunable filters in the UHF band by Raytheon Systems Company [19]. As shown in Figure 2.5 (a) and (b), a capacitive membrane switch is used to construct the variable capacitor which is the main element for the tunable bandpass filter. The whole 5-pole filter is shown in Figure 2.5 (c). Figure 2.5(d) shows five capacitive-

Figure 2.5 Tunable bandpass filter by using capacitive membrane switch. (a) RF MEMS capacitive membrane switch. (b) 4-bit variable capacitor. (c) Tunable capacitor with inductor network (size: 3.5 mm×14 mm) and (d) 5-pole frequency response [19].

coupled L-C filter is shown in Figure 2.5 (c). Figure 2.5 (d) shows five capacitive-coupled L-C resonators are put together and the frequency response of the filter. The tunable passband is between 880-992 MHz, with an insertion loss of around 7 dB.

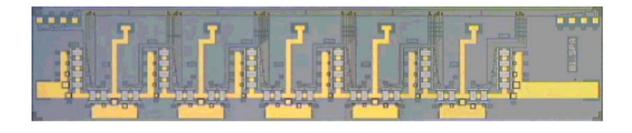

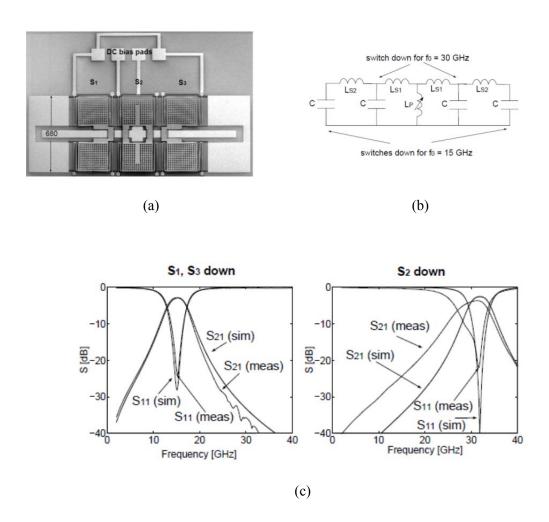

## 2.2.2 Tunable Filter with MEMS Capacitive Membrane Switch on an Inductor

Another tunable filter using some capacitive switches with capacitors is shown in Figure 2.6 [20]. It uses a short-circuit stub connected to the ground to behave as an inductor. By changing the height of the movable plate, the effective inductance is changed. The insertion loss is about 3-5 dB at 15 GHz and 30 GHz, respectively. However, the tunability of an inductor designed this way is very limited.

Figure 2.6 Bandpass filter using the tunable short-circuit inductor (a) Layout of the tunable bandpass filter. (b) Schematic of the bandpass filter and (c) the frequency response for different actuation of the switch [20].

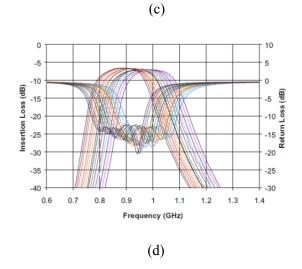

### 2.2.3 Tunable Filter with MEMS Varactor

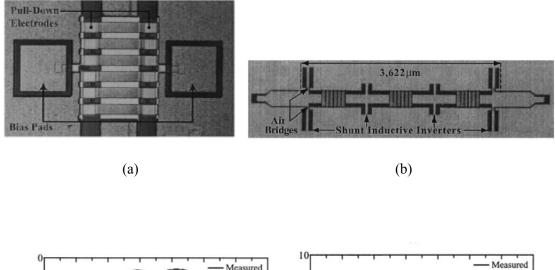

Figure 2.7 shows a tunable bandpass filter using a set of varactors to constitute a slow-wave resonator unit. Figure 2.7 (a) and (b) show the structure of the varactors and the layout of the filter. It can be seen that a miniature filter is achieved by the slow-wave structure with the shunt inductive inverters. The passband is between 18.6 GHz to 21.4 GHz, with an insertion of around 4-5 dB.

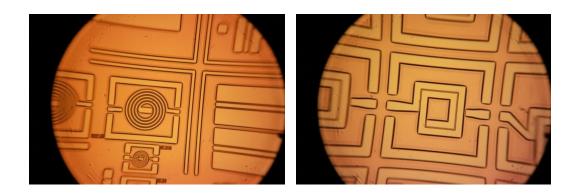

Figure 2.7 Bandpass filter using the MEMS varactor (a) Layout of MEMS varactors. (b) Layout of the bandpass filter and (c) the frequency response for different actuations of the switch [21].

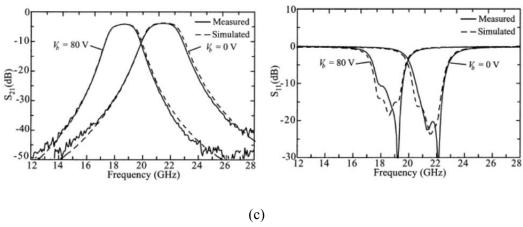

In most of the literature publications, MEMS is mainly used for microwave or millimeter wave frequencies. In fact, most of the RF MEMS filters use transmission lines as the inductor part. Hence, when it comes to lower frequency applications (e.g. 1 GHz), the circuit size is always bulky due to the longer inductive line. Alternatively, off-chip inductors may replace the transmission lines, however, it is difficult to make them small and apply them to a microscale chip. All in all, there is notable potential in integrating the IPD platform and RF MEMS technologies since it is a trade-off among all the current technologies.

Figure 2.8 A two-pole, 850-1750 MHz tunable filter built using the off-chip air coil inductor.

## CHAPTER 3

## DEVELOPMENT OF THE INTEGRATED PASSIVE DEVICE (IPD) FABRICATION PROCESS AND ITS COMPONENTS

#### 3.1 Introduction

High performance passive devices are always needed in the RF front-end and wireless systems. Particularly in demand are high quality (high-Q) factor-passive elements, inductors (L) and capacitors (C), which are the building blocks of most of the compact passive devices. On the other hand, owing to the stringent requirements of the modern communication systems, some high-Q fixed and tunable passive components are preferable in the RF-front ends. As discussed earlier, the loss of the on-chip filter can be very high, mainly because the Q-factor of the on-chip lumped inductor on the CMOS silicon substrate is very low (i.e., around 10) which leads to a poor quality factor of the L-C resonator. As a result, the in-band insertion loss is high, which may increase the noise figure in the overall RF system performance.

In this chapter, the proposed glass-based IPD fabrication process built at the University of Waterloo is first presented. Details of the modeling and characterization of the high-Q lumped elements, L and C, are also investigated. To highlight our low-loss IPD process, a modified three-pole Chebyshev bandpass filter at 1.5 GHz is designed, fabricated and tested, and its RF performance is also compared with a similar design fabricated in a commercial IPD process offered by ON Semiconductor. In addition, a repeated measurement of our 3-year-old wafer is obtained, which verifies the reliability of our proposed IPD process. Finally, an impedance tuner using barium strontium titanate (BST) varactors on our proposed alumina-based IPD process is presented.

## 3.2 Integrated Passive Device (IPD) Fabrication Considerations

#### Metal Layer

To achieve the high-Q passive elements, the choice of metal is of great importance. Table 3.1 shows a general comparison of different metals. Based on cost, compatibility of current and available foundry technology, and the fabrication complexity, copper is chosen, even though silver has a slightly higher conductivity.

TABLE 3.1 COMPARISONS OF ELECTRICAL AND MECHANICAL PROPERTIES OF DIFFERENT METALS

| Metal    | Conductivity (MS/m) | Young's<br>Modulus(GPa) | Thermal Conductivity Wm <sup>-1</sup> K <sup>-1</sup> | Cost      |

|----------|---------------------|-------------------------|-------------------------------------------------------|-----------|

| Copper   | 58                  | 110                     | 401                                                   | Low       |

| Silver   | 62                  | 83                      | 429                                                   | High      |

| Aluminum | 35                  | 69                      | 237                                                   | Low       |

| Gold     | 45.2                | 83                      | 318                                                   | Very High |

#### Thick Photoresist

For planar inductors, the smaller the size (i.e., shorter current path), the less the loss. In other words, the Q-factor is higher at low inductance. In order to boost the Q-factor without increasing the size, a smaller gap is sometimes desirable. However, this comes with the difficulty of high aspect ratio thin-film fabrication, so a good choice of photoresist would be the key to enhancing the Q-factor of the inductor.

In the open literature, SU-8 is popular for micro-molding in MEMS applications, since it is able to achieve high-aspect ratio structure (>20:1) [22]. However, SU-8 has poor adhesion with copper or gold seed layer as well as stress problems in the dense winding inductors, which leads to delamination during development. Moreover, SU-8 is very difficult to be removed after the copper electroplating. A wet etch in N-methyl-2-pyrrolidone (NMP) and oxygen plasma may be needed to remove all the SU-8 residues [23]. Because of the good copper compatibility, AZ-P4000 (AZ-4562) and AZ-9260 are the better choices for making micro-moldings as they both have very similar process steps and characteristics. Owing to the higher aspect ratio, AZ-9260 is chosen for the thick photoresist mold. Its characterization picture is shown in Figure 3.1.

Figure 3.1 Characterization of the 10 μm thick positive photoresist AZ-9260.

#### **Difficulties in using thick photoresist**

In thin-film fabrication, it is assumed that the resist film is homogeneously exposed, and therefore, the time for development and exposure are easily controlled and optimized. However, there are many fabrication challenges with the use of thick photoresist. First, underexposure is a common problem. With thick photoresist, UV energy going to the base of the resist can be slightly different between the top and the bottom, which may affect the linearity of the development rate and exposure time. Another difficulty of applying thick photoresist is edge bead, which induces an undesired gap during exposure. It is common to have this when spin-coating thick photo resists, since they have lower viscosity which increases the tension across the surface. A procedure of edge-bead removal has to be applied in order to achieve an accurate distance between the mask and the sample.

Another challenge is to characterize the rehydration time for the AZ 9260 series thick photoresist. To obtain a reliable development time, a rehydration period of around 30 minutes @ 50%/22 °C for 10 µm photoresist after soft bake is required. The reason for this is that water is one of requirements to help the photoreaction from transforming DiazoNaphtoQuinone- (DNQ-) sulfonate into indene carboxylic acid. This rehydration step helps some water from the air to diffuse into the resist film. However, if the air humidity is too low, even a long rehydration will not provide sufficient water content [24]-[25].

#### Substrate

Table 3.2 shows the electrical characteristics for different substrates. A glass is chosen because its low cost and very high resistivity, which help reduce the eddy current and the loss in the substrate. This will be discussed further in the inductor design section.

TABLE 3.2 COMPARISONS OF DIFFERENT SUBSTRATE MATERIAL

|         |                                             | Cost                              |                     |        |

|---------|---------------------------------------------|-----------------------------------|---------------------|--------|

|         | Relative Dielectric Constant $(\epsilon r)$ | Loss Tangent (×10 <sup>-3</sup> ) | Resistivity (Ω-cm)  |        |

| Quartz  | 3.8                                         | 0.02                              | >10 <sup>15</sup>   | Medium |

| Glass   | 4-5                                         | 1-5                               | >10 <sup>13</sup>   | Low    |

| Si      | 11.9                                        | 50                                | 10-100              | Low    |

| HR-Si   | 12                                          | 1-10                              | 1000-5000           | Medium |

| HR-GaAs | 12.9                                        | 0.6                               | $10^{7}$ - $10^{9}$ | High   |

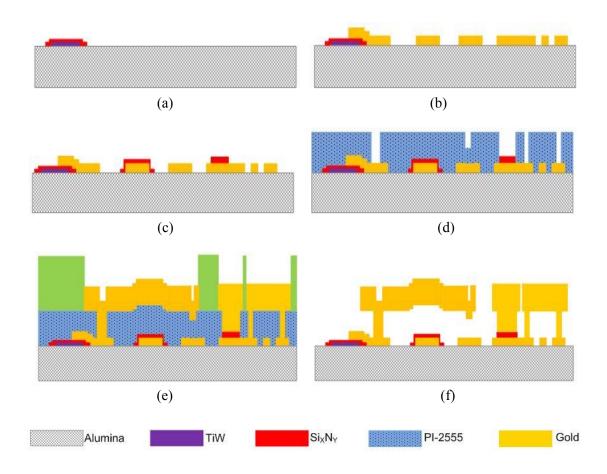

## 3.3 Integrated Passive Devices Process

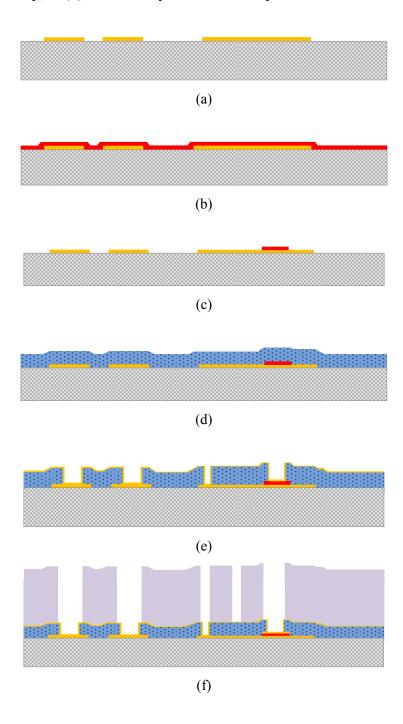

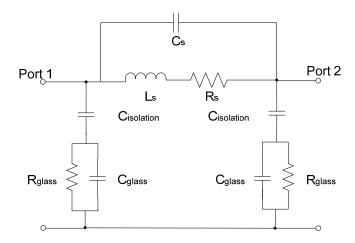

Our proposed 4-mask IPD process developed in the University of Waterloo has two metal layers (1st: Gold and 2nd Copper), as shown in Figure 3.2. In (a), a layer of chromium/gold (Cr/Au: 30 nm/50 nm) is deposited on the boro-aluminosilicate glass substrate as a seed layer, and a gold layer of 1.5 µm is electroplated, which serves as the first metal layer. Then, a 20 nm of chromium (Cr) is deposited on top of the gold and a lift-off process is followed by wet etching of gold and chromium. In (b), a 20 nm of TiW is deposited to serve as a seed layer for nitride, and thereafter, a 0.5 µm of silicon nitride (Si<sub>x</sub>N<sub>y</sub>) is deposited by PECVD. In (c), photoresist is used to help pattern the (Si<sub>x</sub>N<sub>y</sub>) which serves as a dielectric layer for the capacitor with RIE. In (d), after that, a polyimide layer- PI-2611 (4 µm) is spun and patterned using (RIE) to make some via holes. Aluminum is used as a hard mask for patterning the polyimide, and it is etched in the PAN etchant afterwards. In (e), after etching the polyimide, a thin layer Ti (e-beam: 20 nm)/Au (sputtering: 100 nm)/Ti (e-beam: 20 nm) is deposited as a seed layer and the adhesion layer for the thick copper. After that, in (f), a layer of thick

photoresist is spun and patterned, and, in (g), an 8  $\mu$ m thick copper layer (2nd metal layer) is electroplated. Finally, in (h), the seed layer is removed by RIE.

Figure 3.2 Proposed 4-mask IPD fabrication process flow.

In order to characterize the electrical parameters such as loss tangent and dielectric constant for all layers (including the actual dielectric constant of the  $Si_xN_y$ , glass substrate, and polyimide), devices for instance RF filters, inductors, capacitors and CPW transmission lines are designed in the electromagnetic software (HFSS) and the circuit simulator (ADS). Figure 3.3 shows a fabrication picture in steps (e) and (f) in Figure 3.2. The inner square is the first metal layer covered by SiN dielectric and Cr/Au, and the entire place is covered by polyimide, which is denoted in amber color. Figure 3.4 shows the via holes by etching the polyimide using anisotropic dry etching in RIE to obtain vertical sidewalls.

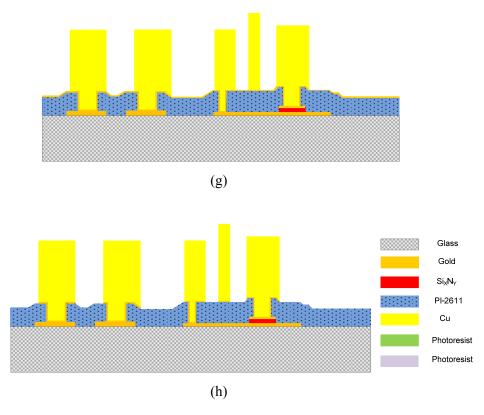

Figure 3.3 Fabrication picture in steps (e) and (f) in Figure 3.2.

Figure 3.4 Fabrication picture in step (g) in Figure 3.2 before depositing the seed layer.

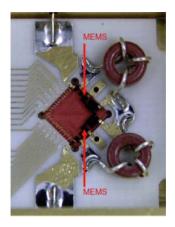

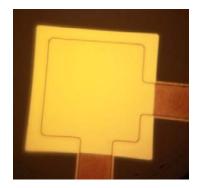

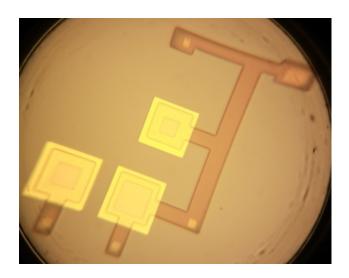

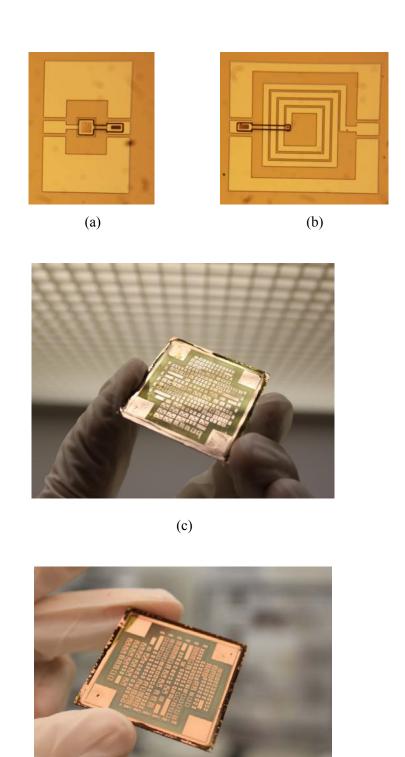

Figure 3.5 (a) - (c) shows one of the IPD capacitor, inductor designs, and, the first preliminary wafer, respectively. It should be mentioned that some of the metals are short-circuited, since the cracking of the thick photoresist in some areas, as shown in Figure 3.5 (c). As a result, the yield of the first preliminary wafer is not very satisfactory. The main reason for this is that a weak alkaline copper electroplating solution was first used to electroplate the thick copper. However, it is found out that there is a possibility that the thick photoresist is attacked by the alkaline solution and resulting in cracking of the photoresist

Figure 3.5 Final fabrication: (a) Capacitor, (b) Inductor and (c) 1st preliminary wafer and (d) completely successful IPD wafer.

(d)

structure. Optimized post-bake times and temperatures were also investigated in order to increase the durability of the photoresist in the plating bath. After several trials of recipe and solution changes, the proposed process is successfully implemented and developed at the University of Waterloo. The final wafer picture is shown in Figure 3.5 (d).

# 3.4 Modeling and Characteristics of IPD Inductor

In designing an RF inductor, there are several important considerations that affect its Q-factor and self-resonant frequency. These factors include: metal thickness, line width, gap distance between metal traces, inductor size, and number of turns. A good understanding of the inductor model is needed to achieve optimum inductance with high-Q factor. They will be discussed below:

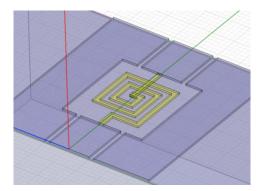

A typical geometry and physical lumped model parameters of a planar spiral inductor are shown in Figure 3.6 and 3.7, respectively.

Figure 3.6 Geometry of the thick copper inductor.

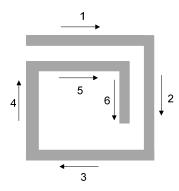

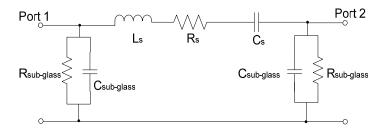

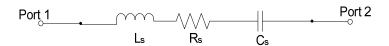

L<sub>s</sub>: Inductance of the spiral including the underpass structure

R<sub>s</sub>: Resistance of the spiral including underpass structure

C<sub>s</sub>: Series capacitance by the capacitive coupling of the overlap between the spiral and the underpass

C<sub>isolation</sub>: Capacitance from the metal to the isolation layer which is polyimide

C<sub>glass</sub>: Capacitance of the substrate

R<sub>glass</sub>: Resistance of the substrate

Figure 3.7 Physical lumped model of a spiral inductor on glass substrate [13].

### **Series Inductance**

By using the Greenhouse model [26], the equation for the inductance is:

$$L_T = L_0 + \sum M \tag{3.1}$$

where  $L_T$  is the total inductance,  $L_0$  is the sum of the self-inductances of all the straight segments, and the summation, M, is the sum of all the mutual inductances, including positive (same current direction) and negative (opposite current direction). This equation can be demonstrated with the help of Figure 3.8 and the equations below:

Figure 3.8 Current flow in the inductor.

$$L_T = L_1 + L_2 + L_3 + L_4 + L_5 + L_6 + 2(M_{15} + M_{26}) - 2(M_{13} + M_{24} + M_{35} + M_{46})$$

(3.2)

$$L_x = 2l_x \{ \ln\left[\frac{2l_x}{w+t} + 0.50049 + \left[\frac{w+t}{3l_x}\right] \right] \}$$

(3.3)

$$M = 2lk (3.4)$$

$$k = \ln \left\{ \frac{l}{GMD} + \left[1 + \left(\frac{l^2}{GMD^2}\right)\right]^2 \right\} - \left[1 + \left(\frac{GMD^2}{l^2}\right)\right]^2 + \frac{GMD}{l}$$

(3.5)

$$\ln GMD = \ln d - \left\{ \left[ \frac{1}{12(d/w)^2} \right] + \left[ \frac{1}{60(d/w)^4} \right] + \left[ \frac{1}{168(d/w)^6} \right] + \cdots \right\}$$

(3.6)

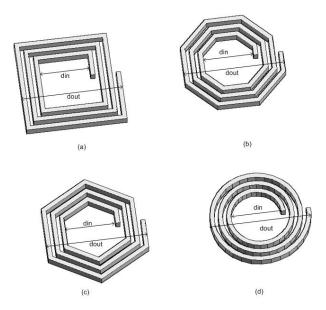

where *l* is the length (in cm) of the conductor, k is mutual-inductance-parameter, w and t are the width of the thickness (in cm) of the conductor and *GMD* is the geometric mean distance between the two conductors which is approximately equal to the distance, *d*, between the track centers. This model gives a good physical sense and relatively accurate results in calculating the inductance. However, it is not easy to design the desired inductance according to the specifications required, and, it is only applicable to the square shape. Furthermore, it cannot deal with other forms, such as in circular, hexagonal and octagonal shapes, as shown in Figure 3.9.

Figure 3.9 Different implementations of inductor (a) square, (b) octagonal, (c) hexagonal and (d) circular.

A simple model based on data fitting (least-square fit) with the experimental results is reported in [27]. This model is verified with more than 10000 inductors in the library,

$$L(nH) = \beta d_{out}^{\alpha 1} w^{\alpha 2} d_{avg}^{\alpha 3} n^{\alpha 4} s^{\alpha 5}$$

(3.7)

therefore, it has a relatively low percentage error. In this model, the inductance is given by Equation (3.7) where coefficients  $\beta$  and  $\alpha$  are layout-dependent, as given in Table 3.3.

TABLE 3.3 COEFFICIENTS FOR DATA-FITTED MONOMIAL EXPRESSION

| Layout    | β                     | $\alpha_1$ | $a_2$  | $\alpha_3$ | $\alpha_4$ | $a_5$  |

|-----------|-----------------------|------------|--------|------------|------------|--------|

| Square    | 1.62×10 <sup>-3</sup> | -1.21      | -0.147 | 2.4        | 1.78       | -0.03  |

| Hexagonal | 1.28×10 <sup>-3</sup> | -1.24      | -0.174 | 2.47       | 1.77       | -0.049 |

| Octagonal | 1.33×10 <sup>-3</sup> | -1.21      | -0.163 | 2.43       | 1.75       | -0.049 |

Using the simulation software of HFSS and MATLAB, some values are verified and the model is found to have a maximum error percentage of less than 10% for inductances is between 1 nH-8 nH.

#### **Series Resistance**

For a transmission line, at DC, the current density is uniform. However, when the frequency becomes higher, the induced eddy current makes the current density non-uniform. This eddy current effect produces its own magnetic field to oppose the original field. As a result, it reduces the net current flow in the conductor and hence increases the ac resistance. The severity of the eddy current effect is determined by the ratio of skin depth to the conductor thickness. The equation for depth of penetration (also known as skin depth) in a good conductor is  $\delta = 1/\sqrt{\pi f \mu \sigma}$  where f is the operating frequency,  $\mu$  is the permeability and  $\sigma$  is the conductivity of the metal conductor [13]. Assume the current density attenuates as a function of distance x away from the bottom surface of a transmission line (i.e. microstrip line) on the substrate [28], which can be represented by the equation below:

$$J = J_0 \cdot e^{-x/\delta} \tag{3.8}$$

$$I = \int J \cdot dA = \int_{0}^{t} J_{0} \cdot e^{-x/\delta} \cdot w \cdot dx$$

(3.9)

$$=J_0 \cdot w \cdot \delta \cdot (1 - e^{-t/\delta}) \tag{3.10}$$

where t is the thickness of the conductor.

The last term in the equation can be defined as an effective thickness:

$$t_{eff} = \delta \cdot (1 - e^{-t/\delta}) \tag{3.11}$$

$$R_s = \frac{\rho \cdot l}{w \cdot t_{eff}} \tag{3.12}$$

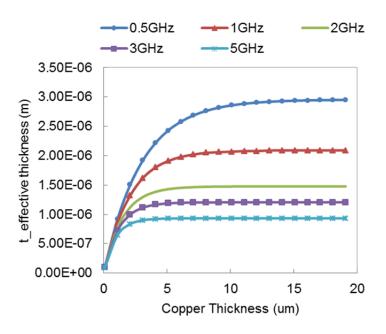

where l is the total length of line segments and  $\rho$  is the resistivity. It can be shown that as  $\delta$  decreases with high frequency,  $R_s$  also increases. Figure 3.10 shows that as the copper thickness increases, the effective thickness increases accordingly, since it lowers the series resistance of the inductor and results in a higher quality factor of inductor. However, as the thickness increases, the RF resistance does not decrease monotonically with the thickness. As the thickness grows, the reduction in RF resistance is negligible. The RF resistance is low enough for copper thickness between 5-10 um in the frequency from 0.5 GHz or above.

Another curve-fitted numerical approach that takes the ground plane into consideration also combines the  $R_{dc}$  and  $R_{hf}$ , which gives a general solution of the  $R_{ac}$  [28]-[29] in terms of film thickness (t),

$$R_{ac} = R_s = \sqrt{[(R_{dc})^2 + (kR_{hf})^2]}$$

(3.13)

$$R_{ac} = R_s = \sqrt{\left[\left(\frac{1}{\sigma wt}\right)^2 + \left(k\frac{l}{2\sigma\delta(w+t)}\right)^2\right]}$$

(3.14)

where  $R_{hf}$  is the ac resistance of the strip conductor at high frequency with equal circumference carrying a uniform current across its skin depth, and k is a correction factor.

Figure 3.10 Effective metal thickness for different frequencies.

## **Series Capacitance**

The series capacitance is the feed-through capacitive coupling between the input and output port of the inductor without passing through the spiral inductor. It is attributed to the crosstalk between the adjacent turns, and the overlap between the spiral and the underpass. Nonetheless, the potential of the adjacent turns is almost the same and is always neglected. On the other hand, because of the larger potential difference, the overlap capacitance between the spiral and the underpass is more significant. It is sufficient to model this series capacitance, C<sub>s</sub>, as the sum of the overall capacitance [13], [30],

$$C_s = n \cdot w^2 \cdot \frac{\varepsilon_{\text{iso}}}{t_{\text{isoM1-M2}}},$$

(3.15)

where n is the number of overlap, w is the width of the spiral line and  $t_{isoM1M2}$  is the isolation layer (polyimide) thickness between the spiral coil and the underpass.

#### Q-factor of an Inductor

In an ideal inductor, the energy is only stored in the magnetic field, and therefore the extra capacitance can be regarded as parasitic elements. Hence, the overall Q of an inductor can be simplified to [31]:

$$Q = 2\pi \left| \frac{\text{energy stored}}{\text{energy loss per one oscillatio n cycle}} \right|$$

(3.16)

$$Q = \frac{\omega L_s}{R_s} \times \frac{R_p}{R_p + \left[\left(\frac{\omega L_s}{R_s}\right)^2 + 1\right] R_s} \times \left[1 - \frac{R_s^2 (C_s + C_p)}{L_s} - \omega^2 L_s (C_s + C_p)\right]$$

Substrate Loss Factor

Self-resonance Factor

where

$$R_{p} = \frac{1}{\omega^{2} C_{iso}^{2} R_{glass}} + \frac{R_{glass} (C_{iso} + C_{glass})^{2}}{C_{iso}^{2}}$$

(3.18)

$$C_{p} = C_{iso} \cdot \frac{1 + \omega^{2} (C_{iso} + C_{glass}) C_{glass} R_{glass}^{2}}{1 + \omega^{2} (C_{iso} + C_{glass})^{2} R_{glass}^{2}}$$

(3.19)

and

$$C_{iso} = \frac{1}{2} \cdot l \cdot w \cdot \frac{\varepsilon_{iso}}{t_{iso}}, C_{glass} = \frac{1}{2} \cdot l \cdot w \cdot C_{sub} \text{ and } R_{glass} = \frac{2}{l \cdot w \cdot G_{sub}}$$

$R_{glass}$  and  $C_{glass}$  are the parasitic resistance and capacitance, respectively. Equation (3.17) shows that the Q-factor consists of three parts which are the intrinsic Q of the inductor, the substrate loss and the self-resonance factor. It can be observed that  $R_p$  is equal to zero if  $R_{glass}$  is infinity. Normally,  $R_{glass}$  is quite large compared with the silicon substrate, hence, it does not affect the overall Q-factor very much [9], [26] and [32].

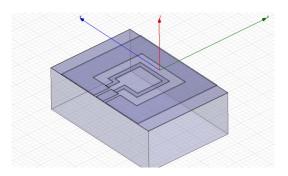

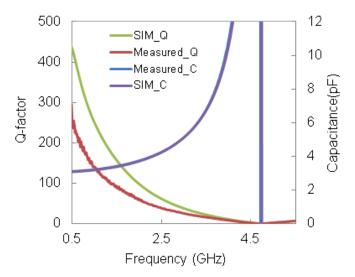

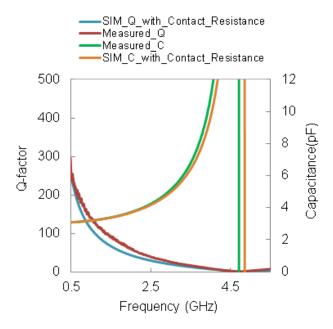

### 3.5 Inductor Design Considerations

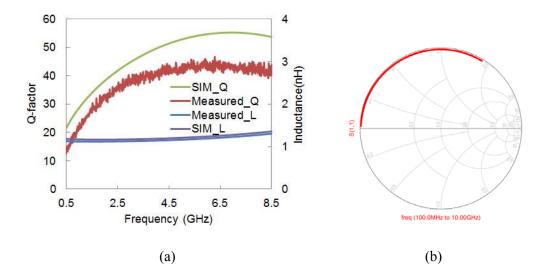

In order to optimize the IPD fabrication process for a high-Q inductor, some parameters have to be considered. Initially, the following parameters were initially selected: a copper (M2) thickness of 8  $\mu$ m, an M1 of 1  $\mu$ m, and an isolation layer of 4  $\mu$ m. The results using those parameters give some insights on the experimental and simulated results obtained from the electromagnetic (EM) simulation software such as Sonnet and HFSS. Figure 3.11 shows a physical example for one-turn thick copper inductor whereas Figure 3.12 shows its simulated and experimental performance.

The Q and L extracted from the network are defined as:

$$Q = \left| \frac{\text{Im}(1/Y_{11})}{\text{Re}(1/Y_{11})} \right|$$

$$L_s = \frac{1}{2\pi} \text{Im}(\frac{1}{Y_{11}})$$

(3.20)

Figure 3.11 One-turn inductor (w: 50 μm and din=500 μm)