# Predictable Shared Memory Resources for Multi-Core Real-Time Systems

by

### Mohamed Hassan

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2017

© Mohamed Hassan 2017

### **Examining Committee Membership**

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

External Examiner Tulika Mitra

Professor

Supervisor Hiren Patel

**Associate Professor**

Internal Member Rodolfo Pellizzoni

**Associate Professor**

Internal Member Catherine Gebotys

Professor

Internal-external Member Bernard Wong

**Associate Professor**

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Statement of Contributions**

In what follows is a list of publications which I have co-authored and used their content in this dissertation. For each publication, I present a list of my contributions.

The use of the content, from the listed publications, in this dissertation has been approved by all co-authors.

- 1. Mohamed Hassan, Hiren Patel, "Requirement- and Criticality-aware Bus Arbitration for Mixed Criticality Systems" *In IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS 2016), Vienna, Austria* [1]

- Developed the arbitration algorithm and implemented it

- Conducted the timing analysis

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

- 2. Mohamed Hassan, Anirudh M. Kaushik, Hiren Patel, "A Predictable Cache Coherence for Multi-core Real-time Systems" *In IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS 2017), Pittsburgh, PA, USA* [2]

- Identified the sources of unpredictability in conventional coherence protocols

- Defined the invariants that maintains predictable behaviors

- Developed the predictable coherence protocol (PMSI)

- Formulated the optimization problem

- Conducted the timing analysis

- Involved in designing the experiments

- Involved in analyzing the experimental results

- Wrote a significant portion of the article

- 3. Mohamed Hassan, Hiren Patel, Rodolfo Pellizzoni, "A Framework for Scheduling DRAM Memory Accesses for Multi-Core Mixed-time Critical Systems" *In IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS 2015), Seattle, USA* [3]

- Developed the mixed page policy

- Developed the optimal harmonic TDM schedule

- Formulated the optimization problem

- Conducted the timing analysis

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

- 4. Mohamed Hassan, Hiren Patel, Rodolfo Pellizzoni, "PMC: A Requirement-aware DRAM Controller for Multi-core Mixed Criticality Systems" *In ACM Transactions on Embedded Computing Systems* (TECS) [4]

- Extended PMC to support multi-rank DRAMs

- Extended PMC to support smaller transaction sizes

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

- 5. Mohamed Hassan, Anirudh M. Kaushik, Hiren Patel, "Reverse Engineering Embedded Memory Controllers through Latency-based Analysis" *In IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS 2015), Seattle, USA* [5]

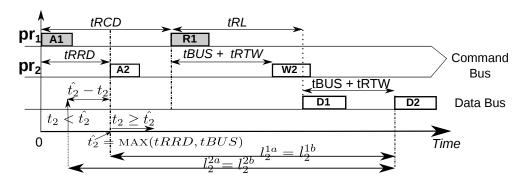

- Developed the reverse-engineering algorithms

- Defined the inference rules used in the reverse-engineering process

- Conducted the latency-based analysis

- Involved in designing the experiments

- Involved in analyzing the experimental results

- Wrote a significant portion of the article

- 6. Mohamed Hassan, Anirudh M. Kaushik, Hiren Patel, "Exposing Implementation Details of DRAM Memory Controllers through Latency-based Analysis" *In IEEE Transactions on Computers (TC) (Under Review)* [6]

- Added the reverse-engineering of the write buffer policy

- Extended the reverse-engineering of the XOR address mapping

- Identified potential applications for exposing the memory controller details

- Involved in designing the experiments for the FPGA

- Involved in analyzing the experimental results from the FPGA

- Wrote a significant portion of the article

- 7. Mohamed Hassan, Hiren Patel, "MCXplore: An Automated Framework for Validating Memory Controller Designs" *In IEEE Design, Automation and Test Conference in Europe (DATE 2016), Dresden, Germany* [7]

- Defined the formal models of the input stimulus of the memory system

- Implemented these models in a modeler checker tool and used them as a test generation engine

- Developed a methodology to use DRAM utilization to validate the memory controller behavior

- Implemented the MCXplore framework as an open-source tool

- Developed the regression test suites that stress the DRAM behavior

- Showed case studies on using MCXplore to validate state-of-the-art DRAM policies

- Applied the proposed methodology to discover timing violations in memory controllers

- Wrote a significant portion of the article

- 8. Mohamed Hassan, Hiren Patel, "MCXplore: Automating the Validation Process of DRAM Memory Controller Designs" *In IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)(Under Review)* [8]

- Illustrated the usage of MCXplore with other high-level statistics

- Extended the framework to validate other DRAM policies

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

#### **Abstract**

A major challenge in multi-core real-time systems is the interference problem on the shared hardware components amongst cores. Examples of these shared components include buses, on-chip caches, and off-chip dynamic random access memories (DRAMs). The problem arises because different cores in the system interfere with each other, while competing to access the shared hardware components. It is a challenging problem for real-time systems because operations of one core affect the temporal behaviour of other cores, which complicates the timing analysis of the system. We address this problem by making the following contributions. 1) For shared buses, we propose CArb, a predictable and criticality-aware arbiter, which provides guaranteed and differential service to tasks based on their requirements. In addition, we utilize CArb to mitigate overheads resulting from system switching among different modes. 2) For the cache hierarchy, we address the problem of maintaining cache coherence in multi-core real-time systems by modifying current coherence protocols such that data sharing is viable for real-time systems in a manner amenable for timing analysis. The proposed solution provides performance improvements, does not impose any scheduling restrictions, and does not require any source-code modifications. 3) At the shared DRAM level, we propose PMC, a programmable memory controller that provides latency guarantees for running tasks upon accessing the off-chip DRAM, while assigning differential memory services to tasks based on their bandwidth and latency requirements. In addition to PMC, we conduct a latency-based analysis on DRAM memory controllers (MCs). Our analysis provides both best-case and worst-case bounds on the latency that any request suffers upon accessing the DRAM. The analysis comprehensively covers all possible interactions of successive requests considering all possible DRAM states. Finally, we formally model request interrelations and DRAM command interactions. We use these models to develop an automated validation framework along with benchmark suites to validate and evaluate PMC and any other MC, which we release as an open-source tool.

#### Acknowledgements

First and foremost, all the praise and thankfulness to Allah for empowering me to complete this thesis. Without his help, I would not have the ability to pass the finish line of this stage in my life.

I would like to seize this opportunity to thank Professor Hiren Patel (my supervisor), and Professor Rodolfo Pellizzoni for their valuable help and guidance. I would also like to thank my committee members: Professor Tulika Mitra, Professor Catherine Gebotys, Professor Rodolfo Pellizzoni, and Professor Bernard Wong for taking the time and effort to participate in my examination committee and provide me with valuable feedback.

I would like to thank my friends in the Computer Architecture and Embedded Systems Research (CAESR) group at the University of Waterloo for all the great collaborations, discussions, and projects: Anirudh M. Kaushik, Nivedita Sritharan, Yunling Cui, Zhuoran Yin, and Danlu Guo.

I cannot find the words to thank my parents for their continuous and endless support throughout my whole life. I thank them for believing in me and for helping me be who I am today. Thanks to my brother, Alaa, my sister, Shimaa, and my dear friend, Youssef Elkady for the unconditional love and support.

I would like to express my deep gratitude to my wife, Hebatullah. Thanks for her patience, support, love, sacrifices, and consideration. I also thank my son, Albaraa, and my daughter, Jannah, for shining our home with their beautiful smiles.

### **Dedication**

Indeed, my prayer, my rites of sacrifice, my living and my dying are for Allah , Lord of the worlds. [Qura'n 6:162]

# **Table of Contents**

| Li | ist of '             | Tables x                                                                                 | vi  |  |  |  |

|----|----------------------|------------------------------------------------------------------------------------------|-----|--|--|--|

| Li | ist of Figures xviii |                                                                                          |     |  |  |  |

| Li | ist of               | Abbreviations                                                                            | αii |  |  |  |

| Li | ist of S             | Symbols                                                                                  | ΚV  |  |  |  |

| 1  | Intr                 | oduction                                                                                 | 1   |  |  |  |

| 2  |                      | icality- and Requirement-aware Bus Arbitration for Multi-core Mixed Critical-<br>systems | 4   |  |  |  |

|    | 2.1                  | Introduction                                                                             | 4   |  |  |  |

|    |                      | 2.1.1 Contributions                                                                      | 6   |  |  |  |

|    | 2.2                  | Related Work                                                                             | 7   |  |  |  |

|    | 2.3                  | System Model                                                                             | 8   |  |  |  |

|    | 2.4                  | Execution Time Decomposition                                                             | 10  |  |  |  |

|    |                      | 2.4.1 Illustrative Example                                                               | 10  |  |  |  |

|    | 2.5                  | Applicability of real-time arbiters in MCS                                               | 11  |  |  |  |

|    | 2.6                  | CArb: Proposed Arbitration Scheme                                                        | 13  |  |  |  |

|    |                      | 2.6.1 Inter-class Arbitration                                                            | 14  |  |  |  |

|    |                      | 2.6.2 Intra-class Arbitration                                                            | 15  |  |  |  |

|   |            | 2.6.3                                                            | Area Overhead                                                                                                                                                                                             | 17                                                   |

|---|------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|   | 2.7        | WC A                                                             | nalysis and Problem Formulation                                                                                                                                                                           | 17                                                   |

|   |            | 2.7.1                                                            | WC analysis                                                                                                                                                                                               | 18                                                   |

|   |            | 2.7.2                                                            | Optimization problem formulation                                                                                                                                                                          | 19                                                   |

|   |            | 2.7.3                                                            | $\Lambda(L)$ : The WC number of memory accesses as a function of CL $$                                                                                                                                    | 21                                                   |

|   | 2.8        | Dynam                                                            | nic Re-arbitration                                                                                                                                                                                        | 21                                                   |

|   |            | 2.8.1                                                            | Motivation                                                                                                                                                                                                | 21                                                   |

|   |            | 2.8.2                                                            | Proposed Solutions                                                                                                                                                                                        | 21                                                   |

|   |            | 2.8.3                                                            | Effect of Re-arbitration on Lower-criticality Tasks                                                                                                                                                       | 24                                                   |

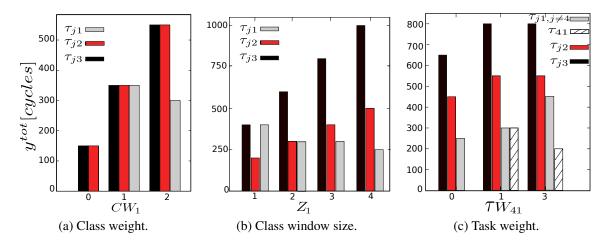

|   | 2.9        | Experi                                                           | mental Evaluation                                                                                                                                                                                         | 25                                                   |

|   |            | 2.9.1                                                            | Avionics Use-case                                                                                                                                                                                         | 26                                                   |

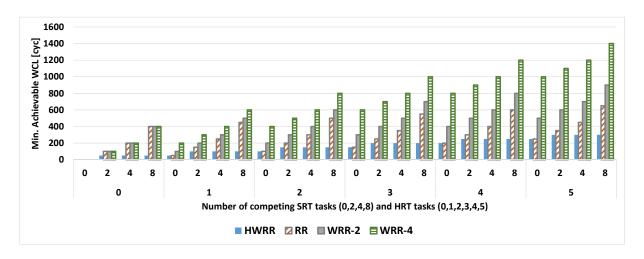

|   |            | 2.9.2                                                            | Minimum Achievable Latency                                                                                                                                                                                | 27                                                   |

|   |            | 2.9.3                                                            | Synthetic Experiments                                                                                                                                                                                     | 27                                                   |

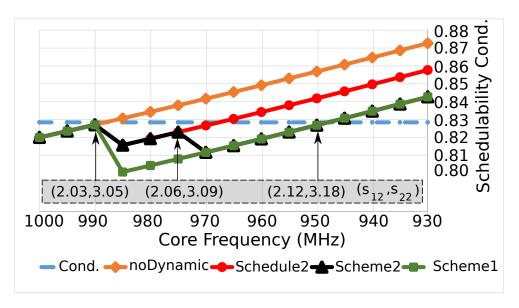

|   |            | 2.9.4                                                            | Dynamic Re-arbitration                                                                                                                                                                                    | 29                                                   |

|   | 2.10       | Summa                                                            | ary                                                                                                                                                                                                       | 32                                                   |

| 3 | PMS        | I: Pred                                                          | ictable Cache Coherence for Multi-core Real-time Systems                                                                                                                                                  | 33                                                   |

|   | 3.1        |                                                                  | iction                                                                                                                                                                                                    |                                                      |

|   |            | 3.1.1                                                            |                                                                                                                                                                                                           |                                                      |

|   |            |                                                                  | Contributions                                                                                                                                                                                             | ככ                                                   |

|   | 3.2        |                                                                  | Contributions                                                                                                                                                                                             |                                                      |

|   | 3.2<br>3.3 | Related                                                          | d Work                                                                                                                                                                                                    | 35                                                   |

|   |            | Related                                                          | d Work                                                                                                                                                                                                    | 35<br>37                                             |

|   |            | Related<br>Backgr                                                | d Work                                                                                                                                                                                                    | 35<br>37<br>39                                       |

|   | 3.3        | Related<br>Backgr<br>3.3.1<br>System                             | d Work                                                                                                                                                                                                    | 35<br>37<br>39<br>40                                 |

|   | 3.3        | Related<br>Backgr<br>3.3.1<br>System                             | d Work                                                                                                                                                                                                    | 35<br>37<br>39<br>40                                 |

|   | 3.3        | Related<br>Backgr<br>3.3.1<br>System<br>Source                   | d Work  cound: Cache Coherence  Transient Cache Coherence States  Model  s of Unpredictability Due to Coherence                                                                                           | 35<br>37<br>39<br>40<br>41                           |

|   | 3.3        | Related<br>Backgr<br>3.3.1<br>System<br>Source<br>3.5.1          | Transient Cache Coherence States                                                                                                                                                                          | 35<br>37<br>39<br>40<br>41<br>42<br>43               |

|   | 3.3        | Related<br>Backgr<br>3.3.1<br>System<br>Source<br>3.5.1<br>3.5.2 | Transient Cache Coherence States  Model  s of Unpredictability Due to Coherence  Source 1: Inter-core Coherence Interference on Same Line  Source 2: Inter-core Coherence Interference on Different Lines | 355<br>377<br>399<br>400<br>411<br>422<br>433<br>444 |

| 3.6        | PMSI:                                                 | A Predictable Coherence Protocol                                                                                              | 47                                     |

|------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|            | 3.6.1                                                 | Architectural Modifications                                                                                                   | 48                                     |

|            | 3.6.2                                                 | Coherence Protocol Modifications                                                                                              | 49                                     |

| 3.7        | Latency                                               | y Analysis                                                                                                                    | 52                                     |

| 3.8        | Evaluat                                               | tion                                                                                                                          | 56                                     |

|            | 3.8.1                                                 | Verification                                                                                                                  | 57                                     |

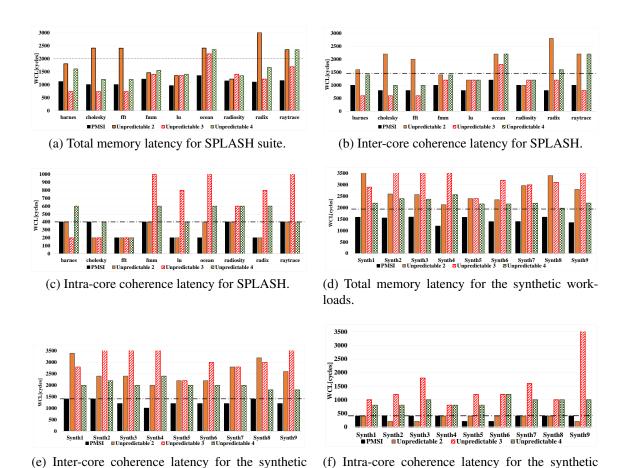

|            | 3.8.2                                                 | Exp.1: Bounding the Memory Latency                                                                                            | 57                                     |

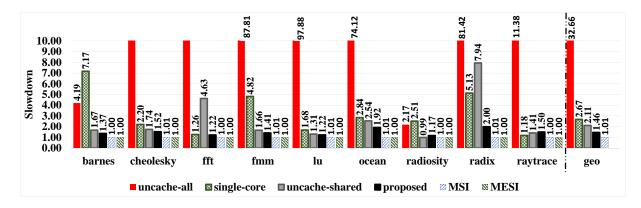

|            | 3.8.3                                                 | Exp.2: Comparing Performance with Conventional Protocols and Alternative Predictable Approaches                               | 59                                     |

|            | 3.8.4                                                 | Exp.3: Comparing to the Ideal Scenario                                                                                        | 60                                     |

|            | 3.8.5                                                 | Exp.4: Scalability                                                                                                            | 61                                     |

| 3.9        | Summa                                                 | ury                                                                                                                           | 62                                     |

| Syst       |                                                       |                                                                                                                               | 63                                     |

| 4.1        |                                                       | ction                                                                                                                         | 63                                     |

| 7.1        | 4.1.1                                                 | Contributions                                                                                                                 | 64                                     |

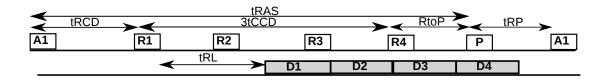

| 4.2        |                                                       | ound: Main Memory                                                                                                             | 66                                     |

| 4.2        | 4.2.1                                                 | •                                                                                                                             | 00                                     |

| 4.3        |                                                       |                                                                                                                               | 60                                     |

| 4.3        |                                                       | Memory Page Policies                                                                                                          | 68                                     |

| 1.1        |                                                       | l Work                                                                                                                        | 69                                     |

| 4.4        | Arbitra                                               | I Work                                                                                                                        | 69<br>71                               |

| 4.4<br>4.5 | Arbitra PMC:                                          | I Work          tion Mechanisms          Γhe Proposed Solution                                                                | 69<br>71<br>72                         |

|            | Arbitra<br>PMC: 7<br>4.5.1                            | The Proposed Solution                                                                                                         | 69<br>71<br>72<br>72                   |

|            | Arbitra<br>PMC: 7<br>4.5.1<br>4.5.2                   | I Work tion Mechanisms The Proposed Solution PMC Architecture Formulating Bundles                                             | 69<br>71<br>72<br>72<br>74             |

|            | Arbitra<br>PMC: 7<br>4.5.1<br>4.5.2<br>4.5.3          | I Work tion Mechanisms The Proposed Solution PMC Architecture Formulating Bundles Dynamic Bank Interleaving                   | 69<br>71<br>72<br>72<br>74<br>76       |

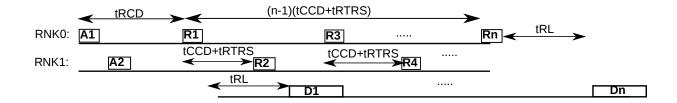

|            | Arbitra<br>PMC: 7<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4 | I Work tion Mechanisms The Proposed Solution PMC Architecture Formulating Bundles Dynamic Bank Interleaving Rank Interleaving | 69<br>71<br>72<br>72<br>74<br>76<br>77 |

|            | Arbitra<br>PMC: 7<br>4.5.1<br>4.5.2<br>4.5.3          | I Work tion Mechanisms The Proposed Solution PMC Architecture Formulating Bundles Dynamic Bank Interleaving                   | 69<br>71<br>72<br>72<br>74<br>76       |

|   |     | 4.6.1    | Proposed Implementation                                                                    | 80  |

|---|-----|----------|--------------------------------------------------------------------------------------------|-----|

|   |     | 4.6.2    | Schedule parameters                                                                        | 82  |

|   |     | 4.6.3    | Schedule Slots                                                                             | 82  |

|   | 4.7 | Timing   | g Analysis                                                                                 | 84  |

|   |     | 4.7.1    | Problem Formulation                                                                        | 86  |

|   | 4.8 | Experi   | mental Evaluation                                                                          | 88  |

|   |     | 4.8.1    | Case-study: Multimedia System                                                              | 88  |

|   |     | 4.8.2    | Synthetic Experiments                                                                      | 90  |

|   | 4.9 | Summa    | ary                                                                                        | 98  |

| 5 | Rev | erse Eng | gineering Embedded DRAM Memory Controllers through Latency-base                            | ed  |

|   | Ana | lysis    |                                                                                            | 99  |

|   | 5.1 | Introdu  | uction                                                                                     | 99  |

|   |     | 5.1.1    | Contributions                                                                              | 100 |

|   | 5.2 | Related  | d Work                                                                                     | 101 |

|   | 5.3 | Memo     | ry Latency Analysis                                                                        | 102 |

|   |     | 5.3.1    | Proof Strategy                                                                             | 103 |

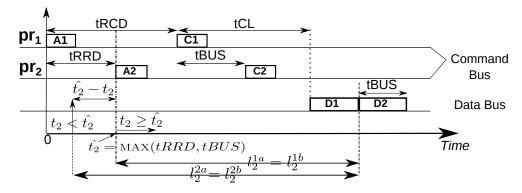

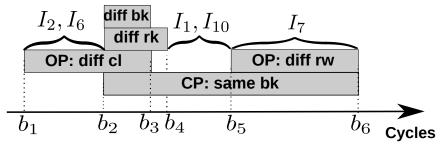

|   |     | 5.3.2    | Example 1: Two accesses with same access type to two different banks in the same rank      | 105 |

|   |     | 5.3.3    | Example 2: Two accesses with different access type to two different banks in the same rank | 106 |

|   | 5.4 | Revers   | se-Engineering Properties of the MC                                                        | 108 |

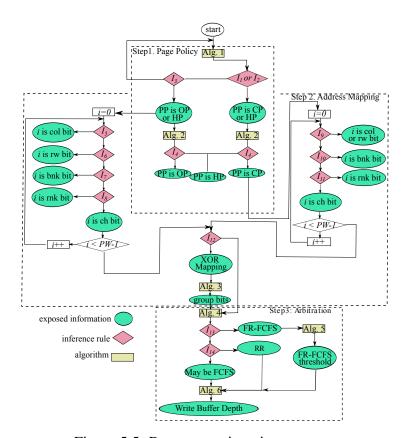

|   |     | 5.4.1    | Reverse-engineering page policy and address mapping                                        | 108 |

|   |     | 5.4.2    | Reverse-engineering the command arbitration scheme                                         | 114 |

|   |     | 5.4.3    | Advanced MC features                                                                       | 115 |

|   |     | 5.4.4    | Performance Counters                                                                       | 117 |

|   | 5.5 | Potenti  | ial Applications                                                                           | 117 |

|   | 5.6 | Experi   | mental Evaluation                                                                          | 119 |

|   |     | 5.6.1    | Reverse-engineering MC's properties of the XUPV5-LX110T platform .                         | 119 |

|   |     | 5.6.2    | Evaluation on simulation framework                                                         | 122 |

|   | 5.7 | Summ     | ory.                                                                                       | 127 |

| 6 | MCXplore: signs |         | CXplore: Automating the Validation Process of DRAM Memory Controller De-<br>gns |       |  |

|---|-----------------|---------|---------------------------------------------------------------------------------|-------|--|

|   | 6.1             | Introdu | action                                                                          | . 128 |  |

|   |                 | 6.1.1   | Contributions                                                                   | . 129 |  |

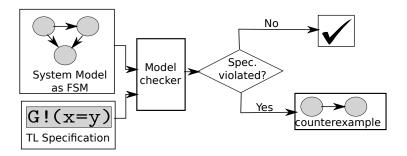

|   | 6.2             | Backgr  | round: Model Checking                                                           | . 130 |  |

|   | 6.3             | Related | d Work                                                                          | . 131 |  |

|   |                 | 6.3.1   | Formal Verification of the Memory System                                        | . 132 |  |

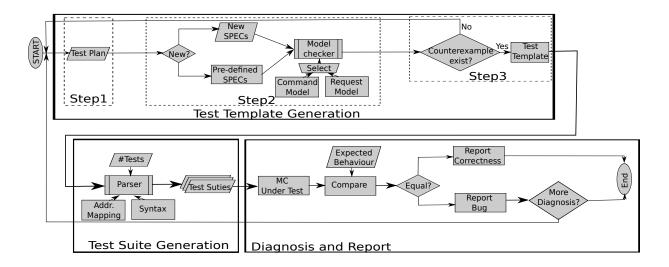

|   | 6.4             | MCXp    | lore Methodology                                                                | . 134 |  |

|   |                 | 6.4.1   | Proposed Models                                                                 | . 135 |  |

|   | 6.5             | Validat | ting MC's Frontend                                                              | . 138 |  |

|   |                 | 6.5.1   | Address Mapping Policies                                                        | . 139 |  |

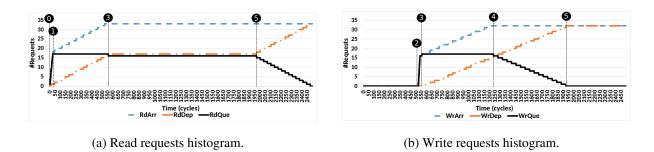

|   |                 | 6.5.2   | Page Management Policies                                                        | . 147 |  |

|   |                 | 6.5.3   | Arbitration Schemes                                                             | . 149 |  |

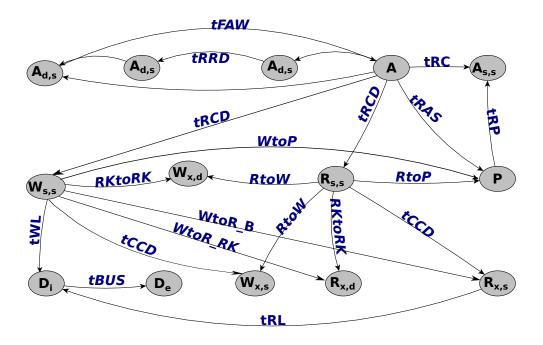

|   | 6.6             | Validat | ting MC's backend                                                               | . 151 |  |

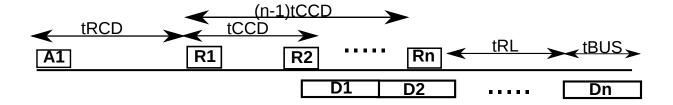

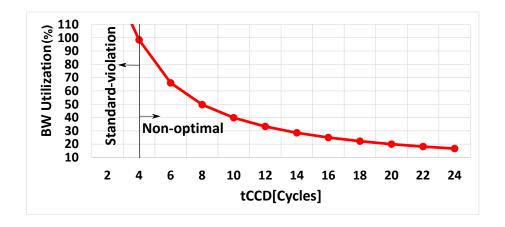

|   |                 | 6.6.1   | tCCD                                                                            | . 152 |  |

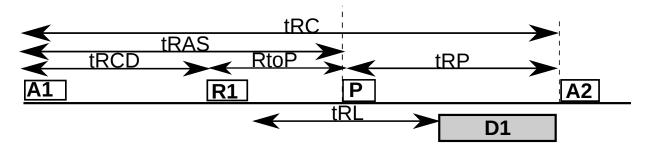

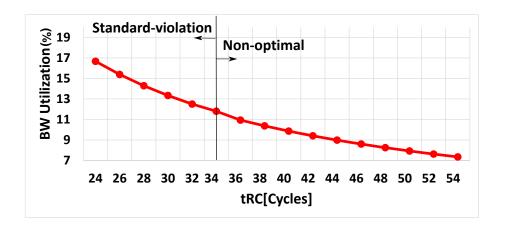

|   |                 | 6.6.2   | tRC                                                                             | . 154 |  |

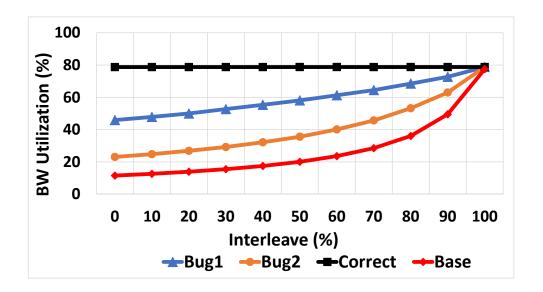

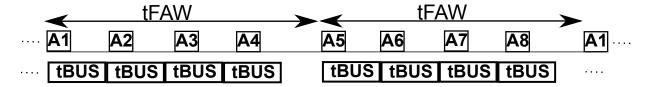

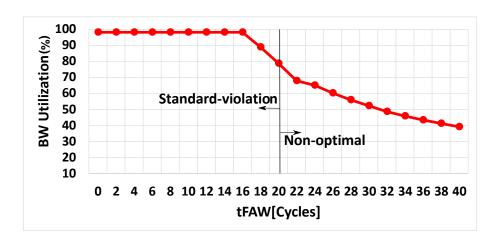

|   |                 | 6.6.3   | tFAW                                                                            | . 155 |  |

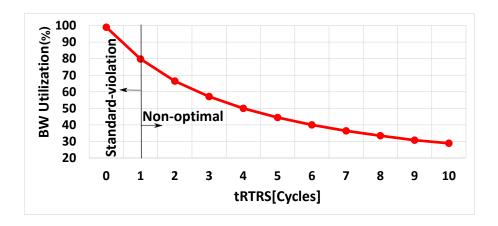

|   |                 | 6.6.4   | tRTRS                                                                           | . 156 |  |

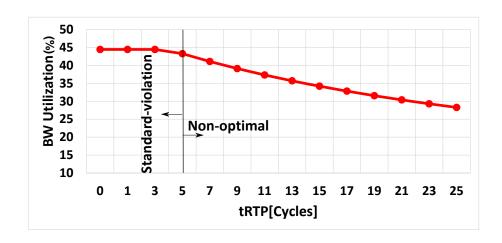

|   |                 | 6.6.5   | tRTP                                                                            | . 158 |  |

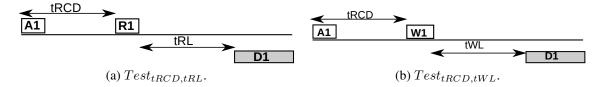

|   |                 | 6.6.6   | tRCD,tWL, and tRL                                                               | . 159 |  |

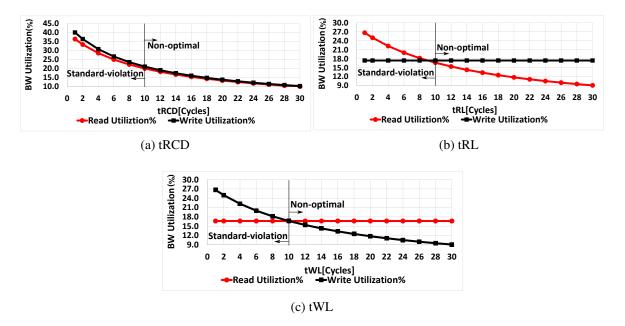

|   |                 | 6.6.7   | tRRD                                                                            | . 161 |  |

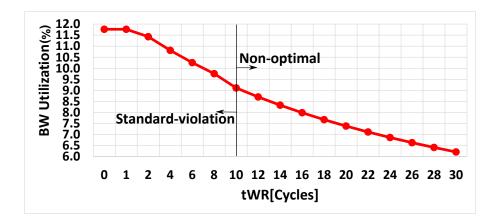

|   |                 | 6.6.8   | tWR                                                                             | . 163 |  |

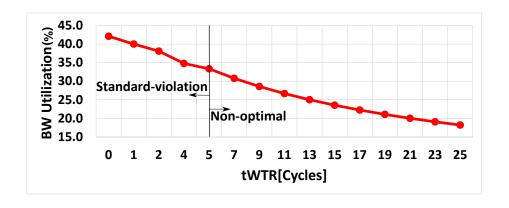

|   |                 | 6.6.9   | tWTR                                                                            | . 164 |  |

|   |                 | 6.6.10  | Summary                                                                         | . 165 |  |

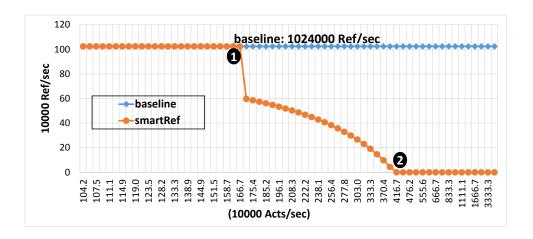

|   |                 | 6.6.11  | Smart Refresh                                                                   | . 167 |  |

|   |                 | 6.6.12  | Command Bus Contention                                                          |       |  |

|   | 6.7             |         | ibility of MCXplore                                                             |       |  |

|   | 6.8             | Summe   |                                                                                 | 170   |  |

| 7  | Bou           | nding Total Memory Latency in Multi-Core Real-Time Systems         | 171   |  |

|----|---------------|--------------------------------------------------------------------|-------|--|

|    | 7.1           | System Model                                                       | . 171 |  |

|    | 7.2           | Timing Analysis of Coherence Interference Assuming CArb's Schedule | . 172 |  |

|    | 7.3           | Aggregated Memory Latency Analysis                                 | . 174 |  |

| 8  | Con           | clusion and Future Work                                            | 176   |  |

| Re | eferences 178 |                                                                    |       |  |

# **List of Tables**

| 2.1 | Experiment using the avionics use-case from Honeywell [9]                                                                                                                                                                                                                                                                                                                              | 25 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Parameters of synthetic experiments                                                                                                                                                                                                                                                                                                                                                    | 28 |

| 2.3 | Parameters of the dynamic case experiment                                                                                                                                                                                                                                                                                                                                              | 30 |

| 3.1 | Transient states between S and I in a conventional MSI protocol. <i>issue msg/state</i> means the core issues the message <i>msg</i> and move to state <i>state</i> . <i>-/state</i> indicates that there is no <i>msg</i> issued. Shaded cells represent the situations where no transition occurs, while cells marked with X denote impossible cases under correct operation [10]    | 40 |

| 3.2 | Private memory states for PMSI. <i>issue msg/state</i> means the core issues the message <i>msg</i> and move to state <i>state</i> . A core issues a <i>load/store</i> request. Once the cache line is available, the core <i>reads/writes</i> it. A core needs to issue a <i>replacement</i> to write back a dirty block before eviction. Changes to conventional MSI are in bold red | 49 |

| 3.3 | Semantics of the proposed transient states to achieve a predictable behavior                                                                                                                                                                                                                                                                                                           | 52 |

| 4.1 | Important JEDEC timing constraints (DDR3-1333) [11]                                                                                                                                                                                                                                                                                                                                    | 68 |

| 4.2 | Different bank interleaving for a single rank DDR3-1333. Bundle widths are in cycles                                                                                                                                                                                                                                                                                                   | 77 |

| 4.3 | Terms and brief descriptions                                                                                                                                                                                                                                                                                                                                                           | 83 |

| 4.4 | Multimedia processing system requirements                                                                                                                                                                                                                                                                                                                                              | 89 |

| 5.1 | Best and worst-case latencies                                                                                                                                                                                                                                                                                                                                                          | 07 |

| 5.2 | Results of XORing different bank and row bits                                                                                                                                                                                                                                                                                                                                          | 15 |

| 5.3 | DDR2 specifications                       |

|-----|-------------------------------------------|

| 5.4 | Address mapping findings for XUPV5-LX110T |

| 5.5 | System configuration                      |

| 5.6 | MC configurations                         |

| 6.1 | Currently supported configurations        |

| 6.2 | Validating <i>tRTP</i>                    |

| 6.3 | Validating $tRCD$ , $tRL$ and $tWL$       |

| 6.4 | Tests of timing parameters                |

# **List of Figures**

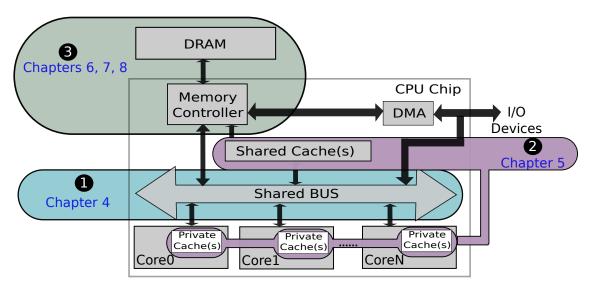

| 1.1 | Multi-core architecture                                                                                                                      | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Multi-core architecture.                                                                                                                     | 8  |

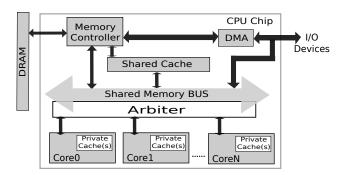

| 2.2 | Real-time arbiters                                                                                                                           | 12 |

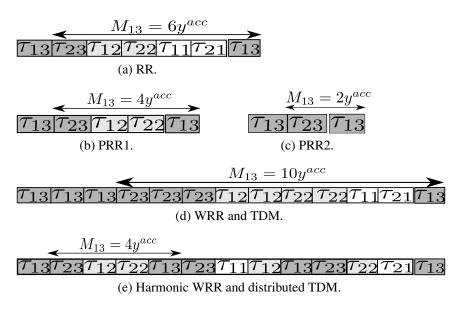

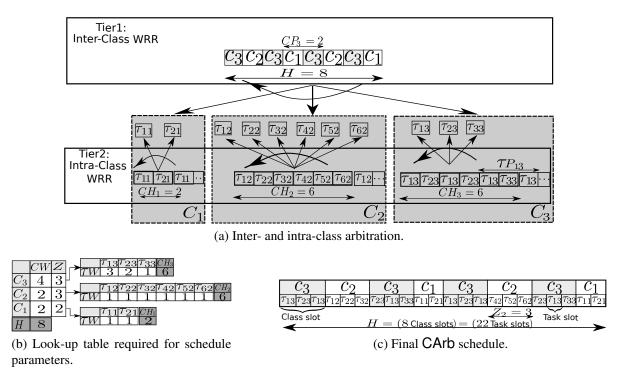

| 2.3 | Memory bus arbitration using CArb                                                                                                            | 14 |

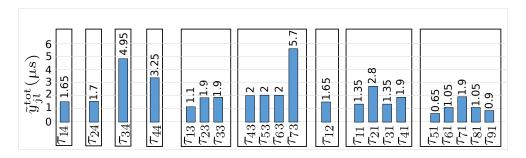

| 2.4 | Avionics use-case results                                                                                                                    | 26 |

| 2.5 | Latency requirements                                                                                                                         | 28 |

| 2.6 | Synthetic experiments (y-axis is the total WCL, $y^{tot}$ )                                                                                  | 29 |

| 2.7 | Effect of decreasing core frequency on tasks of $C_2$                                                                                        | 31 |

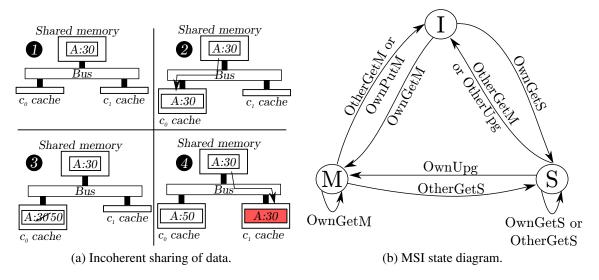

| 3.1 | Cache coherence.                                                                                                                             | 38 |

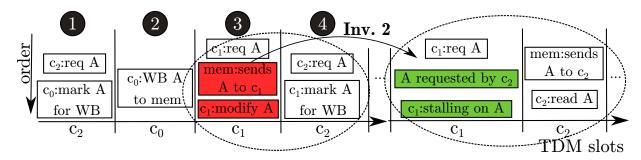

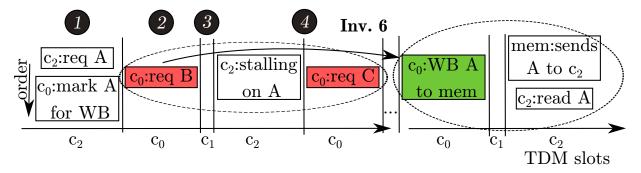

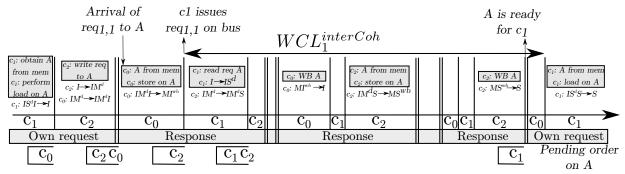

| 3.2 | Unpredictability source 1: inter-core coherence interference on same line. Initially, $c_0$ modified A. $c_2$ is under analysis              | 43 |

| 3.3 | Unpredictability source 2: inter-core coherence interference on different lines. Initially, $c_0$ modified A and B. $c_1$ is under analysis. | 44 |

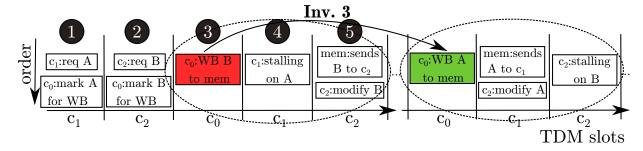

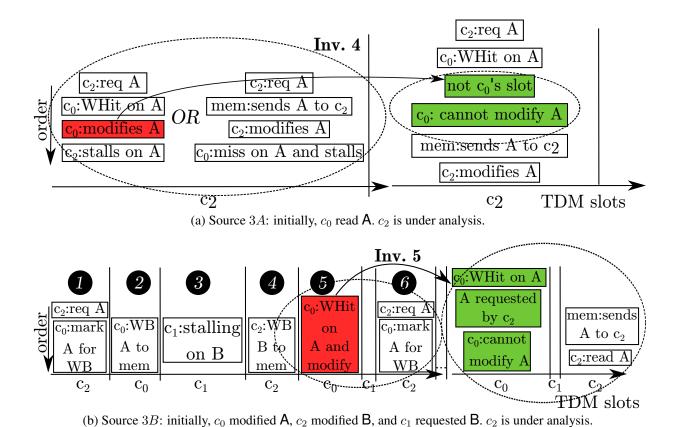

| 3.4 | Unpredictability source 3: inter-core interference due to write hits                                                                         | 45 |

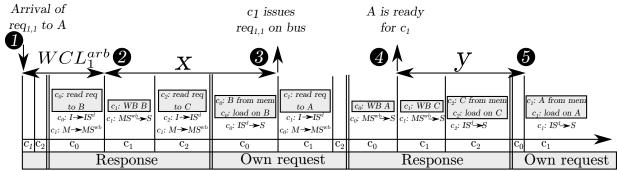

| 3.5 | Unpredictability source 4: intra-core coherence interference. Initially, $c_0$ has modified A. $c_2$ is under analysis                       | 47 |

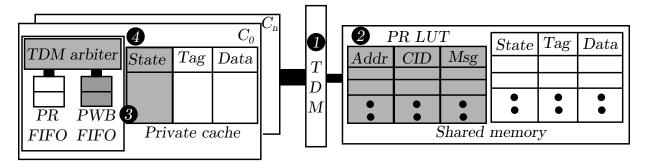

| 3.6 | Architectural changes necessary for PMSI                                                                                                     | 48 |

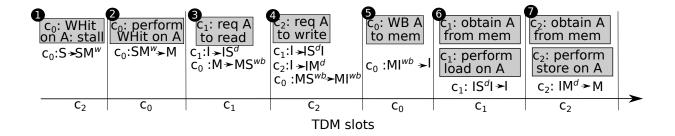

| 3.7 | Transient states example; grey boxes are events, and arrows are state transitions. Initially, $c_0$ has A in S                               | 51 |

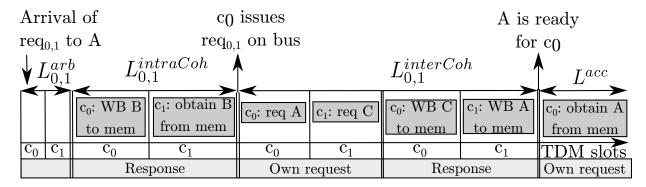

| 3.8 | Different latency components. Initially, $c_0$ modified B and $c_1$ modified A                                                               | 53 |

| 3.9  | The latency bound on each interference component. Empty slots/periods do not have events that are related to $c_1$ 's latency                                                        | 55 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.10 | WC latencies and the effect of unpredictability sources on them. Unpredictable $i$ corresponds to source $i$ in Section 3.5. Horizontal dotted line represents the analytical bound. | 58 |

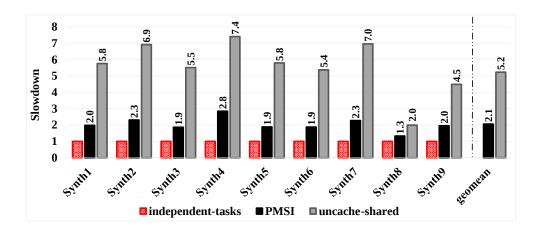

| 3.11 | Execution time slowdown compared to MESI protocol                                                                                                                                    | 60 |

| 3.12 | Slowdown in the execution time of different approaches compared to ideal scenario.                                                                                                   | 61 |

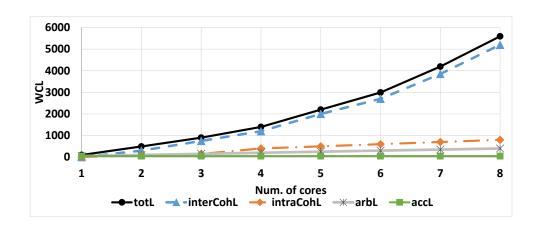

| 3.13 | Latencies with different number of cores                                                                                                                                             | 62 |

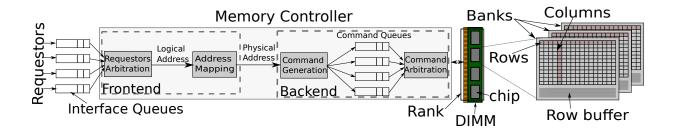

| 4.1  | DRAM subsystem.                                                                                                                                                                      | 66 |

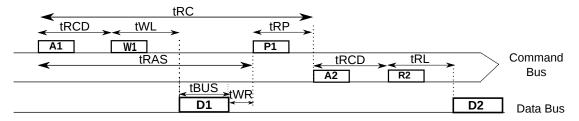

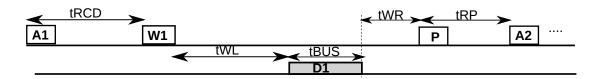

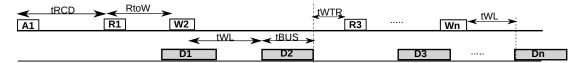

| 4.2  | A write access followed by a write or read access targeting the same bank and rank for close-page policy.                                                                            | 67 |

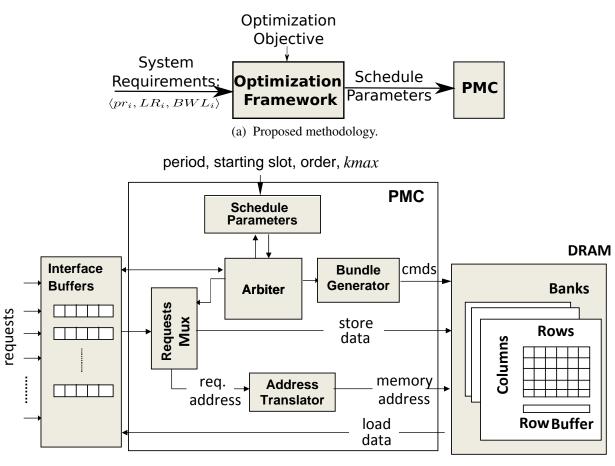

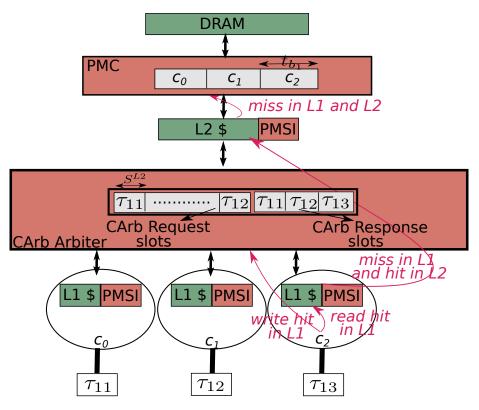

| 4.3  | PMC framework                                                                                                                                                                        | 73 |

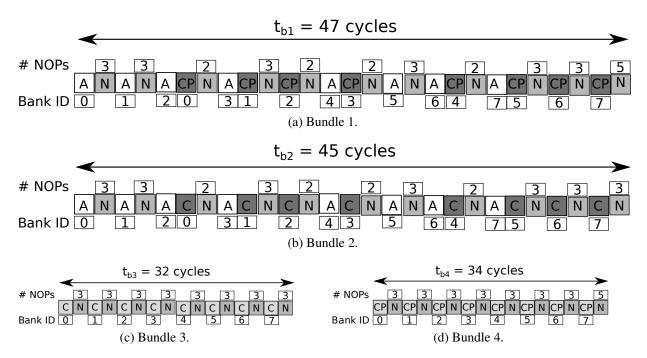

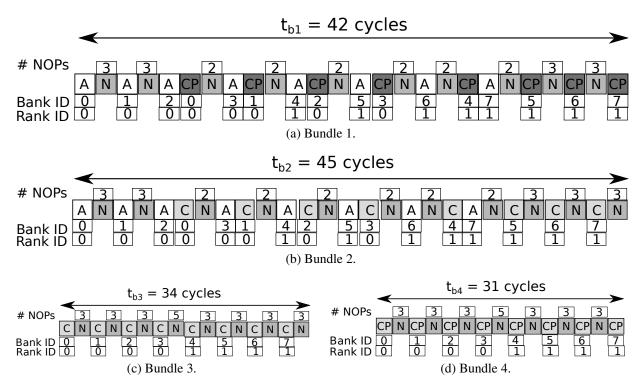

| 4.4  | Command arrangements of the four bundles interleaving across 8 banks of DDR3-1333 for a write request. A: ACTIVATE command, C: CAS command, CP: CASp command, and N: NOP command.    | 74 |

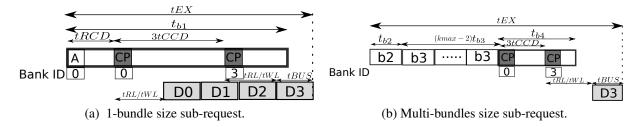

| 4.5  | Bundles usage for the 4 bank interleaving case                                                                                                                                       | 75 |

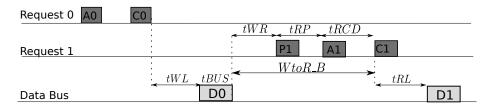

| 4.6  | A write followed by a read both targeting an open row                                                                                                                                | 78 |

| 4.7  | Command arrangements of the four bundles interleaving across 2 ranks and 4 banks per rank                                                                                            | 79 |

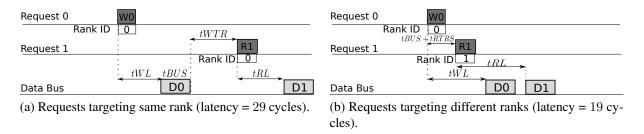

| 4.8  | A write followed by a read for no bank interleaving (single bank bundle)                                                                                                             | 80 |

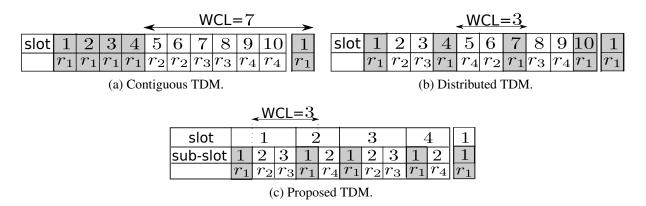

| 4.9  | TDM scheduling mechanisms                                                                                                                                                            | 81 |

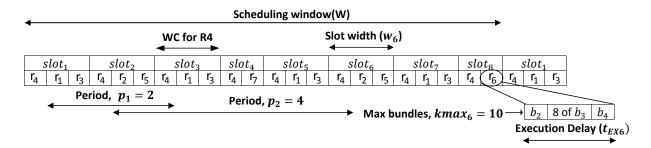

| 4.10 | A schedule example                                                                                                                                                                   | 84 |

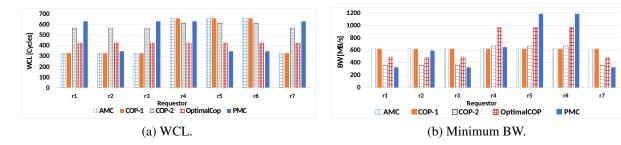

|      | Results for the multimedia processing system use-case                                                                                                                                | 89 |

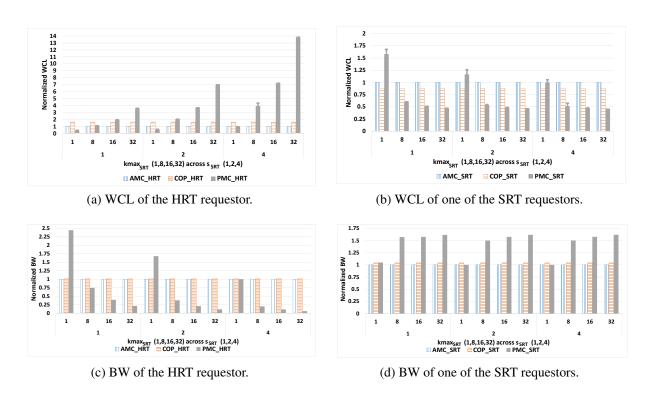

| 4.12 | Effect of varying kmax and s of SRT requestors                                                                                                                                       | 91 |

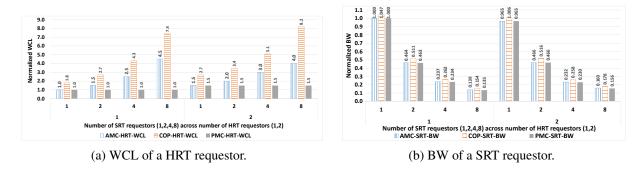

| 4.13 | Effect of varying number of requestors                                                                                                                                               | 93 |

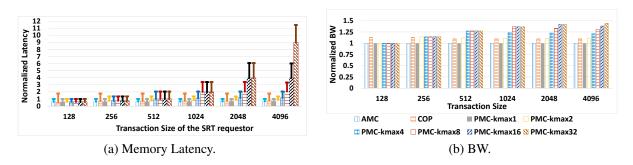

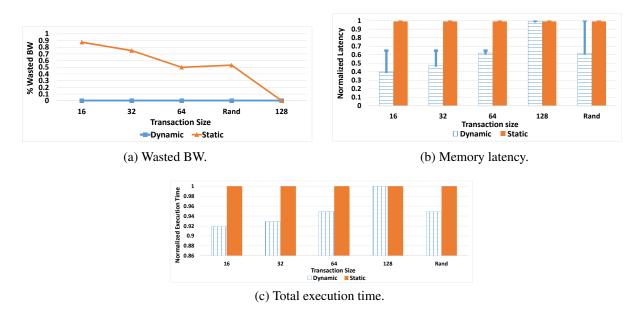

| 4.14 | Effect of the transaction size                                                                                                                                                       | 94 |

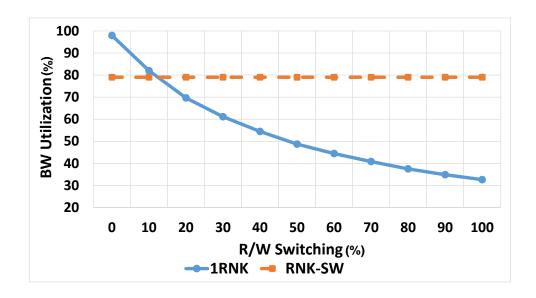

|      | Dynamic vs. static bank interleaving                                                                                                                                                 | 95 |

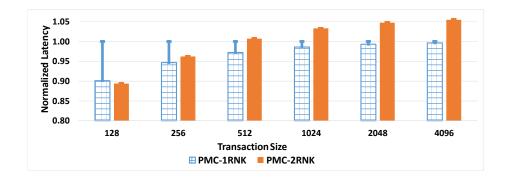

| 4.16 | Effect of rank interleaving on memory latency.                                                                                                                                       | 97 |

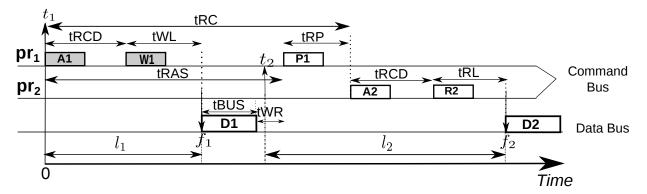

| 5.1  | A write access followed by a write or read access targeting the same bank and rank. A: ACTIVATE, W: WRITE, R: READ, P: PRE, D: DATA                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

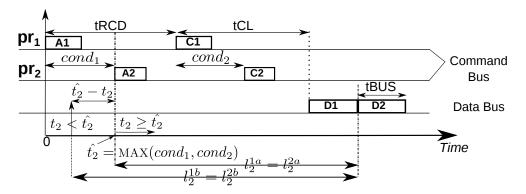

| 5.2  | The two conditions controlling the issuance of the first command of $pr_2$ . C1 and C2 represent CAS1 and CAS2 commands respectively                                                                                                                                                                   |

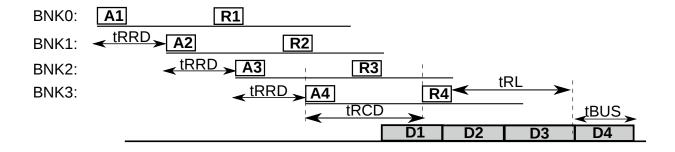

| 5.3  | Two accesses with same access type to two different banks in the same rank 105                                                                                                                                                                                                                         |

| 5.4  | A read access followed by a write access targeting different banks in the same rank. 106                                                                                                                                                                                                               |

| 5.5  | Reverse-engineering process                                                                                                                                                                                                                                                                            |

| 5.6  | Latency bounds for a sequence of two requests                                                                                                                                                                                                                                                          |

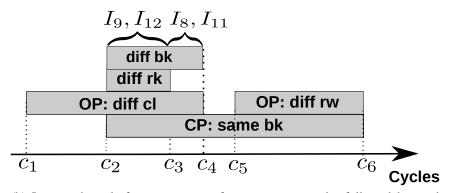

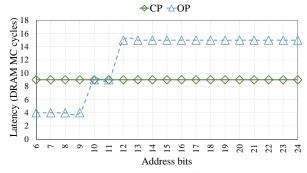

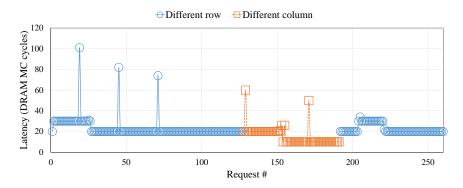

| 5.7  | Latency plots for $test_1$ stimulating the on-board MC of XUPV5-LX110T. OP: open-page policy, and CP: close-page policy                                                                                                                                                                                |

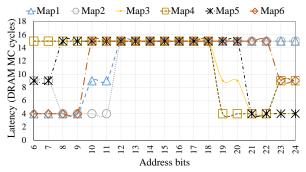

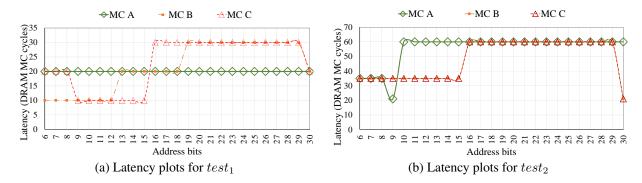

| 5.8  | Latency plots for page policy and address mapping inference tests                                                                                                                                                                                                                                      |

| 5.9  | Latency plot for hybrid-page policy                                                                                                                                                                                                                                                                    |

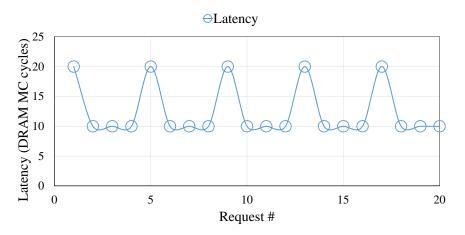

| 5.10 | Latency plot for FR-FCFS threshold test                                                                                                                                                                                                                                                                |

| 5.11 | Write buffer policy                                                                                                                                                                                                                                                                                    |

| 6.1  | Model checking operation                                                                                                                                                                                                                                                                               |

| 6.2  | Proposed validation process of MCs                                                                                                                                                                                                                                                                     |

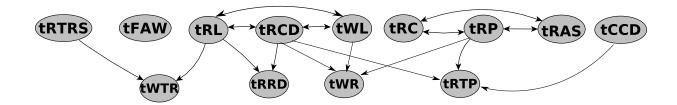

| 6.3  | DRAM commands and timing constraints interaction. Subscripts reflect the targeted bank and rank, respectively. d: different, s: same, x: do not care. Di: start of the data transfer. De: end of the data transfer. P is for same bank. $A_{d,s}$ is an A command to a different bank on the same rank |

| 6.4  | Test generation for validating XOR mapping                                                                                                                                                                                                                                                             |

| 6.5  | XOR address mapping                                                                                                                                                                                                                                                                                    |

| 6.6  | Command sequence of $Suite_{XOR}$ on XOR mapping                                                                                                                                                                                                                                                       |

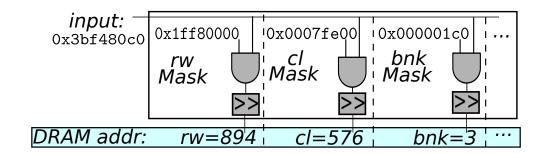

| 6.7  | Address masking operation                                                                                                                                                                                                                                                                              |

| 6.8  | Address masking schemes                                                                                                                                                                                                                                                                                |

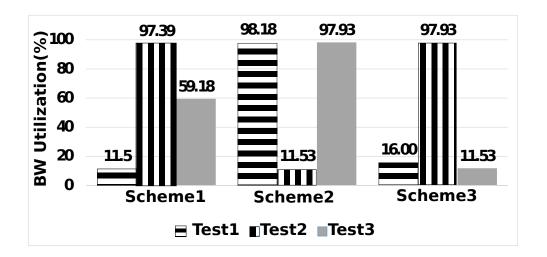

| 6.9  | Address masking results                                                                                                                                                                                                                                                                                |

| 6.10 | Command sequence from executing $Test_i$ on $Scheme_i$ , $i \in \{1, 2, 3\}$ 144                                                                                                                                                                                                                       |

| 6.11 | Rank hopping                                                                                                                                                                                                                                                                                           |

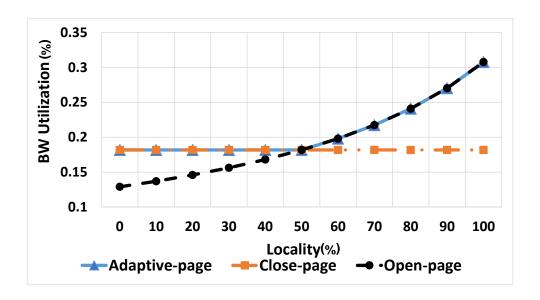

| 6.12 | Evaluation of page policies                                                                                                                                                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

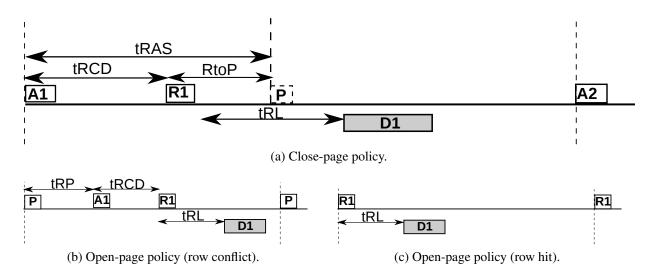

| 6.13 | Command arrangement for $Test_{PP}$                                                                                                                                                                                                                           |

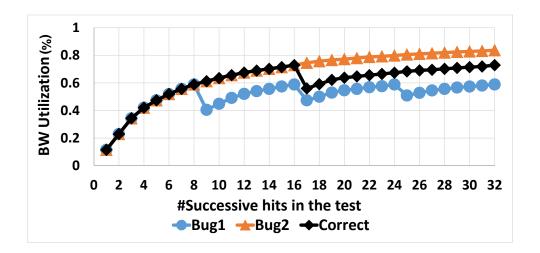

| 6.14 | Evaluation of FR-FCFS threshold                                                                                                                                                                                                                               |

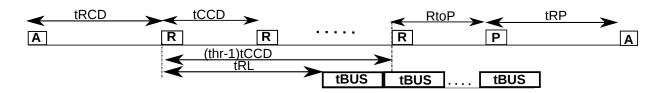

| 6.15 | Command sequence of $Suite_{thr}$ when $hit = thr - 1$                                                                                                                                                                                                        |

| 6.16 | Validation dependency graph for timing parameters                                                                                                                                                                                                             |

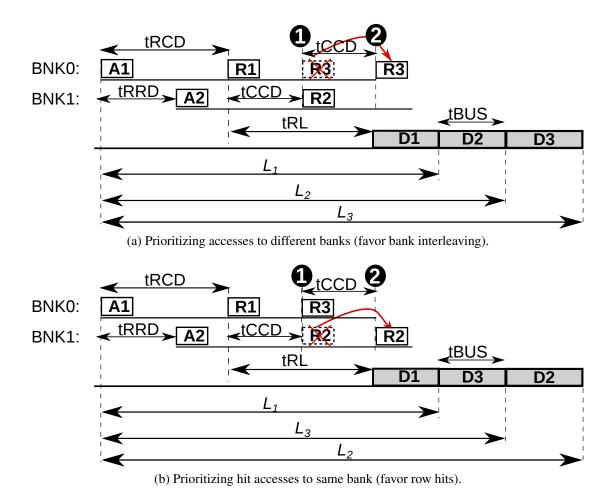

| 6.17 | Command sequence of $Test_{CCD}$                                                                                                                                                                                                                              |

| 6.18 | Test generation for validating $tCCD$                                                                                                                                                                                                                         |

| 6.19 | tCCD validation results                                                                                                                                                                                                                                       |

| 6.20 | tRC validation results                                                                                                                                                                                                                                        |

| 6.21 | tFAW validation results                                                                                                                                                                                                                                       |

| 6.22 | tRTRS validation results                                                                                                                                                                                                                                      |

| 6.23 | Command sequence of $Test_{RTRS}$                                                                                                                                                                                                                             |

| 6.24 | Command sequence of $Test_{RTP}$                                                                                                                                                                                                                              |

| 6.25 | tRTP validation results                                                                                                                                                                                                                                       |

| 6.26 | Validating $tRCD$ , $tRL$ , and $tWL$                                                                                                                                                                                                                         |

| 6.27 | tRCD, $tRL$ , and $tWL$ validation results                                                                                                                                                                                                                    |

| 6.28 | tRRD validation results                                                                                                                                                                                                                                       |

| 6.29 | Command sequence of $Test_{RRD}$                                                                                                                                                                                                                              |

| 6.30 | tWR validation results                                                                                                                                                                                                                                        |

| 6.31 | Command sequence of $Test_{WR}$                                                                                                                                                                                                                               |

| 6.32 | tWTR validation results                                                                                                                                                                                                                                       |

| 6.33 | Command sequence of $Test_{WTR}$                                                                                                                                                                                                                              |

| 6.34 | Smart Refresh behaviour with different number of accessed rows                                                                                                                                                                                                |

| 6.35 | Policies to resolve command bus contention                                                                                                                                                                                                                    |

| 7.1  | An architectural example for the system model used in deriving the total WC memory aggregated latency. The system has three cores and three tasks, where $\tau_{11}$ is mapped to $c_0$ , $\tau_{12}$ is mapped to $c_1$ , and $\tau_{13}$ is mapped to $c_2$ |

### **List of Abbreviations**

ABS Anti-lock Brake System

AMC Analyzable Memory Controller

BMC Bounded Model Checking

BW Bandwidth

CCSP Credit Control Static Priority

CL Criticality Level

COP conservative Open Page COTS Commercial Off The Shelf CPU Central Processing Unit

DIMM Dual In-line Memory Modules

DMA direct Memory Access

DoS Denial of Service

DRAM Dynamic Random Access Memories

FCFS First-Come First-Serve

FIFO First-In First-Out

FR-FCFS First-Ready First-come First-Serve

FSM Finite State Machine

GPU Graphical Processing Unit

HRR Harmonic Round Robin

HRT Hard Real-Time

HWRR Harmonic Weighted Round Robin

IBB Initial Bank Bits

LLC last-level cache

LRU Least Recently Used

LRU Pseudo Least Recently Used

LTL Linear Temporal Logic

LUT Look Up Table

MC Memory Controller

MCS Mixed Criticality Systems

MIG Memory Interface Generator

MSI Modify-exclusive-Share-Invalidate coherence protocol

MSI Modify-Share-Invalidate coherence protocol

PMC Programmable Memory Controller PMSI Predictable MSI coherence protocol

PMU Performance Monitoring Unit

PR Pending Request

PRR Prioritized Round Robin

PWB Pending Writeback

RM Rate Monotonic RR Round Robin

RTL Register Transfer Level

SRT Soft Real-Time

SVA system Verilog Assertion

TDM Time Division Multiplexing TLM Transaction Level Modeling

WC Worst Case

WCET Worst-Case Execution Time

WCL Worst Case Latency WRR Weighted Round Robin

## **List of Symbols**

- $C_l$  Criticality class l

- $D_{il}$  Deadline of task  $\tau_{il}$

- $E_{jl}$  Total WCET.  $E_{jl} = S_{jl} + I_{jl}$ .

- $\Gamma_l$  total number of tasks in  $C_l$

- H Hyperperiod of a CArb schedule

- $I_{jl}(L)$  WC additional latency due to inter-task interference.  $S_{jl}$  is a function of L.

- $L_l$  Criticality level l

- $S_{jl}(L)$  WCET of any job of task  $\tau_{jl}$  when it runs in isolation (no inter-task interference).  $S_{jl}$  is a function of L.

- $\tau_{jl}$  Task j in criticality class l

- $T_{jl}$  Minimum inter-arrival time for jobs of task  $\tau_{jl}$ , which represents the task period

- $CH_l$  The hyperperiod of class  $C_l$  in a CArb schedule

- $CP_l$  The class period of  $C_l$  in a CArb schedule

- $CW_l$  The class weight of  $C_l$  in a CArb schedule

- $\gamma_r$  Total number of tasks in partition r for partitioned scheduling.

- $\Lambda_{jl}$  maximum number of memory accesses issued by any job of  $\tau_{jl}$ .

- $M_{jl}$  Memory latency requirement of task  $\tau_{jl}$ .

- $TP_{jl}$  The task period of  $\tau_{jl}$  in a CArb schedule

- $\tau W_{jl}$  The task weight of  $\tau_{jl}$  in a CArb schedule

- $\hat{U}_r$  The partial utilization granted to partition r for partitioned scheduling

- $U_r$  Total utilization of tasks in partition r for partitioned scheduling.

- $y^{acc}$  CArb's access latency of a request  $req_r$  generated by  $\tau_{il}$ .

- $y_{jl,r}^{sch}$  CArb's scheduling latency of a request  $req_r$  generated by  $au_{jl}$

- $y_{il}^{tot}$  CArb's total worst-case latency of any request generated by  $\tau_{il}$

- $Z_l$  The window size of a CArb schedule, which represents the number of task slots in a class slot

- $BWL_i$  The minimum bandwidth required by  $r_i$

- $LR_i$  The memory access latency requirement of  $r_i$

- R The set of requestors in the system deploying PMC

- $kmax_i$  Maximum number of bundles of a requestor  $r_i$  that are serviced per sub-request

| $LBB_i$ | The lower-bound bandwidth delivered to a requestor $r_i$                                                                                   |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| $p_i$   | Harmonic period: the interval (in slots) between two successive executions of i. It is equal to the total number of slots divided by $s_i$ |

| $pr_i$  | $r_i$ 's relative priority                                                                                                                 |

| $p_i$   | Harmonic period: the interval (in slots) between two successive executions of i. It is equal to the total number of slots divided by $s_i$ |

| $r_i$   | Requestor number i in the system deploying PMC                                                                                             |

| $s_i$   | Harmonic slots: total number of slots allocated to requestor $r_i$                                                                         |

| tBUS    | Time required to transfer a data burst on the data bus                                                                                     |

| tFAW    | The number of cycles in which four activates are allowed within the same rank                                                              |

| tRCD    | The minimum time between activating the row and a read/write access to it                                                                  |

| tRC     | The minimum time between two accesses to different rows in a bank                                                                          |

| tRL     | The minimum time between a read CAS and the start of data transfer                                                                         |

| tRP     | The row pre-charge time                                                                                                                    |

| tRTRS   | The rank to rank switching delay                                                                                                           |

| tRTW    | Read to write switching delay                                                                                                              |

| +\\\/\I | The minimum time between a write CAS and the start of data transfer                                                                        |

tWTR Write to read switching delay

$UBD_i$  The upper-bound latency incurred by a memory request from  $r_i$

$w_i$  The width of slot j in clock cycles

$Y_i$  The total number of requestors assigned to slot j

$L^{acc}$  The time required to transfer the requested data by  $c_i$  between the shared memory

and the private cache of  $c_i$

$L_{ir}^{arb}$  Arbitration latency of request,  $req_{i,r}$ , generated by core  $c_i$

$WCL_i^{arb}$  The worst-case arbitration latency of any request generated by core  $c_i$

$L_{i,r}^{coh}$  Coherence latency of request,  $req_{i,r}$ , generated by core  $c_i$

$WCL_i^{interCoh}$  The worst-case inter-coherence latency of any request generated by core  $c_i$

$L_{i,r}^{interCoh}$  Inter-core coherence latency of request,  $req_{i,r}$ , generated by core  $c_i$

$WCL_i^{intraCoh}$  The worst-case intra-coherence latency of any request generated by core  $c_i$

$L_{i,r}^{intraCoh}$  Intra-core coherence latency of request,  $req_{i,r}$ , generated by core  $c_i$

$t_i$  The arrival time of the first command from  $pr_i$  to the command queue

$l_i^{BEST}$  The best-case latency of  $pr_i$

BKW The number of DRAM bank bits

$bnk_i$  The target bank of the  $i^{th}$  physical request

$ch_i$  The target channel of the  $i^{th}$  physical request

CLW The number of DRAM column bits

CNW The number of DRAM channel bits

$cl_i$  The target column of the  $i^{th}$  physical request

$cs_i$  The memory commands sequence of the  $i^{th}$  physical memory request

$f_i$  The time-stamp at which  $pr_i$  starts its data transfer

$l_i$  The latency of  $pr_i$  defined as  $l_i = f_i - t_i$

$la_i$  The address of the  $i^{th}$  logical memory request

$lr_i$  The  $i^{th}$  logical memory request

$o_i$  The type of the  $i^{th}$  logical memory request. It is either a read or a write,  $o \in \{R,W\}$

$pa_i$  The address of the  $i^{th}$  physical memory request

$pr_i$  The  $i^{th}$  physical memory request

PW The number of bits in the physical address

RKW The number of DRAM rank bits

$rnk_i$  The target rank of the  $i^{th}$  physical request

RWW The number of DRAM row bits

$rw_i$  The target row of the  $i^{th}$  physical request

$l_i^{WORST}$  The worst-case latency of  $pr_i$

$L1_i^{Rhits}$  The number of read requests issued by core  $c_i$  and are hits in L1 cache

$L1_i^{Whits}$  The number of write requests issued by core  $c_i$  and are hits in L1 cache

$L1^{accL}$  L1 hit latency specified by the processor datasheet

$L2_i^{hits}$  The number of requests issued by core  $c_i$  and are hits in L2 cache

$L2_i^{misses}$  The number of requests issued by core  $c_i$  and are misses in L2 cache

$MAL_i$  The total WC memory aggregated latency of a core  $c_i$

$S^{L2}$  The slot width of the TDM schedule managing accesses to L2 cache

$WCL_i^{DRAM}$  The WCL of a read or write request issued by core  $c_i$  upon accessing DRAM

$WCL_i^{RL1}$  The WCL of a read request issued by core  $c_i$  upon accessing L1 cache

$WCL_i^{WL1}$  The WCL of a write request issued by core  $c_i$  upon accessing L1 cache

$WCL_i^{L2}$  The WCL of a read or write request issued by core  $c_i$  upon accessing L2 cache

### Chapter 1

### Introduction

Real-time systems are those, whose behaviour depends not only on their functionality, but also on their response time. Until recently, real-time systems have been limited to safety-critical domains such as avionics and spacecrafts. However, with the emanating cyber-physical systems (CPS) and Internet of Things (IoT) revolution, real-time systems are becoming ubiquitous in many emerging domains [12]. Examples include transportation (such as automobiles, avionics, space vehicles, etc.), infrastructures such as power grids, health care (such as medical devices, and implantable and biomedical devices), and industrial environment (such as manufacturing plants, power plants, and robots) to name a few.

Since application demands from these emerging domains continue to increase, there is a surge in wanting to use multi-core platforms to deploy real-time systems. This is primarily due to the benefits multi-core platforms provide in cost, and performance. However, multi-core platforms impose new challenges towards guaranteeing requirements of running applications. These challenges arise because different cores in the platform may interfere each other, while competing to access memory resources that are shared amongst them. As Figure 1.1 depicts, these shared resources include buses, on-chip caches, and off-chip dynamic random access memories (DRAMs). This interference is a challenge for real-time systems because operations of one core affect the temporal behaviour of other cores, which complicates the timing analysis of the system. Timing analysis is crucial for real-time systems to guarantee that tasks meet their timing requirements such that the task's worst-case execution time (WCET) is less than its deadline. Hence, the highlighted interference challenge is the focus of this thesis. In particular, this thesis proposes predictable architectures for shared buses, caches, and DRAMs. We believe that providing predictable solutions for shared memory resources is of unavoidable necessity towards deploying real-time systems onto multi-core platforms. In addition, the problems associated with this interference are exacerbated in real-time systems deploying tasks with different criticalites, known as *mixed criticality systems* (MCS) since a non-critical task can affect the behaviour of a critical task. Consequently, this thesis pays special attention to MCS.

Figure 1.1: Multi-core architecture.

We address the interference problem on the *shared buses* ( in Figure 1.1) in multi-core MCS by proposing CArb [1], a predictable and criticality-aware arbiter (Chapter 2). In addition, we utilize CArb to mitigate overheads resulting from system switching among different modes, which is one of the onerous challenges in MCS. CArb does not impose any restrictions on mapping applications to cores. Hence, it operates in tandem with existing operating system (OS) scheduling policies. CArb is able to dynamically adapt arbitration at run time to respond to increases in the monitored execution times of tasks. Utilizing this adaptation, CArb is able to offset these increases; hence, it postpones the OS's need to switch to a degraded mode. Our evaluation using an avionics case study from Honeywell shows that CArb is able to meet diverse requirements of tasks with mixed criticalities.

At the *cache hierarchy* level (2) in Figure 1.1), one of the challenging burdens for computer architects is to maintain correctness of shared data stored in cache hierarchies of multi-core platforms, which is known as cache coherence [10]. Although cache coherence has been extensively investigated for conventional performance-oriented platforms, multi-core real-time systems introduce new challenges from the predictability perspective. To exemplify, we show that deploying a conventional coherence protocol in a predictable system can lead to unpredictable

behaviours [2]. In Chapter 3, we highlight those challenges and provide a set of invariants to address them. These invariants are architecture- and protocol-independent. Based on these invariants, we propose the first predictable hardware cache coherence protocol, named PMSI, which enables tasks to simultaneously share data in a manner amenable for timing analysis. PMSI augments the classic modify-share-invalid (MSI) protocol with transient coherence states, and minimal architectural changes. This allows us to derive worst-case (WC) latency bounds that provide timing guarantees. Our empirical results show that PMSI improves average-case performance by up to  $4\times$  over the next best alternative, which avoids caching the shared data on the private cache of each core.

At the *shared DRAM* level (3) in Figure 1.1), we propose PMC [3, 4], a programmable memory controller that provides latency guarantees for running tasks upon accessing the off-chip DRAM, while assigning differential memory services to tasks based on their bandwidth and latency requirements (Chapter 4). PMC supports MCS by enabling the system designer to specify requirements per software task. Leveraging awareness of these requirements, PMC optimally assigns differential memory service per task. We also presented a formal timing analysis that proves latency and bandwidth guarantees.