# **Optimized Hardware Implementations of Lightweight Cryptography**

by

# Gangqiang Yang

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in **Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2017

© Gangqiang Yang 2017

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Radio frequency identification (RFID) is a key technology for the Internet of Things era. One important advantage of RFID over barcodes is that line-of-sight is not required between readers and tags. Therefore, it is widely used to perform automatic and unique identification of objects in various applications, such as product tracking, supply chain management, and animal identification. Due to the vulnerabilities of wireless communication between RFID readers and tags, security and privacy issues are significant challenges. The most popular passive RFID protocol is the Electronic Product Code (EPC) standard. EPC tags have many constraints on power consumption, memory, and computing capability. The field of lightweight cryptography was created to provide secure, compact, and flexible algorithms and protocols suitable for applications where the traditional cryptographic primitives, such as AES, are impractical. In these lightweight algorithms, tradeoffs are made between security, area/power consumption, and throughput.

In this thesis, we focus on the hardware implementations and optimizations of lightweight cryptography and present the Simeck block cipher family, the WG-8 stream cipher, the Warbler pseudorandom number generator (PRNG), and the WGLCE cryptographic engine.

Simeck is a new family of lightweight block ciphers. Simeck takes advantage of the good components and design ideas of the SIMON and SPECK block ciphers and it has three instances with different block and key sizes. We provide an extensive exploration of different hardware architectures in ASICs and show that Simeck is smaller than SIMON in terms of area and power consumption.

For the WG-8 stream cipher, we explore four different approaches for the WG transformation module, where one takes advantage of constant arrays and the other three benefit from the tower field constructions of the finite field  $\mathbb{F}_{2^8}$  and also efficient basis conversion matrices. The results in FPGA and ASICs show that the constant arrays based method is the best option. We also propose a hybrid design to improve the throughput with a little additional hardware.

For the Warbler PRNG, we present the first detailed and smallest hardware implementations and optimizations. The results in ASICs show that the area of Warbler with throughput of 1 bit per 5 clock cycles (1/5 bpc) is smaller than that of other PRNGs and is in fact smaller than that of most of the lightweight primitives. We also optimize and improve the throughput from 1/5 bpc to 1 bpc with a little additional area and power consumption.

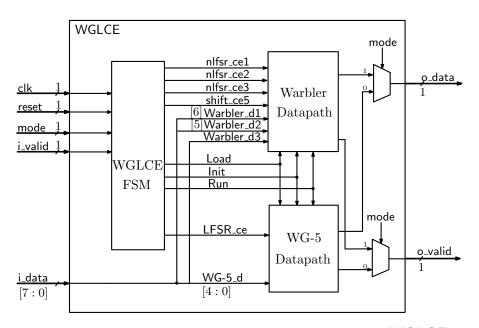

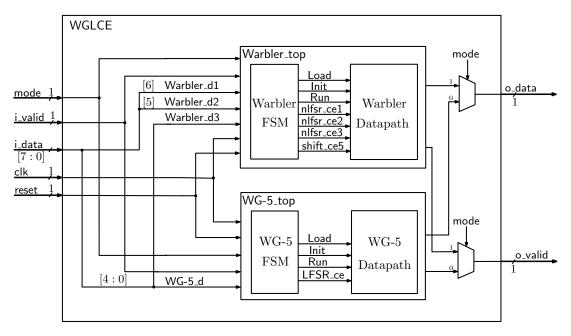

Finally, we propose a cryptographic engine WGLCE for passive RFID systems. We merge the Warbler PRNG and WG-5 stream cipher together by reusing the finite state machine for both of them. Therefore, WGLCE can provide data confidentiality and generate pseudorandom numbers. After investigating the design rationales and hardware architectures, our results in ASICs show that WGLCE meets the constraints of passive RFID systems.

#### Acknowledgements

First and foremost, I would like to express my deepest gratitude to my supervisors Professor Mark Aagaard and Professor Guang Gong for their tremendous support, guidance, and encouragement during the past four and a half years. The continuous help and advice have solved a lot of difficulties I encountered during my research. Their extensive knowledge and expertise in the field have always inspired and motivated me for my research from both the theoretical and practical points of view. Throughout their guidance, I have gained a lot of confidence, which help me think deeply to shorten the gap of the theoretical cryptographic research, hardware implementations, and actual applications. Thanks to the positive attitude towards work and life that the professors have provided, the past four and a half years have been an unforgettable time in my entire life that has given me a tremendous development, both academically and personally.

I would also like to express my appreciation to Professor Yunsi Fei From Northeastern University for serving as my external examiner and giving me many valuable suggestions and comments. I am also grateful to my thesis committee members Professor Anwar Hasan, Professor Hiren Patel, and Professor Alfred Menezes for their valuable comments and time spent on my thesis, which help to improve the quality of my thesis a lot. This thesis would not have been possible without their guidance and assistance.

I would like to give special thanks to all my colleagues and friends during my PhD studies for their enormous support and valuable discussions. I thank Dr. Xinxin Fan for his help, guidance, and collaboration during the first two years of my study. I thank Dr. Bo Zhu and Dr. Valentin Suder for collaborating on writing a paper with me. I thank Dr. Fei Huo and Nusa Zidaric for helping me polish my English writings. I thank Dr. Kalikinkar Mandal for his help during my last term of studies. Thanks are also given to all the members from the Communication Security (ComSec) lab at University of Waterloo for their support and friendship. They are: Dr. Yin Tan, Kaveh Fazli, Dr. Teng Wu, Shasha Zhu, Yao Chen, Qiao Liu, Bo Yang, Khaled Nassar, Dr. Hayssam EI-Razouk, Ahmed Ayoub, Meng Yang, and many others.

I would like to thank ComSec seminars and the conferences that I have attended (WESS 2013, NIST lightweight workshop 2015, CHES 2015, SAC 2016), which broadened my knowledge and provided me opportunities to exchange ideas with others.

Last but not least, I would like to thank my family for their unconditional and endless love. I am indebted to my parents and my brother for their support, encouragements and sacrifices throughout my life. My deepest gratitude goes to my mother for her endless support and love. None of my work would have been possible without them.

## **Dedication**

To my dearest father

To my loved mother

To my brother

# **Table of Contents**

| Li | List of Tables |         |                                     |      |

|----|----------------|---------|-------------------------------------|------|

| Li | st of I        | Figures |                                     | xii  |

| 1  | Intr           | oductio | n                                   | 1    |

|    | 1.1            | Motiva  | ation                               | . 1  |

|    | 1.2            | Thesis  | Organization                        | . 3  |

|    | 1.3            | Contri  | butions                             | . 4  |

| 2  | Bacl           | kground | di                                  | 6    |

|    | 2.1            | Mathe   | matical Background                  | . 6  |

|    |                | 2.1.1   | Finite Field                        | . 6  |

|    |                | 2.1.2   | Feedback Shift Register Sequences   | . 8  |

|    |                | 2.1.3   | The WG Transformation               | . 9  |

|    | 2.2            | Symm    | etric Key Cryptography              | . 10 |

|    | 2.3            | Lightw  | veight Cryptography                 | . 12 |

|    |                | 2.3.1   | Lightweight Block Ciphers           | . 13 |

|    |                | 2.3.2   | Lightweight Stream Ciphers          | . 17 |

|    | 2.4            | Hardw   | vare Design and Optimization        | . 22 |

|    |                | 2.4.1   | Hardware Implementations            | . 22 |

|    |                | 2.4.2   | Reuse, Parallelism and Clock Gating | . 24 |

|      | 2.4.3                        | Choice of Bases                                                                                                                                                                                     | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 2.4.4                        | Tower Field                                                                                                                                                                                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.5  | EPC P                        | assive RFID Systems                                                                                                                                                                                 | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The  | Simeck                       | Family of Lightweight Block Ciphers                                                                                                                                                                 | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1  | Design                       | Specification and Rationale                                                                                                                                                                         | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 3.1.1                        | Specification of Simeck                                                                                                                                                                             | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 3.1.2                        | Design Rationale                                                                                                                                                                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.2  | Hardw                        | are Implementations                                                                                                                                                                                 | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 3.2.1                        | Metrics and Design Flow                                                                                                                                                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 3.2.2                        | Two Different Hardware Architectures for Simeck                                                                                                                                                     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 3.2.3                        | Hardware Evaluations of Simeck                                                                                                                                                                      | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.3  | Results                      | s Comparison between Simeck and SIMON                                                                                                                                                               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.4  | Compa                        | arisons with Other Lightweight Block Ciphers                                                                                                                                                        | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.5  | Summa                        | ary                                                                                                                                                                                                 | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Dagi | an Chas                      | on Explanation of the Lightensiaht Studens Cinker WC 0                                                                                                                                              | <b>5</b> 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                              |                                                                                                                                                                                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.1  |                              |                                                                                                                                                                                                     | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.1.1                        |                                                                                                                                                                                                     | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.1.2                        | Overview of WG-8                                                                                                                                                                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.1.3                        | Hardware Architecture                                                                                                                                                                               | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.2  | Design                       | Strategies for the WG-8 Transformation Module                                                                                                                                                       | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.2.1                        | Using Constant Array                                                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.2.2                        | Using Tower Field 1                                                                                                                                                                                 | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.2.3                        | Using Tower Field 2                                                                                                                                                                                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |                              |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | 4.2.4                        | Using Tower Field 3                                                                                                                                                                                 | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.2.4<br>4.2.5               | Using Tower Field 3                                                                                                                                                                                 | 63<br>69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 3.1 3.2 3.3 3.4 3.5 Desi 4.1 | 2.4.4  2.5 EPC P  The Simeck  3.1 Design  3.1.1  3.1.2  3.2 Hardw  3.2.1  3.2.2  3.2.3  3.3 Results  3.4 Compa  3.5 Summ  Design Space  4.1 Descript  4.1.1  4.1.2  4.1.3  4.2 Design  4.2.1  4.2.2 | 2.4.4 Tower Field  2.5 EPC Passive RFID Systems  The Simeck Family of Lightweight Block Ciphers  3.1 Design Specification and Rationale 3.1.1 Specification of Simeck 3.1.2 Design Rationale  3.2 Hardware Implementations 3.2.1 Metrics and Design Flow 3.2.2 Two Different Hardware Architectures for Simeck 3.2.3 Hardware Evaluations of Simeck  3.3 Results Comparison between Simeck and SIMON  3.4 Comparisons with Other Lightweight Block Ciphers  3.5 Summary  Design Space Exploration of the Lightweight Stream Cipher WG-8  4.1.1 Parameters for WG-8 4.1.2 Overview of WG-8 4.1.3 Hardware Architecture  4.2 Design Strategies for the WG-8 Transformation Module 4.2.1 Using Constant Array 4.2.2 Using Tower Field 1 |

|   |     | 4.3.1 Using Finite Field Arithmetic                                              |

|---|-----|----------------------------------------------------------------------------------|

|   |     | 4.3.2 Using Constant Array                                                       |

|   | 4.4 | Hardware Implementations                                                         |

|   |     | 4.4.1 Finite State Machine                                                       |

|   |     | 4.4.2 FPGA Implementations and Results                                           |

|   |     | 4.4.3 ASIC Implementations and Results                                           |

|   | 4.5 | Results Analysis and Comparison                                                  |

|   |     | 4.5.1 Different Tower Field Methods Analysis                                     |

|   |     | 4.5.2 Comparisons with Other Lightweight Stream Ciphers                          |

|   | 4.6 | Summary                                                                          |

| 5 | War | bler Pseudorandom Number Generator 79                                            |

|   | 5.1 | Description of Warbler                                                           |

|   | 5.2 | ASIC Architecture                                                                |

|   |     | 5.2.1 Entire Architecture                                                        |

|   |     | 5.2.2 FSM                                                                        |

|   |     | 5.2.3 Datapath                                                                   |

|   |     | 5.2.4 Throughput Improvement                                                     |

|   | 5.3 | Results Evaluation                                                               |

|   |     | 5.3.1 ASIC Results                                                               |

|   |     | 5.3.2 Results Analysis                                                           |

|   | 5.4 | Comparisons with Other Lightweight Primitives                                    |

|   | 5.5 | Summary                                                                          |

| 6 | WG  | LCE: A Cryptographic Engine for Passive RFID Systems 98                          |

|   | 6.1 | <b>WGLCE</b> : Overview                                                          |

|   | 6.2 | A New Efficient Hardware Implementations of Ultra-lightweight Stream Cipher WG-5 |

|    |       | 6.2.1   | Description of WG-5                 | . 100 |

|----|-------|---------|-------------------------------------|-------|

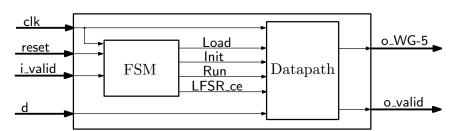

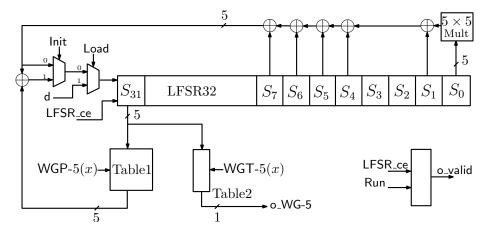

|    |       | 6.2.2   | Hardware Architecture of WG-5       | . 102 |

|    |       | 6.2.3   | ASIC Results                        | . 104 |

|    | 6.3   | Design  | and Implementations of WGLCE        | . 105 |

|    |       | 6.3.1   | Hardware Architectures              | . 105 |

|    |       | 6.3.2   | Implementation Results and Analysis | . 107 |

|    |       | 6.3.3   | Interface of WGLCE                  | . 109 |

|    | 6.4   | Compa   | arisons                             | . 112 |

|    | 6.5   | Summ    | ary                                 | . 112 |

| 7  | Con   | clusion | s and Future Work                   | 113   |

|    | 7.1   | Conclu  | usions                              | . 113 |

|    | 7.2   | Future  | Work                                | . 115 |

| D. | foron | 005     |                                     | 117   |

# **List of Tables**

| 2.1 | Ten SIMON and SPECK Instances                                                                   | 14 |

|-----|-------------------------------------------------------------------------------------------------|----|

| 2.2 | SIMON and SPECK Parameters                                                                      | 16 |

| 3.1 | Differences between SIMON and Simeck                                                            | 36 |

| 3.2 | The Areas of Basic Gates in the Libraries                                                       | 37 |

| 3.3 | Our Implementation Results of Simeck32/64, 48/96, 64/128 in 130nm                               | 42 |

| 3.4 | Our Implementation Results of SIMON32/64, 48/96, 64/128 in 130nm                                | 43 |

| 3.5 | Our Implementation Results of Simeck32/64, 48/96, 64/128 in 65nm                                | 44 |

| 3.6 | Our Implementation Results of SIMON32/64, 48/96, 64/128 in 65nm                                 | 45 |

| 3.7 | Breakdown of the Implementation Results for Simeck before the Place and Route in 130nm          | 47 |

| 3.8 | Comparisons of Hardware Implementations of Lightweight Block Ciphers                            | 49 |

| 4.1 | Tower Construction $\mathbb{F}_{(2^4)^2}$                                                       | 58 |

| 4.2 | Exponentiation Table $T_{exp}$ in Hexadecimal Notation                                          | 59 |

| 4.3 | Logarithm Table $T_{log}$ in Hexadecimal Notation                                               | 59 |

| 4.4 | Tower Construction $\mathbb{F}_{(2^4)^2}$ with Normal Bases                                     | 62 |

| 4.5 | Tower Construction $\mathbb{F}_{((2^2)^2)^2}$ with Normal Bases                                 | 64 |

| 4.6 | Multiplexers and Registers During the Two-clock Computation of $\operatorname{WGP-8}(x^{19})$ . | 68 |

| 4.7 | The Area, Speed, and Power Consumption Results of FPGA Implementations                          | 73 |

| 4.8 | Area, Speed, and Power Consumption Results for ASIC Implementations in 65nm                     | 75 |

| 4.9  | Area, Speed, and Power Consumption Results for ASIC Implementations in 130nm              | 76  |

|------|-------------------------------------------------------------------------------------------|-----|

| 4.10 | The Best Choice of the Tower Field Methods for Different Metrics                          | 76  |

| 4.11 | The Number of Multipliers and Multiplexers, and the Area of Them in FPGA                  | 77  |

| 5.1  | States Transition Conditions for FSM                                                      | 86  |

| 5.2  | Throughput Improvement of Warbler                                                         | 88  |

| 5.3  | Our Implementation Results of Warbler in CMOS 65nm and CMOS 130nm                         | 91  |

| 5.4  | The Sequential Logic Ratios of Warbler                                                    | 91  |

| 5.5  | Breakdown of the Implementation Results of Warbler before the Place and Route Phase       | 93  |

| 5.6  | The Area Reduction Percentages by using Compile Ultra and Compile Ultra plus Clock Gating | 93  |

| 5.7  | The WGT1-5 and WGT2-5 Constant Arrays                                                     | 94  |

| 5.8  | Comparisons with Hardware Implementations of Lightweight Primitives                       | 95  |

| 6.1  | Different Design Options for WGLCE                                                        | 99  |

| 6.2  | States Transition Conditions for FSM in WG-5                                              | 103 |

| 6.3  | ASIC Implementation Results of WG-5 in CMOS 65nm and 130nm                                | 04  |

| 6.4  | States Transition Conditions for FSM in WGLCE                                             | 106 |

| 6.5  | ASIC Implementation Results of WGLCE in CMOS 65nm                                         | 108 |

| 6.6  | ASIC Implementation Results of WGLCE in CMOS 130nm                                        | 108 |

| 6.7  | Breakdown of the Area Results for WGLCE before the Place and Route in 130nm 1             | 108 |

| 6.8  | The Old Initial Value Pattern for the Internal States of Warbler                          | 09  |

| 6.9  | The New Initial Value Pattern for the Internal States of Warbler                          | 110 |

| 6.10 | The Location of Keys and IVs                                                              | 10  |

| 6.11 | Comparisons with the Existing Cryptographic Engines                                       | 112 |

# **List of Figures**

| 2.1  | Feedback Shift Register                                                                       | 8  |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.2  | Block Cipher                                                                                  | 10 |

| 2.3  | Block Cipher Structures                                                                       | 11 |

| 2.4  | General Structure of a Stream Cipher                                                          | 11 |

| 2.5  | Design Tradeoffs between Security, Area, and Throughput                                       | 12 |

| 2.6  | The Round Function of SIMON                                                                   | 14 |

| 2.7  | The Key Expansion of SIMON                                                                    | 15 |

| 2.8  | The Round Function of SPECK                                                                   | 16 |

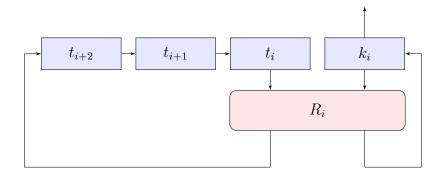

| 2.9  | SPECK Key Expansion, where $R_i$ is the SPECK Round Function with $i$ acting as the Round Key | 17 |

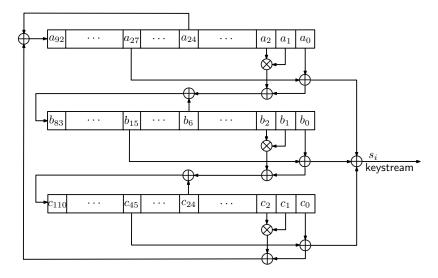

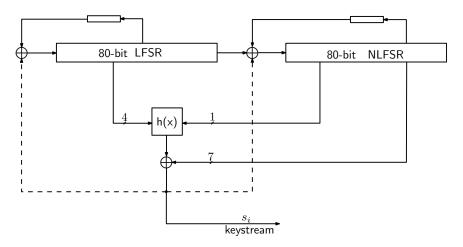

| 2.10 | The Trivium Stream Cipher                                                                     | 18 |

| 2.11 | The Grain Stream Cipher                                                                       | 19 |

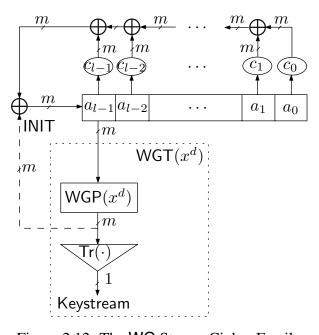

| 2.12 | The WG Stream Cipher Family                                                                   | 21 |

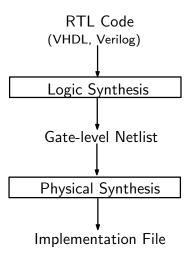

| 2.13 | Hardware Design Process                                                                       | 23 |

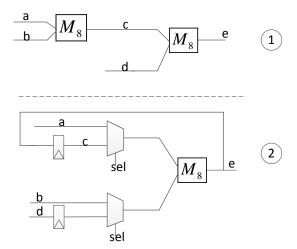

| 2.14 | Reuse the Multiplier in Two Consecutive Clock Cycles                                          | 24 |

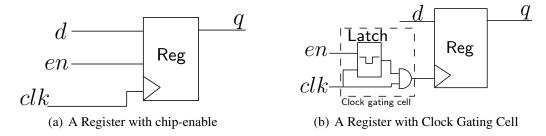

| 2.15 | Clock Gating                                                                                  | 25 |

| 2.16 | The Description of an RFID System                                                             | 27 |

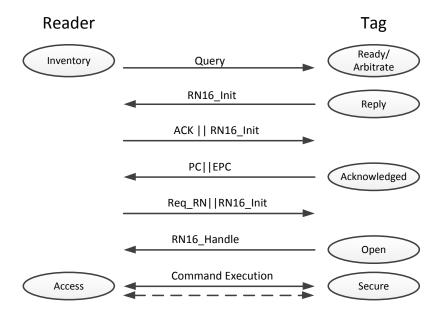

| 2.17 | The Inventory and Access Protocol between the Reader and the Tag                              | 28 |

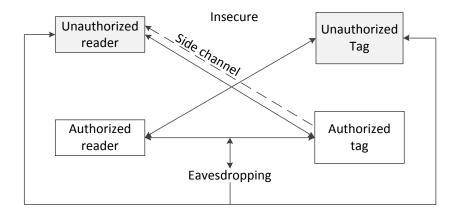

| 2.18 | Threats of an RFID System                                                                     | 29 |

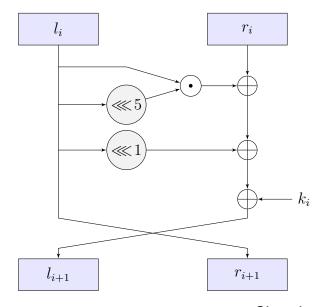

| 3.1  | The Round Function of Simeck                                                                  | 34 |

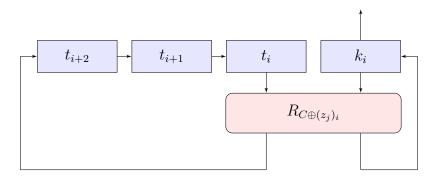

| 3.2 | The Key Expansion of Simeck, where $R_{C \oplus (z_j)_i}$ is the Simeck Round Function with $C \oplus (z_j)_i$ Acting as the Round Key | 34   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|------|

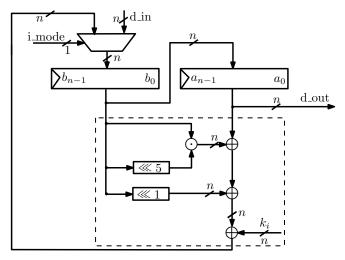

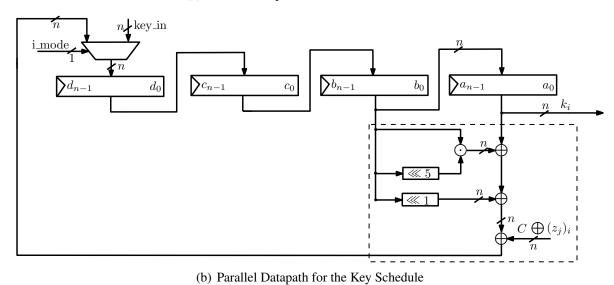

| 3.3 | Parallel Architecture for Simeck                                                                                                       | 38   |

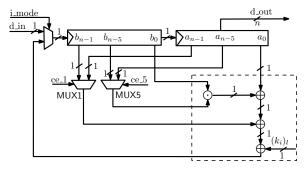

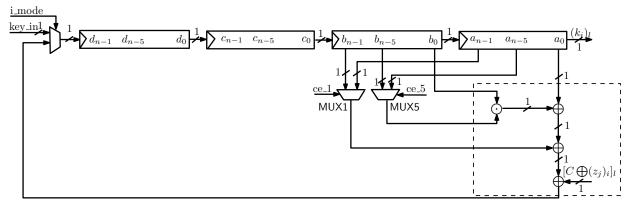

| 3.4 | Fully Serialized Architecture for Simeck                                                                                               | 40   |

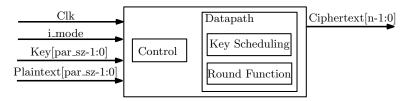

| 3.5 | The Top-level I/O Interface between the Cipher and the Outside Environment                                                             | 41   |

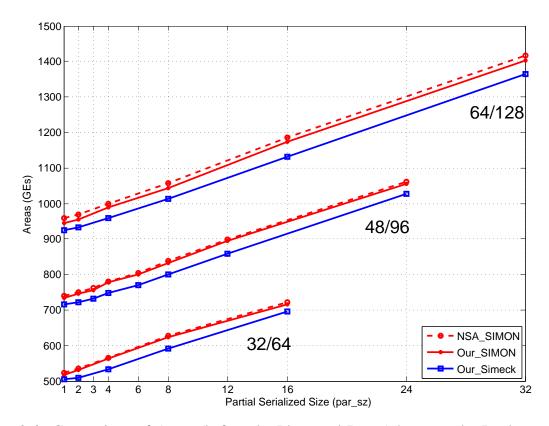

| 3.6 | Comparison of Areas (before the Place and Route) between the Implementation Results of the NSA Researchers' and Ours in CMOS 130nm     | 46   |

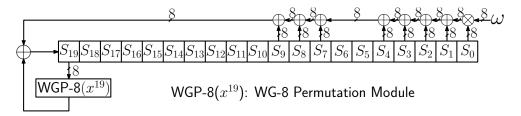

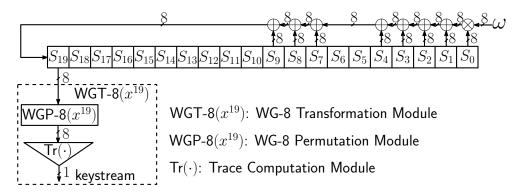

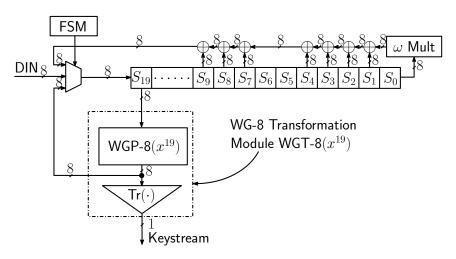

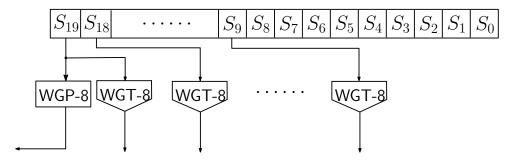

| 4.1 | The Initialization Phase of the Stream Cipher WG-8                                                                                     | 54   |

| 4.2 | The Running Phase of the Stream Cipher WG-8                                                                                            | 55   |

| 4.3 | The High-Level Hardware Architecture of the Stream Cipher WG-8                                                                         | 56   |

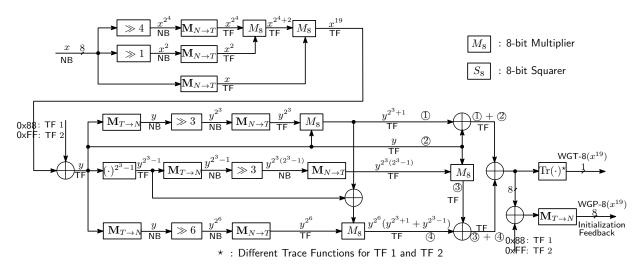

| 4.4 | The Hardware Architecture of the WG-8 Transformation Module WGT-8 $(x^{19})$ .                                                         | 61   |

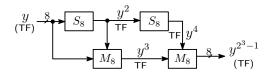

| 4.5 | The Hardware Architecture of Module $(\cdot)^{2^3-1}$                                                                                  | 61   |

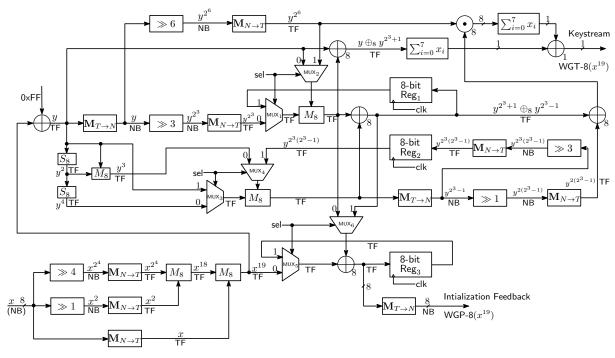

| 4.6 | The Integrated Hardware Architecture for Computing WGP-8 $(x^{19})$ and WGT-8 $(x^{19})$                                               | ) 68 |

| 4.7 | The Hybrid Design for the Constant Array based Method                                                                                  | 70   |

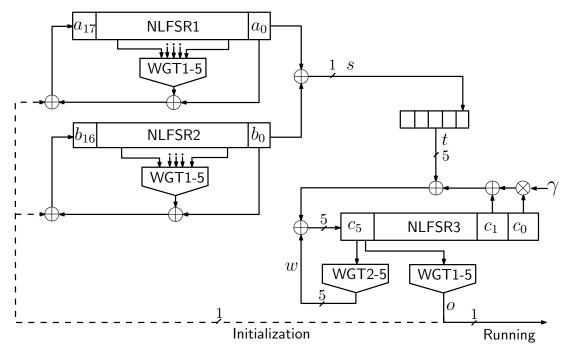

| 5.1 | Key/IV Initialization and Running Phases of Warbler                                                                                    | 81   |

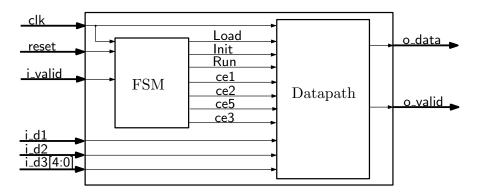

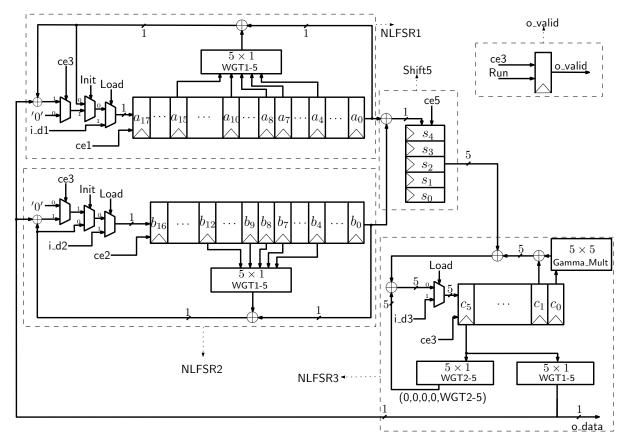

| 5.2 | The Top-level Architecture of Warbler                                                                                                  | 85   |

| 5.3 | Datapath of Warbler for Throughput of 1/5 bpc                                                                                          | 87   |

| 5.4 | Datapath of Warbler for Throughput of 1 bpc                                                                                            | 90   |

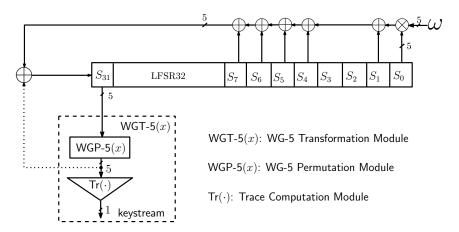

| 6.1 | The Initialization and Running Phases of WG-5                                                                                          | 101  |

| 6.2 | The Top Level Hardware Architecture of WG-5                                                                                            | 102  |

| 6.3 | The Datapath of WG-5                                                                                                                   | 103  |

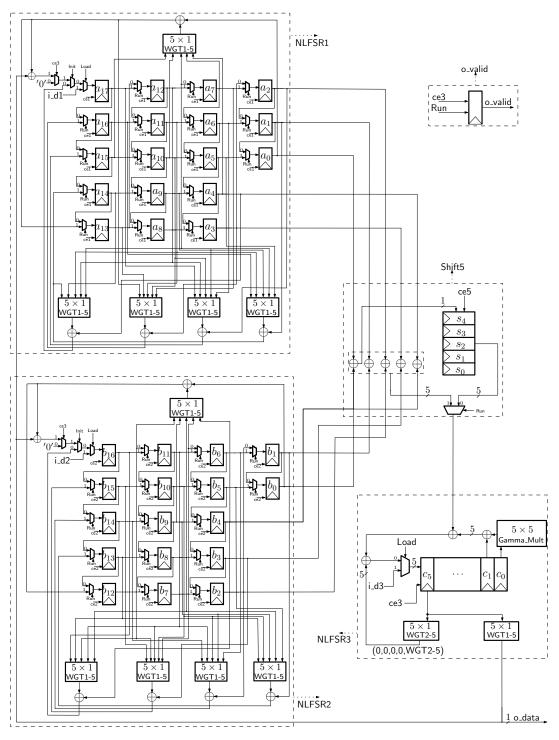

| 6.4 | Hardware Architecture with FSM Reuse for WGLCE                                                                                         | 106  |

| 6.5 | Hardware Architecture without FSM Reuse for WGI CF                                                                                     | 107  |

# **Chapter 1**

# Introduction

In recent years, the Internet of Things (IoT) has become pervasive, with many resource constrained and tiny devices deployed on a large scale and communicating wirelessly with each other and with the Internet at large. Traditional cryptographic primitives, which are designed for desktop computing, do not fit into the constraints of these tiny devices. Therefore, developing security and privacy solutions for these devices and protecting the transmitted and stored data are increasingly important.

## 1.1 Motivation

Among IoT devices, the Radio Frequency Identification (RFID) system is widely used to perform automatic and unique identification of objects [93]. One important advantage of RFID over barcodes is that line-of-sight is not required. Therefore, it is deployed in various applications, such as product tracking, supply chain management, and animal identification [40]. The growth of RFID has been astounding, and the number of RFID tags is expected to grow to 25 billion by 2020 just for retail apparel and shoes with more tags deployed on high value items [4].

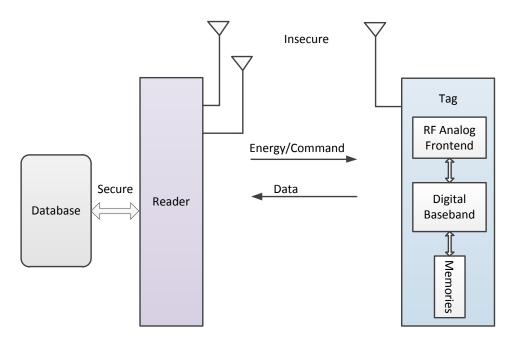

A typical RFID system consists of three components: tags, readers and a back-end database [110, 40, 43]. Each tag is issued with an unique identification number and is attached to an object. Complex tags store information about the object, such as model and serial number, date of production, etc. The readers wirelessly communicate and track these objects via the interrogation process to the tag in order to obtain their data. After that, the readers exchange information about the object with the database through a secure channel. Depending on the power sources of RFID tags, they can be classified into three categories: active, semi-passive, and passive.

Active and semi-passive tags contain batteries. In contrast, passive tags perform computation and communication by using the energy received from the reader's RF electromagnetic signal. We focus on passive RFID systems in this thesis.

The most popular and widely adopted standard for passive RFID systems is the Electronic Product Code (EPC) Class 1 Generation 2 (EPC C1 G2) standard [2, 3], which is also included in the ISO 18000-6 standard. EPC systems operate on the ultra high frequency (UHF) band (860 MHz-960 MHz), the unique identification number is an EPC number, and the read range is around 10 meters. The passive EPC RFID tags are required to be very tiny and inexpensive, *i.e.*, about 5 to 10 cents for each tag, due to large scale deployment [110]. These properties dictate that EPC tags have inherent limited capabilities, such as very limited power consumption, constrained memory and computing capability.

Since the first version of the EPC C1 G2 standard released in 2008 [2], the security and privacy concerns have attracted a lot of attention [104, 59, 9], because there are no cryptographic mechanisms to protect the tags' data. Due to the vulnerabilities of wireless communication between readers and tags, the attacker can easily get the EPC number and access the stored data through an unauthorized reader by eavesdropping, leading to unexpected behaviour, such as malicious tracking of the object and modification of tags' stored data, etc.

Traditional cryptographic primitives which are normally well-suited for desktop computing, such as AES, are often too big and impractical due to the tags' constrained resources. Moreover, public-key cryptography is infeasible for these applications [77]. In general, the well accepted maximum area limit of the security functions for the tags are 2000 GEs (Gate Equivalents) [60, 9, 119, 100], which is around 10% of the total area of an entire tag. However, the smallest available hardware implementation of AES in CMOS 180nm Application Specific Integrated Circuit (ASIC) requires 2400 GEs [82]. In order to overcome this challenge, lightweight cryptography is devised to provide secure, compact, and flexible algorithms and protocols that fit into the constraints of resource constrained devices. The term lightweight is used broadly to mean that an algorithm is suitable for use on a constrained platform. In these lightweight algorithms, tradeoffs are made between security, area/power consumption, and throughput. Generally, a lower security level than AES is often sufficiently enough, because the amount of encrypted data is tiny during the device's lifetime [12]. There are currently no well accepted power consumption and throughput requirements. The power consumption depends on multiple factors, such as activity factor, clock speed, operating voltage, and the adopted CMOS technology. Thus, it is hard to give an upper bound on the allowed power or energy, but it should be kept as small as possible. The minimum throughput requirement relies on the specific applications.

In recent years, a lot of lightweight algorithms were proposed, such as the stream ciphers Trivium [27], Grain [55] and lightweight WG (Welch-Gong) stream ciphers (WG-5 [7], WG-7 [71],

WG-8 [35]); block ciphers TEA [112], XTEA [86], HIGHT [56], SEA [105], PRESENT [17], KATAN and KTANTAN [26], CLEFIA [103], LED [49], PRINCE [18], EPCBC [117], K-LEIN [47], LBlock [113], Piccolo [102], Twine [106], SIMON and SPECK [11] and QTL [68]. In particular, CLEFIA, PRESENT, and Trivium have been adopted by the ISO/IEC Standard 29192. PRESENT-80 and Grain-128 have been adopted by ISO/IEC Standard 29167, which provides the cipher suite for the RFID air interfaces. This cipher suite has been specified in the second version of the EPC C1 G2 standard released in 2013 [3], which includes a security extension framework, such as encryption, authentication, etc. Recently, National Institute of Standards and Technology (NIST) began an effort to standardize lightweight cryptography [5].

According to the aforementioned area, power consumption and throughput requirements, the highly optimized hardware implementations of lightweight cryptography are important for constrained applications. Different cryptographic primitives, such as block ciphers, stream ciphers, and pseudorandom number generators (PRNGs) have different parameters and structures, which affect the hardware implementations and optimizations. Moreover, the hardware performance of the primitive will also influence the parameters and structure selections. As a result, significant emphasis has been given to the hardware implementations in cryptography competition projects, such as stream ciphers in eSTREAM [34], lightweight cryptography in NIST [5], and authenticated encryption candidates in CAESAR [20]. To support multiple security needs, implementing multiple cryptography primitives on a constrained device is non-trivial. For example, integrating a PRNG and an encryption algorithm to EPC tags with minimal cost is challenging.

The main research presented in this thesis is to explore efficient low area/power consumption hardware implementations and optimizations of lightweight cryptography, including lightweight stream cipher, lightweight block cipher, lightweight PRNG, and a lightweight cryptographic engine with multiple security functions. With evaluations of the hardware architectures, the impact on selecting appropriate design parameters for a smaller cipher design is also investigated.

# 1.2 Thesis Organization

The rest of the thesis is organized as follows:

Chapter 2 provides some background and related work. The mathematical background related to finite field, feedback shift register sequences, and the WG transform are firstly reviewed. Then, the related work of lightweight cryptography is provided, and lightweight block ciphers SIMON and SPECK, lightweight stream ciphers Trivium, Grain, and WG are described in detail. We give several efficient hardware implementation techniques, including exploitation of parallelism, clock gating, component reuse and optimizations achieved by choosing appropriate

subfields and different bases representations. Finally, we present the description of the EPC C1 G2 passive RFID system. Additional related work appears in each chapter.

Chapter 3 proposes Simeck, a new family of lightweight block ciphers, which is very suitable for resource constrained devices. Simeck takes advantage of the good components and design ideas of SIMON and SPECK, and it targets low area/power consumption implementations while still keeping a reasonable throughput and maximum frequency. We provide an extensive exploration of different hardware architectures in order to make a balance between area, throughput, and power consumption for SIMON and Simeck in both CMOS 65nm and CMOS 130nm ASICs. We show that it is possible to design a smaller cipher than SIMON in terms of area and power consumption.

Chapter 4 presents the design space exploration of the lightweight stream cipher WG-8 for low-cost FPGA and CMOS 65nm and CMOS 130nm ASICs. We explore four different approaches for the WG transformation module, where one takes advantage of the constant arrays and the other three benefits from the tower constructions of finite field  $\mathbb{F}_{2^8}$  and also efficient basis conversion matrices. Many design options have been explored to make trade-offs in terms of area, power consumption as well as throughput. Consequently, the results for FPGA and ASICs are given, and comparisons with other lightweight stream ciphers are provided.

Chapter 5 evaluates hardware implementations and optimizations of Warbler PRNG in C-MOS 65nm and CMOS 130nm ASICs. We propose an architecture and a standard interface for the implementations of Warbler with throughput of 1 bit per 5 clock cycles (1/5 bpc). More importantly, we also improve the throughput from 1/5 bpc to 1 bpc with a little additional area and power consumption. In addition, the LFSR counter-based design is better than the binary counter-based design in terms of smaller area and lower total power consumption. The comparisons with other PRNGs and lightweight primitives are also given.

Chapter 6 proposes a lightweight cryptographic engine WGLCE for passive RFID systems. WGLCE is a fusion of the Warbler PRNG and the lightweight stream cipher WG-5, which can be easily integrated into the RFID systems. We investigate the rationale and design choices for WGLCE and explore its different hardware architectures and implementations in CMOS 65nm and CMOS 130nm ASICs. Moreover, we provide an interface for its usage. Finally, we compare our results with other lightweight cyptographic engines.

Chapter 7 concludes this thesis and discusses the future potential research directions.

### 1.3 Contributions

The main contributions of this thesis are summarized as follows:

- 1. The Simeck family of lightweight block ciphers.

- The smallest block cipher family with key schedule.

- Improved SIMON's round function by choosing new shift numbers.

- Reduced size of Simon's key schedule by choosing a new LFSR polynomial.

- First published detailed implementation of fully-serialized Feistel architecture.

- 2. The lightweight WG-8 stream cipher.

- A hybrid design architecture for providing parallelism from 1 bit per clock cycle (bpc) to 11 bits per clock cycle.

- Hardware implementation and analysis of constant arrays and three tower field based methods.

- 3. The lightweight Warbler PRNG.

- Detailed and smallest hardware implementations of Warbler.

- Throughput improvement from 1 bit per five clock cycles to 1 bit per clock cycle.

- 4. The lightweight WGLCE cryptographic engine.

- A cryptographic engine which merges WG-5 and Warbler to provide two functionalities: data confidentiality and generating pseudorandom numbers.

- Hardware implementation analysis of different architectures.

- Loading pattern that simplifies the work of the external environment.

- 5. Overall lessons.

- Analysis of effects on area and power consumption by use of clock gating and binary vs LFSR counters.

# Chapter 2

# **Background**

In this chapter, we first recall some mathematical background in Section 2.1. Then, Section 2.2 presents the description of symmetric key cryptography. Section 2.3 reviews a selection of related lightweight symmetric ciphers. In addition, several typical hardware optimization techniques are discussed in Section 2.4. Finally, Section 2.5 describes the system and security issues for a typical passive RFID system.

# 2.1 Mathematical Background

In this section, we review some mathematical background on finite fields, sequences, and the WG transformation. For details, the readers are referred to [45, 44, 52, 80].

#### 2.1.1 Finite Field

Let  $\mathbb{F}_2$  be the finite field with two elements 0 and 1, and  $\mathbb{F}_{2^t}$  be an extension field over the finite field  $\mathbb{F}_2$  with  $2^t$  elements, defined by an irreducible polynomial.

A polynomial f(x) is *irreducible* over  $\mathbb{F}$  if f(x) is only divisible by c or by cf(x), where  $c \in \mathbb{F}$ . An *irreducible* polynomial f(x) of degree t over  $\mathbb{F}_2$  is *primitive polynomial* if  $f(x) \mid (x^{2^t-1}-1)$  but  $f(x) \nmid (x^r-1)$  when  $r < 2^t-1$ .

#### **Polynomial and Normal Bases**

The basis is used to represent the elements in finite field.

**Definition 1** Let  $\alpha$  be a defining element of  $\mathbb{F}_{2^t}$ , which is a root of an irreducible polynomial p(x), i.e.,  $p(\alpha) = 0$ , where p(x) is an irreducible polynomial of degree t over  $\mathbb{F}_2$ . Then, the polynomial basis of  $\mathbb{F}_{2^t}$  is given by  $\{1, \alpha, \alpha^2, \dots, \alpha^{t-1}\}$ . Thus, any element in  $\mathbb{F}_{2^t}$  can be represented as  $A = a_0 + a_1\alpha + a_2\alpha^2 + \dots + a_{t-1}\alpha^{t-1}, a_i \in \mathbb{F}_2$ .

**Definition 2** Let  $\beta \in \mathbb{F}_{2^t}$ , and if the t elements of the set  $\{\beta, \beta^2, \beta^{2^2}, \cdots, \beta^{2^{t-1}}\}$  are linearly independent over  $\mathbb{F}_{2^t}$ , then we call this set as a normal basis of  $\mathbb{F}_{2^t}$  over  $\mathbb{F}_2$ . Thus, every element in  $F_{2^t}$  can be written as  $A = a_0\beta + a_1\beta^2 + a_2\beta^{2^2} + \cdots + a_{t-1}\beta^{2^{t-1}}, a_i \in \mathbb{F}_2$ .

#### **Change of Bases**

For every element  $A \in \mathbb{F}_{2^t}$ , it can be represented using any basis. We choose two bases  $\Psi_1 = \{\alpha_0, \alpha_1, \cdots, \alpha_{t-1}\}$  and  $\Psi_2 = \{\beta_0, \beta_1, \cdots, \beta_{t-1}\}$  of  $\mathbb{F}_{2^t}$ . Assume  $\{a_i\} \in \mathbb{F}_2$  and  $\{b_i\} \in \mathbb{F}_2$  are coordinates of A with respect to  $\Psi_1$  and  $\Psi_2$  respectively. Let  $\mathbf{a} = (a_0, a_1, \cdots, a_{t-1})$  and  $\mathbf{b} = (b_0, b_1, \cdots, b_{t-1})$ , and assume  $\Psi_2^T = \mathbf{C} \cdot \Psi_1^T$ , then,

$$A = \sum_{0}^{t-1} a_i \alpha_i = \mathbf{a} \cdot \Psi_1^T,$$

=

$$\sum_{0}^{t-1} b_i \beta_i = \mathbf{b} \cdot \Psi_2^T = \mathbf{b} \cdot \mathbf{C} \cdot \Psi_1^T.$$

Thus,  $\mathbf{a} = \mathbf{b} \cdot \mathbf{C}$ , where **C** is defined as the conversion matrix.

#### **Subfield**

**Definition 3** Let  $\mathbb{F}_{2^n}$  be a finite field with  $q=2^n$  elements, and  $\mathbb{F}_{2^n}$  contains a subfield  $\mathbb{F}_{2^m}$  if and only if m is a positive divisor of n. An element  $\alpha \in \mathbb{F}_{2^n}$  is in the subfield  $\alpha \in \mathbb{F}_{2^m}$  if and only if  $\alpha^{2^m}=\alpha$ .

Let  $n=m\cdot k$ . Then we may consider  $\mathbb{F}_{2^n}$  as an extension field of  $\mathbb{F}_{2^m}$ . Thus, an element of  $\mathbb{F}_{2^n}$  (i.e.,  $A\in\mathbb{F}_{2^n}$ ) can be expressed as a linear combination of elements in  $\mathbb{F}_{2^m}$  based on a basis with k elements. Assume  $\{\gamma_0,\gamma_1,\cdots,\gamma_{k-1}\}$  is a basis of  $\mathbb{F}_{2^n}$  over  $\mathbb{F}_{2^m}$ , then we have  $A=\sum_0^{k-1}a_i\gamma_i,a_i\in\mathbb{F}_{2^m}$ .

#### **Trace**

**Definition 4** Let  $x \in \mathbb{F}_{2^t}$ , and the trace function for x from  $\mathbb{F}_{2^t}$  to  $\mathbb{F}_2$  is defined by:  $Trace(x) = x + x^2 + x^{2^2} + \cdots + x^{2^{t-1}}$ . For  $\alpha \in \mathbb{F}_{2^t}$ , we simply denote it as  $Tr(\alpha)$ .

**Theorem 1** The trace function satisfies the following properties.

i.

$$Tr(x+y) = Tr(x) + Tr(y)$$

for all  $x, y \in \mathbb{F}_{2^t}$ .

ii.

$$Tr(cx) = cTr(x)$$

for all  $c \in \mathbb{F}_2$ , and  $x \in \mathbb{F}_{2^t}$ .

iii.

$$Tr(c) = tc \pmod{2}$$

for  $c \in \mathbb{F}_2$ .

iv.

$$Tr(x^{2^i}) = Tr(x)^{2^i} = Tr(x)$$

for any positive i.

### 2.1.2 Feedback Shift Register Sequences

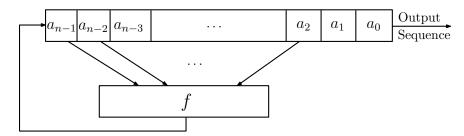

Feedback shift registers (FSRs) are common building block for cryptography. A binary sequence  $\{a_i\}_{i\geq 0}$ ,  $a_i\in \mathbb{F}_2$  can be generated by an *n*-stage FSR, as shown in Figure 2.1. The recursive

Figure 2.1: Feedback Shift Register

relation of the FSR is defined as

$$a_{n+k} = f(a_k, a_{k+1}, \cdots, a_{n+k-1}), k > 0,$$

where  $(a_0, a_1, \dots, a_{n-1})$  is an *initial state* and any n consecutive terms of the sequence represent a state of the shift register, *i.e.*,  $S_k = (a_k, a_{k+1}, \dots, a_{n+k-1})$  is the k-th state of the shift register.

The sequence  $\{a_i\}_{i\geq 0}$  is called a linear feedback shift register (LFSR) sequence if the function f is linear, i.e., it is of the form:

$$f(x_0, x_1, \dots, x_{n-1}) = c_0 x_0 + c_1 x_1 + \dots + c_{n-1} x_{n-1}, \ c_i \in \mathbb{F}_2.$$

Otherwise, it is called a nonlinear feedback shift register (NLFSR) sequence.

The internal state of the FSR can be a non-binary variable, for example, it takes from  $\mathbb{F}_{2^t}$ , and in this case, a sequence generated by the FSR is a non-binary sequence. In other words, the k-th state of the FSR is  $S_k = (a_k, a_{k+1}, \cdots, a_{n+k-1}), a_i \in \mathbb{F}_{2^t}$ . The coefficients of f are also non-binary, i.e.,  $c_i \in \mathbb{F}_{2^t}$ , in order to generate the corresponding feedback for the FSR.

**Definition 5** The sequence  $\{a_i\}_{i\geq 0}$  is called a periodic sequence with period T if  $a_i=a_{i+T}$ ,  $i\geq 0$ .

**Definition 6** Let  $\mathbf{a} = \{a_i\}_{i\geq 0}$  be a periodic binary sequence with period T. The autocorrelation function of  $\mathbf{a}$ , denoted by  $C_{\mathbf{a}}(\tau)$ , is defined as

$$C_{\mathbf{a}}(\tau) = \sum_{i=0}^{T-1} (-1)^{a_{i+\tau}+a_i}.$$

**Definition 7** A binary sequence with period  $2^n - 1$  generated by an n-stage LFSR is called an m-sequence.

**Definition 8** The linear span or linear complexity of a sequence is the length of the shortest LFSR that can generate the entire sequence.

**Definition 9** A binary sequence with period  $2^n - 1$  is called a span n sequence if each non-zero n-tuple occurs exactly once in one period.

#### 2.1.3 The WG Transformation

Let  $t \not\equiv 0 \mod 3$ ,  $3k \equiv 1 \mod t$ , and  $h(x) = x + x^{q_1} + x^{q_2} + x^{q_3} + x^{q_4}$ , where  $q_i$  are given by

$$q_1 = 2^k + 1,$$

$$q_2 = 2^{2k} + 2^k + 1,$$

$$q_3 = 2^{2k} - 2^k + 1,$$

$$q_4 = 2^{2k} + 2^k - 1.$$

Then the function  $\mathsf{WGP}(\cdot): \mathbb{F}_{2^t} \to \mathbb{F}_{2^t}$  given by

$$WGP(x) = h(x+1) + 1$$

is called the Welch-Gong (WG) permutation and the function  $\mathsf{WGT}(\cdot):\mathbb{F}_{2^t}\to\mathbb{F}_2$  given by

$$WGT(x^d) = Tr(WGP(x^d))$$

is known as the Welch-Gong (WG) transformation with decimation d, where d is coprime to  $2^t - 1$  [46].

## 2.2 Symmetric Key Cryptography

In symmetric key cryptography, a secret key is shared between the sender and the receiver. Public key cryptography uses two different keys for encryption and decryption. Public key cryptography involves intensive computations, and it is not feasible, at current research stage, for EPC tags due to the area constraint [77]. The security service of confidentiality can be achieved by ciphers, and authentication can be achieved by challenge/response based protocol, where random numbers are used as challenges. In order to meet these requirements, we mainly focus on the block cipher, stream cipher, and pseudorandom number generator in our following work, therefore we give an overview of them.

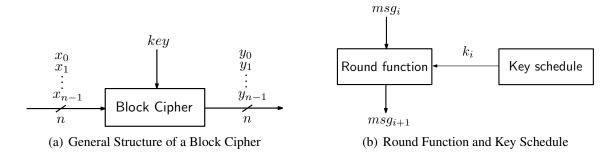

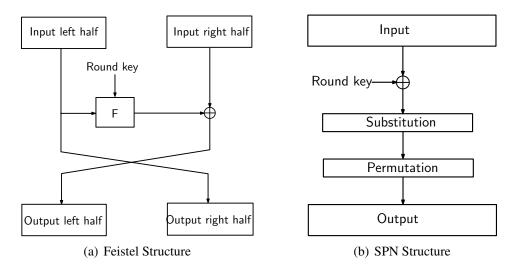

**Block cipher:** A block cipher encrypts an n-bit block of plaintext with a secret key and outputs an n-bit block of ciphertext at a time. Figure 2.2(a) shows the general structure of a block cipher. In general, the block cipher includes two parts: round function and key schedule, as shown in Figure 2.2(b). The round function is iterated multiple times (called round number), in order to increase the unpredictability between the plaintext and ciphertext [23]. The key schedule is used to provide round keys  $(k_i)$  for the round function in each round. There are two common architectures for round functions: the Feistel structure and substitution permutation network (SPN) structure, as shown in Figure 2.3. In the Feistel structure, the input message for each round is split into two parts: left half part and right half part. The right half part of the output message directly comes from the input left part and the output left part equals the XORed result of input right half and the output of the function F with inputs of round key and input left half. For the SPN structure, each round function includes adding round key, substitution, and permutation layers. The typical cipher of Feistel structure is DES, and that of SPN structure is AES.

Figure 2.2: Block Cipher

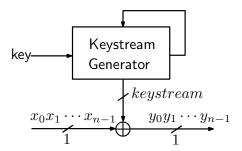

**Stream cipher**: A stream cipher encrypts each bit of plaintext individually and the general structure of a stream cipher is given in Figure 2.4. Each bit of the ciphertext is obtained by

Figure 2.3: Block Cipher Structures

conducting a bitwise exclusive-or (XOR) operation of each bit of the plaintext and a key bit stream. The key bit stream is implemented by a pseudorandom number generator using a secret key as input [23].

Figure 2.4: General Structure of a Stream Cipher

**Pseudorandom number generator**: PRNG is also known as deterministic random number generator, which is constructed from a deterministic function with a secret key, and its output has good statistical properties and approximates a sequence of truly random numbers [89].

## 2.3 Lightweight Cryptography

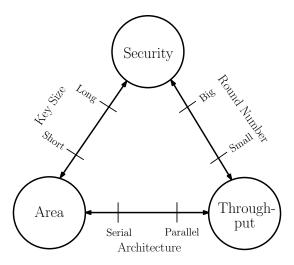

The goal of lightweight cryptography is to achieve a balance of the tradeoffs between security, area and throughput. To illustrate it in a block cipher, as depicted in Figure 2.5, the key size

Figure 2.5: Design Tradeoffs between Security, Area, and Throughput

provides a tradeoff between security and area, the round number provides a tradeoff between security and throughput, and the implementation architecture provides the area and throughput tradeoff. In general, it is easy to optimize two of them, but it is difficult to consider all of them [93, 62, 63].

Generally, the proposals of lightweight symmetric ciphers can be divided into three approaches [93]. The first approach involves optimized and compact hardware implementations of standardized algorithms, e.g., compact AES implementations [82, 50, 39, 38]. The second method leverages the slight modification of a well-studied cipher, such as DESXL [94], a lightweight variant of DES. Finally, the third method is to design new ciphers with the goal of having low hardware implementation costs.

Recent proposals include lightweight block ciphers TEA [112], XTEA [86], HIGHT [56], SEA [105], PRESENT [17], KATAN and KTANTAN [26], CLEFIA [103], LED [49], PRINCE [18], EPCBC [117], KLEIN [47], LBlock [113], and Piccolo [102], Twine [106], and the more recent SIMON and SPECK [11]. There exist also some lightweight stream ciphers, such as Trivium [27], Grain [55] and lightweight WG (Welch-Gong) stream ciphers (WG-5 [7], WG-7 [71], WG-8 [35]). Additionally, several surveys of recently published lightweight cryptographic implementations can be found in [29, 75, 66]. In particular, lightweight ciphers have attracted a lot of

attention from industry. CLEFIA, PRESENT, and Trivium have been adopted by the ISO/IEC Standard 29192. PRESENT-80 and Grain-128 have been adopted by ISO/IEC Standard 29167, which provides the cipher suites for the RFID air interfaces.

In this section, we give a review of the lightweight block ciphers SIMON and SPECK which are related to our cipher Simeck, lightweight stream ciphers Trivium, Grain and WG.

### 2.3.1 Lightweight Block Ciphers

SIMON and SPECK are two lightweight block cipher families, designed by the NSA's researchers in 2013 [11, 13, 12]. Each of SIMON and SPECK contains ten instances with various block sizes and key sizes. SIMON and SPECK offer excellent performance on both hardware and software platforms, such as ASIC, FPGA, and 4/8/16/32-bit microcontrollers, and are designed to perform well across the full spectrum of lightweight applications [11]. SIMON is optimized for hardware implementations, and SPECK is tuned for optimal performance in software. The round functions of SIMON and SPECK are based on the Feistel structure.

The following notations are used to describe SIMON, SPECK and our Simeck in Chapter 3.

- $-x \ll c$  and  $x \gg c$  denote the cyclic shift of x to the left and right by c bits respectively.

- $-x \odot y$  is the bitwise AND of x and y.

- $-x \oplus y$  is the exclusive-or (XOR) of x and y.

- $-x \boxplus y$  is the integer addition modular  $2^n$  of x and y, where n is the word size.

The SIMON and SPECK block ciphers with n-bit word size (2n-bit block size), and m-word (mn-bit) key is denoted as SIMON2n/mn and SPECK2n/mn. There are ten instances for each of SIMON and SPECK family for the combination of n and m, where  $n \in \{16, 24, 32, 48, 64\}$  and  $m \in \{2, 3, 4\}$ . The details of them are listed in Table 2.1.

In this thesis, we only consider SIMON2n/mn and SPECK2n/mn with word size n equals 16, 24, and 32, the key words m equals 4 here, in order to be consistent with our Simeck in Chapter 3. They are SIMON32/64, SIMON48/96, SIMON64/128 and SPECK32/64, SPECK48/96, SPECK64/128.

Table 2.1: Ten SIMON and SPECK Instances

| SIMON        | SPECK        |

|--------------|--------------|

| SIMON32/64   | SPECK32/64   |

| SIMON48/72   | SPECK48/72   |

| SIMON48/96   | SPECK48/96   |

| SIMON64/96   | SPECK64/96   |

| SIMON64/128  | SPECK64/128  |

| SIMON96/96   | SPECK96/96   |

| SIMON96/144  | SPECK96/144  |

| SIMON128/128 | SPECK128/128 |

| SIMON128/192 | SPECK128/192 |

| SIMON128/256 | SPECK128/256 |

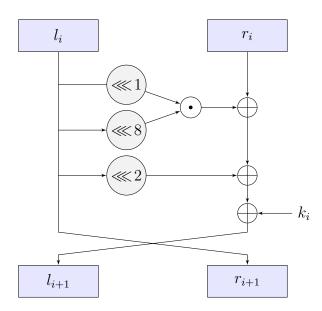

Figure 2.6: The Round Function of SIMON

#### **SIMON**

The *i-th* round function of SIMON (as shown in Figure 2.6) is a two-stage Feistel map  $R_{k_i}$  which is defined by

$$(l_{i+1}, r_{i+1}) = R_{k_i}(l_i, r_i) = (r_i \oplus f(l_i) \oplus k_i, l_i),$$

where  $f(l_i) = ((l_i \ll 1) \odot (l_i \ll 8)) \oplus (l_i \ll 2)$ ,  $k_i$  is the round key, and  $(l_i, r_i)$ ,  $(l_{i+1}, r_{i+1})$  are two internal words in the i-th and (i+1)-th rounds respectively.  $l_i$  and  $r_i$  are the left part and right part of the internal words respectively.  $k_i$  is generated from the key schedule and  $0 \le i \le T - 1$ , where T is the number of rounds. The number of rounds for different SIMON instances are given in Table 2.2.

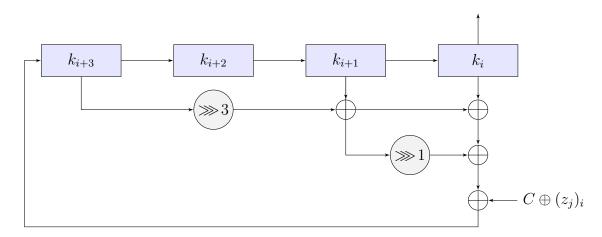

The key schedule (expansion) of SIMON is depicted in Figure 2.7. The round keys for the first four rounds  $(k_0, k_1, k_2, k_3)$  are the four key words, *i.e.*, the input key, of the key schedule, which is used to generate other round keys. The other round keys are generated by

$$k_{i+4} = C \oplus (z_i)_i \oplus k_i \oplus [k_{i+3} \gg 3 \oplus k_{i+1}] \oplus [(k_{i+3} \gg 3 \oplus k_{i+1}) \gg 1],$$

Figure 2.7: The Key Expansion of SIMON

Table 2.2: SIMON and SPECK Parameters

| block | key  | word | SIMON          |        | SPECK    |          |        |  |

|-------|------|------|----------------|--------|----------|----------|--------|--|

| size  | size | size | constant       | rounds | rotation | rotation | rounds |  |

| 2n    | 4n   | n    | sequence $z_j$ | T      | $\alpha$ | $\beta$  | T      |  |

| 32    | 64   | 16   | $z_0$          | 32     | 7        | 2        | 22     |  |

| 48    | 96   | 24   | $z_1$          | 36     | 8        | 3        | 23     |  |

| 64    | 128  | 32   | $z_2$          | 44     | 8        | 3        | 27     |  |

#### **SPECK**

Figure 2.8: The Round Function of SPECK

The *i-th* round function of SPECK, shown in Figure 2.8, is defined by

$$(l_{i+1},r_{i+1})=R_{k_i}(l_i,r_i)=((l_i\ggg\alpha\boxplus r_i)\oplus k_i,r_i\lll\beta\oplus (l_i\ggg\alpha\boxplus r_i)\oplus k_i),$$

where  $0 \le i \le T-1$ . The number of rounds T and the rotations  $\alpha$  and  $\beta$  are different for each instance and they are listed in Table 2.2.

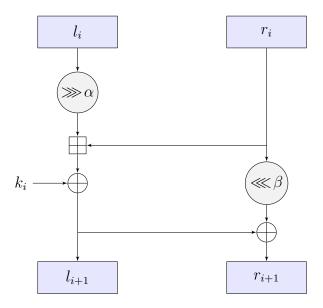

The key schedule reuses the round function to generate the round key  $k_i$ , as shown in Figure 2.9. The four key words, which are taken from the input key, of SPECK are  $(t_2, t_1, t_0, k_0)$ ,

where  $k_0$  is the first round key. The other round keys are generated by