# Electron transport in semiconducting nanowires and quantum dots

by

Gregory Holloway

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Physics (Quantum Information)

Waterloo, Ontario, Canada, 2017

© Gregory Holloway 2017

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Abstract

Single electrons confined in electrostatic quantum dots are a promising platform for realizing spin based quantum information processing. In this scheme, the spin of each electron is encoded as a qubit, and can be manipulated and measured by modulating the gate voltages defining each dot. Since each qubit is realized in a single quantum dot, one could imagine scaling up this system by placing many quantum dots together in a tightly packed array. To be truly scalable each qubit must exhibit minimal variation, such that their behavior is consistent across the entire device. Transport through these quantum dots must therefore be explored in detail, to determine the source of these variations and design strategies to combat their effects.

In this thesis a study of the transport properties of InAs nanowires and Si quantum dots is presented. In both systems the close proximity of the conduction electrons to defect-prone surfaces or interfaces causes them to be very sensitive to the physical properties of these regions. Through cryogenic transport measurements, and the development of relevant physical models, the effects of surface states, oxide charge traps, and interface defects are explored. In general these defects possess a finite charge, which modifies the electrostatic potential and alters electron transport. These additional changes to the electrostatic potential are detrimental for spin based quantum information processing, which requires precise control of this potential. In addition, the severity of each of these effects can be different in each device, leading to variation which limits scalability. By studying these effects we aim to better understand their properties and origins, such that they can be mitigated.

Static defects, such as surface states, are found to be a dominant source of scattering that limits mobility. In InAs nanowires, we find that these effects can be removed through growth of an epitaxial shell that physically separates the nanowire surface from the conducting core. Dynamic defects on the other hand, lead to charge noise that shifts the potential causing instability. This noise originates from charge traps in close proximity to the conduction channel. For nanowires, the native oxide that forms at the surface is a likely location for these traps to occur. Through removal of this oxide and replacement with a defect free dielectric shell, greatly improved stability is observed. To test the viability of these fabrication techniques, nanowires treated with the most promising surface processes are used to fabricate top-gated nanowire field effect transistors. These devices are used to realize electrostatically defined double quantum dots, which show well controlled transport properties and minimal charge noise.

In Si, electron transport is studied in a pair of capacitively coupled metal-oxide-semiconductor quantum dots. Here, the capacitive coupling is used implement charge sensing, such that the electrostatic potential of one dot can be measured down to the single electron regime. The pair of dots is also used to implement a novel memristive system which demonstrates current hysteresis. This shows the versatility of this system and its capability to control individual electrons, similar to the requirements needed to implement spin based quantum information processing.

#### Acknowledgements

I am deeply indebted to the financial support provided for me from the National Science and Engineering Research Council, the Ontario government, the University of Waterloo, the Waterloo Institute for Nanotechnology, and the Institute for Quantum Computing.

Special thanks to my PhD advisor, Prof. Jonathan Baugh, who provided never-ending support during my graduate studies. The opportunities he has provided me have made for a great graduate experience.

I express acknowledgment to my committee members, Profs. Robert Hill, James Martin, and Pavle Radovanovic for their helpful comments and useful feedback on my research. I am thankful to Prof. Simon Watkins for being my external examiner.

I feel deep gratitude towards Prof. Ray Lapierre and his group at McMaster University who provided all of the nanowires used in this thesis. Thank you to Dr. Chris Haapamaki for growing the wires, and Dr. Shahram Tavakoli for technical assistance with the MBE.

I am sincerely thankful to Dr. Brian Goddard, Dr. Nathan Nelson Fitz-Patrick, and the rest of the QNC nanofab team for their help with fabrication. I had minimal cleanroom experience when I started, so I owe much of my knowledge to their thorough training and assistance.

Many thanks to Kaveh Gharavi, Kyle Willick, Dr. Francois Sfigakis, and the other members of the Coherent Spintronics Group for their collaborations, discussions, and support.

A sincere thank you to my family for supporting me throughout my life.

Finally, thank you to Jenn for helping me enjoy all that life has to offer, and Sadie for being a true companion and constant friend.

#### Dedication

To my parents who taught me to use my mind, to follow my heart

## **Table of Contents**

| Li | st of | Tables                                                 | xi        |

|----|-------|--------------------------------------------------------|-----------|

| Li | st of | Figures                                                | xii       |

| 1  | Intr  | oduction                                               | 1         |

|    | 1.1   | Introduction                                           | 1         |

|    | 1.2   | Outline of the thesis                                  | 3         |

|    | 1.3   | Background                                             | 4         |

|    |       | 1.3.1 Nanowire transport                               | 5         |

|    |       | 1.3.2 Quantum dot transport                            | 9         |

|    |       | 1.3.3 Double quantum dot transport                     | 14        |

| 2  | Tem   | perature-dependent electron mobility in InAs nanowires | <b>21</b> |

|    | 2.1   | Introduction                                           | 21        |

|    | 2.2   | Nanowire growth by gas-source MBE                      | 23        |

|    | 2.3   | Mobility in field-effect transistors                   | 25        |

|    | 2.4   | Results                                                | 27        |

|    |       | 2.4.1 Bare InAs nanowires                              | 27        |

|    |       | 2.4.2 $InAs/In_{0.8}Al_{0.2}As$ core/shell nanowires   | 33        |

|    | 2.5   | Numerical modeling                                     | 35        |

|    | 2.6   | Structural defects and mobility                        | 41        |

|   | 2.7 | Discussion                                                                        | 43 |

|---|-----|-----------------------------------------------------------------------------------|----|

|   | 2.8 | Conclusion                                                                        | 44 |

| 3 | Tra | pped charge dynamics in InAs nanowires                                            | 46 |

|   | 3.1 | Introduction                                                                      | 46 |

|   | 3.2 | Methods                                                                           | 47 |

|   | 3.3 | Trapped charge dynamics                                                           | 48 |

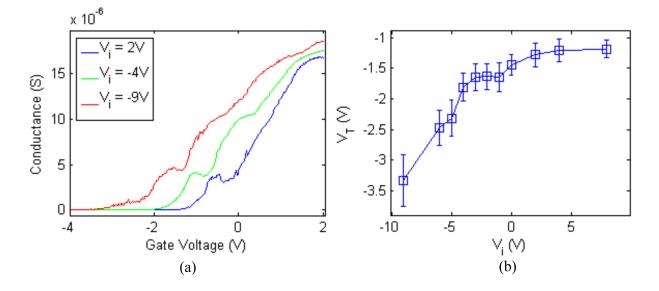

|   | 3.4 | Hysteretic behaviour                                                              | 52 |

|   | 3.5 | Conclusion                                                                        | 54 |

| 4 |     | gnetoconductance signatures of subband structure in semiconductor<br>owires       | 55 |

|   | 4.1 | Introduction                                                                      | 55 |

|   | 4.2 | Model                                                                             | 58 |

|   | 4.3 | Results                                                                           | 59 |

|   |     | 4.3.1 Theory                                                                      | 59 |

|   |     | 4.3.2 Experiment                                                                  | 62 |

|   | 4.4 | Conclusion                                                                        | 68 |

| 5 |     | ctrical characterization of chemical and dielectric passivation of InAs<br>owires | 70 |

|   | 5.1 | Introduction                                                                      | 70 |

|   | 5.2 | Experimental Details                                                              | 71 |

|   | 5.3 | Results                                                                           | 76 |

|   | 5.4 | Discussion                                                                        | 84 |

|   | 5.5 | Conclusion                                                                        | 85 |

| 6 | Si q  | uantum dots                                                                                                                             | 86 |

|---|-------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 6.1   | Introduction                                                                                                                            | 86 |

|   | 6.2   | Experimental details                                                                                                                    | 87 |

|   | 6.3   | Results                                                                                                                                 | 89 |

|   |       | 6.3.1 Single dot transport                                                                                                              | 89 |

|   |       | 6.3.2 Charge sensing                                                                                                                    | 89 |

|   |       | 6.3.3 Memristor                                                                                                                         | 91 |

|   | 6.4   | Conclusion                                                                                                                              | 97 |

| 7 | Con   | nclusions and outlook                                                                                                                   | 99 |

|   | 7.1   | Conclusions                                                                                                                             | 99 |

|   | 7.2   | Outlook and future                                                                                                                      | 02 |

|   |       | 7.2.1 Fast charge sensing                                                                                                               | 02 |

|   |       | 7.2.2 Long distance spin coupling $\ldots \ldots 1$ | 03 |

|   |       | 7.2.3 Error correction                                                                                                                  | 03 |

| R | efere | nces 10                                                                                                                                 | 05 |

| A | PPE   | NDICES 1                                                                                                                                | 19 |

| A | Fab   | rication 1:                                                                                                                             | 20 |

|   | A.1   | Si quantum dots                                                                                                                         | 20 |

|   | A.2   | Nanowire top-gated field effect transistors                                                                                             | 22 |

|   | A.3   | Photolithography                                                                                                                        | 23 |

|   | A.4   | Liftoff                                                                                                                                 | 24 |

|   | A.5   | Metal deposition                                                                                                                        | 26 |

|   | A.6   | Dry etching                                                                                                                             | 27 |

|   | A.7   | Aluminum gate oxidation                                                                                                                 | 29 |

|   | A.8   | Wet etching                                                                                                                             | 29 |

|   | A.9  | Nanowire chemical passivation                  | 130 |

|---|------|------------------------------------------------|-----|

|   | A.10 | Nanowire deposition                            | 131 |

|   | A.11 | Nanowire location                              | 132 |

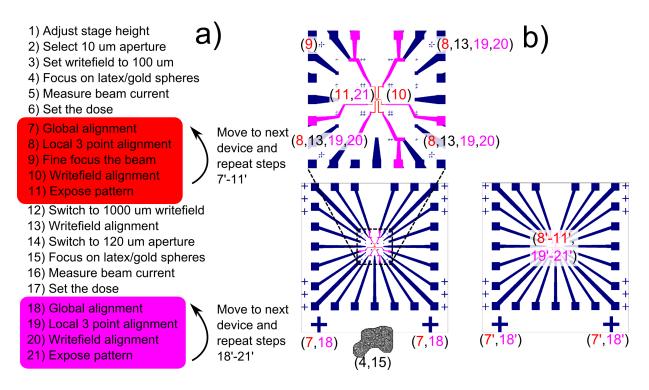

|   | A.12 | Pelectron beam lithography (EBL)               | 133 |

|   |      | A.12.1 Overview                                | 133 |

|   |      | A.12.2 Designing a pattern                     | 135 |

|   |      | A.12.3 Setup and focus                         | 135 |

|   |      | A.12.4 Set the dose: steps 6 and 17 $\ldots$   | 137 |

|   |      | A.12.5 Global alignment: steps 7 and 18        | 137 |

|   |      | A.12.6 Local 3 point alignment: steps 8 and 19 | 137 |

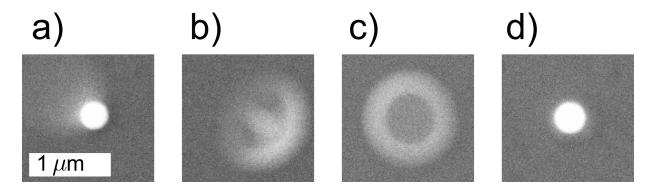

|   |      | A.12.7 Fine focus: step 9                      | 139 |

|   |      | A.12.8 Writefield alignment                    | 140 |

|   |      | A.12.9 Expose the pattern: steps 11 and 21     | 141 |

|   |      | A.12.10Develop                                 | 141 |

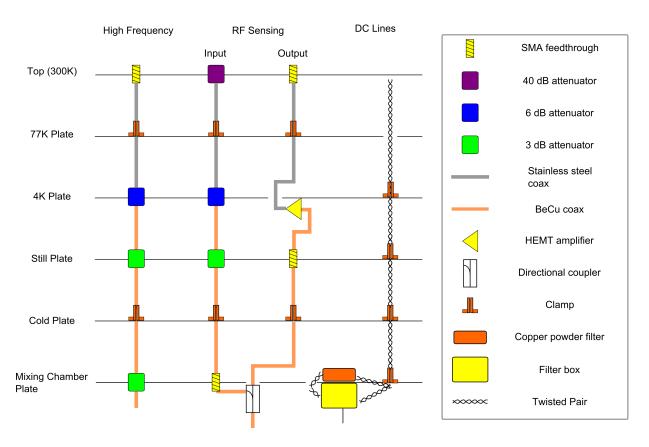

| В | Mea  | asurement setup                                | 142 |

|   | B.1  | Introduction                                   | 142 |

|   | B.2  | Voltage source                                 | 142 |

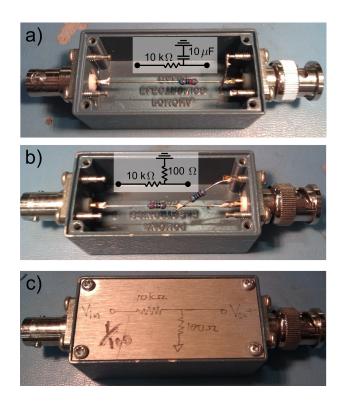

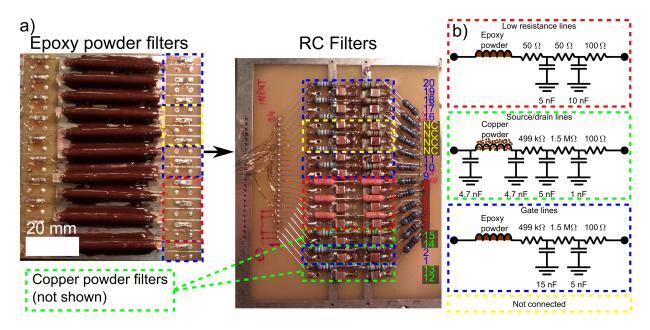

|   | B.3  | Passive filters                                | 143 |

|   | B.4  | Inductively coupled noise                      | 146 |

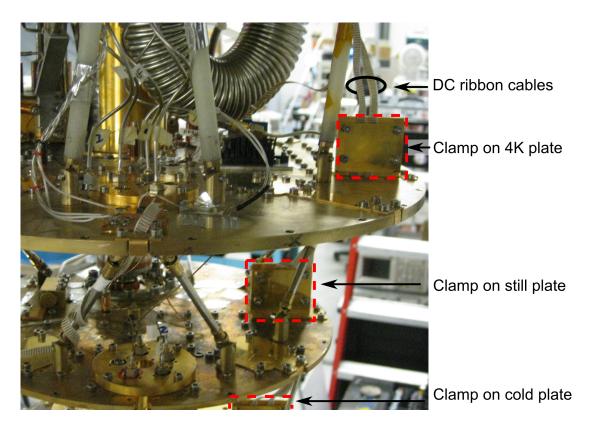

|   | B.5  | Thermalization                                 | 147 |

# List of Tables

| 2.1 | Dimensions and estimated capacitances of various InAs nanowires                                | 28  |

|-----|------------------------------------------------------------------------------------------------|-----|

| A.1 | Rough estimates for the minimum feature size, dose, and step size when performing EBL at 25 kV | 135 |

# List of Figures

| 1.1  | Experimental and simulated current through an InAs nanowire at 20 K, with a bias of 1 mV.                         | 7  |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Simulated current at 20 K through a single delta function potential barrier                                       | 9  |

| 1.3  | Simulated current at 1 K through two delta function potentials                                                    | 10 |

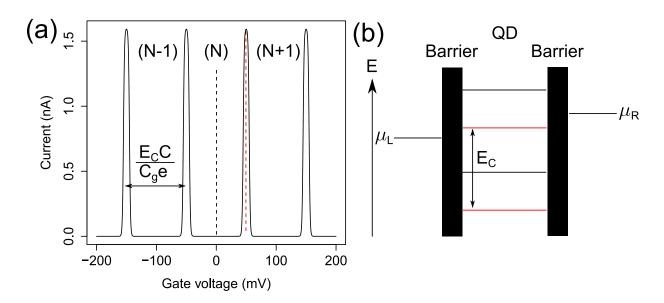

| 1.4  | Quantum dot bias dependence                                                                                       | 12 |

| 1.5  | Quantum dot gate dependence                                                                                       | 13 |

| 1.6  | Simulated current through a quantum dot showing Coulomb diamond struc-<br>ture                                    | 15 |

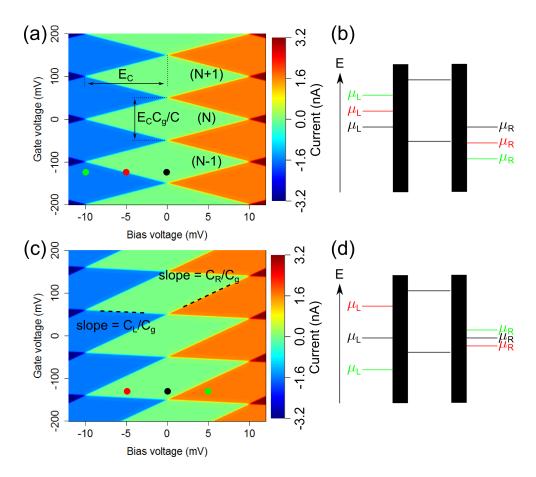

| 1.7  | Schematic of transport through a double quantum dot                                                               | 16 |

| 1.8  | Simulated current through a double quantum dot with different interdot couplings                                  | 17 |

| 1.9  | Double quantum dot stability diagrams with finite cross capacitance and bias                                      | 18 |

| 1.10 | Bias dependence of current through a double quantum dot $\ldots \ldots \ldots$                                    | 19 |

| 1.11 | Spin blockade in a double quantum dot                                                                             | 20 |

| 2.1  | Bright-field TEM images of an InAs nanowire grown by gas source molecular beam epitaxy.                           | 23 |

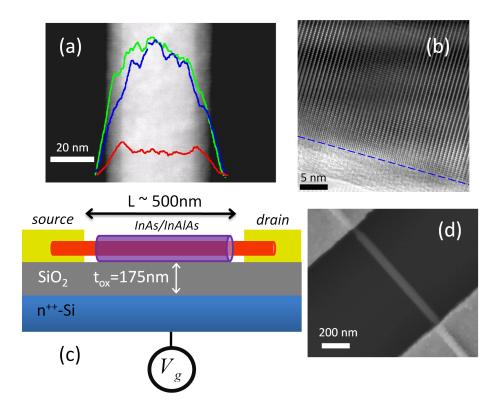

| 2.2  | TEM image and device schematic of a $InAs/In_{0.8}Al_{0.2}As$ core/shell nanowire field effect transistor.        | 25 |

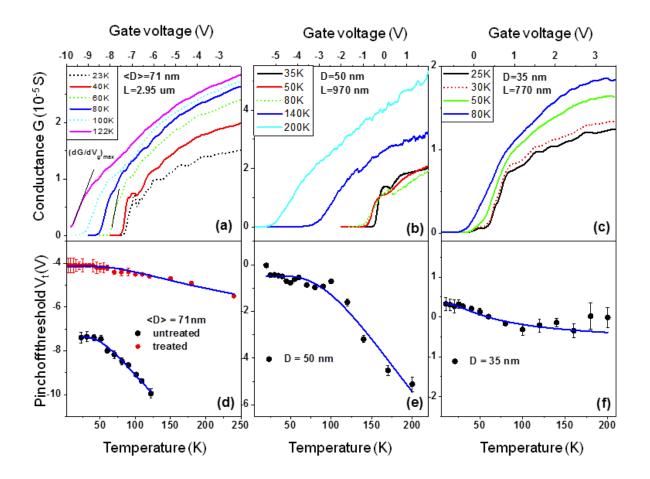

| 2.3  | Transconductance and threshold voltage as a function of temperature for<br>InAs nanowire field effect transistors | 26 |

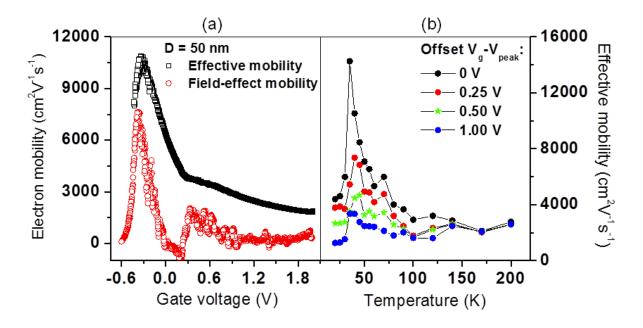

| 2.4  | Field effect, and effective mobility of an InAs nanowire at 40 K                                                  | 29 |

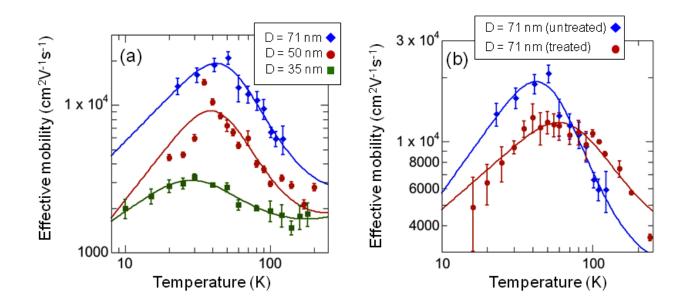

| 2.5  | Effective mobility in InAs nanowires as a function of temperature                                                                      | 30            |

|------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 2.6  | Conductance signatures of charge localization in an InAs nanowire                                                                      | 31            |

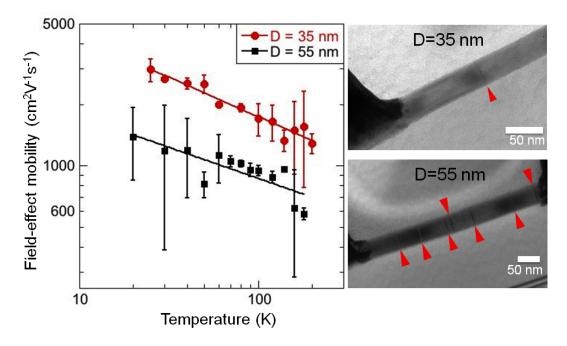

| 2.7  | $\label{eq:links} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                 | 34            |

| 2.8  | Measured carrier concentration as a function of temperature for bare InAs nanowires and core/shell $InAs/In_{0.8}Al_{0.2}As$ nanowires | 36            |

| 2.9  | Simulated surface donor density and Fermi wavenumber used to calculated scattering in InAs nanowires                                   | 37            |

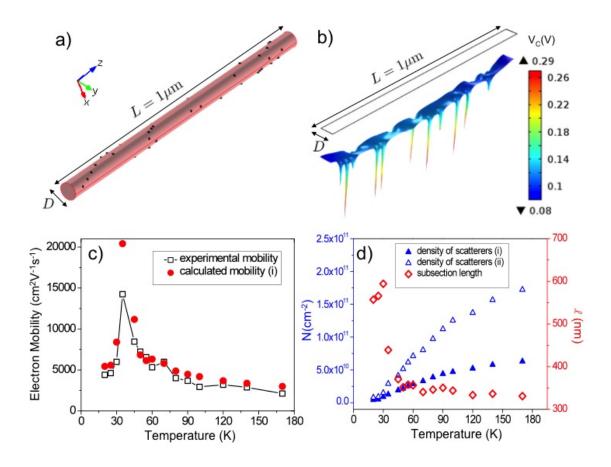

| 2.10 | Model of temperature dependent mobility due to ionized impurity scattering in InAs nanowires                                           | 40            |

| 2.11 | Correlation between structural defects and mobility in InAs nanowires                                                                  | 42            |

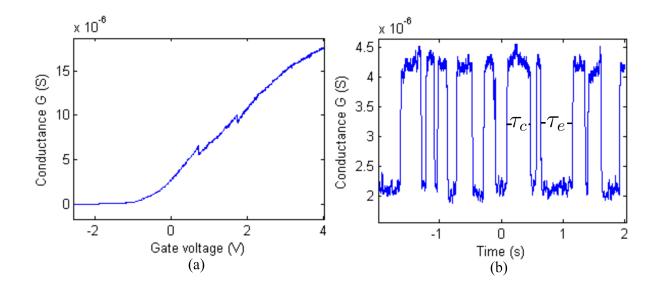

| 3.1  | Charge jumps and random telegraph noise in InAs nanowire field effect transistors                                                      | 48            |

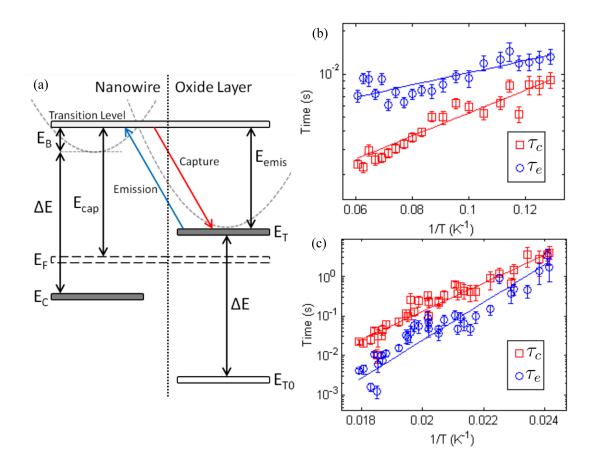

| 3.2  | A model of trap dynamics in InAs nanowires                                                                                             | 50            |

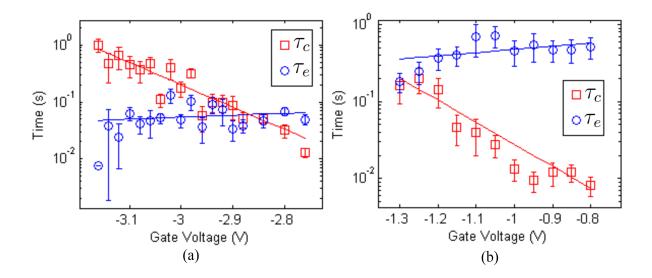

| 3.3  | Gate voltage dependence of charge trap capture and emission times                                                                      | 52            |

| 3.4  | Charge trap induced shifts in transconductance curves                                                                                  | 53            |

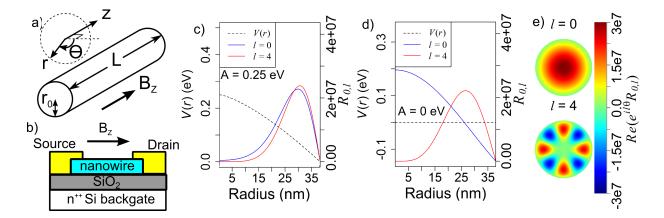

| 4.1  | Model of transverse subband induced magnetoconductance in a cylindrical nanowire.                                                      | 57            |

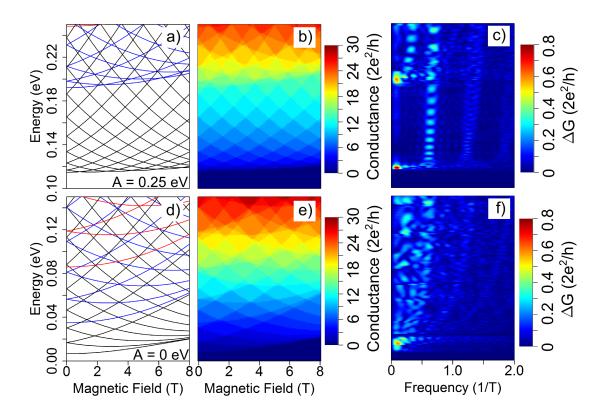

| 4.2  | Simulated magnetoconductance in an InAs nanowire for differing amounts of surface band bending                                         | 61            |

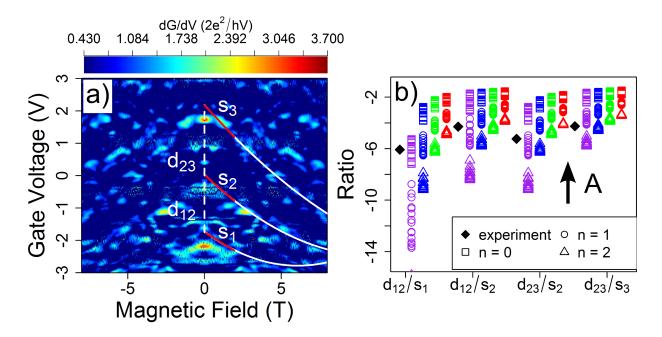

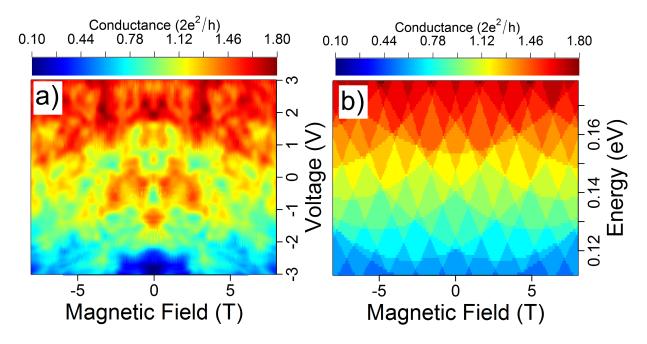

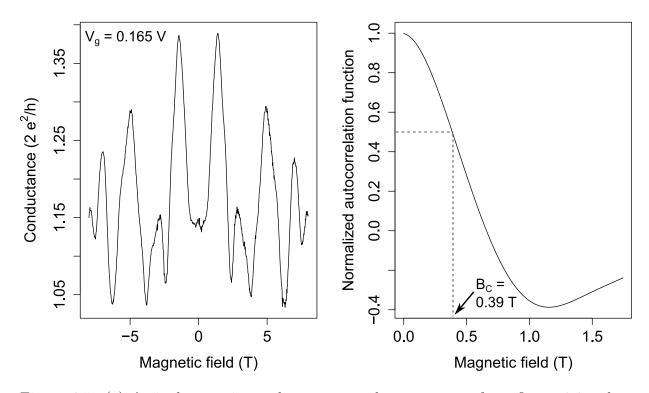

| 4.3  | Extraction of parameters used to fit experimental data to the model of magnetoconductance                                              | 64            |

| 4.4  | Comparison between experimental and simulated magnetoconductance in<br>an InAs nanowire field effect transistor                        | 65            |

| 4.5  | Extraction of phase coherence length using the autocorrelation function                                                                | 67            |

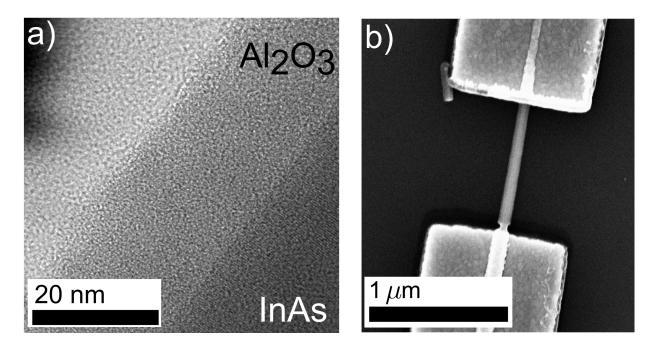

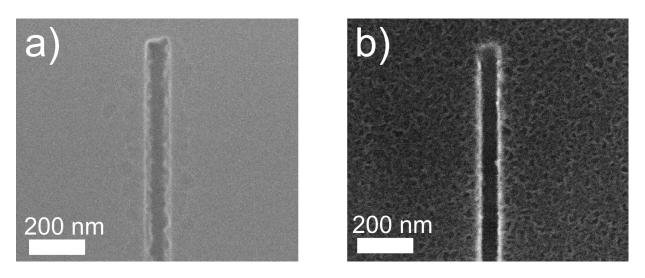

| 5.1  | TEM and SEM images of InAs nanowires with dielectric shells                                                                            | 74            |

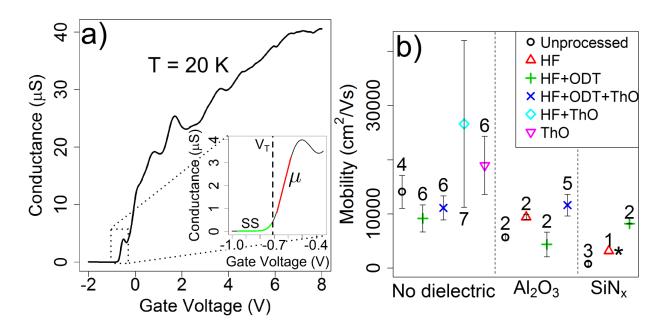

| 5.2  | Effect of surface passivation on InAs nanowire mobility                                                                                | 75            |

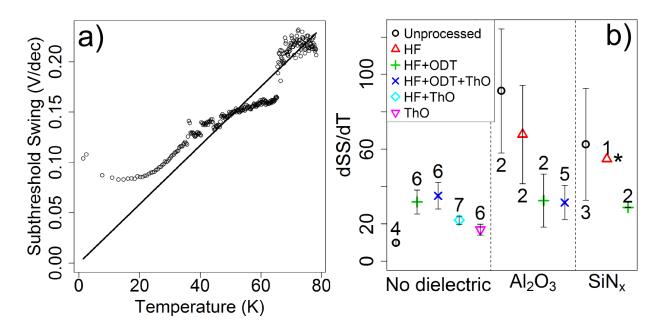

| 5.3  | Subthreshold swing for different surface processing techniques in InAs nanowire                                                        | <b>s</b> . 78 |

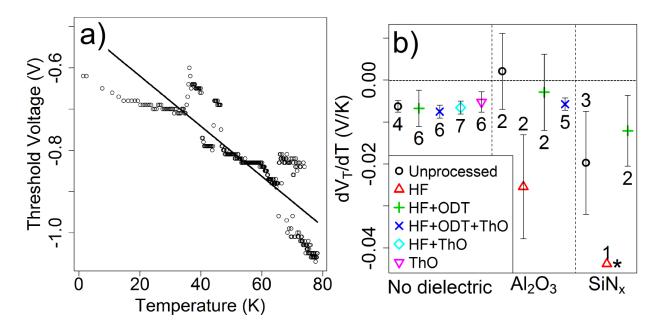

| 5.4               | Effect of surface passivation on threshold voltage in InAs nanowires $\ldots$                                                                                                                                                                                                                                               | 79                       |

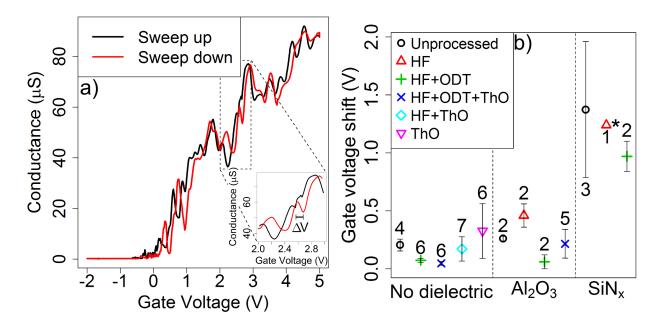

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 5.5               | Gate hysteresis in InAs nanowire treated with different surface processing procedures                                                                                                                                                                                                                                       | 80                       |

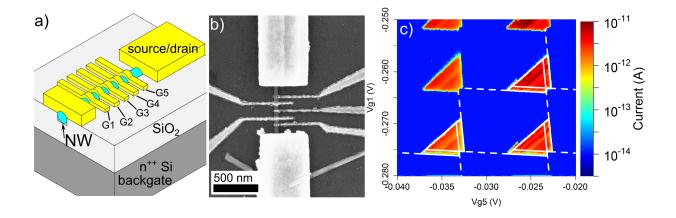

| 5.6               | Entrenched nanowire field effect transistor for electrostatically defined double quantum dots                                                                                                                                                                                                                               | 82                       |

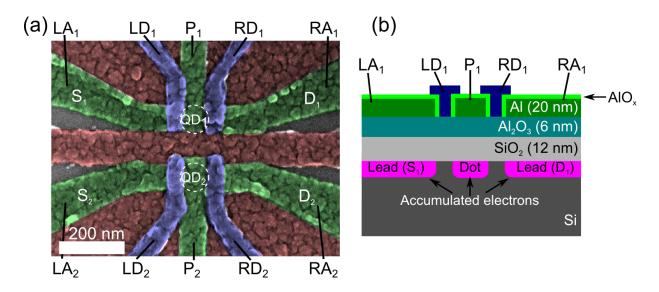

| 6.1               | Geometry of a pair of Si MOS quantum dots, showing the gate layout and a cross-section of the dielectric layers.                                                                                                                                                                                                            | 88                       |

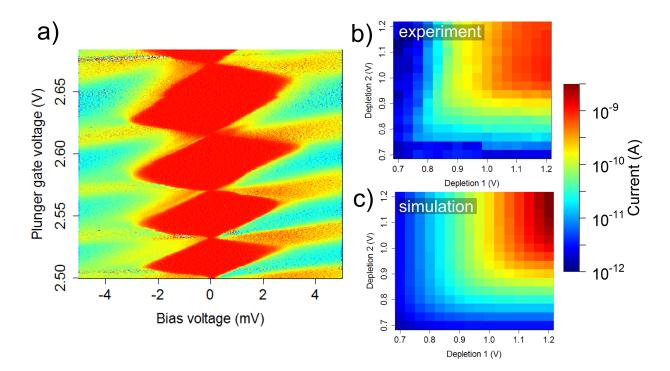

| 6.2               | Current through a Si MOS quantum dot showing Coulomb blockade and modulation of the tunneling rate                                                                                                                                                                                                                          | 90                       |

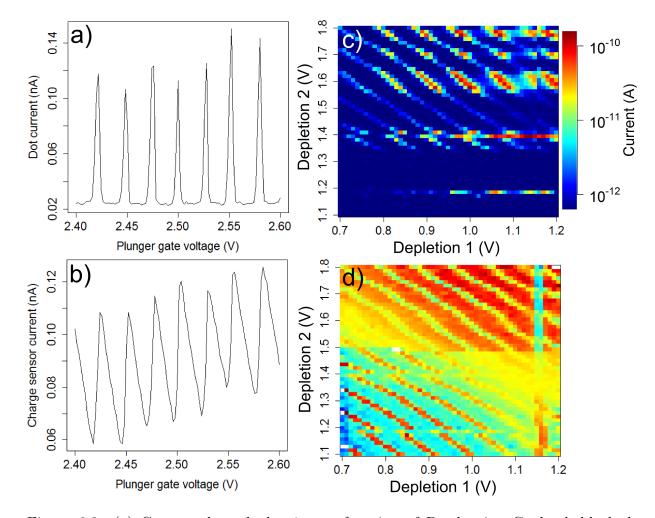

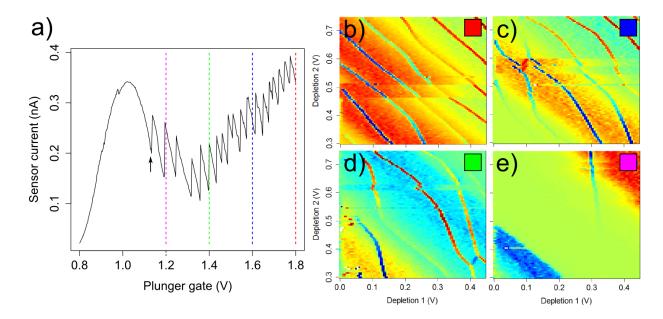

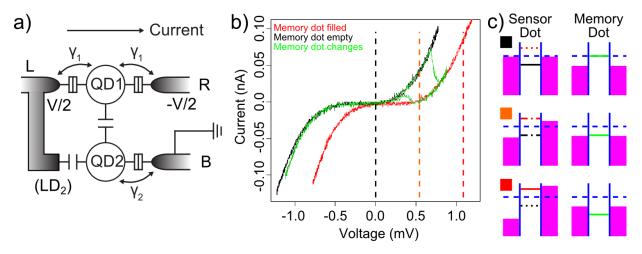

| 6.3               | Charge sensing using a pair of capacitively coupled quantum dots                                                                                                                                                                                                                                                            | 92                       |

| 6.4               | Potential landscape a Si MOS quantum dot in the single electron regime.                                                                                                                                                                                                                                                     | 93                       |

| 6.5               | Circuit schematic and energy level diagrams of a double dot showing mem-<br>ristive current hysteresis                                                                                                                                                                                                                      | 94                       |

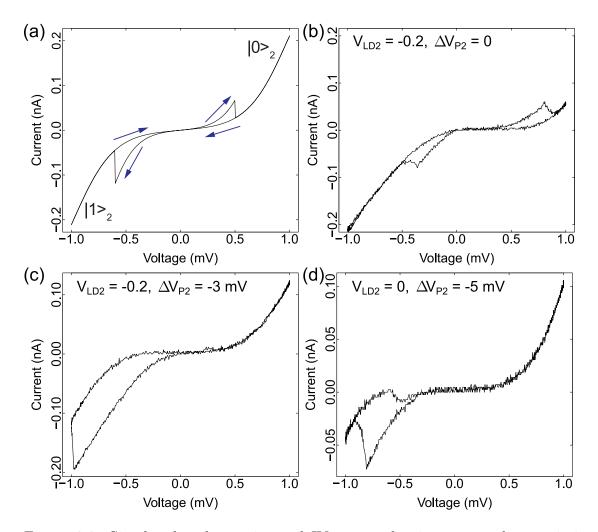

| 6.6               | Simulated and experimental IV curves showing memristive current hysteresis                                                                                                                                                                                                                                                  | 98                       |

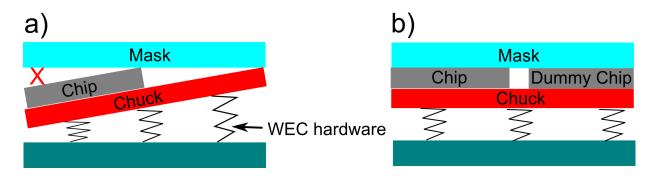

| A.1               | Wedge error correction during photolithography                                                                                                                                                                                                                                                                              | 125                      |

| A.2               | Dry etching of trenches for aligned nanowire deposition                                                                                                                                                                                                                                                                     | 128                      |

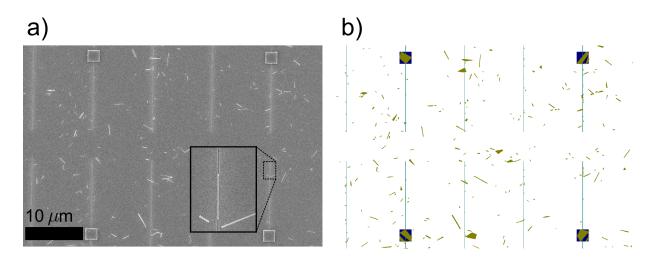

| A.3               | Nanowire location via SEM                                                                                                                                                                                                                                                                                                   | 132                      |

| A.4               | Patterning sequence for multi-aperture exposure in electron beam lithography                                                                                                                                                                                                                                                | 134                      |

| A.5               | 120 $\mu$ m aperture focusing techniques                                                                                                                                                                                                                                                                                    | 136                      |

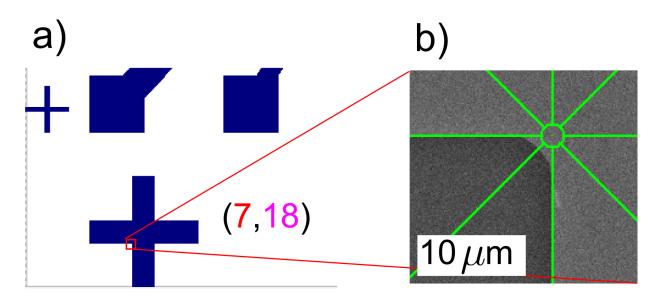

| A.6               | Alignment marks used for global alignment                                                                                                                                                                                                                                                                                   |                          |

| A.7               | Augument marks used for grobal augument                                                                                                                                                                                                                                                                                     | 138                      |

| A.(               |                                                                                                                                                                                                                                                                                                                             | 138<br>138               |

| A.7<br>A.8        |                                                                                                                                                                                                                                                                                                                             |                          |

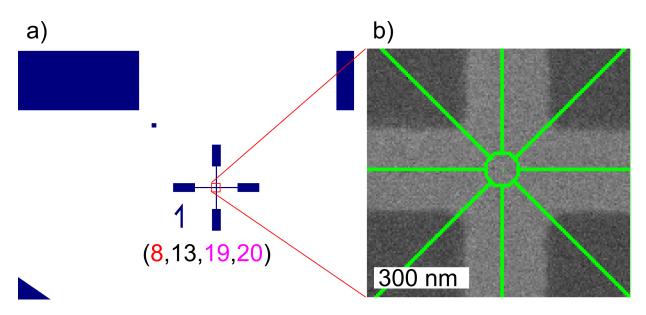

|                   | Pattern of alignment marks used for local 3 point alignment                                                                                                                                                                                                                                                                 | 138                      |

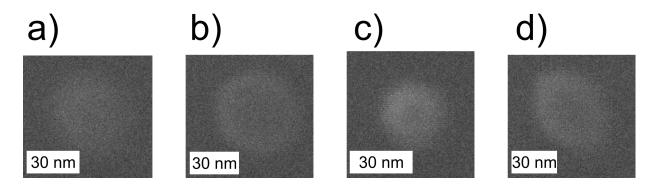

| A.8               | Pattern of alignment marks used for local 3 point alignment $\dots \dots \dots$<br>Fine focusing of the 10 $\mu$ m aperture using spots burned in PMMA $\dots \dots$                                                                                                                                                        | 138<br>139               |

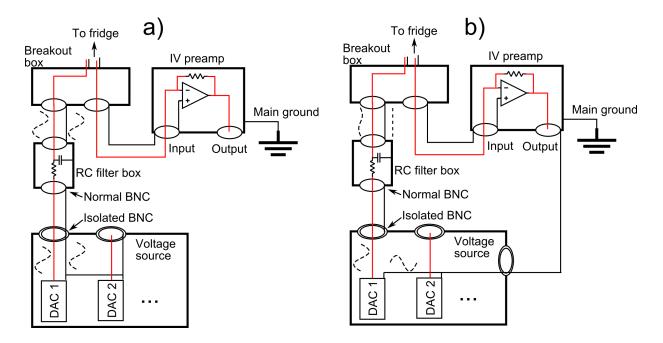

| A.8<br>B.1        | Pattern of alignment marks used for local 3 point alignment $\dots \dots$<br>Fine focusing of the 10 $\mu$ m aperture using spots burned in PMMA $\dots$<br>Wiring schematic for high frequency and DC lines inside the dilution fridge                                                                                     | 138<br>139<br>143        |

| A.8<br>B.1<br>B.2 | Pattern of alignment marks used for local 3 point alignment $\ldots \ldots$<br>Fine focusing of the 10 $\mu$ m aperture using spots burned in PMMA $\ldots$<br>Wiring schematic for high frequency and DC lines inside the dilution fridge<br>Proper grounding of the voltage source for low noise DC measurements $\ldots$ | 138<br>139<br>143<br>144 |

## Chapter 1

## Introduction

Chapter contributions: Simulations were performed using The R Project for Statistical Computing with scripts written by Gregory Holloway.

### 1.1 Introduction

Electron transport in solids plays a major role in our lives as it is the building block for a vast section of our current technology known as electronics. For many years, the flow of electrons in these systems was well described by classical physics in terms of voltage differences leading to current flow. As technology advances, the size of these systems has shrunk towards the atomic scale, leading to the breakdown of classical physics and the emergence of quantum phenomena. While these effects may need to be mitigated to preserve the classical operation of these devices, they also provide the potential for new technologies based on quantum behavior. This requires a thorough understanding of the underlying physics such that progress can be made from observing these effects to actively controlling them.

The overarching physical description of these small scale effects is quantum mechanics. While quantum mechanics is generally accepted as the correct description of the universe, it's effects are often counterintuitive. One major difficulty with understanding quantum mechanics is that our macroscopic view of the world is inherently classical. In classical mechanics objects react to forces to move in fixed trajectories. In contrast, in quantum mechanics an object's behavior is probabilistic allowing it to be in two states at once, or take multiple paths through a system. Electrons which are often pictured as particles of matter moving through a circuit, can quantum mechanically behave as waves. This leads to interesting effects, such as an electron being able to interfere with itself, or tunneling through barriers that would classically be impassable. Observing these effects on individual electrons is difficult, and requires properly designing systems where these properties will dominate.

Electron transport itself can act as a probe of the environment seen by the electron. This transport can be measured as a macroscopic current, providing a means to observe quantum effects. For example, current through microscopic objects can change dramatically as the wave-like nature of the electron is confined. This can result in quantization of the electron's energy, yielding steps or peaks in the current [1]. Other quantum properties of the electron, such as it's intrinsic spin, can also effect transport[2, 3]. Semiconductors provide an ideal platform for studying these effects as the number of electrons in the material can be controlled through doping, or electrostatic gating. However, even when electrons are confined in the range of 20-100 nm, the separation of these energy levels is quite small, on the order of a few meV. This requires that all other energies in the system be lower than this value for these effects to be visible. Thermal energy blurs out quantum behavior at room temperature. This can be overcome by using cryostats to cool samples down to temperatures in the range of 25 mK - 4 K. With all of these requirements in place quantum effects can be observed and studied.

One goal of understanding quantum phenomena is to exploit these effects to realize new and more powerful technologies. The quantum computer is one such device, which combines the binary architecture of modern computing science with the properties of quantum mechanics to implement a new type of computation. In a classical computer, information is stored in classical bits which can be either a 0 or 1. Whereas in a quantum computer, the quantum bit or qubits are encoded quantum mechanically such that they can be in a superposition of the 0 and 1 states simultaneously. For N qubits, the computer can be in  $2^N$ states at once, allowing each state to be operated on simultaneously. This can provide an exponential speed up for finding solutions to certain problems when compared to a classical computer. Theoretical work has developed several algorithms which are predicted to have more efficient solutions with a quantum computer, and include factoring of large numbers [4], and database search[5]. Quantum computers also provide a more natural platform for simulating quantum systems, such as quantum magnets [6], or quantum chemistry [7].

While several implementations of small scale prototypes have been demonstrated, a fully universal scalable computer has not been realized. Systems, like NMR, have been shown to exhibit fully universal control, but suffer from poor scalability [8]. One promising avenue for scalability is solid state systems, where many small devices with the desired electronic properties can be packed into a small space, analogous to modern computer chips. In particular, the realization of electrostatically defined quantum dots can be used to confine and manipulate individual electrons. The electron's spin can then be encoded as a qubit, providing a robust platform for implementing spin-based quantum information processing. In theory the electron's charge could be used to encode a qubit, but the state would be numerous nearby charges leading to fast decoherence. The study of electron transport in semiconducting structures as potential candidates for quantum information processing platforms is the goal of this thesis.

### 1.2 Outline of the thesis

The rest of this chapter is focused on a discussion of the fundamentals of charge transport in nanowires and quantum dots. This theoretical description of transport provides the background information necessary to better understand the rest of the thesis. Chapter 2 presents a study of mobility in InAs nanowires. The temperature dependence of the mobility value is used to determine that ionized impurity scattering from surface states is the primary mechanism limiting mobility in these nanowires. The mobility of core/shell nanowires is also measured, and shows reduced scattering rates indicating that the addition of an epitaxial shell can remove some of the surface states. The presence of cystalline defects in the nanowire, such as stacking faults, is found to further lower the mobility. In chapter 3, the effect of charge noise on electron transport in InAs nanowires is studied. Abrupt jumps in conductance between two values are observed, and attributed to changes in the occupation of single electron charge traps near the nanowire. A model of the dynamics of these traps as a function of temperature and gate voltage is presented. The model shows good agreement with experimental data, and provides an estimate of the trap location relative to the surface of the nanowire. Chapter 4 looks at the occupation of transverse subbands in a nanowire as a function of an applied axial magnetic field. These subbands provide channels for electron transport, and thus directly affect the conductance of the nanowire. We present a model of magnetoconductance based on the subband occupation of a cylindrical wire. Experimental conductance is measured as a function of magnetic field and gate voltage, and the model is fitted to the data to extract the subband occupation, as well as an estimate of the electrostatic potential in the nanowire. The focus of chapter 5 is to test the effect of different surface passivation techniques on various transport properties of InAs nanowires. The ultimate goal being to determine which process gives the cleanest, most stable device suitable for implementing quantum information processing. The surface processes include wet etching of the nanowire oxide, formation of a self assembled monolayer, growth of a thermal oxide, and deposition of a dielectric shell. After fabrication and measurement, each process was characterized based on its mobility, subthreshold swing, charge noise, and gate hysteresis. The most promising combination of techniques was then used to fabricate a top-gated nanowire device in a novel entrenched geometry capable of forming an electrostatic double quantum dot. The device showed unambiguous transport signatures of a double quantum dot, with minimal charge noise confirming the effectiveness of the surface processing.

Chapter 6 looks at Si metal-oxide-semiconductor quantum dots. We move away from III-V's, which are nuclear spin abundant, to group IV (Si), which can be isotopically purified ( $^{28}$ Si) to have no nuclear spins, and thus realize a magnetic "vacuum". This is attractive for spin based quantum information processing, since the low density of nuclear spins should improve electron spin coherence times. Here, transport through a pair of capacitively coupled quantum dots is studied to extract basic properties of each quantum dot. Next, one dot is employed as a charge sensor and used to measure the charge of the other dot down to the single electron regime where spin-based quantum information processing can be performed. The charge sensing not only reveals the electron number, but can also be used to probe the potential landscape of the other dot. The pair of dots is also used to implement a novel quantum memristive system, which has potential future applications as ultra dense, low power memory [9, 10]. In this configuration, the transport through one dot shows hysteretic behavior dependent on the charge state of the other dot. Chapter 7 presents conclusions and discusses future work.

#### **1.3** Background

The purpose of this section is to provide a concise overview of the fundamentals of charge transport through 1D and 0D systems, eg. nanowires and quantum dots. We begin with a discussion of transport along semiconducting nanowires showing how the shape of the nanowire and its crystalline structure modify transport. Specific electrostatic potentials are then added to this system to present the ideas of surface accumulation, and confinement in a quantum dot. The dot is then abstracted away from the nanowire system to allow for a more in-depth explanation of the parameters governing transport through a quantum dot. Finally a look at transport through two quantum dots in series is presented as a means to study the spin of the confined electrons.

#### **1.3.1** Nanowire transport

When placed in a solid the electron's wave function is dictated by the electrostatic potential of the material, due to the nuclei, other fixed charges, applied potentials, and the shape of the material. Including the kinetic term, the Hamiltonian can be written as:

$$H = \frac{\hbar^2 p^2}{2m} + V_{nuclei} + V_{\alpha} \tag{1.1}$$

where  $\hbar = h/2\pi$  and h is Planck's constant, p is the momentum, m is the electron mass,  $V_{nuclei}$  is the electrostatic potential due to the material's positively charged nuclei, and  $V_{\alpha}$  is the electrostatic potential from all other sources. For a crystalline material such as a semiconducting nanowire,  $V_{nuclei}$  is a periodic potential with a minimum at the position of each nucleus. A typical InAs nanowire is roughly 60 nm in diameter, with a lattice constant of  $\sim 0.6$  nm, this suggests that the electron will see roughly 10,000 nuclei in a single nanowire cross-section alone. Trying to keep track of all of these nuclei would be an impossible task, so instead the effective mass approximation is employed. In this approximation, the motion of the electron through the periodic potential of the material can be recast as motion through free-space, but only in certain ranges or bands of energy. The curvature of these bands in momentum space determines the effective mass  $m^*$  of the electron in that band, which can be different from the true electron mass. This provides a simple means to capture some of the inherent properties of the host material, with a material specific value that replaces m in equation 1.1. The equation can thus be rewritten as [11]:

$$H = \frac{\hbar^2 p^2}{2m^*} + V_\alpha \tag{1.2}$$

The first case of  $V_{\alpha}$  that will be assumed is a hard wall potential at the edges of the semiconductor material, i.e. the electron is confined inside the material. The hard wall potential is defined as:

$$V(r, \theta, l) = \begin{cases} 0, & \text{if } 0 < l < L \text{ and } r < R\\ \infty, & \text{otherwise} \end{cases}$$

(1.3)

where  $r, \theta$ , and l are cylindrical coordinates for the nanowire with r = 0 being the center of the nanowire and l = 0 located at one end, R is the radius of the nanowire, and L is the length. By definition, nanowires have a much longer length than radius  $L \gg R$ . Therefore, it is a common assumption that the electron wavefunction is only confined radially, and in the axial direction the electron is allowed to propagate semi-infinitely. The Hamiltonian is then separated into axial and radial parts, and the electron wavefunction is found by solving the time-independent Schrödinger equation. Axially, the electrons propagate as plane waves, whereas radial confinement causes the radial wavefunction to take the form of Bessel functions. The electron energy levels are thus quantized in the transverse direction and given by the 1D density of states in the axial direction.

Translating these electron wavefunctions into current measured through the nanowire is achieved using the Landauer approach. In the case of ballistic transport, the current carried by a single 1D channel at zero temperature is given by [12]:

$$I = \int_0^{eV} ev(E)g_{1D}(E)dE = \int_0^{eV} ev(E)\frac{2}{hv(E)}dE = \frac{2e}{h}(eV)$$

(1.4)

where V is the bias voltage applied to the nanowire, v(E) is the group velocity, and  $g_{1D}$  is the 1D density of states. Thus each 1D channel carries a single quantum of conductance  $G_0 = 2e^2/h$ . The position of these 1D channels is given by the energy levels for the radial wavefunction. The effects of temperature can be included by smearing out these conductance levels with the Fermi-Dirac distribution.

$$I = \frac{2e}{h} \int_{-\infty}^{\infty} D(E) [f(E - \mu_L) - f(E - \mu_R)] dE$$

(1.5)

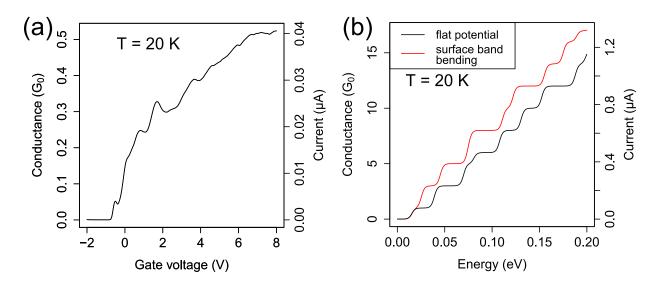

where  $f(E) = [1 + \exp(E/k_{\rm B}T)]^{-1}$ , T is the temperature, E is the energy,  $\mu_{L/R}$  are the chemical potentials of the leads, and D(E) is the transmission coefficient of the system. D(E) indicates the ratio of the number of electrons successfully transmitted through the system relative to the number incident electrons. This coefficient can therefore be used to include the effects of scattering. The voltage across the device sets the chemical potentials of the leads through:  $V = \mu_L - \mu_R$ . Simulated current calculated using equation 1.5 for a bias of 1 mV and a temperature of 20 K is shown in figure 1.1(b). The energies of the subbands are calculated for a cylindrical InAs nanowire with a diameter of 60 nm. For comparison, experimentally measured current through a 65 nm diameter nanowire with a length of 1  $\mu$ m is shown in figure 1.1(a).

In semiconductors, fixed charge can lead to built in electrostatic potentials which can modify transport. For example, InAs has a surface charge density that causes the conduction band to bend down at the surface. Experimentally, this is a nice feature of the material as it induces an accumulation layer at the surface facilitating ohmic contacts with a variety of metals. This built-in potential also changes the electron wavefunction, and can be understood by adding an additional potential term to equation 1.2. The exact form of the radial potential is unknown, but a commonly used analytic form is:  $V(r) = A(1 - (r/R)^{b/2})$  [13], where A and b are coefficients describing the shape of the potential. Since this potential

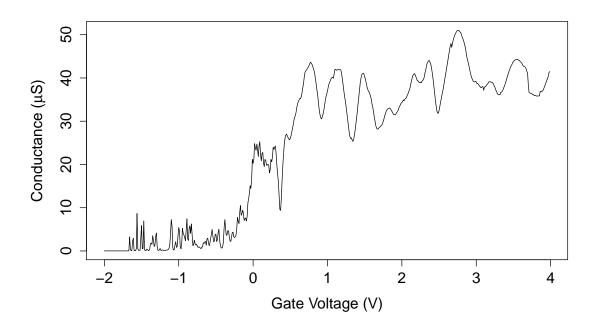

Figure 1.1: Experimental and simulated current through an InAs nanowire at 20 K, with a bias of 1 mV. (a) Current through a 1  $\mu$ m long nanowire as a function of back gate voltage. The back gate changes the Fermi level inside the nanowire bringing different subbands into the bias window. Step-like features are visible in the conductance, but have a height much less than  $G_0$  due to scattering. (b) Simulated current as a function of Fermi energy through a nanowire with and without surface band bending. The steps in current occur each time a new transverse subband is populated. The two curves show similar behavior, but with different subband energy level structures leading to different step positions.

is purely radial, the Hamiltonian can still be separated into axial and radial parts yielding a similar picture of transport in this system. The main effect of this additional potential is to shift the eigenenergies of the radial Hamiltonian, modifying the subband occupation spectrum. Simulated current for a potential with strong surface band-bending (A = 0.25eV, b = 9), and no radial potential (A = 0 eV, b = 0) are shown in figure 1.1(b).

Variation of the electrostatic potential along the length of the nanowire can lead to effects like scattering, where electrons are reflected back towards their source. To understand this mechanism, the case of a delta function somewhere along the length of the nanowire is considered. This potential is assumed to be radially independent, such that it extends across the entire cross-section of the nanowire. The potential will have the form:  $V(l) = g\delta(l - l_1)$ , where g is the strength of the barrier, and  $l_1$  is its position along the nanowire length. Since this potential is dependent only on l, the Hamiltonian can still be separated into axial and radial parts. Physically, this means that the potential does not affect the radial states, and only provides a means for the axial states to couple to one another. Elastic collisions are assumed, such that the energy of the system must be conserved. Therefore, the magnitude of the plane wave's momentum must remain fixed, such that only backscattering can occur. This greatly simplifies the problem as it means we must only consider one dimensional scattering. For potentials with both a radial and axial dependence, the potential can also couple different radial states together leading to interband scattering. To find the transmission through a potential barrier, the transfer matrix is calculated. This matrix acts on the left and right propagating states on the left side of the potential to give the magnitude of the states on the right side of the potential. For a delta function in one dimension this is found to be:

$$M_{b1}(ka) = \frac{1}{ika} \begin{pmatrix} ika+1 & 1\\ -1 & ika-1 \end{pmatrix}$$

(1.6)

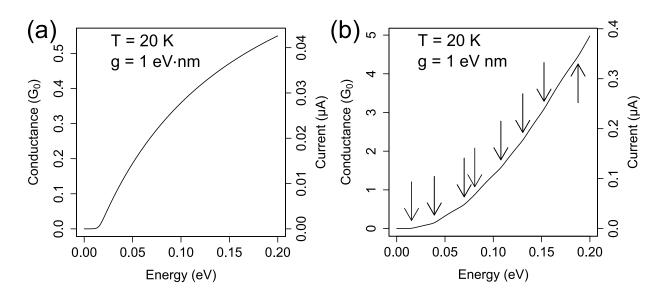

where  $a = \hbar^2/mg$  and  $k = \sqrt{2mE/\hbar^2}$ . Given the transfer matrix, the transmission probability bility is:  $T = 1 - |M_{12}/M_{22}|^2$ . For a delta function potential this transmission probability is:  $T = (ka)^2/(1 + (ka)^2)$ . This can be directly substituted for D(E) in equation 1.5 since k explicitly depends on the energy. Simulated current as a function of energy for a single subband through a delta function potential is shown in figure 1.2(a). Simulated current through an InAs nanowire with a single delta function potential is shown in figure 1.2(b). The arrows indicate each time a new subband becomes filled. The step for each subband has become significantly rounded by the transmission through the tunnel barrier.

For a more interesting example, a second delta function barrier is added in series with the first barrier. This barrier is located at  $l_2$ , and has the potential:  $V(l) = g\delta(l-l_2)$ . The distance between the two barriers is defined as:  $l_{12} = l_2 - l_1$ . The total transfer matrix for this system is now the product of three transfer matricies corresponding to transmission through barrier 1  $(M_{b1})$ , propagation through free space over length  $l_{12}$   $(M_{fs})$ , and then transmission through barrier 2  $(M_{b2})$ :  $M_t = M_{b2} \cdot M_{fs} \cdot M_{b1}$ . The transfer matrix for a barrier is already given above, thus the transfer matrix through free space is all that is needed to complete the calculation. The transfer matrix for free space is:

$$M_{fs}(kl_{12}) = \begin{pmatrix} e^{ikl_{12}} & 0\\ 0 & e^{-ikl_{12}} \end{pmatrix}$$

(1.7)

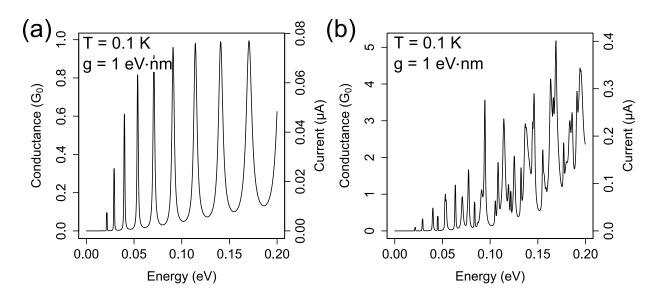

Solving for transmission through the total system and reevaluating equation 1.5 gives current through the two barriers. Figure 1.3(a) shows current for a single subband, which shows markedly different behavior than what was seen for a single barrier. Here, the conductance shows an array of peaks with amplitudes approaching  $G_0$ . Each of these peaks corresponds to a discrete energy level formed between the two barriers, due to confinement of electrons in the axial direction. For the limit of  $g \to \infty$  the energy of these

Figure 1.2: (a) Simulated current as a function of energy, at 20 K, for a single subband through a single delta function potential barrier with g = 1 eV nm, and a bias of 1 mV. The current through the barrier increases as the energy increases, and approaches  $G_0V$  for large energy. (b) Simulated current through a nanowire with no surface band-bending at 20 K. Arrows indicate the energy of each radial subband. The energy of the barrier is large compared to the separation of the subbands causing each step to become rounded.

states approaches  $E = (\hbar n \pi)^2 / 2m l_{12}^2$ . The region of space where the electron is confined in all three directions is called a quantum dot, and is characterized by a fully discretized energy spectrum. In this case electron-electron interactions are neglected such that the energy level spectrum is dictated solely by the orbital energies of the dot. Interestingly, the transmission through these energy levels at low energy is higher than that of the single barrier. This is due to resonant tunneling through the discrete set of energy levels created between the two barriers.

#### 1.3.2 Quantum dot transport

A quantum dot is a region of space confined in all three spatial directions. As was shown above, this geometry can be achieved by adding two barriers in series along the length of a nanowire. Several methods can be used to realize these barriers including: inclusion of different bandgap materials during growth, etching to constrict the nanowires, and electrostatic gating. In this thesis the barriers are formed using electrostatic gating, due

Figure 1.3: (a) Simulated current as a function of energy, at 1 K, through two delta function potentials each with g = 1 eV nm, and bias of 1 mV. The current shows sharp peaks due to resonant tunneling through discrete energy levels formed between the two barriers. At each peak the current is higher than the current seen through a single barrier at the same energy despite both systems having the same g value.(b) Simulation of current in a nanowire with the same double delta function potential as (a). The mixture of the radial energy spectrum and the discrete energy levels between the barriers still leads to peaks in current, but the spacing between peaks is more complicated.

to the increased tunability of the barriers, but the transport through any implementation would behave similarly. For the discussion of quantum dot transport we will focus on a simpler model of a quantum dot connected to semi-infinite leads. This way the physics of the dot is decoupled from other transport effects making them easier to understand, and the discussion is generalized such that they apply to other quantum dot systems such as those defined in 2D materials.

Since an electron in a dot is confined in all three spatial directions, the orbital energy spectrum of the electron is a set of discrete energy levels, whose spacing is dictated by the dimensions of the dot. These energy levels are the solutions to the familiar "electron in a 3D box problem" studied in undergraduate quantum mechanics courses and take the form:

$$E_{orb} = \frac{\hbar^2 \pi^2}{2m^*} \left(\frac{n_x}{L_x} + \frac{n_y}{L_y} + \frac{n_z}{L_z}\right)^2.$$

(1.8)

where,  $m^*$  is the electron effective mass,  $n_{x,y,z}$  are the quantum numbers for each spatial

directions, and  $L_{x,y,z}$  are the lengths of each side of the box. In addition to these orbital energies there is a Coulomb repulsion energy, which also effects how electrons are added to a quantum dot. This energy is due to the Coulomb repulsion between electrons, and creates an energy cost to add more electrons to a dot. This charging energy is determined by the capacitance of the dot through:  $E_C = e^2/C$ , where C is the dot capacitance. In many experimental quantum dots the Coulomb repulsion energy tends to dominate over the orbital energy, particularly when many electrons are present on the dot.

To calculate the current through the quantum dot, equation 1.5 is used by changing D(E) to reflect the discrete energy spectrum of a quantum dot.

$$D(E) = \sum_{N} \gamma_0 h \delta(\mu(N))$$

(1.9)

where the sum is over the N discrete states  $\mu(N)$  in the quantum dot,  $\delta(\mu(N))$  is a delta function centered at  $\mu(N)$ , and  $\gamma_0$  is the total tunneling rate through the dot. The tunnel rate can be written in terms of the tunneling rates through the left and right barriers as:  $\gamma_0 = \gamma_L \gamma_R / (\gamma_L + \gamma_R)$ . For this form of D(E), it is assumed that the tunnel rate is constant for each energy level. The factor of two at the beginning of equation 1.5 is also dropped since spin degeneracy in the quantum dot is broken by the Pauli exclusion principle. Current through the dot is thus given by:

$$I = e\gamma_0 \sum_N f(\mu(N) - \mu_L) - f(\mu(N) - \mu_R)$$

(1.10)

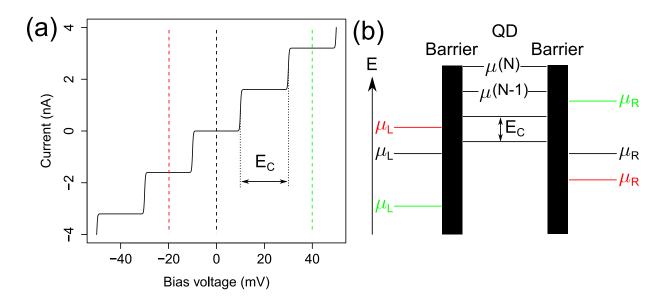

At this point the model for current through a quantum dot has two parameters that can be controlled in an experiment: the bias voltage  $V_b$ , and the temperature T. As a function of  $V_b$  the current through the dot is characterized by a series of steps in current as new energy levels enter the bias window. Simulated current for this case in shown in figure 1.4, along with an energy level diagram of the dot. A nice addition to this model would be a way to control the energy levels of the quantum dot relative to the bias, such that the number of electrons on the dot could be controlled. This is achieved experimentally by placing an electrostatic gate near the dot, which capacitively couples to the energy levels providing a means of tuning the electron number. Theoretically the gate voltage can be understood by looking at the chemical potential of the dot in the constant interaction model [14]:

$$\mu(N) = U(N) - U(N-1) = E_N + \frac{(N - N_0 - 1/2)e^2}{C} - \frac{eC_g V_g}{C}$$

(1.11)

where N is the number of electrons in the dot,  $E_N$  is the orbital energy of the Nth electron,  $V_g$  is the gate voltage,  $C_g$  is the gate capacitance, and  $N_0$  is the number of electrons in the

Figure 1.4: (a) Simulated current through a quantum dot as a function of bias voltage at 1 K. The charging energy of this dot is set to  $E_C = 10$  meV, and the tunnel rate is  $\gamma_0 = 1$  GHz. At zero bias no states fall in the bias window so zero current is observed. As bias is increased above  $E_C$  a state will fall in the bias window giving finite current. (b) Energy level diagram of the quantum dot shown in (a). The bias applied to the device sets the chemical potential of each lead. Three different biases are shown in different colors, corresponding to the dashed vertical lines in (a).

dot when  $V_g = 0$ . The chemical potential of the quantum dot is more useful than the bare energy of the states, since the dot is referenced to leads with chemical potentials  $\mu_L/\mu_R$ . The energy difference between two chemical potentials can also be calculated:

$$\mu(N+1) - \mu(N) = E_{N+1} - E_N + e^2/C \tag{1.12}$$

and gives the difference in orbital energy plus the charging energy as expected. In the case of  $e^2/C \gg E_{N+1} - E_N$  the separation between subsequent chemical potentials would be equal and be given solely by the charging energy.

The addition of the gate voltage in equation 1.11 provides a means to change the energy level of the dots relative to the chemical potential of the leads. If gate voltage is swept when a small finite bias is applied to the quantum dot a series of peaks are observed in the current each time a different energy level passes through the bias window. A plot showing simulated current as a function of  $V_g$  is shown in figure 1.5(a). In between these current peaks are regions of very low current caused by the Coulomb repulsion. Each low current

Figure 1.5: (a) Simulated current through a quantum dot as a function of gate voltage at 1 K, with  $V_b = 1$  mV. The charging energy of the dot is  $E_C = 10$  meV, the tunnel rate is  $\gamma_0 = 1$  GHz, and the gate capacitance is 0.1C. Peaks occur when the chemical potential of the dot falls in the bias window. The low current regions in between each peak correspond to a fixed charge on the dot, as indicated by the numbers in parentheses. (b) Energy level diagram of the dot shown in (a). The two colors of lines in the middle show the chemical potentials in the dot at different gate voltages, corresponding to the vertical dashed lines in (a). At the gate voltage giving the black states no level falls in the bias window giving suppressed current. When the voltage is increased to the point shown by the red lines a state is present in the dot to allow transport between the leads.

region corresponds to a fixed charge on the dot, and is commonly referred to as Coulomb blockade due to this repulsion effect.

Current through the dot can now be calculated as a function of both  $V_b$  and  $V_g$ . Similar to  $V_g$ , it is found that blockade extends over a small portion of  $V_b$ , leading to diamond shaped regions of blockaded current. These Coulomb diamonds are shown in figure 1.6. The horizontal and vertical dimensions of each diamond are determined by C and  $C_g$ . The annotations in figure 1.6(a) show how these capacitances relate to the dimensions. The slope of the edges of the diamonds is dictated by the capacitance between the dot and each of the leads. These capacitances  $C_{L,R}$  for the left and right leads respectively are part of the total capacitance of the dot  $C = C_g + C_L + C_R$ . If  $C_L = C_R$  the slopes are symmetric, and the bias applied to the device drops equally across both tunnel barriers, see figure 1.6(b). As one of these capacitances grows relative to the other it means that more of the bias is being dropped on one side of the dot, as shown in figure 1.6(d). This changes how the energy levels in the dot fall in the bias window, altering the Coulomb diamond pattern. The annotations in figure 1.6(c) show how these capacitances are analytically related to each slope. The number of electrons on the quantum dot can be estimated by identifying the zero electron state, where current is no longer observed through the dot, and then counting the number of Coulomb diamonds from that point.

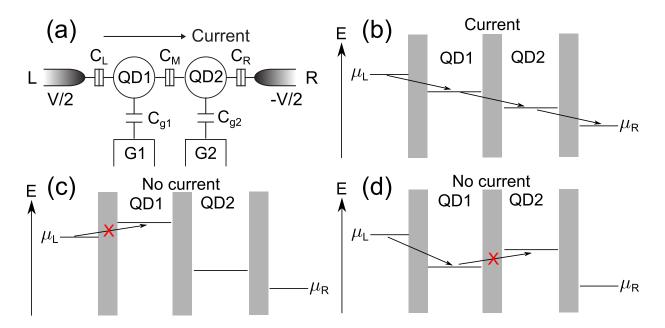

#### **1.3.3** Double quantum dot transport

Transport through a single quantum dot is now extended to the case of two quantum dots in series. This situation can be pictured as two discrete sets of energy levels in series between two thermally populated reservoirs. When a finite bias is applied across the two dots, current can flow when an energy level from each dot is in the bias window, and the energy levels are positioned such that electrons can flow from high to low energy. An energy level diagram of two dots in various energy configurations is shown in figure 1.7. A metallic gate is placed next to each dot to control its chemical potential, identical to the single dot case.

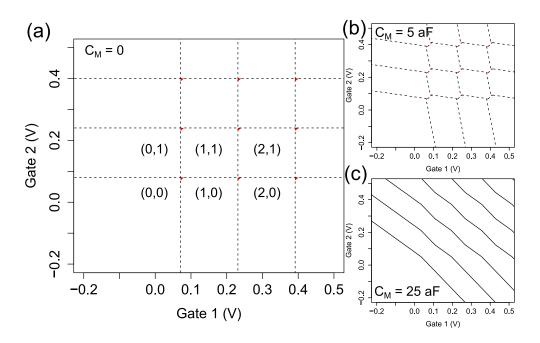

Current through the double dot could be found using a similar formalism as that of the single dot. Therefore, the focus of this section is the electrostatics of the two dots to show how the charge states of the two dots are modulated, and where unblockaded current can be expected. As a starting point it is assumed that there is no coupling between the two dots, such that the charge state and gate of one dot do not affect the chemical potential of the other dot. This means that each gate can act independently to change the charge state of its dot. These couplings are controlled by a gate capacitance  $C_{g1,g2}$  for each gate respectively. For very small bias, current will only be non-zero when a charge state in both dots is aligned with the leads. Current as a function of both gates is then a square array of points, as shown in figure 1.8(a). The dashed lines in figure 1.8(a) indicate the areas of fixed charge on both dots. This type of plot is commonly called a stability diagram since it shows stable regions of charge for each gate. Notice how as a function of one gate, equally spaced regions of fixed charge are observed in each dot, analogous to the situation of transport through a single dot shown in figure 1.5(a).

When a capacitive coupling between the two dots is turned on, the number of charges on one dot will affect the chemical potential of the other dot. In this case, the points of non-zero current in the stability diagram split into two points, and the regions fixed charge become skewed into hexagonal shaped regions. The two current points are known as triple

Figure 1.6: (a,c) Current as a function of bias voltage and gate voltage showing Coulomb diamond structure characteristic of transport through a quantum dot. The green diamonds of zero current contain a fixed number of charges on the dot indicated by the numbers in parentheses. (a) The capacitance between the dot and the two leads is equal giving diamonds symmetric about zero bias. (c) The capacitance to the left lead is 9 times larger than that of the right lead, giving skewed diamonds. The slopes of the edges of the diamond are shown next to each black dashed line. (b,d) energy level diagrams for the two dots shown in (a,c). The three different colored chemical potentials correspond to the points in the Coulomb diamond marked by the colored circles in (a,c). (b) The symmetric lead capacitances cause the chemical potentials of the leads to move equally on each side of the dot. (d) The capacitance to the left lead is larger, causing it to move more than the right, and giving asymmetric bias current.

Figure 1.7: (a) Schematic of a double quantum dot between two leads. In this model, the tunnel barrier between each dot and its adjacent lead is represented by a resistor and capacitor in parallel. Only the value of the capacitance of each barrier is shown in the schematic. Each dot is also capacitively coupled to an electrostatic gate. (b-d) Energy level diagram of a double quantum dot in various charge configurations. (b) The chemical potentials of both dots are within the bias window, and positioned to allow electrons to tunnel from one to the other giving current through the double dot. (c,d) Two charge configurations where transport through the dot is blocked giving no current. The red x's show the charge transition which is not allowed.

points, with each point corresponding to a different ordering of the electrons entering and exiting the two dots. Despite the regions of fixed charge becoming skewed, the location of the triple points still falls on a square array as shown in figure 1.8(b). If the interdot capacitance  $C_m$  is increased far enough the two dots effectively merge into a single dot leading to a stability diagram with parallel diagonal lines, see figure 1.8(c). Each of these lines of finite current are the Coulomb blockade peaks of the single dot.

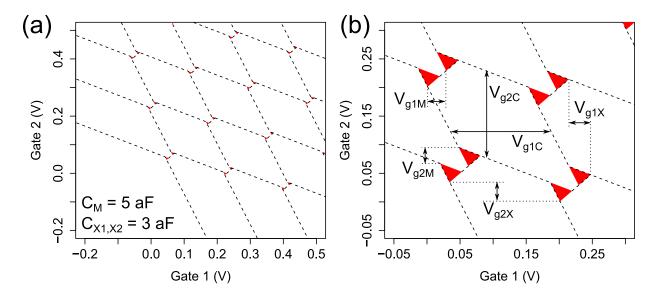

In real systems the chemical potential of a dot can also be affected by the gate of the other dot, i.e. there is some coupling between dot 1 and gate 2. This cross capacitance  $C_{x1,x2}$  can also be included in the electrostatic model and causes a shift between the location of adjacent triple dots. Therefore the points no longer fall on a square array, a stability diagram with non-zero cross capacitance and interdot capacitance is shown in figure 1.9(a).

Figure 1.8: Double quantum dot stability diagrams as a function of the two gate voltages with different interdot capacitance  $C_M$ . Dashed lines show regions of fixed charge on the two dots indicated by the numbers in parentheses. Current flow through the two dots is shown by the red points where two or more lines intersect. (a) For  $C_M = 0$  the stability diagram is an array of squares, where changing a gate voltage changes the number of electrons on that dot without affecting the charge of the other dot. (b) At intermediate  $C_M$  the two dots are coupled giving a honeycomb structure to the stability diagram. The single points of current at the verticies in (a) have now split into two triple points. (c) When  $C_M$  is further increased the stability diagram begins to look like a set of diagonal parallel lines indicating that the two dots have merged into one larger dot.

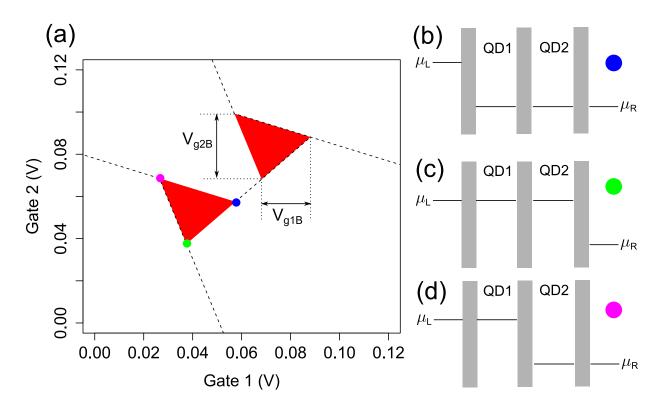

Up until now the case of small bias has been assumed in the double dot system, such that unblockaded current is only observed at the triple points. When a finite bias is applied, each triple point grows into a triangularly shaped region of non-zero current typically called a bias triangle. A stability diagram with non-zero bias is shown in figure 1.9(b). The size of each triangle grows linearly with the applied bias, and change direction if the sign of the bias is flipped. Figure 1.10 shows two bias triangle as well as schematics of the double dot energy levels to show how the positions of these levels determine the extents of the bias triangles. In short, each vertex of the triangle corresponds to a different combination of the energy levels being aligned to the left and right leads. The shape of each bias

Figure 1.9: Stability diagram for a double quantum dot with finite cross capacitance between the gates and dots. The main effect of this cross capacitance on the stability diagram is to skew the location of each pair of triple points relative to the other pairs. (a) Large area of the stability diagram showing the skewed behavior. (b) Zoom-in of a smaller portion of a stability diagram with 10 mV of bias showing bias triangle of non-zero current. Annotations label the critical dimensions of this stability diagram that can be used to extract the capacitances.

triangle is thus determined by the coupling between the gates and the chemical potentials of each dot, which is explained in the previous paragraphs. The analytic equation for each of these couplings is given in reference [15]. The dimensions of the stability diagram labeled in figures 1.9,1.10 can thus be related to the various capacitances. The following equations relate the two set of parameters together, and can be extracted from the chemical potentials by choosing specific values for the number of electrons in each dot and solving for the corresponding changes in gate voltage.

Figure 1.10: (a) Triple points of a double dot at finite bias showing bias triangles. The labeled dimensions of the triangles will be used to extract the capacitances of the double dots. (b-d) Energy level diagram of a double dot at finite bias showing the positions of the chemical potentials of each dot at the verticies of the bias triangles. The colored circles correspond to the circles in (a) and show which diagram matches to which vertex.

$$V_{g1(2)C} = eC_{1(2)}/C_{T1(2)} \tag{1.13}$$

$$V_{g1(2)M} = eC_M / C_{T1(2)} \tag{1.14}$$

$$V_{g1(2)B} = V_b (C_1 C_2 - C_M^2) / C_{T1(2)}$$

(1.15)

$$V_{g1(2)X} = eC_{g1(2)X}/C_U \tag{1.16}$$

$$C_{T1(2)} = C_{g1(2)}C_{2(1)} + C_{g2(1)X}C_M$$

(1.17)

$$C_U = C_{g1X}C_{g2X} - C_{g1}C_{g2} \tag{1.18}$$

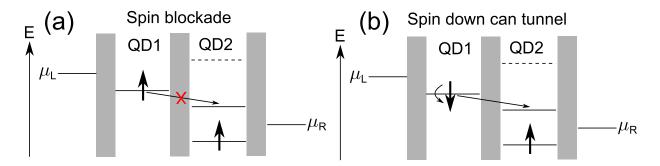

In addition to the electrostatics of the system, the electrons' spin can also effect transport through a double dot [2, 3]. If the second dot is filled with a single electron, transport

Figure 1.11: Energy level diagram of a double quantum dot including the effects of electron spin. The spin up electron in the right dot is fixed, since this state sits below the bias window. (a) The spin up electron in the left dot is unable to tunnel into the second quantum dot due to the Pauli exclusion principle. (b) If the left electron spin can be rotated to the spin down position it can tunnel into the second dot and out of the system giving a brief jump in current. However, another spin up electron is likely to enter the first dot from the left lead returning the system to a blockaded state.

that should be electrostatically allowed can become blockaded due to the Pauli exclusion principle. This prevents electrons from occupying the same state, and adds to the addition energy of the second quantum dot and can block transport. A schematic of this situation referred to as spin blockade is shown in figure 1.11. In this case the electron in the right dot is spin up. Since there is a random distribution of electron spins in the leads there is an equal probability of spin up or spin down electron entering the left dot. If the electron is spin down, then the two electrons have different spin and can both occupy the right dot with no problem. Once the new electron has tunneled to the right dot it can then exit the system. The problem occurs when a spin up electron enters the left dot. The triplet state formed by the two spin up electrons has a much higher energy and prevents the new electron from tunneling from the left to right dot. Since the electron doesn't have anywhere else to tunnel it remains fixed in the left dot, blocking current leading to spin blockade. Interestingly, this provides a simple means of measuring the spin of the left electron, since spin is directly coupled to transport in this system. One could use this a preliminary testbed for spin based quantum information processing by looking at various means of manipulating the electron spin. For example one could prepare the blockade state, and then apply an electromagnetic pulse designed to rotate the left electron's spin. If the pulse is successful a small jump in current would be observed when the now unblockaded electron tunneled to the right dot and out of the system. This spin blockade based measurement scheme is a fundamental building block for other more robust spin readout schemes.

## Chapter 2

## Temperature-dependent electron mobility in InAs nanowires

Chapter contributions: Devices were fabricated by Yipu Song. Cryogenic measurements and data analysis were performed by Gregory Holloway and Yipu Song. Numerical simulations were carried out by Nupur Gupta.

### 2.1 Introduction

Semiconductor nanowires grown by the vapour-liquid-solid (VLS) method [16, 17, 18, 19, 20] are the subject of active study, with many potential applications ranging from nanoscale circuits [21] and gas sensors [22] to high-efficiency solar cells [23, 24, 25, 26]. In particular, InAs nanowires form Ohmic contacts easily[27], and can be grown with low structural defect densities [18], giving rise to high electron mobilities [28], though still low compared to high-quality bulk InAs [29]. The quasi-one-dimensional nature of electron transport at low temperatures [30] together with a spin-orbit coupling  $\sim 40$  times larger than GaAs makes InAs an attractive material for the development of spintronic devices such as electron spin qubits in gate-defined quantum dots [31, 32, 33]. Although transport in InAs nanowires is well-studied [34], the detailed role played by surface states and the surface potential [35, 36, 37, 38] with regard to the electron mobility is not well understood.

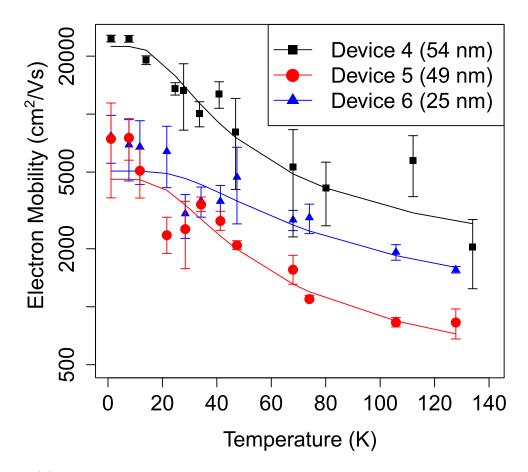

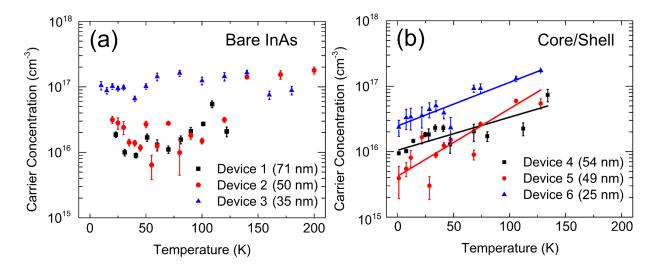

This chapter focuses on temperature dependent electron mobility measurements on InAs and  $InAs/In_{0.8}Al_{0.2}As$  core/shell nanowire field-effect transistors (FETs) that each

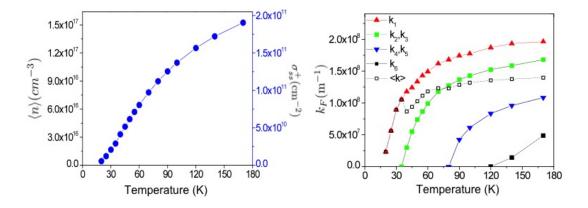

show a characteristic temperature dependence across a wide range of nanowire diameters. For pure InAs nanowires, mobility peaks in the range  $3,000-20,000 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  near 40 K, with a positive slope at lower temperatures and a negative slope at higher temperatures. Conversely, core/shell nanowires show increasing mobility with decreasing temperature. For comparison, mobilities seen in GaAs high electron mobility transistors often exceed  $10^{6} \text{ cm}^{2} \text{V}^{-1} \text{s}^{-1}$  [39], suggesting that carrier electrons in these nanowires experience numerous scattering events. In both types of nanowires, the temperature dependence at high temperature seems consistent with that of acoustic phonon scattering, but the experimental mobility is 2-3 orders of magnitude lower than expected [40]. A similar argument excludes optical phonon scattering as a dominant mechanism in this temperature range (it might dominate at even higher temperatures). We expect this to remain true even in quasi-one-dimensional systems, where phonon scattering is moderately enhanced due to a larger available phase space for scattering [41]. Furthermore, the experimental results are obtained on nanowires with low stacking fault densities, which we confirm for measured devices by using transmission electron microscopy. This excludes stacking faults from explaining this qualitative temperature dependence of mobility. On the other hand, the nanowire geometry suggests that a surface scattering mechanism should be dominant. Surface states are known to be present at densities  $\sim 10^{11} - 10^{12} \text{ cm}^{-2} \text{ eV}^{-1}$  and to act as electron donors. We argue that a sufficient density of these positively charged surface states should be more effective at scattering electrons than surface roughness (charge neutral defects), and therefore limit the mobility. Our numerical simulations show that surface charges at the known densities will indeed lead to scattering rates that produce mobilities of the correct order. We find that the decrease in mobility with temperature above  $\sim 50$  K can be explained by an increase in the number of ionized surface states, presumably due to thermal activation. Consistent with this picture, chemical treatment of the nanowire surface is seen to have a strong effect on the temperature-dependent mobility. Surface roughness scattering, on the other hand, should produce a weaker temperature dependence than what we observe [42]. The difference in the temperature dependence of mobility between the bare and core/shell nanowires is attributed to a decrease in the ionized impurity scattering rate due to the expitaxial shell. These results underscore the need for tailored surface passivation techniques [43, 44] to reduce the density of surface scatterers and smooth the local electronic potential, leading to increased carrier mobility and more ideal devices for a wide range of quantum transport, nanoscale circuitry and optoelectronics applications.

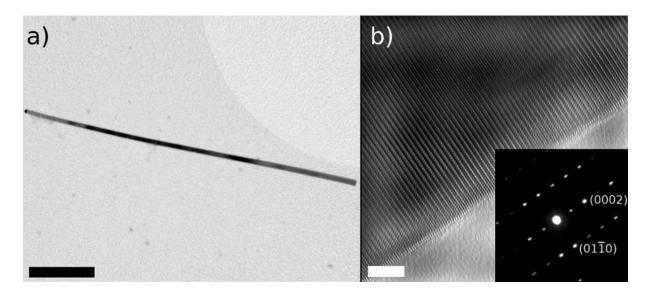

Figure 2.1: (a) Low and (b) high magnification bright-field TEM images of an InAs nanowire grown by GS-MBE at 0.5  $\mu$ m/hr. Scale bars are 500 nm in (a) and 5 nm in (b). The inset in (b) shows selected area diffraction pattern along the  $[2\bar{1}\bar{1}0]$  zone axis indicating pure wurtzite crystal structure. A majority of wires grown under these conditions had low stacking fault densities  $< 1 \ \mu$ m<sup>-1</sup>.

### 2.2 Nanowire growth by gas-source MBE

InAs nanowires were grown in a gas source molecular beam epitaxy (GS-MBE) system using Au seed particles.<sup>1</sup> A 1 nm Au film is heated to form nanoparticles on a GaAs (111)B substrate. For nanowire growth, In atoms were supplied as monomers from an effusion cell, and As<sub>2</sub> dimers were supplied from an AsH<sub>3</sub> gas cracker operating at 950°C. Nanowire growth proceeded at a substrate temperature of 420°C, an In impingement rate of 0.5  $\mu$ m/hr, and a V/III flux ratio of 4. The nanowires grew in random orientations with respect to the GaAs (111)B substrate, possibly due to the large lattice mismatch strain between InAs and GaAs. Transmission electron microscopy (TEM) analysis, shown in 2.1a, indicated a Au nanoparticle at the end of each nanowire (darker contrast at the left end), consistent with the VLS process <sup>2</sup>. Most nanowires had a rod-shaped morphology

<sup>&</sup>lt;sup>1</sup>Nanowires are grown by Chris Haapamaki in Ray LaPierre's group at the Centre for Emerging Device Technologies at McMaster University, Hamilton, Ontario, Canada. Technical assistance with the MBE was provided by Sharam Tavakoli

<sup>&</sup>lt;sup>2</sup>FIB operation and TEM images presented in this chapter were performed by Julia Huang and Fred Pearson at the Canadian Centre for Electron Microscopy, McMaster University, Hamilton, Ontario, Canada

with negligible tapering and a diameter ( $\sim 20 - 80$  nm) that was roughly equal to the Au nanoparticle diameter at the top of each nanowire, indicating minimal sidewall deposition.