# MachineFlow: A Web Tool to Adaptively Select EDA Tool Parameters for Digital ICs Using Statistical Learning

by

Ariq Emtenan

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2016

© Ariq Emtenan 2016

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Digital integrated circuits (ICs) are the driving force behind computing, communication and entertainment in today's world. More powerful and energy efficient ICs continue to be designed and built by the semiconductor industry to meet current demands. In addition, complexity in Electronic Design Automation (EDA) software continues to grow to keep up with the design and technological advances in ICs. Design parameters that control various aspects of EDA software, such as synthesis, placement and routing settings, can affect the performance of ICs, and current standard cell logic synthesis and physical design flow tools consist of hundreds of such parameters to be specified by the designer. Discovering the optimal value for each parameter can result in significant performance and power efficiency gains. In this thesis, we develop a proof of concept web tool that uses open source EDA software to generate datasets for a large number of circuits and uses the data to build predictive models using statistical learning techniques. We use these models to select design parameters for the VLSI physical design flow floorplanning and placement stages that minimize the total wirelength of the integrated circuit. Using empirical evaluation on three real-world test circuits, we show a 15x-35x reduction in time spent to discover predicted values of one of the studied parameters that reduces total wirelength with statistical significance compared to a brute force exploration of the design space, with an error rate below 5%.

The key contributions of this thesis are:

- Development of a web based tool to perform VLSI physical design flow of a standard cell based integrated circuit, as well as to generate and record datapoints at various stages of the flow.

- Development and investigation of predictive models through the web based tool, using the recorded datapoints and utilizing statistical learning techniques, to predict VLSI physical design flow floorplanning and placement tool parameters that minimize total wirelength in a particular integrated circuit.

#### Acknowledgements

I would like to thank Professor Siddharth Garg, my thesis advisor and mentor at the University of Waterloo. Professor Garg has provided me with the wonderful opportunity to participate at exciting research at the University of Waterloo and has been a source of encouragement, support and motivation throughout my studies. Professor Garg introduced me to the world of electronic design automation which has been the central theme of my research, as well as the tools and software used in this field. He encouraged me to develop my own ideas for my thesis while ensuring I was on the right track. I would like to thank him for the time, effort and energy he has spent on my research work.

I would also like to thank my co-supervisor Professor Hiren Patel. Professor Patel has also been a source of support to me during my studies and research work at the University of Waterloo. The weekly student paper presentation sessions organized by Professor Patel introduced me to contemporary research topics and greatly expanded my horizons.

I would also like to express sincere gratitude to Professor Peter Levine and Professor Mahesh Tripunitara. Professor Levine has helped me greatly by providing early feedback after reading my thesis and by making concrete suggestions that improve the thesis. I gained a better understanding of my research while thinking about and addressing Professor Levine's comments on my thesis.

Professor Mahesh Tripunitara taught me practical software engineering skills and techniques in my first semester at the University of Waterloo, which have been extremely valuable in many software projects I've worked on since, including the MachineFlow software project. I would also like to thank Professor Tripunitara for providing valuable feedback to me during the seminar and agreeing to be a reader for my thesis.

I would also like to thank the Electrical and Computer Engineering Department and Faculty at the University of Waterloo for allowing me to study and work in an environment that fosters creativity.

#### Dedication

I dedicate this thesis to my father Md. Abdul Kafi and my mother Mrs. Shanaj Kafi for their love, support and the sacrifices they've made to educate me and my sister Anika.

# **Table of Contents**

| Li | List of Tables v |           |                                                                            |    |  |

|----|------------------|-----------|----------------------------------------------------------------------------|----|--|

| Li | st of            | Figures   |                                                                            | x  |  |

| 1  | Intr             | oduction  | 1                                                                          | 1  |  |

| 2  | Bac              | kground   |                                                                            | 3  |  |

|    | 2.1              | Standard  | d Cell ASIC Design Flow                                                    | 4  |  |

|    | 2.2              | Motivati  | on for Optimizing Total Wirelength                                         | 6  |  |

|    |                  | 2.2.1 O   | On-chip Interconnects                                                      | 6  |  |

|    |                  | 2.2.2 T   | Cotal wirelength minimization in floor<br>planning and placement $\ . \ .$ | 7  |  |

|    | 2.3              | Related ' | Work                                                                       | 8  |  |

| 3  | Stat             | istical L | earning Methods For Regression                                             | 9  |  |

|    | 3.1              | Supervise | ed Learning and Regression Analysis                                        | 9  |  |

|    |                  | 3.1.1 R   | legression                                                                 | 10 |  |

|    |                  | 3.1.2 B   | Bias-Variance TradeOff                                                     | 11 |  |

|    | 3.2              | Linear R  | tegression                                                                 | 12 |  |

|    |                  | 3.2.1 O   | Ordinary Least Squares Regression                                          | 12 |  |

|    |                  | 3.2.2 R   | Regularized Linear Regression                                              | 12 |  |

|    | 3.3              | Non-line  | ar Regression                                                              | 13 |  |

|    |                | 3.3.1   | Decision Trees                                | 13 |  |

|----|----------------|---------|-----------------------------------------------|----|--|

|    |                | 3.3.2   | Random Forests                                | 15 |  |

|    |                | 3.3.3   | Gradient Boosting                             | 16 |  |

| 4  | App            | oroach  |                                               | 18 |  |

|    | 4.1            | EDA S   | Software and Design Parameters                | 18 |  |

|    |                | 4.1.1   | Open Source ASIC Flow: Qflow                  | 18 |  |

|    |                | 4.1.2   | EDA Design Parameters Tuned Using MachineFlow | 19 |  |

|    | 4.2            | Algori  | thm and Experimental Setup                    | 21 |  |

|    | 4.3            | Machi   | neFlow Web Tool                               | 23 |  |

|    |                | 4.3.1   | Features                                      | 24 |  |

|    |                | 4.3.2   | Implementation                                | 28 |  |

| 5  | $\mathbf{Res}$ | ults ar | nd Analysis                                   | 31 |  |

|    | 5.1            | Statist | ical Learning Approach                        | 31 |  |

|    |                | 5.1.1   | Feature Selection from Training Data          | 31 |  |

|    |                | 5.1.2   | Model Selection                               | 34 |  |

|    |                | 5.1.3   | Prediction Results                            | 42 |  |

|    | 5.2            | Brute   | Force Approach                                | 44 |  |

|    | 5.3            | Analys  | sis                                           | 46 |  |

| 6  | Cor            | clusio  | ns                                            | 49 |  |

|    | 6.1            | Summ    | ary of Contributions                          | 49 |  |

|    | 6.2            | Future  | e Work                                        | 49 |  |

| Re | References     |         |                                               |    |  |

| A  | PPE            | NDICI   | $\Xi \mathbf{S}$                              | 55 |  |

| A  | List           | of Int  | egrated Circuits Used to Build Training Data  | 56 |  |

|    |                |         | nd Model Selection Data                       | 58 |  |

# List of Tables

| 4.1  | Components of Qflow, an open source ASIC Design Flow Software Package                   | 19 |

|------|-----------------------------------------------------------------------------------------|----|

| 4.2  | Design Parameters in QFlow choosen to investigate predictive modeling                   | 20 |

| 4.3  | Common headers in Training CSV Files                                                    | 23 |

| 4.4  | ASIC Flow Results                                                                       | 25 |

| 4.5  | Predictive Model Parameters Available for Tuning                                        | 27 |

| 5.1  | Summary of Number of Rows Dataset                                                       | 32 |

| 5.2  | Summary of Acceptance Ratio Dataset                                                     | 32 |

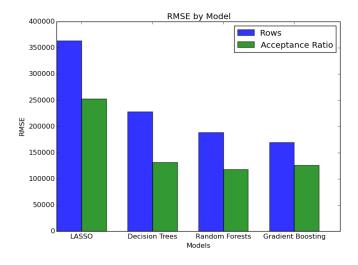

| 5.3  | LASSO: Mean RMSE Values                                                                 | 35 |

| 5.4  | Decision Trees: Mean RMSE Values At Each Maximum Depth Value                            | 37 |

| 5.5  | Random Forests: Mean RMSE Values                                                        | 37 |

| 5.6  | Gradient Boosting: Mean RMSE Values                                                     | 38 |

| 5.7  | Two's Complement Module - ASIC Design Flow Using Predictions from<br>Statistical Models | 43 |

| 5.8  | Ethernet MIIM Module - ASIC Design Flow Using Predictions from Statis-<br>tical Models  | 44 |

| 5.9  | Addition Module - ASIC Design Flow Using Predictions from Statistical<br>Models         | 44 |

| 5.10 | Shortest Wirelength through Brute Force Exploration                                     | 46 |

| 5.11 | Mann–Whitney-Wilcoxon test results                                                      | 47 |

| 5.12 | Percentage Differences and Speedups                                                     | 47 |

|      |                                                                                         |    |

| B.1  | LASSO Regression RMSE Values                                                                                                              | 58 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| B.2  | Decision Tree Model RMSE for Number of Rows Dataset                                                                                       | 58 |

| B.3  | Decision Tree Model RMSE for Acceptance Ratio Dataset                                                                                     | 59 |

| B.4  | Random Forest Model RMSE for Number of Rows Dataset                                                                                       | 59 |

| B.5  | Random Forest Model RMSE for Acceptance Ratio Dataset                                                                                     | 59 |

| B.6  | Gradient Boosting Model RMSE for Number of Rows Dataset                                                                                   | 60 |

| B.7  | Gradient Boosting Model RMSE for Acceptance Ratio Dataset                                                                                 | 60 |

| B.8  | Measured Total Wirelength for Two's Complement Module Circuit $\ \ . \ . \ .$                                                             | 60 |

| B.9  | Measured Total Wirelength for Ethernet MIIM Circuit                                                                                       | 61 |

| B.10 | Measured Total Wirelength for Addition Module Circuit                                                                                     | 61 |

| B.11 | Prediction Results with Random Forests (RF) and Gradient Descent (GM)<br>Models for Number of Rows Dataset for Two's Complement Circuit   | 61 |

| B.12 | Prediction Results with Random Forests (RF) and Gradient Descent (GM)<br>Models for Acceptance Ratio Dataset for Two's Complement Circuit | 62 |

| B.13 | Prediction Results with Random Forests (RF) and Gradient Descent (GM)<br>Models for Number of Rows Dataset for Ethernet MIIM Circuit      | 62 |

| B.14 | Prediction Results with Random Forests (RF) and Gradient Descent (GM)<br>Models for Acceptance Ratio Dataset for Ethernet MIIM Circuit    | 62 |

| B.15 | Prediction Results with Random Forests (RF) and Gradient Descent (GM)<br>Models for Number of Rows Dataset for Addition Circuit           | 63 |

| B.16 | Prediction Results with Random Forests (RF) and Gradient Descent (GM)<br>Models for Acceptance Ratio Dataset for Addition Circuit         | 63 |

| B.17 | Raw Data of Brute Force Number of Rows Exploration                                                                                        | 64 |

| B.18 | Raw Data of Brute Force Acceptance Ratio Exploration                                                                                      | 64 |

|      |                                                                                                                                           |    |

# List of Figures

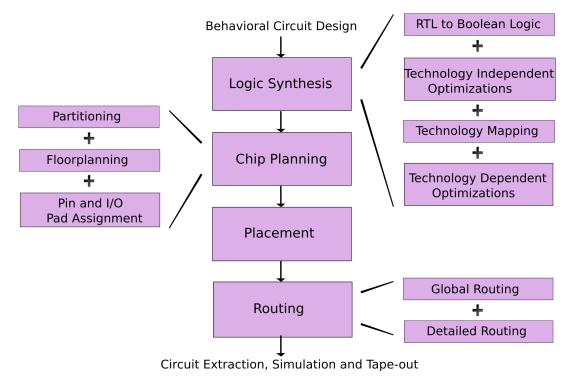

| 2.1 | Standard Cell ASIC Design Flow Steps                                                                                   | 4  |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

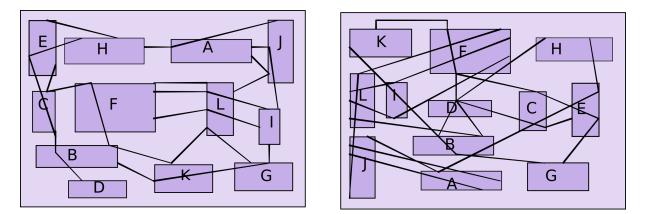

| 2.2 | Efficient(left) vs Inefficient(right) placement of same circuit                                                        | 8  |

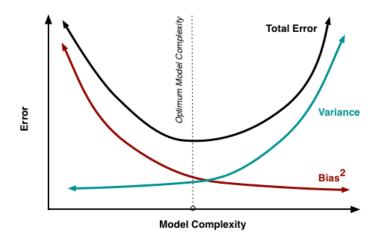

| 3.1 | The Bias-Variance Tradeoff [12]                                                                                        | 11 |

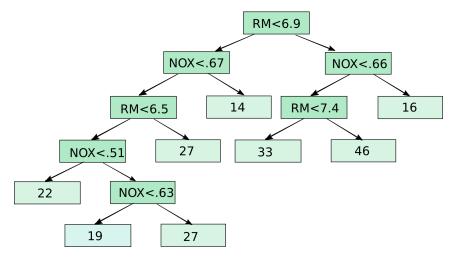

| 3.2 | Decision Tree                                                                                                          | 14 |

| 3.3 | Gradient Boosting Steps 1 and 2 [18]                                                                                   | 17 |

| 3.4 | Gradient Boosting Steps 3 and 4 [18]                                                                                   | 17 |

| 4.1 | Verilog File Upload                                                                                                    | 24 |

| 4.2 | Generating Training Data                                                                                               | 25 |

| 4.3 | Choosing features                                                                                                      | 26 |

| 4.4 | Training and Testing Models                                                                                            | 27 |

| 4.5 | Architecture of MachineFlow                                                                                            | 30 |

| 5.1 | Correlation Heatmap for Number of Rows Dataset                                                                         | 33 |

| 5.2 | Correlation Heatmap for Acceptance Ratio Dataset                                                                       | 34 |

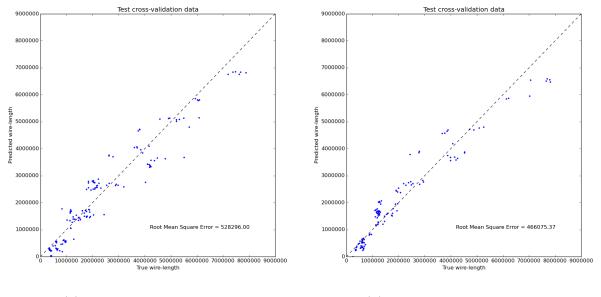

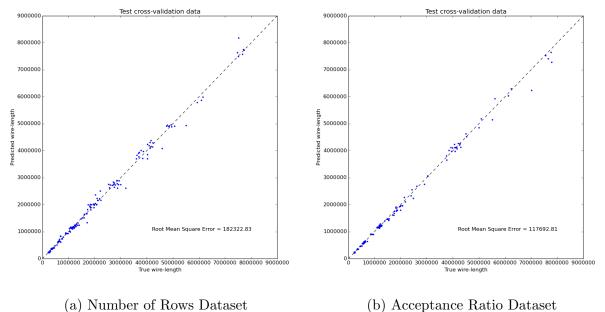

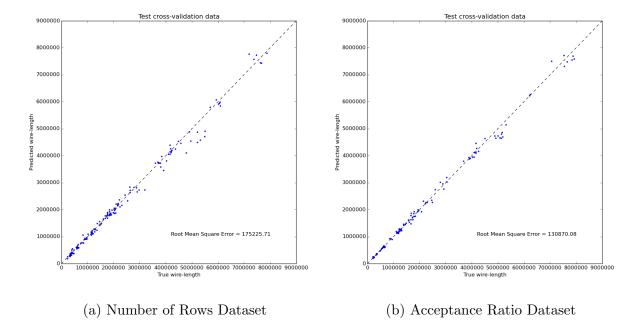

| 5.3 | LASSO Regression Test Scatter Plots<br>(one sample from each dataset) $\ . \ .$                                        | 36 |

| 5.4 | Random Forests Regression Scatter Plots<br>(one sample from each dataset) $% \left( {{{\rm{A}}_{{\rm{B}}}}} \right)$ . | 38 |

| 5.5 | Gradient Boosting Regression Test Scatter Plots(one sample from each dataset)                                          | 39 |

| 5.6 | Mean RMSE values for each model by dataset                                                                             | 39 |

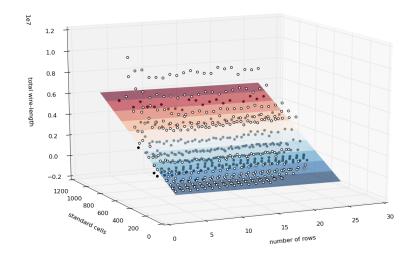

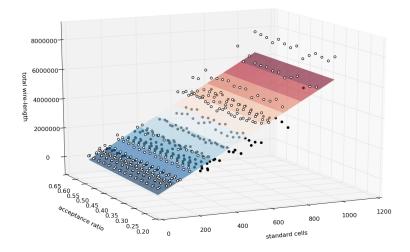

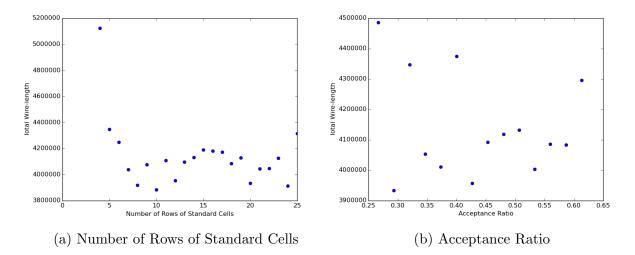

| 5.7 | Scatter Plot for Number of Rows Dataset in Floorplanning                                                               | 40 |

| 5.8 | Scatter Plot for Acceptance Ratio Dataset                                                                              | 41 |

- 5.9 Brute Force Exploration of Design Parameters of Two's Complement Module 45

- 5.10 Brute Force Exploration of Design Parameters of Ethernet MIIM Module .  $\quad 45$

- 5.11 Brute Force Exploration of Design Parameters of Addition Module . . . . . 46

## Chapter 1

## Introduction

The integrated circuit industry, in which digital integrated circuits have the largest marketshare, has been one of the core drivers in the current information revolution. Affordable and powerful electronic devices such as smartphones, tablets, laptops, as well as supporting backend infrastructure, such as data-centers and telecommunications networks have transformed the way humankind works, communicates and lives in today's world. Digital integrated circuits, such as microprocessors, memory chips, wireless and wireline tranceivers, sensors, displays and other ASICs form the core components in the devices driving this revolution.

Performance and power efficiency in digital integrated circuits have continued to improve to keep up with the demands in today's world, governed by Moore's law and Dennard scaling respectively. A dizzying array of design and technological improvements have kept both these trends alive for over 40 years. State of the art digital integrated circuits include the Intel Xeon <sup>®</sup> E5-2600 v3 processor which packs 5.56B transistors on a 31.9mm x 20.8mm die providing 18 dual threaded processor cores at upto 3.8GHz frequency[3]; and the Intel 6th generation Core processor with feature size of 14 nm built using tri-gate technology, consuming 90mW of power on idle[11].

Circuit designers rely on Electronic Design Automation software such as Synopsys Design Compiler, Synopsys IC Compiler, Cadence Encounter etc to create new digital integrated circuits. As the semiconductor industry evolves to accommodate more transistors at smaller geometries, EDA tools need to add an increasing number features to support these changes. For example, IC Compiler II, the current Place and Route solution from Synopsys, allows designers to add trigate transistors known as FinFETs to their designs. Support for FinFETs adds a new power optimization metric to enable designers to balance power goals[36]. This adds to existing design parameters that designers already need to manually tune during the design process; for example, during the floorplanning stage using Cadence Encounter tool, designers can set values for the desired aspect ratio, core utilization, core margins, row spacing and so on[8]. Some of these parameters have default values, but the designer can get better results by using a value different from the default based on the circuit under design. For example, the core utilization metric which determines the density of standard cells in the core has a default value of 70% to make room for in place optimization and clock tree synthesis cells - however for more complex designs the designer can get better results by reducing the default utilization value.[8].

Support for new features results in an increase in the complexity of EDA Tools, and designers have to tune an increasing number of design parameters. This takes a toll on engineers working in design roles[35]. Over the years, while IC Complexity has grown by 58 percent, designer productivity has grown by 21 percent, resulting in the phenomenon known as the design productivity gap[1].

The other effect of increasing complexity in the integrated circuit design process is the widening supply gap between IC design and software engineers[19]. Many students in Engineering at University look for a quicker return on their education and choose a career in the software industry instead of devoting more time in post-graduate education needed for an IC designer position. Building better tools that allow students to retain their interest in circuit design in their undergraduate education is a challenge that needs to be solved to combat this gap.

The objective of this thesis is two-fold. The first objective is to create an intuitive web based interface on top of open source EDA Software to perform the ASIC design flow, using a cloud computing paradigm to perform the design flow on a server through actions by users on a web browser. The second objective is to incorporate features in this web-based tool that uses statistical learning models to simplify certain aspects of the digital integrated circuit design process, in particular, automating the selection of EDA tool parameters that minimize the total wire-length of the integrated circuit. We study various predictive models to evaluate the best approach, and explore the effectiveness of these models in selecting design parameters for the VLSI physical design flow floorplanning and placement stages.

In summary, through this thesis, we demonstrate a way to address the EDA tool complexity issue, helping improve designer productivity and making the EDA tool more approachable for undergraduate students interested in integrated circuit design by utilizing a familiar and intuitive web based solution.

## Chapter 2

## Background

Digital integrated circuits can be designed using a number of implementation strategies. Custom circuit methodology involves building the circuit topology and performing the physical design without using design automation tools. Custom circuits can achieve the best performance, but is expensive and time consuming to design. Semi-custom methodology, or standard cell based design, involves using a library containing a fixed number of standard cells such as logic gates with different fan-in and fan-out counts to implement the design. This approach yields more time savings as design automation tools such as logic synthesis tools and automating placement and routing tools can be used to generate the schematic from ta high level description language such as VHDL or Verilog, significantly reducing the design effort. However, performance of the design can lag behind custom design as fine-tuning the design is harder due to the limited number of gates in the standard cell library.

Standard cell based methodology is now the dominant approach to circuit design, with the majority of integrated circuits in production today built using this approach. For example, in the Intel Pentium (R) 4 Processor, released in the year 2000, only the phase locked-loops and the clock buffers were designed manually, with virtually all other portions designed using standard cell methodology[31]. More modern processors, such as a RISC-V processor built using 45nm Silicon on Insulator technology[23], are designed and implemented entirely using the standard cell methodology. The RISC-V processor design involves writing the RTL in a high level language which is synthesized to Verilog, and using Synopsys physical design tools to map the Verilog to a 45 nm standard cell library. The processor design consists of 425K standard cells.

In the rest of this chapter, we take a look at the standard cell ASIC design flow and

Electronic Design Automation tools for the standard cell methodology.

## 2.1 Standard Cell ASIC Design Flow

The standard cell ASIC design flow, which is the name given to the series of steps to realize a taped out circuit ready for fabrication from a behavioral description of the circuit in a hardware description language, consists of the steps shown in figure 1 and briefly described below.

Figure 2.1: Standard Cell ASIC Design Flow Steps

Logic Synthesis Once a circuit is designed, logic synthesis translates the Register-Transfer Level(RTL) behavioral description of the circuit to a structural model, initially comprising of generic gates. After this step, a series of optimization steps are performed to improve the delay, power and area metrics of the circuit. For standard cell methodology, multi-valued logic minimization[6] and the use of Boolean Satisfiability for formal verification of the synthesized circuit are the popular optimization strategies used. The next step in logic synthesis involves a transformation to an electrical representation by mapping the generic gates to a particular implementation architecture, such as the logic libraries, embedded memories etc available for GLOBALFOUNDRIES 28-nm technology. A series of further optimization steps are performed. The resulting output is a netlist, a network of gates in the implementation technology.

- Chip Planning Chip planning involves identifying and planning the arrangement of blocks and large modules in a circuit, such as caches, sensors, power converters and other intellectual property cores. These modules usually have known area and positional characteristics. Chip planning is useful as it can provide an early estimate of delay, power and area of a chip, allowing designers to identify areas of improvement[20]. Chip planning consists of:

- Partitioning When the modules in a circuit are not specified clearly, partitioning is used to identify these modules[20]. Partitioning helps to divide the design into smaller subcircuits, each of which can operate somewhat independently from the rest. The main goal of partitioning is to perform the partitions in such a way that the connections between subcircuits is minimized, minimizing delay and improving modularity. Some popular partitioning algorithms used by EDA tools are the Kernighan-Lin algorithm and the Fiduccia-Mattheyses algorithm.

- Floorplanning Floorplanning is the arrangement of the subcircuits on the chip. The aspect ratio and position of each module is determined during this stage. Floorplanning optimization goals include a combination of minimizing the area of the bounding box consisting of all floorplan blocks, and minimizing the total wirelength. Cluster growth, where floorplan is constructed by iteratively adding blocks until all blocks have been assigned, and the simulated annealing algorithm, which will be discussed later, are widely used iterative approaches to solving the floorplanning issue.

- Pin Assignment Pin assignment is the assignment of a location to every pin that has an external connection, such as an I/O Pad. The main objectives in Pin Assignment are the reduction in electric parasitics and wirelength.

- **Placement** Once chip planning is completed, in the placement stage of the design flow, each standard cell is assigned a location and orientation while ensuring no overlap occurs and all design constraints are met. The optimization objectives in the placement stage include estimated total wirelength, signal delay and routing congestion minimization. To perform placement, first a cost function is devised to model the placement problem. Next the two approaches that are used are a) analytic approach -

mathematical analysis is used to find optimal value of the cost function(eg. quadratic placement, force-directed placement) and b) stochastic approach - randomized moves are used to search for a configuration with a low cost(eg. simulated annealing).

- **Routing** The routing stage inserts wires needed to connect the placed standard cells of the circuit. The routing task is divided into two stages to manage the complexity of the task.

- Global Routing During global routing, the routing region is broken into tiles, and connections between tiles are determined by respecting the design rules and maximizing routing utility functions, such as wirelength or critical path minimization. In this way an approximate path is found between the pins of different standard cells, and between pins of standard cells and I/O pads. The global routing tiles and interconnections are modeled as a graph, and graph search algorithms such as maze search, A\* search and line search are used for both global and detailed routing.

- Detailed Routing In the detailed routing stage, the connections between tiles discovered in the previous stage are made concrete, by assigning specific tracks, vias and metal layers to these connections.

## 2.2 Motivation for Optimizing Total Wirelength

In this thesis, we explore using statistical learning techniques to speed up floorplanning and placement design parameter selections that minimize total wirelength. In this section we take a deeper look at interconnect wires and the motivation for choosing total wirelength minimization as our optimization goal.

### 2.2.1 On-chip Interconnects

On-chip interconnect wires in todays integrated circuits introduce a number of parasitics that affect the integrated circuits behaviour. Each parasitic causes an increase in signal propagation delay and energy dissipation and adds additional noise to an integrated circuit. These parasitics are

• Resistance - Resistance in wires is directly proportional to the length of the wire and indirectly proportional to the area of the wire. In high frequencies, an additional

resistive effect, skin effect is also present, which is most common in wires carrying high frequency clock signals. Copper is the most popular material used in wires.

- Capacitance In todays circuits with multiple metal layers, capacitance has a large effect in circuits behavior, since capacitance manifests not only between a metal wire and its semiconductor substrate dielectric layer, but also between wires at different layers. Capacitance consists of parallel plate capacitance and fringing capacitance. The most common dielectric material used in integrated circuits is Silicon dioxide.

- Inductance Inductance is also prevalent in modern integrated circuits with high clock frequencies, causing effects such as switching noise, ringing and overshoot effects, and reflection of signals [31].

As device geometries have decreased, wires have not scaled down in an ideal fashion. In particular, while local interconnections have scaled down with device geometries, global interconnections which provide connectivity between subcircuits of the integrated circuit and with I/O have lengths which are proportional to either the die size or the complexity of the circuit[31]. Total wire length on a chip is expected to amount to around 7 km/cm by the year 2020. Other studies have shown that delay of global wires increase 50 percent per year[31], in contrast to gate delay which reduces with device geometry. As a result, interconnect delays caused by parasitics have surpassed gate delay as the major source of latency in an integrated circuit.

### 2.2.2 Total wirelength minimization in floorplanning and placement

Total wirelength minimization is a key optimization goal in the both the floorplanning and placement stage. A shorter total wirelength between the different blocks used for floorplanning can reduce signal propagation delays and power consumption. It also improves the routability of the integrated circuit, as it increases the amount of routing resources needed to route all standard cells and pins of the chip. Finally, since long wires between floorplan blocks can lie on the critical path of the circuit, minimizing the total wirelength between blocks is desirable from a timing closure aspect of the design process, such that the clock frequency requirements are met.

For placement, all three points mentioned in the previous paragraph applies, only the interconnects are now between standard cells instead of modules of the integrated circuit.

The figure shows the effect efficient versus inefficient placement can have on the total wirelength.

Figure 2.2: Efficient(left) vs Inefficient(right) placement of same circuit

## 2.3 Related Work

A number of studied have been conducted earlier that explore the use of learning algorithms to efficiently select EDA tool parameters. Wah et al [38] have explored using Genetic-basedlearning to study parameter selection for Timberwolf Placement and Routing tool in order to reduce cost of placement and routing. Other studies [21] [25] have focused on using learning algorithms to efficiently select FPGA CAD tool parameters. A recent study by Ziegler et al [41] has explored using learning algorithms to tune VLSI flow parameters for the synthesis stage where the objective is to minimizing timing.

Our work is distinct from these other studies in the sense that we use statistical/machine learning algorithms to adaptively select VLSI digital flow parameters for the floorplanning and placement stages by focusing on minimizing the total wirelength.

## Chapter 3

# Statistical Learning Methods For Regression

In this chapter, we take a look at statistical learning methods for regression that are utilized to predict the total wirelength of an integrated circuit from its features in the next chapter.

## 3.1 Supervised Learning and Regression Analysis

Given a dataset containing a set of variables denoted as inputs where each input has an output as shown in equation 3.1, supervised learning is the process of learning a mapping from inputs to outputs. Based on this mapping, the goal of supervised learning is to make a prediction of the output given a certain input.

$$X = \begin{vmatrix} x_{11} & x_{12} & \dots & x_{1n} \\ x_{21} & x_{22} & \dots & x_{2n} \\ \vdots & \vdots & \vdots & \vdots \\ x_{m1} & x_{m2} & \dots & x_{mn} \end{vmatrix} \quad Y = \begin{vmatrix} y_1 \\ y_2 \\ \vdots \\ y_m \end{vmatrix}$$

(3.1)

Supervised learning is categorized into classification and regression.

• Classification - Outputs and predictions take discrete or categorical values. One example of classification is using the iris dataset [2] to predict the type of iris plant from the physical measurements of its flower, such as the petal length, height etc.

• Regression - Outputs and predictions take continuous values. One example of regression is using the abalone dataset[2] to predict the age of an abalone from its physical measurements, such as length, diameter, height and so on.

#### 3.1.1 Regression

We focus on regression for the rest of the chapter. Regression in supervised learning can be further subcategorized as either linear or non-linear regression. A model is said to be linear when the each term in the output function is a sum of either a constant or a product of a single parameter and an input, as shown below

$$Y = \beta_0 + \beta_1 x_1 + \beta_2 x_2 + \dots \tag{3.2}$$

On the other hand, a model is non-linear when it does not follow equation 3.2. A term can contain more than one parameter per input for example, as shown below

$$Y = \beta_0 + \beta_1 \beta_2 x_1 + \dots \tag{3.3}$$

Non-linear regression is preferred for problems where a linear regression is unable to fit the data as it allows the model more degrees of freedom.

Once a regression model is trained using a training dataset, the performance of the model can be assessed by using a test dataset and evaluating the error of the prediction generated by the model compared to the actual output. The following two error measurements are typically used for regression models:

• Root Mean Squared Error - Root mean squared error measures the deviation of the actual output values from the regression prediction line. It is given by the equation 3.4

$$RMS = \sqrt{\frac{1}{n} \sum_{i=1}^{n} (y_i - prediction(x_i))^2}$$

(3.4)

• Mean Absolute Error - Mean absolute error is a measure of the average of the absolute values of errors between the predictions and the actual output using a test set, given by the equation 3.5

$$MAE = \frac{1}{n} \sum_{i=1}^{n} |y_i - prediction(x_i)|$$

(3.5)

#### 3.1.2 Bias-Variance TradeOff

One of the important considerations when choosing a statistical learning model is the biasvariance tradeoff. Bias can be defined as the true error of the model used to predict the sample dataset. A model is said to have high bias if the model is too simple and does not fit the data well, leading to underfitting. Variance, on the other hand, is defined as the variability of a model for a given datapoint. High variance leads to overfitting, which means the model is too closely adapted to the training data and does not generalize well, leading to a big difference between errors on the data used to train the model, versus the data used to test the model. The expected prediction error of a regression fit for a particular input  $X = x_0$  can be expressed with bias and variance terms as

$$Err(x_0) = Irreducible Error + Bias^2 + Variance[13]$$

(3.6)

In an ideal world, models should exhibit low bias and low variance. If a model has high bias, both training and test error will be high, while if a model has high variance, the training error will be low while test error will be high. If we try to make the hypothesis model used to predict the sample data more complicated to reduce bias, variance is increased as the model has overfit on the training data. This leads to the bias-variance tradeoff shown in Figure 3.1.

Figure 3.1: The Bias-Variance Tradeoff [12]

In the next few sections we explore some linear and non-linear models for regression that tackle the bias-variance tradeoff by using strategies such as regularization and ensembles.

## 3.2 Linear Regression

#### 3.2.1 Ordinary Least Squares Regression

Ordinary least squares regression(OLS) is a common linear regression method which involves picking coefficients of the vector  $\beta$  that minimizes the residual sum of squares(equation 3.7) for the training set given in equation 3.1. Residual refers to the signed difference between true target y and the prediction  $\hat{y}$ .

$$RSS = \sum_{i=1}^{n} (y_i - \hat{y}_i)^2$$

=

$$\sum_{i=1}^{n} (y_i - \beta_0 - \sum_{j=1}^{m} x_{ij}\beta_j)^2$$

(3.7)

Using the residual sum of squares as a cost function, a gradient descent algorithm gives a solution of predicted  $\beta$  as

$$\hat{\beta} = (X^T X)^{-1} X^T y \tag{3.8}$$

The full derivation of the equation is given by Hastie, Tibshirani and Friedman[13]. Once  $\hat{\beta}$  is calculated, the predicted  $\hat{y}$  can be calculated as  $\hat{y} = X\hat{\beta}$ .

#### 3.2.2 Regularized Linear Regression

OLS regression has one limitation that reduces its usefulness in modern statistical learning. OLS regression can display high variance resulting in overfitting on the training data and capturing its idiosyncrasies, instead of generalizing. This is due to the fact that OLS does not have a mechanism to throttle back when it overfits[4]. To control overfitting, a number of methods such as subset selection (setting some input variables to 0), shrinkage (shrinking some input variables) and hybrid methods have been developed. Together these approaches are known as regularization of linear regression, as a regularization parameter is introduced to the cost function of linear regression as a control to fitting parameters.

#### LASSO

One approach to regularized linear regression is the Least Absolute Selection and Shrinkage Operator(Lasso)[37]. Lasso regression is formulated by adding a coefficient penalty to the OLS minimization problem in equation 3.7, such that equation 3.7 is minimized with the condition

$$\sum_{j=1}^{p} |\beta_j \le t| \tag{3.9}$$

The bound t acts as a tuning parameter. Lasso regression balances the contradictory goals of minimizing the residual sum of squares, and minimizing the sum of absolute values of coefficients. A large value of t results in normal OLS regression. A small value of t greater than 0 results in solutions of  $\beta$  that are shrunken versions of what are obtained from OLS regression, or even with some coefficients set to 0. This reduces the number of input variables in the prediction, or the influence of certain input variables, resulting in lower variance. Lasso solutions can be obtained by utilizing numerical analysis or through the Least Angle Regression algorithm[13].

### 3.3 Non-linear Regression

When the training data consists of many features that interact with each other in complex, non-linear ways, global functions given by linear models such as OLS regression or regularized regression cannot model the data accurately. Non-linear models such as decision trees come into play for these situations.

#### 3.3.1 Decision Trees

A binary decision tree is a representation of a function that predicts a response or a class Y from a series of inputs  $X_i$ . At each branch of a decision tree, a test is conducted on one of the inputs. Each branch leads to another branch, or to an output. Depending on the result of the test, values that resolve to true go in one direction, and false go to a different direction. Eventually at a leaf node a prediction is made which aggregates all training data points leading to that leaf node[33].

#### **Regression Trees**

A decision tree used for regression is called a regression tree. In a regression tree, the output variables of the training data are continuous valued and the prediction error is measured by taking the squared difference between the observed and predicted values. One example of a regression tree with two input variables is given in the Figure 3.2, which is models Boston housing data from 1978[15]. The goal of the tree is to predict MEDV - Median value of owner occupied homes in \$1000's. The input variables to the regression tree are:

- RM Average number of rooms per dwelling

- NOX Nitric oxides concentration, pphm

Using the regression tree in Figure 3.2, we can make the prediction that given the average number of rooms per dwelling is greater than 6.9 and the Nitric oxides concentration is greater than 0.66 pphm, the median value of a home was \$16,000 in 1978.

Figure 3.2: Decision Tree

#### **Regression Tree Construction**

To grow a regression tree, the algorithm needs to make a number of decisions regarding which input splitting variables j to use at branches, and the split point s for each input variable. Finding the optimal partitioning of data for a decision tree is NP-Complete[17]. As a result, popular decision tree growing algorithms use a greedy approach. For each input

splitting variable, the training data is first divided into two regions  $R_1(j, s) = X | X_j \leq s$ and  $R_2(j, s) = X | X_j \geq s$ , each region is approximated by its average value of y, and then the sum of squared error is calculated. For each splitting variable j an exhaustive search finds the split point s that minimizes this sum of squared error. This procedure is repeated for each splitting variable until j and s are found that minimize overall sum of squared error[13].

After splitting variables and points have been discovered for the regions  $R_1$  and  $R_2$ , the algorithm continues, splitting each region in farther regions and finding the best split variables and points for each. The recursive process stops when a stopping criterion is reached, such as a given tree depth or too small a change sum of squared error. Pruning the tree is pursued in some cases to find a subtree that minimizes the sum of squared error further.

#### Limitation of Decision Trees

Although decision trees are a good model to capture non-linearities in the training data, they display high variance. This is due to the hierarchical nature of the tree construction process that can cause errors at the top nodes of a tree to affect the rest of the tree[27]. Decision trees display low bias, but some bias error is seen due to the greedy nature of tree construction where local cost functions are minimized. In the next few sub-sections we take a look at some techniques to reduce variance and improve the performance of decision tree based models.

#### 3.3.2 Random Forests

Developed by Adele Cutler and Leo Breiman [7], random forests consist of a collection of decision tree models. The random forest algorithm introduces two randomizing aspects to a decision tree based model building process.

- 1. Random sampling with replacement A bootstrap sample consists of a random selection of several datapoints from the training data with replacement. In random forests, a number of bootstrap samples each containing a subset of the training data are used to generate a sequence of decision tree models.

- 2. Random feature selection In addition, the random forest algorithm uses a random subset of attributes for each decision tree it constructs, leaving out some features in the bootstrap sample training data.

Once a collection of M trees  $f_m(x)$  are grown with these two randomizing objectives, for regression, the average of each tree is taken to obtain the resulting random forest model f(x), given by

$$f(x) = \sum_{m=1}^{M} \frac{1}{M} f_m(x)$$

(3.10)

By averaging the trees, the variance displayed by each tree is reduced. The variance is further reduced through random feature selection in each tree, as the trees are now de-correlated from each other in a random forest. Mathematically, Equation 3.11 shows the variance of M identically distributed random variables, each with variance  $\sigma^2$  and pairwise correlation  $\rho$ . Reducing pairwise correlation between the variables and increasing the number of M reduces overall variance.

$$Variance = \rho\sigma^2 + \frac{1-\rho}{M}\sigma^2 \tag{3.11}$$

#### 3.3.3 Gradient Boosting

Gradient boosting is an ensemble tree based learning model developed by Jerome Friedman[14] to solve regression problems. Gradient boosting works by training models sequentially, starting with simple models and moving up in complexity. Each tree in gradient boosting is trained on the error left behind by all trees trained before it[4]. The set of models are combined in the end to give a complex predictor. The following example illustrates the gradient boosting algorithm.

Given a training dataset illustrated as red dots in left panel of Figure 3.3, gradient boosting algorithm initially fits a decision tree of depth 1 on the data, given by the step function in left panel of Figure 3.3. Next, the error residuals are calculated for this model, which is illustrated using green dots in the right panel of Figure 3.3. Using the error residuals as training data, another decision tree of depth 1 is used to predict the error residuals, given by the step function in the right panel of Figure 3.3.

Figure 3.3: Gradient Boosting Steps 1 and 2 [18]

The two models in Figure 3.3 are added together to give a more complex model shown in the left panel of Figure 3.4. We see that the aggregated model has done a better job of predicting the training data compared to the single layer decision tree model in Figure 3.3. This series of steps is repeated, measuring the error residual after each combination, fitting a model to it and combining with earlier models until a stopping criterion is reached, such as the number of boosting stages. The overall prediction is given by a weighted sum of the collection of the individual models.

Figure 3.4: Gradient Boosting Steps 3 and 4 [18]

## Chapter 4

## Approach

In this chapter, we propose MachineFlow, a proof of concept web based ASIC design flow tool that allows integrated circuit designers to perform the following actions:

- Perform ASIC Design flow through an intuitive interface.

- Automate the selection of design parameters by

- Generating training data by varying design parameter values within a range.

- Building and using predictive models using statistical learning methods introduced in Chapter 3.

As highlighted in Section 2.2, we use total wirelength as the metric to optimize when selecting these design parameters adaptively. In particular, our statistical models are trained to minimize the **measured total wirelength after the routing step** of the ASIC flow completes, instead of an estimate of the total wirelength which is often used in existing EDA tools[20]. In the rest of this chapter, we describe the components, features and implementation details of Machineflow as well the experimental setup.

### 4.1 EDA Software and Design Parameters

#### 4.1.1 Open Source ASIC Flow: Qflow

MachineFlow is based on the open source and free digital synthesis flow tool chain, Qflow, developed by Tim Edwards[9]. Using Qflow, a digital circuit defined using the high-level

behavioral language Verilog can be physically laid out with a particular standard cell technology and fabrication process. Qflow does not support the cutting edge technologies supported by commercial EDA tools developed by companies such as Cadence and Synopsys, but it is a capable tool for generating the layout of smaller digital integrated circuits such as signal processing, communication, ALU circuits and so on. For example, openMSP430, a 16bit microcontroller, has been placed and routed by Qflow[9].

| Design Flow Stage | Component                                      | Function                                                      |  |

|-------------------|------------------------------------------------|---------------------------------------------------------------|--|

| Logic Synthesis   | Yosys[40]<br>ABC[5] (Included in Yosys)<br>ABC | ) RTL to Boolean Logic<br>Optimizations<br>Technology Mapping |  |

| Chip Planning     | TimberWolf[32]                                 | Partitioning, floorplanning, pin placement                    |  |

| Placement         | TimberWolf                                     | Placement                                                     |  |

| Routing           | TimberWolf<br>QRouter[10]                      | Global Routing<br>Detailed Routing                            |  |

Qflow tool chain consists of the following components:

Table 4.1: Components of Qflow, an open source ASIC Design Flow Software Package

We use a  $0.35\mu$ m standard cell technology provided by the FreePDK design kit[34] in MachineFlow as it is supported by default in Qflow. The  $0.35\mu$ m standard cell technology used is a 3-metal, 2-poly, n-well standard CMOS process originally developed American Microsystems Inc.

#### 4.1.2 EDA Design Parameters Tuned Using MachineFlow

To investigate if statistical learning techniques can be used to find the design parameters that minimizes total wirelength of an integrated circuit, we focused on two design parameters of Qflow, one in the floorplanning stage and another in the placement stage.

| Design Flow<br>Stage | Parameter                                      | Function Default Valu                                               |        |

|----------------------|------------------------------------------------|---------------------------------------------------------------------|--------|

| Floorplanning        | Floorplanning Number of Rows of Standard Cells |                                                                     | Square |

| Placement            | Acceptance Ratio                               | Determines<br>acceptance<br>probability of<br>new<br>configurations | 0.44   |

Table 4.2: Design Parameters in QFlow choosen to investigate predictive modeling

#### Number of Rows/Aspect Ratio

The number of rows of standard cells affects the area and shape of the global bounding box of an integrated circuit which in turn impacts the performance of an integrated circuit[20]. In Qflow, the number of rows defaults to a number that results in a square aspect ratio. Instead of using the default value, in MachineFlow we try to find an aspect ratio for the integrated circuit under design that will minimize total wirelength.

#### Acceptance Ratio

Acceptance ratio is a design parameter of the TimberWolf placement tool which uses simulated annealing for placement. Simulated annealing is a probabilistic method for finding the approximate global optimum of a combinatorial optimization problem. Annealing in this case refers to heating a system to a high temperature and cooling it down gradually so that ground state for the system is reached as the particles in the system rearrange in a perfectly crystallized state. In order for annealing to be effective, the cooling must be done in a way such that the particles have ample time to be rearranged and reach thermal equilibrium at each temperature involved in the cooling schedule.

In TimberWolf, to use simulated annealing for placement, a cost function C is defined whose major component is total estimated interconnect wirelength. Initially, the standard cells are randomly assigned. Next new states are generated for these cells by displacing cells, interchanging cells or changing the orientation of the cells. These new states are always accepted if change in cost  $\Delta C \leq 0$ , however they can also be accepted if this is not the case due to the hill climbing nature of the simulated annealing algorithm. The temperature parameter T controls the acceptance of new states. Initially during a high temperature regime, every hill climbing move is accepted. Next T is reduced in a manner that  $\Delta C$  is approximately the same at each temperature during a mid temperature regime. Finally a stopping criterion is reached which gives the final placement.

The parameter acceptance ratio  $\alpha$  comes into play during the mid temperature regime. The annealing schedule during the mid temperature regime is given by

$$s + = s + \gamma \frac{4\alpha(1 - \alpha^2)}{s^2(2 - \alpha)^2 \sigma^3(s)} [22]$$

(4.1)

Here s+ is the new inverse of temperature T. Lam et al[22] found that a value of  $\alpha$ =0.44 was ideal to decrease the temperature while maintaining an approximate of the thermal equilibrium needed for simulated annealing. Using MachineFlow, we investigate if we can use predictive models to find a value of  $\alpha$  for each integrated circuit under design that reduces total post routing wirelength.

### 4.2 Algorithm and Experimental Setup

To build predictive models to adaptively select the parameters in Section 4.1.2, we first build up a training dataset for each parameter. The training dataset consists of the following columns according to Equation 3.1:

- Input variables (X) Consist of the design parameter plus other circuit features.

- Design parameter The value of the design parameter is varied within a certain range and the total wirelength is measured for these values. For number of rows of standard cells N, MachineFlow allows designers to vary N from 2 to any integer greater than 2. In our training data, we limit N to 25 rows. For acceptance ratio, MachineFlow is designed to vary the value  $\pm 40\%$  of the default value of 0.44.

- Other circuit features Other circuit features, such as the number of standard cells, global routing tracks etc. are used as other input variables in the training data. A full list of these features is given in Table 4.3.

- Dependent variable (Y) The dependent variable is the total wirelength of the circuit measured after routing stage of the ASIC flow.

#### Algorithm 1 Algorithm for Design Parameter Optimization using Statistical Learning

| 1:  | procedure Training Data and Feature Selection                                                                                                                                              |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:  | Choose between <i>built-in</i> or <i>uploaded</i> initial training dataset                                                                                                                 |

| 3:  | Visually explore the chosen training dataset using boxplots and correlation heat map                                                                                                       |

| 4:  | for each <i>feature</i> that is derived from digital flow stage earlier than stage under examination, and shows <i>correlation</i> to target of over $0.5$ (pearson coefficient) <b>do</b> |

| 5:  | choose <i>feature</i> for final training dataset                                                                                                                                           |

| 6:  | Perform <i>test-train split</i> of training dataset and save. Randomly split data into:<br>train set $\leftarrow 75\%$ of data,<br>test set $\leftarrow 25\%$ of data;                     |

| 7:  | procedure Predictive Model Training & Design Parameter Optimization                                                                                                                        |

| 8:  | Select linear (LASSO) or non-linear (decision tree, random forests,<br>gradient boosting) regression model and build model using train set                                                 |

| 9:  | Use test set to calculate Root Mean Squared Error for chosen model                                                                                                                         |

| 10: | Select predictive model with lowest error, M                                                                                                                                               |

| 11: | Build model M with full training data, instead of using 75% of data                                                                                                                        |

| 12: | for each value of design parameter over its range do                                                                                                                                       |

| 13: | predict target(total post-route wirelength) using model M                                                                                                                                  |

| 14: | store design parameter and target in an associative array                                                                                                                                  |

| 15: | Find value of design parameter, V, from associative array that has smallest total wirelength                                                                                               |

| 16: | Set design parameter to V and perform a ASIC design flow.                                                                                                                                  |

The algorithm for design parameter optimization using statistical learning is given in Algorithm 1. The training data is comprised of 30 integrated circuits with Verilog sources obtained from OpenCores [28] and other sources. A full list of ICs used is provided in Appendix A. Training data is recorded by MachineFlow into two Comma-separated values (CSV) files, one for each design parameter. The training data is also randomly split into two sets, a training set and a test set. The test set contains 25 percent of the data and is not used to train the predictive models, but is held out to evaluate the model. The test set is also used to evaluate a cross-validation score to find the best model parameters, as defined in Section 4.3.1.

The common column headers for each CSV file is given below.

|                 | name                   | description                           |

|-----------------|------------------------|---------------------------------------|

| Common Features | cells                  | number of logic gates                 |

|                 | wire-bits              | number of wire bits                   |

|                 | stdcells               | number of standard cells              |

|                 | global-routing-tracks  | number of global routing tracks       |

|                 | stdcells-after-fillers | number of standard cells with fillers |

|                 | detail-routing-tracks  | number of detailed routing tracks     |

|                 | total-signals          | internal + input + output signals     |

|                 |                        |                                       |

| Target          | total-wire-length      | post routing total wire length        |

Table 4.3: Common headers in Training CSV Files

Once training data is generated, correlation between features and target of training data can be examined and features which show strong correlation can be selected to build predictive models. A number of linear and non-linear regression models are available to the circuit designer. The circuit designer chooses the model that gives the **lowest error rate** for the given training data. Next MachineFlow makes a **sequence of predictions** against this model, using the design parameter varied over the allowed range as input, along with other circuit features chosen earlier that show a strong correlation to the target. The predicted values of the total wirelength and the corresponding design parameters are stored in a key value data structure. We do a search on this data structure to find the value of the design parameter that corresponds to the **lowest total wirelength**. MachineFlow is then configured to use the chosen value of design parameter, and a ASIC design flow is performed.

### 4.3 MachineFlow Web Tool

MachineFlow is used to conduct the experiment described in the previous section. We explore the features, architecture and implementation details of MachineFlow in this section.

#### 4.3.1 Features

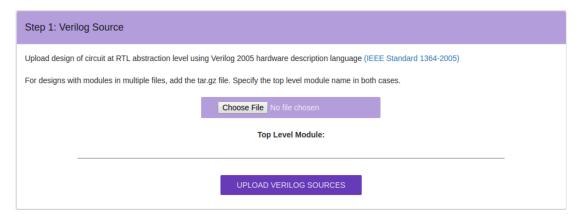

#### Simple ASIC Flow Interface

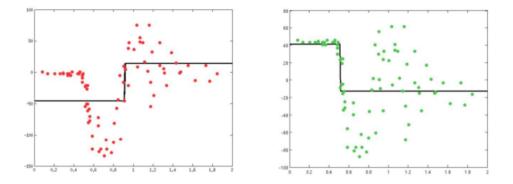

The ASIC flow interface of MachineFlow consists of a simple upload box for the design source. Users are able to submit the Register-Transfer level abstraction of their design using Verilog 2005(IEEE Standard 1364-2005) Hardware Description Language. For designs broken down into multiple Verilog modules in different files, users can upload the archived tarball compressed with gzip (tar.gz file). The top level module identifying the top module in the hierarchy needs to be specified. A screenshot of the ASIC Flow interface is shown in Figure 4.1.

Figure 4.1: Verilog File Upload

If any errors are encountered during the ASIC design flow, the error will be displayed to the user on the MachineFlow site. If no errors are encountered, the results of the ASIC design flow for the uploaded Verilog design is displayed to the user. The results obtained from ASIC design flow is tabulated in Table 4.4. Our objective is to generate a wide variety of data at different points of the design flow to aid us in building predictive models later.

| Presynthesis                                                                                                                                                   | Synthesis | Floorplanning          | Placement/Routing                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| num of wires<br>num of wires<br>num of wire bits<br>num of public wires<br>num of public wire bits<br>total wire bits<br>num of memories<br>num of memory bits | ° .       | rows of standard cells | standard cells with fillers<br>global routing tracks<br>detailed routing tracks<br>routing layers<br>horizontal tracks<br>vertical tracks<br>total wirelength |

| num of processes<br>num of cells                                                                                                                               |           |                        | total whereight                                                                                                                                               |

Table 4.4: ASIC Flow Results

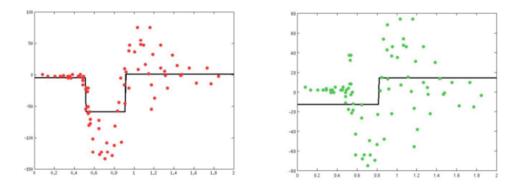

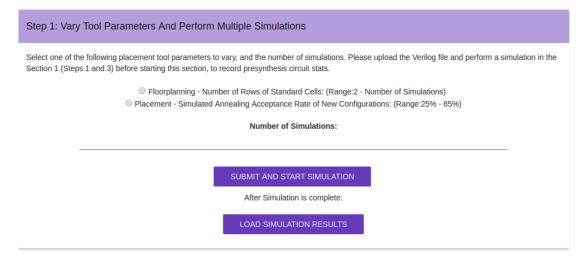

#### Versatile Training Data Generation

Training data can be generated by MachineFlow by choosing one of the available design parameters to tune and vary, and selecting the number of simulations to perform. The interface is shown in Figure 4.2.

Figure 4.2: Generating Training Data

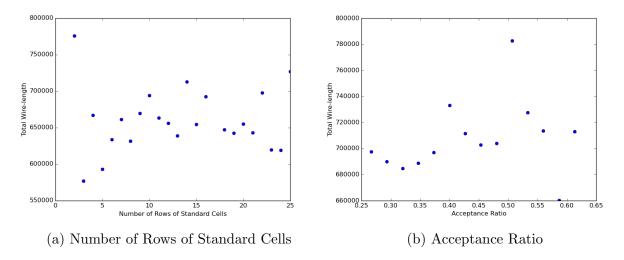

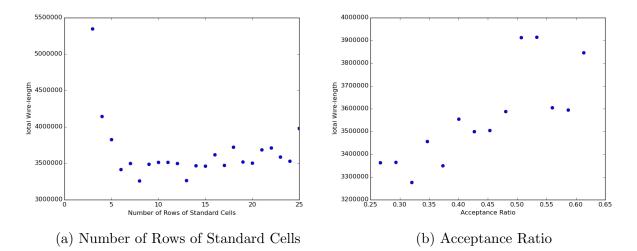

The output of this section is a graph showing the value of the total wirelength for each design flow performed using a particular value of the design parameter. This graph can be used to identify the value of design parameter that results in the shortest total wirelength through a brute force search.

In addition to generating training data, MachineFlow allows users to use existing training data. Figure 4.3 shows the interface which allows users to select the circuit features they want to use alongside design parameters to generate models.

| Step 1: Choose and Explore Datasets and Features                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <ul> <li>Upload CSV file as training dataset</li> <li>Choose Existing Training Dataset: The dataset consists of Verilog sources obtained from OpenCores and elsewhere.</li> </ul>                                                                                                                                                                                                                   |  |  |  |  |  |

| CHOOSE AND EXPLORE EXISTING TRAINING DATA                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| After choosing dataset, choose common dataset features to use as training variables(single or multiple):                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| <ul> <li>number of standard cells [post-synthesis]</li> <li>number of standard cells including filler cells [post-synthesis]</li> <li>number of cells [pre-synthesis]</li> <li>number of wire bits [pre-synthesis]</li> <li>global routing tracks [post-synthesis]</li> <li>detail routing tracks [post-synthesis]</li> <li>number of internal + input + output signals [post-synthesis]</li> </ul> |  |  |  |  |  |

| CHOOSE FEATURES                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

Figure 4.3: Choosing features

### Statistical Learning Method Integration

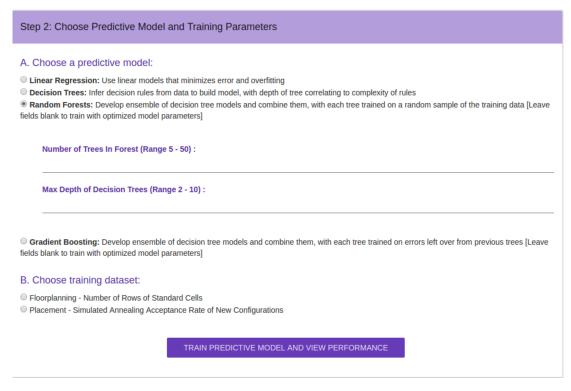

The interface to build predictive models using statistical learning techniques is shown in Figure 4.4. Each algorithm is implemented using the scikit-learn machine learning library [30]. For certain models the user can provide parameters for the models. Table X shows the confiurable parameters for each model. If the fields are left blank for the random forests and gradient boosting models, a scikit-learn feature called Grid Search is used by MachineFlow to generate a grid of parameter values and do an exhaustive search to choose the parameters that give the best cross-validation score.

| Model             | Parameter                                                                                   | Range                           |

|-------------------|---------------------------------------------------------------------------------------------|---------------------------------|

| Decision Trees    | Maximum Depth of Decision Tree                                                              | 2 - 10                          |

| Random Forests    | Number of Trees In Forest<br>Max Depth of Decision Trees                                    | 5 - 100<br>2 - 10               |

| Gradient Boosting | Number of Boosting Stages<br>Max Depth of Decision Trees<br>Learning Rate of Decision Trees | 5 - 100<br>2 - 10<br>0.01 - 1.0 |

Table 4.5: Predictive Model Parameters Available for Tuning

For the decision tree model, scikit-learn does not provide a mechanism to find the depth of the tree that minimizes root mean square error(RMSE). As a result, if the maximum depth of tree field is left blank, we measure the RMSE 3 times at each depth, average them, and choose the depth that minimizes RMSE.

Figure 4.4: Training and Testing Models

Once a model is chosen, the root mean squared error for the model is displayed to the user for train and test data scatter plots. Root mean squared error, as given in equation 3.4 is used to assess the performance of the model.

### 4.3.2 Implementation

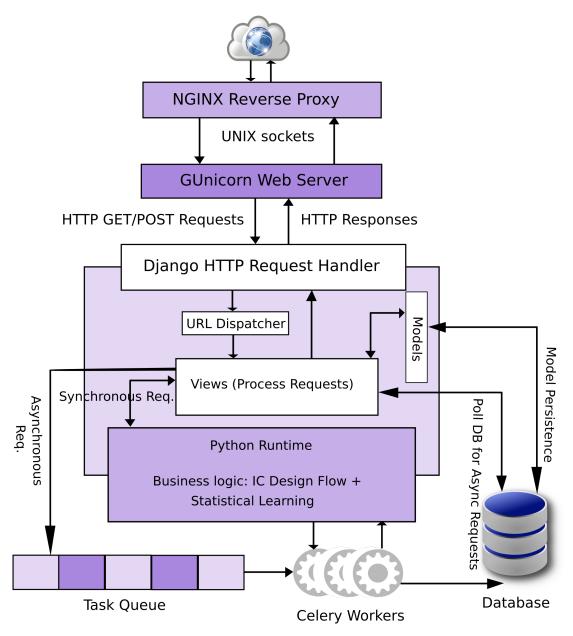

MachineFlow has been developed as a modern web application. The user interface has been implemented using HTML, Javascript, CSS and the Bootstrap front-end framework, while the backend has been implemented using Python and the Django web framework. SQLite has been used as the transactional database engine, while Gunicorn has been used as the HTTP web server and NGINX as the proxy server. Asynchronous requests are handled by the Celery distributed task queue. The workflow and architecture of MachineFlow is shown in Figure 4.5.

When a HTTP request comes in from a user's browser, it first hits MachineFlow's NGINX reverse proxy. A reverse proxy is used for load balancing, security, caching and as an additional layer of abstraction and anonymity. NGINX sends the HTTP request over to Gunicorn web server over UNIX sockets, since they are lighter and faster than TCP/IP sockets. We use Gunicorn over Django's built-in single threaded web server since Gunicorn is multi-threaded and can handle more than one request at a time. Gunicorn consists of a master process and worker processes. The master process monitors incoming requests and manages the worker processes, increasing or reducing their numbers based on the number of concurrent requests. Each worker process handles one request, with each worker basically carrying a copy of the web application to process the request.

Django HTTP request handler receives the request from Gunicorn and sends it to the URL dispatcher, which based on the URL, passes the request to the relevant view Python function. All business logic is contained within the views. For example, specific views start the ASIC design flow process, records generated data, build statistical learning models, make predictions and so on. Requests are processed by views and returned back to the user's browser. For requests which are asynchronous in nature, for example a request to perform multiple design flows while changing the design parameter inputs, the results are not returned immediately to the user, instead a real-time monitoring status for the task is shown. Asynchronous requests are placed in a task queue, where they are processed by Celery worker execution units. Once the task completes, the results are stored in the database, which is polled by Django. This result is then returned to the user.

In addition to data, MachineFlow also responds with relevant visualizations to the user. Visualizations are currently generated by the views using the Matplotlib plotting library[16] and saved as .png files on NGINX which acts as a server for static files, and served to the user on demand.

Python was chosen as the implementation language due to two reasons. First, there exist excellent data processing and statistical learning libraries in Python such as Numpy, Pandas and Scikit-learn which can be easily integrated with a Python web framework to process user requests and send responses to a browser. Secondly, Python is a simple to use interpreted, dynamically typed language allows which allows rapid iteration without compilation. This was instrumental in the fast development of the feature set of MachineFlow through quick develop-test cycles.

Figure 4.5: Architecture of MachineFlow

## Chapter 5

## **Results and Analysis**

We take two approaches to find the values of design parameters a) number of rows of standard cells and b) acceptance ratio described in Section 4.1.2 that minimize total wirelength. First we use predictive models to find the value of each parameter as described in Algorithm 1. Next we perform the same operation by taking a brute force approach. We use an integrated circuit which has not been included as part of the training data for these tests. We demonstrate the performance of the statistical learning approach in comparison to the brute force approach.

## 5.1 Statistical Learning Approach

### 5.1.1 Feature Selection from Training Data

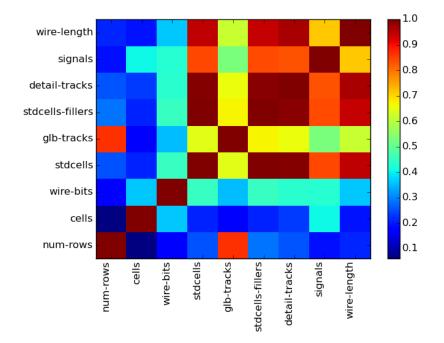

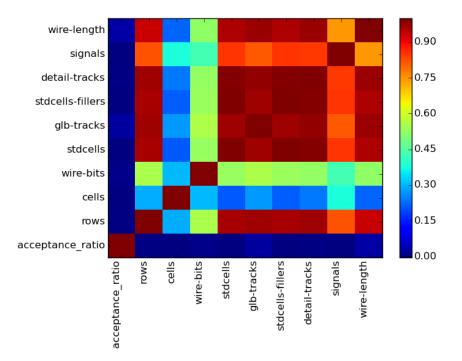

The training data for each design parameter is summarized in Tables 5.1 and 5.2, showing the count, mean, standard deviation, minimum, maximum and quartile values for each column. The number of rows dataset consists of 603 records while the acceptance ratio dataset contains 502 records. This summary is shown upon choosing a training dataset in MachineFlow.

The training dataset summary page also displays a correlation matrix for each variable in the dataset to investigate the dependence between them. Each element of the symmetric matrix is a correlation coefficient between the variables i and j. We use the Pearson correlation coefficient[29] which gives the linear correlation between two variables, with a value of +1 for absolute positive correlation, 0 for no correlation and -1 for absolute

|        | num-of-rows | cells | wire-bits | stdcells | stdcells-with-fillers | global-route-tracks | detail-route-tracks | total-signals | total-wire-length |

|--------|-------------|-------|-----------|----------|-----------------------|---------------------|---------------------|---------------|-------------------|

| count  | 603         | 603   | 603       | 603      | 603                   | 603                 | 603                 | 603           | 603               |

| mean   | 12.48       | 27.47 | 452.75    | 454.8    | 470.68                | 78.53               | 906.66              | 401.43        | 2402922.73        |

| std    | 6.17        | 27.59 | 294.65    | 267      | 269.36                | 39.96               | 545.16              | 236.96        | 1879075.01        |

| $\min$ | 2           | 2     | 81        | 70       | 71                    | 10                  | 135                 | 66            | 210190            |

| 25%    | 7           | 6     | 290       | 237      | 258                   | 46                  | 482                 | 205           | 1060535           |

| 50%    | 12          | 13    | 358       | 376      | 403                   | 73                  | 769                 | 397           | 1811670           |

| 75%    | 17          | 47    | 634       | 634      | 650                   | 104                 | 1268                | 520           | 3812650           |

| $\max$ | 25          | 121   | 1310      | 1044     | 1084                  | 198                 | 2322                | 1136          | 9540120           |

Table 5.1: Summary of Number of Rows Dataset

(The acceptance ratio for this dataset is the default value of 0.44)

| -      | acceptance-ratio | num-of-rows | cells | wire-bits | stdcells | stdcells-with-fillers | global-route-tracks | detail-route-tracks | total-signals | total-wire-length |

|--------|------------------|-------------|-------|-----------|----------|-----------------------|---------------------|---------------------|---------------|-------------------|

| count  | 502              | 502         | 502   | 502       | 502      | 502                   | 502                 | 502                 | 502           | 502               |

| mean   | 0.4403           | 9.47        | 28.69 | 355.23    | 382.01   | 393.45                | 62.59               | 769.12              | 344.46        | 2003895.07        |