# Second-Generation Stack Computer Architecture

**Charles Eric LaForest**

A thesis presented to the Independent Studies Program of the University of Waterloo in fulfilment of the thesis requirements for the degree Bachelor of Independent Studies (BIS)

Independent Studies University of Waterloo Canada April 2007

# Declaration

ž

I hereby declare that I am the sole author of this research paper.

I authorize the University of Waterloo to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Signature: Eine La Forest

I further authorize the University of Waterloo to reproduce this research paper by photocopying or other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Signature: Eric La Forest

The work in this research paper is based on research carried out in the Independent Studies Program at the University of Waterloo, Canada. No part of this thesis has been submitted elsewhere for any other degree or qualification and is all my own work unless referenced to the contrary in the text.

#### Copyright © 2007 by Charles Eric LaForest.

The copyright of this thesis rests with the author. Quotations and information derived from it must be acknowledged.

### **Second-Generation Stack Computer Architecture**

**Charles Eric LaForest**

### Submitted for the degree of Bachelor of Independent Studies April 2007

### Abstract

It is commonly held in current computer architecture literature that stack-based computers were entirely superseded by the combination of pipelined, integrated microprocessors and improved compilers. While correct, the literature omits a second, new generation of stack computers that emerged at the same time. In this thesis, I develop historical, qualitative, and quantitative distinctions between the first and second generations of stack computers. I present a rebuttal of the main arguments against stack computers and show that they are not applicable to those of the second generation. I also present an example of a small, modern stack computer and compare it to the MIPS architecture. The results show that second-generation stack computers have much better performance for deeply nested or recursive code, but are correspondingly worse for iterative code. The results also show that even though the stack computer's zerooperand instruction format only moderately increases the code density, it significantly reduces instruction memory bandwidth.

### Acknowledgements

Firstly, thanks go to my family, immediate and extended, who have always given me the leeway and support I needed, who always believed in me.

Sometime in 2000, Ralph Siemsen and Andrew E. Mileski introduced me to the Forth programming language, which changed my view of programming. Soon after, I discovered the microprocessors of Chen-Hanson Ting, Jeff Fox, and Charles H. (Chuck) Moore, which did the same for my view of computer hardware. Aaron Holtzman suggested I play with FPGA simulations of these computers, and graciously bore all my grumblings about broken Verilog compilers. At the same time, I had stimulating email discussions with Myron Plichota and Jecel Mattos de Assumpcao Jr. which led to some of the new ideas in this thesis.

It was Sheryl Cronk who eventually gave me the arguments and reasons to return to University. Many friends bought my old junk and helped me move. For this kick-start and support, I am forever grateful.

Once at Waterloo, Professor Chrysanne DiMarco became my Adviser. Her thorough knowledge of the English language and of the customs of academia improved me greatly. Thus, I must atone by myself for any linguistic errors in this thesis. Professors Giuseppe Tenti and Barry Ferguson unrusted and expanded my mathematical skills. Professor Manoj Sachdev and his PhD students, Shahab Ardalan and Bhaskar Chatterjee, took much time both inside and outside of class to discuss the details of VLSI circuitry with me. Professors Mark Aagaard helped me gain a broader perspective on computer architecture and led me to the class of Professor Paul Dasiewicz who taught me more about the subject. PhD candidate Brad Lushman took time to help me with my exploration of programming languages. I also thank Professor Anne Innis Dagg of Independent Studies, whose course on independent research rounded me out well.

Outside of class, the denizens of the Computer Science Club provided both enthusiastic discussions and gave me a chance to make my work heard. Mike Jeays provided me with a useful and rare primary source for the KDF9, his favourite computer. Professor Steven M. Nowick of Columbia University helped me understand his MINIMALIST synthesis tool.

The wheels of Independent Studies were kept turning by Professors Bill Abbott and Richard Holmes and especially by Susan Gow, who provided endless enthusiasm, countless good examples, and sage advice.

The writing of this thesis was supervised by Dr. Andrew Morton here at Waterloo, and by Professor J. Gregory Steffan of the University of Toronto. I am very grateful for their feedback and guidance.

And finally, thanks to Joy, my fiancée. You brighten my life. You make me happy. The years ahead with you glow with promise and adventure. "But the speed was power, and the speed was joy, and the speed was pure beauty."

- Richard Bach, Johnathan Livingston Seagull

"If my calculations are correct, when this baby hits eighty-eight miles per hour, you're gonna see some serious shit."

- Emmet "Doc" Brown, in Back To The Future

# Contents

| 1 | Intr | oductio | n                                |

|---|------|---------|----------------------------------|

|   | 1.1  | Resear  | rch Goals                        |

|   | 1.2  | Thesis  | Outline                          |

|   |      | 1.2.1   | Part I: Historical Review        |

|   |      | 1.2.2   | Part II: Qualitative Arguments   |

|   |      | 1.2.3   | Part III: Quantitative Arguments |

### I Historical Review

5

| 2 | Hist | ory of t | he First Generation of Stack Computers                            | 7  |

|---|------|----------|-------------------------------------------------------------------|----|

|   | 2.1  | Lukasi   | iewicz and the First Generation                                   | 7  |

|   |      | 2.1.1    | Poland: Jan Lukasiewicz (1878-1956)                               | 7  |

|   |      | 2.1.2    | Germany: Konrad Zuse (1910 - 1995)                                | 8  |

|   |      | 2.1.3    | Germany: Friedrich Ludwig Bauer (1924-)                           | 8  |

|   |      | 2.1.4    | Australia: Charles Leonard Hamblin (1922-1985)                    | 9  |

|   |      | 2.1.5    | USA: Robert Stanley Barton                                        | 10 |

|   | 2.2  | The Fi   | rst Generation of Stack Computers                                 | 11 |

|   |      | 2.2.1    | Zuse Z4                                                           | 11 |

|   |      | 2.2.2    | English Electric Co. KDF9                                         | 12 |

|   |      | 2.2.3    | Burroughs B5000 and later models                                  | 14 |

|   |      | 2.2.4    | International Computers Ltd. ICL2900 series                       | 16 |

|   |      | 2.2.5    | Hewlett-Packard HP3000                                            | 17 |

|   | 2.3  | Shortc   | omings and Disappearance of the First Generation                  | 18 |

|   |      | 2.3.1    | Explicit High-Level Language Support                              | 18 |

|   |      | 2.3.2    | The Rise of RISC                                                  | 18 |

|   |      | 2.3.3    | Excessive Memory Traffic                                          | 19 |

|   |      | 2.3.4    | The Need for Index Registers                                      | 20 |

| 3 | Hist | ory of t | he Second Generation of Stack Computers                           | 21 |

|   | 3.1  | Charle   | s H. Moore and the Second Generation                              | 21 |

|   |      | 3.1.1    | Charles Havice (Chuck) Moore II                                   | 21 |

|   |      |          | 3.1.1.1 The Forth Programming Language Basis of Second-Generation |    |

|   |      |          | Stack Computers                                                   | 21 |

|   |      | 3.1.2    | Philip J. Koopman, Jr.                                            | 22 |

|   | 3.2               | The Second Generation of Stack Computers3.2.1NOVIX NC4016                                                                                   | 23<br>23        |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|   |                   | 3.2.2 Harris RTX-2000                                                                                                                       | 23              |

|   |                   | 3.2.3 Sh-BOOM (Patriot Scientific IGNITE I)                                                                                                 | 23              |

|   |                   | 3.2.4 MuP21                                                                                                                                 | 25              |

|   |                   | 3.2.5 F21                                                                                                                                   | 26              |

|   |                   | 3.2.6 c18                                                                                                                                   | 26              |

|   | 3.3               | Recent Research                                                                                                                             | 26              |

|   | 3.4               | Strengths and Weaknesses of the Second Generation                                                                                           | 28              |

|   |                   | 3.4.1 The Need for Index Registers                                                                                                          | 28              |

|   |                   | 3.4.2 Stack Manipulation Overhead                                                                                                           | 28              |

|   |                   | 3.4.3 Poor Support of ALGOL-like Languages                                                                                                  | 29              |

|   |                   | 3.4.4 Reduced Instruction Memory Bandwidth and System Complexity                                                                            | 29              |

|   |                   | 3.4.5 Fast Subroutine Linkage and Interrupt Response                                                                                        | 29              |

|   |                   | II Qualitative Arguments                                                                                                                    | 31              |

|   |                   |                                                                                                                                             |                 |

| 4 |                   | inguishing the First and Second Generations                                                                                                 | <b>33</b><br>34 |

|   | 4.1<br>4.2        | Location of Stacks: In-Memory vs. In-Processor                                                                                              | 34<br>35        |

|   | 4.2               | Operations with Stacks: High-Level Language Support vs. Primitive Operations                                                                | 36              |

| _ |                   |                                                                                                                                             |                 |

| 5 | <b>Obj</b><br>5.1 | ections Cited by Hennessy & Patterson                                                                                                       | <b>37</b><br>37 |

|   | 5.1<br>5.2        | The Enormous Influence of Hennessy & Patterson on Computer Architecture .<br>The Disappearance of Stack Computers (of the First Generation) | 38              |

|   | 5.2<br>5.3        | Expression Evaluation on a Stack                                                                                                            | 39              |

|   | 5.4               | The Use of the Stack for Holding Variables                                                                                                  | 40              |

|   | 5.5               | Distorted Historical Arguments                                                                                                              | 40              |

|   | 0.0               |                                                                                                                                             |                 |

|   |                   | III Quantitative Arguments                                                                                                                  | 45              |

| 6 | A St              | ack-Based Counterpart to DLX: Gullwing                                                                                                      | 47              |

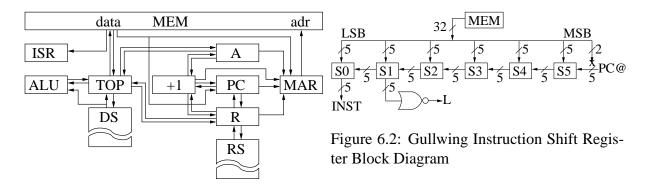

|   | 6.1               | Block Diagram                                                                                                                               | 47              |

|   |                   | 6.1.1 Memory Subsystem                                                                                                                      | 48              |

|   |                   | 6.1.1.1 Single Memory Bus                                                                                                                   | 48              |

|   |                   | 6.1.1.2 Differentiating Loads, Stores, and Fetches                                                                                          | 48              |

|   |                   | 6.1.2 Computation Subsystem                                                                                                                 | 48              |

|   |                   | 6.1.3 Control Subsystem                                                                                                                     | 48              |

|   | 6.2               | Instruction Set                                                                                                                             | 49              |

|   |                   | 6.2.1 Instruction Packing                                                                                                                   | 49              |

|   |                   | 6.2.2 Flow Control                                                                                                                          | 49              |

|   |                   |                                                                                                                                             |                 |

|   |                   | <ul><li>6.2.3 Load, Store, and Literal Fetch</li></ul>                                                                                      | 50<br>50        |

|   |     |          | 6.2.4.1 Synthesizing More Complex Operations                     | 51  |

|---|-----|----------|------------------------------------------------------------------|-----|

|   |     | 6.2.5    | Stack Manipulation                                               | 52  |

|   |     | 6.2.6    | No-Op and Undefined                                              | 52  |

|   |     | 6.2.7    | Instruction Format and Execution Example                         | 53  |

|   | 6.3 | State N  | Aachine and Register Transfer Description                        | 54  |

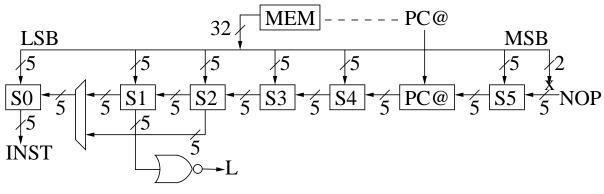

|   |     | 6.3.1    | Improvement: Instruction Fetch Overlap                           | 56  |

| 7 | Con | parisor  | ns With DLX/MIPS                                                 | 59  |

|   | 7.1 | Gullwi   | ing Benchmarks                                                   | 59  |

|   |     | 7.1.1    | Flight Language Kernel (Bare)                                    | 59  |

|   |     | 7.1.2    | Flight Language Extensions (Ext.)                                | 60  |

|   |     | 7.1.3    | Virtual Machine (VM)                                             | 60  |

|   | 7.2 | Compa    | arison of Executed Benchmark Code                                | 61  |

|   |     | 7.2.1    | Dynamic Instruction Mix                                          | 61  |

|   |     | 7.2.2    | Cycles Per Instruction                                           | 64  |

|   |     | 7.2.3    | Memory Accesses Per Cycle                                        | 65  |

|   |     | 7.2.4    | Instructions per Memory Word                                     | 67  |

|   |     |          | 7.2.4.1 Basic Blocks and Instruction Fetch Overhead              | 68  |

|   | 7.3 | Behavi   | iour of Iteration, Recursion, and Subroutine Calls               | 68  |

|   |     | 7.3.1    | Measured Properties                                              | 68  |

|   |     | 7.3.2    | Demonstrators                                                    | 69  |

|   |     | 7.3.3    | Iterative Triangular Numbers                                     | 70  |

|   |     | 7.3.4    | Recursive Triangular Numbers                                     | 72  |

|   |     | 7.3.5    | Tail-recursive Triangular Numbers                                | 74  |

|   |     | 7.3.6    | Subroutine Calls                                                 | 76  |

|   | 7.4 | Pipelin  | ing                                                              | 79  |

|   |     | 7.4.1    | Transforming the DLX Pipeline to Gullwing                        | 79  |

|   |     | 7.4.2    | Altering the ISR to Deal with the Additional Latency             | 81  |

|   |     | 7.4.3    | The Effect of Pipelining on Calls, Jumps, and the CPI            | 83  |

|   | 7.5 | Summa    |                                                                  | 84  |

| 8 | Imp | roving ( | Code Density                                                     | 85  |

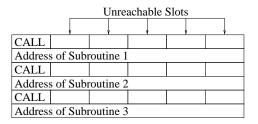

|   | 8.1 | 0        | ving High-Level Code Density by Adding an Instruction Stack      | 86  |

|   |     | 8.1.1    | Side-Effects on Return Stack Manipulation                        | 87  |

|   | 8.2 |          |                                                                  | 88  |

|   | 8.3 | -        | ffect on Code Size, Silicon Area, and Subroutine Overhead        | 88  |

|   | 0.0 | 8.3.1    | The Instruction Stack as an Instruction Cache                    | 89  |

| 9 | Con | clusions | s, Contributions, and Further Work                               | 91  |

| - | 9.1 |          | butions                                                          | 93  |

|   | 9.2 |          | r Work                                                           | 93  |

|   |     | 9.2.1    | Reducing the DLX/MIPS Subroutine Call Overhead by Adding Stacks  | 94  |

|   |     | 9.2.2    | Reducing Gullwing's Instruction Count with Compound Stack Opera- | - 1 |

|   |     |          |                                                                  | 96  |

|    |            | 9.2.3    | Reducing Gullwing's CPI by Executing Multiple Instructions using<br>Generalized Instruction Folding | . 97  |

|----|------------|----------|-----------------------------------------------------------------------------------------------------|-------|

| A  | Gull       | wing Re  | enchmarks Source                                                                                    | 99    |

| 1  |            | 0        | Language Kernel                                                                                     |       |

|    | <b>A.1</b> | A.1.1    | • •                                                                                                 |       |

|    |            | 11.1.1   | A.1.1.1 Counted Strings                                                                             |       |

|    |            | A.1.2    | Utility Functions                                                                                   |       |

|    |            | A.1.3    | String Functions                                                                                    |       |

|    |            | A.1.4    | Input Functions                                                                                     |       |

|    |            | A.1.5    | Name Lookup                                                                                         |       |

|    |            | A.1.6    | Function Definition Functions                                                                       |       |

|    |            | A.1.7    | Compilation Functions                                                                               |       |

|    |            | A.1.8    | Inline Compilation                                                                                  |       |

|    |            | A.1.9    | Main Loop                                                                                           |       |

|    |            | A.1.10   | Decimal to Binary Conversion                                                                        |       |

|    | A.2        |          | Language Extensions                                                                                 |       |

|    |            | A.2.1    | Making the Flight Language More Tractable                                                           |       |

|    |            | A.2.2    | Interactively Usable Opcodes                                                                        | . 112 |

|    |            | A.2.3    | Basic Compiling Functions                                                                           | . 112 |

|    |            | A.2.4    | Terminal Control Characters                                                                         | 113   |

|    |            | A.2.5    | Conditionals and Comparisons                                                                        | 113   |

|    |            | A.2.6    | Code Memory Allocation                                                                              | 115   |

|    |            | A.2.7    | String Copying and Printing                                                                         | . 115 |

|    |            | A.2.8    | De-Allocating Functions                                                                             | 116   |

|    |            | A.2.9    | Unsigned Multiplication and Division                                                                | . 117 |

|    |            | A.2.10   | Binary to Decimal Conversion                                                                        | 118   |

|    |            | A.2.11   | Simple Fibonacci Examples                                                                           | . 119 |

|    |            | A.2.12   | Static Variables                                                                                    | . 120 |

|    |            | A.2.13   | Accumulator Generator                                                                               | . 121 |

|    |            | A.2.14   | Fibonacci Generator                                                                                 | 121   |

|    |            |          | Caesar Cipher Generator                                                                             |       |

|    |            |          | Higher-Order Function (Map)                                                                         |       |

|    | A.3        |          | Machine                                                                                             |       |

|    |            | A.3.1    | VM                                                                                                  |       |

|    |            | A.3.2    | Metacompiler                                                                                        |       |

|    |            | A.3.3    | Self-hosted Kernel                                                                                  |       |

|    |            | A.3.4    | Flight Language Extensions                                                                          | . 140 |

| B  | Stati      | ic and D | Dynamic Gullwing Code Analyses                                                                      | 141   |

| •• | B.1        |          | Analyses                                                                                            |       |

|    |            | B.1.1    | Memory Usage                                                                                        |       |

|    |            | B.1.2    | Range of Literals                                                                                   |       |

|    |            | B.1.3    | Range of Addresses                                                                                  |       |

|    |            | B.1.4    | Instructions per Instruction Word                                                                   |       |

|             | B.1.5 | Instruction Density         | . 143 |

|-------------|-------|-----------------------------|-------|

|             | B.1.6 | Compiled Instruction Counts | . 144 |

| <b>B</b> .2 | Dynam | nic Analyses                | . 145 |

|             | B.2.1 | Overall Execution           | . 145 |

|             | B.2.2 | Executed Instruction Counts | . 145 |

|             | B.2.3 | Average CPI                 | . 147 |

|             | B.2.4 | Instruction Types           | . 147 |

|             | B.2.5 | Basic Block Length          | . 148 |

|             | B.2.6 | Data Stack Depth            | . 149 |

|             | B.2.7 | Return Stack Depth          | . 150 |

| L 1º        | anhu  |                             | 151   |

### Bibliography

# **List of Tables**

| Comparison of Citations of Computer Architecture Texts (as of Fall 2004) | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gullwing Flow Control Instructions                                       | 50<br>50<br>51<br>52<br>52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Compilers Dynamic Instruction Mix                                        | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 1                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Gullwing CPI by Instruction Type                                         | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Gullwing Memory Accesses Per Cycle (Total)                               | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DLX/MIPS Memory Accesses Per Cycle Caused by Loads and Stores            | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                          | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                          | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                          | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                          | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| •                                                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •                                                                        | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| •                                                                        | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                          | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                          | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Add4 Code Comparison                                                     | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Synthesized Stack Operations on MIPS with Stacks                         | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Recursive MIPS32 Instruction Distribution With and Without Stacks        | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Triangular Recursive MIPS32 Code Comparison With and Without Stacks      | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Compiled Flight Code Memory Usage                                        | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Instructions per Instruction Word                                        | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Instruction Density                                                      | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                          | Gullwing Flow Control Instructions         Gullwing Load and Store Instructions         Gullwing ALU Instructions         Gullwing Stack Manipulation Instructions         Gullwing No-Op and Undefined Instruction         Gunglers Dynamic Instruction Mix         Interpreters Dynamic Instruction Mix         DLX CPI with Load and Branch Penalties         Gullwing Memory Accesses Per Cycle (Total)         DLX/MIPS Memory Accesses Per Cycle Caused by Loads and Stores         Triangular Iterative Code Comparison         Triangular Recursive Code Comparison         Recursive Dynamic Instruction Mix         Triangular Tail-Recursive Code Comparison         Tail-Recursive Dynamic Instruction Mix         Add2 Code Comparison         Add2 Dynamic Instruction Mix         Add3 Dynamic Instruction Mix         Add3 Code Comparison         Add4 Dynamic Instruction Mix         Add4 Code Comparison         Add4 Code Comparison |

| B.6          | Compiled Instruction Counts | 144 |

|--------------|-----------------------------|-----|

| B.7          | Overall Execution           | 145 |

| B.8          | Executed Instruction Counts | 146 |

| B.9          | Average CPI                 | 147 |

| <b>B</b> .10 | Instruction Types           | 147 |

| <b>B</b> .11 | Basic Block Length          | 148 |

| B.12         | Data Stack Depth            | 149 |

| B.13         | Return Stack Depth          | 150 |

# **List of Figures**

| 2.1 | Evaluation of Polish Notation expression $/ + 552$            | 8  |

|-----|---------------------------------------------------------------|----|

| 2.2 | Fig. 1 from Bauer and Samelson German Patent #1094019         | 9  |

| 2.3 | Programming model for the Zuse Z4                             | 11 |

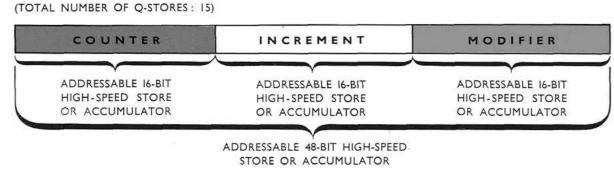

| 2.4 | KDF9 Q-Store Layout                                           | 12 |

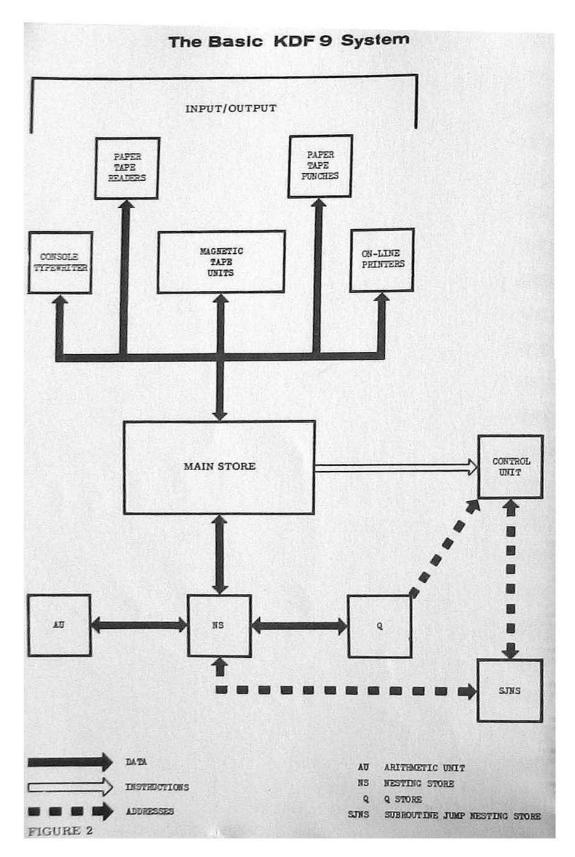

| 2.5 | KDF9 Block Diagram                                            | 13 |

| 2.6 | B6900 Top-of-Stack and Stack Bounds Registers                 | 15 |

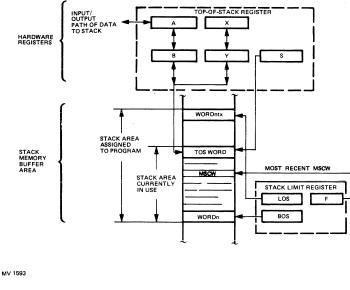

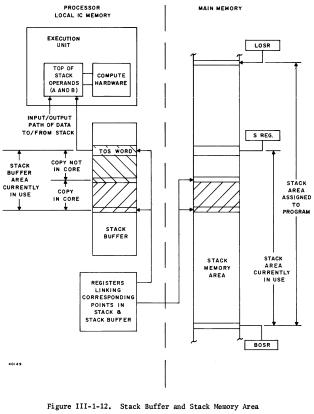

| 2.7 | B7700 Stack Buffer and Stack Memory Area                      | 15 |

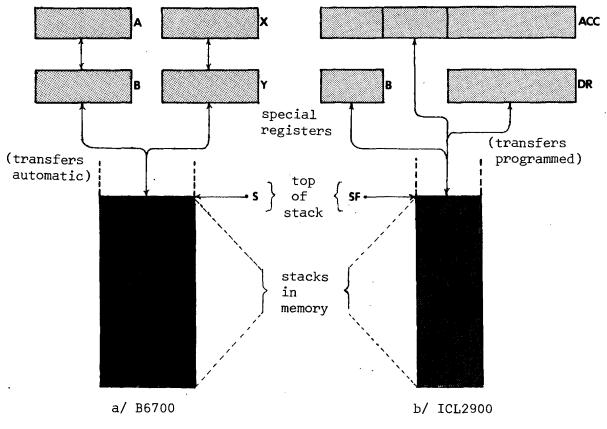

| 2.8 | Comparison of B6700 and ICL 2900 stack mechanisms             | 16 |

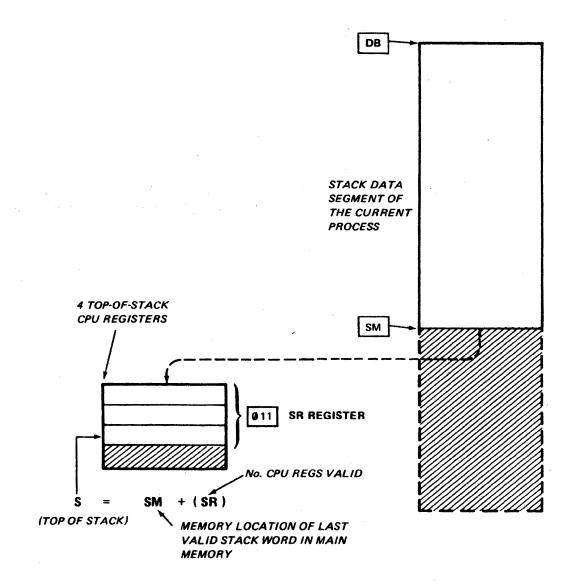

| 2.9 | HP3000 Stack Registers                                        | 17 |

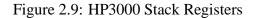

| 3.1 | NC4016 and RTX-2000 Block Diagrams                            | 24 |

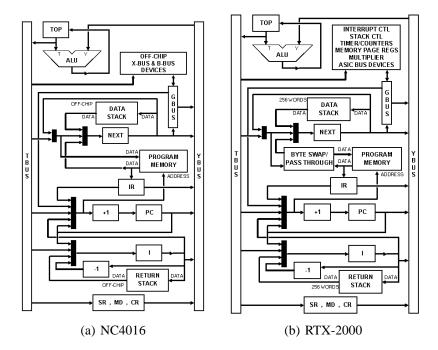

| 3.2 | IGNITE I Block Diagram                                        | 25 |

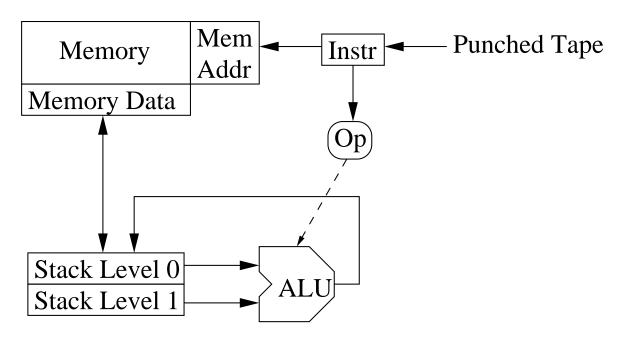

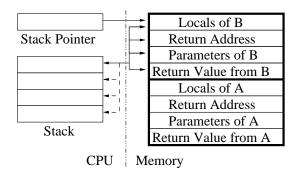

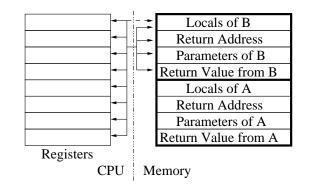

| 4.1 | First-Generation Stack Computer Block Diagram                 |    |

| 4.2 | General-Purpose Register Computer Block Diagram               | 34 |

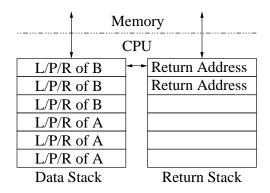

| 4.3 | Second-Generation Stack Computer Block Diagram                | 35 |

| 6.1 | Gullwing Block-Level Datapath                                 | 47 |

| 6.2 | Gullwing Instruction Shift Register Block Diagram             | 47 |

| 6.3 | Gullwing Instruction Format                                   | 53 |

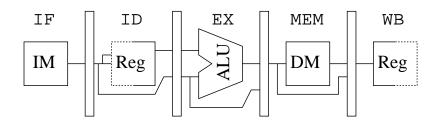

| 7.1 | DLX Pipeline Block Diagram                                    | 79 |

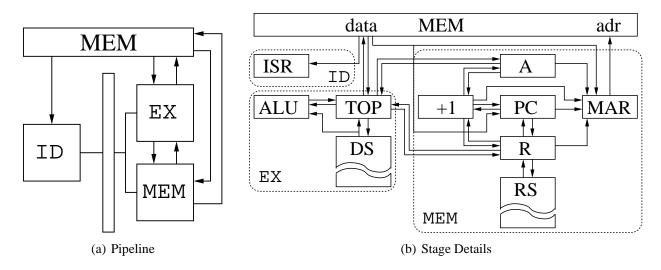

| 7.2 | Gullwing Pipeline Block Diagram                               | 80 |

| 7.3 | Gullwing Pipeline Operation                                   | 81 |

| 7.4 | Gullwing Load/Stores Pipeline Diagram                         | 81 |

| 7.5 | Gullwing ISR Modified for Pipeline                            | 82 |

| 7.6 | Gullwing Instruction Fetch (with Overlap) Pipeline Diagram    | 82 |

| 7.7 | Gullwing Instruction Fetch (without Overlap) Pipeline Diagram | 83 |

| 7.8 | Gullwing Taken Jumps or Calls Pipeline Diagram                | 83 |

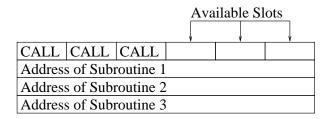

| 8.1 | Gullwing High-Level Code with Unavailable Slots               |    |

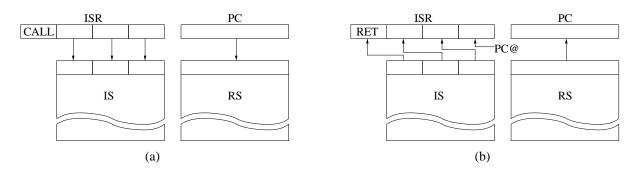

| 8.2 | Instruction Stack During Call and Return                      |    |

| 8.3 | Gullwing High-Level Code with Available Slots                 | 86 |

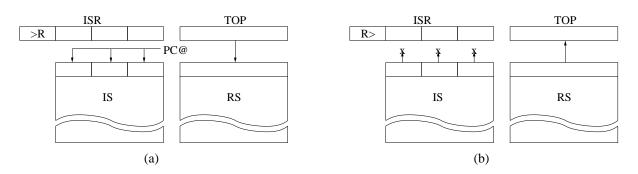

| 8.4 | Instruction Stack During $>$ R and R $>$                      | 87 |

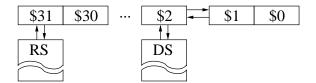

| 9.1 | MIPS Register File with Stacks                                | 94 |

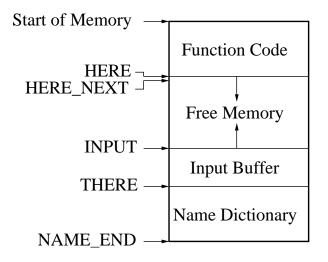

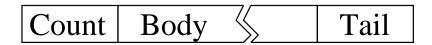

| A.1 | Flight Language Kernel Memory Map | 100 |

|-----|-----------------------------------|-----|

| A.2 | Counted String Format             | 100 |

# **List of Algorithms**

| 1  | Gullwing Synthesis of Subtraction and Bitwise OR                         | 51 |

|----|--------------------------------------------------------------------------|----|

| 2  | Gullwing Synthesis of Multiplication (4x4)                               | 51 |

| 3  | Gullwing Flow Control Instructions                                       |    |

| 4  | Gullwing No-Op and Undefined Instructions                                |    |

| 5  | Gullwing ALU Instructions                                                |    |

| 6  | Gullwing Load and Store Instructions                                     |    |

| 7  | Gullwing Stack Instructions                                              | 55 |

| 8  | Gullwing ALU Instructions with Instruction Fetch Overlap                 | 57 |

| 9  | Gullwing Stack Instructions with Instruction Fetch Overlap               | 57 |

| 10 | Gullwing No-Op and Undefined Instructions with Instruction Fetch Overlap | 57 |

| 11 | Triangular Iterative C Source                                            | 71 |

| 12 | Triangular Iterative MIPS32 Assembly                                     | 71 |

| 13 | Triangular Iterative Gullwing Assembly                                   | 71 |

| 14 | Triangular Recursive C Source                                            | 72 |

| 15 | Triangular Recursive MIPS32 Assembly                                     | 73 |

| 16 | Triangular Recursive Gullwing Assembly                                   | 73 |

| 17 | Triangular Tail-Recursive C Source                                       | 74 |

| 18 | Triangular Tail-Recursive MIPS32 Assembly                                | 75 |

| 19 | Triangular Tail-Recursive Gullwing Assembly                              | 75 |

| 20 | Add2 C Source                                                            | 76 |

| 21 | Add2 MIPS32 Assembly                                                     | 76 |

| 22 | Add2 Gullwing Assembly                                                   |    |

| 23 | Add3 C Source                                                            | 77 |

| 24 | Add3 MIPS32 Assembly                                                     | 77 |

| 25 | Add3 Gullwing Assembly                                                   | 77 |

| 26 | Add4 C Source                                                            | 78 |

| 27 | Add4 MIPS32 Assembly                                                     | 78 |

| 28 | Add4 Gullwing Assembly                                                   | 78 |

| 29 | Alterations to Gullwing to Support an Instruction Stack                  | 88 |

| 30 | Triangular Recursive MIPS32 Assembly with Stacks Added                   | 95 |

| 31 | Gullwing Compound Stack Operations                                       |    |

| 32 | Example Gullwing Instruction Sequence Using Generalized Folding          | 97 |

# Chapter 1

### Introduction

I first learnt about stack computers in 2000 while working at a computer manufacturer where co-workers introduced me to the Forth programming language, a stack-based programming environment. Soon after, while looking for a suitable processor for a homebrew computer system, I came across a mention of the MuP21 [MT95] in the Usenet *Embedded Processor* and *Microcontroller Primer and FAQ*<sup>1</sup>:

The MuP21 was designed by Chuck Moore, the inventor of Forth. With the MuP21, Forth can compile into machine code and still be Forth, because the machine code IS Forth. The MuP21 freaks out at 100 MIPS while consuming only 50 milliwatts. Not only that, the chip includes a video generator, has only about 7000 transistors (that's right, 7000 and not 7,000,000), and costs about \$20.

The assembler on this chip is a sort of dialect of Forth, as the CPU is modeled after the Forth virtual machine. MuP21 is a MINIMAL Forth engine. [...] The CPU programs the video generator and then just manipulates the video buffer. It is composite video out, so it only needs one pin. MuP21 is only a 40 pin chip.

I'd never heard of anything like it. It was smaller and faster, and its machine code was a structured language! I was hooked. Understanding this type of hardware and software became a hobby that ultimately led me to pursue a University degree on the topic. However, I couldn't simply take a Computer Engineering degree since this kind of computer is virtually non-existent in the mainstream literature and totally absent from the curriculum. Therefore, I had to create one under the aegis of the Independent Studies (IS) program.

The IS program is a self-directed course of study guided and vetted by a Faculty Adviser and composed of a combination of Independent Study Units and regular courses. After two years of study (typically), a student petitions to enter Thesis Phase and if approved, spends a year developing a thesis on a selected topic. A successfully completed thesis grants the degree of Bachelor of Independent Studies (BIS). Overall, IS bears more resemblance to graduate studies than undergraduate ones.

The structure of this thesis reflects the directions I have taken throughout the IS program. I began with broad historical explorations of stack architecture and programming languages, complemented by regular engineering courses on digital systems, computer architecture, and

<sup>&</sup>lt;sup>1</sup>Copyright (c) 1997 by Russ Hersch, all rights reserved. http://www.faqs.org/faqs/microcontroller-faq/primer/

integrated circuits. These efforts eventually concentrated on defining, simulating, programming, and partially implementing a particular stack computer design. In this thesis, I leave aside the issues of programming language design and VLSI implementation to focus on the architecture of the computer itself.

### **1.1 Research Goals**

A stack computer performs its operations not upon a randomly accessible set of registers, but upon a simpler, linear list of such. This list is conveniently viewed as a pushdown stack with the visible registers at the top. Since virtually all arithmetic and logical operations are either unary or binary, at a minimum the top two elements of a stack need to be accessible. The operations implicitly access these locations for operands and return values. The stack can be used for evaluating expressions in the manner of Reverse Polish Notation and also for storing a chain of activation records (stack frames) of nested subroutines.

The main problem in reasoning about stack computers is that those usually mentioned in the computer architecture literature, the first generation, have been superseded. They were popular due to their efficient use of hardware, their natural application towards algebraic computation, and the ease with which they could be programmed. Although sophisticated, they were eventually flatly outperformed by the new VLSI microprocessors that came out of the Berkeley RISC [PS81] and Stanford MIPS [HJP<sup>+</sup>82] projects. The first generation of stack computers can be defined by its support for High-Level Language, mainly ALGOL. This required in-memory stacks primarily used to allocate storage for nested procedures, and encouraged a large instruction set which attempted to match the semantics of ALGOL closely. The goal was to make programming easier in the absence of good compilers.

The second generation of stack computers arose just as the first faded away. These computers had simple hardware, high code density, fast subroutine linkage and interrupt response, but garnered little attention since they were aimed at embedded systems instead of general-purpose computing. This separated the second generation from the mainstream of processor design and caused it to become confused with the first generation, further discouraging work. The second generation of stack computers can be defined by its support for the Forth programming language. It defines two stacks, Data and Return, which are separate from main memory and not randomly addressable. The Data Stack is used to evaluate expressions and pass values between procedures in a functional manner. The Return Stack holds the return addresses of subroutines and can also act as temporary storage. The small instruction set is mostly composed of Forth primitives, which are simple stack manipulations, loads and stores, and basic arithmetic and logical functions similar to those found in conventional register-based computers.

The purpose of this thesis is to argue for a distinction of stack computers into first and second generations. I do this by recapitulating the evolution of stack computers, revisiting old arguments against them, and comparing the design of a model second-generation stack computer to a modern computer architecture. Given this refreshed view, I hope to fill the gap in the literature about stack computers and uncover some interesting avenues in computer architecture.

### **1.2** Thesis Outline

This thesis is divided into three major parts: a Historical Review, Qualitative Arguments, and Quantitative Arguments. The first and third may be read independently. However, the second part depends on the background provided by the first and is supported by data from the third.

### **1.2.1** Part I: Historical Review

Current computer literature only briefly touches upon stack architecture, always from the first generation, and usually as an introductory contrast to register-based computers. Chapter 2 provides a more detailed summary of the history of the people and machines that make up the first generation of stack computers, starting with their conceptual origins and ending with the main reasons for their downfall. It uncovers two different fundamental approaches to the design of stack computers: support for the ALGOL programming language, and composition of functions. This difference turns out to be the main criterion for distinguishing first-generation stack computers from second-generation ones.

Chapter 3 contains an overview of the second generation of stack computers. It focuses on the latest wave of such machines which originated with the work of Charles H. Moore and were extensively studied by Philip J. Koopman. It gathers together the scattered publications on the subject and also much information that was never formally published.

#### **1.2.2 Part II: Qualitative Arguments**

Before any comparison can be made between second-generation stack computers and current register-based computers, the confusion about stack computers in the mainstream literature must first be addressed. Chapter 4 proposes a set of three criteria to divide stack computers into a first and a second generation. They concern the location of the stacks, their purpose, and the operations done upon them. Stacks in a second-generation computer resemble registers used for calculations and parameter-passing, while the stacks of a first-generation machine are effectively call stacks holding procedure activation records.

With these criteria and the historical data in mind, Chapter 5 addresses the arguments against stack architectures cited by Hennessy & Patterson. These arguments are found to rely on outdated assumptions about compiler and hardware technology, and have also been distorted through secondhand citations. The original arguments are cited, and found to be much less critical of stack architectures than suggested by Hennessy & Patterson.

#### **1.2.3** Part III: Quantitative Arguments

Given that past arguments have been found lacking, the comparison between second-generation stack computers and current register-based computers needs to be revisited. Chapter 6 describes in detail the design of a small, modern stack computer architecture, named 'Gullwing', along with a simple optimization to its instruction fetch mechanism which makes practical the use of a single memory bus for both instructions and data.

Chapter 7 compares Gullwing to the DLX and MIPS processors used as demonstrators by Hennessy & Patterson. The processors are compared with aggregate benchmarks and with low-level analyses of how they execute iterative, recursive, tail-recursive, and nested subroutine code. The issue of pipelining Gullwing is explored as a transformation of the DLX pipeline. Gullwing is found to have a definite advantage at subroutine calls and memory bandwidth, but is unfortunately architecturally equivalent to a DLX processor without load or branch delay slots, with the same penalty to performance.

Chapter 8 addresses Gullwing's inefficient usage of memory for holding compiled code by adding a third stack to temporarily hold instructions during subroutine calls. This new architectural feature will increase the density of code to the maximum possible value and accelerate returns from subroutines.

Finally, Section 9.2 outlines the addition of stacks to a MIPS processor, without altering the pipeline or instruction set, in order to give it the efficient subroutine call mechanism of a stack computer. This section also introduces the addition of two forms of parallelism to Gullwing: one which reduces its instruction count with compound stack operations, and the other which reduces its CPI by overlapping the execution of instructions.

Appendix A provides the source to the Flight language kernel and the software used to benchmark Gullwing. Appendix B contains the tabulated raw data from the analyses of the dynamic and static properties of Gullwing machine code.

# Part I Historical Review

### Chapter 2

# **History of the First Generation of Stack Computers**

I present here the first generation of stack computers in the context of the pioneers of the field and of the machines that followed their insights. I discuss the organization and design goals of these computers, their shortcomings, and ultimately their replacement by RISC designs.

### 2.1 Lukasiewicz and the First Generation

The idea of using stacks for computation seems to have occurred independently, in slightly different forms, to several people worldwide within an interval of about a decade. It is difficult to tell if they were aware of each other's work at the time. Nonetheless, there seems to be a chronological order to the discoveries.

#### 2.1.1 Poland: Jan Lukasiewicz (1878-1956)

In 1929, while a professor at Warsaw University, Lukasiewicz wrote *Elements of Mathematical Logic* [Luk29]. In it he introduced a parenthesis-free notation for arithmetic and logic which eventually became known as Polish Notation or Prefix Notation. Its main feature is that it makes the order of operations explicit, contrary to the usual algebraic notation (correspondingly called Infix Notation) which depends on a knowledge of operator precedence and the use of parentheses to override it where necessary.

For example, the expression (5+5)/2 requires the use of parentheses to specify that the result should be 5 and not 7.5 due to the higher precedence of the division operator. The equivalent Prefix expression / + 552 is unambiguous and can be evaluated left-to-right by leaving the application of an operator pending until enough operands are available. The alternative interpretation of the infix expression would be written in prefix notation as +/525 or +5/52. Figure 2.1 shows how the expression is evaluated one symbol at a time. It is easy to see how the operators and operands could each reside in separate stacks until they are respectively executed or consumed.

//+/+55/10/1025

Figure 2.1: Evaluation of Polish Notation expression / + 552

### 2.1.2 Germany: Konrad Zuse (1910 - 1995)

The case of Konrad Zuse is unusual. He did his work privately, outside of academia or industry, and it was destroyed multiple times during the World War II air raids on Berlin. He also did not base his work on Lukasiewicz, but appeared to have come to the use of a stack out of simple engineering need. He constructed a series of computers of increasing capability, arriving at the stack-based Z4 in 1945, predating all other stack computers by at least 15 years [BFPB97, 10.3]. Unfortunately, except for the various machines produced up to 1969 by the Zuse KG company, there are no architectural descendants of the Z4 in Germany or abroad.

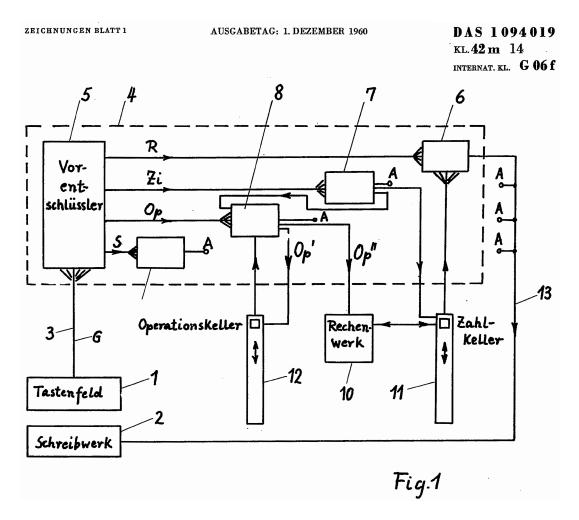

### 2.1.3 Germany: Friedrich Ludwig Bauer (1924-)

The earliest known mechanical realization of Lukasiewicz's idea was Bauer's STANISLAUS relay calculator [Bau60], first conceived in 1950/1951. It emerged out of the desire to mechanically test the well-formedness of formulae. The publication of this achievement was delayed by the need for secrecy while patents for the evaluation method were filed in Germany, the United States, France, the United Kingdom, and Sweden [BSc][BSd][BSa][BSb]. Figure 2.2 shows Fig. 1 from the original German patent, clearly showing an 'OperationsKeller' (Operations Cellar) and a 'ZahlKeller' (Number Cellar) used to evaluate Polish Notation expressions. The method is also discussed in a paper published after the patents were filed in 1957/1958 [SB60].

This 'cellar principle', now referred to as the stack principle, made its way into a proposal for an International Algebraic Language [Car58, BBRS58] as the natural method for the block structure of storage allocation for subroutines [Bau90]. This language evolved into ALGOL 60 [BBG<sup>+</sup>60]. Its use of a dynamic stack to support subroutine nesting and recursion has since become the dominant organizing principle of programming languages. It is important to note that the support of this structure is one of the hallmarks of first-generation stack computers (Figure 4.1).

In a recent talk [Bau02, BD02], Bauer mentioned some other appearances of the stack principle:

*Hardware* cellars, stacks, and pushdown stores have been discussed elsewhere, possibly as early as 1947 by Alan Turing, certainly in 1949 by Harry D. Huskey

in connection with the ZEPHYR (SWAC) computer and in 1956 by Willem L. van der Poel in connection with the design of the MINIMA computer; in all cases presumably for the treatment of return jumps in subroutines. [...]

Figure 2.2: Fig. 1 from Bauer and Samelson German Patent #1094019

#### 2.1.4 Australia: Charles Leonard Hamblin (1922-1985)