# Synthesis and Exploration of Multi-Level, Multi-Perspective Architectures of Automotive Embedded Systems

by

Jordan Ross

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2016

© Jordan Ross 2016

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

In industry, evaluating candidate architectures of automotive embedded systems is routinely done during the design process. Today's engineers, however, are limited in the number of candidates that they are able to evaluate in order to find the optimal architectures. This limitation results from the difficulty in defining the candidates as it is a mostly manual process. In this work, we propose a way to synthesize multi-level, multi-perspective candidate architectures and to explore them across the different layers and perspectives. Using a reference model similar to the EAST-ADL domain model but with a focus on early design, we explore the candidate architectures for two case studies: an automotive power window system and the central door locking system. Further, we provide a comprehensive set of questions, based on the different layers and perspectives, that engineers can ask to synthesize only the candidates relevant to their task at hand. Finally, using the modeling language Clafer, which is supported by automated backend reasoners, we show that it is possible to synthesize and explore optimal candidate architectures for two highly configurable automotive subsystems.

#### Acknowledgements

I want to first and foremost thank my supervisor, **Krzysztof Czarnecki**, for giving me this wonderful opportunity to learn from him and deepen my understanding. I have learned more than I ever have these last couple of years because of him.

I also want to thank **Michał Antkiewicz** for all of the discussions and guidance he provided me these last couple of years, it was a pleasure.

Lastly, I want to thank my family for their patience as I embarked on this adventure.

#### Dedication

I dedicate this to my lovely wife Emily.

# **Table of Contents**

| Li | st of | Tables                                                 | ix |

|----|-------|--------------------------------------------------------|----|

| Li | st of | Figures                                                | xi |

| 1  | Intr  | roduction                                              | 1  |

| 2  | Cla   | fer Background                                         | 4  |

|    | 2.1   | Types of clafers and inheritance                       | 5  |

|    |       | 2.1.1 Instance generation                              | 6  |

|    | 2.2   | Clafer multiplicity and group cardinality              | 7  |

|    | 2.3   | References                                             | 8  |

|    | 2.4   | Writing Basic Constraints                              | 10 |

|    | 2.5   | Working with Integers                                  | 13 |

|    | 2.6   | Optimization Objectives                                | 14 |

| 3  | Ref   | erence Model                                           | 17 |

|    | 3.1   | Reference Model Layers                                 | 18 |

|    | 3.2   | Reference Model Perspectives                           | 24 |

| 4  | Cha   | aracterizing the Possible Design Scenarios             | 27 |

|    | 4.1   | Possible Design Exploration Scenarios                  | 29 |

|    | 4.2   | Generalizing the Possible Design Exploration Scenarios | 30 |

|    | 4.3   | Example Design Exploration using Templates             | 34 |

| 5  | Enc   | oding the Reference Model in Clafer                    | 36 |

|    | 5.1   | Encoding of Reference Model Layers in Clafer           | 37 |

|    |       | 5.1.1 Using Clafer to Model a Simplified Power Window  | 45 |

|    | 5.2   | The Supporting Reasoner and Tools                      | 47 |

| 6  | Mo    | deling Two Case Studies in Clafer                                                                                                        | <b>48</b> |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|    | 6.1   | Power Window                                                                                                                             | 48        |

|    |       | 6.1.1 Single Door: Driver                                                                                                                | 49        |

|    |       | 6.1.2 Two Door: Driver & Front Passenger                                                                                                 | 58        |

|    |       | 6.1.3 Quality Attributes & Timing Analysis                                                                                               | 63        |

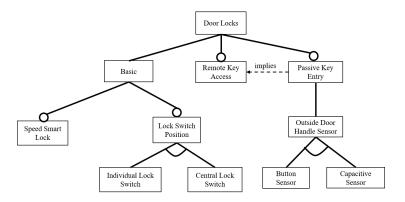

|    | 6.2   | Door Locks                                                                                                                               | 65        |

|    |       | 6.2.1 Feature Model                                                                                                                      | 65        |

|    |       | 6.2.2 Functional Analysis Architecture                                                                                                   | 67        |

|    |       | 6.2.3 Device Node Classification                                                                                                         | 71        |

|    |       | 6.2.4 Power Topology                                                                                                                     | 74        |

|    |       | 6.2.5 Communication Topology                                                                                                             | 74        |

|    |       | 6.2.6 Deployment                                                                                                                         | 75        |

|    |       | 6.2.7 Quality Attributes & Timing Analysis                                                                                               | 77        |

| 7  | Eva   | luation                                                                                                                                  | 79        |

|    | 7.1   | Research Methodology                                                                                                                     | 80        |

|    |       | 7.1.1 Comparison to State-of-the-Art Tools                                                                                               | 80        |

|    |       | 7.1.2 Role of Multiple Layers                                                                                                            | 81        |

|    |       | 7.1.3 Performance Evaluation                                                                                                             | 81        |

|    | 7.2   | Comparison to State-of-the-Art Tools                                                                                                     | 84        |

|    |       | 7.2.1 Research Question $1 \dots $ | 90        |

|    |       | 7.2.2 Research Question 2                                                                                                                | 91        |

|    | 7.3   | Role of Multiple Layers (Research Question 3)                                                                                            | 94        |

|    | 7.4   | Performance Evaluation                                                                                                                   | 94        |

|    |       | 7.4.1 Research Question 4                                                                                                                | 94        |

|    |       | 7.4.2 Research Question $5 \dots $ | 97        |

| 8  | Th    | ceats to Validity                                                                                                                        | 100       |

|    | 8.1   | Research Questions $1 \& 2 \ldots \ldots$                                 | 100       |

|    | 8.2   | Research Question 3                                                                                                                      | 100       |

|    | 8.3   | Research Questions 4 & 5                                                                                                                 | 101       |

| 9  | Rel   | ated Work                                                                                                                                | 102       |

|    | 9.1   | Survey of Architecture Optimization                                                                                                      | 102       |

|    | 9.2   | Recent Advances in E/E Architecture Evaluation & Optimization                                                                            | 103       |

|    | 9.3   | Extensions to Previous Work                                                                                                              | 105       |

| 10 | ) Cor | nclusions & Future Work                                                                                                                  | 106       |

#### **APPENDICES**

| 1 | n | 7 |

|---|---|---|

| Т | υ | 1 |

| A Full Source Code for Clafer Models 10 | )8        |

|-----------------------------------------|-----------|

| A.1 Reference Model                     | )8        |

| A.2 Generalized Power Window            | 12        |

| A.3 Two Door Power Window 11            | 17        |

| A.4 Central Door Locks                  | 23        |

| References 14                           | <b>17</b> |

# List of Tables

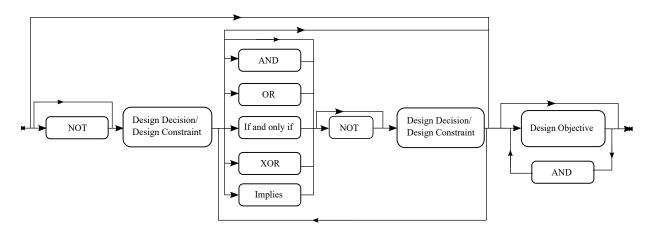

| 4.1<br>4.2<br>4.3 | A set of decision templates based on the reference architecture model<br>A set of constraint templates based on the reference architecture model<br>A set of the design objective templates based on the reference architecture model                     | 32<br>33<br>34 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 7.1               | Number of concrete components for each reference model element, number<br>of deployment configurations, and number of possible candidates for each<br>design-space model. $(n)$ denotes that $n$ of the concrete components have<br>presence variability. | 82             |

| 7.2               | Size of Clafer encoding for each model. The design-space model numbers are reported minus the reference model elements.                                                                                                                                   | 83             |

| 7.3               | Details for selected state-of-the-art tools to compare with Clafer                                                                                                                                                                                        | 87             |

| 7.4               | Limitations we encountered when modeling the single door variant of the power window system introduced in Chapter 3                                                                                                                                       | 90             |

| 7.5               | Supported (Yes) and unsupported (No) decision templates for each of the surveyed tools. If the decision is unsupported, one of the following reasons is listed: 1) Model element not supported 2) Variability not captured                                | 92             |

| 7.6               | Supported (Yes) and unsupported (No) constraint and objective templates<br>for each of the surveyed tools. If unsupported, one of the following reasons                                                                                                   | 92             |

|                   | is listed: 1) Quality not supported 2) Expression not supported                                                                                                                                                                                           | 93             |

| 7.7               | Resulting quality attribute values when removing portions of the power win-                                                                                                                                                                               |                |

|                   | dow model (single door variant). The margin latency is for the timing chain                                                                                                                                                                               |                |

|                   | from the switch to the motor. The margin latency value is given as a range                                                                                                                                                                                |                |

|                   | denoting the smallest and largest values for the reported instances. We use                                                                                                                                                                               |                |

|                   | the curly braces to denote an ordered set of values when more than one set                                                                                                                                                                                |                |

|                   | of values exists on the Pareto front                                                                                                                                                                                                                      | 95             |

| 7.8  | Design decision and constraint solving time for three case study models. A     |    |

|------|--------------------------------------------------------------------------------|----|

|      | timeout is reported if the solver takes more than 10 minutes to find the first |    |

|      | 10 non-optimal solutions                                                       | 97 |

| 7.9  | Design objective solving time for three case study models. A timeout is        |    |

|      | reported if the solver takes more than 45 minutes to find the first 10 optimal |    |

|      | solutions.                                                                     | 98 |

| 7.10 | Design exploration scenario specification solving time for the power window    |    |

|      | case study models. A timeout is reported if the solver takes more than 10      |    |

|      | minutes to find the first 10 non-optimal solutions and more than 45 minutes    |    |

|      | to find the first 10 optimal solutions.                                        | 99 |

|      |                                                                                |    |

# List of Figures

| 1.1               | EAST-ADL Architecture                                                                                                                                                                                                                                                                                                                                                                                                       | 2                    |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $2.1 \\ 2.2$      | Overall workflow of Clafer and supported backend solvers                                                                                                                                                                                                                                                                                                                                                                    | 5<br>16              |

| 3.1               | The reference model used for early design of automotive E/E systems architecture.                                                                                                                                                                                                                                                                                                                                           | 18                   |

| 3.2<br>3.3        | Power window feature models                                                                                                                                                                                                                                                                                                                                                                                                 | 19<br>20             |

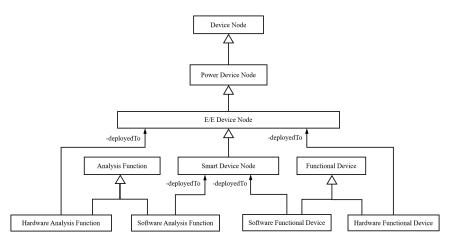

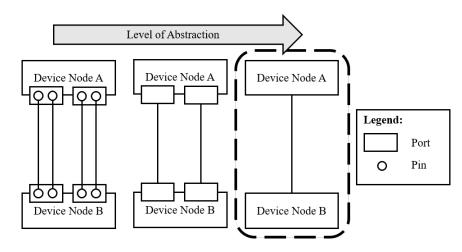

| 3.4<br>3.5        | or software, respectively.<br>Class diagram showing classification of device nodes and functions.<br>Modeling of data connectors at different levels of abstraction. The lowest<br>level is shown on the left, where connectors are modeled between pins; the<br>middle shows connectors between ports; the right is the highest level, where<br>two device nodes are connected via a connector. The dashed selection shows | 20<br>21             |

| 3.6<br>3.7<br>3.8 | the level of abstraction used for data and power connectors in this paper. Power window communication topology. Power window power topology. Power window FAA with variability. Optional components are shown by a dotted border/line. "HW/SW" indicates the function can be implemented in either software or hardware.                                                                                                    | 22<br>23<br>23<br>25 |

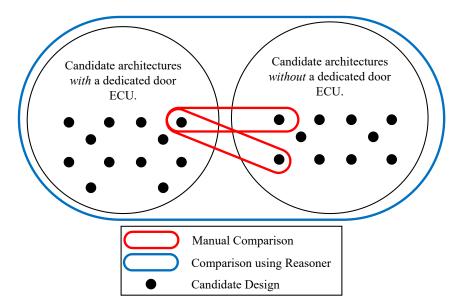

| 4.1<br>4.2        | Illustration of comparing candidate designs for different sets of architectures<br>using a manual versus an automated model-based approach                                                                                                                                                                                                                                                                                  | 28<br>35             |

| 5.1         | A unified view of the reference model used for early design of automotive E/E systems architecture                                                | 37 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1         | The feature model for a single door power window                                                                                                  | 49 |

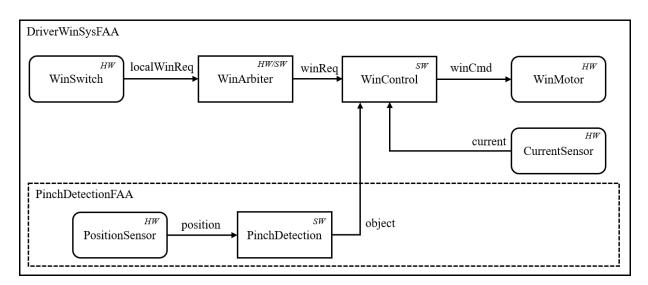

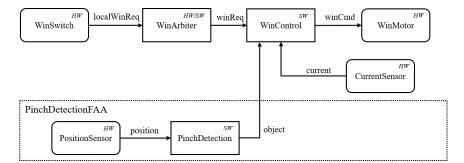

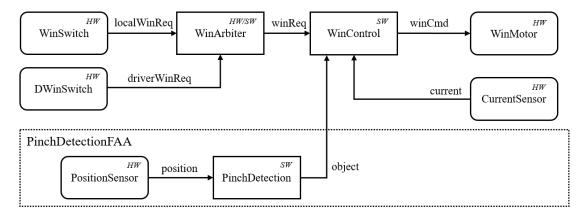

| 6.2         | The functional analysis architecture for a single door power window. The "HW" or "SW" in upper right corner of a function indicates the implemen- |    |

|             | tation choice in hardware or software respectively. "HW/SW" indicates the function can be implemented in either software or hardware.             | 50 |

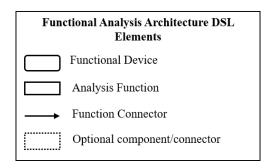

| 6.3         | Legend for the graphical domain-specific language (DSL) for describing the                                                                        | 50 |

| 0.0         | FAA for E/E architectures                                                                                                                         | 50 |

| 6.4         | The power topology for a single door power window. The inside dotted box                                                                          |    |

|             | for the BCM denote that it is an optional remote device node                                                                                      | 54 |

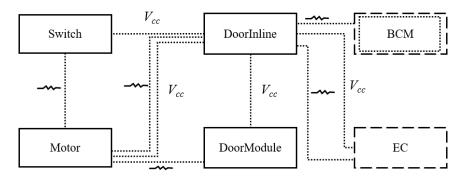

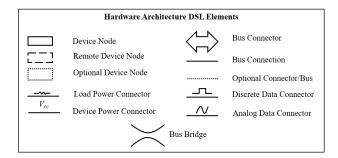

| 6.5         | Legend for the graphical domain specific language (DSL) for describing the                                                                        |    |

|             | hardware architecture for E/E architectures.                                                                                                      | 55 |

| 6.6         | The communication topology for a single door power window                                                                                         | 57 |

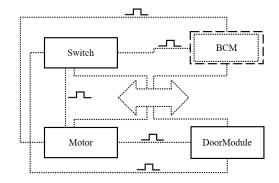

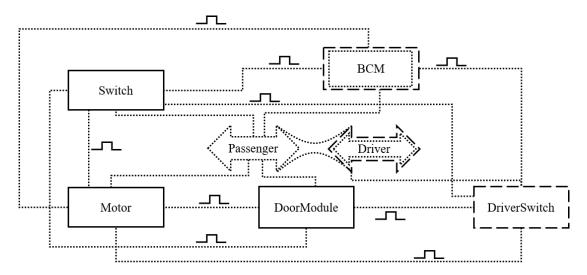

| 6.7         | The functional analysis architecture for a passenger door power window system                                                                     | 61 |

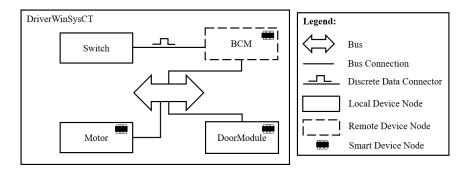

| 6.8         | CT                                                                                                                                                | 63 |

| 6.9<br>6.10 | The feature model for a central door locks system                                                                                                 | 66 |

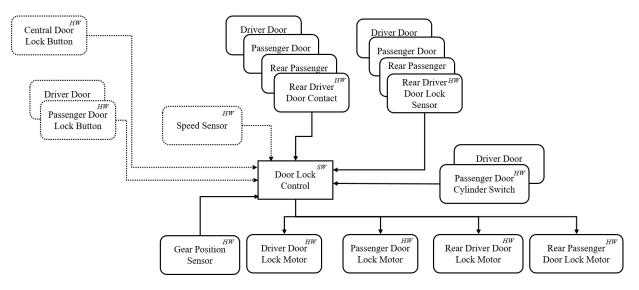

| 6.10        | The functional analysis architecture for the basic features in the door locks system                                                              | 67 |

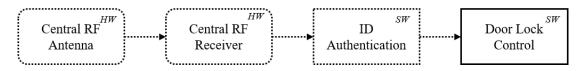

| 6.11        |                                                                                                                                                   | 07 |

| 0.11        | system                                                                                                                                            | 68 |

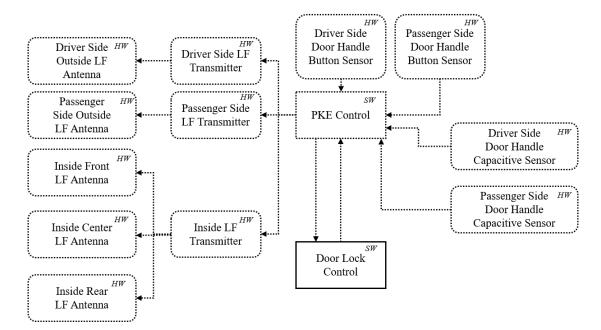

| 6.12        | The functional analysis architecture for the PKE fragment in the door locks                                                                       | 00 |

|             | system                                                                                                                                            | 70 |

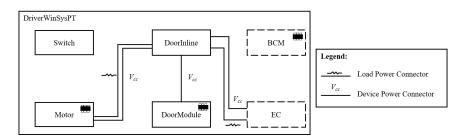

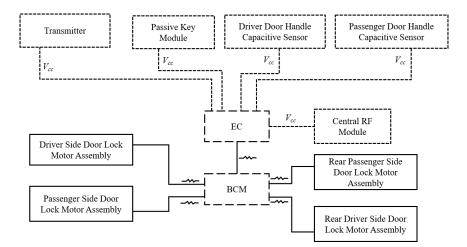

| 6.13        | The power topology for the door locks system                                                                                                      | 74 |

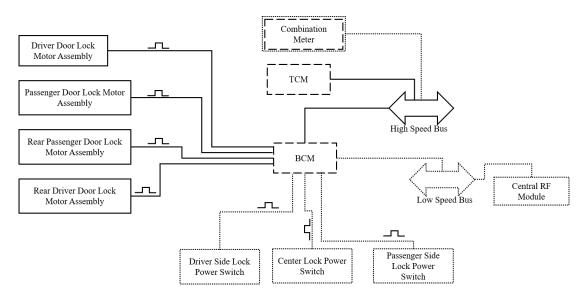

| 6.14        | The communication topology for the door locks system basic and RKA                                                                                |    |

|             | fragments                                                                                                                                         | 75 |

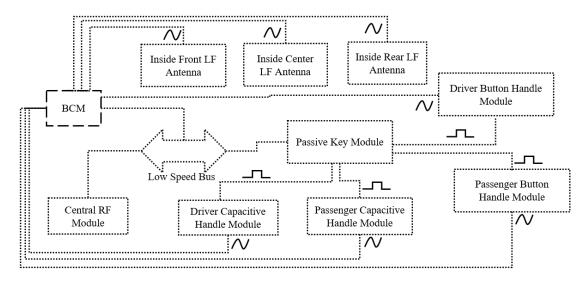

| 6.15        | The communication topology for the door locks system PKE fragment which                                                                           |    |

|             | uses the BCM as a transmitter                                                                                                                     | 76 |

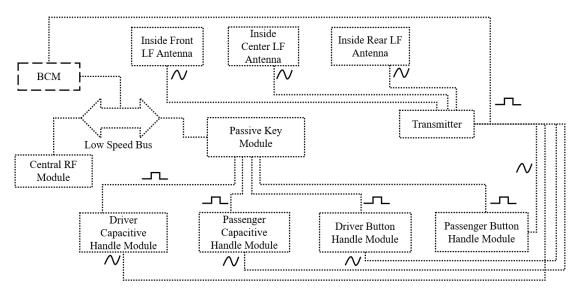

| 6.16        |                                                                                                                                                   |    |

|             | uses the transmitter device node                                                                                                                  | 77 |

## Chapter 1

## Introduction

Automotive E/E (electrical and electronic) architectures are continuing to grow in size and complexity due to the increasing amount of software functions being deployed to cars. These architectures consist of sensors, actuators, electronic control units (ECUs), and the physical connection media such as discrete signal wires, analog signal wires, and digital network buses. Premium cars can have 3 km of wiring connecting more than 70 ECUs with at least 2,000 software functions running on them [17,31]. Additionally, the architectures contain large amounts of variability in features, functions, devices, and the deployment, which further increases the complexity.

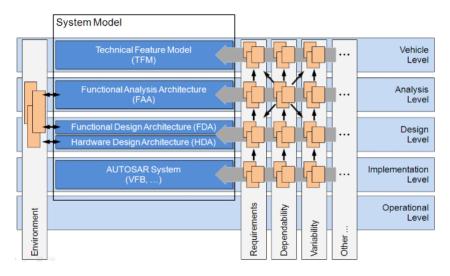

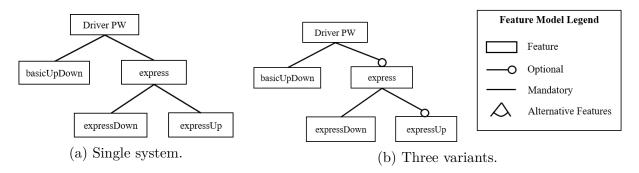

EAST-ADL is a reference architecture model and a set of domain-specific languages for modeling automotive E/E architectures. It was designed to capture E/E systems with sufficient detail to allow modeling for documentation, design, analysis, and synthesis [25]. Figure 1.1 shows the domain model for EAST-ADL and how the system model is composed of multiple abstraction levels which can be cross-cut by one or more perspectives (or extensions). Using EAST-ADL to model a system (or a family of systems) aids in managing the associated complexity [20]. In Chapter 3, we define a reference model for modeling architecture of E/E systems that is simplified (compared to EAST-ADL) for early design, where decomposition of software components may be too detailed to capture. However, the presented model could be extended to cover full EAST-ADL and the presented synthesis and optimization would be equally applicable. Additionally, while being simplified, the presented reference model is composed of multiple abstraction levels and perspectives. We apply the reference model to building architectural models which represent many possible candidate architectures and which affords the engineers to optimize quality attributes of the architecture such as total cost, mass, and timing and explore the tradeoffs among them.

Figure 1.1: EAST-ADL Domain Model [25]

In Chapter 4, we present a mechanism for constructing a set of design specifications to use in exploring the possible candidate architectures captured in models constructed using the reference model from Chapter 3.

To appreciate the motivation, consider the following example scenario used throughout the remainder of the paper. Emily is an engineer at an automotive company. She is working on designing the E/E system architecture for the door power window. Emily wants to consider a set of candidate architectures and to compare them based on their mass and cost. The candidates themselves should be correct, meaning that they must meet any requirements and constraints specified by Emily (e.g., end-to-end latency and deployment restrictions).

While the EAST-ADL can help Emily in modeling multiple candidate E/E architectures, there is currently no approach allowing Emily to synthesize the candidate architectures, while considering design decisions at all layers, and explore trade-offs among them. In this work, we use a modeling language Clafer (see Chapter 2) to model multi-layer, multi-perspective architectures (Chapter 5). We show that by using Clafer we can model alternative design decisions for any component in addition to design constraints and objectives for a number of qualities such as latency, mass, and parts cost. Furthermore, we can join these decisions, constraints, and objectives together using first-order logic to write fine-grained design specifications for exploring the possible design space (Chapter 4).

In Chapter 6 we give the full details, including their Clafer encoding, for a power window

system and door locks system. We evaluate our approach in Chapter 7 to show how it improves the state of the art. Additionally, we evaluate the performance of synthesizing the candidate architectures. We then provide the threats to validity, related work, and conclude in Chapters 8, 9, and 10, respectively.

This work provides the following contributions:

- Design exploration approach for E/E architectures based on a multi-layer and multiperspective reference model; in contrast to previous work (see related work section), the approach explores many types of design decisions (at least 15) from multiple layers, constraints (at least 13), and objectives (at least 5) simultaneously

- The approach is supported by a modeling language, reasoning tool, and results visualization tool to enable a wide range of design exploration scenarios, which are characterized using specification templates.

- Two large case studies of realistic automotive E/E systems; the corresponding models and exploration scenarios can serve as a future benchmark for comparing design exploration tools in the E/E systems domain.

- We use one of the case studies to show the relevance of capturing multiple layers for obtaining more realistic exploration results.

- We show that the majority of the exploration scenarios of the case studies are feasible in terms of performance; we also show that exact optimization is feasible for most of the optimization scenarios for most of the studied models; however, future work will need to address scalability to larger models.

## Chapter 2

## **Clafer Background**

Clafer [4] is a lightweight, general-purpose, structural modeling language that was originally developed for feature modeling [15]. In this section we provide readers with an informal background and basic understanding of the Clafer language and its constructs. The formal semantics of the language can be found in [15].

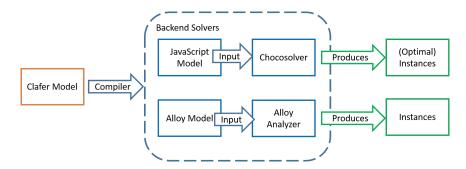

Clafer currently supports two backend solvers that generate instances from Clafer models. The first solver (not used in this work) is Alloy [1] and the second is Choco3 CSP based solver called *chocosolver*<sup>1</sup>. Clafer compiler translates an input Clafer model into the input language of each backend solver. We use *chocosolver* to generate both non-optimal and optimal instances for the modeled E/E architectures. Figure 2.1 shows the workflow of how a Clafer file is compiled into one of the backend model formats then processed to generate instances. *Chocosolver* uses exact algorithms in order to find optimal instances based on single or multiple objectives.

In the following sections, the constructs of a Clafer model are explained along with examples. Additionally, we use the solver to show what instances are generated from the corresponding example models.

<sup>&</sup>lt;sup>1</sup>https://github.com/gsdlab/chocosolver

Figure 2.1: Overall workflow of Clafer and supported backend solvers.

### 2.1 Types of clafers and inheritance

In Clafer, a model consists of  $clafers^2$ . The name "clafer" comes from the words <u>cla</u>ss, <u>feature</u>, and <u>reference</u> because a clafer provides modeling capabilities of all these language constructs.

Clafers are organized in a containment hierarchy: root clafers can contain nested clafers, similarly to how classes can contain other classes and attributes. Each clafer defines a set of instances, similarly to how a class defines a set of its instances (objects). A clafer can be one of two types: abstract or concrete, similarly to classes. A concrete clafer results in an instance being generated, while an abstract one does not. Clafers are also organized in an inheritance hierarchy, like classes, with a restriction that only abstract clafers can be superclafers. Listing 2.1 shows an example of two abstract clafers Car and ElectricCar and two concrete clafers JanesCar and JohnsCar. Comments begin with //.

Listing 2.1: Example for concrete and abstract clafers

```

abstract Car // top-level abstract clafer

engine // nested concrete clafer

// an abstract clafer inheriting from an abstract clafer

abstract ElectricCar : Car

battery

// a concrete clafer inheriting from an abstract clafer

JanesCar : ElectricCar

// error: cannot inherit from a concrete clafer

```

$<sup>^{2}</sup>$ Throughout this paper if the word Clafer begins with an uppercase letter it describes the language, whereas a lowercase one denotes the language construct.

JohnsCar : JanesCar

The containment is specified using indentation, whereas inheritance if specified using colon (:). With respect to the containment hierarchy, we say that a clafer is a child of another clafer (e.g., engine is a child of Car) and a clafer is a parent of another clafer (e.g., Car is the parent of engine). With respect to the inheritance hierarchy, we say that a clafer is a superclafer of another one (e.g., Car is the superclafer of ElectricCar, which itself is a superclafer of JanesCar). Conversely, a clafer inherits from/is a subclafer of/extends another clafer (e.g., ElectricCar inherits from/is a subclafer of/extends Car).

#### 2.1.1 Instance generation

Given a Clafer model, a backend reasoner can generate all instances of the model in a given finite scope. For example, for the model in Listing 2.1 (without the incorrect JohnsCar) we get the following instance:

```

=== Instance 1 Begin ===

JanesCar

engine

battery

--- Instance 1 End ---

```

As we can see, only instances of the concrete clafer JanesCar and the inherited concrete clafers are generated. For simplicity, the instances have the same names as the clafers. To be fully explicit one would have to write the following, which we usually omit (we overload : to mean *instanceOf* relationship).

```

=== Instance 1 Begin ===

JanesCar : JanesCar

engine : engine

battery : battery

--- Instance 1 End ---

```

Note, that because inheritance is transitive, the instance JanesCar is also an instance of ElectricCar and Car.

### 2.2 Clafer multiplicity and group cardinality

Up to this point none of the concepts introduced have allowed for expressing variability in the model. Clafer provides two constructs expressing variability: clafer multiplicity and group cardinality. Clafer multiplicity is a range n..m indicating the allowed number of instances of the given clafer with respect to its parent. The most common multiplicities are 1..1 (mandatory) which requires one instance of the given clafer per instance of its parent; and 0..1 (optional) which allows for at most one instance of the given clafer per instance of its parent.

Group cardinalities are used to express variability over a group of children of the given clafer, hence the name. All clafers, by default have the group cardinality of 0...\*, that is, they do not impose any constraints on their children.

In Listing 2.2, we explicitly show the multiplicities of all clafers. By default, all abstract clafers have the multiplicity of 0..\*, which we usually omit. Also, by default, clafers have the multiplicity of 1..1 unless they are children of a group with cardinality other than 0..\*, in which case the default multiplicity is 0..1. For example, the clafer engine has multiplicity of 1 (short for 1..1), wheel has multiplicity of 4, and seat has the multiplicity of 2..4. These multiplicities specify that every instance of Car contains exactly one instance of engine, four instances of wheel, and between two and four instances of seat, respectively.

In Listing 2.2, the clafer transmission has group cardinality xor (keyword for 1..1) meaning that every instance of transmission must contain exactly one instance of its children (automatic or manual).

Listing 2.2: Example with explicit clafer multiplicities and a group cardinality

```

abstract Car 0..*

engine 1

xor transmission 1

automatic 0..1

manual ?

wheel 4

seat 2..4

abstract Chevy : Car 0..*

JohnsCar : Chevy 1

```

Using the instance generator, two of the 6 instances are:

=== Instance 1 Begin ===

```

JohnsCar

engine

transmission

automatic

wheel

wheel$1

wheel$2

wheel$3

seat

seat$1

--- Instance 1 End ---

=== Instance 4 Begin ===

JohnsCar

engine

transmission

manual

wheel

wheel$1

wheel$2

wheel$3

seat

seat$1

seat$2

--- Instance 4 End ---

```

Note that in order to distinguish the multiple instances of the same clafer from each other, a suffix **\$n** where n is the instance number is added.

Both model instances satisfy all multiplicity and group cardinality constraints; for example, the instance generator will never generate an instance which has both kinds of transmission or neither of them.

### 2.3 References

The last Clafer construct which allows for variability in models are reference clafers, that is, clafers whose instances can point to instances of other clafers or primitive values. Listing 2.3 shows an example of a clafer Car that contains two references driver and passenger, which denote the driver and passengers of the car, respectively. The type of the reference clafer driver is Person, which means that every instance of the clafer driver points to one instance of the clafer Person. The multiplicity of driver is 1..1, by default, so every instance of a Car will be always connected with one instance of Person via an instance of the reference clafer driver. The reference clafer passenger can have between zero and four instances, each pointing to an instance of Person. There are two kinds of reference clafers: set (specified using ->) and bag (multiset, specified using ->>). In our example, we do not want to allow the same person to be a passenger more than once, that is, the collection of passengers should be a set and we used -> to express that constraint.

Listing 2.3: Example using references

```

abstract Car

driver -> Person

passenger -> Person 0..4

MyCar : Car

John : Person

Jane : Person

```

abstract Person

A correct instance of this model then would have John or Jane as the driver because they are the only clafers of type Person in the model. The reference clafer passenger points to a set of size 0 to 4 meaning that up to four passengers can be in the car. A correct instance of this model can have no passengers, both John and Jane as passengers, or only John or only Jane as a passenger.

Two of eight possible instances for Listing 2.3 are:

```

=== Instance 1 Begin ===

MyCar

driver -> John

John

Jane

--- Instance 1 End ---

=== Instance 8 Begin ===

MyCar

driver -> Jane

```

```

passenger -> John

passenger$1 -> Jane

John

Jane

--- Instance 8 End ---

```

We can see two instances of the reference clafer passenger (passenger and passenger\$1) pointing to the instances of John and Jane, respectively. The following instance is incorrect.

```

MyCar

passenger -> John

passenger$1 -> John

John

Jane

```

First, a required instance of driver is missing, which violates the multiplicity driver 1..1; second, the same instance of John is a passenger twice, which violates the set constraint.

### 2.4 Writing Basic Constraints

So far all we have shown with Clafer is the ability to create models with large amounts of variability using references and cardinalities. When modeling real systems and problems a modeler also wants to use constraints in order to restrict the targets of references and the allowed configurations of the model. Additionally, constraints are used when wanting to query a model for one or more specific instances which satisfy the given constraints.

In this section, we give readers some of the basics for writing constraints but for conciseness it is not exhaustive. Readers should refer to other documentation found at http://www.clafer.org (we recommend "Clafer Cheat Sheet"<sup>3</sup> for an informal language reference). One general rule when writing constraints in Clafer, is that there are no scalars in the language, only sets, and therefore writing a number 1 really means a singleton set containing the number one. Similarly, we cannot directly access clafer instances (since they only exist at instance generation time) and instead we often use singleton sets. For example, the concrete clafer John : Person 1 is a singleton set which will contain exactly one instance, thus by writing constraints about the clafer John, we write constraints about its only instance.

$<sup>^{3}</sup> http://t3-necsis.cs.uwaterloo.ca:8091/ClaferCheatSheet$

Listing 2.4 builds on the previous two examples and adds some constraints. The constraints that we want to model are:

- C1: John is the driver of MyCar

- C2: Only Dan and Jane can be passengers in MyCar

- C3: The driver should not be in the set of passengers in a car

- C4: The total number of passengers with the driver can't exceed the number of seats in a car

A constraint is a Boolean expression surrounded by square brackets "[]". Just like clafers, constraints can be either top-level or nested. Nested constraints must hold for every instance of their context clafer (the clafer they are nested under); consequently an instance of the context clafer cannot exist unless all of its nested constraints hold.

In Listing 2.4, the constraint C1 is captured in line 10, whereby .dref gets the target value of the reference clafer (much like dereferencing a pointer in C/C++). C2 is then captured in line 11 in the model. Note the subtle differences between C1 and C2 in the constraints and the wording. For C1, set equality (the operator =) is used to restrict that the target of the reference *has to be* John. In C2, the wording is "can be" so subsetting is used (the keyword in). The difference between in and = is that the former can let the set be any of values to the right of the operation where the latter requires that the set is equal to the right of the operation (note the correct instances that can be generated). In C2, the wording is used (alternatively, it can be written as Jane ++ Dan).

Listing 2.4: Example using constraints

```

1 abstract Person

2

abstract Car

3

seat 2..4

driver -> Person

4

5

passenger -> Person 0..4

6

[driver.dref not in passenger.dref] // C3

7

[#(passenger, driver) <= #seat] // C4

8

9

MyCar : Car

10

[driver.dref = John] // C1

11

[passenger.dref in (Jane, Dan)] // C2

12

John : Person

13

Jane : Person

14 Dan : Person

```

Constraints C3 and C4 pertain to every instance of Car so the constraints are nested under Car. For C3 the not in enforces that the target of driver is not present in the set passenger.

C4 uses # to get the size of a set such that one can say the size of the union of sets passenger and driver is less than or equal to the size of the set seat. When using the instance generator 12 instances are found that satisfy the constraints and two of them are as follows:

```

=== Instance 3 Begin ===

MyCar

seats

seats$1

driver -> John

passenger -> Dan

John

Jane

Dan

--- Instance 3 End ---

=== Instance 11 Begin ===

MyCar

seats

seats$1

seats$2

seats$3

driver -> John

passenger -> Jane

passenger$1 -> Dan

John

Jane

Dan

--- Instance 11 End ---

```

Constraints are one of the most important aspects of Clafer for modeling systems since restrictions on system configurations, deployments, etc. can be constrained such that only correct systems are synthesized.

#### 2.5 Working with Integers

Clafer and its backends also support working with integers allowing for adding quantitative information to models. Currently, only integer arithmetic is supported, so working with numbers is cumbersome when modeling real systems.

Constraints can be used to model numerical relationships between components and get the total for a set of component. For example, Listing 2.5 takes the car example and models three features which have an associated cost.

Listing 2.5: Example using constraints

```

abstract Feature

cost -> integer

abstract Car

bluetooth : Feature

heatedSeats : Feature

passiveKeyEntry : Feature

MyCar : Car

[bluetooth.cost = 5]

[heatedSeats.cost = 10]

[passiveKeyEntry.cost = 25]

```

The constraints nested under MyCar configure an instance of Car by giving values to the different feature costs. The dot "." operator navigates from a parent to a child clafer or to the target of a reference. Using the instance generator gives just one correct instance as there is no variability in the model (all references have been tightly constrained and all multiplicities are fixed).

```

=== Instance 1 Begin ===

MyCar

passiveKeyEntry

cost -> 25

heatedSeats

cost$1 -> 10

bluetooth

cost$2 -> 5

--- Instance 1 End ---

```

#### 2.6 Optimization Objectives

In order to do optimization over qualities of a model, objectives must be defined. In Clafer, optimization objectives are captured through goals as in lines 26 and 27 of Listing 2.6. In this example the car with features is used but a second quality is added to represent the *comfort level* for a user. Also note that all of the features are optional (denoted by the ?, meaning cardinality 0..1) such that there is variability among the available features. In order to populate the used feature set of the Car the constraint C1 on lines 9, 13, and 17 constraints that this (the Feature) is in the set of parent's (the Car's) child feature. The constraint C2 on lines 21 and 22 sum the cost and comfort (respectively) of all the present features in the car to be used for the optimization goals.

Listing 2.6: Example using optimization

```

1

abstract Feature

2

cost -> integer

3

comfort -> integer

4

abstract Car

5

feature -> Feature 2..*

6

totalCost -> integer

7

totalComfort -> integer

8

bluetooth : Feature ?

9

[this in parent.feature] // C1

10

[cost = 5]

11

[comfort = 30]

12

heatedSeats : Feature ?

[this in parent.feature] // C1

13

14

[cost = 30]

[comfort = 10]

15

16

passiveKeyEntry : Feature ?

[this in parent.feature] // C1

17

\left[ \text{cost} = 40 \right]

18

19

[comfort = 10]

20

[totalCost = sum feature.cost] // C2

21

22

[totalComfort = sum feature.comfort]

23

24

MyCar : Car

25

26

<< minimize MyCar.totalCost >>

27

<< maximize MyCar.totalComfort >>

```

The instance generator configured for optimization finds 2 Pareto-optimal instances which

```

are shown below:

=== Instance 1 Begin ===

MyCar

feature -> bluetooth

feature$1 -> heatedSeats

totalCost -> 35

totalComfort -> 40

bluetooth

cost -> 5

comfort -> 30

heatedSeats

cost$1 -> 30

comfort $1 -> 10

--- Instance 1 End ---

=== Instance 2 Begin ===

MyCar

feature -> bluetooth

feature$1 -> heatedSeats

feature$2 -> passiveKeyEntry

totalCost -> 75

totalComfort -> 50

bluetooth

cost -> 5

comfort -> 30

heatedSeats

cost$1 -> 30

comfort -> 10

passiveKeyEntry

cost$2 -> 40

comfort $2 -> 10

--- Instance 2 End ---

```

What are the tradeoffs between these two instances? Instance 1 has the lowest cost, while sacrificing the comfort. Instance 2 has the highest comfort at the higher cost. Clafer tools include Clafer Multi-Objective Optimization (MOO) Visualizer, a tool for visualizing and exploring the set of optimal instances of a model, which allows the users to perform tradeoff analysis and find the instances most suitable for their needs [6]. A screenshot from the tool is shown in Figure 2.2 when visualizing the instances generated from Listing 2.6.

| Θ 😁                                                                                                                                                             | Input Clafer Model and Options                                      | : ?                              | Θ 😁                                                                                                                                                                                                                                                                                                                                                   | Bubble Front Graph                                                      | ? (             | ) 🕀 🔿                                                        | jectives and Quality | Ranges    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|--------------------------------------------------------------|----------------------|-----------|

| Choose File No file chose                                                                                                                                       | sen Opti                                                            | imize 🗹 Load into editor         |                                                                                                                                                                                                                                                                                                                                                       | · · · · · · · · · · · · · · · · · · ·                                   | min             | MyCar.totalCost                                              |                      | 3575      |

| Or Choose Example                                                                                                                                               | ▼ Opti                                                              | imize Use cached results         |                                                                                                                                                                                                                                                                                                                                                       |                                                                         | max             | MyCar.totalComf                                              | ort                  | 4050      |

| r enter your model:                                                                                                                                             | Opti                                                                | imize Scopes: Fast 🔻             |                                                                                                                                                                                                                                                                                                                                                       |                                                                         |                 |                                                              |                      |           |

| 1 → abstract Feature<br>2 cost -> integer                                                                                                                       |                                                                     |                                  | 51 -                                                                                                                                                                                                                                                                                                                                                  |                                                                         |                 |                                                              |                      |           |

| 3 comfort -> inte                                                                                                                                               |                                                                     |                                  | 50                                                                                                                                                                                                                                                                                                                                                    | 2                                                                       | 6               | •                                                            | Spider Chart         |           |

| 4 → abstract Car<br>5 feature -> Feat                                                                                                                           | ture 2*                                                             |                                  | 49 -<br>둔 48 -                                                                                                                                                                                                                                                                                                                                        | •                                                                       |                 |                                                              | MyCar.totalCost      | Variants: |

| 6 totalCost -> in                                                                                                                                               |                                                                     | *                                | ŭ 47 -                                                                                                                                                                                                                                                                                                                                                |                                                                         |                 |                                                              | • <sup>75</sup>      | 1         |

| Run optimization                                                                                                                                                | ☑ Def. scopes: 25                                                   | Max. int.: 127                   | 48 -<br>47 -<br>46 -<br>45 -<br>45 -<br>44 -                                                                                                                                                                                                                                                                                                          |                                                                         |                 |                                                              | 56.25                | 2         |

| Choco-based (MOO & ma                                                                                                                                           |                                                                     |                                  | 5 43-<br>5 44-                                                                                                                                                                                                                                                                                                                                        |                                                                         |                 |                                                              | 37.5                 |           |

|                                                                                                                                                                 |                                                                     |                                  | <u>ू</u> 43 -                                                                                                                                                                                                                                                                                                                                         |                                                                         |                 |                                                              | 18.75                |           |

| ⊖ ⊕                                                                                                                                                             | Output                                                              | Clear ?                          | ≥ 42-<br>41-                                                                                                                                                                                                                                                                                                                                          | -                                                                       |                 |                                                              |                      |           |

| Optimizing<br>Senerated all 2 optimal                                                                                                                           | L instance(s) within the scope                                      | <b>^</b>                         | 40 -                                                                                                                                                                                                                                                                                                                                                  |                                                                         |                 |                                                              |                      |           |

| laferMooVisualizer> Ba                                                                                                                                          | ackend output ends<br>ackend successfully executed                  |                                  | 39                                                                                                                                                                                                                                                                                                                                                    | <b>—</b>                                                                |                 |                                                              | ¥                    |           |

| ClaferMooVisualizer≻ Ba<br>ClaferMooVisualizer≻ Up                                                                                                              | ackend successfully executed<br>odating the views ClaferMooVisualiz | er> done!                        | 30                                                                                                                                                                                                                                                                                                                                                    | 35 40 45 50 55 60 65 70 75 80                                           |                 |                                                              |                      |           |

|                                                                                                                                                                 |                                                                     | v                                |                                                                                                                                                                                                                                                                                                                                                       | MyCar.totalCost                                                         |                 | м                                                            | vCar.totalComfort    |           |

|                                                                                                                                                                 |                                                                     |                                  |                                                                                                                                                                                                                                                                                                                                                       |                                                                         |                 |                                                              |                      |           |

|                                                                                                                                                                 |                                                                     |                                  |                                                                                                                                                                                                                                                                                                                                                       |                                                                         |                 |                                                              |                      |           |

|                                                                                                                                                                 |                                                                     |                                  |                                                                                                                                                                                                                                                                                                                                                       | Feature and Quality Matrix                                              | 1               |                                                              |                      |           |

| earch: search                                                                                                                                                   | Distinct Reset filters Save all v                                   |                                  | satisfy the cri                                                                                                                                                                                                                                                                                                                                       | Feature and Quality Matrix                                              | ality attribute | ۰ <u>د</u>                                                   |                      |           |

| earch: search                                                                                                                                                   |                                                                     |                                  | satisfy the cri                                                                                                                                                                                                                                                                                                                                       | Feature and Quality Matrix<br>teria Shown all matching @ Show nested qu | ality attribute | 15                                                           | 2                    |           |

|                                                                                                                                                                 | Distinct Reset filters Save all v<br>Model \ Variants               |                                  |                                                                                                                                                                                                                                                                                                                                                       | teria   Shown all matching   🖉 Show nested qu                           | ality attribute |                                                              | 2                    |           |

| iearch: search<br>MyCar = २                                                                                                                                     |                                                                     | variants 2 out of 2 variant(s) : | ×                                                                                                                                                                                                                                                                                                                                                     | teria   Shown all matching   🖉 Show nested qu<br>1                      | ality attribute | bluetooth                                                    | 2                    |           |

| iearch: search<br>MyCar = २                                                                                                                                     |                                                                     |                                  | blue                                                                                                                                                                                                                                                                                                                                                  | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats                                |                      |           |

| iearch: search<br>AyCar = २<br>feature 2*                                                                                                                       |                                                                     | variants 2 out of 2 variant(s) : | blue<br>hea                                                                                                                                                                                                                                                                                                                                           | teria   Shown all matching   🖉 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry             |                      |           |

| fearch: search<br>4yCar = ຈ<br>feature 2*<br>totalCost                                                                                                          |                                                                     | variants 2 out of 2 variant(s) : | blue<br>l23 35                                                                                                                                                                                                                                                                                                                                        | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75       |                      |           |

| earch: search<br>lyCar = v<br>feature 2*<br>totalCost<br>totalComfort                                                                                           |                                                                     | variants 2 out of 2 variant(s) : | k k k k k k k k k k k k k k k k k k k                                                                                                                                                                                                                                                                                                                 | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry             |                      |           |

| iearch: search<br>AyCar = = =<br>feature 2*<br>totalCost<br>totalCost<br>totalComfort<br>bluetooth ? = =                                                        |                                                                     | variants 2 out of 2 variant(s) : | ×<br>blue<br>hea<br>223 35<br>223 40                                                                                                                                                                                                                                                                                                                  | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75       |                      |           |

| <pre>kearch: search dyCar = s feature 2* totalCost totalComfort bluetooth ? = s cost = 5</pre>                                                                  |                                                                     | variants 2 out of 2 variant(s) : | 23 35<br>123 40                                                                                                                                                                                                                                                                                                                                       | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75       |                      |           |

| AyCar = s<br>feature 2*<br>totalCost<br>totalComfort<br>bluetooth ? = s<br>cost = 5<br>comfort = 30                                                             |                                                                     | variants 2 out of 2 variant(s) : | K           blue           123           40           123           123           123           123                                                                                                                                                                                                                                                   | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75       |                      |           |

| <pre>kearch: search  dyCar = = = feature 2*  totalCost totalComfort bluetooth? = ===== comfort = ====== heatedSeats ? = =================================</pre> |                                                                     | variants 2 out of 2 variant(s) : | 23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>2                                                                                                                                                                                                                                                                       | teria   Shown all matching   🗹 Show nested qu<br>1                      | allty attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75       |                      |           |

| AyCar = s<br>feature 2*<br>totalCost<br>totalComfort<br>bluetooth ? = s<br>cost = 5<br>comfort = 30                                                             |                                                                     | variants 2 out of 2 variant(s) : | 23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>2                                                                                                                                                                                                                                                                       | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75       |                      |           |

| <pre>kearch: search  dyCar = = = feature 2*  totalCost totalComfort bluetooth? = ===== comfort = ====== heatedSeats ? = =================================</pre> |                                                                     | variants 2 out of 2 variant(s) : | ×         blue           ka         blue           ka         35           ka         40           ka         ka              | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | X<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75<br>50 |                      |           |

| earch: search<br>dyCar = n<br>feature 2*<br>totalCost<br>totalComfort<br>bluetooth ? = n<br>cost = 30<br>cost = 30                                              |                                                                     | variants 2 out of 2 variant(s) : | x<br>bluk<br>hea<br>282<br>35<br>40<br>283<br>40<br>283<br>283<br>40<br>283<br>283<br>283<br>283<br>283<br>283<br>293<br>293<br>293<br>293<br>293<br>293<br>293<br>293<br>293<br>29                                                                                                                                                                   | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | ×<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75       |                      |           |

| <pre>tearch: search  dyCar = n feature 2*  totalCost  totalCost  totalComfort  bluetooth ? = n cost = 5  comfort = 30  comfort = 10 </pre>                      |                                                                     | variants 2 out of 2 variant(s) : | X           blue           ka           ka | teria   Shown all matching   🗹 Show nested qu<br>1                      | ality attribute | X<br>bluetooth<br>heatedSeats<br>passiveKeyEntry<br>75<br>50 |                      |           |

Figure 2.2: Screenshot of MOO Visualizer for Listing 2.6.

## Chapter 3

# **Reference Model**

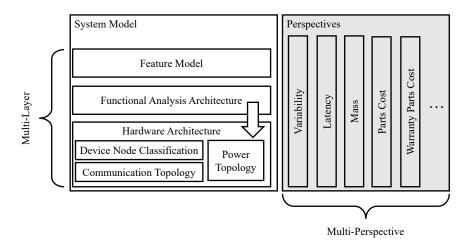

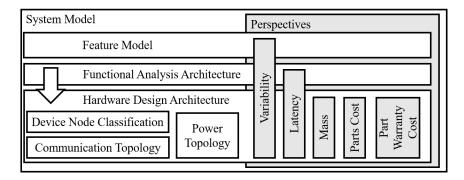

Using the motivational scenario, in this section we define a reference model (for the remainder of this paper we refer to it as the reference model) that supports early design of E/E system architectures. Similar to the EAST-ADL, the reference model is made up of multiple abstraction layers. Each layer describes the system, but at a different level of abstraction. We use the term *multi-layer* to describe models consisting of multiple layers. The reference model also contains multiple perspectives, which augment the system with analysis-task or stakeholder-specific information such as points of variability, latency, and mass; we use the term *multi-layered*, *multi-perspective* reference model with the supported perspectives covered in this paper. We use an ellipses in the perspectives to show that the reference model is not limited to the ones shown, but could be extended with additional ones.

When a perspective is combined with a multi-layered model, it may cross-cut some or all the layers. For example, the mass perspective applies primarily to the hardware architecture, where devices and wires are assigned mass; however, mass information can also be aggregated at the feature level.

The reference model we define is similar to the EAST-ADL domain model; however, the one defined here focuses on the early design stages and does not consider the lower-level software decomposition for the system. More precisely, the simplified model does not consider the functional design architecture of the EAST-ADL; instead, it maps the functional analysis architecture on the hardware design architecture. Additionally, the reference model contains cross-cutting concerns that are not present in the EAST-ADL such as cost and

Figure 3.1: The reference model used for early design of automotive E/E systems architecture.