# Memory Efficient Scheduling for Multicore Real-time Systems

by

Ahmed Alhammad

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2016

© Ahmed Alhammad 2016

### Author's Declaration

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Statement of Contributions**

This dissertation is split into six chapters. In Chapter 2, we provide background material and discuss the related work. In particular, we first discuss the memory subsystem and focus on the relevant issues that may influence the predictability of timing behavior. Second, a survey of related work is provided for the problem of memory bus contention including the co-scheduling approach. For the latter, we discuss the limitations that may arise in some practical settings. We conclude Chapter 2 by providing an overview of multiprocessor real-time scheduling theory for both sequential and parallel tasks. Some of the discussion about cache management in Section 2.1.1 is reprinted, with permission, from [62] in which I am a co-author.

We recall that the main contribution of this dissertation is integrating memory time into multiprocessor real-time scheduling for both sequential and parallel tasks. In Chapter 3 and 4, we focus on sequential tasks while in Chapter 5 we focus on parallel tasks. The main findings of these three chapters have been disseminated in four published papers in which I am the main author [4, 7, 6, 5]. In particular, Chapter 3 extends the coscheduling approach [108], originally with two phases of load and computation, by adding an extra phase to unload modified data back to main memory. As well, we show how to dynamically schedule the new 3-phase execution model in a multitasking environment. We further propose an algorithm to globally schedule 3-phase sequential tasks on a multicore processor. Since the schedulability test is as important as the scheduling algorithm, we also provide a schedulability analysis for this algorithm. In particular, a new concept of schedule hole is introduced to account for memory time. Furthermore, an analysis method is proposed for the same algorithm where each task is split into multiple segments. This scheme is necessary for some large tasks that cannot fit inside the local memory of one core at one time. We note that sections 3.4 and 3.6 are reprinted, with permission, from [4]. The notations and the figures have been modified to harmonize with the rest of the dissertation.

While the previous chapter assumes that processor cores are stalled while loading from main memory, Chapter 4 proposes a new memory efficient algorithm to globally schedule 3-phase sequential tasks on a multicore processor equipped with a DMA component to further enhance the memory utilization. In this chapter, the DMA is used to load one task while the core is busy executing another task. Since the system comprises two types of active components (processor cores and DMA), a new concept of *scheduling interval* is introduced to account for the workload of 3-phase tasks on processor cores and the DMA. Sections 4.1 to 4.3 of this chapter are reprinted, with permission, from [7]. Again, the notations and the figures have been modified. In Chapter 5, a novel method is proposed to trade in processor cores for memory bandwidth. This method works for parallel tasks that need more than one core to execute. In particular, a federated scheduling scheme is adopted in which each parallel task is assigned a dedicated number of cores and memory bandwidth. Unlike the co-scheduling approach, we assume no arrival pattern of memory requests (no load and unload phases) and the scheduling algorithm of each parallel task on its cluster of cores can be any dynamic work-conserving algorithm. To further enhance the execution performance, we propose a static algorithm to schedule parallel tasks on their dedicated cluster of cores. The objective of this algorithm is to minimize the *makespan* of real-time parallel tasks. In addition, the co-scheduling approach is used to enhance the memory time. Sections 5.8 and 5.9 are reprinted, with permission, from [5], and the rest of the sections are reprinted, with permission, from [6].

We conclude this dissertation in Chapter 6 and provide directions to carry out relevant research in the future.

#### Abstract

Modern real-time systems are becoming increasingly complex and requiring significant computational power to meet their demands. Since the increase in uniprocessor speed has slowed down in the last decade, multicore processors are now the preferred way to supply the increased performance demand of real-time systems.

A significant amount of work in the real-time community has focused on scheduling solutions for multicore processors for both sequential and parallel real-time tasks. Even though such solutions are able to provide strict timing guarantees on the overall response time of real-time tasks, they rely on the assumption that the worst-case execution time (WCET) of each individual task is known. However, physical shared resources such as main memory and I/O are heavily employed in multicore processors. These resources are limited and therefore subject to contention. In fact, the execution time of one task when run in parallel with other tasks is significantly larger than the execution time of the same task when run in isolation. In addition, the presence of shared resources increases the timing unpredictability due to the conflicts generated by multiple cores. As a result, the adoption of multicore processors for real-time systems is dependent upon solving such sources of unpredictability.

In this dissertation, we investigate memory bus contention. In particular, two main problems are associated with memory contention: (1) unpredictable behavior and (2) hindrance of performance. We show how to mitigate these two problems through scheduling. Scheduling is an attractive tool that can be easily integrated into the system without the need for hardware modifications. We adopt an execution model that exposes memory as a resource to the scheduling algorithm. Thus, the theory of real-time multiprocessor scheduling, that has seen significant advances in recent years, can be utilized to schedule both processor cores and memory. Since the real-time workload on multicore processors can be modeled as sequential or parallel tasks, we also study parallel task scheduling by taking memory time into account.

#### Acknowledgements

First of all, I would like to thank my advisor Rodolfo Pellizzoni. It has been an honor to be his first PhD student. I really appreciate all his efforts of time and ideas that made my PhD productive and fruitful. His dedication and contiguous enthusiasm on my research have been motivational for me to proceed during the tough times.

I also would like to thank my committee members, Marko Bertogna, Sebastian Fischmeister, Hiren Patel and Bill Cowan for their valuable feedback and suggestions.

Special thanks go to my colleague Saud Wasly for his great support in many occasions during my study. In particular, the times before the comprehensive exam and the PhD defense. I am also grateful for my meetings with him to brainstorm new ideas and discuss the small details of my research.

My thanks extend to the rest of my research group that I sadly did not have a chance to write papers with them, but their help and feedback are highly appreciated. I would also like to express my thanks and appreciation to my co-authors Giovani Gracioli and Renato Mancuso.

I am grateful to King Saud University for their financial support. Without their support, I probably would not have the opportunity to attend a great school like the University of Waterloo. I am also grateful for Saudi Cultural Bureau in Canada for being always available to answer my questions and provide support.

My time at Waterloo was made enjoyable due to the many friends that became a part of my life. I would like to thank the Saudi Club at Waterloo for organizing the weekly gatherings and outdoor activities. I am grateful for the time spent with my friends cycling and kayaking the Grand river.

Foremost, I thank my parents Haya and Ibrahim for their endless love, optimism and being with me at all times with their prayers. You always inspirit me to do the best in my life. My great thanks go to my wife Hajer for her love, patience and trust that I was doing the right thing. I could not have finished my PhD without you.

### Dedication

To my wife Hajer and my son Ibrahim

# **Table of Contents**

## List of Figures

| 1 | Intr | oducti | ion                                               | 1  |

|---|------|--------|---------------------------------------------------|----|

|   | 1.1  | Memo   | ry Bus Contention                                 | 3  |

|   | 1.2  | The C  | o-Scheduling Approach                             | 3  |

|   | 1.3  | Disser | tation Theme and Problem Statement                | 6  |

| 2 | Bac  | kgrou  | nd and Related Work                               | 7  |

|   | 2.1  | Memo   | ry Subsystem                                      | 7  |

|   |      | 2.1.1  | Cache Memory                                      | 8  |

|   |      | 2.1.2  | Scratchpad memory                                 | 11 |

|   |      | 2.1.3  | Off-chip Memory                                   | 12 |

|   | 2.2  | Memo   | ry Bus Contention                                 | 13 |

|   |      | 2.2.1  | The Co-Scheduling Approach                        | 16 |

|   |      | 2.2.2  | Limitations Imposed by the Co-Scheduling Approach | 18 |

|   |      | 2.2.3  | Memory Space Allocation                           | 20 |

|   | 2.3  | Multip | processor Real-time Scheduling                    | 21 |

|   |      | 2.3.1  | Task Model                                        | 22 |

|   |      | 2.3.2  | Hard Real-time                                    | 23 |

|   |      | 2.3.3  | Preemption and Migration                          | 24 |

|   |      | 2.3.4  | Static and Dynamic                                | 24 |

|   |      | 2.3.5  | Schedulability Test                               | 25 |

xi

| 3 | Global Scheduling of 3-phase Sequential Tasks |                             |                                             | <b>29</b> |

|---|-----------------------------------------------|-----------------------------|---------------------------------------------|-----------|

|   | 3.1                                           | Conte                       | ntion-based Execution                       | 31        |

|   | 3.2                                           | System                      | n Model                                     | 31        |

|   | 3.3                                           | Deadli                      | ine Analysis                                | 34        |

|   | 3.4                                           | Schedu                      | uling Example of gPREM                      | 38        |

|   | 3.5                                           | 5 Scheduler Design of gPREM |                                             |           |

|   | 3.6 Schedulability Analysis                   |                             |                                             | 40        |

|   |                                               | 3.6.1                       | Carry-in Workload Limit                     | 41        |

|   |                                               | 3.6.2                       | Bounding $W_k^{CI}(\Gamma)$                 | 44        |

|   |                                               | 3.6.3                       | Bounding $W_k^{NC}(\Gamma)$                 | 45        |

|   |                                               | 3.6.4                       | Schedulability Condition                    | 51        |

|   | 3.7                                           | Task S                      | Splitting                                   | 53        |

|   |                                               | 3.7.1                       | The Problem Window of Multi-segment Job     | 54        |

|   |                                               | 3.7.2                       | The Workload of Multi-segment Carry-out Job | 54        |

|   |                                               | 3.7.3                       | The Workload at the Beginning Interval      | 56        |

|   |                                               | 3.7.4                       | The Workload at the Middle Intervals        | 57        |

|   | 3.8                                           | 8 Evaluation                |                                             | 59        |

|   |                                               | 3.8.1                       | An Intuitive View                           | 59        |

|   |                                               | 3.8.2                       | Results                                     | 60        |

|   | 3.9                                           | Summ                        | ary                                         | 64        |

| 4 | DM                                            | A Glo                       | bal Scheduling of 3-phase Sequential Tasks  | 65        |

|   | 4.1                                           | Schedu                      | uling Algorithm                             | 66        |

|   | 4.2                                           | Schedu                      | uler Design of gDMA                         | 68        |

|   | 4.3                                           | 3 Schedulability Analysis   |                                             | 69        |

|   |                                               | 4.3.1                       | Bounding the Interfering Jobs               | 70        |

|   |                                               | 4.3.2                       | Bounding the Individual Workload $W_k(J_i)$ | 74        |

|   |                                               | 4.3.3                       | Bounding the Total Workload $W_k(\Gamma)$   | 77        |

|   |                                               |                             |                                             |           |

|    |                | 4.3.4 Bounding the Interference on a Problem Job | 80  |  |  |

|----|----------------|--------------------------------------------------|-----|--|--|

|    |                | 4.3.5 Schedulability Condition                   | 81  |  |  |

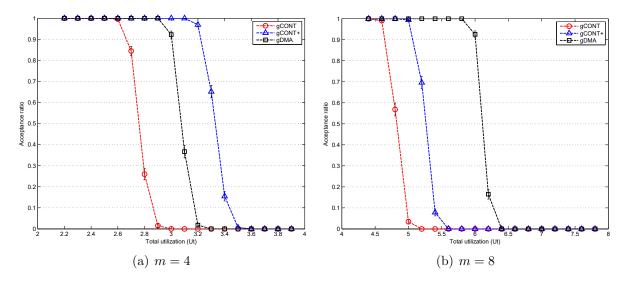

|    | 4.4            | Evaluation                                       | 82  |  |  |

|    |                | 4.4.1 Results                                    | 84  |  |  |

|    | 4.5            | Summary                                          | 86  |  |  |

| 5  | Tra            | ding Cores for Memory Bandwidth                  | 87  |  |  |

|    | 5.1            | System Model                                     | 89  |  |  |

|    | 5.2            | Federated Scheduling                             | 90  |  |  |

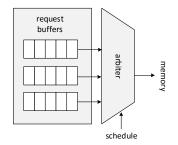

|    | 5.3            | Bus Arbiter                                      | 92  |  |  |

|    | 5.4            | Integrating Memory Demand                        | 93  |  |  |

|    |                | 5.4.1 RR with $(m)$ Request Buffers $\ldots$     | 95  |  |  |

|    |                | 5.4.2 RR with $(n)$ Request Buffers              | 95  |  |  |

|    | 5.5            | Trading Cores for Memory Bandwidth               | 96  |  |  |

|    | 5.6            | Optimal-Assign Implementation                    | 98  |  |  |

|    |                | 5.6.1 Software Regulated Memory                  | 98  |  |  |

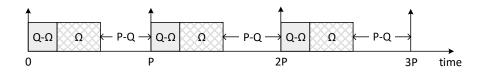

|    |                | 5.6.2 Harmonic RR                                | 104 |  |  |

|    | 5.7            | Evaluation                                       | 107 |  |  |

|    | 5.8            | Static Scheduling of 3-phase Parallel Task       | 111 |  |  |

|    | 5.9            | mthPREM Evaluation                               | 116 |  |  |

|    | 5.10           | Summary                                          | 119 |  |  |

| 6  | Con            | nclusion 1                                       | 121 |  |  |

| Re | References 123 |                                                  |     |  |  |

# List of Figures

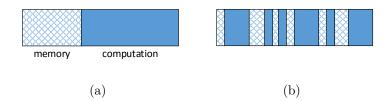

| 1.1 | In (a), memory accesses are concentrated at the beginning while in (b) they are spread across task's execution.             | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

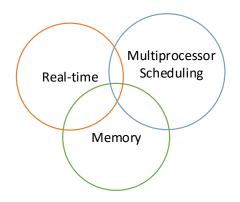

| 1.2 | Dissertation theme and scope                                                                                                | 5  |

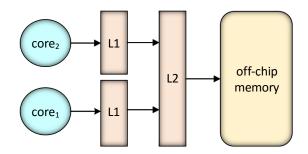

| 2.1 | The levels of memory hierarchy.                                                                                             | 8  |

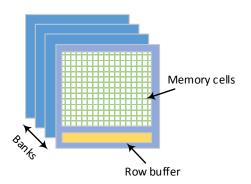

| 2.2 | Multibank DRAM.                                                                                                             | 12 |

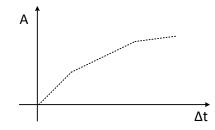

| 2.3 | An arrival curve specifies the maximum number of memory requests that can be generated within a window of time $\Delta t$ . | 14 |

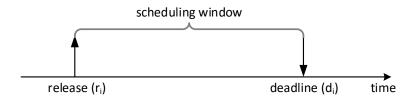

| 2.4 | A job needs to execute for amount of time equal to its WCET between its release time and deadline.                          | 22 |

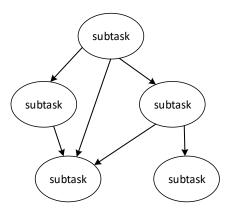

| 2.5 | DAG task                                                                                                                    | 23 |

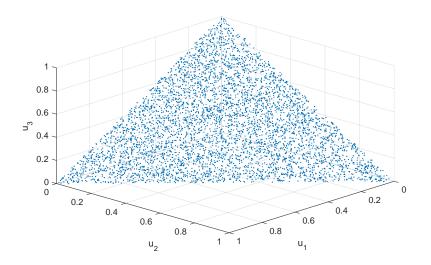

| 2.6 | 5000 task sets of UUNIFAST $(3,1)$                                                                                          | 26 |

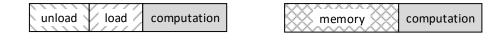

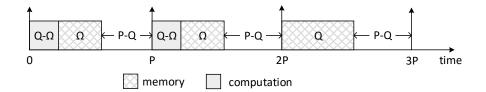

| 3.1 | 3-phase execution model                                                                                                     | 29 |

| 3.2 | Simplified 3-phase task                                                                                                     | 30 |

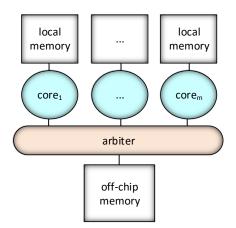

| 3.3 | Abstracted hardware architecture                                                                                            | 32 |

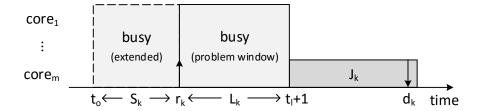

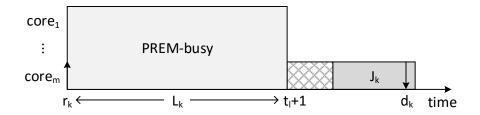

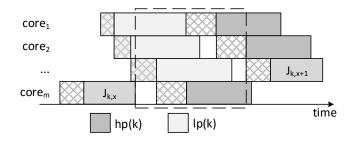

| 3.4 | The necessary condition for $J_k$ to miss its deadline                                                                      | 34 |

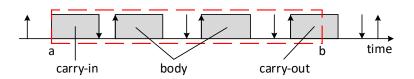

| 3.5 | The workload of a task inside a window of time $[a, b]$                                                                     | 35 |

| 3.6 | The workload without and with carry-in                                                                                      | 37 |

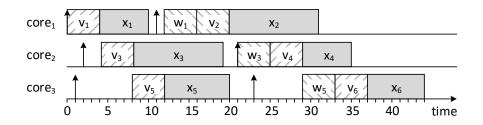

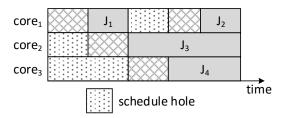

| 3.7 | An example of gPREM schedule for six jobs on three cores                                                                    | 38 |

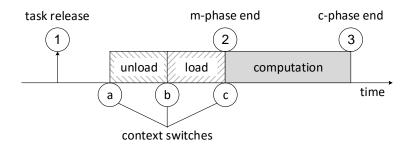

| 3.8 | Scheduling decisions and context switches.                                                                                  | 39 |

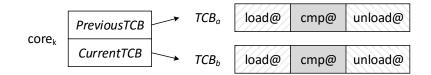

| 3.9 | Task's TCB and core's pointers.                                                                                             | 40 |

| 3.10 | A necessary condition for a problem job $J_k$ to miss its deadline                                      | 41 |

|------|---------------------------------------------------------------------------------------------------------|----|

| 3.11 | Only one task can have memory carry-in at $t_o$                                                         | 43 |

| 3.12 | The workload in a window of interest                                                                    | 44 |

| 3.13 | gPREM schedule with <i>schedule holes</i>                                                               | 46 |

| 3.14 | Based on the order of execution, the size of schedule hole changes $(h_1 < h_2)$ .                      | 47 |

| 3.15 | An example for computing a lower bound on <i>overlap</i>                                                | 48 |

| 3.16 | The way $overlap'$ is computed                                                                          | 49 |

| 3.17 | The gaps between memory phases increase the amount of overlap                                           | 50 |

| 3.18 | An illustrative diagrams to help proving lemma 6                                                        | 50 |

| 3.19 | A necessary condition for $J_k$ to miss its deadline                                                    | 54 |

| 3.20 | The workload of multi-segment carry-out job.                                                            | 55 |

| 3.21 | The workload of $lp(k)$ tasks in a middle interval                                                      | 58 |

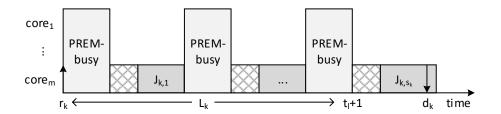

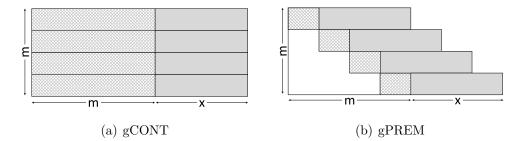

| 3.22 | The workload of gCONT and gPREM                                                                         | 59 |

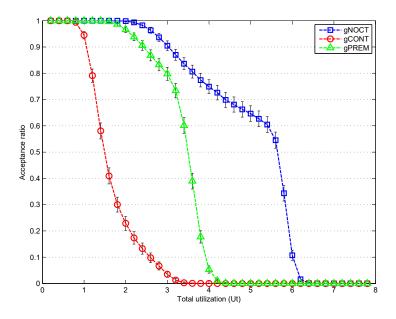

| 3.23 | The schedulability of gPREM against gCONT and gNOCT.                                                    | 62 |

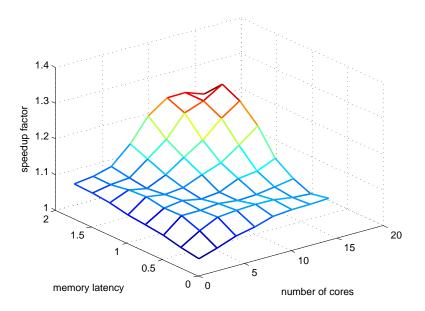

| 3.24 | The speedup factor by varying $m$ and memory latency                                                    | 62 |

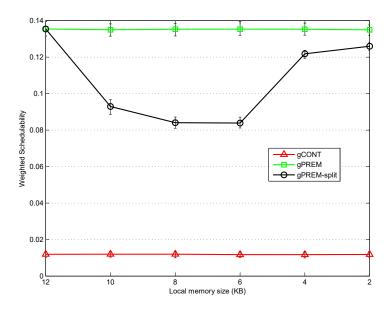

| 3.25 | Weighted schedulability as a function of local memory size                                              | 63 |

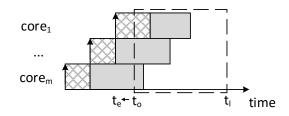

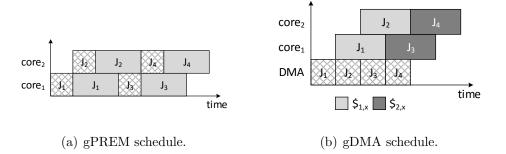

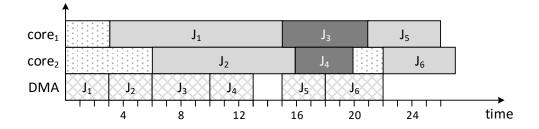

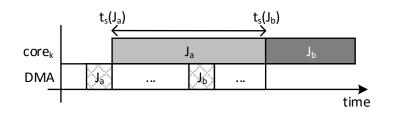

| 4.1  | The memory phases of $J_3$ and $J_4$ are completely hidden                                              | 66 |

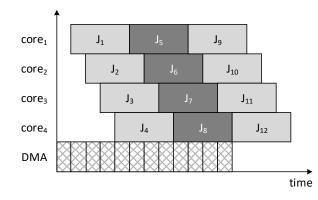

| 4.2  | An example of gDMA schedule of 6 jobs on 2 cores                                                        | 67 |

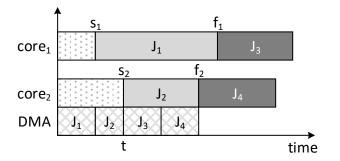

| 4.3  | The cores are chosen based on minimum $s_k$                                                             | 68 |

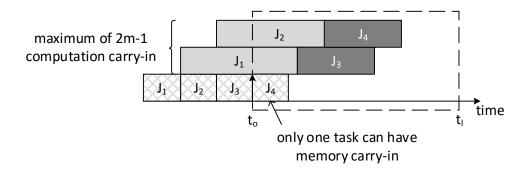

| 4.4  | Carry-in limit.                                                                                         | 72 |

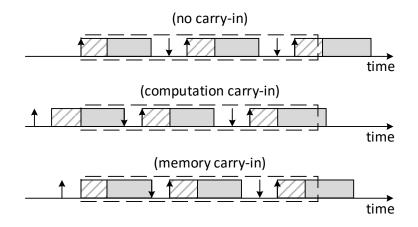

| 4.5  | The interfering jobs of tasks $\in hp(k)$ with no carry-in, computation carry-in<br>and memory carry-in | 73 |

| 4.6  | Scheduling interval examples.                                                                           | 75 |

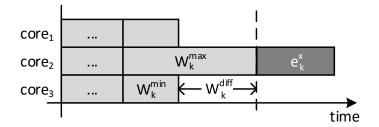

| 4.7  | The computation phase of the problem job executes after $W_k^{max}$                                     | 80 |

| 4.8  | A comparison between gDMA and gCONT.                                                                    | 83 |

| 4.9  | The schedulability of gDMA, gCONT and gCONT+                                                            | 84 |

| 4.10 | The schedulability of gDMA, gPREM, gCONT.                                                               | 85 |

| 5.1  | Bus arbiter design.                                                                                     | 92  |

|------|---------------------------------------------------------------------------------------------------------|-----|

| 5.2  | 4-core bus schedule and $\{\frac{1}{2}, \frac{1}{4}, \frac{1}{8}, \frac{1}{8}\}$ bandwidth requirements | 93  |

| 5.3  | Two sub-cases for contention mode                                                                       | 101 |

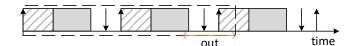

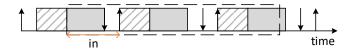

| 5.4  | Two modes of operation for Memguard                                                                     | 104 |

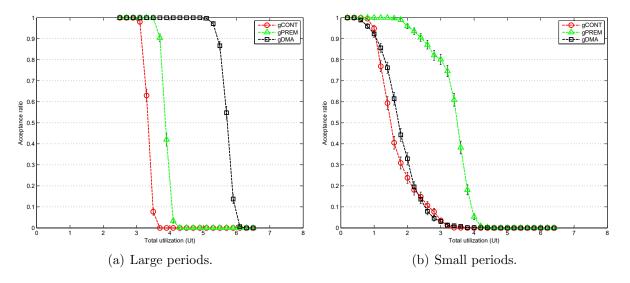

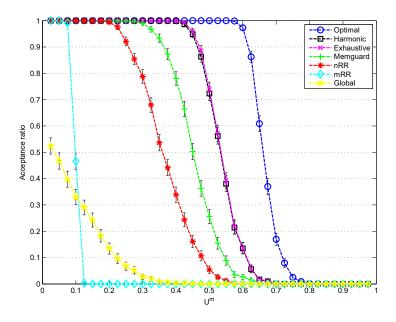

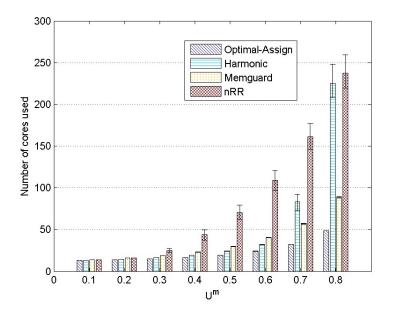

| 5.5  | The schedulability for all arbitration policies with acceptance ratio metric and varying $Um$ .         | 107 |

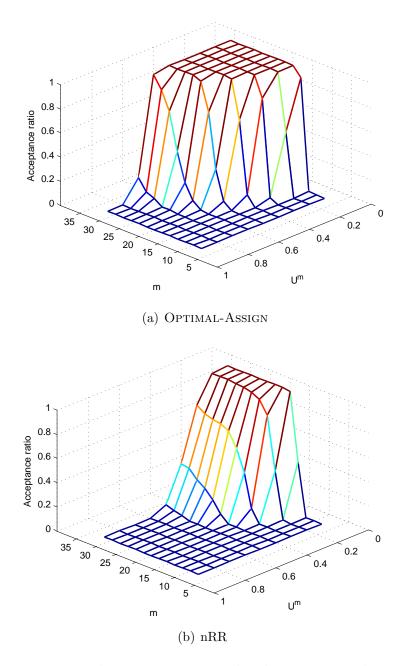

| 5.6  | The acceptance ratio by changing $m$ and $Um$                                                           | 109 |

| 5.7  | The number of cores used, $m^{used}$                                                                    | 110 |

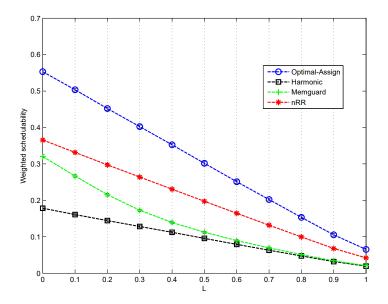

| 5.8  | The effect of changing $L_i$                                                                            | 111 |

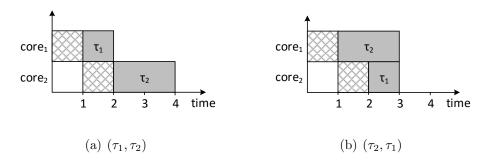

| 5.9  | The order of execution decides the makespan length. $\ldots$                                            | 112 |

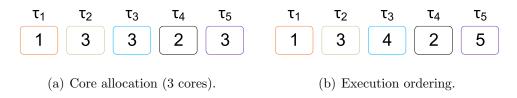

| 5.10 | GA chromosomes.                                                                                         | 114 |

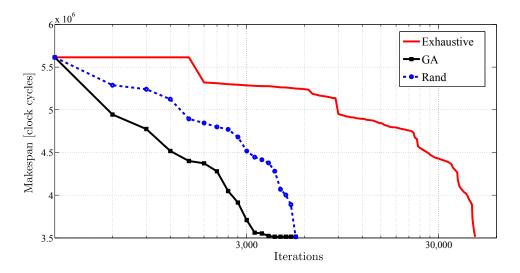

| 5.11 | Comparison between exhaustive, random and GA                                                            | 115 |

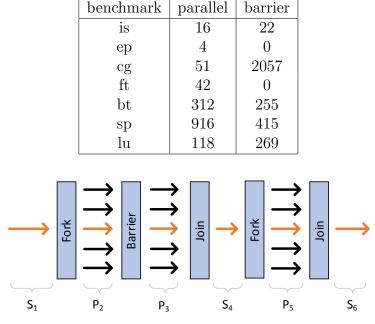

| 5.12 | Fork-join parallel model.                                                                               | 116 |

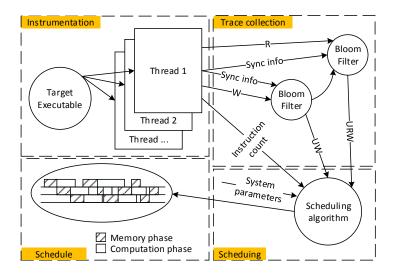

| 5.13 | Evaluation framework.                                                                                   | 117 |

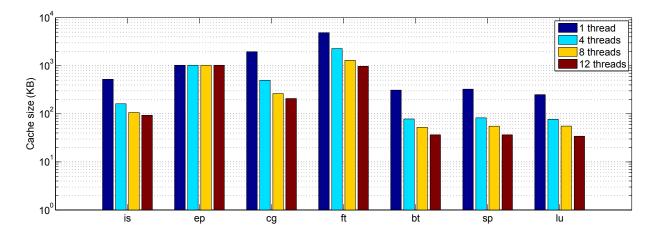

| 5.14 | Maximum memory footprint                                                                                | 118 |

| 5.15 | Simulation results for 8 subtasks and 4 cores processor                                                 | 119 |

| 5.16 | Memory scatter ratio.                                                                                   | 120 |

# Chapter 1

## Introduction

Modern real-time applications are becoming increasingly complex and asking for more computational power. They expand beyond simple control loops to include image and video processing, advanced I/O and distributed coordination. In order to meet the increasing demands of real-time applications, a higher performance computing platform is needed. Unfortunately, *uniprocessor* design hits a fundamental problem: heat dissipation. The faster the processor runs; the more heat it generates. In fact, the development of a new uniprocessor design from Intel, the world's largest chip maker, has been canceled in 2004 due to heat dissipation and extreme power consumption. Two years later, Intel released the first dual-core processor which marked a trend in current technology to replicate multiple processors in order to increase the processing power. Thus, real-time applications are inevitably forced to use *multicore* processors to supply their increasing processing demand. Moreover, the speed of memory subsystem is equally important for the overall execution performance. As a result, multicore processors need to use architectural features such as caches or scratchpads to bridge the gap between the processing power and memory speed.

Most hard real-time systems are safety critical in which system failure leads to severe damage or loss of life. These systems are required to respond to events within a limited time-span referred to as a *deadline*. Thus, hard real-time systems require a timing validation known as *schedulability analysis* to guarantee, before executing the system, that system's tasks will complete by their deadlines. However, the schedulability analysis needs as input the **worst-case execution time (WCET)** of each task. The estimation of WCET has to be *safe*, i.e., above or equal any possible execution time, and should be *tight*, i.e., close to the actual execution time. It is worthwhile to note that in real-time systems there is no advantage in completing the task before its deadline; instead, the matter is how to precisely estimate its WCET. Often, overestimates can cause a task to be unschedulable even though the existing system has the capacity to accommodate its demands. A related property is *predictability* of temporal behavior. Instead of having Boolean (black and white) definition, [10] defines predictability as the ratio between the best-case and the worst-case behavior. That is, a component with constant-time behavior is 100% predictable, and this percentage decreases as the difference between the best-case and the worst-case behavior increases.

Still, estimating the WCET of any task is difficult because it may vary from execution to execution for several reasons. First, the control flow of the application may contain different conditional branches in which their flow depends on the input and these branches have different execution times. Second, the hardware platform usually has stateful components such as caches or pipelines. The state of these components affects the application execution time as the component state depends on the execution history. Third, a core inside multicore processor is not an independent entity but rather shares physical resources with other cores such as last-level cache and main memory. In single core processor, concurrent tasks are executed sequentially, even though virtual parallelism is permitted. The sequential execution implies that two tasks can never access two shared resources simultaneously. However, the situation is different in multicore processor. Two tasks can run simultaneously on different cores and access shared resources at the same time. It has been shown in [148] that the execution time of one application can vary significantly due to shared resource contention. In particular, an experiment is conducted on Intel 4-core processor with SPEC CPU2006 applications. The results show that the execution time of one application can increase by 56% compared to the execution time of the same application when run in isolation. Resource contention has also been acknowledged by certification authorities [55], and it represents a source of concern for the use of multicore processors in avionics systems.

Previous research has mainly focused on cache-space contention [62]; however, the results in [148] indicate, through extensive experimentation on real systems, that memory bus contention is also significant in influencing the execution time of applications. Memory requests of processor cores are mediated by an *arbiter*. Once one core gains access to main memory, all other cores are blocked, and hence experience delays. Thus, memory contention introduces additional blocking times during execution. These additional delays must be accounted for in the response time of real-time tasks. In this dissertation, we will focus on this problem that affects the predictability of WCET of real-time tasks.

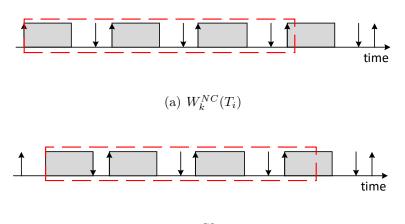

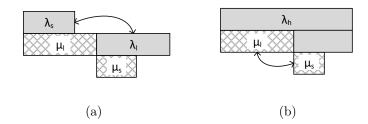

Figure 1.1: In (a), memory accesses are concentrated at the beginning while in (b) they are spread across task's execution.

### **1.1** Memory Bus Contention

The classical multiprocessor real-time scheduling theory focuses on processor cores in which the scheduling algorithm knows nothing about the resulting memory latency of its schedule. It either assumes an idealized multicore processor where tasks access memory without contention or the contention delay is integrated into the WCET of tasks. Prior work has proposed analysis-based methods to account for these memory delayes [120, 36, 127, 109, 125, 43]. These methods rely on these two pieces of information to derive the memory delay: the arbitration policy of the hardware and the memory access pattern of real-time tasks. However, these approaches have some drawbacks. First, it is very hard to capture the task's memory access pattern. In a cache-based system, for instance, memory accesses are results of cache misses, and these misses depend on the program execution path as well as the replacement policy and the current state of the cache. Second, some platforms employ unfair arbitration policies in which some requests are favored against others to utilize the memory bandwidth or, in some cases, the arbitration policy is not documented. Third, the notion of task priority is not reflected in hardware arbiters. Thus, the analysis often assumes that tasks on other cores have higher priority memory requests. Finally, most of these works analyze individual tasks or assume tasks repeat a simple offline schedule. To avoid these drawbacks, we adopt in this dissertation the co-scheduling approach [108] which can provide a tighter upper-bound on memory time while using the existing solutions for multiprocessor real-time scheduling.

## 1.2 The Co-Scheduling Approach

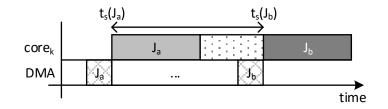

In this approach, each task is split into two phases: memory and computation as shown in Figure 1.1(a). During a memory phase, the code and data of each real-time task is

loaded from main memory to local memory of processor core before execution. Then, the core, during the computation phase, executes the task out of its local memory without accessing main memory. This ensures that the memory accesses are concentrated at the beginning of the task, i.e., simple and clear access pattern. In contrast, memory accesses, if not controlled, are very hard to predict as in Figure 1.1(b). As mentioned early, memory requests are results of cache misses, and these requests depend on the execution path of the program and the state of the cache. In addition, by explicitly exposing the memory demand of each task to the scheduling algorithm, the toolbox of multiprocessor real-time scheduling can be leveraged to schedule both memory and processor cores, hence the name co-scheduling. This approach has been demonstrated on real hardware platforms in [119, 53, 30]. A detailed discussion about the implementation part of this approach is presented in Section 2.2.2.

Prior work has looked into the co-scheduling approach for different reasons. First, it is used in [108] to de-conflict the traffic to main memory between tasks running on single core and I/O devices. Second, the work in [15] uses **time division multiple access** (**TDMA**) to partition the memory bandwidth between cores. To utilize the slots of a memory schedule, the priority of memory phases is increased over computation phases during the allotted slots. Thus, a memory slot is never wasted while there is a ready memory phase. Third, it is used in [99] to speedup the transfer time of memory. The rationale behind this work is that it is generally easier to improve memory bandwidth than it is to reduce memory latency. In fact, cache designers tend to increase block size to take advantage of high memory bandwidth [70]. This advantage is clear with memory phases are engineered to perform efficient back-to-back transfers.

In this dissertation, however, we adopt the co-scheduling approach as a way to (1) avoid memory contention in a multicore processor and (2) enhance memory utilization. First, memory contention is avoided by allowing only one memory phase to be active in the system at any time. In other words, the scheduler from software level ensures in proactive manner that tasks do not interfere for access to main memory. Second, the memory utilization is improved when the execution of one memory phase is overlapped with computation phases of other tasks. In general purpose computing, a large number of techniques, such as out-of-order execution and prefetching, are employed to harness such overlap at the level of one task or between different tasks (hardware multi-threading). That is, while waiting for main memory to return the requested data, the processor is busy executing other instructions. Although these techniques improve the average case performance, it is difficult to extract worst-case guarantees. In contrast, we focus this dissertation on techniques that are suitable for hard real-time systems with guaranteed bounds. Three

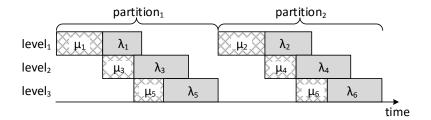

Figure 1.2: Dissertation theme and scope.

levels to overlap the memory phases can be distinguished: (1) between tasks on different cores, (2) between tasks on the same core and (3) within one task. We will focus in this dissertation on the first two and ignore the last one. The reason is that in order to exploit the overlap within one task, a compiler analysis is needed to insert prefetch commands in the code at the right places. In contrast, we capture the overlap between tasks from a higher level: the scheduler, without relying on compiler-level techniques.

As we mentioned earlier, the co-scheduling approach has the advantage to speedup the memory transfer time. Another advantage is that since one core is given the whole access to main memory during memory phase, this avoids the interleaving effect of other requests coming from other cores. This can benefit platforms with hardware arbitration policy that is unfair. For example, with a fair arbiter such as **round-robin (RR)**, the inflated memory time (due to contention) for one memory request can be bounded by multiplying the memory latency with m, the number of cores in the system, assuming each memory request is preceded by m-1 other requests in the worst case. However, with an unfair arbiter, the inflated memory time can exceed m. For example, **dynamic random access memory (DRAM)** controllers are designed to utilize the memory bandwidth; thus, they may favor some requests that are ready to be served over others using polices such as **first-ready first-come first-serve (FR-FCFS)**.

## **1.3** Dissertation Theme and Problem Statement

The main focus of this dissertation is scheduling real-time applications on multicore processors by taking memory time into account. These three aspects are depicted in Figure 1.2. In particular, *multiprocessor scheduling* means spatial and temporal assignment of tasks on multiprocessor, *real-time* introduces the notion of time and predictable execution, and *memory* considers the memory time.

The problem of this dissertation can be stated as follows. The classical multiprocessor real-time scheduling theory focuses on processor cores and ignores memory. However, the *contention* for access to main memory can significantly change the execution time of real-time tasks on multicore processors. A real-time task, like any other computer program, can be abstracted as a stream of memory and CPU instructions. Similar to CPU instructions, we argue that these memory instructions (memory requests) have to be scheduled to avoid the contention conflicts and enhance their execution by hiding their latency. To achieve these goals, the real-time tasks have to be split into two phases: memory and computation.

## Chapter 2

## **Background and Related Work**

This chapter provides the essential background material and reviews the related work. The multiprocessor system we consider in this dissertation is the **symmetric shared-memory multiprocessor (SMP)**. Here, all processors have equal access to one shared main memory and can exchange data through this shared memory. Shared memory design has gained wide acceptance due to its simplified programming and natural transition from uniprocessors. Furthermore, as Moore's prediction is expected to continue in the next few years, the trend in current technology is to put more processors on the same chip. These processors inside the same chip are called cores. Therefore, the term multiprocessor also includes multicore or **chip multiprocessor (CMP)**.

There are two topics that are directly related to the subject of this dissertation: memory contention and real-time scheduling. We recall that the goal of this dissertation is to solve memory contention problem through scheduling. Thus, we first overview the memory subsystem of SMP architectures. Then, we discuss the memory contention problem. Lastly, we overview the theory of multiprocessor real-time scheduling.

### 2.1 Memory Subsystem

A single high-performance processor can generate two data memory requests and fetch four instructions per clock cycle [70]. For example, Intel Core i7 with 3 GHz clock rate can generate 6 billion 64-bit data requests per second, in addition to fetching 12 billion 32-bit instructions per second; this is a total peak bandwidth of 96 GB/s. In contrast, the peak bandwidth of DDR3 memory is 17 GB/s (only 18 %). The situation in multiprocessor

Figure 2.1: The levels of memory hierarchy.

systems is even worse. In fact, the number of memory requests per second grows as the number of processors increases. Theoretically, four Intel Core i7 can generate a peak bandwidth of 384 GB/s which is far more than what current DRAM technology can supply.

In order to mitigate the huge performance gap between multiprocessor and main memory, different techniques are often used such as multilevel caches. While these techniques enhance the average-case performance, they introduce unpredictable behavior. It is more challenging to support real-time applications on systems with the presence of caches. In what follows, we discuss the hierarchy levels in a typical memory subsystem as shown in Figure 2.1. In particular, we will focus on the relevant issues that may influence the predictability of timing behavior. We note that the cache levels can be larger than two in some platforms but we restrict our discussion in this section to two levels: one private and one shared.

### 2.1.1 Cache Memory

Predicating cache-related delays is a typical component of WCET analysis [138]. Several well-developed cache analysis techniques have been proposed for single-core processors. These techniques analyze the interference due to intra-task and intra-core cache conflicts. The latter is known as **cache related preemption delay (CRPD)**. The CRPD focuses on cache reload overhead due to preemption while the intra-task analysis focuses on the cache conflicts within the same task assuming non-preemptive execution.

In existing multicore processors [73], the last-level cache is typically shared by multiple cores. This design has several merits such as increasing the cache utilization, reducing the complexity of cache coherency and facilitating a fast communication medium between cores. However, it is extremely difficult to accurately determine the cache miss rate because the cache content depends on the size, organization and replacement strategy of the cache in addition to the order of accesses. Shared caches in multicore processors are similar to caches in single core processors in that they all have inter/intra-task interference. In addition, when multiple cores share a cache, they can evict each other cache lines, resulting in a problem known as inter-core interference.

Unfortunately, single-core cache timing analysis techniques are not applicable for multicore with shared caches. Inter-core interference is caused by tasks that can run in parallel and this requires analyzing all system's tasks. The analysis of non-shared caches has been already considered as a complex process and extending it to shared caches is even harder. In fact, the researchers in the community of WCET analysis [131] seem to agree that "it will be extremely difficult, if not impossible, to develop analysis methods that can accurately capture the contention between multiple cores in a shared cache".

Despite this challenge, few works have been proposed to address the problem of shared caches. These techniques are applicable for simple architectures and statically scheduled tasks. The first work that studies the analysis of shared caches in multicore processors is proposed in [141]. This work assumes a system with two tasks simultaneously running on two cores with direct-mapped shared instruction cache. Later, cache conflict graphs were used to capture the potential inter-core conflicts [147]. The work in [85] improves upon [141] by exploiting the lifetime information of tasks and bypassing the disjoint tasks (tasks that cannot overlap at run-time) from the analysis. This work assumes a task model where all tasks are synchronized. Clearly, for systems with dynamic scheduling, it will be extremely difficult to identify the disjoint tasks. Other research [66] proposes to bypass the shared cache for single-usage cache lines to avoid inter-core conflicts and therefore improve the timing analysis. For systems where tasks are allowed to migrate between cores, **cache** related migration delay (CRMD) has been studied in [67]. This work estimates the number of cache lines that can be reused from the L2 shared cache when a task migrates from one core to another. Due to the lack of analysis techniques for multicore platforms with multiple tasks scheduled dynamically, an empirical study has been proposed in [23] to evaluate the impact of cache-related preemption and migration delays (CPMD). An interesting result is that delays related to preemption and migration do not differ significantly on a heavily loaded system.

Furthermore, cache memories in single core processors have three types of misses: compulsory, conflict and capacity. Beside these three types of misses, private caches in multicore processors introduce another type: coherency misses. They pose another challenge because shared variables, that may simultaneously exist in several caches, are automatically updated by the cache coherency hardware in a hidden way (without explicit instructions). If frequent shared memory accesses occur, the WCET can be largely affected [63]. In general, private caches introduce two problems in multicore processors [29] that could affect the execution of real-time tasks: (1) access serialization (atomic) to shared cache lines. When a core writes to a shared cache line, the write is not considered complete until all shared cache lines are invalidated. Similarly, before a core reads a dirty cache line written by another core, the cache line has to be written back to main memory and the source core has to change the cache line state into shared. (2) A large number of coherency messages are sent across the interconnection network to keep the shared data between multiple processors coherent. This could saturate the interconnection network and cause further delays that could reduce the parallel processing gain and more importantly the time predictability for real-time systems. Depending on the application, shared data is intrinsic and cannot be avoided. To the best of our knowledge, no existing static WCET analysis technique is able to account for the effects of coherency misses.

Another line of research has suggested to randomize the cache and employ a stochastic analysis to determine the cache miss rate [115]. In particular, **probabilistic timing analysis (PTA)** has been proposed as an alternative to conventional timing analysis that can be highly pessimistic for the worst-case [34]. PTA provides **probabilistic WCET (pWCET)** estimates that can be exceeded with a given probability. That is, a pWCET with an associated low probability, say  $10^{-15}$ , means that the probability for the execution time to exceed this pWCET is  $10^{-15}$ . However, PTA techniques require the execution times to have a probability of occurrence that is independent and identically distributed. These two features are essential to allow using random variables and apply statistical methods for analyzing the system. At the cache level, caches with LRU replacement policy cannot be used because the result of each memory access is dependent on the previous accesses. A fully-associative cache with random replacement is one example that can be used for PTA. Along this line of research, PTA has been applied to a single level cache [77], multilevel caches [78] and for CRPD [48]. Recently, PTA was used for shared caches to estimate the inter-core cache conflicts [130].

In contrast to timing analysis techniques where caches are used without restrictions, the approach of managed caches has the advantage to avoid complex analysis methods for estimating the cache behavior [62]. Indeed, the time predictable architecture in [106] proposes a statically-partitioned L2 cache to avoid the inter-core cache conflicts. In addition, managed caches can be used in situations where the static analysis cannot be used, for example, the case where the cache replacement policy is not documented. On the other hand, while managing the cache space provides a timing isolation between tasks, the reduced cache space may impact the task execution time [8]. The basic idea of managed caches is to give each task a portion of cache space so that no other task is allowed to have access. The cache memory can be seen as a two dimensional array in which the columns are the cache ways, and the rows are the cache sets. The shared cache can be partitioned in sets (rows), ways (columns) or individual cache lines.

Page coloring is a technique used to map virtual pages to physical pages (frames) by taking into account the cache structure. It can be employed to implement cache partitioning in software by re-arranging the physical addresses [135]. Cache locking is a mechanism that hooks some cache lines from being evicted until explicitly unlocked [94]. It has the advantage of controlling the partition at cache line granularity. Cache locking has two different schemes: either static or dynamic. With a static scheme, locked cache lines remain unchanged throughout execution, i.e., locked once. On the other hand, dynamic locking allows cache lines to be reloaded on the fly. The limitations of static locking manifest when an application has multiple hot regions and limited cache space. With dynamic locking, this limited cache space can be utilized multiple times.

These cache portions can be assigned to individual tasks or processors. Processor-based partitioning allows tasks to enjoy more cache space; in contrast, task-based partitioning avoids cache reloading at preemption. When combined with cache locking, many different schemes can be obtained. Suhendra and Mitra [131] explore these different schemes and evaluate their effects on the worst-case performance. They conclude that processor-based partitioning is better than task-based partitioning independent of the locking scheme.

As we stated above, there is no analysis method available to account for cache coherency delays. Thus, caches are not used for shared data in hard real-time systems [114]. Recently, the work in [113] proposes **on-demand cache coherent (ODC**<sup>2</sup>), a hardware approach that relies on software support to guarantee coherent accesses to data inside critical regions. Thus, ODC<sup>2</sup> allows applications to use caches for shared data.

### 2.1.2 Scratchpad memory

An alternative to cache memory is scratchpad memory (SPM). The advantages include reduced power consumption and predictable behavior [137]. The SPM is a special static RAM placed close to the processor (on-chip, similar to L1 cache). The address space of the SPM is mapped into a predefined memory address of the processor. Unlike cache memory, the SPM has to be explicitly managed. In other words, the memory blocks have to be moved in software from main memory and copied into the SPM before being used. Thus, SPM is highly predictable in the sense that it has one access latency compared to caches with two different latencies for cache hit and miss.

Figure 2.2: Multibank DRAM.

There has been a significant amount of work in literature that proposes solutions to dynamically manage the SPM for one task [50, 90, 13, 52, 134] by reusing the available space over task's execution. These works propose solutions for managing task's code and data including stack and heap. Since SPM is not transparent with respect to address translation, management schemes have to impose constraints on analyzable code; in particular, memory aliases must be statically resolved, since otherwise the management scheme risks loading the same data into two different positions in the SPM.

In this dissertation, the focus is co-scheduling memory and computation phases in which the memory phase is the time to load a task from main memory to local memory. We use the term *local memory* to include either cache memory or SPM. As we discuss above, the literature is rich of software and hardware techniques that can be employed to let cache memory behave like SPM without conflict misses.

### 2.1.3 Off-chip Memory

The off-chip memory is often made of cost-effective technology such as DRAM. It is a 3dimensional array of memory cells organized as banks, rows and columns as in Figure 2.2. DRAM accesses are controlled by a *memory controller* which can be seen as a mediator between processor cores or last-level cache on one side and the DRAM chip on the other side. It translates read/write memory requests into corresponding commands and schedules them while satisfying the timing constraints of a DRAM chip. Each memory bank has its own row buffer which acts as a cache for the DRAM. Before data can be transferred, the target row has to be opened (moved to the row buffer). A memory request that hits the row buffer is faster than a memory request that needs to close the current row buffer and open a new one. Thus, DRAM access latency is variable and depends on the previous accesses. It is a hardware component that holds a state information (like cache memory) which may affect the application timing behavior. In addition, an arbitration policy like FR-FCFS is often used to utilize DRAM bandwidth by favoring requests that are ready to be served over other requests. Furthermore, DRAM is divided into banks to increase efficiency by interleaving memory requests. In other words, while data is transferred for a bank, the other bank can be activated. In fact, this parallelism can be exploited to enhance the application execution performance. However, one has to trade-off between performance and predictability. If memory pages of one core are mapped into the same bank, an isolation between different cores can be achieved. On the other hand, an application can gain higher memory bandwidth when memory pages are interleaved between different banks.

Due to the dynamic nature of DRAM controllers, they are ill-suited for hard real-time systems. Thus, several designs of predictable memory controllers have been proposed as in [2, 61, 68]. These designs change the internals of memory controller such as the page policy and the command scheduler to produce tighter bounds. In this dissertation, we look at off-chip memory as a black-box with constant access latency similar to most of the related work we discuss in the next section. However, as we mention in Section 1.2, the memory phase of co-scheduling approach has the advantage to exploit the DRAM structure to greatly reduce the access latency without the involved complexity of other work to derive bounds on memory latency.

## 2.2 Memory Bus Contention

The memory bandwidth in multicore processors is shared and therefore subject to *contention*. At the hardware level, the memory requests are mediated by an *arbiter*. Based on the arbitration policy, the access latency of one request can be delayed by other requests. The research community has recognized memory contention as a significant challenge that may affect both performance and predictability. An experimental evaluation on the accuracy of some task scheduling algorithms is done in [128]. The results show that these scheduling algorithms show a very poor accuracy where the real execution time is most often multiple of the estimated one. The problem stems from the assumption that all processors are fully connected in a way that communications can proceed concurrently without contention and without the processor involvement in the communication. The same authors as in [128] suggest that the task model should be modified to include the

Figure 2.3: An arrival curve specifies the maximum number of memory requests that can be generated within a window of time  $\Delta t$ .

processor involvement in the communication and reflect the fact that the communication subsystem is not contention-free [129]. Furthermore, the work in [109] shows that the task execution time due to memory contention can increase linearly with number of processors.

The topic of memory bus contention has received a significant attention in recent years. [106] proposes RR arbitration for memory bus. In this case, the memory request of one task can be delayed by at most m - 1 other requests of other cores. Thus, the inflated memory time of one request can be bounded as  $m \times \sigma$  where  $\sigma$  is the memory latency of single request without interference. In [86], the authors propose a memory wheel where each task is given a window of time to access memory. We note that RR, unlike memory wheel, is work-conserving and there is no wasted time. Consider a memory with access latency of  $\sigma = 20$  cycles and a system with m = 4 cores. With memory wheel, a memory request can take  $19 + 4 \times 20 = 99$  cycles if this request arrives one clock cycle after the beginning of its wheel window. In contrast, with RR arbitration, the memory time of a request, regardless of its arrival time, is always bounded by  $4 \times 20 = 80$  cycles.

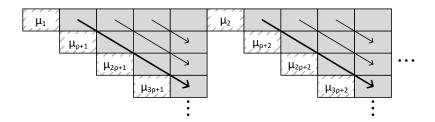

The work in [109] models each task as a set of super-blocks and derives an arrival curve for these super-blocks. Then, it introduces an analysis method to compute an upper bound on memory contention delay by assuming RR and **first-come first-serve (FCFS)** arbitration at the hardware level. The concept of arrival curves is also used in [125] to model the memory load of each processor. As shown in Figure 2.3, the arrival curve  $A(\Delta t)$  is a cumulative function that specifies the maximum number of memory requests that can arrive within a window of time. Thus, many conflicts are guaranteed to be eliminated with large request distances (time windows). A measurement-based method is proposed in [43] to capture the arrival pattern of memory requests. This work assumes a partitioned non-preemptive scheduling at the task-level and unspecified work-conserving arbitration at the hardware level.

Recently, a framework to analyze memory bus contention is proposed in [44]. The problem is split into two steps: hardware arbitration dependent and independent. In the first step, a bus availability model is derived using worst-case and best-case start times. In the second step, task request-profile is used to model the traffic generated by tasks. To tighten the traffic distribution, the task request-profile is split into equal-size temporal regions where each region is characterized by the maximum number of memory requests. Using task request-profile and bus availability model, an algorithm is proposed to compute the maximum memory bus contention. [44] idles processors if tasks execute for less than their WCET to ensure that the number of memory requests within a time window is not higher at run-time than the computed one at design time. In contrast, we allow tasks in our design to execute for less than their WCET; thus, the system can accommodate soft real-time tasks to utilize the over-provisioning of hard real-time tasks.

Another line of research uses TDMA arbitration [120, 126, 36]. In this case, the bus is divided into time slots and these slots are assigned to cores. Thus, each core is associated with slots with known start and finish times. This distribution of time slots to cores is called, *bus schedule*. Access to main memory is allowed for one core in its assigned slot. The memory or bus arbiter stores the bus schedule in a lookup table and grants access to cores accordingly. If a core requests memory at a time slot that belongs to another core, it will be delayed until its next slot. Clearly, this scheme determines exactly when a core will be granted the bus, thus, it allows analyzing the memory time for each core separately without the interference effect of other cores. Given a bus schedule, the WCET of one task can be determined using static WCET analysis. This requires the locations of memory requests in time to be known. In other words, there should be a guaranteed alignment between memory requests and bus schedule. A drawback of this approach is that the memory locations of a task can only be specified for a particular hardware architecture by using its micro-architectural model to account for the timing effects of underlying components such as the pipeline. A thorough discussion of this topic can be found in [37].

The work in [127] also uses TDMA to arbitrate for main memory. However, instead of knowing the exact locations of memory requests, the task is modeled as a sequence of super-blocks and each super-block is divided into three phases: acquisition phase, execution phase and replication phase. Access to main memory is limited to an acquisition phase at the beginning and a replication phase at the end. This work then proposes an analysis framework to compute the **worst case response time (WCRT)** of each task for a given TDMA schedule.

Other research considers priority based arbitration. The work in [3] proposes creditbased arbitration scheme. Similarly, the work in [103] proposes an arbitration scheme based on weighted fair queuing theory at the granularity of memory requests. However, these two schemes involve large overhead when implemented in hardware.

Yun *et al.* [146] propose a memory bandwidth reservation system called Memguard that works at the operating system level and can reserve memory bandwidth for a specific core. Furthermore, a **hardware performance counter (HPC)** is used to measure the resource usage and enforce it using a run-time monitor. The authors also use a resource reclaiming approach to dynamically adjust the bandwidth upon request to maximize memory bandwidth utilization. Memguard [146] is a software technique proposed to provide bandwidth partitioning without changing the bus arbiter at the hardware level. However, it relies on hardware arbiters to provide the fine-grained arbitration. Therefore, it can be seen as a coarse-grained bandwidth partitioning for a group of memory requests originated from one core. A similar hardware-implemented approach is proposed in [54]. Memguard for partitioned multicore processor has been analyzed in [142]. This work considers sequential tasks and assumes the resource budget for each core is given. The main focus is to compute the response time of real-time tasks on regulated cores.

The work in [104] proposes an analysis method to compute an inflated WCET due to the contention for access to main memory. This approach requires the knowledge of memory demand for each task in a quantified value such as the total number of accesses. However, this analysis is only applicable for time-triggered execution in which cores are synchronized and tasks periodically repeat an off-line schedule. Most of previous discussed works have a similar assumption about the execution pattern of tasks. It is not clear, however, how these approaches can leverage the massive progress in multiprocessor scheduling theory. In what follows, we discuss an emerging technique that explicitly treats memory as a resource similar to processor cores. Thus, memory can be scheduled using the same algorithms proposed for processor cores.

### 2.2.1 The Co-Scheduling Approach

The work in [108] proposes a co-scheduling approach that can avoid memory contention from a software level. In this approach, each task is split into two phases called memory and computation. During the memory phase, the task's code and data is loaded from main memory to the local memory of processor core, and during the computation phase, the task executes out of the local memory without access to main memory. The co-scheduling approach exactly aligns with the **software managed multicore (SMM)** architectures. SMMs are promising alternatives for real-time systems due to their scalability, power efficiency and predictability [76]. In SMM, each core can only access an SPM while main memory accesses are explicitly done through the use of DMA. Good examples for SMM architecture are Cell processor [92] and FlexPRET [149]. In contrast, traditional multicore platforms with coherent caches are very hard to adopt for real-time systems because they make the analysis very difficult and often result in pessimistic bounds.

While [108] is introduced to avoid contention between single core and I/O devices, the work in [143] uses this model for multicore with partitioned scheduling. A TDMA arbitration is applied to avoid the contention between cores for access to main memory. To utilize memory slots, the priority levels of memory phases are increased over computation phases during the allotted time. In this case, the separation of memory and computation phases has the advantage to control memory phases and allow them to preempt computation phases. A simulation-based evaluation for partitioned scheduling is conducted in [15] using different scheduling policies.

In [99], the authors focus on the theoretical aspect of this model and identify the critical instant (the worst-case activation pattern that leads to WCRT of task under analysis) assuming fully preemptive scheduling of both memory and computation phases on single core. By knowing the critical instant, an exact response time analysis is derived. While we adopt this deterministic model to avoid memory contention, the main motivation in [99] is to exploit the burst-feature of some DMA engines to speedup the memory transfer time. Recently, [144] applies the co-scheduling approach to avoid memory contention in multicore processor. In this work, a global preemptive scheduling is considered in which each task is assumed to have a dedicated partition in each local memory to avoid re-loading the task content after each preemption point. In addition, the memory phases are designed to have priorities higher than the computation phases. This latter point is designed to ensure that memory phases are not interfered from computation phases.

The explicit nature of the co-scheduling approach has been utilized indirectly by other work. For example, tasks migrate between cores in global scheduling and this causes CRMD. A technique has been proposed to warm up the cache before the task execute on the new processor [124]. The transfer of cache lines is initiated explicitly by the scheduler from the source core to the target core. It is contrasted with the traditional pull mechanism where the target cache has to implicitly pull the data from the source cache or the shared cache. Another example is the work in [94] which proposes a framework to manage the cache using cache locking, a technique used to make caches behave like scratchpads [112]. An important step in this framework requires knowing the memory footprint of the task to do prefetching and then locking.

### 2.2.2 Limitations Imposed by the Co-Scheduling Approach

A real implementation of the co-scheduling approach has been demonstrated on many available **commercial off-the-shelf (COTS)** platforms. In particular, our recent work [119] ports the full automotive suite of EEMBC benchmarks <sup>1</sup> to execute according to the coscheduling approach on MPC5777M, a quad-core **micro-controller unit (MCU)** from Freescale <sup>2</sup>. This MCU includes four cores: two E200Z710 application cores operating at 300 MHz, one E200Z425 I/O core and one additional core for delayed lockstep operation. Each core features private SPM for instruction and data of sizes 16 KB and 64 KB, respectively, and all cores share a single SRAM of size 404 KB. Since tasks have to be loaded into the local memory before execution, Erika OS <sup>3</sup> has been modified to load the task's code and data sections from SRAM into SPM. Similarly, the work in [53] ports a simplified version of a flight management system to execute on TMS320C6678, a COTS architecture from Texas Instruments <sup>4</sup>. In addition, the work in [30] explores the applicability of the co-scheduling approach on an embedded multicore heterogeneous platform <sup>5</sup>. This platform has a 4-core host processor and a cluster of eight **digital signal processing (DSP)** cores serving as an accelerator.

Even though the co-scheduling approach has been implemented on several fully COTS platforms, we discuss in this section some limitations that may arise in different settings. In particular, the discussion is split into four limitations, and we discuss how each one can be addressed.

(1) Local memory size: since code and data of each task must be explicitly loaded into a local memory before being executed, tasks must fit inside the local memory of one core. We note that there are existing COTS platforms with relatively large local memories that can fit many existing real-time applications. For example, Cell Processor has 256KB SPM for each core. To put things into prospective, FreeRTOS which is a popular OS in the real-time systems domain, has around 8-10KB memory footprint (based on the underlying hardware and the compiler used). Also, the work in [136] has transformed many applications from EEMBC benchmarks to execute according to the co-scheduling approach with a relatively small size of SPM (16KB). In fact, a large number of real-life embedded applications including those for control have a small memory requirement [56, 132]. If, however, the code and data of one task cannot fit in the available local memory space, we

<sup>&</sup>lt;sup>1</sup>http://www.eembc.org/

$<sup>^2\</sup>mathrm{Acquired}$  by NXP Semiconductors in December 2015

<sup>&</sup>lt;sup>3</sup>http://erika.tuxfamily.org/drupal/

<sup>&</sup>lt;sup>4</sup>http://www.ti.com/product/TMS320C6678

<sup>&</sup>lt;sup>5</sup>http://www.ti.com/product/66AK2H12

can split the task into multiple segments such that each segment can fit inside the available local memory as discussed in Section 3.7.

(2) Determining the working set: the co-scheduling approach relies on obtaining the set of memory blocks that is needed by each task for load and unload phases. The task memory footprint can be represented as a set of memory blocks, including both code and data, where each block could be a cache line or memory page. In general, the memory blocks can be determined by means of either compiler-driven approaches [134, 98], using program annotations [108] or using measurement-based methods [94]. In particular, the authors in [94] propose a measurement-based method that can be used to determine the memory blocks of load and unload phases at the level of virtual memory pages. They basically profile the task and convert the absolute addresses of memory accesses to relative values with respect to the execution-independent memory regions. Hence, load and unload code can be written based on these relative addresses.

We acknowledge that the working set for some tasks can be very hard to perfectly determine before run-time. In this case, the co-scheduling approach can be partially applied, say for 80-90% of memory accesses and the remaining 10-20% can be analyzed assuming contention for access to main memory. In particular, the recent work in [95] introduces an automated profiling tool that can modify arbitrarily C programs to behave according to the co-scheduling approach by inserting prefetch statements before the function under analysis. The results show that both overhead and missed accesses are small for a number of non-trivial real-time benchmarks. For example, 95% of cache misses are reduced for a JPEG image encoding benchmark. In addition, the work in [35] proposes MadT, a tool that detects data memory accesses of general purpose applications. It translates the virtual addresses to their symbolic variable names, a relevant feature that can be used to implement load and unload phases. In addition, the results in [108] based on the automotive program group of MiBench and DES benchmarks indicate that the amount of loaded data is only slightly higher than the amount actually used.

(3) Handling I/O data: since tasks can load data from main memory before they execute, this data can also be memory mapped I/O. However, I/O that reads or writes to main memory directly using DMA has to be controlled to avoid the interference with application cores. The work in [14] shows how this can be done through hardware modifications. Alternatively, some COTS platforms, like MPC5777M, have a dedicated bus to handle I/O transactions. In this case, traffic traversing the dedicated I/O bus has to be processed by an I/O core and buffered before reaching the application cores, similar to our implementation in [119].

(4) Cache related issues: local memory can be either cache or SPM. For caches, it

is particularly important to facilitate load and unload phases. In particular, the platform API should provide cache prefetching primitives, e.g., P4080 platform [58] has a stashing mechanism that allows a DMA component to put data directly into the cache; otherwise, LOAD instructions can be used to move data from main memory. In addition, the cache should employ a write-back policy and have primitives to invalidate some cache lines and write them back to main memory. For example, Intel platforms provide CLFLUSH instruction [71].

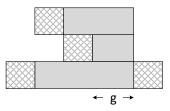

Furthermore, during load phase, self-eviction should be avoided, in the sense that loading a cache line should not evict another cache line loaded within the same phase. To illustrate how memory blocks can be allocated without conflicts, we can think of cache memory as a two dimensional array in which the columns are the cache ways and the rows are the cache sets. In systems with virtual memory, the memory blocks can be allocated without conflict along cache ways by re-arranging the physical addresses (page coloring). However, in caches with non-deterministic replacement policy, only one cache way can be utilized. Fortunately, some cache controllers have a *lockdown* feature that can be implemented at the granularity of either a single line or way. This feature allows memory blocks to be hooked on a particular cache way without being overwritten until they are explicitly unlocked. In fact, the *Colored Lockdown* technique proposed in [94] can be used to avoid conflicts in loading task's code or data. The key idea of this technology is to combine coloring and cache locking to deterministically control cache allocation of memory blocks. With this combined method, the whole cache can be utilized to allocate memory blocks without conflicts. Similarly, the work in [38] proposes column caching, a hardware modification to the replacement unit of the cache in order to limit replacement to the column (way) specified by a bit-vector stored in page table entries.

The multicore processor can also have a **last-level cache (LLC)** that is shared between cores as common in today's architectures [73]. Spatial isolation techniques as discussed in Chapter 2 can be used to partition the shared cache among different cores. Here, we assume there is no timing interference between cores for access to shared cache. This can be achieved using *bankization* [106], a technique to partition the cache into banks and each core is assigned a private set of banks.

### 2.2.3 Memory Space Allocation

The memory used by real-time applications is usually statically allocated to avoid nondeterministic memory management systems. This used to be a sufficient solution for some real-time applications; however, modern real-time systems are increasingly becoming complex and demanding for more flexible memory allocation. In fact, building a timepredictable memory manager is a challenging task. The problem is that the memory state changes as data come and leave. Thus, memory allocation time is not always fixed. Halffit [105] was the first dynamic memory manager that allocates memory space in a constant time, but the cost can be wasting half of the memory space. Another work [41] proposes a scheme called **compact-fit (CF)**. It provides a bounded response time (either constant or linear to the size of allocated data) for allocating data regardless of the current state of the memory. Since our main focus is the arbitration time for access to main memory (the temporal aspect), the timing interference due to memory space management is out of this dissertation's scope.

## 2.3 Multiprocessor Real-time Scheduling

Uniprocessor real-time scheduling has received a significant amount of consideration in the past [31]. The computational model has been extended from a simple theoretical model to include more realistic models found in today's systems. On the other hand, multiprocessor real-time scheduling has not received the same amount of consideration as in uniprocessor. The theory of multiprocessor real-time scheduling studies the scheduling of real-time workloads on multiprocessor systems. This topic has seen big advances over the past years and is still growing in a fast pace. We will discuss in this section the most closely related aspects, and refer the reader to a recent book on this topic by Baruah *et al.* [20]. In multiprocessor real-time scheduling, one has to distinguish two scheduling paradigms: (1) sequential tasks and (2) parallel tasks. The real-time research community until recently has focused on the first paradigm in which the real-time system is modeled as being composed of a finite number of sequential tasks. The work in [46] surveyed the literature of different techniques for scheduling sequential tasks on multiprocessor systems. Although scheduling parallel tasks without deadlines has been addressed by parallel-computing researchers for a long time [1], there has been a recent attention to schedule parallel tasks in real-time systems. This has been observed in [122], "the growing importance of parallel task models for real-time applications poses new challenges to real-time scheduling theory that has mostly focused on sequential task models." Modeling modern real-time systems as being composed of parallel applications is crucial because the timing constraints of computationheavy real-time applications such as synthetic vision and object tracking [79] cannot be feasibly executed on single core processor. We will provide a brief survey of these works in Section 2.3.5.

Figure 2.4: A job needs to execute for amount of time equal to its WCET between its release time and deadline.

### 2.3.1 Task Model

The real-time workload comprises units of work known as *jobs*. These jobs are generated by a finite collection of independent recurrent tasks  $\Gamma = \{T_1, \dots, T_n\}$ . Each job is characterized by three values: release time  $r_i$ , absolute deadline  $d_i$  and WCET as depicted in Figure 2.4. Over the years, different models have been proposed for hard real-time tasks. One widely-used model is the 3-parameter model. As the name indicates, each task is characterized by WCET  $e_i$ , period  $p_i$  and relative deadline  $D_i$ . This model extends the classical **Liu and Layland (LL)** model [87] which has only two parameters: WCET and period. Adding relative deadline as a third parameter allows to model tasks that occur infrequently (large period) but with urgent deadline (small deadline). Based on the relationship between the relative deadline and the period, a 3-parameter task system may be classified as follows.

- An implicit-deadline where the relative deadline is equal to the period. This is exactly the same as LL model.

- A constrained-deadline where the relative deadline is no larger than the period.

- An arbitrary-deadline where there is no restriction on the values of the relative deadline and the period.

In addition, a *sporadic* task model specifies a lower bound on the arrival of successive jobs of one task. In contrast, a *periodic* task model specifies an exact separation of successive jobs.

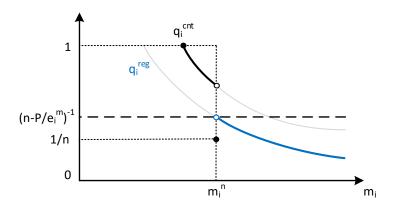

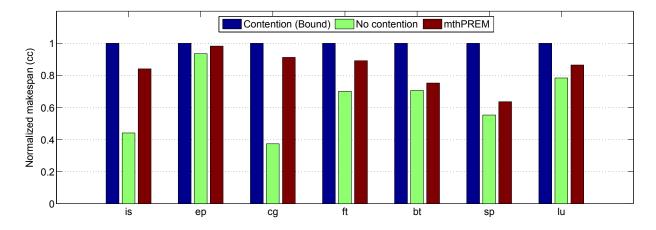

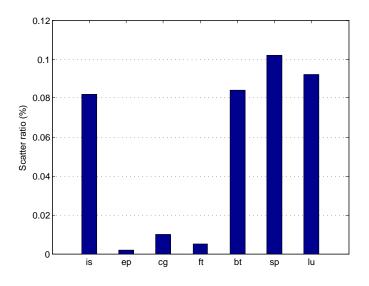

Figure 2.5: DAG task.