# An Energy-Efficient System with Timing-Reliable Error-Detection Sequentials

by

Yaoqiang Li

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2016

© Yaoqiang Li 2016

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

A new type of energy-efficient digital system that integrate Error Detection Sequential (EDS) and Dynamic Voltage Scaling (DVS) circuits has been developed [1, 2, 3, 4]. In these systems, EDS-monitored paths convert the Process, Voltage and Temperature (PVT) variations into timing variations. Nevertheless, the conversion can suffer from the reliability issue (extrinsic EDS-reliability). EDS circuits detect the unfavorable timing variations (so called "error") and guide DVS circuits to adjust the operating voltage to a proper lower level to save the energy. However, the error detection is generally susceptible to the metastability problem (intrinsic EDS-reliability) due to the synchronizer in EDS circuits. The Mean Time Between Failure (MTBF) due to metastability is exponentially related to the synchronizer delay.

This dissertation proposes a new EDS circuit deployment strategy to enhance the extrinsic EDS-reliability. This strategy requires neither buffer insertion nor an extra clock and is applicable for Field-Programmable Gate Array (FPGA) implementations. An FPGAbased Discrete Cosine Transform with EDS and DVS circuits deployed in this fashion demonstrates up to 16.5% energy savings over a conventional design at equivalent frequency setting and image quality, with a 0.8% logic element and 3.5% maximum frequency penalties.

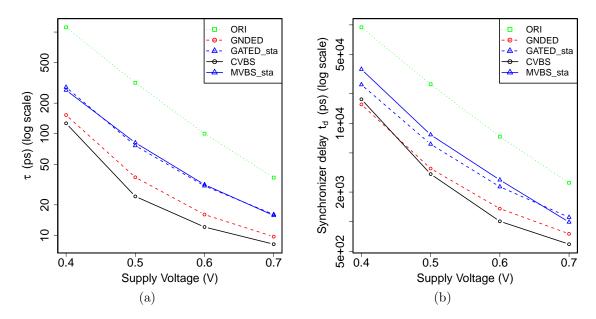

Voltage-Boosted Synchronizers (VBSs) are proposed to improve the synchronizer delay under single low-voltage supply environments. A VBS consists of a Jamb latch and a switched-capacitor-based charge pump that provides a voltage boost to the Jamb Latch to speed up the metastability resolution. The charge pump can be either Clock-driven Voltage-Boosted Synchronizer (CVBS) or Metastability-driven Voltage-Boosted Synchronizer (MVBS). A new methodology for extracting the metastability parameters of synchronizers under changing biasing currents is proposed. For a 1-year MTBF specification, MVBS and CVBS show 2.0 to 2.7 and 5.1 to 9.8 times the delay improvement over the basic Jamb latch, respectively, without large power consumption. Optimization techniques including transistor sizing, Forward Body Biasing (FBB) and dynamic implementation are further applied. For a common MTBF specification at typical PVT conditions, the optimized MVBS and CVBS show 2.97 to 7.57 and 4.14 to 8.13 times the delay improvement over the basic Jamb latch, respectively. In post-Layout simulations, MVBS and CVBS are 1.84 and 2.63 times faster than the basic Jamb latch, respectively.

#### Acknowledgements

I am extremely grateful to Professor Sachdev, my Ph.D advisor, for his support and guidance throughout this work. I would also like to thank Professor Aagaard, Professor Bishop and Professor Trefler for being on the Ph.D committee. Special thanks go to Professor Fei Yuan from the Ryerson University as the external examiner. Thank you for all your valuable feedbacks and suggestions.

I would also like to thank Professor David Nairn, Professor Siddharth Garg and Professor Adam Neale for their helpful support.

I would also like specially thank Pierce Chuang for being the best collaborator and friend during the academic project. I would also like to thank Qing Li for helping me solving layout issues and everyone else in the CMOS Design and Reliability Group at the University of Waterloo for their support.

I would like to acknowledge the financial support from the China Scholarship Council (CSC).

Finally, I would like to thank my family for their support and encouragement during my Ph.D study.

### Dedication

To my beloved wife, son and mom.

# **Table of Contents**

| A  | utho  | rs Declaration  | ii   |

|----|-------|-----------------|------|

| A  | bstra | nct             | iii  |

| A  | cknov | wledgements     | v    |

| D  | edica | tion            | vi   |

| Li | st of | Figures         | x    |

| Li | st of | Tables          | xiii |

| Li | st of | Abbreviations   | xiv  |

| 1  | Intr  | roduction       | 1    |

|    | 1.1   | Introduction    | 1    |

|    | 1.2   | Motivation      | 2    |

|    | 1.3   | Thesis Overview | 3    |

| 2 | Ene | ergy-Ef | ficient Digital Design with EDS circuits                   | 4  |

|---|-----|---------|------------------------------------------------------------|----|

|   | 2.1 | Introd  | luction                                                    | 4  |

|   | 2.2 | Digita  | l Circuits and Variability                                 | 5  |

|   |     | 2.2.1   | Conventional Synchronous Design                            | 5  |

|   |     | 2.2.2   | Circuit Scaling and Variability                            | 5  |

|   | 2.3 | Energ   | y-Efficient Digital Systems with EDS Circuits              | 7  |

|   |     | 2.3.1   | State-of-Art Approaches to Deal With Data-path Variability | 7  |

|   |     | 2.3.2   | Variability and EDS circuits                               | 8  |

|   |     | 2.3.3   | EDS Circuits Timing                                        | 9  |

|   |     | 2.3.4   | EDS-Triggered System Responses                             | 10 |

|   | 2.4 | EDS A   | Applications                                               | 10 |

|   |     | 2.4.1   | Microprocessors with EDS                                   | 10 |

|   |     | 2.4.2   | digital signal processing (DSP) Circuits with EDS          | 12 |

|   | 2.5 | Synch   | ronizer and Metastability Considerations for EDS Circuits  | 14 |

|   |     | 2.5.1   | Synchronization Parameters                                 | 15 |

|   |     | 2.5.2   | Figure-of-Merit of Synchronizer Design                     | 18 |

|   |     | 2.5.3   | Synchronizer Design Fundamentals                           | 20 |

|   |     | 2.5.4   | Synchronizer Validation                                    | 22 |

|   |     | 2.5.5   | Existing Synchronizer Design                               | 24 |

|   | 2.6 | Conclu  | usion                                                      | 27 |

| 3 | Des | ign foi | an Energy-Efficient System with EDS Circuits               | 28 |

|   | 3.1 | Introd  | luction                                                    | 28 |

|   | 3.2 | Propo   | sed Circuit Design                                         | 28 |

|    |       | 3.2.1   | Proposed EDS Design and Deployment                | 29 |

|----|-------|---------|---------------------------------------------------|----|

|    |       | 3.2.2   | DVS Algorithm Design and Implementation           | 32 |

|    |       | 3.2.3   | Reliability Analysis                              | 33 |

|    |       | 3.2.4   | Design Methodology and Parameter Tuning           | 35 |

|    | 3.3   | Exper   | imental Results                                   | 36 |

|    | 3.4   | Conclu  | usion                                             | 43 |

| 4  | Des   | ign for | Metastable-Hardened Voltage-Boosted Synchronizers | 46 |

|    | 4.1   | Voltag  | ge-Boosted Synchronizer Design                    | 46 |

|    |       | 4.1.1   | Consistency between Jamb Latch and Charge Pump    | 47 |

|    |       | 4.1.2   | The Working Mechanism of Charge Pump              | 49 |

|    |       | 4.1.3   | Metastability Parameters Calculation              | 52 |

|    |       | 4.1.4   | Simulation Results                                | 53 |

|    | 4.2   | Impro   | ved Voltage-Boosted Synchronizers                 | 58 |

|    |       | 4.2.1   | Synchronizer Improvements                         | 58 |

|    |       | 4.2.2   | Schematic Simulation Results                      | 64 |

|    |       | 4.2.3   | Layout Implementation and Simulations             | 67 |

|    | 4.3   | Conclu  | usions                                            | 67 |

| 5  | Cor   | nclusio | n and Future Work                                 | 71 |

|    | 5.1   | Conclu  | usions                                            | 71 |

|    | 5.2   | Future  | e Work                                            | 72 |

| P۱ | ublic | ations  |                                                   | 74 |

| R  | efere | nces    |                                                   | 75 |

# List of Figures

| 2.1 | Conventional Design.                                                                                                                                 | 5  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | (a) The trend of Complementary Metal-Oxide-Semiconductor (CMOS) technologies; (b) a demonstration of path delay variations (from [6]).               | 7  |

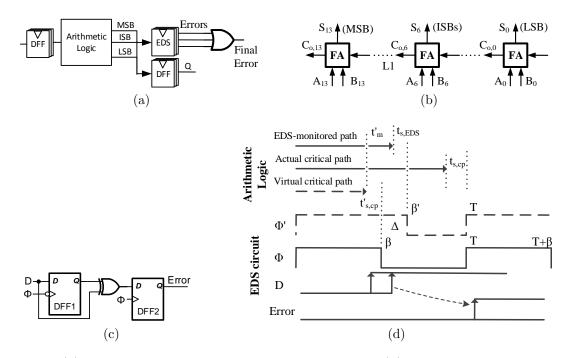

| 2.3 | <ul><li>(a) EDS abstraction (b) An EDS circuit: Double Sampling with Time Borrowing (c) EDS brief timing. (d) EDS circuit deployment.</li></ul>      | 9  |

| 2.4 | EDS detailed timing: (a) timing region division; (b) normal, (c) erroneous, (d) metastable timing.                                                   | 11 |

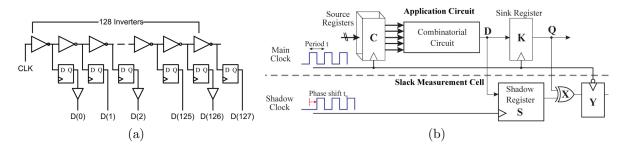

| 2.5 | (a) Logic Delay Measurement Circuit (LDMC) (from [25]); (b) Slack measurement (from [24]).                                                           | 14 |

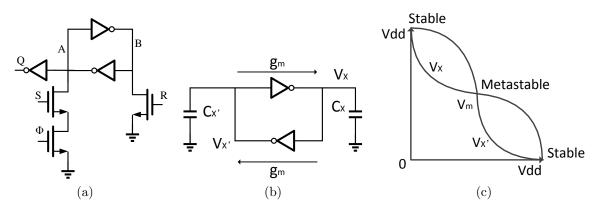

| 2.6 | A synchronizer (a) The Original Jamb Latch (ORI) schematic (b) Cross-<br>Coupled Inverters (CCIs) (c) voltage transfer curve.                        | 15 |

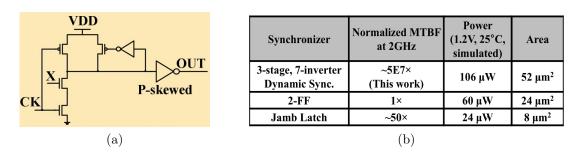

| 2.7 | The dynamic synchronizer (screen-shots from [7]) (a)schematic; (b) valida-<br>tion results.                                                          | 25 |

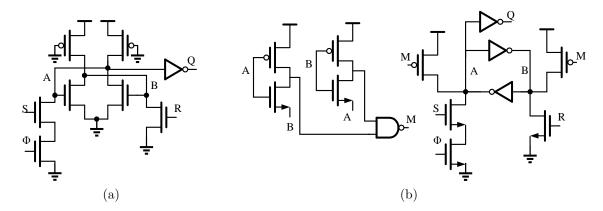

| 2.8 | The power-hungry synchronizers: (a) Grounded Jamb Latch (GNDED); (b) Gated Jamb Latch (GATED).                                                       | 26 |

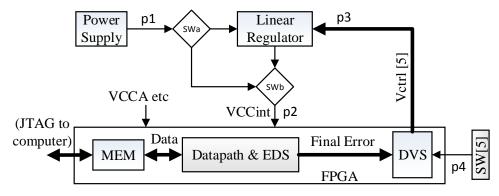

| 3.1 | Block diagram of the proposed FPGA-based design.                                                                                                     | 29 |

| 3.2 | (a)DSP Datapaths deployed with EDS circuits, (b) an arithmetic logic ex-<br>ample (ripple-carry adder); (c) EDS circuitry implementation; (d) timing |    |

|     | analysis.                                                                                                                                            | 31 |

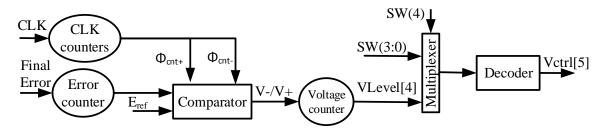

| 3.3  | The proposed DVS circuit implementation                                                                                                                                                                                                                                                        | 34      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

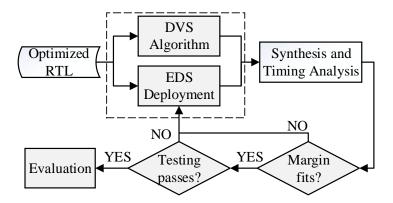

| 3.4  | Design methodology for integrating EDS circuits and DVS systems into a standard FPGA design flow.                                                                                                                                                                                              | 36      |

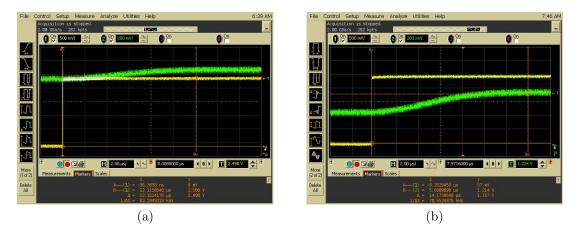

| 3.5  | $T_{regulator}$ measurement: (a) from 1.10V to 1.20V ( $\delta = 12 \mu s$ ); (b) from 0.95V to 1.20V ( $\delta = 14 \mu s$ )                                                                                                                                                                  | 38      |

| 3.6  | Timing Reports for : (a) Critical paths; (b) EDS-monitored paths                                                                                                                                                                                                                               | 39      |

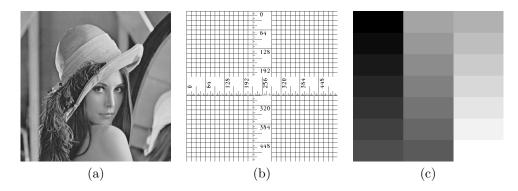

| 3.7  | Images: (a) Lena, (b) Ruler and (c) Gray represent the input data with normal, fairly-low and extremely-low entropy, respectively.                                                                                                                                                             | 4       |

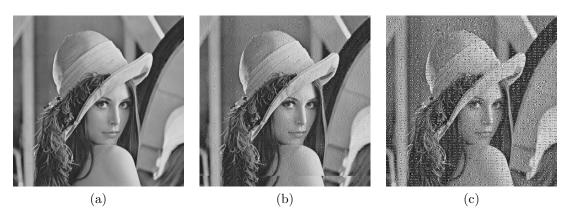

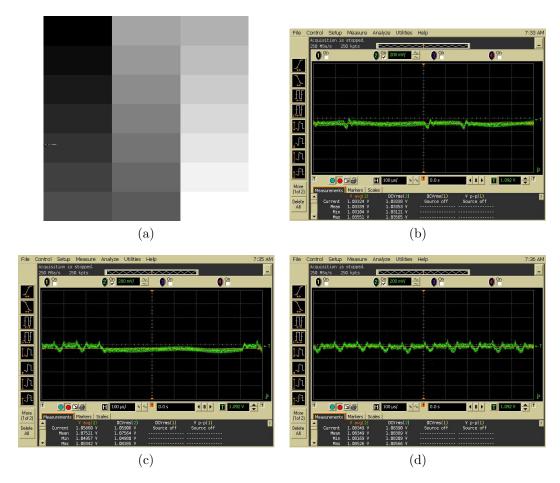

| 3.8  | Lena at Peak-Signal-Noise-Ratio (PSNR) : (a) $40.7 \mathrm{dB}$ ; (b) $21.1 \mathrm{dB}$ ; (c) $6.6 \mathrm{dB}$ .                                                                                                                                                                             | 4       |

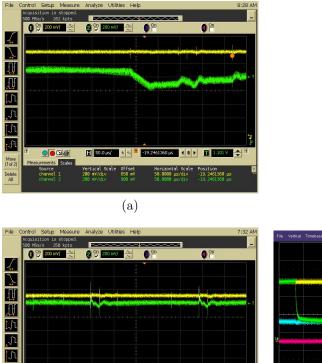

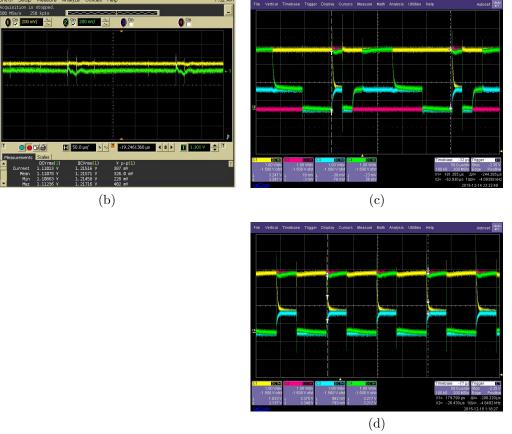

| 3.9  | Oscilloscope Waveforms: the Linear Regulator (LR) output supply voltage<br>for (a) the initialization of DVS for Lena and (b) the normal status of DVS<br>for Lena; the LR control signals for (c) Lena and (d) Ruler                                                                          | 44      |

| 3.10 | Evaluations for Gray: (a)the processed Gray with some scratches with the PSNR of 43.0 dB and three patterns of supply voltage when processing Gray : (b) $V_{DVS} = 1.033$ V which is a Voltage Over-Scaling (VOS) and causes the scratches; (c) $V_{DVS} = 1.075$ V; (d) $V_{DVS} = 1.083$ V. | 4       |

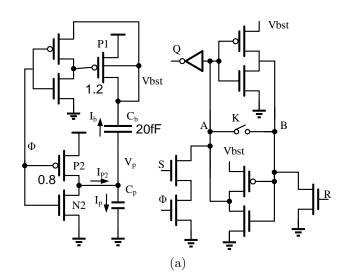

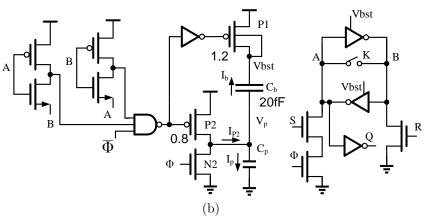

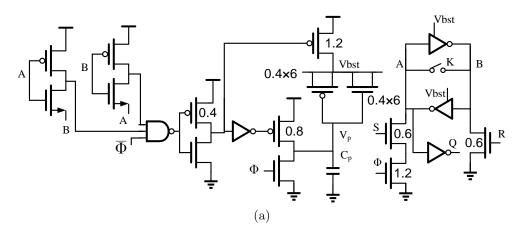

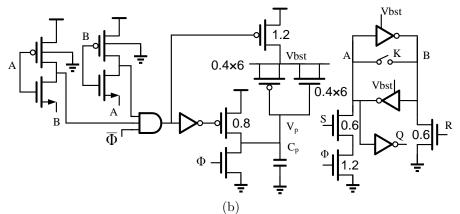

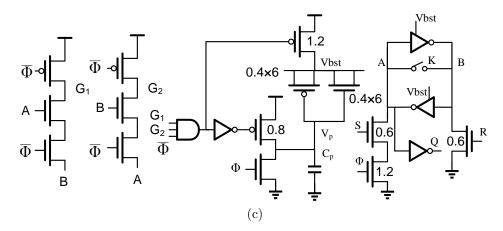

| 4.1  | VBSs: (a) CVBS, (b) MVBS.                                                                                                                                                                                                                                                                      | 48      |

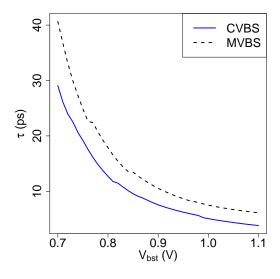

| 4.2  | $\tau$ for VBSs at $V_{dd} = 0.7 \mathrm{V}.$                                                                                                                                                                                                                                                  | $5^{2}$ |

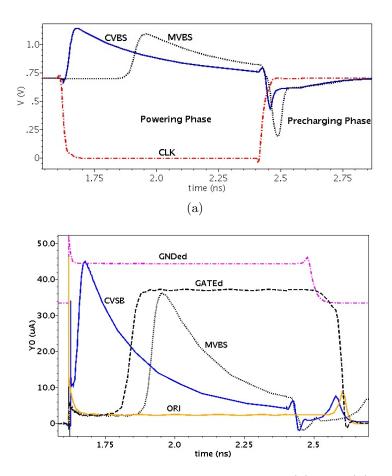

| 4.3  | Voltage-boosting simulations at $V_{dd} = 0.7 \text{ V}$ : (a) $V_{bst}$ ; (b) biasing currents.                                                                                                                                                                                               | 5       |

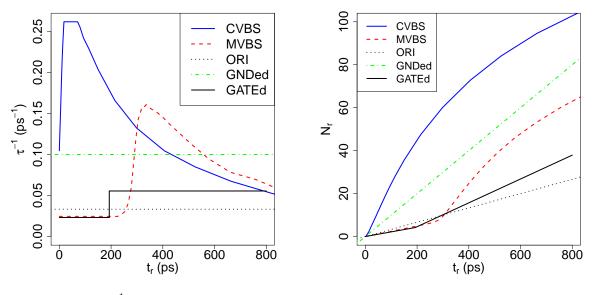

| 4.4  | $\tau^{-1}$ vs $t_r$ at $V_{dd} = 0.7$ V                                                                                                                                                                                                                                                       | 5       |

| 4.5  | $N_r$ vs. $t_r$ at $V_{dd} = 0.7$ V                                                                                                                                                                                                                                                            | 5       |

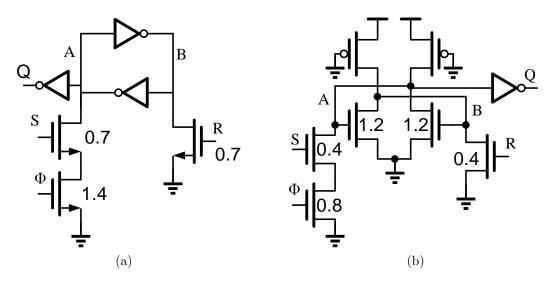

| 4.6  | Improved Synchronizers (sizing in µm): (a)ORI; (b) GNDED                                                                                                                                                                                                                                       | 5       |

| 4.7  | Improved Synchronizers (sizing in µm): (a)GATED_sta; (b) GATED_fbb;<br>(c) GATED_dyn.                                                                                                                                                                                                          | 59      |

| 4.8  | Improved Synchronizer CVBS (sizing in µm).                                                                                                                                                                                                                                              | 60 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9  | Improved Synchronizers (sizing in µm): (a) MVBS_sta; (b) MVBS_fbb; (c) MVBS_dyn.                                                                                                                                                                                                        | 61 |

|      | WVD5_uyii                                                                                                                                                                                                                                                                               | 01 |

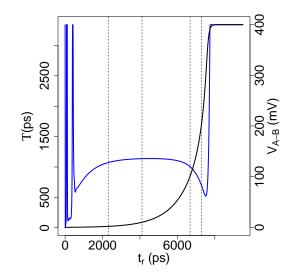

| 4.10 | The curves of $V_{A-B}$ (the black one) and $T(t_r)$ (the blue one)                                                                                                                                                                                                                     | 63 |

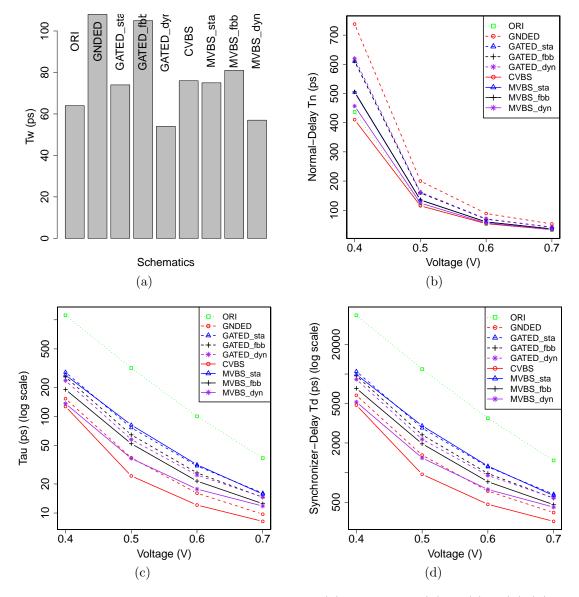

| 4.11 | Synchronizer timing parameters: (a) $t_w$ at 0.4V; (b) $t_n$ ; (c) $\tau$ ( $\bar{\tau}$ );(d) $t_d$                                                                                                                                                                                    | 65 |

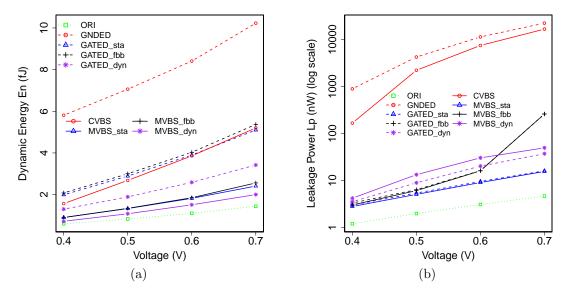

| 4.12 | (a)Dynamic energy; (b)Leakage power                                                                                                                                                                                                                                                     | 66 |

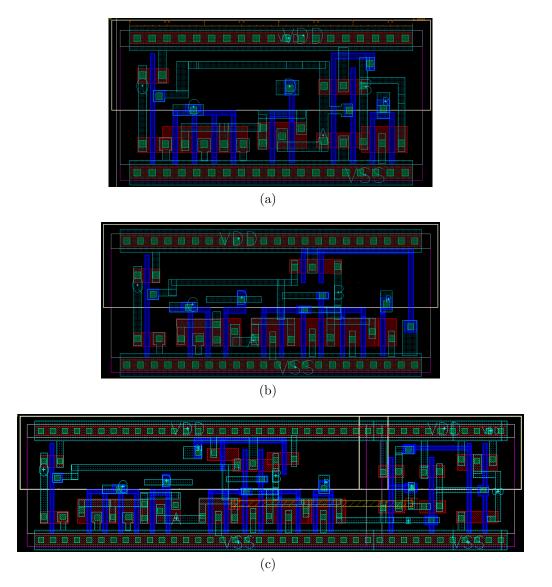

| 4.13 | Layouts and Area of synchronizers (all widths $W = 1.8 \mu\text{m}$ in standard cells): (a)ORI(Length $L = 3.8 \mu\text{m}$ and area $A = 6.84 \mu\text{m}^2$ ); (b) GNDED $L = 4.4 \mu\text{m}, A = 7.92 \mu\text{m}^2$ ; (c) GATED ( $L = 7.8 \mu\text{m}, A = 14.04 \mu\text{m}^2$ ) | 69 |

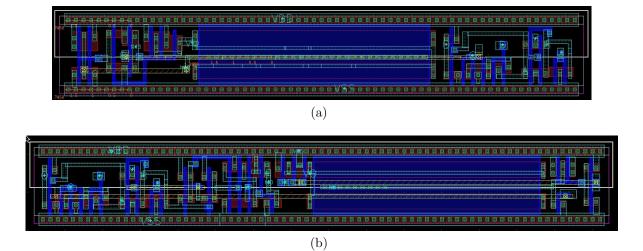

| 4.14 | Synchronizer Layouts (all widths $W = 1.8 \mu\text{m}$ in standard cells): (a) CVBS $(L = 13.4 \mu\text{m}, A = 24.12 \mu\text{m}^2)$ ; (b)MVBS $(L = 15 \mu\text{m}, A = 27 \mu\text{m}^2)$                                                                                            | 70 |

| 4.15 | Post-Layout Simulation Results: (a) $\tau$ ; (b) $t_d$                                                                                                                                                                                                                                  | 70 |

|      |                                                                                                                                                                                                                                                                                         |    |

# List of Tables

| 2.1 | Definitions of timing parameters.                                                                                                                                                                                                                                                     | 17 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Voltage Level Division for the voltage regulator. "VLevel" stands for the 4-bit voltage counter. "Vctrl" stands for the 5 tri-state control signals ( $Vo_2$ , $Vo_1, Vo_0, MARGSEL, MARGTOL$ ) of the voltage regulator. "Voltage" is the output voltage calculated according to [5] | 37 |

| 3.2 | Compilation Results (Combinational functions and logic registers are inside Logic Elements (LE)).                                                                                                                                                                                     | 40 |

| 3.3 | PSNR vs. Operating Voltage around $V_{safe}$ at the Power Supply (PS) configuration.                                                                                                                                                                                                  | 41 |

| 3.4 | Evaluations Results for Lena and Ruler.                                                                                                                                                                                                                                               | 43 |

| 4.1 | The Performance of the GATED                                                                                                                                                                                                                                                          | 54 |

| 4.2 | The Energy Consumption and Performance of the Baseline and Proposed<br>Synchronizers with a given $N_r = 35$                                                                                                                                                                          | 57 |

| 4.3 | Improvement Ratio of $t_d$ over the basic Jamb latch                                                                                                                                                                                                                                  | 64 |

| 4.4 | The Fullness of Charge Pump (in %)                                                                                                                                                                                                                                                    | 66 |

| 4.5 | Post-layout simulations results for the $35\tau$ specification                                                                                                                                                                                                                        | 68 |

# List of Abbreviations

- ASIC Application-Specific Integrated Circuit

- **DSP** digital signal processing

- **DCT** Discrete Cosine Transform

- **CCI** Cross-Coupled Inverter

- CMOS Complementary Metal-Oxide-Semiconductor

- **DFS** Dynamic Frequency Scaling

- **DVS** Dynamic Voltage Scaling

- **EDS** Error Detection Sequential

- FPGA Field-Programmable Gate Array

- $\mathbf{MOS}$  Metal-Oxide-Semiconductor

- NMOS N-channel Metal-Oxide-Semiconductor

- MTBF Mean Time Between Failure

- PLL Phase-Locked Loop

- PMOS P-channel Metal-Oxide-Semiconductor

- **PVT** Process, Voltage and Temperature

- **TRC** Tunable Replica Circuit

- **TSMC** Taiwan Semiconductor Manufacturing Company

FOM Figure-of-Merit

VCO Voltage-Controlled Oscillator

**PSNR** Peak-Signal-Noise-Ratio

LSB Least-Significant Bit

**VOS** Voltage Over-Scaling

**DFS** Dynamic Frequency Scaling

**STA** Static Timing Analysis

LDMC Logic Delay Measurement Circuit

FBB Forward Body Biasing

**PS** Power Supply

**LR** Linear Regulator

LE Logic Element

$\mathbf{PnR}\ \mathbf{Place}\ \mathbf{and}\ \mathbf{Route}$

**ISB** Intermediate-Significant Bit

**RTL** Register-Transfer Level

**SEU** Single Event Upset

**ORI** Original Jamb Latch

${\bf GNDED}\,$  Grounded Jamb Latch

GATED Gated Jamb Latch

${\bf VBS}$  Voltage-Boosted Synchronizer

$\mathbf{MVBS}\,$  Metastability-driven Voltage-Boosted Synchronizer

${\bf CVBS}\,$  Clock-driven Voltage-Boosted Synchronizer

# Chapter 1

# Introduction

## 1.1 Introduction

As CMOS technologies evolve into nanometer regions, performance, power and reliability are the three most critical problems in digital design. High performance saves computational time, low power economizes energy while strong reliability assures long-term quality. Nowadays, low power/energy design has become more and more important mainly for two reasons [8, 9]. First, digital circuit applications powered by batteries such as laptops, car devices and cellphones are becoming ubiquitous. The speed of these digital circuits has evolved to satisfy the average usage. However, their power/energy consumptions have gained more concerns due to the slow evolution of battery technologies[10]. Second, since the integration scale of transistors in systems such as data centers [11] is increasing, the power consumption shall be limited and/or heat removals shall be added.

However, timing variation due to the effect of PVT variations of digital systems has become a major obstacle for high-performance and low-power. In order to counteract the impact of these variations, a delay- or voltage-margin is often added to clock period or supply voltage, respectively. However, the added margin deteriorates the performance or increases the power consumption. Energy-efficient designs with EDS circuits have been developed as alternatives in which error signals quantifying the timing variation are used for further responses such as timing error recovery or DVS. Nevertheless, this type of systems suffers from the timing-reliability problem due to EDS circuits (in this work the EDS-reliability is referred to this problem). The EDS-reliability directly affects the system reliability. The EDS-reliability of EDS circuits can be quantified using MTBF. Both the intrinsic and extrinsic EDS-reliability exist. The intrinsic EDS-reliability is caused by the metastability behavior of synchronizers in EDS circuits which perform as a classifier in the timing domain (essentially synchronizer reliability). The extrinsic EDS-reliability is defined as the avoidance of the actual timing errors when the EDS circuits are deployed to detect the errors (slack deficit or timing errors). The MTBF for the extrinsic EDS reliability is directly related to the EDS circuits deployment in the application systems.

## 1.2 Motivation

To improve the EDS reliability, often circuit parameters such as performance, area, and energy are sacrificed. The motivation of this research is to improve the EDS reliability with much improved circuit parameters. In particular, this thesis makes contributions in two areas: (1) the effectiveness of an EDS system for power savings is demonstrated in a FPGA with real life data. In this experiment a feedback loop was constructed with EDS. A DSP unit with Discrete Cosine Transform (DCT) was implemented for image processing. Experimental results show that substantial power saving can be achieved without compromising image quality. (2) synchronizers are often used in digital systems for a broad range of applications. In general, they help synchronize an asynchronous event to the synchronous system. A register or a latch is a simple synchronizer aligning data to an incoming clock. Synchronizers are also key elements in EDS systems determining error signals. Metastability can compromise synchronizers and EDS reliability; and it becomes an issue when the supply voltage is aggressively lowered to conserve power and energy. We are proposing VBSs which demonstrate better metastability performance.

# 1.3 Thesis Overview

The rest of the dissertation is organized as follows: Chapter 2 discusses the background of energy-efficient systems with EDS circuits and the EDS-reliability related issues. This chapter first introduces the effects of PVT variations and the conventional methods to combat these effects. EDS circuits and state-of-the-art digital systems with EDS circuits are studied. The metastability problem of synchronizers in EDS circuits is discussed. Chapter 3 proposes a new EDS deployment strategy to improve the extrinsic EDS-reliability. The proposed strategy is applied to an FPGA-based DCT unit with EDS and DVS circuits. Chapter 4 proposes VBSs to solve the performance bottleneck with a MTBF specification of the intrinsic EDS reliability, in an Application-Specific Integrated Circuit (ASIC) technology. A new methodology of metastability parameter extraction is also proposed. Simulation results of proposed synchronizers show the significant improvement of  $\tau$ . Chapter 5 concludes the contributions and proposes the future work.

# Chapter 2

# Energy-Efficient Digital Design with EDS circuits

### 2.1 Introduction

Chapter 1 introduced the concept of the energy-efficient systems with EDS circuits and the motivation of timing-reliable EDS circuit design and deployment. This chapter first introduces the PVT variations and the conventional methods to counteract the effects of the variations. EDS circuits that detect the PVT variations are introduced and the detailed timing of EDS circuits is analyzed. In the next section, state-of-the-art digital systems with EDS circuits are introduced and the extrinsic reliability problem of EDS circuits is discussed. Later, the metastability problem of EDS circuits is discussed in detail, including basic concepts of metastability, metastable signal transformation, metastability failure mode, metastability mitigation and the methodologies for metastability parameter extraction. Finally conclusions are drawn.

## 2.2 Digital Circuits and Variability

### 2.2.1 Conventional Synchronous Design

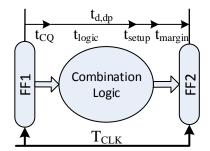

As shown in Fig 2.1, the delay  $t_{d,dp}$  of one stage of a data-path pipeline in a conventional synchronous design is given by

$$t_{d,dp} = t_{CQ} + t_{setup} + t_{logic} + t_{margin}, \qquad (2.1)$$

where  $t_{CQ}$  and  $t_{setup}$  are the CLK-to-Q output time and the setup time of the sequential circuits (used as storage elements) FF1 and FF2 respectively,  $t_{logic}$  is the longest path delay of the combinational circuits. The margin  $t_{margin}$  is added to counteract the effect of the worst-case combination of PVT variations to ensure correct functionality. The  $t_{margin}$  restricts the clock frequency.

Figure 2.1: Conventional Design.

We have the first constraint for clock period  $T_{CLK}$  from the data-path:

$$T_{CLK} \ge t_{d,dp}.\tag{2.2}$$

### 2.2.2 Circuit Scaling and Variability

Low-power/energy design has become important for digital applications. However, it is faced with unavoidable obstacles such as PVT variations that occur globally or locally in chips, spread across CMOS product lifespans.

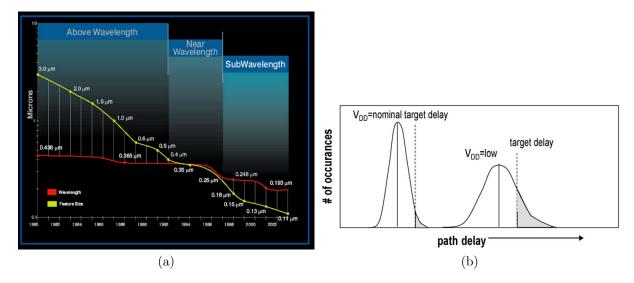

Due to the imperfect manufacturing, actual transistor sizes and routing delays vary among chips and inside a single chip. Aging effects [6] also requires an extra margin. As process technologies scale down into deep sub-micron levels, device feature sizes eventually become smaller than the optical wavelength of lithography process in advanced processes (c.f. Fig 2.2a)[6]. Thus, the process variations have become even larger than before.

Although power supplies are used to maintain stable external voltages, data switching activities can still induce significant internal voltage variations. Abrupt data switching activities can cause sudden current changes that induce IR droop and inductance voltage drop. In high data switching activities, a large current flows through resistances, generating heat from inside a chip. As supply voltages scale down to low levels, path delays of circuits vary more severely (c.f Fig 2.2b) [6].

Since CMOS integrations such as the emerging 3D integrated circuits and circuit performance are rapidly increasing, the power density has become a constrain for CMOS chip designs. However, packaging approaches for sufficient heat removal is still not economical [12]. As the junction temperature goes up, both the carrier's mobility and the driving current of the transistors decrease. Thus the speed of the circuit is degraded. Assuming the same ambient temperature, the junction-temperature variation is more and more exacerbated, leading to worse circuit delays.

In summary, as technologies further scale, the PVT variations have become more severe. Thus data-path delays vary in a larger scope, requiring a larger  $t_{margin}$ .

Figure 2.2: (a) The trend of CMOS technologies; (b) a demonstration of path delay variations (from [6]).

# 2.3 Energy-Efficient Digital Systems with EDS Circuits

# 2.3.1 State-of-Art Approaches to Deal With Data-path Variability

[6] provides a summary of stage-of-art approaches to deal with Data-path variabilities, listed as follows according to the level of the variability awareness.

Transistor level optimizations, including transistor sizing and dual  $V_{TH}$ , have been proposed to both speed up data-path and reduce the timing uncertainty at the expense of the area and/or power consumption.

*Critical instruction management.* The critical instructions trigger the critical paths and can be executed in a different way as compared with other instructions, such as reducing operating frequency and using a dedicated unit to process them. Nevertheless, the latency is increased or an extra area is needed.

*Post-silicon calibration.* To counteract the effect of the process variations, in addition to adding a part of margin for process variations to all chips, conventional designs also use benchmarks to measure the speed of each taped-out chip. After the measurement, the process-variation margin can be reduced by applying adaptive voltage or frequency. The energy is saved or the speed is improved at the cost of calibration effort.

Sensor-based adaptive architecture technique. Here a sensor is the circuit that provide dynamic information. Examples include on-chip leakage sensors, the control voltage of Voltage-Controlled Oscillator (VCO) ([13]) in a Phase-Locked Loop (PLL) that can dynamically capture performance variations in a circuit, on-chip wearout detection circuit, temperature sensor and EDS circuits. Nevertheless, EDS circuits are relatively light and provide the finest information. This dissertation focus on EDS circuits only.

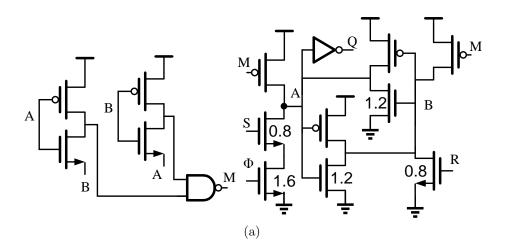

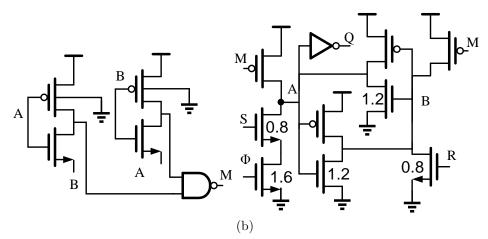

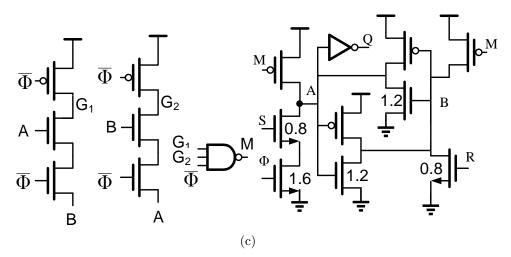

### 2.3.2 Variability and EDS circuits

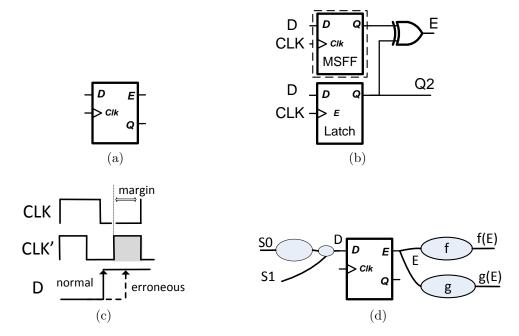

PVT variations are unavoidable, however, their worst-case combination is assumed to be rare ([14]). Leveraging this characteristic, EDS circuits have been developed to detect the variations [1, 2, 3, 4]. As the name suggests, EDS circuits are special sequential circuits that detect errors. Here an error means unfavorable timing variations of the EDS-monitored data-paths, such as a slack deficit or an actual timing error. Nearly all state-of-the-art EDS circuits follow the architecture abstraction in Fig 2.3a. An EDS circuit like Fig 2.3b consists of a storage element (from D to Q), a synchronizer (from D to E), and an XOR gate. Fig 2.3d shows a simple deployment of EDS circuits. In this deployment, signals S0 and S1 are the outputs of precedent stages at t = 0 (Fig 2.4a) and propagate through the combinational logic (so called EDS-monitored paths) to port D at variable time that depends on paths and PVT variations. EDS-monitored paths map the effect of the PVT variations into timing variations and the EDS circuits act as binary classifiers to detect slack-deficit or timing errors.

### 2.3.3 EDS Circuits Timing

The brief timing of EDS circuits are shown in Fig 2.3c where D, Q and E represent the signals at port D, Q and E respectively). Various arrival time of The signal D causes diverse EDS output combinations of Q and E, triggering normal or abnormal system behaviors.

Figure 2.3: (a) EDS abstraction (b) An EDS circuit: Double Sampling with Time Borrowing (c) EDS brief timing. (d) EDS circuit deployment.

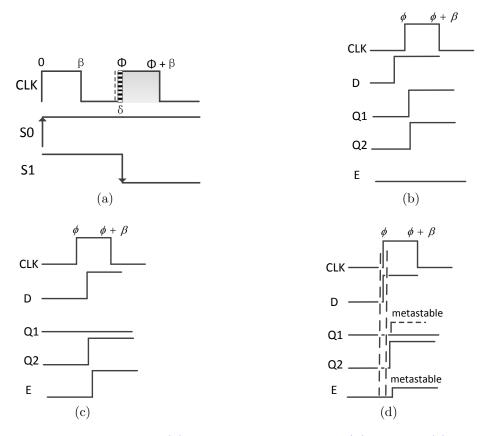

If D arrives between  $(\beta, \phi)$  ("normal windows", Fig 2.4b), Q shows no timing errors ("false") and E indicates "negative". This case represents normal executions with the highest probability among all the output combinations.

If D arrives between  $(\phi, \phi + \beta)$  ("detection window", Fig 2.4c), Q outputs a timing error ("true") while E indicates "positive". This "True positive" will not lead to system failure if the timing error is to be corrected.

If D arrives too early (from S1) between  $(\phi, \phi + \beta)$  ("min-delay window", Fig 2.4c), Q is "false" and E reports "positive". During the recovery of "false positive", the data of the errant instruction still corrupts the data of the earlier instruction in the latch of EDS circuits. Thus the min-delay constraint must be satisfied for all the EDS-monitored paths in these systems, which can be done by inserting buffers into the short ones of the EDS-monitored paths (such as S1).

If D and CLK transition simultaneously at  $t=\phi$ , i.e., D falls into "the metastable window"  $\delta$  (Fig 2.4d), E becomes metastable. The synchronizer in the EDS circuit is ambivalent in identifying the arrival time of D. Therefore, port E outputs an intermediatelevel signal (Fig 2.4d), namely "synchronization metastability". To be distinct from timing errors in data paths, in this thesis metastability only denotes the "synchronization metastability" in the control paths.

### 2.3.4 EDS-Triggered System Responses

Further responses are applied accordingly to achieve energy efficiency or performance improvement and this will be discussed later. For example, the guided DVS circuits accordingly adjust the operating voltage to a proper lower level. Due to the quadratic relationship between dynamic power consumption and supply voltage, significant power saving can be achieved.

## 2.4 EDS Applications

### 2.4.1 Microprocessors with EDS

To reduce energy consumption, EDS circuits have been applied in microprocessors [1, 15, 16] to monitor critical paths. To ensure no system failures, the detected timing errors are then corrected by timing error recovery circuits implemented by a microprocessor's inherent mechanisms such as instruction stalling and jumping. The slow response circuits like DVS or Dynamic Frequency Scaling (DFS) then accordingly and properly adjust supply voltage  $V_{op}$  or clock frequency (for simplicity, this dissertation only considers DVS).

Figure 2.4: EDS detailed timing: (a) timing region division; (b) normal, (c) erroneous, (d) metastable timing.

The timing error recovery mechanisms have one primary advantage. By the virtue of the timing error recovery mechanism, a faster clock CLK' can be used instead of the CLK used in the conventional design for error-free operations at the same supply voltage. This is illustrated in Fig 2.3c. Thus, at the same clock frequency, the operating voltage  $V_{op}$  for microprocessors with EDS circuits can be automatically lowered by DVS circuits, which is illustrated by

$$V_{lower} \le V_{op} \le V_{upper}.$$

(2.3)

Here the voltage  $V_{upper}$  is the point where conventional designs can operates. The  $V_{lower}$  is the lowest safe limit for DVS in microprocessors with EDS. This limit can be obtained by Static Timing Analysis (STA) [15]. The lower  $V_{op}$  leads to energy reduction. Nevertheless, extra circuits and error recovery actions can induce some energy penalty. If the energy reduction surpasses the energy penalty, the total energy is saved.

Many state-of-the-art microprocessors with EDS have been proposed in a variety of architectures, processes and supply voltages. Researchers reported 22% to 52% energy savings at equivalent performance in [15]. About 41% throughput gain at equivalent energy consumption was reported by [1]. Other examples of similar energy savings were reported in [17],[18],[19],[20], [21].

Nevertheless, the timing error recovery mechanisms have several disadvantages:

(1) Adding significant design complexity. Currently, timing error recovery mechanisms are built based on the inherent microprocessor control logic which usually is not available in DSP circuits.

(2) Adding indeterminate latency. This may not be acceptable for real-time DSP circuits. Large or small latency may or may not be a problem for many DSP circuits, however, indeterminate latency can be troublesome for the control logic of DSP circuits.

(3) Metastability problem. It mostly impacts fast responses such as timing error recovery circuits. [22] calculates  $P_{meta}$  to be 2e–30 under the supply voltage ranging 1.2 V-1.8 Vin a 0.18 µm technology. However, it is unclear whether it is calculated under the worst-case or normal PVT conditions. Even so, recently, after analyzing the state-of-the-art academic microprocessors with EDS circuits, [23] believes the metastability problem to be one of possible reasons for why there has been no industrial microprocessor with EDS circuits. Nevertheless, a large amount of time for metastability resolution can be added to slow responses such as DVS. Thus, the metastability problem is less likely to crash the systems with only slow responses.

### 2.4.2 **DSP** Circuits with **EDS**

For real-time DSP circuits, it is preferable to apply the mentioned slack-deficit-detectiononly techniques. The difficulty of these techniques mainly lies in PVT-to-timing converters. Due to the lack of error correction and DVS limit, PVT-to-timing converters must satisfy speculative and accuracy requirements to avoid direct and indirect timing errors, respectively. The speculative requirement is that neither monitored nor non-monitored paths should generate unacceptable timing errors when slack-deficits are being detected. The accuracy requirement can be viewed from the two perspectives of spatial and temporal sampling: EDS-monitored paths should be placed close to the actual circuits to achieve high correlation or else a larger extra margin is needed to compensate for local variations; EDS-monitored paths should be regularly activated with realistic input data for accurate detection or else there is a possibility of misguided VOS (temporal sampling).

Targeting to satisfy the requirements with minimum penalties, various EDS circuit deployment strategies were proposed. In [1] Tunable Replica Circuits (TRCs) consist of a series of delay-tunable buffers with EDS circuits placed at the endpoints of TRCs. A TRC mimic the worst case delay of a pipeline system with a small timing margin. A limited number of TRC can be placed along with the actual circuits and activated in every clock cycle to detect global PVT fluctuations. In [2], it was shown that a small number of timing errors at LSB in some error-tolerant DSP circuits do not significantly degrade overall quality. Thus, the non-critical Least-Significant Bit (LSB) paths of a DCT unit are purposely extended by adding buffers as critical paths. EDS circuits are augmented to these extended paths. A test image Lena is used as the input data. PSNR is a typical measurement method for image processing. PSNR of the output of the proposed design is only degraded about 4 dB compared to that of the DCT design. Nevertheless, only simulation results are provided and no actual circuit was implemented.

Unlike ASIC, finely-tuned buffers are impractical in an FPGA [24, 3, 4]. Instead, [25] introduced a method namely LDMC. As in Fig. 2.5a, 128 inverters form a very-long chain. The input of the chain is the clock CLK. CLK also drives 128 flip-flops as EDS circuits to monitor outputs of each inverter. The 128 outputs of the flip-flops represent the delay of the chain and thus indicate the PVT status of the FPGA chip. Accordingly, a DVS circuit is driven to adjust the supply voltage.

Another way is to use fine-tuned clocks in FPGA. As in Fig. 2.5b from [24, 3, 4], EDS circuits (the shadow register) monitor some of the critical paths of FPGA-based DSP

Figure 2.5: (a) LDMC (from [25]); (b) Slack measurement (from [24]).

circuits. An extra phase-shifted clock (shadow clock) together with the main clock is used to drive these EDS circuits, precluding buffer insertions. Nevertheless this method can have two major disadvantages, an extra clock and validation with realistic data. The extra clock phase-shifting requires more resource, place-and-route effort and energy consumption. More importantly, the critical paths are not often activated with realistic data. Typically, a new FPGA design methodology should be validated from two perspectives, various hardware styles and extensive input data. [3, 4] provides numerous types of test hardware (even including the DCT that will be used for my work). However, I was unable to discover the exact input data set for the measurement in the papers. Nevertheless, the problem of unexercised paths is mentioned. It is also stated that various methods are being studied to alleviate this problem. However, no recent research is reported.

# 2.5 Synchronizer and Metastability Considerations for EDS Circuits

Synchronizers and their metastability are an elusive topic. A tutorial of metastability is provided in [26]. Further details of synchronizer knowledge can be found in the book *Synchronization and Arbitration in Digital Systems* [27]. In the following paragraphs, synchronizers and metastability will be described in brief.

Usually a latch (Fig 2.6a) (including the CCI Fig 2.6b) is a basic synchronizing unit.

Normally S fully charges the CCI to true stable states  $((V_X, V'_X) = (V_{dd}, 0)$  or  $(V_X, V'_X) = (0, V_{dd})$ , shown in Fig 2.6c). However, if S and  $\Phi$  transition simultaneously, from the circuit perspective, the setup or hold time of the synchronizer will be violated, the CCI are only partially-charged and enter an intermediate level  $V_m$  shown in Fig 2.6c. Ideally the CCI stay at  $V_m$  forever, however, in the actual world even a very small noise can break the balance and force the CCI to settle down to true stable states. This phenomenon is called metastability.

Figure 2.6: A synchronizer (a) The ORI schematic (b) CCIs (c) voltage transfer curve.

### 2.5.1 Synchronization Parameters

#### **MTBF** due to Metastability

Metastability failure probability per operation, i.e., the probability that the metastability resolution time reaches or exceeds a given value  $t_r$  is defined as [28]

$$P_{meta} = f_c t_w e^{-\frac{t_r}{\tau}} \tag{2.4}$$

and MTBF due to metastability is [28]

$$MTBF = \frac{1}{P_{meta}f_d} = \frac{e^{\frac{t_T}{\tau}}}{T_w f_c f_d}$$

(2.5)

where  $t_w$  is the asymptotic width of the metastability window,  $\tau$  is the resolution time constant,  $f_d$  and  $f_c$  are data and clock frequencies, respectively. The metastability parameters such as  $\tau$  and  $t_w$  describe the relationship between delay  $t_r$  and MTBF.  $t_w$  is usually a small portion of clock period and  $t_w f_c$  is calculated as 0.05 for a 90 µm technology at 0.3 V in [29].

#### Synchronizer Delay

For synchronizers with constant  $\tau$ ,  $t_r$  can be expressed as

$$t_r = N_r \cdot \tau \tag{2.6}$$

where  $N_r$  is a *normalized* unit-less value of the metastability resolution time.  $N_r$  is a dominant term for MTBF. Although MTBF,  $P_{meta}$  and  $N_r$  are all useful parameters for describing synchronizer reliability, researchers tend to use  $N_r$ .

The delay  $t_d$  of a synchronizer such as a Jamb latch [30] in Fig. 2.6a is approximated as [29]

$$t_d \simeq t_n + t_r \tag{2.7}$$

where  $t_n$  is the nominal delay of a synchronizer without violating the setup time requirement.  $t_n$  is given by

$$t_n = t_{setup} + t_{CQ}.$$

(2.8)

Thus

$$t_d \simeq t_n + N_r \cdot \tau = t_n + \tau \cdot \ln(MTBF \cdot T_w \cdot f_c \cdot f_d)$$

(2.9)

So far we have another constraint for the clock period from the synchronization paths which is given by

$$T_{CLK} \ge t_d, \tag{2.10}$$

assuming synchronizer delay  $t_d$  is the speed bottleneck. Here provides a summary (Table. 2.1) of the timing parameters in this Chapter.

| Timing parameter | Definition                                                  |

|------------------|-------------------------------------------------------------|

| $t_{d,dp}$       | the delay of one stage of a data-path pipeline              |

| $t_{CQ}$         | the CLK-to-Q output time of the sequential circuits         |

| $t_{setup}$      | the setup time of the sequential circuits                   |

| $t_{logic}$      | the longest path delay of the combinational circuits        |

| $t_{margin}$     | the margin added to counteract the effect of PVT variations |

| $t_r$            | the metastability resolution time                           |

| $t_w$            | the asymptotic width of the metastability window            |

| au               | the metastability resolution time constant                  |

| $t_d$            | the delay of a synchronizer                                 |

| $t_n$            | the nominal delay of a synchronizer                         |

#### **Energy Consumption**

The overall average energy consumption  $E_{total}$  can be estimated as

$$E_{total} = (1 - a\%)E_{idle} + a\%[(1 - b\%)E_{norm} + b\%E_{meta})]$$

(2.11)

where  $E_{idle}$ ,  $E_{norm}$  and  $E_{meta}$  are the energy consumption during the idle status, a normal data activity and metastability, respectively.  $a\% = \frac{f_d}{f_c}$  is data activity and  $b\% = T_w f_c$  is metastability probability with data activities. For asynchronous communication systems or the final synchronizers in a resilient digital systems, a% is usually very small due to the hand-shake protocol or the small timing-error rate setting. For synchronizers used as data samplers such as shadow flip-flops in the Razor-style designs, a% is the same as data-path activities. b% is very small as calculated. Thus  $E_{total}$  is mainly determined by  $E_{idle}$  and  $E_{norm}$ . However, synchronizers are not always operated at the maximum clock frequency. Thus in this case, extra energy can be represented by the leakage power of the synchronizers.

### 2.5.2 Figure-of-Merit of Synchronizer Design

This dissertation classifies digital design parameters into three categories: system parameters, circuit external parameters and circuit internal parameters. System parameters such as MTBF and  $t_d$  are determined or designed by system designers. Circuit external parameters such as  $t_n$ ,  $t_w$  and  $\tau$  are visible to system designers and designed by circuit designers. Circuit internal parameters such as the capacitance C and the transconductance  $g_m$  are invisible to system designers and determined by circuit designers. An Figure-of-Merit (FOM) is chosen from circuit external parameters. It is the key prerequisite to the success of a circuit design. In other words, if targeting an improper FOM, fancy circuit designs may easily be introduced. However, these designs might not meet the requirements of actual systems where a circuit FOM should be evaluated. Hence, this work adopts the FOM of synchronizers that are well accepted and explored by mainstream research. Nevertheless, this could place a tougher task for innovative circuits design than using a self-proposed FOM. The FOM of synchronizers in this dissertation is obtained and reviewed from a system perspective as follows.

Firstly, MTBF due to metastability of synchronizers can directly constrain the overall system MTBF. This is because the overall system MTBF is upper-bounded by the smallest MTBF among various kinds of failure mechanisms. Secondly, the synchronizer delay  $t_d$  can possibly constrain the system speed  $T_{CLK}$  for a fixed system architecture or increase the latency of the system. Thirdly, the number of such synchronizers in typical system designs is usually only a few. Typical system designs use no or only a few synchronizers for peripherals, and these synchronizers consume a negligible percentage of power consumption. These extra synchronizing flip-flops in EDS circuits consume < 0.9% ([1]) to 5.7% ([17]) of the entire power. Asynchronous communication systems (sakurai [31]) can also leverage only a few synchronizers. [30], [28], [32],[33]). Thus, the delay of critical synchronizers is usually weighted heavier than their power and area. Synchronizer delay and MTBF of synchronizers due to metastability exclusively constrain each other and  $\tau$  is the key coefficient to describe this constraining relationship. A common viewpoint is that in synchronizer designs, MTBF due to metastability is prioritized the highest and specified first, while synchronizer delay is usually weighted heavier than energy consumption or area cost and targeted to be improved by methods such as reducing  $\tau$  of the synchronizer. In simple words,  $\tau$  is the main FOM of synchronizers. Notice that  $t_d$  and MTBF are NOT circuit parameters but system parameters. In other words, "high speed(performance)" or "reliable" may not be proper words to describe a synchronizer and "metastable-hardened" is used instead for describing synchronizers with better metastability parameters ( $\tau$  and  $t_w$ ).

Nevertheless, the circuit parameter  $\tau$  alone is less intuitive. It is better illustrated and understood along with MTBF and  $t_d$ . The specification of the metastability-induced MTBF needs to be set first. Researchers [34] report a metastability-induced MTBF 10<sup>10</sup> times greater than the targeted Single Event Upset (SEU) induced MTBF. Similarly, authors in [22] calculate  $P_{meta} = 2e-30$  in its system, which is roughly converted into  $N_r = 65$  (two stages). Conventional synchronizer design suggests a  $N_r$  around 29-40 for single stage synchronizing. This work applies a  $N_r = 35$  specification for one synchronizing latch, indicating a 1-year MTBF for the latch if assuming  $t_w f_c = 0.05$  [29] and  $f_d = 10^9$ (assuming the worst case scenario).

EDS circuits inspire a deeper understanding of the roles that sequential circuits play in system designs, either storage elements or synchronizers. Storage elements do not suffer from the metastability problem since they are protected by timing margins even in the systems with EDS circuits. Thus neither  $\tau$  nor  $T_w$  is a FOM of storage element. This is evident since the standard cell flip-flops show very poor  $\tau$ . When used as storage elements, their number usually is large and the power(energy) consumption and the nominal delay  $(t_n)$  of sequential circuits usually constitute considerable percentages of the system's power(energy) and speed, respectively. Thus, these two parameters are similarly important and the Power(Energy) Delay Product can be used as the FOM of storage elements [35]. In summary, synchronizers and storage elements have a different FOM. Furthermore, not only system designers but also STA tools are able to identify the roles of sequential circuits as synchronizers or storage elements because properly installed storage elements (synchronizers) always satisfy (violate) the static timing constraint shown in Eq. (2.1). Due to all these reasons, it is better to design dedicate synchronizers than to design general sequential circuits for both usages.

#### Impact of Scaling on Synchronizer FOM

As mentioned both synchronizer delay and data-path delay can bottleneck system speed, thus a comparison between them is necessary for system designers. however, this comparison is unknown to circuit designers and estimated by

$$k = \frac{\tau}{t_{FO4}} \tag{2.12}$$

where  $t_{FO4}$  is the delay of a inverter with a fan-out of 4. As technologies scales, though the absolute data-path delay and synchronizer delay (control-path) are both improved, the former gain more improvement than the latter. Similarly, as supply voltages scale down, the synchronizer delay worses more than the data-path delay does. Thus synchronizer delay  $t_d$  becomes more likely than data-path delay  $t_{d,dp}$  to bottleneck system performance.

As mentioned in Section 2.2.2, technology scaling also enlarge PVT variations. This can impact not only data-path delays but also synchronizer delay.

### 2.5.3 Synchronizer Design Fundamentals

To minimize  $t_d$ , two techniques have been developed, including synchronization pipelining or improving metastability parameters. Similar to data-path pipelining, the synchronizer pipelining is to convey the metastable status of the current synchronizer to those of the subsequent synchronizers and continue to settle down. Thus it gives more metastability resolution time. This is shown in

$$t_r = t_{r,1} + t_{r,2} + \dots + t_{r,n}, \tag{2.13}$$

where  $t_{r,i}$  is the metastability resolution time of the *ith* synchronizer. This equation implies that each synchronizer in the synchronization pipeline is identically important, even though the metastability is initialized at the first stage. More importantly, for the same overall metastability-induced MTBF requirement, the MTBF specification of each stage can be reduced, leading to a smaller  $t_d$  for each stage. Nevertheless, this pipelining technique has the same disadvantages as data-path pipelining does. First, each stage adds an extra  $t_n$ . Second, more importantly, it significantly increases the latency and data-path complexity. Generally, synchronization pipelining techniques have different impacts on three types of systems: Type 1 systems where synchronization-latency is non-important, for example, the proposed system with slow responses for synchronization results in Chapter 3; Type 2 Systems where synchronization-latency has some negative impact, for example, microprocessors with EDS need the corresponding extensions of the data-path; Type 3 Systems where synchronization-latency is critically important such as [16] where a local stall is used for error recovery and only one clock cycle is given for metastability resolution.

Thus, metastable-hardened synchronizers are beneficial for type-2 systems and critical for type-3 systems. We focus on improving the synchronizer circuit parameters (the FOM of synchronizers), especially  $\tau$  which is determined by

$$\tau = \frac{C}{g_{m,sum}} \tag{2.14}$$

where  $g_{m,sum}$  is the sum of the transconductance  $g_m$  of inverters in Jamb latch and C is lumped capacitance at nodes A and B of Jamb latch. Furthermore,  $g_{m,sum}$  is expressed as

$$g_{m,sum} = g_{mP} + g_{mN} (2.15)$$

where  $g_{mP}$  and  $g_{mN}$  are the transconductance of P-channel Metal-Oxide-Semiconductor (PMOS) and N-channel Metal-Oxide-Semiconductor (NMOS) transistors, respectively. The transconductance of a single Metal-Oxide-Semiconductor (MOS) transistor is calculated as

$$g_{m,MOS} = k' \frac{W}{L} (V_{GS} - V_{th}) = \sqrt{2I_D k' \frac{W}{L}}$$

(2.16)

where k' is a process parameter, W and L are width and length of the transistor, respectively,  $V_{GS}$  is the gate-source voltage,  $V_{th}$  is the threshold voltage, and  $I_D$  is the drain current of the transistor. Thus,  $\tau$  is greatly influenced by transistor topologies and sizing, supply voltages, and other factors.

So far, Eq. (2.14) implies a self constraint for synchronizer design between  $g_m$  and C. Besides, there needs to be a trade-off between  $t_n$  and  $\tau$ . Nevertheless, both of these two trade-offs have been well studied. The bottom line is that the CCIs should be able to resolve the metastability at the critical nodes to stable states and the driving transistors should be able to drive the states at the critical nodes to the target stable states. New circuit topologies, transistor sizing, using low  $V_{th}$  and other techniques need a trade-off between  $\tau$  and  $t_n$  to optimize  $t_d$  in Eq. (2.9). Transistor sizing is an inefficient way since  $g_m$  and C are both increased.

#### 2.5.4 Synchronizer Validation

Since in Eq. (2.14) the capacitance and the transconductance cannot be directly validated, two methodologies for  $\tau$  extraction in the measurable timing and voltage domains are developed: Method One in [30] and Method Two (The proofs of these two methodologies are provided in [27].). Method One is performed as follows: in Fig. 2.6a, an ideal switch Kand a voltage source U with a small value are placed in between nodes A and B. K is first closed to force A and B to enter the true metastability state and then released to let them resolve. The small voltage source U (in our case this is smaller than 200 µV ) initializes the metastability resolution, acting like the noise in real circuits (otherwise this resolution may not happen in simulations). The  $\tau$  is calculated as

$$\tau = \frac{t_{r,1} - t_{r,2}}{\ln \frac{V_{A-B,1}}{V_{A-B,2}}} \tag{2.17}$$

where  $t_{r,1}$  and  $t_{r,2}$  are two time points during the metastability resolution and  $V_{A-B,1}$  and  $V_{A-B,2}$  are the corresponding voltage differences of node A and B for time points  $t_{r,1}$  and  $t_{r,2}$ , respectively.  $t_r$  for a specified  $N_r$  is further obtained by Eq. (2.6). Method One is simple and suitable for computer simulations. However, the extracted  $\tau$  may be inaccurate technically because these course-grained simulations generate only a few data points for

the metastability resolution region.

Method Two is to change the input data time  $(\delta_1 \text{ and } \delta_2)$  around the balance point and measure the synchronizer output time  $(t_{d,1} \text{ and } t_{d,2})$ . The  $\tau$  is calculated as

$$\tau = \frac{t_{d,1} - t_{d,2}}{\ln \frac{\delta_2}{\delta_1}}.$$

(2.18)

Method Two is complex and suitable for silicon measurement. The  $\tau$  accuracy also depends on the selection of  $\delta_1$  and  $\delta_2$ .

Furthermore, due to on-chip variability,  $\tau$  measured from the dedicated circuits does not directly apply to the actual application scenarios. Nevertheless, synchronizer measurement in actual application circuits will induce large circuit penalty and high manual effort. Many silicon-measurements of  $\tau$  are based on method Two. However, generally there exist a conflict of MTBF requirement between artifact design and reliability testing. For synchronizer measurement, special circuits namely digitally controllable delay lines are needed to generate aggressive input data with fine-tuned timing (usually precise in several ps) to set synchronizers in a deep metastable status. Even though, the observation of metastability in post-silicon measurements needs significant sampling time. On the contrary, the power, energy or speed measurement of other digital circuits requires less circuit penalty and manual effort. For example, power or energy can be obtained directly from measurements of supply rails.

Nevertheless, the above methodologies are only for one stage of synchronizer, i.e., one latch. Notice that a master-slave flip-flop is two consecutive synchronizers (pipelining) and showing  $\tau$  of the master stage alone is insufficient to represent the overall  $\tau$  of a flip-flop. However, even in simulations, it is usually impractical to measure  $\tau$  of the slave stages by using method Two to input data from the master stage. Thus, mainstream research focuses on single latches. There are a few exceptions that people work on flip-flop synchronizers such as measuring metastability parameters of the readily-available circuits such as the standard cell or FPGA registers. Nevertheless, even these measurements only show  $\tau$  of the master stages of tested circuits. Due to lack of related research literature, this dissertation believes that post-silicon measurements for multiple synchronizers need to be carried out

one synchronizer by one, even though these synchronizers form a synchronization pipeline like a master-slave flip-flop. On the contrary, though each component of a data-path may be designed and tested individually, the measurement of the data-path delay can be done by one overall test. In summary, much more design complexity and manual efforts are paid for post-silicon measurements for multiple synchronizers.

#### 2.5.5 Existing Synchronizer Design

Many synchronizer techniques (summarized in [36]) have been developed, however, not all of them work sufficiently at low supply voltages. Even worse, several cases of deceptive synchronizers are described in [37]. Here this work provides some existing synchronizers.

Jamb latch (Fig 2.6a) in [30] is built using non-CLK-controlled CCI as the feedback loop instead of other gates because non-CLK-controlled inverters have a higher gain and less capacitance than other gates do [30] [27], thus achieving a low  $\tau$ . A similar conclusion is drawn after extensive studies on the metastability of several high performance flip-flops ([38]). Thus, Jamb latch and its derivatives gain extensive research interest.

Assuming that flip-flops are becoming more susceptible to metastability due to the PVT variations ([39], [40], [38], [41]) and that the master stage of a flip-flop has the most impact on metastability resolution ([41] [39] [40]), [41] proposes two flip-flops with the master stages using differential CCI , namely pre-discharge flip-flop (first appeared in [42]) and sense-amplifier transmission-gate flip-flop. These two flip-flops both with significantly-sized CCI shows 30% and 24%  $\tau$  reduction over a CLK-controlled flip-flop with minimum-sized CCI , respectively. Simulations results in [39] [40] show that a storage cell namely Quatro with two non-CLK-controlled coupled feedback paths has  $\tau$  that are 11% smaller than that of a reference flip-flop with CLK-controlled CCI. In summary, these simulation results show that conventional methods such as non-CLK-controlled CCI and transistor sizing are still effective synchronizer techniques. Nevertheless, most innovatively and importantly, two useful FOM for flip-flops design, namely the metastability-delay-product ( $\tau \times t_n$ ) and the metastability-power-delay-product ( $\tau \times power \times t_n$ ), are proposed and used for analysis

throughout [41], [43], [39], [40]. Nevertheless, my dissertation still applies the FOM discussed in Section. 2.5.2 in this Chapter.

In [7], a new synchronizer is proposed as shown in Fig 2.7a and the measurement results in Fig 2.7b. However,  $\tau$  is not mentioned in [7] and needs an estimation. Typically,  $\tau$  of a Jamb latch for this situation is about 7 ps where  $t_{FO4}$  is 11 ps [7]. Assuming that all other factors ( $T_w$ ,  $f_c$ ,  $f_d$ ) are the same, a simple math using Eq. (2.5) would lead to  $\tau = 5.87$  ps for this dynamic synchronizer, around 16%  $\tau$  improvement over the basic Jamb latch. Nevertheless, the power and area penalties are large.

Figure 2.7: The dynamic synchronizer (screen-shots from [7]) (a)schematic; (b) validation results.

Power-hungry (or current-mode) synchronizers based on Jamb latches have been developed. One power-hungry method is to ground the amplifying PMOS transistors (Fig. 2.8a) as biasing transistors to provide very large bias current [44], [29]. However, the transconductance of the PMOS transistor is removed as expressed in Eq. (2.15) and the direct-path or leakage current is large. To reduce the power consumption, extra biasing transistors can be added and controlled by a metastability detector [29] (Fig. 2.8b) or a signal pulse (symmetric boost synchronizers [45]). Nevertheless, for the first case of the metastabilitydriven synchronizers, delay improvement is significantly degraded due to the additional capacitance at the latching nodes and the metastability detector delay.

The other power-hungry method for low supply voltage is to reduce the  $V_{th}$  of transistors. FBB has been exploited to reduce the  $V_{th}$  of PMOS and NMOS of the driving transistors and the CCIs for sub-threshold regions [29] and thus both  $\tau$  and  $t_n$  are sig-

Figure 2.8: The power-hungry synchronizers: (a) GNDED; (b) GATED.

nificant reduced. Furthermore, FBB is controlled and disabled when operated in nominal voltages to reduce power consumption. However, as I demonstrate the delay bottleneck of the metastability-driven synchronizers lies in the metastability detector delay. The FBB implementation for NMOS is non-trivial and requires expensive process options. Similarly, [43] advocates using low- $V_{th}$  transistors for only the CCI pair and standard- $V_{th}$  transistors for the remaining circuits to improve  $\tau$  in sub-threshold regions.

In [46], synchronizers are optimized by adapting them to the effect of on-chip variability at the post-silicon calibration stage. After the measurement of synchronizers on an FPGA, the best synchronizer among several redundant synchronizers is chosen to use, or, the clock frequency is adjusted accordingly for the measured synchronizer. For the latter method, the performance improvement is approximately 33% [46]. Nevertheless, the area penalty of additional circuits is very large.

Among all the synchronizers that this work has been researched on, this work deliberately chooses these techniques as our reference designs: the basic Jamb latch because of its excellent metastability performance and wide acceptance in mainstream research, the power-hungry synchronizers since they extremely improve  $\tau$  at low supply voltages and the PVT-variation adaptation technique as it is a rarely-seen post-silicon optimization technique for synchronizers. Nevertheless, all these could place another tough task for our design.

## 2.6 Conclusion

EDS circuits can be used to detect PVT variations for further responses to save energy; however, they suffer the intrinsic and extrinsic reliability problems. The intrinsic EDSreliability is caused by the metastability behavior of the synchronizers in EDS circuits. The MTBF due to metastability and the delay of synchronizers exclusively constrain each other and the  $\tau$  is the key coefficient to describe this constraining relationship. In synchronizer designs, the MTBF due to metastability is prioritized the highest and specified first, while the synchronizer delay is usually weighted heavier than the energy consumption or area cost and targeted to be improved by methods such as reducing the  $\tau$  of the synchronizer. The extrinsic EDS-reliability describes the ability of EDS circuits to avoid actual timing errors when the EDS circuits are deployed to detect the errors (slack deficit or timing errors). The extrinsic EDS-reliability depends on the EDS circuit deployment in the application systems.

# Chapter 3

# Design for an Energy-Efficient System with EDS Circuits

## 3.1 Introduction

To address the extrinsic EDS-reliability problem mentioned in Chapter 2, a new strategy for EDS circuit deployment is proposed in this chapter. Later, the proposed strategy is applied to an FPGA-based DCT unit together with EDS and DVS circuits as a proof of concept. In the next section, the experiment results are presented and finally the conclusions are drawn.

## 3.2 Proposed Circuit Design

In the proposed EDS deployment strategy, the non-critical paths with much higher data activities instead of the critical ones, are monitored by the EDS circuits. The speculative characteristic of EDS circuits is achieved by sampling at the clock falling edge and tuning clock duty cycle instead of sampling by an extra clock and tuning clock phase, precluding an extra clock. The effectiveness of the proposed design is demonstrated using FPGA-

Figure 3.1: Block diagram of the proposed FPGA-based design.

based DCT with EDS and DVS circuits in a closed-loop system consists of an Altera FPGA board and a linear voltage regulator to dynamically adjust the FPGA's supply voltage (c.f. Fig. 3.1). The FPGA board (Terasic DE0 development board with an Altera Cyclone III FPGA) has two power configurations: powered either directly through the PS or via the LR (LT3070 [5]) by configuring the two switches  $SW_a$  and  $SW_b$ . In PS configuration, supply voltage can be finely tuned to nominal voltage ( $V_{nominal}$ ) or a subcritical voltage. The LR ([5]) is digitally programmable by DVS circuits inside FPGA. LR has two operating modes: the nominal mode where supply voltage is 1.20 V and automatic mode (the so-called "DVS" mode), controlled by the switches SW[5] attached to FPGA.

#### 3.2.1 Proposed EDS Design and Deployment

Fig. 3.2a shows that multiple EDS circuits are inserted at the endpoints of only non-critical paths such as Intermediate-Significant Bits (ISBs) in a DSP data-path. The midway nodes (such as L1 in Fig. 3.2b) of the critical paths can be alternative locations, however, this work does not consider this case. This is because this work does not intend to break down the arithmetic logics such as the "+" operator at the Register-Transfer Level (RTL). In FPGA, these built-in adders are implemented using special purpose logic and not easily modified without incurring a performance degradation. Thus, the latter case may be more suitable for balanced arithmetic circuits in an ASIC.

Fig. 3.2c depicts a schematic of FPGA-based EDS circuit utilizing two flip-flops (DFF1 and DFF2). DFF1 samples signal D at the clock falling edge. The sampled and the late signals are XOR-ed as the ERROR signal that is held by DFF2 in the next clock cycle. In Fig. 3.2d, D should arrive before the clock falling edge in normal conditions and does not trigger the ERROR signal. On the other hand, an ERROR signal is generated if D arrives later than that edge due to PVT variations. Nevertheless, an ERROR signal is only an indication of slack-deficit (actually it is a timing error at the sampling DFF1 but not a system failure). The ERROR signals from EDS circuits are combined together as the final ERROR signal through an OR tree (Fig. 3.2a).

Here a knowledge about FPGA clocking is necessary for understanding the sampling at the clock falling edge and provided by [47, 48, 49]. FPGA clocks can be classified as base clocks that are externally supplied to FPGA and internally generated clocks. The internally generated clocks can be further categorized as gated clocks and derived clocks. Gated clocks are a clock gated by combinatorial circuits and thus no new timing nodes are generated. Usually this is not recommended in FPGA as it would introduce skew due to the added circuits or jitter due to the deviation from the dedicated clock network. Derived clocks are a new clock that are generated though registers or a PLL driven by a primary clock. Thus features such as frequency or phase can be different from the primary clock. Here an important special case is an inverted clock. It can be generated by an inverter or a PLL with a 180 degree phase shift. However, as [47, 48] clearly state, the best way is to sample the data on the opposite clock edge since most FPGA devices provide a programmable option to input a clock or an inverted clock to a register. In common sense, this is understandable since FPGA devices should provide a choice for system designers to use either the rising or falling clock edge. By this way, the clock signal traverses from the source such as a PLL to the destination registers through the dedicated clock-tree, regardless of whether its rising or falling edge will be used.

The non-monitored critical paths can also be protected from timing errors if the monitored paths (namely p1) maintain a *relative margin* over the most critical path (namely p2). To guide the Quartus II software to deploy the EDS circuits to achieve this, this work has developed a methodology that differentiates the duty cycles  $\beta$  and  $\beta'$  of the actual clock

Figure 3.2: (a)DSP Datapaths deployed with EDS circuits, (b) an arithmetic logic example (ripple-carry adder); (c) EDS circuitry implementation; (d) timing analysis.

$\phi$  and the constraint clock  $\phi'$  (only exists during the synthesis stage) by  $\Delta = (\beta' - \beta) \cdot T$ where T is the clock period. As shown in Fig. 3.2d, the EDS-monitored and the critical paths are sampled at the clock falling and rising edges, respectively. Hence, a virtual critical path relative to the clock falling edge, which is scaled based on the actual critical path by  $\beta$ , is generated. Thus, the relative margin  $t'_m$  provided by the EDS-monitored paths over the virtual critical path is given by

$$t'_m = \Delta + \left(\beta \cdot t_{s,cp} - t_{s,EDS}\right) \tag{3.1}$$

where  $t_{s,EDS}$ ,  $t_{s,cp}$  and  $t'_{s,cp} = \beta \cdot t_{s,cp}$  are the slacks of the EDS-monitored paths, the most critical path and the virtual critical path, respectively. Nevertheless, only those EDSmonitored paths that satisfy  $t'_m > 0$  protect the most critical path and can be defined as speculative paths ("s-path") which are the so-called PVT-to-timing converters while EDS circuits are the timing-to-digital converters. That is

$$t_{s,EDS} < \Delta + \beta \cdot t_{s,cp} \tag{3.2}$$

## 3.2.2 **DVS** Algorithm Design and Implementation

This work applies a DVS algorithm driven by the comparison of the actual and reference error rates,  $E_{rr}\%$  and  $E_{ref}\%$  which are the ratios of the actual and maximum-allowable numbers of errors ( $E_{rr}$  and  $E_{ref}$ ) over the sampling clock cycles, respectively. For the algorithm to match with  $t'_m$ , the operating voltage  $V_{DVS}$  should be scaled to where EDS circuits just start to detect errors. To achieve this,  $E_{ref}\%$  should be configured extremely small and can be further simplified to whether an error occurs during  $\phi_{cnt}$  clock cycles, where

$$E_{ref}\% = \frac{E_{ref}}{sampling \ clock \ cycles} = \frac{1}{\phi_{cnt}}$$

(3.3)

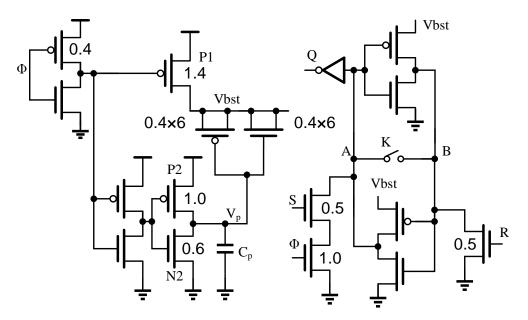

This configuration simplifies the error counter and the comparator to be only 1-bit in the DVS algorithm implemented in Fig. 3.3. The X-bit voltage counter divides the voltage range into  $2^X$  levels. The final ERROR signal from Fig. 3.2a is recorded in the error