# Broadband Doherty Power Amplifiers with Enhanced Linearity for Emerging Radio Transmitters

by

Hamed Golestaneh

A thesis presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2016

© Hamed Golestaneh 2016

#### Author's Declaration

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Hamed Golestaneh

#### Statement of Contributions

The work presented in Chapter 6 of this thesis was the result of collaboration with Kasyap Patel, who validated the proposed current contour based design methodology by designing a proof-of-concept circuit prototype (Section 6.5).

#### Abstract

The ever-increasing demand for utilizing wireless spectra has led to development of spectrally efficient radio systems. While these systems offer much higher data throughput, they employ more sophisticated modulation schemes, which result in wideband signals with high peak-to-average power ratios. These signal characteristics significantly complicate the design of RF transmitters, particularly power amplifiers, in terms of power efficiency and linearity requirements. Furthermore, upcoming wireless standards, such as long term evolution advanced (LTE-A) require adoption of carrier aggregation which incorporates multiple component carriers to yield aggregated channels of larger bandwidth (up to 100 MHz). On the other hand, the emerging systems are expected to support legacy standards with minimum area, cost, and power overhead, and thus call for highly-efficient linear broadband power amplifiers capable of efficiently amplifying concurrent modulated signals located over a broad carrier frequency range.

This thesis focuses on Doherty power amplifiers (DPAs) with extended high-efficiency range, enhanced bandwidth and improved linearity as a solution for high-efficiency multiband multi-standard transmitters. It addresses three major concerns associated with DPAs, namely, back-off efficiency, bandwidth, and linearity. The Thesis begins with a detailed theoretical analysis of two-way and three-way Doherty configurations from which the governing equations are derived. This is followed by a comprehensive study of bandwidth limitation in DPA variants.

As the first contribution, it is shown that the two existing three-way Doherty structures, i.e., conventional and modified DPAs have inherently broadband characteristics and thus are promising solutions for multi-standard base station transmitters. As a proof of concept, a 30-W three-way modified Doherty amplifier was designed and implemented using packaged GaN transistors over 0.73–0.98 GHz. The prototype was successfully linearized under modulated signals with up to 20 MHz modulation bandwidth.

To further improve the linearizability of the DPAs under wideband and multi-band modulated signals, this thesis investigates major sources of static and dynamic nonlinearity in two-way DPAs both at device and circuit levels and explores circuit techniques to mitigate them. Furthermore, the challenges of applying the Doherty technique for concurrent transmission of multiple modulated signals are tackled.

The most significant contribution of this thesis is to develop a novel waveform engineering approach to designing ultrawideband DPAs. This approach completely reformulates the DPA's output combiner conditions in order to accommodate complex-valued load modulation. Moreover, it relaxes the harmonic termination requirements of the DPAs to further enlarge the Doherty design space, thereby enhancing the bandwidth. A 50-W waveform-engineered two-way DPA prototype was designed for 1.5–2.5 GHz range and was successfully linearized under intra- and inter-band carrier-aggregated signals with up to 600 MHz carrier spacing.

Lastly, an input matching network design methodology is proposed for broadband DPAs. This methodology uses the novel concept of "current contours" to minimize the bandwidth, efficiency and linearity degradation of DPAs caused by device input non-idealities.

#### Acknowledgements

I would like to express my deepest gratitude to my supervisor, Prof. Slim Boumaiza for his priceless help, support, and guidance throughout my PhD. I sincerely thank him for teaching me various aspects of independent research. I would also like to thank my committee members, Prof. de Vreede, Prof. Long, Prof. Safavi, and Prof. Nieva for reviewing my thesis and providing insightful feedback.

Over the past four years, I have been blessed with wonderful friends in the EmRG group who always provided me with great encouragement and cheer. It is my great pleasure to take this opportunity to also thank all my friends in Canada. A special thanks to Sajjad Mosharraf and Kamal Rahimi for their immense support and companionship.

Last but not least, I would like to thank my parents for their endless love, support, and prayers throughout the years. There are no words that can express my gratitude and appreciation for all you have done for me. Dedication

To my loving family

# **Table of Contents**

| Author's Declaration                                                                                     | ii         |

|----------------------------------------------------------------------------------------------------------|------------|

| Statement of Contributions                                                                               | iii        |

| Abstract                                                                                                 | iv         |

| Acknowledgements                                                                                         | vi         |

| Dedication                                                                                               | <b>vii</b> |

| List of Tables                                                                                           | ix         |

| List of Figures                                                                                          | х          |

| List of Abbreviations                                                                                    | xi         |

| 1 Introduction                                                                                           | 1          |

| 1.1 Motivation $\ldots$ | 1          |

| 1.2 Thesis Objectives                                                                                    | 3          |

| 1.3 Thesis Outline                                                                                       | 5          |

| 2 High Efficiency Multi-Standard RF Transmitters                                                         | 7          |

| 2.1 Introduction                                                                                         | 7          |

|   | 2.2                                                                                      | Ideal I                                                                              | FET Model                                          | 7                                                                                                                      |

|---|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   | 2.3                                                                                      | Device                                                                               | e Technologies                                     | 9                                                                                                                      |

|   | 2.4                                                                                      | Efficie                                                                              | ncy Enhancement                                    | 10                                                                                                                     |

|   |                                                                                          | 2.4.1                                                                                | Drain Modulation Technique                         | 12                                                                                                                     |

|   |                                                                                          | 2.4.2                                                                                | Load Modulation Technique                          | 13                                                                                                                     |

|   | 2.5                                                                                      | Doher                                                                                | ty Amplifier Technique                             | 14                                                                                                                     |

|   |                                                                                          | 2.5.1                                                                                | Basic Principle                                    | 14                                                                                                                     |

|   |                                                                                          | 2.5.2                                                                                | Circuit Analysis                                   | 16                                                                                                                     |

|   |                                                                                          | 2.5.3                                                                                | Practical Design Challenges                        | 22                                                                                                                     |

|   |                                                                                          | 2.5.4                                                                                | DPA for extended PAPR                              | 26                                                                                                                     |

|   |                                                                                          | 2.5.5                                                                                | DPA with Asymmetrical Drain Voltages               | 27                                                                                                                     |

|   |                                                                                          | 2.5.6                                                                                | Bandwidth Analysis of Two-way DPAs                 | 30                                                                                                                     |

|   |                                                                                          | 2.5.7                                                                                | DPAs in Literature                                 | 33                                                                                                                     |

|   |                                                                                          |                                                                                      |                                                    |                                                                                                                        |

| 3 | Mu                                                                                       | lti-Way                                                                              | V DPA With Extended Bandwidth                      | 38                                                                                                                     |

| 3 | <b>Mu</b><br>3.1                                                                         |                                                                                      | V       DPA With Extended Bandwidth         uction | <b>38</b><br>38                                                                                                        |

| 3 |                                                                                          | Introd                                                                               |                                                    |                                                                                                                        |

| 3 | 3.1                                                                                      | Introd                                                                               | $\mathbf{uction}$                                  | 38                                                                                                                     |

| 3 | 3.1                                                                                      | Introd<br>Multi-                                                                     | uction                                             | 38<br>38                                                                                                               |

| 3 | 3.1                                                                                      | Introd<br>Multi-<br>3.2.1                                                            | uction                                             | 38<br>38<br>39                                                                                                         |

| 3 | 3.1                                                                                      | Introd<br>Multi-<br>3.2.1<br>3.2.2<br>3.2.3                                          | uction                                             | 38<br>38<br>39<br>45                                                                                                   |

| 3 | 3.1<br>3.2                                                                               | Introd<br>Multi-<br>3.2.1<br>3.2.2<br>3.2.3<br>Design                                | uction                                             | 38<br>38<br>39<br>45<br>52                                                                                             |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                | Introd<br>Multi-<br>3.2.1<br>3.2.2<br>3.2.3<br>Design<br>Conch                       | uction                                             | 38<br>38<br>39<br>45<br>52<br>56                                                                                       |

|   | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                | Introd<br>Multi-<br>3.2.1<br>3.2.2<br>3.2.3<br>Design<br>Conche                      | uction                                             | 38<br>38<br>39<br>45<br>52<br>56<br>61                                                                                 |

|   | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Ana</li> </ul>              | Introd<br>Multi-<br>3.2.1<br>3.2.2<br>3.2.3<br>Desigr<br>Conch<br>alysis c<br>Introd | uction                                             | <ol> <li>38</li> <li>38</li> <li>39</li> <li>45</li> <li>52</li> <li>56</li> <li>61</li> <li>63</li> </ol>             |

|   | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Ana</li> <li>4.1</li> </ul> | Introd<br>Multi-<br>3.2.1<br>3.2.2<br>3.2.3<br>Desigr<br>Conch<br>alysis c<br>Introd | uction                                             | <ul> <li>38</li> <li>38</li> <li>39</li> <li>45</li> <li>52</li> <li>56</li> <li>61</li> <li>63</li> <li>63</li> </ul> |

|   |     | 4.2.3 Sources of Distortion at Circuit Level      |

|---|-----|---------------------------------------------------|

|   | 4.3 | Dynamic Distortion Mechanisms in DPAs    83       |

|   |     | 4.3.1 Thermal and Trapping Effects                |

|   |     | 4.3.2 Magnitude/Phase Dispersion                  |

|   |     | 4.3.3 Drain Induced Memory Effects                |

|   | 4.4 | Conclusion                                        |

| 5 | Bro | adband Waveform-Engineered DPA 90                 |

|   | 5.1 | Introduction                                      |

|   | 5.2 | Doherty Amplifier and Waveform Engineering        |

|   |     | 5.2.1 WeDPA Concept                               |

|   |     | 5.2.2 Analysis of WeDPA                           |

|   |     | 5.2.3 On the Role of Phase Difference             |

|   | 5.3 | WeDPA Implementation                              |

|   | 5.4 | Experimental Results                              |

|   | 5.5 | Conclusion                                        |

| 6 | Inp | ut Matching Network Design for Broadband DPAs 112 |

|   | 6.1 | Introduction                                      |

|   | 6.2 | Broadband Input Matching Design Challenges        |

|   | 6.3 | Concept of Current Contours 114                   |

|   |     | 6.3.1 Class-B Contours                            |

|   |     | 6.3.2 Class-C Contours                            |

|   | 6.4 | Input Matching Design Methodology 117             |

|   |     | 6.4.1 Class-B Matching Design                     |

|   |     | 6.4.2 Class-C Matching Design                     |

|   |     | 6.4.3 Bilateral Effect                            |

|   | 6.5 | Validation                                        |

|   | 6.6 | Conclusion                                        |

| 7              | Conclusion 124                                                                                    |                          |     |

|----------------|---------------------------------------------------------------------------------------------------|--------------------------|-----|

|                | 7.1                                                                                               | Summary of Contributions | 125 |

|                | 7.2 Future Work                                                                                   |                          | 126 |

|                | 7.3                                                                                               | List of Publications     | 128 |

| References 12  |                                                                                                   | 129                      |     |

| APPENDICES 130 |                                                                                                   | 136                      |     |

| Α              | A Effect of Nonlinear Input Capacitance on AM/AM and AM/PM 137                                    |                          | 137 |

| в              | B Frequency Dispersion Effect of Impedance Inverter on AM/AM and AM/PM of a Doherty Amplifier 140 |                          |     |

# List of Tables

| 2.1 | Doherty power amplifier benchmarks                                       | 37  |

|-----|--------------------------------------------------------------------------|-----|

| 3.1 | 3-Way conventional and modified DPA design parameters                    | 51  |

| 3.2 | Benchmarks of DPAs with extended bandwidth/BO efficiency $\ldots \ldots$ | 61  |

| 4.1 | AM/AM and AM/PM distortions due to the nonlinear $C_{gs}$                | 68  |

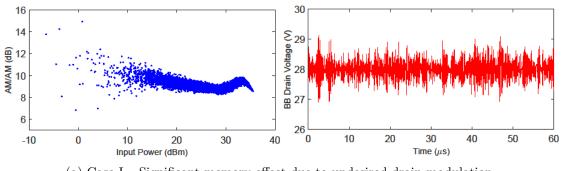

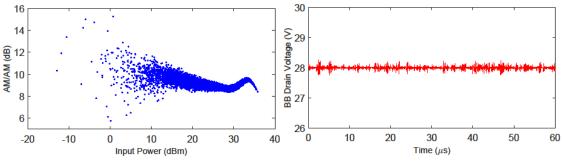

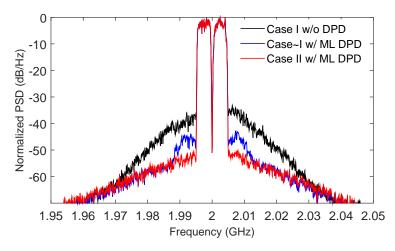

| 4.2 | Summary of the simulation results for the two DPA cases                  | 89  |

| 5.1 | Example of WeDPA modes based on class B/J theory                         | 98  |

| 5.2 | Benchmarks of Broadband DPAs                                             | 110 |

| 6.1 | Comparison of published DPA literature.                                  | 121 |

# List of Figures

| 1.1  | Characteristics of a 10 MHz long term evolution (LTE) signal                                                         | 2  |

|------|----------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Drain efficiency of an ideal class-B power amplifier vs. power back-off                                              | 2  |

| 1.3  | Three options for carrier aggregation                                                                                | 3  |

| 2.1  | Ideal FET model                                                                                                      | 8  |

| 2.2  | DC characteristics of an ideal transistor.                                                                           | 8  |

| 2.3  | A generic transistor large-signal model                                                                              | 9  |

| 2.4  | Drain current characteristics of a typical LDMOS and GaN transistor                                                  | 11 |

| 2.5  | Simplified envelope tracking block diagram.                                                                          | 13 |

| 2.6  | Optimal load impedance for ideal load modulation as well as the practical implementation                             | 14 |

| 2.7  | Conceptual representation of load modulation through Doherty technique.                                              | 15 |

| 2.8  | Final schematic representation of the DPA                                                                            | 16 |

| 2.9  | Fundamental current and voltage profiles of transistors in the classical DPA.                                        | 18 |

| 2.10 | Impedance and admittance profiles of the main and peaking transistors in a DPA                                       | 19 |

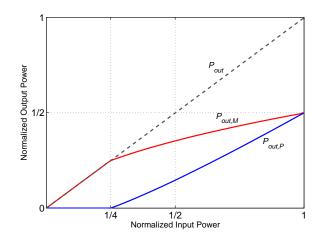

| 2.11 | Output power profiles of each cell as well as the total power of the DPA.                                            | 20 |

| 2.12 | The efficiency profile of the classical DPA.                                                                         | 22 |

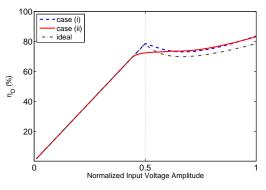

| 2.13 | DPA characteristic profiles considering the soft turn-on effect of the peaking device for two class-C biasing cases. | 24 |

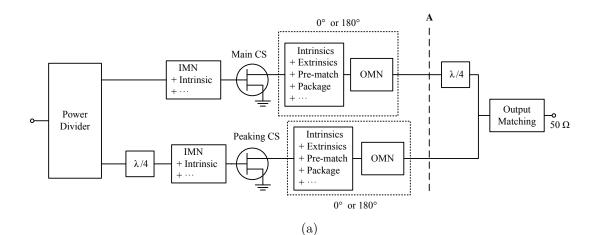

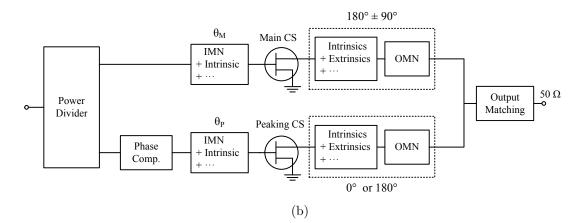

| 2.14 | Generic DPA block diagram with actual transistors                                                                    | 25 |

|      |                                                                                                                      |    |

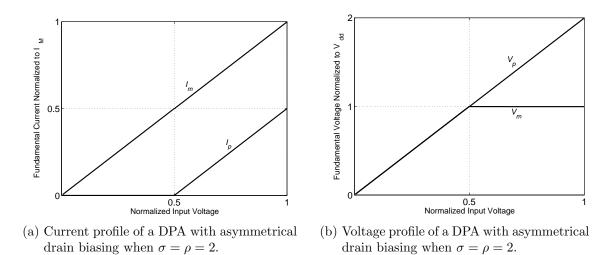

| 2.15 | Characteristic profiles of an asymmetrical DPA.                                                                                                                   | 28 |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 2.16 | Current and voltage profiles of an asymmetrically-biased DPA                                                                                                      |    |  |

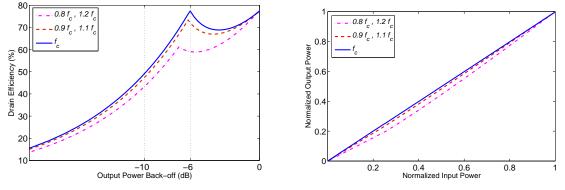

| 2.17 | Frequency characteristics of the classical DPA                                                                                                                    |    |  |

| 2.18 | Drain efficiency of an asymmetric DPA vs. bandwidth                                                                                                               | 32 |  |

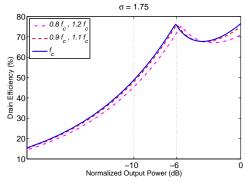

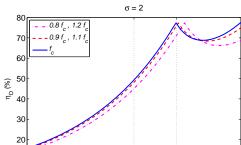

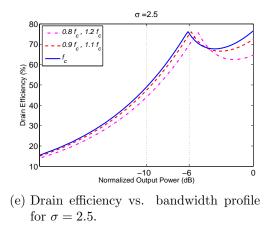

| 2.19 | Efficiency-bandwidth characteristics for different $\sigma$ values                                                                                                | 34 |  |

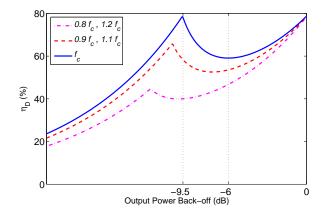

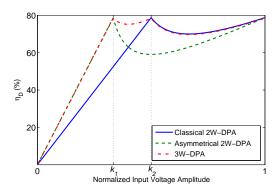

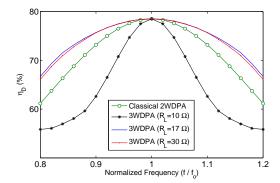

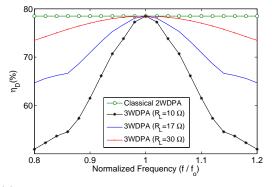

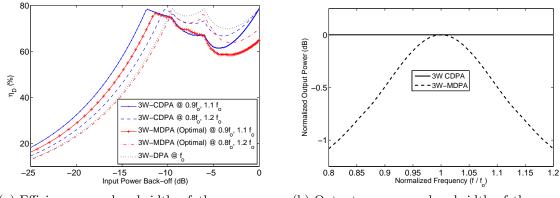

| 3.1  | Drain efficiency comparison of three Doherty topologies.                                                                                                          | 39 |  |

| 3.2  | Simple schematic of a 3W-CDPA                                                                                                                                     | 39 |  |

| 3.3  | Characteristic profiles of a 3W-CDPA.                                                                                                                             | 43 |  |

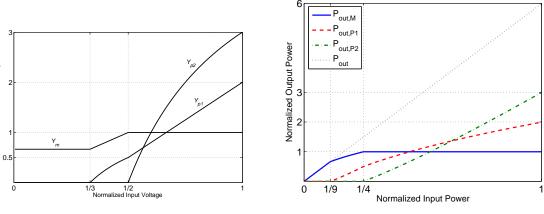

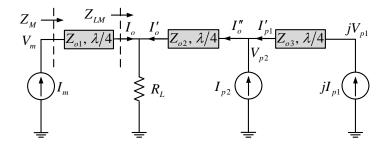

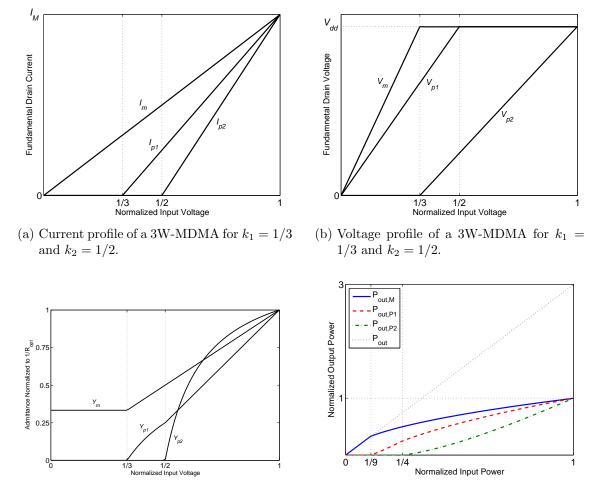

| 3.4  | Simple schematic of a 3W-MDPA                                                                                                                                     | 46 |  |

| 3.5  | Characteristic profiles of a 3W-MDPA.                                                                                                                             | 49 |  |

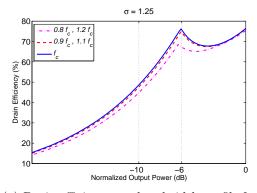

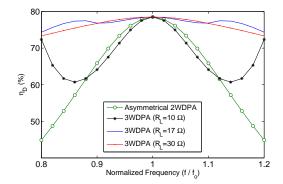

| 3.6  | Drain efficiency bandwidth comparison of the 3W-MDPA with three different load resistances versus classical and asymmetric 2W-DPA, for $R_{opt} = 35 \Omega$ . 53 |    |  |

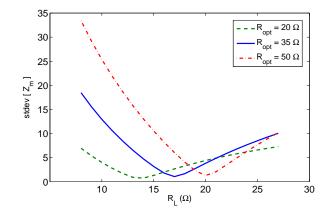

| 3.7  | The standard deviation of the main transistor impedance vs. the load resistance for different $R_{opt}$ values                                                    |    |  |

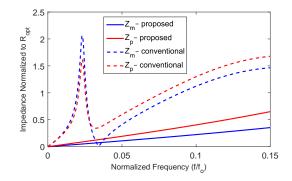

| 3.8  | Comparison between frequency characteristics of the conventional and mod-<br>ified architectures.                                                                 | 55 |  |

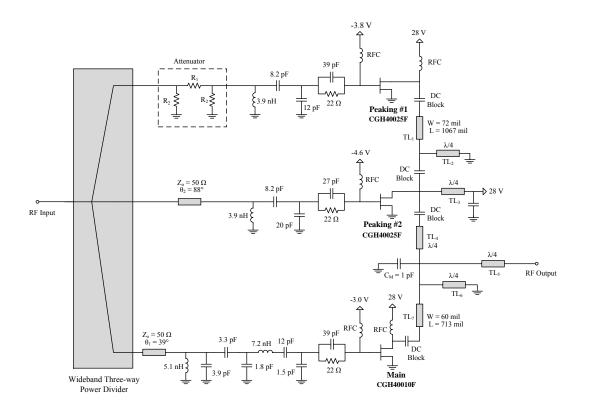

| 3.9  | Complete schematic of the 3W-DPA.                                                                                                                                 | 56 |  |

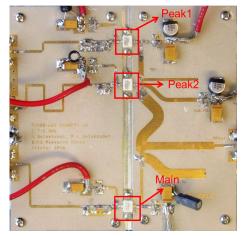

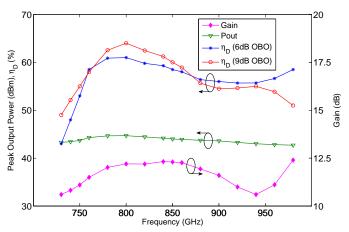

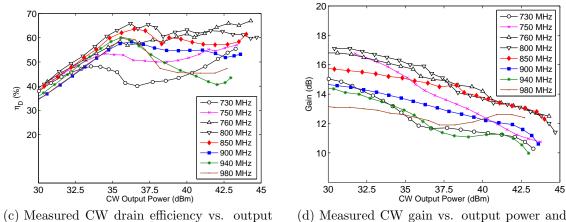

| 3.10 | The fabricated 3W-DPA and its CW measurement results                                                                                                              | 57 |  |

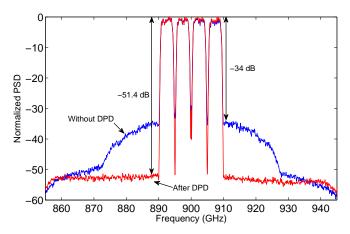

| 3.11 | The output PSD of the 3W-MDPA under modulated test signals                                                                                                        | 58 |  |

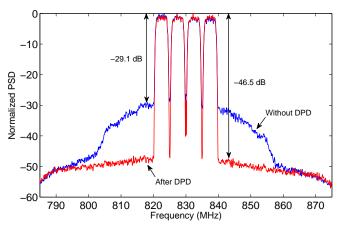

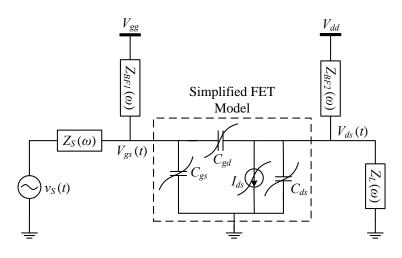

| 3.12 | Measured AM/AM and AM/PM of the wideband 3W-DPA under modu-<br>lated signal                                                                                       | 59 |  |

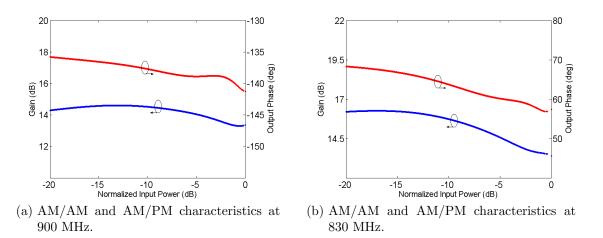

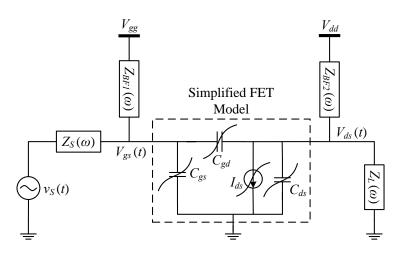

| 4.1  | A simplified FET large-signal model.                                                                                                                              | 64 |  |

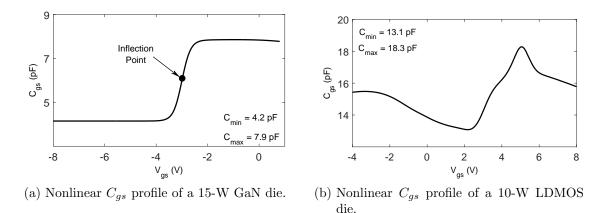

| 4.2  | Nonlinear profile of the gate-source capacitance for GaN and LDMOS tran-<br>sistors                                                                               | 66 |  |

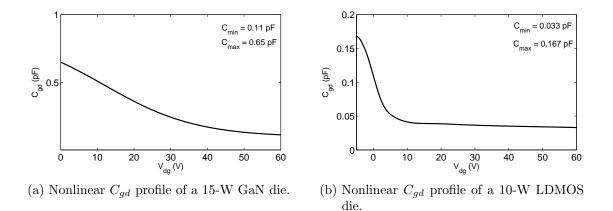

| 4.3  | Nonlinear C-V profile of the gate-drain capacitance for for GaN and LDMOS transistors                                                                             | 68 |  |

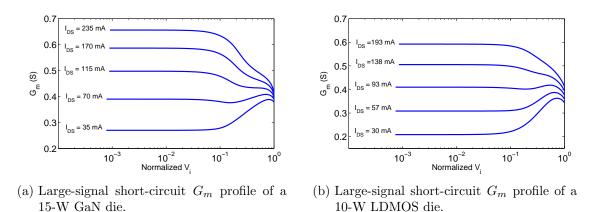

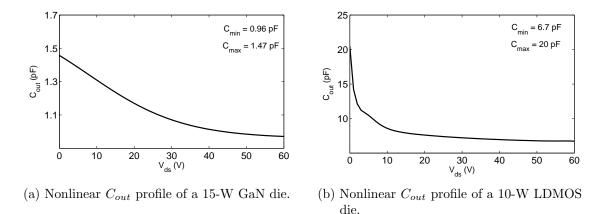

| 4.4  | Large-signal transconductance profile of GaN and LDMOS transistors                                                                                                | 70 |  |

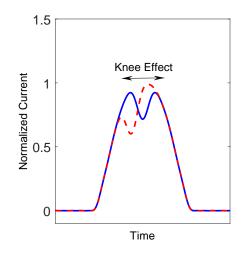

| 4.5  | Drain current source can be approximated by a gate voltage-controlled cur-<br>rent source in parallel with a nonlinear conductance to model the knee effect.      | 71 |  |

| 4.6  | Nonlinear output capacitance profiles of GaN and LDMOS transistors                                                             | 72 |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

| 4.7  | Knee region intrusion when the transistor is terminated with a pure resistive load (solid) and an inductive load (dashed).     | 73 |

| 4.8  | Second harmonic source-pull contours of a class-B biased GaN HEMT at 0.8 GHz.                                                  | 74 |

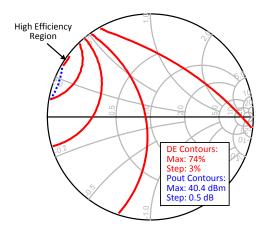

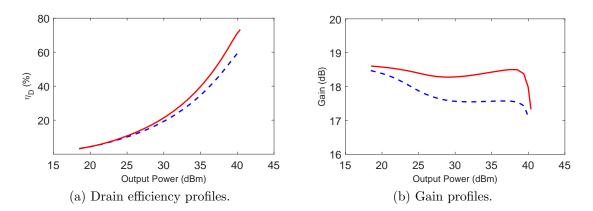

| 4.9  | Efficiency and gain profiles of a class B GaN PA with a good (solid) and a poor (dashed) input second harmonic termination.    | 75 |

| 4.10 | Second harmonic source-pull contours of a class-B biased GaN HEMT at 2 GHz and peak power                                      | 75 |

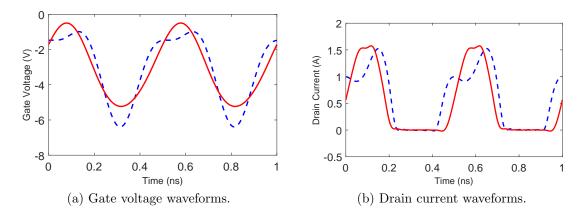

| 4.11 | Waveforms of a class-B GaN PA with a good (solid) and a poor (dashed) input second harmonic termination.                       | 76 |

| 4.12 | Second harmonic source-pull contours of a class-C biased GaN HEMT at 0.8 GHz and PEP.                                          | 77 |

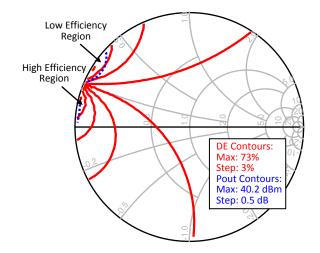

| 4.13 | Efficiency and current profiles of a class C GaN PA with a good (solid) and a poor (dashed) input second harmonic termination  | 77 |

| 4.14 | Second harmonic source-pull contours of a class-C biased GaN HEMT at 2 GHz and PEP.                                            | 78 |

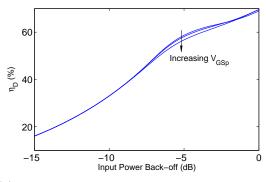

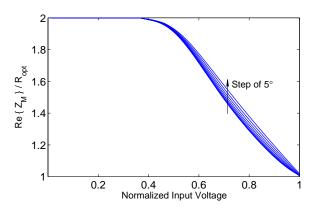

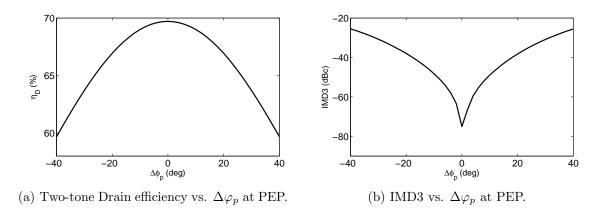

| 4.15 | Two-tone performance degradation vs. peaking gate biasing                                                                      | 80 |

| 4.16 | Load modulation curves for different $\Delta \varphi_p$ values                                                                 | 81 |

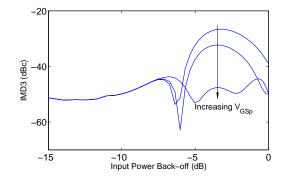

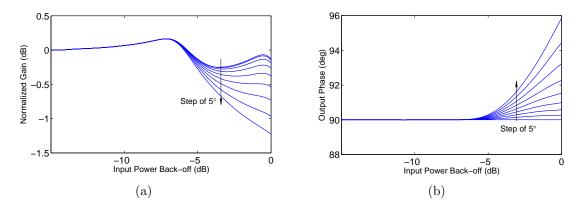

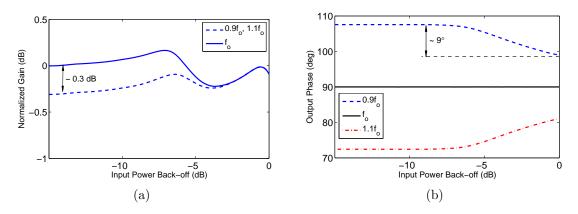

| 4.17 | AM/AM and AM/PM caused by misalignment between the main and peak-<br>ing paths.                                                | 81 |

| 4.18 | Performance degradation due to the misalignment between the main and peaking paths obtained from a two-tone simulation at PEP. | 82 |

| 4.19 | AM/AM and AM/PM caused by frequency dispersion of the quarter-wave impedance inverter.                                         | 83 |

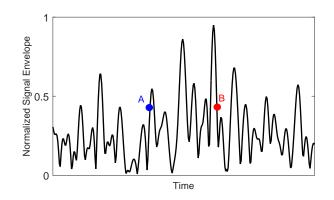

| 4.20 | Envelope waveform of a typical modulated signal.                                                                               | 83 |

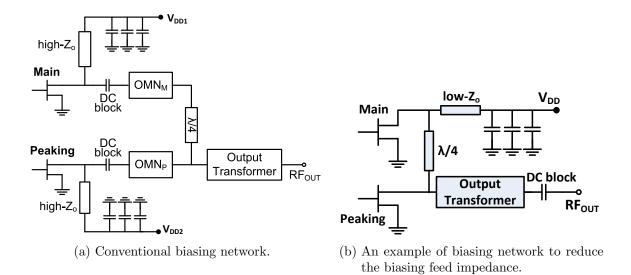

| 4.21 | Illustration of conventional vs. recommended biasing networks for DPAs                                                         | 87 |

| 4.22 | Biasing feed of a conventional vs. proposed DPA.                                                                               | 87 |

| 4.23 | Simulated AM/AM responses and baseband drain voltages of Case I and II.                                                        | 88 |

| 4.24 | Simulated spectrum of Case I and II with and without memoryless DPD                                                            | 89 |

|      |                                                                                                                                |    |

| 5.1  | Simplified schematic of a conventional DPA.                                                                                                                                                                                                                                                                                                                                   | 91   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.2  | Fundamental components of drain current, voltage, and impedance of the main and peaking transistor in a conventional DPA                                                                                                                                                                                                                                                      | 92   |

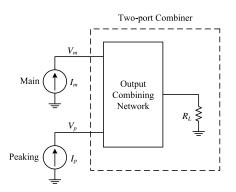

| 5.3  | Generic illustration of a DPA with ideal current sources and a lossless com-<br>bining network. Device output parasitics are embedded in the output com-<br>bining network.                                                                                                                                                                                                   | 93   |

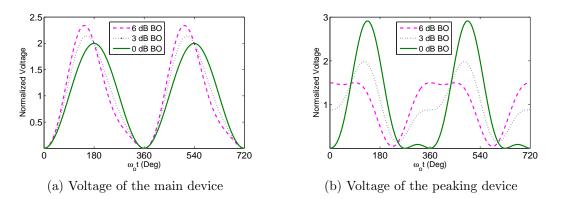

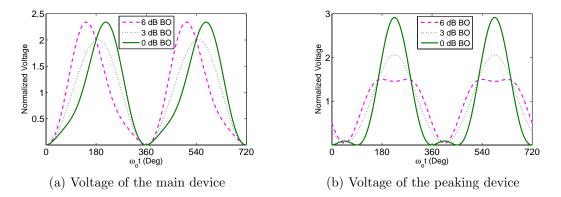

| 5.4  | Theoretical voltage waveforms of the (a) main , and (b) peaking transistors for $\{1,0,-1\}$ .                                                                                                                                                                                                                                                                                | 97   |

| 5.5  | Theoretical voltage waveforms of the (a) main , and (b) peaking transistors for $\{0.5, -0.5, 1\}$ .                                                                                                                                                                                                                                                                          | 97   |

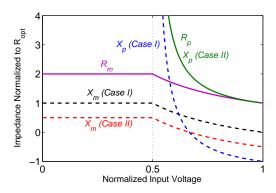

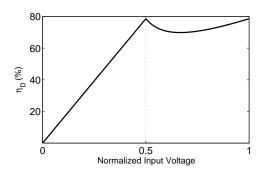

| 5.6  | Fundamental impedance profiles of the main and peaking devices for Cases I and II.                                                                                                                                                                                                                                                                                            | 99   |

| 5.7  | Efficiency profile of the WeDPA                                                                                                                                                                                                                                                                                                                                               | 99   |

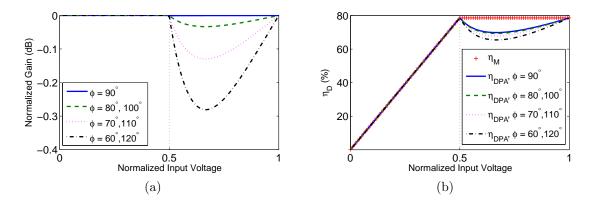

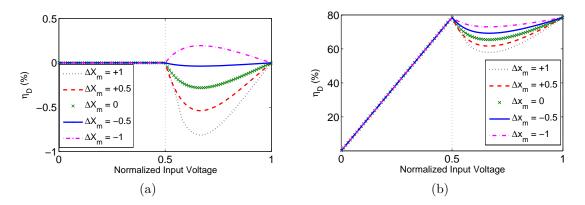

| 5.8  | (a) Gain and (b) efficiency profiles for $\{0,0,0\}$ mode and different $\phi$ values.<br>$\eta_M$ and $\eta_{DPA}$ represent the main transistor's and overall efficiency, respectively                                                                                                                                                                                      | .100 |

| 5.9  | (a) Gain and (b) efficiency profiles for different $\Delta x_m$ values and $\phi = 60^{\circ}$ .                                                                                                                                                                                                                                                                              | 100  |

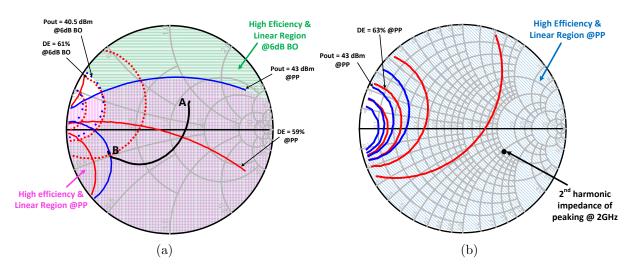

| 5.10 | Second harmonic load-pull efficiency (red) and power (blue) contours at the package plane for the (a) main device at BO (dotted lines) and PP (solid lines), and (b) peaking device at PP at $f_o=2$ GHz (50 $\Omega$ impedance system). The realized impedance profiles at second harmonic are shown in black. The fficiency and power steps are 5% and 0.5 dB, respectively | 102  |

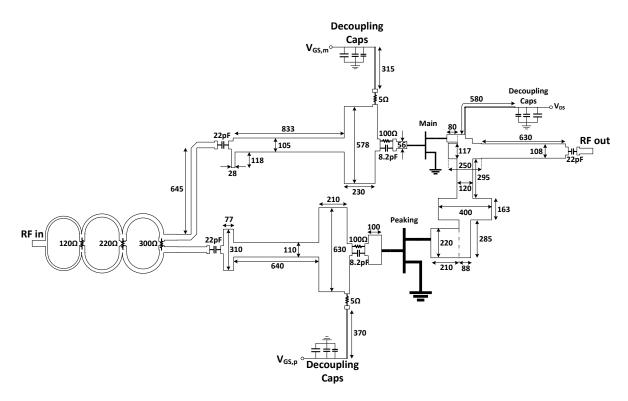

| 5.11 | Schematic of the designed WeDPA. All dimensions are in mils (0.001 inch). The substrate is RT 6035HTC ( $\epsilon_r = 3.6, h = 20$ mil) from Rogers                                                                                                                                                                                                                           | 103  |

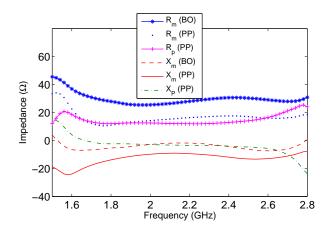

| 5.12 | Simulated impedances presented to the main and peaking devices at back-off (BO) and peak power (PP) levels                                                                                                                                                                                                                                                                    | 105  |

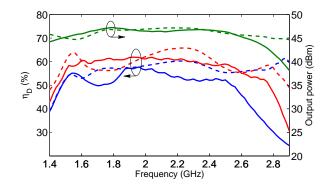

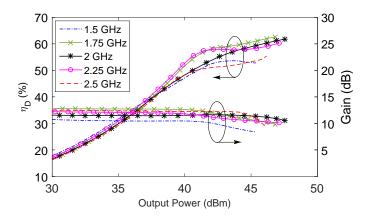

| 5.13 | Simulated efficiency at 6-dB back-off (blue) and peak power (red) levels and peak output power (green) with (solid line) and without (dashed line) input matching networks.                                                                                                                                                                                                   | 105  |

| 5.14 | Simulated CW drain efficiency and gain versus output power at various frequency points.                                                                                                                                                                                                                                                                                       | 106  |

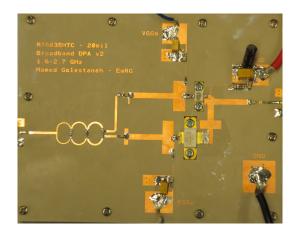

| 5.15 | Photograph of the fabricated WeDPA.                                                                                                                                                                                                                                                                                                                                           | 107  |

| 5.16 | Measured CW performance of the WeDPA versus frequency.                                                                                                                                                                                                                                                                                                                        | 108  |

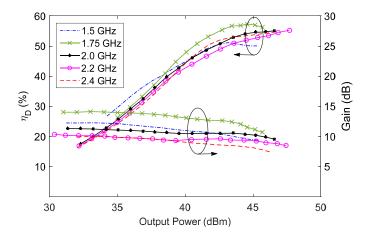

| 5.17 | Measured CW drain efficiency and gain versus output power at various fre-<br>quency points                                                                             | 108 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

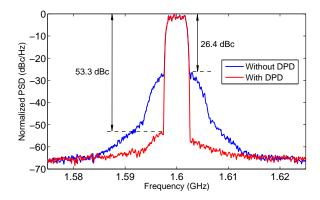

| 5.18 | Normalized output PSD of the WeDPA with and without memoryless DPD when driven with 5 MHz WCDMA signal at 1.6 GHz                                                      | 109 |

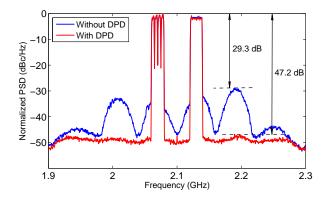

| 5.19 | Normalized output PSD of the WeDPA with and without DPD when driven with an 80 MHz modulated signal at 2.1 GHz.                                                        | 109 |

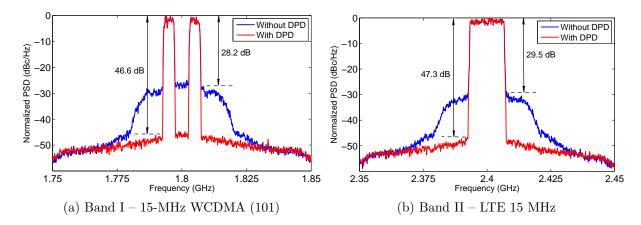

| 5.20 | Normalized output PSD of the WeDPA with and without DPD when driven with a dual-band modulated signal.                                                                 | 110 |

| 6.1  | Fundamental current and voltage profiles in the classical DPA                                                                                                          | 113 |

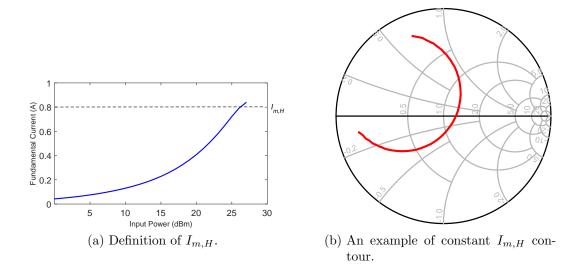

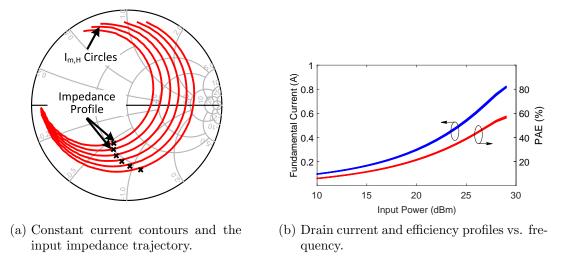

| 6.2  | Illustration of $I_{m,H}$ contours                                                                                                                                     | 115 |

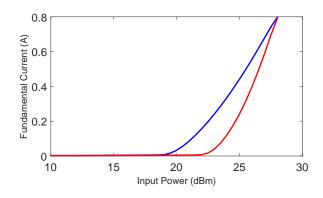

| 6.3  | An example of input nonlinearity implications in GaN DPAs. Two different fundamental impedances can create similar currents at PEP but have dissimilar turn-on points. | 115 |

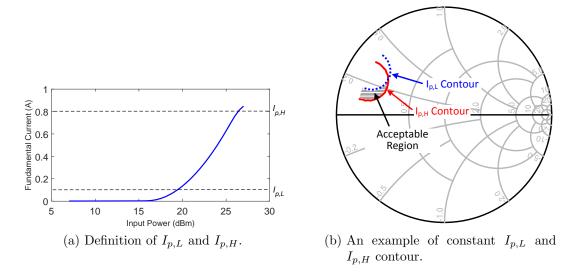

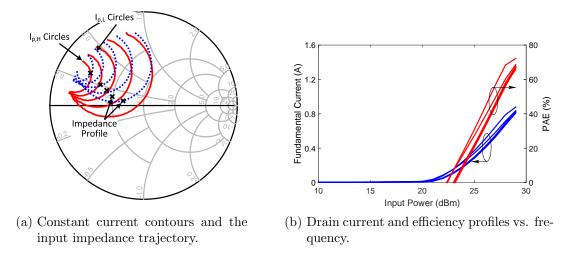

| 6.4  | Illustration of $I_{p,L}$ and $I_{p,H}$ contours.                                                                                                                      | 116 |

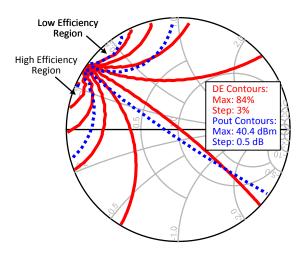

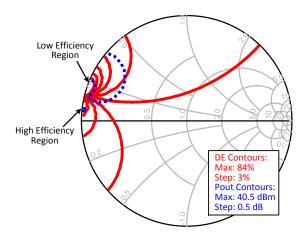

| 6.5  | An example of IMN design for main PA using constant current contours.                                                                                                  | 118 |

| 6.6  | An example of IMN design for main PA using constant current contours.                                                                                                  | 119 |

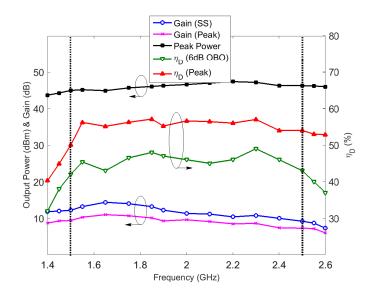

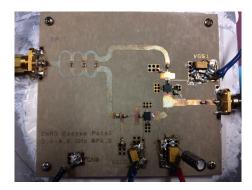

| 6.7  | Fabricated DPA using the proposed methodology [1]                                                                                                                      | 120 |

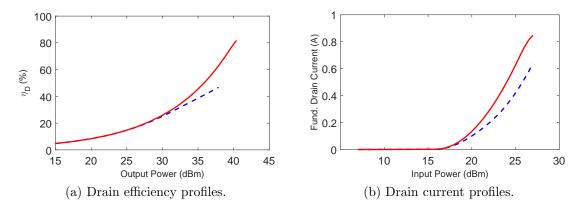

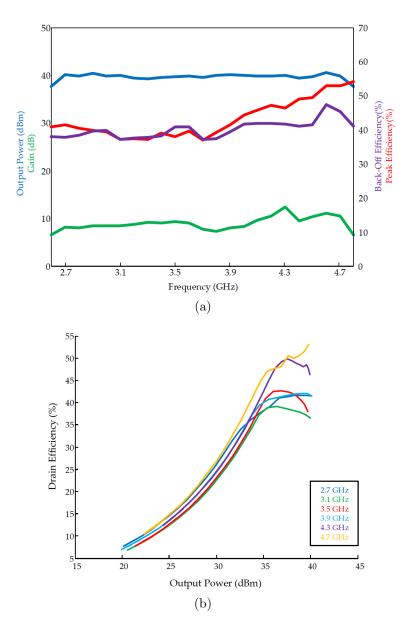

| 6.8  | Measured CW performance of the DPA versus (a) frequency, and (b) output power [1].                                                                                     | 122 |

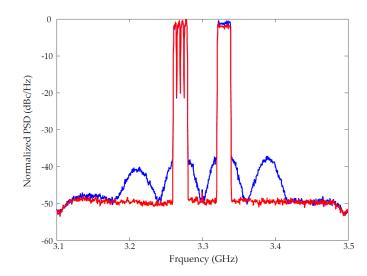

| 6.9  | Measured output spectrum of the DPA under a 80-MHz modulated signal at 3.3 GHz before (blue) and after (red) DPD [1]                                                   | 123 |

| A.1  | A simplified equivalent circuit of a PA                                                                                                                                | 138 |

# List of Abbreviations

| 2W-DPA           | Two-Way Doherty power amplifier                |

|------------------|------------------------------------------------|

| 3G               | Third generation                               |

| 3W-CDPA          | Conventional three-Way Doherty power amplifier |

| 3W-DPA           | Three-Way Doherty power amplifier              |

| 3W-MDPA          | Modified three-Way Doherty power amplifier     |

| $4\mathrm{G}$    | Fourth generation                              |

| $5\mathrm{G}$    | Fifth generation                               |

| AC               | Alternating current                            |

| ACLR             | Adjacent channel leakage ratio                 |

| ADS              | Advanced design system                         |

| AM/AM            | Amplitude to amplitude modulation              |

| $\mathrm{AM/PM}$ | Amplitude to phase modulation                  |

| CMOS             | Complementary metal-oxide-semiconductor        |

| CW               | Continuous wave                                |

| DC               | Direct current                                 |

| DE               | Drain efficiency                               |

| DLM              | Dynamic load modulation                        |

|                  |                                                |

| DPA   | Doherty power amplifier                      |

|-------|----------------------------------------------|

| DPD   | Digital pre-distortion                       |

| ET    | Envelope tracking                            |

| EVM   | Error vector magnitude                       |

| FBW   | fractional bandwidth                         |

| FET   | Field effect transistor                      |

| GaAs  | Gallium arsenide                             |

| GaN   | Gallium nitride                              |

| HBT   | Heterojunction bipolar transistor            |

| HEMT  | High electron mobility transistor            |

| IMN   | Input Matching Network                       |

| ITR   | Impedance transformation ratio               |

| LDMOS | Laterally diffused metal oxide semiconductor |

| LTE   | Long term evolution                          |

| MEMS  | Micro-electro-mechanical systems             |

| MMIC  | Monolithic microwave integrated circuit      |

| OFDM  | Orthogonal frequency division multiplexing   |

| PA    | Power amplifier                              |

| PAE   | Power added efficiency                       |

| PAPR  | Peak-to-average power ratio                  |

| PDF   | Probability density function                 |

| RF    | Radio frequency                              |

| SOI   | Silicon on insulator                         |

|       |                                              |

| SRFT  | Simplified real frequency technique             |

|-------|-------------------------------------------------|

| VCCS  | Voltage-controlled current source               |

| VCVS  | Voltage-controlled voltage source               |

| WCDMA | Wideband code division multiple access          |

| WeDPA | Waveform-engineered Doherty power amplifier     |

| WiMAX | Worldwide Interoperability for Microwave Access |

## Chapter 1

## Introduction

### 1.1 Motivation

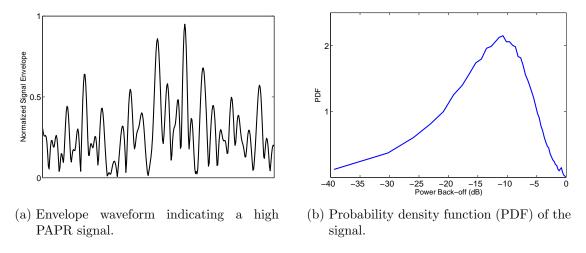

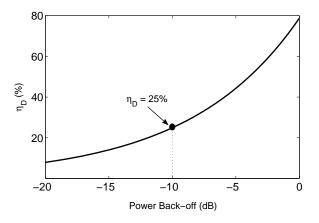

The growing demand for multimedia services via wireless communications with higher throughput necessitates modern wireless networks to support spectrally-efficient modulation schemes and wideband signals. For instance, emerging 4G standards employ multi-carrier multiplexing techniques such as orthogonal frequency division multiplexing (OFDM) with overlapping carriers to optimally use the spectrum. This, in turn, has led to large variation in the envelope of the signal waveform, namely, characterized as peakto-average power ratio (PAPR). This signal characteristic significantly increases the design complexity of the underlying transmitters, particularly the constituent radio frequency power amplifiers (RF PAs) to be deployed in modern wireless infrastructure. On the one hand, the PA is required to linearly amplify the input signal so as to maintain signal quality and minimize out-of-band emissions in adjacent channels, and thus it must be backed off from the nominal output power. On the other hand, statistics suggest that the signal is mostly transmitted at much lower power levels (see Figure 1.1), meaning that the PA operates at its inefficient region most of the time. Figure 1.2 illustrates the drain efficiency of an ideal class-B PA, as a function of the power back-off. It shows that, for a signal with PAPR = 10 dB, for example, the instantaneous drain efficiency is most often around 25% (53.5% lower than the peak efficiency), which substantially degrades the average efficiency of the PA.

Furthermore, upcoming networks are expected to handle legacy communication standards. This calls for multi-standard radio systems that are capable of operating over a broad range of carrier frequencies and of concurrently processing various signals encoded

Figure 1.1: Characteristics of a 10 MHz long term evolution (LTE) signal.

Figure 1.2: Drain efficiency of an ideal class-B power amplifier vs. power back-off

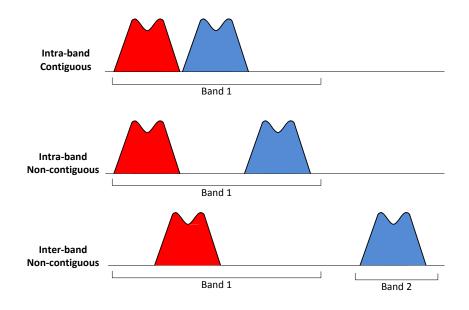

according to dissimilar standards. On top of that, communication signals required by the 3GPP specifications for Long Term Evolution Advanced (LTE-A) will have to utilize carrier aggregation to meet the need for transmission bandwidth. Carrier aggregation refers to the use of more than one spectrum portion to deploy multiple component carriers in order to obtain aggregated channels of wider transmission bandwidth (up to 100 MHz). Figure 1.3 illustrates the three carrier aggregation scenarios envisaged: (i) intra-band contiguous carrier aggregation (contiguous carrier aggregated in the same operating band), (ii) intra-band non-contiguous carrier aggregation (non-contiguous carriers)

Figure 1.3: Three options for carrier aggregation.

aggregated in the same operating band) and (iii) inter-band carrier aggregation (carrier aggregation of component carriers in different operating bands which may be contiguous or non-contiguous within each band). These scenarios impose additional challenge for designing high efficiency linear PAs. In fact, a single RF PA is expected to efficiently amplify multi-band high-PAPR signals concurrently. In addition, the same RF PA must comply with the linearity requirements imposed by wireless standards.

In conclusion, despite all the advantages provided by the the modern wireless standards, more challenges are also introduced in designing RF PAs, in terms of linearity, power efficiency, and fractional bandwidth (FBW), which are yet to be addressed.

### 1.2 Thesis Objectives

To tackle the challenges discussed in Section 1.1, various efficiency enhancement techniques were proposed in the literature, among which Doherty power amplifier (DPA) has gained continued interest in recent years. Although primarily employed for narrowband amplification, the DPA has also shown potential for broadband transmitters. Nevertheless, few publications have tackled concurrent amplification of multi-band signals. This limits the application of such wideband or multi-band DPAs for carrier aggregated signals, such as those used in LTE-A.

This thesis is thus focused on DPAs with extended FBW and enhanced linearity for base-station applications, including both theoretical analysis and implementation aspects. The objectives of the thesis are enumerated below:

- 1. Study of bandwidth limitation in two- and three-way DPAs. The analysis is initially based on an ideal transistor model and is later extended to include the transistor non-idealities.

- 2. Developing a three-way DPA (3W-DPA) with extended FBW (~30%), suitable for efficient amplification of signals with PAPRs up to 12 dB. Two distinct architectures, i.e., conventional and modified DPAs are analyzed in terms of FBW capability. An approach is also devised to compensate for the device parasitics. Finally, the theoretical analyses are validated by developing a proof-of-concept prototype.

- 3. Analysis of static and dynamic sources of distortion in broadband DPAs and investigation of techniques to minimize/mitigate them. This study provides guidelines for designing broadband DPAs with enhanced linearity and linearizability when driven with carrier-aggregated signals.

- 4. Developing a waveform engineering approach to enhance the bandwidth of the output combiner in 2W-DPAs far beyond the conventional bandwidth extension techniques proposed in the literature (i.e. more than 50%) and with minimum linearity compromise. This approach combined with guidelines from 3, enables efficient amplification of inter-band carrier-aggregated signals with arbitrary carrier spacings across the bandwidth.

- 5. Developing a systematic approach to designing input matching networks for DPAs based on the linearity analysis conducted in 3. While the input matching design problem has not been addressed in literature, the proposed design technique enables the DPA to reach the full potential FBW of the output combiner obtained in item 4, with minimum compromise in linearity/efficiency.

The power, bandwidth, and linearity requirements of the DPAs in this thesis for CA signal transmission are as follows:

- Average output power > 1 W under modulated signals with PAPR of 6–12 dB

- FBW > 50%

- Adjacent channel leakage ratio (ACLR) < -45 dB

- Error vector magnitude (EVM) < 5%.

Note that the linearity specifications must be met after applying an existing linearizer [e.g., digital pre-distortion (DPD)] to the DPA.

#### **1.3** Thesis Outline

This thesis is organized as follows: Chapter 2 overviews some of the existing efficiency enhancement techniques, in which state-of-the-art DPAs are particularly discussed. Bandwidth analysis of DPAs and asymmetrically-biased DPAs are presented in the light of recent publications.

Chapter 3 presents novel analysis and design methodologies of three-way Doherty architectures devised to improve efficiency over a broad bandwidth and back-off range. The efficiency-bandwidth capability of these topologies is also compared. Based on the presented analysis, a proof-of-concept prototype was designed and fabricated with excellent efficiency improvement across 29% fractional bandwidth over a wide back-off range (9– 10 dB).

Chapter 4 investigates static and dynamic sources of distortion in DPAs. The static nonlinearities on device and circuit level are detailed and how different sources contribute to the overall nonlinearity. Moreover, sources of memory effects are discussed along with techniques to minimize/mitigate them. The ultimate goal of the chapter is to provide design guidelines to ensure linearizability of a DPA under different carrier-aggregation scenarios.

Chapter 5 proposes a novel approach for designing ultrawideband output combiners for DPAs using the concept of waveform engineering. Theoretical analysis as well as practical considerations are detailed. Based on the proposed approach, a broadband linearity-enhanced 2W-DPA is designed and fabricated with 50% fractional bandwidth. The overall

DPA's bandwidth was limited due to the challenges of designing broadband input matching networks.

Chapter 6 presents a novel methodology to design input matching networks for broadband DPAs, taking advantage of the linearity study conducted in Chapter 4. The proposed technique is validated through simulation and measurement results.

Finally, Chapter 7 concludes the thesis by summarizing the contributions of this work, as well as suggesting potential research directions for future.

## Chapter 2

# High Efficiency Multi-Standard RF Transmitters

### 2.1 Introduction

This chapter begins with describing an ideal transistor model used throughout this proposal for RF amplifier analysis. This is followed by introducing typical high power field-effect transistor (FET) technologies for base stations and their large-signal models. The rest of the chapter expounds on prevalent techniques for improving the efficiency of RF transmitters and their suitability for multi-standard radio. The main focus of this chapter is on Doherty technique and its usability for broadband/multiband operation in the light of recent publications. It also presents an analysis of the conventional two-way DPA to develop the governing equations. These equations provide a better understanding of the load modulation mechanism which is required to analyze more advanced DPA architectures, such as asymmetrically biased DPAs where the drains of the main and peaking transistors are biased differently. Finally, bandwidth analysis of the two-way DPAs are presented in light of recent publications.

### 2.2 Ideal FET Model

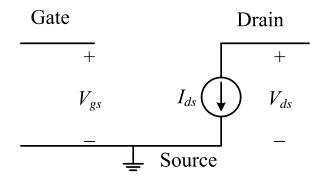

FET devices, the currently dominant transistors in base station PAs, in the most ideal case consist of a linear voltage-controlled current source (VCCS) when operating in saturation region in common source configuration, as shown in Figure 2.1. This means that the

Figure 2.1: Ideal FET model.

Figure 2.2: DC characteristics of an ideal transistor.

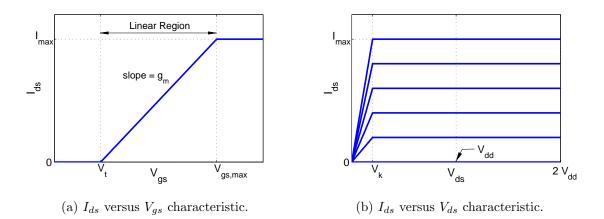

input voltage swing,  $V_{gs}$ , is unilaterally converted to the drain (output) current,  $I_{ds}$ , by a constant bias-dependent transconductance,  $g_m$ . The output current is in turn transformed into the output voltage through a finite load resistance. Note that unlike a small-signal amplifier, the transistor may move to the cut-off or knee region back and forth along a loadline, depending on the chosen class of operation. Figures 2.2(a) and (b) illustrate the profile of the instantaneous  $I_{ds}$  as a function of  $V_{gs}$  and  $V_{ds}$ , respectively. As can be seen, linear amplification occurs when  $V_t < V_{gs} < V_{gs,max}$  and  $V_k < V_{ds} < 2V_{dd}$ , where  $V_t$  and  $V_k$  represent the threshold and knee voltage, respectively, and  $V_{dd}$  is the drain supply voltage.

As can be seen, the model includes no parasitic elements, and thus the input and output impedances are infinity. Furthermore, the ideal model does not consider the feedback or Miller effect,  $g_m$  nonlinearity as a function of  $V_{qs}$ , channel length modulation, and transistor

Figure 2.3: A generic transistor large-signal model.

breakdown effects. However, this model can be used to illustrate the harmonic components of the current at the biasing point, the nonlinearities associated with the class of operation (such as the soft turn-on effect of a class-C-biased transistor) and the knee effect.

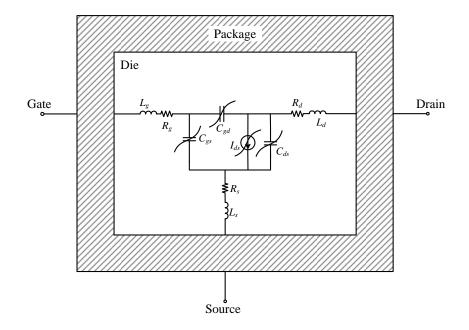

### 2.3 Device Technologies

Even though the ideal FET model is often very helpful for theoretical analysis purposes, it has to be replaced by an accurate large-signal model for the device, in a practical design. The base-station power amplifier market is dominated by two major technologies, i.e., laterally diffused metal oxide semiconductor (LDMOS) and GaN high electron mobility transistor (HEMT) devices. A generic large-signal bare die model that applies to both technologies is depicted in Figure 2.3. As can be seen, other than the nonlinear drain current source,  $I_{ds}(V_{gs}, V_{ds})$ , the model includes some parasitics, which are often divided into intrinsic and extrinsic elements. Intrinsic elements, including  $C_{gs}$ ,  $C_{gd}$ , and  $C_{ds}$  are associated with the device active channel, where the fundamental transistor action occurs, and are nonlinear functions of "intrinsic" gate/drain terminal voltage in general. The extrinsic components, on the other hand, are bias-independent passives that connect the active element to the outside world, including manifolds, bond-pads, bondwires, etc. [2]. Commercial transistors are often embedded in a package, as shown in Figure 2.3 for the sake of protection and better thermal dissipation. The package introduces additional parasitics, usually modelled by EM simulations. Sometimes the package includes other integrated passives, known as pre-matching circuitry, to facilitate impedance matching over a certain frequency range.

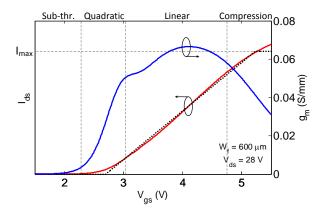

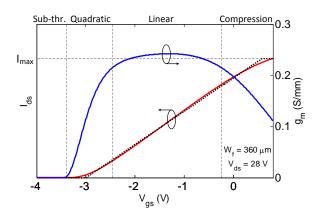

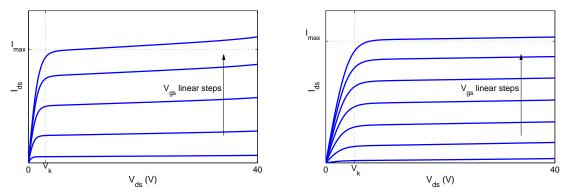

Figure 2.4 illustrates the drain current of typical LDMOS and GaN transistors, as compared with ideal characteristics shown in Figure 2.2. It is observed that both devices deviate from the ideal case, due to the gradual turn-on (expansion) and gradual saturation (compression). Figures 2.4(a) and (b) also provide a better understanding of the nonlinear I-V characteristics of the transistors by illustrating the small-signal  $g_m$  profile as a function of  $V_{gs}$ . More discussions on the nonlinear profile of the intrinsics elements and their impacts on the PA performance will be presented in Chapter 4.

### 2.4 Efficiency Enhancement

The devices introduced in Section 2.3 serve as the core of the RF PA. As illustrated in Chapter 1, the average efficiency of a linear power amplifier (operating in class B or AB) when employed in modern radio transmitters is very low due to the high PAPR of the signals being used in those systems. Various techniques has thus been proposed in the literature to enhance the efficiency of the amplifier at power levels backed off from the peak value.

The basic idea of improving the back-off efficiency arises from the fact that the efficiency of a class-B biased PA is linearly proportional to the ratio of the drain voltage swing of the transistor to the drain supply voltage. Assuming the ideal transistor model described in Section 2.2 and a load impedance,  $R_L$ , the amplitude of the output voltage swing follows Ohm's law, i.e.,

$$V_1 = I_1 \cdot R_L \tag{2.1}$$

where  $I_1$  and  $V_1$  denote the fundamental drain current and voltage components, respectively, and  $R_L$  is the load resistance (at fundamental frequency). Generally,  $R_L$  is selected to achieve the optimum performance at the peak power, thus is referred to as the optimum load impedance of the transistor,  $R_{opt}$ . In other words, setting  $R_L = R_{opt}$  results in full rail-to-rail voltage swing at the nominal peak current of the device, meaning that the

(a)  $I_{ds}$  and  $g_m$  vs.  $V_{gs}$  characteristics of an LDMOSFET.

(b)  $I_{ds}$  and  $g_m$  vs.  $V_{gs}$  characteristics of a GaN HEMT.

(d) DC-IV characteristics of GaN HEMT.

Figure 2.4: Drain current characteristics of a typical LDMOS and GaN transistor.

maximum efficiency coincides with the peak output power.  $R_{opt}$  for a particular device is given by,

$$R_{opt} = \frac{(V_{dd} - V_k)^2}{2P_{out,max}}.$$

(2.2)

Eq. (2.2) is the origin of various techniques devised to maximize efficiency at a desired power level. These techniques are broadly divided into two main categories. In the first one, the load resistance  $R_L$  is preserved as the optimum load impedance over the entire power range. In fact, the transistor drain supply voltage is varied as a function of  $P_{out}$ , i.e., proportional to the signal envelope, according to (2.2). These techniques are known as drain supply modulation techniques. Unfortunately, the efficiency improvement is significantly reduced at high back-off levels due to the nonzero knee voltage of the device. Alternatively, one could modulate the effective load impedance of the transistor (also called the load impedance "seen" by the transistor) to maintain the maximum voltage swing and efficiency over a given power range. The latter group are called the load modulation techniques, the most prominent of which is the Doherty architecture. The two groups of techniques will be reviewed in this section.

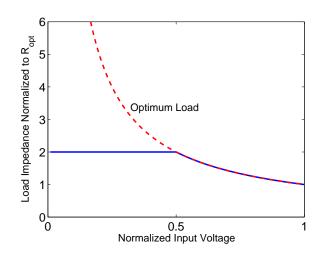

#### 2.4.1 Drain Modulation Technique

As mentioned before, in this technique the drain supply voltage is adjusted as a function of input power to reduce the DC power consumption at back-off levels. There are various architectures based on drain modulation technique. Envelope elimination and restoration (EER) transmitter combines high-efficiency but nonlinear RF PAs with a linear envelope amplifier to realize a highly efficient linear transmitter [3]. In this transmitter, the envelope is eliminated from the RF signal fed into the PA, and then restored by drain modulation of the PA. Therefore, the linearity of the systems is directly dependent on the linear operation of the envelope amplifier and the phase alignment between the two paths.

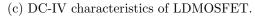

Envelope tracking (ET) system is one of the most widely-used transmitters based on the drain modulation technique. Unlike the EER system, ET employs a linear RF PA, whose drain supply voltage is modulated by the signal envelope to maintain high efficiency in back-off levels, as illustrated in Figure 2.5. Ideally, except for the operation in knee region, the linearity of the transmitter is determined only by the linear PA, which relaxes the design of envelope modulator as compared to the EER system. However, similar to an EER system, the bandwidth and efficiency of the envelope amplifier is critical.

Recent publications on ET, have mainly focused on linearity and efficiency improvement of the envelope modulator for multi-standard transmitters. As the drain supply decreases

Figure 2.5: Simplified envelope tracking block diagram.

at low power levels, the device is more likely to intrude into the knee region which results in significant nonlinearity and memory effects when the system is driven with wideband signals. For instance, authors in [4,5] suggested shaping of the original envelope to avoid the knee region at the expense of decreased power efficiency. Even though ET technique has been recently considered for base-station transmitters [6,7], the application of ET systems are mainly limited to handset applications.

#### 2.4.2 Load Modulation Technique

In the load modulation technique, load impedance of the device is varied as a function of power to enhance the back-off efficiency. Dynamic load modulation (DLM) technique [8] uses electronically tunable output matching network to dynamically modulate the impedance according to the signal envelope, and thus requires load-pull measurements/simulations to determine the optimum impedance trajectory vs. power, and varactors to realize the tunable matching networks. Thus far, variants of DLM technique has been proposed in the literature. For instance, the PA has been implemented in class-E [8,9] or class-J [10] configurations, and has been successfully designed for broadband operation [11]. However, the linearity of the transmitter is a major concern and the technique has not been successfully deployed to amplify modulated signals yet.

Doherty power amplifier (DPA) is one of the most widely-adopted transmitters based on load modulation technique, for both handset and base station applications. A detailed overview of the Doherty technique will be presented in Section 2.5.

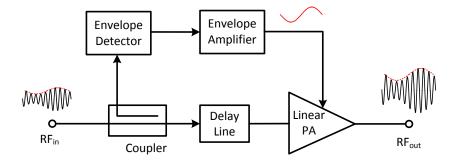

Figure 2.6: Optimal load impedance for ideal load modulation as well as the practical implementation

### 2.5 Doherty Amplifier Technique

#### 2.5.1 Basic Principle

As mentioned before, the load impedance,  $R_L$ , in a class-B is typically selected to simultaneously achieve the peak output power and peak efficiency. Alternatively,  $R_L$  can be increased such that the peak efficiency occurs at a power backed off from the peak value. This would, however, lead to a decreased output power compared to the nominal peak value, since the output current swing would be less than the peak value. Any further increase in input voltage from this point on, would push the transistor into the knee region and cause nonlinearity problems. To maintain the linearity, one can gradually decrease  $R_L$ , inversely proportional to the input voltage (or drain current), so that the maximum swing is maintained without entering into the knee region. For example, Figure 2.6 shows the required impedance profile of the transistor in the most ideal case in order to achieve the maximum efficiency over the entire input voltage range. As can be seen, this impedance approaches infinity as the input drive becomes too small, which is not realizable. In practice, one may fix the impedance below a certain threshold voltage instead of further increasing it. For instance, Figure 2.6 illustrates a case where the load impedance below  $v_{in} = 0.5$  is kept constant at  $2R_{opt}$ . Obviously, it will cause the efficiency to drop for the input drives below this threshold level. This is the core of the DPA idea [12].

An interesting approach to modulate the load impedance of a transistor is to use

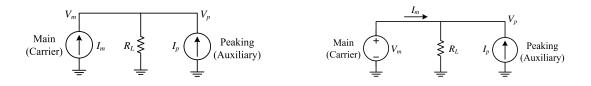

(a) Initial realization of load modulation with two (b) modified circuit with the main VCCS replaced by a VCVS.

Figure 2.7: Conceptual representation of load modulation through Doherty technique.

an "auxiliary" or "peaking" transistor as illustrated in Figure 2.7(a). In this case, the impedance seen by the "main" VCCS can be written as,

$$Z_M = \frac{V_m}{I_m} = R_L \left( 1 + \frac{I_p}{I_m} \right).$$

(2.3)

This equation shows that the load impedance of the main VCCS is controlled by the current supplied by the peaking VCCS. If the peaking VCCS is turned off,  $I_p = 0$ ; then  $Z_M = R_L$ . As  $I_p$  increases in phase with  $I_m$ ,  $Z_M$  also increases, according to (2.3). For instance, if  $I_p = I_m$  the effective impedance seen by the main transistor will be twice the load impedance  $R_L$ . Nevertheless, this approach does not work properly for our purpose, since the impedance of the main transistor increases as a result of the current injected by the peaking transistor. One could combine  $I_p$  in antiphase with  $I_m$  to reduce  $Z_M$  as  $I_p$  grows, but that would lead to power and efficiency loss in the output combiner.

A modification to the previous circuit is depicted in Figure 2.7(b), in which the main amplifier is implemented as a voltage-controlled voltage source (VCVS). The advantage of this topology is that while the voltage across the load (or equivalently linearity) is enforced by the main amplifier, the current supplied by the peaking VCCS controls the admittance seen by main VCVS (or equivalently efficiency) as,

$$Y_M = \frac{I_m}{V_m} = \frac{1}{R_L} - \frac{I_p}{V_m}$$

(2.4)

Since all the transistors behave as a VCCS by nature, one can simply add an impedance inverter (such as a  $\lambda/4$  transmission line) to the output of a transistor to realize the voltage source,  $V_m$ , as shown in Figure 2.8. This architecture is known as the DPA in its classical form [12]. The main device is usually biased in class B or deep AB, whereas the peaking one is biased in class C, as it must be operating only after the main device reaches its maximum voltage swing at the desired power back-off.

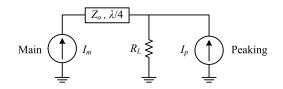

(a) Doherty amplifier representation with ideal (b) Doherty amplifier representation with  $\lambda/4$  impedance inverter.

Figure 2.8: Final schematic representation of the DPA.

#### 2.5.2 Circuit Analysis

For the simplified schematic shown in Figure 2.8, the governing equations of the DPA can be derived in terms of fundamental currents of the main and peaking devices,  $I_m$  and  $I_p$ , and the optimum impedance of the main device at peak power,  $R_{opt}$  [13]. This analysis helps to understand the efficiency enhancement of the DPA structure in a qualitative manner.

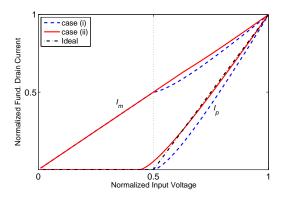

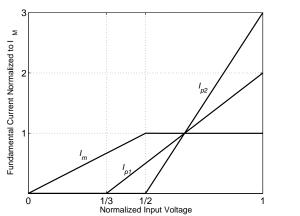

In general, the main and peaking currents are nonlinear functions of both input and output signal amplitudes. To simplify our theoretical analysis, however, it is assumed that the fundamental current profile for the main and peaking transistors are expressed by,

$$I_m(v_{in}) = \begin{cases} v_{in} \cdot I_M & 0 < v_{in} < 1\\ I_M & v_{in} > 1\\ 0 & \text{elsewhere} \end{cases}$$

(2.5)

$$I_p(v_{in}) = \begin{cases} 2(v_{in} - 0.5)I_P & k < v_{in} < 1\\ I_P & v_{in} > 1\\ 0 & \text{elsewhere} \end{cases}$$

(2.6)

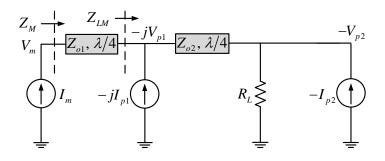

where  $v_{in}$  is the normalized instantaneous input voltage, and  $v_{in} = k$  is the breakpoint at which the peaking current starts to flow (k = 1/2 for the classical DPA). It is assumed that the currents are combined in phase at the output combiner, meaning that the voltage and current of the peaking device must lag by 90°. To analyze the circuit, the ABCD-parameters of the impedance inverter shall be used to relate the current and voltage components at its input and output terminals, i.e.,

$$\begin{pmatrix} V_2 \\ I_2 \end{pmatrix} = \begin{pmatrix} 0 & -jZ_o \\ -j/Z_o & 0 \end{pmatrix} \begin{pmatrix} V_1 \\ I_1 \end{pmatrix}$$

(2.7)

where ports 1 and 2 represent the output of main and peaking devices, respectively.

The following relations can help understand the circuit function:

$$Y_M = \frac{1}{R_L} - \frac{I_p}{V_p}$$

from (2.4) (2.8)

$$V_p = Z_o I_m \qquad \qquad \text{from (2.7)} \tag{2.9}$$

$$Z_M = \frac{V_m}{I_m} = Z_o^2 Y_m = Z_o \left(\frac{Z_o}{R_L} - \frac{I_p}{I_m}\right) \qquad \text{from (2.8) and (2.9)}.$$

(2.10)

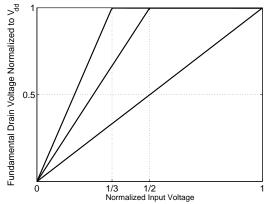

Eq. (2.10) reveals that the impedance seen by the main transistor,  $Z_M$ , is "modulated" as  $I_p$  starts to increase. This provides the desired load modulation of the main transistor to prevent its saturation, yet maintain high efficiency at power back-off. The circuit parameters,  $Z_o$  and  $R_L$ , can be determined in terms of  $R_{opt}$ , which in turn depends on the peak output power, considering (2.9) and (2.10), (i) at low power levels  $(v_{in} < \frac{1}{2})$ , and (ii) at peak power  $(v_{in} = 1)$ . In the low power region,  $I_p = 0$ ; thus,

$$Z_M^L = Z_o^2 / R_L = 2R_{opt} \qquad \text{(low power)} \tag{2.11}$$

where the "L" superscript denotes the quantity evaluated in the low power region. At the peak power, on the other hand, both transistors should see their optimum impedances, i.e.,  $Z_M^F = R_{opt}$ , where "F" superscript represents the impedance of the main transistor at full power. Assuming that both the transistors share the same drain supply voltage, then  $V_m^F = V_p^F = V_{dd}$  at the full power. Hence, one can deduce the circuit parameters,  $R_L$  and  $Z_o$  as

$$Z_o = \frac{V_{dd}}{I_M} = R_{opt} \qquad \qquad \text{from (2.9)} \tag{2.12}$$

$$R_L = \frac{R_{opt}}{2}$$

from (2.11). (2.13)

Moreover, evaluating (2.10) at peak power yields,

$$Z_o\left(\frac{Z_o}{R_L} - \frac{I_P}{I_M}\right) = R_{opt} \tag{2.14}$$

which can be manipulated to give the ratio between the transistors' peak current, i.e.,

$$I_P = I_M. (2.15)$$

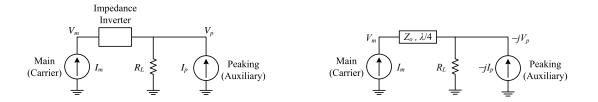

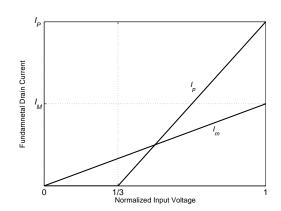

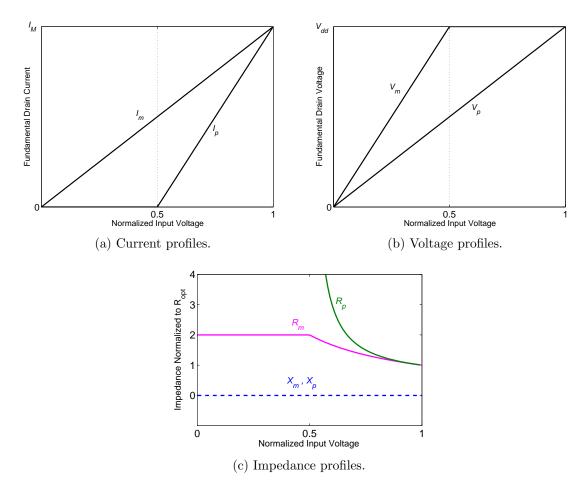

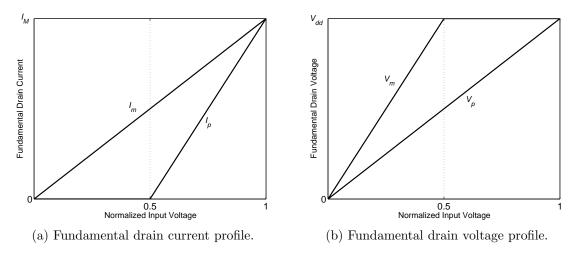

It can be shown that (2.12)-(2.15) are sufficient to fully describe the DPA's behavior. The fundamental current and voltage profiles of the classical DPA is depicted in Figure 2.9.

Figure 2.9: Fundamental current and voltage profiles of transistors in the classical DPA.

Based on the current profiles, one may notice an immediate challenge in realization of a DPA. Since the peaking transistor starts operating at half the maximum input voltage drive, it will not be able to provide the same peak current as the main device  $(I_M)$  if identical devices are used. One solution could be using a larger peaking device [ideally twice as large according to Figure 2.9(a)]. This would, however, lead to a decreased power utilization factor (PUF), since the power delivered by the peaking device is at best half its power capability. Alternatively, one could identical devices and unequally split the input power instead to compensate for the peaking gain shortage [14]. Ideally, the power must be divided with a ratio of 2:1 between the two cells in favor of the peaking amplifier for proper Doherty operation. This will however lead to an overall gain loss of at least  $20 \log(2/3) = 3.5$  dB which may not be acceptable for many cases. It should also be noted the synthesis problem of the peaking devices' current exacerbates when using a real transistor, due to the soft turn-on effect and inherently lower  $g_m$  of the class-C operation as compared to class B.

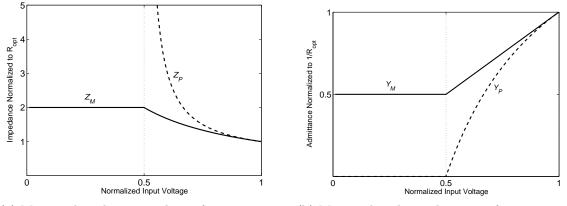

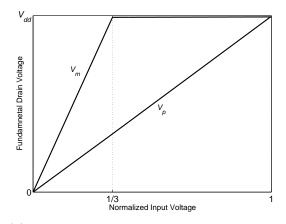

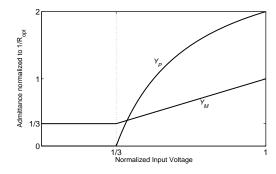

The current and voltage profiles presented can be used to calculate the impedance seen

(a) Main and peaking impedance functions vs. normalized input voltage.

(b) Main and peaking admittance functions vs. normalized input voltage.

Figure 2.10: Impedance and admittance profiles of the main and peaking transistors in a DPA.

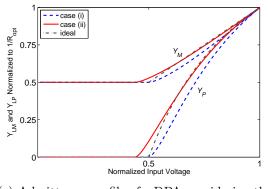

by each transistor as a function of  $v_{in}$ , i.e.,

$$Z_M(v_{in}) = \begin{cases} 2R_{opt} & 0 < v_{in} < 0.5\\ R_{opt}/v_{in} & 0.5 < v_{in} < 1 \end{cases}$$

(2.16)

$$Z_P(v_{in}) = \begin{cases} \infty & 0 < v_{in} < 0.5\\ \frac{1}{2} \cdot \frac{R_{opt}}{v_{in} - 0.5} & 0.5 < v_{in} < 1 \end{cases}$$

(2.17)

which are plotted in Figure 2.10, along with the admittance functions. It can be seen that the main impedance exactly follows the required profile shown in Figure 2.6 after the breakpoint. This confirms while the the efficiency of the main stage is maintained after the breakpoint, linearity is also preserved over the entire input drive range. Note that the admittance functions can be interpreted in the same manner and moreover, they are easier to verify in practice, thus the admittance will only be plotted for the next Doherty architectures discussed in this chapter.

The output power delivered by the main and peaking amplifiers is given by,

$$P_{out,M} = \frac{1}{2} \Re\{\mathbf{V}_{\mathbf{m}} \cdot \mathbf{I}_{\mathbf{m}}^*\}$$

(2.18a)

$$P_{out,P} = \frac{1}{2} \Re\{\mathbf{V}_{\mathbf{p}} \cdot \mathbf{I}_{\mathbf{p}}^{*}\}.$$

(2.18b)

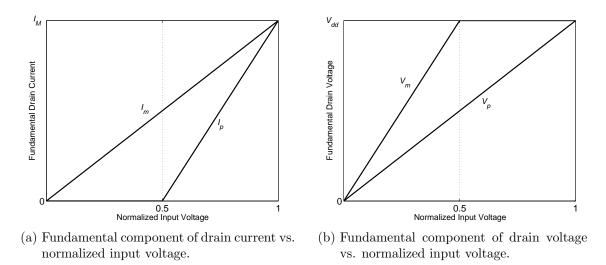

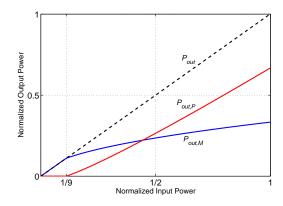

Figure 2.11: Output power profiles of each cell as well as the total power of the DPA.

The total output power can then be calculated by,

$$P_{out} = P_{out,M} + P_{out,P}$$

$$= V_L^2 / R_L.$$

(2.19)

where  $V_L = V_p$  is the fundamental voltage across the load,  $R_L$ . The plot of  $P_{out,M}$ ,  $P_{out,P}$ , and  $P_{out}$  is shown in Figure 2.11. It would be interesting to consider the overall output power at the two important levels, (a) the amplitude of the input voltage is equal to the breakpoint voltage ( $|v_{in}| = 0.5$ ,) and (b) the maximum input voltage ( $|v_{in}| = 1$ ). At power level in (a), the peaking transistor is still off and so it provides no power, and the power delivered by the main amplifier is half of its peak value, which is

$$P_{out} = P_{out,M} = \frac{1}{2} V_{dd} \cdot \frac{I_M}{2} \qquad \text{(at breakpoint)}. \tag{2.20}$$

At power level in (b), the main and peaking devices contribute equally to the output power, since,

$$P_{out} = \frac{1}{2} (V_{dd} \cdot I_M + V_{dd} \cdot I_P)$$

=  $V_{dd} \cdot I_M$  (at peak power). (2.21)

It is observed that the output power at the breakpoint is one-fourth (or 6 dB lower than) the peak power. This is expected since the input voltage amplitude is one-half of the peak value and the amplifier is linear (see Figure 2.11), which means that the input power

back-off is equal to the output power back-off. In fact, even though the main and peaking output powers are nonlinear functions of the input drive, their combination is a linear one. This is because the voltage across the load is dictated by the main current,  $I_m$  according to (2.9). In other words, linearity of the DPA depends entirely on the main device, provided that the main transistor does not enter into the knee region by the function of the peaking device.

Assuming ideal class-B waveforms, the DC power consumed by the main and peaking transistor is given by,

$$P_{dc,M} = V_{dd} \cdot I_{dc,M}$$

$$= V_{dd} \cdot \frac{2I_m}{\pi}$$

$$P_{dc,P} = V_{dd} \cdot I_{dc,P}$$

$$2I_{dd}$$

(2.22a)

$$= V_{dd} \cdot \frac{2I_p}{\pi}.$$

(2.22b)

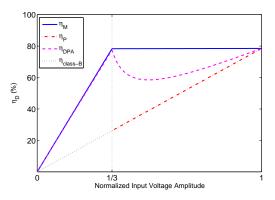

The overall power dissipated by the DPA is obviously equal to  $P_{dc,M} + P_{dc,P}$ . Hence, one can readily calculate the drain efficiency of the main and peaking devices as well as the overall efficiency of the DPA using (2.18), (2.19), and (2.22) as,

$$\eta_M = \frac{Pout_M}{P_{dc,M}} \times 100\% \tag{2.23a}$$

$$\eta_P = \frac{Pout_P}{P_{dc,P}} \times 100\% \tag{2.23b}$$

$$\eta_{DPA} = \frac{Pout_M + Pout_P}{P_{dc,M} + P_{dc,P}} \times 100\%.$$

(2.23c)

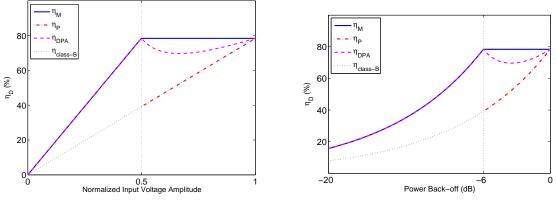

The resulting efficiency plots are illustrated in Figure 2.12, as a function of the input voltage amplitude and output power back-off. The main efficiency is exactly as was aimed for, i.e., it peaks at the breakpoint (6-dB back-off) and is maintained thereafter. The overall drain efficiency, however, slightly decreases past this point, due to the low efficiency of the peaking transistor.

It is helpful, at this point, to assess the power gain of a DPA and compare it with that of a class-B PA. Since the DPA is ideally a linear amplifier, the gain is calculated only in the low power region, for the sake of simplicity. It is also assumed for both PAs that the input side is conjugately matched to the signal source impedance, i.e.,  $R_{in} = Z_S^*$ . Assuming equal power is fed into the both Doherty and class-B amplifiers for a fair comparison, the

(a) Efficiency vs. normalized input voltage amplitude.

(b) Efficiency vs. output power back-off.

Figure 2.12: The efficiency profile of the classical DPA.

ratio of the gains will be equal to the ratio of the output powers, which is expressed as

$$\frac{G_p^D}{G_p^B} = \frac{P_{out}^D}{P_{out}^B} = \frac{\frac{1}{2}(G_m V_{im})^2 \cdot 2R_{opt}}{\frac{1}{2}(G_m V_S)^2 \cdot R_{opt}}.$$

(2.24)

where  $V_{im}$  and  $V_S$  denote the voltage swings across the gate of the transistor in the Doherty and main topology, respectively, and  $G_p$ . Note that  $V_{im} = V_S/\sqrt{2}$  assuming equal input power division for the DPA. Hence, it can be inferred that

$$G_p^D = G_p^B. (2.25)$$

Therefore, employing the Doherty technique to enhance the back-off efficiency does not affect the gain of the main (class B) amplifier.

## 2.5.3 Practical Design Challenges