# High Frequency Receiver Front-End Module for Active Antenna Applications

by

## Stanley Ituah

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2015

© Stanley Ituah 2015

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

This research is based on the analysis and development of an integrated receiver frontend module for high gain active antenna systems at the K-band  $(20 \, GHz)$ . In the design of conventional satellite receivers (such as reflector antennas), the system is usually specified by the gain/directivity, gain-to-temperature ratio (G/T) and radiation pattern requirements. The challenge in high gain active antenna systems development, in addition to beam-forming/beam-steering requirements, is to develop transmit/receive modules which will meet the power, noise and radiation pattern requirements of the conventional antenna. In order to guarantee an optimal design, it is important to be able to translate the specifications from the system level to the transistor level. The focus is on the development of a single-channel CMOS-based integrated receiver module.

The G/T requirement is analysed to derive the noise figure and gain specifications for the low noise amplifier(LNA). An LNA design in 65nm CMOS is demonstrated to achieve a 2.6 dB noise figure and uses only 7 mW of DC power. The digital phased shifter specifications are studied. The generation of "quantization lobes" is analysed and used to estimate the number of bits based on side-lobe level requirements. The design of a 5-bit digital phase shifter based on quadrature signal modulation and a unique digital control logic is presented and tested at 20 GHz. The phase shifter is shown to achieve  $< 5.5^{\circ}$  rms phase error and > 10 dB input and output return loss between 16 - 21 GHz. The effect of pattern tapering on the side-lobe level is investigated and used to specify the minimum dynamic range for a variable gain amplifier (VGA). A VGA design is demonstrated to meet this dynamic range with low phase-frequency variation.

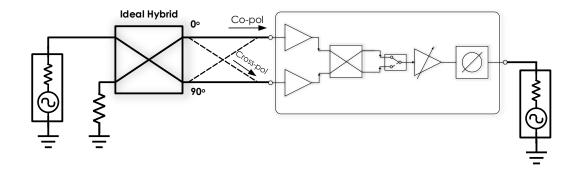

A schematic level design of the proposed single-channel array is studied featuring a hybrid coupler and switch for polarisation requirements, as well as a low-voltage bandgap reference circuit. Simulations results verify that the receiver can be used to generate two hands of polarisation (right and left) with < 1.1 dB axial ratio.

#### Acknowledgements

I would like to thank my supervisor, Professor Safavi Naeini, for giving me the opportunity and encouragement to undergo this research study at the University of Waterloo. His knowledge and expertise in electromagnetic and antenna theory, microwave engineering and wireless communication has been a source of inspiration and direction in my graduate studies and research. I am grateful to have had the chance to complete my dissertation under his guidance.

I especially gives my thanks to Professor Abdolreza Nabavi for suggesting my topic and overlooking my research progress. I would also like to acknowledge his contributions to my understanding of several circuits and systems presented in this dissertation. His expertise on the areas of microwave integrated circuits has been invaluable in my studies of the subject.

I would like to thank my fellow professors who offered valuable advice and courses that have led to my broad understanding of the topics of microwave systems and integrated circuits. In particular, Professor Slim Boumaiza, who offered the course on microwave systems and non-linear circuits and taught me many practical design techniques. Also Professor David Nairn, who taught me Analog Integrated Circuits and offered me advice on Raising and ESD. And also Professor John Long, who gave excellent tips on RFIC layout. Thanks to Hamed Holisaz for seeing my potential and presenting the proposal for this project along with Professor Nabavi, and thanks to all the members of the Centre for Intelligent Antenna and Radio Systems group (CIARS) at the University of Waterloo, for all their support and encouragement throughout my degree.

And a very special thanks to Phil Regier, the best IT specialist I've ever worked with, without whom none of this would be possible.

# **Table of Contents**

| Li       | st of | Tables   | <b>i</b>                                  | ix |

|----------|-------|----------|-------------------------------------------|----|

| Li       | st of | Figure   | 25                                        | x  |

| 1        | Intr  | oducti   | on                                        | 1  |

|          | 1.1   | Satellit | te Communication Link                     | 1  |

|          | 1.2   | Satellit | te Communication Services                 | 2  |

|          |       | 1.2.1    | Classification of Satellite Services      | 2  |

|          |       | 1.2.2    | Fixed Satellite Service                   | 3  |

|          | 1.3   | Antenn   | nas for VSAT Communications               | 4  |

|          |       | 1.3.1    | Link Budget Specification                 | 4  |

|          |       | 1.3.2    | High Gain Reflector Antennas              | 6  |

|          |       | 1.3.3    | Antenna Arrays                            | 8  |

|          | 1.4   | Thesis   | Objective                                 | 10 |

| <b>2</b> | Low   | Noise    | Amplifiers                                | 12 |

|          | 2.1   | System   | n Noise Considerations                    | 12 |

|          | 2.2   | High F   | Trequency Cascode CMOS Amplifiers         | 15 |

|          |       | 2.2.1    | Cascode Amplifier Analysis                | 15 |

|          | 2.3   | 20GHz    | 2 Low Noise Amplifier Design in 65nm CMOS | 24 |

|          |       | 2.3.1    | Overview of the Architecture              | 24 |

|   |     | 2.3.2   | Schematic Level Design                          | 25 |

|---|-----|---------|-------------------------------------------------|----|

|   |     | 2.3.3   | Stability Considerations                        | 26 |

|   |     | 2.3.4   | Inductors and Interconnects                     | 28 |

|   |     | 2.3.5   | Simulation and Measurements                     | 31 |

| 3 | Pha | se Shi  | fters                                           | 36 |

|   | 3.1 | Phase   | Shifter Requirements                            | 36 |

|   |     | 3.1.1   | Digital and Continuous Phase Shifters           | 36 |

|   |     | 3.1.2   | Effect of Phase Quantization                    | 37 |

|   | 3.2 | Vector  | r-Sum Active Phase Shifter                      | 41 |

|   |     | 3.2.1   | Theory of Operation                             | 41 |

|   |     | 3.2.2   | Error in the Quadrature Generator               | 43 |

|   |     | 3.2.3   | Generating 360° Phase Shift                     | 44 |

|   | 3.3 | 20GHz   | z 5-bit Vector-Sum Active Phase Shifter in CMOS | 45 |

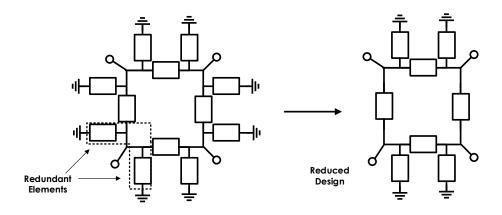

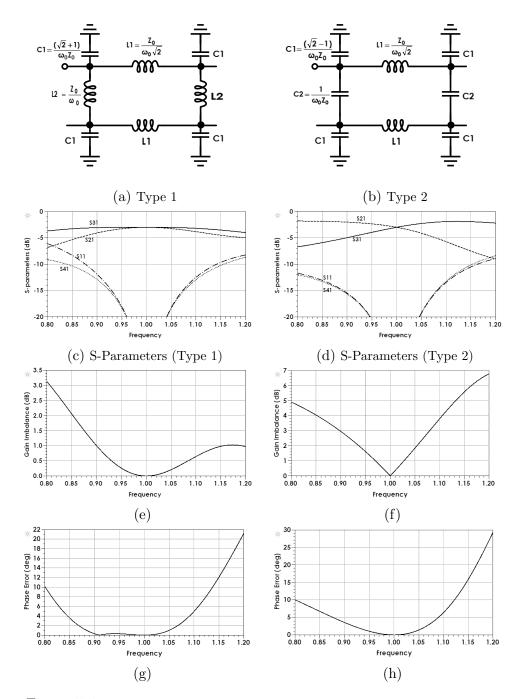

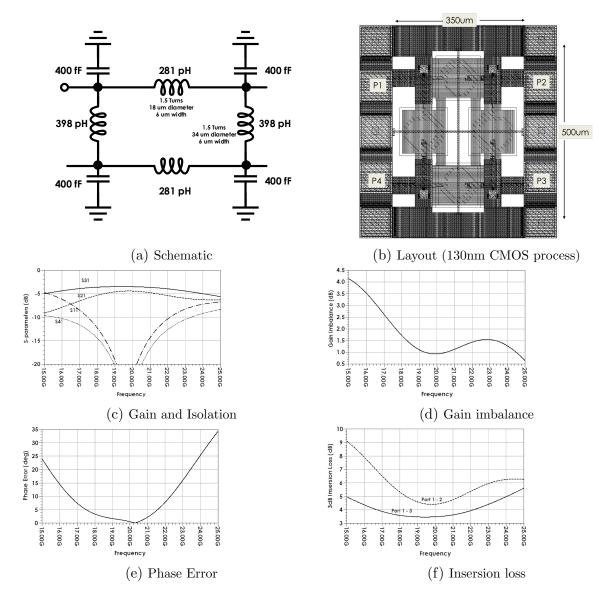

|   |     | 3.3.1   | Quadrature Generator                            | 45 |

|   |     | 3.3.2   | Amplifier and Combiner Network                  | 53 |

|   |     | 3.3.3   | Current DAC                                     | 57 |

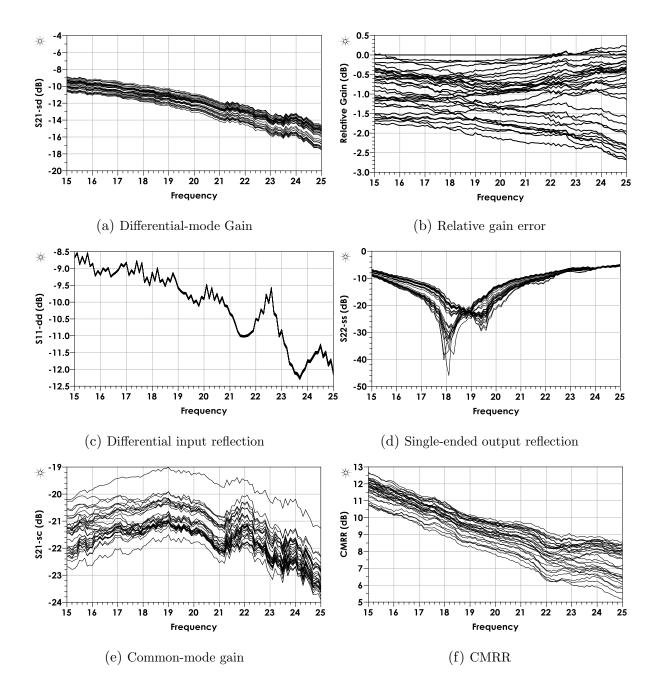

|   |     | 3.3.4   | Complete Schematic, Simulation and Measurements | 59 |

| 4 | Var | iable G | Gain Amplifiers                                 | 65 |

|   | 4.1 | Variab  | ble Gain Amplifier Requirements                 | 65 |

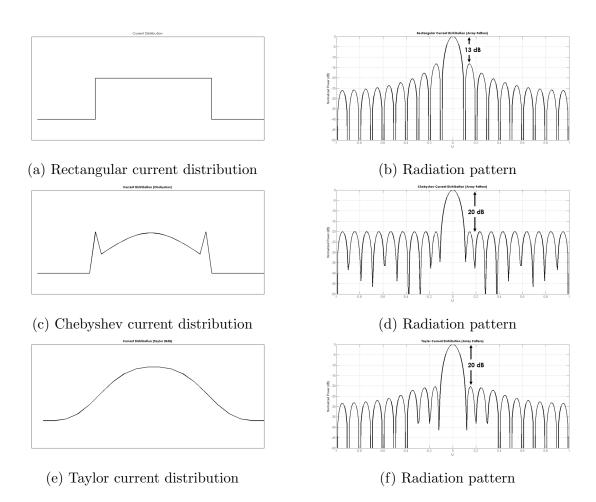

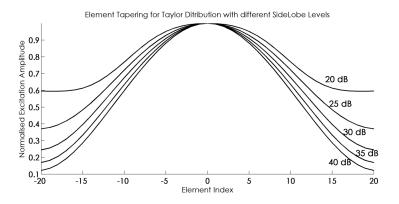

|   |     | 4.1.1   | Pattern Synthesis                               | 65 |

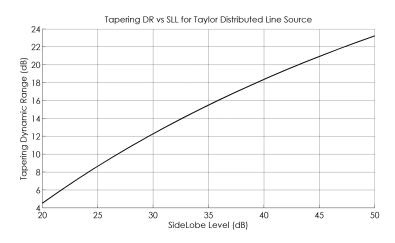

|   |     | 4.1.2   | Tapering and Dynamic Range                      | 66 |

|   | 4.2 | Digita  | lly Controlled Variable Gain Amplifiers         | 68 |

|   |     | 4.2.1   | VGA Implementation in CMOS                      | 68 |

|   |     | 4.2.2   | Current Steering VGA Analysis                   | 70 |

|   |     | 4.2.3   | 10dB DR, 5-bit Digital VGA in 65nm CMOS         | 72 |

|   |     | 4.2.4   | Complete Design, Simulation and Results         | 76 |

|   |     |         |                                                 |    |

| <b>5</b>     | Sing | gle Ch  | annel System Analysis                                            | 80  |

|--------------|------|---------|------------------------------------------------------------------|-----|

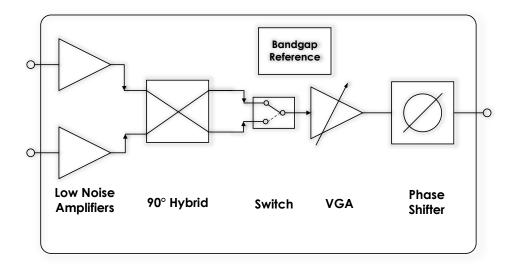

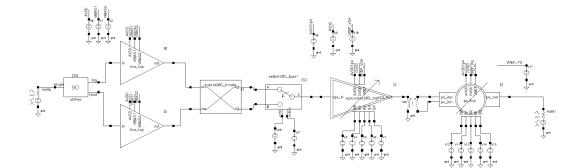

|              | 5.1  | System  | n Overview                                                       | 80  |

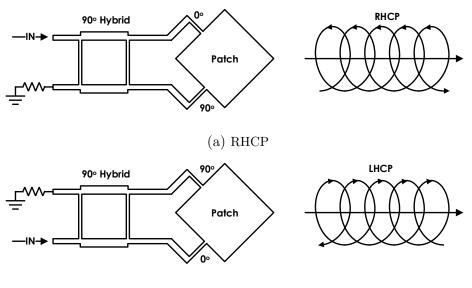

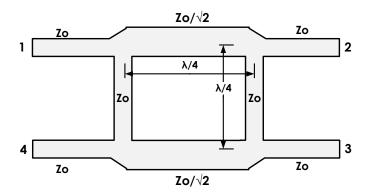

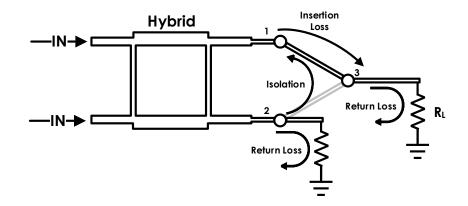

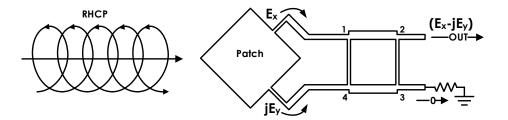

|              | 5.2  | Quadr   | rature (90°) Hybrid Coupler $\ldots$                             | 82  |

|              |      | 5.2.1   | Branch Line Coupler                                              | 82  |

|              |      | 5.2.2   | On-Chip Implementation of the Branch-Line Coupler                | 83  |

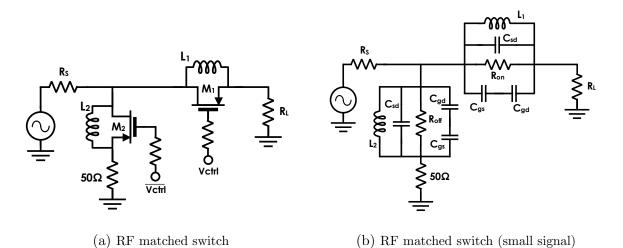

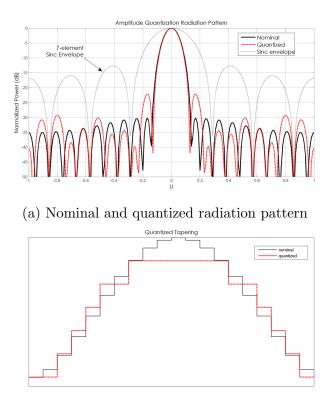

|              | 5.3  | High l  | Isolation SPDT RF Switch                                         | 84  |

|              |      | 5.3.1   | High Frequency CMOS Switches                                     | 84  |

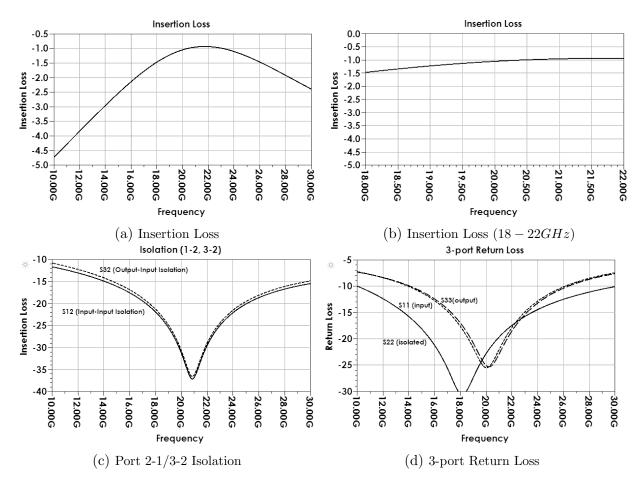

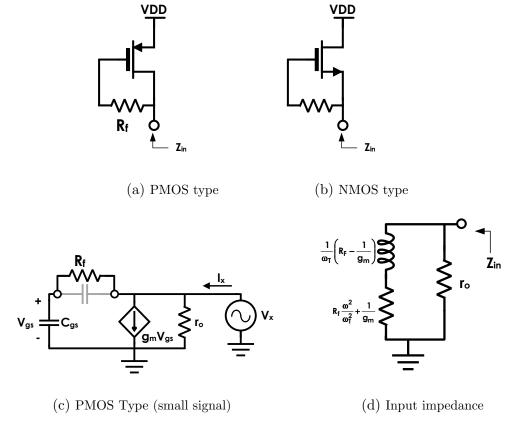

|              |      | 5.3.2   | 20GHz Tuned SPDT Switch in 65nm-CMOS                             | 88  |

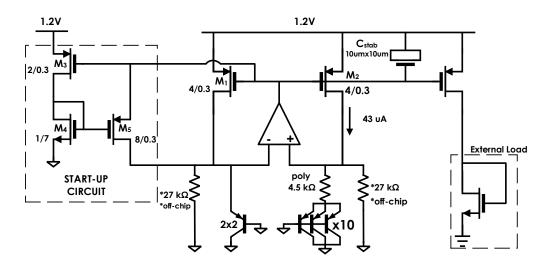

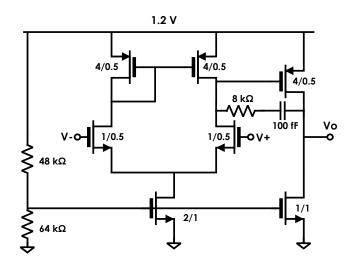

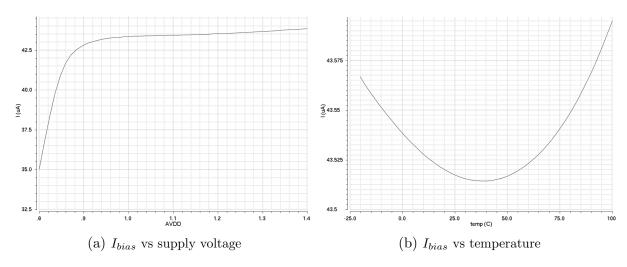

|              | 5.4  | Low $V$ | Voltage (1.2V) Bandgap Reference                                 | 89  |

|              |      | 5.4.1   | Current Mode Bandgap Reference in CMOS $\ . \ . \ . \ . \ . \ .$ | 91  |

|              | 5.5  | Single  | Channel Simulation and Performance                               | 93  |

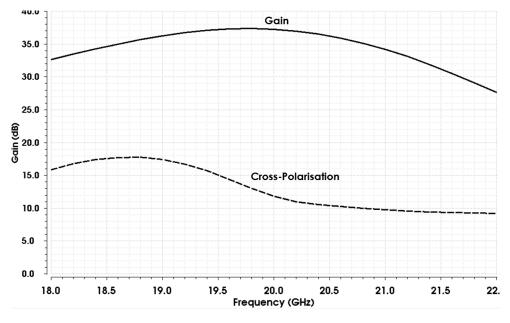

|              |      | 5.5.1   | Gain, Cross Polarisation                                         | 93  |

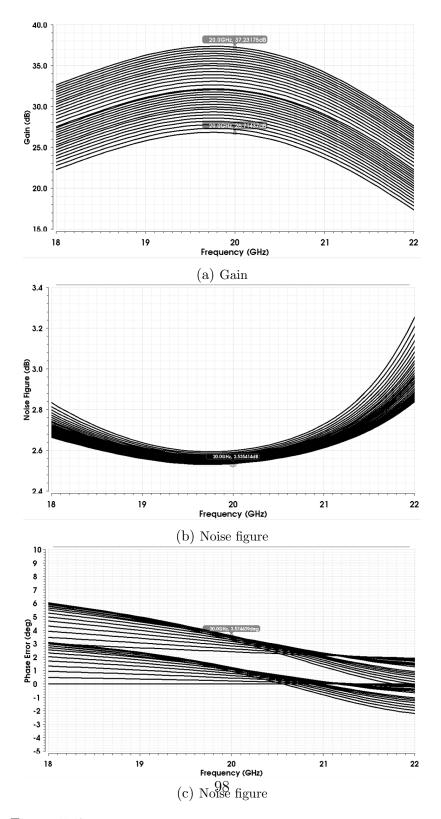

|              |      | 5.5.2   | Gain, Noise Figure and Phase Error with Variable Gain Settings   | 96  |

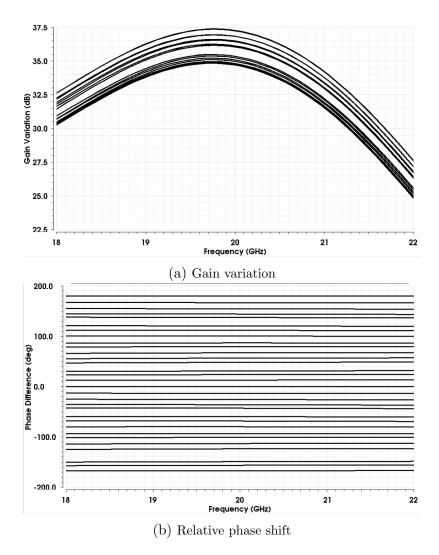

|              |      | 5.5.3   | Gain, Phase Variation with Phase Shifter Settings                | 97  |

|              | 5.6  | Summ    | ary and Conclusion                                               | 97  |

| 6            | Cor  | nclusio | n                                                                | 102 |

|              | 6.1  | Summ    | ary and Conclusion                                               | 102 |

|              | 6.2  | Summ    | ary of Future Work                                               | 104 |

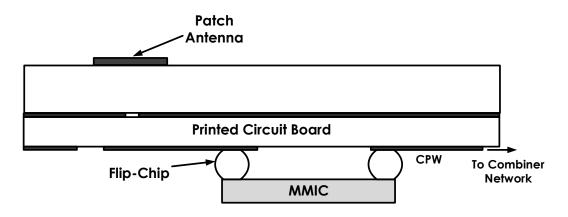

|              |      | 6.2.1   | Complete Receiver MMIC                                           | 104 |

|              |      | 6.2.2   | Complete Transmitter MMIC                                        | 104 |

|              |      | 6.2.3   | Antenna Module                                                   | 105 |

| $\mathbf{A}$ | PPE  | NDIC    | ES                                                               | 107 |

| A            | Noi  | se and  | Power Specifications                                             | 108 |

|              |      | A.0.4   | Power Specification                                              | 108 |

|              |      | A.0.5   | Noise Specification                                              | 110 |

| В            | Common Source Amplifier Impedance  | 112 |

|--------------|------------------------------------|-----|

| С            | Effect of Amplitude Quantization   | 118 |

| D            | Active Inductors                   | 121 |

| $\mathbf{E}$ | Quarter-Wave Length Implementation | 124 |

| Re           | eferences                          | 126 |

# List of Tables

| 1.1 | Ka-band uplink specification                                              | 6   |

|-----|---------------------------------------------------------------------------|-----|

| 1.2 | K-band downlink specification                                             | 7   |

| 2.1 | Design and performance summary of the $20 GHz$ LNA $\ldots \ldots \ldots$ | 32  |

| 3.1 | Design and performance summary of the $20 GHz$ phase shifter              | 64  |

| 4.1 | VGA design and performance summary                                        | 78  |

| 5.1 | Summary of system simulation and performance                              | 101 |

# List of Figures

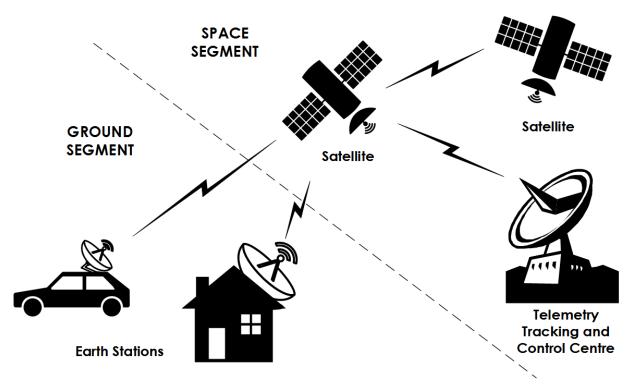

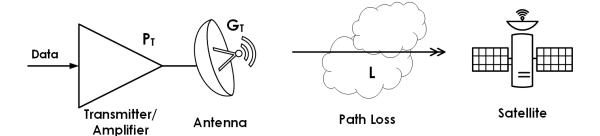

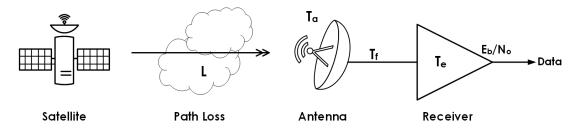

| 1.1  | Satellite communication system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

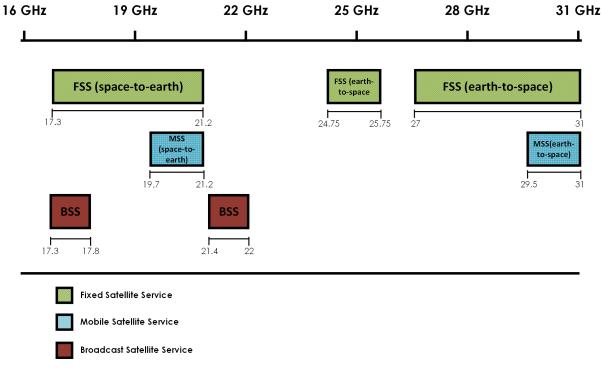

| 1.2  | Ka/Ku band spectrum allocation for satellite services in canada $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  |

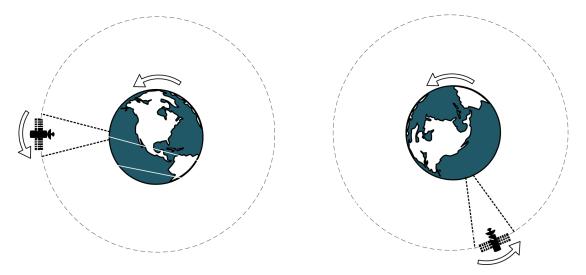

| 1.3  | Geostationary-earth-orbit (GEO) satellites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4  |

| 1.4  | Reflector VSAT antenna (Courtesy of iNetVu®) $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8  |

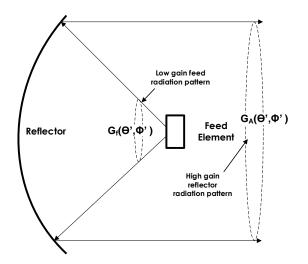

| 1.5  | Parabolic reflector radiation pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9  |

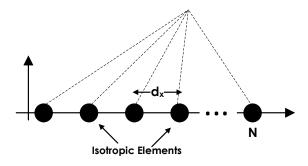

| 1.6  | Linear array of isotropic antenna elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 |

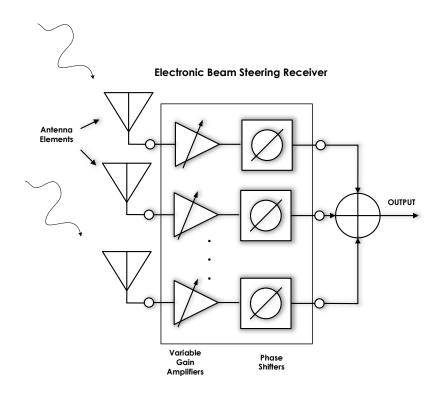

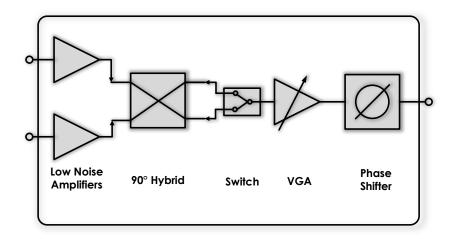

| 1.7  | Electronic beam-steering receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11 |

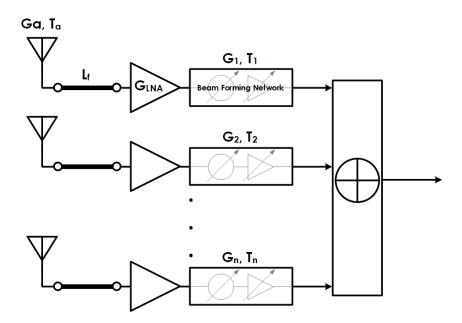

| 2.1  | Active antenna model for noise consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13 |

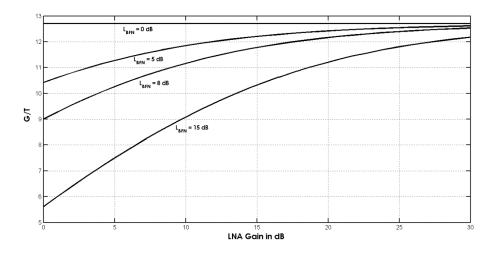

| 2.2  | Effect of the LNA gain on the system's $G/T$ $\hdots$ .<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 |

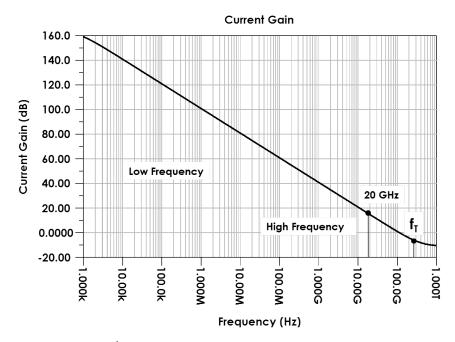

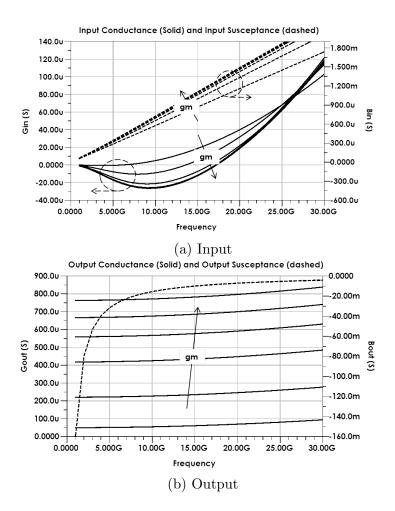

| 2.3  | Current gain $\left(\frac{i_d}{i_g}\right)$ of NMOS transistor in $65nm$ technology $(f_T \approx 290  GHz)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

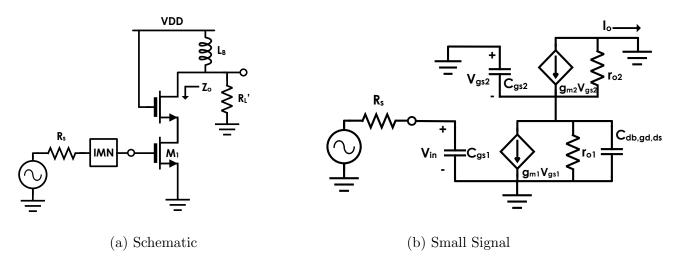

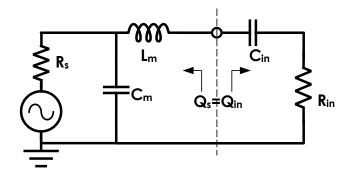

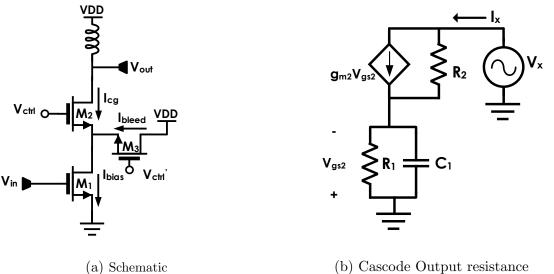

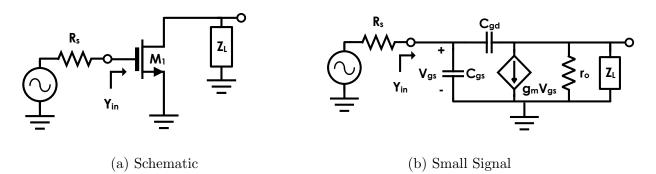

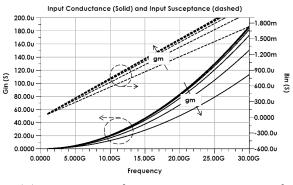

| 2.4  | Cascode LNA Configuration and small-signal model $\ . \ . \ . \ . \ . \ . \ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17 |

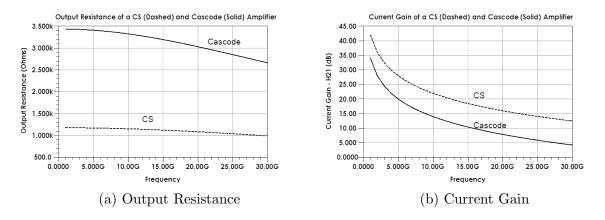

| 2.5  | Current gain and output resistance of a common-source and cascode amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

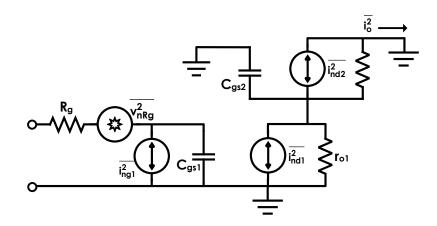

| 2.6  | Small signal model of a cascode amplifier with channel noise sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18 |

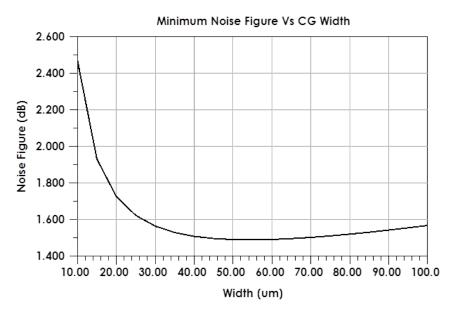

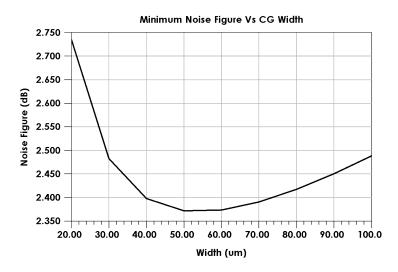

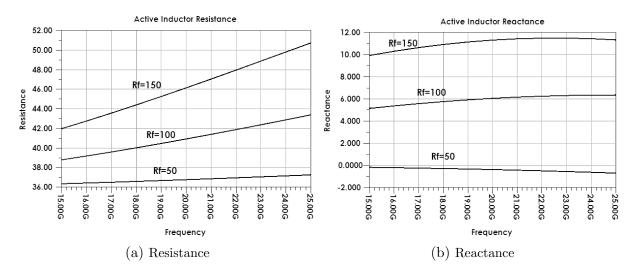

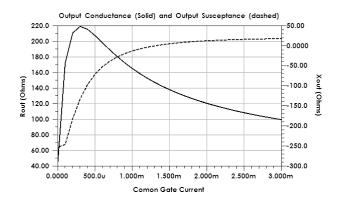

| 2.7  | Minimum noise figure variation with the width of the common-gate device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 |

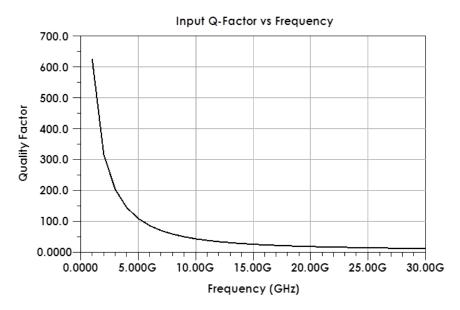

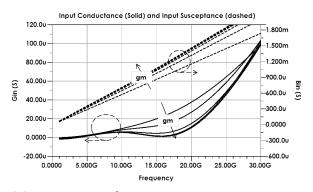

| 2.8  | Quality factor of the cascode transistor $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

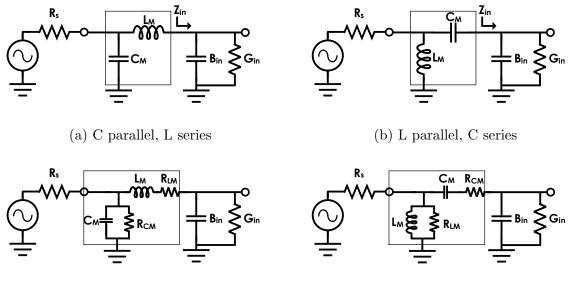

| 2.9  | Impedance transformation networks for $Re(Z_{in}) < R_S$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22 |

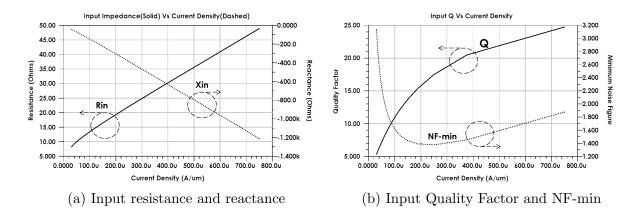

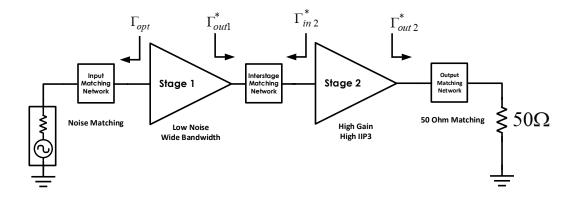

| 2.10 | Transistor parameters vs current density (constant current, varying width) $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22 |

| 2.11 | The unloaded-Q of a conjugately matched network $\hfill \ldots \hfill \hfill \ldots $ | 23 |

| 2.12 | Transistor parameters vs current density (constant current, varying width) with inductive degeneration $[L_S = 80  pH]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24 |

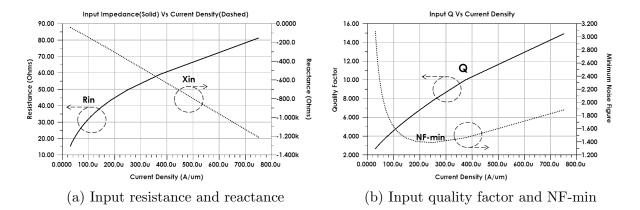

| 2.13 | $f_T$ , $f_{max}$ and $NF_{min}$ at 20GHz for TSMC 65 nm CMOS technology                                                  | 25 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

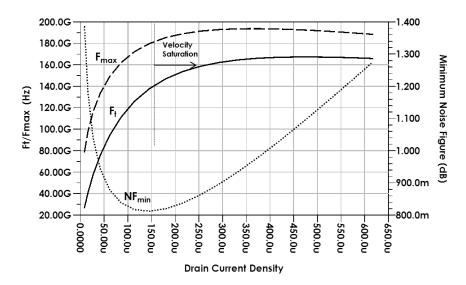

| 2.14 | Two-stage LNA block diagram                                                                                               | 26 |

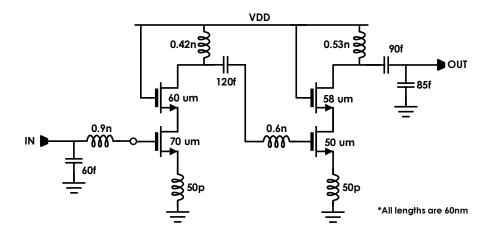

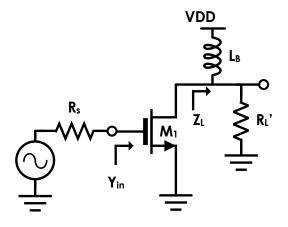

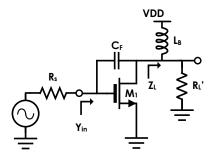

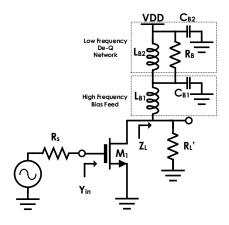

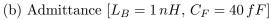

| 2.15 | Simple two-stage LNA schematic                                                                                            | 27 |

| 2.16 | Noise figure at 20GHz with varying common gate transistor width                                                           | 28 |

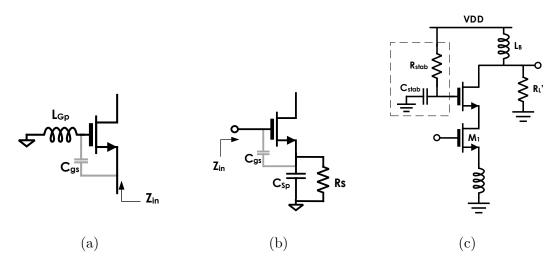

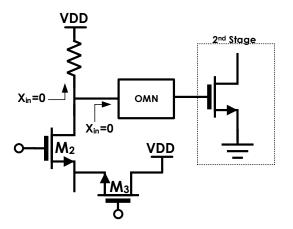

| 2.17 | Unstable common-gate Configuration (a) and (b). Nullifying the inductance and feedthrough (c).                            | 29 |

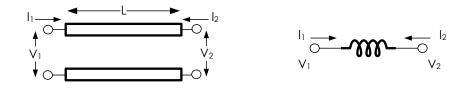

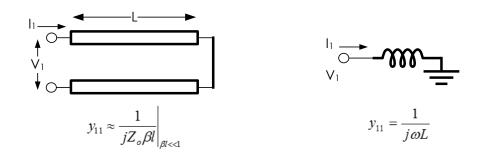

| 2.18 | Equivalent quasi-lumped inductor element $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 30 |

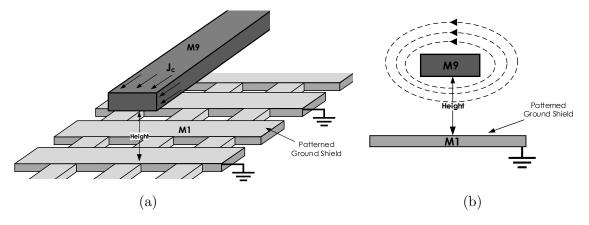

| 2.19 | Stripline inductor element                                                                                                | 30 |

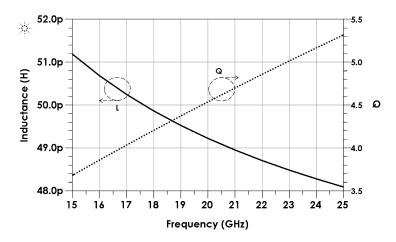

| 2.20 | Inductance and quality factor of the microstrip line                                                                      | 31 |

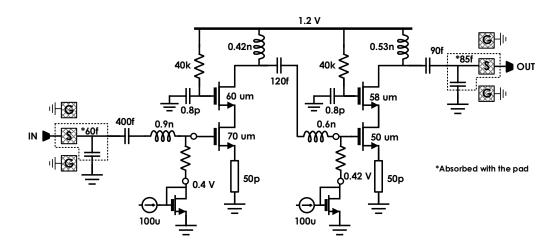

| 2.21 | Complete $20GHz$ LNA schematic                                                                                            | 33 |

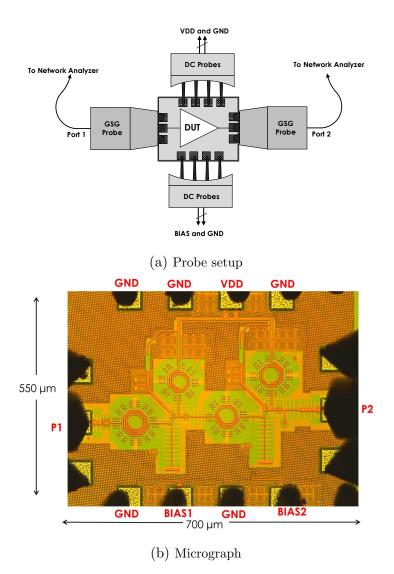

| 2.22 | Measurement setup and chip micrograph                                                                                     | 34 |

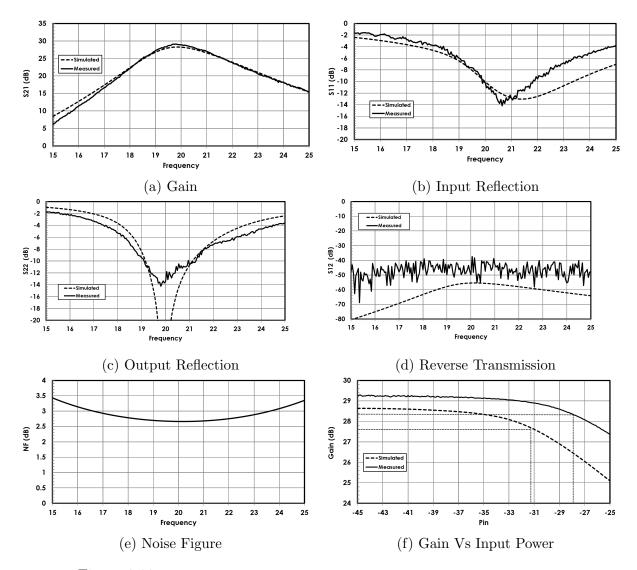

| 2.23 | Simulated and Measured results for the $20GHz$ Low Noise Amplifier $\ldots$ $\ldots$ $\ldots$                             | 35 |

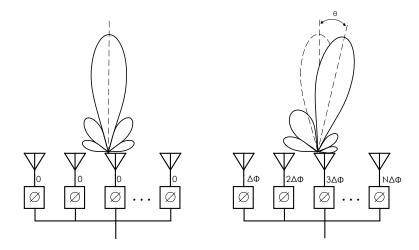

| 3.1  | Illustration of beam-steering using elements excited by a progressive phase                                               | 37 |

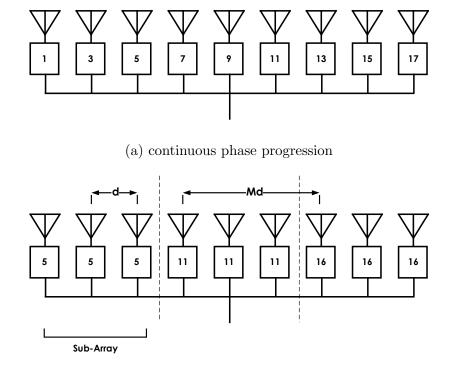

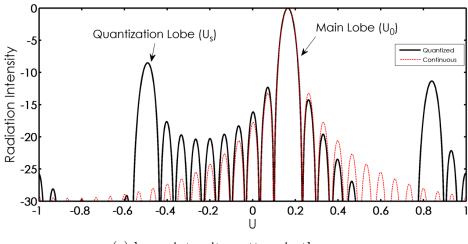

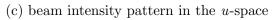

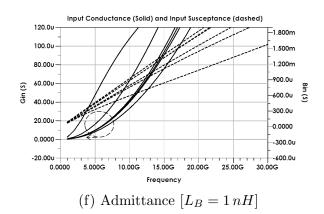

| 3.2  | Effect of phase quantization on the intensity pattern                                                                     | 39 |

| 3.3  | Quantization lobe level                                                                                                   | 40 |

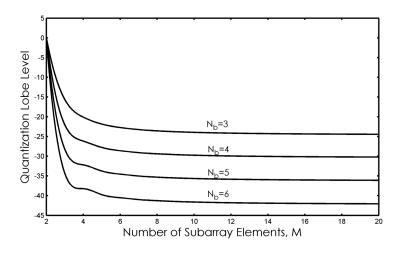

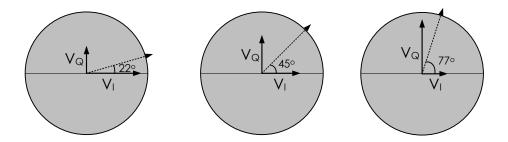

| 3.4  | Vector-sum phase shifter block diagram                                                                                    | 41 |

| 3.5  | Unit circle illustation of the vector-sum magnitude/phase control $\ldots$ .                                              | 43 |

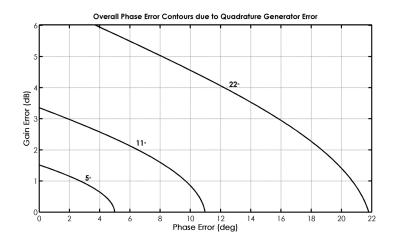

| 3.6  | Maximum phase error contours as a function of the quadrature generator gain error and phase error                         | 45 |

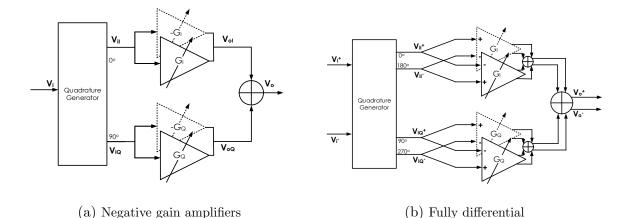

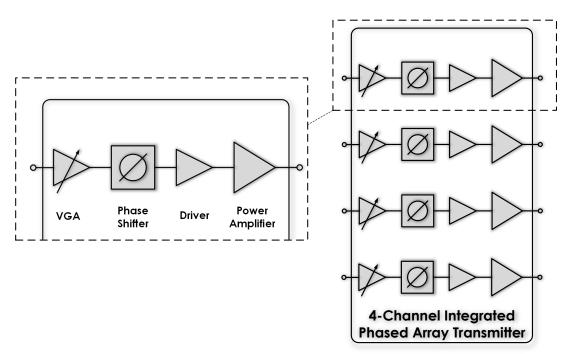

| 3.7  | 360° Vector-Sum Phase Shifter Implementation                                                                              | 46 |

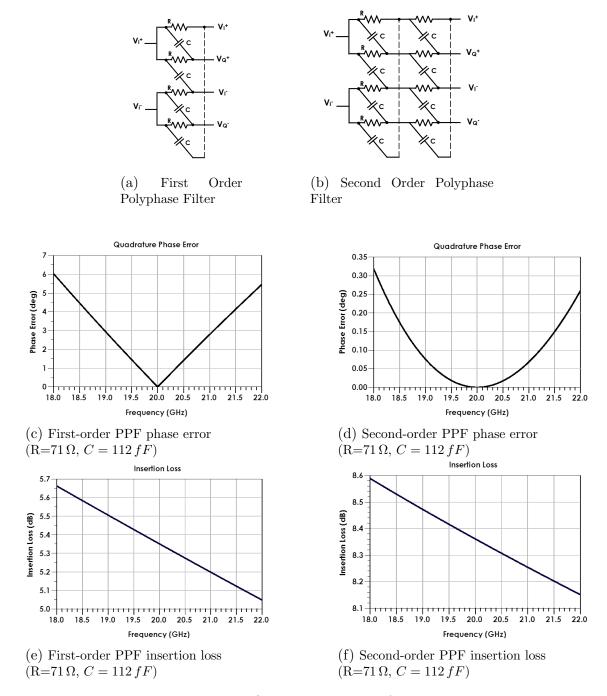

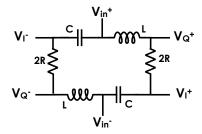

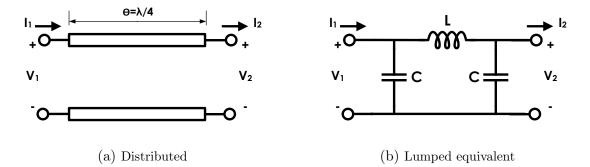

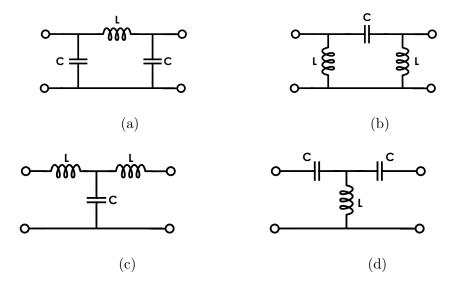

| 3.8  | Polyphase filter networks and frequency response                                                                          | 47 |

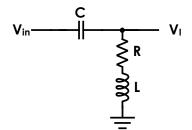

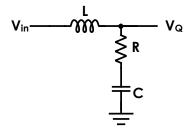

| 3.9  | Quadrature All-Pass Filter                                                                                                | 48 |

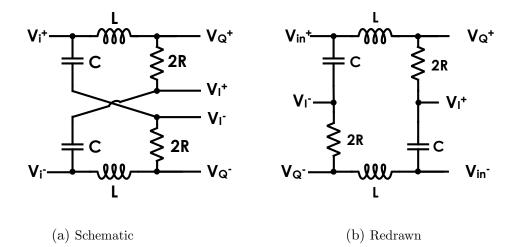

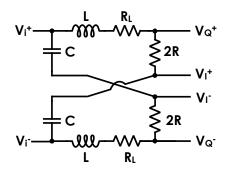

| 3.10 | Quadrature all-pass filter network single-ended and differential schematic .                                              | 49 |

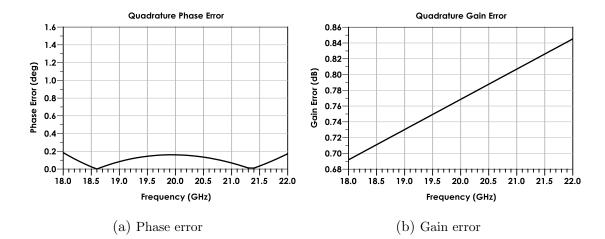

| 3.11 | Quadrature All-Pass Filter Frequency Response                                                                             | 50 |

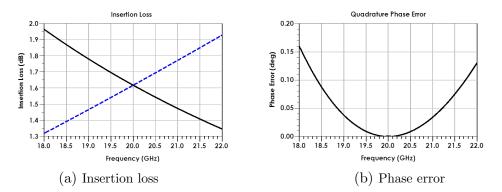

| 3.12 | Quadrature filter with load capacitance                                                                                   | 51 |

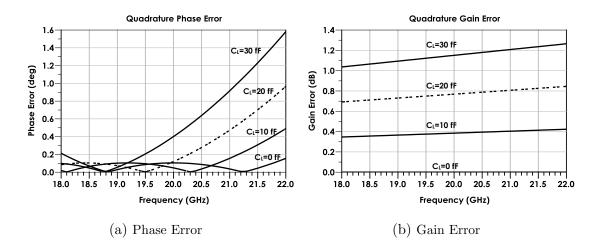

| 3.13 | Effect of Load Capacitance on the Filter Gain and Phase error $[L = 280  pH, C = 220  fF, R = 35\Omega]$                  | 52 |

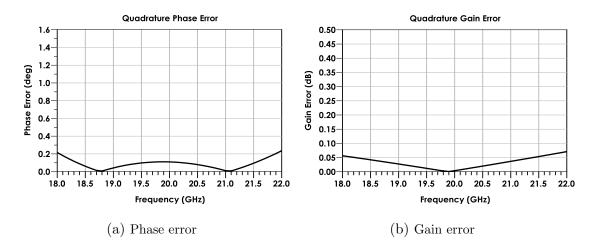

| 3.14 | Filter gain and phase error after phase error correction with $C_{load} = 20 f F [L' = 257 pH, C' = 213 f F, R = 35\Omega]$ .                    | 52 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

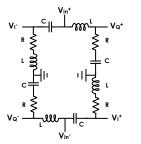

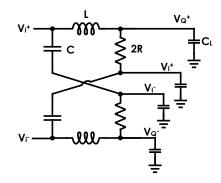

| 3.15 | Complete quadrature filter                                                                                                                       | 53 |

| 3.16 | Filter gain and phase error after gain and phase error correction $(C_{load} = 20 fF)$ $[L' = 257 pH, C' = 213 fF, R = 35\Omega, R_c = 6\Omega]$ | 54 |

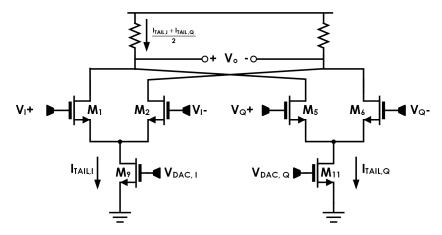

| 3.17 | Variable gain amplifier network                                                                                                                  | 55 |

| 3.18 | Simplified variable gain amplifier network                                                                                                       | 56 |

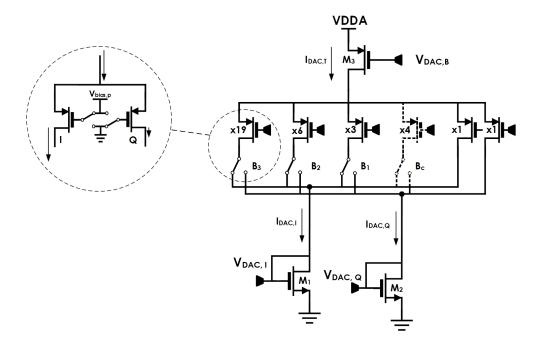

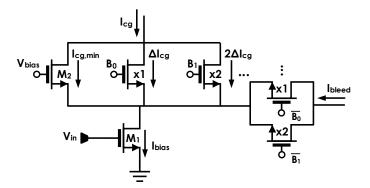

| 3.19 | Current DAC (simplified schematic)                                                                                                               | 57 |

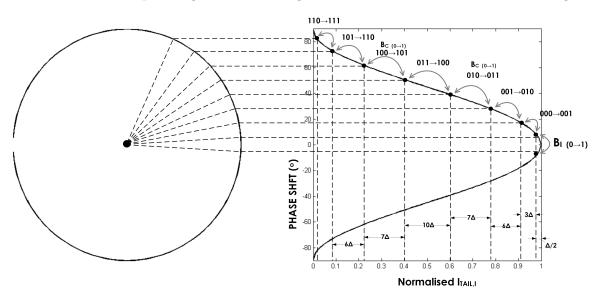

| 3.20 | Current DAC digital phase control                                                                                                                | 58 |

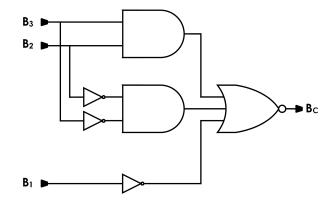

| 3.21 | AND-OR-INVERT implementation of $B_C$                                                                                                            | 59 |

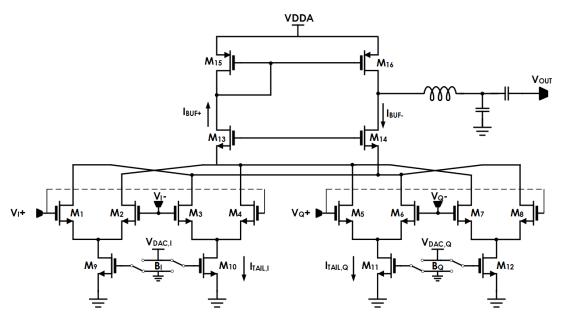

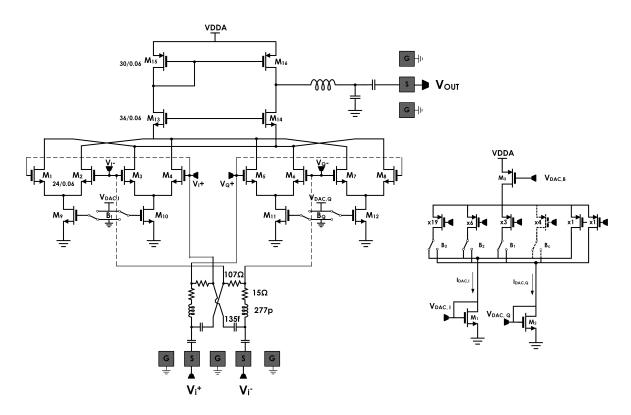

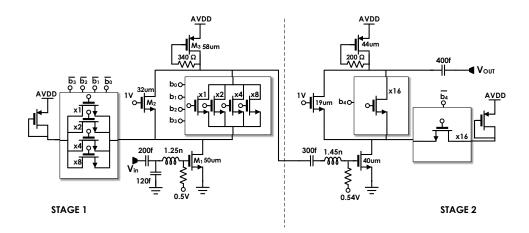

| 3.22 | Phase shifter schematic                                                                                                                          | 60 |

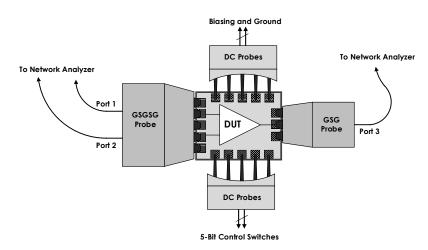

| 3.23 | Differential to single-ended probe configuration                                                                                                 | 61 |

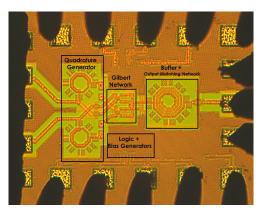

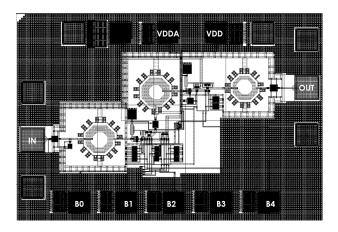

| 3.24 | Phase shifter chip micrograph. $(0.6 \times 0.5  mm^2)$                                                                                          | 62 |

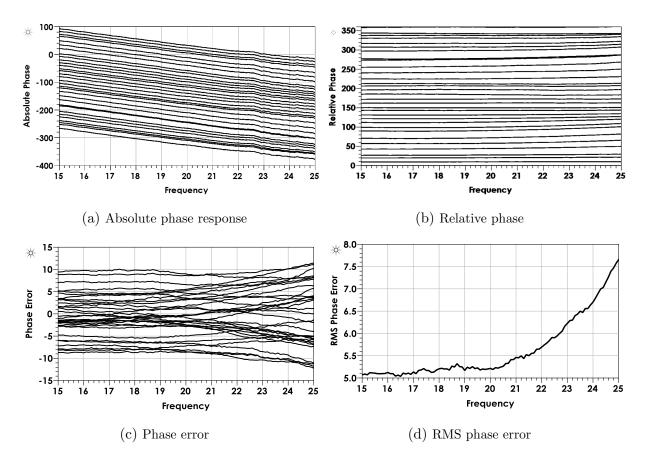

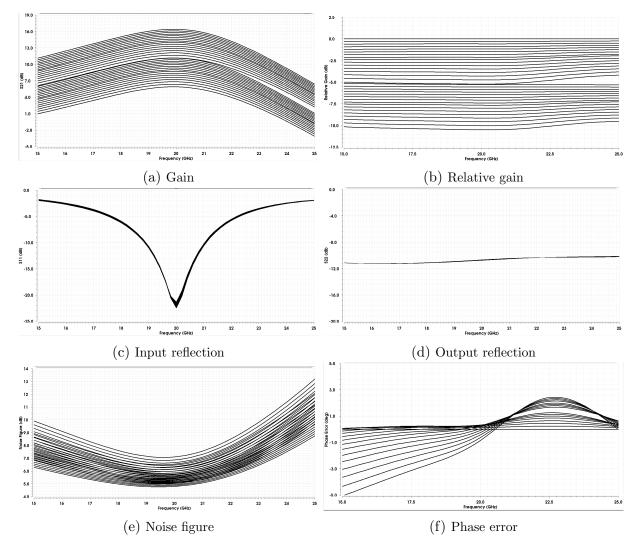

| 3.25 | Phase shifter measured phase response for 32 States                                                                                              | 62 |

| 3.26 | Phase shifter gain and matching measurements for 32 states                                                                                       | 63 |

| 4.1  | Tapered current distribution and the corresponding radiation pattern $\ldots$ $\ldots$ $\ldots$                                                  | 67 |

| 4.2  | Line source distribution for various side-lobe levels                                                                                            | 68 |

| 4.3  | Tapering dynamic range vs side-lobe level                                                                                                        | 69 |

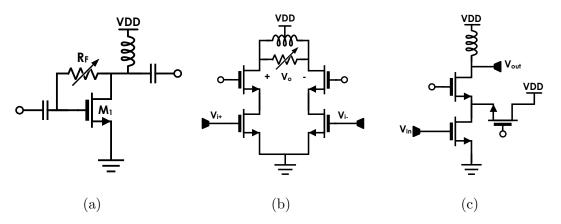

| 4.4  | Typical VGA implementations                                                                                                                      | 70 |

| 4.5  | Analog current steering VGA schematic                                                                                                            | 71 |

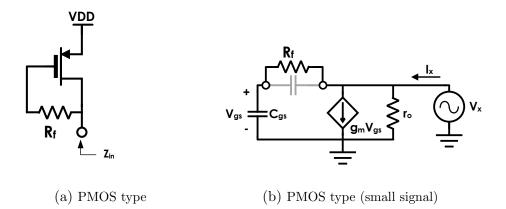

| 4.6  | Resistive drain network for low VGA phase-frequency variation                                                                                    | 73 |