# Design Techniques for Lithography-Friendly Nanometer CMOS Integrated Circuits

by

# Ayman Hamouda

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2015

©Ayman Hamouda 2015

#### Abstract

The Integrated Circuits industry has been a major driver of the outstanding changes and improvements in the modern day technology and life style that we are observing in our day to day life. The continuous scaling of CMOS technology has been one of the major challenges and success stories. However, as the CMOS technology advances deeply into the deep sub-micron technology nodes, the whole industry (both manufacturing and design) is starting to face new challenges. One major challenge is the control of the variation in device parameters. Lithography variations result from the industry incapability to come up with new light sources with a smaller wavelength than ArF source (193 nm wavelength).

In this research, we develop better understanding of the photo-lithography variations and their effect on how the design gets patterned. We investigate the state-of-the-art mask correction and design manipulation techniques. We are focusing in our study on the different Optical Proximity Correction (OPC) and design retargeting techniques to assess how we can improve both the functional and parametric yield. Our goal is to achieve a fast and accurate Model Based Re-Targeting (MBRT) technique that can achieve a better functional yield during manufacturing by establishing the techniques to produce more lithography-friendly targets. Moreover, it can be easily integrated into a fab's PDK (due to its relatively high speed) to feedback the exact final printing on wafer to the designers during the early design phase.

In this thesis, we focus on two main topics. First is the development of a fast technique that can predict the final mask shape with reasonable accuracy. This is our proposed Model-based Initial Bias (MIB) methodology, in which we develop the full methodology for creating compact models that can predict the perturbation needed to get to an OPC initial condition that is much closer to the final solution. This is very useful in general in the OPC domain, where it can save almost 50% of the OPC runtime. We also use MIB in our proposed Model-Based Retargeting (MBRT) flow to accurately compute lithography hot-spots location and severity. Second, we develop the fast model-based retargeting methodology that is capable of fixing lithography hot spots and improving the functional yield. Moreover, in this methodology we introduce to the first time the concept of distributed retargeting. In distributed MBRT, not only the design portion that is suffering from the hot-spot is moving to get it fixed but also the surrounding designs and design fragments also contribute to the hot-spot fix. Our proposed model-based retargeting methodology also includes the multiple-patterning awareness as well as the electrical-connectivity-awareness (via-awareness). We used Mentor Graphics Calibre Litho-API c-based programing to develop all of the methodologies we explain in this thesis and tested it on 20nm and 10nm nodes.

#### Acknowledgements

I would like to express my special appreciation and thanks to my supervisors Professor Dr. Mohab Anis and Professor Karim Karim for their tremendous support and understanding during the course of this research works. This has been a long journey with lots of challenges that would not have been possible without their understanding and support. I would like also to thank my PhD advisory committee Professor Chettypalayam Selvakumar, Prof. Siva Sivoththaman, Prof. Patricia Nieva, Professor Andrew Brzezinski and Professor Siddharth Garg for all their support.

I would like to express my gratitude to GLOBALFOUNDRIES for the financial and technical support that allowed this work to come out in its present quality after allowing me to work on the state-of-the-art technical problems and the wonderful exposure of the technical challenges and opportunities in the foundry world in deep sub-micron technologies. I'd like to thank Chidam Kallingal and Sarah McGowan for their continuous support of this work over the past few years inside GLOBALFOUNDRIES.

I am always very grateful to my wife, Doaa Soliman, for her continuous support and encouragement to have my PhD work done since day one. Also, my little angels Mariam and Youssef, I love you so much. And last but not least, to my late parents, I wish you were here beside me at this moment.

## Dedication

To my late parents, I wish you were here.

To my lovely wife, without you I wouldn't have been standing here today.

# Table of Contents

| Li | st of | Tables                                             | ix |

|----|-------|----------------------------------------------------|----|

| Li | st of | Figures                                            | x  |

| 1  | Intr  | roduction                                          | 1  |

|    | 1.1   | Introduction                                       | 1  |

|    | 1.2   | Challenges and Motivation                          | 3  |

|    | 1.3   | Structure of the thesis                            | 4  |

| 2  | Sou   | rces and Implications of Process Variations        | 5  |

|    | 2.1   | The Impact of Variability on Yield and Performance | 6  |

|    | 2.2   | Statistical Nature of Process Variation            | 7  |

|    |       | 2.2.1 Random vs. Systematic                        | 7  |

|    |       | 2.2.2 Correlated vs. Uncorrelated                  | 8  |

|    | 2.3   | Sources of Process variations                      | 8  |

|    |       | 2.3.1 Variability extension                        | 9  |

|    |       | 2.3.2 Random-particle defects                      | 10 |

|    |       | 2.3.3 Photo-lithography                            | 12 |

|    |       | 2.3.4 Etching                                      | 20 |

|    |       | 2.3.5 Chemical Mechanical Polishing (CMP)          | 22 |

|    |       | 2.3.6 Stress                                       | 25 |

|   |     | 2.3.7   | Atomistic variability                                                 | 25 |

|---|-----|---------|-----------------------------------------------------------------------|----|

|   | 2.4 | Process | s Variations Control and Mitigation                                   | 27 |

|   | 2.5 | Summa   | ary                                                                   | 28 |

| 3 | Des | ign for | Manufacturability and Optical lithography                             | 29 |

|   | 3.1 | Introdu | action                                                                | 29 |

|   | 3.2 | Design  | for Manufacturing (DFM)                                               | 30 |

|   |     | 3.2.1   | Recommended (Restrictive) Designs Rules (RDR)                         | 30 |

|   |     | 3.2.2   | Litho-Friendly Designs (LFD)                                          | 32 |

|   |     | 3.2.3   | Parametric DFM                                                        | 35 |

|   | 3.3 | Retarge | eting for Yield                                                       | 39 |

|   |     | 3.3.1   | Rules-Based ReTargeting (RBRT)                                        | 39 |

|   |     | 3.3.2   | Model-Based Re-Targeting (MBRT)                                       | 41 |

|   | 3.4 | Optical | l Proximity Correction (OPC)                                          | 41 |

|   |     | 3.4.1   | OPC Process Models                                                    | 46 |

|   |     | 3.4.2   | OPC Algorithms and their objectives                                   | 46 |

|   | 3.5 | Summa   | ary                                                                   | 60 |

| 4 | Aer | ial Ima | ge Retargeting (AIR): A proof of feasibility                          | 61 |

|   | 4.1 | Introdu | action                                                                | 61 |

|   | 4.2 | Aerial- | Image Retargeting (AIR)                                               | 62 |

|   | 4.3 | AIR Te  | esting Results                                                        | 68 |

|   | 4.4 | Summa   | ary                                                                   | 83 |

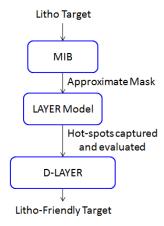

| 5 |     |         | Yield-Enhancing Retargeting (LAYER): A full Model-Based g Methodology | 84 |

|   | 5.1 | Introdu | action                                                                | 84 |

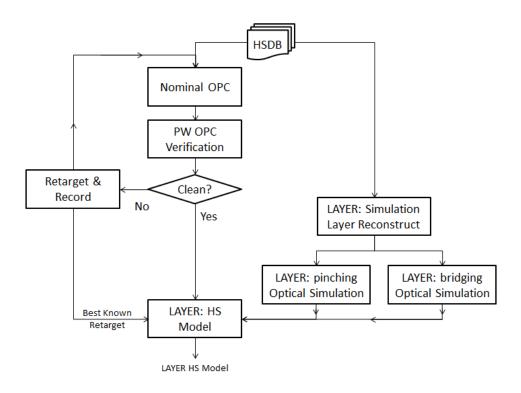

|   | 5.2 | LAYEI   | R: Simulation Layer Construction                                      | 85 |

|   | 5.3 | LAYEI   | R: Optical Simulation Conditions                                      | 87 |

|   | 5.4  | LAYER: Hot-Spots Modeling                                    | 88  |

|---|------|--------------------------------------------------------------|-----|

|   | 5.5  | LAYER: Auto-Retargeting Methodology and Implementation       | 91  |

|   | 5.6  | LAYER: Testing Results                                       | 93  |

|   | 5.7  | Conclusions                                                  | 96  |

| 6 | Mo   | del-based Initial Bias (MIB): Towards a Single-Iteration OPC | 99  |

|   | 6.1  | introduction                                                 | 99  |

|   | 6.2  | Background                                                   | 100 |

|   | 6.3  | MIB: Model-based Initial Bias                                | 100 |

|   |      | 6.3.1 MIB: The concept                                       | 104 |

|   |      | 6.3.2 MIB: Modeling                                          | 105 |

|   |      | 6.3.3 MIB: Correction                                        | 110 |

|   | 6.4  | Testing Results                                              | 111 |

|   |      | 6.4.1 Metal Layer Testing                                    | 111 |

|   |      | 6.4.2 Via Layer Testing                                      | 114 |

|   | 6.5  | Conclusions                                                  | 116 |

| 7 | Dist | tributed Model-Based Retargeting                             | 117 |

|   | 7.1  | Introduction                                                 | 117 |

|   | 7.2  | D-LAYER: Distributed Litho- And Yield-Enhancing Retargeting  | 118 |

|   |      | 7.2.1 Problem Definition                                     | 119 |

|   |      | 7.2.2 D-LAYER: Retargeting Forces                            | 119 |

|   |      | 7.2.3 D-LAYER: Restraining Forces                            | 125 |

|   |      | 7.2.4 D-LAYER: Overall Algorithm                             | 132 |

|   | 7.3  | Testing Results                                              | 135 |

|   | 7.4  | D-LAYER: An LFD perspective                                  | 138 |

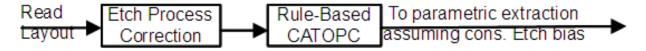

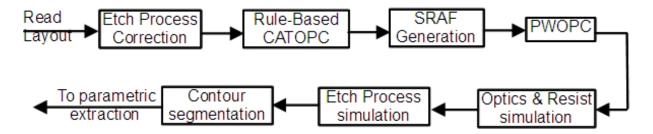

|   | 7.5  | D-LAYER: Parasitic-Extraction Applications                   | 142 |

|   | 7.6  | Conclusion                                                   | 145 |

| 8  | Con   | clusion and Future Work         | 146 |

|----|-------|---------------------------------|-----|

|    | 8.1   | Summary of Contribution         | 146 |

|    | 8.2   | Limitations and Recommendations | 147 |

|    | 8.3   | Future Work                     | 148 |

| A] | PPE   | NDICES                          | 149 |

| A  | Pub   | lications from this work        | 150 |

| В  | Glo   | ssary                           | 151 |

| Re | efere | nces                            | 153 |

# List of Tables

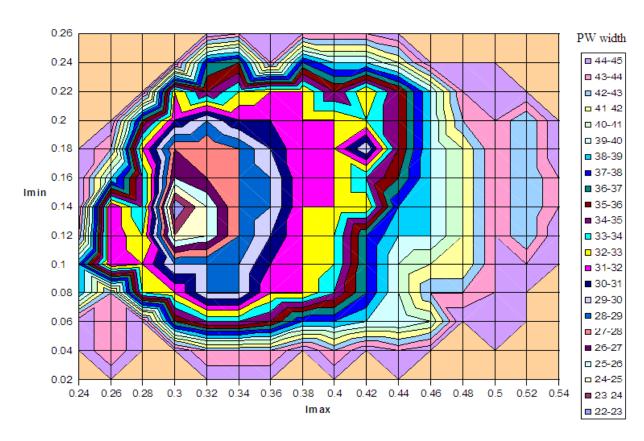

| 4.1 | Intensity-PW width map for curvature between -6 and -2        | 75 |

|-----|---------------------------------------------------------------|----|

| 4.2 | Intensity-PW space map for curvature between -6 and -2        | 75 |

| 4.3 | Intensity-PW width map for curvature between -2 and 2 $\dots$ | 76 |

| 4.4 | Intensity-PW space map for curvature between -2 and 2         | 76 |

| 4.5 | Intensity-PW width map for curvature between 2 and 6          | 76 |

| 4.6 | Intensity-PW space map for curvature between 2 and 6          | 77 |

| 4.7 | Intensity-PW width map for curvature between 6 and 10         | 77 |

| 4.8 | AIR table                                                     | 78 |

# List of Figures

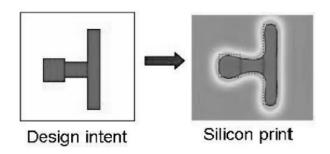

| 1.1  | An illustration of the deviation of the Lithography to resolve the design intent without deformation. [1]                                                                                                                          | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

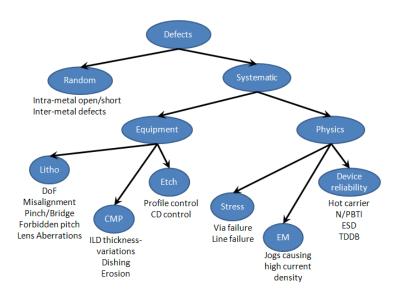

| 2.1  | A map showing different sources of process variations and their classification.                                                                                                                                                    | 9  |

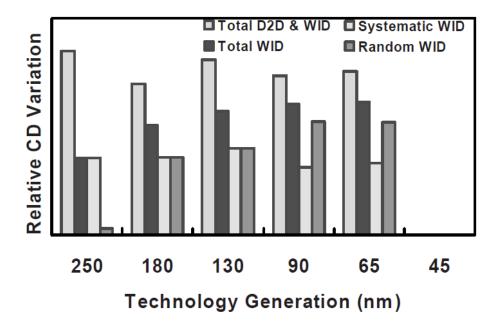

| 2.2  | Total within-die (intra-die) contribution to CD variation is increasing each node and will be dominating in deep-subwavelength nodes. [2]                                                                                          | 10 |

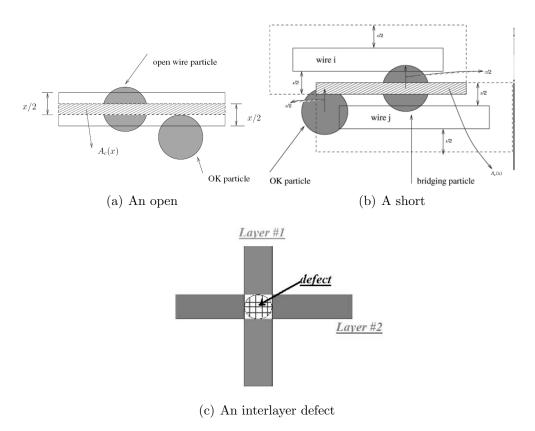

| 2.3  | Examples of common problems caused by random particles defects. $[1]$                                                                                                                                                              | 11 |

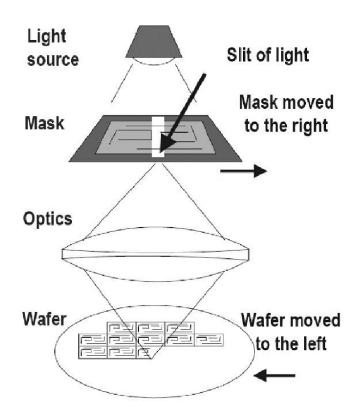

| 2.4  | Step and scan lithography system illustration. [1]                                                                                                                                                                                 | 13 |

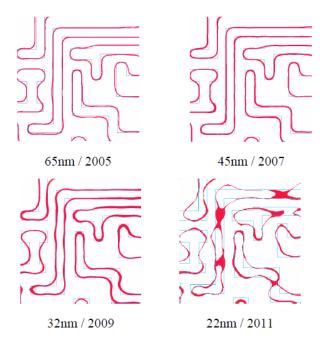

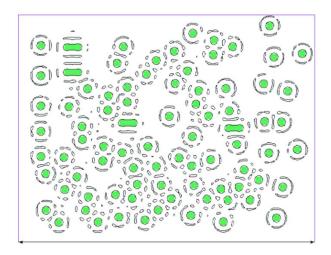

| 2.5  | Contour bands illustrate how a first metal layout images under node-specific levels of process variability. Process variation design-immunity is shown to degrade from a node to the next until it completely fails at 22nm. [3]   | 14 |

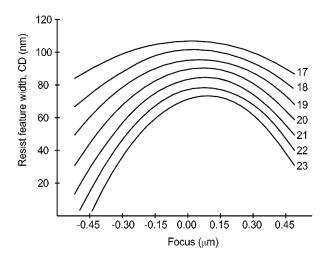

| 2.6  | Bossung plot represents CD linewidth as a function of defocus at different dose values. [4]                                                                                                                                        | 16 |

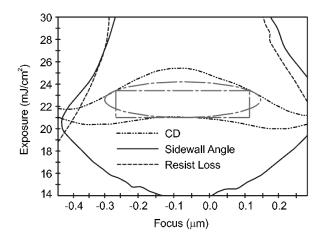

| 2.7  | E-D process-window plots contours of constant CD, resist sidewall, and resist thickness values in the exposure-defocus space. Their overlap establishes the process-window which is given in the figure by the inscribed rectangle |    |

|      | or ellipse. [4]                                                                                                                                                                                                                    | 16 |

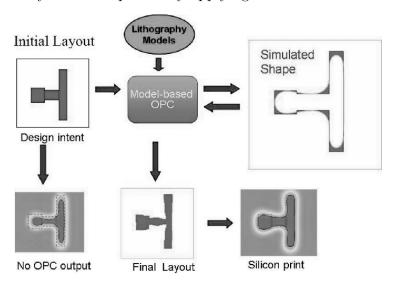

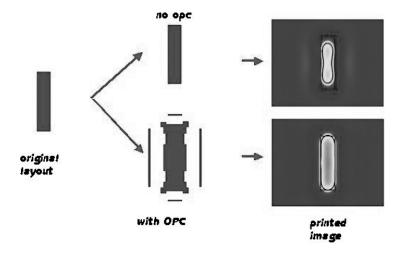

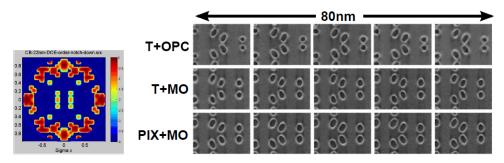

| 2.8  | Design fidelity improvement due to OPC. [1]                                                                                                                                                                                        | 17 |

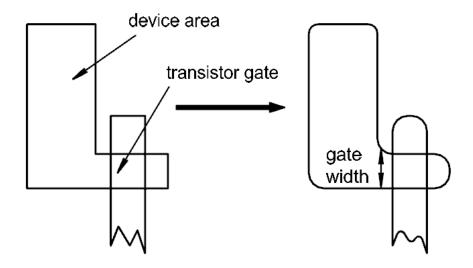

| 2.9  | The effect of corner rounding and how it can impact the gate. [4]                                                                                                                                                                  | 18 |

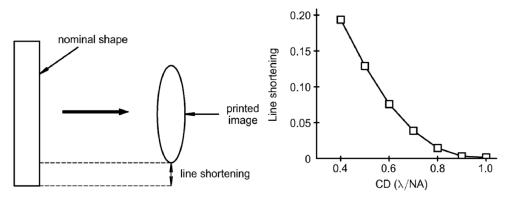

| 2.10 | Line-end Shortening has a strong dependence on process variations and the design proximity. [4]                                                                                                                                    | 18 |

| 2.11 | Inserting Auxiliary patterns to improve design immunity to process variations [5]                                                                                                                                                  | 19 |

| 2.12 | In Information Inf | 20 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

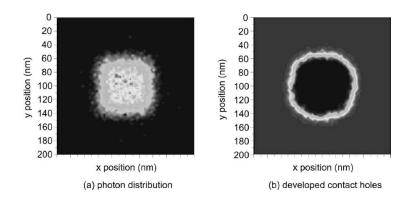

| 2.13 | Simulation of the exposure and development of a via hole with extreme ultraviolet lithography. [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

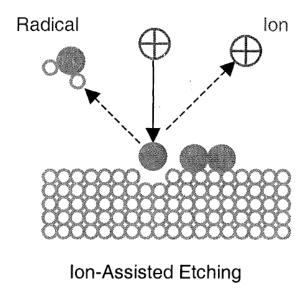

| 2.14 | An illustrative diagram for RIE. [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 |

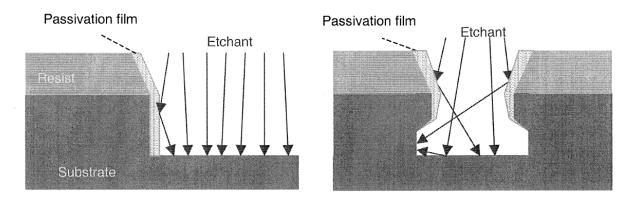

| 2.15 | An illustration of the root cause of the aperture effect in etching. [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22 |

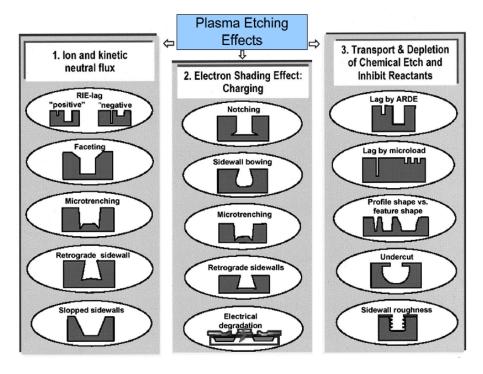

| 2.16 | RIE non-uniformity issues. [9]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23 |

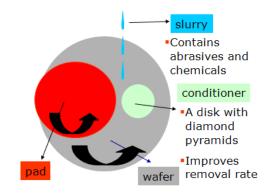

| 2.17 | An illustration of CMP process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23 |

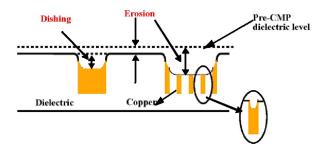

| 2.18 | CMP Metal Dishing and Dielectric Erosion. [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |

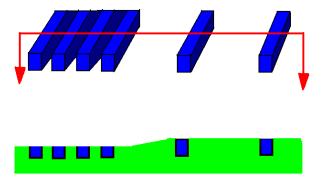

| 2.19 | Density-dependent thickness variations during CMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 |

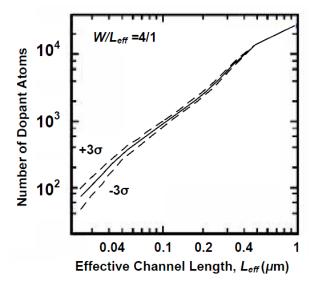

| 2.20 | The doping concentration variance increases as the technology shrinks. [11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27 |

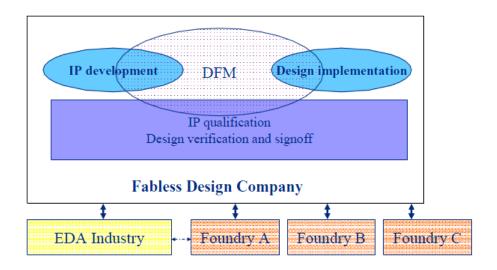

| 3.1  | DFM Model for Fabless companies. [12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31 |

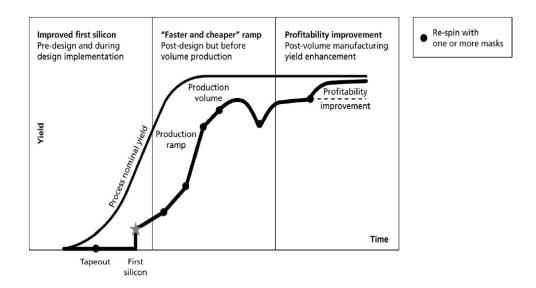

| 3.2  | DFM methodologies play a key role in the yield improvement of the first silicon, in achieving a more effective ramp to volume production and in improving the profitability during volume production. [13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31 |

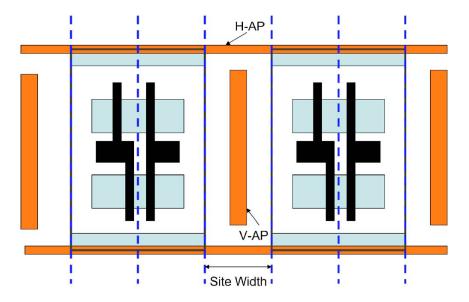

| 3.3  | Auxillary pattern insertion for a more regular poly pitch. [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |

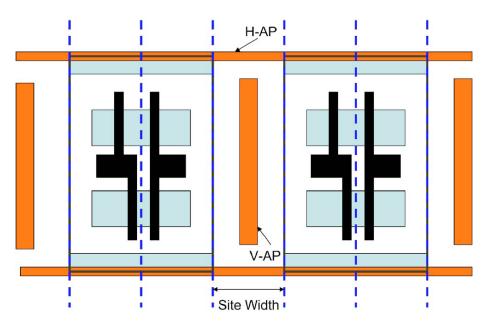

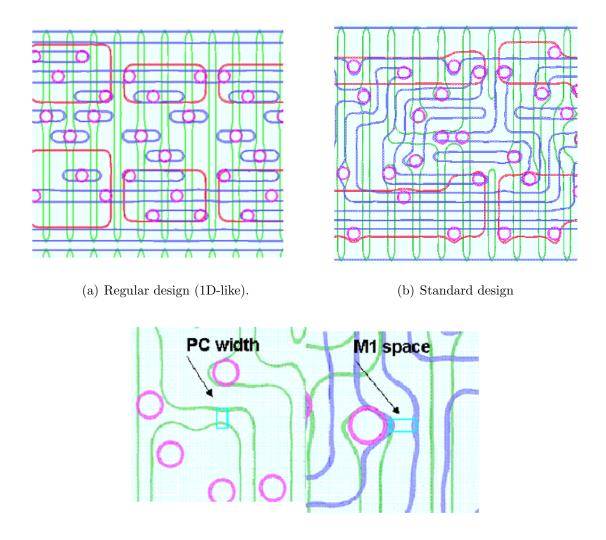

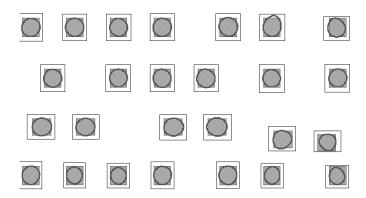

| 3.4  | Regular design fabrics tend to exhibit better immunity against process variations. [15]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

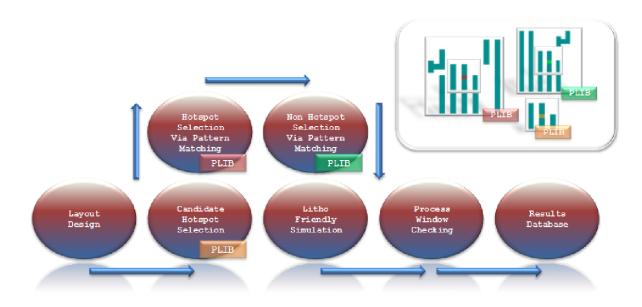

| 3.5  | Using a Hybrid Pattern Recognition- MBLFD approach to improve the LFD flow speed. [16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34 |

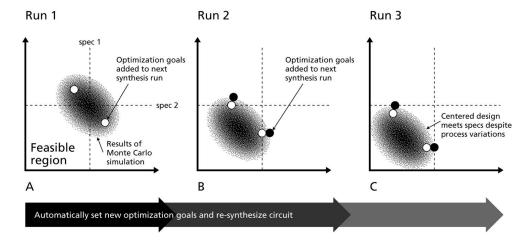

| 3.6  | Yield-focused design tools automatically center a design by iteratively adding corners in successive runs until the design is re-centered in the optimum feasibility region. [13]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35 |

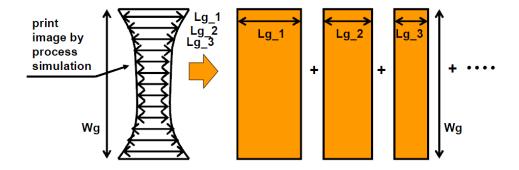

| 3.7  | Lithography Simulation and Gate Segmentation to extract the realistic device parameters. [17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36 |

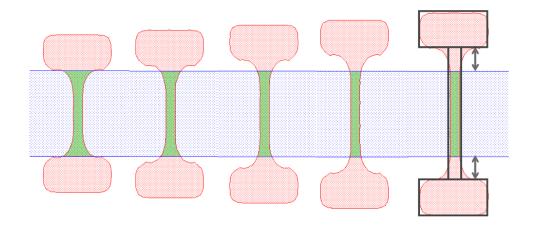

| 3.8  | Using lithography simulations to improve the gate length control. [17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

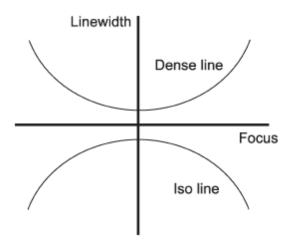

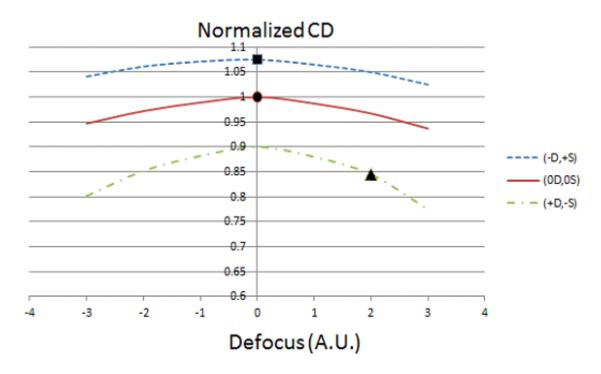

| 3.9  | An idealized Bossung plot representing the systematic and opposing behavior of dense and iso patterns through defocus. [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |

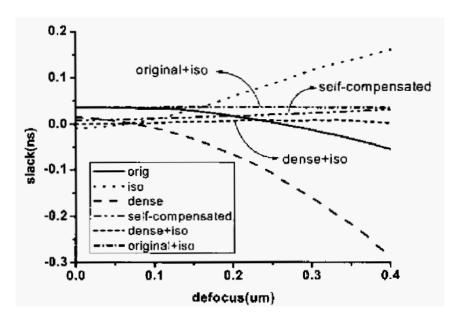

| 3.10 | Slack(ns) vs. defocus for a testcase showing the effective compensation in self-compensating design options. [19]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38 |

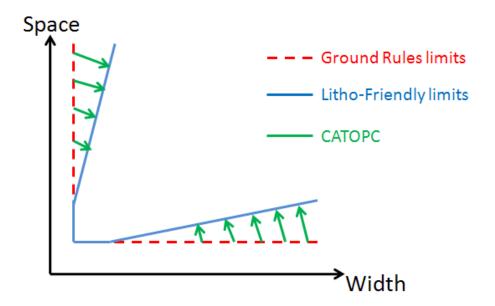

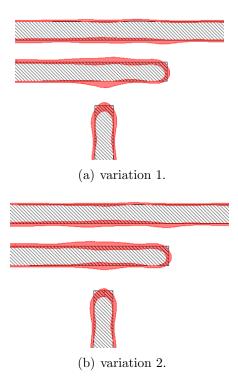

| 3.11 | Rules-Based (Geometry-Based) Retargeting to improve the yield                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 |

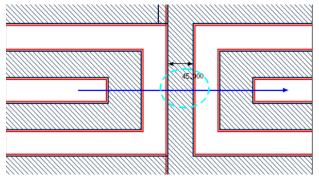

| 3.12 | The Aerial Image Intensity distribution showing that in advanced nodes the proximity effects extend even beyond directly adjacent design patterns | 40 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

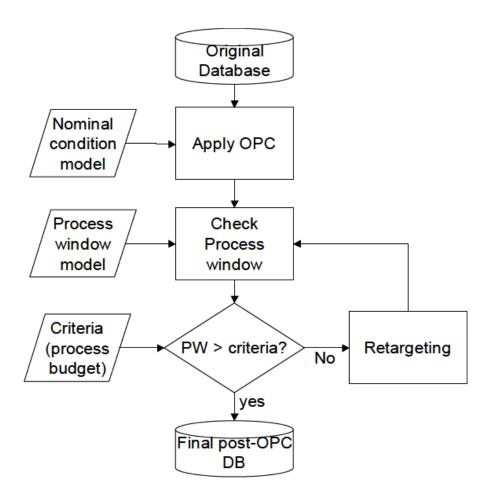

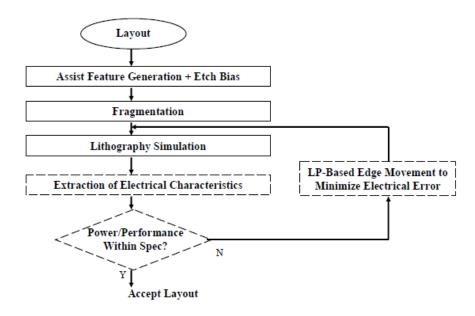

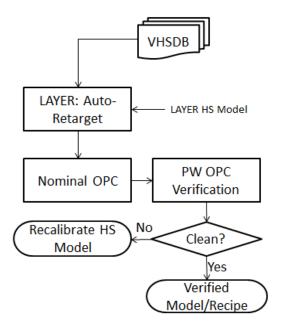

| 3.13 | The flow chart of during-OPC MBRT. [20]                                                                                                           | 42 |

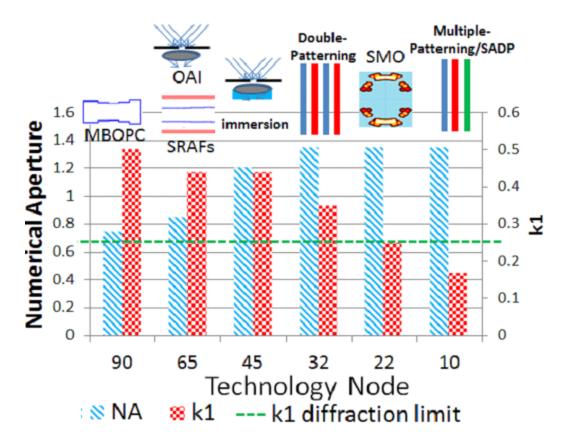

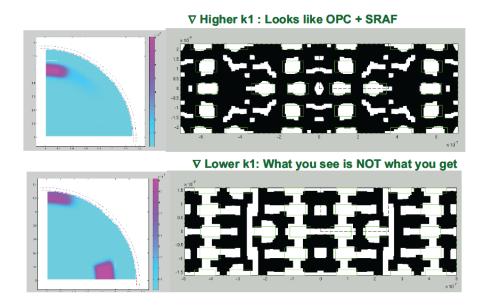

| 3.14 | An illustration of the RET evolution in sub-wavelength nodes, demonstrating both $k_1,\mathrm{NA}$ and the mainstream RET development             | 43 |

| 3.15 | Non-idealities in optical lithography. [21]                                                                                                       | 45 |

| 3.16 | An OPC example showing how an isolated pattern is printing with and without OPC. [1]                                                              | 45 |

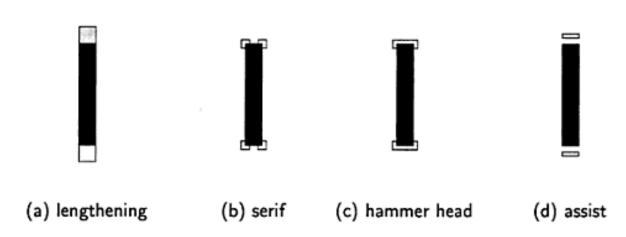

| 3.17 | An example of Rules-Based correction for Line-Ends. $[21]$                                                                                        | 47 |

| 3.18 | An example of Nominal Model-Based OPC                                                                                                             | 48 |

| 3.19 | Nominal MBOPC Flow                                                                                                                                | 49 |

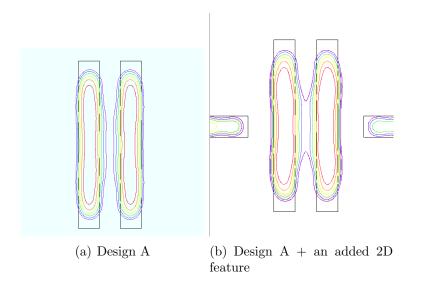

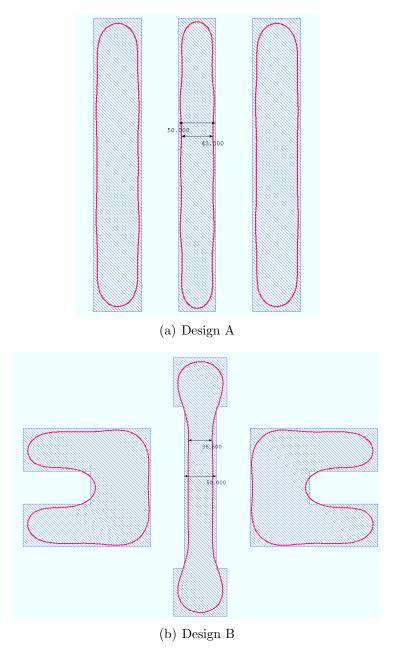

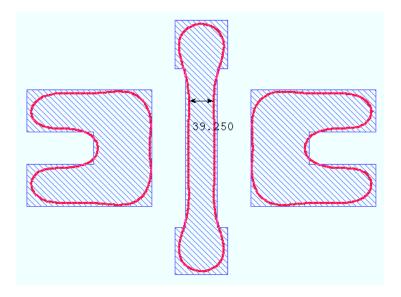

| 3.20 | The through-PW innermost resist contours comparison for to designs with the same width-space                                                      | 52 |

| 3.21 | Design B from figure 3.20(b) after applying PWOPC                                                                                                 | 53 |

| 3.22 | An example of ILT of a contact level. [22]                                                                                                        | 53 |

| 3.23 | Through-Process-Window performance improvement in ILT. [23]                                                                                       | 54 |

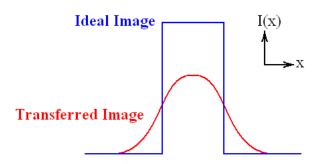

| 3.24 | An ideal (lossless with an infinite NA) vs. the practical transmitted image.                                                                      | 55 |

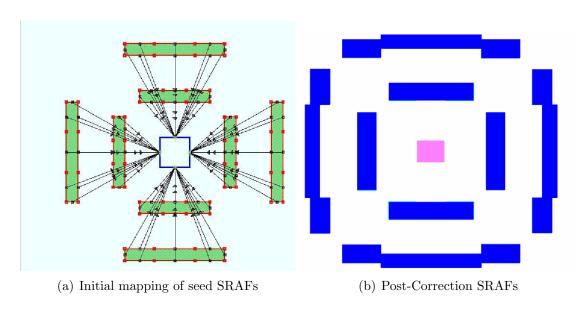

| 3.25 | Free-Form SRAFs in ILT (blue) vs. manufacturable SRAFs (red) [24]                                                                                 | 55 |

| 3.26 | Optimized Source and on-wafer improved printing quality. [25]                                                                                     | 56 |

| 3.27 | SMO Mask does not necessarily look close to the original target (green) at low $k_1$ values (i.e. at extremely aggressive RET). [26]              | 57 |

| 3.28 | The Basic Concept of DMOPC [27]                                                                                                                   | 58 |

| 3.29 | Nominal Contour segmentation into multiple transistor equivalent. $[28]$                                                                          | 58 |

| 3.30 | The flow chart of Electricall-Driven OPC flow. [28]                                                                                               | 59 |

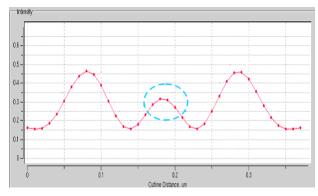

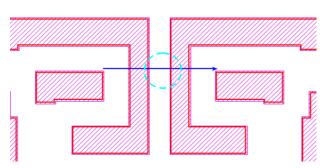

| 4.1  | Analyzing hot-spot (1)                                                                                                                            | 64 |

| 4.2  | Analyzing hot-spot (2)                                                                                                                            | 65 |

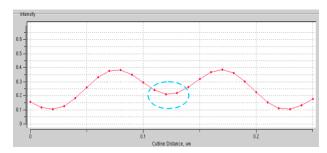

| 43   | The PW width errors manned on the I -I.                                                                                                           | 66 |

| 4.4  | Mapping the contours of constant contrast on the $I_{max}$ - $I_{min}$ map (while the severity level is color coded). It is shown that for the same contrast value passes through different regions of the map that goes between very critical and non critical |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

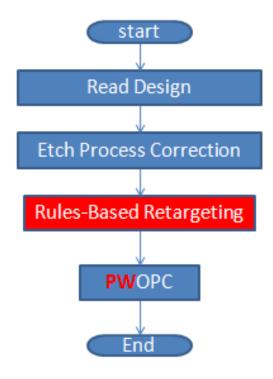

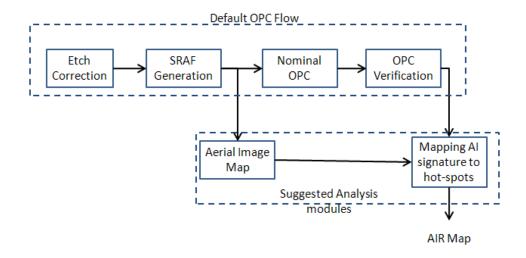

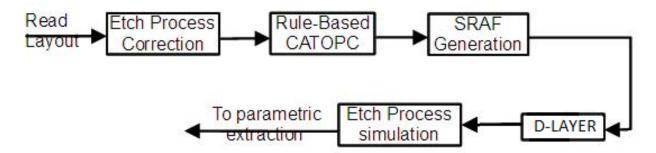

| 4.5  | Mask tapeout Flow after AIR insertion                                                                                                                                                                                                                           |

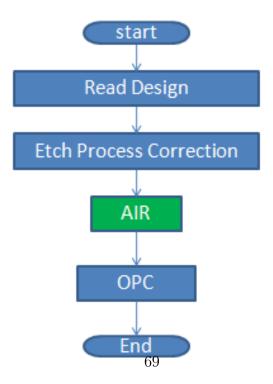

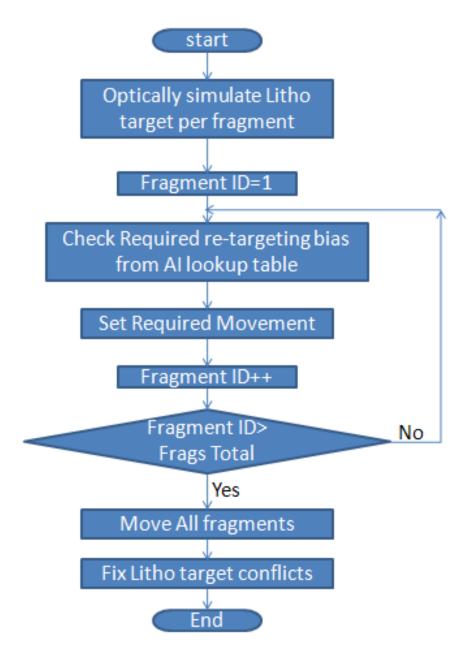

| 4.6  | AIR correction flow                                                                                                                                                                                                                                             |

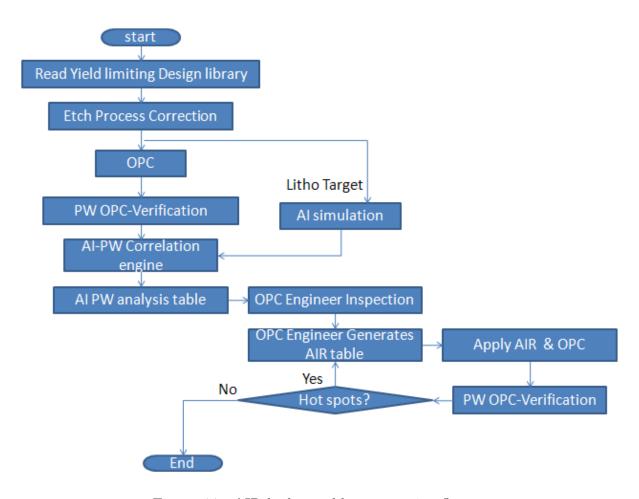

| 4.7  | AIR lookup table preparation flow.                                                                                                                                                                                                                              |

| 4.8  | The Flow used in generating the Aerial Image Maps                                                                                                                                                                                                               |

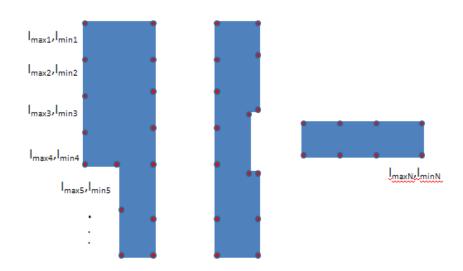

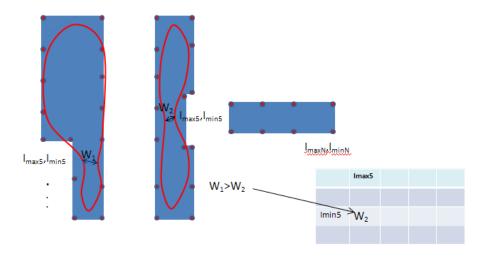

| 4.9  | Calculating the $I_{max}$ , $I_{min}$ , etc for each fragment                                                                                                                                                                                                   |

| 4.10 | Mapping the worst PW measurement to the AI map                                                                                                                                                                                                                  |

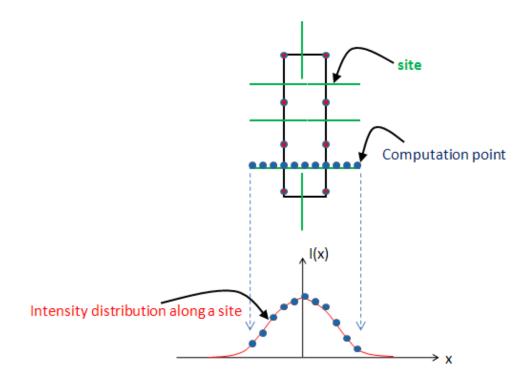

| 4.11 | The basic concept of Sparse Aerial Image intensity computation                                                                                                                                                                                                  |

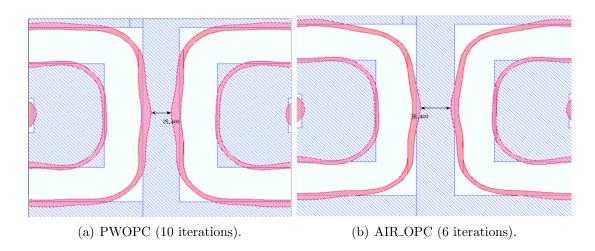

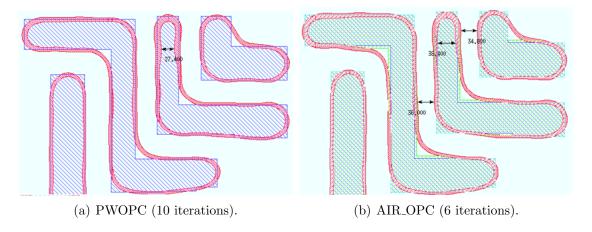

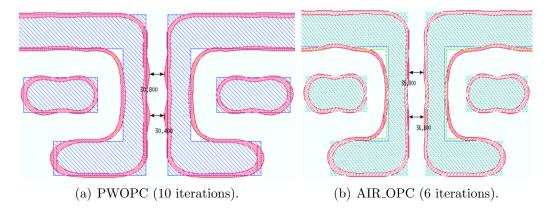

| 4.12 | Comparing PWOPC recipe vs. OPC+AIR for hot-spot (1)                                                                                                                                                                                                             |

| 4.13 | Comparing PWOPC recipe vs. OPC+AIR for hot-spot (2)                                                                                                                                                                                                             |

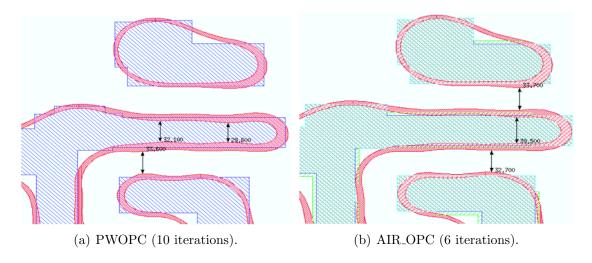

| 4.14 | Comparing PWOPC recipe vs. OPC+AIR for hot-spot (3)                                                                                                                                                                                                             |

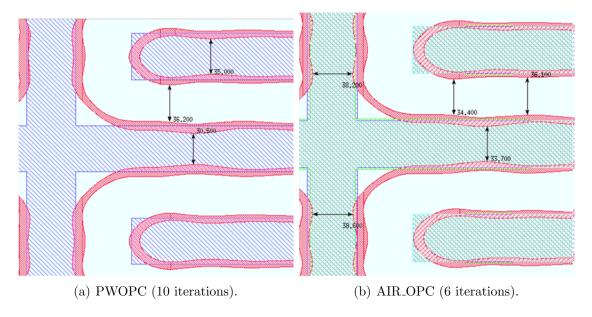

| 4.15 | Comparing PWOPC recipe vs. OPC+AIR for hot-spot (4)                                                                                                                                                                                                             |

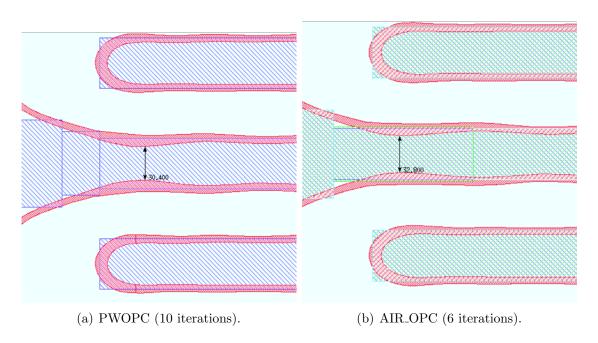

| 4.16 | Comparing PWOPC recipe vs. OPC+AIR for hot-spot (5)                                                                                                                                                                                                             |

| 4.17 | Comparing PWOPC recipe vs. OPC+AIR for hot-spot (6)                                                                                                                                                                                                             |

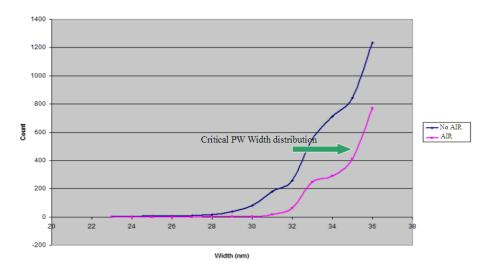

| 4.18 | Hot-spots Width distribution                                                                                                                                                                                                                                    |

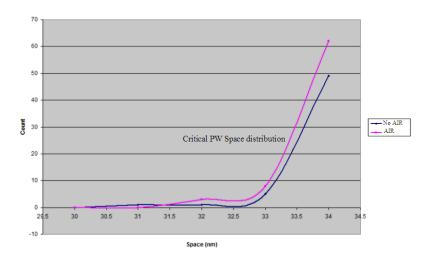

| 4.19 | Hot-spots Space distribution                                                                                                                                                                                                                                    |

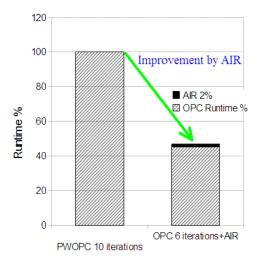

| 4.20 | Comparing the Runtime of PWOPC and AIR+OPC                                                                                                                                                                                                                      |

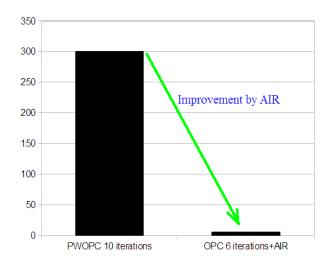

| 4.21 | Comparing Hot-spots count between PWOPC and AIR+OPC 8                                                                                                                                                                                                           |

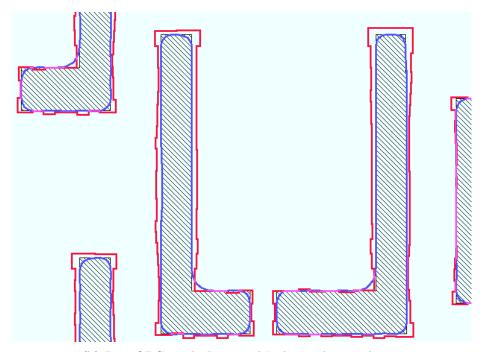

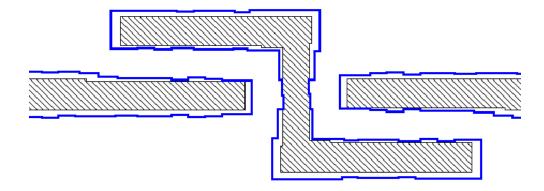

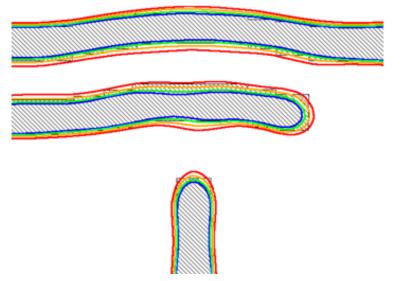

| 5.1  | An actual example comparing the final OPC mask to the OPC target, showing that the final mask shape is nothing but a perturbed joggy clone of the target shape.                                                                                                 |

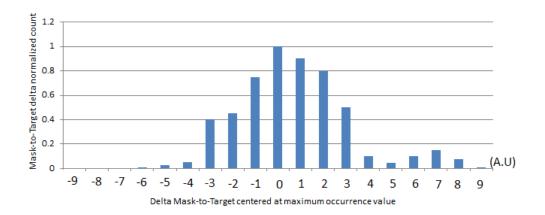

| 5.2  | An example of the normalized distribution of the mask-to-target delta distribution                                                                                                                                                                              |

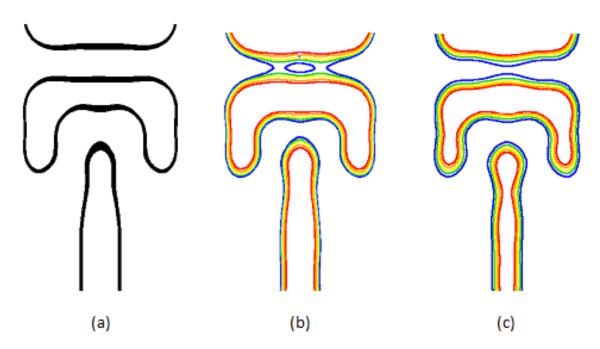

| 5.3  | Comparing the (a) post-OPC PVBands, optical simulation contours for both (b) post-OPC mask and (c) the pre-OPC target, they could have different magnitudes but they still share a reasonably similar behavior                                                  |

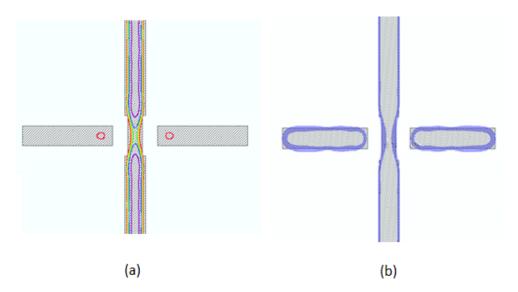

| 5.4  | Real simulation example showing the validity of using the optical simulation of the OPC target to capture potential lithography hot-spots. (a) Optical simulation contours at different threshold values. (b) Post-OPC PW verification PVBands, showing that the PW weakness is due to design aggressiveness and that it correlates to the contours in (b) 87 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5  | An illustration of the process variations Bossung plots and the choice of the simulation conditions to capture lithography hot-spots                                                                                                                                                                                                                          |

| 5.6  | Flow chart of the LAYER model calibration                                                                                                                                                                                                                                                                                                                     |

| 5.7  | Flow chart of the LAYER model verification                                                                                                                                                                                                                                                                                                                    |

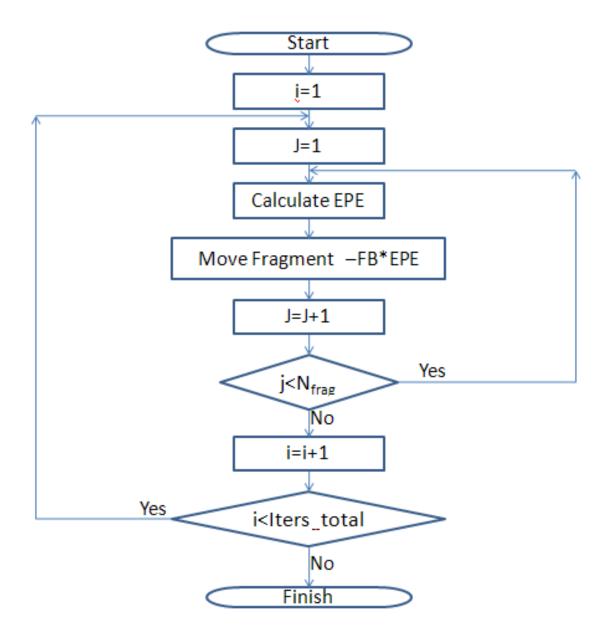

| 5.8  | The flow diagram of the design Auto-Correction using LAYER 92                                                                                                                                                                                                                                                                                                 |

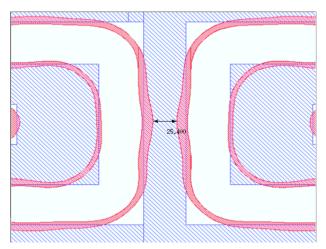

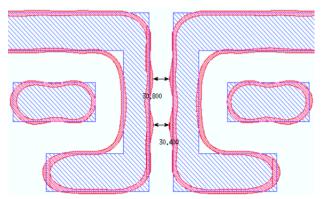

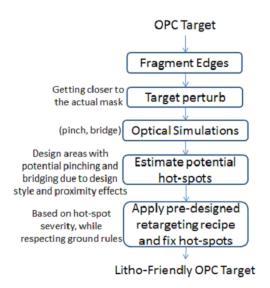

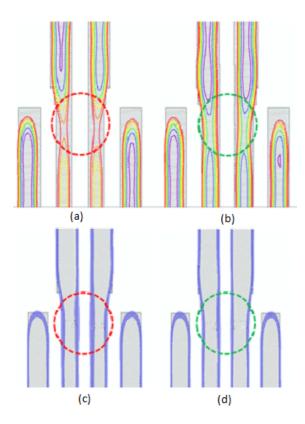

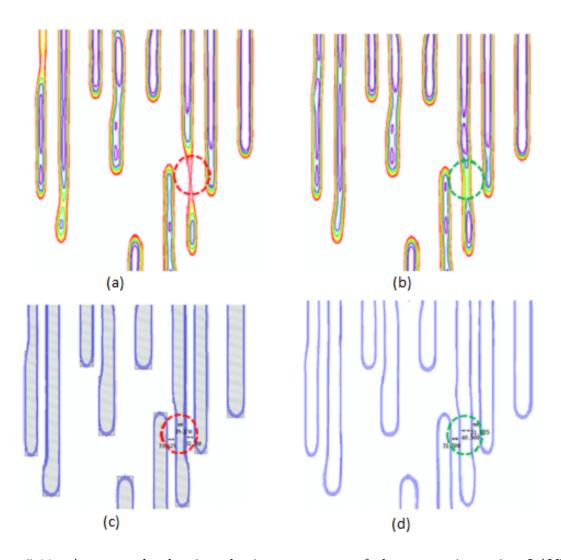

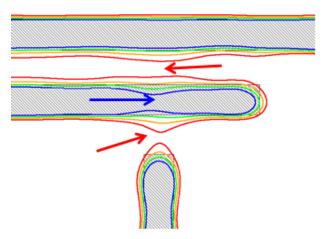

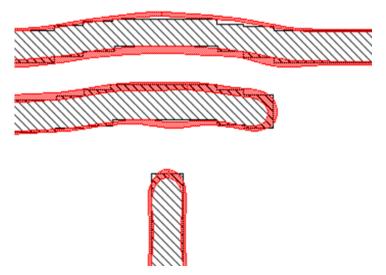

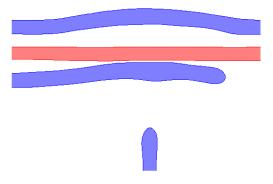

| 5.9  | An example showing the improvements of the patterning using LAYER.  (a) The optical simulation contours of the Target shapes. (b) The optical simulation contours post LAYER. (c) Post-PWOPC PW Verification contours without LAYER. (d) Post-Nominal OPC PW Verification contours with LAYER.                                                                |

| 5.10 | An example showing the improvements of the patterning using LAYER.  (a) The optical simulation contours of the Target shapes. (b) The optical simulation contours post LAYER. (c) Post-PWOPC PW Verification contours without LAYER. (d) Post-Nominal OPC PW Verification contours with LAYER.                                                                |

| 5.11 | An example showing the improvements of the patterning using LAYER.  (a) The optical simulation contours of the Target shapes. (b) The optical simulation contours post LAYER. (c) Post-PWOPC PW Verification contours without LAYER. (d) Post-Nominal OPC PW Verification contours with LAYER.                                                                |

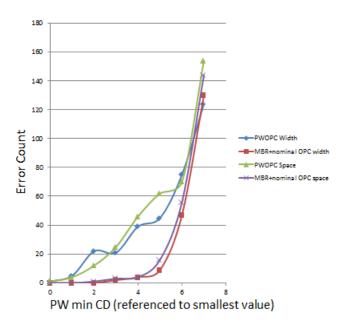

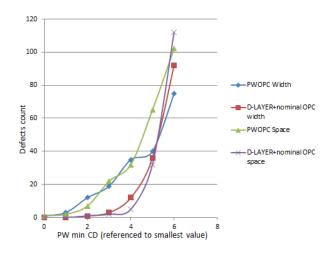

| 5.12 | The PW width and space hot-spots distribution comparison between the reference PWOPC solution and the proposed LAYER solution. X-axis is the PW CD delta to the minimum CD of the PWOPC hot-spots 96                                                                                                                                                          |

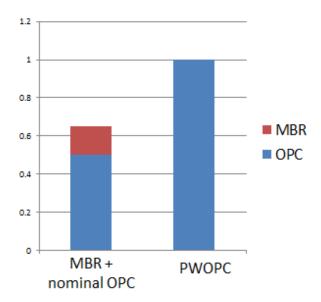

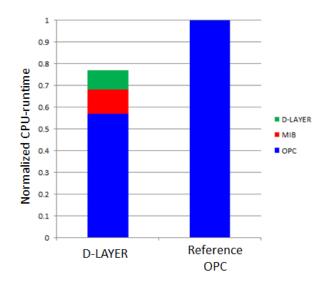

| 5.13 | Normalized resource-runtime product comparison between the reference PWOPC recipe and the LAYER+nominal OPC solution                                                                                                                                                                                                                                          |

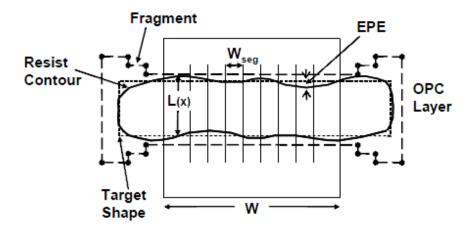

| 6.1  | A demonstration of OPC basic concepts, (a) Pre-OPC fragmentation and Litho simulation for a pre-OPC mask, where the dots represent the fragmentation points, while the contour predicts the wafer printing if no OPC is used. (b) Post-OPC mask-shape (red) and Litho-simulation (blue) 103                                                                   |

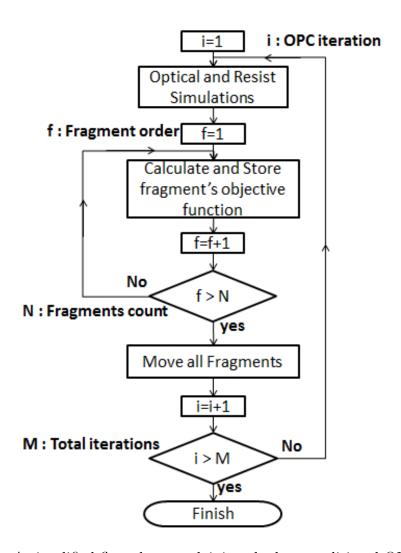

| 6.2  | A simplified flow chart explaining the how traditional OPC works                                                                                                               | 102 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

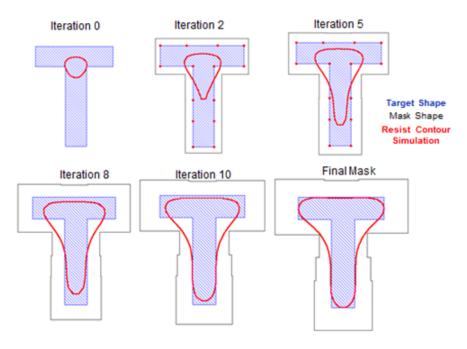

| 6.3  | An example of the evolution of the mask shape                                                                                                                                  | 103 |

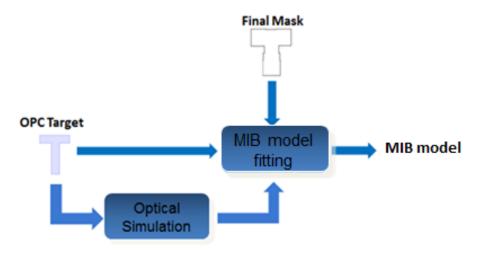

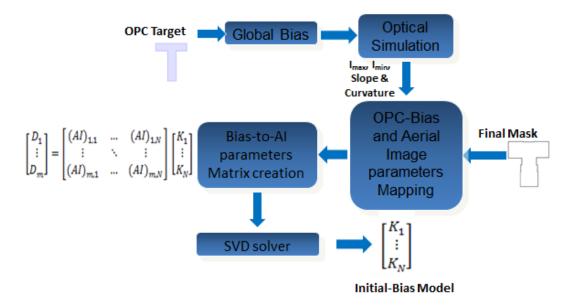

| 6.4  | An illustrative diagram of MIB model calibration                                                                                                                               | 104 |

| 6.5  | An illustrative diagram of using MIB to improve the OPC initial condition.                                                                                                     | 104 |

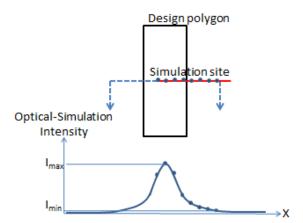

| 6.6  | An illustration of the main intensity parameters along the simulation sites.                                                                                                   | 105 |

| 6.7  | An illustration of MIB model calibration flow                                                                                                                                  | 107 |

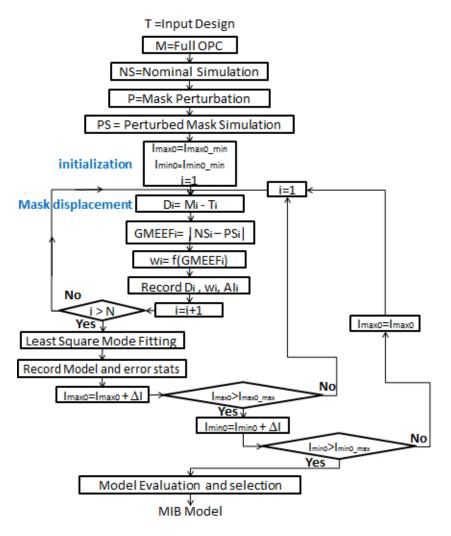

| 6.8  | A detailed Flow Chart for the MEEF-Aware MIB Model Calibration                                                                                                                 | 109 |

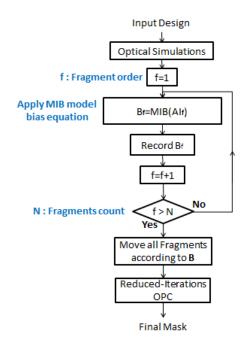

| 6.9  | A detailed Flow Chart for the integration of MIB inside the OPC flow                                                                                                           | 111 |

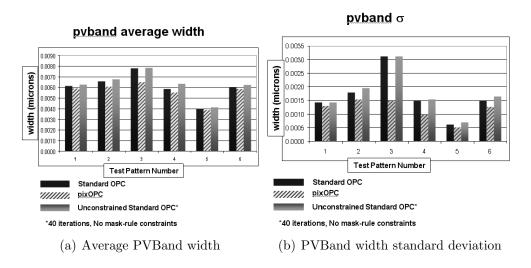

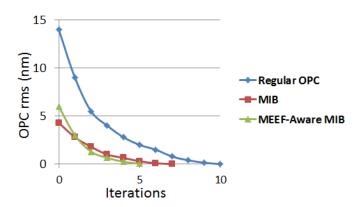

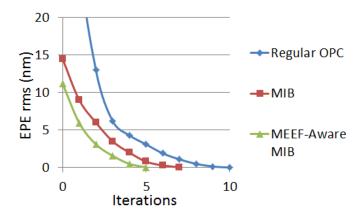

| 6.10 | OPC mask conversion comparison showing how MIB and MEEF-Aware MIB are improving the OPC convergence of metal layer.                                                            | 113 |

| 6.11 | EPE conversion comparison showing how MIB and MEEF-Aware MIB are improving the OPC convergence of metal layer.                                                                 | 113 |

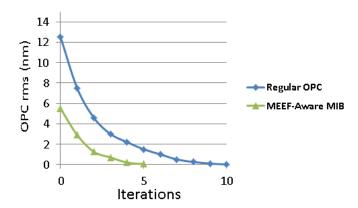

| 6.12 | EPE conversion comparison showing how MIB and MEEF-Aware MIB are improving the OPC convergence of metal layer.                                                                 | 114 |

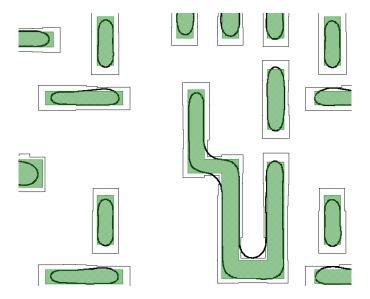

| 6.13 | OPC mask conversion comparison showing how MIB and MEEF-Aware MIB are improving the OPC convergence of via layer                                                               | 115 |

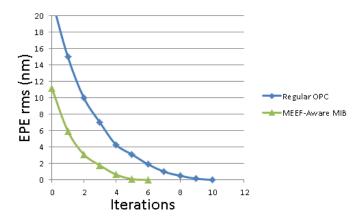

| 6.14 | EPE conversion comparison showing how MIB and MEEF-Aware MIB are improving the OPC convergence of via layer                                                                    | 115 |

| 6.15 | EPE conversion comparison showing how MIB and MEEF-Aware MIB are improving the OPC convergence of via layer                                                                    | 116 |

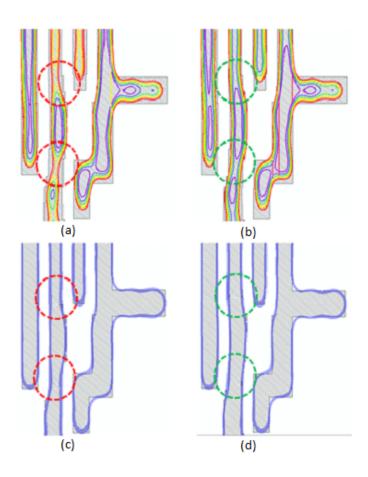

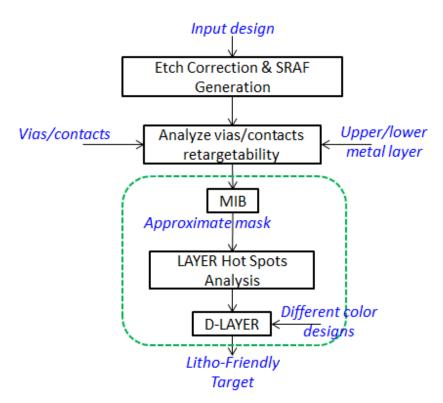

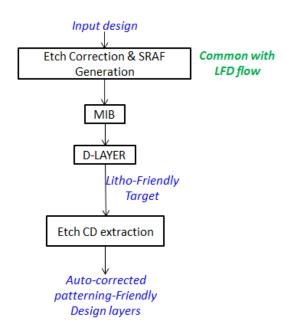

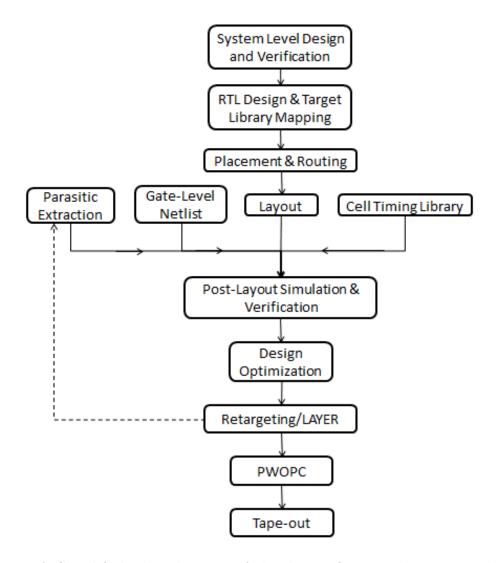

| 7.1  | An illustration of the overall MBR flow after integrating MIB and LAYER models                                                                                                 | 118 |

| 7.2  | Potential hot spots captured by the LAYER model and verified using PW simulations after PWOPC                                                                                  | 120 |

| 7.3  | PW simulations for PWOPC recipe variations and it is clear that no solution can ultimately fix all hot spots, but rather making one of them worse on the expense of the others | 121 |

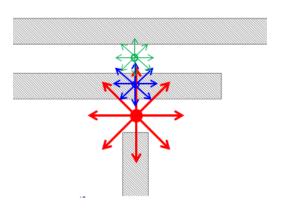

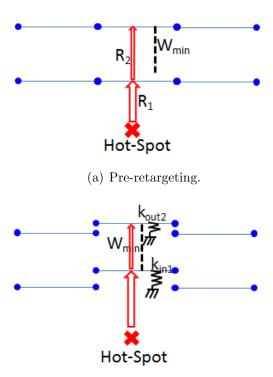

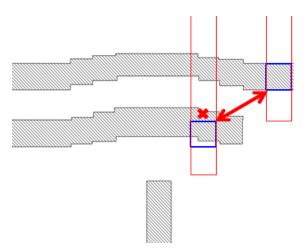

| 7.4  | Retargeting force flux representation of lithography hot-spots                                                                                                                 | 121 |

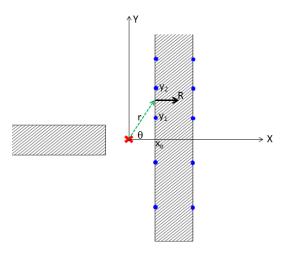

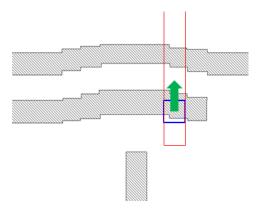

| 7.5  | An illustrative diagram explaining the retargeting force R originating from the hot-spot center and forcing the fragment shift away from it                                    | 123 |

| 7.6  | Distributed retargeting output from D-LAYER methodology                                                                                                                                      | 123 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.7  | D-LAYER successfully applying the distributed retargeting and fixing the lithography hot-spots.                                                                                              | 124 |

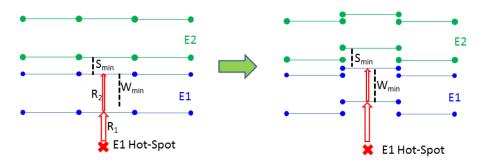

| 7.8  | Applying minimum CD constrains together with retargetability as restraining forces to prevent from over-retargeting                                                                          | 126 |

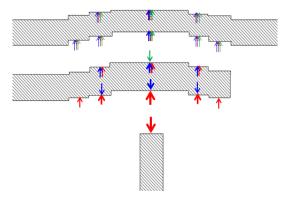

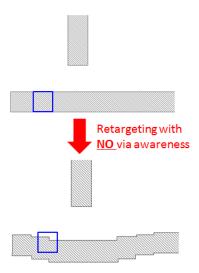

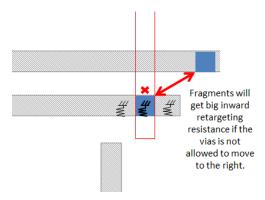

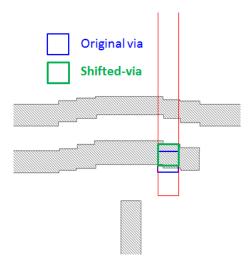

| 7.9  | Retargeting needs to be Multi-layer aware otherwise poor connectivity situations could arise due to via layer exposure                                                                       | 127 |

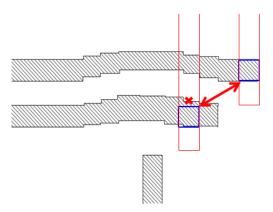

| 7.10 | Metal-above (red) extension affects how a via (blue) would affect the retargeting                                                                                                            | 128 |

| 7.11 | Via-to-via spacing (red arrow) affects how a via would affect the retargeting retargeting.                                                                                                   | 128 |

| 7.12 | An illustration of how the via retargetability is linked to the metal fragments retargetability by increasing their spring constant                                                          | 129 |

| 7.13 | D-LAYER output after adding the via awareness, the retargeting is minimized near where the via is positioned to ensure its coverage post D-LAYER                                             | 129 |

| 7.14 | Retargeting needs to be Multi-layer aware otherwise poor connectivity situations could arise due to via layer exposure                                                                       | 130 |

| 7.15 | Post-etch simulations show how model-based metal retargeting can result into short circuit risks in multiple patterning if the different color distances are not respected                   | 130 |

| 7.16 | Multiple patterning-aware D-LAYER by enforcing minimum spacing between different color designs and allowing the different color design to move around to give more space to the hot-spot fix | 131 |

| 7.17 | Multiple patterning-aware D-LAYER can apply implicit retargeting to different color designs to avoid inter-color bridging                                                                    | 131 |

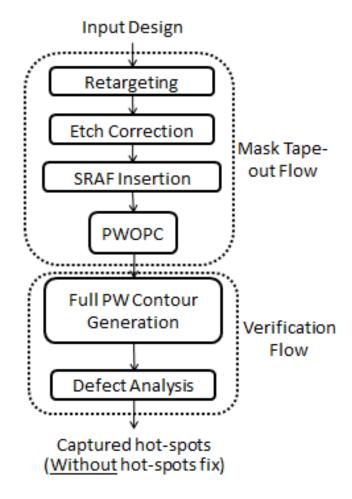

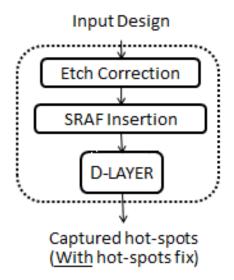

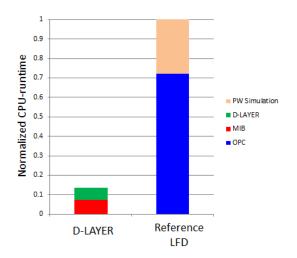

| 7.18 | The general flow for using D-LAYER in the mask tape-out flow or in LFD.                                                                                                                      | 132 |

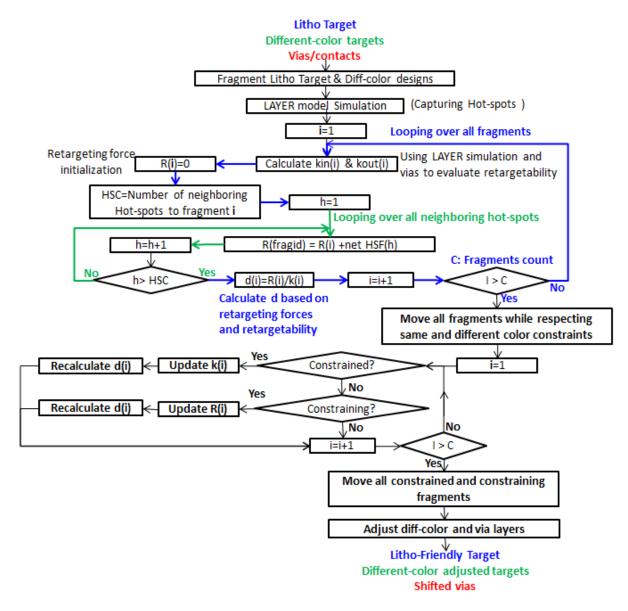

| 7.19 | The flow chart explaining the details of the D-LAYER implementation                                                                                                                          | 134 |

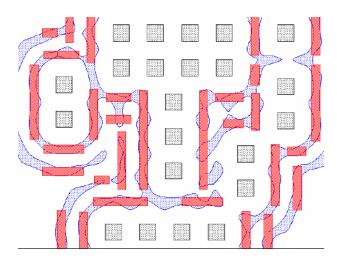

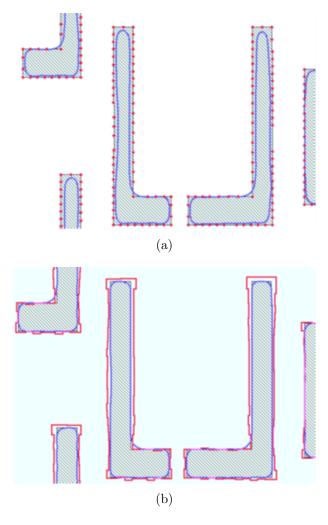

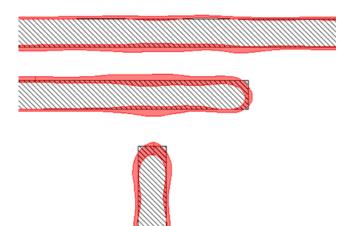

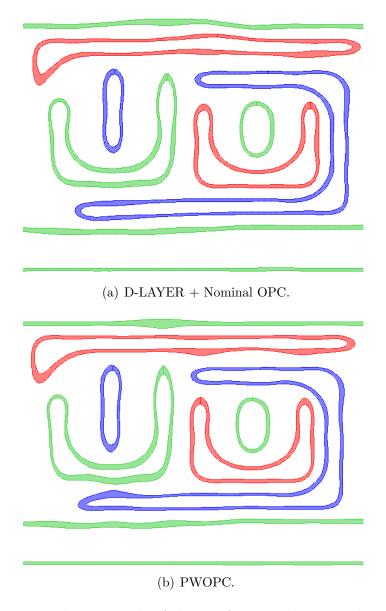

| 7.20 | Comparing the PVBands of the D-LAYER solution to the reference PWOPC solution as expected on wafer for the multiple patterning solution                                                      | 136 |

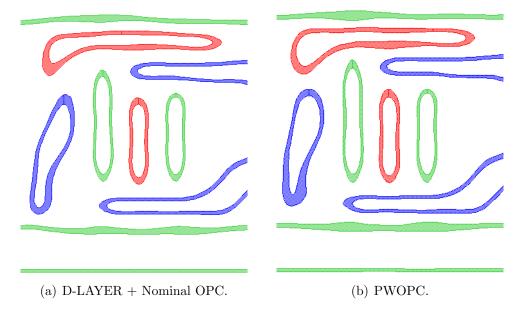

| 7.21 | Comparing the post-etch PVBands of the D-LAYER solution to the reference PWOPC solution, D-LAYER shows better overall results                                                                | 137 |

| 7.22 | Through PW width and space CD distribution, comparing the tail distribution for both D-LAYER and the reference PWOPC                                                                                              | 137 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|