## Parallelizing quantum circuit synthesis

by

### Olivia Di Matteo

A thesis presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Master of Science in Physics - Quantum Information

Waterloo, Ontario, Canada, 2015

© Olivia Di Matteo 2015

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

We present an algorithmic framework for parallel quantum circuit synthesis using meet-in-the-middle synthesis techniques. We also present two implementations thereof, using both threaded and hybrid parallelization techniques.

We give examples where applying parallelism offers a speedup on the time of circuit synthesis for 2and 3-qubit circuits. We use a threaded algorithm to synthesize 3-qubit circuits with optimal T-count 9, and 11, breaking the previous record of T-count 7. As the estimated runtime of the framework is inversely proportional to the number of processors, we propose an implementation using hybrid parallel programming which can take full advantage of a computing cluster's thousands of cores. This implementation has the potential to synthesize circuits which were previously deemed impossible due to the exponential runtime of existing algorithms.

#### Acknowledgements

I am very grateful to my supervisor Michele Mosca for introducing me to an interesting area of work, and always being willing to try out new ideas. I also thank my advisory committee members Richard Cleve, Daniel Gottesman, and Roger Melko for their useful input on my progress, and Vlad Gheorghiu for reading through this entire thesis and providing very helpful comments.

I am lucky to have been able to consult with many senior (now former) members of our research group. David Gosset and Vadym Kliuchnikov are indispensable, and I can't thank them enough for helping me understand their T-count algorithm, offering suggestions for my implementations, and simply being around and willing to let me bounce ideas off them. Stacey Jeffery helped get me on the right track with complexity analysis of my algorithm, in addition to providing company as an office mate.

Conversations with Erik Schnetter about MPI were very helpful while getting started, and ultimately led to the ideas behind the hybrid parallel scheme of Chapter 6. I also thank Matt Amy, who's original meet-in-the-middle algorithm and code served as a starting point for my own implementation. Theo Belaire and Gary Graham helped sanity check my code when it did strange things.

I'm grateful to my parents for encouraging me to pursue a graduate degree, and Gary for supporting me throughout and making sure I took time to relax. Friends in the circuit synthesis group, IQC members, and my office mates Mária and Chunhao were very supportive and provided much-needed distractions. They also put up with my ramblings, such as "look at this pretty graph!", "my program found a claw!" and "all my computing jobs failed". I'm lucky to have had my coworkers at Udacity cheering me on from across the continent; my work there has taught me many useful things which helped with the writing of this thesis. Finally, I thank my undergraduate supervisor Hubert de Guise for his excellent mentorship, and for reminding me that a 50-page thesis will only get me 50%.

I acknowledge SHARCNET for use of their computing resources, and conservations with Jemmy Hu which taught me how to make best use of their machines. Funding for this research was provided by NSERC, the Department of Physics and Astronomy, and the Institute for Quantum Computing.

## Contents

| 1        | Introduction                                                |                                                                                                                                                                                          |   |  |  |  |  |  |  |  |  |  |

|----------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|--|--|--|

|          | 1.1                                                         | Quantum compilation                                                                                                                                                                      | 1 |  |  |  |  |  |  |  |  |  |

|          | 1.2                                                         | Quantum circuits                                                                                                                                                                         | 1 |  |  |  |  |  |  |  |  |  |

|          |                                                             |                                                                                                                                                                                          | 1 |  |  |  |  |  |  |  |  |  |

|          |                                                             | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                  | 2 |  |  |  |  |  |  |  |  |  |

|          | 1.3                                                         | Parallel computing                                                                                                                                                                       | 3 |  |  |  |  |  |  |  |  |  |

|          | 1.4                                                         | Thesis objective                                                                                                                                                                         | 5 |  |  |  |  |  |  |  |  |  |

| <b>2</b> | Qua                                                         | Quantum circuit synthesis 6                                                                                                                                                              |   |  |  |  |  |  |  |  |  |  |

|          | 2.1                                                         | An overview of existing algorithms                                                                                                                                                       | 6 |  |  |  |  |  |  |  |  |  |

|          | 2.2                                                         | Meet-in-the-middle circuit synthesis                                                                                                                                                     | 3 |  |  |  |  |  |  |  |  |  |

|          | 2.3                                                         | An algorithm for the $T$ -count $\ldots \ldots \ldots$                   | 0 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 2.3.1 Smallest denominator exponents                                                                                                                                                     | ) |  |  |  |  |  |  |  |  |  |

|          |                                                             | 2.3.2 The channel representation                                                                                                                                                         | 1 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 2.3.3 Coset labels                                                                                                                                                                       | 1 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 2.3.4 Finding $T$ -optimal circuit decompositions $\ldots \ldots \ldots$ | 2 |  |  |  |  |  |  |  |  |  |

| 3        | Parallel collision finding 15                               |                                                                                                                                                                                          |   |  |  |  |  |  |  |  |  |  |

|          | 3.1                                                         | Overview                                                                                                                                                                                 | 5 |  |  |  |  |  |  |  |  |  |

|          | 3.2                                                         | Algorithm details                                                                                                                                                                        | 5 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 3.2.1 Collisions and claws                                                                                                                                                               | 5 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 3.2.2 Collision finding                                                                                                                                                                  | 6 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 3.2.3 Claw finding 18                                                                                                                                                                    | 8 |  |  |  |  |  |  |  |  |  |

| <b>4</b> | Apr                                                         | Application of parallel framework to circuit synthesis 20                                                                                                                                |   |  |  |  |  |  |  |  |  |  |

|          | $4.1^{-1}$                                                  | Framework                                                                                                                                                                                | C |  |  |  |  |  |  |  |  |  |

|          | 4.2                                                         | Runtime estimation and algorithm complexity                                                                                                                                              | 1 |  |  |  |  |  |  |  |  |  |

|          | 4.3                                                         | Applications and use cases                                                                                                                                                               | 1 |  |  |  |  |  |  |  |  |  |

| <b>5</b> | Implementation details and results of threaded algorithm 23 |                                                                                                                                                                                          |   |  |  |  |  |  |  |  |  |  |

|          | $5.1^{-1}$                                                  | MITM for optimal <i>T</i> -count circuit synthesis                                                                                                                                       | 3 |  |  |  |  |  |  |  |  |  |

|          | 5.2                                                         | Implementation                                                                                                                                                                           | 4 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 5.2.1 Language and computer specifications                                                                                                                                               | 4 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 5.2.2 Special techniques to make the program faster $\dots \dots \dots$                  | 4 |  |  |  |  |  |  |  |  |  |

|          |                                                             | 5.2.3 Program flow                                                                                                                                                                       | 6 |  |  |  |  |  |  |  |  |  |

|          | 5.3                                                         | Results                                                                                                                                                                                  | С |  |  |  |  |  |  |  |  |  |

|          |                                                             | 5.3.1 Timing random parallel code                                                                                                                                                        | C |  |  |  |  |  |  |  |  |  |

|          |                                                             | 5.3.2 2-qubit synthesis                                                                                                                                                                  | C |  |  |  |  |  |  |  |  |  |

|        |                                                                              |                                      | 5.3.2.a                              | Controlled-Hadamard                          | 30               |

|--------|------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------|------------------|

|        |                                                                              |                                      | $5.3.2.\mathrm{b}$                   | Controlled-phase                             | 32               |

|        |                                                                              |                                      | 5.3.2.c                              | Varying the $T$ -count                       | 32               |

|        |                                                                              | 5.3.3                                | 3-qubit s                            | synthesis                                    | 33               |

|        |                                                                              |                                      | 5.3.3.a                              | T-count 7                                    | 33               |

|        |                                                                              |                                      | $5.3.3.\mathrm{b}$                   | A new regime: $T$ -count 9 and $T$ -count 11 | 38               |

|        |                                                                              |                                      | 5.3.3.c                              | Varying the number of threads                | 39               |

|        |                                                                              |                                      | 5.3.3.d                              | Varying the fraction of distinguished points | 40               |

|        | 5.4                                                                          | Algori                               | thm limit                            | ations                                       | 41               |

|        |                                                                              |                                      |                                      |                                              |                  |

| 6      | Adv                                                                          | vanced                               | implem                               | entation: hybrid parallel programming        | 42               |

| 6      | <b>Adv</b><br>6.1                                                            |                                      | -                                    | entation: hybrid parallel programming        | <b>42</b><br>42  |

| 6      |                                                                              | Progra                               | am flow .                            |                                              |                  |

| 6      | 6.1                                                                          | Progra<br>Prelim                     | am flow .<br>linary res              |                                              | 42               |

| 6<br>7 | $     \begin{array}{l}       6.1 \\       6.2 \\       6.3     \end{array} $ | Progra<br>Prelim<br>Advan            | am flow .<br>iinary res<br>tages and | ults                                         | 42 $43$          |

| 7      | $     \begin{array}{l}       6.1 \\       6.2 \\       6.3     \end{array} $ | Progra<br>Prelim<br>Advan<br>at else | am flow .<br>iinary res<br>tages and | ults      l limitations                      | $42 \\ 43 \\ 45$ |

# List of Figures

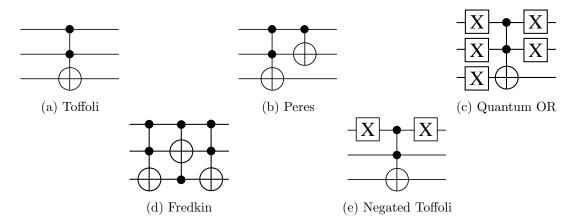

| $1.1 \\ 1.2$ | Quantum circuit depth    2      Commonly used gates in quantum circuits    3                                                |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|

| 2.1          | Timeline of circuit synthesis algorithms                                                                                    |

| 3.1          | Schematic of trail used in collision finding 16                                                                             |

| 3.2          | Trails and distinguished points 16                                                                                          |

| 3.3          | Colliding trails                                                                                                            |

| 3.4          | Claw-finding trails                                                                                                         |

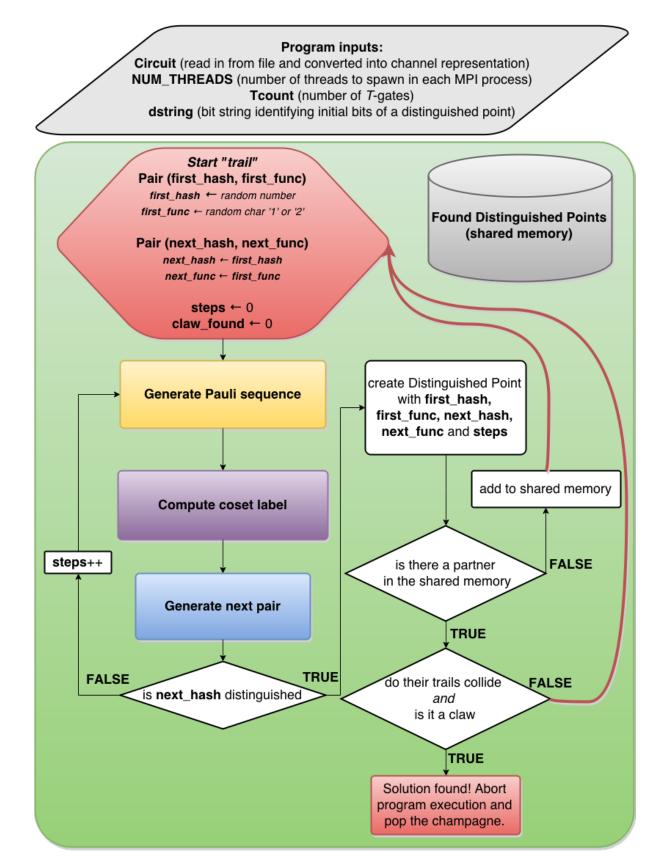

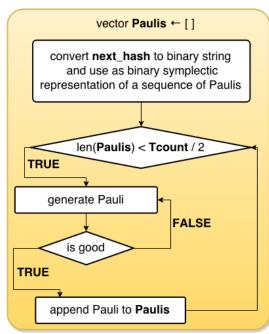

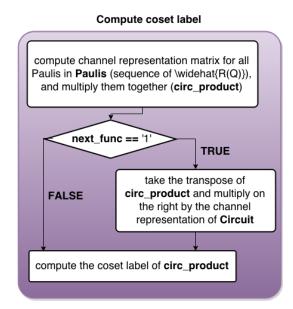

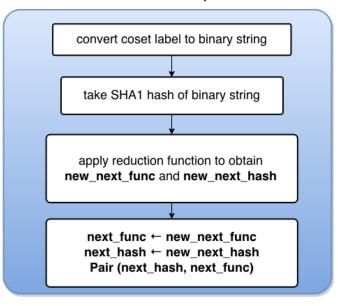

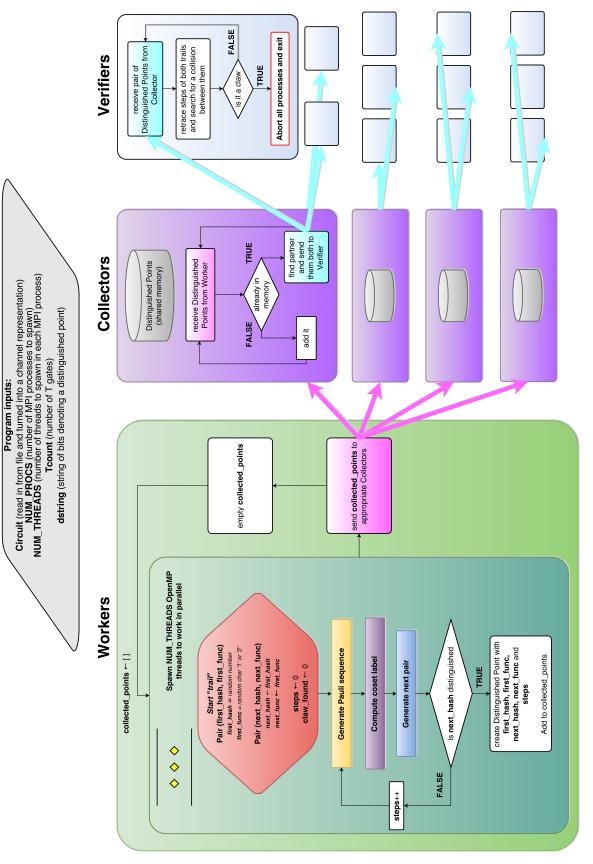

| 5.1          | Algorithm flowchart for OpenMP implementation                                                                               |

| 5.2          | Subroutine flowcharts                                                                                                       |

| 5.3          | Controlled-Hadamard                                                                                                         |

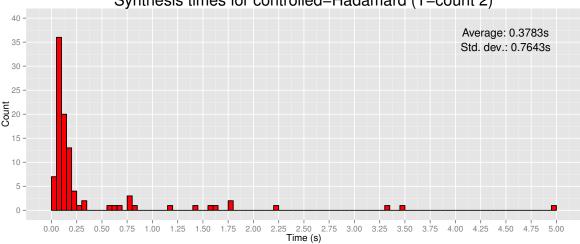

| 5.4          | Histogram of controlled-Hadamard runtimes                                                                                   |

| 5.5          | Controlled-phase                                                                                                            |

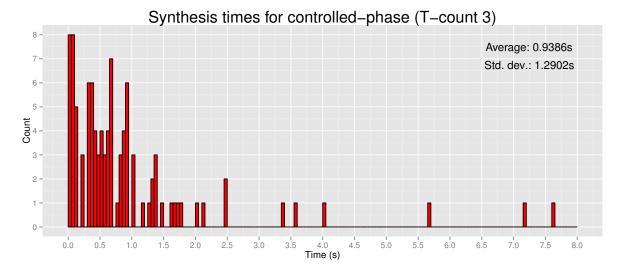

| 5.6          | Histogram of controlled-phase runtimes                                                                                      |

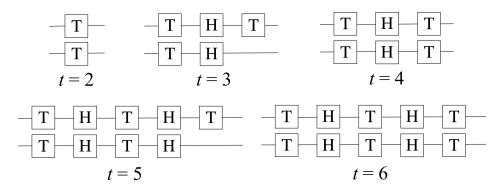

| 5.7          | Circuit series with varying $T$ -count $\ldots \ldots 33$    |

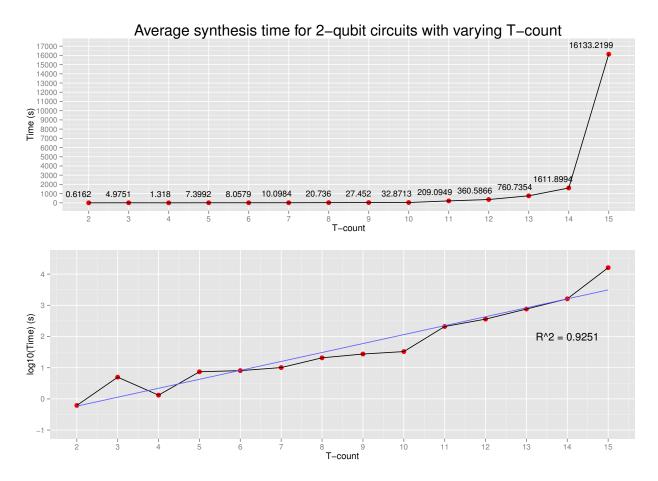

| 5.8          | Synthesis times of circuits with varying <i>T</i> -count                                                                    |

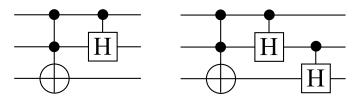

| 5.9          | 3-qubit circuits with $T$ -count 7 $\ldots \ldots 35$        |

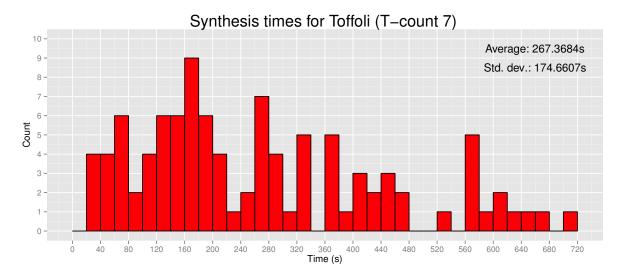

| 5.10         | Histogram of Toffoli synthesis times                                                                                        |

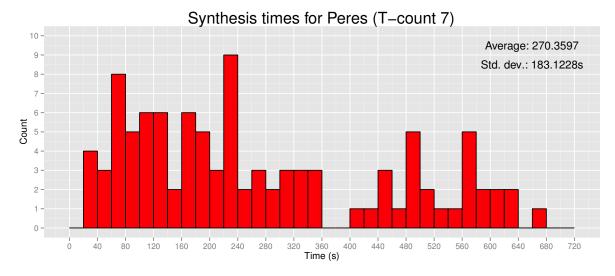

| 5.11         | Histogram of Peres synthesis times                                                                                          |

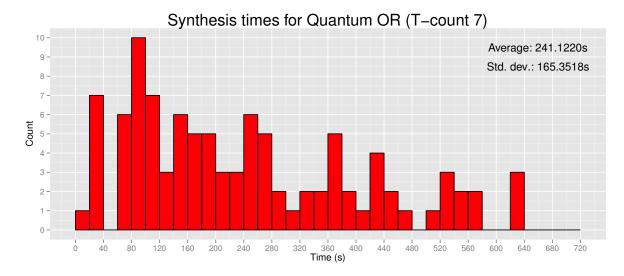

| 5.12         | Histogram of QOR synthesis times                                                                                            |

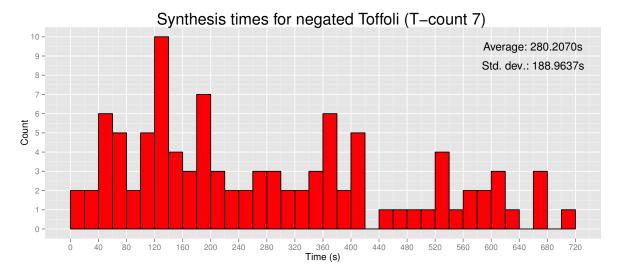

| 5.13         | Histogram of negated Toffoli synthesis times                                                                                |

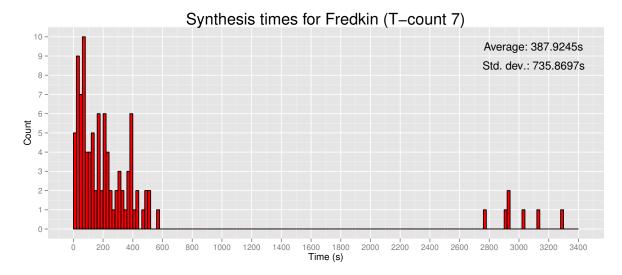

| 5.14         | Histogram of negated Fredkin synthesis times                                                                                |

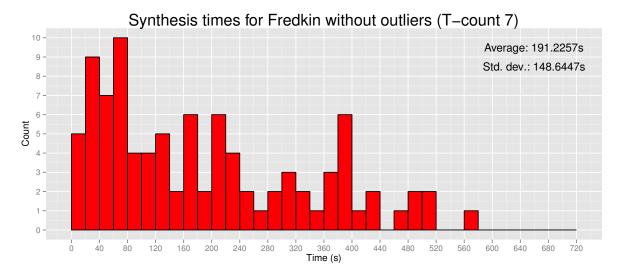

| 5.15         | Histogram of negated Fredkin synthesis times with outliers removed                                                          |

|              | 3-qubit circuits with T-count 9 and T-count 11                                                                              |

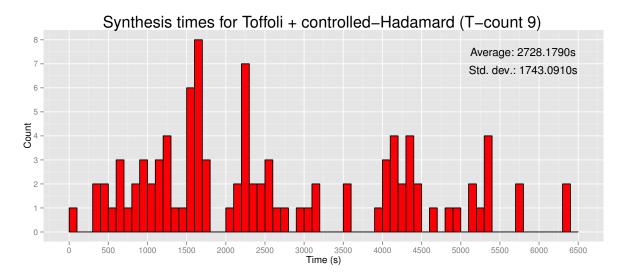

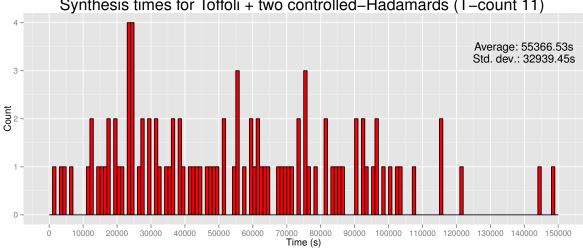

| 5.17         | Synthesis times for $T$ -count 9 circuit $\ldots \ldots 39$  |

| 5.18         | Synthesis times for $T$ -count 11 circuit $\ldots \ldots 39$ |

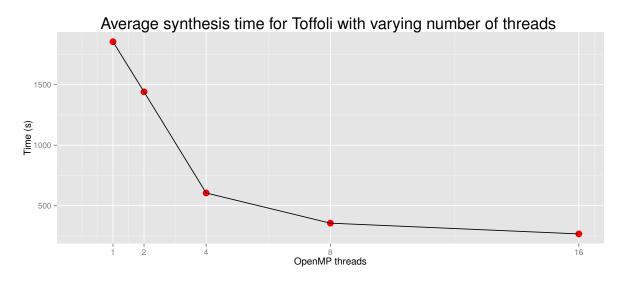

| 5.19         | Synthesis time vs. thread count                                                                                             |

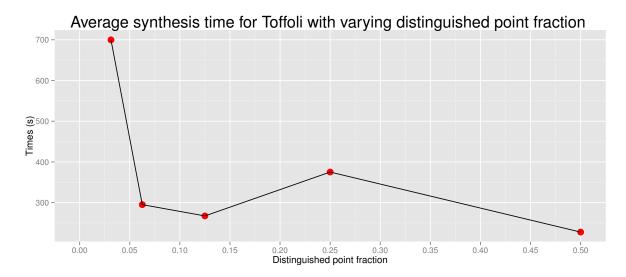

| 5.20         | Synthesis time vs. distinguished point fraction                                                                             |

| 6.1          | Algorithm flowchart for hybrid OpenMP/MPI implementation                                                                    |

# List of Tables

| 5.1 | Average runtimes for 3-qubit circuits with $T$ -count 7 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 35 |

|-----|-------------------------------------------------------------------------------------------------------------------|----|

| 6.1 | Average runtimes for Toffoli synthesis with varying MPI process distribution                                      | 45 |

### Chapter 1

## Introduction

#### 1.1 Quantum compilation

Compilers are an indispensable tool for programmers. Computers do not understand a human-readable programming language, such as C or Java, directly - they understand only a fixed set of instructions known as assembly, or machine code. Any operation you can imagine can ultimately be broken down into a sequence of the building blocks which comprise machine code. Writing machine code, however, is very cumbersome and prone to errors. The task of a compiler is to "translate" from human-readable code to machine code so that the computer can understand and execute the desired operations.

A quantum computer, once one is built, will require something akin to a compiler. The quantum compilation process will look very different from its classical counterpart, but the underlying idea remains the same: a quantum computer will need a translator. It may only know how to implement a fixed set of operations both efficiently and fault-tolerantly (i.e. with proper error-correction protocols). It will thus need a program with the ability to take any arbitrary operation it is given, and turn it into something it can understand and implement well. This part of the compilation process is called *quantum circuit synthesis*, and its implementation is the focus of this thesis.

#### **1.2** Quantum circuits

#### 1.2.1 Graphically representing circuits

Operations that run on a standard quantum computer are represented as unitary matrices. We commonly organize sequences of these operations graphically in the form of circuits. These circuits are somewhat analogous to the Boolean logic circuits of classical computers, but with operations acting on qubits rather than bits.

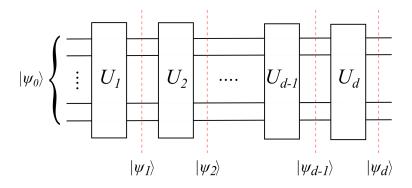

Suppose we have n qubits, and we would like to execute a sequence of unitary operations on them. Let us start with our qubits in some initial state  $|\psi_0\rangle$ . Say we want to apply the operations  $\{U_1, \ldots, U_d\}$  to the qubits, in that order, with  $U_i \in \mathcal{U}(2^n)$  (the set of  $2^n \times 2^n$  unitary matrices).

In matrix notation, the state vector  $|\psi_0\rangle$  evolves as follows:

$$|\psi_1\rangle = U_1|\psi_0\rangle \tag{1.1}$$

$$|\psi_2\rangle = U_2|\psi_1\rangle = U_2U_1|\psi_0\rangle \tag{1.2}$$

$$\vdots \psi_d \rangle = U_d |\psi_{d-1}\rangle = U_d U_{d-1} \cdots U_2 U_1 |\psi_0\rangle.$$

(1.3)

Instead of writing the evolution of the state in equation form, we can write it as a circuit diagram (shown in Figure 1.1).

Figure 1.1: A simple circuit diagram acting on a register of qubits. Unitary operations  $U_1, \ldots U_d$  are applied, and the resultant state is labeled below (corresponding to Eqs. (1.1-1.3)). As the circuit has d operations, or layers, we say this circuit has *depth d*.

Each horizontal line in Figure 1.1 represents a qubit. A group of qubits is called a *register*. Unitary operations are represented as boxes; they act only on the qubits whose lines they sit atop. Each unitary operation can be imagined as one *layer* of a circuit. The number of layers in the circuit is called the *depth*. Note that the ordering of the operations pictured appears reversed. Operations in the circuit are applied in the order in which they are read, from left to right, whereas the matrix operations in Eqs. (1.1 - 1.3) operate from right to left.

#### 1.2.2 Paulis, Cliffords, and universal gate sets

Just like machine code provides a classical computer with a fixed set of instructions, a quantum computer has an analogous fixed set of unitary operations which can be used to implement an arbitrary operation. Such a set is termed a *universal gate set*. There are many of examples of universal sets; we will focus primarily on just one of them.

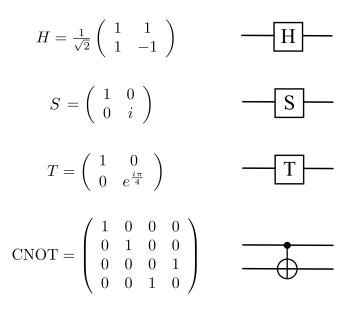

We introduce here a few very important gates which are frequently used in quantum operations: the single-qubit Hadamard gate H; the phase gate S; the  $\frac{\pi}{8}$  gate T; and the 2-qubit controlled-NOT gate CNOT. Their matrix representations and circuit diagram elements are shown in Figure 1.2.

Another group of important gates is the familiar set of single-qubit Pauli operators:

$$I = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}, \quad X = \begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}, \quad Z = \begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}, \quad Y = \begin{pmatrix} 0 & -i \\ i & 0 \end{pmatrix}.$$

(1.4)

These matrices and their *n*-qubit tensor products form a group which we will call  $\mathcal{P}_n$ , the *n*-qubit Pauli group. We define the *n*-qubit Clifford group  $\mathcal{C}_n$  as the group of operations which are the *normalizer* of the Pauli group. In other words, for every  $P \in \mathcal{P}_n$ , there exists a  $P' \in \mathcal{P}_n$  such that

$$CPC^{\dagger} = (-1)^{b}P', \qquad C \in \mathcal{C}_{n}, \quad b \in \{0, 1\}.$$

(1.5)

Essentially Cliffords map Paulis to Paulis (up to a possible phase of -1) under conjugation.

The Clifford group can be specified using some of the gates in Figure 1.2. Its generators are

$$\mathcal{C}_1 = \langle H, P \rangle, \tag{1.6}$$

$$\mathcal{C}_n = \langle H_{(i)}, S_{(i)}, \text{CNOT}_{(i,j)} \rangle, \quad i, j = 1, \dots, n, \qquad i \neq j, \quad n \ge 2,$$

(1.7)

Figure 1.2: Commonly used quantum operations and their graphical representation in circuit diagrams.

where we borrow the notation of [1] and use subscripts to denote which qubits the gates act on.

It is well known that the Hadamard and T gate can be combined to produce arbitrarily precise approximations of any single-qubit unitary [2]. With the addition of the 2-qubit CNOT, this becomes universal, meaning any *n*-qubit gate can be written in terms of only 1- and 2-qubit gates [3, 4]. In this thesis, we focus on this so-called "Clifford+T" universal gate set, which consists of  $C_n$  and the single-qubit T gate [2, 5].

It is important to note that the Clifford+T set is not unique - there are other possible choices, for example the Clifford group and the Toffoli gate [2]. A quantum computer, depending on its physical implementation, may be very good at performing just one of these gates sets efficiently and fault-tolerantly. At this time, many error correction and fault-tolerant protocols work efficiently with Clifford gates [6], so the focus of many existing circuit synthesis algorithms [7, 8, 9, 10, 11, 12] has been on this set.

#### **1.3** Parallel computing

Advances in classical computing technology have seen processing speeds increase by orders of magnitude in the last decade or so. This is largely accomplished by making smaller chips, with smaller components packed closer and closer together - the closer the transistors are, the less distance the information must travel, and thus the faster the processor runs. Furthermore, placing transistors closer together allows us to fit more of them on a chip of the same size. This trend can not continue forever, though. There is physical limit, at the atomic level, to how close you can place two transistors together. Furthermore, a computed bound on how fast a quantum state can change showed that there is a limit to the operation rate of *any* system [13]. At some point, we simply won't be able to make processors any faster. Our computational problems, however, are only getting bigger. So, if we can't make our processors faster, the next best thing is to use *more*. This is the essence of parallel computing: rather than a single processor doing all the work, work is distributed among multiple processors.

Take the simple example of image processing, for instance. Suppose we are working with an image containing millions of pixels, and we want to apply some operation to each pixel to change the appearance of the image (for example, changing it to gray scale, or making it brighter). One way to approach this problem would be to use a single processor and iterate sequentially over each pixel and apply the transformation. The parallel approach would be to send groups of pixels to different processors, and process all the groups simultaneously. Even if the time for each parallel processor to do a single transformation is greater than that of the single one, parallelism will outperform the single processor because everything is processed at the same time. For example, in a video game, where images are processed and rendered continuously at high frame rates, parallelization is essential.

Aside from graphics, parallel programming has found many uses in the scientific community. For example, in astrophysics, simulating supernovae in large regions of space is accomplished using a grid of processors, each assigned to a physical coordinate - differential equations are then discretely solved on the appropriate processor in every region of space. Many linear algebra operations can also be parallelized, such as matrix multiplication - give each processor a different row and column index to multiply together and all new matrix entries can be computed simultaneously.

A problem like image processing is called *embarrassingly parallel* - essentially, the entirety of the algorithm can be run in parallel. True embarrassingly parallel problems are extremely rare, as generally at least some of the runtime is spent initializing data serially (or waiting). Other problems contain only certain sections which can be parallelized. The speedup one obtains depends on the degree of parallelizability of the problem, and is determined by a relationship called Amdahl's law [14]. Suppose that a fraction P of a computing problem is parallelizable (the remaining 1-P must be done sequentially). If we use N processors for a problem, Amdahl's law tells us that the maximum possible speedup we could expect is [15]

$$S(N) = \frac{1}{(1-P) + P/N}.$$

(1.8)

If P = 1 (embarrassingly parallel), we can easily see that the speedup would be linear in the number of processors. If  $P \neq 1$ , and we simply increase the number of processors, the limit of the speedup tends to 1/(1 - P) - this means that for some problems we will never see much of a speedup, regardless of how many processors we use. Thus, choosing whether or not to use parallel computing is highly dependent on the problem at hand.

There are many different types of hardware and techniques which can execute code in parallel. One such example is the GPU (Graphical Processing Unit). These are specialized cards which contain thousands of tiny processors, and are used primarily for image processing on millions of pixels. The processors themselves are not particularly powerful, but their sheer number provides a huge advantage [16]. In the image processing example provided above, using a GPU would be the most effective means of solving that problem. GPUs, however, require special programming techniques and also suffer from bottlenecks due to the time spent transferring memory between the GPU and the host computer. This is a point we will return to in Chapter 7.

In this thesis, we focus on parallel computing using only CPUs (Central Processing Units). We will often speak of *nodes*: a collection of processors, or cores. There are many different computational models using CPUs. They differ in how the nodes are used, organized, and how the memory is shared.

A simple approach is called threading. Threading is often accomplished by placing instructions called *directives* around the code we wish to run in parallel, using for example a library such as OpenMP [17]. Suppose we have a single node with 16 cores. Each core may be assigned a single thread. Generally, all the threads are allowed to access a shared memory bank. Threads cannot pass messages between themselves, but can exchange information using the shared memory. The number of threads, however, is limited by the number of physical cores on the node (one can *hyperthread* and assign multiple threads to each core, but this often results in poor performance).

A way around this limitation is to use a library such as MPI (Message Passing Interface) [18] which provides a means of communication between different nodes, each of which has multiple cores. Each node has its own memory - another node cannot access that memory, and must be sent any data it requires via messages. Implementations of such programs are more complex, as one has to deal not only with the problem at hand, but to coordinate a number of nodes and make sure all the data gets passed between them correctly. This approach is better than simple threading, however it may not take full advantage of the fact that each node has multiple cores.

The final approach, which we explore in Chapter 6, is *hybrid* programming. MPI is used to send messages between nodes, while threading is used within each node to further subdivide the problem and take advantage of its multiple cores. There are a multitude of ways to divide up the computation and the message passing done by the threads [19, 20]. These techniques make use of the entire node, and are thus advantageous for many problems.

#### 1.4 Thesis objective

The goal of this work is to develop and implement an algorithm for quantum compilation (quantum circuit synthesis) which leverages parallel computing techniques. Full-scale implementations of quantum computers will emerge in the (perhaps not-so-distant) future. When this occurs, having a working algorithm which can efficiently compile large operations on many qubits will be extremely advantageous and will allow for faster testing, development, and progress.

This thesis is organized as follows. Chapter 2 introduces the main ideas behind quantum circuit synthesis, and details some of the key algorithms of the field. Chapter 3 explores the framework of parallel collision finding techniques and the advantages thereof. Chapter 4 combines the ideas of Chapters 2 and 3 and explains in detail how to apply parallel collision finding to circuit synthesis. We present a general framework for these techniques, and provide complexity and runtime estimates of the algorithm. Chapter 5 presents a fully-functioning, threaded parallel implementation of this framework applied to a specific synthesis algorithm. Chapter 6 details the hybrid parallel implementation, which is in progress. Finally, in Chapter 7 we discuss the future uses and improvements of our scheme.

### Chapter 2

### Quantum circuit synthesis

Quantum circuit synthesis is an important part of the quantum compilation process. Let us return to the analogy of classical compilers: a compiler translates human-readable code into computer-readable code. Quantum circuit synthesis is quite similar in spirit. A quantum computer will not be able to implement just any operation requested of it. Instead, it will understand and be able to efficiently, and fault-tolerantly, implement only a small subset of gates: those of the so-called universal gate set.

The goal of quantum circuit synthesis is, given an arbitrary operation, to break it down, or synthesize, an equivalent circuit using only gates from the universal set. In other words, given an arbitrary operation U, quantum circuit synthesis is the process which constructs the sequence of operations  $U_1, \ldots, U_k$  from a universal gate set  $\mathcal{G}$  such that

$$U_k \cdots U_1 = U. \tag{2.1}$$

There are two types of synthesis: *exact*, and *approximate*. Exact synthesis constructs a sequence  $U_1, \ldots, U_k$  such that Eq. (2.1) holds, and their product is exactly equal to U. On the other hand, approximate synthesis yields a set of operators whose product is within some distance  $\varepsilon$  from the target unitary U, where the distance between two operators is measured using some distance function. The work presented in this thesis focuses on exact synthesis.

#### 2.1 An overview of existing algorithms

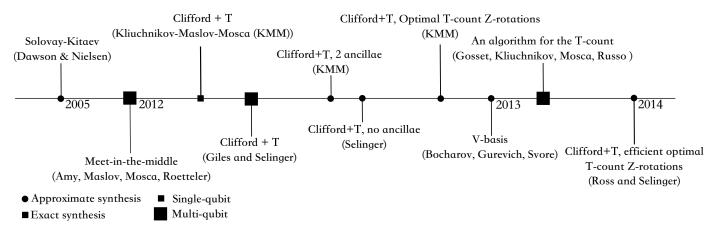

A number of algorithms exist for circuit synthesis; they are varied in their nature and techniques, and in what they can accomplish. Figure 2.1 is a timeline which shows the development history of such techniques. At the beginning is one of the pillars of circuit synthesis, the Solovay-Kitaev (SK) algorithm [21]. The SK algorithm allows one to efficiently perform approximate synthesis of a single-qubit<sup>1</sup> operation over a given set of gates. Synthesis is performed by recursively generating a sequence of gates which at every step moves closer and closer to the target gate, up to a distance of  $\varepsilon$ . The complexity analysis of this algorithm shows that it scales very well - it runs in time  $\mathcal{O}(\log^{2.71}(1/\varepsilon))$  and produces a sequence of gates with length  $\mathcal{O}(\log^{3.97}(1/\varepsilon))$ . This algorithm is also advantageous because it works over any arbitrary gate set. Provided that [21]:

- 1. All gates in the set are unitary and have determinant 1,

- 2. For each gate in the set, its adjoint is also in the set,

<sup>&</sup>lt;sup>1</sup>The SK algorithm can be generalized to both single qudits, as well as multiple qubits. In the qudit case, however, the runtime scales much worse, increasing exponentially with the dimension of the system [21]. For consistency and for comparison with the other algorithms discussed here, we restrict ourselves to the single-qubit version.

3. The chosen set is *dense* over the set of all single qubit unitaries SU(2), i.e. for any  $\varepsilon$ , an arbitrary operation chosen from SU(2) will always be within  $\varepsilon$  of some operation in the gate set,

we can always find an approximation over it. The disadvantages, however, are just that - we can only ever find an approximation.

Other approximation algorithms were developed which improved on the runtime of the SK algorithm. For example, with the addition of two ancillary (i.e. extra) qubits, the algorithm in [7] can synthesize a single-qubit operation over the Clifford+T set with only  $\mathcal{O}(\log(1/\varepsilon))$  gates in time  $\mathcal{O}(\log^2(1/\varepsilon) \log \log(1/\varepsilon))$ . An algorithm without ancillae was developed shortly afterward in [8]. It is a randomized algorithm, based on some principles of number theory, which approximates single-qubit circuits to Clifford+T gates with (heuristic) runtime polynomial in  $\log(1/\varepsilon)$ . The same paper also proved a bound on the T-count of the resultant circuits. The algorithm of [9] found a means of optimally implementing Z-rotations over Clifford+T, also with no ancillae and optimal T-count, up to an accuracy of  $10^{-15}$ . The resultant algorithm however, took time and memory exponential in the T-count. A subsequent algorithm [10] uncovered a means of finding these optimal T-count Z rotations efficiently. Optimizing the number of T gates is a pertinent problem, as T gates are 'expensive' to implement fault-tolerantly (see Section 2.3).

Figure 2.1: A timeline showing recent advances in quantum circuit synthesis. Algorithms are ordered chronologically based on their first appearance on the arXiv.

Approximations inevitably introduce some error. In a large quantum computing protocol with many operations, continuous approximations lead to the accumulation of these errors. We thus want to synthesize the gates as precisely as possible; it is even better if we can synthesize the gates *exactly*. An exact synthesis algorithm for single-qubit gates was introduced in [11]. Here the gate set is limited to the Clifford+T set, as we can take advantage of the fact that all the matrix elements of the Clifford+T gates are in the following ring:

$$\mathbb{Z}\left[i,\frac{1}{\sqrt{2}}\right] = \left\{\frac{a+b\sqrt{2}+ci+di\sqrt{2}}{\sqrt{2}^k}: \quad a,b,c,d\in\mathbb{Z}, \quad k\in\mathbb{N}\right\}.$$

(2.2)

As a result, any combination of these gates also has elements over this ring. Thus, given an arbitrary operation with elements over this ring, there should be a sequence of Clifford+T gates which produce it.

The algorithm uses special properties of the ring structure to reverse-engineer, or unravel, a sequence of H and T which produced it. The synthesis algorithm makes use of patterns in the power k of  $\sqrt{2}$ in the denominators of matrix elements which occur after successive multiplications by H and T: when considering the absolute value squared of the matrix elements, k increases by 1 each time the combination (HT) is applied. A small set of combinations of H and T are precomputed and stored in a database. Next, synthesis is performed by iteratively producing a sequence of H and T combinations, starting from the value of k observed in the candidate matrix, and unraveling it all the way down to the level of the database, in which a search for the remaining part of the sequence is done. The resultant sequence is *optimal* [11].

This algorithm can indirectly perform approximate synthesis: for an arbitrary gate, use the SK algorithm, or any of the above approximation algorithms to produce an approximation of the gate with all elements over  $\mathbb{Z}\left[i, \frac{1}{\sqrt{2}}\right]$ . Then, use the exact synthesis method to find a decomposition of the approximated gate. The downside to this exact synthesis technique is of course that it is a single-qubit algorithm. A conjecture was made for a similar technique for multiple qubits, but would require ancillae [11].

The need for ancillae was considered in [12]. An exact synthesis algorithm for multiple qubits was provided, and it was proven that though ancillae are necessary, only a single one is ever required. Their algorithm is far from optimal however - the number of gates in the synthesized circuits is of the order  $\mathcal{O}(3^{2^n}nk)$  where n is the number of qubits and k is the highest denominator exponent of ring elements in the target operation. Reference [12] also details further conditions on which operations can be exactly synthesized without any ancillae. Due to the fact that the determinant of a product of matrices is the product of their determinants, these exact synthesis algorithms are limited to synthesizing gates which not only have elements over  $\mathbb{Z}\left[i, \frac{1}{\sqrt{2}}\right]$  but also have determinants which belong to the set of determinants possible from combinations of gates of the universal set. For example, for 2 qubits the set is  $\{1, -1, i, -i\}$ . Any 2-qubit gate which does not have a determinant here, for example the controlled-T gate, requires a single ancilla for exact synthesis.

Finally, we note that algorithms also exist for synthesis over other universal sets. The so-called Vbasis is a universal gate set being explored as an alternative for the Clifford+T set. There are six gates in the V-basis and they represent rotations by  $\cos^{-1}(-3/5)$  around the x, y and z axes. An approximation algorithm for synthesizing single-qubit circuits over the V-basis (and allowing Pauli operations) was presented in [22]. It was previously proven that decomposition over this basis could be done in time linear in  $\mathcal{O}(\log(1/\varepsilon))$  [23]. Two variations were presented in [22], one a randomized algorithm which achieves this expected runtime using  $\leq 12 \log_5(2/\varepsilon)$  gates, and the other a direct search which produces circuits 1/4 to 1/3 of this length, and runs in time  $\mathcal{O}(\log^3(1/\varepsilon) \log \log(1/\varepsilon))$ .

#### 2.2 Meet-in-the-middle circuit synthesis

Perhaps the most important recent advance in quantum circuit synthesis is the meet-in-the-middle (MITM) approach considered in [24]. This algorithm forms the basis of the parallel framework we later present, so it is prudent to devote some time to understanding both how it works, and its advantages and disadvantages.

The MITM approach relies on generating a large database of possible circuits, which is subsequently searched through to find a solution. It begins with a gate set  $\mathcal{G}$  - we will assume that  $\mathcal{G}$  is a universal set suitable for quantum computing applications. Let  $\gamma$  be the number of single-qubit gates in  $\mathcal{G}$ . Recall that in the quantum circuit formalism, we can arrange the circuit in *layers*; the total number of layers in a circuit is its *depth*. Hence, we define the set  $\mathcal{V}_{(n,\mathcal{G})}$ , where *n* is the number of qubits, to be the set of all operations which constitute a single layer of depth in the circuit. Given that there are  $\gamma$  single-qubit gates, using simple combinatorics we can compute an upper bound of the size of this set:  $|\mathcal{V}_{(n,\mathcal{G})}| \leq \gamma^n$ .

Now, suppose we are presented with an arbitrary unitary operation U. The goal of circuit synthesis is to find a set of  $\{U_i\}, i = 1, ..., k$  such that

$$U_k U_{k-1} \cdots U_1 = U, \tag{2.3}$$

where all  $U_i \in \mathcal{V}_{(n,\mathcal{G})}$ , and the depth k is optimal.

The brute force approach would be to take our set  $\mathcal{V}_{(n,\mathcal{G})}$ , generate all possible combinations of the elements, from depth 1 up to depth k, and check if any of them are equal to U. The runtime of such an algorithm would be abysmal:  $\mathcal{O}(|\mathcal{V}_{(n,\mathcal{G})}|^k)$  or  $\mathcal{O}(\gamma^{nk})$ , which is exponential in both the number of qubits and the depth. Such an algorithm would hardly scale well past small numbers of qubits and low depth.

The MITM approach offers roughly a square-root speed-up over the brute force case. Rather than generating combinations for all k possible layers, we split Eq. (2.3) as follows:

$$U_{\left\lceil\frac{k}{2}\right\rceil}\cdots U_{1} = U_{\left\lceil\frac{k}{2}\right\rceil+1}^{\dagger}\cdots U_{k}^{\dagger}U, \qquad (2.4)$$

$$V = W^{\dagger}U, \qquad (2.5)$$

where we define

$$V := U_{\left\lceil \frac{k}{2} \right\rceil} \cdots U_1, \tag{2.6}$$

$$W := U_k \cdots U_{\left\lceil \frac{k}{2} \right\rceil + 1}. \tag{2.7}$$

We can see here an immediate advantage: rather than generating all possible combinations of circuits up to depth k, we only need to generate the sets up to depth  $\left\lceil \frac{k}{2} \right\rceil$ .

Let  $S_i$  represent the set of combinations of  $\mathcal{V}_{(n,\mathcal{G})}$  having depth i, and let  $S_i^{\dagger}$  be the set containing the corresponding adjoints having depth i. Then, a solution to the synthesis problem exists if we can find some  $V \in S_{\lfloor \frac{k}{2} \rfloor}$  and  $W \in S_{\lfloor \frac{k}{2} \rfloor}^{\dagger}$  such that Eq. (2.5) holds. In other words, a solution exists if we find some k such that  $S_{\lfloor \frac{k}{2} \rfloor} \cap S_{\lfloor \frac{k}{2} \rfloor}^{\dagger} U \neq \emptyset$ .

The algorithm runs as follows: we begin with i = 1, and sequentially generate the next  $S_i$  by building off the previous set one layer at a time. We take  $S_0 = 1$  and  $S_1 = \mathcal{V}_{(n,\mathcal{G})}$ . For each new set  $S_i$ , a search is executed to compare it with its possible 'other halves' - sets  $S_{i-1}^{\dagger}U$  and also  $S_i^{\dagger}U$ , taking into account the fact that the depth k may be odd or even, respectively. The algorithm terminates if a match is found in one of these sets; otherwise, it continues to the next level of depth, up to a specified limit k.

What is the runtime of this algorithm? For this, we look to the best classical search algorithms. The data structure used to store the sets  $S_i$  plays an important role in how long the searching process takes. A well-chosen structure such as a binary tree or red-black tree can be completely searched for matches from a newly generated  $S_i$  in time  $\mathcal{O}(|S_i|\log(|S_i|))$ . Searching itself takes  $\mathcal{O}(\log(|S_i|))$  [25], and this must be done for all  $|S_i|$  elements.

Thus, at each step in the algorithm, comparing the new set with the other halves would take time  $|S_i|\log(|S_{i-1}^{\dagger}|) + |S_i|\log(|S_i^{\dagger}|) \le 2|S_i|\log(|S_i|)$ , since the  $i^{\text{th}}$  set is always larger than the  $(i-1)^{\text{th}}$ , and  $|S_i| = |S_i^{\dagger}|$  [24]. Furthermore, we know that  $|S_i| \le |\mathcal{V}_{(n,\mathcal{G})}|^i$ . Thus, we obtain an upper bound of  $\mathcal{O}(|\mathcal{V}_{(n,\mathcal{G})}^i|\log(|\mathcal{V}_{(n,\mathcal{G})}^i|))$  for the  $i^{\text{th}}$  iteration.

To obtain an upper bound for the total runtime needed to find a circuit of optimal depth k, we sum over all depths i [24]:

$$T_{MITM} = \sum_{i=1}^{\left\lceil \frac{k}{2} \right\rceil} |\mathcal{V}_{(n,\mathcal{G})}|^i \log(|\mathcal{V}_{(n,\mathcal{G})}|^i)$$

(2.8)

$$\leq \sum_{i=1}^{\left\lfloor \frac{k}{2} \right\rfloor} |\mathcal{V}_{(n,\mathcal{G})}|^{i} \log(|\mathcal{V}_{(n,\mathcal{G})}|^{\left\lceil \frac{k}{2} \right\rceil})$$

$$(2.9)$$

$$\leq |\mathcal{V}_{(n,\mathcal{G})}|^{\left\lceil \frac{k}{2} \right\rceil} \log(|\mathcal{V}_{(n,\mathcal{G})}|^{\left\lceil \frac{k}{2} \right\rceil}), \qquad (2.10)$$

where in each successive step we have used the highest exponent to generate an upper bound. Since  $|\mathcal{V}_{(n,\mathcal{G})}| \leq \gamma^n$ , we can rewrite the above as  $\mathcal{O}(\gamma^{n\lceil \frac{k}{2}\rceil} \log(\gamma^{n\lceil \frac{k}{2}\rceil}))$ . This is roughly a square root improvement over the brute force result of  $\mathcal{O}(\gamma^{nk})$ .

In [24], this framework was used to generate circuits with a number of properties, such as optimal depth, optimal T-depth (i.e. optimizing the number of layers which contain T gates), and minimization of specified cost functions. Some of the largest depth-optimal circuits synthesized were depth 12 for 2 qubits, 10 for 3 qubits, and 6 for 4 qubits.

The disadvantages of the MITM algorithm lie in the fact that databases must be generated and stored. This is of course a procedure which must only be done once - subsequent executions of the program can reuse the databases as synthesis is always taking place over the same gate set. Databases were stored as red-black trees in binary files generated by the program. Rather than storing entire unitaries, storage was simplified by storing only the action of each candidate unitary on an arbitrary vector 'key' - in a sense, it stored a type of hash which was highly likely to be unique to each unitary [24]. Furthermore, the databases were pruned by choosing canonical representatives of unitaries which differed only by a global phase. For example, to synthesize the Toffoli gate, the largest database file which needed to be generated was about 36 MB in size and took about 24 minutes to generate. Subsequent searching for matches through the largest database took about 7.5 minutes <sup>2</sup>. The time and space, however, are highly dependent on the synthesis problem at hand. For example, in the case of optimal *T*-depth circuits, generation of the 3-qubit Clifford group required almost four days [24]. Regardless, the principles of MITM synthesis offer significant benefits which we take advantage of in Chapter 4.

#### 2.3 An algorithm for the *T*-count

Most of the algorithms presented above synthesize circuits over the Clifford+T gate set. However, T gates are an 'expensive' resource. To implement a T gate fault-tolerantly requires the addition of an ancilla qubit, a fault-tolerant measurement procedure, and additional fault-tolerant operations of other gates [2, 26]. The T-count of a circuit is the total number of T and  $T^{\dagger}$  gates it contains. Due to their 'cost', it is important to have an algorithm which produces circuits with optimal T-count. Such an algorithm was developed in [1] - it determines whether the T-count of a unitary is less than a candidate value, and finds the corresponding circuit decomposition. We proceed by first stating a few key concepts that we use here and in future chapters. We then go through a brief overview of how the algorithm determines optimal T-count circuits.

#### 2.3.1 Smallest denominator exponents

Consider an element over the ring  $\mathbb{Z}\left[i, \frac{1}{\sqrt{2}}\right]$ . Similar to how we can reduce simple fractions when there are common factors, we can also reduce ring elements so that the coefficients are as small as possible.

**Definition 1** (sde). The smallest denominator exponent of x, sde(x), is defined as the smallest value of k such that

$$x = \frac{a + b\sqrt{2} + ci + di\sqrt{2}}{\sqrt{2}^k},$$

(2.11)

holds, where a, b, c, d are integers and  $k \ge 0$  [1, 11]. We also define sde(0) = 0.

The sde of a matrix with its elements over the ring is defined as the smallest sde of all its constituent elements [1].

<sup>&</sup>lt;sup>2</sup>Reported times are from a test run on a machine with a 2.80 GHz Intel i7, and 32 GB of RAM.

#### 2.3.2 The channel representation

The channel representation is a very important tool used in the optimal T-count algorithm [1]. It also provides an extremely convenient representation of T gates, and as a consequence was used in the implementation discussed in Chapter 5.

Consider the conjugation of a Pauli operator by some matrix U,  $UP_sU^{\dagger}$ . We can expand the result by using the fact that the Pauli operators form an operator basis:

$$UP_s U^{\dagger} = \sum_{P_r \in \mathcal{P}_n} \widehat{U}_{rs} P_r, \qquad (2.12)$$

where the  $\hat{U}_{rs}$  are the expansion coefficients. The channel representation  $\hat{U}$  of a unitary operation U is a superoperator with these coefficients as its matrix entries:

$$\widehat{U}_{rs} = \frac{1}{2^n} \operatorname{Tr}(P_r U P_s U^{\dagger}).$$

(2.13)

Defining  $N = 2^n$ , the channel representation is essentially an  $N^2 \times N^2$  matrix with its rows and columns indexed by Paulis.

Channel representations have an additional useful property for our chosen gate set. When the entries of U are from  $\mathbb{Z}\left[i, \frac{1}{\sqrt{2}}\right]$ , so are the entries of  $\hat{U}$ . However, since one may note that  $\hat{U}$  is Hermitian, the entries must be over the sub-ring

$$\mathbb{Z}\left[\frac{1}{\sqrt{2}}\right] = \frac{a+b\sqrt{2}}{\sqrt{2}^k}, \quad a, b \in \mathbb{Z}, \quad k \in \mathbb{N}.$$

(2.14)

Finally, channel representations respect matrix multiplication:  $\widehat{UV} = \widehat{U}\widehat{V}$ .

#### 2.3.3 Coset labels

Cosets are partitions of a group, built with respect to a subgroup, which divide the original group into equal sized partitions. Any element of a coset can serve a representative for that coset. We define a coset label that is unique for each coset and can be computed easily from any of its constituent elements. The coset label of a circuit matrix is a means of checking its equivalency with other circuits. Computation of the coset label of a channel representation  $\hat{V}$  is done according to Algorithm 1. Reference [1] proves that two channel representations  $\hat{V}, \hat{W}$  have the same coset label if and only if they are related by a Clifford:  $\hat{W} = \hat{V}\hat{C}$  (in other words, they are in the same coset).

Algorithm 1 Computation of the coset label

- 1: Given a channel representation  $\hat{V}$ , rewrite  $\hat{V}$  so that each non-zero entry of the matrix has a common denominator of  $\sqrt{2}^{\operatorname{sde}(\hat{V})}$ .

- 2: For each column of  $\hat{V}$ , look at the first non-zero entry. If a < 0, or if a = 0 and b < 0, multiply all elements in the column by -1; otherwise, do nothing.

- 3: Permute the columns so that they are in lexicographical order<sup>3</sup>.

<sup>&</sup>lt;sup>3</sup>Sorting by lexicographical order can be accomplished using any deterministic sorting algorithm. For example, in the C++ implementation of Chapter 5, we use a combination of std::lexicographical\_compare in conjunction with std::sort from the <algorithm> library.

#### 2.3.4 Finding *T*-optimal circuit decompositions

We now review the basic framework of the algorithm and how it can be used to determine an optimal T-count decomposition. Recall the MITM decomposition of a circuit in Eq. (2.3). Since we expect the unitaries  $U_i$  to be part of the Clifford+T gate set, we can consider a similar decomposition which explicitly displays the presence of T gates within the circuit U:

$$U = e^{i\phi}C_{(k)}T_{(q_k)}C_{(k-1)}T_{(q_{k-1})}\cdots T_{(q_1)}C_{(0)}$$

(2.15)

where the subscripts on the  $T_{(q_i)}$  indicate that they act on qubit  $q_i$ , and  $\phi$  is a global phase, which we will soon show is irrelevant. This circuit has k T gates acting on a single qubit, thus it has T-count k.

We can rearrange this expression into a more convenient form by inserting extra Cliffords so that every T gate is conjugated by a Clifford, like so:

$$U = e^{i\phi} \prod_{i=k}^{1} \left( D_i T_{(q_i)} D_i^{\dagger} \right) D_0, \qquad (2.16)$$

where the  $D_i$  are products of the original Cliffords  $C_i$  according to  $D_i = \prod_{j=k}^i C_j$ .

Now, let's expand a single-qubit T gate in the Pauli basis. Since there are no off-diagonal elements, we know that it must be combination of only I and Z:

$$T = aI + bZ. (2.17)$$

Solving for coefficients a and b yields

$$a = \frac{1}{2} \left( 1 + e^{\frac{i\pi}{4}} \right) \tag{2.18}$$

$$b = \frac{1}{2} \left( 1 - e^{\frac{i\pi}{4}} \right). \tag{2.19}$$

We can extend this to multiple qubits:  $T_{(q_i)} = aI_{2^n} + bZ_{(q_i)}$ , where the identity matrix has dimensions  $2^n \times 2^n$  and n is the number of qubits. With this, we can rewrite  $D_i T_{(q_i)} D_i^{\dagger}$  as

$$D_i T_{(q_i)} D_i^{\dagger} = \frac{1}{2} (1 + e^{\frac{i\pi}{4}}) D_i I_{2^n} D_i^{\dagger} + \frac{1}{2} (1 - e^{\frac{i\pi}{4}}) D_i Z_{(q_i)} D_i^{\dagger}$$

(2.20)

$$= \frac{1}{2}(1+e^{\frac{i\pi}{4}})I_{2^n} + \frac{1}{2}(1-e^{\frac{i\pi}{4}})P, \qquad (2.21)$$

where P is a Pauli since the  $D_i$  are Cliffords and  $Z_{(q_i)}$  is a Pauli.

We use the shorthand notation [1]

$$R(P) = \frac{1}{2} (1 + e^{\frac{i\pi}{4}}) I_{2^n} + \frac{1}{2} (1 - e^{\frac{i\pi}{4}}) P$$

(2.22)

so that we can rewrite Eq. (2.16) as

$$U = e^{i\phi} \left(\prod_{i=k}^{1} R\left(P_{i}\right)\right) D_{0}.$$

(2.23)

The benefit of writing the equation in this form is that now, to synthesize an optimal *T*-count circuit, it suffices to find a set of Paulis  $\{P_i\}$  and a Clifford  $D_0$  which satisfy Eq. (2.23) up to a phase. Even

more convenient is that, if we consider the channel representation of all the above matrices, the global phase vanishes (as promised) [1]:

$$\widehat{U} = \left(\prod_{i=k}^{1} \widehat{R(P_i)}\right) \widehat{D_0}.$$

(2.24)

Eq. (2.24) is the structure we will use for the rest of this thesis, and also in the implementation presented in Chapters 5 and 6. With this expression, we will generate an optimal *T*-count circuit. The process is vaguely similar to the database generation and search of the MITM algorithm presented previously. Rather than circuit databases consisting of products in the universal gate set, we compute databases of coset labels. A sorted coset database  $\mathcal{D}_k^n$  is defined in [1] as a list of *n*-qubit unitaries in channel representation form such that:

- 1. All elements in  $\mathcal{D}_k^n$  have *T*-count *k*.

- 2. For any  $\widehat{V}$  with *T*-count *k*, there is a unique coset label in  $\mathcal{D}_k^n$ .

- 3. The database is lexicographically sorted (to allow for easy binary search).

Coset databases are built as follows.  $\mathcal{D}_0^n = \{1\}$ , the  $N^2 \times N^2$  identity matrix. Subsequent levels of the database are built by left multiplying by a single  $\widehat{R(P)}$  to each element in the previous level, and selectively adding only the unique new products. This has the effect, at each step, of adding a single T gate.

Suppose we want to check if the *T*-count of an *n*-qubit circuit  $\hat{U}$  is  $\leq m$ . The procedure for accomplishing this is shown in Algorithm 2 [1]. Such an algorithm not only determines the *T*-count, but also the sequence of Paulis used and the terminal Clifford  $D_0$  (since we can invert Eq. (2.24) to recover its channel representation once we know the Paulis). Efficient algorithms exist for subsequently converting the  $R(P_i)$  back to Clifford and *T* gates [1, 27].

Algorithm 2 Generation of optimal T-count circuits

- 1: Generate all sorted coset databases from  $\mathcal{D}_0^n, \ldots \mathcal{D}_{\lceil \frac{m}{2} \rceil}^n$ .

- 2: Sequentially execute a binary search to determine if there exists an element in one of the databases which is equal to the coset label of  $\hat{U}$ . If such an element exists in database  $\mathcal{D}_i^n$ , then we have found the *T*-count is *i* and we stop.

- 3: If no such element is found in the previous step, then the *T*-count must be greater than  $\left\lceil \frac{m}{2} \right\rceil$ . Rather than generating further coset databases, we can perform a MITM-style search within them to find combinations with higher *T*-counts. Begin at  $r = \left\lceil \frac{m}{2} \right\rceil + 1$ . Starting with coset database  $\mathcal{D}_{r-\left\lceil \frac{m}{2} \right\rceil}^{n}$ , for each  $\hat{V}$ , use binary search to check if there exists a  $\widehat{W}$  such that the coset labels of  $\widehat{W^{\dagger}U}$  and  $\widehat{V}$ are equal. If a pair is found, then we know that the *T*-count is *r*. If no pair is found, increase *r* by 1 until we complete the case r = m, in which case the algorithm terminates as the *T*-count is larger than *m*.

This algorithm, like some others examined so far [12, 24], runs in exponential time. It also has the disadvantage of generating databases of exponential size, in both the number of qubits and the desired T-count. Let us briefly compute its storage space and runtime.

For the storage space, the largest database has size on the order of  $N^{2\left\lceil \frac{m}{2} \right\rceil}$ , where we recall  $N = 2^n$ . Each item in the database is an  $N^2 \times N^2$  matrix - therefore an upper bound on the estimate for space required by the database is  $\mathcal{O}(N^m \text{poly}(m, N))$ , where poly indicates a polylogarithmic term. In the implementation of [1], database generation was done in C++ and databases were stored as trees in binary files. The largest such file generated was on the order of 4 GB.

For the runtime, the first step is to generate all the databases - this takes time  $\mathcal{O}(N^m \operatorname{poly}(m, N))$ . The next step is to execute the binary search on all the databases with the coset label of the unitary this takes time  $\mathcal{O}(\operatorname{poly}(m, N))$  since binary search can be done in logarithmic time. Finally, to compare the remaining steps takes time  $\mathcal{O}(N^m \operatorname{poly}(m, N))$ , since we need to search through the entire database at each iteration to find the MITM-style pair. Thus, the total runtime is equivalent to the storage time:  $\mathcal{O}(N^m \operatorname{poly}(m, N))$ , a quantity exponential in both m and the number of qubits. This algorithm is thus impractical for circuits larger than about 3 qubits and T-count 7 (the largest case solved in [1]).

### Chapter 3

## Parallel collision finding

#### 3.1 Overview

The parallel collision finding algorithm we adapt to circuit synthesis was developed by van Oorschot and Wiener in 1996 [28]. Their initial application was cryptographic in nature: how does one find collisions within a hash function, or an encryption function? Parallel collision finding offers an elegant, distributed, and scalable means of finding collisions in large spaces, many of which are exponential in size. For example, the space size of the double DES encryption scheme is  $2^{112}$ , a number far too great to simply brute force with one processor, but manageable using parallel techniques [29].

The initial framework has a multitude of uses, from cryptography, to physics, and to mathematics. Any large search problem in which one is searching for a collision can benefit from these techniques, if the problem at hand can be framed in the formulation that follows. In this chapter, we provide an overview of the algorithm, the time-memory tradeoffs on which it depends, and the runtime estimate.

#### 3.2 Algorithm details

#### 3.2.1 Collisions and claws

In what follows, for the purpose of example let us consider f and g to be hash functions. Their spaces have size  $N_f$  and  $N_g$ , and they are many-to-one (otherwise there would be no collisions to find). Let their domains be  $\mathbb{D}_f$  and  $\mathbb{D}_g$ , and ranges  $\mathbb{R}_f$  and  $\mathbb{R}_g$  respectively.

We begin by defining the objects for which we are searching.

**Definition 2.** Let f be a hash function, and x, y be elements in  $\mathbb{D}_f$ . The elements x and y are said to be a collision if

$$f(x) = f(y), \quad x \neq y. \tag{3.1}$$

**Definition 3.** Let f and g be (different) hash functions, and  $x \in \mathbb{D}_f$ ,  $y \in \mathbb{D}_g$ . Let  $\mathbb{R}_f = \mathbb{R}_g$ . The elements x and y are said to be a claw if

$$f(x) = g(y). \tag{3.2}$$

In essence, a collision is a pair of elements in the domain of a function which map to the same element. A claw, on the other hand, is an instance of two elements which cause the two separate functions map to the same element.

#### 3.2.2 Collision finding

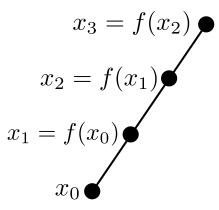

Parallel collision finding is essentially a series of random walks through the hash space, which (hopefully) collide at some point. Suppose we have some hash function f; if f is a 'good' hash function, given an arbitrary input, the output should be roughly random. Repeatedly applying f to a given input, say  $x_0$ , produces a "trail" of random points in the space:

Figure 3.1: Basic structure of a trail; an initial value is hashed repeatedly, which is equivalent to a random walk through the hash space.

Now, we must define a stopping condition for these random walks. A certain fraction of the points in the space are denoted as *distinguished* points; if at any point in the walk,  $x_i$  is found to be distinguished, then the trail terminates. These terminal points are generally chosen as having some easily distinguishable property (for example, if we convert the  $x_i$  to binary strings, we might denote all strings starting with a certain number of 0 bits as distinguished). A complete trail will now look similar to Figure 3.2.

Figure 3.2: Trails stop when they hit a distinguished point (or reach a specified maximum iteration limit).

At the beginning of the algorithm, a number of processors set out, with randomly chosen starting points, to generate trails. A location common to all processors is used to store the collection of trails in which unique distinguished points are found. As a trail is completely deterministic we need only store the starting point, ending point, and number of steps in between.

The fraction of points which are marked as distinguished is a *time-memory tradeoff*. Suppose we denote a fraction  $\theta$  of the points as distinguished. Therefore on average, a trail will have to take  $1/\theta$  steps before it finds a distinguished point, if the function is roughly random. The value of  $\theta$  is chosen according to the computational resources available. More distinguished points means more storage space but less time required for each trail to terminate. Fewer distinguished points take up less space but each trail may have to run for a longer time. When searching through small spaces, there may be enough memory available to let all the points be distinguished points is enough to consume all the allotted RAM. A means of choosing this parameter wisely is discussed in [28]. Unfortunately, it is possible for cycles to occur, as well as for trails to go a very long time without finding anything. Thus, an iteration limit is generally set (as some function of  $\theta$ ) in order to guarantee no processes are wasting unnecessary time on trails that may not end.

Now, suppose a processor finds a distinguished point, tries to store it, and sees that there is already a trail with the same distinguished end point in storage. There are two possibilities:

- 1. The two trails started at the same place, and thus ended at the same place.

- 2. The two trails merged, i.e. there is a collision.

This second possibility is exactly what we're looking for, and is shown graphically in Figure 3.3. We can see that  $x_1$  and  $y_3$  are a collison of f, since

$$f(x_1) = f(y_3). (3.3)$$

$$x_{d} = f(x_{d-1}) \bigcirc y_{d'} = f(y_{d'-1})$$

$$x_{d-1} = f(x_{d-2}) \oiint y_{d'-1} = f(y_{d'-2})$$

$$\vdots$$

$$x_{3} = f(x_{2}) \oiint y_{5} = f(y_{4})$$

$$x_{2} = f(x_{1}) \oiint y_{4} = f(y_{3})$$

$$x_{1} = f(x_{0}) \oiint y_{3} = f(y_{2})$$

$$x_{0} \oiint y_{2} = f(y_{1})$$

$$y_{1} = f(y_{0})$$

$$9_{0}$$

Figure 3.3: A depiction of the collision between two trails,  $f(x_1) = f(y_3)$ . The trails move forward together after the collision at point  $x_2 = y_4$  and thus terminate at the same distinguished point  $x_d = y_{d'}$ .

What the processor does next is trace back through the sequence of both trails, and find the point where they collided. We start with the longer of the two trails, and apply f to the initial value a number of times equal to the difference in trail lengths (in the case of the example, we would apply f twice to

arrive at  $y_2$ ). Then, the two trails apply f simultaneously (in the example, the short trail will compute  $x_1$  and the longer  $y_3$ ). The results are tested for equality at the end of each step - if we find two equal values, we've found a collision and the problem is solved (here, we'd eventually find  $x_2 = y_4$ ).

The authors of [28] produced an estimate of a runtime for this algorithm. They suppose that, though there were many collisions, only one such collision is the solution to the problem at hand (i.e. the golden collision). There are also many different versions of f, all of which contain a golden collision (for example, if f was an encryption function and our goal was to find a collision in encrypted messages, perhaps we might denote different keys as leading to different versions of f). Let m be the number of processors, and let w be the number of distinguished points that the memory can hold. Simulations run in [28] with varying values of w and  $N_f$  showed that the best achievable runtime was when they choose  $\theta = 2.25\sqrt{w/N_f}$  and generated 10w distinguished points per version of f before choosing a new one. The runtime was

$$T_{col} = \left(2.5\sqrt{\frac{N_f^3}{w}}\frac{1}{m}\right)\tau,\tag{3.4}$$

where  $\tau$  is the amount of time required for a single iteration of f in a trail. They estimate that on average,  $0.45N_f/w$  functions must be tried before finding a solution.

We note that in theory this algorithm depends inversely on the number of processors used; it is also inversely proportional to the square root of memory available to store distinguished points. This implies that more processors and more memory should make the algorithm run faster. However, in practice the time spent accessing the shared memory causes a bottleneck [28].

#### 3.2.3 Claw finding

Finding claws rather than collisions is largely the same idea, however we must now consider two functions, f and g. Rather than randomly walking just over an element of the domain, we represent each step in the trail as a pair  $(x_i, b_i)$ , where  $b_i$  is a flag which tells us whether to use function f or g in the next step. Trails begin by choosing  $x_0$  and  $b_0$  at random. Every subsequent step must first compute the result of the function f or g. This result is then used to deterministically derive a new  $b_i$  so that it 'knows' which function to perform in the next step. The result is also used to determine the next  $x_i$  such that is it in the proper domain corresponding to  $b_i$ . This deterministic step is termed a reduction function.

Execution of the algorithm is very similar to the collision case. An example of two trails merging to produce a claw is shown in Figure 3.4. Here, we find that  $f(x_1) = g(y_3)$ , and then the trails continued on to end at the same distinguished point.

An estimate for the runtime of claw finding is also provided in [28]. Let our functions f and g be hash functions on spaces of size  $N_f$  and  $N_g$  respectively. Let g be a function over a larger space  $N_g = cN_f$  for some constant  $c \ge 1, c \in \mathbb{Z}$ . If  $N_g$  is larger than  $N_f$ , we divide  $N_g$  into c chunks of size  $N_f$  and execute searches over each set sequentially.

Note that the search is not executed just over a space of size  $N_f$ . Now the space has size  $2N_f$ , because at each step, we have an element of f or g and a flag which can take one of two values. We can apply the result of Eq. (3.4) directly to these parameters:

$$T_{claw} = \frac{N_g}{N_f} \left( 2.5 \sqrt{\frac{(2N_f)^3}{w}} \frac{1}{m} \right) \tau$$

(3.5)

$$= 2.5 * \sqrt{8} N_g \sqrt{\frac{N_f}{w} \frac{1}{m}} \tau \tag{3.6}$$

$$x_{d} = f(x_{d-1}) \bigcirc y_{d'} = f(y_{d'-1})$$

$$x_{d-1} = f(x_{d-2}) \bigodot y_{d'-1} = f(y_{d'-2})$$

$$\vdots$$

$$x_{3} = g(x_{2}) \bigodot y_{5} = g(y_{4})$$

$$x_{2} = f(x_{1}) \biguplus y_{4} = g(y_{3})$$

$$x_{1} = f(x_{0}) \biguplus y_{3} = g(y_{2})$$

$$y_{2} = f(y_{1})$$

$$y_{1} = g(y_{0})$$

$$y_{0}$$

Figure 3.4: Finding a claw between two trails,  $f(x_1) = g(y_3)$ . Similar to the collision case, the trails move forward together after the claw occurs at  $x_2 = y_4$ . This is because the next step is completely and deterministically determined from the previous step using a reduction function.

$$\approx 7N_g \sqrt{\frac{N_f}{w}} \frac{1}{m} \tau \tag{3.7}$$

where  $\tau$  is now the runtime of a whole step in the trail, and where we added the prefactor  $N_g/N_f$  because the process must be repeated for each of the *c* subsets of *g*. Once again we see that the runtime depends inversely on the number of processors and inversely on the square root of available memory. This equation will be important for us later in Chapters 4 and 5 when we analyze the runtime of the parallelized circuit synthesis algorithm.

### Chapter 4

## Application of parallel framework to circuit synthesis

In this chapter we combine the ideas of the previous two chapters. We show how the parallel claw finding algorithm of Chapter 3 can be applied to the MITM circuit synthesis algorithm of Chapter 2 to produce a new framework for parallel quantum circuit synthesis.

#### 4.1 Framework

We begin with an arbitrary quantum circuit U on n qubits, which can be implemented over a universal gate set  $\mathcal{G} = \{G_1, G_2, \ldots, G_N\}$ , where the  $G_i$  are unitary matrices. We can write U as

$$U_k \cdots U_1 = U, \tag{4.1}$$

where the  $U_i$  are depth 1 unitaries from  $\mathcal{G}$  for i = 1, ..., k, as in the MITM approach, and k is the depth of the circuit. Our goal is, given U, to recover the set of  $\{U_i\}$  such that Eq. (4.1) holds.

We use the MITM approach to rewrite Eq. (4.1) by splitting it in half:

$$U_{\left\lceil \frac{k}{2} \right\rceil} \cdots U_1 = U_{\left\lceil \frac{k}{2} \right\rceil + 1}^{\dagger} \cdots U_k^{\dagger} U.$$

$$(4.2)$$

We propose the following new method for circuit synthesis, using the time-memory tradeoffs offered by parallel search techniques to synthesize our circuits. Let

$$V := U_{\left\lceil \frac{k}{2} \right\rceil} \cdots U_1, \tag{4.3}$$

$$W := U_{\left\lceil \frac{k}{2} \right\rceil+1}^{\dagger} \cdots U_{k}^{\dagger} U$$

$$(4.4)$$

be the LHS and RHS of Eq. (4.2) respectively. We use the parallel claw finding method presented in Chapter 3 to execute a search over unitaries (circuit matrices) of type V and W. Our goal is to find a pair (V, W) that satisfy Eq. 4.2, i.e. they are a claw.

Let the function g be a function which produces a circuit matrix of type V, and function f one which produces a circuit matrix of type W. Parallel collision search over the possible circuits is executed as follows. First, we define a means of hashing a circuit matrix of type V or W to a simple data type, such as an integer or a string. Then, we require a means of converting the latter back to a matrix.

To perform claw finding, we begin with a number of processors. Each processor chooses a random starting point and flag and uses its data to generate a new matrix of type V or W. The resultant matrix