# Design and Analysis of an Adjacent Multi-bit Error Correcting Code for Nanoscale SRAMs

by

## Adam Neale

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical & Computer Engineering

Waterloo, Ontario, Canada, 2014

© Adam Neale 2014

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Increasing static random access memory (SRAM) bitcell density is a major driving force for semiconductor technology scaling. The industry standard 2x reduction in SRAM bitcell area per technology node has lead to a proliferation in memory intensive applications as greater memory system capacity can be realized per unit area. Coupled with this increasing capacity is an increasing SRAM system-level soft error rate (SER). Soft errors, caused by galactic radiation and radioactive chip packaging material corrupt a bitcell's data-state and are a potential cause of catastrophic system failures. Further, reductions in device geometries, design rules, and sensitive node capacitances increase the probability of multiple adjacent bitcells being upset per particle strike to over 30% of the total SER below the 45 nm process node. Traditionally, these upsets have been addressed using a simple error correction code (ECC) combined with word interleaving. With continued scaling however, errors beyond this setup begin to emerge. Although more powerful ECCs exist, they come at an increased overhead in terms of area and latency. Additionally, interleaving adds complexity to the system and may not always be feasible for the given architecture.

In this thesis, a new class of ECC targeted toward adjacent multi-bit upsets (MBU) is proposed and analyzed. These codes present a tradeoff between the currently popular single error correcting-double error detecting (SEC-DED) ECCs used in SRAMs (that are unable to correct MBUs), and the more robust multi-bit ECC schemes used for MBU reliability. The proposed codes are evaluated and compared against other ECCs using a custom test suite and multi-bit error channel model developed in Matlab as well as Verilog hardware description language (HDL) implementations synthesized using Synopsys Design Compiler and a commercial 65 nm bulk CMOS standard cell library. Simulation results show that for the same check-bit overhead as a conventional 64 data-bit SEC-DED code, the proposed scheme provides a corrected-SER approximately equal to the Bose-Chaudhuri-Hocquenghem (BCH) double error channel. While, for 3 additional check-bits (still 3 less than the BCH DEC code), a triple adjacent error correcting version of the proposed code provides a 2.35x improvement in corrected-SER over the BCH DEC code for 90.9% less ECC circuit area and 17.4% less error correction delay.

For further verification, a 0.4-1.0 V 75 kb single-cycle SRAM macro protected with a programmable, up-to-3-adjacent-bit-correcting version of the proposed ECC has been fabricated in a commercial 28 nm bulk CMOS process. The SRAM macro has undergone neutron irradiation testing at the TRIUMF Neutron Irradiation Facility in Vancouver, Canada. Measurements results show a 189x improvement in SER over an unprotected memory with no ECC enabled and a 5x improvement over a traditional single-error-correction (SEC) code at 0.5 V using 1-way interleaving for the same number of check-bits. This is comparable with the 4.38x improvement observed in simulation. Measurement results confirm an

average active energy of 0.015 fJ/bit at 0.4 V, and average 80 mV reduction in VDD<sub>M I N</sub> across eight packaged chips by enabling the ECC. Both the SRAM macro and ECC circuit were designed for dynamic voltage and frequency scaling for both nominal and low voltage applications using a full-custom circuit design flow.

#### Acknowledgements

I would like to take this opportunity to express my gratitude and thanks to my supervisor **Professor Manoj Sachdev** at the University of Waterloo. I could not have asked for a better supervisor to work with. Without his guidance, knowledge, kindness, and patience, this work would not have been possible. I would also like to thank my examining committee **Dr. Bill Bishop**, **Professor Vincent Gaudet**, **Professor Edlyn Teske-Wilson**, and **Professor Ali Sheikholeslami**. I realize how valuable everyone's time is, and how much of it is required to be a part of a Ph.D. examining committee. Thank you for agreeing to be a part of mine, and thank you for all of your valuable comments and suggestions.

It has been a great pleasure to be a part of the CMOS Design and Reliability (CDR) Group for the last six years throughout this degree and my M.A.Sc. degree. The dedication and talent within this group and its simple but powerful moto of "Aim High" has always inspired me to strive for my best in everything I do. My sincere appreciation goes out to all of the past and current members of this group especially Dr. David Rennie, Dr. Jaspal Singh Shah, and Pierce Chuang.

I would also like to thank the varsity track and field team for supporting me throughout my studies. Having running as an outlet has allowed me to stay physically active, and remain (quasi-)sane over the last four years. Thank you Shane, Kate, Jacob, Oly, Lawrence, Trevor, Justin, Chantel, Kofi, Jenny, Nathan, Mo, Tommy, and everyone else.

Lastly, I would like to acknowledge the funding that I received throughout the duration of my degree from the Natural Sciences and Engineering Research Council (NSERC), Waterloo Institute for Nanotechnology (WIN), and the University of Waterloo. Thank you for believing in my ability to do research.

# Contents

| Li       | st of | Tables                                   | xi   |

|----------|-------|------------------------------------------|------|

| Li       | st of | Figures                                  | xiii |

| Li       | st of | Abbreviations                            | xix  |

| 1        | Intr  | roduction                                | 1    |

|          | 1.1   | Problem Statement                        | 1    |

|          | 1.2   | Soft Error Mechanisms                    | 2    |

|          | 1.3   | Soft Errors in SRAM                      | 4    |

|          | 1.4   | SRAM Soft Error Mitigation Strategies    | 9    |

|          |       | 1.4.1 Process                            | 9    |

|          |       | 1.4.2 Circuit                            | 10   |

|          |       | 1.4.3 Architecture                       | 10   |

|          | 1.5   | Goal of This Research                    | 14   |

|          | 1.6   | Outline                                  | 15   |

| <b>2</b> | Erre  | or Correcting Codes in Computer Memories | 16   |

|          | 2.1   | The Communication Channel                | 16   |

|          | 2.2   | Recent Advances in Coding Theory         | 18   |

|          | 2.3   | SRAM Organization                        | 19   |

|          | 2.4   | Error Types                              | 22   |

|          | 2.5   | ECC Classifications                      | 24   |

|   | 2.6 | Mathe            | ematical Foundation                                                            | 25 |

|---|-----|------------------|--------------------------------------------------------------------------------|----|

|   |     | 2.6.1            | Algebraic Definitions for ECC                                                  | 26 |

|   |     | 2.6.2            | Generator and Parity Check Matrices                                            | 29 |

|   |     | 2.6.3            | Syndrome                                                                       | 32 |

|   |     | 2.6.4            | Encoding-Decoding Example                                                      | 34 |

|   | 2.7 | Perfor           | mance Metrics                                                                  | 35 |

|   |     | 2.7.1            | Area Overhead                                                                  | 35 |

|   |     | 2.7.2            | Performance Impact                                                             | 36 |

|   |     | 2.7.3            | Robustness                                                                     | 37 |

|   | 2.8 | Exam             | ple Codes                                                                      | 38 |

|   |     | 2.8.1            | Single-Parity-Bit Codes                                                        | 38 |

|   |     | 2.8.2            | Hamming SEC Codes                                                              | 39 |

|   |     | 2.8.3            | Hamming SEC-DED Codes                                                          | 41 |

|   |     | 2.8.4            | Hsiao SEC-DED Codes                                                            | 41 |

|   |     | 2.8.5            | BCH Codes                                                                      | 42 |

|   |     | 2.8.6            | Reed-Solomon Codes                                                             | 43 |

|   |     | 2.8.7            | Dutta SEC-DED-DAEC Codes                                                       | 44 |

|   | 2.9 | Summ             | ary                                                                            | 46 |

| 3 | Pro | $\mathbf{posed}$ | Class of Error Correction Codes                                                | 47 |

|   | 3.1 | Code S           | Structure                                                                      | 47 |

|   |     | 3.1.1            | Design Constraints                                                             | 49 |

|   | 3.2 | Code             | Design Procedure                                                               | 51 |

|   |     | 3.2.1            | Degree of Adjacent Error Detection                                             | 52 |

|   |     | 3.2.2            | Degree of Burst Error Detection                                                | 55 |

|   |     | 3.2.3            | Required Number of Check-bits                                                  | 55 |

|   |     | 3.2.4            | Column Vector Selection Procedure for DAEC                                     | 56 |

|   |     | 3.2.5            | Check- and Syndrome-bit Generation XOR Logic Depth and Check-<br>bit Selection | 59 |

|   |     | 3.2.6            | Row Weight Balancing                                                           | 60 |

|   |     | 3.2.7  | Triple Adjacent-bit Error Correction           | 61  |

|---|-----|--------|------------------------------------------------|-----|

|   |     | 3.2.8  | Encoder-Decoder Circuit                        | 63  |

|   | 3.3 | Encod  | ling Process                                   | 64  |

|   | 3.4 | Encod  | ling, Error Injection, Decoding Example        | 65  |

|   |     | 3.4.1  | Encoding                                       | 66  |

|   |     | 3.4.2  | Error Injection                                | 66  |

|   |     | 3.4.3  | Decoding                                       | 67  |

|   | 3.5 | H-Ma   | trix Generation and Verification               | 68  |

|   |     | 3.5.1  | Construction Algorithm                         | 68  |

|   | 3.6 | Evalua | ation                                          | 69  |

|   |     | 3.6.1  | Error Correction and Detection Capabilities    | 71  |

|   |     | 3.6.2  | Implementation Area                            | 71  |

|   |     | 3.6.3  | Encoder and Decoder Propagation Delay          | 74  |

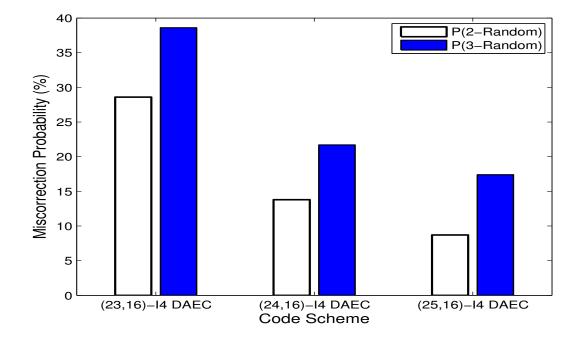

|   |     | 3.6.4  | Miscorrection Probability                      | 76  |

|   |     | 3.6.5  | Implementation Summary                         | 77  |

|   |     | 3.6.6  | Modified Codes                                 | 78  |

|   | 3.7 | Summ   | nary                                           | 85  |

| 4 | Imp | olemen | tation, Verification, and Measurement          | 86  |

|   | 4.1 | Soft E | Error Rate Modeling                            | 86  |

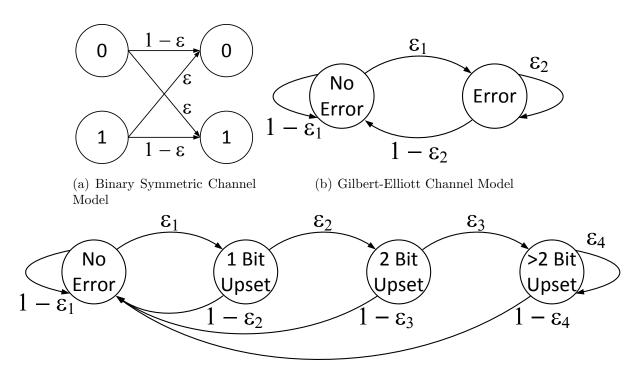

|   |     | 4.1.1  | Error Channel Model                            | 86  |

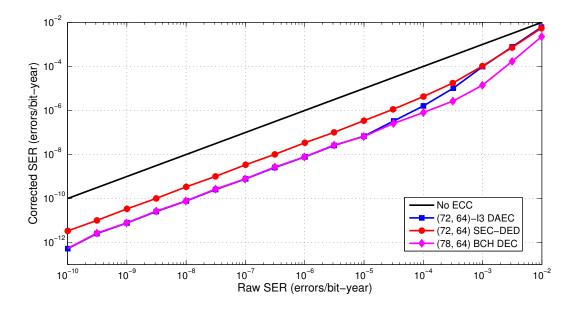

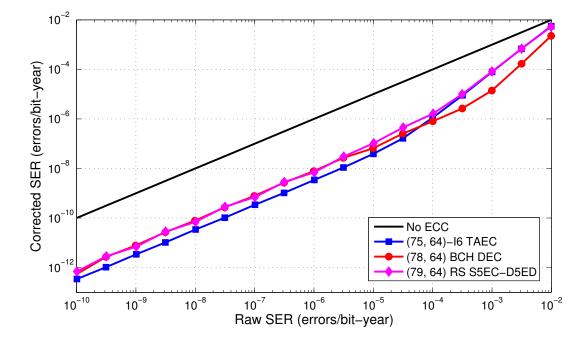

|   |     | 4.1.2  | Simulation Results - Corrected-SER vs. Raw-SER | 89  |

|   | 4.2 | Test C | Chip Design                                    | 95  |

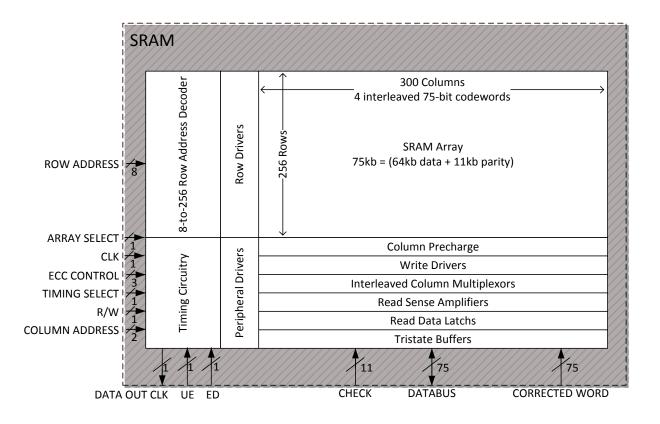

|   |     | 4.2.1  | Memory Organization                            | 98  |

|   |     | 4.2.2  | Memory Address Space                           | 99  |

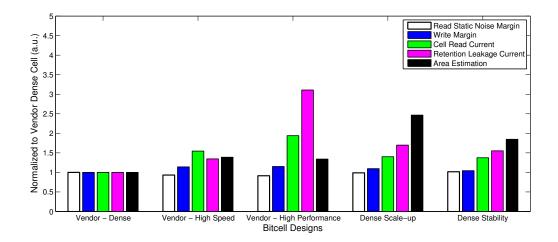

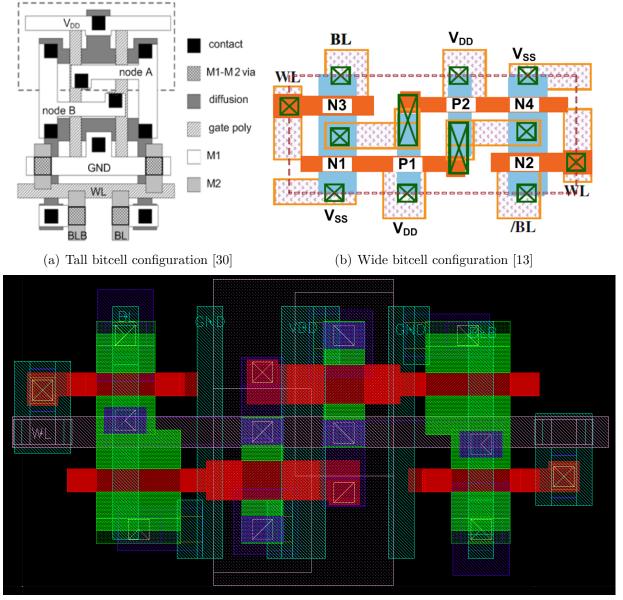

|   |     | 4.2.3  | Memory Bitcell                                 | 101 |

|   |     | 4.2.4  | Row Conditioning Circuitry                     | 104 |

|   |     | 4.2.5  | Column Conditioning Circuitry                  | 105 |

|   |     | 4.2.6  | ECC Circuit                                    | 109 |

|          |       | 4.2.7   | Timing and Control Circuitry                                        | 112  |

|----------|-------|---------|---------------------------------------------------------------------|------|

|          |       | 4.2.8   | Performance Simulations                                             | 116  |

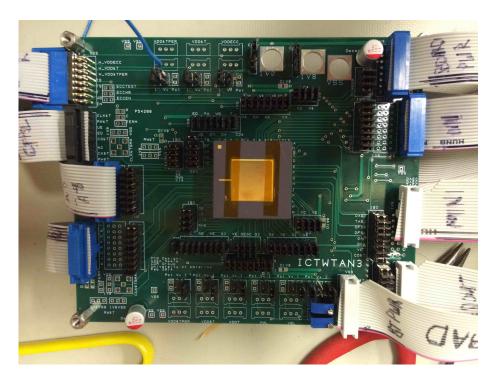

|          |       | 4.2.9   | Printed Circuit Board Design                                        | 116  |

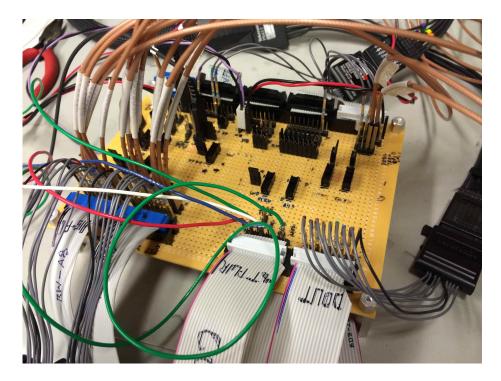

|          | 4.3   | Silicon | Measurement                                                         | 119  |

|          | 4.4   | Radiat  | ion Testing                                                         | 124  |

|          |       | 4.4.1   | Experimental Setup                                                  | 126  |

|          |       | 4.4.2   | Measurement Results                                                 | 127  |

|          | 4.5   | Vendo   | r Cell SER Estimation                                               | 133  |

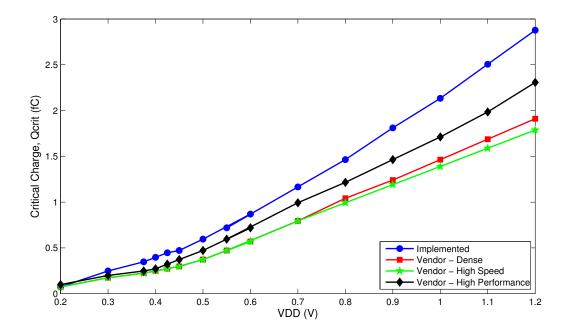

|          |       | 4.5.1   | Critical Charge SPICE Estimations                                   | 133  |

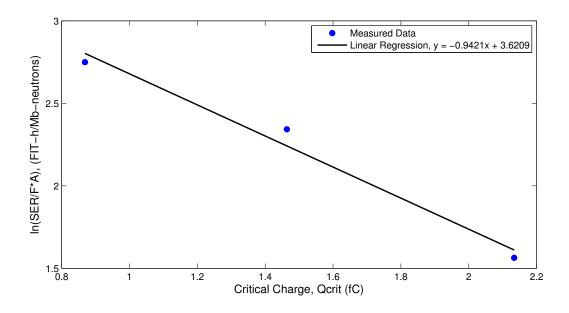

|          |       | 4.5.2   | Parameter Extraction                                                | 135  |

|          |       | 4.5.3   | SER Performance                                                     | 138  |

|          | 4.6   | Summ    | ary                                                                 | 142  |

| <b>5</b> | Con   | clusior | ns and Future Work                                                  | 143  |

|          | 5.1   |         | butions to the Field                                                | 143  |

|          |       | 5.1.1   | A New Class of Error Correcting Codes for Adjacent Multi-bit Upsets | 3143 |

|          |       | 5.1.2   | Soft Error Rate Modeling                                            | 144  |

|          |       | 5.1.3   | 28 nm Test Chip Design and Implementation                           | 144  |

|          |       | 5.1.4   | Soft Error Rate Estimations for Vendor Cells                        | 145  |

|          |       | 5.1.5   | Publications                                                        | 145  |

|          | 5.2   | Future  | Work                                                                | 145  |

| ٨        | Trees | lomon   | ted II Matricea                                                     | 147  |

| A        |       |         |                                                                     |      |

|          | A.1   |         | ca-bit Codes                                                        | 147  |

|          |       | A.1.1   | SEC-DED-DAEC-yAED                                                   | 147  |

|          |       | A.1.2   | SEC-DED-TAEC-yAED                                                   | 148  |

|          | A.2   |         | ca-bit Codes                                                        | 149  |

|          |       | A.2.1   | SEC-DED-DAEC-yAED                                                   | 149  |

|          |       | A.2.2   | SEC-DED-TAEC-yAED                                                   | 150  |

|          | A.3   | 64 Dat  | a-bits                                                              | 151  |

|    |        | A.3.1    | SEC-DED-DA      | EC-yAEI    | D    |    | <br>• • | <br> | <br> | • | <br>• |  | • | 151 |

|----|--------|----------|-----------------|------------|------|----|---------|------|------|---|-------|--|---|-----|

|    |        | A.3.2    | SEC-DED-TA      | EC-yAEI    | )    |    | <br>    | <br> | <br> | • |       |  |   | 152 |

|    | A.4    | Increas  | sed Identity Ma | atrix Size | Code | в. | <br>    | <br> | <br> | • |       |  |   | 153 |

|    |        | A.4.1    | 32 Data-bits .  |            |      |    | <br>    | <br> | <br> | • |       |  |   | 153 |

|    |        | A.4.2    | 64 Data-bits .  |            |      |    | <br>    | <br> | <br> | • |       |  |   | 154 |

|    | A.5    | Increas  | sed Check-bit ( | Codes      |      |    | <br>    | <br> | <br> | • |       |  |   | 155 |

|    | A.6    | Optim    | ized Code       |            |      |    | <br>    | <br> | <br> |   |       |  |   | 155 |

|    | A.7    | Dutta    | Codes           |            |      |    | <br>    | <br> | <br> | • |       |  |   | 156 |

|    | A.8    | BCH (    | Codes           |            |      |    | <br>    | <br> | <br> |   |       |  |   | 157 |

|    | A.9    | Reed S   | olomon Codes    |            |      |    | <br>    | <br> | <br> | • |       |  |   | 158 |

| в  | Deta   | ails of  | Test Chip       |            |      |    |         |      |      |   |       |  |   | 159 |

| С  | Pub    | olicatio | ns From This    | s Work     |      |    |         |      |      |   |       |  |   | 169 |

| Re | eferei | nces     |                 |            |      |    |         |      |      |   |       |  |   | 171 |

# List of Tables

| 1.1 | MCU bit width and percentage of the total SER for 45 nm, 32 nm, and 22 nm technologies [6]                                                                                            | 7   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Code Parameters for RS SbEC-DbED Codes                                                                                                                                                | 44  |

| 2.2 | (22, 16) SEC-DED-DAEC Dutta Code Column Uniqueness Table $\ldots$ .                                                                                                                   | 46  |

| 3.1 | (24, 16) $\mathbf{I}_5$ SEC-DED-DAEC-7AED Column Uniqueness Table                                                                                                                     | 59  |

| 3.2 | Set of 3-bit Columns with Various Column Weights                                                                                                                                      | 61  |

| 3.3 | (24, 16) $\mathbf{I}_5$ SEC-DED-TAEC-6AED Column Uniqueness Table $\ldots \ldots$                                                                                                     | 62  |

| 3.4 | H-Matrix Code Comparison Summary                                                                                                                                                      | 79  |

| 3.5 | Synthesis Results Comparison Summary                                                                                                                                                  | 80  |

| 3.6 | Increased Identity Matrix Size Code Comparison                                                                                                                                        | 82  |

| 3.7 | (24, 16) $\mathbf{I}_5$ Optimized Code Example $\ldots \ldots \ldots$ | 84  |

| 4.1 | Example Error Distribution Before and After Error Correction Using the SEC-DED-TAEC-8AED Code                                                                                         | 88  |

| 4.2 | MCU bit width and percentage of the total SER comparison between the 4-state Markov chain model and 22 nm technology in [6]                                                           | 89  |

| 4.3 | ECC Check-bit Overheads                                                                                                                                                               | 89  |

| 4.4 | Test Chip Operating Modes                                                                                                                                                             | 98  |

| 4.5 | Test Chip 16-bit Memory Address Space                                                                                                                                                 | 100 |

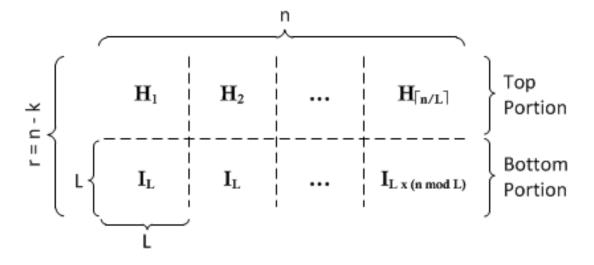

| 4.6 | 8-bit Byte Divisions for 75-bit Codewords                                                                                                                                             | 101 |

| 4.7 | Implemented 6T Bitcell Sizing                                                                                                                                                         | 102 |

| 4.8 | Programmable Error Correction Controller                                                                                                                                              | 110 |

| 4.9  | Features of Fabricated 28 nm Test Chip                                       | 121 |

|------|------------------------------------------------------------------------------|-----|

| 4.10 | $VDD_{MIN}$ Measurement for 8 Test Chips                                     | 122 |

| 4.11 | Average Power Measurement for 2 Test Chips Capable of 400 mV Operation       | 122 |

| 4.12 | Measured Error Injection Example                                             | 123 |

| 4.13 | Design Comparison                                                            | 124 |

| 4.14 | Soft Error Rate Calculation from Radiation Test Data for 0.4 V to 1.0 V $$ . | 129 |

| 4.15 | SER using Different Data Patterns for $V_{DD} = 0.5$ V, time = 2 hours       | 131 |

| 4.16 | 28 nm SRAM Bitcell SER Comparison at Nominal (1.0 V) Supply Voltage          | 139 |

| 4.17 | $28~\mathrm{nm}$ SRAM Bitcell MCU Width Comparison at 500 mV Supply Voltage  | 142 |

|      |                                                                              |     |

| B.1  | Pin Description for ICTWTAN3 120 PGA Test Chip - Pins 120-61                 | 167 |

| B.2  | Pin Description for ICTWTAN3 120 PGA Test Chip - Pins 60-1                   | 168 |

|      |                                                                              |     |

# List of Figures

| 1.1 | Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion [4]                     | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | 6-Transistor SRAM Cell. Assuming the cell is holding the data ( $Q = 1, QB = 0$ ), the drain diffusions for devices N1 and P2 are sensitive to particle induced upsets. | 5  |

| 1.3 | SRAM parameters - normalized cell area, normalized $Q_{crit}$ , and operating voltage as a function of technology node [4], [10]                                        | 6  |

| 1.4 | System-SER, bit-SER and percentage MCU of the total SER as a function of technology node [6].                                                                           | 7  |

| 1.5 | Frequency distribution of the number of soft errors generated per SEU due to neutron irradiation of 65 nm and 90 nm SRAMs [16].                                         | 8  |

| 1.6 | Maximum adjacent MBU width as a function of technology. Derived from [18, 19, 16, 20, 6]                                                                                | 8  |

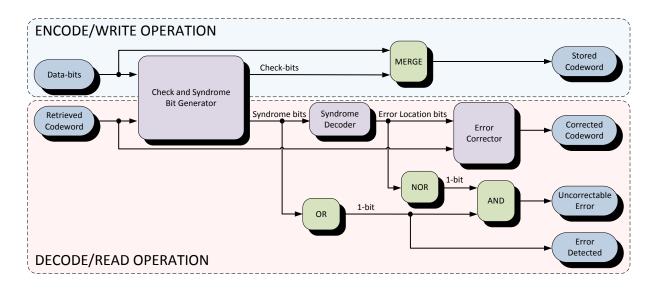

| 1.7 | ECC Block Diagram                                                                                                                                                       | 11 |

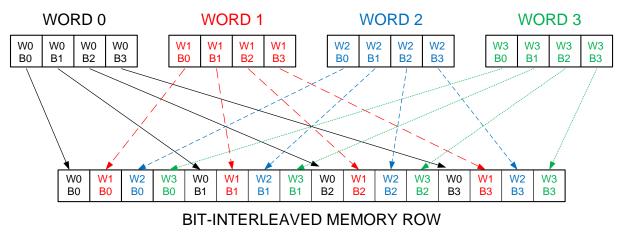

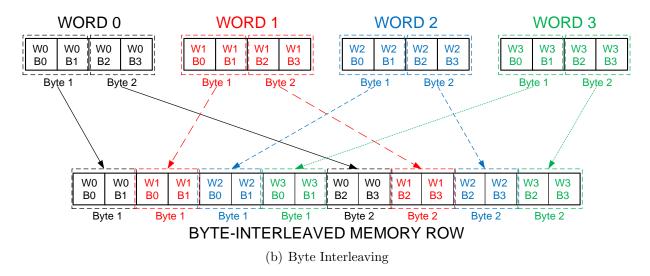

| 1.8 | Types of Interleaving                                                                                                                                                   | 13 |

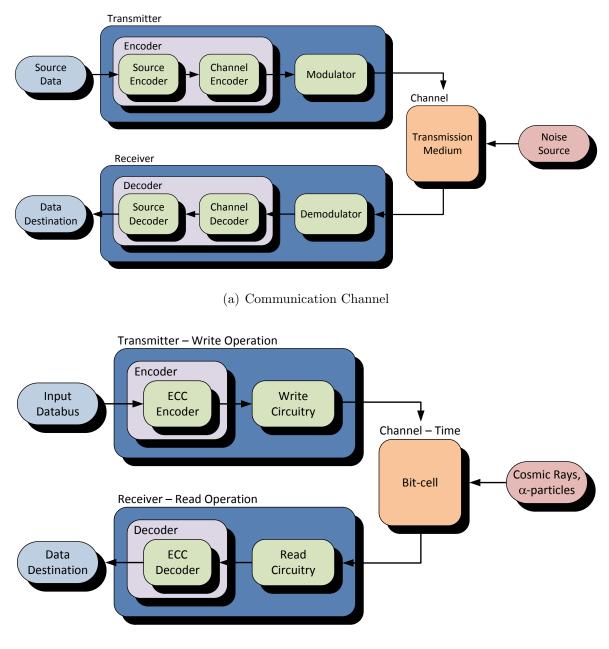

| 2.1 | Block diagrams for the communication channel and memory storage systems including ECC blocks. Adapted from [49, 50]                                                     | 17 |

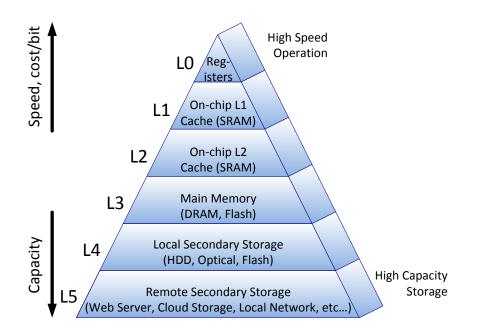

| 2.2 | Computer memory hierarchial organization structure. SRAM is typically<br>used as the main building block for system registers, on-chip cache, and                       | 20 |

|     | various buffers.                                                                                                                                                        | 20 |

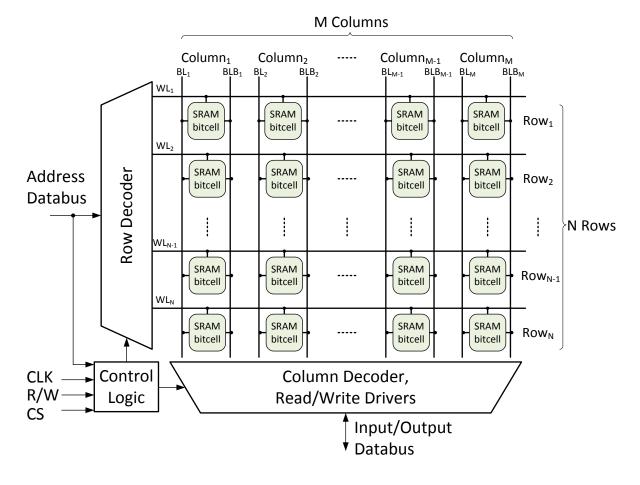

| 2.3 | $N \times M$ SRAM Array with Peripheral Circuitry                                                                                                                       | 21 |

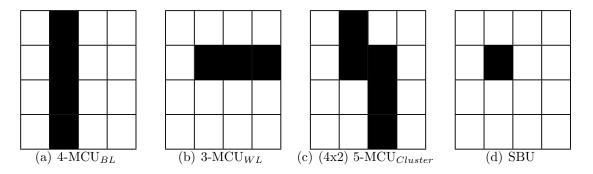

| 2.4 | MCU Upset Classifications                                                                                                                                               | 22 |

| 2.5 | MBU Upset Classifications                                                                                                                                               | 23 |

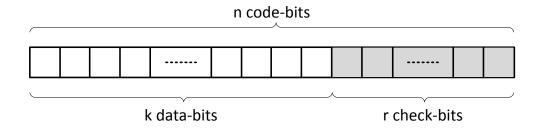

| 2.6 | (n, k) codeword structure. The <i>n</i> -bit codeword consists of k data-bits and r parity check-bits                                                                   | 25 |

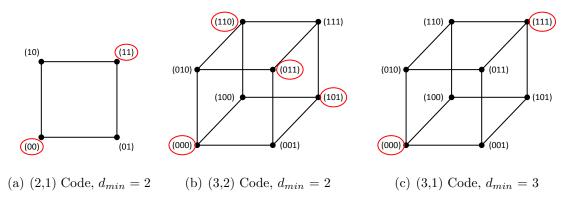

| 2.7  | Minimum Hamming Distance Example                                                                                                                                                                                                                                                                                                                                                  | 27 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

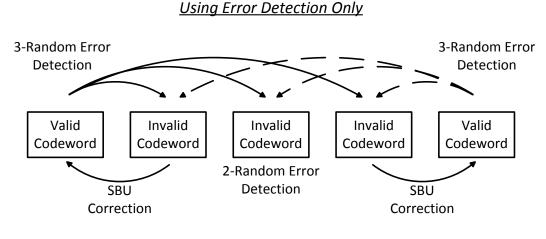

| 2.8  | Provided that $d_{min} = 4$ , the code is capable of either 1-bit error correction,<br>3-bit error detection, or 1-bit error correction with 2-bit error detection                                                                                                                                                                                                                | 28 |

| 2.9  | Example <b>H</b> -matrix Configurations Using Sub-matrices                                                                                                                                                                                                                                                                                                                        | 31 |

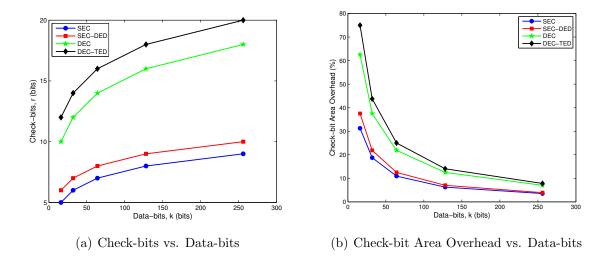

| 2.10 | Area overhead comparisons for SEC, SEC-DED, DEC BCH, and DEC-TED BCH codes of various data lengths.                                                                                                                                                                                                                                                                               | 36 |

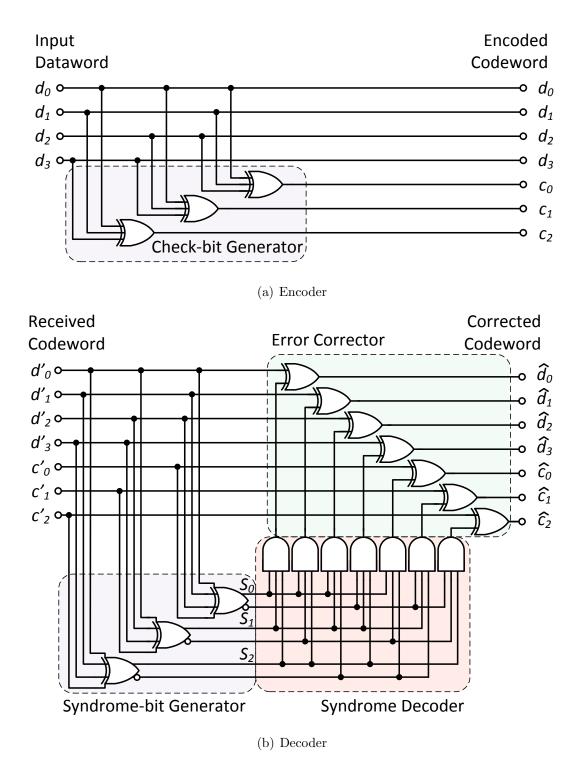

| 2.11 | Encoder and decoder of the Hamming $(7,4)$ SEC code                                                                                                                                                                                                                                                                                                                               | 40 |

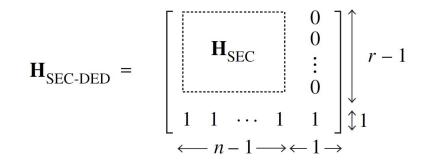

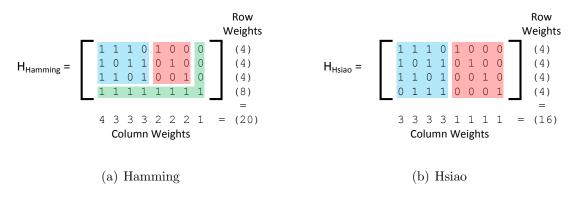

| 2.12 | (8,4) Hamming and Hsiao SEC-DED Matrices                                                                                                                                                                                                                                                                                                                                          | 42 |

| 2.13 | (26, 16) BCH DEC Syndrome Generation Logic                                                                                                                                                                                                                                                                                                                                        | 43 |

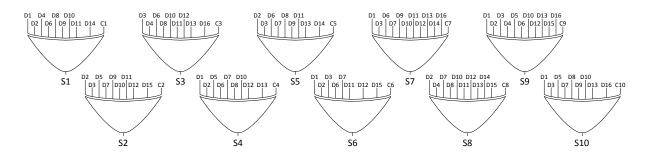

| 2.14 | (25, 16) $b = 3$ Reed Solomon code byte organization                                                                                                                                                                                                                                                                                                                              | 44 |

| 2.15 | (22, 16) SEC-DED-DAEC Dutta code. Adapted from [44]                                                                                                                                                                                                                                                                                                                               | 45 |

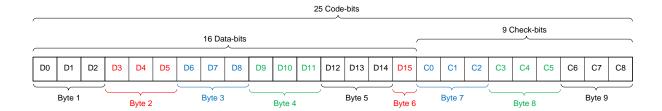

| 3.1  | Generalized $(n, k)$ $\mathbf{I}_L$ <b>H</b> -matrix structure for the proposed class of ECCs .                                                                                                                                                                                                                                                                                   | 48 |

| 3.2  | Example (23, 16) $I_4$ SEC-DED-DAEC-5AED Code $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                | 48 |

| 3.3  | Example (24, 16) $\mathbf{I}_5$ SEC-DED-DAEC-7AED Parity Check Matrix                                                                                                                                                                                                                                                                                                             | 51 |

| 3.4  | Identity matrix check-bit organization. Selecting check-bits in this manner allows for adjacent error detection.                                                                                                                                                                                                                                                                  | 53 |

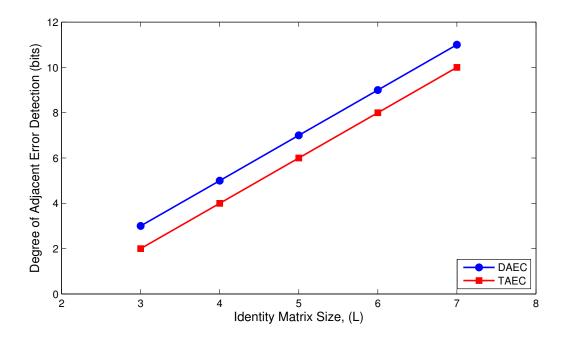

| 3.5  | Degree of adjacent error detection versus identity matrix size, L $\ldots$ .                                                                                                                                                                                                                                                                                                      | 54 |

| 3.6  | Column vector selection procedure.                                                                                                                                                                                                                                                                                                                                                | 57 |

| 3.7  | Example (24, 16) $\mathbf{I}_5$ SEC-DED-TAEC-6AED Parity Check Matrix                                                                                                                                                                                                                                                                                                             | 62 |

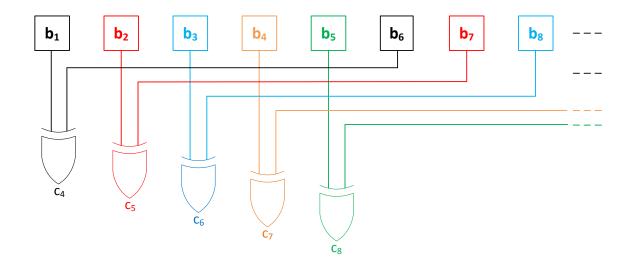

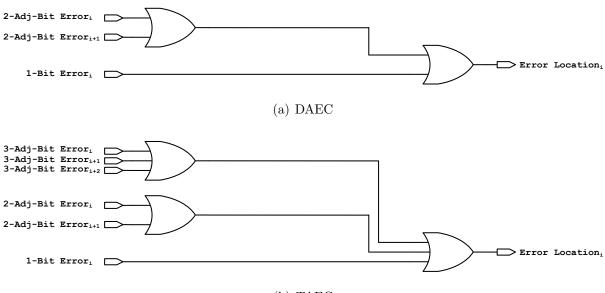

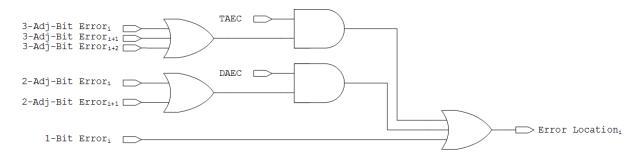

| 3.8  | For the DAEC and TAEC codes, each codeword bit can be involved in 3 and 6 different correctable error patterns respectively. By OR'ing the decoded syndrome value for each of these error patterns together, it can be determined if a particular bit was involved in an error. By implementing this circuitry for each codeword bit, and error location vector can be generated. | 63 |

| 3.9  | (24, 16) $\mathbf{I}_5$ SEC-DED-TAEC-6AED Encoder Generator Matrices                                                                                                                                                                                                                                                                                                              | 64 |

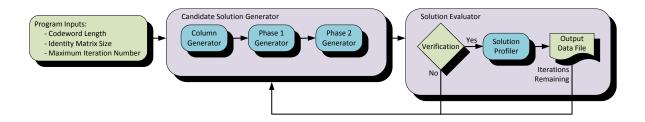

| 3.10 | Matlab Solution Solver Flow Graph                                                                                                                                                                                                                                                                                                                                                 | 68 |

| 3.11 | <b>H</b> -matrix construction algorithm $\ldots \ldots \ldots$                                                                                                                                                                                                                                                     | 70 |

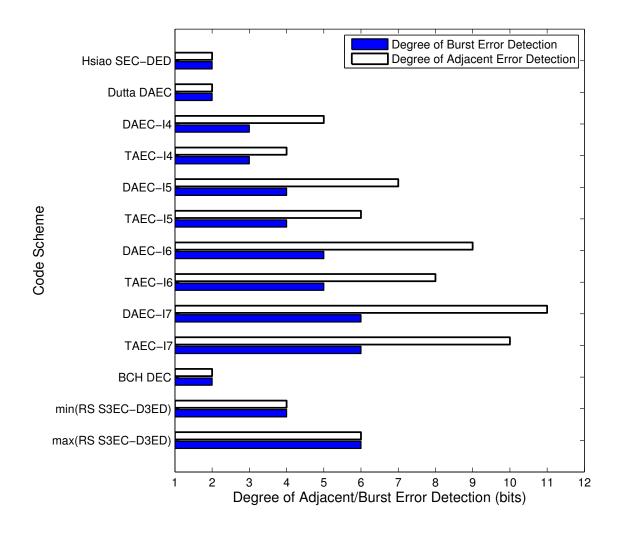

| 3.12 | Adjacent and burst error detection for the proposed codes as a function of $I_L$ matrix size compared with the SEC-DED-DAEC Dutta, BCH DEC, and RS S3EC-D3EC codes.                                                                                                                                                                                                               | 72 |

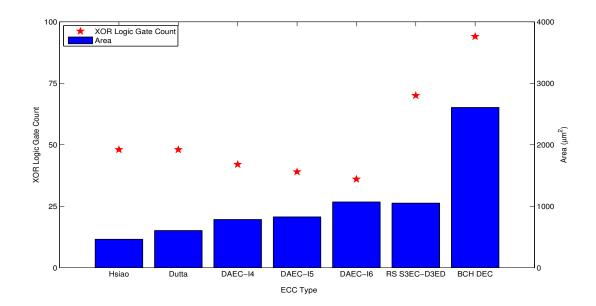

| 3.13 | Check- and syndrome-bit generation XOR logic gate count and synthesized<br>area for the proposed 16 data-bit SEC-DED-DAEC-yAED code implemen-<br>tations, (22, 16) SEC-DED-DAEC Dutta code, (25, 16) RS code, and (26,<br>16) DEC BCH code                                                     | 73         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

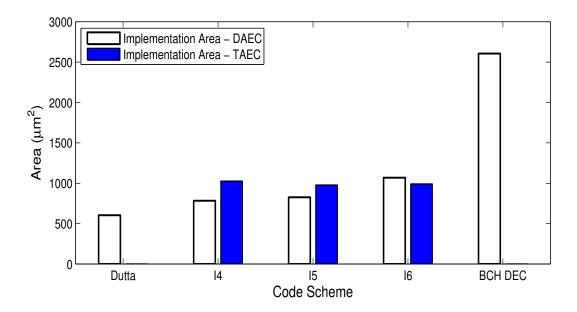

| 3.14 | Synthesized area comparison between the proposed 16 data-bit DAEC and TAEC code implementations for the equivalent number of check bits 7                                                                                                                                                      | 74         |

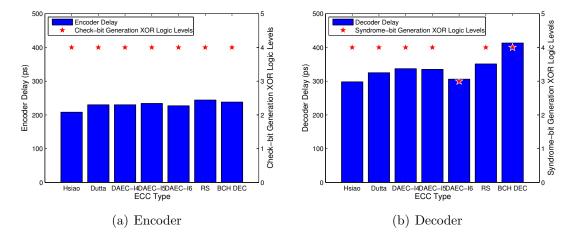

| 3.15 | Synthesized propagation delay estimation for the proposed 16 data-bit SEC-<br>DED-DAEC-yAED code implementations, (22, 16) SEC-DED-DAEC Dutta<br>code, (25, 16) RS code, and (26, 16) DEC BCH code                                                                                             | <i>'</i> 5 |

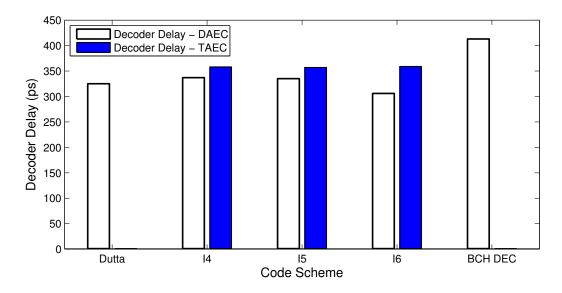

| 3.16 | Synthesized propagation delay comparison between the proposed 16 data-<br>bit DAEC code implementations and the TAEC implementations for the<br>equivalent number of check bits                                                                                                                | 76         |

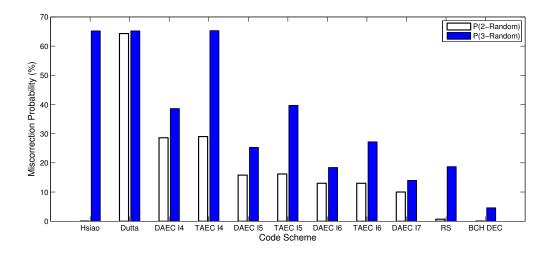

| 3.17 | Miscorrection probabilities for 2-random and 3-random bit errors for the proposed 16 data-bit SEC-DED-DAEC-yAED code implementations, (22, 6) Hsiao SEC-DED code, (22, 16) SEC-DED-DAEC Dutta code, (25, 16) RS code, and (26, 16) DEC BCH code                                                | 77         |

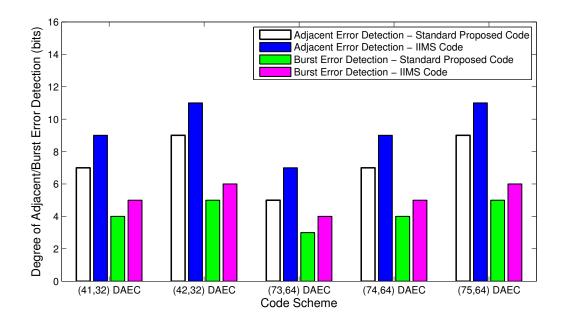

| 3.18 | Degree of adjacent and burst error detection for Increased Identity Matrix<br>Size codes compared to their equivalent SEC-DED-DAEC-yAED codes for<br>the same number of check-bits                                                                                                             | 31         |

| 3.19 | Miscorrection probabilities for 16 Data-bit Increased Check-bit codes 8                                                                                                                                                                                                                        | 82         |

| 3.20 | Optimized (24, 16) $\mathbf{I}_5$ code with maximum row weight of 8                                                                                                                                                                                                                            | 84         |

| 4.1  | Radiation Induced Noise Channel Models    8                                                                                                                                                                                                                                                    | 87         |

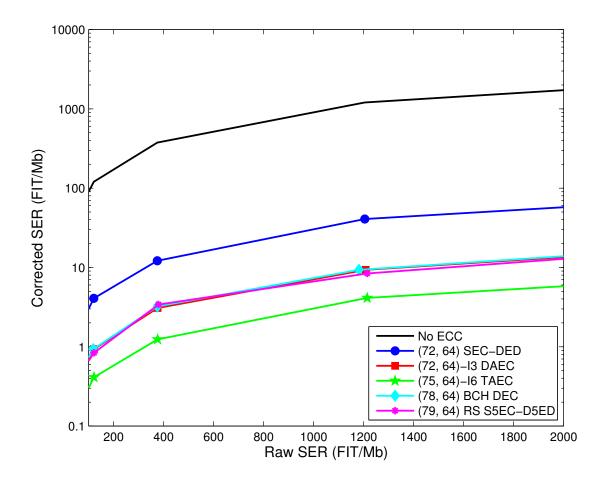

| 4.2  | Corrected-SER vs. raw-SER for $(72, 64)$ -I <sub>3</sub> SEC-DED-DAEC-3AED, (72, 64) SEC-DED, and (78, 64) BCH DEC codes using a 4-state Markov chain error channel model. $\dots \dots \dots$ | 90         |

| 4.3  | Corrected-SER vs. raw-SER for (75, 64)-I <sub>6</sub> SEC-DED-TAEC-8AED, (78, 64) BCH DEC, and (79, 64) Reed Solomon S5EC-D5ED codes using a 4-state Markov chain error channel model                                                                                                          | )1         |

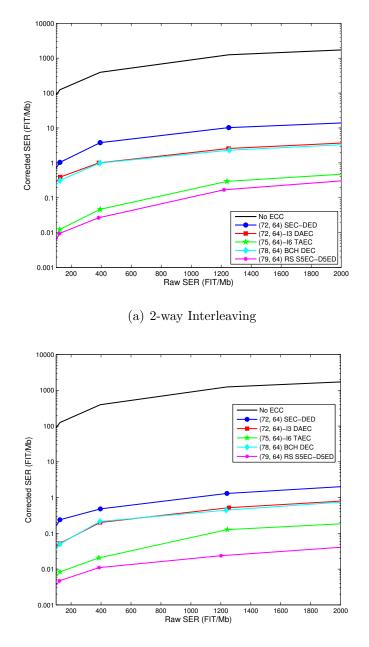

| 4.4  | Simulated corrected-SER vs. raw-SER for various ECC schemes using 1-way interleaving                                                                                                                                                                                                           | 92         |

| 4.5  | Simulated corrected-SER vs. raw-SER for various ECC schemes using 2-, and 4-way interleaving                                                                                                                                                                                                   | )3         |

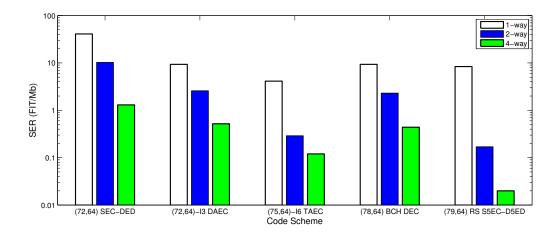

| 4.6  | Simulated corrected-SER as a function of word interleaving for various ECC schemes at a raw-SER of 1200 FIT/Mb                                                                                                                                                                                 | 95         |

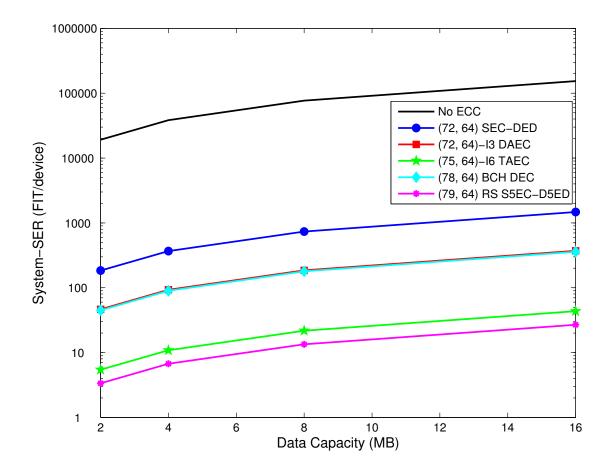

| 4.7  | System level SER/device for 2 to 16 MB data capacity for various ECC schemes at a raw-SER of 1200 FIT/Mb using 2-way interleaving                                       | 96  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

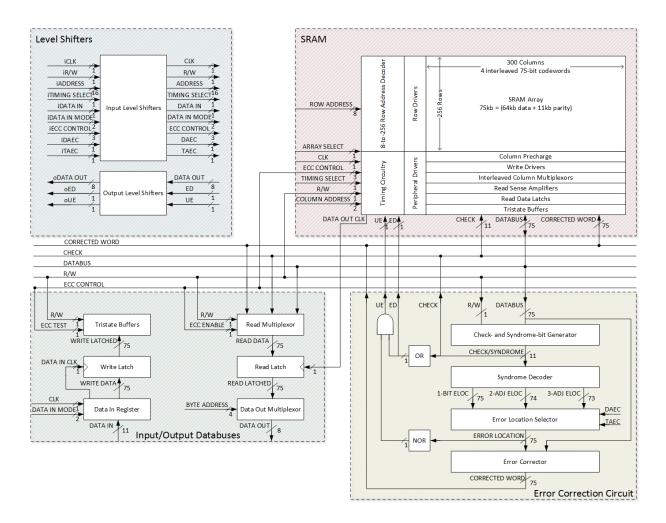

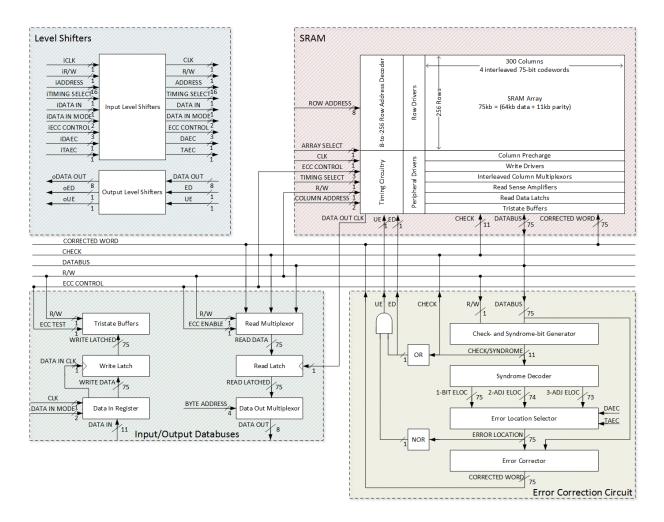

| 4.8  | 6T SRAM macro and error correction circuit block diagram with input/output databus interface and voltage domain level shifters                                          | 97  |

| 4.9  | SRAM Macro Block Diagram                                                                                                                                                | 99  |

| 4.10 | Row organization for 1-, 2-, and 4-way interleaving                                                                                                                     | 100 |

| 4.11 | SRAM bitcell design comparison with vendor supplied bitcells $\ldots$ .                                                                                                 | 102 |

| 4.12 | SRAM bitcell layout configurations                                                                                                                                      | 103 |

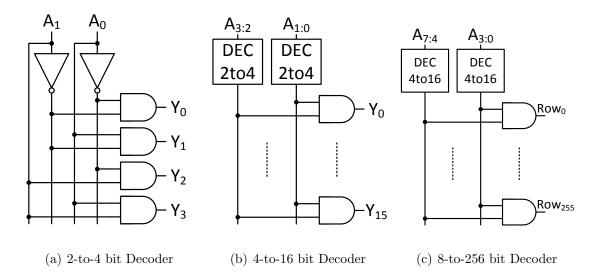

| 4.13 | Hierarchical 2-input AND Gate-based 8-to-256 Address Decoder Unit $\ .\ .$ .                                                                                            | 104 |

| 4.14 | Wordline Driver Circuit                                                                                                                                                 | 105 |

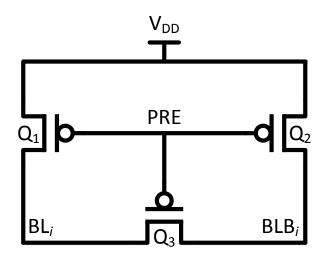

| 4.15 | Precharge and Equalize Circuit                                                                                                                                          | 106 |

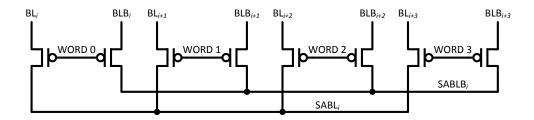

| 4.16 | 4-to-1 Differential Column Multiplexer Circuit                                                                                                                          | 107 |

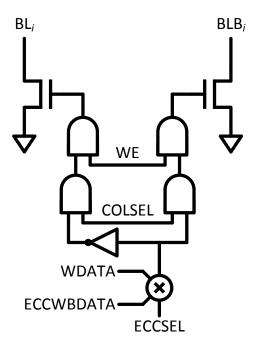

| 4.17 | Write Driver Circuit                                                                                                                                                    | 108 |

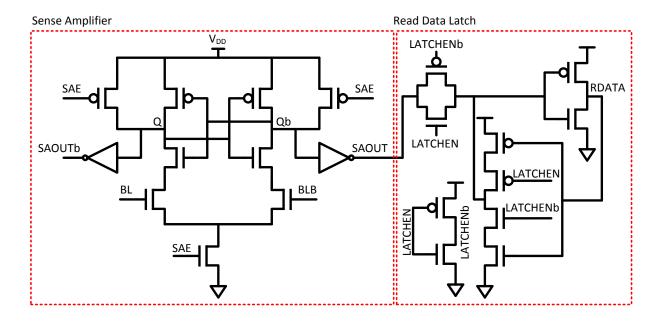

| 4.18 | Current Latch-Based Sense Amplifier Circuit with Read Data Latch                                                                                                        | 109 |

| 4.19 | Implemented (75, 64) $\mathbf{I}_6$ SEC-DED-TAEC-8AED Code <b>H</b> -matrix                                                                                             | 110 |

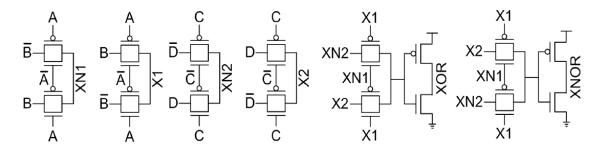

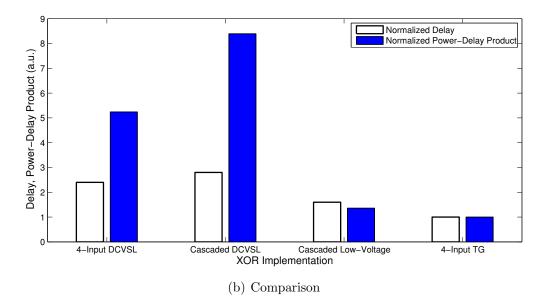

| 4.20 | 4-input transmission-gate based XOR circuit schematic and XOR gate com-<br>parision.                                                                                    | 111 |

| 4.21 | Programmable Syndrome Decoder Selector Logic Bit-slice                                                                                                                  | 111 |

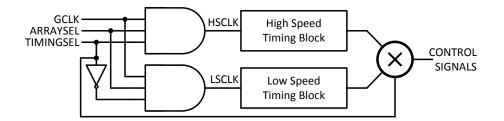

| 4.22 | Timing Block Select Circuitry                                                                                                                                           | 112 |

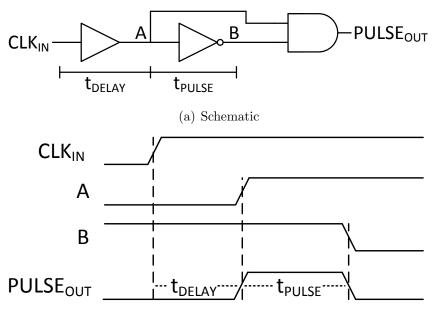

| 4.23 | An inverter-delay-line-based pulse generator is used for generating internal timing signals based solely on the rising edge transition of the input clock signal (CLK). | 113 |

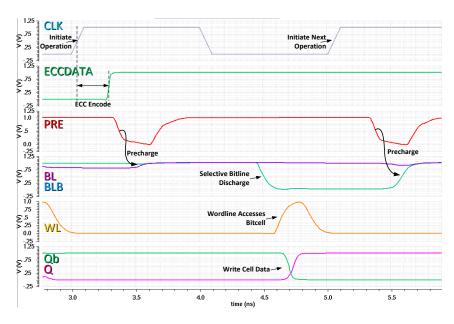

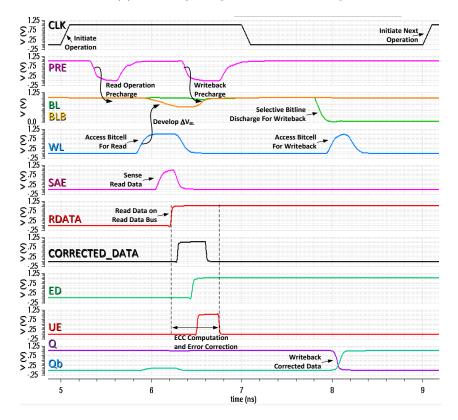

| 4.24 | Write and read timing control signals with ECC functionality.                                                                                                           | 115 |

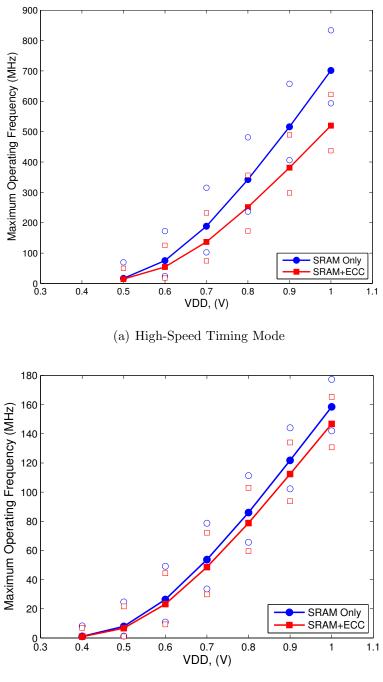

| 4.25 | Simulated memory timing performance with and without ECC enabled as a function of supply voltage. Simulations performed at $(TT/27 \ ^{o}C)$ , $(SS/-$                  |     |

|      | 25 °C), and (FF/85 °C)                                                                                                                                                  | 117 |

| 4.26 | PCB for test chip measurements                                                                                                                                          | 118 |

| 4.27 | PCB for external controller card                                                                                                                                        | 119 |

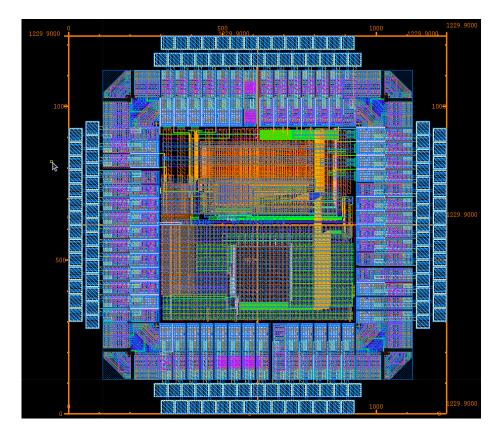

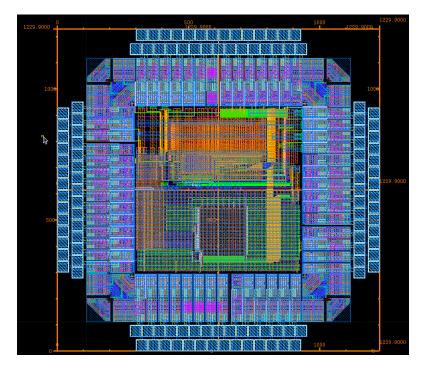

| 4.28 | 75 kb SRAM Macro with ECC Full Chip Layout                                                                                                                              | 120 |

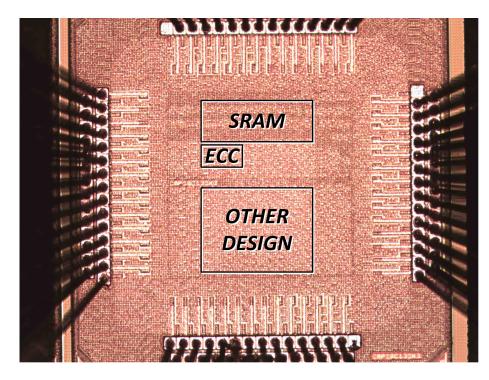

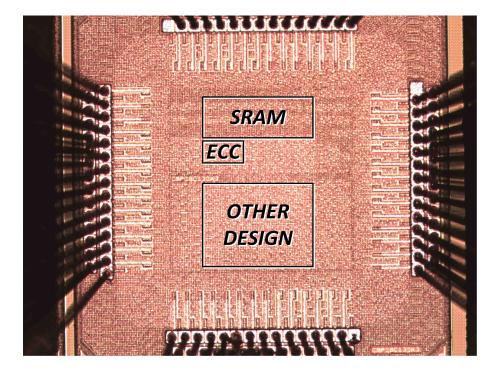

| 4.29 | 75 kb SRAM Macro with ECC Die Photo                                                                                                                                     | 121 |

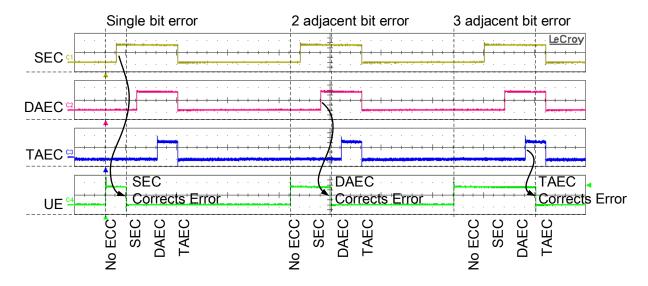

| 4.30 | Measured error injection example. Additional ECC functionality is required to perform error corrections as the injected error size increases                            | 123 |

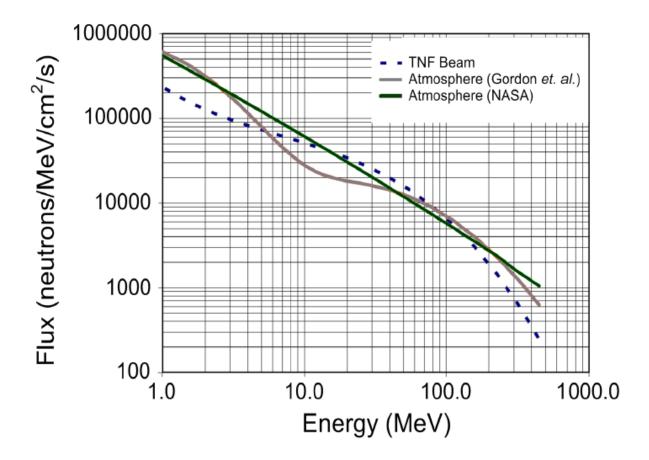

| 4.31 | NIF neutron beam spectrum compared with the atmospheric spectrum [81].                                                                                                                                                                                                                                                                                                                                                           | 125  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

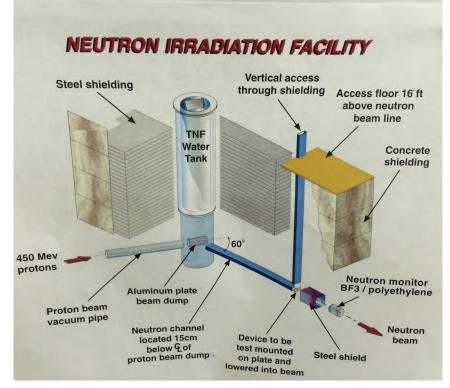

| 4.32 | TRIUMF NIF test facility and test station equipment setup                                                                                                                                                                                                                                                                                                                                                                        | 128  |

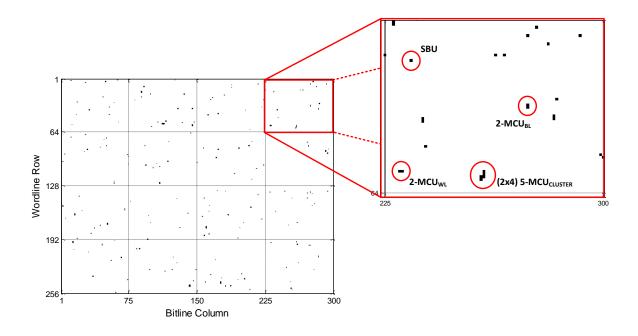

| 4.33 | Superposition of all soft error measurement error location bitmaps for $V_{DD} = 500 \text{ mV}.$                                                                                                                                                                                                                                                                                                                                | 129  |

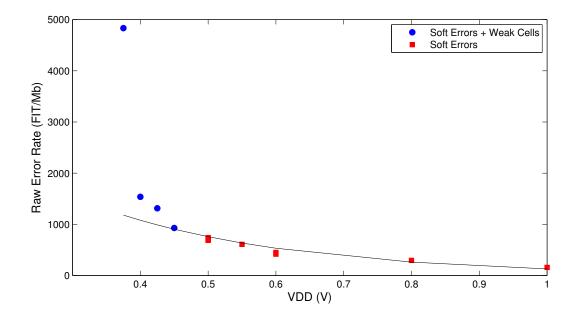

| 4.34 | Raw error rate (radiation induced soft errors plus weak cells) vs. $V_{DD}$ without ECC protection.                                                                                                                                                                                                                                                                                                                              | 130  |

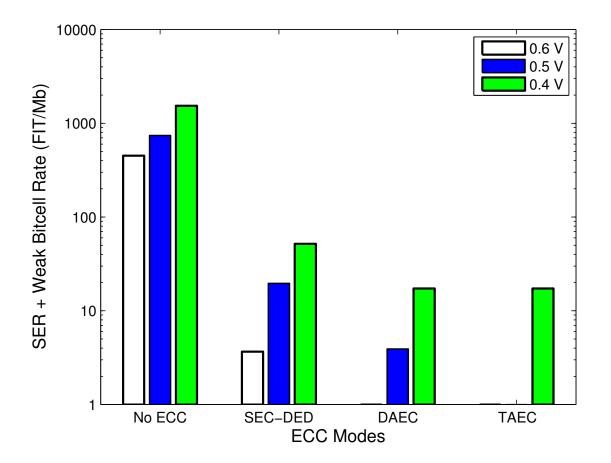

| 4.35 | Radiation induced SER plus VDD induced weak bitcell rates for each ECC mode. Weak bitcell upsets only occur at the 400 mV datapoints                                                                                                                                                                                                                                                                                             | 132  |

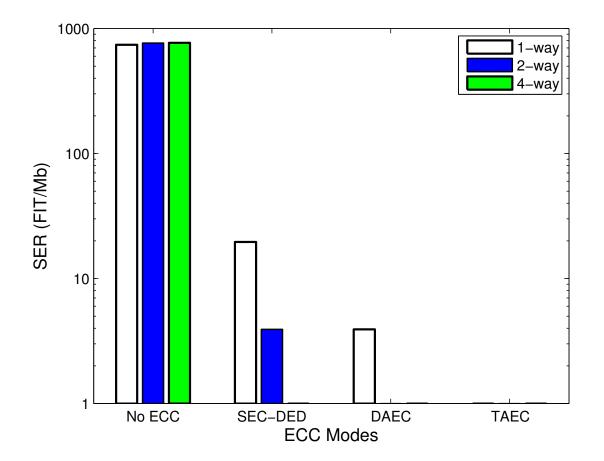

| 4.36 | Radiation induced SER for each ECC mode at $V_{DD} = 500$ mV for 1-, 2-, and 4-way interleaving.                                                                                                                                                                                                                                                                                                                                 | 134  |

| 4.37 | 6T SRAM Bitcell Critical Charge Testbench                                                                                                                                                                                                                                                                                                                                                                                        | 135  |

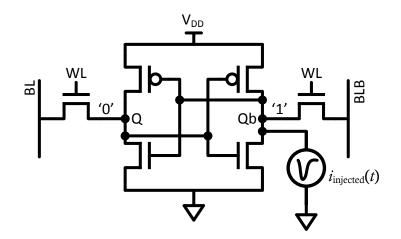

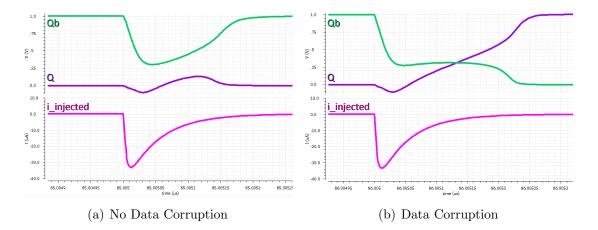

| 4.38 | By incrementally increasing the peak charge, $Q$ , deposited by an exponential current pulse, $i_{injected}(t)$ , the critical charge, $Q_{crit}$ , necessary to corrupt a bitcell can be determined.                                                                                                                                                                                                                            | 136  |

| 4.39 | Critical charge as a function of supply voltage $V_{DD}$ for the implemented bitcell and vendor supplied cells.                                                                                                                                                                                                                                                                                                                  | 136  |

| 4.40 | Extraction of charge collection efficiency, $Q_s$ , and proportionality constant, $k$                                                                                                                                                                                                                                                                                                                                            | .137 |

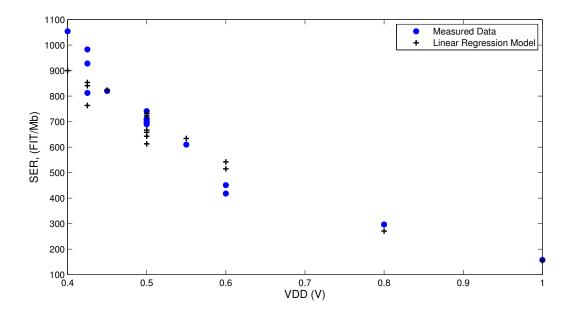

| 4.41 | Measured and modeled SER vs. $V_{DD}$ . Modeled data is within 15% of measured data for all data points except for one point at $V_{DD} = 0.6$ V, Measured = 417.95 FIT/Mb, Model = 541.80 FIT/Mb, Percent Difference = 29.6%.                                                                                                                                                                                                   | 138  |

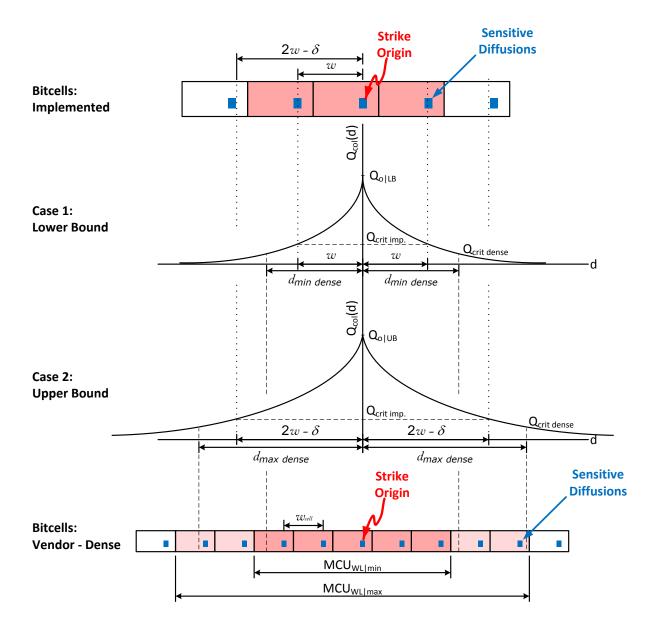

| 4.42 | MCU width bounds for vendor supplied cells can be determined from their $Q_{crit}$ , bitcell width, and $Q_o$ upper and lower bound parameter extracted from the implemented bitcell's simulated and radiation test data. In this example, a particle strike causing a $3$ -MCU <sub>WL</sub> using the implemented bitcell could create an upset ranging from a $5$ -MCU <sub>WL</sub> to a $9$ -MCU <sub>WL</sub> for an array |      |

|      | implemented using the vendor's dense bitcell.                                                                                                                                                                                                                                                                                                                                                                                    | 141  |

| A.1  | 16 Data-bit SEC-DED-DAEC-yAED Codes                                                                                                                                                                                                                                                                                                                                                                                              | 147  |

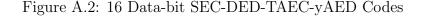

| A.2  | 16 Data-bit SEC-DED-TAEC-yAED Codes                                                                                                                                                                                                                                                                                                                                                                                              | 148  |

| A.3  | 32 Data-bit SEC-DED-DAEC-yAED Codes                                                                                                                                                                                                                                                                                                                                                                                              | 149  |

| A.4  | 32 Data-bit SEC-DED-TAEC-yAED Codes                                                                                                                                                                                                                                                                                                                                                                                              | 150  |

| A.5  | 64 Data-bit SEC-DED-DAEC-yAED Codes                                                                                                                                                                                                                                                                                                                                                                                              | 151  |

| A.6  | 64 Data-bit SEC-DED-TAEC-yAED Codes                                                                                                                                                                                                                                                                                                                                                                                              | 152  |

| A.7  | 32 Data-bit SEC-DED-DAEC-yAED IIMS Codes                                                                                                                                                          | 153 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A.8  | 64 Data-bit SEC-DED-DAEC-yAED IIMS Codes                                                                                                                                                          | 154 |

| A.9  | 16 Data-bit SEC-DED-DAEC-yAED ICB Codes                                                                                                                                                           | 155 |

| A.10 | Optimized (24, 16) I-5 Code with maximum row weight of 8 Check-bits(1-<br>8) = Columns{1 4 13 6 12 8 24 10} $\ldots \ldots \ldots$ | 155 |

| A.11 | Various Length Dutta Codes                                                                                                                                                                        | 156 |

| A.12 | Various Length BCH Codes                                                                                                                                                                          | 157 |

| A.13 | Various Length Reed Solomon Codes                                                                                                                                                                 | 158 |

| B.1  | ICTWTAN3 - 6T SRAM + ECC + I/O + Level Shifter Circuit Level Block<br>Diagram                                                                                                                     | 160 |

| B.2  | ICTWTAN3 - Full Chip Layout                                                                                                                                                                       | 161 |

| B.3  | ICTWTAN3 - Die Photo                                                                                                                                                                              | 161 |

| B.4  | ICTWTAN3 - Die Pad Frame Connectivity                                                                                                                                                             | 162 |

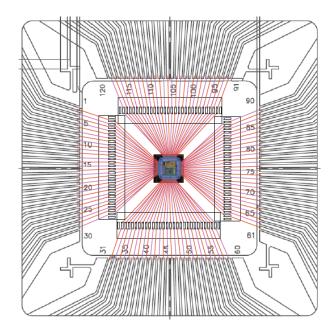

| B.5  | ICTWTAN3 - Bonding Diagram - Two tiered bonding using two short wires<br>and conductive interposers, die in center of package cavity. Bonding by<br>Corwil Technology Corportation [79]           | 163 |

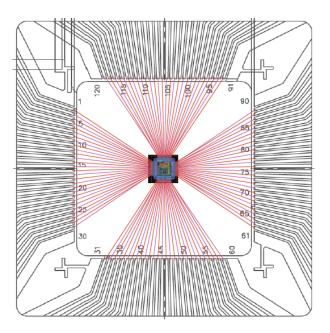

| B.6  | ICTWTAN3 - Bonding Diagram - Two tiered bonding using single long wire, die in center of package cavity. Bonding by Quik-Pak [78]                                                                 | 163 |

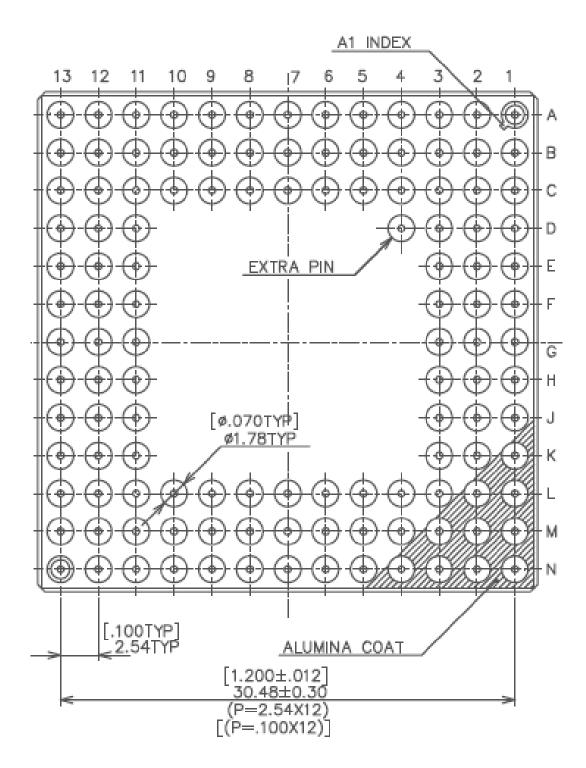

| B.7  | ICTWTAN3 - 120 Pin Grid Array (PGA) Package Pin Configuration                                                                                                                                     | 164 |

| B.8  | ICTWTAN3 - Pin Map                                                                                                                                                                                | 165 |

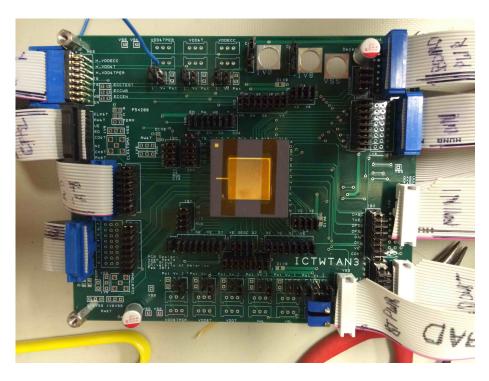

| B.9  | ICTWTAN3 - Testboard for Device Under Test                                                                                                                                                        | 166 |

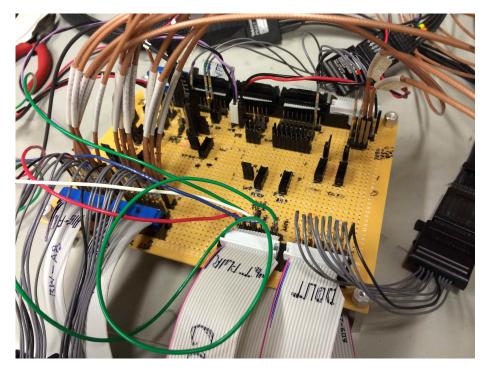

| B.10 | ICTWTAN3 - External Controller Card for Device Under Test                                                                                                                                         | 166 |

# List of Abbreviations

GF(2) Binary Galois Field

- $Q_{col}$  Collected Charge

- $Q_{crit}$  Critical Charge

- $\mathbf{I}_r \ r \times r$  Identity Matrix

- $a_n$  Neutron Fluence Acceleration Factor

- $a_t$  Irradiation Time Acceleration Factor

- $d_{min}$  Minimum Hamming Distance

- **G-matrix** ECC Generator Matrix

- **H-matrix** ECC Parity Check Matrix

$\mathbf{6T}$  6 Transistors

- BCH Bose Chaudhuri Hocquenghem

- **BL/BLB** SRAM Complementary Bitline and Bitline Bar Pair

- CMOS Complementary Metal Oxide Semiconductor

- **DAEC** Double Adjacent Error Correction

- **DEC** Double Error Correcting

- **DEC-TED** Double Error Correcting Triple Error Detecting

- **DED** Double Error Detecting

- **DICE** Dual Interlocking Cell Element

**DRAM** Dynamic Random Access Memory

**DVFS** Dynamic Voltage and Frequency Scaling

ECC Error Correcting Code, or Error Correction Code

EG-LDPC Euclidean Geometry Low Density Parity Check

**FF** Fast n-type Transistor Devices, Fast p-type Transistor Devices

**FIT** Failures in Time, 1 FIT = one failure in  $10^9$  device-hours

${\bf HDL}\,$  Hardware Description Language

**HK+MG** High  $\kappa$  Dielectric plus Metal Gate

ICB Increased Check-Bit codes

**IIMS** Increased Identity Matrix Size codes

**JEDEC** Joint Electron Device Engineering Council

LET Linear Energy Transfer

MBU Multi-Bit Upset

MCU Multi-Cell Upset

**NIF** Neutron Irradiation Facility

PCB Printed Circuit Board

PGA Pin Grid Array

**RAM** Random Access Memory

$\mathbf{RS}$  Reed-Solomon

SbEC-DbED Single Byte Error Correcting Double Byte Error Detecting

${\bf SBU}$  Single Bit Upset

**SEC** Single Error Correcting

- **SEC-DED** Single Error Correcting Double Error Detecting

- **SEC-DED**-*x***AEC**-*y***AED** Single Error Correcting Double Error Detecting x-bits Adjacent Error Correcting y-bits Adjacent Error Detecting

- **SEC-DED-DAEC** Single Error Correcting Double Error Detecting Double Adjacent Error Correcting

- **SET** Single Event Transient

- **SEU** Single Event Upset

- **SOI** Silicon on Insulator

- **SPICE** Simulation Program with Integrated Circuit Emphasis

- **SRAM** Static Random Access Memory

- SS Slow n-type Transistor Devices, Slow p-type Transistor Devices

- TAEC Triple Adjacent Error Correction

- **TRIUMF** Tri-University Meson Facility

- **TT** Typical n-type Transistor Devices, Typical p-type Transistor Devices

- **UE** Uncorrectable Error

- $\mathbf{VDD}_{MIN}$  Minimum Operating Supply Voltage

- **VLSI** Very Large Scale Integration

- ${\bf WL}\,$  SRAM Wordline

- **xAEC** A variable degree of Adjacent Error Correction

- **yAED** A variable degree of Adjacent Error Detection

- **zBED** A variable degree of Burst Error Detection

## Chapter 1

## Introduction

This chapter provides an introduction to the soft error problem in nanoscale integrated circuits with an emphasis on SRAMs. The sources of soft errors and their underlying mechanisms are first described, and the increasing SRAM soft error rate in light of technology scaling is used as the main motivating factor driving this research.

### **1.1 Problem Statement**

Driven by consumer demand for increased functionality and reduced power consumption, transistor device dimensions and chip operating voltages for the complementary metal oxide semiconductor (CMOS) technology used in computer electronics continues to scale. The increased demand for chip functionality has caused a proliferation in memory intensive applications. New applications requiring large capacity memory modules can occupy a considerable portion of a chip's total area. To fulfill the demand for increasing on-chip storage capacity, while mitigating against chip real estate penalties, embedded memories are being designed using state-of-the-art technologies with minimum features sizes currently on the order of 14-16 nm [1, 2, 3]. These gains however do not come without an associated cost. Technology scaling, coupled with reduced operating voltage, can lead to an increase in a memory cell's sensitivity to external radiation effects [4]. This issue is particularly noticeable in static random access memory (SRAM), and Flash-based memories [5]. As devices scale deep into the sub-45 nm regime, radiation induced soft errors become a serious reliability challenge facing embedded memories [6].

Soft errors arise as a result of energetic neutrons from galactic particles and from alpha particles emitted by chip packaging material [7]. Originally termed "antenna pickup", seemingly random upsets in digital electronics were reported as early as the 1940's, but it was not until the 1970's that radiation was considered to be a potential source of these

upsets [7]. In 1978, Intel reported that radioactive uranium contamination was causing "soft fails" in some of their dynamic random access memory (DRAM) and microprocessor chips [8], then in 1979, Ziegler and Lanford predicted that cosmic rays could cause a major electronic reliability problem at both terrestrial sites and aircraft altitudes [9]. The high energy particles create free electron-hole pairs as they pass through semiconductor devices which can lead to large current/voltage transients if they come within close proximity of a transistor's depletion region. These single event transients (SET) appear at circuit nodes and can unintentionally corrupt data stored in memory cells and other storage elements. When a SET leads to the data corruption of one of these storage elements it is defined as a single event upset (SEU). An SEU corrupting a single-bit of data is classified as a single bit upset (MCU). A MCU that corrupts multiple bits within the same logical memory word is defined as a multi-bit upset (MBU). Since each of these upsets corrupt the data state but do not necessarily permanently damage the device itself, they are referred to as soft errors.

Until recently, large node capacitances and high noise margins in storage devices have prevented soft errors at ground level from becoming a major concern. As a byproduct of aggressive technology scaling and increased bitcell packing density however, the nature of soft errors is changing, and designers are being forced to deal with these issues during earlier stages of the design cycle. Although many solutions have been developed for high reliability in extreme environments such as military and aerospace applications, they are not necessarily being adopted for commercial applications at ground level due to the significant area, performance, and power consumption penalties they incur where these metrics are at a higher premium. Additionally, as bit-cell packing densities increase, many adjacent cells are now being corrupted by a single SEU as the external radiation source remains constant. SEUs that would have once caused only a single SBU are now causing MBU and MCUs. This leads to the failure of traditional error mitigation strategies, and severely limits the prospect of continued device scaling [10].

### **1.2** Soft Error Mechanisms

When an energetic cosmic neutron enters a silicon substrate, it can either pass directly through the substrate, or cause a disturbance by striking an atom, thereby generating an ion [11]. Alpha particles are already ionized and therefore can cause a disturbance directly on contact with the substrate. The magnitude of these disturbances depends on the linear energy transfer (LET) of the ion or particle, and is measured in megaelectron volt square centimeter per milligram (MeV-cm<sup>2</sup>/mg). The LET is dependent on the mass and energy of the particle, and the material through which it is traveling. The reverse-biased p-n junctions are the most charge-sensitive areas of a circuit [4]. This is due to the

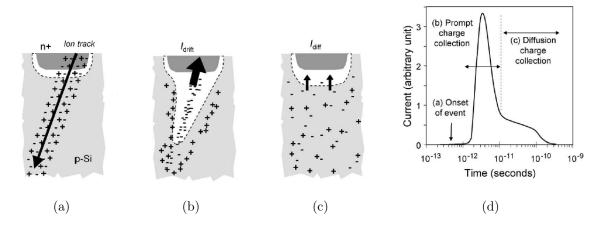

Figure 1.1: Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion [4].

high electric field within their depletion region allowing for efficient charge collection [7]. Charge collection generally occurs within a few microns of the junction, and the collected charge  $(Q_{col})$  for these events range from 1 to several 100 fC depending on the type of ion, its trajectory, and energy over the path through or near the junction.

At the onset of an ionizing radiation event, as shown in Figure 1.1(a), a cylindrical track of electron-hole pairs is created in the wake of the incident ion's path. When one of these ion tracks is in the vicinity of a reverse biased junction, carriers are quickly collected by the junction's electric field creating a large current/voltage transient at the particular circuit node Figure 1.1(b). This high intensity charge collection process happens briefly over the period of no more than a nanosecond, and is then followed by more a subdued phase of diffusion dominated charge collection lasting over several hundred nanoseconds Figure 1.1(c). This phase continues until all of the excess carriers have been collected, recombined, or diffused away from the junction area. The resulting current transient associated with this phenomena is shown in Figure 1.1(d).

The amount of charge collected at a junction is inversely proportional to the distance from which the radiation event occurs. The farther away the strike is from the junction, the lower the probability that the event will cause an upset. The overall charge collection process is further complicated however, as circuit nodes do not exist in isolation, but rather as part of a more complex circuit structure with many nodes in close proximity to one another. The magnitude of  $Q_{col}$  depends on a complex combination of factors including the size of the device, biasing of the surrounding circuit nodes, substrate structure, device doping, the type of ion, its energy, its trajectory, the initial position of the event within the device, and the data-state of the device itself. For an upset to occur, the  $Q_{col}$  must exceed a certain critical value. This minimum critical charge threshold  $(Q_{crit})$  is defined as the minimum amount of charge necessary to trigger a change in the data state of the storage device. A SET will only cause an upset in the event that  $Q_{col} > Q_{crit}$ , otherwise the storage element will be able to return to its original state, and no upset will occur. The  $Q_{crit}$  has several dependencies of its own including, node capacitance, operating voltage, and strength of any feedback components, and is used as a figure of merit to assess the soft error susceptibility of a particular storage element.

The soft error rate (SER) is used to measure the frequency of occurrence of soft errors. It is measured in terms of failures in time (FIT), where one FIT is the equivalent to one failure in  $10^9$  device-hours. SER is typically normalized either per-bit to describe the cell-level soft error susceptibility or per-device as a measure of the system-level susceptibility. To put the SER into perspective, the aggregate failure rate for traditional "hard" failure mechanisms (such as gate oxide breakdown, metal electronmigration, latch-up, etc...) in advanced technologies is typically in the range of 50-200 FIT/device. Whereas the unabated SER for memories can easily exceed 50 000 FIT/device [4]. As an example, if we consider a 16 MB SRAM (as in the Intel Xeon L3 cache [12]) and assume a bit-level SER of 100-1000 FIT/Mb [5], this provides between 19 200-192 000 FIT/device.

While  $Q_{crit}$  remains essentially unchanged for scaled DRAMs, the critical charge in SRAM and Flash memories scale with the technology, and as memory bit-cell densities increase, system-level soft error rates continue to grow [4, 5]. Due to the different data storage mechanisms and shear contrast in capacity between Flash and SRAM memories, mitigation design approaches exploiting these differences can lead to more targeted, memory-type-specific solutions. Since on-chip embedded SRAM constitutes more that 50% of the die area for state-of-the-art microprocessors and systems-on-chip (with this value expected to increase in the future), this work is in the context of SRAM soft error mitigation. Although many of the concepts could be transferred to other memory types, SRAM scaling limitations are at the forefront computer memory research, and are of immediate concern.

### **1.3 Soft Errors in SRAM**

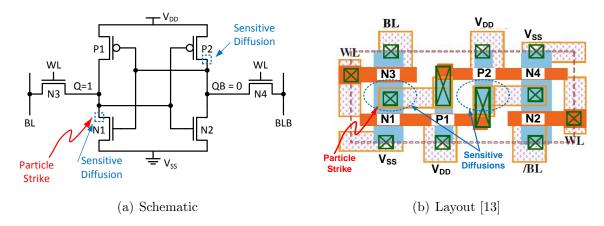

The conventional six-transistor (6T) SRAM bit-cell, shown in Figure 1.2, stores one bit of data and its complement in a cross coupled inverter pair. Since the inverters continuously drive one another, the cell is able to retain its data provided the power supply remains on. For the sake of explanation, we can assume the cell is holding the data '1' and '0' at the nodes Q and QB respectively. Under these conditions, transistors N1 and P2 are off, and the drain diffusion junctions of these devices are reverse biased and sensitive to upset. When an energetic particle strikes one of these sensitive cell diffusions, the charge

Figure 1.2: 6-Transistor SRAM Cell. Assuming the cell is holding the data (Q = 1, QB = 0), the drain diffusions for devices N1 and P2 are sensitive to particle induced upsets.

collected at the junction results in a transient current through the struck transistor [14]. As this current flows through the device, the restoring transistor (P1 for N1 and N2 for P2) sources current in an attempt to balance the particle-induced SET. As current flows through the restoring transistor, a voltage transient occurs at the struck drain's storage node. If this transient voltage exceeds the switching threshold of the inverter that is being driven by the node, then the inverter can switch, causing the forward feedback action of the inverter pair to unintentionally latch the transient data. Assuming the cell data is reversed (i.e., Q = 0, and QB = 1), then the upset sensitive diffusions are the drains of transistors N2 and P1 respectively.

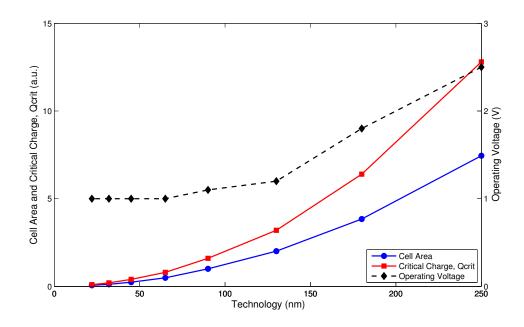

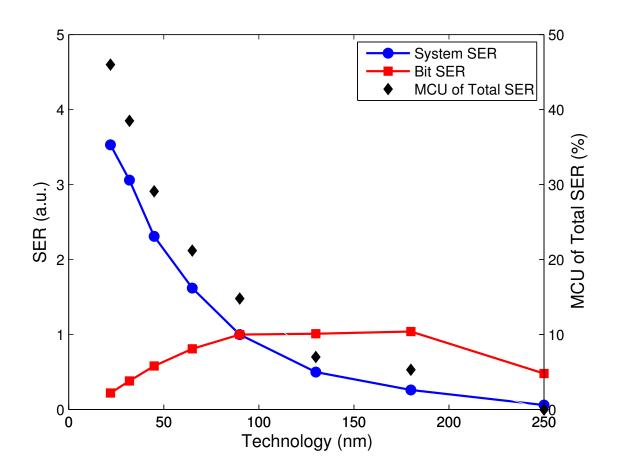

Bit-cell area, critical charge, and operating voltage are shown as a function of technology node in Figure 1.3. Transistor device scaling allows for a roughly two-fold reduction in SRAM bit-cell area per technology generation [15]. These shrinking device dimensions lead to a reduction in the  $Q_{crit}$  necessary to corrupt a bit-cell. Coupled with reductions in SRAM operating voltage, technology scaling should lead to an increase in the bit-level SER; however, the reduction in device depletion region cross sectional area leads to a decrease in cell charge collection efficiency. For the 180 nm and 130 nm nodes these effects essentially cancel one another out and lead to a saturation in the bit-level SER shown in Figure 1.4. As the supply voltage saturates below 100 nm technologies however, the bit-level SER begins to decrease. Despite this decrease, the system-level SER increases with technology generation. This is shown by the seven-fold increase in system-level SER between the 130 nm and 22 nm nodes brought on by the increase in memory system capacity per unit area made possible by the smaller cell size.

The reduction is SRAM bitcell cross sectional area also reduces the distance between adjacent bitcells. This, coupled with a lower  $Q_{crit}$ , allows for not only lower energy particles

Figure 1.3: SRAM parameters - normalized cell area, normalized  $Q_{crit}$ , and operating voltage as a function of technology node [4], [10].

to cause SEUs but for more cells to be upset per particle strike [17]. Also shown in Figure 1.4 is the MCU percentage of the total (system) SER as a function of technology generation from the 250 nm to 22 nm node [6]. From the figure, we can see that MCUs comprise over 30% of the SER below the 45 nm node.

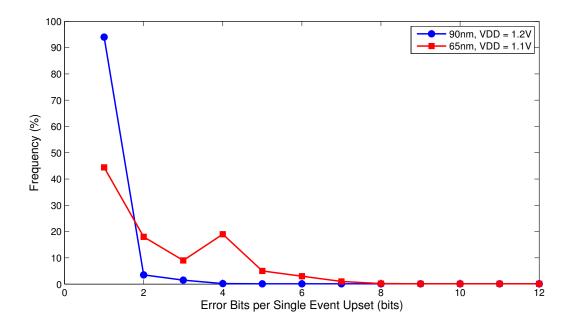

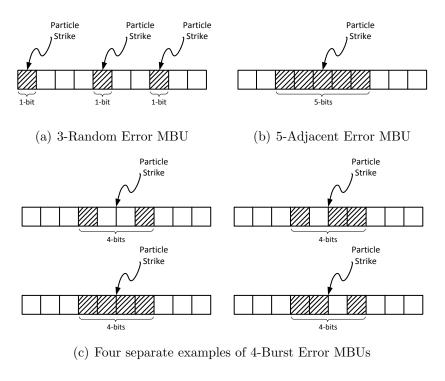

Although the MCU percentage of the total SER is increasing, not all MCUs are of the same size and shape. If an MCU occurs down a single bitline column, each of the cells will reside in a separate memory word and can be recovered individually. It is the upsets that corrupt multiple bits within the same memory word (i.e., MBUs) that require a higher degree of circuit complexity to correct. A distribution of the percentage of different width upsets for 45 nm, 32 nm, and 22 nm technologies is shown in Table 1.1 [6]. From the table it is clear that the number and size of these upsets increase with scaling. Further, Figure 1.5 shows a measured same-word MBU distribution for a 65 nm and 90 nm SRAM [16]. The figure shows that the frequency of larger sized MBUs decays exponentially with the number of bits upset per SEU. This means that although, the proportion of MBUs is on the rise, the majority of MBUs will still be comprised of only a small number of bits.

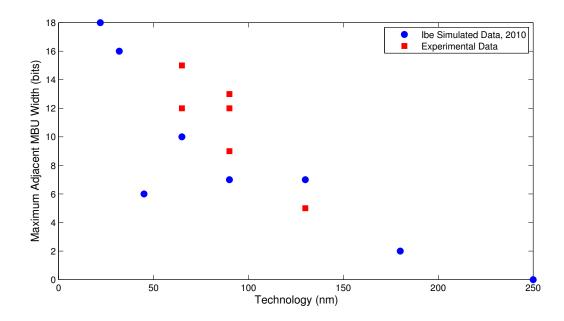

Despite the rarity of larger MBUs, there is still a non-zero probability of their occurrence. In Figure 1.6 the maximum adjacent upset size per particle strike is shown as a function of technology scaling. The data presented with squares has been collected from a

Figure 1.4: System-SER, bit-SER and percentage MCU of the total SER as a function of technology node [6].

| Table 1.1: MCU b | oit width and | percentage | of the | total | SER | for 4 | 5  nm, | $32~\mathrm{nm},$ | and 2 | 22 nm |

|------------------|---------------|------------|--------|-------|-----|-------|--------|-------------------|-------|-------|

| technologies [6] |               |            |        |       |     |       |        |                   |       |       |

| Technology | % of Total | Bit width |     |     |       |            | Bit width |  |  |  |

|------------|------------|-----------|-----|-----|-------|------------|-----------|--|--|--|

| (nm)       | SER        | 2         | 3   | 4-8 | >8    | Max (bits) |           |  |  |  |

| 45         | 2.2        | 1.9       | 0.2 | 0.1 | < 0.1 | 6          |           |  |  |  |

| 32         | 3.1        | 2.6       | 0.2 | 0.3 | < 0.1 | 16         |           |  |  |  |

| 22         | 3.6        | 3.0       | 0.2 | 0.3 | 0.1   | 18         |           |  |  |  |

Figure 1.5: Frequency distribution of the number of soft errors generated per SEU due to neutron irradiation of 65 nm and 90 nm SRAMs [16].

Figure 1.6: Maximum adjacent MBU width as a function of technology. Derived from [18, 19, 16, 20, 6].

series of radiation experimental results ranging from 130 nm to 65 nm, and shows between 12-15 adjacent-bit upsets at the 65 nm node [18, 19, 16, 20]. The data presented with circles uses a predictive model ranging from 250 nm to 22 nm and predicts 10 adjacent-bit upsets at the 65 nm node, and 18 adjacent-bit upsets at the 22 nm. The actual number of adjacent bit upsets depends heavily on the design and layout of the SRAM bitcell, but this data provides an indication of what to expect for a given technology. Finally, it also provides an indication that for scaling to continue, SRAM SEU mitigation strategies must move beyond their current SBU focus, and increase their robustness to adjacent MBUs.

### **1.4 SRAM Soft Error Mitigation Strategies**

Recent developments in raw material purification during the semiconductor fabrication process has lead to a significant reduction in alpha particle induced upsets caused by packaging material [21]. Reducing cosmic neutron induced upsets unfortunately proves to be a greater challenge. Concrete has been shown to reduce the cosmic radiation flux at a rate of approximately 1.4x per foot of concrete thickness [4]. Thus, by operating a system in a basement surrounded by many feet of concrete, the SER due to cosmic neutrons can be reduced. While this may be a viable option for mainframes, it is not very practical for personal computers or other portable electronic devices. Therefore, rather than reducing cosmic radiation flux, cosmic neutron induced soft errors require onchip mitigation strategies to minimize the SER. The soft error mitigation strategies for SRAMs can be classified into three separate categories, including: process-, circuit-, and architectural-level techniques.

#### 1.4.1 Process

The primary method for soft error mitigation at the process level is to reduce the amount of charge collection at sensitive nodes. This can be achieved by increasing the doping of the p-well [22], using triple [23] or quadruple-well [24] structures, or utilizing a silicon-oninsulator (SOI) substrate. SRAM SERs have been reported with a 5x reduction relative to bulk CMOS when fabricated in a partially-depleted SOI technology [25]. Although processlevel techniques significantly improve the soft error performance of SRAMs, the techniques do require modification of the standard CMOS fabrication process. Therefore these techniques are not readily available to companies that do not have control over the fabrication process, such as fab-less design groups. Additionally, process mitigation techniques require additional processing costs, which may further detract from their practicality.

### 1.4.2 Circuit