# Adaptive Power Amplifiers for Modern Communication Systems with Diverse Operating Conditions

by

Ahmed Mahmoud Mohamed

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2013

©Ahmed Mahmoud Mohamed 2013

### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### Abstract

In this thesis, novel designs for adaptive power amplifiers, capable of maintaining excellent performance at dissimilar signal parameters, are presented. These designs result in electronically reconfigurable, single-ended and Doherty power amplifiers (DPA) that efficiently sustain functionality at different driving signal levels, highly varying time domain characteristics and wide-spread frequency bands. The foregoing three contexts represent those dictated by the diverse standards of modern communication systems.

Firstly, two prototypes for a harmonically-tuned reconfigurable matching network using discrete radio frequency (RF) microelectromechanical systems (MEMS) switches and semiconductor varactors will be introduced. Following that is an explanation of how the varactor-based matching network was used to develop a high performance reconfigurable Class  $F^{-1}$  power amplifier.

Afterwards, a systematic design procedure for realizing an electronically reconfigurable DPA capable of operating at arbitrary centre frequencies, average power levels and back-off efficiency enhancement power ranges is presented. Complete sets of closed-form equations are outlined which were used to build tunable matching networks that compensate for the deviation of the Doherty distributed elements under the desired deployment scenarios. Off-the-shelf RF MEMS switches are used to realize the reconfigurability of the adaptive Doherty amplifiers.

Finally, based on the derived closed-form equations, a tri-band, monolithically integrated DPA was realized using the Canadian Photonics Fabrication Centre (CPFC<sup>®</sup>) GaN500 monolithic microwave integrated circuit (MMIC) process. Successful integration of high power, high performance RF MEMS switches within the MMIC process paved the way for the realization of the frequency-agile, integrated version of the adaptive Doherty amplifier.

### **Acknowledgements**

I would like to recognize all my colleagues in the EmRG and CIRFE research groups who have been constantly providing me with help and support during my research. A special acknowledgement should be remembering our great CIRFE lab manager; Bill Jolley for all his valuable efforts during every stage in my work. Last but not least, I would like to express my deep gratitude to my supervisors who gave me the support and the strength to face challenges in research; Prof. Slim Boumaiza, and Prof. Raafat Mansour.

### Dedication

I would like to dedicate this dissertation to my parents, my lovely wife and my awesome sister who are always supportive to me and believe in me in reaching my dreams. Also, my work is dedicated to all my friends who present the model of true friendship and are always helpful to me.

# **Table of Contents**

| AUTHOR'S DECLARATION ii                                                                         |

|-------------------------------------------------------------------------------------------------|

| Abstractiii                                                                                     |

| Acknowledgementsiv                                                                              |

| Dedicationv                                                                                     |

| Table of Contents                                                                               |

| List of Figures                                                                                 |

| List of Tables                                                                                  |

| Chapter 1 Motivation and Introduction 1                                                         |

| 1.1 Introduction1                                                                               |

| 1.2 Power Amplifiers in Modern Communication Systems 1                                          |

| 1.3 High Efficiency Multi-mode Multi-frequency Power Amplifiers                                 |

| 1.4 Thesis Objectives                                                                           |

| 1.5 Thesis Outline                                                                              |

| Chapter 2 Overview of Power Amplifier Efficiency Enhancement Techniques for Modern Radio        |

| Systems                                                                                         |

| 2.1 Power Amplifier Classes of Operation                                                        |

| 2.2 Power Amplifier Efficiency Enhancement                                                      |

| 2.2.1 Single-Ended High Efficiency Multi-frequency Power Amplifiers                             |

| 2.2.2 Envelope Tracking                                                                         |

| 2.2.3 The Doherty Power Amplifier                                                               |

| 2.3 Transistor Technology                                                                       |

| 2.4 Discussion                                                                                  |

| Chapter 3 Electronically Tunable Inverse Class F Power Amplifier for Multi-Frequency Multi-Mode |

| Base Stations                                                                                   |

| 3.1 Introduction                                                                                |

| 3.2 Harmonically-Tuned Reconfigurable Class F <sup>-1</sup> Power Amplifier                     |

| 3.2.1 Theory and Design of Tunable Matching Network                                             |

| 3.2.2 Fabrication and Measurement Results                                                       |

| 3.2.3 Load Modulated Varactor-Based Frequency Agile Class F <sup>-1</sup> HEPA                  |

| Chapter 4 Reconfigurable Doherty Power Amplifiers for Multi-Band Multi-Mode Base Stations 36    |

| 4.1 Introduction                                                                                |

| 4.2 Novel Reconfigurable Multi-Standard Multi-Frequency Reconfigurable Doherty Power     |    |

|------------------------------------------------------------------------------------------|----|

| Amplifier                                                                                |    |

| 4.2.1 Multi-Standard Multi-Frequency Doherty Power Amplifier Synthesis                   |    |

| 4.2.2 Multi-Frequency Single Standard Doherty Power Amplifier Prototype                  | 42 |

| 4.2.3 Multi-Standard Single Frequency Doherty Power Amplifier Prototype                  | 47 |

| 4.2.4 Multi-Standard Multi-Frequency Doherty PA Prototype                                | 50 |

| 4.3 Conclusion                                                                           | 55 |

| Chapter 5 Reconfigurable Doherty Power Amplifiers with Enhanced Efficiency at Extended   |    |

| Operating Average Power Levels                                                           | 57 |

| 5.1 Introduction                                                                         | 57 |

| 5.2 Conventional Doherty Power Amplifier Efficiency vs. Average Power                    | 57 |

| 5.3 Design of Doherty Amplifier with Enhanced Efficiency at Variable Average Power       | 61 |

| 5.3.1 Low Power Compensation                                                             | 62 |

| 5.3.2 High Power Compensation                                                            | 64 |

| 5.4 Experimental Validation                                                              | 68 |

| 5.5 Conclusion                                                                           | 74 |

| Chapter 6 Frequency Agile Monolithic Integrated Reconfigurable GaN Doherty Power Amplifi | er |

| using MEMS on GaN Integration                                                            | 75 |

| 6.1 Introduction                                                                         | 75 |

| 6.2 CPFC <sup>®</sup> GaN500 MMIC HFET Process                                           | 75 |

| 6.3 High Power GaN Monolithically Integrated RF MEMS Switches                            | 78 |

| 6.4 Multi-band Monolithically integrated GaN Reconfigurable Doherty PA                   | 85 |

| 6.4.1 DPA MMIC Module Design                                                             | 85 |

| 6.4.2 DPA MMIC Measurement Results                                                       |    |

| Conclusion                                                                               | 91 |

| Bibliography                                                                             | 94 |

# List of Figures

| Figure 1-1, Modern Radio Systems Block Diagram                                                    | . 2 |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 1-2, Block Diagram for a High Performance Power Amplifier                                  | . 3 |

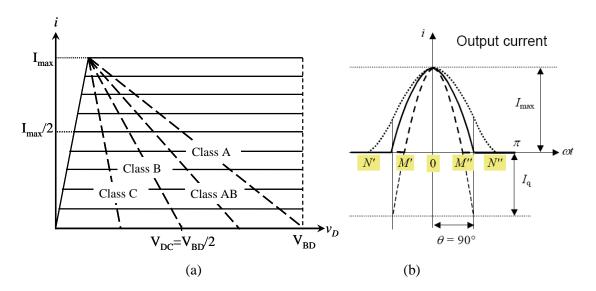

| Figure 2-1, Trade-off between Linearity and Efficiency of Power Amplifiers                        | . 6 |

| Figure 2-2, Different Classes of Operation for Power Amplifiers                                   | . 7 |

| Figure 2-3, (a) Load/line Characteristics for Different Classes, (b) Output Current Waveforms for |     |

| Class AB (dotted), Class B (solid), and Class C (dashed) [2]                                      | . 8 |

| Figure 2-4, Schematic diagram for a Reconfigurable Power Amplifier                                | . 9 |

| Figure 2-5, Schematic and Efficiency Enhancement Results for a Power Amplifier [4]                | 10  |

| Figure 2-6, Circuit Demonstrator and Resulting Efficiency Enhancement Values [5]                  | 10  |

| Figure 2-7, (a) Dual-band Dual Operating Frequency Matching Network Design, (b) Fabricated        |     |

| Power Amplifier, (c) Drain Efficiency Results for the Broadband Power Amplifier [12]              | 12  |

| Figure 2-8, (a) Peak Output Power and Efficiency Contours of the Power Amplifier, (b) Circuit     |     |

| Demonstrator, (c) Measurement Results for the Broadband Class F Power Amplifier [13]              | 13  |

| Figure 2-9, Envelope Tracking Architecture Block Diagram [2]                                      | 13  |

| Figure 2-10, Broadband Saturated Amplifier (a) Demonstrator and (b) Continuous Wave               |     |

| Measurements; ET System (c) Circuit Schematic and (d) Continuous Wave Measurements [27]           | 14  |

| Figure 2-11, Conventional Doherty Amplifier Block Diagram                                         | 16  |

| Figure 2-12, Ideal Profiles for (a) Main Amplifier Output Impedance and (b) Auxiliary Transistor  |     |

| Drain Current at Variable Peak to Average Power Ratio Values                                      | 17  |

| Figure 2-13, Ideal Drain Efficiency Profiles at Different Peak to Average Power Ratio Values      | 18  |

| Figure 2-14, Main Transistor Output Impedance vs. Frequency for Different Doherty Power           |     |

| Amplifier Configurations at Variable Peak to Average Power Ratio Values                           | 20  |

| Figure 2-15, Main Transistor Drain Efficiency Deterioration vs. Frequency for Different Doherty   |     |

| Power Amplifier Configurations at Variable Peak to Average Power Ratio Values                     | 21  |

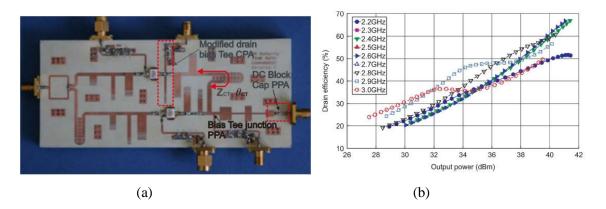

| Figure 2-16, (a) Circuit Photograph and (b) Measured Drain Efficiency Results for the Broadband   |     |

| Doherty Power Amplifier [34]                                                                      | 21  |

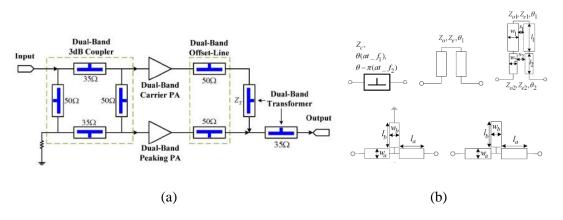

| Figure 2-17, (a) Dual-band Doherty Power Amplifier Schematic and (b) Equivalent Circuit for the   |     |

| Dual-band Distributed Element [35]                                                                | 22  |

| Figure 2-18, (a) 6-dB PAPR Efficiency Enhancement at Different Frequency Bands and (b) Multi-     |     |

| PAPR Efficiency Enhancement Results at 2 GHz [41]                                                 | 23  |

| Figure 2-19, (a) Optimal Auxiliary Drain Current and Main Drain Bias Values for Different PAPR                          |

|-------------------------------------------------------------------------------------------------------------------------|

| Values, (b) Circuit Schematic and Demonstrator, and (c) Efficiency Enhancement Measurement                              |

| Results [42]                                                                                                            |

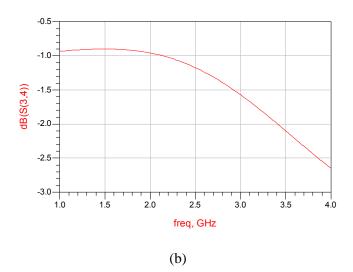

| Figure 2-20, CPFC <sup>®</sup> GaN MMIC Fabricated Class J PA (a) Photo, (b) CW Measured Output Power                   |

| and Efficiency [65]                                                                                                     |

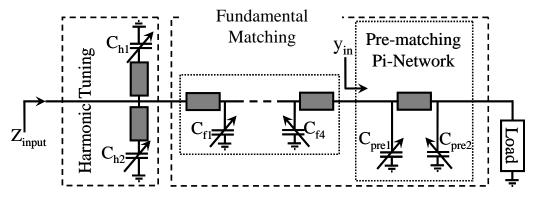

| Figure 3-1, Proposed Design For the Harmonically-Tuned Matching Network                                                 |

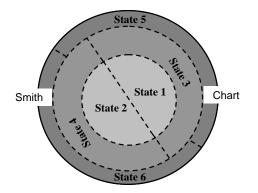

| Figure 3-2, Smith Chart Regions Covered by Each State                                                                   |

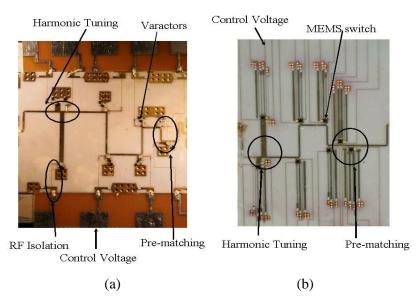

| Figure 3-3, Fabricated (a) Varactor-Based Frequency Agile, (b) MEMS-based 2.5 GHz Matching                              |

| Network                                                                                                                 |

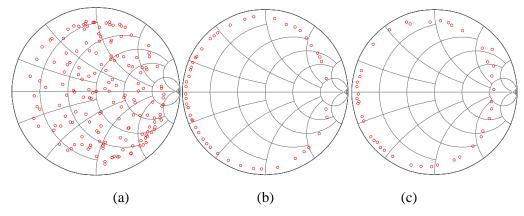

| Figure 3-4, Selected Measured Impedance States to Prove Coverage for 2.5 GHz Design; (a)                                |

| Fundamental 2.5 GHz, (b) Second Harmonic 5 GHz, (c) Third Harmonic 7.5 GHz                                              |

| Figure 3-5, Measured IL =-1.213 dB for 2.5 GHz Design at Maximum $ \Gamma $ of 0.834                                    |

| Figure 3-6, Selected Measured Impedance States to Prove Fundamental Impedance Coverage for                              |

| Frequency Agile Design; (a) 1.8 GHz, (b) 1.9 GHz, (c) 2.1 GHz, (d) 2.4 GHz, and (e) 2.7 GHz 32                          |

| Figure 3-7, Examples for Measured Harmonic Tuning for Frequency Agile Design; (a) 3.8 GHz, (b)                          |

| 4.8 GHz, and (c) 5.4 GHz                                                                                                |

| Figure 3-8, Measured Insertion Loss of (a) -1.121 dB at $ \Gamma $ of 0.862 for 1.8 GHz, (b) -1.313 dB at $ \Gamma $    |

| of 0.868 for 1.9 GHz, (c) -1.38 dB at $ \Gamma $ of 0.853 for 2.1 GHz, and (d) -1.328 dB at $ \Gamma $ of 0.876 for 2.4 |

| GHz                                                                                                                     |

| Figure 3-9, Fabricated Harmonically-Tuned Reconfigurable Power Amplifier                                                |

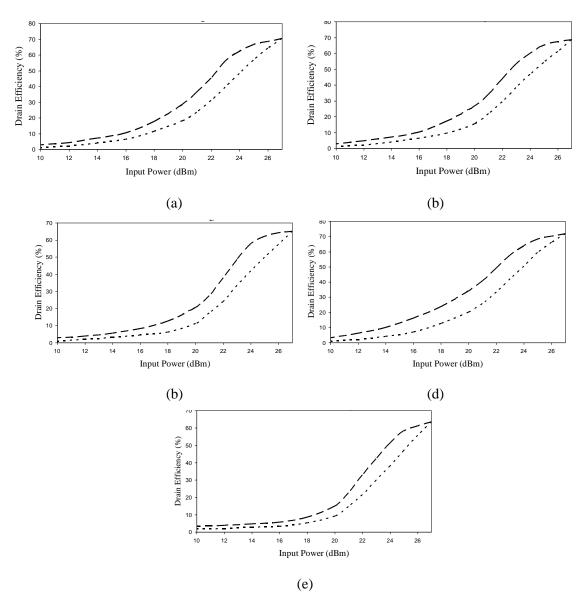

| Figure 3-10, Efficiency vs. Input Power at (a) 1.8 GHz with 12.73% Enhancement at 6 dB Back-off,                        |

| (b) 1.9 GHz with 12.29% Enhancement at 6 dB Back-off, (c) 2.1 GHz with 10.23% Enhancement at 6                          |

| dB Back-off, (d) 2.4 GHz with 14.97% Enhancement at 6 dB Back-off, and (e) 2.7 GHz with 8.3%                            |

| Enhancement at 6 dB Back-off                                                                                            |

| Figure 4-1, Generalized Multi-Standard Multi-Frequency Doherty Block Diagram                                            |

| Figure 4-2, Equivalent Circuits of the Conventional and Proposed Doherty Amplifiers at Low Power                        |

| Levels Compensation                                                                                                     |

| Figure 4-3, Equivalent Circuits of the Conventional and Proposed Doherty Amplifiers at High Power                       |

| Levels Compensation                                                                                                     |

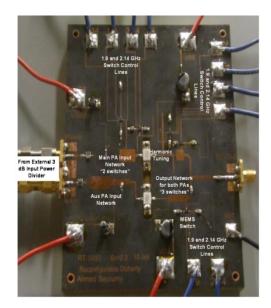

| Figure 4-4, Frequency-Agile Doherty Amplifier Prototype [75]                                                            |

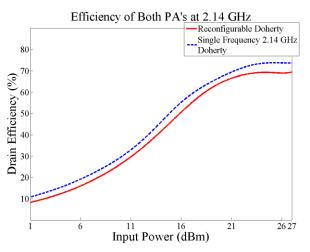

| Figure 4-5, Efficiency of Single Frequency and Frequency-Agile Amplifiers at 2.14 GHz                                   |

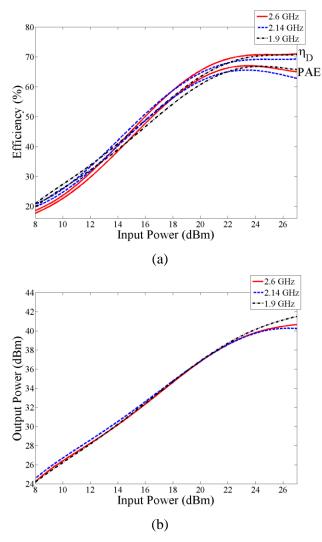

| Figure 4-6, Multi-frequency Doherty PA (a) Efficiencies and (b) Output Power Enhancement Results  |

|---------------------------------------------------------------------------------------------------|

|                                                                                                   |

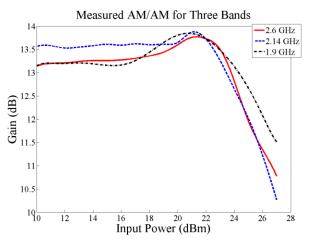

| Figure 4-7, AM/AM Characteristics of the Frequency-Agile Doherty amplifier 45                     |

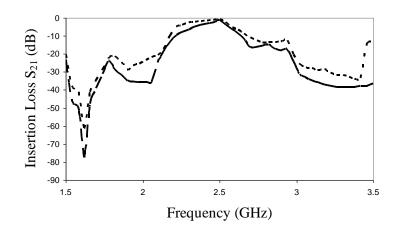

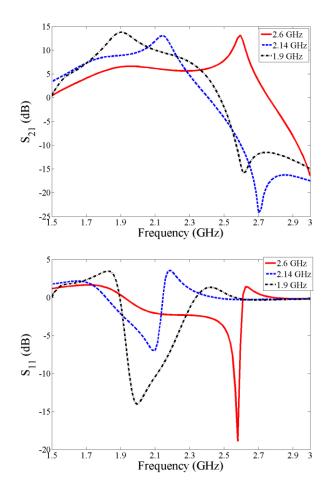

| Figure 4-8, Measured Doherty S-parameters at Different Switching States                           |

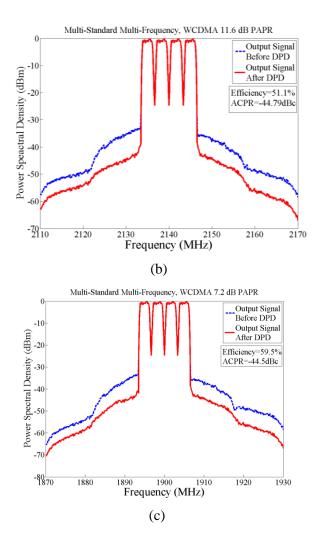

| Figure 4-9, Output Spectrum of the Linearized and Non-linearized Frequency-agile Doherty          |

| Figure 4-10, Reconfigurable DPA Demonstrator for Variable PAPR Signals [77] 48                    |

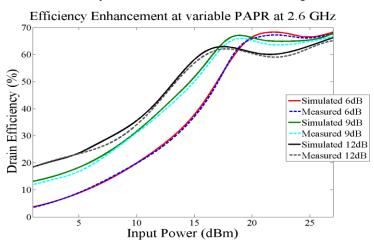

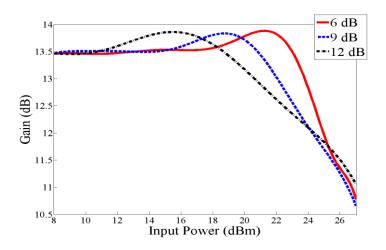

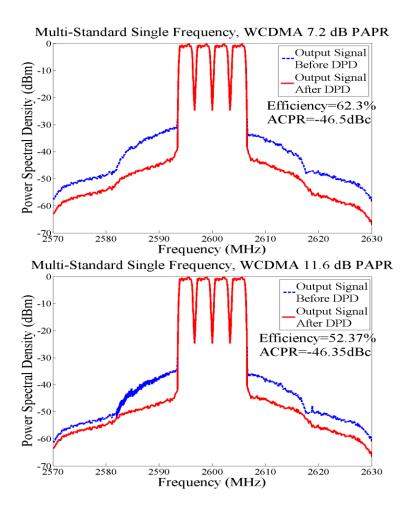

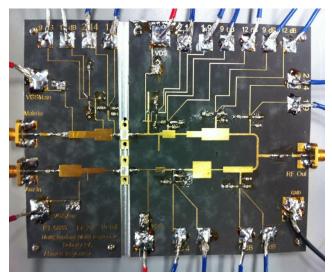

| Figure 4-11, Simulated and Measured Results for the Reconfigurable DPA at 6, 9 and 12 dB Back-off |

| Levels at 2.6 GHz                                                                                 |

| Figure 4-12, AM/AM Characteristics of the Multi-standard DPA 49                                   |

| Figure 4-13, Output Spectrum of the Linearized Multi-standard DPA 49                              |

| Figure 4-14, The Proposed Multi-standard Multi-frequency DPA Prototype [78] 50                    |

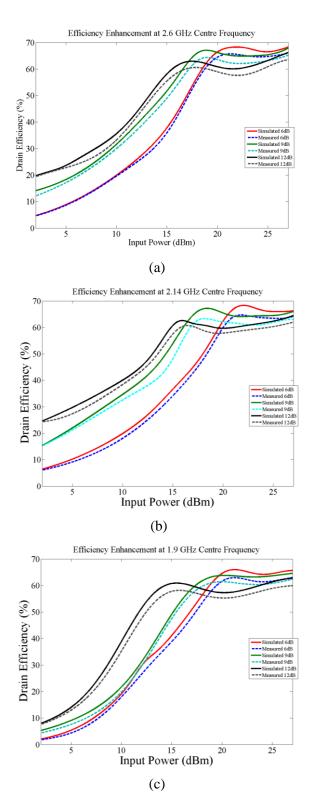

| Figure 4-15, Multi-standard Multi-frequency DPA Efficiency Enhancement Results                    |

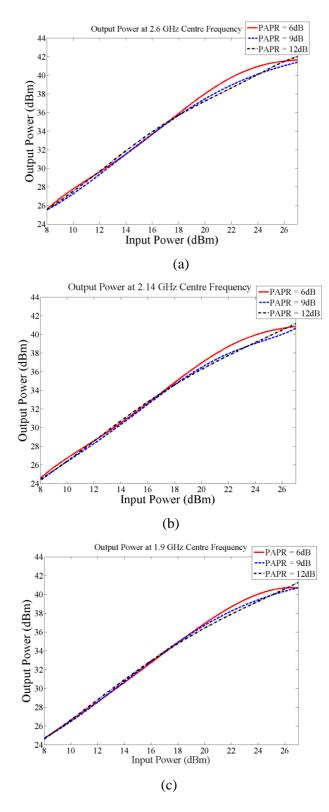

| Figure 4-16, Multi-standard Multi-frequency DPA Measured Output Power                             |

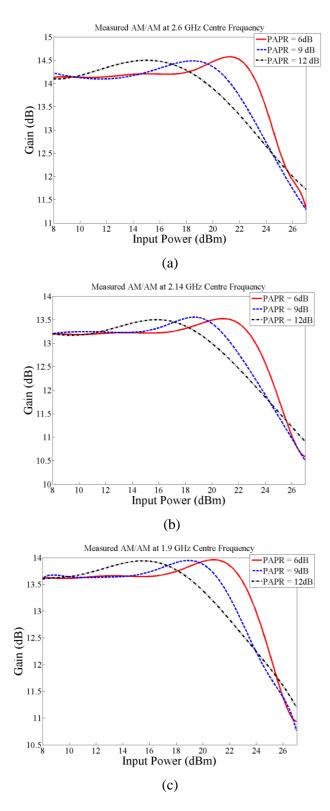

| Figure 4-17, AM/AM Characteristics of the Multi-standard Multi-frequency DPA 53                   |

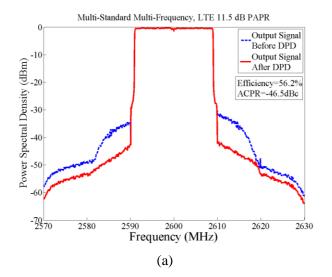

| Figure 4-18, Output Spectrum of the Linearized and Non-linearized Reconfigurable DPA 55           |

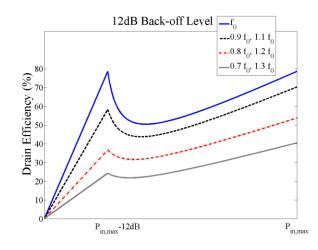

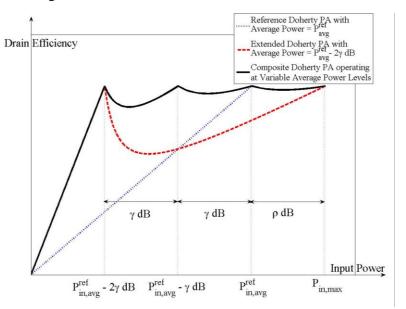

| Figure 5-1, Variable Operating Average Power DPA Efficiency Enhancement 59                        |

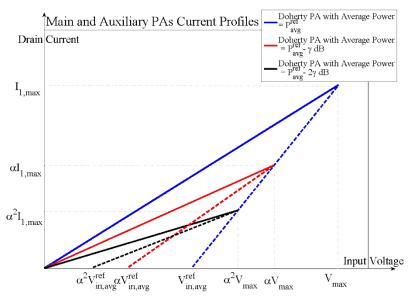

| Figure 5-2, Ideal Main and Auxiliary PAs Current Profiles for Variable Operating Average Power    |

| Levels                                                                                            |

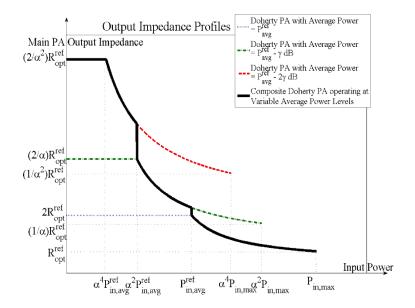

| Figure 5-3, Main Transistor Output Impedance Profiles at Each Average Power Level as well as the  |

| Targeted Profile for Variable Operating Power Levels in a Doherty Amplifier                       |

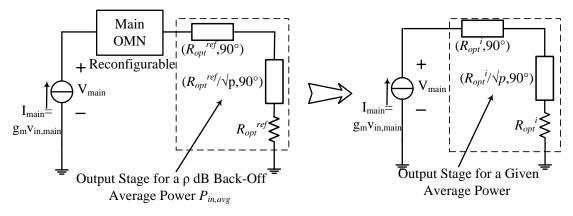

| Figure 5-4, Equivalent Low Power Levels Circuits of the Conventional and the Proposed Doherty,    |

| Capable of Operation at Any Given Average Power Level                                             |

| Figure 5-5, Equivalent High Power Levels Circuits of the Conventional and the Proposed Doherty,   |

| Capable of Operation at Any Given Average Power Level                                             |

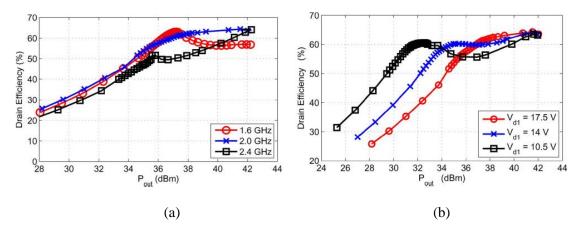

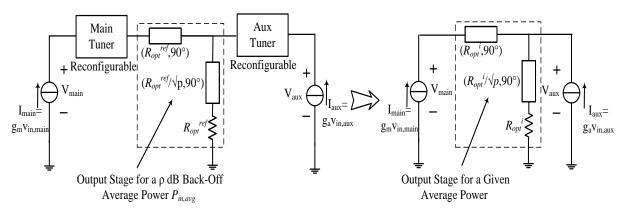

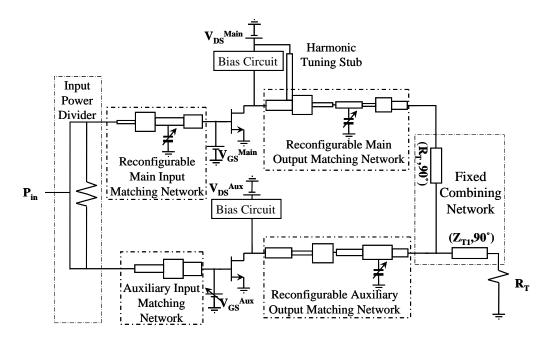

| Figure 5-6, Block Diagram of the DPA with Enhanced Efficiency for Variable Average Input Power    |

| (11, 16 and 21 dBm)                                                                               |

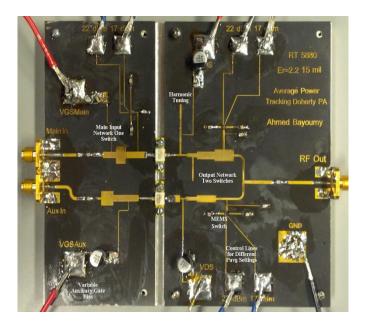

| Figure 5-7, The Proposed Prototype for the Reconfigurable DPA for Three Average Power Settings at |

| 2.6 GHz                                                                                           |

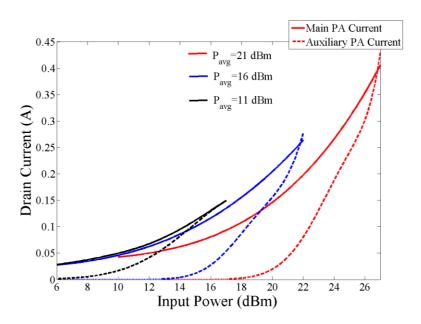

| Figure 5-8, Measured Main and Auxiliary Active Devices' Drain Currents for the Reconfigurable     |

| Doherty Amplifier for Three Average Power Settings at 2.6 GHz                                     |

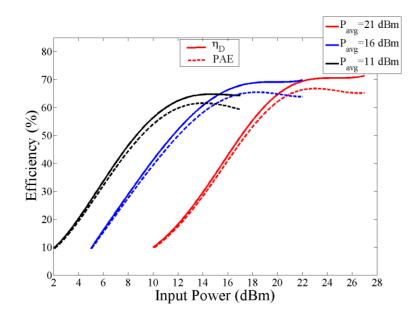

| Figure 5-9, Measured Drain and Power Added Efficiencies of the Reconfigurable Doherty Amplifier   |

| for Three Average Power Settings at 2.6 GHz70                                                     |

|                                                                                                   |

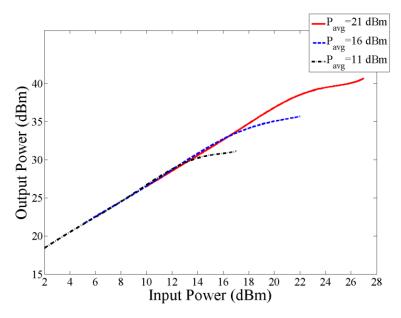

| Figure 5-10, Measured Output Powers of the Reconfigurable Doherty Amplifier for Three Average     |

|---------------------------------------------------------------------------------------------------|

| Power Settings at 2.6 GHz70                                                                       |

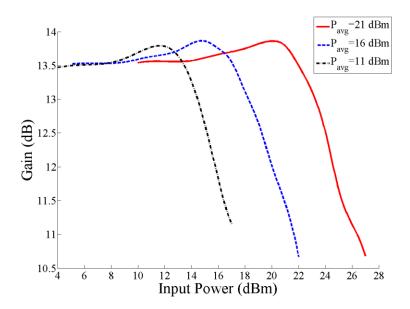

| Figure 5-11, AM/AM Measurements for the Reconfigurable DPA for Three Average Power Settings       |

| at 2.6 GHz                                                                                        |

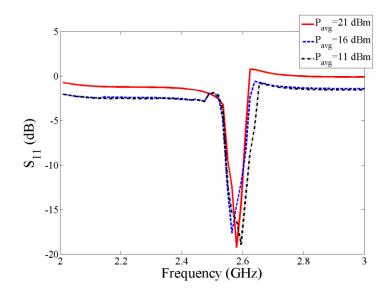

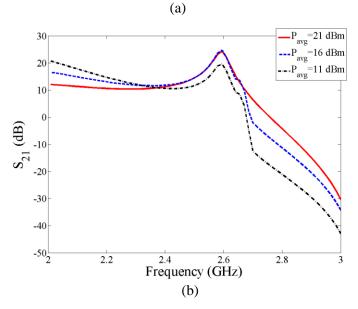

| Figure 5-12, Scattering Parameters Measurements for the Reconfigurable DPA for Three Average      |

| Power Settings at 2.6 GHz                                                                         |

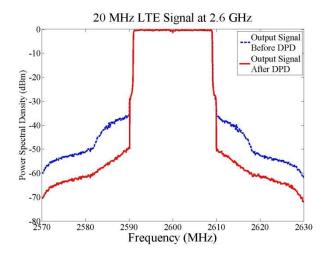

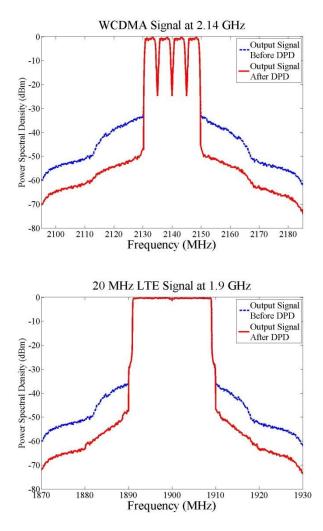

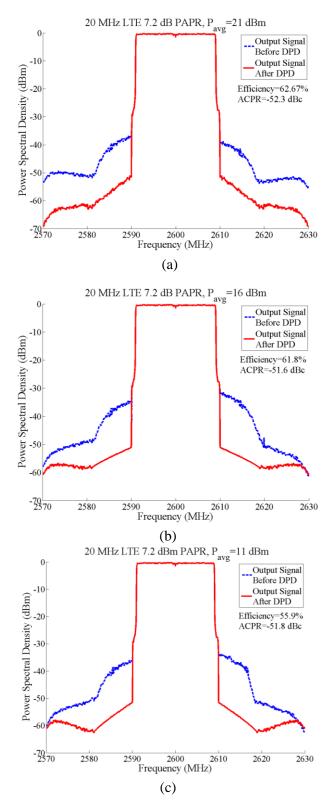

| Figure 5-13, Output Spectrum of the Linearized and Non-linearized Reconfigurable DPA for Three    |

| Average Power Settings at 2.6 GHz                                                                 |

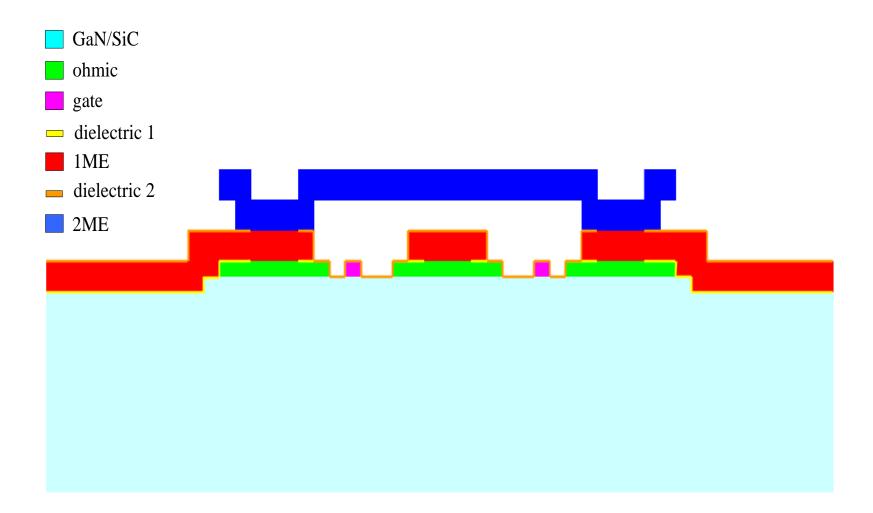

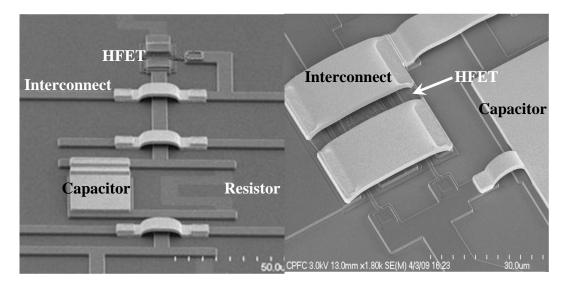

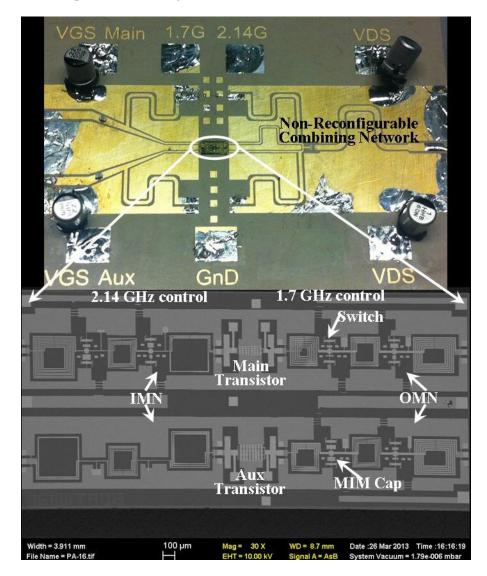

| Figure 6-1, Cross-section of a 2-Gate Device with an Air Bridge Interconnection77                 |

| Figure 6-2, SEM Photo of CPFC <sup>®</sup> GaN500 Process Components                              |

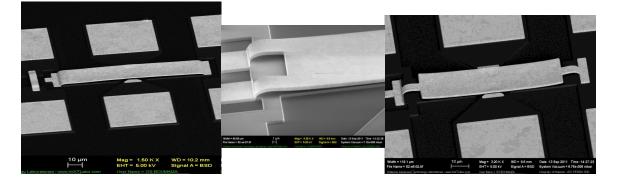

| Figure 6-3, First Patch of the Fabricated RF MEMS Switches Showing the Curling in the Suspended   |

| Plates that Increases the Stiffness                                                               |

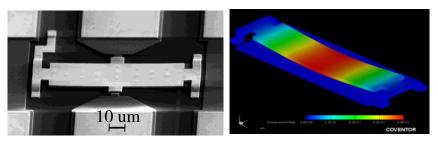

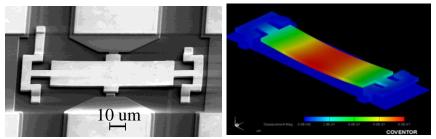

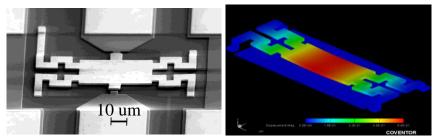

| Figure 6-4, The SEM Image and the Corresponding Simulated Actuation of Each Switch Design 80      |

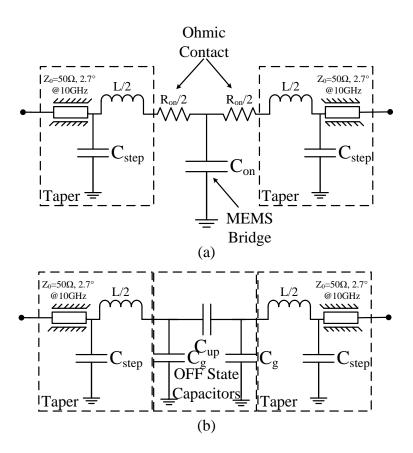

| Figure 6-5, (a) ON-state and (b) OFF-state Switch Equivalent Circuit                              |

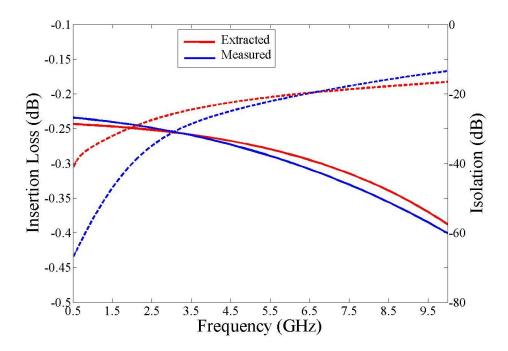

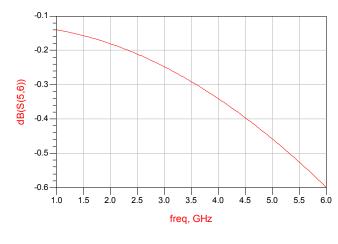

| Figure 6-6, Switch 1 Extracted and Measured Insertion Loss and Isolation                          |

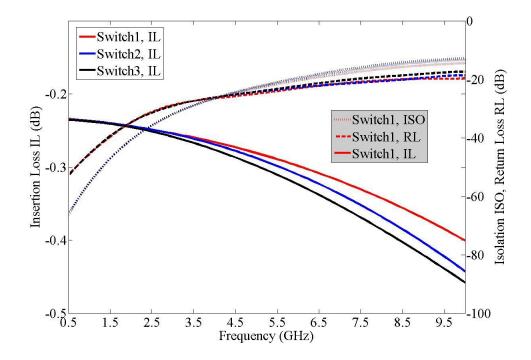

| Figure 6-7, Switches Measurement Results                                                          |

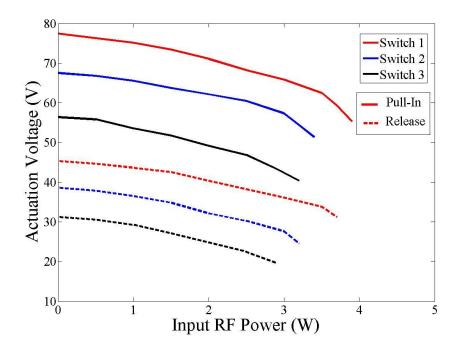

| Figure 6-8, Switch Pull-in and Release Voltages Variation at Different Input RF Power Levels83    |

| Figure 6-9, Switches Pull-in and Release Voltages Variation at Different Input RF Power Levels 84 |

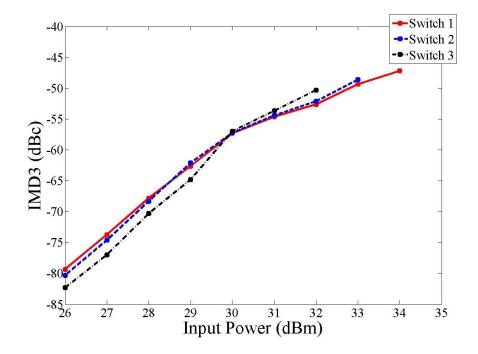

| Figure 6-10, Switches Linearity Measurements                                                      |

| Figure 6-11, Simulated Insertion Loss for (a) 3 Turns and (b) 9 Turns MMIC Inductors with 250 um  |

| Side Length                                                                                       |

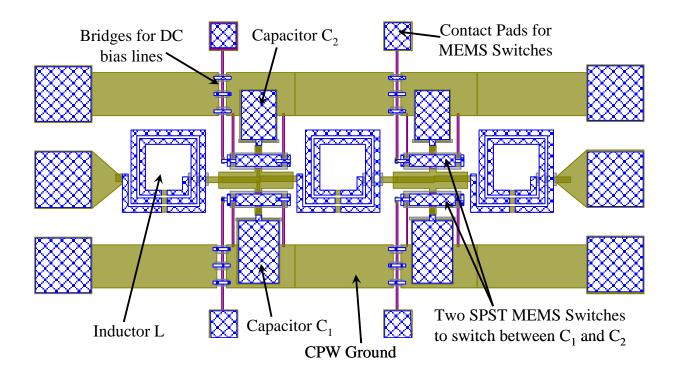

| Figure 6-12, Circuit Schematic for the Matching Networks of the Integrated Reconfigurable DPA 87  |

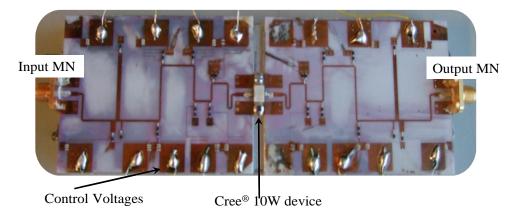

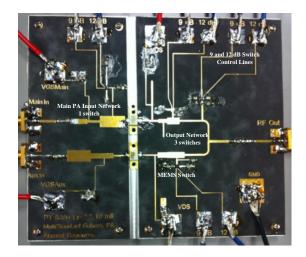

| Figure 6-13, Frequency Agile Monolithic GaN DPA [82]88                                            |

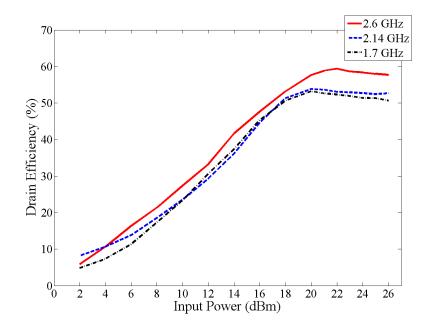

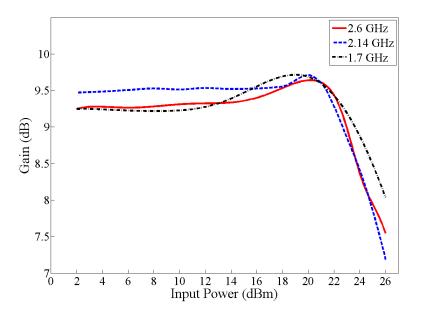

| Figure 6-14, Measured Drain Efficiency at 1.7 GHz, 2.14 GHz and 2.6 GHz                           |

| Figure 6-15, AM/AM Measurement Results at the Three Operating Frequencies90                       |

|                                                                                                   |

## List of Tables

| Table 2-1, Competitive Advantages of GaN Devices                                             | 24   |

|----------------------------------------------------------------------------------------------|------|

| Table 3-1, 2.5 GHz Design Pre-matching Capacitor Values for Different States                 | 29   |

| Table 3-2, Peak Efficiency and Efficiency Enhancement for the Harmonically-Tuned Reconfigura | able |

| Power Amplifier at Different Frequencies                                                     | 34   |

| Table 5-1, Variable Average Power Doherty Design Parameters                                  | 68   |

| Table 6-1, Switches Extracted Equivalent Circuit Parameters                                  | 81   |

| Table 6-2, Switch 1 Extracted Performance Parameters                                         | 83   |

| Table 6-3, Recent MEMS Switch Performance Summary                                            | 85   |

# Chapter 1 Motivation and Introduction

### 1.1 Introduction

Recent developments in wireless communications have brought numerous challenges which are considerably increasing the complexity of wireless networks infrastructure design. One of the considerable consequences of these developments is the introduction of a broad spectrum of communication standards. Mobile systems such as the global system for mobile communications (GSM) and wideband code division multiple access (WCDMA), as well as wireless local area networks such as WiFi and WiMAX, are expected to co-exist and, hence, dynamic management of wireless networks is becoming an essential requirement.

Consequently, a shift from dedicated single operating condition radios to versatile and adaptive systems, capable of maintaining efficient operation over diverse deployment scenarios, is unavoidable. These scenarios include wide spread of carrier frequencies with different operating bandwidths as well as dissimilar signal characteristics which result in diverse peak to average ratios in the corresponding signals of values up to 6 or even 12 dB, depending on the standard and the modulation scheme. In addition, the continuously changing characteristics (e.g., average power) of the communication signals engendered by the dynamic networks' loads are posing additional performance challenges.

The diverse requirements of modern communication systems create numerous challenges in the design of infrastructure for radio systems and the corresponding RF frontend circuitry. The latter is expected to maintain competitive performance when fed with dissimilar signal characteristics such as centre frequencies, bandwidths, time domain statistics and modulation schemes. In summary, intelligent radio systems have to maintain their high efficiency and quality of signal (i.e., minimal distortion), when processing multi-mode and multi-standard communication standards.

### 1.2 Power Amplifiers in Modern Communication Systems

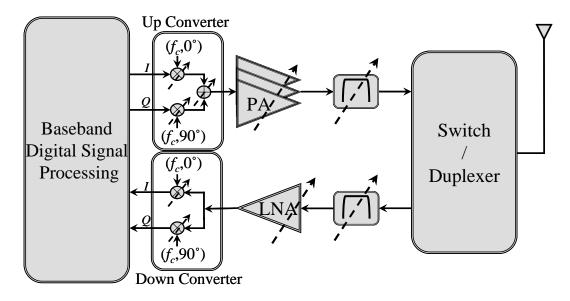

Like any communication system, radio systems are composed of numerous building blocks (BBs). These BBs can be either passive or active. Examples of passive BBs are switches, filters, couplers, power dividers, and antennas. These BBs are responsible for signal shaping and filtering. Active BBs consist of, among others, amplifiers; power amplifiers (PAs) in transmitters

and low noise amplifiers (LNAs) in receivers. They are responsible for boosting the transmitted and receiving signals' power. Other active blocks are mixers and oscillators essential for signal synthesis and frequency conversion of the signals (Figure 1-1).

Figure 1-1, Modern Radio Systems Block Diagram

For adaptive radio systems, the different BBs have to maintain their expected performance parameters at various standards and for different applications. Among others, the radio front-end module (FEM), used in base stations and handsets, is required to meet various performance criteria, such us linearity and power efficiency, under different operation conditions (i.e., carrier frequency, modulation techniques, access technologies, and power levels).

The efficiency and linearity of the FEM are mainly dominated by that of PAs. The PA converts the direct current (DC) power into output radio frequency (RF) power which is provided to the transmitted signal. Hence, the design of the PA is extremely challenging as it is required to maintain high efficiency and minimize nonlinearities during multi-frequency and multi-mode operation.

### 1.3 High Efficiency Multi-mode Multi-frequency Power Amplifiers

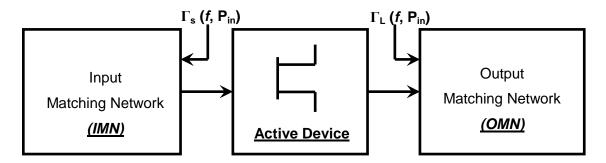

PAs are generally designed to maximize efficiency at a given operating condition (i.e., peak power level and centre frequency) by presenting optimal source and load terminations at this arrangement. Hence, PAs only maintain high efficiency at a single frequency and peak input power level. Consequently, techniques must be developed to enhance the PA efficiency by targeting the PA's optimum performance parameters, in other words source and load optimal terminations, at various back-off power levels and wide spread centre frequencies (Figure 1-2).

Figure 1-2, Block Diagram for a High Performance Power Amplifier

One of the potential techniques for PA efficiency enhancement is the reconfigurable PA. The design of electronically tunable matching networks at the source and load of the transistor, providing optimum impedances at back-off power levels as well as at the peak power level, becomes of great interest. These tunable source and load terminations enable PA reconfigurability versus power levels, however, handling dissimilar centre frequencies is still challenging. In order to fulfill the multi-standard operation of PAs, the matching networks have also to be multi-band, broadband or frequency agile.

Multi-band and broadband PAs are among the alternative solutions for PA efficiency enhancement for a preset group of operating frequencies. Multi-band PAs rely on the design of matching networks capable of simultaneous realization of optimal terminations at two or more frequencies. On the other hand, broadband PA designs achieve optimal terminations for a wide range of frequencies instead. These techniques improve PA operation versus the operating frequency. Maintaining competitive performance at reduced input signal levels, however, is still a challenge. One of the possible solutions is to extend the operating band of a pre-established efficiency enhancement technique, for example Doherty or Envelope Tracking. These techniques were originally designed to enhance the PA efficiency at back-off power levels.

### **1.4 Thesis Objectives**

From the previous discussion it can be seen that the main limitation of RF PAs in modern radio systems is their optimized performance at a single operating scenario with dedicated single carrier frequency when the input signal operates at peak power level. Several efficiency enhancement techniques, discussed in detail in Chapter 2, are available to maintain the PA optimized performance at reduced input power levels and efficiently handle signals with predetermined statistics. In this thesis, we focus on the complete design and development of PAs capable of maintaining their competitive performance under different operating scenarios including dissimilar signals statistics and centre frequencies. PAs with variable operating conditions (e.g., peak-to-average power ratios (PAPR), centre frequencies and variable peak driving signal levels) are addressed throughout the presented work. Towards realizing the targeted adaptive PAs for modern radio systems, specific objectives were set for this research;

- Development and implementation of reconfigurable impedance matching networks using discrete tunable elements capable of synthesizing diverse impedances at widely spaced centre frequencies while controlling the corresponding harmonic impedances. The reconfigurable networks will be applied to implement a reconfigurable Class F<sup>-1</sup> PA with harmonic tuning for efficiency enhancement at different power levels and diverse center frequencies.

- Development of a reconfigurable Doherty PA (DPA) for efficient amplification of multi-frequency, multi-standard radio signals.

- Development of a reconfigurable DPA for efficient handling and amplification of signals with variable average power levels.

- Development and implementation of GaN-based, high power RF microelectromechanical systems (MEMS) switches using the available NRC-CPFC<sup>®</sup> GaN500 monolithic microwave integrated circuit (MMIC) process.

- Development and implementation of an electronically tunable, integrated DPA, for multi-band radio systems operation, using the GaN500-compatible designed RF MEMS switches to achieve the required reconfigurability.

### **1.5 Thesis Outline**

In Chapter 2, a brief review will be conducted of PA classes of operation. These classes are optimized to efficiently operate around a predetermined frequency and at a peak input power level. In addition, efficiency enhancement techniques targeting reduced input power level operation will be presented. Afterwards, a comparative study is presented of different approaches and techniques devised to maintain the PA's competitive performance over different frequency bands, dissimilar signals' time domain characteristics and back-off input power levels. Special attention is given to the DPA as an astute approach to back-off PA efficiency enhancement. DPAs

achieve this enhancement by actively modulating the load impedances for a predetermined PAPR value. Practical and theoretical limitations of DPAs under wideband operation and dissimilar signal PAPR values are examined. In addition, the features of AlGaN/GaN technology will be discussed as a candidate technology for realizing reconfigurable PAs.

Chapter 3 presents different solutions for extending the single-ended PA's high performance to simultaneous handling of wireless signals with different time domain characteristics, in other words PAPR, which are centered around widely spread operating frequencies. Complete design, fabrication and measurement results for two prototypes of harmonically-tuned reconfigurable Class  $F^{-1}$  PAs will be presented.

Afterwards, in Chapter 4, the design of electronically tunable multi-frequency multistandard Doherty amplifier is presented. Systematic closed form equations are developed in order to achieve this. The design methodology is applied to design three Doherty prototypes; multifrequency single PAPR, single frequency multi-PAPR and multi-frequency multi-mode DPAs. Fabrication and measurement results will be presented and discussed in details.

In Chapter 5, a similar design approach is conducted to develop closed form equations for designing a reconfigurable DPA that maintains high efficiency when driven by communication signals with highly varying average power levels for dynamic loads networks. The design procedure is then applied to realize a 10 W DPA that operates efficiently at average output power levels of 35, 30 and 25 dBm.

Chapter 6 discusses the GaN MMIC process available for realizing the integrated version of the reconfigurable Doherty PA. Challenges associated with implementing the tunable RF MEMS switch using the GaN MMIC process are highlighted in details. The design, fabrication and measurements of an integrated frequency-agile DPA, based on the analysis conducted in Chapter 4, is presented and discussed in this chapter.

Finally, we conclude what has been achieved through this research and the possible future developments for completing a fully integrated power amplifier for all possible operating conditions of modern wireless radio systems.

### Chapter 2

# Overview of Power Amplifier Efficiency Enhancement Techniques for Modern Radio Systems

### 2.1 Power Amplifier Classes of Operation

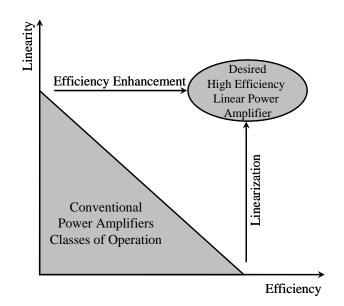

Power amplifiers (PAs) are used to convert the supply direct current (DC) power into radio frequency (RF) power which results in an enlarged version of the input signal at the output. Different design characteristics are considered when dealing with PAs including gain, output power delivered, bandwidth, and drain efficiency. The design of a PA is challenging as it is required to amplify the input RF signal with a minimum of distortion; this contradicts the nonlinear nature of the PA (Figure 2-1). As a result, a trade-off between efficiency and linearity must be carefully considered in the design of a PA. Different PA classes of operation were introduced to target the efficiency-linearity trade-off [1]. Conventional classes range from linear, low efficient class A to highly nonlinear, highly efficient class C. Other classes of high efficiency PAs (HEPAs) exploit harmonic impedance terminations to engineer the voltage and current waveforms, consequently maximizing the efficiency.

Figure 2-1, Trade-off between Linearity and Efficiency of Power Amplifiers

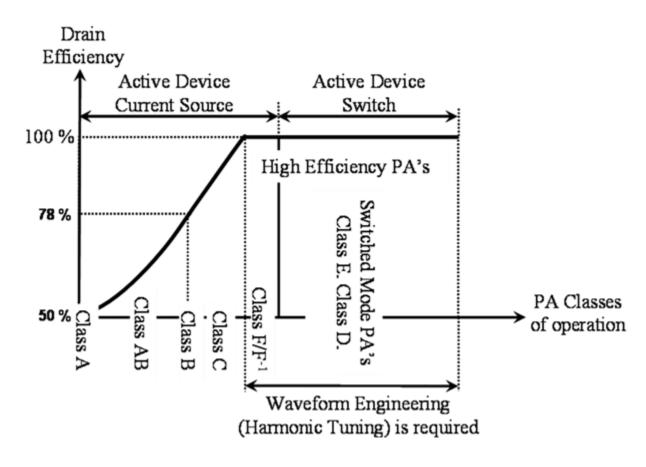

Figure 2-2 depicts various classes of operation of PAs. The conventional classes of operation, A, AB, B and C, consider the active device as a current source. Efficiency is increased from class

A all the way to class C, at the expense of linearity [2], [3], by reducing the current conduction angle,  $2\theta$  (Figure 2-3). High efficiency classes of operation were introduced so that the efficiency can ideally be equal to one. For instance, class  $F/F^{-1}$  is biased like conventional PA classes yet requires appropriate tuning of harmonic impedances as well as fundamental ones. Switched mode PAs such as class D and E, where the active device operates as a switch, introduce a new generation of PAs that can deal directly with incoming digital signals. All of the high efficiency classes require tuning of harmonic impedances to achieve the theoretical highest efficiency. The more the harmonics are appropriately tuned, the more the efficiency approaches unity.

Figure 2-2, Different Classes of Operation for Power Amplifiers

Figure 2-3, (a) Load/line Characteristics for Different Classes, (b) Output Current Waveforms for Class AB (dotted), Class B (solid), and Class C (dashed) [2]

### 2.2 Power Amplifier Efficiency Enhancement

Conventional PA circuits are generally designed to operate at single predetermined centre frequency and, at the same time, are optimally matched at a single input power level which is normally the peak power. However, recent evolutions in wireless communications have resulted in a broad spectrum of standards which involve highly varying envelope signals with different average power levels and which are centered around widely spaced frequency bands. As a result, adaptive PAs that maintain their competitive performances under diverse conditions are needed.

#### 2.2.1 Single-Ended High Efficiency Multi-frequency Power Amplifiers

Development of efficiency enhancement techniques has been the objective of numerous research initiatives aimed at efficiently amplifying signals at back-off power levels and different operating frequencies. As previously mentioned, PAs require the precise introduction of optimal source and load terminations for the operating condition in order to efficiently amplify the incoming RF signal. In order to accommodate dissimilar deployment scenarios, like those dictated by modern radio systems, the PA matching networks should create the terminations of the preset operating conditions. Several techniques, including reconfigurable multi-band and broadband matching networks, may be utilized to acquire the desired PA designs for modern communication systems.

### 2.2.1.1 Reconfigurable Power Amplifiers

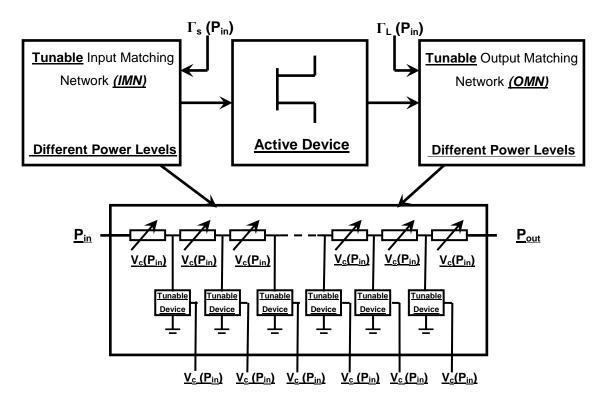

Figure 2-4, Schematic diagram for a Reconfigurable Power Amplifier

The load and source impedances of the active device can be passively modulated in order to introduce the transistor optimal impedances at different power levels, thus, realizing a reconfigurable PA (Figure 2-4). Passive load modulation implies the introduction of discrete, distributed, or integrated tunable devices in the matching networks circuitry. Optimal impedances at back-off power levels are introduced to improve the PA efficiency; tunable matching devices such as semiconductor varactors and switches, microelectromechanical systems (MEMS) based tunable devices, and tunable dielectrics are utilized to realize reconfigurable matching networks [4], [5], [6], [7].

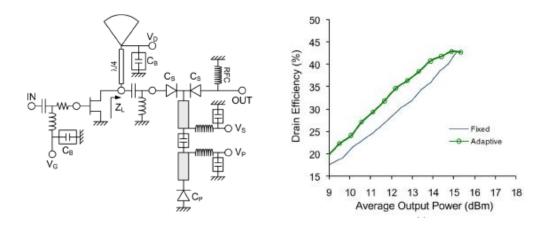

In [4], a reconfigurable PA was fabricated using GaAs semiconductor varactors. The enhancement was only targeted at 1.75 GHz versus different power levels. Figure 2-5 shows the PA circuit schematic and the efficiency enhancement achieved.

Figure 2-5, Schematic and Efficiency Enhancement Results for a Power Amplifier [4]

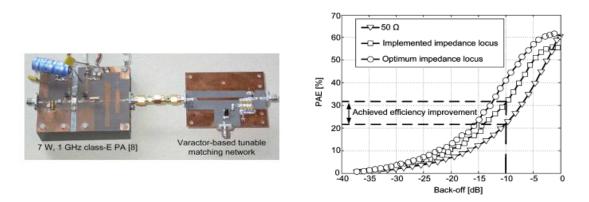

Another passively load modulated laterally-diffused metal oxide semiconductor (LDMOS) class E 7 W PA with enhanced efficiency at 10 dB output back-off power levels is presented in [5]. Tunability was achieved with 2x2 SiC Schottky diode stacked varactors to improve the tuning range and increase the breakdown voltage. The fabricated amplifier was centered around three different frequencies: 1 GHz which achieved more than 60% power-added efficiency (PAE) at peak output power, 7 W which achieved 30% PAE, and 0.7 W which achieved more than 10% enhancement (Figure 2-6).

Figure 2-6, Circuit Demonstrator and Resulting Efficiency Enhancement Values [5]

The frequency-agile operation required for an adaptive PA is still challenging for reconfigurable PA prototypes. Moreover, the nonlinearity of the available tunable device technologies affects the linearity of the overall PA design. MEMS technology which on the contrary is highly linear, suffers from slow switching speeds. This limitation makes it challenging for variable envelope and wideband signals.

#### 2.2.1.2 Multi-Band and Broadband Power Amplifiers

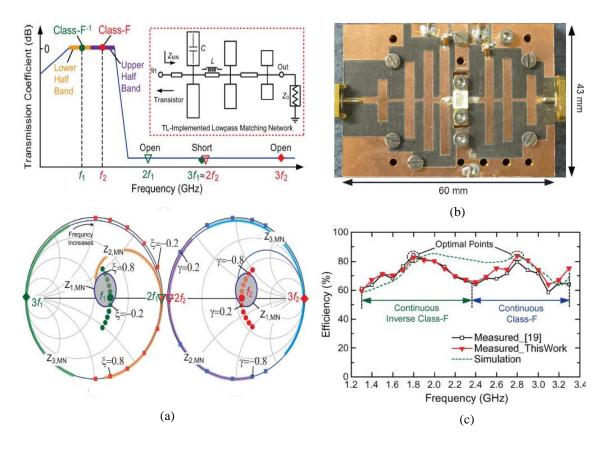

With a view to tackling the limited band of operation of conventional PAs, various approaches have been investigated to design broadband and multi-band amplifiers capable of handling multiple standards [8], [9], [10], [11], [12], [13], [14], [15]. These approaches have employed the class J design space [16], [17], [18], [19], [20] and dynamic passive load modulation. As an example, a novel methodology for dual-band PA design is achieved by transferring between Class F and Class  $F^{-1}$  operations [12] (Figure 2-7a). This design presents a three stage transmission lines-based low pass matching network for a Cree 10 W packaged device. Complete analysis was conducted to ensure the dual-band nature of the matching networks and subsequently, the demonstrator was fabricated as shown in Figure 2-7b. The dual-band PA achieved gain of higher than 10 dB and drain efficiency of about 80% for centre frequencies ranging between 1.8 and 2.8 GHz (Figure 2-7c). The approach, presented in this paper, is valid only when two frequencies

have a specific relationship  $(\frac{f_2}{f_1} = 1.5)$ .

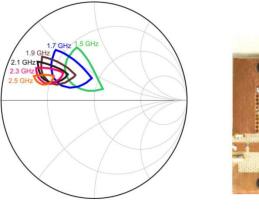

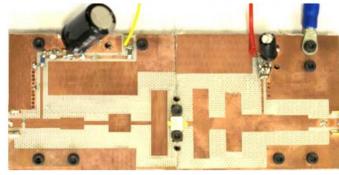

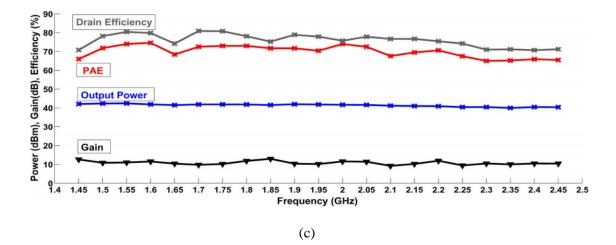

A broadband design for a linearized class F PA is designed and presented in [13]. The PA design reduces the device sensitivity to harmonic terminations by using the device nonlinear capacitance for voltage and current wave-shaping. A complete analysis of the nonlinear device capacitance CDS was conducted to determine the high efficiency reactance values region in the design plane. Figure 2-8a shows the merged output power and peak efficiency optimal fundamental impedance contours at the appropriate output reactance termination. The fabricated prototype (Figure 2-8b) used a packaged 10 W Cree active device and achieved drain efficiency of more than 70% in the 1.45-2.45 GHz band (Figure 2-8c).

**Figure 2-7**, (a) Dual-band Dual Operating Frequency Matching Network Design, (b) Fabricated Power Amplifier, (c) Drain Efficiency Results for the Broadband Power Amplifier [12]

**Figure 2-8,** (a) Peak Output Power and Efficiency Contours of the Power Amplifier, (b) Circuit Demonstrator, (c) Measurement Results for the Broadband Class F Power Amplifier [13]

### 2.2.2 Envelope Tracking

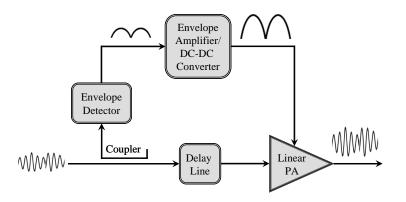

Unlike passive load modulation of the PA optimal loads which uses reconfigurable matching networks, Envelope Tracking (ET) [21], [22], [23], [24], [25], [26], [27] achieves PA efficiency enhancement at back-off power levels by modulating the active device drain supply as a function of the input signal strength. Figure 2-9 shows the ET architecture with analog control where an envelope detector is used at the input to detect the signal envelope. A DC-DC converter (envelope amplifier) is used to provide the dynamically controlled supply voltage to a linear PA. ET architecture needs a delay line to compensate for the phase misalignment between the envelope and the RF signal due to the envelope feedback path. The ET system suffers from linearity issues to a greater extent than does the PA with fixed supply voltage.

Figure 2-9, Envelope Tracking Architecture Block Diagram [2]

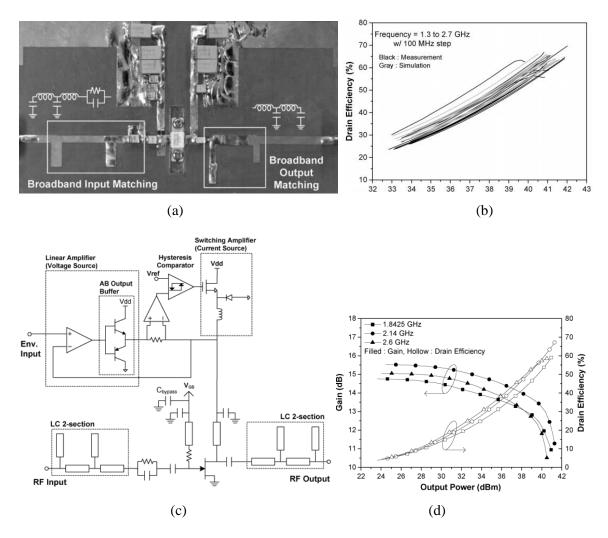

Thus, ET achieves PA efficiency enhancement versus reduced input power levels, however, the frequency agility remains unsolved. This challenge is addressed in [27]. The ET saturated amplifier's broadband matching networks are capable of covering the band from 1.3 to 2.7 GHz, achieving peak drain efficiency higher than 55% over the operating bandwidth (Figure 2-10a, b). The switching amplifier has a hybrid configuration, a schematic of which is shown in Figure 2-10c. The continuous wave (CW) measurements of the ET system's overall gain and efficiency at three selected frequencies are depicted in Figure 2-10d.

**Figure 2-10**, Broadband Saturated Amplifier (a) Demonstrator and (b) Continuous Wave Measurements; ET System (c) Circuit Schematic and (d) Continuous Wave Measurements [27]

ET technique is an attractive candidate for realizing multi-frequency multi-mode PAs, however, the limited speed of the DC-DC converter presents challenges for wideband and highly

varying signal operation. The Doherty technique, however, achieves high efficiency over reduced power levels for rapidly varying envelope signals.

### 2.2.3 The Doherty Power Amplifier

#### 2.2.3.1 Doherty Power Amplifier Operation Overview

The Doherty technique is an astute approach that has achieved a considerable shift in back-off power drain efficiency levels by actively modulating the load impedance of the PA; referred to as the main. The Doherty technique was first introduced in 1936 [28]. It actively modulates the load seen by the main transistor to improve its efficiency in the back-off via a judiciously configured auxiliary transistor [29], [30], [31]. This auxiliary transistor starts conduction at a desired power threshold value which is determined based on the efficiency enhancement power range calculated from the input signal peak-to-average power ratio (PAPR). The relatively challenging realization of the Doherty technique in practice, with real devices, delayed its successful implementation to the late 1990s and its commercial adoption to recent years. In the following paragraphs, a brief analysis of the Doherty technique will be given to demonstrate the limitations of the technique for efficient handling of modern wireless signals under multiple operating conditions.

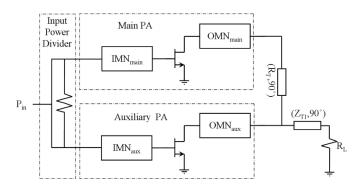

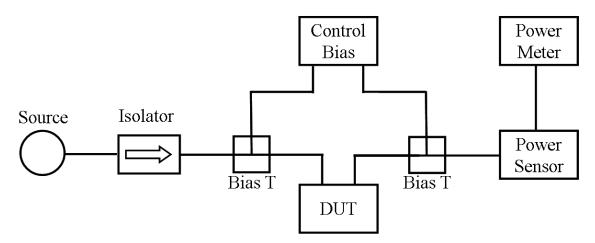

Figure 2-11 depicts a generic Doherty amplifier block diagram that includes peaking and main transistors, input and output matching networks (IMN and OMN respectively), and two impedance inverters. The main amplifier is class AB biased and matched to ensure peak efficiency at a predetermined power level, denoted here as  $\rho$ -dB which corresponds to a reduced input voltage level of  $\frac{V_{in,max}}{p}$  where  $\rho(dB) = 20 \log p$ . The auxiliary device is biased at class C and is required to start conducting at the given reduced input voltage. In order to maintain the maximum efficiency at the widely separated values of the desired back-off power levels, the output impedance seen by the main amplifier needs to follow (2-1) for given values of p, while at the same time, the auxiliary amplifier should be capable of supplying the required current values for proper load modulation (2-2).

Figure 2-11, Conventional Doherty Amplifier Block Diagram

$$Z_{main} = \begin{cases} pR_L & 0 \le v_{in} \le \frac{1}{p} V_{in,\max} \\ pR_L (1 - \frac{\alpha(p-1)}{1 + (p-1)\alpha}) & \frac{1}{p} V_{in,\max} \le v_{in} \le V_{in,\max} \end{cases}$$

(2-1)

$$I_{aux} = I_{main} \frac{p\alpha(p-1)}{1 + \alpha(p-1)}$$

(2-2)

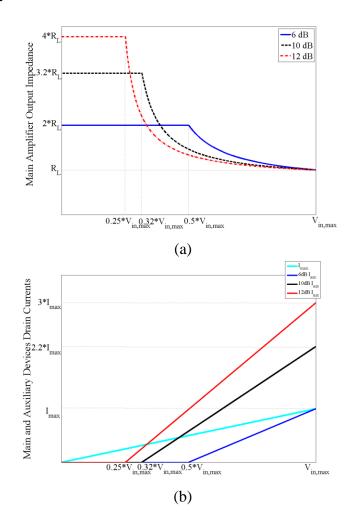

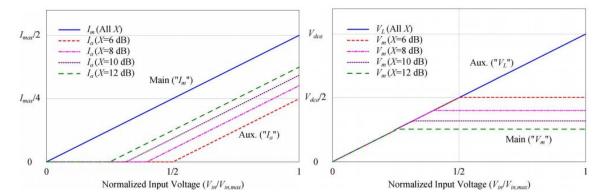

#### 2.2.3.2 Multi-frequency Multi-mode Doherty Power Amplifier Design Challenges

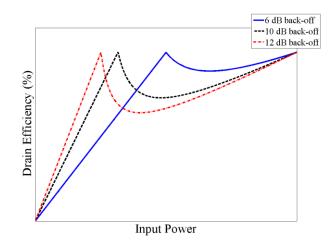

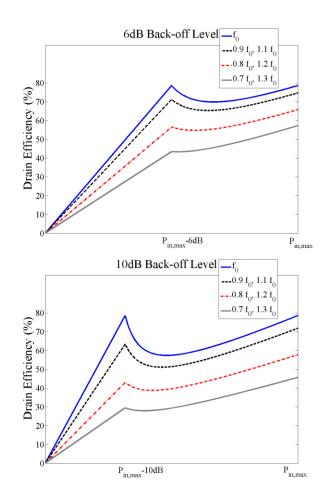

In this section, we explore the challenges that accompany the extension of Doherty PA (DPA) design to signals with different centre frequencies and extended PAPR levels. From the previous discussion, it can be seen that the dependence of the Doherty generic network design on the operating frequency and the preset PAPR value is non-negligible. Figure 2-12 illustrates the necessary variation of the desired main amplifier output load impedances and the corresponding auxiliary current profiles at PAPR values between 6 and 12 dB to achieve the proper load modulation. The resulting ideal drain efficiency profiles vs. input power for different back-off levels were obtained and are plotted in Figure 2-13.

In equations 2-1 and 2-2,

$$\alpha = \frac{pv_{in} - V_{in,max}}{V_{in,max}}$$

.  $Z_{T1}$ ,  $R_T$  and  $R_L$  represent the two inverters?

characteristic impedances and the Doherty load resistance, respectively. For proper Doherty operation, the characteristic impedance and the load resistance are equal to

$$R_{L} = R_{opt}, \quad R_{T} = R_{L} = R_{opt}, \quad Z_{T1} = \frac{R_{opt}}{\sqrt{p}} = \frac{R_{L}}{\sqrt{p}}$$

(2-3)

where  $R_{out}$  denotes the optimum load impedance for the Doherty amplifier at peak input power.

The plots in Figure 2-12 and Figure 2-13 were obtained at an operation frequency for which the length of the impedance inverters in Figure 2-11 were equal to quarter-wavelength. However, as the frequency varied, the load modulation in the DPA was affected directly by the varying of the impedance inverters' electrical lengths with frequency. The inclusion of the frequency dependency of the impedance inverters in (2-1) leads to the following expression of the impedance seen by the main transistor:

Figure 2-12, Ideal Profiles for (a) Main Amplifier Output Impedance and (b) Auxiliary Transistor Drain Current at Variable Peak to Average Power Ratio Values

Figure 2-13, Ideal Drain Efficiency Profiles at Different Peak to Average Power Ratio Values

$$Z_{main} = \begin{cases} R_L \frac{(\sqrt{p}\cos^2\theta - p\sin^2\theta) + j(1 + \sqrt{p})\sin\theta\cos\theta}{(\sqrt{p}\cos^2\theta - \sin^2\theta) + j(p + \sqrt{p})\sin\theta\cos\theta} \\ 0 \le V_{in} \le \frac{V_{in,max}}{p} \end{cases}$$

(2-4)

$$R_L \frac{(\sqrt{p}\beta\cos^2\theta - p\sin^2\theta) + j(\beta + \sqrt{p})\sin\theta\cos\theta}{(\sqrt{p}\cos^2\theta - \beta\sin^2\theta) + j(p + \sqrt{p}\beta)\sin\theta\cos\theta} \\ \frac{V_{in,max}}{p} \le V_{in} \le V_{in,max} \end{cases}$$

where  $\beta = 1 + \frac{I_{aux}}{I_{main}} = 1 + \frac{p(p-1)\alpha}{1 + (p-1)\alpha}$ , *p* refers to the desired back-off level and  $\theta$  denotes the new

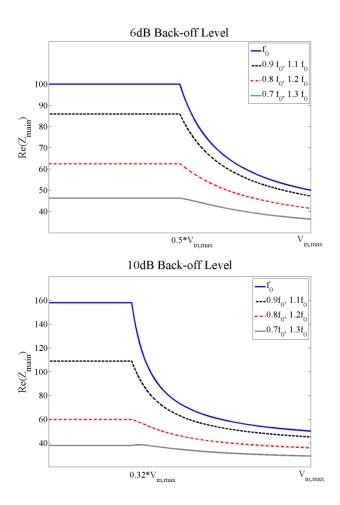

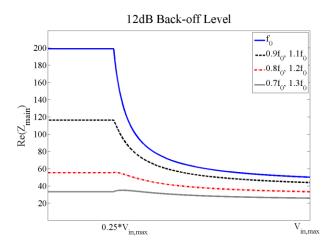

electrical length of the impedance inverters at a given frequency. The real impedance seen by the main transistor,  $R_L = 50\Omega$ , deviates from the ideal as presented in Figure 2-14. The improper load modulation resulting from the frequency variation accentuates the efficiency degradation versus frequency as the value of p increases. Figure 2-15 shows the efficiency deterioration due to the strong sensitivity to frequency deviation of the Doherty amplifier impedance inverters. It is worth mentioning, that both the main and auxiliary transistors exhibit additional parasitics and, therefore, require output impedance matching networks. These parasitics contribute to the frequency dependence of the DPA circuitry and cause additional challenges when attempting to satisfy the conditions of proper load modulation over widely separated frequencies.

### 2.2.3.3 Multi-band and Broadband Doherty Power Amplifiers

Several attempts have targeted the development of broadband and multi-band DPAs [32], [33], [34], [35], [36], [37] and yielded, thus far, relatively reduced efficiency compared to their

narrowband counterparts especially in the back-off regions. In [34], a complete circuit analysis was presented to design a broadband DPA which would achieve the optimal load impedances for the main and auxiliary transistors over the targeted bandwidth. The design used packaged Cree devices to assemble symmetrical broadband DPA matching networks using 2.6 GHz centre frequency which covered a bandwidth of 2.2-3 GHz of operation. Figure 2-16 shows the maximum available flat drain efficiency, over 40% at 6 dB output back-off, over the desired frequency band.

**Figure 2-14,** Main Transistor Output Impedance vs. Frequency for Different Doherty Power Amplifier Configurations at Variable Peak to Average Power Ratio Values

**Figure 2-15,** Main Transistor Drain Efficiency Deterioration vs. Frequency for Different Doherty Power Amplifier Configurations at Variable Peak to Average Power Ratio Values

**Figure 2-16**, (a) Circuit Photograph and (b) Measured Drain Efficiency Results for the Broadband Doherty Power Amplifier [34]

A dual-band DPA operating at 0.88 and 1.96 GHz was designed and presented in [35] using careful design of dual-band T-shaped passive network components. The proposed design and the equivalent circuits for the dual-band building components are depicted in Figure 2-17. The paper presented two fabricated DPA prototypes with balanced and unbalanced input power division for enhancing the drain efficiency at back-off power levels.

Figure 2-17, (a) Dual-band Doherty Power Amplifier Schematic and (b) Equivalent Circuit for the Dual-band Distributed Element [35]

### 2.2.3.4 Extended Peak to Average Power Ratio Doherty Power Amplifiers

For extended PAPR Doherty values, the efficiency profile in the back-off region drops. Several variations of the DPA main circuit design have been introduced for amplifying signals with extended PAPR values. Tailoring the efficiency curve requires N-way DPA [38], [39], [40] with N-1 auxiliary devices. However, as in [39], the size of the auxiliary transistors is directly proportional to the desired PAPR values. Hence, relatively large auxiliary amplifiers are required to shift the efficiency profile up in the back-off region. Recently, authors have proposed an interesting approach to reconfigure a Doherty amplifier, using die transistors, as a function of the input signal [41]. The PA was designed to operate at centre frequencies between 1.5 and 2.5 GHz. The reconfigurability was achieved by varying the drain supply voltage of the main transistor. Despite excellent drain efficiency achieved at PAPR as high as 10 dB (Figure 2-18) the overall gain was relatively low and the linearizability of the DPA was not presented. Moreover, the effect of reducing the main transistor drain bias on the power utilization factor was not discussed.

### **Figure 2-18,** (a) 6-dB PAPR Efficiency Enhancement at Different Frequency Bands and (b) Multi-PAPR Efficiency Enhancement Results at 2 GHz [41]

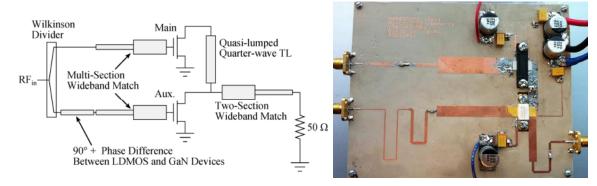

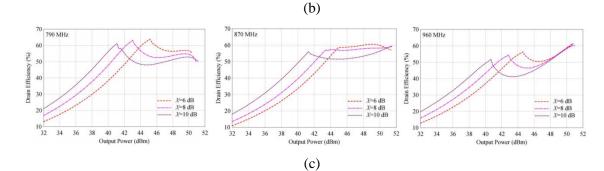

In order to solve the problem of linearizability of the extended PAPR DPA, a modified design which deviated from the basic DPA circuit was presented in [42]. New auxiliary current profiles, and main amplifier drain bias values, optimized for every targeted PAPR value were derived. These findings are depicted in Figure 2-19a. The output matching network absorbed the parasitic capacitances of the main and auxiliary devices for wide band operation (Figure 2-19b). The amplifier achieved efficiency of greater than 50% (Figure 2-19c) and a small signal gain of more than 15 dB for output back-off up to 10 dB at 790, 870 and 960 MHz.

(•)

Figure 2-19, (a) Optimal Auxiliary Drain Current and Main Drain Bias Values for Different PAPR Values, (b) Circuit Schematic and Demonstrator, and (c) Efficiency Enhancement Measurement Results [42]

### 2.3 Transistor Technology

As the market for cellular, personal communications services, and broadband access is expanding, and fourth-generation (4G) standards are becoming closer to reality, high power RF PAs are beginning to be the focus of attention. A variety of PA technologies are in the market now, such as, bipolar devices, GaAs metal-semiconductor field-effect transistors (MESFETs) [43], [44], GaAs heterojunction bipolar transistors (HBTs) [45], [46], [47], SiC MESFETs [48], [49] LDMOS technology [50], [51], [52], [53], [54], [55], [56], [57], [58], and GaN high-electron mobility transistors (HEMTs). The latter technology [59] is an attractive candidate for high power handling applications. The high power at high frequency capacity is the biggest advantage of GaN HEMT over LDMOS technology. Excellent high frequency ( $f_i$  =110 GHz for a 0.15 µm gate length [60]) and high power density (30 W/mm at 10 GHz [61]) have been demonstrated. The wide bandgap feature allows high breakdown voltage (typically > 100 V) and the higher amount of charge provides high current (1-1.4 A/mm for GaN HEMT compared to 150 mA/mm for LDMOS).

The competitive advantages of GaN devices and amplifiers for commercial products are described in Table 2-1. In every single category, GaN devices excel over conventional technology. The last column summarizes the resulting performance advantages at the system level for the customer. The high power per unit width translates into smaller devices that are not only easier to fabricate, but offer much higher impedance as well. This makes the GaN-based devices much easier to match to the system. The task of matching is often a complex one with conventional devices (e.g., GaAs and LDMOS devices have three to five times lower optimum impedances than those of GaN devices).

| Need from a new Technology      | Enabling feature of GaN<br>Technology           | Performance Advantage                      |

|---------------------------------|-------------------------------------------------|--------------------------------------------|

| High Power Handling/ unit width | Wide band gap (3.4 eV),<br>High breakdown field | Compact, therefore; easier<br>for matching |

| High Voltage Operation | High breakdown field   | Reducing need for high current      |

|------------------------|------------------------|-------------------------------------|

| High Frequency         | High electron velocity | Fast operation speed                |

| High Efficiency        | High operating voltage | Reducing cooling due to low current |

| Low SNR                | High power gain        | High dynamic range                  |

| Thermal Management     | SiC substrates         | Reducing cooling needs              |

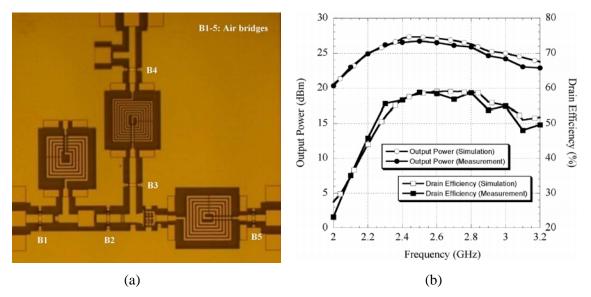

Research attempts have targeted integrated high efficiency broadband and multi-mode PAs, among them DPAs, for wireless communications using the existing GaN monolithic microwave integrated circuit (MMIC) technology [62], [63], [64], [65], [66], [67], [68]. As an example, a monolithically integrated class J PA was fabricated [65] using the Canadian Photonic Fabrication Centre® (CPFC) GaN800, 0.8um gate length MMIC process offered by the National Research Council (NRC) of Canada. Complete load/source-pull simulations for the selected device and the required fundamental and second harmonic terminations were conducted to obtain the required terminations over frequency band 2.25-3.05 GHz. The targeted output power was 0.5 W, and the transistor was biased at 15 V. Figure 2-20a shows a photograph of the fabricated MMIC PA. The amplifier achieved more than 50% drain efficiency and 23 dBm over the whole band (Figure 2-20b).

**Figure 2-20,** CPFC<sup>®</sup> GaN MMIC Fabricated Class J PA (a) Photo, (b) CW Measured Output Power and Efficiency [65]

### 2.4 Discussion

In the previous literature survey, research initiatives targeting the efficiency enhancement of PAs for different operating conditions, including wide spread centre frequencies and extended peak-to-average power ratios were presented. Broadband and multi-band as well as reconfigurable matching networks were aimed at introducing optimal device terminations under different deployment scenarios. However, both solutions only solve the performance preservation versus either the power level or frequency. Moreover, the optimization nature of broadband/multi-band designs result in performance figures that cannot compete with their single frequency counterparts.

Doherty technique, using active load modulation, is used for PA efficiency enhancement at reduced power levels but, at the same time, suffers from narrow band limitation. Intensive efforts were exercised in the design of broadband and multi-band DPAs which extended the power back-off efficiency enhancement range. Reconfigurable, in other words frequency agile, DPAs are interesting candidates to manage all the variations in operating situations. As previously presented from the literature, tuning the drain bias for the main transistor can target multiple centre frequencies and PAPRs. However, this approach is not able to handle wideband signals due to the slow speed of the DC-DC converter. In our work we focus on designing electronically tunable matching networks for DPAs which maintain competitive performance at different frequencies, different PAPR values and different peak power levels.

In Chapter 4, a complete, systematic design approach to the design of high efficiency DPAs capable of efficiently amplifying signals with dissimilar PAPR centered around wide spread operating frequencies, using electronically tunable matching networks, is introduced. The design approach is then modified, in Chapter 5, to realize a DPA capable of handling incoming signals with variable peak and average power levels depending on dynamic networks loads. Knowing the attributes of candidate realizations of electronically tunable devices, MEMS devices [69], [70], [71], [72], [73] are considered to modulate the load seen by the transistor as a function of the incoming signal centre frequency and PAPR.

In Chapter 6, we present a detailed design and fabrication of high power RF MEMS switches on the CPFC® GaN500 0.5 um gate length MMIC process as a first step towards the design of a fully integrated, electronically tunable DPA for multi-standard operation. Afterwards, the strengths of the GaN transistor and the flexibility of MEMS devices are combined to build a high efficiency frequency agile, monolithically integrated DPA.

## Chapter 3

# Electronically Tunable Inverse Class F Power Amplifier for Multi-Frequency Multi-Mode Base Stations

### 3.1 Introduction

Evolution of wireless communications has resulted in a broad spectrum of standards. These multiple standards are expected to co-exist, and dynamic management of wireless networks becomes an essential attribute. This calls for an important shift from dedicated, single operating condition wireless systems to adaptive systems capable of handling dissimilar signal requirements (e.g., centre frequency, signal peak average power ratio (PAPR), bandwidth, and modulation scheme).

In the following sections we propose a novel harmonically tuned reconfigurable class  $F^{-1}$  power amplifier (PA) which achieves high efficiency enhancement at input power levels and widely spread centre frequencies. This is accomplished by using a reconfigurable matching network (MN) that utilizes the optimal fundamental terminations at the given power level and frequency settings, as well as tuning the impedances of the second and third harmonic frequencies for appropriate operation of high efficiency PAs (HEPAs).

# 3.2 Harmonically-Tuned Reconfigurable Class F<sup>-1</sup> Power Amplifier

### 3.2.1 Theory and Design of Tunable Matching Network

The design of HEPAs requires proper fundamental and harmonic terminations in order to obtain appropriate current and voltage waveforms. This design targets the design of a reconfigurable MN that should enable fundamental and harmonic tuning as well as maximizing the tuning range (Figure 3-1).

The proposed fundamental/harmonically tunable MN is composed of two main blocks, second and third harmonic tuning, and fundamental matching blocks. First, the desired values for harmonic impedances are set by adjusting the capacitance value. Then, the fundamental impedance is matched in two steps to maximize the tuning range. The load impedance is first set to a certain predetermined impedance region in the Smith Chart using a pi-matching pre-matching network with two variable capacitors and a transmission line (TL). Then, a TL loaded with four variable capacitors is used to obtain the final value of desired impedance.

Figure 3-1, Proposed Design For the Harmonically-Tuned Matching Network

### 3.2.1.1 Harmonic Impedance Tuning

HEPAs require optimum harmonic impedance to be either open or short circuited. This fact leads to the design of two-state matching which makes the impedance short or open. Practically speaking, packaging the transistor can change the overall phase of the required impedances. Consequently, the complete harmonic MN should reflect the harmonic impedance and have a unity reflection coefficient with tunable phase shift.

The basic idea is to achieve tunable pure imaginary input impedance in a shunt TL terminated with a variable capacitor. Choosing the appropriate characteristic impedance  $Z_0$ , and the electrical length  $\theta$ , for the shunt TL should achieve the desired tuning in the input impedance for a given varactor tuning range. For a 2.5 GHz design, two parallel stubs were used to achieve an extra degree of freedom in the design for wider tuning range at the edge of the Smith Chart. The susceptance of the parallel connection is as follows:

$$B_{in} = \frac{Z_{01} + X_{ch1}\alpha_1}{Z_{01}X_{ch1} + Z_{01}^2\alpha_1} + \frac{Z_{02} + X_{ch2}\alpha_2}{Z_{02}X_{ch2} + Z_{02}^2\alpha_2}$$

(3-1)

where  $\alpha_n = tan (2\theta_n)$  is the second harmonic and  $\alpha_n = tan (3\theta_n)$  is the third harmonic.

In this design, the varactor value was chosen arbitrarily to vary from 0.5 pF to 1.5 pF. Thus, the impedance spans for  $X_{ch1}$  and  $X_{ch2}$  are from 21 to 63  $\Omega$  at 5 GHz and from 14 to 42  $\Omega$  at 7.5 GHz. In order to maximize the coverage of the Smith Chart outer circle, the variance of  $B_{in}$  given by (3-1) needed to be maximized at both the second and third harmonic frequencies simultaneously. The optimum values obtained for this objective were 20 and 25  $\Omega$  for  $Z_{01}$  and  $Z_{02}$ , while the electrical lengths of the two stubs were set to 10 and 105° respectively.

To extend the harmonic tuning to the point of being frequency agile, three parallel stubs were used instead. The corresponding optimum values of  $Z_{01}$ ,  $Z_{02}$ , and  $Z_{03}$ , were set to be 55, 30 and 25  $\Omega$  and the electrical length of the three stubs was set to 15, 125 and 20° respectively at 1.9 GHz.

The first estimate of the TL's optimal parameters was obtained by a MATLAB<sup>®</sup> code which maximized the variance of  $B_{in}$ , while the exact values were finalized using the tuning feature in Agilent ADS<sup>®</sup>.

### 3.2.1.2 Fundamental Impedance Matching

In order to extend the fundamental impedance tuning range inside Smith Chart coverage, the pre-matching concept was used. A C-L-C pi-network was selected for this purpose. Low Q-factor inductors were avoided by replacing them with an equivalent TL. In (3-2) and (3-3)  $b_{pre1}$ ,  $b_{pre2}$  and x designate the susceptance of the capacitance and the reactance of the inductor. The equations to design the circuit to achieve the desired input admittance,  $y_{in}$ , in Figure 4-1, are given by

$$\sqrt{\frac{1+b_{h1}^{2}-g_{in}}{g_{in}}} = xb_{h1}^{2}-b_{h1}+x$$

(3-2)

$$b_{h2} = b_{in} + \frac{(1+b_{h1}^{2})(xb_{h1}^{2}-b_{h1}+x)}{1+(xb_{h1}^{2}-b_{h1}+x)}$$

(3-3)

The value of x was chosen to be 0.5. Six different sets of  $(b_{prel}, b_{pre2})$ , called 'states', were chosen to divide the Smith Chart into 6 pre-determined regions (Figure 3-2). The values of  $(b_{prel}, b_{pre2})$  of the 6 states depend on the targeted frequency. Table 3-1 presents the calculated values for the pre-matching capacitors and the corresponding average reflection coefficient for each state for the 2.5 GHz design.

For the frequency agile design, the impedance values were calculated at 1.9 GHz. The only modification was found to be varying the value of  $C_{pre2}$  for 'State 1' only to select the operating frequency and covering 'State 1' for every frequency. For 1.8, 1.9, and 2.1 GHz, the optimal  $C_{pre2}$  was 7.5, 6.5, and 4.5 pF respectively, whereas for 2.4, and 2.7 GHz,  $C_{pre2}$  is 3.5 pF.

|         | $C_{pre2}$ (pF) | $C_{pre1}$ (pF) | Reflection Coefficient $(\Gamma)$ |  |

|---------|-----------------|-----------------|-----------------------------------|--|

| State 1 | 6.5             | 3.5             | (0.5,10°)                         |  |

| State 2 | 1.75            | 1.25            | (0.5,190°)                        |  |

| State 3 | 4               | 0.5             | (0.8,10°)                         |  |

| State 4 | 10              | 3               | (0.8,190°)                        |  |

| State 5 | 16              | 4               | (0.95,-60°)                       |  |

| State 6 | 16              | 2               | (0.95,120°)                       |  |

Table 3-1, 2.5 GHz Design Pre-matching Capacitor Values for Different States

Figure 3-2, Smith Chart Regions Covered by Each State

For the remaining part of the fundamental MN, we used a capacitively loaded TL with a total of four varactors that varied from 0.5 to 1.5 pF. The lengths of the TL sections between the shunt varactors were optimized using tuning in Agilent ADS®.

It is worth mentioning here that we avoided any tunable devices in the main signal line so as to not limit the power handling capabilities of networks to those of tunable devices. This assumption was strengthened by running a harmonic balance simulation for the final fundamental MN design in Agilent ADS® with an input power level of 40 dBm. The maximum power level at any shunt tunable element was found not to exceed 1.6 W which is within the safe power handling capabilities for the discrete matching components used. Consequently, the condition of the power handling capabilities for tunable devices has been highly relaxed and at the same time the total power handling of the whole network is no longer sensitive to that of the tunable devices.

### 3.2.2 Fabrication and Measurement Results

Both MN prototypes were fabricated using a microwave integrated circuit (MIC) process fabricated at the University of Waterloo in the Centre for Integrated RF Engineering (CIRFE) lab with via-holes [74]. The substrate used was alumina substrate with 25 mils thickness, relative permittivity of 9.8, and loss tangent of 0.001 at 1 MHz. The conductor layer was a 4  $\mu$ m electroplated Au layer on top of a 50nm/0.1  $\mu$ m evaporated Cr/Au seed layer. The sputtered gold was found to be sufficient to plate the via-holes with Au. Figure 3-3 presents the complete fabricated circuits using both Radant MEMS® SP4T switches and Skyworks® semiconductor varactors.

Figure 3-3, Fabricated (a) Varactor-Based Frequency Agile, (b) MEMS-based 2.5 GHz Matching Network

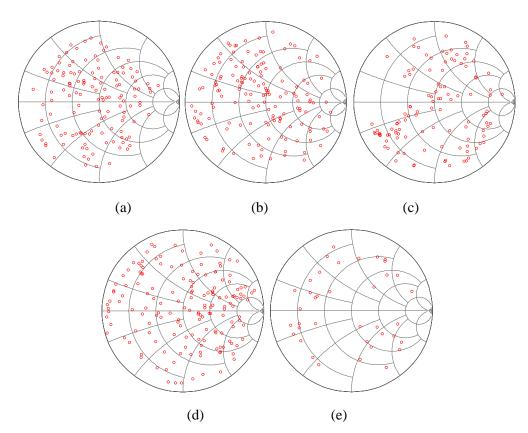

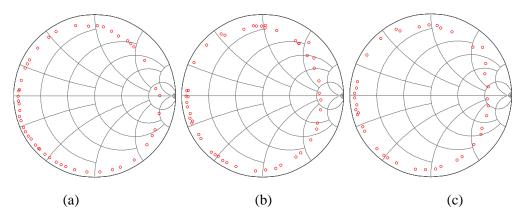

For the MEMS-based design, excellent impedance coverage was achieved at the fundamental frequency (Figure 3-4). It allowed for a maximum  $|\Gamma|$  of 0.834 with corresponding insertion loss of less than 1.213 dB (Figure 3-5). Moreover, almost all the rim of the Smith Chart was covered at the second and third harmonics (Figure 3-6) except for the impedance near the open circuit where fundamental matching part affected the performance. Similar results were obtained for the varactor- based design (Figure 3-6, and Figure 3-7) with satisfactory coverage for all targeted frequencies except 2.7 GHz as it was far away from the design frequency, 1.9 GHz. The maximum covered reflection coefficient was higher than 0.85 except at 2.7 GHz. The measured insertion loss did not exceed 1.4 dB at the highest covered  $|\Gamma|$  (Figure 3-8).

**Figure 3-4**, Selected Measured Impedance States to Prove Coverage for 2.5 GHz Design; (a) Fundamental 2.5 GHz, (b) Second Harmonic 5 GHz, (c) Third Harmonic 7.5 GHz

Figure 3-5, Measured IL =-1.213 dB for 2.5 GHz Design at Maximum  $|\Gamma|$  of 0.834

**Figure 3-6**, Selected Measured Impedance States to Prove Fundamental Impedance Coverage for Frequency Agile Design; (a) 1.8 GHz, (b) 1.9 GHz, (c) 2.1 GHz, (d) 2.4 GHz, and (e) 2.7 GHz

**Figure 3-7**, Examples for Measured Harmonic Tuning for Frequency Agile Design; (a) 3.8 GHz, (b) 4.8 GHz, and (c) 5.4 GHz

**Figure 3-8**, Measured Insertion Loss of (a) -1.121 dB at  $|\Gamma|$  of 0.862 for 1.8 GHz, (b) -1.313 dB at  $|\Gamma|$  of 0.868 for 1.9 GHz, (c) -1.38 dB at  $|\Gamma|$  of 0.853 for 2.1 GHz, and (d) -1.328 dB at  $|\Gamma|$  of 0.876 for 2.4 GHz

## 3.2.3 Load Modulated Varactor-Based Frequency Agile Class F<sup>-1</sup> HEPA

The first step towards a harmonically-tuned tunable PA was using the fabricated varactor-based MN as an output MN for the PA with a fixed input MN operating at 2.4 GHz, for proof of concept purposes. For the fabricated PA, at 6 dB back-off, the drain efficiency was improved by

18% compared with what was obtained using a static MN optimized only at the peak input power level. The varactor-based frequency agile MN is subsequently used for the source and load modulation of a class  $F^{-1}$  HEPA. Two tunable MN were fabricated for source and load impedance tuning. The active device used was the 10 W GaN device from Cree<sup>®</sup>, CGH40010F. Figure 3-9 shows a photo of the fabricated reconfigurable class  $F^{-1}$  PA for efficiency enhancement. The PA was measured by manual tuning of the fundamental and harmonic impedances of the MN simultaneously at every input power level at the operating frequencies.

Table 3-2 summarizes the obtained drain efficiency, and the efficiency enhancement at various frequencies. Moreover, Figure 3-10 shows efficiency curves vs. input power levels.

Figure 3-9, Fabricated Harmonically-Tuned Reconfigurable Power Amplifier

| Table 3-2, Peak Efficiency and Efficiency Enhancement for the Harmonically-Tuned |

|----------------------------------------------------------------------------------|

| Reconfigurable Power Amplifier at Different Frequencies                          |

| Frequency of<br>Operation | Drain Efficiency at<br>Peak Input Power (%) | Efficiency          | Efficiency           |

|---------------------------|---------------------------------------------|---------------------|----------------------|

|                           |                                             | Enhancement at 6 dB | Enhancement at 10 dB |

|                           |                                             | back-off (%)        | back-off (%)         |

| 1.8 GHz                   | 70.55                                       | 12.73               | 6.1                  |

| 1.9 GHz                   | 68.72                                       | 12.29               | 7.71                 |

| 2.1 GHz                   | 65.21                                       | 10.23               | 5.145                |

| 2.4 GHz                   | 72.05                                       | 14.97               | 10.18                |

| 2.7 GHz                   | 63.54                                       | 8.03                | 4                    |

Figure 3-10, Efficiency vs. Input Power at (a) 1.8 GHz with 12.73% Enhancement at 6 dB Backoff, (b) 1.9 GHz with 12.29% Enhancement at 6 dB Back-off, (c) 2.1 GHz with 10.23%

Enhancement at 6 dB Back-off, (d) 2.4 GHz with 14.97% Enhancement at 6 dB Back-off, and (e) 2.7 GHz with 8.3% Enhancement at 6 dB Back-off

# **Chapter 4**

# Reconfigurable Doherty Power Amplifiers for Multi-Band Multi-Mode Base Stations

### 4.1 Introduction

In this chapter, a complete systematic procedure for the design of high efficiency Doherty power amplifiers (DPAs), able to efficiently amplify signals with different peak to average power ratios (PAPR) centered around diverse operating frequencies, is outlined. This procedure was applied to design three different demonstrators that operated under different conditions: three different frequency bands and a single PAPR value, three PAPR values centered around the same frequency, and three simultaneous centre frequencies and three PAPR values.

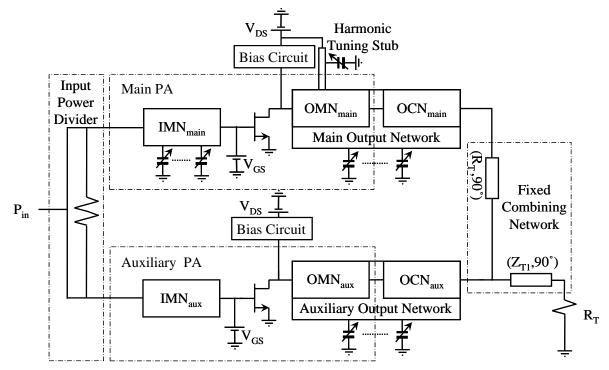

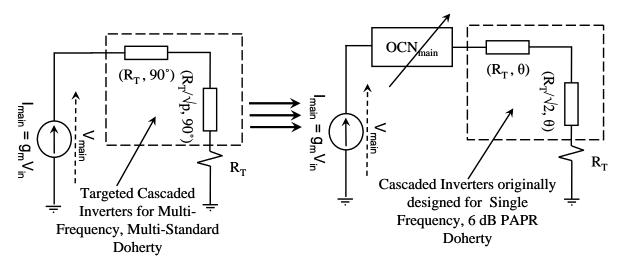

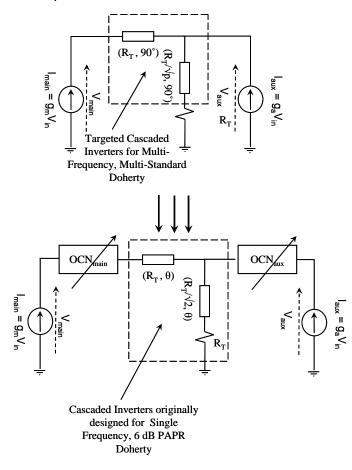

# 4.2 Novel Reconfigurable Multi-Standard Multi-Frequency Reconfigurable Doherty Power Amplifier

Following the analysis for the DPA in Chapter 2, eq. 2-4 shows the deviation of the main impedance profile, compulsory for proper load modulation, while changing the frequency ( $\theta$ ) and peak to average power ratio (PAPR; p). To mitigate the effects of the frequency and PAPR variation in a conventional Doherty amplifier, a new reconfigurable Doherty architecture is proposed. This new architecture includes two reconfigurable output compensation networks (OCN) that are added in the main and auxiliary paths of the Doherty architecture in addition to the reconfigurable input and output matching networks (IMN, OMN). The reconfigurable OCNs are carefully designed to:

- Eliminate the deviation of the impedance profiles from the ideal profiles implied by the frequency variation as shown before (Figure 2-11) and

- Adjust the impedance profiles as the value of *p* varies.

The reconfigurable IMN and OMN are designed to:

- Attain the optimal source and load impedances needed to be seen by the transistors at different drive levels and operating frequencies and

- Compensate for the transistors' parasitics at different operating conditions.

The design of the two compensation networks was conducted using the following procedure where a set closed form equations serves to make it systematic. These equations allow the determination of the ABCD parameters of the compensation networks given the values of the frequency (represented by  $\theta$ ), and the input signal PAPR (represented by p). It is worth

mentioning that the impedance inverters are kept unchanged vs. frequency and *p*.

### 4.2.1 Multi-Standard Multi-Frequency Doherty Power Amplifier Synthesis