# A Low Jitter Analog Circuit for Precisely Correcting Timing Skews in Time-Interleaved Analog-to-Digital Converters

by

## Adam Bray

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo Ontario, Canada, 2013

©Adam Bray 2013

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners

I understand that my thesis may be made electronically available to the public

#### Abstract

Time-interleaved analog-to-digital converters are an attractive architecture for achieving a high speed, high resolution ADC in a power efficient manner. However, due to process and manufacturing variations, timing skews occur between the sampling clocks of the sub ADCs within the TI-ADC. These timing skews compromise the spurious free dynamic range of the converter. In addition, jitter on the sampling clocks, degrades the signal-to-noise ratio of the TI-ADC. Therefore, in order to maintain an acceptable spurious free dynamic range and signal-to-noise ratio, it is necessary to correct the timing skews while adding minimal jitter.

Two analog-based architectures for correcting timing skews were investigated, with one being selected for implementation. The selected architecture and additional test circuitry were designed and fabricated in a 0.18µm CMOS process and tested using a 125 MSPS 16-bit ADC. The circuit achieves a correction precision on the order of 10's of femtoseconds for timing skews as large as approximately 180 picoseconds, while adding less than 200 femtoseconds of rms jitter.

## Acknowledgements

There are a multitude of people I wish to thank for helping me get through this thesis and degree and I deeply apologize to anyone I miss. Professor David Nairn, thank you for everything you have done for me. From taking me as graduate student, having an endless supply of patience as I worked though my degree, teaching me every analog circuit's course at the university and how to think circuits, to our talks about education and the general craziness that is the world today. Thank you to Professor Ajoy Opal and Professor Vincent Gaudet for talking time out of their busy schedules to review this thesis and for attending my MASc. seminar.

To all the friends and colleagues I have made over my time at Waterloo, we have shared many good times together and I will remember them always. I wish you all the very best, a speedy completion of the battle that is graduate school and hope that we all keep in touch. Hassan, if I ever run into Barrie Gilbert, I will be sure to relay your fondness of his cell and try and get you an autograph.

Last and most importantly I want to thank my family and the person who is dearest to my heart and soul, DongNi Zhang. Mom, Dad, Amelia and Jason, thank you for all the support and encouragement you gave me throughout my degree. Also, for enduring the many times I was busy and couldn't be with you, love you all. Dad, I will miss you always and wish we could go out and celebrate. DongNi, if there is anyone who made this all possible it is you. You truly are the most special person I have ever met; the one and only gorgeous goddess angel. You give me a reason each day to wake up, be happy and better myself so that we can have the life we've always dreamed of. For these reasons and a million more, thank you for being the best part of my life and know I will forever and always be there for you my love, as you have been and are for me.

## Table of Contents

| List of Figu | ires                                               | xiii |

|--------------|----------------------------------------------------|------|

| List of Tab  | les                                                | xix  |

| 1 Introduc   | tion                                               | 1    |

| 1.1 Thesi    | s Outline                                          | 2    |

| 2 Time-Int   | terleaved Analog-to-Digital Converters             | 5    |

| 2.1 ADC      | Concepts                                           |      |

| 2.1.1        | Sampling Rate, Aliasing and Analog Input Bandwidth | 7    |

| 2.1.2        | Resolution and Quantization Noise                  |      |

| 2.1.3        | Signal-to-Noise Ratio                              | 10   |

| 2.1.4        | Spurious Free Dynamic Range                        |      |

| 2.2 TI-AI    | DC Concepts                                        | 13   |

| 2.2.1        | Mismatches                                         | 15   |

| 2.3 Timir    | ng Skews                                           | 17   |

| 2.3.1        | Analysis                                           | 19   |

| 2.3.2        | Timing Skew Requirements                           |      |

|   | 2.4 | Jitter. |                                                            |    |

|---|-----|---------|------------------------------------------------------------|----|

|   |     | 2.4.1   | Jitter Requirements                                        |    |

|   | 2.5 | Summ    | nary                                                       |    |

| 3 | Ana | alog T  | Techniques to Correct Timing Skews                         | 37 |

|   | 3.1 | Analo   | g vs. Digital Correction                                   |    |

|   | 3.2 | Circui  | t Techniques                                               | 40 |

|   |     | 3.2.1   | Analysis                                                   | 42 |

|   |     | 3.2.2   | Comparison                                                 |    |

|   | 3.3 | Circui  | t Architectures                                            | 51 |

|   |     | 3.3.1   | Single Differential Buffer with Variable Capacitor Load    | 53 |

|   |     | 3.3.2   | <i>P</i> Fixed Delay Buffers and One Variable Delay Buffer | 54 |

|   |     | 3.3.3   | Comparison                                                 | 56 |

|   | 3.4 | Implei  | mentation and Testing Architecture                         | 58 |

|   | 3.5 | Summ    | nary                                                       | 63 |

| 4 | Des | sign o  | f an Analog Timing Skew Correction Circuit                 | 65 |

|   | 4.1 | Variat  | ble Delay Differential Buffer                              | 66 |

|   |     | 4.1.1   | Common-Mode and Output Swing                               | 67 |

|   |     | 4.1.2   | Output Noise and Jitter                                    | 69 |

|   |     | 4.1.3   | Gain and Bandwidth                                         |    |

|   |     | 4.1.4   | Bias                                                       |    |

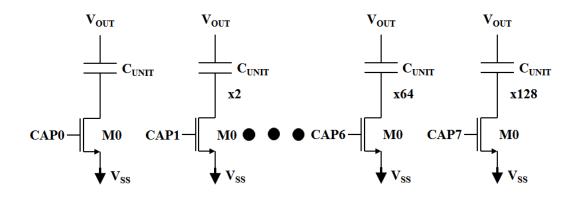

|   |     | 4.1.5  | Variable Capacitor Load                      | 75  |

|---|-----|--------|----------------------------------------------|-----|

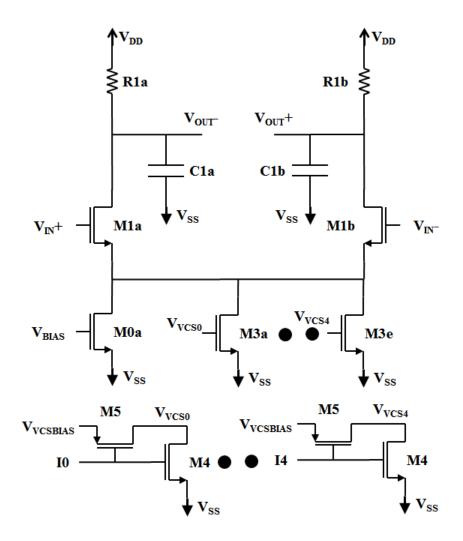

|   |     | 4.1.6  | Variable Current Source                      | 77  |

|   |     | 4.1.7  | Final Circuit and Simulation Results         | 79  |

|   | 4.2 | Differ | ential NAND                                  | 85  |

|   |     | 4.2.1  | Final Circuit and Simulation Results         | 89  |

|   | 4.3 | Differ | ential D-Flip Flop                           |     |

|   | 4.4 | Comp   | lete Test Circuit                            |     |

|   |     | 4.4.1  | Layout and Fabrication                       | 103 |

| 5 | Tes | ting I | Details and Measurement Results              | 107 |

|   | 5.1 | Test B | Board Design                                 | 108 |

|   | 5.2 | Test B | Sench Setup and Procedures                   | 110 |

|   |     | 5.2.1  | Chip Staging and DC Measurement Details      | 112 |

|   |     | 5.2.2  | Transient Measurement Details                | 114 |

|   |     | 5.2.3  | Timing Skew Precision and Range Measurements | 115 |

|   |     | 5.2.4  | Additive Jitter Measurement Details          | 118 |

|   | 5.3 | Measu  | red Results                                  | 121 |

|   |     | 5.3.1  | Chip Staging and DC Measurements             | 121 |

|   |     | 5.3.2  | Transient Measurements                       | 124 |

|   |     | 5.3.3  | Timing Skew Precision and Range Measurements | 126 |

|   |     | 5.3.4  | Additive Jitter Measurements                 | 139 |

|   | 5.4 | Impro  | vements and Future Considerations            | 140 |

| 6 Conclusions and Future Work | 143 |

|-------------------------------|-----|

| Appendices                    | 145 |

| Appendix A                    | 145 |

| Appendix B                    | 150 |

| References                    | 159 |

## List of Figures

| Figure 2.1 : Ideal FFT Illustrating Aliasing and Analog Input Bandwidth                                              |

|----------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 : FFT Plot Illustrating Various SNR Calculations for a<br>FIN = 110.00442553 MHz and FSAMPLE = 125 MHz 11 |

| Figure 2.3 : SFDR as Defined by Two Different Spur Magnitudes 13                                                     |

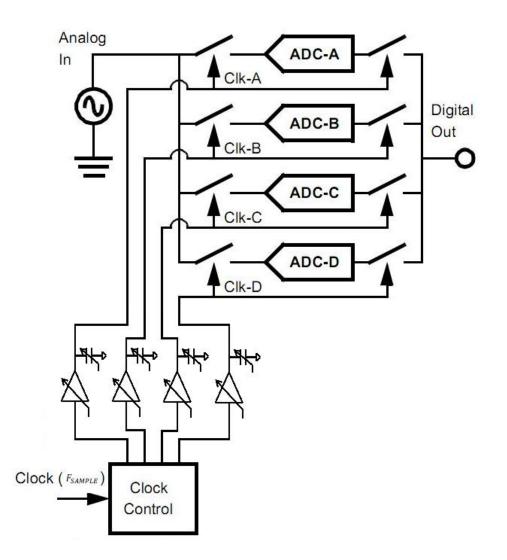

| Figure 2.4 : 4-Way TI-ADC System with Clocking [1] 14                                                                |

| Figure 2.5 : Time-Domain Plot of an Ideal and Timing Skewed Sampled Sine<br>Waves                                    |

| Figure 2.6 : FFT Plot of a 2-way TI-ADC Subject to a 6 ps Timing Skew 25                                             |

| Figure 2.7 : Input Frequency vs. Timing Skew for Specific Resolutions                                                |

| Figure 2.8 : SFDR vs. Timing Skew for Specific Input Frequencies 29                                                  |

| Figure 2.9 : Sampling Clock Jitter's Effect on the Sample Analog Input [2] 31                                        |

| Figure 2.10 : Input Frequency vs. Jitter for Specific Resolutions                                                    |

| Figure 2.11 : SNR vs. Input Frequency for Various Amounts of Jitter                                                  |

| Figure 3.1 : Schematic a Differential Buffer/Inverter                                                                |

| Figure 3.2 : Single-Ended Model of a Differential Buffer/Inverter                                                    |

| Figure 3.3 : Simplified Noise Model of a Differential Buffer/Inverter                                                |

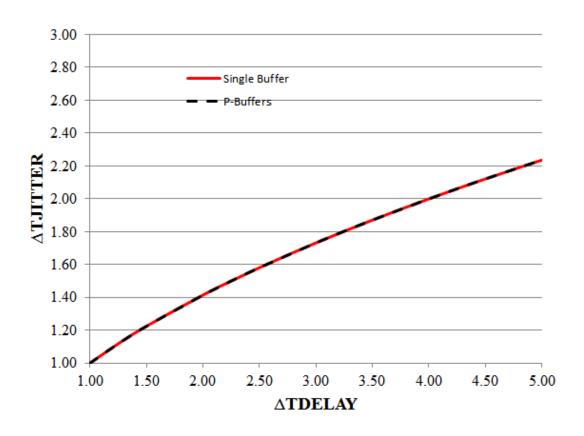

| Figure 3.4 : $\Delta T J ITTER$ vs. TDELAY Trade-off when Varying R, IBIAS and C. 50                                 |

| Figure 3.5 : Two Circuit Architectures for Correcting Timing Skews                        | 52 |

|-------------------------------------------------------------------------------------------|----|

| Figure 3.6 : $\Delta T J ITTER$ vs. TDELAY Trade-off for the Two Circuit Architectures    |    |

|                                                                                           | 56 |

| Figure 3.7 : A TI-ADC with the Proposed Timing Skew Correction Circuit                    | 59 |

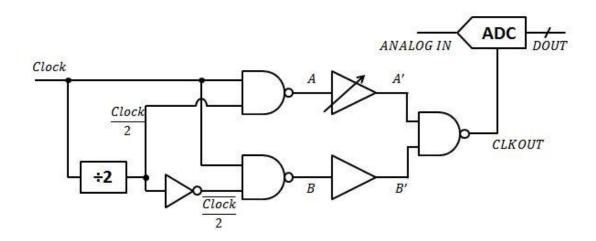

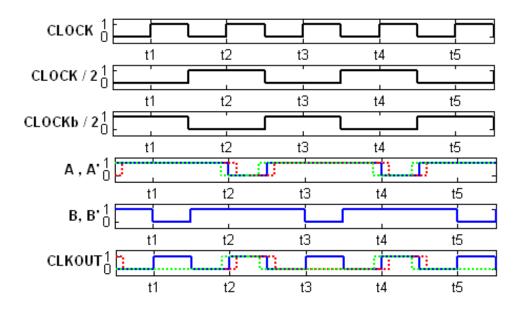

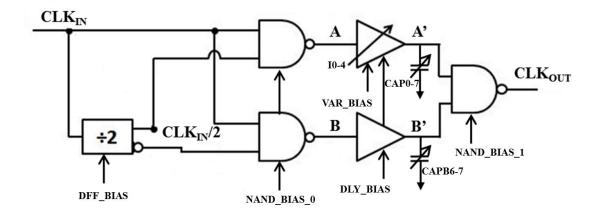

| Figure 3.8 : Schematic and Operation of the Proposed Test Architecture                    | 61 |

| Figure 4.1 : Schematic of the Variable Delay Differential Buffer                          | 66 |

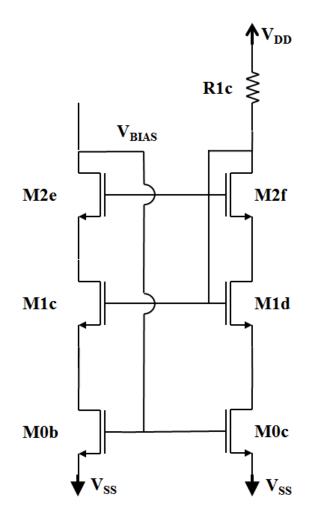

| Figure 4.2 : Replica Bias Circuit for the Variable Delay Differential Buffer              | 74 |

| Figure 4.3 : Final Variable Capacitor Load                                                | 76 |

| Figure 4.4 : Variable Current Source Added to The Variable Delay Differential             |    |

| Buffer                                                                                    | 78 |

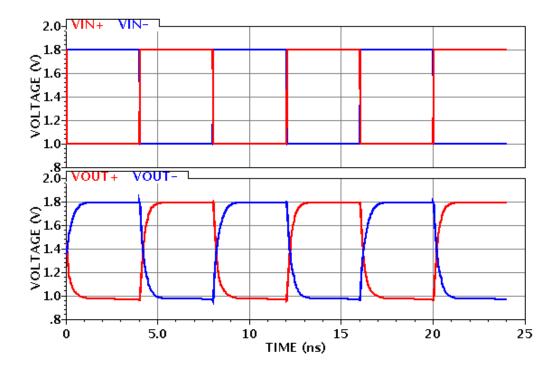

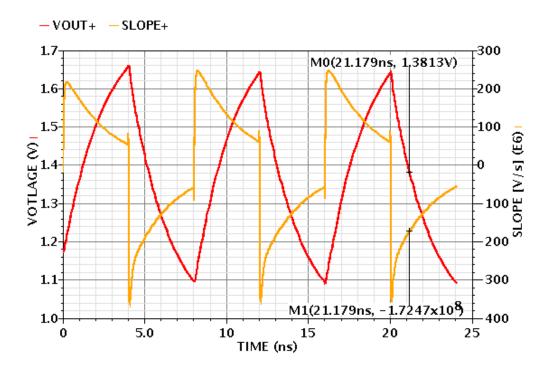

| Figure 4.5 : Simulated Transient Response of the Variable Delay Differential Buffer       | 82 |

| Durier                                                                                    | 02 |

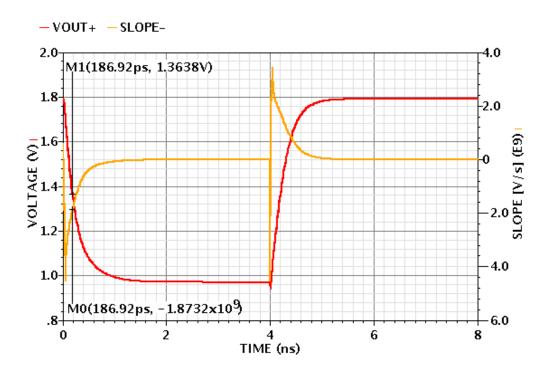

| Figure 4.6 : Simulated Slope of the Worst-Case Slew-Rate Edge for the Differential Buffer | 83 |

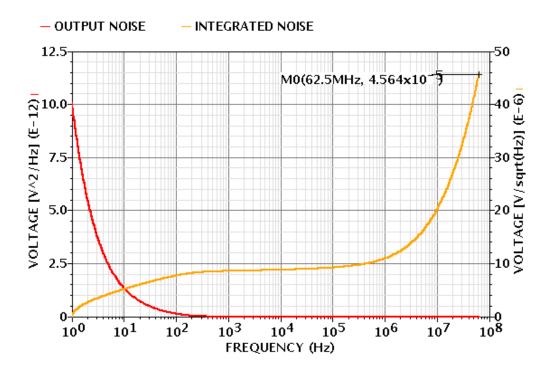

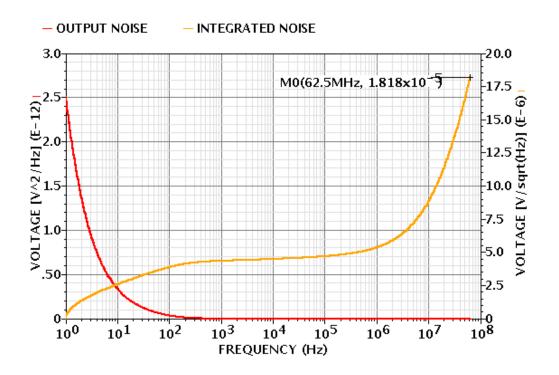

| Figure 4.7 : Simulated Total Output Noise for the Differential Buffer                     | 84 |

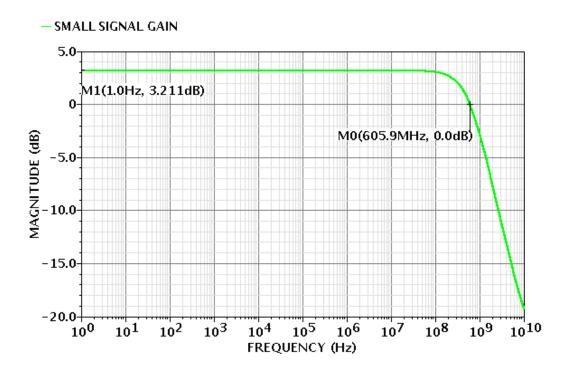

| Figure 4.8 : Simulated Gain and Bandwidth of the Differential Buffer                      | 85 |

| Figure 4.9 : Schematic of a CML NAND Gate [14]                                            | 86 |

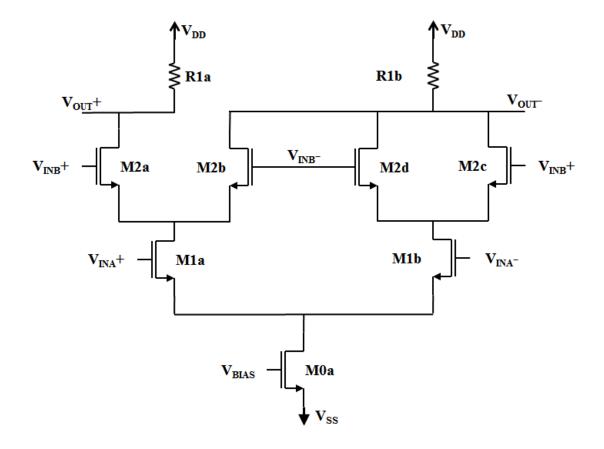

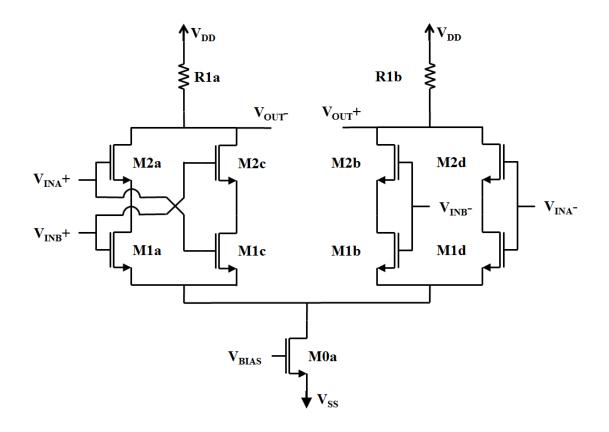

| Figure 4.10 : Schematic of the Proposed Differential NAND Circuit                         | 87 |

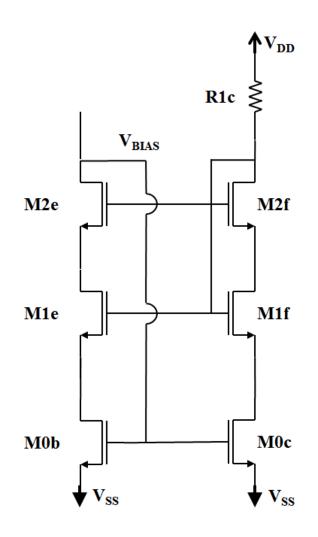

| Figure 4.11 : Schematic of the Differential NAND Replica Bias Circuit                     | 88 |

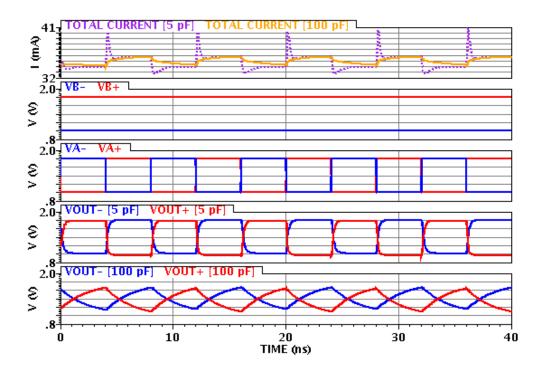

| Figure 4.12 : Simulated Transient Response of the Differential NAND                       | 91 |

| Figure 4.13 : Simluated Slope of the Worst-Case Slew-Rate Edge for the                    |    |

| Differential NAND with a 100 pF Load                                                      | 92 |

| Figure 4.14 : Simulated Total Output noise for the Differential NAND with a       |

|-----------------------------------------------------------------------------------|

| 100 pF Load                                                                       |

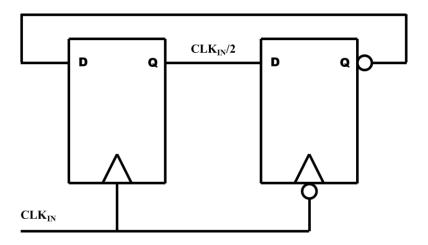

| Figure 4.15 : Schematic of the Differential DFF Using Two Latches                 |

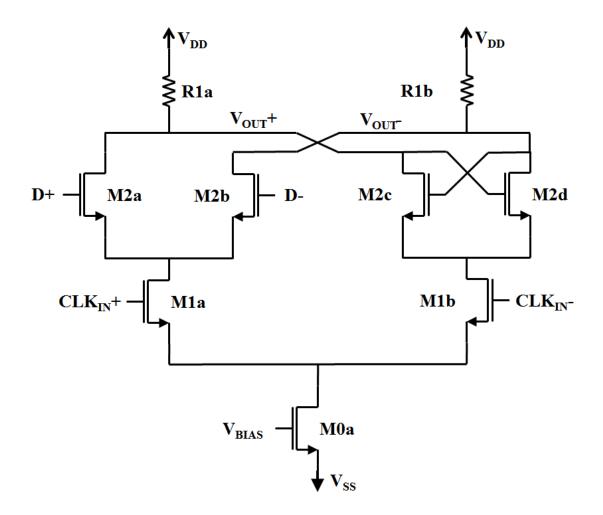

| Figure 4.16 : Schematic of a Differential Latch [14]96                            |

| Figure 4.17 : Schematic of the Replica Bias Circuit for the Differential Latch 98 |

| Figure 4.18 : Schematic of the Complete Test Circuit                              |

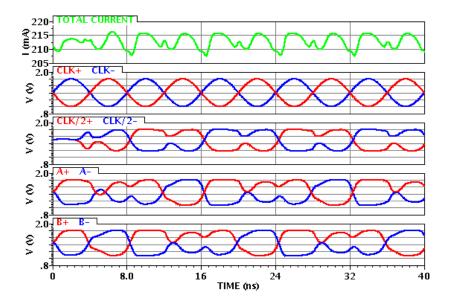

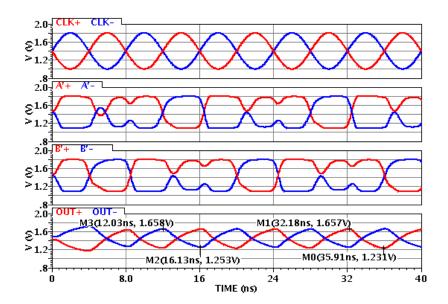

| Figure 4.19 : Simulated Transient Response of the Complete Test Circuit101        |

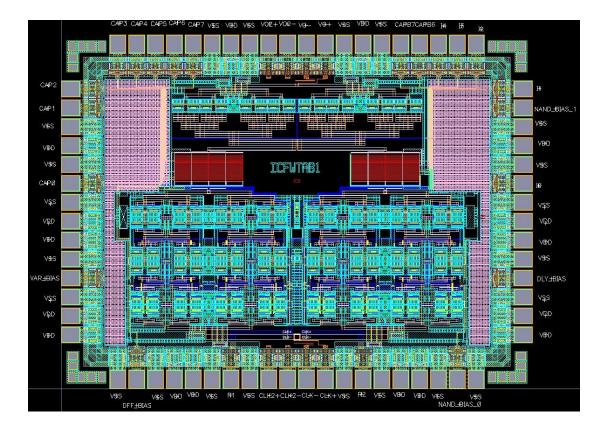

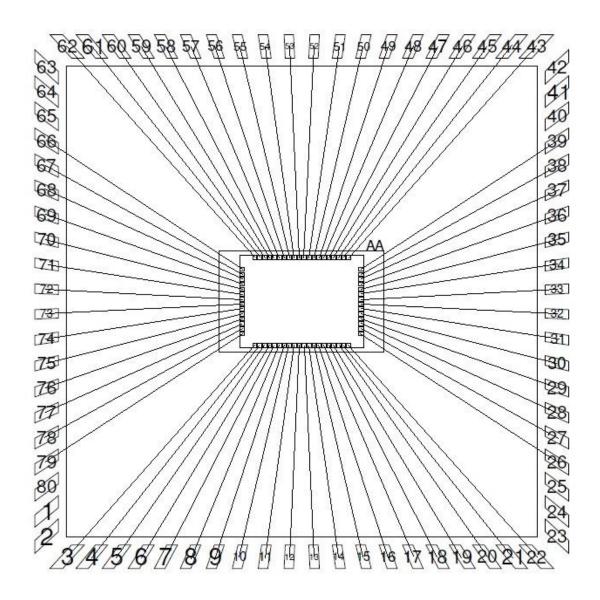

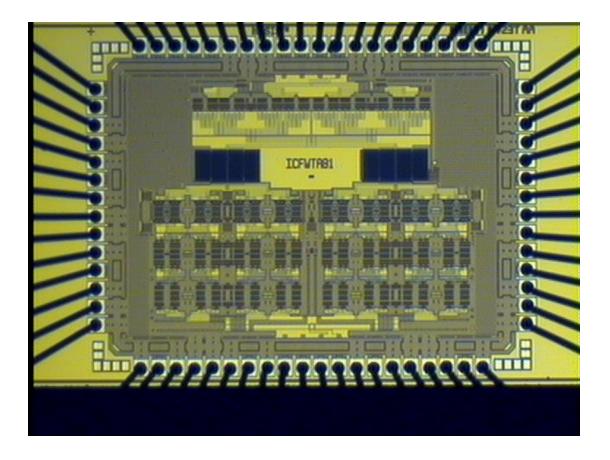

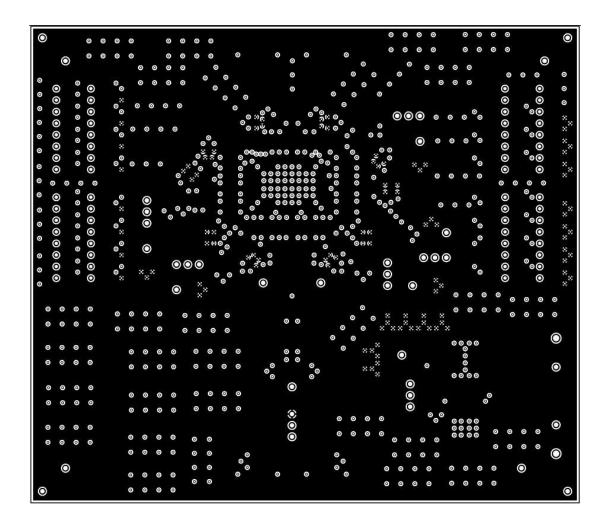

| Figure 4.20 : Final Layout of the Test Chip104                                    |

| Figure 4.21 : ICFWTAB1 Test Chip Bonding Diagram105                               |

| Figure 4.22 : ICFWTAB1 Test Chip Die Photograph106                                |

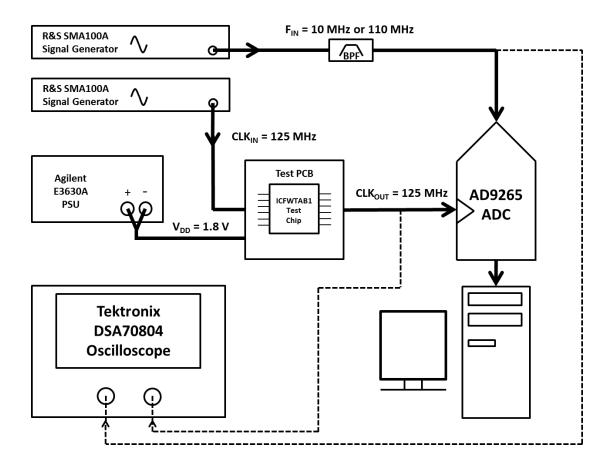

| Figure 5.1 : Test Bench Setup                                                     |

| Figure 5.2 : AD 9265 SNR vs. Input Frequency for Various Amounts of Jitter        |

|                                                                                   |

| [13]                                                                              |

|                                                                                   |

| [13]                                                                              |

| <ul><li>[13]</li></ul>                                                            |

| <ul> <li>[13]</li></ul>                                                           |

| <ul> <li>[13]</li></ul>                                                           |

| <ul> <li>[13]</li></ul>                                                           |

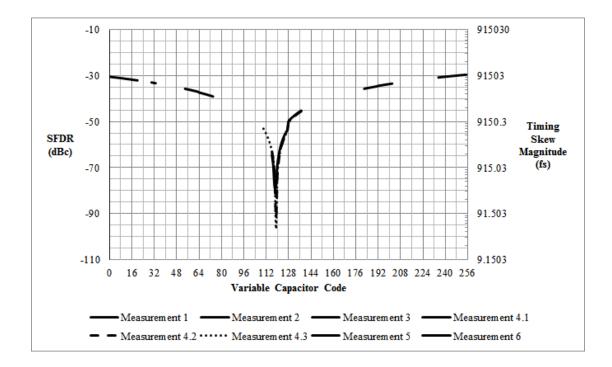

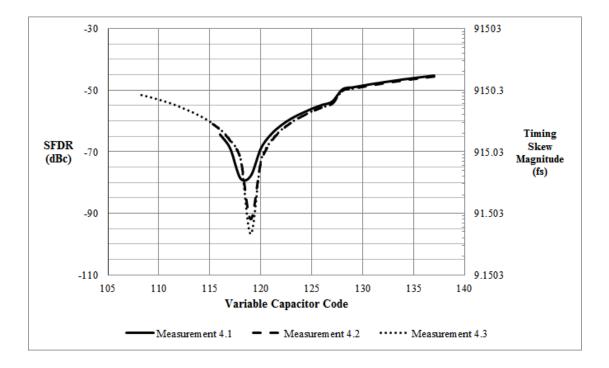

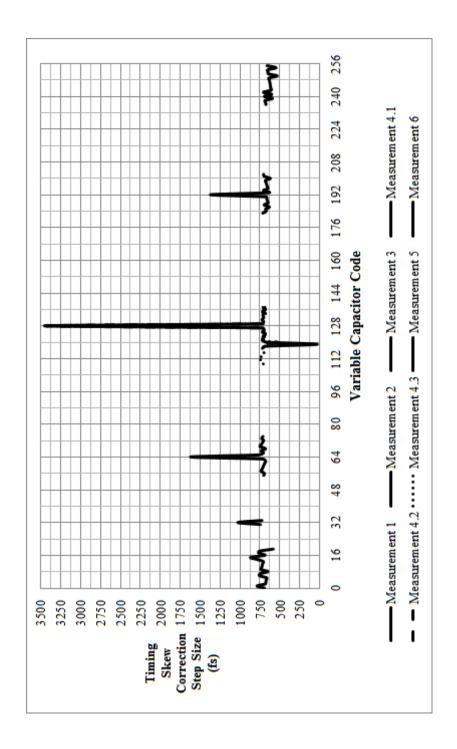

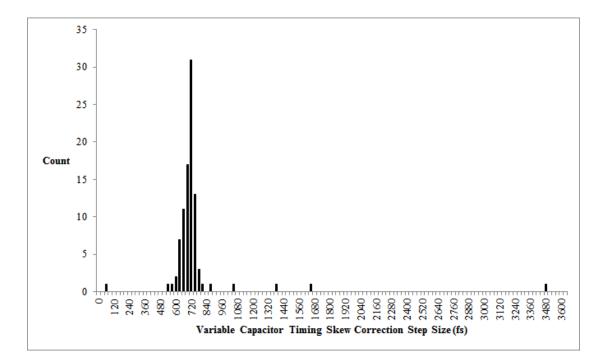

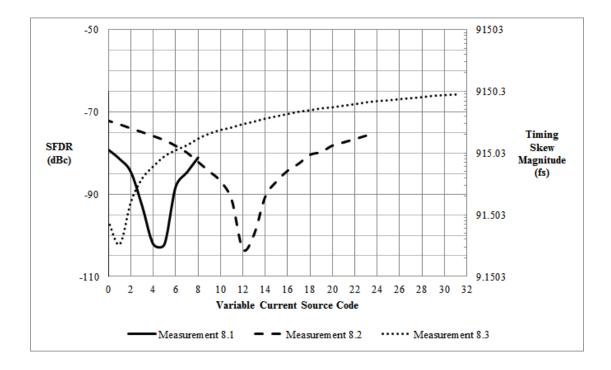

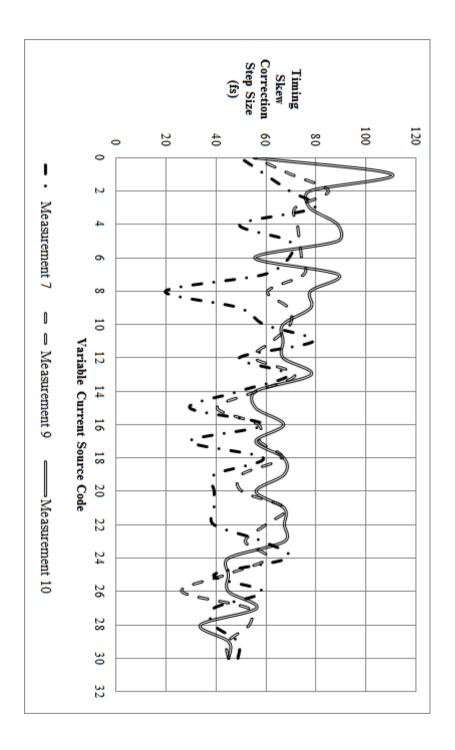

| Figure 5.9 : Variable Current Source Timing Skew Minimization Performance 131                                                  |

|--------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.10 : Variable Current Source Timing Skew Precision Over Current Source Codes                                          |

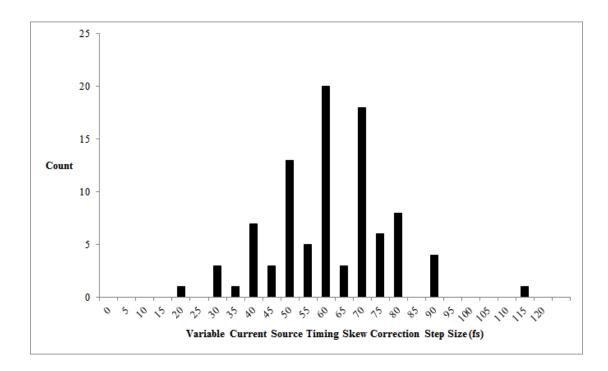

| Figure 5.11 : Distribution of Variable Current Source Timing Skew Correction<br>Precision                                      |

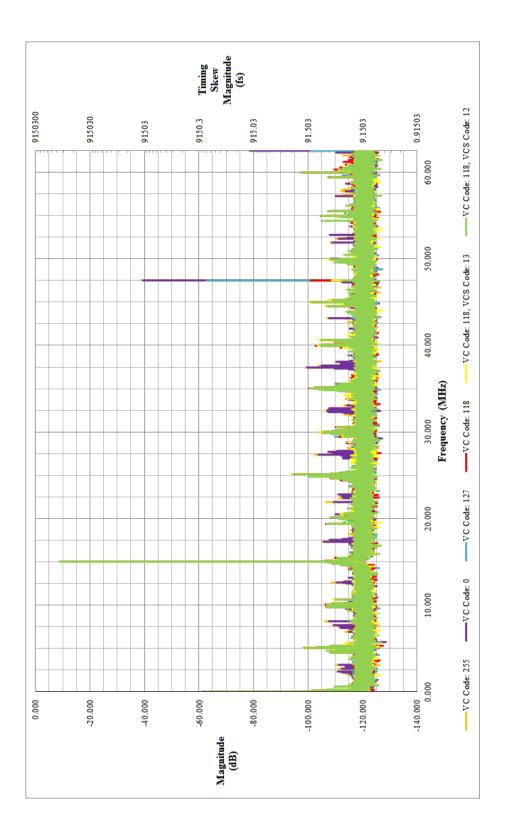

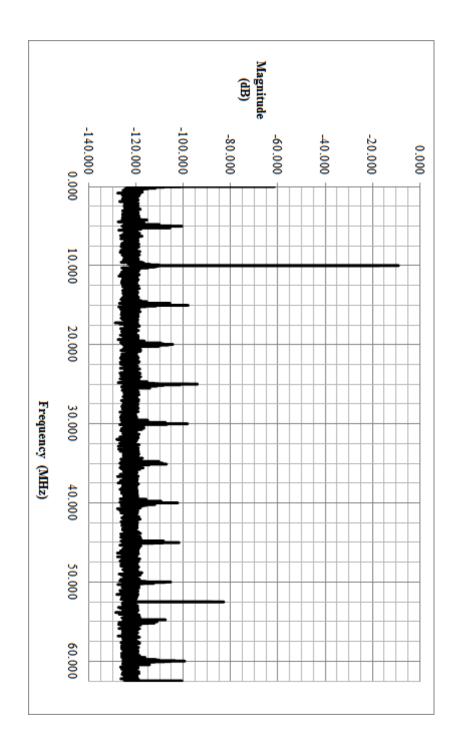

| Figure 5.12 : FFT Timing Skew Correction Range and Precision Performance.135                                                   |

| Figure 5.13 : Alternate Input Frequency FFT Performance for Variable Capacitor<br>Code 127                                     |

| Figure 5.14 : Alternate Input Frequency FFT Performance for the Variable<br>Capacitor Code 118                                 |

| Figure 5.15 : Alternate Input Frequency FFT Performance for Variable Capacitor<br>Code 118 and Variable Current Source Code 13 |

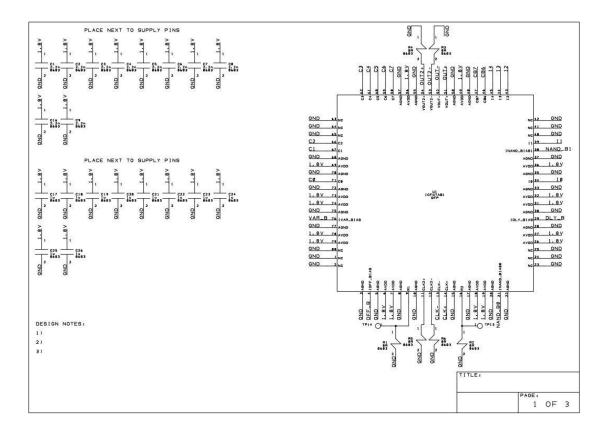

| Figure B.1 : Page 1 of the PCB Schematics Showing the Test Chip Connections                                                    |

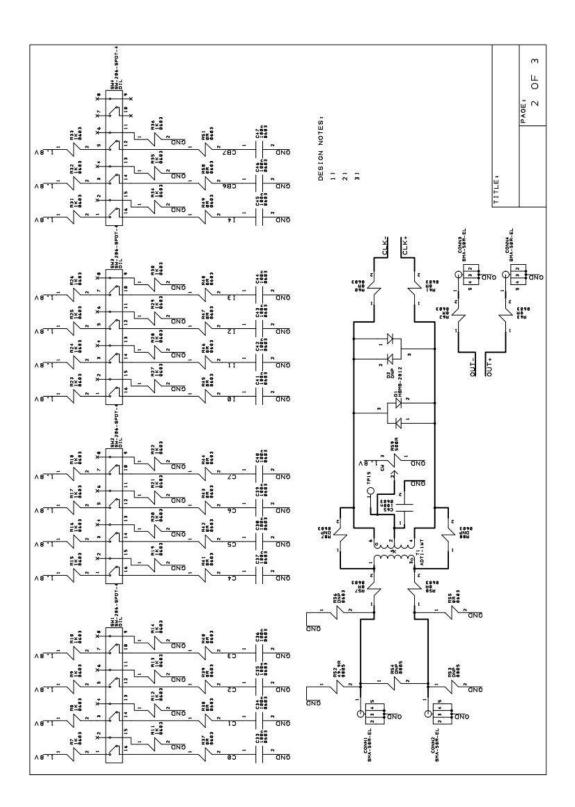

| Figure B.2 : Page 2 of the PCB Schematics Showing the I/O Connections151                                                       |

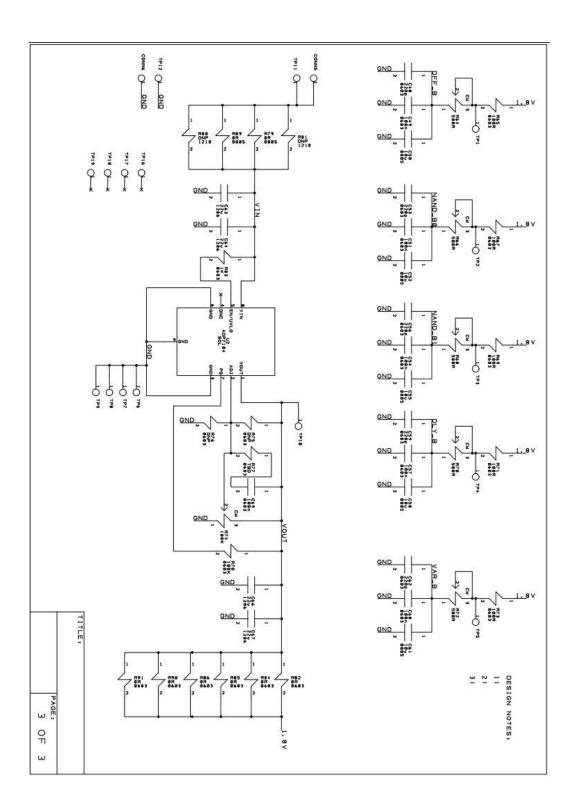

| Figure B.3 : Page 3 of the PCB Schematics Showing the Power and Bias Supplies                                                  |

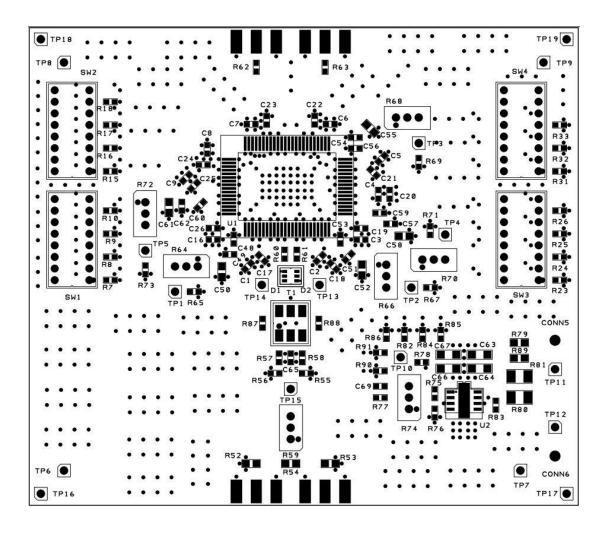

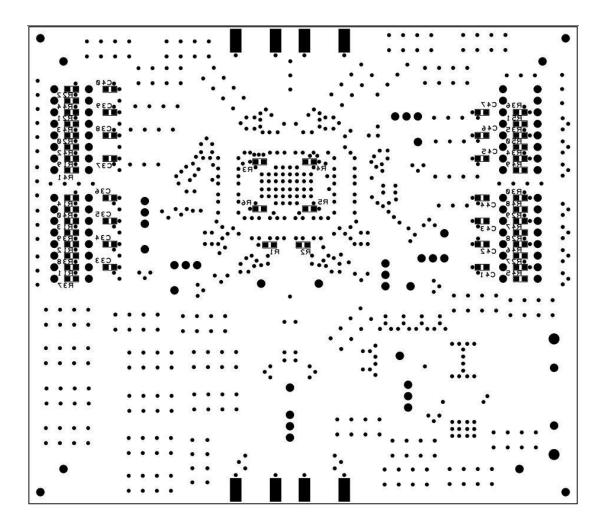

| Figure B.4 : Component Locations on Top Layer of the Test PCB153                                                               |

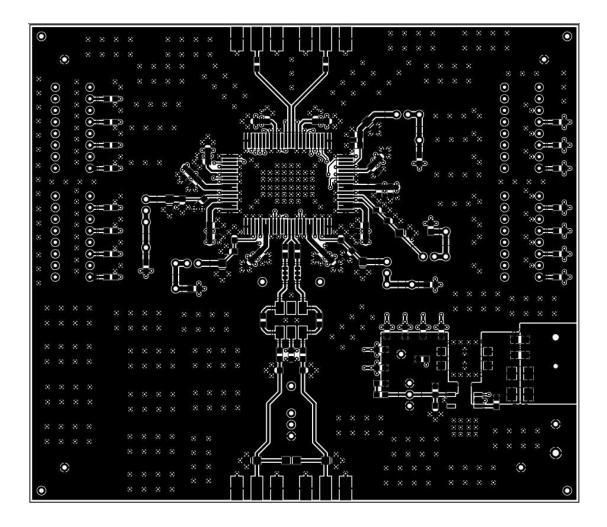

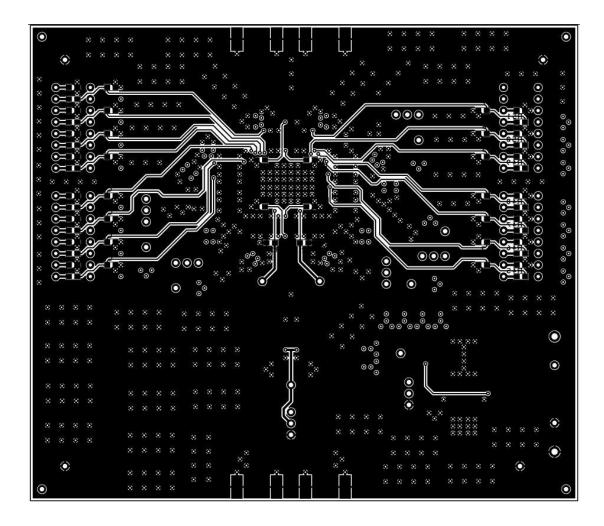

| Figure B.5 : Signal Routing on Top Layer of the Test PCB154                                                                    |

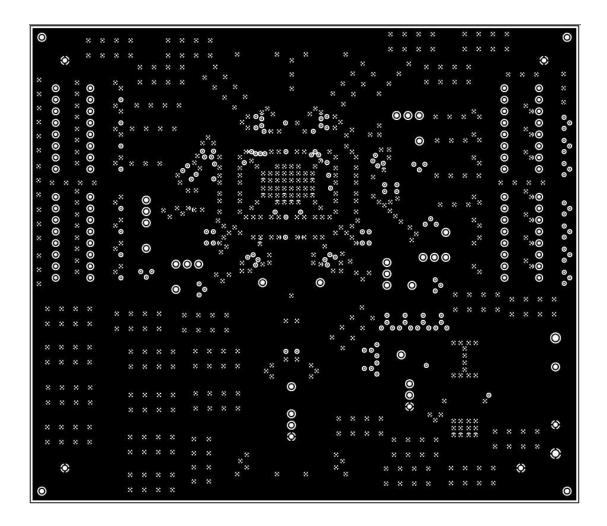

| Figure B.6 : Ground Plane (2 <sup>nd</sup> layer) of the Test PCB155                                                           |

| Figure B.7 : Power Plane (3 <sup>rd</sup> Layer) of the Test PCB156                                                            |

| Figure B.8 : Component Locations on Bottom Layer of the Test PCB157                                                            |

Figure B.9 : Signal Routing on Bottom Layer of the Test PCB ......158

## List of Tables

| Table 3.1 : Performance Comparison of Analog Domain and Digital Domain                                       |

|--------------------------------------------------------------------------------------------------------------|

| Timing Skew Correction                                                                                       |

| Table 3.2 : Effect of Varying <i>R</i> , <i>IBIAS</i> and <i>C</i> on <i>TDELAY</i> and $\Delta TJITTER$ 49  |

| Table 4.1 : Variable Current Source's Switch Currents    79                                                  |

| Table 4.2 : Final Device Sizes and Bias Currents for the Variable DelayDifferential Buffer                   |

| Table 4.3 : Final Device Sizes and Bias Currents for the Differential Buffer Bias         Circuitry       80 |

| Table 4.4 : Final Device Sizes and Bias Currents for the Unit Current Source 81                              |

| Table 4.5 : Final Device Sizes and Bias Current for the Variable Current SourceBias Circuitry                |

| Table 4.6 : Final Device Sizes and Bias Currents for the Differential NAND 89                                |

| Table 4.7 : Final Device Sizes and Bias Currents for the Differential NAND Bias      Circuit                 |

| Table 4.8 : Final Device Sizes and Bias Currents for the Differential Latch 97                               |

| Table 4.9 : Final Device Sizes and Bias Currents for the Differential Latch Bias      Circuit      97        |

| Table 5.1 : Test Signals Used for Timing Skew Measurements                                                   |

| Table 5.2 : Measurements for Characterizing the Timing Skew Correction Ability |

|--------------------------------------------------------------------------------|

|                                                                                |

| Table 5.3 : Initial Measured DC Bias Points of the Test Chip    121            |

| Table 5.4 : Comparison of Simulated and Measured Variable Current Source       |

| Currents                                                                       |

| Table 5.5 : Corrected DC Bias Point for the DFF123                             |

| Table 5.6 : SNR Measurements for Output Jitter Calculation                     |

| Table A.1 : Pin Mapping and Pin Description of the Test Chip and PCB145        |

## Chapter 1

## Introduction

Speed, magnitude and efficiency; for better or for worse, the world demands that the boundaries be pushed for how fast, how many and how efficiently things can be done. Within the realm of analog-to-digital converters (ADCs) this means pushing the boundaries to obtain: higher analog input bandwidths (to handle RF carrier frequencies), faster sample rates (to accommodate wider bandwidths), higher resolutions (to meet the linearity requirements of the advanced coding schemes) and an energy efficient architecture. One technique that is used to help ADCs achieve these requirements is time-interleaving [1].

The theory and operational details behind time interleaving and timeinterleaved analog-to-digital converters (TI-ADCs) is left to Chapter 2 to be discussed. For now the technique of time-interleaving can be viewed as paralleling multiple ADCs, not unlike the trend in microprocessors to use multiple cores to accomplish processing tasks. Like multi-core processors, the idea and necessity behind using TI-ADCs is that it is more energy efficient and practical (in terms of heat dissipation) to use multiple, slower, high resolution ADCs in parallel than to design a single very high speed, high resolution ADC [1]. However, implementing a TI-ADC such that it achieves all of the previously mentioned requirements is nontrivial.

One challenging aspect of implementing a TI-ADC is achieving the correct clock timing between each of the sub ADCs within the TI-ADC [1]. If there is a skew in the clock timing, here-in referred to as timing skew, of one or more of the interleaved ADCs then the resolution of the TI-ADC will be degraded in proportion to the magnitude of the skew relative to the other interleaved ADCs and the frequency of the input signal to the TI-ADC [1]. Correcting the timing skews requires adjustment of the clocks (analog domain) or the digital output data (digital domain) to an accuracy and precision on the order of femtoseconds or better [1]. In addition the method of correction is required to add as little jitter to the clock as possible in order to minimize the impact on the TI-ADC's noise performance [1]. This thesis presents an option to address the challenge and requirements of correcting timing skews in TI-ADCs. It details the design and implementation of a low jitter analog circuit/method which can correct timing skews to the femtosecond level.

## 1.1 Thesis Outline

This thesis is divided into 5 main chapters dealing with the background theory, potential architectures, design and implementation, measured results and the major conclusions. Chapter 2 presents relevant background concepts on ADCs and TI-ADCs as well as the pertinent performance specifications. In addition the theory on timing skews and their impact on the TI-ADCs performance specifications are presented as well as the performance impact of clock jitter on ADCs. Lastly, Chapter 2 concludes with a definition of the performance requirements for a timing skew correction system/circuit. Chapter 3 begins with a comparison of analog and digital methods of correcting timing skew. It then presents analog circuit techniques that can be used to adjust the timing skew of a clock. Chapter 3 then continues by

comparing two circuit architectures that can introduce timing skews and their relative performance in terms of jitter and precision. Lastly, Chapter 3 concludes with a recommendation for which circuit structure to implement and the necessary systemlevel architecture in order to test the structure's performance. Chapter 4 presents the design, layout and fabrication of the various circuits required to implement the system described in Chapter 3 in TSMC's 0.18µm CMOS. Chapter 5 discusses the implementation details of the fabricated chip, including the accompanying printed circuit board (PCB) design and test setup details. In addition the measured results of the fabricated chip are presented, with relevant comparisons to post-layout simulations. Finally, Chapter 6 presents the major conclusions within the thesis as well as future considerations and directions for this research.

## Chapter 2

# Time-Interleaved Analog-to-Digital Converters

As discussed in Chapter 1, time-interleaving is one technique that can be used to increase the sample rate of an ADC without requiring excessive power dissipation [1]. However, issues arise when designing TI-ADCs beyond those already present in the design of a typical ADC. The issue that this thesis focuses on is timing skews. In order to understand the impact and source of timing skews in a TI-ADC, it is useful to understand the concepts surrounding a TI-ADCs operation and the ADC performance metrics the timing skews affect. It is important to note that although the focus is on timing skews, other issues that can impact or limit the ability to measure or correct timing skews are covered as well.

This chapter begins with an overview of how the performance of an ADC is measured and a description of the fundamental performance metrics and limits that are useful when evaluating a TI-ADC's operation subject to timing skews. Next, the basic operation of a TI-ADC is shown along with an explanation of timing skews and other related issues that occur when the operation is non-ideal. The issue of timing skews is then expanded on with a mathematical analysis showing their impact and the degree to which timing skews need to be corrected. After this, the concept of jitter is presented, along with the desired limits to which jitter needs to be controlled. Lastly, a summary of the desired performance for a system to correct timing skews is discussed, setting two of the key design goals of this thesis.

## 2.1 ADC Concepts

The important ADC concepts, beyond those dealing with the operation of the ADC, have to do with understanding the performance specifications and the fundamental limits of an ADC. In most cases the performance specifications of an ADC are measured using a single-tone sinusoidal input, which can be represented as:

$$V_{IN} = \frac{V_{FS}}{2} \cos(2\pi F_{IN} t)$$

(2.1)

where  $V_{FS}$  is the full-scale input voltage and  $F_{IN}$  is the frequency of the sinusoidal tone. Note that within this thesis, unless otherwise noted, when there is an input to an ADC or TI-ADC it is assumed to be a single-tone represented by Equation (2.1). For evaluation purposes, the digital output of the ADC is converted to the frequency domain via a Fast Fourier Transform (FFT). The performance specifications can then be measured and/or calculated from the FFT plot. In short, the FFT converts a discretized (digital) signal of a specific length, *L*, into a magnitude versus frequency spectrum which contains L/2 discrete frequency bins, each spaced apart by  $F_{SAMPLE}/L$ , over a bandwidth of  $DC \rightarrow F_{SAMPLE}/2$ , where  $F_{SAMPLE}$  is the sampling frequency. One very important assumption buried within the FFT operation is that the discretized signal is sampled uniformly, meaning all the samples have exactly the same spacing in time between one another. Knowledge of this assumption is important when analyzing timing skews in TI-ADCs, as is shown in Section 2.3.

## 2.1.1 Sampling Rate, Aliasing and Analog Input Bandwidth

As previously mentioned,  $F_{SAMPLE}$  is the frequency the analog input signal to an ADC is sampled at. Alternatively, this frequency is commonly referred to as the sample rate of the ADC and is usually expressed as the number of samples per second (SPS). The sample rate sets the limit for the widest bandwidth,  $F_{BW}$ , the ADC can accurately convert, which is determined by the Nyquist rate as:

$$F_{BW} < \frac{F_{SAMPLE}}{2} \tag{2.2}$$

However, it is very important to note that this is not the limit for the highest frequency the ADC can convert, which is roughly determined by the ADC's analog input bandwidth [2].

Knowing that the FFT only recognizes frequencies between *DC* and  $F_{SAMPLE}/2$ , aliasing together with Nyquist zones describe how a frequency higher than  $F_{SAMPLE}/2$  is represented in an FFT plot. Aliasing is the phenomenon of a higher than Nyquist rate signal being reflected back to the ( $DC \rightarrow F_{SAMPLE}/2$ ) range or first Nyquist zone. A Nyquist zone is a region of width  $F_{SAMPLE}/2$ , whose zone number and frequency range is determined by [2]:

$$i^{th}Nyquist Zone = \frac{(i-1)F_{SAMPLE}}{2} \rightarrow \frac{iF_{SAMPLE}}{2}$$

(2.3)

$i = 1, 2, 3, \dots \infty$

The Nyquist zone in which the input frequency falls, determines the frequency of the reflected (aliased) signal,  $F_{ALIAS}$  and is given by:

Odd Nyquist Zone:

$$F_{ALIAS} = F_{IN} - \frac{(i-1)F_{SAMPLE}}{2}$$

(2.4)

$$i = 1, 3, 5, ... \propto$$

Even Nyquist Zone:

$$F_{ALIAS} = \frac{iF_{SAMPLE}}{2} - F_{IN}$$

$$i = 2, 4, 6, \dots \infty$$

(2.5)

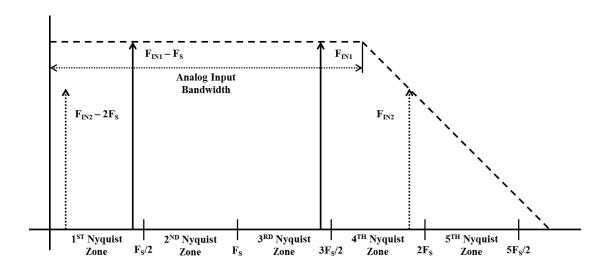

To illustrate how all of these concepts tie together, Figure 2.1 shows an ideal FFT plot over 5 Nyquist zones of two discrete signals and their aliases along with an overlay of a typical analog bandwidth profile. For simplicity, the images that also appear with aliasing are ignored.

Figure 2.1: Ideal FFT Illustrating Aliasing and Analog Input Bandwidth

#### 2.1.2 Resolution and Quantization Noise

The resolution of an ADC indicates the ideal number of distinct levels the analog input signal to the ADC can be discretized to. It is usually expressed in terms of the number of bits, N, that are required to represent the binary number of discrete levels,  $2^N$ . Due to the finite number of levels an ADC can represent, an error will typically exist between the actual sampled analog signal level and the discrete level the ADC uses to represent it. Provided certain conditions are met, this error is random and is commonly referred to as quantization noise. Mathematically the magnitude of the quantization noise can be expressed as [2]:

$$V_{QNOISE} = \frac{V_{FS}}{2^N \sqrt{12}} \tag{2.6}$$

where  $V_{QNOISE}$  is the root mean squared (rms) noise voltage due to quantization. Note that  $V_{QNOISE}$  is the total quantization noise and it is spread uniformly over the first Nyquist zone ( $DC \rightarrow F_{SAMPLE}/2$ ).

The value,  $V_{QNOISE}$ , is commonly used as a limit or level to which non-ideal behaviours in ADCs should be kept below and one that is used in later sections to set the desired degree to which to correct timing skews and limit jitter.

## 2.1.3 Signal-to-Noise Ratio

The signal-to-noise ratio (SNR) of an ADC is typically defined as the ratio between the input signal's rms amplitude and the rms value of the sum of all other frequencies within the first Nyquist zone, excluding harmonics of the input and DC [2]. If the only noise present in the ADC is due to the quantization noise given by (2.6) then the SNR is:

$$SNR = \frac{\frac{V_{FS}}{2\sqrt{2}}}{\frac{V_{FS}}{2^N\sqrt{12}}}$$

(2.7)

More commonly, Equation (2.7) is expressed in decibels (dB) as:

$$SNR = 6.02N + 1.76 \, dB$$

(2.8)

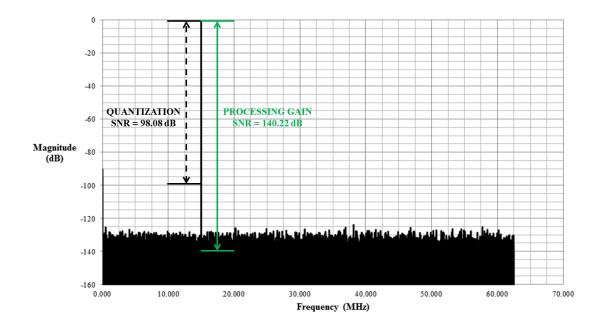

Note that this is the best possible SNR for an ADC and in reality, it is degraded by many additional noise sources, one of which, as is shown in Section 2.4, is jitter. However, when an FFT plot of the output of the ADC is produced, the apparent SNR is often much better than the level predicted by (2.8).

The FFT conversion process takes the total noise in the discretized input signal and divides it uniformly, assuming the noise is random, among the frequency bins in the first Nyquist zone. This spreading of the noise appears as a decrease in the SNR of the ADC (processing gain), where the improvement in the SNR, in dB, is given by [2]:

$$10\log_{10}\left(\frac{L}{2}\right) \tag{2.9}$$

Adding this to (2.8) gives the output SNR for an *N*-bit ADC, viewed by an *L* point FFT as:

$$SNR = 6.02N + 1.76 \, dB + 10 \log_{10} \left(\frac{L}{2}\right) \tag{2.10}$$

Figure 2.2 illustrates the different SNR's with an L = 32,768 point FFT plot of an N = 16 ADC with only quantization noise, sampling an input with a  $F_{IN} = 110 \ MHz^1$  at a rate  $F_{SAMPLE} = 125 \ MHz$ .

Figure 2.2: FFT Plot Illustrating Various SNR Calculations for a  $F_{IN} = 110 MHz$  and  $F_{SAMPLE} = 125 MHz$

<sup>&</sup>lt;sup>1</sup> The actual coherent frequency used is 110.00442553 MHz

### 2.1.4 Spurious Free Dynamic Range

A spurious tone is a distinct frequency that is generated from non-idealities within an ADC or TI-ADC as they sample a signal. Spurious tones (spurs) are almost always undesirable as they can interfere in trying to resolve the sampled input signal. An important performance specification for ADCs that measures how bad the worst spurious tone is in the ADC is the spurious free dynamic range (SFDR). It is usually defined as the ratio between the magnitude of the input sinusoid and the magnitude of the largest spurious tone  $V_{SPUR}$ , as seen on an FFT plot:

$$SFDR = \frac{|V_{IN}|}{|V_{SPUR}|} \tag{2.11}$$

In Section 2.3, it is shown that TI-ADCs subject to timing skews, give rise to spurious tones. For the purpose of this thesis, unless otherwise noted, SFDR is the ratio between the magnitude of the input and the magnitude of the timing skew spurious tone  $V_{\Delta SKEW}$ :

$$SFDR = \frac{|V_{IN}|}{|V_{\Delta TSKEW}|} \tag{2.12}$$

Figure 2.3 illustrates this definition of the SFDR for two different magnitudes of timing skew spurious tones.

Figure 2.3: SFDR as Defined by Two Different Spur Magnitudes

It is important to note that the SFDR provides a direct measurement for characterizing timing skews in TI-ADCs.

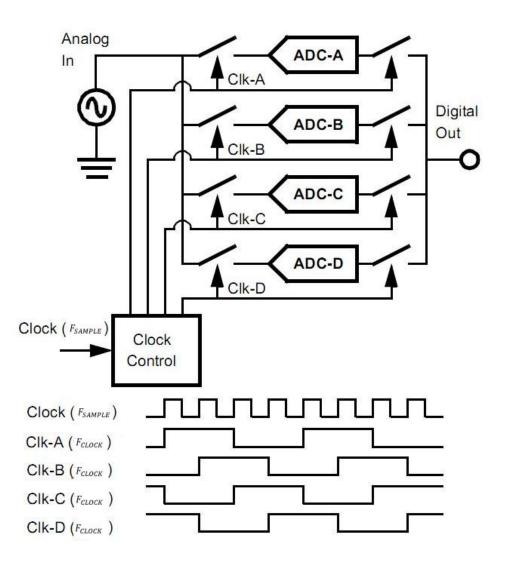

## 2.2 TI-ADC Concepts

A TI-ADC is composed of M sub ADCs whose inputs and outputs are clocked at a rate of  $F_{CLOCK}$  or  $1/T_{CLOCK}$ . Each of the sub ADCs clocks are precisely shifted relative to one another, such that only one of the sub ADCs at a time samples the input signal and outputs a digital code. The shifts for each of the clocks are derived from a master clock whose rate  $F_{SAMPLE}(1/T_{SAMPLE})$  is given by:

$$F_{SAMPLE} = MF_{CLOCK} \tag{2.13}$$

which sets the overall sample rate of the TI-ADC [1]. In other words, if an ADC with a sample rate of  $F_{CLOCK}$  is time-interleaved *M* times, the overall sample rate  $F_{SAMPLE}$ of the formed TI-ADC has increased by *M* times compared to the sub ADCs sample rate. An example of an M = 4 TI-ADC, with the corresponding clocking scheme, is shown in Figure 2.4.

Figure 2.4: 4-Way TI-ADC System with Clocking [1]

It should be noted that each of the digital codes output by the sub ADCs are combined to form the complete digital representation of the sampled signal.

Two important implementation details are assumed in the above theory. The first is that each of the sub ADCs has an analog input bandwidth equal to or greater than  $F_{SAMPLE}/2$  such that it can sample a Nyquist rate signal (i.e.  $DC \rightarrow F_{SAMPLE}/2$ ). The second assumption is that everything is ideal, as in each of the sub ADCs are identical and the clocks have perfect relative timing to one another such that they can sample a signal uniformly. In reality, things are non-ideal and mismatches occur between the sub ADCs and the timings of each of the clocks are skewed from their ideal positions.

#### 2.2.1 Mismatches

A mismatch in this thesis refers to the variation in a designed operating parameter between each of the sub ADCs within the TI-ADC. Mismatches in the offset, gain and clock timing (timing skews) are usually the most problematic for TI-ADCs, however bandwidth and linearity mismatches also pose problems [1]. A brief discussion of offset, gain and bandwidth mismatches is presented below. A detailed discussion of timing skews is left to Section 2.3.

Mismatches in the offsets between the sub ADCs of a TI-ADC spawn spurious tones. The frequencies of these tones  $F_{Vos}$  are given by [1]:

$$F_{Vos} = \frac{iF_{SAMPLE}}{M}$$

(2.14)

$i = 0, 1, ..., M - 1$

These offset induced tones can interfere with the spurious tones produced as a result of gain and timing skews. For example, as will be shown later, in a 4-way TI-ADC with  $F_{IN} = F_{SAMPLE}/4$ , the spurious tones due to offset, gain and timing skew mismatches all overlap. However, with careful selection of  $F_{IN}$ , the use of a 2-way TI-ADC or the correction and/or elimination of the possibility of the offset mismatches, the spurious tones induced only due to timing skews can be isolated.

Gain mismatches between each of the sub ADCs result in spurious tones whose frequencies  $F_{\Delta A}$  are given by [1]:

$$F_{\Delta A} = \frac{iF_{SAMPLE}}{M} \pm F_{IN}$$

$$i = 1, 2, \dots M - 1$$

$$(2.15)$$

Unfortunately, the frequencies of these tones are not exclusive to gain mismatches. It will be shown in the next section that timing skews also result in spurious tones whose frequencies are given by (2.15). When trying to characterize, measure and/or correct timing skews, all of which are of vital importance to this thesis, it is critical to have the ability to correct or eliminate the possibility of gain mismatches. This ensures that the observed spurious tones in the output of the TI-ADC under consideration are only due to the timing skews themselves and not the combination of gain and timing skew mismatches.

Finally, bandwidth mismatches between the sub ADCs result in both gain mismatches and timing skews producing spurious tones at frequencies given by (2.15). However, in the bandwidth mismatch case, the magnitude of the gain and timing skew tones depend non-linearly on the input frequency  $F_{IN}$  [3]. Once again, care must be taken to correct or remove the possibility of bandwidth mismatches if analysis of only timing skews in TI-ADCs is the goal. A testing architecture that does this is presented in Chapter 3.

### 2.3 Timing Skews

Clock timing mismatches or more commonly, timing skews, pose one of the biggest challenges for TI-ADCs. To explain what timing skews are, it is useful to refer back to the clocking diagram in Figure 2.4. Each of the clocks for the sub ADCs are shifted with respect to one other by exactly  $1/MF_{CLOCK}$ , such that the rising edge of each clock, the edge that an ADC samples on, does not overlap with any of the others. This allows only one sub ADC to sample at a time. For a M = 2 TI-ADC, this can be mathematically expressed as:

$$T_2 - T_1 = \frac{1}{MF_{CLOCK}}$$

(2.16)

where  $T_1$  and  $T_2$  are the times consecutive samples are taken by the first and second sub ADCs respectively. Based on this, a timing skew  $\Delta T_{SKEW}$  exists if  $T_2 - T_1 \neq 1/MF_{CLOCK}$  which is defined as:

$$\Delta T_{SKEW} = \left| (T_2 - T_1) - \frac{1}{MF_{CLOCK}} \right|$$

(2.17)

Once a TI-ADC is manufactured there are 3 main components that can contribute to  $\Delta T_{SKEW}$ ; fixed timing shifts between the sub ADCs due to design and process variations, drifts in timing between sub ADCs due to aging and random noise or jitter on each of the sub ADCs clocks'. Note that in general, timing skews can exist between each sub ADC within the TI-ADC.

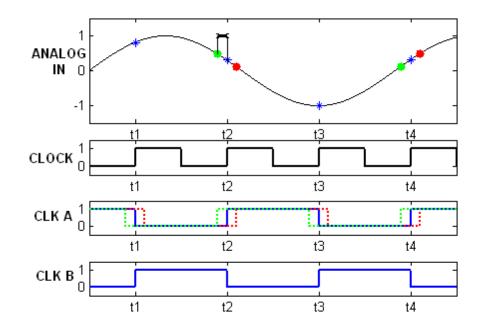

Timing skews are problematic because they shift the times at which each of the sub ADCs sample the input, which causes non-uniform sampling of the input signal [4]. An illustration of a timing skew in an M = 2 TI-ADC and its impact on the sampling of a sine wave is shown in Figure 2.5. The blue waveform/points are the ideal sampled sine wave, which can also be thought of as the average between the red and green points. The red waveform/point corresponds to sub ADC 'A' sampling later in time than it should, whereas the green waveform is sub ADC 'A' sampling sooner in time than it should.

Figure 2.5: Time-Domain Plot of an Ideal and Timing Skewed Sampled Sine Waves

### 2.3.1 Analysis

A full frequency domain analysis of non-uniform sampling, which can be thought of as timing skews being applied to a uniformly sampled signal, is performed in [4]. This thesis analyzes timing skews in an alternative, time-domain based way, yielding similar results as [4]. To simplify the analysis and to match the test architecture used to evaluate the circuit designed in this thesis, an M = 2 TI-ADC case is presented where the timing skew between the two sub ADCs is  $\Delta T_{SKEW}$ . Note that for an M = 2case, the SFDR is the worst for a given  $\Delta T_{SKEW}$  and the difference between the SNR for an M = 2 case and the  $M = \infty$  case is only 3 dB, with typical practical values being  $M \leq 8$ , however very large scale integration (VLSI) makes larger values of Mpractical [4].

Referring back to Figure 2.5, it shows that the non-uniform sampling of a sine wave appears like two sine waves that are uniformly sampled and shifted with respect to one another by the amount  $2\pi F_{IN}\Delta T_{SKEW}$ . Alternatively, the shift can be viewed with respect to the input sine wave by  $+2\pi F_{IN}(\Delta T_{SKEW}/2)$  for the red wave and  $-2\pi F_{IN}(\Delta T_{SKEW}/2)$  for the blue wave. These two sine waves can then be thought of as inputs to two sub ADCs which exhibit no timing skew, since the sine waves themselves now capture the timing skew. One sine wave is applied to the first sub ADC and the other to the second, where the sine waves can be mathematically expressed using (2.1) as:

$$V_{IN1} = \frac{V_{FS}}{2} \cos\left(2\pi F_{IN}t + 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right)$$

(2.18)

$$V_{IN2} = \frac{V_{FS}}{2} \cos\left(2\pi F_{IN}t - 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right)$$

(2.19)

When the outputs of the two interleaved ADCs are combined, the overall output contains two terms, an average of the two inputs and an error term as explained in [5]. Taking the average of the two input terms yields:

$$V_{OUTAVG} = \frac{1}{2} \begin{pmatrix} \frac{V_{FS}}{2} \cos\left(2\pi F_{IN}t + 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ + \frac{V_{FS}}{2} \cos\left(2\pi F_{IN}t - 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \end{pmatrix}$$

(2.20)

Simplifying (2.20) gives:

$$V_{OUTAVG} = \frac{V_{FS}}{4} \begin{pmatrix} \cos\left(2\pi F_{IN}t + 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ +\cos\left(2\pi F_{IN}t - 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \end{pmatrix}$$

(2.21)

Equation (2.21) can be further simplified by using the cosine identity  $\cos(a \pm b) = \cos(a)\cos(b) \mp \sin(a)\sin(b)$  to give:

$$V_{OUTAVG} = \frac{V_{FS}}{4} \begin{pmatrix} \cos(2\pi F_{IN}t)\cos\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ -\sin(2\pi F_{IN}t)\sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ +\cos(2\pi F_{IN}t)\cos\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ +\sin(2\pi F_{IN}t)\sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \end{pmatrix}$$

(2.22)

which, when reduced to its most compact form, results in:

$$V_{OUTAVG} = \frac{V_{FS}}{2} \left( \cos(2\pi F_{IN}t) \cos\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \right)$$

(2.23)

According to (2.23)  $\Delta T_{SKEW}$  affects the amplitude of the signal, however given that timing skews are usually on the order of picoseconds at most which result in a negligible change in amplitude, (2.23) can be further reduced using the small-angle approximation of  $\cos(x) = 1$  for small x, yielding:

$$V_{OUTAVG} = \frac{V_{FS}}{2} \cos(2\pi F_{IN} t) = V_{IN}$$

(2.24)

Note that this is the ideal sampled input from (2.1), which shows that the desired input does appear in the output of a TI-ADC subject to timing skews.

Dealing now with the error term, it appears in the output as a consequence of the difference between the sine waves that each sub ADC sees and the interleaving process. As the interleaving process grabs one sample from one sub ADC and next from the other sub ADC, the interleaved output samples appear to oscillate back and forth. This oscillation can be represented by a series of alternating magnitude impulses, i.e. (1, -1, 1, -1 ...), with a frequency of  $F_{SAMPLE}/2$  [5]. The impulses modulate the difference between the two sine waves. Given this, the error term,  $V_{OUTERROR}$  can be expressed as follows:

$$V_{OUTERROR} = V_{ERROR} \sin\left(2\pi \frac{F_{SAMPLE}}{2}t\right)$$

(2.25)

$V_{ERROR}$  is obtained by taking the difference between the sine waves, (2.18) and (2.19) yielding:

$$V_{ERROR} = \frac{V_{FS}}{2} \begin{pmatrix} \cos\left(2\pi F_{IN}t + 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ -\cos\left(2\pi F_{IN}t - 2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \end{pmatrix}$$

(2.26)

Once again using the cosine identity to simplify results in:

$$V_{ERROR} = \frac{V_{FS}}{2} \begin{pmatrix} \cos(2\pi F_{IN}t)\cos\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ -\sin(2\pi F_{IN}t)\sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ -\cos(2\pi F_{IN}t)\cos\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \\ -\sin(2\pi F_{IN}t)\sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \end{pmatrix}$$

(2.27)

Combining terms reduces (2.27) to:

$$V_{ERROR} = -V_{FS}\sin(2\pi F_{IN}t)\sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right)$$

(2.28)

Substituting (2.28) into (2.25) gives:

$$V_{OUTERROR} = -V_{FS} \sin\left(2\pi F_{IN} \frac{\Delta T_{SKEW}}{2}\right) \sin(2\pi F_{IN} t) \sin\left(2\pi \frac{F_{SAMPLE}}{2} t\right) \quad (2.29)$$

Equation (2.29) shows the amplitude modulation,  $K \sin(at) \sin(bt)$ , that occurs due to the interleaving impulses. Using the sine identity  $\sin(a)\sin(b) = \frac{1}{2}(\cos(a-b) - \cos(a+b))$  on (2.29) results in:

$$V_{ERROR} = \frac{-V_{FS}}{2} \sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \begin{pmatrix} \cos\left(2\pi F_{IN}t - 2\pi\frac{F_{SAMPLE}}{2}t\right) \\ -\cos\left(2\pi F_{IN}t + 2\pi\frac{F_{SAMPLE}}{2}t\right) \end{pmatrix}$$

(2.30)

Rearranging the arguments of the two cosine terms:

$$V_{ERROR} = \frac{-V_{FS}}{2} \sin\left(2\pi F_{IN} \frac{\Delta T_{SKEW}}{2}\right) \begin{pmatrix} \cos\left(2\pi \left(F_{IN} - \frac{F_{SAMPLE}}{2}\right)t\right) \\ -\cos\left(2\pi \left(F_{IN} + \frac{F_{SAMPLE}}{2}\right)t\right) \end{pmatrix}$$

(2.31)

The total output is given by the sum of (2.23) and (2.31):

$$V_{OUT} = \frac{V_{FS}}{2} \begin{pmatrix} \cos\left(2\pi F_{IN} \frac{\Delta T_{SKEW}}{2}\right) \cos(2\pi F_{IN}t) \\ -\left(\sin\left(2\pi F_{IN} \frac{\Delta T_{SKEW}}{2}\right) \begin{pmatrix} \cos\left(2\pi (F_{IN} - \frac{F_{SAMPLE}}{2})t\right) \\ -\cos\left(2\pi (F_{IN} + \frac{F_{SAMPLE}}{2})t\right) \end{pmatrix} \end{pmatrix}$$

(2.32)

Equation (2.32) shows that for an M = 2 TI-ADC with a timing skew  $\Delta T_{SKEW}$  between the two sub ADCs clocks there are three tones that appear in the output. The first tone is the desired sampled input tone with a magnitude of:

$$|V_{IN}| = \frac{V_{FS}}{2} \cos\left(2\pi F_{IN} \frac{\Delta T_{SKEW}}{2}\right) \tag{2.33}$$

The two other tones are spurious tones, generated by the timing skew with magnitudes of:

$$|V_{\Delta TSKEW}| = \frac{V_{FS}}{2} \sin\left(2\pi F_{IN} \frac{\Delta T_{SKEW}}{2}\right)$$

(2.34)

and frequencies of:

$$F_{\Delta TSKEW} = F_{IN} \pm \frac{F_{SAMPLE}}{2}$$

(2.35)

It should be noted that the two frequencies actually appear as the same spurious tone in an FFT plot, as they both alias to the same frequency. In general, with M > 2, additional spurious tones appear with magnitudes typically less than the tone in the M = 2 case and at frequencies given by [1]:

$$F_{\Delta TSKEW} = F_{IN} \pm \frac{iF_{sAMPLE}}{M}$$

$$i = 1, 2, \dots M - 1$$

(2.36)

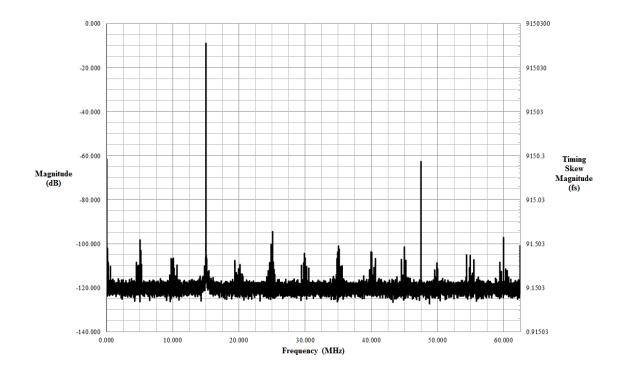

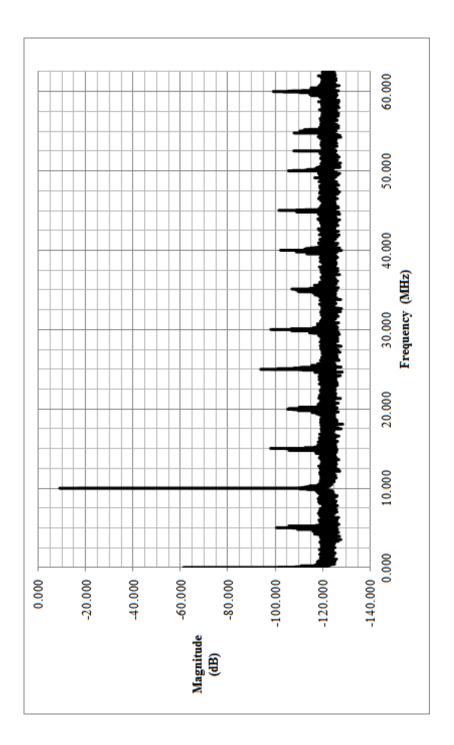

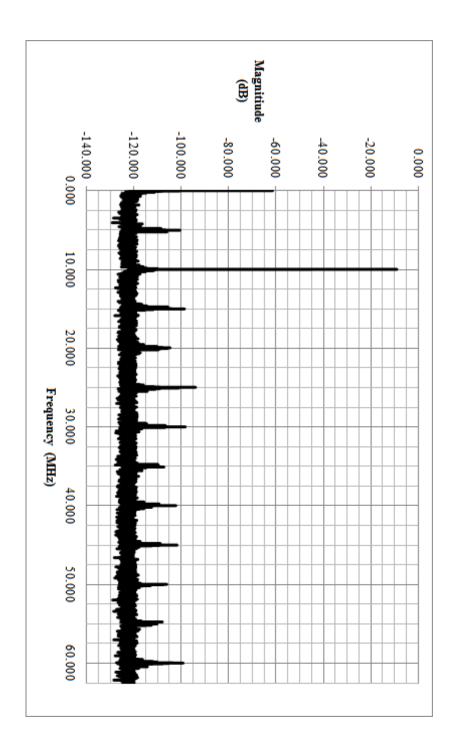

As an example, Figure 2.6 shows a 32,768 point FFT plot of an  $F_{IN} = 110 MHz$ input, sampled at a rate  $F_{SAMPLE} = 125 MHz$  with an M = 2 TI-ADC, subject to a timing skew  $\Delta T_{SKEW} = 6 ps$ .

Figure 2.6: FFT Plot of a 2-way TI-ADC with  $F_{IN} = 110 MHz$  and  $F_{SAMPLE} = 125 MHz$ , Subject to a 6 ps Timing Skew

The most useful way to consider Figure 2.6, in terms of timing skews, is to calculate the SFDR. Using equations (2.12), (2.33) and (2.34), the SFDR for a M = 2 TI-ADC is given by:

$$SFDR = \frac{\frac{V_{FS}}{2\sqrt{2}}\cos\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right)}{\frac{V_{FS}}{2\sqrt{2}}\sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right)}$$

(2.37)

Simplifying (2.37) yields:

$$SFDR = \frac{\cos\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right)}{\sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right)}$$

(2.38)

Equation (2.38) shows that the SFDR for a 2-way TI-ADC subject to timing skews directly depends on the ratio between the input and the spurious tone due to the timing skew. This is a very important result, implying that timing skews can be detected and characterized from the measured SFDR of a TI-ADC.

From Figure 2.6 and the analysis in this chapter, it is clear that timing skews degrade output spectrum of TI-ADCs. This degradation is captured in the resolution and SFDR specifications and must be corrected to a certain limit described in the next section.

### 2.3.2 Timing Skew Requirements

The timing skews and corresponding spurious tones that occur in a TI-ADC system can never be eliminated entirely, as this would require a correction method with infinite precision. However, perfect elimination is not required. It is only necessary to supress the spurious tones to a level that does not affect the desired resolution and SFDR of the TI-ADC. Usually this means correcting the timing skews to the point where the spurious tones are below the quantization noise level.

To establish concrete design goals for this thesis and push the boundaries of what current ADCs are doing by time interleaving, a modern high resolution, high speed ADC is considered. The 16-bit, 20 MSPS AD9266 by Analog Devices is representative of a modern high resolution, high speed ADC [6]. It is assumed that an

improvement of 16 to 32 times the original sample rate (interleaving 16 or 32 AD9266 ADCs) is representative of a push in the boundaries. This assumption is valid as recent, state of the art TI-ADCs have 2 to 24 interleaved ADCs [7], [8], [9], [10], [11]. In addition, it is assumed that achieving a timing skew limited  $SFDR = 100 \, dBc$  for a  $F_{IN} = 100 \, MHz$  is representative of boundary pushing performance. The implication this value has on the precision the analog timing skew correction circuit needs to achieve is shown later in this section.

Considering the previous statement about the quantization noise level, the rms values of (2.6) and (2.34) are used to express, for a 2-way TI-ADC, the relationship between the quantization noise level and the magnitude of the timing skew spurious tone:

$$\frac{V_{FS}}{2^N \sqrt{2}\sqrt{12}} \ge \frac{V_{FS}}{2\sqrt{2}} \sin\left(2\pi F_{IN}\frac{\Delta T_{SKEW}}{2}\right) \tag{2.39}$$

Using the small-angle approximation sin(x) = x for small x and rearranging to solve for the input frequency  $F_{IN}$  yields:

$$F_{IN} \le \frac{2}{\pi 2^N \sqrt{12} \Delta T_{SKEW}} \tag{2.40}$$

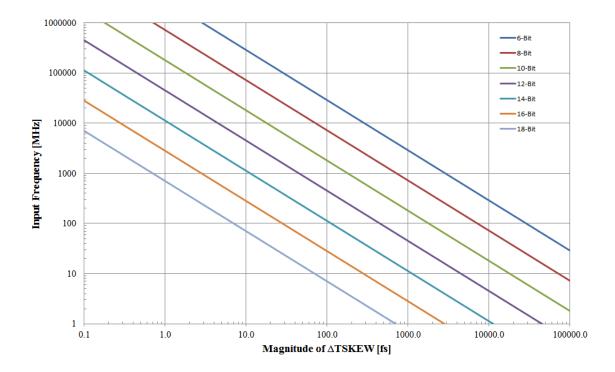

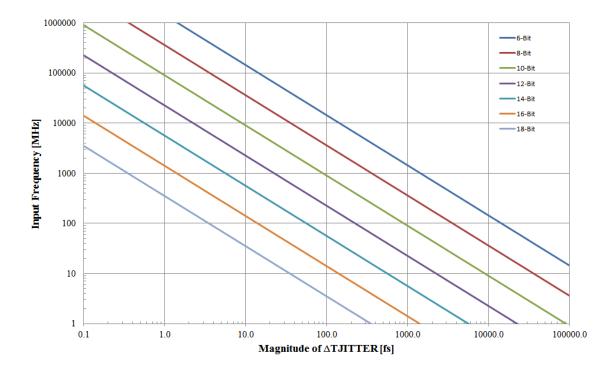

This relation shows that for a given resolution N and timing skew  $\Delta T$  there is a limit on the maximum input frequency to the TI-ADC such that the resolution does not degrade below N bits. A plot of (2.40) is shown in Figure 2.7, illustrating the maximum input frequency possible for a given resolution, subject to various orders of timing skew.

Figure 2.7: Input Frequency vs. Timing Skew for Specific Resolutions

It is evident from Figure 2.7 that as the input frequency increases, the degree to which timing skews need to be corrected also increases in order to maintain a certain resolution. Alternatively, if the assumption is made that the input frequency to the TI-ADC will be set at the highest rate possible within the first Nyquist zone, i.e.  $(F_{IN} = 1/2T_{SAMPLE})$ , then (2.40) becomes:

$$\frac{\Delta T_{SKEW}}{T_{SAMPLE}} \le \frac{4}{\pi 2^N \sqrt{12}} \tag{2.41}$$

Equation (2.41) is also a useful way to think of timing skews as it relates them to the sample rate. Furthermore, it works out that the ratio of  $\Delta T_{SKEW}/T_{SAMPLE}$  needs to be on the same order as the resolution of the converter when sampling at the Nyquist rate.

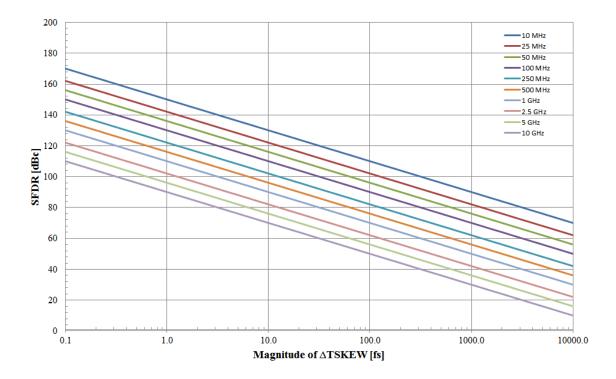

As mentioned in the previous section, a very useful way to consider timing skews is in terms of the SFDR of the TI-ADC. Equation (2.38) can be further simplified by using the small angle approximations for both cos(x) and sin(x) and putting it in dB, which results in:

$$SFDR = 20 \log_{10} \left( \frac{1}{\pi F_{IN} \Delta T_{SKEW}} \right)$$

(2.42)

Equation (2.42) shows that the SFDR of a TI-ADC will degrade as  $F_{IN}$  increases, unless there is a corresponding decrease in the timing skew  $\Delta T_{SKEW}$ . Figure 2.8 illustrates this behaviour, showing the expected SFDR for a range of input frequencies, given various orders of timing skew.

Figure 2.8: SFDR vs. Timing Skew for Specific Input Frequencies

It is very important to note that Figure 2.8 is a vital reference as it quickly shows the precision level to which timing skews need to be corrected for a given input frequency and SFDR. This is useful to know when either designing or measuring the performance of a circuit for correcting timing skews in TI-ADCs since the precision level is one of the main specifications to consider for such a circuit. Based on Figure 2.8 then, a timing skew limited  $SFDR = 100 \, dBc$  for a  $F_{IN} = 100 \, MHz$ , results in a precision requirement of 25 fs for the timing skew. This means that in order reduce the spurious tone 100 dB below the fundamental; the correction circuit requires a precision/step size of 25 fs when correcting the timing skew. This serves as the first main design goal of this thesis and is representative of a boundary pushing goal as recently reported TI-ADCs [7], [11], [9] are achieving approximately 65 fs, 250 fs and 570 fs of timing skew correction precision respectively.

The second main design goal related to timing skews is the largest magnitude of timing skew the correction circuit can handle, which herein is referred to as the range. The range requirement determines how large of a timing skew can exist between any two sub ADCs in a TI-ADC and still be corrected for down to the precision requirement. The maximum range that needs to be covered is usually on the order of tens to hundreds of picoseconds, with 25 ps [12], 50 ps [13] and 500 ps [14] being reported in the literature. In this thesis, a range of approximately 100 ps to 200 ps is set as the design goal. This range specification represents a rough average of what the literature reports, leaning more towards the low end in order to cater to integrated circuit based TI-ADCs.

#### 2.4 Jitter

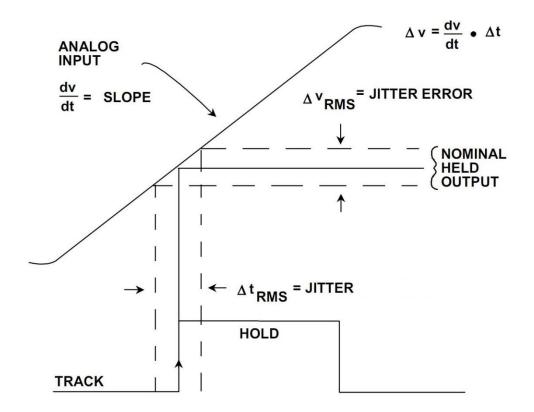

Jitter is the random variation in timing of when a signal crosses a specific threshold. The random variation in timing is a result of noise being present on the signal whose threshold crossing is important. All ADCs whether they are TI-ADCs or not, are degraded by the presence of jitter on their sampling clocks and on the input signal to the ADC. In this thesis the jitter of concern is that on the sampling clocks provided to the sub ADCs in a TI-ADC. Jitter on a sampling clock gives rise to an error in the sampled voltage as shown in Figure 2.9.

Figure 2.9: Sampling Clock Jitter's Effect on the Sample Analog Input [2]

Figure 2.9 shows that for a given jitter  $\Delta T_{JITTER}$ , the error in the sampled voltage  $V_{NOISE}$  is related to the jitter through the slope or slew rate (SR) of the sampled signal. Mathematically this is expressed as:

$$V_{NOISE} = SR \times \Delta T_{IITTER} \tag{2.43}$$

Note that the error in the sampled voltage is referred to as a noise  $V_{NOISE}$  because  $\Delta T_{JITTER}$  is a random value, which means the voltage error is a random value and will appear as a noise on the output of the ADC. Furthermore  $\Delta T_{JITTER}$  is typically expressed as an rms value, resulting in  $V_{NOISE}$  also being an rms voltage.

As mentioned in Section 2.1, ADCs are usually tested with a sinusoidal input signal. Given this, the worst-case  $V_{NOISE}$  for a given  $\Delta T_{JITTER}$  on the sampling clock, occurs when the maximum slew rate is observed on the sinusoidal input. The sinusoidal input can be expressed as follows:

$$V_{IN} = \frac{V_{FS}}{2} \sin(2\pi F_{IN} t)$$

(2.44)

Taking the derivative with respect to t and solving for the maximum value yields:

$$\frac{dV_{IN}}{dt} = V_{FS}\pi F_{IN} = SR(max)$$

(2.45)

Substituting (2.45) into (2.43) results in:

$$V_{NOISE} = V_{FS} \pi F_{IN} \Delta T_{IITTER}) \tag{2.46}$$

It is important to note that for either an increase in  $\Delta T_{JITTER}$  or an increase in  $F_{IN}$  the noise output from the ADC will increase. Additionally the jitter does not depend on the sample rate. The sample rate only establishes the Nyquist zone that  $F_{IN}$  falls into.

### 2.4.1 Jitter Requirements

As in the case with the timing skews, jitter can never be eliminated from a TI-ADC or any ADC for that matter, only controlled to within a set limit. Similarly then, it is desirable to have the jitter controlled to a level that is below the quantization floor. This can be expressed, using the rms values of (2.6) and (2.46), as follows:

$$\frac{V_{FS}}{2^N \sqrt{2}\sqrt{12}} \ge \frac{V_{FS}}{\sqrt{2}} \pi F_{IN} \Delta T_{JITTER}$$

(2.47)

Rearranging to solve for  $F_{IN}$  yields:

$$F_{IN} \le \frac{1}{\pi 2^N \sqrt{12} \Delta T_{JITTER}}$$

(2.48)

A plot of (2.48) is shown in Figure 2.10, which illustrates the highest  $F_{IN}$  for a specific resolution subject to various amounts of jitter on the sampling clock.

Figure 2.10: Input Frequency vs. Jitter for Specific Resolutions

Just as in the timing skew case, as a higher  $F_{IN}$  is required, the amount of jitter that can be tolerated on the sampling clocks is reduced for a given resolution. One interesting observation that is seen when comparing Figure 2.7 with Figure 2.10 is the factor of 2 difference between the  $\Delta T_{SKEW}$  level and the  $\Delta T_{JITTER}$  level at the same  $F_{IN}$ .

Alternatively if a specific SNR is desired, which is jitter limited, it is useful to have an expression as follows:

$$SNR = \frac{\frac{V_{FS}}{2\sqrt{2}}}{\frac{V_{FS}}{\sqrt{2}}\pi F_{IN}\Delta T_{JITTER}}$$

(2.49)

Simplifying (2.49) and putting it in dB yields:

$$SNR = 20 \log_{10} \left( \frac{1}{2\pi F_{IN} \Delta T_{JITTER}} \right)$$

(2.50)

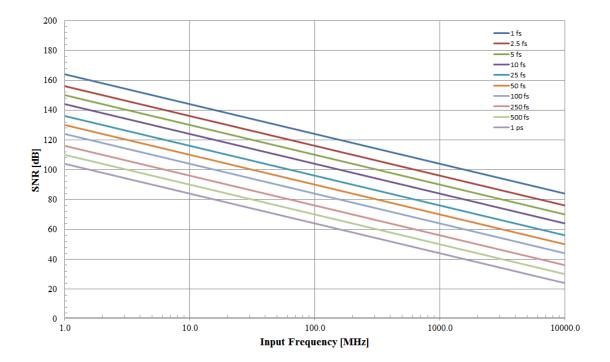

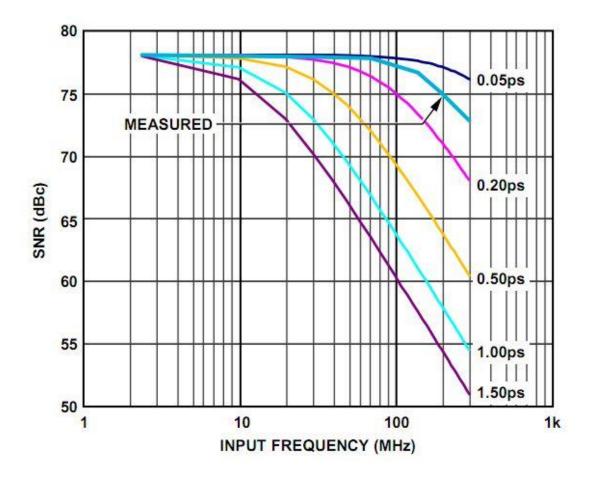

Figure 2.11 shows a plot of (2.50) for various amounts of jitter.

Figure 2.11: SNR vs. Input Frequency for Various Amounts of Jitter

Just as in the case with timing skews, it is important to control the amount of additive jitter that the clocking sources for the sub ADCs experience. Similar to the

timing skew SFDR goal, an additive jitter limited  $SNR = 95 \, dB$  for a  $F_{IN} = 100 \, MHz$  is assumed representative of a boundary pushing performance goal. Based on Figure 2.11 then, an additive jitter limited  $SNR = 95 \, dB$  for a  $F_{IN} = 100 \, MHz$ , results in the correction circuit having an additive jitter requirement of 25 fs rms allowing the *SNR* degradation due to jitter to not mask the desired timing skew correction precision. This serves as the third and final main design goal of this thesis.

### 2.5 Summary

Timing skews result in non-uniform sampling of a signal in TI-ADCs. This nonuniform sampling gives rise to distinct spurious tones, whose magnitude depends on the input frequency to the TI-ADC and the how large of a timing skew is present between any two sub-ADCs. These spurious tones degraded the SFDR and resolution of the TI-ADC. In addition, jitter on the sampling clocks to the sub ADCs further degraded the resolution or SNR of the TI-ADC. From these two phenomena, timing skews and jitter, three system level requirements or design goals are established. The first being the precision required to correct timing skews, the second being the largest range required to correct the timing skews and the third being the amount of additive jitter that can be tolerated on the sampling clocks, such that the SFDR, resolution and SNR are not impacted up to a maximum input frequency. Based on the example TI-ADC system with boundary pushing performance levels of a timing skew limited  $SFDR = 100 \ dBc$  and an additive jitter limited  $SNR = 95 \ dB$  for a  $F_{IN} = 100 \ MHz$ , the resulting design goals are a precision/step size of 25 fs for  $\Delta T_{SKEW}$  with a range of 100 ps to 200 ps for  $\Delta T_{SKEW}$  and an additive jitter  $\Delta T_{IITTER}$  of 25 fs. Circuits to achieve these design goals are explored in the following chapters.

## Chapter 3

# Analog Techniques to Correct Timing Skews

This chapter begins with a brief comparison between correcting timing skews in the analog domain and correcting them in the digital domain. It then proceeds to analyze and compare different analog circuit techniques that can be used to correct timing skews. Next, two circuit architectures that use the analog circuit techniques are compared, with one being selected as the design for this thesis. After this, a discussion is presented on how the selected architecture is implemented such that it can be tested in terms of the three design goals. Lastly, a summary of the complete architecture to be designed is presented along with the design goals for each block within the architecture.

### 3.1 Analog vs. Digital Correction

At the heart of any method to correct timing skews in TI-ADCs is the idea of adjusting the timing of the samples such that they appear as uniform as possible. In

the analog domain, this is accomplished by adjusting the clock edges of each sub ADC such that the TI-ADC's samples are taken in a uniform manner. Whereas in the digital domain, the samples are taken with the timing skews present and then the output is post processed, adjusting the phase of each sub ADCs data such that the overall digital data appears to be uniformly sampled. Correction methods designed in either domain are subject to the three main design requirements of precision, additive jitter and range. Additionally the bandwidth over which the correction method operates and how power intensive they are, matter to both analog and digital domain correction methods. Given these five requirements, the two domains can now be compared.

As previously mentioned correcting timing skews in the analog domain requires a circuit to adjust the clock edges the sub ADCs use to sample. Fortunately there are circuits already present in TI-ADCs that can be modified to perform the clock edge adjustment such as the on chip clock buffers or clock divider circuits. In addition, analog correction does not affect the bandwidth  $F_{BW}$  of the TI-ADC and allows multiple input signals in different Nyquist zones to be converted while having the timing skews corrected. Analog correction circuits also offer high correction precision, while not always being directly proportional to the power. Unfortunately, analog circuits are subject to noise and thus jitter, which usually requires adding power to reduce the jitter. Similarly, in order to cover a larger range, i.e. larger timing skew between any two sub ADCs, more power is also needed.

Digital correction of timing skews is usually accomplished through the design of a fractional delay filter or interpolation filter, which allows for the phase shifting of the digital data samples [1]. This signal processing adds noise due to the finite precision of the arithmetic and rounding errors, requiring more bits for less noise and thus more power. In addition, the precision, range and bandwidth are all proportional to the order of the digital filters used to correct the timing skews, meaning better performance in any of these requires more power. Furthermore, the bandwidth is fundamentally limited to slightly less than one Nyquist zone due to aliasing. This means that for digital correction methods to cover more of one Nyquist zone, more power is required. Furthermore, if the signal being sampled by the TI-ADC changes Nyquist zones, the digital correction method has to re-configure the filter for the new Nyquist zone in real-time. Finally, the filters require multipliers running at a rate at least equal to the sub ADC rate if not the full clock rate of the TI-ADC. This is also power intensive, as high-speed multiplication is generally a high power operation.

A summary of how analog domain and digital domain timing skew correction compare in terms of the five requirements; additive jitter/noise, precision, range, bandwidth and power is presented in Table 3.1.

|                       | Analog Correction         | Digital Correction                    |

|-----------------------|---------------------------|---------------------------------------|

| Additive Jitter/Noise | $\propto \frac{1}{Power}$ | $\propto$ Power through               |

|                       |                           | the number of bits                    |

| Precision Level       | dependent but not         | ∝ Power                               |

|                       | always $\propto$ Power    | ~ I ower                              |

| Range                 | ∝ Power                   | ∝ Power                               |

| Bandwidth             | Independent of Power      | $\propto$ <i>Power</i> and limited to |

|                       | and not limited           | < one Nyquist zone                    |

Table 3.1: Performance Comparison of Analog Domain and Digital Domain Timing

Skew Correction

There are two important things to note between analog and digital correction of timings skews. The first is that while analog correction requires power to reduce the

amount of additive jitter, digital correction requires power to increase the precision level to which timing skews are corrected. The second is that analog correction can tolerate signals that change Nyquist zones or span multiple Nyquist zones, while digital correction for the most part cannot tolerate these signals. Both domains are useful for the specific applications that are unaffected by the limitations they each have. This thesis focuses on analog correction and minimizing the limitations that exist with it.

### 3.2 Circuit Techniques

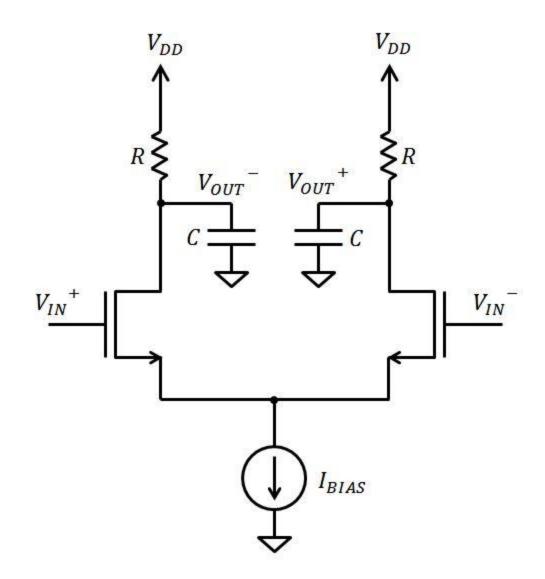

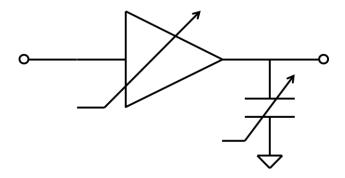

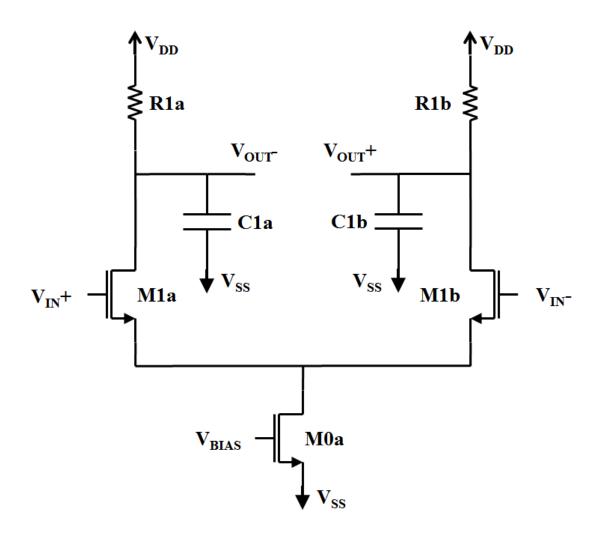

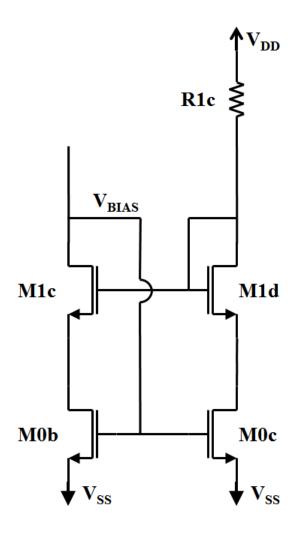

Analog correction of timing skews is a matter of adjusting clock edges while affecting little else in the TI-ADC. In circuit terms, this means being able to vary the delay of a clock edge while not loading the clock or adding significant jitter. To understand what techniques can be used to accomplish this, it is best to consider a buffer or inverter. Figure 3.1 shows the schematic of a MOSFET based differential buffer/inverter with a capacitive load.

Figure 3.1: Schematic a Differential Buffer/Inverter

A buffer/inverter takes in a clock edge and outputs a delayed edge due to the charging/discharging of the capacitive load *C*. This delay,  $T_{DELAY}$ , is usually on the order of 10's of picoseconds for a capacitive load comparable to the intrinsic capacitance of the buffer/inverter. The intrinsic delay of a single buffer then is too small to cover the desired delay range of 100 ps to 200 ps. The delay is also too large for fine-tuning, as placing two buffers in series provides too large a delay step to

achieve the desired precision or step size of 25 fs. Given this, it is useful to analyze the buffer/inverter to see how delays in between a single buffer and two buffers can be achieved and varied to meet the precision requirement. Note the analysis of how delays much larger than the intrinsic delay can be achieved is left to Section 3.3.

### 3.2.1 Analysis

Two important aspects of the differential buffer/inverter need to be considered, how the delay can be varied and how this impacts the additive jitter of the buffer. To simplify the analysis of the differential buffer/inverter in Figure 3.1, a single-ended model of it is considered, shown in Figure 3.2

Figure 3.2: Single-Ended Model of a Differential Buffer/Inverter

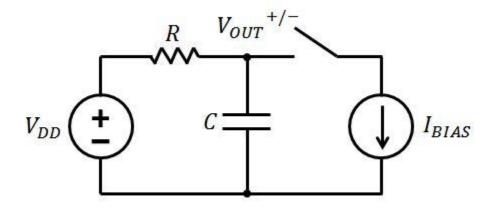

The switch in the model is controlled by the input clock, opening when it transitions from high to low (falling edge) and closing when transitioning from low to high (rising edge). To understand the delay behaviour of the model in terms of  $I_{BIAS}$ , R and C, the step response is calculated. Equations (3.1) and (3.2) are the step responses for

the rising  $V_{OUTR}$  and falling  $V_{OUTF}$  input clock edge respectively assuming zero initial voltage on the capacitor.

$$V_{OUTR} = V_{DD} - I_{BIAS} R e^{\frac{-t}{RC}}$$

(3.1)

$$V_{OUTF} = V_{DD} - I_{BIAS} R (1 - e^{\frac{-t}{RC}})$$

(3.2)

The step response of the model turns out to be very similar to that of the familiar *RC* circuit and shows that varying  $I_{BIAS}$ , *R* or *C* will vary  $V_{OUTR}$  and  $V_{OUTF}$  and correspondingly the delay. Note  $V_{DD}$  is considered the supply voltage for the majority of analog circuits in the TI-ADC and thus a constant, non-variable value since it would change the behaviour of other circuits. Additionally, it is assumed that the output swing  $V_{DD} - I_{BIAS}R$  is kept constant due to practical reasons, i.e. the need to keep the current source MOSFET in saturation. The implication of this is that if  $I_{BIAS}$  increases by a factor of two, *R* must decrease by a factor of two to maintain the same output swing.

For differential circuits, a common way to calculate the delay is based off when the output reaches the common-mode value, since it is at this point the following stage switches. Typically, the common-mode value corresponds to the time when the output has achieved 50% of its final value, assuming a symmetric swing about the common-mode. In terms of the single-ended model this corresponds to the time t when  $V_{OUTR/F} = V_{DD} - (I_{BIAS}R)/2$ . Using this, the assumption of a fixed swing, (3.1) and (3.2), the delay  $T_{DELAY}$  is solved for yielding the familiar RC circuit expression:

$$t = 0.69RC = T_{DELAY} \tag{3.3}$$

Note that (3.3) applies for either the rising or falling edge. Equation (3.3) shows that the delay of the differential buffer/inverter is proportional to *C* and *R* or  $1/I_{BIAS}$ . The delay then can be varied by scaling *C*, *R* or  $I_{BIAS}$  such that it covers the range in between a single buffer and two series buffers. With the delay behaviour of the differential buffer/inverter characterized, the jitter behaviour is now considered.

Referring back to (2.43), the jitter for a circuit can be approximated to the first order by:

$$\Delta T_{JITTER} = \frac{V_{NOISE}}{SR} \tag{3.4}$$

In this case,  $V_{NOISE}$  is the total rms noise voltage at the  $T_{DELAY}$  point and SR is the slew rate at the same point. Using (3.1), (3.2) and (3.3) the slew rate at time  $t = T_{DELAY}$  is calculated yielding:

$$SR = \frac{I_{BIAS}}{2C} \tag{3.5}$$

Note the slew rate is the same whether  $V_{OUT}$  is rising or falling. Furthermore, the slew rate is linked to *R* only through the fixed output swing assumption.

To simplify the calculation of  $V_{NOISE}$  it is assumed that only *R* and  $I_{BIAS}$  contribute noise and not the switch or supply  $V_{DD}$ . Note that the noise due to  $I_{BIAS}$  is a result of the current source being implemented by using a MOSFET in saturation. In addition, only the thermal noise of the two elements is considered to simplify further

the analysis of  $V_{NOISE}$ . Given these assumptions, Figure 3.3 shows the noise model of the circuit in Figure 3.2.

Figure 3.3: Simplified Noise Model of a Differential Buffer/Inverter

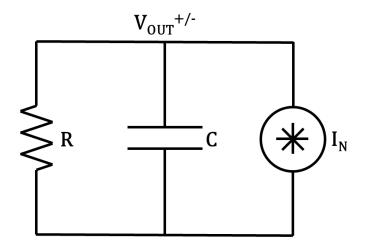

In Figure 3.3,  $I_N$  is the total thermal noise, which is composed of the  $I_{BIAS}$  noise  $(I_{NI})$  and R thermal noise  $(I_{NR})$ . The expressions for the thermal noise of a MOSFET in saturation  $I_{NI}$ , thermal noise of a resistor  $I_{NR}$  and the total noise  $I_N$  are [15]:

$$I_{NI}^{2} = \frac{8KTg_m}{3}\Delta F \tag{3.6}$$

$$I_{NR}^{2} = \frac{4KT}{R}\Delta F \tag{3.7}$$

$$I_N^2 = \left(\frac{8g_m}{3} + \frac{4}{R}\right) KT\Delta F \tag{3.8}$$

where *K* and *T* are constants and  $\Delta F$  implies that the noise is per Hz.  $\Delta F$  is usually set to 1/4RC which approximates the noise bandwidth of the circuit [15]. The term  $g_m$  is the transconductance of the MOSFET and relates to  $I_{BIAS}$ , i.e.  $(g_m \propto \sqrt{I_{BIAS}})$ . Given these things, (3.8) is rewritten as:

$$I_N \propto \sqrt{\left(\frac{8\sqrt{I_{BIAS}}}{3} + \frac{4}{R}\right)\frac{KT}{4RC}}$$

(3.9)

Relating  $I_N$  to the output noise  $V_{NOISE}$  requires multiplying  $I_N$  by R yielding:

$$V_{NOISE} \propto \sqrt{\left(\frac{8R\sqrt{I_{BIAS}}}{3} + 4\right)\frac{KT}{C}}$$

(3.10)

Simplifying and rearranging results in:

$$V_{NOISE} \propto \sqrt{\left(1 + \frac{2R\sqrt{I_{BIAS}}}{3}\right)\frac{KT}{C}}$$

(3.11)

The  $R\sqrt{I_{BIAS}}$  term is usually appreciably greater than one to allow a reasonable output swing. Note that this implies that the active device (MOSFET) noise is typically greater than the passive devices. Using this, (3.11) is approximated as:

$$V_{NOISE} \propto \sqrt{\left(\frac{2R\sqrt{I_{BIAS}}}{3}\right)\frac{KT}{C}}$$

(3.12)

Since only the relation of  $I_{BIAS}$ , R and C to  $V_{NOISE}$  matter; (3.12) is simplified resulting in:

$$V_{NOISE} \propto \sqrt{\frac{R\sqrt{I_{BIAS}}}{C}}$$

(3.13)

Using equations (3.4), (3.5) and (3.13) the relationship between  $I_{BIAS}$ , R and C and the additive jitter  $\Delta T_{JITTER}$  is given by:

$$\Delta T_{JITTER} \propto \frac{\sqrt{\frac{R\sqrt{I_{BIAS}}}{C}}}{\frac{I_{BIAS}}{2C}}$$

(3.14)

Simplifying (3.14) gives:

$$\Delta T_{JITTER} \propto \frac{\sqrt{R}\sqrt{C}}{I_{BIAS}^{3/4}}$$

(3.15)

With (3.15), the relationship between *R*,  $I_{BIAS}$  and *C* is established and a comparison can be made between each in terms of their influence on  $T_{DELAY}$  and  $\Delta T_{JITTER}$ .

### 3.2.2 Comparison

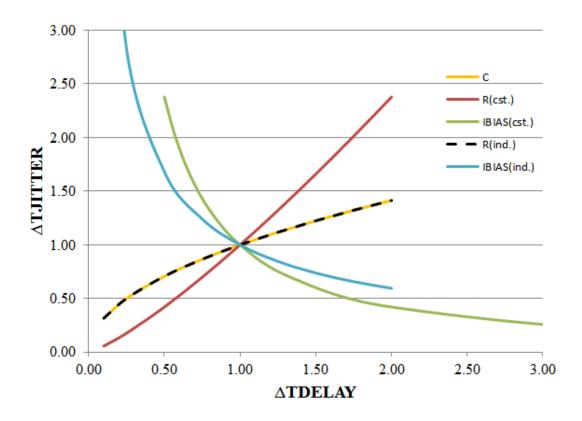

Using (3.15), the effects of varying *R*,  $I_{BIAS}$  and *C* on the delay and jitter of the differential buffer/inverter are shown in Table 3.2 and Figure 3.4. *C* is varied independently of *R* and  $I_{BIAS}$ , whereas *R* and  $I_{BIAS}$  are varied in two ways. The first way is that for both  $T_{DELAY}$  and  $\Delta T_{JITTER}$ , the assumption that  $I_{BIAS}R = Constant$  is considered. The second way is that for only  $\Delta T_{JITTER}$ , the effect of varying *R* and  $I_{BIAS}$  independently is considered. Although the effect on the delay is not considered in Table 3.2 for the second way, the general trend is that increasing  $I_{BIAS}$  by 2 × results in a > 2 × decrease in  $T_{DELAY}$  whereas increasing *R* by 2 × results in a  $\ll 2 \times$  increase in  $T_{DELAY}$  when considering the same output voltage level at which  $T_{DELAY}$  is measured. The opposite variation of *R* and  $I_{BIAS}$  is not valid as decreasing either shrinks the signal swing, which can lead to the output not swinging enough to switch subsequent gates.

|                   |                      |                      | $\Delta(\Delta T_{JITTER})$                                           |                                                              |

|-------------------|----------------------|----------------------|-----------------------------------------------------------------------|--------------------------------------------------------------|

|                   | $\Delta(Parameter)$  |                      | $I_{BIAS} \times R =$<br>Constant (cst.)                              | $I_{BIAS}, R =$<br>Independant(ind.)                         |

| R                 | 2 ×                  | 2 ×                  | $\frac{\sqrt{2}}{\left(\frac{1}{2}\right)^{3/4}} \times \approx 2.38$ | $\sqrt{2} \times \cong 1.41$                                 |

|                   | $\frac{1}{2}$ ×      | $\frac{1}{2}$ ×      | $\frac{\frac{1}{\sqrt{2}}}{(2)^{3/4}} \times \cong 0.42$              | $\frac{1}{\sqrt{2}} \times \cong 0.71$                       |

| С                 | 2 ×                  | 2 ×                  | $\sqrt{2} \times \cong 1.41$                                          | $\sqrt{2} \times \cong 1.41$                                 |

|                   | $\frac{1}{2} \times$ | $\frac{1}{2} \times$ | $\frac{1}{\sqrt{2}} \times \cong 0.71$                                | $\frac{1}{\sqrt{2}} \times \cong 0.71$                       |

| I <sub>BIAS</sub> | 2 ×                  | $\frac{1}{2}$ ×      | $\frac{\frac{1}{\sqrt{2}}}{(2)^{3/4}} \times \cong 0.42$              | $\frac{1}{(2)^{3/4}} \times \cong 0.59$                      |

|                   | $\frac{1}{2}$ ×      | 2 ×                  | $\frac{\sqrt{2}}{\left(\frac{1}{2}\right)^{3/4}} \times \cong 2.38$   | $\frac{1}{\left(\frac{1}{2}\right)^{3/4}} \times \cong 1.68$ |

Table 3.2: Effect of Varying *R*,  $I_{BIAS}$  and *C* on  $T_{DELAY}$  and  $\Delta T_{JITTER}$

Figure 3.4:  $\Delta T_{IITTER}$  vs.  $T_{DELAY}$  Trade-off when Varying R,  $I_{BIAS}$  and C

Based on Table 3.2 and the above statements it is best to vary the load capacitance (*C*) to achieve delays larger than a single intrinsic buffer as it provides a better delay increase vs. additive jitter trade-off as compared to *R* and  $I_{BIAS}$ . However, the precision of the delay steps is limited to the smallest capacitor that can be implemented in the chosen process. If a more precise delay step is desired an interesting option exists in terms of the best delay vs. jitter trade-off. Consider adding a unit *C*, the smallest *C* possible, to the load, the current  $I_{BIAS}$  can then be increased to shrink the delay step from the unit *C*, which according to Table 3.2, allows for better precision and for the jitter to improve as more current is added. Note that this assumes  $I_{BIAS}$  can be increased in smaller units relative to its original value then a unit *C*. The validity of this assumption will be shown in Chapter 4.

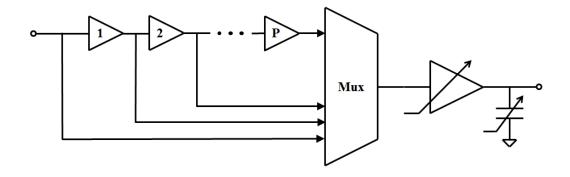

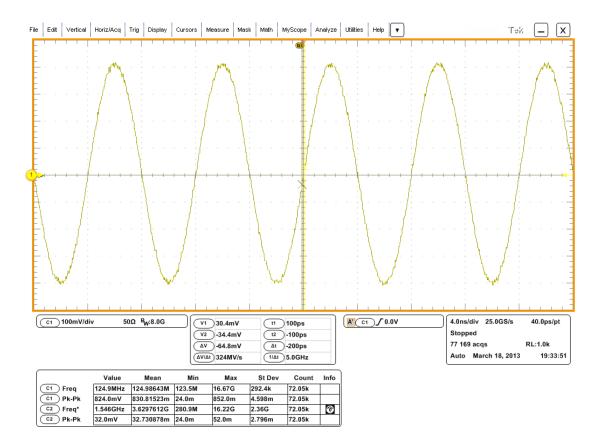

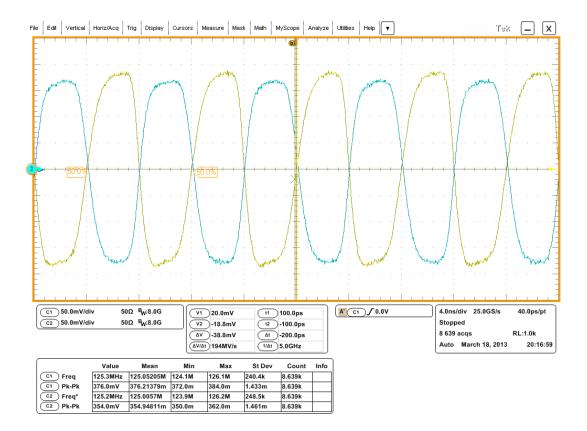

### 3.3 Circuit Architectures