## Analysis and Design of Clock-glitch Fault Injection within an FPGA

by

Masoumeh Dadjou

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2013

© Masoumeh Dadjou 2013

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

In modern cryptanalysis, an active attacker may induce errors during the computation of a cryptographic algorithm and exploit the faulty results to extract information about the secret key in embedded systems. This kind of attack is called a fault attack. There have been various attack mechanisms with different fault models proposed in the literature. Among them, clock glitch faults support practically dangerous fault attacks on cryptosystems. This thesis presents an FPGA-based practical testbed for characterizing exploitable clock glitch faults and uniformly evaluating cryptographic systems against them. Concentrating on Advanced Encryption Standard (AES), simulation and experimental results illustrates proper features for the clock glitches generated by the implemented on-chip glitch generator. These glitches can be injected reliably with acceptably accurate timing. The produced faults are random but their effect domain is finely controllable by the attacker. These features makes clock glitch faults practically suitable for future possible complete fault attacks on AES. This research is important for investigating the viability and analysis of fault injections on various cryptographic functions in future embedded systems.

#### Acknowledgements

I would like to express my sincere thanks to my supervisor, Prof. Cathy Gebotys, for her valuable advices, guidance and encouragement throughout my graduate studies. This thesis would not have been possible without her kind support and motivation.

In addition, thanks to my colleagues in Prof. Gebotys's laboratory at the University of Waterloo: Dr. Edgar Mateos Santillan, Dr. Marcio Juliato, Farhad Haghighizadeh, and Najma Jose for their encouragement and friendship. I would like to especially thank Edgar Mateos Santillan for his help with the laboratory part of this thesis.

Finally, I would like to express my deepest gratitude to my parents, Behrooz Dadjou and Zohreh Amiri, and my siblings, Hossein, Mahsa and Mahla, for their unconditional love and irreplaceable support throughout my life. This thesis is dedicated to my parents

$for \ their \ unconditional \ love, \ support \ and \ encouragement$

## **Table of Contents**

| Li | List of Tables vii |         |                                                                              |    |  |  |  |  |  |

|----|--------------------|---------|------------------------------------------------------------------------------|----|--|--|--|--|--|

| Li | st of              | Figure  | es                                                                           | ix |  |  |  |  |  |

| 1  | Intr               | oducti  | on                                                                           | 1  |  |  |  |  |  |

|    | 1.1                | Side C  | Channel Attacks                                                              | 2  |  |  |  |  |  |

|    |                    | 1.1.1   | Classifications of Side Channel Attacks                                      | 2  |  |  |  |  |  |

|    |                    | 1.1.2   | Fault Attacks                                                                | 4  |  |  |  |  |  |

|    | 1.2                | Introd  | uction to AES                                                                | 5  |  |  |  |  |  |

|    |                    | 1.2.1   | AES Functions                                                                | 5  |  |  |  |  |  |

|    |                    | 1.2.2   | Sbox Implementation                                                          | 10 |  |  |  |  |  |

|    | 1.3                | Thesis  | Overview                                                                     | 13 |  |  |  |  |  |

| 2  | Bac                | kgrour  | nd and related work                                                          | 14 |  |  |  |  |  |

|    | 2.1                | Fault i | injection method: The model and type of the fault $\ldots$ $\ldots$ $\ldots$ | 14 |  |  |  |  |  |

|    |                    | 2.1.1   | Fault types                                                                  | 14 |  |  |  |  |  |

|    |                    | 2.1.2   | Fault models                                                                 | 15 |  |  |  |  |  |

|    | 2.2                | Fault 1 | Injection Mechanisms                                                         | 15 |  |  |  |  |  |

|    |                    | 2.2.1   | Power Spikes                                                                 | 16 |  |  |  |  |  |

|    |                    | 2.2.2   | Optical Fault Injection                                                      | 16 |  |  |  |  |  |

|    |                    | 2.2.3   | Electromagnetic Attack                                                       | 17 |  |  |  |  |  |

|   |       | 2.2.4 Clock Glitches                                                 | 17 |

|---|-------|----------------------------------------------------------------------|----|

|   | 2.3   | Previous Fault Attacks on AES                                        | 18 |

|   | 2.4   | Attacking the AES State rather than Key schedule                     | 25 |

|   | 2.5   | Summary                                                              | 27 |

| 3 | Exp   | perimental Setup                                                     | 28 |

|   | 3.1   | Using the clock glitch to inject the fault                           | 28 |

|   | 3.2   | Clock glitch generating on FPGA                                      | 30 |

|   |       | 3.2.1 Comparison to previous clock glitch generators                 | 33 |

|   | 3.3   | Experimental setup                                                   | 34 |

|   |       | 3.3.1 The target cryptographic device                                | 34 |

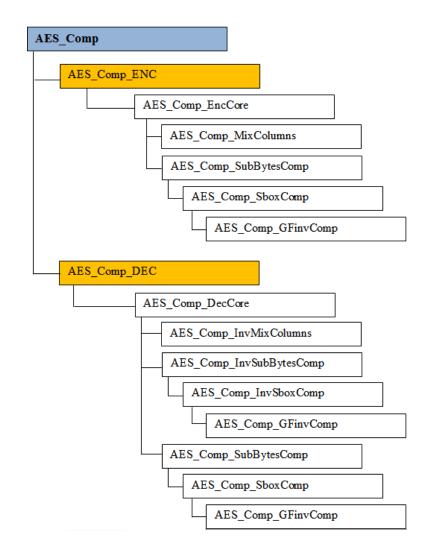

|   |       | 3.3.2 The target AES architecture                                    | 36 |

|   | 3.4   | Summary                                                              | 36 |

| 4 | Exp   | perimental Results                                                   | 38 |

|   | 4.1   | Fault injection simulation in an Sbox architecture                   | 38 |

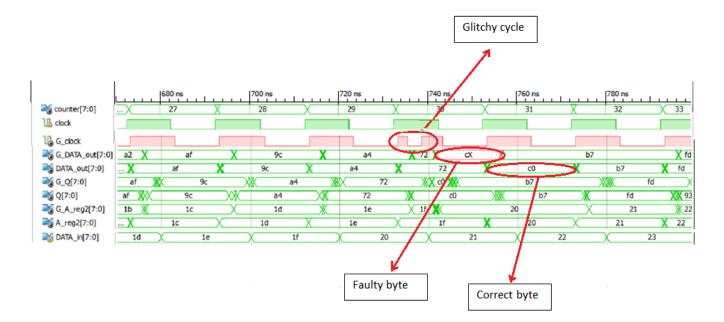

|   |       | 4.1.1 Simulation result for the Sbox with a glitchy-cycle clock      | 38 |

|   | 4.2   | Fault injection in the last round of the AES implementation $\ldots$ | 41 |

|   |       | 4.2.1 The number of faulty bytes and bits                            | 43 |

|   |       | 4.2.2 The position of faulty bytes and bits                          | 45 |

|   |       | 4.2.3 Repeating the experiment with a different set of plaintext     | 48 |

|   | 4.3   | Fault injection in the penultimate round of the AES implementation   | 53 |

|   | 4.4   | The Effect of Heating the device                                     | 53 |

|   | 4.5   | Summary                                                              | 54 |

| 5 | Dis   | cussion and Conclusions                                              | 55 |

|   | 5.1   | Summary and Discussion                                               | 55 |

|   | 5.2   | Conclusion and Future Work                                           | 57 |

| R | efere | nces                                                                 | 59 |

## List of Tables

| 1.1 | Key-Block-Round Combinations [37]                                                       | 5  |

|-----|-----------------------------------------------------------------------------------------|----|

| 2.1 | Classification of fault attacks into two classes: DFA on datapath, DFA on key schedule. | 26 |

| 2.2 | Optimal results of DFA on AES-128 [45]                                                  | 27 |

## List of Figures

| 1.1  | The Black Box view in traditional cryptography                                 | 2  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | The Side channel view of the cryptography                                      | 3  |

| 1.3  | AES encryption process                                                         | 6  |

| 1.4  | SubBytes [37]                                                                  | 7  |

| 1.5  | ShiftRows transformation [37]                                                  | 7  |

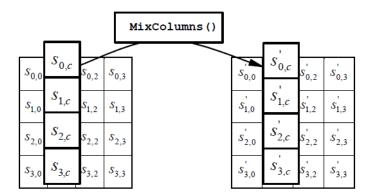

| 1.6  | MixColumns transformation [37]                                                 | 8  |

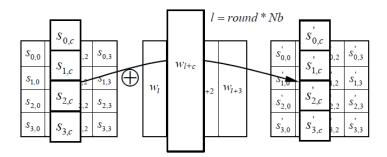

| 1.7  | AddRoundKey transformation [37]                                                | 9  |

| 1.8  | Pseudo code of the KeyExpansion schedule in AES_128 [17]                       | 9  |

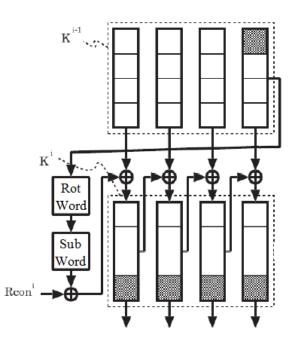

| 1.9  | The block diagram of the Key<br>Expansion schedule in AES_128 $\ldots$         | 10 |

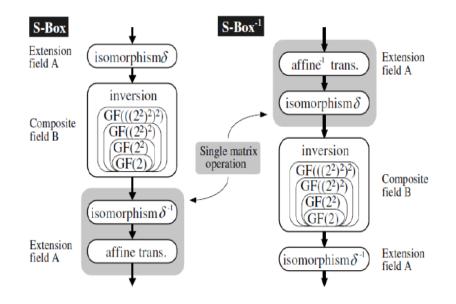

| 1.10 | Computation sequence of S-box implementation [43]                              | 11 |

| 2.1  | An smartcard contact assignment according to ISO 7816-2 [1]                    | 17 |

| 2.2  | The effect of the fault injected between rounds 8 and 7 $\ldots \ldots \ldots$ | 24 |

| 3.1  | Combinatorial logic and synchronous representation of a digital IC $[6]$ $$ .  | 29 |

| 3.2  | Latching the data with normal and glitchy clock $[20]$                         | 30 |

| 3.3  | Delay Locked Loop (DLL) in Virtex FPGAs [2]                                    | 32 |

| 3.4  | DLL output signals from ISE software before the LOCKED signal activates.       | 32 |

| 3.5  | Delay line taps $[3]$                                                          | 33 |

| 3.6  | Timing chart of the glitch generator                                           | 34 |

| 3.7  | Block diagram of SASEBO-GII board [4]                                          | 35 |

| 3.8  | The hierarchy of the AES code used in fault injection experiments                                                                                                                                    | 37 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

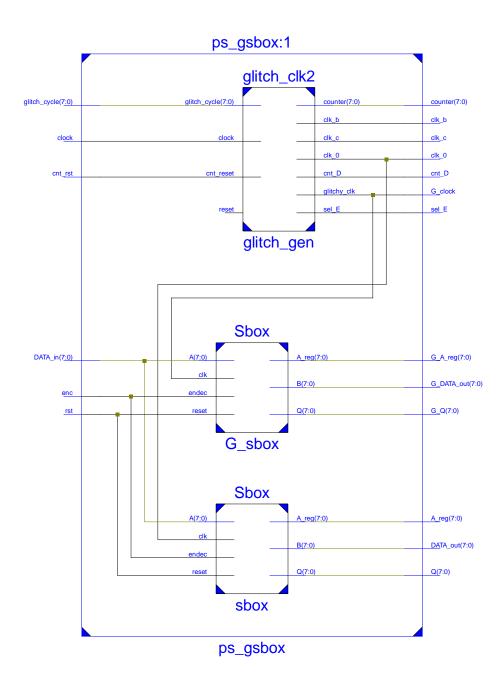

| 4.1  | The RTL view of the Sbox design with a glitch generator.                                                                                                                                             | 39 |

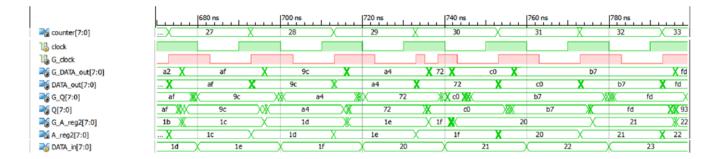

| 4.2  | The waveform from the post-route timing simulation. It shows the outputs and the intermediate values from both normal and faulty Sbox modules.                                                       | 41 |

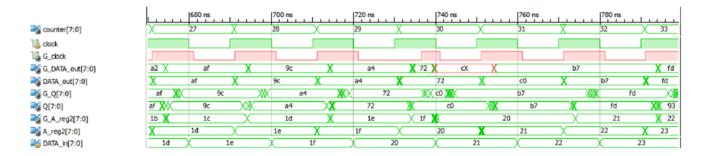

| 4.3  | A case where the ISE software cannot display the glitch but its effect is obvious in the waveform.                                                                                                   | 42 |

| 4.4  | A case where the ISE software cannot recognize the glitch as a clock and no fault is generated.                                                                                                      | 42 |

| 4.5  | A case where the glitch does not cause a fault in the Sbox output. $\ldots$                                                                                                                          | 42 |

| 4.6  | The SASEBO_AES_Checker software screen                                                                                                                                                               | 44 |

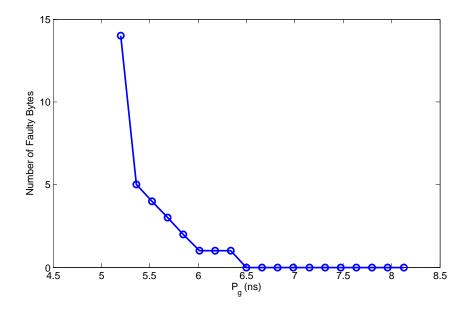

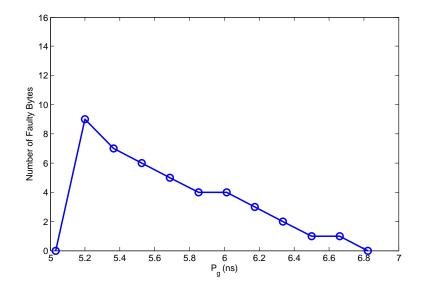

| 4.7  | The number of faulty bytes when the glitch is injected in round 10                                                                                                                                   | 46 |

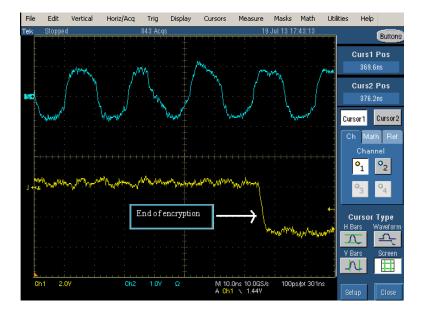

| 4.8  | The experiment environment cannot generate a glitch in the glitchy clock signal (the upper signal) with a very short interval. The lower signal is the BSY output which shows the end of encryption. | 47 |

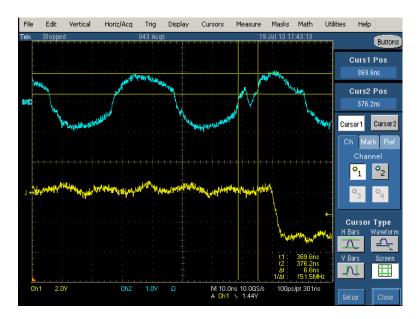

| 4.9  | The period of the clock glitch is 6.6ns. Glitch is treated as a normal clock and there is no fault in the output. Upper: glitchy clock, lower: BSY signal.                                           | 47 |

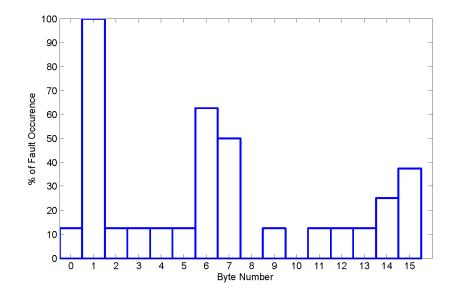

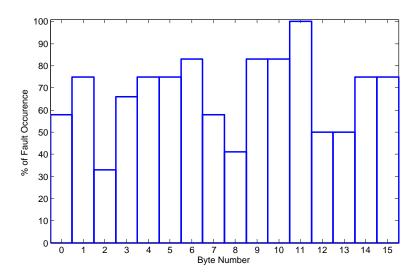

| 4.10 | Position of faulty bytes when the glitch is injected in round 10 $\ldots$ .                                                                                                                          | 48 |

| 4.11 | The number of faulty bytes when the glitch is injected in round 10 for a second set of plaintexts                                                                                                    | 49 |

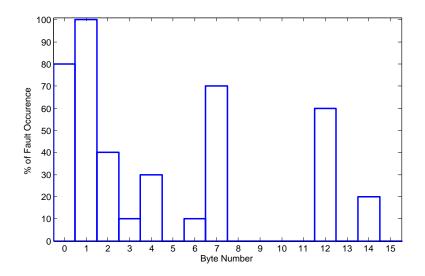

| 4.12 | Position of faulty bytes when the glitch is injected in round 10 for a second set of plaintexts                                                                                                      | 50 |

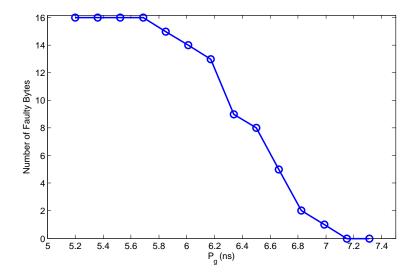

| 4.13 | The number of faulty bytes when the glitch is injected in round 9 $\ldots$ .                                                                                                                         | 51 |

| 4.14 | Position of faulty bytes when the glitch is injected in round 9                                                                                                                                      | 51 |

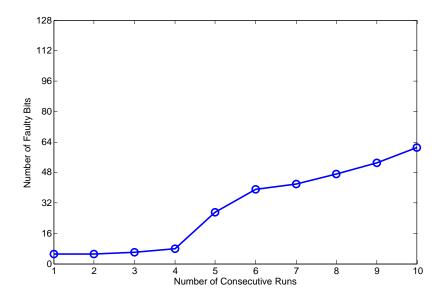

| 4.15 | Reprogramming the FPGA increases the board temperature, and the number of output faulty bits as the result                                                                                           | 52 |

## Chapter 1

## Introduction

Security is a major concern in computing, communication systems, and e-commerce among others and significant ongoing research is underway to address this concern. Cryptographic algorithms such as symmetric ciphers, public-key ciphers, and hash functions are used to construct security mechanisms. Modern cryptography relies on the assumption that cryptography primitives are perfectly secure; however, it is an unproven assumption. For example, public-key cryptosystem is based on the idea of one-way functions–functions which are easy to compute but computationally infeasible to invert. But, it has not been proven that the functions used in public-key cryptosystem are one-way functions or even whether one-way functions really exist. Still, some cryptographic algorithms are unbroken and remain widely used. Hence, some algorithms are assumed to be secure and unbreakable.

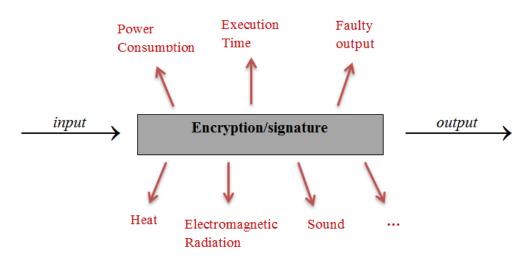

Cryptographic algorithms can be viewed from two perspectives: classical and side channel. From a classical perspective, they are perceived as a mathematical object which receives a plaintext or message and using a key, transforms the input into a ciphertext or vice-versa. The adversaries are assumed to have a complete understanding of the underlying algorithm and access to both ciphertext and plaintext. In addition, they may have more control over the exchanged data between the two parties e.g., by selecting the plaintexts in a chosen-plaintext attack, or by selecting the ciphertexts in a chosen-ciphertext attack. The attackers are only lacking knowledge of the secret key. This is the black-box view depicted in figure 1.1 in which the attacker attempts to solve the underlying problems– assumed to be computationally intractable–in the cryptographic protocol by exploiting the mathematical specifications without necessarily having to implement the algorithms and use the system.

Figure 1.1: The Black Box view in traditional cryptography

## 1.1 Side Channel Attacks

In the real world, cryptographic protocols have to be implemented in software or hardware on a device which interacts with its environment. This interaction with the environment can be monitored by the adversary. For example, the device gives information about the time or power consumption of operations and produces sounds or electromagnetic radiations during the computations. In addition, the device may have some unintentional inputs such as voltage or clock frequency which may be modified to create predictable or faulty outputs. Such information leakage during the protocols execution is called the side channel which is not considered in the classical security model. Figure 1.2 represents the cryptographic view including side channels. In side channel analysis (SCA), the adversary goes beyond the pure mathematics and takes advantage of side channel information to recover the secret key. This kind of attack, which was presented in 1996 by Kocher [33] for the first time, works because, the state of the cryptographic device, which is related to the secret key, can be correlated with the measured side channel information.

## 1.1.1 Classifications of Side Channel Attacks

Side-channel attacks can be classified into the following three categories where these categories are orthogonal i.e. a specific type of attack can be in more than one category [49].

### Control over the process: Passive vs. Active

The first category is based on the level of control over the process execution and divides the SCA attacks into **passive attacks** and **active attacks**. In a passive attack, the attacker does not interfere with the device's computation and gains information by simply observing the device behavior, which is exactly as if there is no attack. Passive attacks are

Figure 1.2: The Side channel view of the cryptography

based on the observation and analysis of various measurable side channels including power consumption, computation time, and electromagnetic or radio frequency emanation of the device. They use the correlation between the operations, processed data and collected measures. While in an active attack, the attacker tampers with the functioning device and tries to affect its behavior. Active attacks are based on interrupting the algorithm process to cause an abnormal behavior or erroneous result that can be exploited to recover the secret key.

### Access to the device: Invasive vs. Non-invasive

Depending on the attack surface (the set of physical, electrical and logical interfaces that are exposed to a potential adversary) Anderson et al. in [4] divided the attacks into three classes: *invasive attacks*, *semi-invasive attacks* and *non-invasive attacks*. Invasive attacks require depackaging the device to have direct access to its components, for example, placing a probing needle on a data bus to see the data transfer. A noninvasive attack is usually an undetectable and low-cost attack that only uses the sidechannel information which is externally available. Timing analysis and power consumption analysis are in this class. The semi-invasive attack involves depackaging of the device to get access to its surface, but does not require electrical contact to the metal layer. For example, in a fault induction attack, the attacker may use a laser beam to ionize a device and change some of its memories to change the output.

#### Analysis process: Simple vs. Differential

The sampled data in a side-channel attack needs to be analyzed to reveal information about the secret key. In the analysis process, if a single side-channel trace is used and the secret key is directly related to that trace, the attack is referred to as a *simple side channel attack (SSCA)*. While, if due to too much noise in the measurements SSCA is not feasible, a *differential side channel attack (DSCA)* is used. In DSCA many traces are used to exploit the correlation between the processed data and the side-channel leakage. Since this correlation is usually small, statistical methods are needed to exploit it efficiently.

## 1.1.2 Fault Attacks

A fault attack is a fundamentally different kind of side-channel attack. Here, the adversary induces faults into the device during the computation of a cryptographic algorithm and observes its behavior. Other side-channel attacks are passive in which there is no tampering with the attacked device. While, a fault attack is an active attack which aims at recovering the secret key by altering the computation process and analyzing the faulty output or reaction of the system.

The first successful fault attacks have been reported by Boneh et al. in 1997 [14] and later in 2001 on the RSA signature scheme, the Fiat-Shamir and Schnorr identification protocols [15]. They injected random hardware faults and showed that an RSA implementation based on the Chinese Remainder Theorem (CRT) can be broken using a single erroneous RSA signature. A non-CRT implementation of RSA needs a larger number (e.g. 1000) of erroneous signatures. Their results also illustrates that the secret key can be revealed in Fiat-Shamir and Schnorr identification protocols after a small number (e.g. 10) and a larger number (e.g. 10000) of faulty executions respectively. Fault attack on ElGamal, Schnorr and digital signature algorithm (DSA) was presented by Bao et al. in 1998[9]. Biehl et al. in 2000[11] presented the fault attacks on elliptic curve public-key encryption. In 1997 Biham and Shamir[12] described fault attacks on the DES symmetric-key encryption. Transient faults or glitches were discussed by Anderson and Huhn in 1997[7]. In 2002 Skorobogatov and Anderson[46] proposed a powerful and practical optical fault attack using inexpensive equipment on a smartcard.

The fault attacks mentioned above indicate that this kind of attack may be practical and very realistic to mount, although more advanced knowledge and tools are needed.

| Table 1.1: | Key-Block-Round Combinations | $\lfloor 37 \rfloor$ |  |

|------------|------------------------------|----------------------|--|

|------------|------------------------------|----------------------|--|

|         | Key Length (Nk words) | Block Size (Nb words) | Number of Rounds (Nr) |

|---------|-----------------------|-----------------------|-----------------------|

| AES-128 | 4                     | 4                     | 10                    |

| AES-192 | 6                     | 4                     | 12                    |

| AES-256 | 8                     | 4                     | 14                    |

Thus, these fault attacks may be much more effective and dangerous. Fault attacks can break an unprotected system more quickly than any other kind of side-channel attack such as power analysis or electromagnetic analysis. For example, the attacker can break RSA-CRT with one faulty result, and DES and AES with two. Furthermore, the fault attack countermeasures are more costly in terms of chip area. Hence, they must be taken into account during the design and test of secure systems and devices.

## **1.2** Introduction to AES

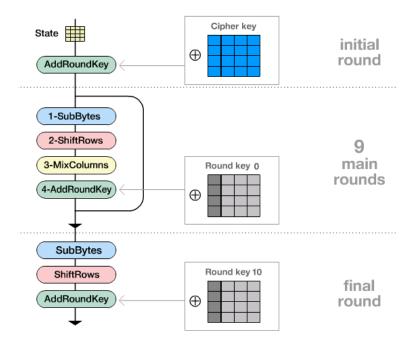

The Advanced Encryption Standard (AES) algorithm is a symmetric 128-bit block cipher with a key of length 128, 192 or 256, and the corresponding number of rounds for each is 10, 12, and 14 rounds respectively. The Key-Block-Round combinations is given in Table 1.1. From the original key, a different round key is computed for each of these rounds. Consider the key length of 128 bits and hence 10 rounds. AES operates on a  $4 \times 4$  array of bytes named a state. This state undergoes 4 transformations in each round, in order, called **SubBytes**, **ShiftRows**, **MixColumns**, and **AddRoundKey**. Before the first round (round 0), the block is processed by AddRoundKey. The last round (round 10) skips the MixColumns step. The complete description of the algorithm can be found in [37]. Figure 1.3 shows the encryption process in AES algorithm.

## **1.2.1 AES Functions**

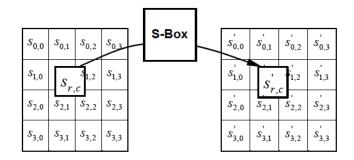

#### SubBytes

SubByte transformation is a highly nonlinear byte substitution where each byte is replaced with another from a look up table called Sbox. This nonlinear function involves finding the

Figure 1.3: AES encryption process

inverse of the 8-bit numbers as elements of the Galois Field  $GF(2^8)$ . The Sbox function of an input byte *a* is defined by two substeps:

1.  $b = a^{-1}$ : Multiplication inverse in  $GF(2^8)$  (inverse of 0 is 0)

2. a' = M.b + c: Affine transformation (linear plus a constant)

Figure 1.4 depicts the SubBytes transformation on the State. The affine transformation element of the Sbox can be expressed as:

$$\begin{pmatrix} a_0' \\ a_1' \\ a_2' \\ a_3' \\ a_4' \\ a_5' \\ a_6' \\ a_7' \end{pmatrix} = \begin{pmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 1 \end{pmatrix} \begin{pmatrix} b_0 \\ b_1 \\ b_2 \\ b_3 \\ b_4 \\ b_5 \\ b_6 \\ b_7 \end{pmatrix} + \begin{pmatrix} 1 \\ 1 \\ 0 \\ 0 \\ 0 \\ 1 \\ 1 \\ 0 \end{pmatrix}$$

Figure 1.4: SubBytes [37]

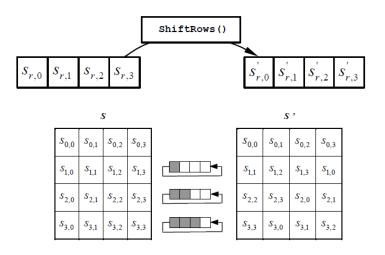

Figure 1.5: ShiftRows transformation [37]

### ShiftRows

The ShiftRows transformation cyclically shifts the last three rows in the State and the first row, r = 0, is not shifted. The effect is moving the bytes to lower position in the row as illustrated in Figure 1.5.

### MixColumns

In MixColumns, each column of the State is treated as a polynomial over  $GF(2^8)$  and multiplied with a fixed polynomial a(x) modulo  $x^4 + 1$  where  $s'(x) = a(x) \otimes s(x)$  and:

Figure 1.6: MixColumns transformation [37]

$$a(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$$

The matrix multiplication is as follows and the MixColumns transformation is illustrated in Figure 1.6

$$\begin{pmatrix} s'_{0,c} \\ s'_{1,c} \\ s'_{2,c} \\ s'_{3,c} \end{pmatrix} = \begin{pmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 01 & 01 & 02 \end{pmatrix} \begin{pmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{pmatrix} for 0 \le c < Nb$$

### AddRoundKey

As Figure 1.7 shows, AddRoundKey transformation is simply a bitwise XOR between each column of the State and a word of the key matrix from the key schedule.

### **KeyExpansion**

The KeyExpansion schedule computes the round keys. Figure 1.8 shows the pseudo code of KeyExpansion and a block diagram of this function is displayed in Figure 1.9. The KeyExpansion consists of SubWord and RotWord functions and Rcon Table. The Sub-Word accepts a word as input, performs the SubBytes on each of the four bytes and returns a word. The Rotword applies a cyclic permutation on a word  $(s_0, s_1, s_2, s_3)$  and outputs the word  $(s_1, s_2, s_3, s_0)$ . Rcon is a constant word array which contains the values  $(x^{i-1}, 0, 0, 0), i \in 1, 2, 3, 4$ .

Figure 1.7: AddRoundKey transformation [37]

|    | key[]: The input 16-byte key.                                                |

|----|------------------------------------------------------------------------------|

|    | $w[]\colon$ The resulting round keys, stored in an array of four-byte words. |

| 01 | KeyExpansion(byte $key$ [16], word $w$ [44]){                                |

| 02 | word temp;                                                                   |

| 03 | for $(i = 0; i < 4; i++)$                                                    |

| 04 | w[i] = (key[4*i], key[4*i+1], key[4*i+2], key[4*i+3]);                       |

| 05 | for $(i = 4; i < 11; i++)$ {                                                 |

| 06 | temp = w[i-1];                                                               |

| 07 | if $(i \mod 4 == 0)$                                                         |

| 08 | $temp$ = SubWord(RotWord( $temp$ )) $\oplus$ Rcon[ $i/4$ ];                  |

| 09 | $w[i] = w[i-4] \oplus temp;$                                                 |

| 10 | }                                                                            |

| 11 | }                                                                            |

Figure 1.8: Pseudo code of the Key Expansion schedule in AES\_128  $\left[17\right]$

Figure 1.9: The block diagram of the KeyExpansion schedule in AES\_128

## 1.2.2 Sbox Implementation

One of the most common and straight forward implementations of the S-box was to have the pre-computed values stored in a ROM based look-up table (LUT) in which the substitution bytes of all possible bytes are stored in a table. However, there are two drawbacks for the LUT-based approach:

- All 256 possible values of a byte are stored in a ROM and the input byte would be wired to the ROM's address bus. This method suffers from a fixed delay since ROMs have a fixed access time for read and write operations.

- Each copy of the table requires 256 bytes of storage, along with the circuitry to address the table. Each of the 16 bytes can go through the S-box function independently. This then effectively requires 16 copies of the S-box table for one round. To fully pipeline, the encryption would require unrolling the loop of 10 rounds into 10 sequential copies of the round calculation. This needs 160 copies of the S-box table, a significant allocation of hardware resources.

Figure 1.10: Computation sequence of S-box implementation [43].

Designing a compact S-box is one of the most critical problems for reducing the total circuit size of AES hardware. It is possible to implement the S-box as a particular circuit based on its functional specification by using automatic logic synthesis tools. However, in [42] a significant reduction in the size of the S-box was achieved, by using composite field arithmetic. In [43], they have proposed further optimization of S-box by introducing a new composite field based on Polynomial Basis (PB). Figure 1.10 shows the outline of such S-box implementation.

The most costly operation in the S-box is the multiplicative inversion over a field A, where A is an extension field over  $GF(2^8)$  with the irreducible polynomial  $m(x) = x^8 + x^4 + x^3 + x + 1$ . We performed the composite field arithmetic to calculate the multiplication inversion of the Sbox under Normal Basis (NB) rather than polynomial basis, which is done in previous works. This is done by decomposing  $GF(2^8)$  to  $GF(2^8)/GF(2^4)/GF(2^2)/GF(2)$ , performing the required calculations and then, bringing the result to  $GF(2^8)$ . The following 3-stage method is to be adopted to reduce the cost of the inversion operation [43]:

1. Map all elements of the field A to a composite field B , using an isomorphism function  $\delta^{-1}.$

- 2. Compute the multiplicative inverse over the field B.

- 3. Re-map the computation results to A, using the function  $\delta$ .

The composite field B in stage 2 is constructed not by applying a single degree-8 extension to GF (2), but by applying multiple extensions of smaller degrees. To reduce the cost of stage 2 as much as possible, the composite field B is built by repeating degree-2 extensions under a normal basis through the following steps:

- 1. Isomorphism between  $GF(2^8)$  and  $GF(2^8)/GF(2^4)$ : NB= $\{U^{16}, U\}, A \in GF(2^8) \Rightarrow A = r_1U^{16} + r_0U$ , where  $r_0, r_1 \in GF(2^4)$ . Irreducible polynomial:  $u^2 + u + \lambda = (u + U)(u + U^{16})$ .

- 2. Isomorphism between  $GF(2^4)$  and  $GF(2^4)/GF(2^2)$ :  $NB = \{V^4, V\}, r \in GF(2^4) \Rightarrow r = x_1V^4 + x_0V$ , where  $x_0, x_1 \in GF(2^2)$ . Irreducible polynomial:  $v^2 + v + \phi = (v + V)(v + V^4)$ .

- 3. Isomorphism between  $GF(2^2)$  and  $GF(2^2)/GF(2)$ :  $NB = \{W^2, W\}, x \in GF(2^2) \Rightarrow x = p_1W^2 + p_0W$  where  $p_0, p_1 \in GF(2) = \{0, 1\}$ . Irreducible polynomial:  $w^2 + w + 1 = (w + W)(w + W^2)$ .

To change bases we need an  $8 \times 8$  multiplication bit matrix.  $\delta^{-1}$  refers to the matrix that converts a given byte  $(a_7, a_6, a_5, a_4, a_3, a_2, a_1, a_0)$  as an element of  $GF(2^8)$ , from the standard basis into the subfield basis. Likewise,  $\delta$  represents the matrix to convert from the subfield basis into the standard basis.

| $p_7$ |                | $\langle a_7 \rangle$ |       | $\langle a_7 \rangle$ |           | $p_7$ |

|-------|----------------|-----------------------|-------|-----------------------|-----------|-------|

| $p_6$ |                | $a_6$                 |       | $a_6$                 |           | $p_6$ |

| $p_5$ |                | $a_5$                 |       | $a_5$                 |           | $p_5$ |

| $p_4$ | $=\delta^{-1}$ | $a_4$                 | , and | $a_4$                 | $=\delta$ | $p_4$ |

| $p_3$ | _ 0            | $a_3$                 | , and | $a_3$                 | - 0       | $p_3$ |

| $p_2$ |                | $a_2$                 |       | $a_2$                 |           | $p_2$ |

| $p_1$ |                | $a_1$                 |       | $a_1$                 |           | $p_1$ |

| $p_0$ |                | $\langle a_0 \rangle$ |       | $\langle a_0 \rangle$ |           | $p_0$ |

Where,

|                | /1            | 1 | 1 | 0 | 0 | 1 | 1 | 1  |                   | /0                 | 0 | 0 | 1 | 0 | 0 | 1 | 0  |

|----------------|---------------|---|---|---|---|---|---|----|-------------------|--------------------|---|---|---|---|---|---|----|

|                | 0             | 1 | 1 | 1 | 0 | 0 | 0 | 1  |                   | 1                  | 1 | 1 | 0 | 1 | 0 | 1 | 1  |

|                | 0             | 1 | 1 | 0 | 0 | 0 | 1 | 1  |                   | 1                  | 1 | 1 | 0 | 1 | 1 | 0 | 1  |

| $\lambda^{-1}$ | 1             | 1 | 1 | 0 | 0 | 0 | 0 | 1  | and $\delta$ –    | 0                  | 1 | 0 | 0 | 0 | 0 | 1 | 0  |

| 0 —            | 1             | 0 | 0 | 1 | 1 | 0 | 1 | 1  | $, and, \delta =$ | 0                  | 1 | 1 | 1 | 1 | 1 | 1 | 0  |

|                | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 1  |                   | 1                  | 0 | 1 | 1 | 0 | 0 | 1 | 0  |

|                | 0             | 1 | 1 | 0 | 0 | 0 | 0 | 1  |                   | 0                  | 0 | 1 | 0 | 0 | 0 | 1 | 0  |

|                | $\setminus 0$ | 1 | 0 | 0 | 1 | 1 | 1 | 1/ |                   | $\left( 0 \right)$ | 0 | 0 | 0 | 0 | 1 | 0 | 0/ |

## 1.3 Thesis Overview

This thesis focuses on a particular fault attack called the glitch attach in which a glitch is generated in the input clock signal and the targeted cryptosystem is the Advanced Encryption Standard (AES). The effect of the glitchy clock cycle on the registered values in the output registers and how it can be used to recover the secret key is explored in this thesis.

The thesis is organized as follows: Chapter 2 introduces the fault type and models, and presents a survey on the most important approaches to create fault injection, including: power spikes, clock glitches, electromagnetic and optical fault injections. This is followed by an literature review on previous fault attacks applied on AES focused on the attack method used, complexity and results. Chapter 3 illustrates the experimental setup by explaining the fault model, how to use the glitch characteristics, and how to generate the desired glitch accurately. It continues by introducing the cryptographic board and the target AES architecture. The simulation results for an Sbox architecture based on normal basis, and experimental result for real fault injection in AES are presented in chapter 4. Finally, Chapter 5 provides a summary, conclusions and recommendations for future work.

## Chapter 2

## Background and related work

This chapter provides a review of fault injection methods by introducing fault types and models. This is followed by a discussion of the most common fault injection mechanisms and surveying previous fault attacks against AES. Finally, attacking the AES datapath rather than key schedule is discussed.

# 2.1 Fault injection method: The model and type of the fault

There has been a large variety of fault attacks reported in the literature. The difference between them is based on their *fault types* and *fault models*.

## 2.1.1 Fault types

There are two different fault types based on the durability of the effect of the attack: permanent faults and transient faults.

- **Permanent faults** A permanent fault certainly changes the value of a cell and the behavior of the device, and returning to the initial state is impossible. It can be caused by injecting a fault in a ROM or by using a laser cutter to cut a wire inside the chip.

- **Transient faults** A transient fault is a provisional fault in which the device can return to its initial state and resume its original behavior after a short time, for example, by

resetting the circuit or ceasing the fault's stimulus. The transient fault in a memory block, RAM, causes the fault to be memorized and the modified value lasts until overwriting the variable holding it.

## 2.1.2 Fault models

Attackers must know the fault model they are going to inject in a proposed attack and then use it in practice. This knowledge helps to distinguish whether or not the proposed attack is practical. The most important factors indicating a fault model are as follows[29]:

- Bit vs. byte fault In fault attacks it is plausible to affect the value of only one bit or one byte. Modifying a single bit is more difficult and needs more precise equipments but makes it possible to break almost all ciphers. On the other hand, since the storage or transferring the data is done in the byte level, the attacks modifying a byte are more practical.

- **Specific vs. random fault** In this category the attackers determine if they assume to change the bit or byte value to a specific or random value. In practice, it is easier to inject a random value fault.

- Static vs. computational fault If the attack aims to change the value of the memory itself, for example flipping a secret key bit in the memory, it is of the static model, which is usually difficult in practice. On the other hand, computational faults occur when inducing a fault during an operation computation and is easier than the static one to inject.

- **Data vs. control fault** When the fault causes an omission of an instruction or iteration, it is of the control fault group. Whereas, modifying the data is more common in attacking on the secret key or the intermediate states.

## 2.2 Fault Injection Mechanisms

In a cryptographic device there are flip flops to define the current state, and combinational logic to calculate the next state from the current state in each clock cycle [31]. There are also input clock and voltage, transistor current, among others with many analog effects that can be used in non-invasive attacks like the following:

## 2.2.1 Power Spikes

Embedded systems such as smartcards need power supply which is provided externally. Variations in the supply voltage can impede the device's functionality with misinterpretation or omission of instructions as well as data misread. It enables an adversary to both tamper with the power feeding and measuring the power consumption.

According to the "Electronic signals and transmission protocols" standard, ISO/IEC 7816-3, a smartcard must tolerate the power supply variation of  $\pm 10\%$  of the standard voltage. For variations higher than 10%, the system no longer works properly. **Spikes** are short massive variations of the power supply and can be used to induce faults during the computation of the smartcard. Spikes do not require a modification of the device itself but provoke faults by modifying the working conditions. They have different effects depending on different parameters including time, voltage value, and the transition shape. A spike attack is a non-invasive, or at least semi-invasive, method which can lead to wrong computation result when the device is still able to complete the computation. Experimental results for injecting faults into smartcards using spikes are described in details in [8].

## 2.2.2 Optical Fault Injection

Due to the photoelectric effects, the semiconductor transistors and the EEPROM are sensitive to lasers and ion-beams and the memory cells can be set to 0[46]. In [31], they depackage the device and use an optical microscope to reconstruct the layout and apply invasive fault attacks including laser cutting and focused ion-beam manipulation to recover the covered data. But it was not sufficiently precise to change the chosen bits. The attacker needs to be able to control the light's wavelength, energy, location, and emission time. In 2008, Hutter at al. [24] described a precise locolized fault injection method with affordable equipments which enables them to interfere data, control lines, memory blocks and driver circuits. This method is the underlying method used in a fault analysis attack against HB+ authentication protocol used in radio-frequency identification (RFID) tags [16]. In 2010, Agoyan et al.[5] showed that it is possible to reproduce single-bit faults on SRAM which was considered unfeasible before. In addition, today the laser attack can be applied to the back side of the chip where there is no protecting mechanism.

Figure 2.1: An smartcard contact assignment according to ISO 7816-2 [1]

### 2.2.3 Electromagnetic Attack

Emitting a powerful magnetic pulse close to the silicon area of the cryptographic device is another way to inject faults. This emission creates local current called Eddy current on the component's surface. Eddy current can modify the number of electrons inside a transistor's oxide grid and change its threshold voltage. As a result it impedes the transistor's switching and ensures the attacker that a memory cell contains the value 1 or 0[38]. Another usage of the Eddy current is to heat a material uniformly and hence, to generate transient or permanent faults by inducing the heat.

This attack can be performed on small parts of the device if the attacker has the knowledge of the layout of the device to control the targeted area precisely. As reported in [40], Eddy current can enable the adversary to induce faults very accurately and even set or reset the individual selected bits. Hence, it has been considered a practical method [25].

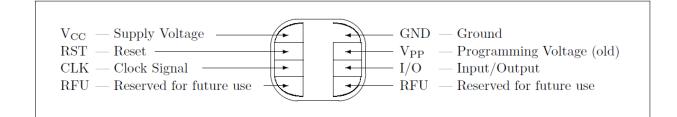

### 2.2.4 Clock Glitches

As shown in figure 2.1, cryptographic devices such as smartcards have an external clock signal. According to the ISO/IEC 7816-3, a smartcard must work properly in the clock signal with voltage variation in the range of 0.7 Vcc to Vcc for the high signal and 0 to 0.5 Vcc for low signal. Another constraint is to tolerate the clock rise and the clock fall times of 9% from the period cycle. A deviation of the external clock which is out of the specified tolerance scope is called *glitch*. Glitches may be generated by temporarily increasing the clock frequency in one or a half cycle. Clock glitch can cause data misread in which the circuit samples the input before it gets the new state or reads the values from the data bus before being latched into the memory. The other possible effect can be the omission

of instructions in which the next instruction starts executing before finishing the current one. As presented by Agoyan et al. in [6], injecting the fault by clock glitches is currently the simplest and most practical fault attack.

## 2.3 Previous Fault Attacks on AES

This sections reviews past research in fault analysis attacks on AES, attacking both the AES datapath as well as the AES key expansion circuitry.

## Fault based cryptanalysis of the Advanced Encryption Standard (AES), Blomer-Seifert [13]

A fault attack against AES using an optical fault injection method (from [46]) has been demonstrated in [13]. The attack was implementation independent and it recovered the complete 128-bit AES cipher key by generating 128 faulty ciphertexts. First, they consider the case where the block length is greater than or equal to the key length 128 ( $Nb \ge Nk$ ). In this case the complete cipher key is used in the initial AddRoundKey. The cipher key is stored in a  $4 \times 4$  array of bytes  $k_{ij}$  and the l - th bit of the byte is denoted by  $k_{ij}^l$  where  $0 \le l \le 7$  and  $0 \le i, j \le 3$ . The attack encrypts a block of plaintext where each bit has the value of 0. Then the initial AddRoundKey transformation will be performed as

$$s_{ij} = 0 \oplus k_{ij} = k_{ij}$$

Before the next transformation, the attacker tries to set  $s_{ij}^l$  to 0 and let the encryption process proceed without further fault injection. If  $k_{ij}^l = 0$  then the encryption results the correct ciphertext as if there was no fault. But if  $k_{ij}^l = 1$ , setting the state bit to 0 affects the temporary state and causes an incorrect ciphertext or resetting the device—if the device can detect the corruption and reset itself. Hence, with one encryption process the value of  $k_{ij}^l$  can be deduced and the attacker can determine all bits of the cipher key by encrypting the null plaintext for 128 times, each time inducing a single fault.

If the key size is greater than the input block (Nk > Nb), the attack obtains the first 128 bits of the key as described above and then continues up to the next AddRoundKey in round 1. The plaintext can be chosen such a way that all bits of the state before the AddRoundKey are equal to 0. Then the attacker can set the remaining bits of the state one by one after the AddRoundKey of round 1. As before, if the ciphertext is correct the key bit  $k_{ij}^l$  is 0, otherwise  $k_{ij}^l = 1$ .

### DFA on AES, Giraud [21]

Giraud [21] presents two different differential fault analysis (DFA) attacks on AES. In the first attack, the fault model is a single-bit fault which must occur right before the SubByte transformation in the last round. If C denotes the correct ciphertext and  $C^*$  the faulty ciphertext, the following equations hold:

$$\begin{cases} \delta = C^i \oplus C^{*i}, \\ \delta = (SubBytes[S] \oplus K^{10}) \oplus (SubBytes[S'] \oplus K^{10}). \end{cases}$$

where fault is injected in i - th byte, S is the correct byte and S' is the faulty byte. If the following two conditions hold:

- $\delta = SubBytes[S] \oplus SubBytes[S']$

- one bit fault  $:S \oplus S' = 2^i, i \in 0, ..., 7$

then, by an exhaustive search for the couple of (S, S'), a list of possible key bytes can be computed such that  $K^i = SubBytes[S] \oplus C^i$ .

Each pair of (S, S') gives one possible key which is put in a list  $\alpha$ . If the number of guessed keys is more than one, this process will be repeated with a new plaintext and generate a new set  $\beta$ . Taking the intersection of these two sets and repeating the operation will eventually result in only one candidate left for the key. With the probability of about 97%, using three ciphertexts will be sufficient to recover one byte of the last round key. So, by less than 50 faulty ciphertexts the 128-bit AES key can be obtained. If the attacker has the ability to choose the affected byte, this attack can reach the key with only 35 faulty ciphertexts.

The second attack is more realistic because it assumes that the temporary fault affects a whole byte. The attacker aims to induce the fault in the Key Schedule unit and pursues the attack in 3 steps:

- 1. Before computing  $K^{10}$ , a fault is inserted in  $K^9$  and using the resulting ciphertexts, the last 4 bytes of  $K^9$  are obtained.

- 2. Before computing  $K^9$ , a fault is inserted in  $K^8$  and using the resulting ciphertexts, another 4 bytes of  $K^9$  are obtained.

- 3. Before starting round 9, a fault is inserted in  $S^8$  and using the resulting ciphertexts and the recovered 8 bytes of  $K^9$  the AES key will be obtained.

According to he author's claim, the complete key can be reached by less than 250 ciphertexts and in an extended scenario where the attacker can choose which byte to affect, the number of required faulty ciphertext is 31.

### Differential fault analysis on AES key schedule and some countermeasures, Chen and Yen

The attack presented in [17] uses the same method as the second attack in Giraud's publication [21], on the keypath instead of the datapath, to disclose the secret key but with less required ciphertexts. A fault is injected into one of the last four bytes (last word) of  $K^9$  which results in 5 faulty bytes in the last round key and consequently in the final output. Repeating this process for a few different faults and intersecting the results of solving the equations and statements from each process gives the exact values of these 5 key bytes. Then a fault is injected in the round key  $K^8$  in a different position (e.g. the penultimate word). It affects 6-7 output bytes and leads to guess another 8 key bytes. The remaining 3 bytes can be reached by a light exhaustive search. With an accurate fault inducing method, the whole AES secret key can be disclosed by exploiting less than 44 fault injections.

### Differential Fault Analysis on A.E.S, Dusart et al. [18]

The idea in this work is to first retrieve the last round key and then, using the invertibility feature of the AES key schedule, to retrieve the initial cipher key. It is assumed that the attacker can inject a random fault in a single byte before the last MixColumns operation. The fault is spread over only four bytes of the ciphertext which according to their location, the location of the fault can be deduced. Hence, the location of fault injection is not essential and the attack is highly realistic. Suppose F is the faulty state and the unknown fault  $\varepsilon$  is injected in the first element of the state. Then we will have

Then the effect of the fault will be as follows: After the MixColumns:

$$F_{9,MixColumns} = S_{9,MixColumns} + \begin{pmatrix} 2 \cdot \varepsilon & 0 & 0 & 0 \\ \varepsilon & 0 & 0 & 0 \\ \varepsilon & 0 & 0 & 0 \\ 3 \cdot \varepsilon & 0 & 0 & 0 \end{pmatrix}.$$

After the AddRoundKey:

$$F_{9,AddRoundKey} = S_{9,AddRoundKey} + \begin{pmatrix} 2 \cdot \varepsilon & 0 & 0 & 0 \\ \varepsilon & 0 & 0 & 0 \\ \varepsilon & 0 & 0 & 0 \\ 3 \cdot \varepsilon & 0 & 0 & 0 \end{pmatrix}.$$

After the last round SubBytes:

$$F_{10,SubBytes} = S_{10,SubBytes} + \begin{pmatrix} \dot{\varepsilon_0} & 0 & 0 & 0\\ \dot{\varepsilon_1} & 0 & 0 & 0\\ \dot{\varepsilon_2} & 0 & 0 & 0\\ \dot{\varepsilon_3} & 0 & 0 & 0 \end{pmatrix}.$$

After the last round ShiftRows:

$$F_{10,ShiftRows} = S_{10,ShiftRows} + \begin{pmatrix} \dot{\varepsilon_0} & 0 & 0 & 0\\ 0 & 0 & 0 & \dot{\varepsilon_1} \\ 0 & 0 & \dot{\varepsilon_2} & 0\\ 0 & \dot{\varepsilon_3} & 0 & 0 \end{pmatrix}.$$

And finally after the last round AddRoundKey:

$$F_{10,AddRoundKey} = S_{10,AddRoundKey} + \begin{pmatrix} \dot{\varepsilon_0} & 0 & 0 & 0\\ 0 & 0 & 0 & \dot{\varepsilon_1} \\ 0 & 0 & \dot{\varepsilon_2} & 0\\ 0 & \dot{\varepsilon_3} & 0 & 0 \end{pmatrix}.$$

As shown above, when a random byte fault is injected before the MixColumns operation, the fault will be spread over all four bytes of the same column. The subsequent AddRoundKey and the last round operations modify the bytes independently. The only operation that could exploit information about the last round key is the last SubBytes transformation because due to the nonlinearity, some assumptions can be made on the error value. We have the general equation

$$s(x+c.\varepsilon) + s(x) = \acute{\varepsilon}, \tag{2.1}$$

in which  $c \in 01, 02, 03$  and  $\varepsilon \in GF(2^8) - 0$ . The following four equations are driven from the above general equation:

$$\begin{cases} s(x_0 + 2 \cdot \varepsilon) = s(x_0) + \varepsilon_0' \\ s(x_1 + \varepsilon) = s(x_1) + \varepsilon_1' \\ s(x_2 + \varepsilon) = s(x_2) + \varepsilon_2' \\ s(x_3 + 3 \cdot \varepsilon) = s(x_3) + \varepsilon_3' \end{cases}$$

Solving each equation results in a set of possible values for the error. The intersection of these sets is a smaller set which reduces the number of required ciphertexts for the full analysis. The corresponding four key bytes can be guessed for each possible value of fault. According to this paper, intersecting the solution sets will retrieve four bytes of the round key quickly and the full 128-bit key can be found by analysing less than 50 ciphertexts.

### A Differential Fault Attack Technique against SPN Structures, with Application to the AES and KHAZAD, Piret and Quisquater [39]

Piret and Quisquater use a realistic fault model as they consider a random fault affecting a byte. In the first attack scenario, the fault is induced between the MixColumns of round 9 and 8. The MixColumn of round 9 spreads the fault over the whole column. After the non-linear computation of SubBytes the 4 faulty bytes are scattered over different columns according to the ShiftRows transformation. This leads to obtain a set of candidates for the 4 key bytes among which the unique correct candidate can be found by a couple of well-located faults. Suppose a one-byte fault occurring before the MixColumns of round 9 on one of the state bytes  $S_{0,0}$ ,  $S_{1,1}$ ,  $S_{2,2}$ , or  $S_{3,3}$ . Using one pair of correct and faulty ciphertexts  $(C; C^*)$ , the attacker obtains about 1036 candidates for  $(K_{0,0}^{10}, K_{1,3}^{10}, K_{2,2}^{10}, K_{3,1}^{10})$ . By exploiting two pairs of  $(C; C^*)$ , the only correct candidate for these 4 key bytes is remained. Hence, for the whole 16 bytes of the key, only 8 faults at carefully chosen locations are required, which in comparison with [21], [18], and [13], this attack scenario requires a considerable less number of faulty ciphertexts. The basic attack algorithm is as follows:

- 1. Consider a one-byte difference at the input of the MixColumns of round 9. There are 255 possible differences for a byte and 4 possible locations for fault that affect the same 4 bytes of the output.

- 2. Compute  $255 \cdot 4$  possible differences at the output of the MixColumns and store them in a list D.

- 3. Take a guess on the  $(K_{0,d}^{10}, K_{1,(1-d)mod4}^{10}, K_{2,(2-d)mod4}^{10}, K_{3,(3-d)mod4}^{10})$ .

- 4. Compute the difference  $\Delta = SubBytes^{-1}((C \oplus K^{10})_{*,d}) \oplus SubBytes^{-1}((C^* \oplus K^{10})_{*,d})$ . Verify if  $\Delta$  is in list *D*. If yes, add the key bytes to the list *L* of potential key candidates.

- 5. Repeat the above steps with a new plaintext P and its corresponding C and  $C^*$  with the key guesses only from the list L, until only one candidate remains.

In a second attack scenario, a complete 128-bit key can be obtained by only 2 faulty ciphertexts, assuming that the fault occurs in between the 7-th and 8-th round MixColumns operations. As depicted in Figure 2.2, a one-byte fault before the MixColumns of round 8 leaves 4 faulty bytes at the output of round 8. Then the last MixColumns spreads the 4 faults over the whole state and affects all 16 bytes. This makes it possible to recover the complete 128-bit key using only 2 faults.

## Differential Fault Analysis of the Advanced Encryption Standard using a Single Fault, Tunstall et al. [48]

In 2009, Tunstall et al. reported a differential fault analysis on AES using only a one-byte random fault at the input of the round 8. The attack includes two steps where in the first one the number of possible key candidates is reduced to  $2^{32}$ , and then to  $2^8$  in the second step. Considering  $C_i$  and  $C'_i$  as the correct and faulty bytes of the ciphertext, sixteen equations can be obtained from MixColumns operation. This results in  $2^{32}$  hypotheses for

| After | ShiftRows - round | 8 |

|-------|-------------------|---|

|-------|-------------------|---|

$S_{0,0}$  $S_{0,1}$  $S_{0,2}$  $S_{0,3}$ *S*<sub>1,3</sub>  $S_{1,2}$  $S_{1,0}$  $S_{2,0}$  $S_{2,1}$  $S_{2,2}$  $S_{2,3}$  $S_{3,2}$  $S_{3,0}$  $S_{3,1}$  $S_{3,3}$

$S_{0,0}$  $S_{0,3}$  $S_{0,2}$ *S*<sub>1,0</sub>  $S_{1,2}$  $S_{1,3}$  $S_{2,3}$  $S_{2,2}$  $S_{2,0}$  $S_{3,0}$  $S_{3,2}$  $S_{3,3}$

After MixColumn – round 8

| After AddRoundKey – round 8 |                  |                         |                  |  |  |  |  |  |

|-----------------------------|------------------|-------------------------|------------------|--|--|--|--|--|

| S <sub>0,0</sub>            | S <sub>0,1</sub> | <i>S</i> <sub>0,2</sub> | $S_{_{0,3}}$     |  |  |  |  |  |

| S <sub>1,0</sub>            | S <sub>1,1</sub> | $S_{1,2}$               | S <sub>1,3</sub> |  |  |  |  |  |

| S <sub>2,0</sub>            | $S_{2,1}$        | S <sub>2,2</sub>        | $S_{2,3}$        |  |  |  |  |  |

| S <sub>3.0</sub>            | S <sub>3.1</sub> | S <sub>3.2</sub>        | S <sub>3.3</sub> |  |  |  |  |  |

After SubBytes - round 9

| <i>S</i> <sub>0,0</sub> | S <sub>0,1</sub>        | $S_{0,2}$        | S <sub>0,3</sub> |   |

|-------------------------|-------------------------|------------------|------------------|---|

| <i>S</i> <sub>1,0</sub> | <i>S</i> <sub>1,1</sub> | $S_{1,2}$        | S <sub>1,3</sub> | 1 |

| S <sub>2,0</sub>        | S <sub>2,1</sub>        | S <sub>2,2</sub> | $S_{2,3}$        | - |

| S <sub>3,0</sub>        | S <sub>3,1</sub>        | S <sub>3,2</sub> | $S_{3,3}$        |   |

After ShiftRows - round 9  $S_{0,0}$  $S_{0,2}$  $S_{0,3}$  $S_{1,2}$  $S_{1,3}$  $S_{1,1}$  $S_{2,0}$  $S_{2,1}$  $S_{2,2}$  $S_{3,1}$  $S_{3,0}$  $S_{3,3}$

After MixColumn - round 9

|   | $S_{\rm 0,0}$ | $S_{0,1}$        | $S_{0,2}$        | $S_{0,3}$ |

|---|---------------|------------------|------------------|-----------|

|   | $S_{1,0}$     | S <sub>1,1</sub> | $S_{1,2}$        | $S_{1,3}$ |

| ~ | $S_{2,0}$     | $S_{2,1}$        | S <sub>2,2</sub> | $S_{2,3}$ |

|   | $S_{3,0}$     | $S_{3,1}$        | S <sub>3,2</sub> | $S_{3,3}$ |

After AddRoundKey - round 9

| $S_{0,0}$ | $S_{0,1}$ | S <sub>0,2</sub>        | S <sub>0,3</sub> |   |

|-----------|-----------|-------------------------|------------------|---|

| $S_{1,0}$ | $S_{1,1}$ | <i>S</i> <sub>1,2</sub> | S <sub>1,3</sub> |   |

| $S_{2,0}$ | $S_{2,1}$ | S <sub>2,2</sub>        | S <sub>2,3</sub> | - |

| $S_{3,0}$ | $S_{3,1}$ | S <sub>3,2</sub>        | S <sub>3,3</sub> |   |

After SubBytes - round 10

$S_1$

$S_{\gamma}$  $S_3$

| S | ubByte           | s - round | 10               | _ | After            | ShiftRo                 | ws-rou           | nd 10            |

|---|------------------|-----------|------------------|---|------------------|-------------------------|------------------|------------------|

|   | $S_{0,1}$        | $S_{0,2}$ | $S_{0,3}$        |   | $S_{\rm 0,0}$    | $S_{0,1}$               | $S_{0,2}$        | S <sub>0,3</sub> |

|   | $S_{1,1}$        | $S_{1,2}$ | S <sub>1,3</sub> | ~ | S <sub>1,0</sub> | <i>S</i> <sub>1,1</sub> | S <sub>1,2</sub> | $S_{1,3}$        |

|   | $S_{\rm 2,1}$    | $S_{2,2}$ | S <sub>2,3</sub> | ~ | $S_{2,0}$        | S <sub>2,1</sub>        | $S_{2,2}$        | S <sub>2,3</sub> |

| Γ | S <sub>3,1</sub> | $S_{3,2}$ | S <sub>3.3</sub> |   | $S_{3,0}$        | $S_{3,1}$               | S <sub>3.2</sub> | S <sub>3.3</sub> |

After AddRoundKey - round 10: Ciphertext

| $S_{0,0}$               | $S_{0,1}$               | $S_{0,2}$        | S <sub>0,3</sub> |

|-------------------------|-------------------------|------------------|------------------|

| <i>S</i> <sub>1,0</sub> | <i>S</i> <sub>1,1</sub> | S <sub>1,2</sub> | S <sub>1,3</sub> |

| $S_{2,0}$               | S <sub>2,1</sub>        | $S_{2,2}$        | S <sub>2,3</sub> |

| $S_{3,0}$               | $S_{3,1}$               | $S_{3,2}$        | S <sub>3,3</sub> |

Figure 2.2: The effect of the fault injected between rounds 8 and 7

the key. By exploiting the relationship between round 9 and 10, and using the Inverse MixColumns, a set of four other equations is made which tests all  $2^{32}$  candidates reached from step one. From these potential keys,  $2^8$  candidates remain among which a simple brute-force search can determine the right cipher key.

Note that the attacks explained above are not implemented on a hardware such as FPGA. They are attack descriptions assuming that there exist fault injection mechanisms to induce the desired fault into the targeted part of the AES architecture with a wanted timing.

## 2.4 Attacking the AES State rather than Key schedule

In reviewing the fault attacks on AES, as discussed above, we have attacks on both datapath and key schedule. These attacks are classified into two tables in table 2.1. This research only focuses on injecting faults into the datapath. As it will be discussed in next sections, we use clock glitch which causes the fault in the output by violating the setup time. Since generally the path delay of the key schedule in AES is much smaller than that of the datapath, attacking the key schedule using clock glitches is not easy in practice.

To investigate the attack limits on the State, the attacker injects a random single byte fault between the MixColumns of rounds 8 and 7. In the case of the attack on the Key schedule, it is assumed that the same fault model can be induced in the first column of  $K^8$ . Another assumption is that the AES is theoretically unbreakable i.e. almost all attacks have the time complexity of an exhaustive search. If the security level of AES is denoted by  $K_s$ , then  $K_s = 2^{128}$ .

In a DFA, when attacking the State, a fault is induced during a round computation, causes a difference  $\Delta S$  and leads to a faulty ciphertext C'. Suppose that instead of a fault injection, there is a classical collision based adversary  $Adv_{col}$  who tries different plaintexts in order to find a pair (P, P') which generate two states with a specific difference  $\Delta S$  after a target round r. Note that the ciphertext pair (C, C') is exactly the same as in DFA. If the probability of reaching such a pair is  $Pr(\Delta S)$  then the number of required plaintext pairs would be  $\frac{1}{Pr(\Delta S)}$ . If the DFA reduces the key search space to  $K_l$  then  $K_s \leq \frac{1}{Pr(\Delta S)} \cdot K_l \Rightarrow K_l \geq K_s \cdot Pr(\Delta S)$ . This means that a DFA in the best case decreases

Table 2.1: Classification of fault attacks into two classes: DFA on datapath, DFA on key schedule.

| (a) DFA on datapath |       |                           |  |  |

|---------------------|-------|---------------------------|--|--|

| Attack              | Model | Number of required faults |  |  |

| Blomer et al [13].  | Byte  | 90,112                    |  |  |

| Giraud [21]         | Byte  | 250                       |  |  |

| Dusart et al [18].  | Byte  | 50                        |  |  |

| Piret et al. [39]   | Byte  | 2,1                       |  |  |

| (b) DFA on key schedule |       |                           |  |  |

|-------------------------|-------|---------------------------|--|--|

| Attack                  | Model | Number of required faults |  |  |

| Blomer et al [13].      | Bit   | 128                       |  |  |

| Chen et al. [17]        | Byte  | 44                        |  |  |

| Takahashi et al. [47]   | Byte  | 7,4,2                     |  |  |

| Kim et al. $[30]$       | Byte  | 2                         |  |  |

the search space to  $K_s \cdot Pr(\Delta S)$ . In a single byte fault model,  $\Delta S$  is a byte difference and the probability of obtaining a plaintext pair generating a state with one byte difference (15 similar bytes) is  $2^{-15\times8} = 2^{-120}$ . Therefore an *optimal* one-byte fault DFA reduces the search space to  $2^{-120} \cdot 2^{128} = 2^8$ . It can be derived that if the fault affects *i* bytes in the State, then the minimum search space would be  $2^{8\cdot i}$  [45].

With a similar analysis, the search space limits for the DFA on Key schedule can be computed. Here, the attacker tries to find a plaintext pair such that they generate a required difference  $\Delta K$  in the  $r^{th}$  round key. This creates a difference  $\Delta K_p$  after the next round operation. Therefore, the number of choices for P' is  $\frac{1}{Pr(\Delta K_p)}$  and the optimal DFA is at  $K_s \cdot Pr(\Delta K_p)$  level. With the assumption of a one-byte fault in the first column of  $K^9$  in AES-128, which causes a four-byte difference in the ninth round key, the attack reduces the key space to  $2^{128} \cdot (\frac{255}{(2^8)^4} \cdot \frac{1}{(2^8)^{12}}) = 2^8$ . However, there is no reported attack which reaches this limit. In [30] a fault affects three bytes in the first column of the ninth round key while generating the key and thus causes a 12-byte difference in the round key 9. Therefore in the best case the key space reduces to  $2^{128} \cdot (\frac{255^3}{(2^8)^4} \cdot \frac{1}{(2^8)^{12}}) = 2^{24}$ .

Table 2.2 shows the optimal limits for DFA on AES-128. The second column corresponds to the case in which the attacker has access to plaintext and can apply a brute force

Table 2.2: Optimal results of DFA on AES-128 [45]

|              | Number of faults | Number of remaining keys | Number of faults for unique key |

|--------------|------------------|--------------------------|---------------------------------|

| State        | 1                | 28                       | 2 [39]                          |

| Key schedule | 1                | $2^{8}$                  | 2 [27]                          |

search on the key hypotheses, as explained above. The third column represents the results when the attacker does not have access to the plaintext and thus must uniquely determine the key. It can be seen that there is no reported attack which reaches the AES-128 limits for the number of the remaining keys. However, in the case of results for unique key, Piret's attack[39] obtains the best result to recover the AES-128 unique correct key by injecting only two faults in the State. There are also attacks on the State for the AES-192 and AES-256 which eventuates only one key after injecting 3 faults in 5 minutes, and 2 faults in 10 minutes respectively[26]. For the DFA on Key schedule, there is only a recent attack on AES-128 which requires 2 pairs of faulty and correct ciphertexts[28].

#### 2.5 Summary

In this chapter fault types and models along with the most common fault injection mechanisms were introduced and analysed. Then various DFA attacks targeting the AES algorithm were synthesized. Among them, two attacks, Piret's attack [39] and Tunstall's attack [48], are particularly powerful because the number of required faults to disclose the 128-bit AES key is only 1 or 2. This increases the attack feasibility as usually it is difficult to generate different faulty outputs from the same fault injections. Moreover, they induce the fault into the datapath as it is easier to disturb than the key schedule. In the next chapter, the experimental setup to inject a glitch fault in a FPGA-based implementation of AES is described. The design of the glitch generator and how it is used for a setup time violation in a glitch attack is described. This attack targets the critical paths which are mostly in the datapath than in the key schedule path.

# Chapter 3

# **Experimental Setup**

This chapter describes the experimental setup of a FPGA-based fault attack testbed. The details of the FPGA board and AES circuit, clock glitch creation and implementation, and final experimental setup is described and compared to previous research.

## 3.1 Using the clock glitch to inject the fault

In this thesis, the goal is to experimentally characterize faults generated by clock glitches, and then determine how it can be used to implement theoretical fault analysis attacks. Clock glitch attacks are known as a serious and practical threat since they are easy to implement and repeatable. Being repeatable is a significant feature since as discussed in the previous chapter, most of the practical attacks rely on the possibility of having more than one fault occurrence to obtain the unique key. This section will briefly discuss how clock faults occur, in purticular how a setup time violation can be created from a clock glitch.

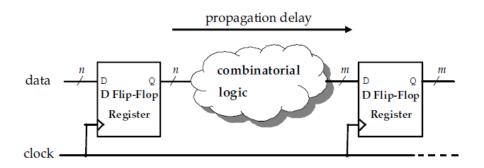

ICs usually process the data in combinatorial blocks and the D-flip-flops are used in between the combinatorial blocks to separate them. For example a few hundred flip-flops may define the IC's current state and the combinatorial logic calculates the next state from the current state during each clock cycle. In a synchronous circuit(figure 3.1), the flip-flops use the same clock input and registers may latch the data at the rising edge of the clock. The intermediate combinatorial logic modifies the data while traveling between the registers. There are some features that can be used by an attacker including:

Figure 3.1: Combinatorial logic and synchronous representation of a digital IC [6]

- The propagation delay can vary within a chip or between same-type chips.

- If the result of a combinatorial logic is not stabilized on a previous state, the flip-flops do not accept the correct new state.

- During a short time slot, the flip-flops sample their input and compare it with the power supply voltage. This sampling time is fixed, however, it can vary between different flip-flops.

The **Propagation delay** (time needed for the data to propagate through the combinatorial logic blocks) depends on the data, the logic performed on the data, and the capacitance and resistance of the transistors and interconnections. It also varies with the temperature and power supply voltage [6]. The maximum propagation delay is called **Critical path**, which imposes a limit on the maximum speed of the circuit. A second parameter affecting the clock speed is the **Setup time** which applies to flip-flops. The setup time is the minimum time before the clock event during which the data must be stable in order to be reliably sampled by the clock.

In order to ensure proper circuit functionality, the clock period must be greater than the critical path propagation delay plus the register's setup time.

$$T_{clk} > t_{critical} + t_{setup}.$$

(3.1)

In a glitch attack the attacker intentionally causes one or more flip-flops to accept the wrong state. This may modify an instruction, or corrupt the data or state. One method to do this is *Overclocking* in which the clock period decreases (or the frequency increases).

Figure 3.2: Latching the data with normal and glitchy clock [20]

Decreasing the clock period potentially can violate the condition in equation 3.1. Therefore, the register's input does not have the sufficient time to be correctly latched, which causes the faulty data to be latched instead. It is crucial to have the ability to precisely control the clock period, especially when the temperature and power supply change. In this thesis, a single transient clock glitch is generated by overclocking only in a specific time interval. As shown in Figure 3.2, in the normal case, clock cycles are longer than the maximum delay plus the setup time and the intermediate states are correctly stored. But, when the glitch occurs and the generated clock cycle is shorter than the sum of maximum delay and the setup time, a timing violation called a *setup time violation* happens. This causes the output of the combinational logic (r-in)to be latched in the register (r-out) before the correct output value is produced.

## 3.2 Clock glitch generating on FPGA

Generating the faulty clock with a sufficiently accurate glitch is crucial to launch an attack on AES. To do so, there are some conditions that the glitch generator must fulfill. For example:

• The attacker should be able to induce the glitchy cycle into any position of the clock.

This makes it plausible to inject the fault into any desired round of the cipher. Since as we saw in the previous sections, each fault model requires a specific AES round to inject the fault into.

- The attacker should be able to change the glitch specifications to support a wide range of control on the effects.

- In order to be able to acquire power traces during an attack, timing of the target operation should be available and an internal clock counter is needed.

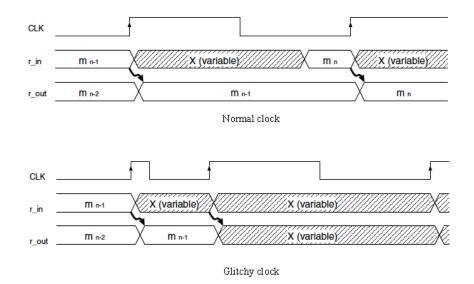

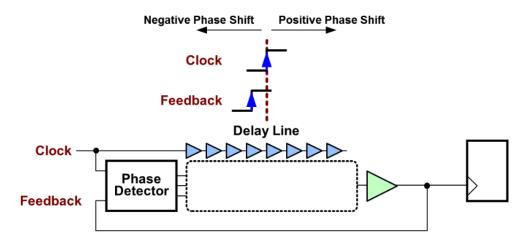

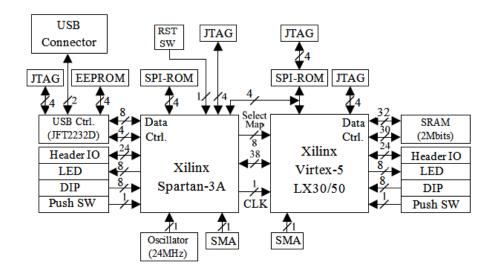

To generate a glitchy clock with the above mentioned features, the embedded Delay Locked Loop (DLL) of an FPGA of Xilinx Virtex-5 family is used. The DLL circuit is implemented by Digital Clock Manager (DCM) in Xilinx FPGAs. The Virtex-5 user guide (UG190) provides information on clock management technology. Alternatively, in Altera FPGAs the Phase Locked Loop (PLL) can be used. The basic function of the DLL is to remove the clock distribution delay. It also provides additional applications such as frequency multiplication and division, duty cycle correction, and phase shifting. In the simplest form, a DLL consists of a variable delay line and control logic. The delay line provides a delayed version of the input clock CLKIN. The DLL inserts a delay between the input clock and the feedback clocks, the DLL locks are in the same phase. After aligning the input and feedback clocks, the DLL locks and as long as the circuit is processing the data, there is no difference between the two clocks (see Figure 3.3).

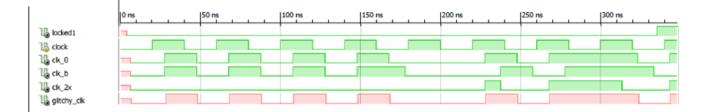

To achieve the lock, DLL needs to sample several clock cycles. After achieving the lock, the LOCKED signal, which is one of the DLL outputs, activates. Until this signal activates, the DLL outputs are not valid and cannot be used or analyzed. They can exhibit unwanted glitches, spikes or other imprecise movements. For instance it might affect the duty cycle, or the CLK2X output appears as a 1X clock with a 25/75 duty cycle. Figure 3.4 shows a timing simulation waveform representing the output signals before reaching the LOCKED signal.

In the glitch generator the DCM's phase shifting feature which provides various phase shift options was used. The dedicated phase shift output signals including CLK0, CLK90, CLK180, and CLK270 always maintain their relationship. Using the "PHASE\_SHIFT" attribute an arbitrary fixed delay value was set and the phase relationship of all DCM clock outputs was adjusted. The "CLKOUT\_PHASE\_SHIFT" attribute determines the phase shift mode and can be initialized as "NONE" (no delay) or "FIXED" (a fixed arbitrary

Figure 3.3: Delay Locked Loop (DLL) in Virtex FPGAs [2]

Figure 3.4: DLL output signals from ISE software before the LOCKED signal activates.

delay).

As shown in Figure 3.5 there are a number of taps in the delay line each of 30 ps to 60 ps. The number of taps and the maximum guaranteed delay line changes per data sheet. For the Virtex5-XC5VLX30 FPGA, there are 255 taps for the negative phase shifts and 1023 taps for the positive phase shifts, and the maximum guaranteed delay line or the FINE\_SHIFT\_RANGE is 7ns. This means that if the period of the CLKIN input clock is  $T_{CLKIN}$ , then this condition must be met:  $PHASE\_SHIFT \cdot T_{CLKIN}/256 < 7ns$  [3]. for example if the input clock period is 40ns the maximum PHASE\_SHIFT we can choose is  $\pm [integer(256 \cdot \frac{7ns}{40ns})] = \pm 44$ , and the corresponding attributes to be set are:

defparam dcm.CLKOUT\_PHASE\_SHIFT = "FIXED"; defparam dcm.PHASE\_SHIFT = 44;

Note that the DCM has a fixed phase shift of  $10^{\circ}$ . This means that, for instance, the phase relationship between CLKIN and CLK0 is  $0^{\circ} + 10^{\circ} = 10^{\circ}$ , or the phase relationship between CLKIN and CLK90 is actually  $90^{\circ} + 10^{\circ} = 100^{\circ}$ . But, the output clocks hold

Figure 3.5: Delay line taps [3]

their phase difference i.e. the phase relationship between CLK0 and CLK90 is exactly 90°.

#### 3.2.1 Comparison to previous clock glitch generators

The glitch generator proposed in [20] uses two clock sources with the same frequency and different phases, generated by an external pulse generator. When switching between the two clock sources at the right time, a glitch occurs in the desired round. An oscilloscope is employed to control the switching time in order to select or change the fault injection round, and to measure the shortened interval of the clock cycle. However, we want to have the whole environment integrated on a single FPGA without the need to an external pulse generator or oscilloscope. In addition, we prefer to control the timing and shape of the generated glitch more precisely using parameters via a control PC. Therefore, the glitch generator we utilized, has the design idea of the one used in [19] to perform a safe-error attack against RSA. In their attack, the clock glitch characteristics and the fault effect is not explored. Instead it is just checked whether or not the fault has an effect on the output power trace.

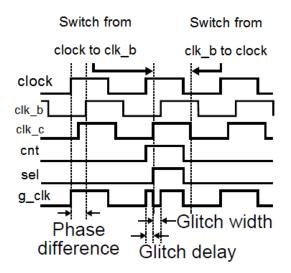

The glitch generator uses a DLL to generate a shifted clock named clk\_b which will be switched with the input clock at the proper time. Another DLL is used to generate clk\_c with a delay less than that of the clk\_b. A counter is activated by the input clock and outputs 1 when it reaches the required clock cycle. The 1 output lasts for a half clock cycle. The AND operation of clk\_c and counter output gives the selector of the MUX and

Figure 3.6: Timing chart of the glitch generator

the output of the mux is the demanded glitchy clock. Figure 3.6 shows the timing chart of the signals.

## 3.3 Experimental setup

This section provides an overview of the evaluation board on which the AES code is implemented, and other software and hardware equipments needed for the experiment. The on-chip glitch generator, which is designed on the evaluation board to generate the desired glitch in the clock signal, is discussed and the target AES cryptosystem is introduced.

#### 3.3.1 The target cryptographic device