# An Attack and a Defence in the Context of Hardware Security

by

Frank Imeson

A thesis presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2013

© Frank Imeson 2013

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners. I understand that my thesis may be made electronically available to the public.

#### Abstract

The security of digital Integrated Circuits (ICs) is essential to the security of a computer system that comprises them. We present an improved attack on computer hardware that avoids known defence mechanisms and as such raises awareness for the need of new and improved defence mechanisms. We also present a new defence method for securing computer hardware against modifications from untrusted manufacturing facilities, which is of concern since manufacturing is increasingly outsourced.

We improve upon time triggered based backdoors, inserted maliciously in Prior work has addressed deterministic timer-based triggers hardware. those that are designed to trigger at a specific time with probability 1. We address open questions related to the feasibility of realizing non-deterministic timer-based triggers in hardware — those that are designed with a random component. We show that such timers can be realized in hardware in a manner that is impractical to detect or disable using existing countermeasures of which we are aware. We discuss our design, implementation and analysis of such a timer. We show that the attacker can have surprisingly fine-grained control over the time-window within which the timer triggers. From the attacker's standpoint our non-deterministic timer has key advantages over traditional timer designs. For example the hardware footprint is smaller which increases the chances of avoiding detection. Also our timer has a much smaller time-window for which a volatile state needs to be maintained which in turn makes the power reset defence mechanisms less effective.

Our proposed defence mechanism addresses the threat of a malicious agent at the IC foundry who has information of the circuit and inserts covert, malicious circuitry. The use of 3D IC technology has been suggested as a possible technique to counter this threat. However, to our knowledge, there is no prior work on how such technology can be used effectively. We propose a way to use 3D IC technology for security in this context. Specifically, we obfuscate the circuit by lifting wires to a trusted tier, which is fabricated separately. We provide a precise notion of security that we call k-security and point out that it has interesting similarities and important differences from k-anonymity. We also give a precise specification of the underlying computational problems and their complexity and discuss a comprehensive empirical assessment with benchmark circuits that highlight the security versus cost trade-offs introduced by 3D IC based circuit obfuscation.

### Acknowledgements

I would like to thank my supervisors Siddharth Garg and Mahesh V. Tripunitara for sharing their insights and knowledge. Also I would like to acknowledge the collaboration between my supervisors and myself on this work, hence the use of "we, our, and us".

### Dedication

I dedicated this thesis to the Internet; without the Internet my perceived intelligence would only be a fraction of what it is.

PS. Spell check has also been very useful in this respect.

# **Table of Contents**

| List of Tables vii |                           |                  |                                       | viii                                                                   |

|--------------------|---------------------------|------------------|---------------------------------------|------------------------------------------------------------------------|

| Li                 | st of                     | Figur            | es                                    | ix                                                                     |

| 1                  | <b>Intr</b><br>1.1<br>1.2 | oducti<br>Attacl |                                       | $     \begin{array}{c}       1 \\       2 \\       5     \end{array} $ |

| <b>2</b>           |                           |                  | nd and Related Work                   | 10                                                                     |

|                    | 2.1                       | Design           | and Fabrication Process               | 10                                                                     |

|                    | 2.2                       | Relate           | ed Work                               | 12                                                                     |

|                    |                           | 2.2.1            | Attacks                               | 12                                                                     |

|                    |                           | 2.2.2            | Countermeasures                       | 13                                                                     |

| 3                  | The                       | Non-             | Deterministic Timer                   | 17                                                                     |

|                    | 3.1                       | Deterr           | ministic Timers                       | 18                                                                     |

|                    |                           | 3.1.1            | State of The Art                      | 18                                                                     |

|                    |                           | 3.1.2            | Modified Deterministic Timer Protocol | 19                                                                     |

|                    |                           | 3.1.3            | Trade-off                             | 21                                                                     |

|                    | 3.2                       | Non-E            | Deterministic Timer                   | 22                                                                     |

|                    | 3.3                       | Hardw            | vare Realization                      | 26                                                                     |

|                    |                           | 3.3.1            | TRNG Implementation                   | 27                                                                     |

|                    |                           | 3.3.2            | Timer Design                          | 28                                                                     |

|                    | 3.4                       | Result           | $\tilde{\mathbf{S}}$                  | 29                                                                     |

|                    |                           | 3.4.1            | TRNG                                  | 30                                                                     |

|                    |                           | 3.4.2            | Non-deterministic Timer               | 31                                                                     |

|                    |                           | 3.4.3            | Hardware Resource Utilization         | 31                                                                     |

|                    |                           | 3.4.4            | Non- vs. Deterministic Timers         | 32                                                                     |

| 4            | 3D-   | Security 3                                                             | 4        |

|--------------|-------|------------------------------------------------------------------------|----------|

|              | 4.1   | 3D IC Design and Fabrication                                           | 4        |

|              | 4.2   | Attack Model                                                           | 57       |

|              | 4.3   | Problem Formulation                                                    | 8        |

|              |       | 4.3.1 Formulation as a Graph Problem                                   | 9        |

|              | 4.4   | Approach                                                               | 3        |

|              |       | 4.4.1 Computing Security $\ldots \ldots \ldots \ldots \ldots \ldots 4$ | 4        |

|              |       | 4.4.2 Wire Lifting Procedure                                           | 5        |

|              |       | 4.4.3 Practical Considerations                                         | 6        |

|              | 4.5   | Results                                                                | 7        |

|              |       | 4.5.1 Security-Cost Tradeoffs                                          | 8        |

| <b>5</b>     | Dis   | cussion 5                                                              | <b>2</b> |

|              | 5.1   | Non-Deterministic Timer                                                | <b>2</b> |

|              |       | 5.1.1 Pre-fabrication Simulation and Validation 5                      | <b>2</b> |

|              |       | 5.1.2 Logic Signature Detection                                        | 3        |

|              |       | 5.1.3 Hardware Signature Detection                                     | 5        |

|              |       |                                                                        | 6        |

|              |       |                                                                        | 6        |

|              | 5.2   | k-security                                                             | 6        |

|              |       | 5.2.1 Case Study: DES Circuit                                          | 6        |

|              |       | 5.2.2 Hiding Wire Selections                                           | 9        |

|              |       |                                                                        | 9        |

| 6            | Cor   | aclusions 6                                                            | 1        |

| $\mathbf{A}$ | PPE   | NDICES 6                                                               | <b>2</b> |

| A            | No    | n-Deterministic Timer 6                                                | 3        |

|              |       |                                                                        | 3        |

| в            |       | ecurity 6                                                              | 4        |

|              | B.1   | Proof of CIRCUIT-SUBISO is NP-hard 6                                   | 64       |

| $\mathbf{R}$ | efere | nces 6                                                                 | 6        |

# List of Tables

| 3.1 | NIST test results for TRNG implementation (16 ROs, 3 wide,                                                                                                                                                                                                                                                                                                                                         |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 1024 decimation). (See Section 3.4.1.) $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                               | 30 |

| 3.2 | FPGA resource utilization of an non-deterministic and deter-<br>ministic timer (ND-Timer and D-Timer respectively), and a<br>32-bit RISC processor. Resources are measured using logic<br>elements ( <i>LE</i> ), registers ( <i>REG</i> ), and equivalent logic cells<br>( <i>ELC</i> ), where $ELC = 12 \times LE + REG$                                                                         | 32 |

| 4.1 | Power, delay, wire length and area analysis for different levels<br>of security on the c432 circuit. 1 <sup>*</sup> is the base circuit with no<br>wires lifted and 48 <sup>*</sup> has all of the wires lifted.                                                                                                                                                                                   | 51 |

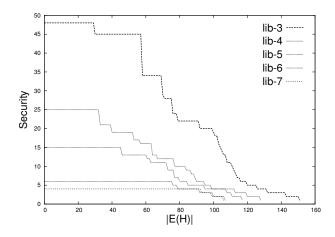

| 4.2 | Technology libraries used for the experiment in Figure 4.7. lib-x corresponds to a library with $x$ different gate types                                                                                                                                                                                                                                                                           | 51 |

| A.1 | 15 non-deterministic timers set to trigger in 24 hours with<br>a standard deviation of 2.84 minutes (left) and 16 minutes<br>(right). The resulting distributions of the number of timers<br>that finish by a certain time were tested against the expected<br>distribution with the $\chi^2$ test, and yielded P-values of 0.878<br>(left) and 0.985 (right). The random variable T is the number | 60 |

|     | of finished timers. (See Section 3.2.)                                                                                                                                                                                                                                                                                                                                                             | 63 |

# List of Figures

| 1.1 | A two tier 3D IC. In this instance, the top tier is an interposer, i.e., it only implements metal wires, while the bottom tier has both transistors/gates and wires.                                                                                                                                           |   | 7  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

| 2.1 | The hardware fabrication process. Malicious circuitry may be<br>inserted at either the design and synthesis, or the fabrication<br>phase. The former may be detectable at either the pre- or<br>post-fabrication testing and validation phases. The latter is<br>detectable at the post-fabrication phase only | 1 | .1 |

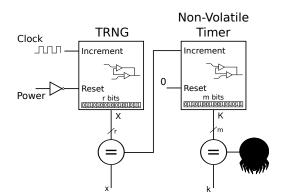

| 3.1 | Block diagram of a deterministic timer attack that utilizes a volatile timer chained with a non-volatile timer.                                                                                                                                                                                                | 2 | 20 |

| 3.2 | Timing diagram for the operation of deterministic timers. The graph shows three signals: the primary clock signal (Clock), the count stored in the volatile state (V-Timer), and the count                                                                                                                     |   |    |

|     | stored in NV memory (NV-Counter).                                                                                                                                                                                                                                                                              | 2 | 20 |

| 3.3 | Block diagram of a non-deterministic timer attack that uti-<br>lizes a TRNG chained with a non-volatile timer. The key is                                                                                                                                                                                      |   |    |

| 9.4 | compare with the output of the TRNG (see Section 3.3.1).                                                                                                                                                                                                                                                       | 2 | 23 |

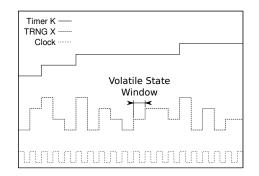

| 3.4 | Operation of non-deterministic timers. The bottom graph<br>shows the IC's clock signal and the top graph shows the timer's<br>current count. The graph shows three signals: the clock signal<br>(Clock), the output of the TRNG (TRNG X) and the count<br>stored in NV memory (Timer K).                       | 2 | 23 |

| 3.5 | The pmfs (left) and cdfs for three different timer designs. Each trigger is designed to have an expectation $E(N) = 1000$ . The deterministic timer is shown as dotted, the single event trigger is shown in bold and the multiple event non-deterministic                                                     |   |    |

|     | timer is shown as solid, not bold.                                                                                                                                                                                                                                                                             | 2 | 25 |

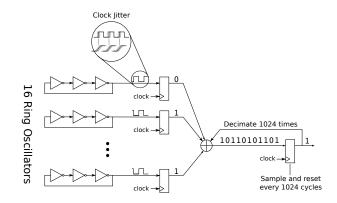

| 3.6          | Circuit diagram of the TRNG that we implement.                                                                                                                                                                                                                                                                                                                                                                                                                | 27  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

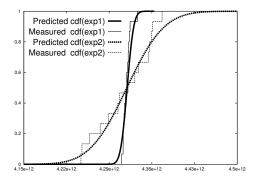

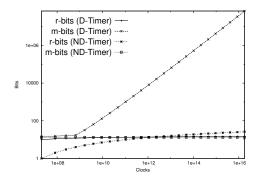

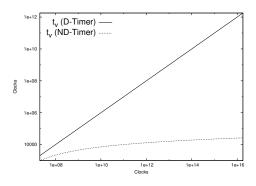

| $3.7 \\ 3.8$ | Measured and predicted cdfs for the timer experiments<br>The volatile and NV memory sizes, with the same volatile                                                                                                                                                                                                                                                                                                                                             | 31  |

|              | state window, as a function of the expected trigger time for deterministic and non-deterministic timers.                                                                                                                                                                                                                                                                                                                                                      | 33  |

| 3.9          | The volatile state window, with the same NV memory size, as<br>a function of the expected trigger time for deterministic and<br>non-deterministic timers.                                                                                                                                                                                                                                                                                                     | 33  |

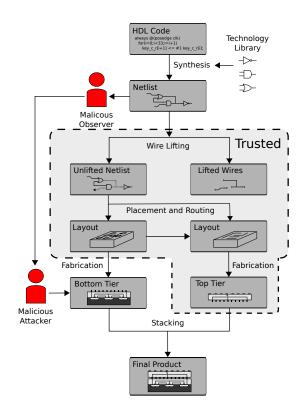

| 4.1          | Secure 3D IC design and fabrication flow.                                                                                                                                                                                                                                                                                                                                                                                                                     | 36  |

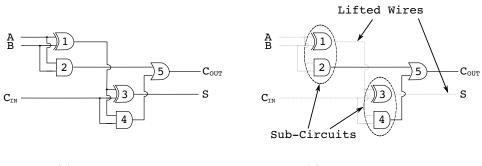

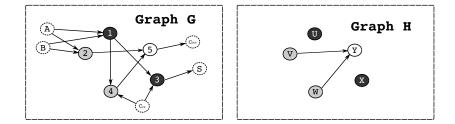

| 4.2          | Full adder circuit and it's obfuscated version. Grey wires are                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 4.3          | lifted.<br>Full adder graphs: G is the full graph representation of the                                                                                                                                                                                                                                                                                                                                                                                       | 38  |

|              | full adder circuit, H is the remaining graph after wires have been lifted.                                                                                                                                                                                                                                                                                                                                                                                    | 40  |

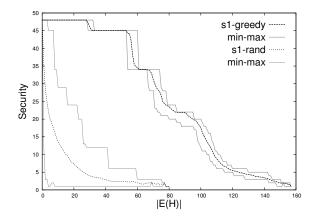

| 4.4          | Maximum, average and minimum security levels for the c432 circuit using the proposed greedy wire lifting procedure and                                                                                                                                                                                                                                                                                                                                        |     |

|              | random wire lifting.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48  |

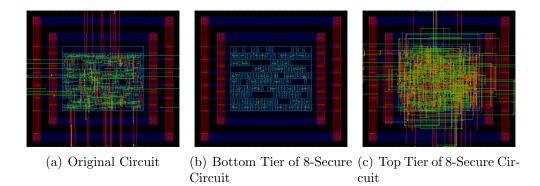

| 4.5          | Layout of c432 without any lifting (left), and the bottom (mid-<br>dle) and top (right) tiers of an 8-secure version of c432. Green<br>and red lines correspond to metal wires.                                                                                                                                                                                                                                                                               | 49  |

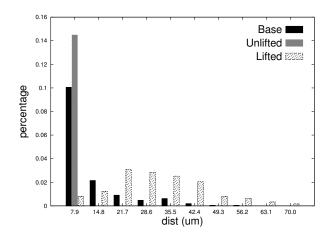

| 4.6          | Comparison of the c432 circuit wire lengths the original 1-<br>secure circuit and the bottom and top tiers of the 8-secure                                                                                                                                                                                                                                                                                                                                    |     |

| 4.7          | circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50  |

| 4.1          | cuit mapped with different technology libraries.                                                                                                                                                                                                                                                                                                                                                                                                              | 51  |

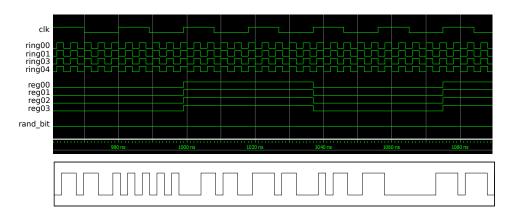

| 5.1          | A test simulation done in Modelsim is shown as the top dia-<br>gram for a sample non-deterministic -timer using four ring os-<br>cillators ringXX. Note how all the ring oscillators are in phase<br>without any clock jitter. All the ring sampling registers regXX<br>are also in phase and thus the decimation of a even number<br>of rings will always be 0 = rand_bit. The bottom diagram<br>shows a typical pattern for rand_bit gathered from the FPGA | - 0 |

|              | itself.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53  |

| 5.2 | Two possible dynamic choices are shown for the key. The cur-<br>rent value of the count (left) and some function of the count<br>and the current value of the key (right). Adopting a non-<br>constant key defeats logic-signature based countermeasures |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | such as UCI.                                                                                                                                                                                                                                             | 54 |

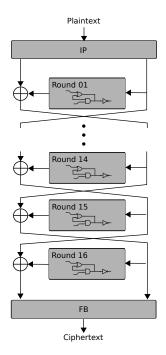

| 5.3 | Block diagram of the DES encryption circuit.                                                                                                                                                                                                             | 57 |

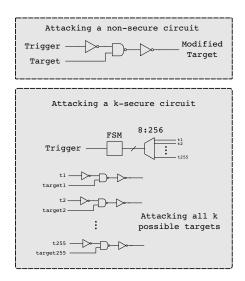

| 5.4 | Attack scenarios of 1-secure and k-secure circuits.                                                                                                                                                                                                      | 58 |

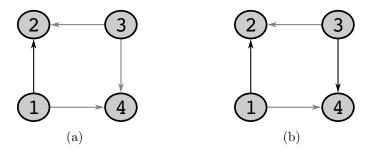

| 5.5 | Revealing the removed edge set (grey edges) would comprise                                                                                                                                                                                               |    |

|     | k-security for the left graph but not the right graph. $\ldots$ .                                                                                                                                                                                        | 59 |

|     |                                                                                                                                                                                                                                                          |    |

# Chapter 1

# Introduction

The security of computer hardware, particularly digital Integrated Circuits (ICs), is an important aspect of the overall security of computer systems. Of particular concern is the potential for insider-abuse [61] — the insertion of malicious backdoors by trusted insiders that are involved in the manufacturing process of an IC. A backdoor allows an attacker to bypass system-safeguards.

Hardware security has several similarities to software security. However, as recent work points out [33], the compromise of hardware can be more harmful than the compromise of software for two reasons. One is that attack vectors are more persistent, given that hardware is not as easy to patch as software. The other is that hardware is at the lowest level of the computer system, and thereby, a vulnerability in hardware affects the software that runs above it as well.

This thesis presents two new contributions in the context of hardware security: (i) a non-deterministic timer, a new type of trigger used to attack hardware that utilizes random events to evade current defence mechanisms; and (ii) k-security, a defence mechanism that embeds security into the fabrication process by leveraging 3D IC technology and thereby obfuscating the circuit.

The rest of this chapter will introduce the non-deterministic timer and k-security followed by Chapter 2 which introduces the necessary background of hardware and reviews current research on security in the context of our proposed contributions. In Chapter 3 and Chapter 4 we formally introduce the theory and results of the non-deterministic timer and k-security respectively, review strengths and weaknesses of our contributions in Chapter 5 and finally in Chapter 6 we conclude with a summary of our findings.

### 1.1 Attacks

Hardware attacks compromise the integrity of the IC. Specifically an adversary can design his or her attack to leak information, degrade performance and or modify the logical. To motivate the importance of hardware security consider an orbital satellite with a maliciously compromised IC designed to fail after one year of operation. This one incident, would cost millions of dollars and the execution of the attack is possible due to the multiple opportunities the design and fabrication process allow, as shown in Figure 2.1.

The insertion of a hardware backdoor is a particularly dangerous kind of attack [74, 75]. It can be used by an attacker to affect a part, or even take over the entire system. A backdoor is typically passive until it is triggered. Once triggered, it performs some malicious action such as unauthorized privilege escalation or even destruction of hardware and software components. A trigger is usually one of two types [74]: data-based or time-based. (A combination of the two is also possible.) With the former, an attack is initiated by a cheat-code, a sequence of bits embedded in the data or instruction stream. With the latter, an attack takes place after the elapse of some time, measured, for example, by CPU cycles.

While both data-based and time-based attacks can be destructive, timebased triggers seem to be particularly dangerous because they do not require any cooperation at run-time, whether accidental or intentional, from a higherlevel component such as software or a user. With a time-based attack, the attacker typically embeds a timer that triggers the attack as part of the malicious circuitry. As prior work observes [74], such a timer is simple to implement in hardware.

Our proposed attack pertains to timer-based triggers. That is, attacktriggers that are set off by a hardware circuit that implements a timer. We distinguish two types of timers: deterministic and non-deterministic . A deterministic timer triggers at a time of the attacker's choosing with probability 1. A non-deterministic timer does not; it has a random component to it. (A deterministic timer is a special case of a non-deterministic timer.)

Given the potentially devastating effects of timer-based triggers, prior work has considered how their effects can be mitigated. Waksman and Sethumadhavan [75] propose power-cycling the IC as a general countermeasure to timer-based triggers.

Power cycling, in this context, is fine-grained and is not intended to impede the running of higher-level software. Specifically, the execution of instructions is interrupted briefly and some volatile state (e.g., content of registers) is lost as a consequence of power cycling, but the persistent state (e.g., content of caches and of non-volatile memory) is retained. The program counter is saved to and restored from non-volatile memory. Waksman and Sethumadhavan's [75] empirical observation is that such power-cycling every 1,000,000 cycles results in negligible performance overhead.

They propose that such power-cycling be carried out at both the postfabrication testing and validation stage of the manufacturing process, and in the field. They show that the former is effective in disabling a particular kind of deterministic timer. We show that there exists a deterministic timer that cannot be disabled by power-cycling in the post-fabrication testing and verification stage, but can be rendered useless by power-cycling in the field (see Section 3.1).

More importantly, prior work leaves open issues related to non-deterministic timer-based triggers. It has been conjectured that from the attacker's standpoint, such a trigger may be of limited value given the random component — the attacker has insufficient control over when it triggers [75]. These open issues are the focus of our attack.

We show that an attacker can realize a non-deterministic timer-based trigger in hardware in a manner that is impractical to detect or disable using existing countermeasures of which we are aware. Furthermore, we show that an attacker can have surprisingly fine-grained control over the behaviour of such timers. For example, an attacker can ensure that the timers in all <sup>1</sup> instances of an IC trigger within the same small time-window, i.e., he is able to ensure that the standard deviation of the timer is small around its expectation. Alternately, an attacker can have such timers trigger at different, seemingly random times.

From the standpoint of the attacker, our construction has other appealing features as well. (See Section 5 for a comprehensive discussion.) It is carried out using digital components only, thereby refuting suggestions in

<sup>&</sup>lt;sup>1</sup>All in this context means a very high percent of ICs will trigger within a window. In other words, since the trigger is non-deterministic there is a very small probability that an IC may trigger outside of the window in question.

some prior work [75] that analog circuitry is necessary to exploit true randomness. (Our construction requires true randomness — see Section 3.3.) The timer is fully synthesizable, and therefore the attacker can insert such a timer at any stage of the design and fabrication process for ICs, given access to Non-Volatile (NV)-Memory. If the attacker inserts the timer in the design stage, simulations with even unbounded resources cannot detect its presence. (Simulation-based testing is customarily part of pre-fabrication testing.)

The size of the non-volatile state we need to maintain, and the corresponding size of the NV-memory we need for the functioning of the timer, is very small: only the state for a counter, i.e., a few bits. The time-window of volatile state between updates to the non-volatile state is so small (two orders of magnitude smaller than the frequency of power cycling that prior work [75] considers) that it is impractical to power-cycle the circuit sufficiently frequently to interrupt it.

**Contributions** Our research contribution is a design, implementation and thorough analysis of a non-deterministic timer in hardware that can be used to trigger backdoors in ICs. Our work demonstrates that non-deterministic timer-based triggers, with dangerous characteristics, can be feasibly realized by an attacker that has access to the IC manufacturing process. In particular, compared to deterministic timer attacks, which have been the focus of prior study, the non-deterministic timers are more pernicious for the following reasons:

- Non-deterministic timers are immune to the post-fabrication test time power cycling defence proposed by Waksman and Sethumadhavan [75] that is effective against a class deterministic timer attacks.

- Deterministic timers that escape post-fabrication test time defence mechanisms are easily disabled by even infrequent power cycling in the field. On the other hand, non-deterministic timers can be defeated only by very frequent power cycling, at rates high enough to be almost impractical because of the significant performance penalty that they impose. For example, a non-deterministic timer with an expected trigger time of one year is only defeated if the chip is power cycled once every 27  $\mu s$ , while an equivalent deterministic timer is defeated even if the chip is power cycled once every 50 minutes (see Case Study in Section 3.4).

- Our implementation of the non-deterministic timer requires (perhaps

counter-intuitively) fewer logic gates and fewer bits of NV memory than an equivalent deterministic timer implementation. Thus, nondeterministic attacks are more immune to detection techniques based on IC fingerprinting and physical screening.

• Non-deterministic timers that exploit physical random processes (as our attack does) behave very differently in pre-fabrication simulation and validation tests than they do in the field. This fact has important implications for the immunity of the non-deterministic timer attack to pre-fabrication validation testing — the non-deterministic timer never triggers in logic or circuit simulation tests. On the other hand, deterministic timers do trigger and are consequently detected during pre-silicon validation if the simulations are run for a sufficiently large number of clock cycles.

A possible critique of non-deterministic timers is that the trigger time is, by definition, a random variable and not a deterministic value. Non-deterministic timers can therefore trigger, with some probability, during postfabrication testing, resulting in early detection. We show, however, that by appropriate choice of design parameters, the probability of the non-deterministic timer triggering can be reduced to values as small as  $10^{-100}$  even if each fabricated chip can be tested for 10 days before shipping to the customer. At the same time, we show that the non-deterministic timer can be engineered to trigger within short confidence intervals with high likelihood resulting in very precise, controlled attacks — for example, more than 99.5% of the timers trigger within 10 days of the expected trigger time for an attack designed to trigger in one year (see Case Study in Section 3.3).

As such, our work is intended to alert hardware verification and test engineers to the considerable threat to the safety of digital ICs from nondeterministic timer based attacks, which have previously received little or no attention because of their perceived impracticality. On the contrary, we show that non-deterministic attacks are not only practical, but potentially more pernicious than deterministic timer attacks.

### **1.2** Countermeasures

Countermeasures with respect to computer hardware security occur in one of two forms deterrents and preventatives. Unfortunately deterrents often present an initial investment of work to the adversary, but allows for a permanent solution with little to no extra cost in the long run. This is due to the fact that adversary is privy to knowledge of the entire circuit, which fact is likely responsible for the absence of more preventative methods. We propose our technique as a true form of prevention which is realized by hiding knowledge of the entire circuit to the adversary by means of 3D integration.

Three-dimensional (3D) integration, an emerging IC manufacturing technology, is a promising technique to enhance the security of computer hardware. A 3D IC consists of two or more independently manufactured ICs that are vertically stacked on top of each other — each IC in the stack is referred to as a *tier*. Interconnections between the tiers are accomplished using vertical metal pillars referred to as through-silicon vias (TSV).

3D IC manufacturing can potentially enhance hardware security since each tier can be manufactured in a separate IC foundry, and vertically stacked in a secure facility. Thus, a malicious attacker at any one foundry has an incomplete view of the entire circuit, reducing the attacker's ability to alter the circuit functionality in a desired manner.

Tezarron, a leading commercial provider of 3D stacking capabilities, has alluded to the enhanced security offered by 3D integration in a white paper [1]. The white paper notes that "A multi-layer circuit may be divided among the layers in such a way that the function of each layer becomes obscure. Assuming that the TSV connections are extremely fine and abundant, elements can be scattered among the layers in apparently random fashion." However, the paper does not provide any formal notion of security for split manufacturing, nor does it propose techniques to quantify security or achieve a certain security level. These are the open challenges that our proposed defence mechanism addresses in this paper.

Our threat model assumes a malicious attacker in an IC foundry who wants to modify the functionality of a digital IC in a specific, targeted manner. Skorobogatovin et al. [61] found an exploit on an Actel FPGA that leaks secret information stored on the chip when a specific cheat code is observed at the JTAG interface. Similarly, the attack proposed by King et al. [41] modifies the state of hardware registers in a processor to raise the privilege level of the attacker.

To effect a targeted attack, an attacker must first identify specific logic gates or wires in the circuit that implement the functionality that he wants to monitor and/or modify; for example, the gate or wire that corresponds to the privilege bit for the privilege escalation attack proposed in [41]. A

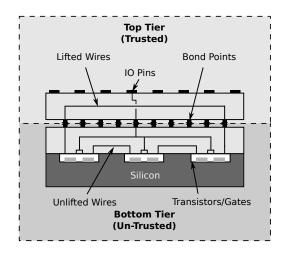

Figure 1.1: A two tier 3D IC. In this instance, the top tier is an interposer, i.e., it only implements metal wires, while the bottom tier has both transistors/gates and wires.

malicious foundry can trivially identify the functionality of every gate and wire in the circuit if it gets to fabricate the entire chip, i.e., if a conventional planar, 2D fabrication process is used. On the other hand, as we show in this paper, 3D integration significantly reduces the ability of an attacker in a malicious foundry to correctly identify gates or wires in the circuit that he wants to attack.

The specific 3D integration technology that we exploit in this work, since it is the only one that is currently in large volume commercial production [15], splits a design into two tiers. The bottom tier consists of digital logic gates and metal wires used to interconnect logic gates. The top tier, also referred to as an *interposer*, only consists of metal wires that provide additional connections between logic gates on the bottom tier.

The bottom tier — this tier is expensive to fabricate since it implements active transistor devices and passive metal — is sent to an external, untrusted foundry for fabrication. This is referred to as the untrusted tier. The top tier implements only passive metal and can be fabricated at lower cost in a trusted fabrication facility. We refer to this tier as the trusted tier.

Assume, for the sake of argument, that all interconnections between logic gates are implemented on the trusted tier, the attacker (who only has access to the untrusted tier) observes only a "sea" of disconnected digital logic gates. From the perspective of the attacker, gates of the same type, for example all NAND gates, are therefore indistinguishable from each other. (Assuming that the relative size or placement of gates reveals no information about interconnections between gates. This is addressed later in the thesis.) Assume also that the attacker wants to attack a specific NAND gate in the circuit, and not just *any* NAND gate. The attacker now has two choices: (a) the attacker could randomly pick one NAND gate to attack from the set of indistinguishable NAND gates, and only succeed in the attack with a certain probability; or (b) the attacker could attack all indistinguishable NAND gates, primarily in cases where the attacker wants to monitor but not modify gates in the circuit, at the expense of a larger malicious circuit and thus, an increased likelihood of the attack being detected. In either instance, the attacker's ability to effect a malicious, targeted attack on the circuit is significantly hindered. We argue that forcing the adversary to either guess or spend more resources then they can afford, while still avoiding detection is a preventative method. We refer to this technique as *circuit obfuscation*.

In general, we define a *k*-secure gate as one that, from the attacker's perspective, cannot be distinguished from k - 1 other gates in the circuit. Furthermore, a *k*-secure circuit is defined as one in which each gate is at least *k*-secure.

**Contributions** In this paper, we make the following contributions:

- We propose a concrete way of leveraging 3D IC technology to secure digital ICs from an active attacker at the foundry. Whereas the use of 3D IC technology has been mooted for security before, we are not aware of prior work like ours that discusses how it can be used.

- We give a precise characterization of the underlying technical problems and identify their computational complexity.

- We propose a meaningful way to characterize security that we call k-security. It has appealing similarities to k-anonymity, but important differences.

- We have devised an approach to addressing our problem of lifting wires, which comprises a greedy heuristic to identify a candidate set of wires to be lifted, and the use of a constraint (SAT) solver to compute k-security.

- We have conducted a thorough empirical assessment of our approach on benchmark circuits. We have also conducted a case-study of a DES

circuit that illustrates the inability of an attacker to effectively attack circuits secured using 3D IC based obfuscation.

# Chapter 2

# **Background and Related Work**

In this chapter, we overview the IC manufacturing process (Section 2.1) and discuss related work (Section 2.2) along two aspects: attacks and countermeasures. Also, we place our work in the context of the related work.

### 2.1 Design and Fabrication Process

Computer hardware is the realization of digital logic in the form of an integrated circuit (IC) or a chip. In the design phase of an IC, the desired behaviour of the digital logic is first described using a Hardware Description Language (HDL), which is then synthesized into a network of digital logic gates.

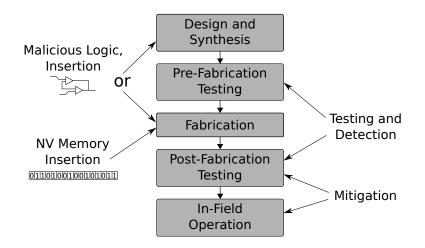

The network of interconnected digital logic gates is referred to as a netlist. The gates and wires in the netlist are then placed and routed, respectively, on the surface of the chip, which results in a circuit layout file that is passed on to the IC fabrication facility (foundry). A simplified view of the IC design and fabrication process is shown in Figure 2.1.

Before the design is sent to a foundry for fabrication, it is subjected to pre-fabrication testing and validation. The traditional objective of this phase is to ensure that the design meets functional and performance specifications. The complexity of modern day ICs prohibits the use of formal verification tools to exhaustively verify the entire state-space of the design. Instead, simulation-based testing is used with the goal of covering a significant portion of the state-space.

Fabricated ICs are subjected to post-fabrication testing and validation.

Figure 2.1: The hardware fabrication process. Malicious circuitry may be inserted at either the design and synthesis, or the fabrication phase. The former may be detectable at either the pre- or post-fabrication testing and validation phases. The latter is detectable at the post-fabrication phase only.

Due to cost concerns, only a relatively small portion of the state-space, compared to pre-fabrication testing, can be verified during post-fabrication testing. The traditional purpose of post-fabrication testing is to identify chips that have random, non-malicious defects.

ICs of even moderate complexity can consist of millions of lines of HDL code and millions of gates and wires. In a typical design flow, the HDL code is programmed by teams of programmers in different parts of the world. In addition, portions of the HDL may be purchased from external vendors. Finally, a large majority of IC design companies are *fabless*, i.e., they outsource IC fabrication to a potentially untrusted third-party foundry. The complexity and decentralized nature of the IC design and fabrication processes is the primary reason for the increased threat of malicious hardware being inserted in one or more stages of the design and fabrication flow.

Attacker Model Malicious circuitry can potentially be inserted at the design/synthesis phase or the fabrication phase, or both, of the process shown in Figure 2.1. The former involves an attacker modifying the HDL code or the circuit netlist. The latter involves the attacker modifying the circuit layout at the IC foundry.

Malicious hardware inserted during the design/synthesis stage must avoid

detection during the pre- and post-fabrication testing process, while hardware inserted in the fabrication process only needs to escape post-fabrication testing. Although it might seem beneficial to only insert attacks post-fabrication, we note that the attacker has less flexibility in modifying the layout file compared to the HDL code or circuit netlist — once a layout file is sent from the IC vendor to the foundry, any changes in the layout that change the physical dimensions of the chip are immediately observable. Thus, the malicious foundry is restricted to inserting attacks in the "dead space" — unused silicon area between logic gates.

Our work proposes a non-deterministic timer attack that can be inserted in the design or fabrication process of which the exact details are discussed in Chapter 3. Our proposed defence mechanism only addresses the threat from outsourcing the fabrication to an untrusted source of which the details are discussed in Chapter 4.

### 2.2 Related Work

There is a considerable body of prior work on hardware security. Our work pertains to the design of a non-deterministic timer that can be used to trigger a maliciously inserted hardware backdoor and a defence mechanism that adds security to the fabrication process of ICs in non-trusted facilities. We discuss the related work in the context of both the proposed attack and countermeasure. We also discuss prior research on the technology used in our contributions, namely the use of True Random Number Generators (TRNGs) and 3D IC technology.

#### 2.2.1 Attacks

Broadly, an attack on computer hardware is the modification of the circuitry so that it behaves in a manner not intended by the original designer. The malicious circuitry is typically dormant till it is triggered. Three types of triggers are discussed in prior work [75]: data based, timer based and hybrid triggers. Jin et al. [37] describe the outcome of a competition in which teams of researchers were tasked with inserting hardware attacks in the HDL description of a cryptographic device. The hardware trojans that Jin et al. describe all utilize either a data- or time-trigger to enable the malicious backdoor circuit. Data-based triggers monitor internal wires of the circuit for specific bit patterns, and trigger when this pattern is detected. King et al. [41] describe an attack that is triggered by the receipt of an unsolicited network packet containing a "magic" byte; this is an example of a data based trigger. On the other hand, ticking time bombs trigger after a certain number of clock cycles have elapsed. (A ticking time bomb is what we call timer-based trigger.)

The number of clock cycles elapsed before the time bomb is triggered can be either deterministic [76, 75] or non-deterministic (as in this work). Wang et al. [76] quantify the hardware resource utilization of a number of different trigger implementations including a deterministic ticking time bomb and a hybrid data and time trigger.

Once triggered, backdoors can either log and transmit sensitive information, modify the circuit functionality, or modify performance specification such as clock frequency and power dissipation [69]. A number of backdoor attacks encompassing these broad categories have been proposed in the literature and we refer the reader to the work of Tehranipoor and Koushanfar for more details [69]. We note that the proposed non deterministic timer based trigger can, in theory, be used to activate any hardware backdoor.

#### 2.2.2 Countermeasures

The most natural phases at which attack-mitigation can occur are the preand post-fabrication testing and validation phases of Figure 2.1. Attack mitigation techniques aim to detect or disable malicious circuitry. Indeed, for an attack to be successful, it must evade detection or disablement at these stages.

Hicks et al. [33] propose a pre-fabrication validation technique, referred to as unused circuit identification (UCI), to detect pairs of wires in the design that have the same logic value for all test inputs. The intervening logic between these wires is then flagged as potentially malicious. UCI has since been defeated [65], but we show an alternative exploit that is discussed in more detail in Section 5.1.2.

Banga and Hsiao [10], and Zhang and Tehranipoor [81] propose using equivalence checking and formal verification techniques to check the functionality of a gate level netlist or HDL code against a formal specification. As prior work [75] points out, such techniques are ineffective against timers. Furthermore, as the trigger cannot be activated by external inputs and does not by itself interact with the original design (although the backdoor it triggers presumably does), it is undetected by pre-fabrication equivalence checking and formal verification.

Post-fabrication IC fingerprinting, i.e., measuring the physical characteristics — power dissipation, clock frequency, temperature and electro-magnetic (EM) signatures — of fabricated ICs and comparing them to a gold standard has been proposed as a technique to detect malicious circuitry by a number of prior researchers [3, 6, 38, 54, 78, 80]. These measurements are typically noisy because of inherent variability in the fabrication process and limited precision of measurement instruments. To escape detection, the impact of malicious hardware on the physical characteristics of the IC should be small enough to be statistically indistinguishable from measurement noise.

As we discuss in Section 5.1.4, IC fingerprinting appears to offer the most promise in defending against our non-deterministic timer. However, as we discuss there, some technical challenges need to be addressed before it can be effective.

Waksman and Sethumadhavan [75] propose countermeasures specifically to defend against hardware triggers. In particular, they note that any deterministic timer based trigger must maintain some internal volatile state that can be reset by intermittently power cycling the chip. As we point out in Section 1.1, power cycling, in this context, is a limited operation by which some volatile state such as register- and pipeline-contents are lost, but other state such as cache- and non-volatile memory-contents are retained. Program execution also stops briefly, and the program counter is saved to and restored from non-volatile memory.

They propose also that any on-chip NV-memory used to maintain state can be disabled during post-fabrication testing using a sufficiently large number of such power cycles. We discuss the ineffectiveness of these countermeasures against our timer in Section 3.1. The main issue here is the frequency of power cycling — to disable our timer, it has to be two orders of magnitude more frequent than prior work considers [75], a frequency that is impractical.

Use of TRNGS and NV Memory for Hardware Security Hardware TRNGs have been widely used in cryptographic primitives and security protocols. A number of hardware TRNG implementations have been proposed in the literature — for our proposed non-deterministic attack, we focus on fully-synthesizable implementations that utilize digital logic only and build upon the design suggested by Sunar et al. [67]. Recently, Wang et al. [77] have proposed a non-volatile Flash memory based TRNG that could conceivably be used for a non-deterministic timer attack, but provides lower throughput. In addition, an NV memory based malicious TRNG can be disabled by the post-fabrication test time power cycling defence proposed by Waksman and Sethumadhavan [75]. Finally, we note that the recently proposed TARDIS technique [55] exploits randomness to measure time spent in power off state, but has no direct relationship to our work.

**3D** Integration for Hardware Security Valamehr et al. [73] also exploit 3D integration capabilities to enhance the security of computer hardware, although in a manner orthogonal to ours. Their proposal involves adding a "control tier" on top of a regular IC to monitor the activity of internal wires in the IC in a cost effective way. By monitoring internal wires on the chip, the control tier is able to detect potentially malicious activity and take appropriate recourse. Adding the monitors vertically on top of the IC to be protected reduces the power and performance cost of monitoring the IC. Another technique along similar lines was proposed by Bilzor [14].

Or technique exploits 3D integration in a different way, i.e., we use it to provide a malicious attacker in an IC foundry with an incomplete view of the circuit netlist, thus deterring the attack. Although the potential for this kind of defence mechanism has been alluded to before by Tezarron in their white paper [71], ours is the first work to address this technique in any consequential way.

Anonymizing Databases and Social Networks Our proposed defence bears relationship to prior work on anonymizing databases and social network graphs, but also has significant differences. A database is k-anonymous if the information for each individual is indistinguishable from k - 1 other individuals [68] in the database. The notion of k-anonymity for a social network is similar, except that instead of operating on relational data, it operates on a graph. Two individuals in a social network are indistinguishable if their local neighbourhoods are the same [83].

In our setting, the similarity of the local neighbourhood of two gates is only a necessary but not sufficient condition for indistinguishability. This is because the attacker is assumed to have access to the original circuit netlist and an incomplete view of the same netlist, and must thus match *all* gates in the incomplete netlist to gates in the original netlist.

The circuit obfuscation problem also introduces a number of distinct practical issues. These include the additional information that might be conveyed by the circuit layout (for example, the physical proximity of gates), and the role of the number of gate types in the technology library.

## Chapter 3

# The Non-Deterministic Timer

In this chapter we formalize the exact attack model that pertains to our nondeterministic timer attack, review the previous work on defence mechanisms in Section 3.1. Then we present the theory that allows for a controllable random timer in Section 3.2, in Section 3.3 we show the frame work of our non-deterministic timer on real hardware and in Section 3.4 we analyze the results and costs of the non-deterministic timer in comparison to the deterministic timer.

Attacker Model The proposed non-deterministic timer is comprised of two distinct hardware components, a circuit consisting of digital logic gates (including ring oscillators), and NV-memory. The phase in which each of these malicious components are inserted in the hardware depends on the specific design flow adopted by the IC vendor. For example, in their deterministic timer attack, Waksman and Sethumadhavan [75] assume collusion between a malicious designer that inserts digital logic during the design/synthesis phase and a malicious foundry that inserts NV-memory during fabrication. The same scheme can be used by an attacker to insert the proposed non-deterministic timer attack, as shown in Figure 2.1.

Alternatively, the attack could also be inserted entirely in the design/synthesis phase or entirely in the fabrication phase. An attacker might prefer the former for an IC design and fabrication flow in which CMOS compatible NV-memory technology can be directly instantiated in the design. Such capabilities are increasingly beginning to appear in IC foundry design kits [53, 62]. On the other hand, a fabrication phase only attack is also feasible if sufficient dead space is available on the chip. In our analysis of the strength of the proposed attack, we have evaluated all relevant pre- and post-fabrication countermeasures against malicious hardware of which we are aware. We show that, regardless of the attack model, a non-deterministic timer can be at least as, if not more pernicious than a deterministic timer.

### **3.1** Deterministic Timers

In this section, we discuss deterministic timers. In Section 3.1.1, we discuss the state of the art in deterministic timers, and a countermeasure from prior work. In Section 3.1.2, we discuss a new kind of deterministic timer we have conceptualized, and demonstrate that it cannot be disabled in the manner that the timer from Section 3.1.1 can. In Section 3.1.3, we point out that such deterministic timers introduce a trade-off between the size of non-volatile state, and the time-window that volatile state has to be maintained.

#### 3.1.1 State of The Art

A deterministic timer triggers after exactly t clock cycles of chip operation. All deterministic timer implementations of which we are aware, for example the implementations proposed by Waksman and Sethumadhavan [75] and Wang et al. [76], need access to non-volatile state. In a counter based timer, for example, the current count is persistent state.

The simplest deterministic timer stores non-volatile state in on-chip volatile memory. A simple defence against such a timer is to periodically turn off the power to the chip. When the power is restored, the state in the volatile memory is reset to a default value. This is referred to as power cycling. If the number of clock cycles between successive power cycles,  $t_p$ , is less than the trigger time, t, then the timer never triggers.

In their work, Waksman and Sethumadhavan [75] consider a more powerful deterministic timer-based trigger that makes use of on-chip NV memory. A drawback of using NV memory is that it has limited write durability. This means that each bit in NV memory can only be written to a limited number of times, after which it loses its ability to store data. Therefore, an attack, to be practical, must be frugal in the number of updates it makes to its non-volatile state.

To address the limited write durability of the NV memory, the timer

proposed by Waksman and Sethumadhavan [75] uses the following protocol. The state of the counter is stored in volatile memory. However, if the chip is powered off, the volatile state is transferred to NV memory <sup>1</sup>. It is transferred back to volatile memory when the chip is powered back on. To defend against this attack, that work proposes an elegant defence mechanism. The chip is repeatedly power cycled during post-fabrication testing. As the NV memory is written to once in every power cycle, it burns out if the number of power cycles exceeds its write durability. Thus the timer is rendered ineffective.

#### 3.1.2 Modified Deterministic Timer Protocol

We now discuss a modification of the deterministic timer-based trigger proposed by Waksman and Sethumadhavan [75], which makes the attack immune to repeated power cycling during post-fabrication testing by sacrificing some of the state. In the modified protocol, the NV memory is not written to every time the chip is powered off. Instead, the NV memory is only updated at regular intervals of time, which will drop the current volatile state during a power cycle but will retain the previously stored state.

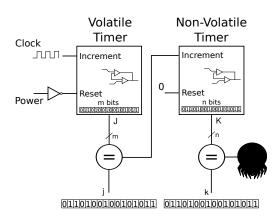

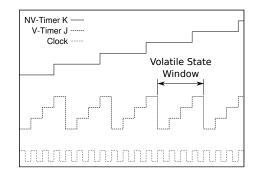

A simple implementation of the modified timer comprises both a volatile timer and an NV timer that uses m bits of NV memory. The volatile timer triggers after  $t_v$  clock cycles, increments the NV timer and resets. The attack is triggered when the NV timer reaches a value k, where  $k \leq 2^m - 1$ . This protocol is illustrated in Figure 3.1 and 3.2 for clarity. Compared to the deterministic timer of Waksman and Sethumadhavan [75], the NV memory is updated at most k times, regardless of how many times the chip is power cycled. Therefore, the NV memory cannot be burned out during postfabrication testing. (Of course, we need to ensure that the number of writes to each of the m bits is upper-bounded by the write durability. A sufficient condition is that k is bounded by the write durability.)

While power cycling cannot be used to burn out NV memory in the post-fabrication testing phase, it is still possible to defend against the attack using power cycling in the field. This is another countermeasure proposed by Waksman and Sethumadhavan [75]. In particular, if the number of clock cycles between successive power cycles,  $t_p \leq t_v$ , the volatile counter will never trigger and the NV memory will never get updated.

<sup>&</sup>lt;sup>1</sup>This scheme writes to the NV memory the minimum number times to avoid any loss of state. In other words this scheme is the most frugal protocol that always maintains state.

Figure 3.1: Block diagram of a deterministic timer attack that utilizes a volatile timer chained with a non-volatile timer.

Figure 3.2: Timing diagram for the operation of deterministic timers. The graph shows three signals: the primary clock signal (Clock), the count stored in the volatile state (V-Timer), and the count stored in NV memory (NV-Counter).

We now consider a case study that demonstrates that for realistic attack scenarios, even relatively infrequent power cycling can defend against a deterministic timer attack.

We assume that the attacker wants the trigger to occur after the IC operates for one year in the field. We assume also, based on the characterization of 30-nm NAND Flash technology by Cai et al. [20], that the NV memory can tolerate 10,000 program/erase cycles. Based on these assumptions, the NV memory can be written to at most once every 52 minutes (365 days / 10,000 writes). Therefore, power cycling the chip at any rate faster than once every 52 minutes prevents the timer from going off.

To put this in perspective, Waksman and Sethumadhavan [75] have shown that power cycling complex digital logic as frequently as once a second results in negligible performance impact. This case study illustrates that the limited write durability of NV memory severely limits the effectiveness of deterministic timer based triggers.

#### 3.1.3 NV Memory and Volatile State Window Trade-off

In this section, we continue our discussions of the deterministic timer-based trigger from the previous section. Specifically, we observe that it introduces a trade-off between the size of non-volatile state, and the time-window that volatile state needs to be maintained.

Thus far in our discussions, we have implicitly assumed that binary encoding is used to store data in the NV memory. Thus, the Least Significant Bit (LSB) in the NV memory changes value every time the count is updated. Counting up to a value k results in k writes to the LSB of the NV memory.

To reduce the length of the time-window of volatile state, redundant bits in the NV memory can be used to reduce the number of times each bit in the NV memory is written to while counting up to a value k. However, as we express with the following lemma, it is easy to intuit a lower-bound on the number of bits m required to represent k as a function of k and the write-durability of the NV memory, w.

**Lemma 1.** At least one bit of an m bit memory is written to at least  $\frac{k}{m}$  times to count up to k. Therefore,  $m \geq \frac{k}{w}$ .

We now analyze our scenario from the case study in the previous section. We assume a desired trigger time of one year and an NV memory with a write durability of 10,000 program/erase cycles. We pose the following question: how many bits of NV memory are required that allow it to be written to only once every second? Our intent with this question is to shrink the time-window that volatile state is maintained in an attempt to evade the countermeasure of power-cycling.

If the NV memory is updated every second, it will be written to  $\approx 3.154 \times 10^7$  in a year. Based on Lemma 1, at least 3154 bits of NV memory are needed to reduce the volatile state window to one second. This is a > 200× increase in the number of bits compared to the prior case study where a compact binary encoding was assumed.

NV memory has a different circuit structure compared to on-chip digital logic or volatile memory. Therefore, larger NV memory increases the likelihood of the attack being detected by visually inspecting a small number of fabricated chips. In our proposed non-deterministic timer, we seek to use as few bits of NV memory as possible.

### **3.2** Non-Deterministic Timer

In this section, we present the design of our non-deterministic timer. Adopting the mindset of the attacker, we have two design goals. One is is to break the apparent trade-off that we discuss in the previous section: between the size of non-volatile storage (NV-memory), and the length of time that volatile state has to be maintained. That is, we want the size of NV-memory to be only the bare minimum. Yet, we would like the time that volatile state must be maintained to be brief as well so that the timer is resistant to countermeasures that erase the volatile state, specifically power cycling. As we discuss in the previous section, this design goal is related to the write durability of the NV memory as well.

Our other design goal is to gain control over when the timer triggers. Our non-deterministic timer is based on random events. So what we want is sufficient control over the expectation and standard deviation of when the timer triggers. We want, with high probability, the timer to trigger at a time of our choosing.

In the next section, we discuss an implementation of our design. The implementation requires that we address some technical challenges of its own. We defer a discussion of those to the next section.

Our timer works as follows. We maintain a counter K to keep track of when the timer should trigger. When K reaches a pre-defined value k, the timer triggers.

We do not use a periodic clock to increment a counter, as in deterministic timers. Instead, we assume access to a source of randomness. (We discuss in the next section how we realize one in practice.) We conduct a series of Bernoulli trials. Each such trial has one of only two outcomes: success or failure. We increment K if and only if we have a successful trial.

We need persistent state to maintain the counter K, up to a value k, only. Each of our Bernoulli trials is independent of the others, and their probabilities are identically distributed. We can choose the probability of success of a trial to be arbitrarily low to increase the expected number of trials between successful events to be arbitrarily large. This way, we can avoid over-utilization of the NV memory.

Other than the counter K, we need to maintain no state. The only actions we perform between increments of K (updates to the non-volatile state) are the Bernoulli trials, and a check of the outcome of each. There is no difference

Figure 3.3: Block diagram of a non-deterministic timer attack that utilizes a TRNG chained with a non-volatile timer. The key is compare with the output of the TRNG (see Section 3.3.1).

Figure 3.4: Operation of nondeterministic timers. The bottom graph shows the IC's clock signal and the top graph shows the timer's current count. The graph shows three signals: the clock signal (Clock), the output of the TRNG (TRNG X) and the count stored in NV memory (Timer K).

between Bernoulli trials before or after a power-cycle.

**Single-event trigger** To explain our design in more detail, we first consider the somewhat simpler objective of a single-event trigger. That is, a timer that triggers after one successful Bernoulli trial. If our design is used for a single-event trigger, we can control the expectation, but not the standard deviation.

Let  $N \in [1, \infty)$  be the random variable that measures the number of trials up to and including the first success. We consider what the Probability Mass Function (pmf), expectation, variance and standard deviation are for the random variable N. For some value n that N can take, the pmf, denoted f(n) maps n to the probability that N = n. The variance measures how widely spread the values that N takes with non-zero probability are, and the standard deviation is the square root of variance. We have the following for the pmf, expectation, variance and standard deviation, respectively, where p is the probability that a Bernoulli trial succeeds.  $f(n) = p(1-p)^{n-1}$ ,  $E(N) = \frac{1}{p}$ ,  $V(N) = \frac{1-p}{p^2}$ , and,  $\sigma \approx \frac{1}{p}$ , for small p. For small p, the ratio  $\sigma/E(N) \approx 1$  which indicates a wide distribution around the expected value.

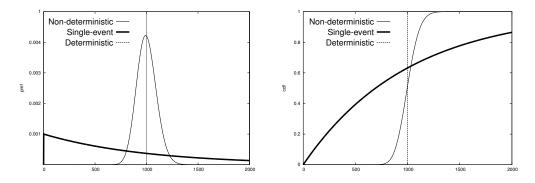

As an example let E(N) = 1000, p = 0.001. In Figure 3.5, we show the

corresponding pmf and the Cumulative Distribution Function (cdf). The cdf is the probability that the random variable N takes a value at most n, for various n (the horizontal axis in Figure 3.5). We observe from the cdf that more than half of the timers are likely to go off before 750 trials, which is less than the expected trigger time of 1000 trials.

The single event trigger has another drawback from the perspective of the attacker: it has a high probability of detection during the post-fabrication testing phase. Assume that the testing phase lasts for the first 100 trials. From the cdf in Figure 3.5, we observe that there is a 9.5% chance of a timer being triggered in this phase, thus compromising the attack. Even worse for the attacker, if each fabricated IC is tested, the likelihood that the attack is detected in at least one IC is even higher. If even 100 ICs are tested, the attack is detected with probability 0.999.

We now discuss the multiple event trigger which results in a more favourable distribution of attack time in terms of emulating a deterministic trigger and reducing the likelihood of early detection.

**Multiple-event trigger** We now analyze the statistics of waiting for k successes, instead of a single success, before triggering the attack. Let  $N_i$  be a random variable that represents number of Bernoulli trials between the  $(i-1)^{th}$  and  $i^{th}$  success. As before, let N represent the total number of trials before k successes. We know that:

$$N = \sum_{i=1}^{k} N_i$$

$N_i$ , for all  $i \in [1, K]$ , are independent and identically distributed random variables with a distribution that was derived in the preceding discussion on the single event trigger. As a consequence of the Central Limit Theorem [52], the distribution of random variable N will, as  $k \to \infty$ , tend to a Normal distribution with expectation

$$E(N) = kE(N_i) = \frac{k}{p}$$

and standard deviation

$$\sigma_N = \sqrt{k}\sigma_{N_i} = \frac{\sqrt{k}}{p}$$

We observe that standard deviation as a percentage of the expected number of trials after which the attack triggers depends on the value of k only. In

Figure 3.5: The pmfs (left) and cdfs for three different timer designs. Each trigger is designed to have an expectation E(N) = 1000. The deterministic timer is shown as dotted, the single event trigger is shown in bold and the multiple event non-deterministic timer is shown as solid, not bold.

particular,  $\frac{\sigma_N}{E(N)} = \frac{1}{\sqrt{k}}$ . Thus, large values of k result in a narrow distribution around the expected trigger time, while smaller values of k result in a wider distribution. Thus, k is a knob that the attacker can control to effect an attack that either resembles a deterministic attack (large k), or appears to be seemingly random.

Figure 3.5 shows the pmf and cdf of attack time for a multiple event non-deterministic timer (k = 100, p = 0.1 and E(N) = 1000), along with the deterministic and single event trigger distributions for reference. Observe from the figure, that the pmf and cdf of the multiple event timer are, qualitatively, much closer to that of a deterministic timer than that of a single event timer.

In addition, compared to a single event trigger, the multiple event trigger has a much lower likelihood of early detection. As before, if 100 trials are used in post-fabrication testing, the probability that the attack is detected on any given IC is only  $10^{-100}$ . Thus, even if 100,000 ICs are fabricated and each is tested, the attack is detected with probability of only  $\approx 10^{-94}$ .

We note that, in the discussion so far, we have used the abstract notion of trials as a measure to time. This is easily converted to physical units by noting the time period (in seconds) between successive trials. We discuss this in more detail in the next section.

# 3.3 Hardware Realization