# Design of a Time Based Analog to Digital Converter

by

#### Mohamed Amin

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2012

© Mohamed Amin 2012

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Analog to digital converter (ADC) plays a very important role in any mixed analog/digital system. Because digital CMOS technology can take advantage of technology scaling, system designers try to increase the percentage of the digital part of the system. This means moving the ADC more and more towards the input of the system which results in making the role of the ADC more and more critical. With technology scaling, the switching characteristics of MOS transistors offer superb timing accuracy at high frequencies. This makes the time based analog to digital converter (TADC) a good alternative to the conventional ADCs in sub-micron region.

In this thesis, an all digital TADC structure is proposed. This TADC is based on an analog to time converter (ATC), followed by a time to digital converter (TDC). The TDC is based on sigma-delta ( $\Sigma\Delta$ ) modulation. A non-linear multi-bit internal quantizer in  $\Sigma\Delta$  modulator is used to counteract the nonlinearity introduced when the VCO is used as the ATC. The novel TADC also uses an implicit sample and hold (S/H) circuit to reduce area. Dynamic element matching (DEM) is used to improve the robustness of the system against random mismatch in the multi-bit quantizer. Both first and second order  $\Sigma\Delta$  modulator TADC are proposed. Simulations and measurements on the proposed TADC are provided. Measurements, from a prototype chip fabricated using  $0.13\mu m$  CMOS technology, show that the first order TADC has achieved a dynamic range of 11 bits for a bandwidth of 2MHz. While simulation results show a dynamic range of 12 bit. Simulations show that the second order TADC has achieved a dynamic range of 12bit for a bandwidth of 20MHz.

#### Acknowledgements

I would like to express my gratitude to my supervisor, Dr. Bosco Leung, whose expertise, understanding, and patience, added considerably to my graduate experience. I appreciate his vast knowledge, and his assistance in writing this thesis.

I would like to thank the members of my committee, Dr. Ajoy Opal, Dr. Slim Boumaiza, and Dr. Ehab Abdel-Rahman for the assistance they provided at all levels of the research work. I would also like to thank Dr. Shahriar Mirabbasi from the University of British Columbia for taking time out from his busy schedule to be the external committee member.

My gratitude also goes to Canadian Microelectronics Cooperation (CMC) and all its stuff, there are not enough words to describe your excellent work. Sarah Neville, and Feng Liu, thanks for your support during the layout and fabrication of my chips. Special thanks to Mariusz Jarosz for providing me with the testing equipments.

I am grateful to Phil Regier and Fernando Hernandez for helping me out on various computer-related issues. I am also grateful to all my friends inside and outside the university how helped me during my stay in Kitchener/Waterloo. Special thanks to Hassan Mostafa, Mostafa Hassan, Noman Hai, and Adam Neale.

I would also like to thank my parents. It is their love, dedication, selflessness, encouragement, support, confidence in my abilities and most importantly their prayers that have helped me overcome all the challenges of my academic life. Their personal tutoring, mentoring and interest in my overall academics during my school years have helped shape my career into what it is now. No words of appreciation can accurately reflect how thankful I am to them. I pray for their health and long and happy lives. I would also like to thanks my brother and sister. I cannot imagine my life without them.

### Dedication

To my parents, My brother, and my sister

## Contents

|   | List | of Ta           | bles        |                                      | X    |

|---|------|-----------------|-------------|--------------------------------------|------|

|   | List | List of Figures |             |                                      |      |

|   | Lis  | t of A          | bbreviat    | ions                                 | xvii |

| 1 | INT  | ΓROD            | UCTIO       | N                                    | 1    |

|   | 1.1  | Motiv           | ation       |                                      | 2    |

|   | 1.2  | Thesis          | s Organiza  | ation                                | 3    |

| 2 | BA   | CKGI            | ROUND       |                                      | 4    |

|   | 2.1  | Analo           | g to digita | al converter                         | 4    |

|   | 2.2  | Sampl           | ing         |                                      | 5    |

|   | 2.3  | Quant           | ization     |                                      | 6    |

|   | 2.4  | ADC             | characteri  | stics                                | 6    |

|   | 2.5  | ADC             | types .     |                                      | 7    |

|   |      | 2.5.1           | Nyquist     | rate direct conversion ADCs          | 8    |

|   |      | 2.5.2           | Oversan     | npling direct-conversion ADCs        | 9    |

|   |      | 2.5.3           | Nyquist     | rate TADCs                           | 14   |

|   |      |                 | 2.5.3.1     | Dual slope ADC                       | 14   |

|   |      | 2.5.4           | Oversan     | npling TADC                          | 16   |

|   |      |                 | 2.5.4.1     | Analog-to-time converter             | 16   |

|   |      |                 | 2.5.4.2     | Time to Digital converter            | 17   |

|   |      |                 | 2.5.4.3     | Analog-to-frequency/period converter | 17   |

|   |      |                 | 2.5.4.4     | Period to digital converter          | 20   |

| 3 | TIN | IE-BA   | SED $\Sigma\Delta$ A    | NALOG-TO-DIGITAL CONVERTER                                                               | <b>22</b> |

|---|-----|---------|-------------------------|------------------------------------------------------------------------------------------|-----------|

|   | 3.1 | First-o | rder $\Sigma\Delta$ mod | ulator in time domain                                                                    | 22        |

|   | 3.2 | Implici | t sample and            | hold in the VCO                                                                          | 26        |

|   |     | 3.2.1   | The VCO im              | plicit sample and hold operation                                                         | 26        |

|   |     | 3.2.2   | Tracking erro           | or                                                                                       | 28        |

|   |     | 3.2.3   | Non-uniform             | sampling                                                                                 | 30        |

|   | 3.3 | The no  | n-linear inter          | nal quantizer                                                                            | 31        |

|   | 3.4 | Prelim  | nary design:            | varying the reference clock                                                              | 33        |

|   | 3.5 | Design  | I: First-order          | $\Sigma \Delta$ modulator, phase interpolation incorporated                              | 37        |

|   |     | 3.5.1   | New structur            | e for the input VCO                                                                      | 38        |

|   |     | 3.5.2   | Phase interpo           | olation                                                                                  | 39        |

|   |     | 3.5.3   | -                       | g the non-linear multibit internal quantizer in PI                                       | 42        |

|   |     |         | 3.5.3.1 Inpu            | ut VCO with PI                                                                           | 42        |

|   |     |         | 3.5.3.2 Refe            | erence VCO with PI                                                                       | 44        |

|   |     | 3.5.4   | The function            | ality of the proposed TADC                                                               | 44        |

|   |     | 3.5.5   | Simulation re           | esults                                                                                   | 47        |

|   |     | 3.5.6   | Nonidealities           |                                                                                          | 50        |

|   |     |         | 3.5.6.1 Non             | n-uniform sampling                                                                       | 50        |

|   |     |         | 3.5.6.2 Miss            | match in the DTC                                                                         | 51        |

|   | 3.6 | _       |                         | er $\Sigma\Delta$ modulator, PI, and Dynamic element ed (to further decrease distortion) | 53        |

|   |     | 3.6.1   | Dynamic eler            | ment matching: Review                                                                    | 53        |

|   |     |         | 3.6.1.1 Clo             | cked level averaging DEM                                                                 | 54        |

|   |     |         | 3.6.1.2 Indi            | ividual level averaging DEM                                                              | 56        |

|   |     |         | 3.6.1.3 Dat             | a weighted averaging DEM                                                                 | 56        |

|   |     |         | 3.6.1.4 Sto             | chastic level averaging DEM                                                              | 56        |

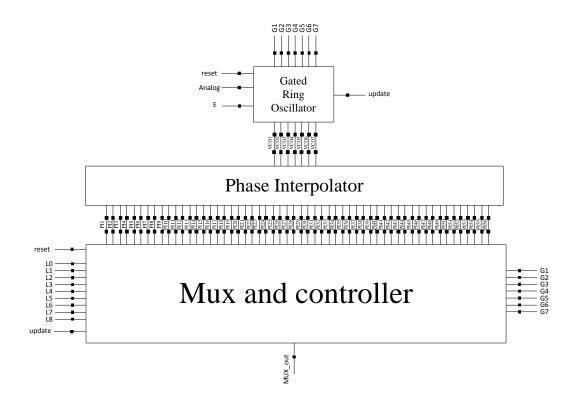

|   |     | 3.6.2   | Proposed VC             | O structure: block diagram                                                               | 56        |

|   |     | 3.6.3   | -                       | O: Implementation of non-linear multibit quan-                                           | 59        |

|   |     | 3.6.4   |                         | feedback DAC                                                                             | 60        |

|   |     |         |                         |                                                                                          |           |

|   |     | 3.6.5  | Simulati    | on results                                                              | 60  |

|---|-----|--------|-------------|-------------------------------------------------------------------------|-----|

|   | 3.7 | _      |             | ond-order $\Sigma\Delta$ modulator, PI, and DEM incorporated bandwidth) | 65  |

|   |     | 3.7.1  | The seco    | ond-order sigma-delta modulator in time domain                          | 66  |

|   |     |        | 3.7.1.1     | Gated Ring Oscillator                                                   | 69  |

|   |     |        | 3.7.1.2     | Second order TADC with GRO                                              | 69  |

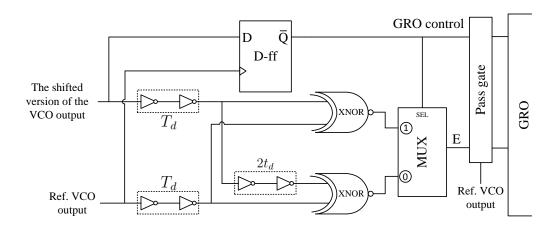

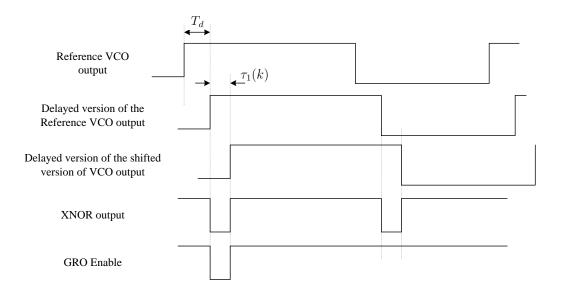

|   |     |        | 3.7.1.3     | The phase detector and the timing circuit for the GRO                   | 71  |

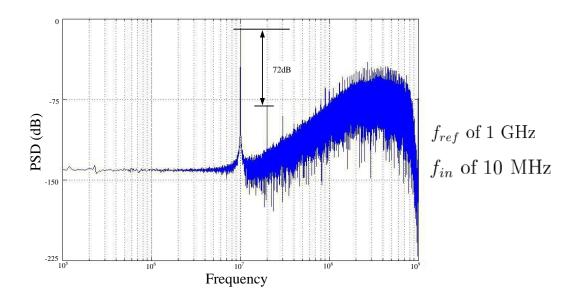

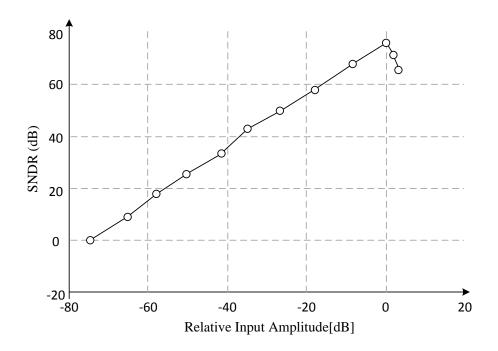

|   |     | 3.7.2  | Simulati    | on results                                                              | 73  |

| 4 | TES | STINO  | J           | EVEL SIMULATIONS, FABRICATION, AN                                       | 75  |

|   | 4.1 |        |             | order $\Sigma\Delta$ modulator, phase interpolation incorporated        |     |

|   |     | 4.1.1  |             | or-level simulation                                                     | 75  |

|   |     | 4.1.2  |             | Jitter                                                                  | 84  |

|   |     | 4.1.3  |             | onsumption                                                              | 89  |

|   |     | 4.1.4  |             |                                                                         | 89  |

|   |     | 4.1.5  | PCB de      | $\operatorname{sign}$                                                   | 89  |

|   |     | 4.1.6  | Testing     |                                                                         | 89  |

|   | 4.2 | _      |             | t order $\Sigma\Delta$ modulator, PI, and Dynamic element porated       | 98  |

|   |     | 4.2.1  | Transist    | or-level simulation                                                     | 98  |

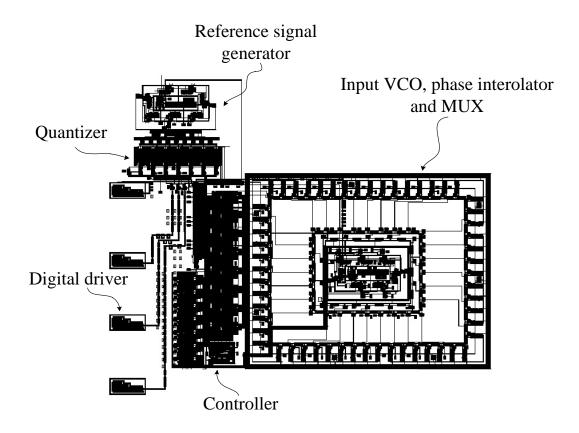

|   |     | 4.2.2  | Layout      |                                                                         | 110 |

|   |     | 4.2.3  | Testing     |                                                                         | 111 |

|   | 4.3 | Design | ı III: Seco | and order $\Sigma\Delta$ modulator, PI, and DEM incorporated            | 111 |

|   |     | 4.3.1  | Transist    | or level simulation                                                     | 111 |

|   |     | 4.3.2  | Layout      |                                                                         | 116 |

|   |     | 4.3.3  | Testing     |                                                                         | 116 |

| 5 | CO  | NCLU   | SIONS       | AND FUTURE WORK                                                         | 117 |

|   | 5.1 | Major  | contribu    | tions                                                                   | 118 |

|   | 5.2 | The st | ate-of-the  | e-art                                                                   | 119 |

|   | 5.3 | Future | work        |                                                                         | 110 |

| API            | APPENDIX                                                          |     |  |  |

|----------------|-------------------------------------------------------------------|-----|--|--|

| A.1            | Static specification                                              | 122 |  |  |

| A.2            | Dynamic specification                                             | 125 |  |  |

| A.3            | Maximum frequency due to the tracking error $\dots \dots \dots$ . | 127 |  |  |

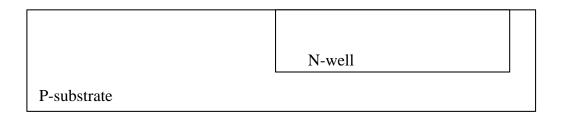

| A.4            | Fabrication of MOS transistor                                     | 131 |  |  |

| A.5            | Design of printed circuit board                                   | 137 |  |  |

| BIBLIOGRAPHY 1 |                                                                   |     |  |  |

| ענע            | DIDDIOGICAL ILL                                                   |     |  |  |

## List of Tables

| 4.1 | Definitions of symbols used in Figure 4.5                                | 81  |

|-----|--------------------------------------------------------------------------|-----|

| 4.2 | Analog values and feedback codes that result in $1ns$ VCO period         | 81  |

| 4.3 | Definitions of symbols used in Figure 4.26                               | 100 |

| 4.4 | current status/feedback codes pairs to active $C_8$                      | 105 |

| 4.5 | Conditions for change-group control signal activation                    | 105 |

| 4.6 | Definitions of symbols used in Figure 4.34                               | 109 |

| 4.7 | Definitions of symbols used in Figure 4.37                               | 114 |

| 4.8 | Definitions of symbols used in Figure 4.38                               | 114 |

| 5.1 | Comparison of performance of the proposed TADC with the state-of-the-art | 121 |

|     |                                                                          |     |

# List of Figures

| 2.1  | Example of 3-bit ADC                                                  | 4  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | The spectrum of the samples signal in case $f_s \geq 2 \times f_{BW}$ | 5  |

| 2.3  | The spectrum of the samples signal in case $f_s \geq 2 \times f_{BW}$ | 6  |

| 2.4  | An example of quantization noise                                      | 7  |

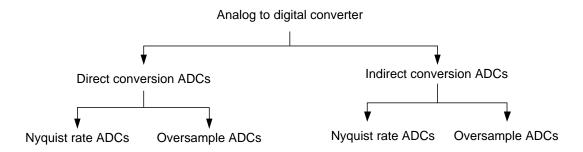

| 2.5  | ADCs Types                                                            | 8  |

| 2.6  | Flash ADC                                                             | 9  |

| 2.7  | First-order sigma-delta modulator                                     | 10 |

| 2.8  | First-order sigma-delta modulator equivalent circuit                  | 11 |

| 2.9  | The spectral density of $N(f)$ compared with that of $E(f)$           | 12 |

| 2.10 | The second order sigma-delta modulator                                | 13 |

| 2.11 | The dual slope ADC                                                    | 15 |

| 2.12 | Current starved inverter                                              | 16 |

| 2.13 | An example TDC                                                        | 17 |

| 2.14 | Vernier delay line                                                    | 18 |

| 2.15 | Simplified diagram of VCO                                             | 18 |

| 2.16 | Example of VCO output signal                                          | 19 |

| 2.17 | One simple PDC                                                        | 20 |

| 2.18 | Modulo $2^n$ implementation of the FDC                                | 21 |

| 2.19 | Modulo $2^1$ implementation of the FDC $\dots$                        | 21 |

| 3.1  | Time version of the first order $\Sigma\Delta$ modulator              | 23 |

| 3.2  | Waveform representation of Fig. 3.1 when $V_{in} = V_{ref}/2$         | 24 |

| 3.3  | Block diagram representation of equation (3.3)                        | 25 |

| 3.4  | The input VCO                                                                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5  | The inherent sample and hold                                                                                                                                                                      |

| 3.6  | Definition of tracking error                                                                                                                                                                      |

| 3.7  | The relation between $t_{error}$ and $t_{1LSB}$                                                                                                                                                   |

| 3.8  | The relation between the triangle and sinusoidal $V_{in}$                                                                                                                                         |

| 3.9  | Non-linearity due to non-uniform sampling followed by uniform reconstruction                                                                                                                      |

| 3.10 | An example of a triangle wave                                                                                                                                                                     |

| 3.11 | An example of non-linear quantizer                                                                                                                                                                |

| 3.12 | Improving the linearity of the TADC by using non-linear quantizer technique                                                                                                                       |

| 3.13 | Reference VCO structure                                                                                                                                                                           |

| 3.14 | Preliminary design block diagram                                                                                                                                                                  |

| 3.15 | Waveform example of the preliminary design                                                                                                                                                        |

| 3.16 | FFT of the digital output                                                                                                                                                                         |

| 3.17 | FFT of the digital output for the improved system                                                                                                                                                 |

| 3.18 | The new structure for the input VCO                                                                                                                                                               |

| 3.19 | Representative waveforms for the VCO shown in Figure $3.18 \dots 40$                                                                                                                              |

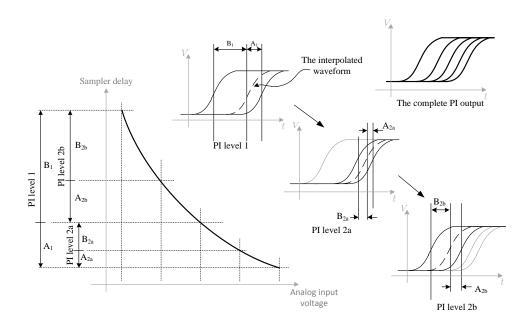

| 3.20 | The phase interpolator                                                                                                                                                                            |

| 3.21 | 2-level phase interpolator                                                                                                                                                                        |

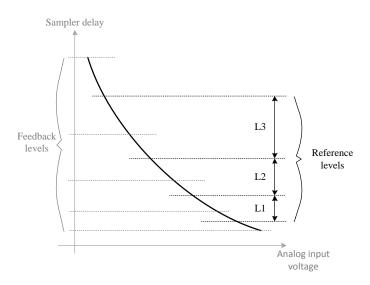

| 3.22 | Non-uniform phase interpolation: an example                                                                                                                                                       |

| 3.23 | An example of a reference levels for a nonlinear curve                                                                                                                                            |

| 3.24 | Input VCO with PI                                                                                                                                                                                 |

| 3.25 | The reference VCO with PI                                                                                                                                                                         |

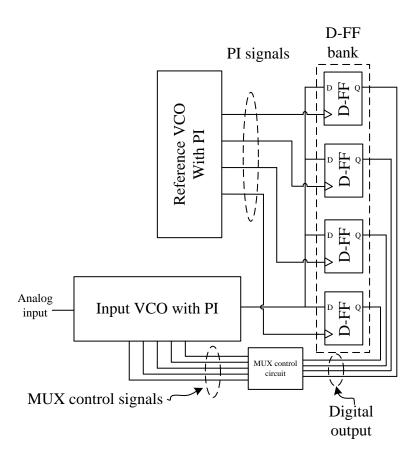

| 3.26 | The proposed TADC with PI                                                                                                                                                                         |

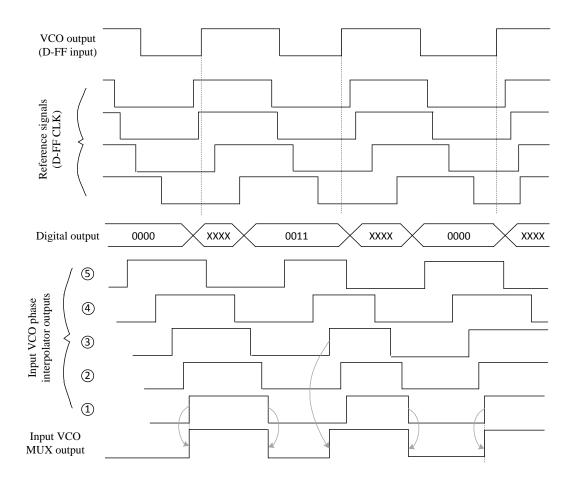

| 3.27 | Set of representative waveforms for the proposed TADC when $V_{in} = V_{ref}/2 \dots \dots$ |

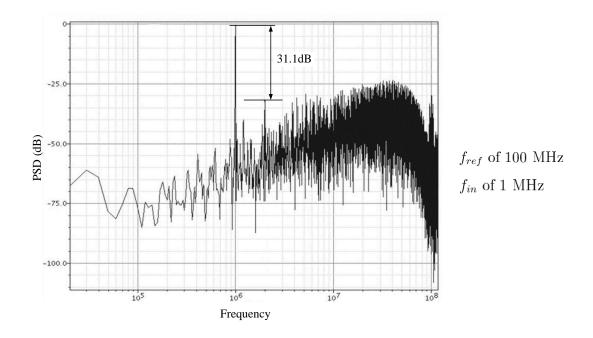

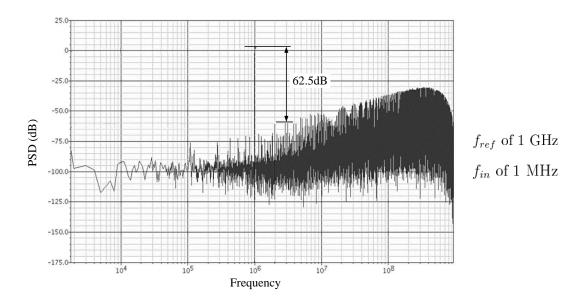

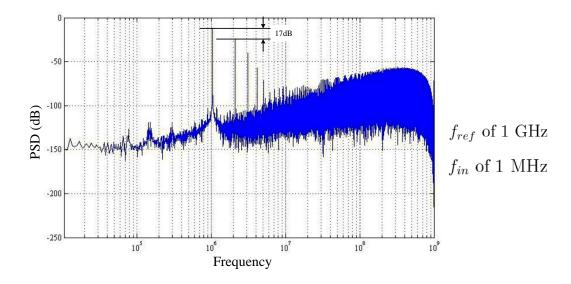

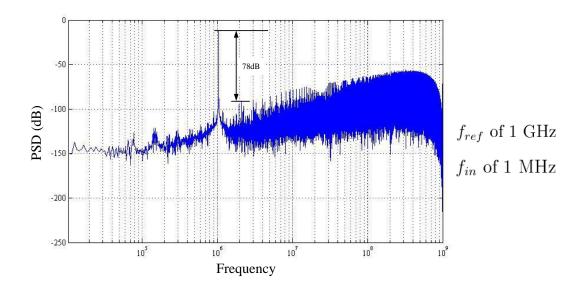

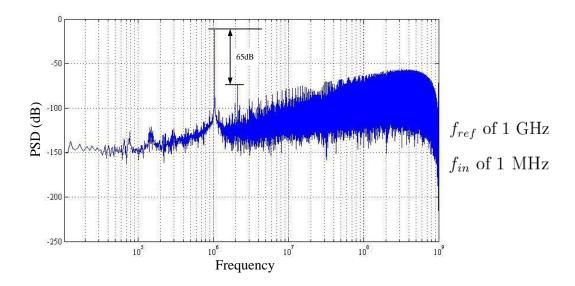

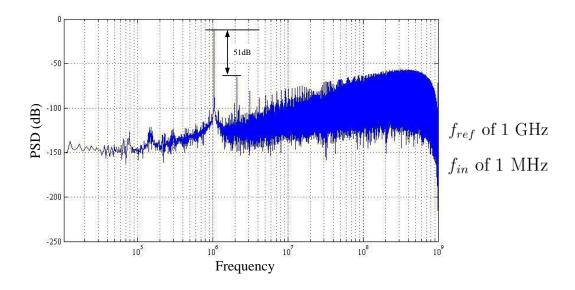

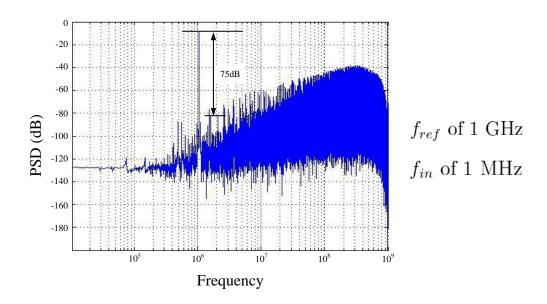

| 3.28 | FFT of the system with linear quantizer                                                                                                                                                           |

| 3.29 | FFT of the system with non-linear multibit quantizer                                                                                                                                              |

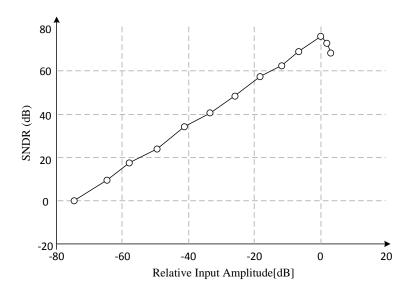

| 3.30 | System level simulation SNDR as function of signal amplitude $\dots$ 49                                                                                                                           |

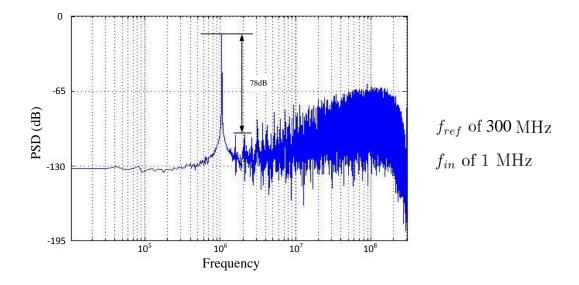

| 3.31 | FFT of the system with non-linear multi-bit quantizer, and 300MHz reference frequency, same distortion level as the 1GHz case                                                                     |

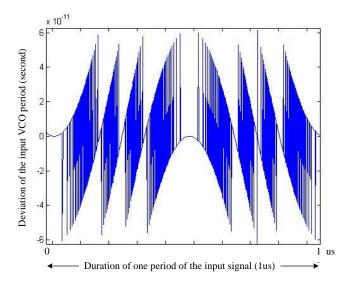

| 3.32 | The deviation of the input VCO period from its nominal value                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

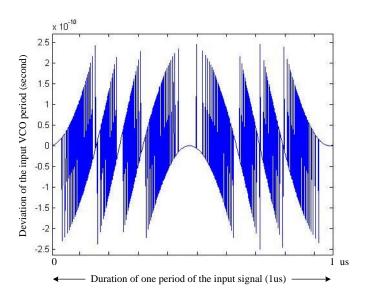

| 3.33 | The deviation of the input VCO period from its nominal value, $K_{VCO}$ is four time that of Figure 3.32                                                       |

| 3.34 | FFT of the TADC with NUS distortion that is present at input VCO period deviation of $250ps$                                                                   |

| 3.35 | FFT of the TADC with $5\%$ mismatch                                                                                                                            |

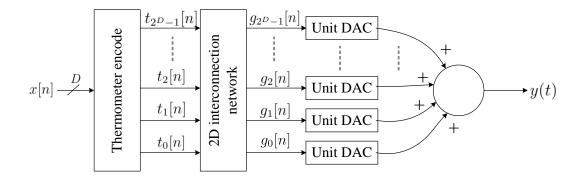

| 3.36 | D bit DEM DAC                                                                                                                                                  |

| 3.37 | An example of a clocked level averaging                                                                                                                        |

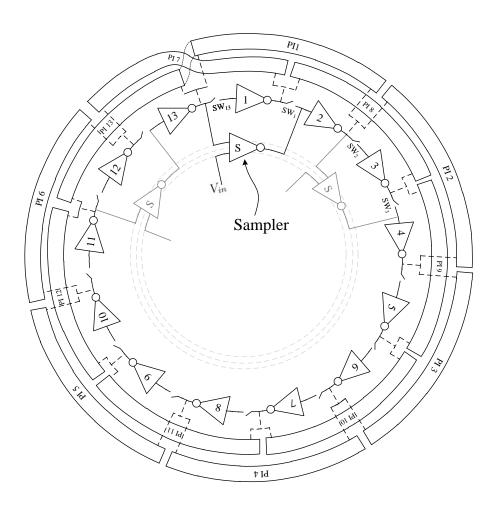

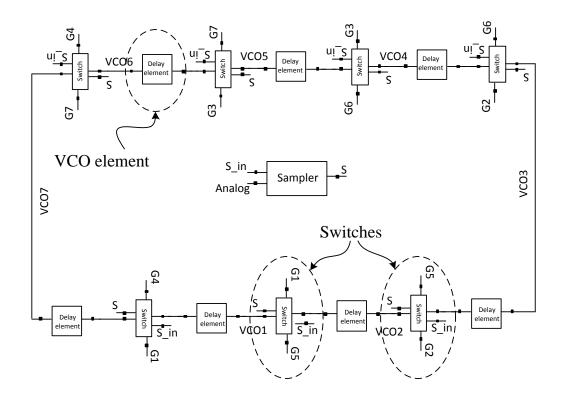

| 3.38 | The proposed input VCO structure with DEM                                                                                                                      |

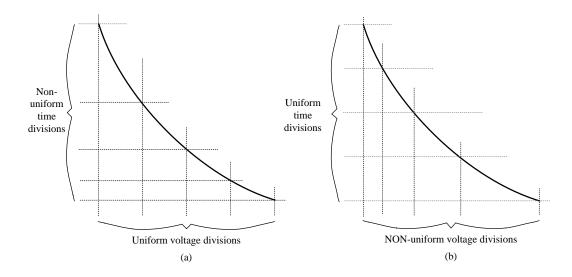

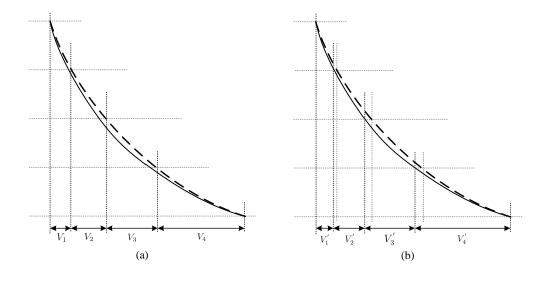

| 3.39 | (a)uniform voltage non-linear quantizer approach (b)uniform time non-linear quantizer approach                                                                 |

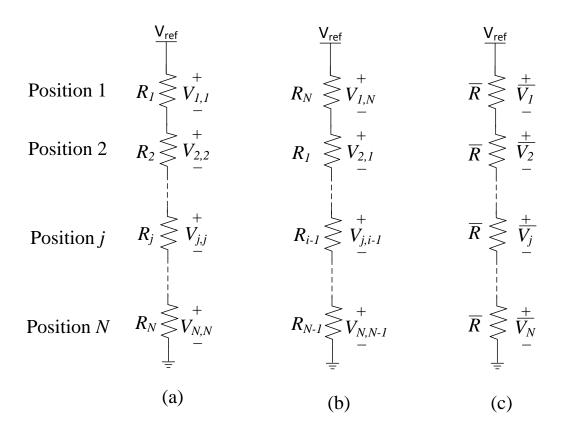

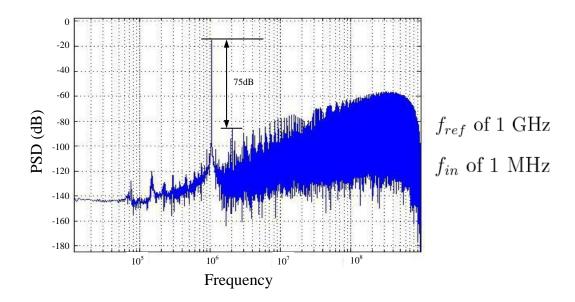

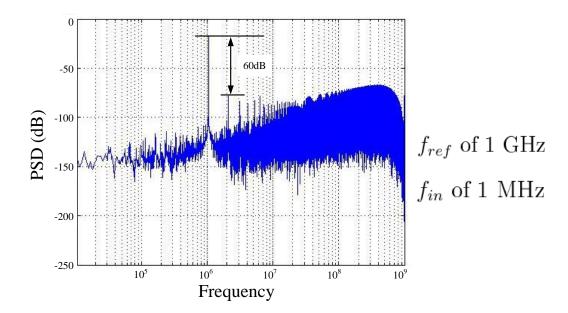

| 3.40 | FFT of the output of the proposed system                                                                                                                       |

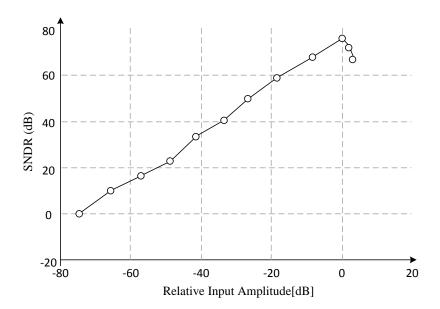

| 3.41 | System level SNDR as function of signal amplitude                                                                                                              |

| 3.42 | FFT of the output of the proposed system with 10% mismatch                                                                                                     |

| 3.43 | Improving the mismatch between the piecewise linear approximation and the actual characteristic curve of the sampler using digital correction                  |

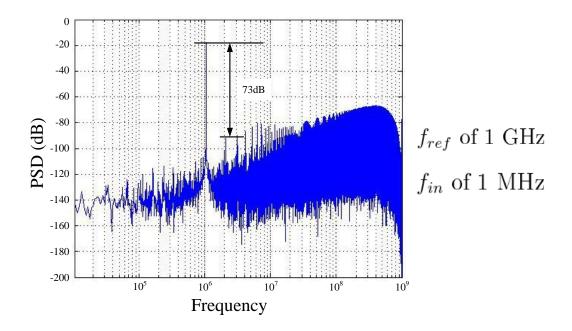

| 3.44 | FFT of the output of the proposed system with 10% mismatch between the piecewise linear approximation curve and the actual characteristic curve of the sampler |

| 3.45 | FFT of the output of the proposed system with digital correction .                                                                                             |

| 3.46 | The second order system proposed in literature                                                                                                                 |

| 3.47 | Block diagram of the second order $\Delta\Sigma$ TADC                                                                                                          |

| 3.48 | Representative waveforms for the system shown in Figure 3.47, $V_{in} = V_{ref}/2$                                                                             |

| 3.49 | The equivalent block diagram of $(3.17)$ , and $(3.18)$                                                                                                        |

| 3.50 | The gated ring oscillator                                                                                                                                      |

| 3.51 | (a)GRO is enabled (b)GRO is not enabled                                                                                                                        |

| 3.52 | The second order system with GRO                                                                                                                               |

| 3.53 | The proposed idea to decrease the GRO period                                                                                                                   |

| 3.54 | The timing circuit for the GRO                                                                                                                                 |

| 3.55 | Waveform of timing circuit for the GRO, only one GRO enable pulse per period                                                                                   |

| 3.56 | FFT of the output of the second order system                                                | 74  |

|------|---------------------------------------------------------------------------------------------|-----|

| 3.57 | system level simulation SNDR as function of signal amplitude, $10\%$ mismatch is included   | 74  |

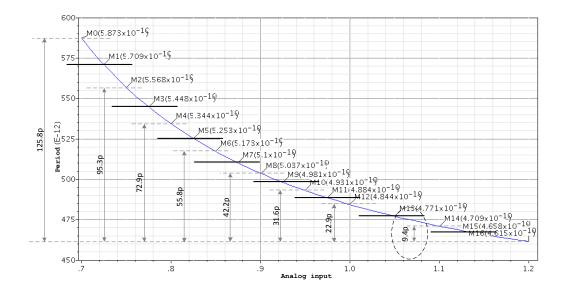

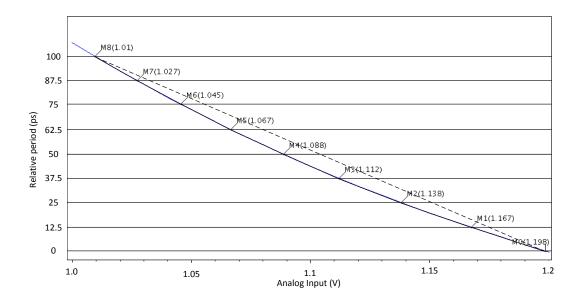

| 4.1  | The non-linear characteristic curve of the VCO sampler                                      | 76  |

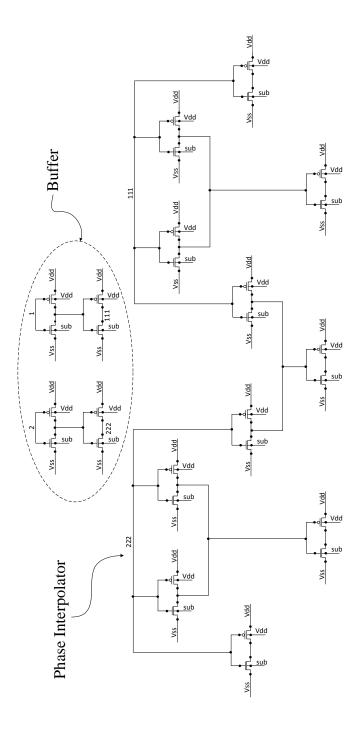

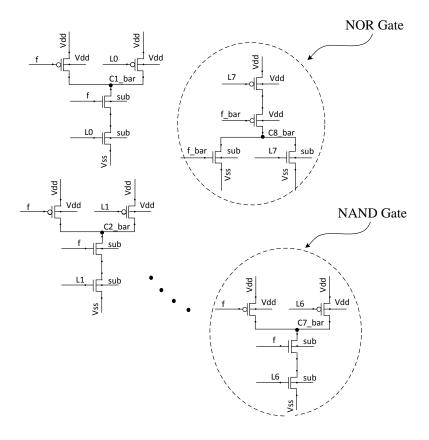

| 4.2  | Schematic of the phase interpolator                                                         | 77  |

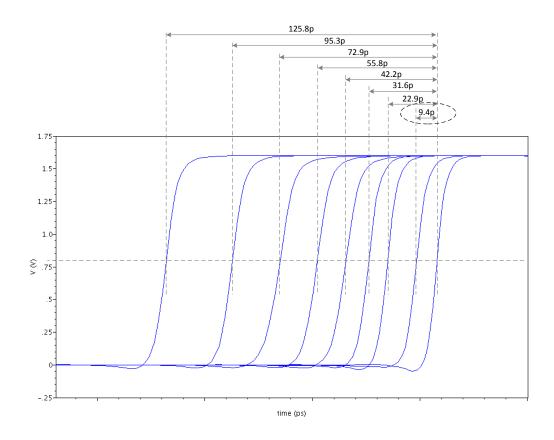

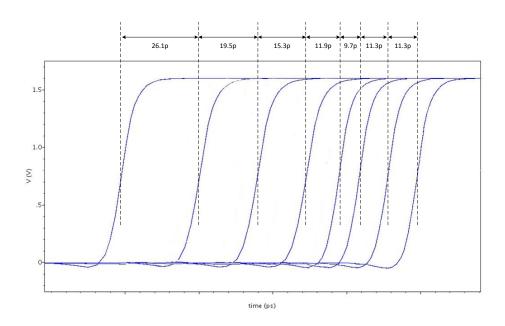

| 4.3  | The output of the phase interploator                                                        | 78  |

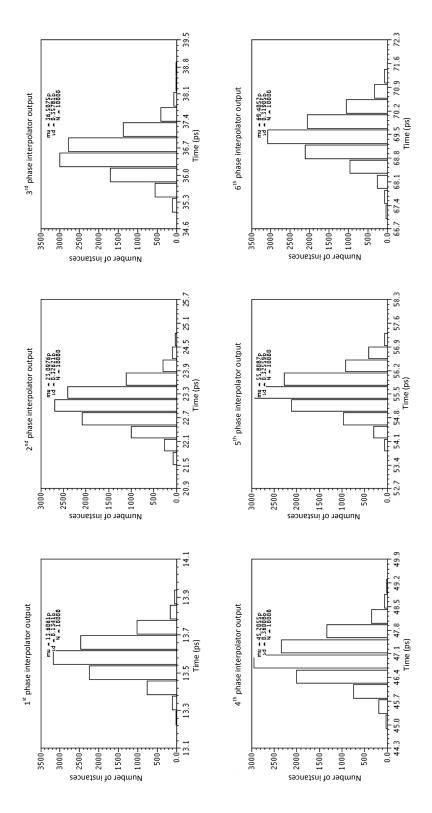

| 4.4  | Monte-carlo simulations on the output of the phase interploator, $0.1\%$ standard deviation | 79  |

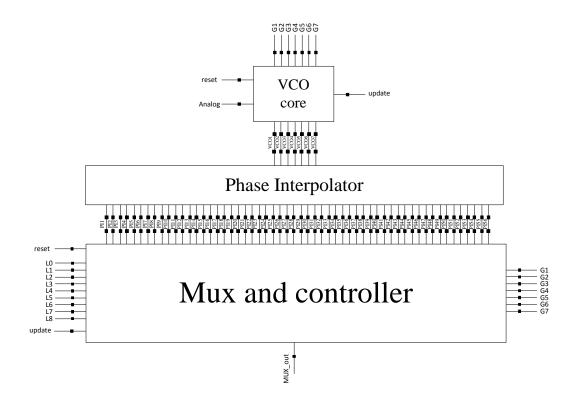

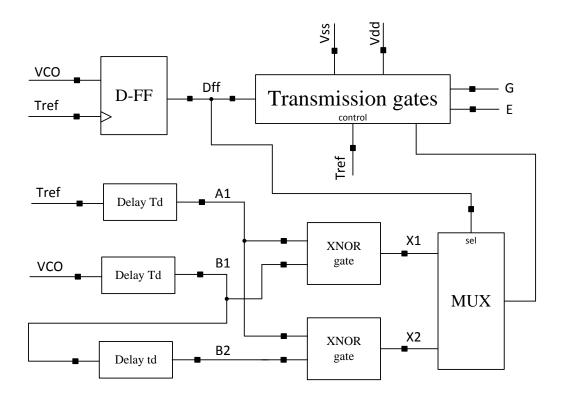

| 4.5  | Schematic of the MUX control circuit                                                        | 80  |

| 4.6  | Schematic of the VCO with PI                                                                | 82  |

| 4.7  | The output of the phase interpolator of the reference phase generator                       | 83  |

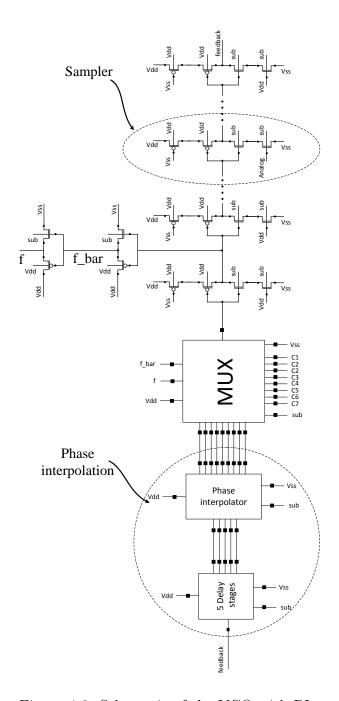

| 4.8  | Schematic of the TADC                                                                       | 83  |

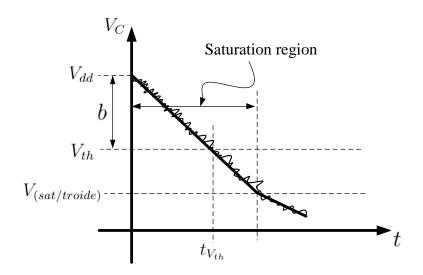

| 4.9  | Timing jitter when $V_{th}$ is greater than $V_{(sat/troide)}$                              | 85  |

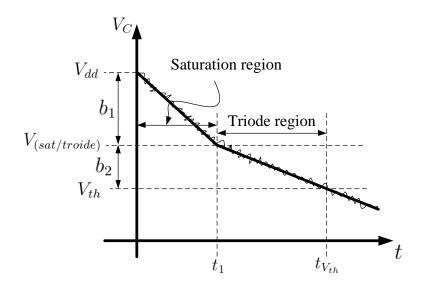

| 4.10 | Timing jitter when $V_{th}$ is smaller than $V_{(sat/triode)}$                              | 85  |

| 4.11 | the 4-transistor inverter                                                                   | 87  |

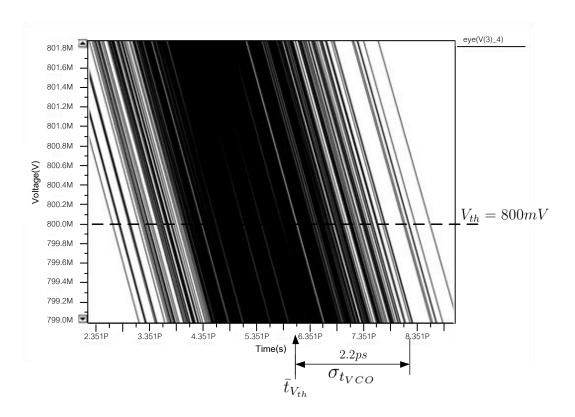

| 4.12 | Eldo simulation for the timing jitter                                                       | 88  |

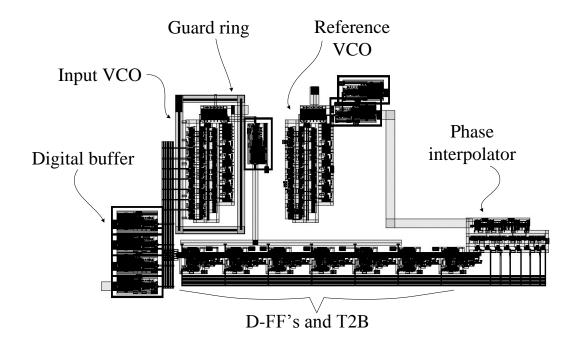

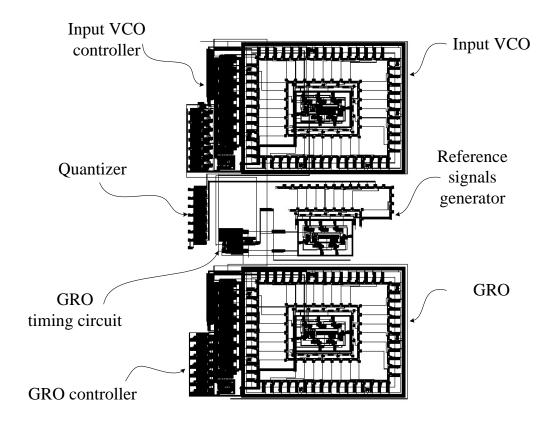

| 4.13 | The layout of the core TADC                                                                 | 90  |

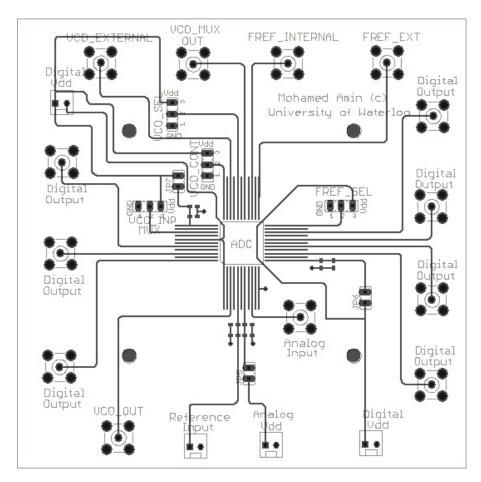

| 4.14 | The top view of the PCB used to test design I                                               | 91  |

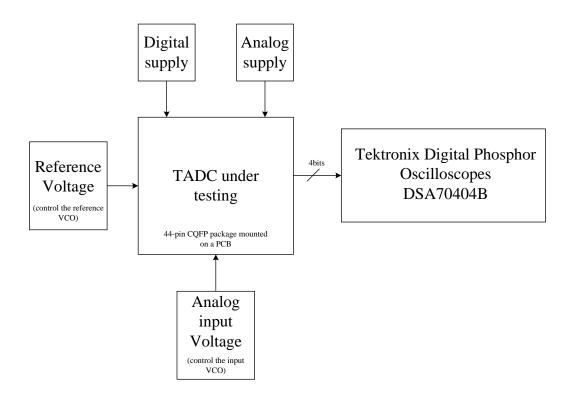

| 4.15 | Testing setup for design I                                                                  | 92  |

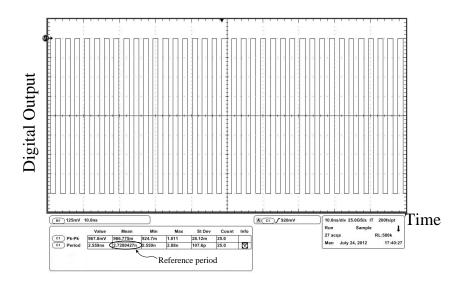

| 4.16 | The output of the reference VCO                                                             | 93  |

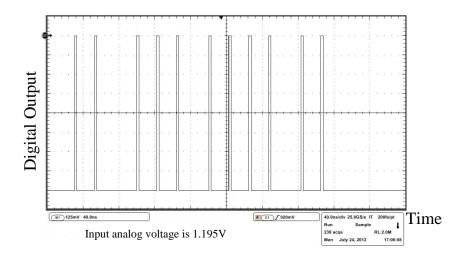

| 4.17 | Examples of the output of the TADC's D-FF when $V_{in}=1.195V$                              | 93  |

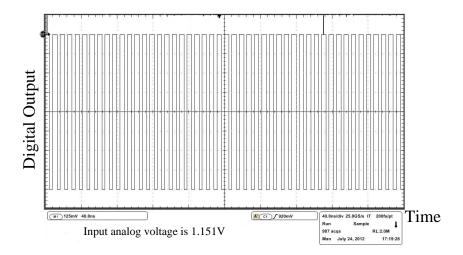

| 4.18 | Examples of the output of the TADC's D-FF when $V_{in}=1.151V$                              | 94  |

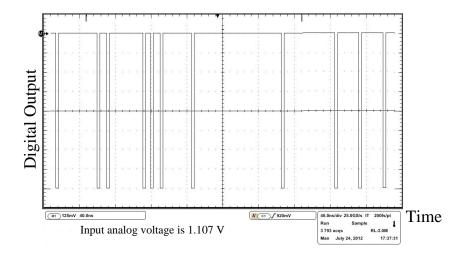

| 4.19 | Examples of the output of the TADC's D-FF when $V_{in}=1.107V$                              | 94  |

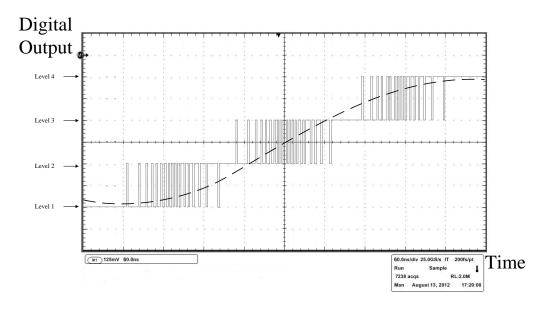

| 4.20 | The output of the TADC for a sinusoidal input signal                                        | 95  |

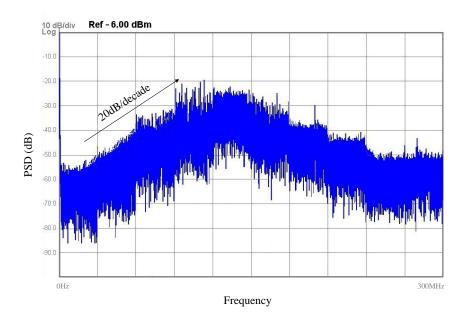

| 4.21 | $2^{19}$ point FFT of the signal shown in Figures 4.20                                      | 95  |

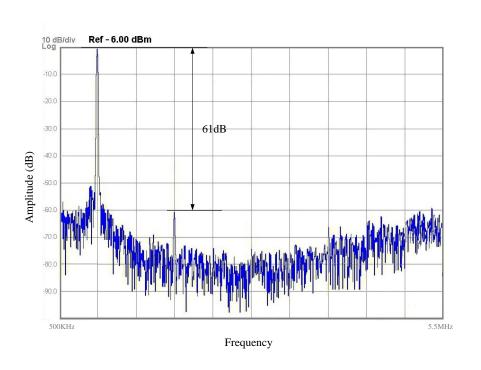

| 4.22 | A zoom in version of Figure 4.21                                                            | 96  |

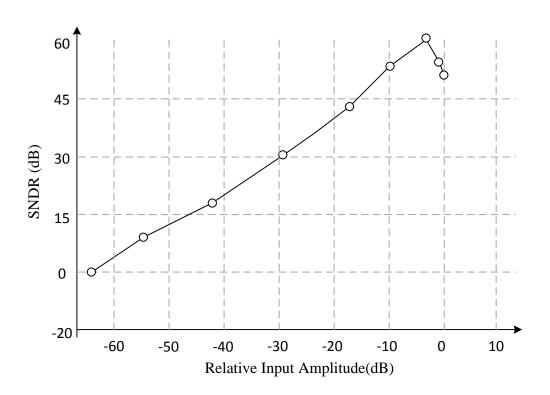

| 4.23 | SNDR as function of signal amplitude                                                        | 97  |

| 4.24 | The non-linear characteristic curve of the VCO sampler                                      | 98  |

| 4.25 | Schematic of the VCO                                                                        | 99  |

| 4.26 | Schematic of the VCO core                                                                   | 100 |

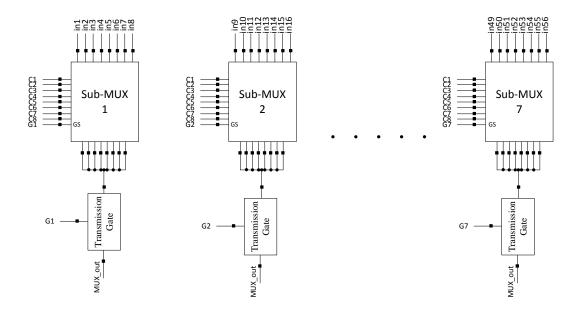

| 4.27       | Schematic of the MUX                                             | 101 |

|------------|------------------------------------------------------------------|-----|

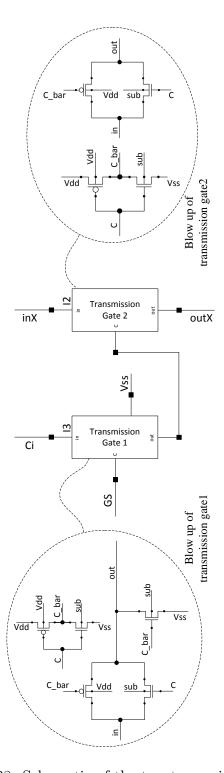

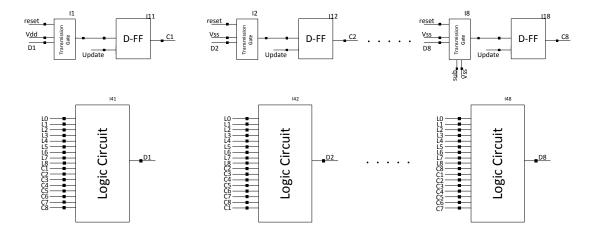

| 4.28       | Schematic of the two transmission unit                           | 102 |

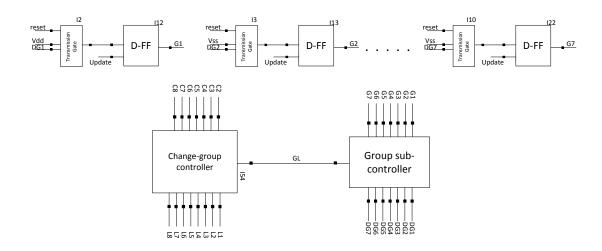

| 4.29       | Schematic of the group controller                                | 103 |

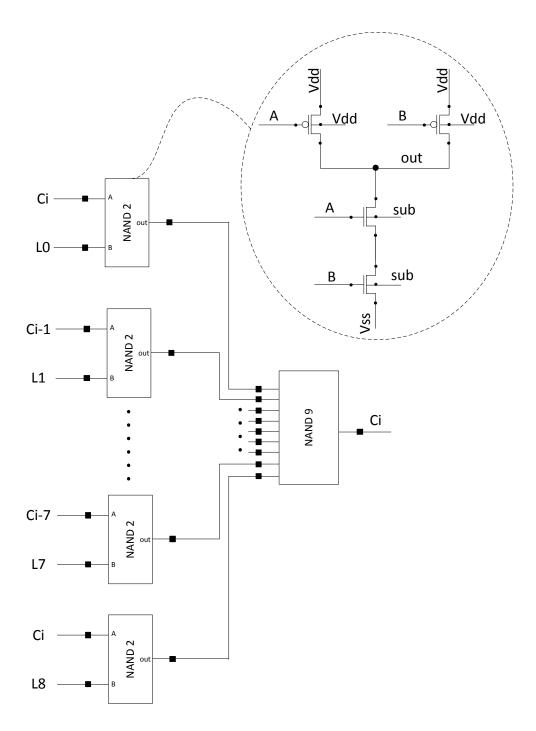

| 4.30       | Schematic of the element controller                              | 103 |

| 4.31       | Schematic of the element-sub-controller                          | 104 |

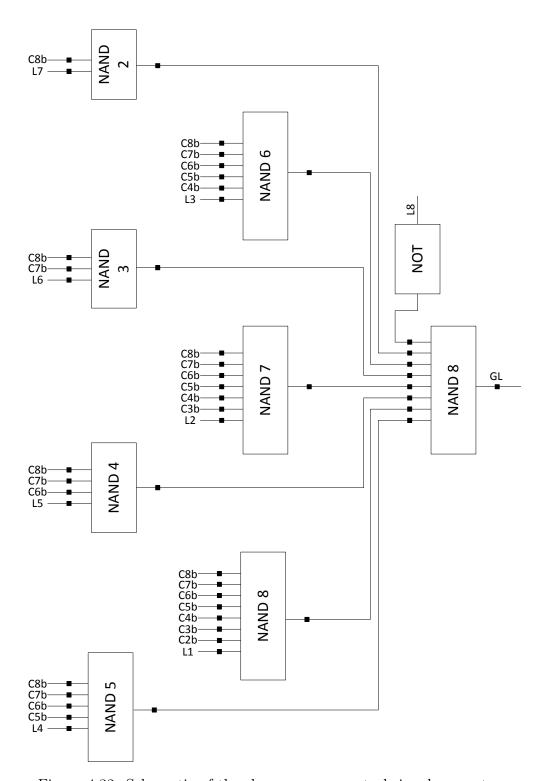

| 4.32       | Schematic of the change-group control signal generator $\dots$ . | 106 |

| 4.33       | Schematic of the group controller sub-sub-controller             | 108 |

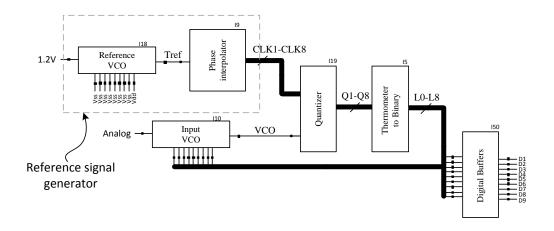

| 4.34       | Schematic of the TADC                                            | 109 |

| 4.35       | The layout of the TADC $$                                        | 110 |

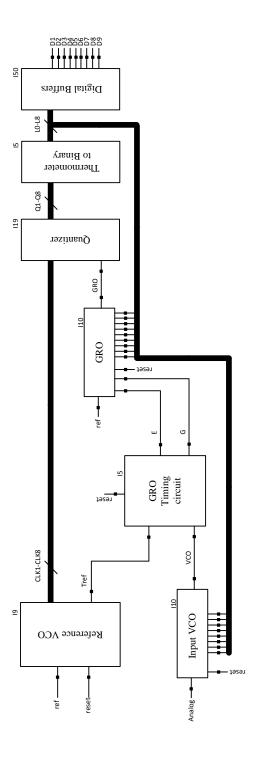

| 4.36       | Schematic of the GRO                                             | 112 |

| 4.37       | Schematic of the GRO timing circuit                              | 113 |

| 4.38       | Schematic of the TADC                                            | 115 |

| 4.39       | The layout of the TADC $$                                        | 116 |

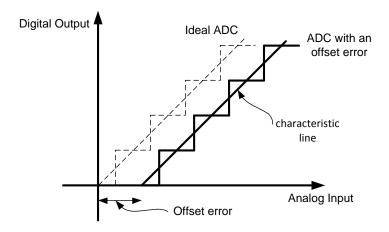

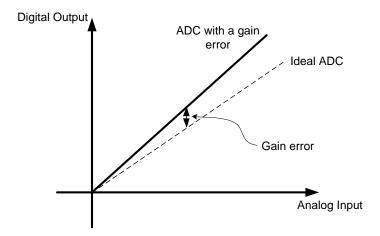

| A.1        | Example of an ADC has an offset error                            | 122 |

| A.1<br>A.2 |                                                                  | 123 |

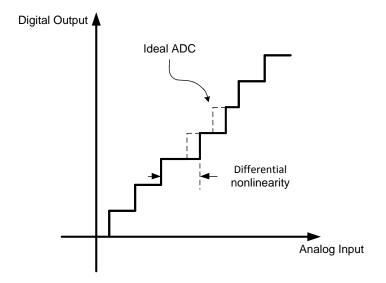

| A.3        | Example of differential non linearity in ADC                     |     |

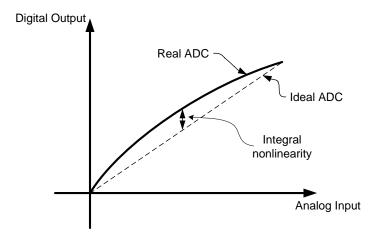

| A.4        | Example of integral non linearity in ADC                         | 125 |

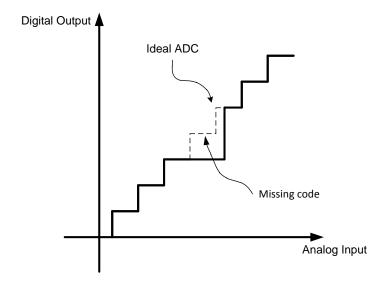

| A.4<br>A.5 | Example of a missing codes                                       | 125 |

| A.6        |                                                                  | 127 |

| A.7        |                                                                  | 127 |

|            |                                                                  | 131 |

|            | $v_{1LSB}$ changes as $v_{in}$ sweep through the range           |     |

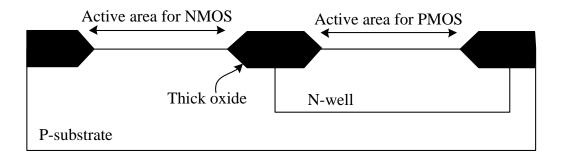

|            | Active area identification                                       | 132 |

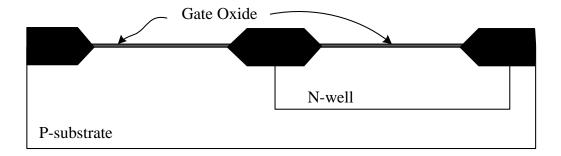

|            | Gate oxide foundation                                            | 132 |

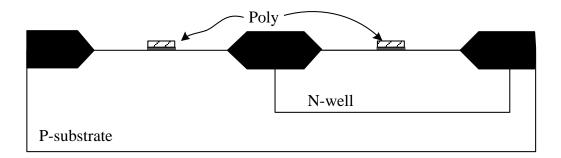

|            | Poly gate formation                                              | 133 |

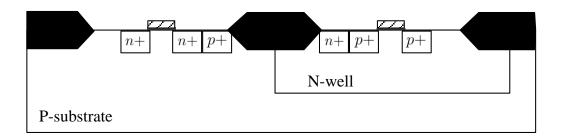

|            | Sources and drains formation                                     | 133 |

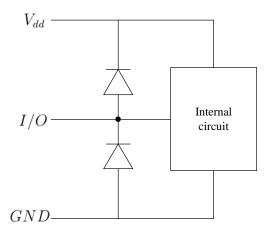

|            | Double diode for ESD                                             | 135 |

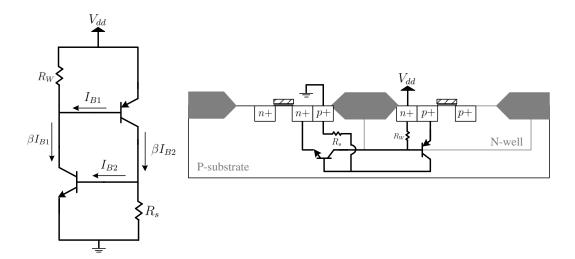

|            |                                                                  | 136 |

|            | The thyristor                                                    |     |

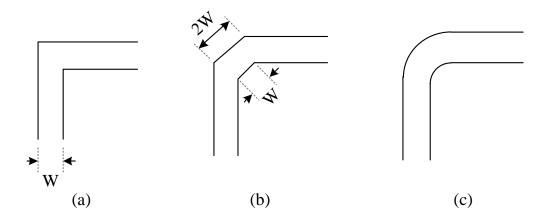

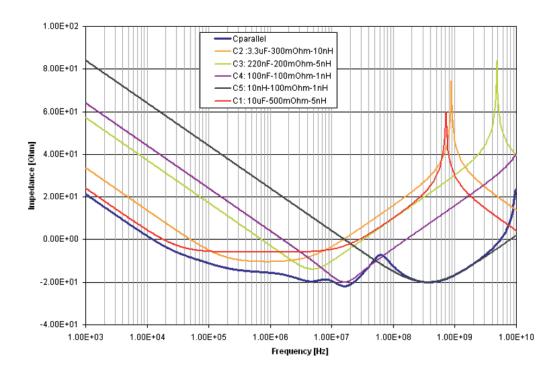

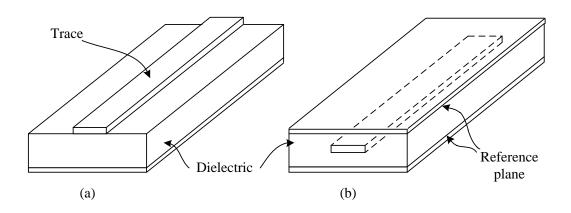

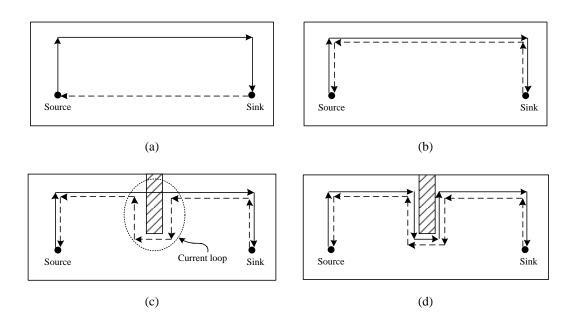

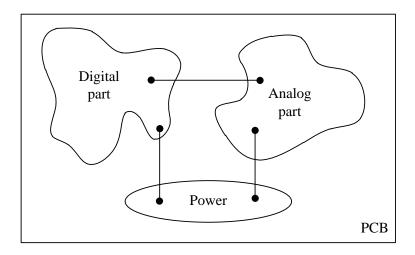

|            | Different trace routing                                          | 138 |

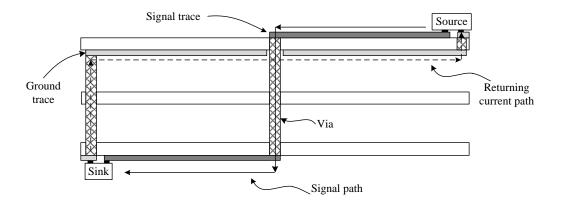

| A.1 (      | Current loop due to via                                          | 139 |

| A.18 An example of a combination of decoupling capacitors | 140 |

|-----------------------------------------------------------|-----|

| A.19 Two common structures for trace                      | 141 |

| A.20 Return current and resulting loop area               | 144 |

| A.21 Common ground plane                                  | 144 |

## LIST OF ABBREVIATIONS

ADC Analog to Digital Converter AFC Analog to Frequency Converter APC Analog to Period Converter

BW Bandwidth

CAL Clocked Level Averaging

CMC Canadian microelectronics cooperation CMOS Complementary Metal Oxide Semiconductor

D Number of bits

DAC Digital to Analog Converter

dB decible

DEM Dynamic Element Matching

D-FF D flip-flop

DMD Dual Modulus DividerDNL Differential Non Linearity

DR Dynamic Range

DSP Digital Signal Processing DWA Data Weighted Averaging ENOB Effective Number Of Bits

FDC Frequency to Digital Converter

FFT Fast Fourier Transform FM Frequency Modulation

FS Full Scale signal

GRO Gated Ring Oscillator

ILA Individual Level Averaging

INL Integral Non Linearity LSB Least Significant Bit

MOS Metal Oxide Semiconductor

MSB Most Significant Bit

MUX Multiplexer

NMOS N-type Metal Oxide Semiconductor

NUS Non-Uniform Sampling op-amp Operational Amplifier

OSR Oversampling Ratio

PCB Printed Circuit Board

PDC Period to Digital Converter

PI Phase Interpolation PM Phase Modulation

PMOS P-type Metal Oxide Semiconductor

RF Radio Frequency S/H Sample and Hold  $\Sigma\Delta$  Sigma Delta

SAR Successive Approximation Register

SNR Signal to Noise Ratio

SNRD Signal to Noise and Distortion Ratio TADC Time based Analog to Digital Converter

TDC Time to Digital converter  $T_{ref}$  The reference period

VCO Voltage Controled Oscillator

VDL Vernier Delay Line  $V_{dd}$  The supply voltage

$V_{in}$  The analog input voltage  $V_{ref}$  The reference voltage

$V_{th}$  The threshold of the inverter

## Chapter 1

## INTRODUCTION

Analog to digital converter is an essential block used in any mixed analog/digital system. As an example, in communication transceiver ADC plays the role of an interface between the analog front-end and the back-end digital signal processing (DSP) functions. Another example of other mixed analog/digital systems is disk drives application. Digital CMOS enjoys the advantage of technology scaling in terms of reducing the area of the digital part of the system [1,2]. This results in making the ratio of analog to digital blocks increases. Thus, the general trend is to reduce the analog portion of the system (which generally cannot take advantages of this scaling) as much as possible, and to move the ADC more and more towards the input of the system. Moving the ADC towards the system input makes its design more challenging.

According to the way in which sampling is preformed, ADCs are divided into two types. The first type is called the Nyquist-rate ADCs. Flash ADC, successive-approximation ADC, and pipelined ADC are examples of this type of ADCs. The second type is called oversampling ADCs. Sigma-delta modulator is an example of this type. The oversampling conversion technique has recently become popular as it avoids many of the difficulties encountered with Nyquist ADCs, such as the use of anti-aliasing analog filters. According to the way in which conversion is performed, ADCs are divided into two types. The first type directly converts the analog input into digital output. The second type does the conversion in an indirect way by first converting the analog signal into an intermediate representation such as time. Then it converts this intermediate representation into digital code [3]. The focus of

this thesis is on the second type which is more suitable in deep submicron region. Time-based ADC (TADC) is more suitable in deep submicron region because the supply voltage reduction that comes along with technology scaling results in lower voltage swing. Small voltage swing causes two problems. The first problem is the low signal to noise ratio. The second problem arises from the fact that the threshold voltage of the transistor does not decrease with the same rate as the supply voltage. This results in making the design of the operational amplifier (opamp), which is an essential building block in design of the ADC, difficult. Meanwhile with technology scaling, the switching characteristics of MOS transistors improve at high frequencies.

#### 1.1 Motivation

One way to convert the analog voltage into a time representation is to use a voltage controlled oscillator (VCO). The VCO converts the analog voltage into time format by modulating its period according to the value of the analog voltage. The modulation is done by using the analog input to control the charging/discharging current of a capacitor that is connected to one of the VCO stages. The charging/discharging time of a capacitor,  $t_{ch/disch}$ , is governed by the non-linear input/output equation

$$t_{ch/disch} = C \frac{V_{swing}}{K \times V_{in}} \tag{1.1}$$

Here we assume that the charging/discharging current is linearly related to the analog input voltage,  $V_{in}$ . This non-linear relation results in making the conversion from analog to time a non-linear operation. This inherent non-linear property of VCO is the bottleneck for TADC design and cause distortion.

In the past, feedback [4] and digital calibration [5] techniques have been used to overcome this problem. However, the feedback technique reduces the input range while the calibration technique is complicated.

Timing jitter is another important aspect of the TADC. Reducing the timing jitter results in increasing the TADC resolution. Technology scaling helps directly in reducing the timing jitter by increasing the speed and hence slew rate of the circuit. However, technology scaling's role in reducing the distortion due to the non-linear relation in (1.1) is less obvious.

The objective of this thesis is to present a novel TADC structure. This TADC is based on an analog to time converter (ATC), followed by a time-to-digital converter (TDC). The TDC is based on sigma-delta ( $\Sigma\Delta$ ) modulation. A non-linear internal quantizer in  $\Sigma\Delta$  modulator is used to counteract the non-linearity introduced when the VCO is used as a ATC. The TADC uses an implicit sample and hold (S/H) circuit to reduce area. Dynamic element matching (DEM) is used to improve the robustness of the system against random mismatch.

### 1.2 Thesis Organization

The thesis consists of five chapters. Chapter 2 presents a review on some background material for ADC. Four new TADCs are presented in Chapter 3. System-level simulations are presented in this chapter along with some techniques to improve the performance of the TADC. In Chapter 4, circuit implementations of three TADC designs along with their layouts, and the printed circuit board (PCB) used for testing are presented. Circuit level simulations using Cadence and Eldo, and measurement results are also presented in Chapter 4. The conclusions of this work are drawn in Chapter 5. The suggested future work are also presented in this chapter.

## Chapter 2

## BACKGROUND

## 2.1 Analog to digital converter

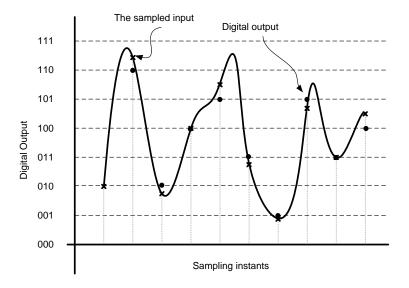

An ADC is a device which converts continuous analog input signals to discrete output digital codes. Each digital code is a quantized version of the sampled analog signal at the corresponding time instant. Figure 2.1 shows an example of the output of a 3-bit ADC. The reverse operation is performed by a digital-to-analog converter (DAC) [6].

Figure 2.1: Example of 3-bit ADC

### 2.2 Sampling

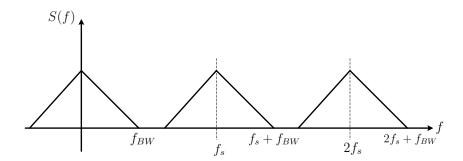

The ADC samples the input signal with a rate called the sampling frequency,  $f_s$ . The sampling frequency must be at least equal to twice the maximum frequency appearing in the input signal Bandwidth  $f_{BW}$ , this condition is referred to as the Nyquist criterion [7].

$$f_s \ge 2 \times f_{BW} \tag{2.1}$$

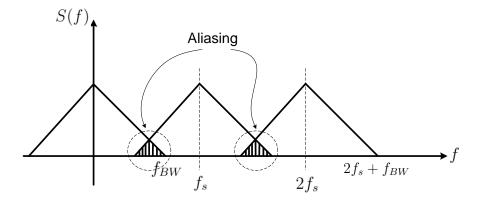

If the system does not meet the Nyquist criterion, aliasing occurs, and we will not be able to reconstruct the original signal from its samples. Aliasing can be understood if we study the frequency spectrum of the signal. Assume that we have a signal which has a triangle frequency spectrum representation. From the Fourier transform theory, the sampling of a signal in time domain with a frequency  $f_s$  is represented in frequency domain by replicating the frequency spectrum of the signal around multiples of  $f_s$ . If  $f_s > 2f_{BW}$ , the frequency spectrum of the sampled signal will be as shown in Figure 2.2; otherwise it will be as shown in Figure 2.3.

Figure 2.2: The spectrum of the samples signal in case  $f_s \geq 2 \times f_{BW}$

As we can see from Figure 2.2, the replica around  $f_s$  does not affect the original spectrum of the signal. The original signal can be reconstructed using a low-pass filter. However, in Figure 2.3, the replica around  $f_s$  distorts the original spectrum of the signal (the dashed areas in Figure 2.3), and we will not be able to reconstruct the original signal from its samples. To avoid aliasing, an aliasing filter is usually required to band limit the input signal before applying it to the ADC.

Figure 2.3: The spectrum of the samples signal in case  $f_s \geq 2 \times f_{BW}$

#### 2.3 Quantization

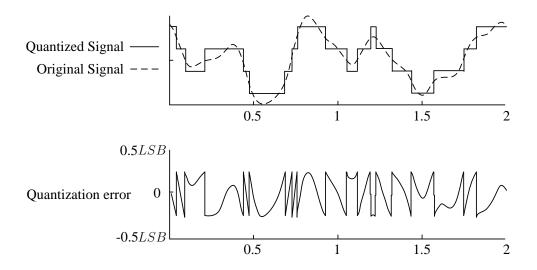

Quantization error happens when the ADC produces the same output for a certain range of the input. We define the resolution of the ADC as the smallest change in the input that results in change in the output digital code. Thus, making the resolution of the ADC as small as possible will result in reducing the quantization error in the ADC.

The resolution is defined in terms of the least significant bit (LSB), which is defined as

$$LSB = \frac{V_{FS}}{2^D} \tag{2.2}$$

Here,  $V_{FS}$  is the full scale input of the ADC and D is the number of the bits contained in the output digital code of the ADC. Therefore, to increase the resolution of the ADC we need to increase the number of bits. Quantization error (quantization noise) is defined as the difference between the original analog input and the resulting digital output. Figure 2.4 gives an example of quantization noise.

For an ADC, quantization error is always in the range of

$$-0.5 \times LSB \leq Quantization\ error \leq 0.5 \times LSB$$

### 2.4 ADC characteristics

Understanding the ADC characteristics helps to decide which type of ADC is suitable for a certain application. Due to non-idealities in circuit implementation of

Figure 2.4: An example of quantization noise

the ADC, new types of error, other than the quantization error, are introduced. Appendix A.1 reviews some of these types of error that are independent of time (static). Appendix A.2 reviews some of these types of error that are time dependent (dynamic).

## 2.5 ADC types

As we can see in Figure 2.5, ADCs are divided into direct conversion ADCs, and indirect conversion ADCs. Direct conversion ADCs directly convert the analog signal into digital code. Indirect conversion ADCs do the conversion in an indirect way by first converting the analog signal into an intermediate representation; like time, by modulating the edges of a reference signal. Then this intermediate representation is converted into digital code. According to the sample frequency rate, both direct conversion ADCs and indirect conversion ADCs are divided into Nyquist rate ADCs, and oversampling ADCs. Nyquist rate ADCs, compared to oversampling ADCs, are usually suitable for applications that require high input signal frequency, while oversampling ADCs are usually suitable for applications that require low input signal frequency but also require high resolution.

Figure 2.5: ADCs Types

#### 2.5.1 Nyquist rate direct conversion ADCs

A Nyquist rate ADC is an ADC type in which the sampling frequency is equal to twice the maximum frequency in the input signal BW (the Nyquist frequency) [6], practically the sampling frequency is 5-10 times the BW. Flash ADC, pipelined ADC, and successive-approximation ADC are typical Nyquist-rate direct-conversion ADCs. As an example, we overview the flash ADC.

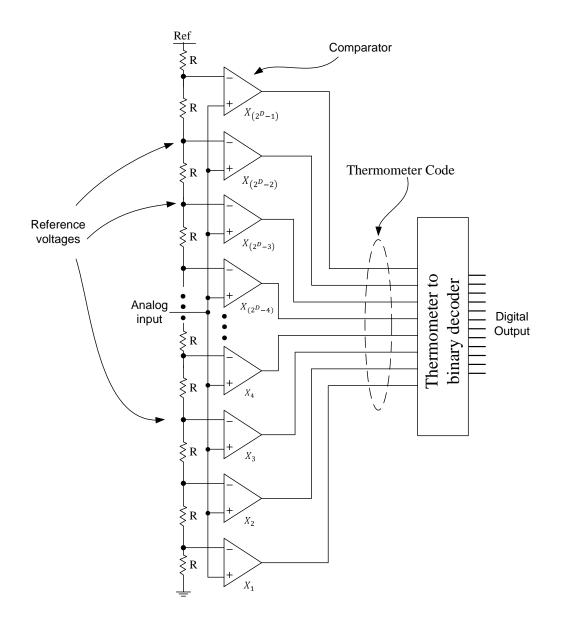

Flash ADC is the fastest type of ADC [8]. In this type of ADC the analog voltage input sample is compared with  $2^D - 1$  reference values using  $2^D - 1$  comparators. As we can see from Figure 2.6, the reference voltages are generated using a resistive divider with  $2^D$  resistors. Each reference voltage is one LSB greater than the reference voltage immediately below it. Each reference voltage is connected to one of the comparators inputs, while the other input is connected to the analog voltage input sample. Each comparator produces a "1" when the analog input voltage sample is higher than the reference voltage connected to it. Otherwise, the comparator produces "0". The comparators produce thermometer code. The thermometer code is then decoded to the appropriate digital output code.

The drawback of this type of ADC is that it requires a large number of comparators compared to other types of ADCs, which means consuming large area and more power. This drawback makes flash converters typically impractical for resolution greater than 8 bits (255 comparators). Moreover, the large number of comparators connected to input voltage results in a large parasitic capacitance that load the input terminal and limit the speed of the converter and requires a power-hungry buffer at the input terminal [6].

Figure 2.6: Flash ADC

### 2.5.2 Oversampling direct-conversion ADCs

The oversampling ADC is the ADC type in which the sampling frequency is much higher than the input signal frequency [6]. The oversampling conversion technique have become popular as it avoids many of the difficulties encountered with conventional method for analog-to-digital conversion, such as use of anti-aliasing analog

filters [9].

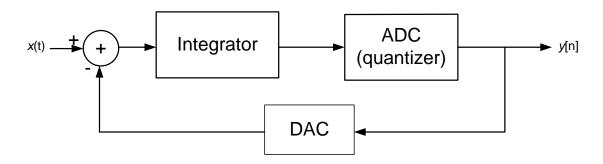

The basic concept of the sigma-delta modulator is the use of high sampling rate and feedback for improving the effective resolution of the quantizer [9]. Sigma-delta modulator modulates the analog signal into a digital code, usually single-bit code, at a frequency much higher than the Nyquist rate. The use of high frequency modulation and demodulation eliminates the need for sharp cutoffs in the analog anti-aliasing filter at the input of the ADC. One of the most important sigma-delta modulator characteristics is the oversampling ratio (OSR), which is defined as the ratio of the sampling frequency  $f_s$  to the Nyquist frequency. Figure 2.7 shows the simplest sigma-delta modulator, the first-order sigma-delta modulator. The input to the circuit feeds to the quantizer via an integrator, and the quantized output is fed back to be subtracted from the input signal [10].

Figure 2.7: First-order sigma-delta modulator

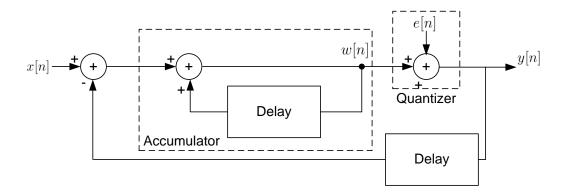

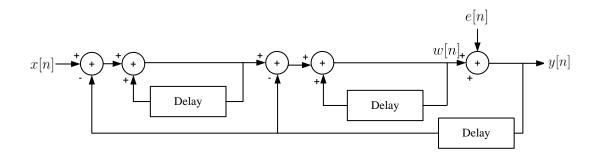

We will analyze the first-order sigma-delta ADC by using the equivalent circuit shown in Figure 2.8. For simplicity, we replace the nonlinear operation of the ADC with a linear one through the addition of signal e[n], which represents the quantization error of the internal quantizer. Moreover, we assume both the ADC and DAC have a gain of unity. As this is a sampled-data circuit, we represent the integration by accumulation, also with unity gain.

We can write the output of the accumulator as

$$w[n] = (x[n] - y[n-1]) + w[n-1]$$

(2.3)

Figure 2.8: First-order sigma-delta modulator equivalent circuit

as y[n] can be written as

$$y[n] = w[n] + e[n] \tag{2.4}$$

Then we can rewrite w[n] as

$$w[n] = x[n] - e[n-1] (2.5)$$

and then we can write y[n] as

$$y[n] = x[n] + (e[n] - e[n-1])$$

(2.6)

As we can see, the system differentiates the quantization error, while leaving the signal unchanged. Assuming the input signal is uncorrelated, the error e behaves as a white noise that is uncorrelated with the signal. N(f), the spectral density of the overall quantization noise,  $\epsilon[n]$ , calculated as  $\epsilon[n] = e[n] - e[n-1]$ , can be written as

$$N(f) = E(f)(1 - e^{-jt}) = 2e_{rms}\sqrt{T}\sin(\frac{\omega T}{2}), \ e_{rms}^2 = \frac{\Delta^2}{12}$$

(2.7)

where E(f) is the power spectral density of the noise of the internal quantizer, and  $\Delta$  is its step size.

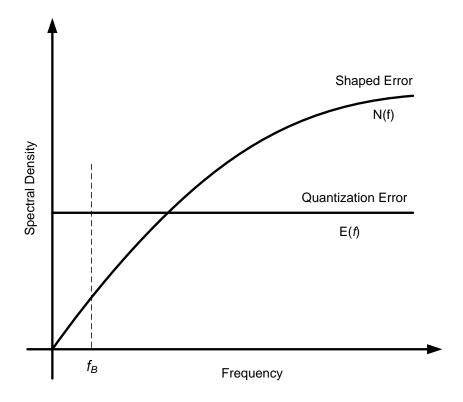

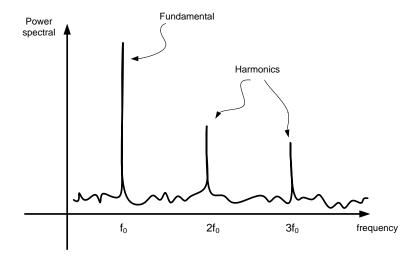

Figure 2.9 compares between the spectral densities of the noise. As we can see from Figure 2.9, the feedback around the quantizer reduces the noise at low frequencies but increases it at high frequencies. This process is called noise shaping.

Figure 2.9: The spectral density of N(f) compared with that of E(f)

We can calculate,  $e_{SB}$ , the total noise power in the signal bandwidth (BW) by integrating the square of the absolute value of N(f) over the signal BW, which gives

$$e_{SB}^2 = \int_0^{f_{BW}} |N(f)|^2 = \frac{\pi^2}{3} e_{rms}^2 \ OSR^{-3}, \ OSR = \frac{f_s}{2f_{BW}}$$

(2.8)

and the noise value is then given by

$$e_{SB} = \frac{\pi}{\sqrt{3}} e_{rms} \ OSR^{-3/2}$$

(2.9)

From equation (2.9), we can see that doubling the oversampling ratio of this circuit reduces the noise by 9 dB and provides 1.5 bits of extra resolution.

Figure 2.10 shows the second order sigma-delta modulator. As we can see, the differences between the second and the first-order modulator are the existence of another integrator (accumulator), and another feedback path from the output [10].

Figure 2.10: The second order sigma-delta modulator

Following the same analysis procedure used with the first-order sigma-delta ADC, the quantizer output can be written in the form

$$y[n] = x[n] + (e[n] - 2e[n-1] + e[n-2])$$

(2.10)

As we can see, the system differentiates the quantization error, but this time making the modulation error the second difference of the quantization error, while leaving the signal unchanged. The spectral density of the modulated noise  $\epsilon[n]$  defined as  $\epsilon[n] = e[n] - 2e[n-1] + e[n-2]$  can be written as

$$N(f) = E(f)(1 - e^{-jt})^2 = 4e_{rms}\sqrt{T}\sin^2(\frac{\omega T}{2})$$

(2.11)

and the noise rms value is then given by

$$e_{SB} = \frac{\pi^2}{\sqrt{5}} e_{rms} \ OSR^{-5/2} \tag{2.12}$$

From equation (2.12), doubling the OSR results in decreasing the quantization error by 15 dB and providing 2.5 bits of extra resolution. A complete design of second-order sigma-delta modulator is covered in [11].

The technique can be extended to higher order loop ADC by adding more feedback loops to the circuit [10]. In general, when a modulator has L loops, it can be shown that the spectral density of the modulation noise is

$$N(f) = E(f)(1 - e^{-jt})^{L} = e_{rms}\sqrt{T}\left(2\sin\left(\frac{\omega T}{2}\right)\right)^{L}$$

(2.13)

And the rms noise in the signal band is given by

$$e_{SB} = \frac{\pi^L}{\sqrt{2L+1}} e_{rms} \ OSR^{-(L+\frac{1}{2})}$$

(2.14)

From equation (2.14), doubling the OSR results in decreasing the quantization error by 3(2L+1) dB and providing (L+1/2) extra bits of resolution. The reason behind not using L-order sigma-delta modulator, where L is greater than 2, is the stability of the system [10]. Due to feedback, signal at the input of the quantizer may accumulate. This leads to overloading the modulator, and making the modulator unstable.

#### 2.5.3 Nyquist rate TADCs

TADC is the type of ADC that performs the analog to digital conversion in an indirect manner by first converting the analog input to time representation and then quantizes this time representation into digital code. This means that TADC is a type of indirect conversion ADCs. Dual slope ADC is an example of Nyquist rate TADC.

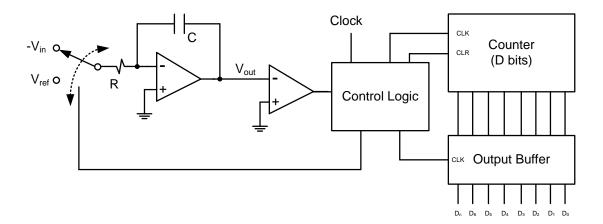

#### 2.5.3.1 Dual slope ADC

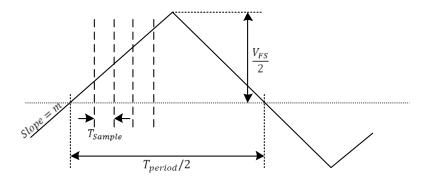

Dual slope ADC, also called integrating converter, is usually used for application that requires high accuracy but low data rate. This type of ADC has very low offset and gain error. It also requires only small amount of circuitry to be implemented [6]. Figure 2.11 shows a simplified diagram of the dual slope ADC.

The ADC name, dual slope, comes from the fact that this type of ADC performs the conversion on two phases. The first phase has a fixed duration  $T_1$  controlled by the running of a counter for  $2^D$  clock cycles. During this phase, the integrator input is connected to the analog input sample and the integrator output starts to ramp up. Thus, we can write the integrator output as

$$V_{out} = -\int_0^t \frac{-V_{in}}{RC} dt = \frac{V_{in}t}{RC}$$

(2.15)

Figure 2.11: The dual slope ADC

At the end of the first phase the integrator output will be given by

$$V_{out} = \frac{V_{in}T_1}{RC} \tag{2.16}$$

In the second phase, the input of the integrator is switched to the reference voltage  $V_{ref}$ . This means that the slope is fixed during this phase, unlike the first phase, which has variable slope. This results in a variable duration  $T_2$  for the second phase. The integrator output starts to go down until it reaches zero. Again we can write  $V_{out}$  as

$$V_{out} = -\int_{T_1}^{t} \frac{V_{ref}}{RC} dt + \frac{V_{in}T_1}{RC} = \frac{-V_{ref}}{RC}(t - T_1) + \frac{V_{in}T_1}{RC}$$

(2.17)

To calculate the value of  $T_2$ , we equate  $V_{out}$  to zero, giving:

$$T_2 = T_1 \frac{V_{in}}{V_{ref}} \tag{2.18}$$

In the beginning of this phase, the counter is first reset and then start to count during the time in which the integrator output is greater than zero. The value of the time constant RC does not affect the digital output, as we can see from equation (2.18). However, this value should be properly chosen such that it does not cause clipping of the integrator output in the first phase [6].

#### 2.5.4 Oversampling TADC

#### 2.5.4.1 Analog-to-time converter

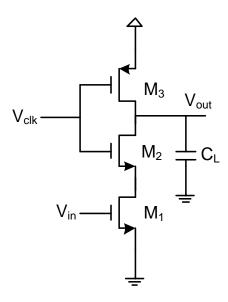

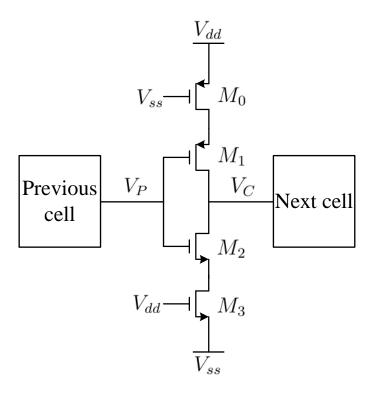

The conversion form the analog domain to the time domain is usually implemented either by using single-input-single-output inverter or by differential pair inverter. The conversion is done by using the analog input signal to control the rate by which the output capacitor,  $C_L$ , is charged or discharged. Figure 2.12 shows an example of current starved inverter. The upper two transistors (M2, and M3) are the transistors appearing in a conventional inverter, while M1 is introduced to control the discharging current of  $C_L$ .

Figure 2.12: Current starved inverter

By controlling the discharging current of  $C_L$ , through the varying of the input voltage  $V_{in}$ , we control the delay time it takes  $V_{out}$  to reach a certain voltage, say the threshold voltage of another inverter driven by  $V_{out}$ . The main problem with this delay cell is the nonlinear relationship between the control voltage  $(V_{in})$  and the delay time. This nonlinear relationship introduces distortion. Many publications address the improvement of the linearity of the current starved cell, such as the one reported in [12].

#### 2.5.4.2 Time to Digital converter

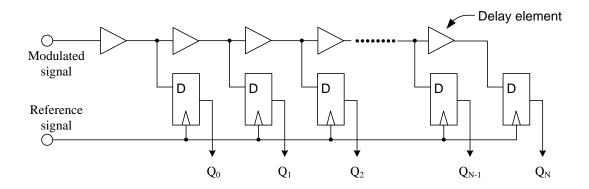

The function of the time to digital converter (TDC) is to quantize the time representation of the analog input into a digital code. Figure 2.13 shows one TDC approach [13, 14]. In this TDC, the modulated signal propagates along a line of delay elements. The output node of each delay element is connected to the data input of a D-flip-flop. The state of the delay line is sampled on the rising edge of the reference signal. The position of one/zero transfer in the thermometer code represents the time difference between the modulated and the reference signal. This type of TDC uses only two very simple and small cells, namely, digital delay elements and flip-flops. The resolution is given by the delay of the delay cell.

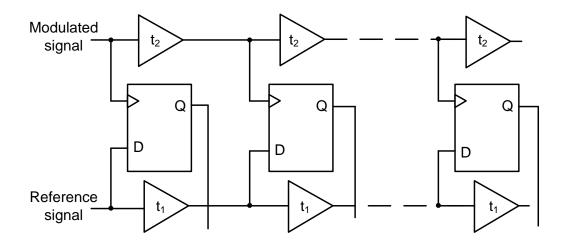

The resolution of the TDC can be improved by using the Vernier method [14], shown in Figure 2.14. In a Vernier delay line (VDL) two delay buffer chains are used. The delay of the cell in the upper delay chain  $t_1$  is slightly greater than the delay of the cell in the lower delay chain  $t_2$ . As the modulated and reference signals propagate in their delay chains, the time difference between the two pulses decreases in each Vernier stage by  $t_{\Delta} = t_1 - t_2$ . The position in the delay line, at which the reference signal catches up with the modulated signal, gives information about the measured time, with a resolution  $t_{\Delta}$ .

Figure 2.13: An example TDC

#### 2.5.4.3 Analog-to-frequency/period converter

The function of the analog-to-frequency converter (AFC) and analog-to-period converter (APC) is to manipulate the frequency and the period, respectively, of the

Figure 2.14: Vernier delay line

output waveform according to the value of the analog input. For example, ring oscillator based voltage controlled oscillator (VCO) [10] is an AFC/APC.

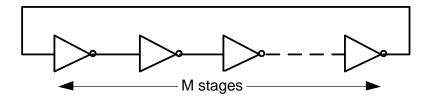

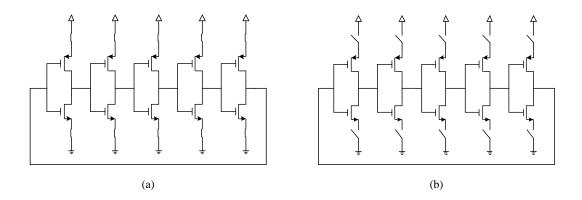

Figure 2.15: Simplified diagram of VCO

As we can see from Figure 2.15, a ring oscillator generally consists of a chain of delay cells connected in series, and a ring is formed by connecting the output of the last stage to the input of the first stage. The delay cell can be implemented either by using a single-input-single-output inverter or by using a differential pair inverter. In case of single-input-single-output inverters, the number of delay cells (M) must be an odd number. In case of differential-pair-inverters, the number of stages can be either odd or even, but if we use an even number of stages the output of the one of the the stages must be swapped before connecting to the input of the next stage [15]. To understand how the ring works, assume that we have an odd number of single-input-single-output inverters and the output of the first stage is one. As the output of the second stage is the input of the same procedure continue in

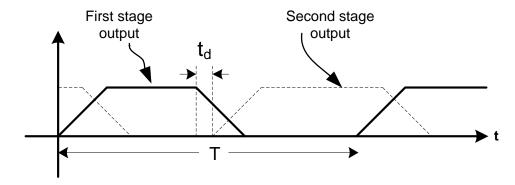

all the ring stages until we reach the last stage whose output is one. The output of the last stage forces the output of the first stage to switch to zero and this output starts to propagate in the ring until the output of the first stage is forced again to be one and so on. As we can see, it takes two cycles through the ring to complete one period, as shown in Figure 2.16. Thus, we can write the relation between the period of oscillation T and the delay of one delay cell  $t_d$  as

$$T = 2Mt_d (2.19)$$

and so we can write the frequency of the VCO output as

Figure 2.16: Example of VCO output signal

$$f = \frac{1}{T} = \frac{1}{2Mt_d} \tag{2.20}$$

As we can see from the above equation, besides the condition on the number of the stages M, the value of M is determined from the required output frequency and the value of  $t_d$ . Controlling the value of  $t_d$ , through the change of the input voltage  $V_{in}$ , will enable us to control the value of F. We define the tuning parameter  $K_{VCO}$  as the ratio of the change in the output frequency to the change in the input voltage [10]

$$K_{VCO} = \frac{d\omega}{dV_{in}} = 2\pi \frac{dF}{dV_{in}} \tag{2.21}$$

As an example, for the VCO built by single-input-single-output inverter we can write  $K_{VCO}$  as

$$K_{VCO} = \frac{2\pi G_m}{2MCV_{swing}} \tag{2.22}$$

where  $G_m = dI_{tune}/dV_{in}$ ,  $I_{tune}$  is the inverter current, and  $V_{swing}$  is the voltage swing.

Many work and publications, such as those reported in [16, 17], address the design of VCOs that are suitable for various types of applications.

#### 2.5.4.4 Period to digital converter

The primary objective of the period-to-digital converter (PDC) is to convert the period of a modulated signal,  $T_{in}$ , into a digital code. To do this, the PDC counts and quantizes the number of rising edges of the period modulated signal during the sampling interval  $T_{ref}$ .

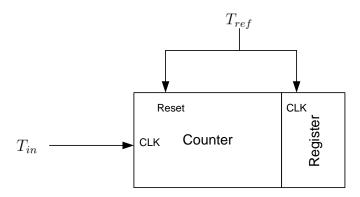

Figure 2.17: One simple PDC

One simple PDC may be implemented as a count and dump converter [17], as shown in Figure 2.17. The drawback of this type of PDC is the counter resetting operation, which is a limiting factor for high-speed operation.

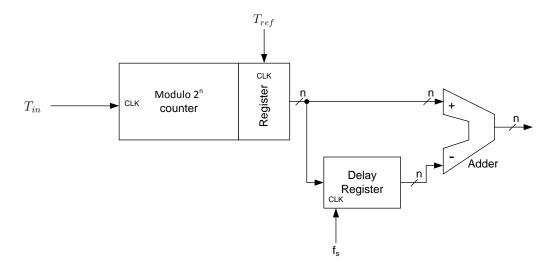

The counter does not need to be reset every  $T_{ref}$ , if the count and dump circuit is considered as an ideal counter with no upper limit followed by a digital differentiator. The ideal counter may be realized as a modulo  $2^n$  counter, as shown in Figure 2.18, on the condition that the maximum number of received rising edges during  $T_{ref}$  is smaller than the module of the counter to avoid signal aliasing [17]. The differentiation is done by subtracting two consecutive readings of the counter.

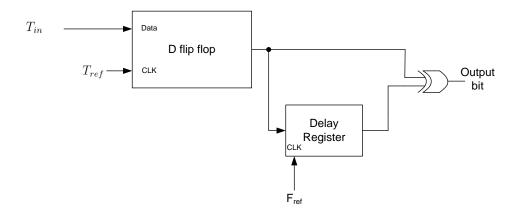

If the maximum received number of edges during  $T_{ref}$  is smaller than two, we may use modulo  $2^1$  arithmetic (D-flip-flop), and the subtraction operation can be

Figure 2.18: Modulo  $2^n$  implementation of the FDC

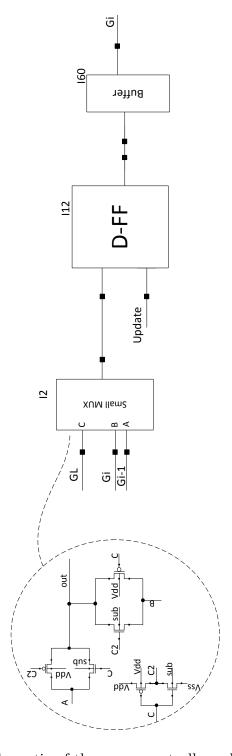

Figure 2.19: Modulo 2<sup>1</sup> implementation of the FDC

implemented using an XOR gate [17], as shown in Figure 2.19. The only problem with decreasing module size of the counter is that we need very high sampling frequency equal to the free running frequency of the VCO.

Time-based sigma-delta modulator [12, 18–25]can also be used to act as PDC. This is the focus of this thesis and we will discuss it in details in Chapter 3.

# Chapter 3

# TIME-BASED $\Sigma\Delta$ ANALOG-TO-DIGITAL CONVERTER

In this chapter, four different implementations of TADC are presented. The four implementations consist of an APC followed by a PDC. The PDC is a time-based  $\Sigma\Delta$  modulator. The idea of dispensing with the explicit sample-and-hold circuit is also discussed in this chapter.

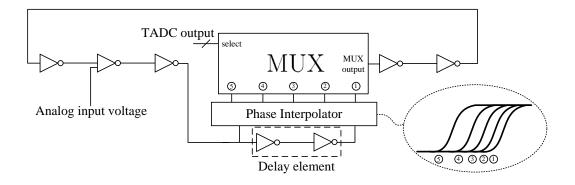

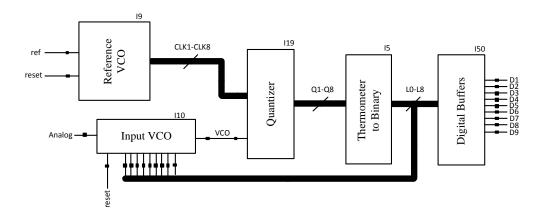

# 3.1 First-order $\Sigma\Delta$ modulator in time domain

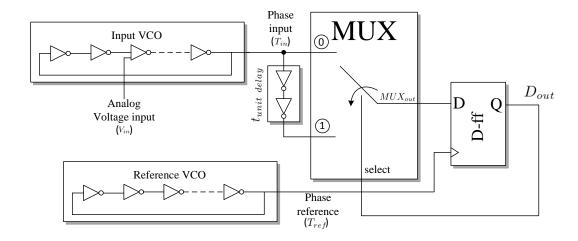

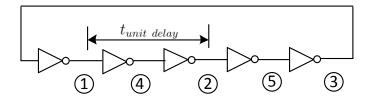

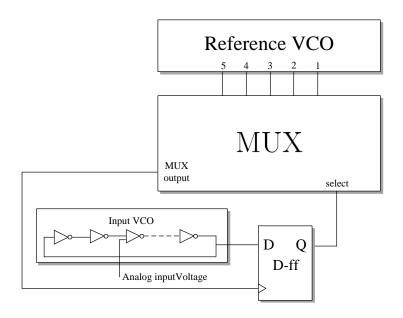

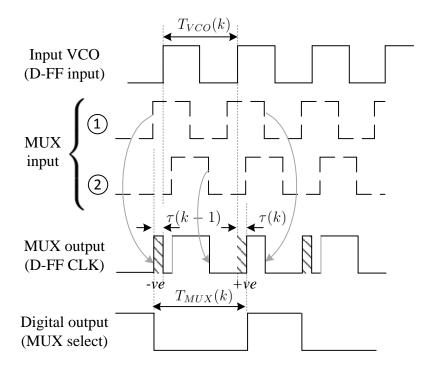

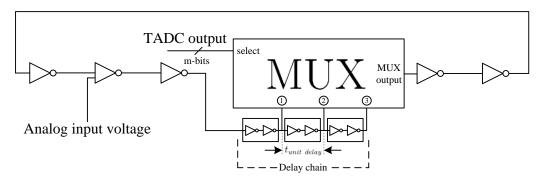

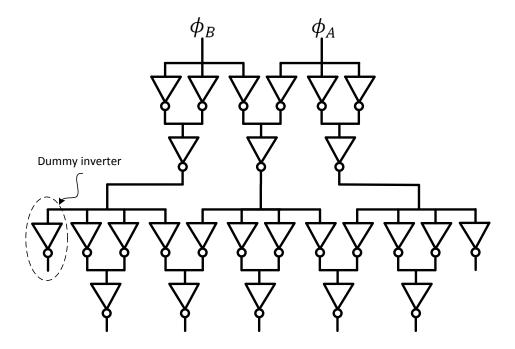

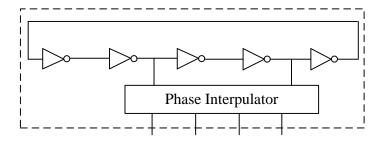

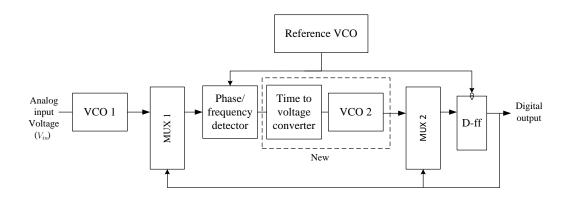

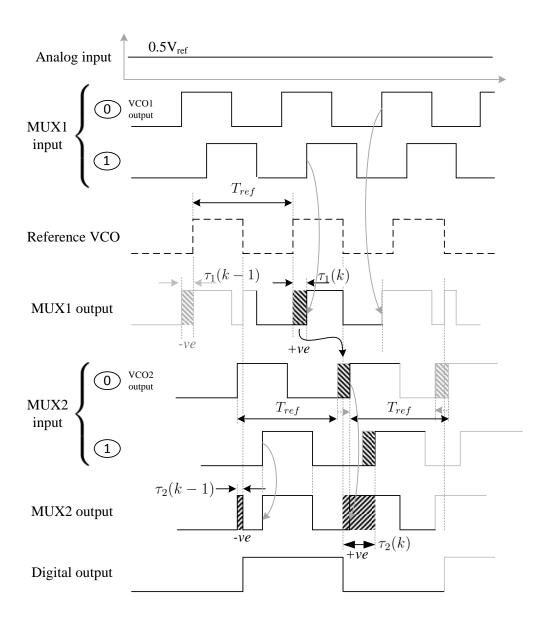

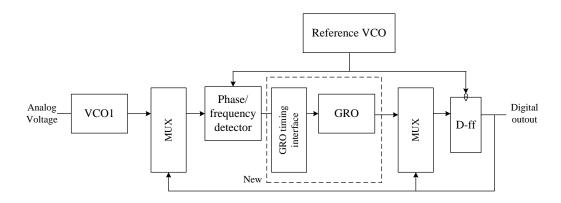

Time version of amplitude-based  $\Sigma\Delta$  modulator has been presented and discussed in literature such as [26–28]. In this work we are proposing new  $\Sigma\Delta$ -based TADCs. To elaborate on the new idea, let's start with Figure 3.1 which shows the block diagram of a simple system that will be used to demonstrate how the time-based  $\Sigma\Delta$  action is implemented. As we can see in Figure 3.1, the system contains two VCO's. The first VCO, denoted as the input VCO, converts the analog voltage input into phase input,  $T_{in}$ , by varying its period according to the value of the analog voltage. The second VCO, denoted as the reference VCO, generates a reference phase/period,  $T_{ref}$ . The multiplexer (MUX) generates a shifted version of the phase input signal, where the amount of shift is governed by the  $\Sigma\Delta$  output,  $D_{out}$ , through the  $\Sigma\Delta$

feedback action. The MUX allows the phase input to pass to the D flip flop (D-FF), when the MUX select signal is "0"; or delay it by  $t_{unit\ delay}$  before feeding it to the D-FF, when the MUX select signal is "1". The D-FF acts as a quantizer. It compares  $MUX_{out}$  with the reference phase, digitizes it, and generates the  $\Sigma\Delta$  output.

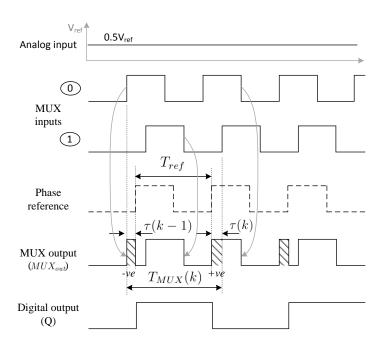

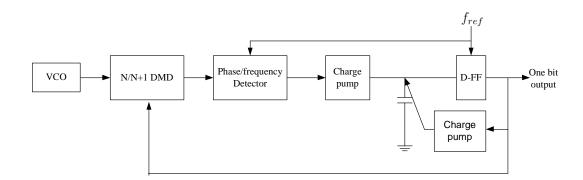

Figure 3.1: Time version of the first order  $\Sigma\Delta$  modulator

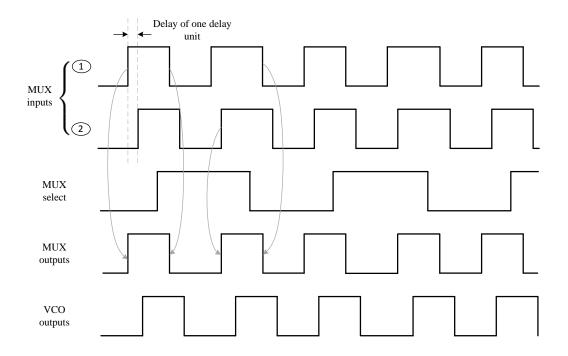

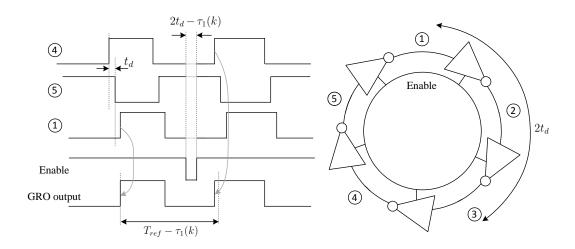

Figure 3.2 illustrates the waveform of the case when the analog voltage is at  $V_{ref}/2$ . This sets the period of the analog VCO to be equal to that of the reference VCO. Assume that the digital output is initially "0". This results in making the MUX copies from the the input labeled by "0", the output of the input VCO. Compared to the first edge of the reference signal, the phase of the MUX output signal leads the phase of the reference signal. This results in making the digital output of the D-FF goes to "1". Because the digital output changes, the MUX starts copying from the input labeled by "1", the delayed version of the output of the input VCO. Compared to the second edge of the reference signal, the phase of the MUX output signal lags the phase of the reference signal. This results in making the digital output of the D-FF goes back to "0" and so on.

We can model the system, shown in Figure 3.1, mathematically, by writing the time domain equation that governs the variable  $\tau(k)$ , in Figure 3.2.  $\tau(k)$  represents the phase/time difference between  $MUX_{out}$  and reference phase, and k is the time index.  $\tau(k)$  is considered positive when the reference phase leads the MUX output

and it is considered negative when the MUX output leads the reference phase. The time equation of  $\tau(k)$  can be written as

Figure 3.2: Waveform representation of Fig. 3.1 when  $V_{in} = V_{ref}/2$

$$\tau(k) + T_{ref} = \tau(k-1) + T_{MUX}(k)$$

(3.1)

where  $T_{MUX}(k)$  is defined as

$$T_{MUX}(k) = T_{VCO}(k) - Sgn(\tau(k-1)) \times t_{unit\ delay}$$

(3.2)

here  $T_{VCO}(k) (= T_{ref} + T_{in}(k))$ , is the period of the input VCO, and  $T_{in}(k)$  is the variation of the input VCO period, from  $T_{ref}$ , that corresponds to the value of the analog input voltage.  $T_{in}(k)$  is equal to zero in the example shown in Figure 3.2. Sgn() is the sign function. Substitute equation (3.2) into equation (3.1),  $\tau(k)$  can be written as

$$\tau(k) = \tau(k-1) + T_{in}(k) - Sgn(\tau(k-1)) \times t_{unit\ delay}$$

(3.3)

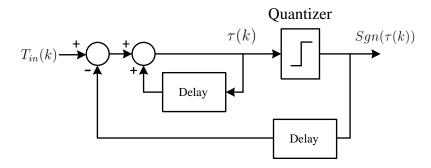

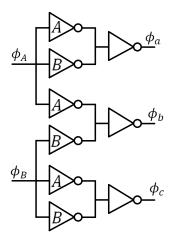

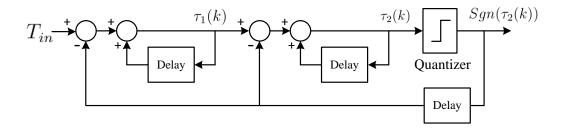

Figure 3.3 shows the block diagram representation of equation (3.3). As we

can see, it represents a time version of amplitude-based first-order single-bit  $\Sigma\Delta$  modulator.

Figure 3.3: Block diagram representation of equation (3.3)

The system in Figure 3.1 works fine only in the case when the analog input is equal to  $V_{ref}/2$  (period of the input VCO is equal to the reference period). In other words, when the digital output is toggling equally between "0" and "1". This is because the system can advance or delay the phase of the phase input signal, through the MUX and the unit delay, only one time. However, if the analog input voltage is changed such that sequences of consecutive "0's" or "1's" is generated, the phase of the phase input signal will need to be delayed/advanced more than one time. The single delay element, shown in Figure 3.1, will not be enough to do this. Theoretically speaking, to be able to delay/advance the phase of the phase input signal for any arbitrary sequence of "0's" or "1's", a chain of infinite delay elements is needed, but this solution is not practical.

The key feature in the system shown in Figure 3.1 is the ability of changing the period of the D-FF input according to the previous output of the D-FF. The period is increased, by  $t_{unit\ delay}$ , if the D-FF output is "1" and it is decreased if the D-FF output is "0". To overcome the problem of requiring a chain of infinite delay elements, [27] has proposed the usage of dual modulus divider (DMD). The dividing ratio of the DMD is controlled by the output of the D-FF. In this work, three other different techniques will be proposed to overcome this problem.

# 3.2 Implicit sample and hold in the VCO

In this section, the usage of the implicit sample and hold (S/H) in the input VCO, instead of using an explicit S/H, will be discussed. This has the advantage of saving area and reducing complexity. Also, the effects of the non-idealities that accompany the usage of the implicit S/H have on the system performance will be investigated.

# 3.2.1 The VCO implicit sample and hold operation

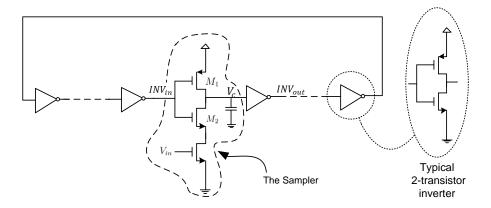

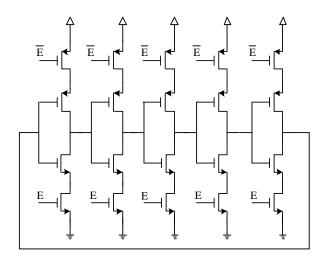

In this subsection, the implicit S/H mechanism happening in the input VCO will be explained. Figure 3.4 shows the input VCO. It is a typical 2-transistor inverter-based ring oscillator, except that one of its stages, the sampler, has an extra transistor that samples the input. It acts like a current starved inverter.

Figure 3.4: The input VCO

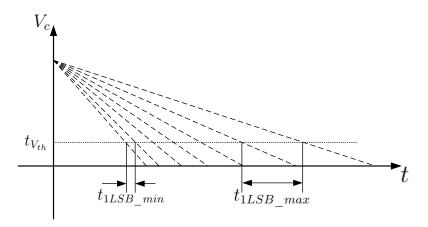

As shown in Figure 3.5, at the rising edge of  $INV_{in}$  (the gate voltage of  $M_1$ , and  $M_2$ ),  $V_C$  (the voltage on the parasitic capacitor at the drain of  $M_1$ , and  $M_2$ ) starts to fall down, at a rate determined by the analog input voltage,  $V_{in}$ . To illustrate the operation, let us consider the situation when  $V_{in}$  is a low frequency signal, so that it varies slowly. As the input signal frequency is small, we can consider it constant during the discharging operation of the capacitor, and so  $V_C$  will discharge linearly with time, as shown in the zoomed in area of Figure 3.5.

When  $V_C$  crosses the threshold of the next inverter,  $V_{th}$  at  $t_{V_{in}}$ , the inverter output  $(INV_{out})$  will switch to  $V_{dd}$ . After this point, any further change in  $V_{in}$  will

Figure 3.5: The inherent sample and hold

not have any effect on  $t_{V_{in}}$  and so  $t_{V_{in}1}$  is sampled. On the next rising edge of the  $INV_{in}$ ,  $V_C$  will again fall down but this time with different slope that depends on the new value of  $V_{in}$ . A new  $t_{V_{in}}$  ( $t_{V_{in}2}$ ) results, which corresponds to the new value of  $V_{in}$ . Thus, as shown in the lowest trace (the zoom in circle) of Figure 3.5, the sample and hold operation is done inherently. The sampling window starts at the rising edge of  $INV_{in}$  and ends when  $V_C$  crosses  $V_{th}$  of the next inverter. Then the hold operation starts from this point and lasts until the next rising edge of  $INV_{in}$ .

The usage of the inherent S/H to sample input signal saves area and eliminates the non-idealites that accompany the explicit S/H, like charge injection and clock feed through. However, the usage of the inherent S/H introduces some nonidealites to the system. Examples of these nonidealites are the tracking error and the non

uniform sampling. These nonidealites will be investigated in the next subsections.

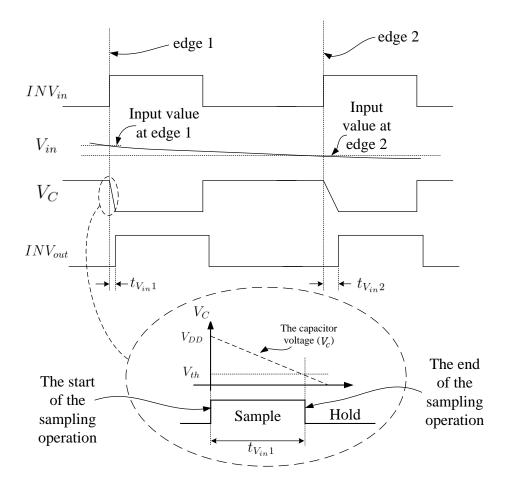

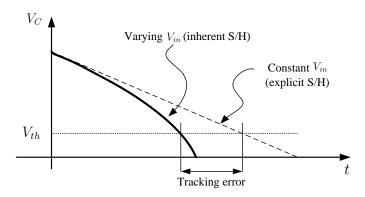

### 3.2.2 Tracking error

In real life,  $V_{in}$  is not varying slowly and so cannot be considered constant during the capacitor discharging operation. If  $V_{in}$  is assumed to vary linearly during this operation and if the relation between the capacitor discharging current and  $V_{in}$  is assumed to be linear, then  $V_c$  falls down quadratically, as shown in Figure 3.6 (solid line). Thus,  $V_c$  crosses  $V_{th}$  at a time that is different than the case when an explicit S/H is used. There  $V_{in}$  is the sampled (explicitly) input, and is constant while  $V_c$  is falling (dotted line in Figure 3.6). If  $V_{in}$  is increasing with time, this means that

Figure 3.6: Definition of tracking error

the current increases, and so the output voltage will cross the threshold earlier than the explicit S/H case. However, if  $V_{in}$  is decreasing with time, the output voltage will cross the threshold latter than the explicit S/H case.

The difference between the two times (for implicit S/H and for constant  $V_{in}$ ) is called the tracking error,  $t_{error}$ . This reflects that the implicit S/H is trying to track the varying  $V_{in}$  by adjusting the threshold crossing times. To be able to use an inherent S/H, this error has to be less than the time corresponding to 1 LSB change in the  $V_{in}$ ,  $t_{1LSB}$ . This  $t_{1LSB}$  is calculated for 2 values of  $V_{in}$ . In each value;  $V_{in}$  is assumed to be explicitly sampled and hence constant in the sampling window. This is shown in Figure 3.7. Note that because  $V_{in}$  is constant, the two dotted line

have constant, but different, slopes. This is because  $V_{in}$  increases by  $V_{1LSB}$ , where  $V_{1LSB}$  is the voltage corresponding to 1 LSB.

Figure 3.7: The relation between  $t_{error}$  and  $t_{1LSB}$

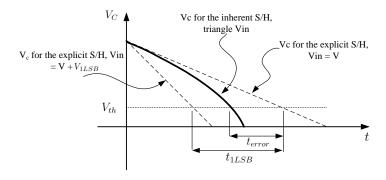

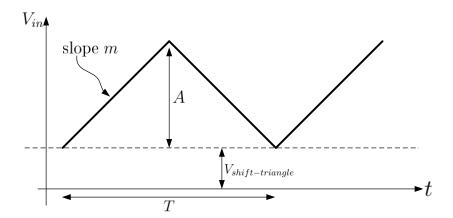

The tracking error sets a condition on the maximum frequency of the input signal to the VCO. For a triangle wave input, we can derive the maximum allowed frequency,  $F_{max}$  (see Appendix A.3) as

$$F_{max} = k_f \frac{V_{1LSB}(V_{start} + V_{1LSB})}{A(V_{dd} - V_{th})}$$

(3.4)

where  $k_f$  is a constant depending on the design of the inherent S/H and  $V_{start}$  is the value of  $V_{in}$  when the capacitor starts discharging.  $V_{start}$  depends on the relative phase between  $V_{in}$  and  $INV_{in}$ . To get a bound on  $F_{max}$ ,  $F_{(max-bound)}$ , which is true for all relative phases, we should set  $V_{start}$  to be the worst case, which happens when  $V_{start}$  is at the minimum, i.e.,  $V_{(shift-triangle)}$  in Figure 3.8.

Figure 3.8: The relation between the triangle and sinusoidal  $V_{in}$

$$F_{max} = k_f \frac{V_{1LSB}(V_{(shift-triangle)} + V_{1LSB})}{A(V_{dd} - V_{th})}$$

(3.5)

Now let us investigate the case when  $V_{in}$  is a sinusoidal wave. To find a bound on  $F_{max}$  let us assume that the frequency of the sine wave is equal to the frequency of the triangle wave, as shown in Figure 3.8. Since the triangle wave has a slope greater than or equal to the slope of the sine wave,  $F_{(max-bound)}$ , derived from the triangle wave (equation (A-23)) provides a bound on  $F_{(max-bound)}$ , using a sine wave.

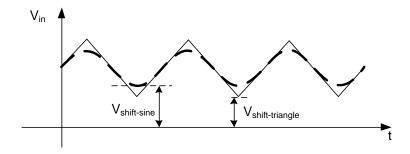

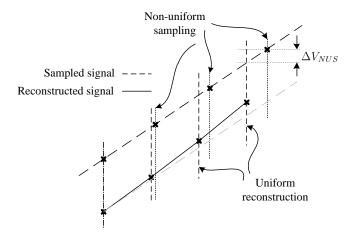

## 3.2.3 Non-uniform sampling

The non-uniform sampling (NUS) [29] can lead to distortion/non-linearity due to the fact that the reconstruction of the signal is done using a periodic clock. Figure 3.9 shows an example of a linearly ramping signal that is sampled non-uniformly. When the samples are used to reconstruct the signal using a periodic clock, the reconstructed signal is no longer ramping up linearly.

Figure 3.9: Non-linearity due to non-uniform sampling followed by uniform reconstruction

From the ADC design point of view, if the difference  $\Delta V_{NUS}$ , between the non-uniform sampled voltage and the uniformed sampled counterpart, as shown in Figure 3.9, is less than the resolution of the ADC, the NUS distortion is acceptable. Thus, our design requirement is that

Figure 3.10: An example of a triangle wave

$$\Delta V_{NUS} \le \frac{V_{FS}}{2^D} \tag{3.6}$$

For a ramp signal with slope m, as shown in Figure 3.10, we can express  $\Delta V_{NUS}$  in terms of the deviation in the sampling period  $\Delta T$  as

$$\Delta V_{NUS} = m \times \Delta T \tag{3.7}$$

From Figure 3.10, we can express m in terms of  $V_{FS}$  and  $T_{period}$  as

$$m = \frac{2V_{FS}}{T_{period}} \tag{3.8}$$

where  $T_{period}$  is the period of the input signal. By substituting in equation (3.7), we can write

$$\Delta T \le \frac{T_{period}}{2^{D+1}} \tag{3.9}$$

Equation (3.9) sets the maximum time difference between the uniform and the non-uniform sampling edges.

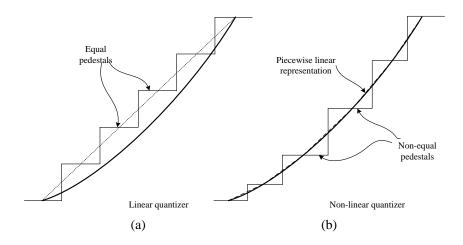

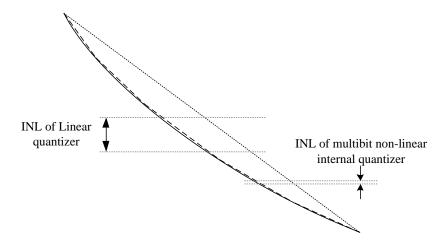

# 3.3 The non-linear internal quantizer

The internal quantizer of a  $\Sigma\Delta$  modulator can be either single-bit or multi-bit. A 1-bit quantizer is inherently linear since it has just two quantization levels. However in the case of multi-bit quantizers, the mismatch between quantization steps causes the quantizer to become non-linear.

If the APC input/output relation is linear, the  $\Sigma\Delta$  TDC internal quantizer characteristic curve must also be linear to achieve a linear TADC input/output relationship. However, in the case when the VCO is used as APC, the APC output,  $T_{in}$  in Figure 3.1, is not linearly related to the analog input voltage. This non-linearity arises due to the non-linear relation between  $t_{delay}$  and  $V_{in}$  (which arises from charging/discharging of C; for simplicity, here, I is further assumed to be linearly related to  $V_{in}$ )

$$t_{delay} = \frac{C \ V_{swing}}{I} = \frac{C \ V_{swing}}{KV_{in}} \tag{3.10}$$

Thus, making the quantizer linear will result in non-linear relation between the input and the output of the TADC and this will result in distortion.