# Development of Non-planar Interconnects for Flexible Substrates using Laser-assisted Maskless Microdeposition

by

Steven Tong

A thesis

presented to the University of Waterloo

in fulfillment of the degree of

Master of Applied Science

in

Mechanical Engineering

Waterloo, Ontario, Canada, 2012

© Steven Tong 2012

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Steven Tong

#### Abstract

With the industry striving for smaller devices, new technologies are developed to further miniaturize electronics devices. To this end, realization of 3D/non-planar interconnects, which aim at miniaturizing the interconnects formed between components on the same device, has attracted many researchers. This thesis focuses on a feasibility analysis for developing nonplanar interconnects on various flexible substrates using laser assisted maskless microdeposition (LAMM), which is a pressure-less process. There are two types of flexible substrates that are used: double-sided copper substrates separated by a layer of polyethylene terephthalate (PET) as well as a polyethylene terephthalate flexible substrate with surface-mounted resistors. For both substrates, multiple types of experiments were conducted to discover procedures which result in the highest rate of success for forming conductive interconnects. Optimal process parameters and deposition techniques were determined after multiple experiments. After experiments were completed, the resultant substrates were subject to various characterization methodologies including optical and scanning electron microscopy, energy-dispersive X-ray spectroscopy, Xray diffraction and profilometery. The results of these methodologies are documented in this thesis.

After many types of experiments involving substrate manipulation of the double-sided copper substrates, it was shown that the silver nano-particles were more likely to form a conductive interconnect when a polished slant was fabricated on the substrate.

Many deposition patterns were used for the flexible substrates with surface-mounted resistors. Of these patterns, the two patterns, the 'zigzag' and 'dot solder' patterns, proved to

have a much higher success rate for creating conductive interconnects compared to the other patterns.

During this study, the results of the experiments using the LAMM process show that this technology has great potential for creating non-planar interconnects on flexible substrates. The experiments however suggest that the process is very sensitive to the material composition and process parameters. As such, with a small change in parameters, the 3D interconnects can fail to be produced. It was also observed that the possibility of silver interconnect fractures is higher where dissimilar materials with different thermal expansion rates are used for the underlying substrates.

### **Acknowledgements**

I would like to thank my supervisor Dr Ehsan Toyserkani for all the help and support he has given me during my research. The opportunity he has given me to become a part of academic research has been a very valuable experience. I would also like to thank Hamidreza Alemohammad for the various advice and troubleshooting help he has provided and Elahe Jabari for working closely with me during my time here. Thanks also go out to Yuquan Ding, Ryan Norris, Xiaogang Li, Tirdad Niknejad, Jason Benninger and the members of the Canadian Centre for Electron Microscopy at McMaster University for their help in providing me with characterization methodologies and fabrication.

I would also like to thank The Natural Sciences and Engineering Research Council of Canada (NSERC), Initiative for Automotive Manufacturing Innovation (IAMI) and Assembly Automation Alternatives (AAA) for their financial support in this research.

I would also like to thank the rest of the members of the Multi-Scale Additive

Manufacturing Laboratory: Amir Azhari, Ahmad Basalah, Bradley Cotton, Ehsan Foroozmehr,

Thomas Hudson, Teresa King, Joyce Lam, Richard Liang, Negar Rasti, Yaser Shanjani, Mihaela

Vlasea, and Xixi Zhang for their help, advice, friendship and encouragement as well as making

the past two years a wonderful experience.

Lastly, I would like to thank my family for their support and my fellow on-campus undergraduate friends: Yan Ma, Trevor Sabourin, Nannan Sun, and Edward Yam for their friendship and providing me with precious memories throughout the years.

## **Table of Contents**

| AUTHOR'S DECLARATION                                                | ii   |

|---------------------------------------------------------------------|------|

| Abstract                                                            | iii  |

| Acknowledgements                                                    | v    |

| Table of Contents                                                   | vi   |

| List of Figures                                                     | ix   |

| List of Tables                                                      | xiii |

| Introduction                                                        | 1    |

| 1.1 3D Interconnects for Flexible Substrates                        | 1    |

| 1.2 Thesis Objective                                                | 2    |

| 1.3 Outline                                                         | 3    |

| Literature Review                                                   | 4    |

| 2.1 3D Interconnect Techniques                                      | 4    |

| 2.1.1 Wire Bonding                                                  | 4    |

| 2.1.2 Through Silicon VIAs (TSVs)                                   | 6    |

| 2.1.3 Thin Film Deposition using Aerosol Jet® Direct Write Printing | 8    |

| 2.2 Applications                                                    | 12   |

| 2.3 Summary                                                         | 13   |

| Laser Assisted Maskless Microdeposition                             | 15   |

| 3.1 LAMM Process                                                    | 15   |

| 3.2 Deposition Process                                              | 16   |

|      | 3.3      | Lase      | r Specifications                                                | 18 |

|------|----------|-----------|-----------------------------------------------------------------|----|

|      | 3.4      | LAN       | IM Process Parameters                                           | 22 |

| Doul | ble-side | ed Flexil | ble Copper Substrates                                           | 23 |

|      | 4.1      | Mate      | erials                                                          | 23 |

|      | 4.2      | Char      | racterization Methodologies                                     | 25 |

|      | 4.2      | Expe      | eriments involving Substrates with Chamfered Vias               | 26 |

|      |          | 4.2.1     | Fabrication of a Chamfered Via                                  | 26 |

|      |          | 4.2.2     | Depositing the Silver Track for a Substrate with Chamfered Via  | 27 |

|      |          | 4.2.3     | Results for Substrates with a Chamfered Via                     | 29 |

|      | 4.3      | Expe      | eriments Involving Substrates with Polished Slants              | 31 |

|      |          | 4.3.1     | Fabrication of Polished Slants                                  | 31 |

|      |          | 4.3.2     | Depositing the Silver Track for Substrates with Polished Slants | 32 |

|      |          | 4.3.3     | Initial Results for Substrates with a Polished Slant            | 33 |

|      |          | 4.3.4     | Repeated Deposition and Sintering                               | 36 |

|      |          | 4.3.5     | Insufficient Heating of Substrate                               | 39 |

|      |          | 4.3.6     | Increasing the Laser Power                                      | 42 |

|      |          | 4.3.7     | Alternative Sintering Method                                    | 44 |

|      |          | 4.3.8     | Profilometery Analysis                                          | 47 |

|      | 4.4      | Expe      | eriments Involving Substrates Mounted on an Incline             | 49 |

|      |          | 4.4.1     | Fabrication Process for Substrates Mounted on an Incline        | 49 |

|             | 4.4.2                    | Depositing the Silver Track for Substrates Mounted on an Incline |

|-------------|--------------------------|------------------------------------------------------------------|

|             | 4.4.3                    | Results for Substrates Mounted on an Incline                     |

| 4.5         | 4.5 Contaminant Analysis |                                                                  |

|             | 4.5.1                    | X-ray Diffraction Analysis                                       |

|             | 4.5.2                    | X-ray Spectroscopy Analysis                                      |

| 4.6         | Sum                      | mary                                                             |

| Flexible Bo | ards wit                 | h Surface Mounted Resistors6                                     |

| 5.1         | Mate                     | erials and Fabrication61                                         |

| 5.2         | Char                     | acterization Methodologies                                       |

| 5.3         | Depo                     | osition Patterns64                                               |

|             | 5.3.1                    | Overhead Pass Deposition Pattern                                 |

|             | 5.3.2                    | Across Path Deposition Pattern                                   |

|             | 5.3.3                    | Zigzag Path Deposition Pattern                                   |

|             | 5.3.4                    | Dot Solder Deposition Pattern                                    |

|             | 5.3.5                    | Summary                                                          |

| Conclusion  | s and Re                 | ecommendations                                                   |

| 6.1         | Conc                     | elusions                                                         |

| 6.2         | Reco                     | ommendations                                                     |

| References  |                          |                                                                  |

## **List of Figures**

| Figure 1 – Schematic showing an example of wire bonding on stacked dies, adapted from [2]4                |

|-----------------------------------------------------------------------------------------------------------|

| Figure 2 - TSV formation process, adapted from [11], showing (a) photoresist deposition, (b) etching of   |

| the VIA, (c) deposition of the insulator material, and (d) deposition of the conductive material7         |

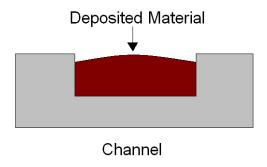

| Figure 3 – A schematic of deposited material using a direct-write deposition technique9                   |

| Figure 4 - Images showing various patterns of silver tracks deposited using an Aerosol Jet ® Deposition   |

| system. Patterns fabricated at the Multi-Scale Additive Manufacturing lab of the University of            |

| Waterloo10                                                                                                |

| Figure 5 - Schematic showing a cross-section of the deposited material inside the fabricated channel,     |

| adapted from [28]12                                                                                       |

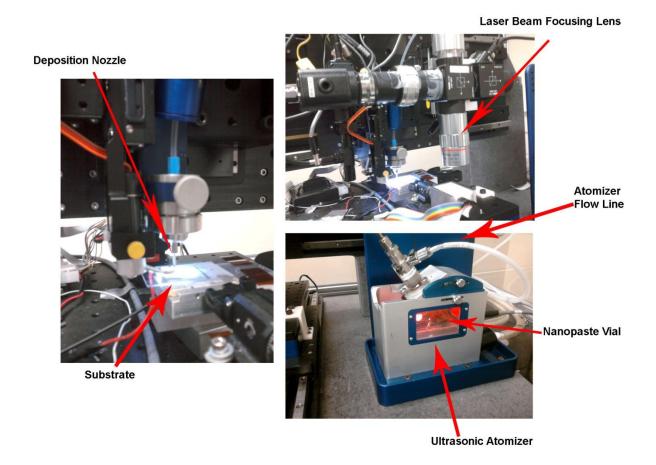

| Figure 6 - The main components of the LAMM system: Atomizer (bottom right), Deposition Nozzle             |

| (left), Laser (top right)                                                                                 |

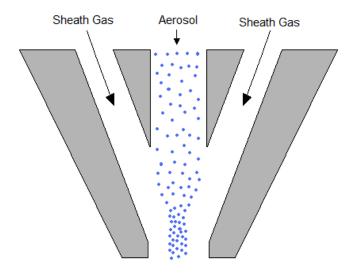

| Figure 7 - Diagram showing the main stream of nano-particles and the sheath gas that is introduced in the |

| nozzle, adopted from [19]                                                                                 |

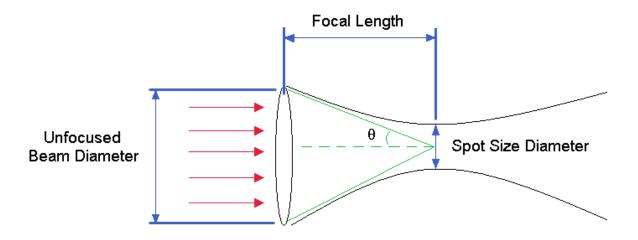

| Figure 8 - Diagram showing the beam size as the unfocused beam travels through the lens                   |

| Figure 9 - Diagram showing variables used in Equation 3.3 for laser spot size                             |

| Figure 10 - Process of agglomeration: (a) before sintering, (b) solvent evaporation, (c) beginning of     |

| agglomeration, (d) end of agglomeration. Image adapted from [20]21                                        |

| Figure 11 - SEM images of silver nano-particles sintered at 0.44 W (left) and 1.24 (right). Image taken   |

| from a JEOL JSM7000F field emission scanning electron microscope                                          |

| Figure 12 - Cross-sectional diagram of copper and PET substrate                                           |

| Figure 13 - Side view of double-sided copper substrates as seen from microscope                           |

| Figure 14 - Cross-sectional view of copper and PET substrate with a chamfered VIA25                       |

| Figure 15 – Cross-sectional schematic showing the manufacturing process for fabrication of chamfered      |

| VIAs (a) before and (b) after                                                                             |

| Figure 16 - Cross-sectional schematic showing silver deposition on substrates fabricated with a conic drill |

|-------------------------------------------------------------------------------------------------------------|

| Figure 17 - Cross-sectional schematic showing the ideal result of a successfully formed silver              |

| interconnect                                                                                                |

| Figure 18 - Cross-sectional schematic showing deposited silver tracks on double-sided copper substrates     |

| with a chamfered VIA29                                                                                      |

| Figure 19 - SEM image of an attempt to form an interconnect on the fabricated chamfered via                 |

| Figure 20 - Cross-sectional Schematic Showing the Deposition Process on Substrates with a Polished          |

| Slant                                                                                                       |

| Figure 21 - Top view of a substrate with a polished slant after 4 layers of deposition at 0.1 mm/s and      |

| sintering at 0.4 W and 1 mm/s                                                                               |

| Figure 22 - Top view of a substrate with a polished slant after 4 layers of deposition at 0.1 mm/s and      |

| sintering at 1.24 W and 1 mm/s                                                                              |

| Figure 23 - SEM Image of a substrate with a polished slant displaying a crack in the interconnect35         |

| Figure 24 - Top view of a deposited silver track that was sintered multiple times, resulting in a slightly  |

| melted area of PET around the silver track                                                                  |

| Figure 25 - SEM image of a conductive interconnect formed on a substrate with a polished slant. Two         |

| stages of deposition were performed, each with 5 layers at 1 mm/s                                           |

| Figure 26 - SEM images of substrates with polished slants after deposition during insufficient substrate    |

| heating temperatures. The substrates were sintered with (a) 1.25 W at 1 mm/s, which formed a                |

| successful interconnect and (b) 1 W at 2 mm/s, which did not form a successful interconnect 41              |

| Figure 27 - SEM images of a substrate with a polished slant after deposition during insufficient substrate  |

| heating temperatures. This substrate was sintered at 1.24 W and 1 mm/s                                      |

| Figure 28 - Images of substrate with polished slant after high-power sintering (3W) at 4 mm/s. Images       |

| taken from an (a) optical microscope, and (b) SEM.                                                          |

| Figure 29 - SEM image of a substrate with a polished slant after sintering with a hotplate                  |

| Figure 30 - SEM images of cracks formed between (a) the top layer of copper and top layer of epoxy, and           |

|-------------------------------------------------------------------------------------------------------------------|

| (b) the PET layer and the bottom layer of epoxy                                                                   |

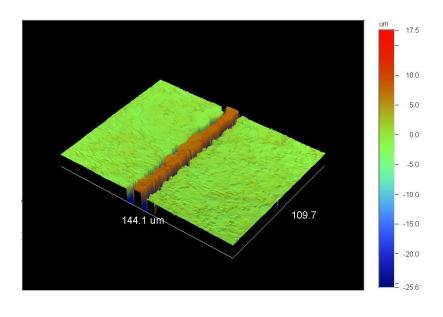

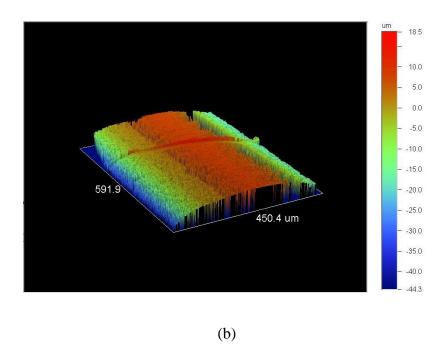

| Figure 31 - Images generated by a profiler when analyzing a substrate with a successful interconnect.             |

| Different views show (a) the silver track on the top layer of copper and (b) the silver track along the           |

| polished edge of the substrate                                                                                    |

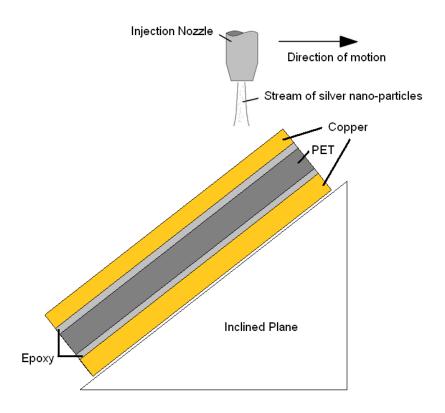

| Figure 32 - Schematic showing the deposition process for substrates mounted on an incline50                       |

| Figure 33 - Mounting containing various inclination angles                                                        |

| Figure 34 - Images taken from an optical microscope for substrates mounted on a (a) $30^\circ$ and (b) $45^\circ$ |

| incline. Sintering was done at 1.25W and 2 mm/s                                                                   |

| Figure 35 - SEM images of inclined substrates deposited at (a) 25°, (b) 30° and (c) 35°. Sintering was            |

| done at 1.25W with a speed of 2 mm/s                                                                              |

| Figure 36 - SEM image of silver track deposited on an inclined substrate before sintering                         |

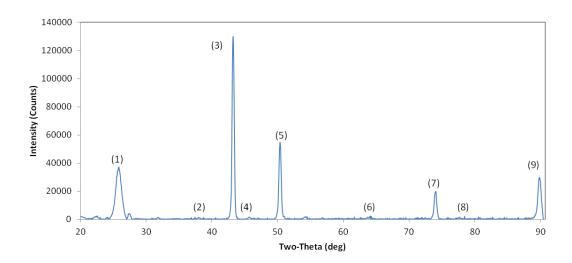

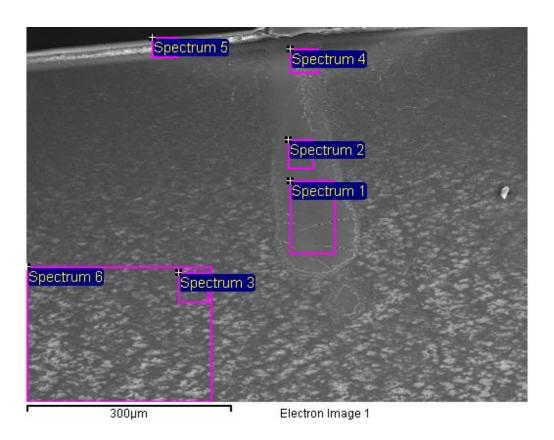

| Figure 37 - XRD curve of a conductive substrate with a polished slant                                             |

| Figure 38 - EDS image for a substrate that was sintered at 1.4W with a speed of 2 mm/s                            |

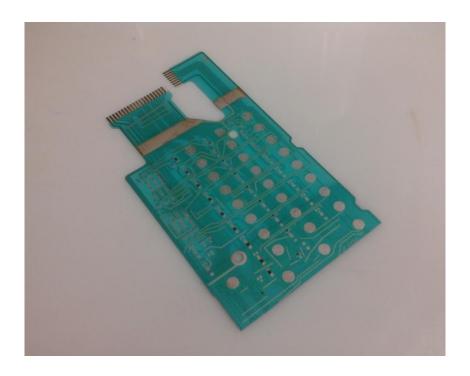

| Figure 39 - Flexible board with surface mounted resistors                                                         |

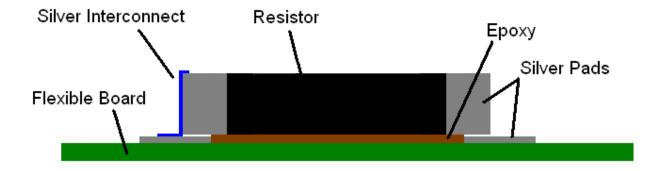

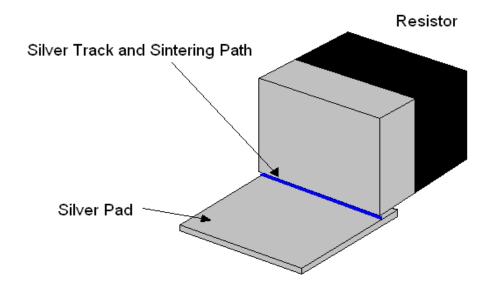

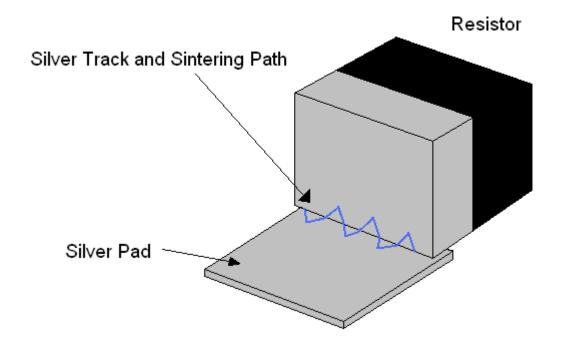

| Figure 40 - Schematic of a surface mounted resistor on the flexible board after deposition                        |

| Figure 41 – Set-up for resistance measurements (left) and a close-up image of the probes (right)64                |

| Figure 42 - Schematic showing the deposition process of the 'overhead pass' pattern                               |

| Figure 43 - Isometric schematic of a surface mounted resistor over a silver pad that contains a hole 67           |

| Figure 44 - Images showing parts of the flexible substrate which burned due to (a) laser passing too close        |

| to the edge of the silver pad during sintering, and (b) laser passing over the silver track which was             |

| too close to the hole in the silver pad                                                                           |

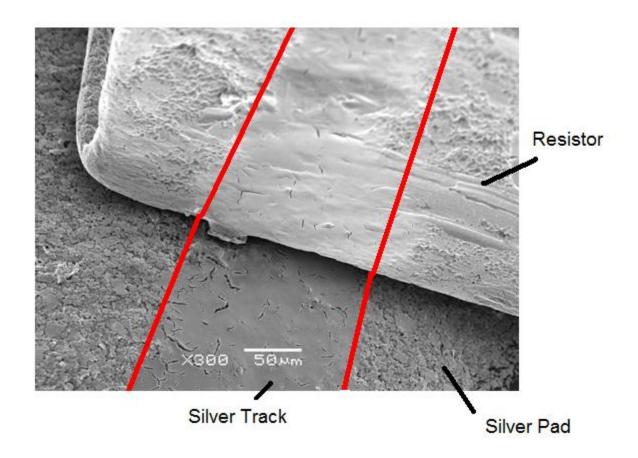

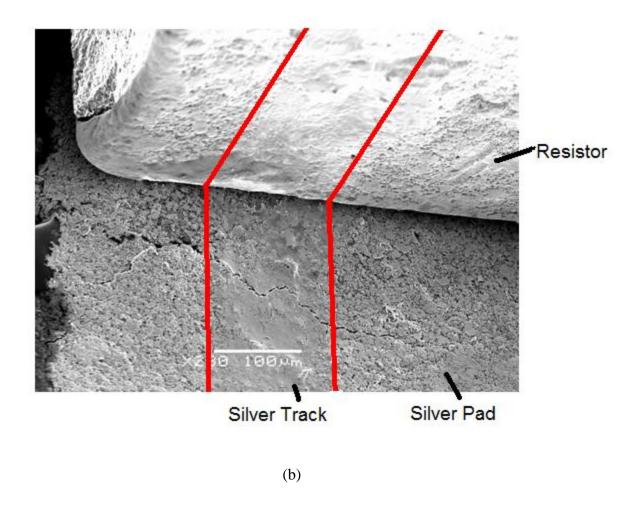

| Figure 45 - SEM images of mounted resistors after deposition at (a) $40^{\circ}$ inclination, 5 mm/s and 16       |

| layers, (b) 45° inclination, 5 mm/s and 32 layers. The red lines in both images show the area where               |

| the silver path was denosited 71                                                                                  |

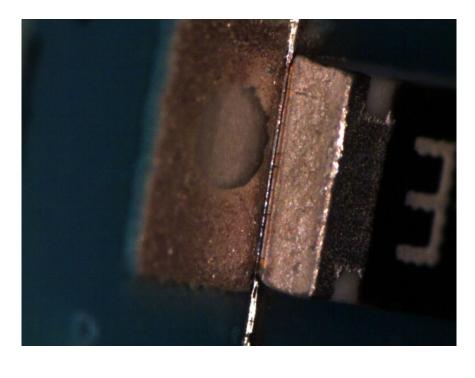

| Figure 46 - Images of a fillet formed with silver deposition shown from (a) an optical camera, and (b)                     |

|----------------------------------------------------------------------------------------------------------------------------|

| SEM                                                                                                                        |

| Figure 47 - SEM image showing a cracked silver track containing 100 layers of silver74                                     |

| Figure 48 - Schematic showing the across path deposition pattern                                                           |

| Figure 49 - Optical images showing a deposited silver track using the 'across path' pattern76                              |

| Figure 50 - SEM images of a successful interconnect formed with the 'across path' pattern. (a) shows the                   |

| overall path while (b) shows a close-up of one of the interconnect fillets formed                                          |

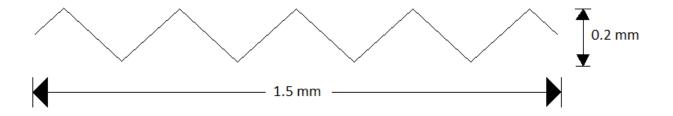

| Figure 51 - Zigzag Path Deposition Pattern 80                                                                              |

| Figure 52 - Schematic showing the zigzag path pattern of deposition                                                        |

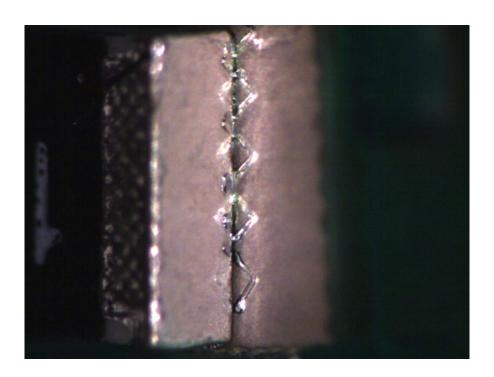

| Figure 53 - Optical image showing a conductive interconnect deposited using a zigzag path pattern81                        |

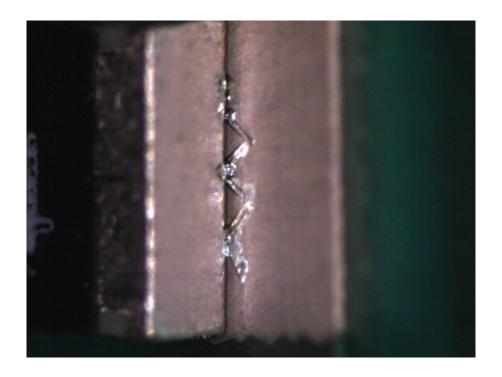

| Figure 54 - Optical image of a silver interconnect deposited using a shortened zigzag path pattern 82                      |

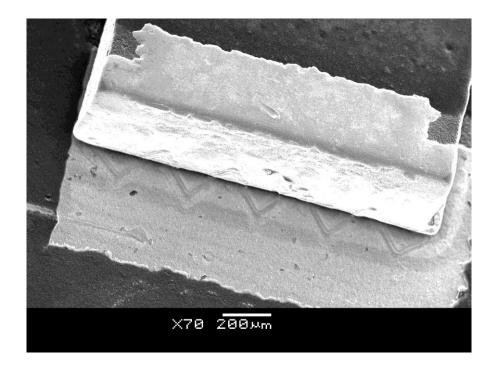

| Figure 55 - SEM images of the silver interconnect formed using the zigzag path pattern. Full interconnect                  |

| is shown in (a) and one of the connections formed between the resistor and the silver pad is shown                         |

| in (b)86                                                                                                                   |

| Figure 56 - Optical image of a silver interconnect that did not adhere well to the front face of a surface                 |

| mounted resistor                                                                                                           |

| Figure 57 - Schematic showing the deposition process using a 'dot solder' method                                           |

| Figure 58 - SEM images showing the resultant 'dot solder' experiments that used the parameters of (a)                      |

| Experiment A, and (b) Experiment E                                                                                         |

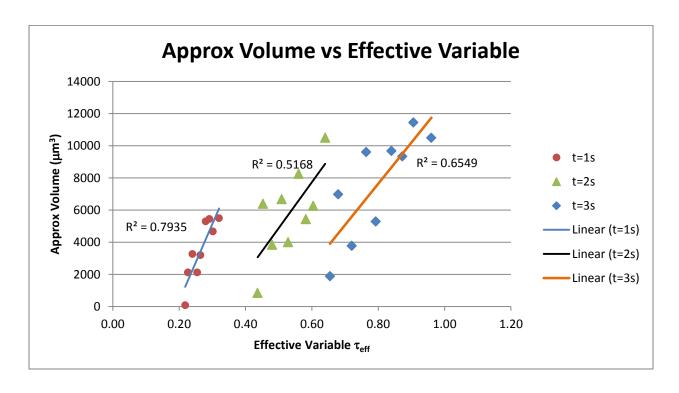

| Figure 59 - Approximate volume of deposited silver on a glass plate plotted against the effective variable                 |

| $\tau_{\mathrm{eff}}$                                                                                                      |

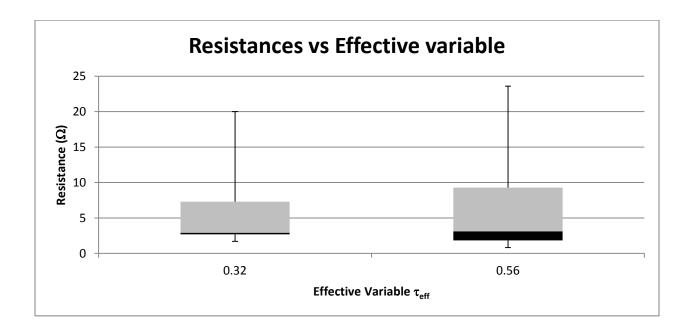

| Figure $60$ – Box and whisker plot showing measured resistances plotted against effective variable $\tau_{\text{eff}}$ for |

| Experiments A (0.32) and D (0.56)                                                                                          |

## **List of Tables**

| Table 1 - LAMM process parameters                                                                            |

|--------------------------------------------------------------------------------------------------------------|

| Table 2 - LAMM Process Parameters for Deposition on Substrates with Chamfered Holes                          |

| Table 3 - LAMM Process Parameters for Substrates with a Polished Slant                                       |

| Table 4 - EDS results for locations shown in Figure X                                                        |

| Table 5 - Tabulated results of a design of experiments for surface mounted resistors on flexible boards . 66 |

| Table 6 - Conductivity results using a full zigzag path pattern on surface mounted resistors manually        |

| placed on a flexible board83                                                                                 |

| Table 7 - Conductivity results using a shortened zigzag path pattern on surface mounted resistors            |

| manually placed on a flexible board84                                                                        |

| Table 8 - Process parameter ranges for the design of experiments using the 'dot solder' method               |

| Table 9 - Results for the design of experiments regarding the 'dot solder' method                            |

| Table 10 - Repeatability results for the 'dot solder' method                                                 |

| Table 11 - Ranges of values for parameters used in experiment to determine volumetric value of silver        |

| deposition94                                                                                                 |

## **Chapter 1**

#### Introduction

#### 1.1 3D Interconnects for Flexible Substrates

Industries are constantly investigating new technologies and methods that will allow them to produce smaller and faster devices. In addition to miniaturization, the industry strives for more reliable and higher quality devices, which leads to new technologies that grant improvements such as using less material and consuming less energy during operation [1]. Fabrication of 3D interconnects are one such method that has garnered much interest and research. Traditionally, components on electronic devices are designed on planar surfaces; however, as components are designed smaller, wire routing becomes more complex, which can lead to longer signal delays due to inefficient routing patterns while compromising the miniaturization goal. As the industry is constantly striving for faster devices, the aforementioned problem needs to be addressed. By introducing a third dimension into devices, routing patterns can be more efficiently developed. This also allows substrates to be stacked, which allows for shorter interconnects due to having more components in proximity. Shorter interconnects allow shorter signal travelling time, and stacked substrates will allow components to be rearranged such that there can be optimal component arrangements which reduce the interconnect length.

Stacked substrates also reduce the size of devices as well as allowing different types of substrates to be combined on a single device with less difficulty. A very popular technology that stacks substrates is wire bonding, which has been available for many decades. During these decades, devices have been constantly designed to be smaller, to a point where wire bonding is unable to meet some of the demands in miniaturization. Due to the desire to miniaturize devices

further, other technologies have been introduced such as through-silicon VIAs and direct-write printing. Certain 3D interconnect technologies such as Aerosol® Jet deposition also allow interconnects to be formed on non-planar surfaces, allowing manipulation of substrate designs as well as forming interconnects on flexible substrates.

Although this technology holds very much promise, the substrates are usually restricted to rigid substrates due to the sintering process, which takes place after deposition. The sintering process will allow the deposited material to adhere well to the substrate, with the most common form of sintering being oven or hotplate curing. Oven and hotplate curing have no issues with rigid substrates, but flexible substrates are generally unable to endure the high temperatures without distorting. This causes a problem, as flexible substrates are used in many applications, and miniaturization of components on flexible substrates are also highly desired. Some flexible substrate applications include devices that are disposable; making a need for a fast, cost-efficient and low temperature process for creating 3d interconnects on flexible substrates.

#### 1.2 Thesis Objective

In this study, a method for creating 3D interconnects is applied to various flexible substrates to investigate the feasibility of this method, while also adjusting experimental parameters to optimize the process. The method involves using Aerosol® Jet technology, which is a relatively new technology that has been introduced for creating 3d interconnects. This pressure-less process also does not have multiple stages during the formation of the interconnects, making the process a fast and low-cost approach to creating interconnects. The formation of the interconnects in this process is also laser-assisted, which allows for localized sintering that will not damage heat-sensitive substrates. The flexible substrates in which the interconnects are printed upon in this study are planned to be used for a variety of applications

such as electrocardiography purposes. Flexible substrates are excellent for this purpose, as they can conform to the movement of a person's body as well as being comfortable and unobtrusive to have under clothing. Research is conducted on developing non-planar interconnects upon the surface of flexible substrates for the purpose of analyzing a fast and cost-efficient method of forming non-planar interconnects that can be used not only for electrocardiography purposes, but also in any situation where non-planar interconnects are manufactured in large succession.

#### 1.3 Outline

The thesis is outlined as follows: Chapter 1 contains the introduction and goals of the project. Chapter 2 includes literature review of some 3d interconnect technologies currently in existence as well as their applications. Chapter 3 presents details on the technology, laser-assisted maskless microdeposition, which is used for the experiments. Chapter 4 contains the experimental procedures and results of experiments performed on double-sided copper substrates that have been separated by a layer of polyethylene terephthalate. Chapter 5 contains the experimental procedures and results of experiments performed on flexible substrates with surface mounted resistors. Lastly, Chapter 6 presents the conclusions drawn from the experiments as well as recommendations for future work.

## **Chapter 2**

#### **Literature Review**

#### 2.1 3D Interconnect Techniques

There are a variety of 3D interconnect techniques that are available, with some techniques already in use within the industry. This chapter provides background on the advantages and shortcomings of various 3D interconnect techniques, namely wire bonding, through silicon VIAs and thin film deposition.

#### 2.1.1 Wire Bonding

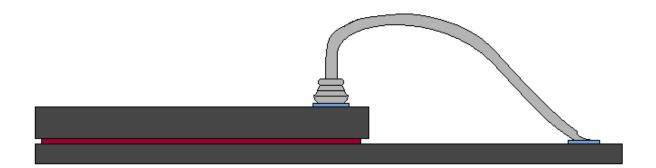

One of the first technologies that was discovered and used in the industry for creating 3D interconnects was wire bonding. This technology involves physically stacking substrates on top of one another and then routing wires that travel from one substrate to another substrate that is above or below it, as shown in Figure 1.

Figure 1 – Schematic showing an example of wire bonding on stacked dies, adapted from [2]

There are a variety of techniques to form a wire bond; however, most of the techniques rely on the same principle. The main principle consists of feeding a wire through a capillary, in which the wire is then melted at the tip of the capillary to form a ball. The capillary then presses

the newly formed ball of wire onto the contact pad. During contact, ultrasonic waves are then emitted into the ball, which allows the ball to be welded onto the surface of the contact pad. Once the ball is welded, the capillary moves towards the second contact pad, while feeding the wire out from the capillary. The capillary then presses down on the second contact pad, welding the wire to the second contact pad. Afterwards, the wire is sheared from the capillary, resulting in a wire ball bond formed on two contact pads. The most predominant material that is used for wiring was gold. However, due to increases in the prices of gold, other materials such as copper have been considered [3, 4].

Wire bonding has existed for many decades, and as such has become a very mature method and has been used in very many industries for creating electronics. By allowing the stacking of substrates, wire bonding reduces the total system size of electronics as well as reducing the signal travel time. Heterogeneous integration of different substrate materials is also an option when stacking substrates, as the components are no longer required to be placed on the same substrate [5]. This is particularly useful for many purposes such as sensor array applications, which rely on specific materials and require high-density circuits [6]. Wire bonding is excellent in many cases; however, as the industry strives for smaller electronics, new methods and technologies are discovered in order to create smaller interconnects.

With regards to flexible boards, wire bonding has a number of shortcomings. The first shortcoming is the suspended wires, which can be applied to all 3D interconnect applications. The suspended wires increase the system size slightly due to the wires looping from one substrate to another. This also causes some substrates to require a protective cover or mold to prevent external forces from damaging the wire bonds. Although stacking of substrates reduces the system size, the nature of wire bonding causes the entire system to be larger compared to

other techniques used in a similar fashion. Lastly, the formation of wire bonds requires the capillary to press down the ball bond onto the substrate. Rigid substrates can tolerate the pressure; however, when used on flexible substrates, there can be cases of permanent deformation due to the pressure induced by the ball bond creation process [7]. This is not to say that wire bonding on flexible boards is impossible. Wire bonding on flexible boards can still be accomplished through use of more heat resistant substrates or compromising the speed, temperature or wire composition of the process [8].

#### 2.1.2 Through Silicon VIAs (TSVs)

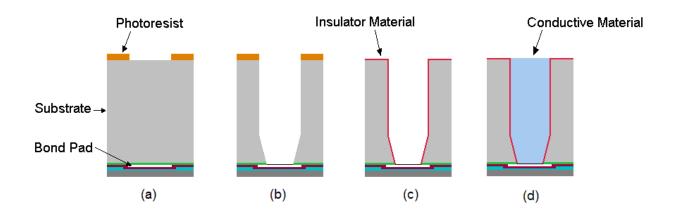

A new 3D interconnect technology that has begun to gain much attention is that of through-silicon VIAs (TSVs). TSV technology uses VIAs created in substrates to form interconnects, which can be a lengthy process, but can provide very short interconnects. The process is outlined in Figure 2. A VIA is first etched into the substrate, as shown in Figure 2(b). Normally, the etching process is performed with the use of lithography and dry etching processes such as reactive ion etching [9, 10]. However, there has also been some success with using laser etching in order to reduce the cost of the overall process [11, 12]. Once the VIA has been formed, an insulation layer is deposited on the walls of the VIA, shown in Figure 2(c), which can be performed with deposition techniques such as chemical vapor deposition. Next, a conductive material is used to fill the VIA, shown in Figure 2(d). This conductive material becomes the interconnect itself, which connects the bond pad to the desired location on the substrate. If one is required, a diffusion barrier layer can also be deposited along the walls of the VIA before filling the VIA with the conductive material [13].

Figure 2 - TSV formation process, adapted from [11], showing (a) photoresist deposition, (b) etching of the VIA, (c) deposition of the insulator material, and (d) deposition of the conductive material.

Compared to wire bonding, TSVs are able to provide a smaller system size, due to the interconnects residing inside the substrate rather than outside. Consequently, the interconnects are also shorter, which reduces signal travelling time as well. The process to creating a TSV, however, is an extremely lengthy process, which generally involves many different stages of manufacturing due to the various etching and deposition processes that are required. Due to the number of stages in this process, the cost of producing TSVs becomes a major issue. Variations of producing TSVs have been investigated, such as using laser etching in the place of reactive ion etching or using mechanical caulking when assembling the substrates. However, for the case of laser etching, the resultant TSVs were intended for applications that valued low cost and did not require high-speed signal transmissions [11]. The use of mechanical caulking during assembly can increase the speed of the process, while reducing the cost [14]. Although an improvement in terms of yield, it remains that the process is still multi-staged and require etching due to the nature of TSVs.

#### 2.1.3 Thin Film Deposition using Aerosol Jet® Direct Write Printing

Another technology for creating 3D interconnects that has begun to gain attention is thin film deposition. As opposed to wire bonding, which creates an interconnect suspended in air, and TSVs, which create interconnects within the substrates, thin film deposition aims to create conformal interconnects along the face of the substrate. One such technology that can perform this task is the Aerosol Jet® system. This system includes a pattern-generating device, such as an ink deposition nozzle or laser optics, as well as a positioning stage that is computer controlled [15]. The process works by generating a mist of the conductive material, which is then injected onto the substrate. The Aerosol® Jet system is capable of printing on a large variety of substrates, such as metals, glass, ceramics, solar cells, polymer substrates and resins [16, 17, 18, 19]. This system is also capable of depositing a variety of materials, such as metals, polymers adhesives and even single-walled carbon nanotubes, into complex patterns that can be made on both planar and non-planar surfaces [20, 21, 22].

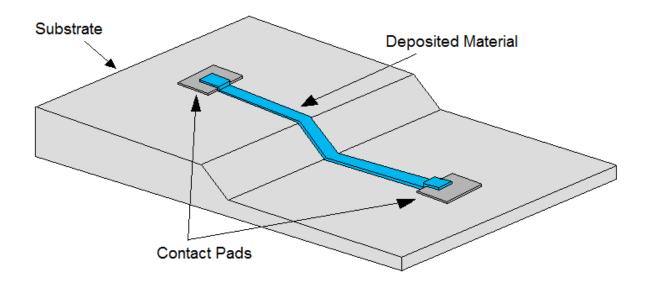

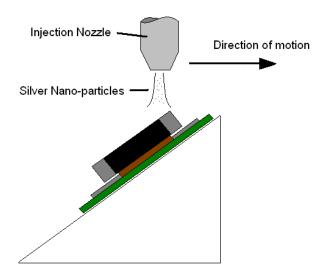

By controlling the speed of the injection nozzle and the volume of silver that is deposited, a variety of shapes and paths can be formed. Due to the material being in an aerosol form, the substrate is not limited to material or shape as long as there is proper adhesion between the deposited material and the substrate. This allows the process to create tracks or patterns of conductive material over non-planar surfaces. A schematic showing an example of the types of interconnects that can be formed is shown in Figure 3.

Figure 3 – A schematic of deposited material using a direct-write deposition technique

The direct-write technology is an additive process, as opposed to the traditional fabrication processes used in many manufacturing methods, particularly in integrated circuits, which use subtractive processing methods such as photolithography, nano-imprinting or various etching techniques [23, 24]. The subtractive method is a multi-stage process, which is similar to how TSVs are fabricated, with the use of chemical etching and photolithography. By using an additive process, there is no need for chemical etchants or masks, which are rather expensive. In addition, a mask must be created for each pattern that is desired when using a subtractive process, but with an additive process, only a CAD model is required for each pattern that is desired [25]. This makes the direct-write technology a much faster and cheaper alternative to the existing subtractive methods for creating micro-sized patterns on substrates. However, the direct-write technology does not fare as well for larger scaled patterns, as it would take much more time in order to draw the pattern onto the substrate. Using direct-write technology on patterns with the

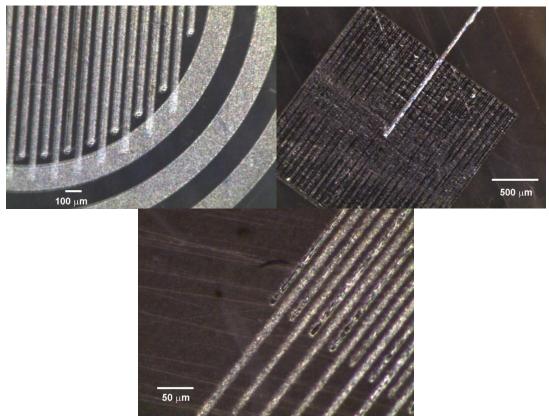

width of multiple millimeters can be compared to that of painting a wall with a toothbrush. Some images of deposited patterns are shown in Figure 4.

Figure 4 - Images showing various patterns of silver tracks deposited using an Aerosol Jet ® Deposition system. Patterns fabricated at the Multi-Scale Additive Manufacturing lab of the University of Waterloo.

After the material has been deposited, sintering will take place in order to cure the newly deposited material. This process can be done in a variety of ways, such as with a laser, hotplate, oven curing or electrical sintering [26, 27]. For thermally sensitive substrates, sintering methods such as laser and electrical sintering that can be focused towards a specific area are generally preferred as these methods will only heat the area in which the material has been deposited, rather than the entire substrate, which can lead to thermal expansion problems or damaging of the substrate. Although these methods are slightly more sophisticated, the sintering process can be performed much faster.

The system size of a substrate does not increase too greatly with the use of direct-write printing, since the deposition is deposited as a thin film that is on the surface of the substrate, making the system size reduction comparable to that of TSVs. Compared to wire bonding however, the direct-write printing process provides a much smaller system size.

The Aerosol Jet ® process does not perform very well for high frequency applications, where edge accuracy and surface roughness are extremely important. The Aerosol Jet ® system is known to have variations in edge accuracy and occasionally overspray, which produces a varying width of the deposited track. Inconsistent surface roughness can lead to signal loss in high frequency applications, due to the skin effect, where the current travels close to the outer edge of the conductive material. Overspray can be reduced by controlling the process parameters, but it is extremely difficult to prevent it entirely. Marinov V and Atanasov Y approached this problem and developed a method termed "Enhanced M3D", which introduces micromachining to produce a substrate with a channel that will contain the deposited material, shown in Figure 5 [28]. The channel can be fabricated with a number of micromaching methods, such as laser cutting, chemical etching, electron-beam micromaching, etc. The purpose of the channel is to contain the deposited material such that overspray has a very minimal effect on the system. Once tested, Marinov V and Atanasov Y found that the signal quality increased significantly [28]. Bhattacharya S and Marinov V used a similar approach with laser etching trenches within a substrate and achieved the goal of creating interconnects within a close proximity of around 6 µm [29]. Although this method is capable of producing interconnects for high frequency applications, the inclusion of micromachining increases costs greatly, and it must be remembered that cost is one major factor that makes direct-write printing very appealing.

Figure 5 - Schematic showing a cross-section of the deposited material inside the fabricated channel, adapted from [28]

#### 2.2 Applications

3D interconnects can be used in a variety of applications. With wire bonding being available for the past few decades and being one of the most widely used techniques for creating 3d interconnects, it comes as no surprise for this technology to be used in a variety of industries, such as automotive, computer, communication and network applications [30]. Although the applications remain the same, a desire to switch from gold wire bonding to copper wire bonding is apparent, especially with the increasing prices on gold.

Some TSV applications include MEMs, mobile applications, integrated circuits and a variety of sensors such as CMOS image sensors [31, 32, 33, 34]. TSVs can be applied to any industry that uses devices that contain stacked dies or wafers, making TSVs applicable to many industries immediately. Though there are not many devices using TSVs that are on the market at the moment, TSVs can certainly miniaturize devices, and much research is being performed to make this technology more affordable.

Aerosol® Jet direct write technology can also be used in many applications, such as solar cells, radio-frequency devices, touch screen displays, integrated circuits and automotive applications [16, 35, 36, 37, 38]. Recently, a "smart wing" was created for a small aerial drone in a joint project involving Optomec, Aurora Flight Sciences and Stratasys. The Aerosol® Jet

process was used to print circuits, sensors and an antenna on the wing of this aerial drone [39]. Due to this technology being capable of producing thin film interconnects, there exists a lot of potential on using direct write technology for flexible substrates. Due to the nature of flexible substrates, any devices mounted upon them must be able to maintain functionality amidst the stresses upon bending the flexible substrates. Thin filmed deposition is one method of producing interconnects capable of withstanding stress on flexible substrates. Flexible substrates also bring with itself many industry applications, such as temperature and pressure sensors, smart cards, electrocardiogram patches and light emitting diodes [28, 40].

#### 2.3 Summary

There are many different types of techniques for creating 3D interconnects on various substrates. Wire bonding was one of the earlier techniques discovered and is still widely used in industries today for creating 3D interconnects. This allows for the stacking of substrates and the wire bonds are formed from one substrate layer to another. Due to the nature of suspended wires in wire bonding, the wire bonding process has limitations on miniaturization. The wire bonding process also has some difficulty with flexible substrates, as the pressure from the process has the potential to permanently deform the substrates.

Different techniques have been discovered and researched to address some of these limitations. One such technology is through-silicon VIAs (TSVs), which is based on creating interconnects within substrates rather than the traditional exterior methods such as wire bonding. By having the interconnects within the substrates, further miniaturization can be reached; however, the process is time consuming and costs of TSVs is extremely high due to the various processes involved. Many flexible substrate applications are towards disposable devices, which make cost an extremely important factor when manufacturing.

Thin film deposition techniques are fast and cost-efficient, which make this process excellent for creating 3D interconnects for flexible substrates, including those of which are used for disposable applications. The thin film deposition process works by depositing aerosols of material onto a substrate to form conformal interconnects on the exterior of the substrate, followed by sintering. Since the interconnects are conformal, miniaturization is still achieved. Very little research has been documented in using thin film deposition for flexible substrates, and the published documentation that is available has not performed any optimization of parameters. For many of the published experiments regarding Aerosol® Jet technology, the sintering methods performed were with the use of a hotplate. As such, there is a lack of knowledge in this field with regards to using laser sintering in addition to Aerosol® Jet deposition. The goal of this work is to investigate the usage of Aerosol® Jet technology incorporated with laser sintering for various flexible substrates and find optimal parameters for creating thin film 3D interconnects on the aforementioned flexible substrates.

## **Chapter 3**

## **Laser Assisted Maskless Microdeposition**

#### 3.1 LAMM Process

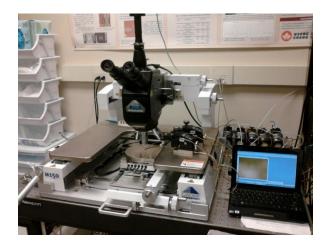

The 3D-interconnect technology that is used in this research study is called a laser assisted maskless microdeposition (LAMM) process, which is based on the Aerosol Jet ® direct-write technology, with a continuous-wave single-mode erbium fiber laser (ELR-20-1550, IPG Photonics Corporation, Oxford, Massachusetts) with a wavelength of 1550 nm that has been installed into the system. The laser assisted maskless microdeposition (LAMM) process consists of two main steps. The first step is microdeposition, where nano-particles suspended in a liquid are atomized and then deposited onto the substrate. The second step is laser sintering, where a laser is used to pass over the newly deposited nano-particles, sintering them and causing them to agglomerate. The main components of the system are shown in Figure 6. The atomizer and positioning stage are both manufactured by OPTOMEC Inc.

Figure 6 - The main components of the LAMM system: Atomizer (bottom right), Deposition Nozzle (left), Laser (top right).

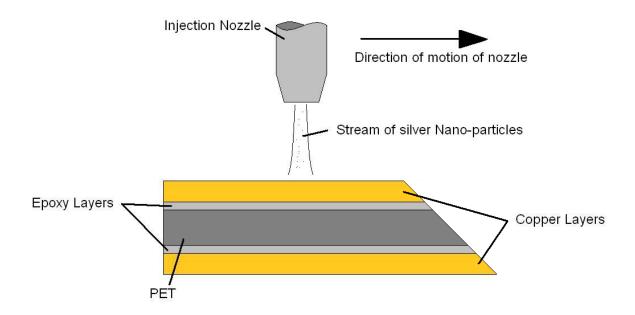

#### 3.2 Deposition Process

The LAMM process begins at the ultrasonic atomizer, where a VIAl of nano-particles is suspended in a liquid. This solution is generally labeled as nano-paste. When ultrasonic waves approach the nano-paste, droplets of the solution are released into the air, forming a dense mist from the accumulation of released droplets. This phenomenon of the ejection of droplets that occurs during atomization can be described with the cavitation and capillary wave hypotheses [41, 42]. The size of the droplets are a function of the density, viscosity, ultrasonic wave frequency and liquid surface tension [42, 43]. Larger droplets are formed with high values in surface tension and viscosity, while smaller droplets are formed with high values in density and

ultrasonic wave frequency. Thus, the thermo-physical properties of the nano-paste are required to be in a specific range. This can be achieved by diluting the nano-paste before it is placed within the atomizer [20].

After the nano-paste has been atomized into a mist, the mist is carried towards the deposition nozzle with the help of a neutral gas such as  $N_2$ . Once the stream of mist arrives at the deposition nozzle, another flow of a neutral gas, called sheath gas, is introduced into the stream, as shown in Figure 7. This secondary flow of gas will focus the nano-particles stream such that the diameter of the stream that exits the nozzle can be as small as 10% the diameter of the nozzle, which typically has a diameter between 100 and 250  $\mu$ m. The deposited patterns can have widths as small as 10  $\mu$ m [20].

Figure 7 - Diagram showing the main stream of nano-particles and the sheath gas that is introduced in the nozzle, adopted from [19].

The nano-particles are then deposited onto the desired substrate, which is mounted upon the positioning stage. This stage is controlled by a motion control module and has two degrees of

freedom, allowing a large variety of patterns to be formed by moving the positioning stage while the nano-particle stream is exiting the deposition nozzle. A heater can also be mounted upon the stage, which can heat the mounted substrate during deposition.

Once the deposition has completed, laser sintering will take place with the use of a continuous-wave single-mode erbium fiber laser with a wavelength of 1550 nm, which was installed onto the system, as seen in Figure 6. By having the laser mounted on the same stage as the deposition nozzle, the axis of motion is retained, allowing the laser to trace the same deposited path of material by executing the same path adjusted with an offset.

#### 3.3 Laser Specifications

The laser has a focal length of 40 mm and an unfocused diameter of 5 mm, shown in Figure 8. The diameter of the beam at the focal point can be calculated with Equation (3.1):

$$\omega_0 = \frac{4\lambda f}{\pi D} \tag{3.1}$$

where  $\omega_0$  is the focal point diameter,  $\lambda$  is the laser wavelength, f is the focal length and D is the unfocused beam diameter. Using Equation (3.1), the diameter at the focal point can be calculated as 15  $\mu$ m. The angle  $\theta$ , as seen in Figure X can be calculated with the use of Equation (3.2):

$$NA = n\sin\theta \tag{3.2}$$

where N is the numerical aperture, n is the index of refraction of the medium and  $\theta$  is half of the angle that represents the largest cone of light that can exit the lens. With the numerical aperture of the objective lens as 0.14,  $\theta$  can be solved for, which will be used in a later equation.

Figure 8 - Diagram showing the beam size as the unfocused beam travels through the lens

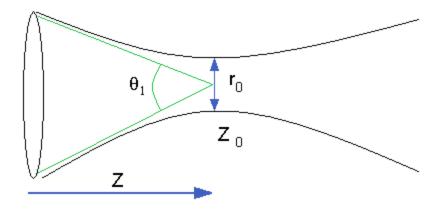

The beam shape is a  $TEM_{00}$  Gaussian beam, which means that the laser spot size can be characterized with the use of Figure 9 and Equation (3.3):

$$r^{2}(z) = r_{0}^{2} + 4\theta_{1}^{2} (z - z_{0})^{2}$$

(3.3)

where r is the diameter of the beam with respect to distance z from the focal point,  $r_0$  is the beam diameter at the focal point,  $\theta_1$  is twice the angle of  $\theta$  which was solved for earlier, and  $z_0$  is the offset. With this equation, the laser spot size can be calculated and controlled with the distance at which the object to be irradiated is placed from the laser. The laser beam produced is capable of emitting 0.5 to 3.5 W of power to the desired area. With laser powers under 2 W, the laser beam does not act consistently and is unstable at times. In order to allow use of low laser powers, a splitter and damper were installed onto the processing head of the laser, which reduces the power of the laser by 50%. This splitter also enables the attachment of a camera to view the area of irradiation from the point of view of the laser.

Figure 9 - Diagram showing variables used in Equation 3.3 for laser spot size

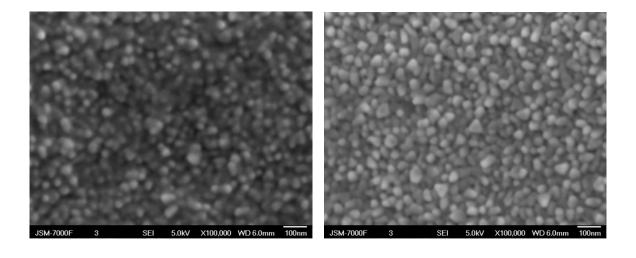

Once the laser irradiates the deposited material, the material will begin to sinter. During this process, the solvent that the nano-particles were originally suspended in will evaporate, and the nano-particles will begin to agglomerate, as shown in Figure 10 and 11. By applying the laser energy to the nano-particles, the density of these particles would increase, resulting in an increased electrical conductivity [44, 45, 46].

Figure 10 - Process of agglomeration: (a) before sintering, (b) solvent evaporation, (c) beginning of agglomeration, (d) end of agglomeration. Image adapted from [20]

Figure 11 - SEM images of silver nano-particles sintered at 0.44 W (left) and 1.24 (right). Image taken from a JEOL JSM7000F field emission scanning electron microscope

#### 3.4 LAMM Process Parameters

The parameters that are used to control the LAMM process are listed in Table 1. For proper atomization, the atomizer voltage should be higher than the threshold value of 37-48 V, while the viscosity of the nano-paste should be within (0.7 – 30 cP). In order to successfully atomize the nano-paste, the vial containing the nano-paste must also be placed in a specific location relative to the atomizer. The atomizer gas flow rate, deposition nozzle velocity and number of layers control the amount of silver that will be deposited onto the substrate. The sheath gas flow rate in combination with the atomizer gas flow rate controls the width of the track that will be deposited. The substrate temperature will determine how well the nanoparticles will adhere to the surface on contact. The laser power, velocity and beam size control the amount of power that is introduced to the substrate during sintering [20].

**Table 1 - LAMM process parameters**

| Atomization               | Microdeposition            | Laser Sintering |

|---------------------------|----------------------------|-----------------|

| Atomizer voltage          | Atomizer gas flow rate     | Laser power     |

| Nano-paste viscosity      | Deposition nozzle velocity | Laser velocity  |

| Nano-paste vial placement | Number of layers           | Laser beam size |

|                           | Sheath gas flow rate       |                 |

|                           | Substrate temperature      |                 |

The nano-particles that are deposited for the experiments included in this study are silver nano-particles suspended in a liquid. The suspension was 45-55wt% of silver with an average particle size of 60 nm in ethylene glycol (C<sub>2</sub>H<sub>4</sub>(OH)<sub>2</sub>) provided by Cabot Superior Micro Powders. The Aerosol® Jet is also capable of depositing a variety of materials, including other conductor inks such as platinum, palladium and copper [47].

## **Chapter 4**

## **Double-sided Flexible Copper Substrates**

This chapter details the experiments and results of depositing non-planar interconnects on double-sided copper substrates separated by a layer of polyethylene terephthalate (PET). The initial goal was to deposit a non-planar interconnect on a chamfered via. Due to technical complications, numerous types of substrate modifications were performed to simplify the process. Results for each modification are detailed in their respective sections.

#### 4.1 Materials

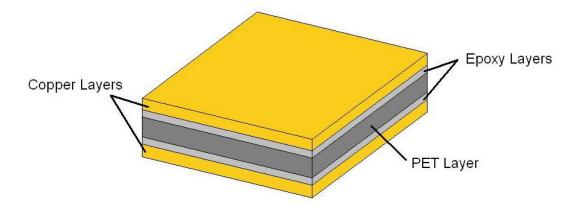

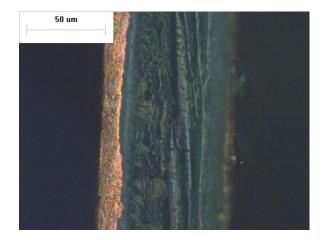

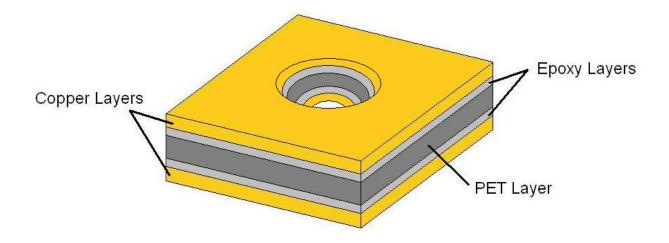

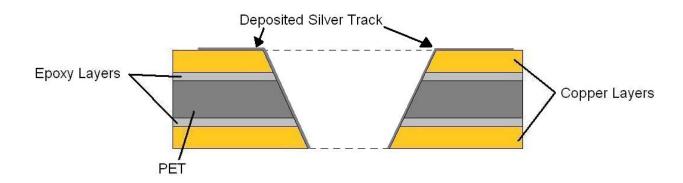

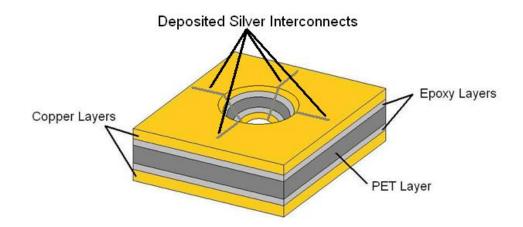

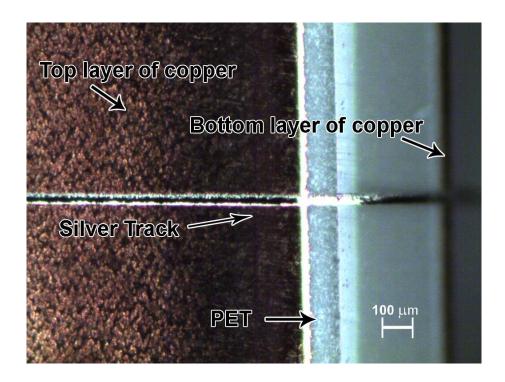

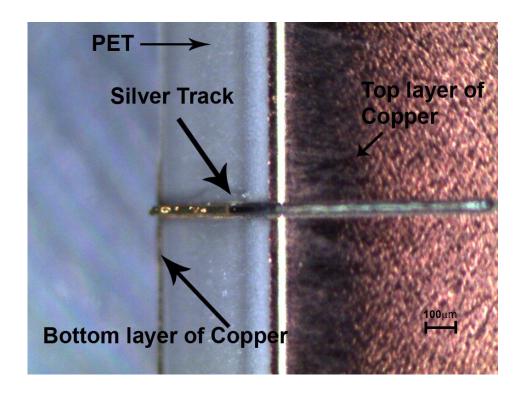

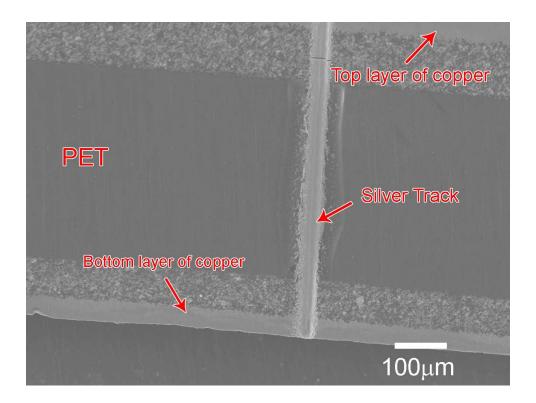

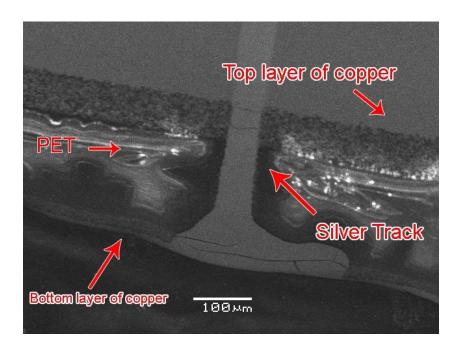

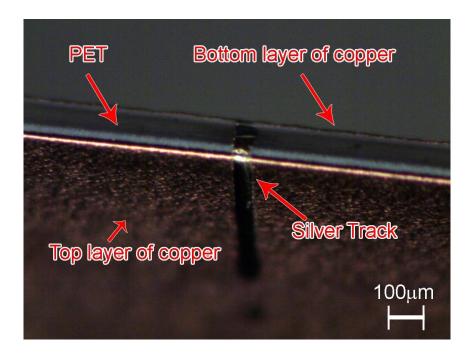

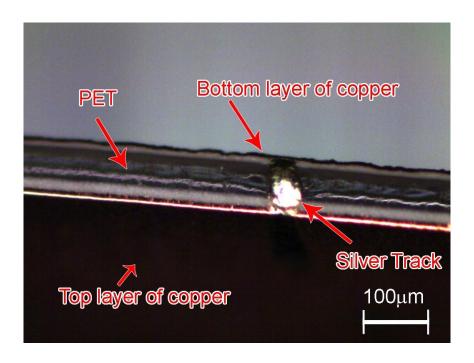

For the purpose of these experiments, the substrate that was used was a double-sided flexible copper substrate separated by a layer of polyethylene terephthalate (PET), provided by Assembly Automation Alternatives (AAA). The copper layers were adhered to the PET layer through the means of an epoxy. A cross-sectional diagram of this substrate is shown in Figure 12 and an optical image of a side view is shown in Figure 13. The total height of the substrate is 0.21 mm.

Figure 12 - Cross-sectional diagram of copper and PET substrate

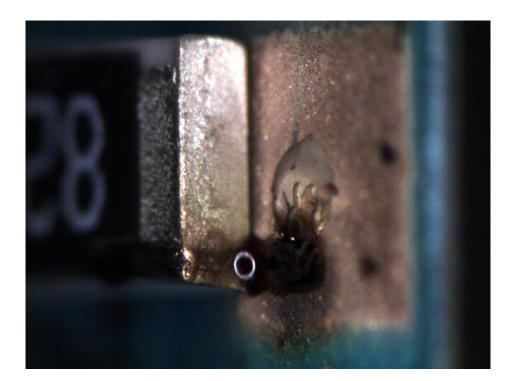

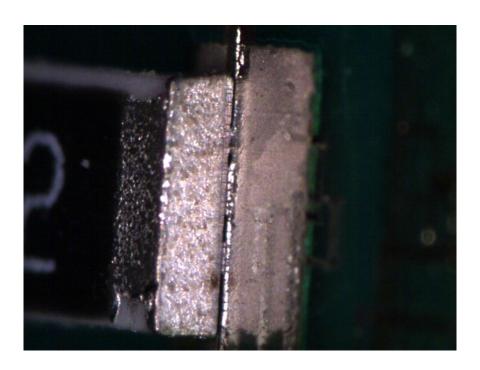

Figure 13 - Side view of double-sided copper substrates as seen from microscope

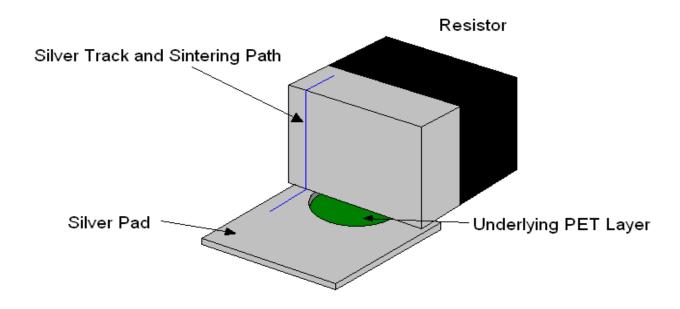

The goal for the double-sided copper substrates was to successfully form a silver interconnect that would travel from the top layer of copper to the bottom layer of copper while passing over the PET layer. For the specific application at AAA, the interconnect was requested to travel through a micro-sized circular chamfered VIA within the substrate, as shown in Figure 14. The diameter of the top of the chamfered VIA was desired to be around 0.5 mm. Since the provided double-sided copper substrates did not include a chamfered VIA, it was required to manufacture this VIA.

Figure 14 - Cross-sectional view of copper and PET substrate with a chamfered VIA

## 4.2 Characterization Methodologies

After depositing and sintering, the substrates were examined with the use of optical imaging and scanning electron microscopes. For optical imaging, a machine vision camera (EO-3112, Edmund Optics, Barrington, New Jersey, USA) was used in combination with a zoom imaging lens (Techspec® VZM 1000I, Barrington, New Jersey, USA) and a fiber optic illuminator (Dolan Jenner MI-150, Barrington, New Jersey, USA). The scanning electron microscopes used were a LEO 1530 FESEM (LEO 1530, Zeiss, Oberkochen, Germany) and a JEOL JSM-6460 SEM (JSM-6460, JEOL Ltd, Tokyo, Japan) with energy-dispersive X-ray spectroscopy (EDS). For further analysis, an optical profiler (WYKO NT1100, Veeco Instruments Inc, Plainview, New York, USA) was used to examine the profile of the silver track and a micro x-ray diffraction machine (Rigaku SA-HF3, Rigaku Corporation, Tokyo, Japan) was used to observe the crystalline structure of the substrate.

The substrates were also measured for resistance after deposition and sintering with a digital multimeter (Omega® HHM32, Omega® Engineering Inc, Stamford, Connecticut, USA)

in order to determine the successfulness of the silver interconnects. Although these measurements are not an exact representation of the resistance value due to the contact resistance of the measurement probes, an approximate resistance value can be obtained to determine the resistance of the track. In order to determine a more accurate resistance value, a source-measure unit (Keithley 2612 SourceMeter, Keithley Instruments, Cleveland, Ohio, USA) was used.

## 4.2 Experiments involving Substrates with Chamfered Vias

#### 4.2.1 Fabrication of a Chamfered Via

Many different fabrication methods were proposed. A vast number of these methods were discarded due to inconsistency. Some of these methods included physically puncturing the substrate with a sharp object as well as laser drilling. The major issue with the majority of these methods rested upon the inability to create substrates with consistent VIAs. Each VIA produced using these methods was unique and thus, would not provide meaningful experimental results. It would also not be a good representation of the chamfered VIA that was desired.

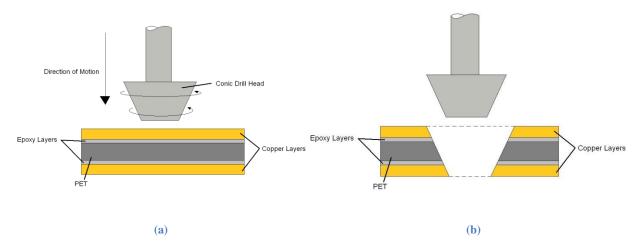

The method for manufacturing the chamfered VIAs that was chosen was based on lowering a spinning conic-shaped drill head onto the substrate. The substrate would be placed upon a hard surface while the conic-shaped drill head would be lowered extremely slowly into the substrate. This procedure is shown in Figure 15. After drilling, the substrates are washed with isopropanol and sonicated. Once finished, the samples would then be ready for deposition.

Due to the machining of the chamfered holes, the walls of the holes were not very smooth, but attempts to create an interconnect between the two layers of copper using these substrates were performed regardless.

Figure 15 – Cross-sectional schematic showing the manufacturing process for fabrication of chamfered VIAs (a) before and (b) after

## 4.2.2 Depositing the Silver Track for a Substrate with Chamfered Via

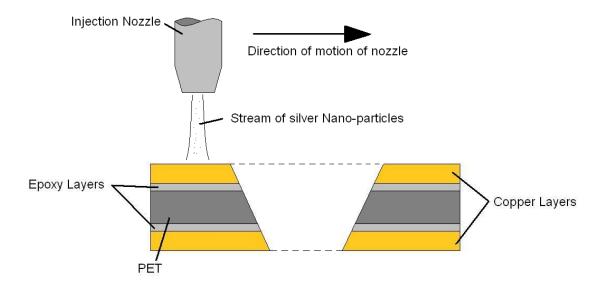

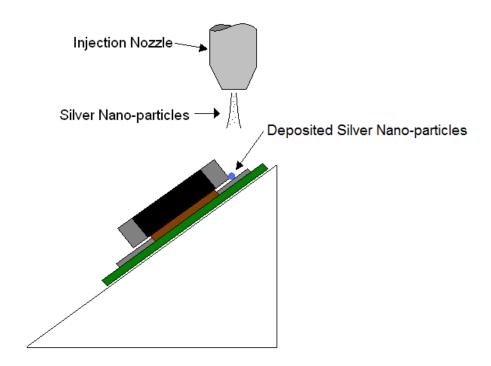

In order to form an interconnect to join the two copper layers, the injection nozzle was to move horizontally across the substrate while depositing the silver nano-particles. This process would allow a silver track to be deposited along the chamfered hole that was produced from the conic drill. This process is shown in Figure 16.

Figure 16 - Cross-sectional schematic showing silver deposition on substrates fabricated with a conic drill

With the deposition process done as such, the silver nano-particles would ideally be able to form a thin-film silver track along the chamfered edge of the hole, as shown in Figure 17, which should provide the substrate with a successful interconnect between the two layers of copper. This deposition process would then be repeated to provide multiple layers of silver as desired. The width of each track of silver is approximately 50 to 60  $\mu$ m.

Figure 17 - Cross-sectional schematic showing the ideal result of a successfully formed silver interconnect

There are many parameters that must be managed in order to produce silver interconnects that are free of cracks and delamination. Optimum parameters and their chosen values are listed in Table 2. There are a few parameters in this table that have ranges of values. This is mainly due to placing the formation of the silver track in higher priority than other parts of the process, such as sintering. The reason for this was due to uncertainty of success, since the fabricated chamfered holes were not as smooth as originally thought. If the current parameters produced good interconnects, the parameters with ranges of values can be optimized and other lower priority

parameters can be optimized afterwards, particularly parameters involving speed such as injection nozzle and laser sintering speeds.

Table 2 - LAMM Process Parameters for Deposition on Substrates with Chamfered Holes

|                   |              | LAMM Process Parameters |              |               |        |        |

|-------------------|--------------|-------------------------|--------------|---------------|--------|--------|

| <b>Sheath Gas</b> | Atomizer Gas | Atomizer                | Injection    | Number of     | Laser  | Laser  |

| Flow Rate         | Flow Rate    | Voltage                 | Nozzle Speed | Silver Layers | Speed  | Power  |

| 50 ccm            | 12 - 14 ccm  | 50 V                    | 0.1 mm/s     | 20 - 50       | 1 mm/s | 1.24 W |

### 4.2.3 Results for Substrates with a Chamfered Via

The silver nano-particles were deposited across the chamfered hole in a cross-like fashion, as shown in Figure 18. By introducing more than one path of silver over the chamfered hole, there would be a higher chance of creating a successful silver interconnect, since a total of four tracks would be deposited for each sample.

${\bf Figure~18~-~Cross-sectional~schematic~showing~deposited~silver~tracks~on~double-sided~copper~substrates~with~a~chamfered~VIA}\\$

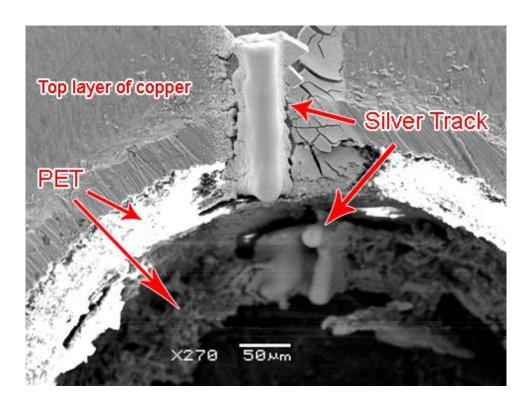

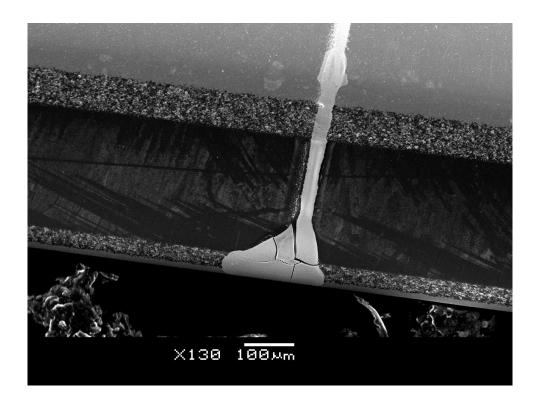

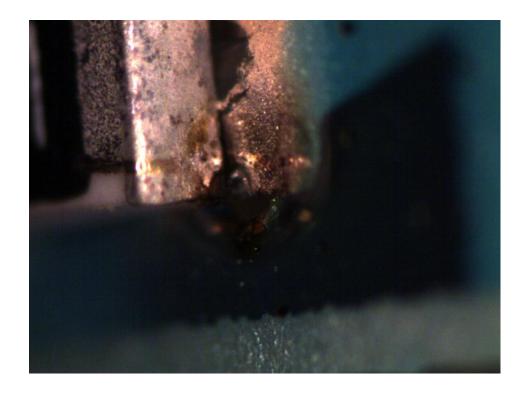

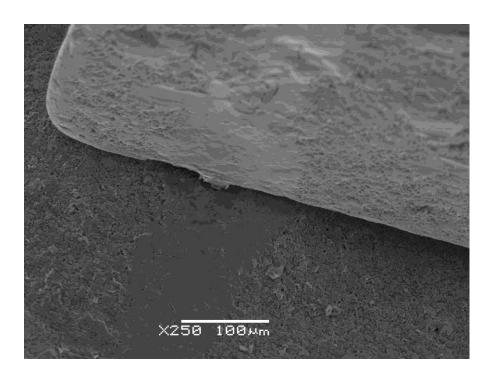

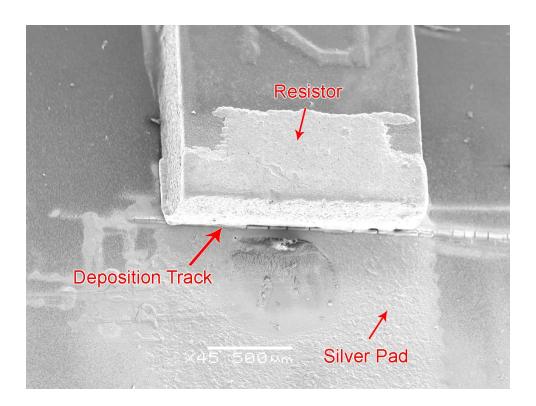

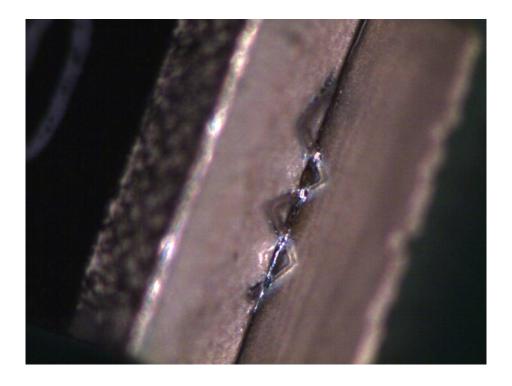

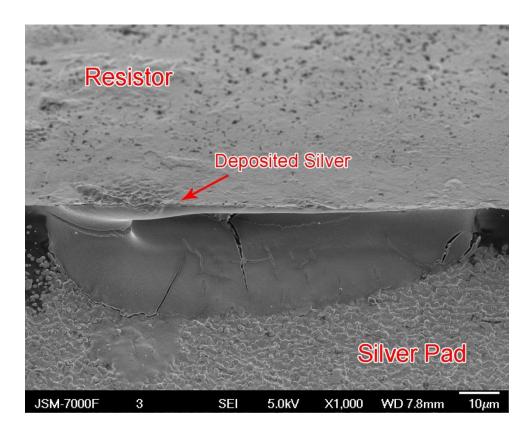

After many experiments with the substrates containing chamfered VIAs, it was evident that this process was not very successful. A JEOL JSM-6460 scanning electron microscope

(SEM) was used to examine the substrate after deposition and sintering. An SEM image is shown in Figure 19, which shows some of the challenges associated with these experiments. As seen, the steepness and inaccuracies of the fabrication process combined caused the interconnects to break at various points. The VIA was expected to be smooth and uniform, but from SEM images, it could be seen that the surface was not as well machined as desired. It was concluded that this approach towards creating an interconnect between the two layers of copper had an extremely low chance of success, due to inaccuracies of the fabrication process.

Figure 19 - SEM image of an attempt to form an interconnect on the fabricated chamfered via

# 4.3 Experiments Involving Substrates with Polished Slants

### 4.3.1 Fabrication of Polished Slants

A different approach was taken to create silver interconnects that connected the two layers of copper. Due to the fabrication inaccuracies of the conic-drilling process, the fabrication of the chamfered VIAs was simplified down to a slant created after polishing the substrate at an angle, shown in Figure 20. Since depositing along the chamfered VIA would be equivalent to depositing along a slanted edge, the experiments were simplified to depositing nano-silver particles onto slanted edges. In industrial practices, fabrication of the chamfered VIAs would not be extremely difficult, as automated tools with high precision can be used.

Figure 20 - Cross-sectional Schematic Showing the Deposition Process on Substrates with a Polished Slant

The polishing process is much more controlled compared to conic drilling, and the resultant edge is extremely smooth. The substrates were polished at an angle of 45° to the polishing pad with a very fine abrasive. The abrasive used was an aluminum oxide powder with

grain sizes of 0.05 µm. The finished polished substrate would have the bottom layer of copper exposed along the polished edge, much like the intended result of the conic drilling process.

After polishing, the substrates are washed with an isopropanol solution and sonicated.

## 4.3.2 Depositing the Silver Track for Substrates with Polished Slants

As shown in Figure 20, the deposition process performed on the substrates with polished slants is identical to that of the substrates with chamfered VIAs. The injection nozzle would be passed over the substrate's polished edge, depositing silver nano-particles in a single path that would span the length of the polished slant. This silver track would then be sintered using a laser to complete the process. The process parameters are listed in Table 3.

Table 3 - LAMM Process Parameters for Substrates with a Polished Slant

|  |                         | LAMM Process Parameters   |                     |                           |                         |                 |                |

|--|-------------------------|---------------------------|---------------------|---------------------------|-------------------------|-----------------|----------------|

|  | Sheath Gas<br>Flow Rate | Atomizer Gas<br>Flow Rate | Atomizer<br>Voltage | Injection<br>Nozzle Speed | Number of Silver Layers | Laser<br>Speed  | Laser<br>Power |

|  | 50 ccm                  | 12 - 14 ccm               | 50 V                | 0.1 - 1 mm/s              | 4 - 10                  | 1 mm/s - 5 mm/s | 0.44 - 3.1 W   |

Upon running various experiments, it was discovered that the silver track would form much easier than the experiments with a fabricated VIA. With this information, many process parameter values were modified in order to better optimize the experiments. The most time consuming part of the process was the deposition of the silver nano-particles. Due to the silver track forming much easier on the polished slant, the injection nozzle speed was increased and the number of silver layers was decreased.

The main reason for the high number of silver layers used in the experiments with chamfered VIAs was due to the extremely large crack formations of the silver track that appeared consistently along the face of the VIA. With the substrates with a polished slant, there

did not appear to be much of a difference between 10 and 50 silver layers, as both were able to create a silver track that spanned the entire face of the polished slant. Although cracks did appear for the silver tracks deposited along the polished slants, these cracks were not caused by the injection nozzle having difficulty depositing the silver nano-particles upon certain areas of the surface and would be investigated.

## 4.3.3 Initial Results for Substrates with a Polished Slant

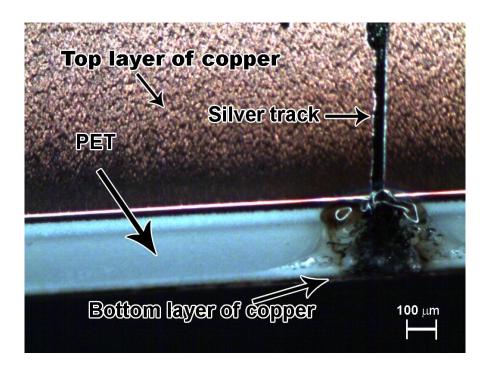

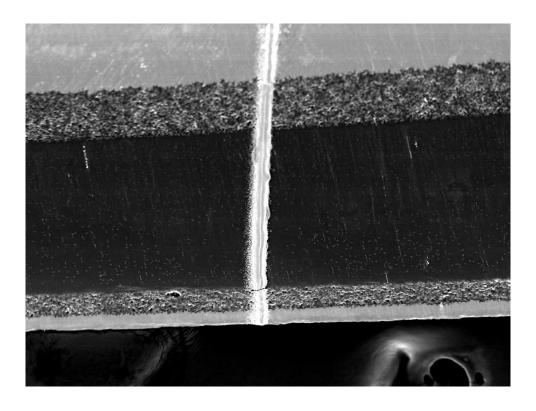

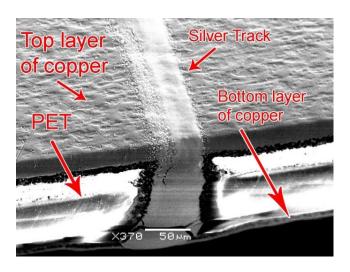

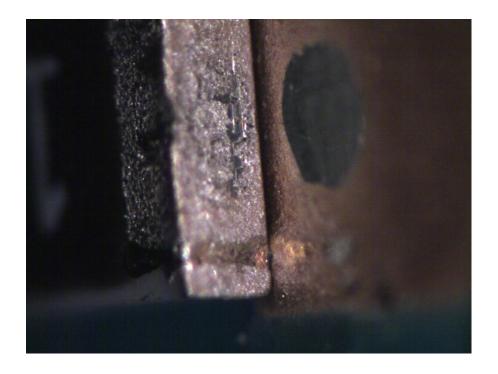

When examining the substrates with the use of the optical imaging system, it was noted that the deposited silver track appeared to form a solid track that travelled from the top copper layer to the bottom copper layer, as shown in Figure 21. The images taken of the substrates with polished slants appeared to be much better than that of the substrates with chamfered VIAs, since there were no extremely large cracks visible. It can also be noted that the bottom layer of copper does not have a large amount of exposure when viewed from the top, since the copper layers are very thin.

Figure 21 - Top view of a substrate with a polished slant after 4 layers of deposition at 0.1 mm/s and sintering at 0.4 W and 1 mm/s.

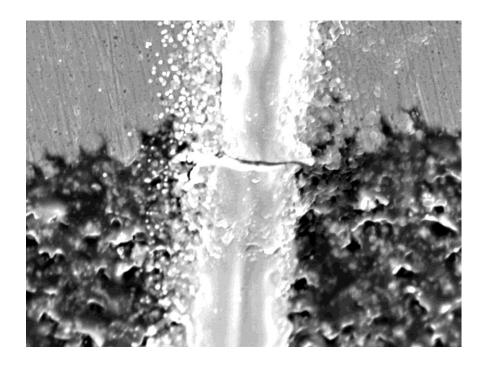

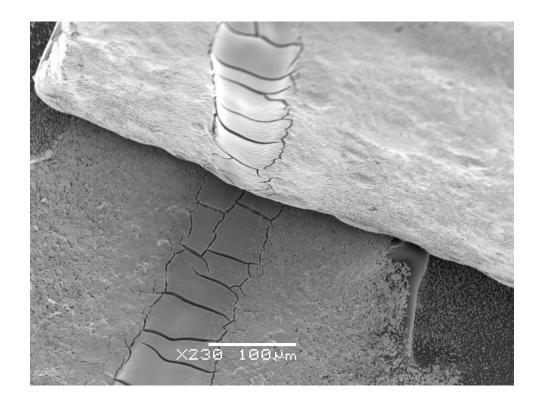

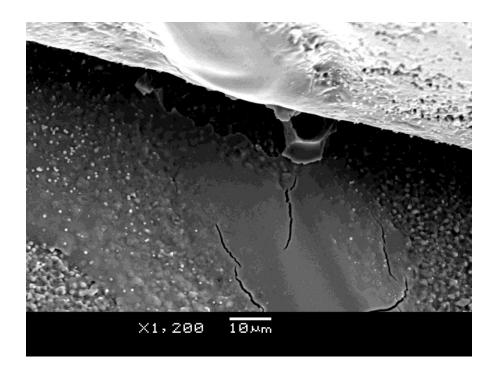

At times there would be cracks in the silver track visible from the optical images, as shown in Figure 22 along the face of the PET. However, these cracks were not on the same magnitude as those from the substrates with chamfered VIAs. In order to view the cracks, the substrate would be required to be examined with a scanning electron microscope. Upon viewing the interconnects with an SEM as shown in Figure 23, very fine cracks were seen in both conductive and non-conductive interconnects. When measured with an ohmmeter by connecting a probe on either end of the interconnect, the conductive samples showed resistances in the range of 7  $\Omega$  to 10  $\Omega$ .

Figure 22 - Top view of a substrate with a polished slant after 4 layers of deposition at 0.1 mm/s and sintering at 1.24 W and 1 mm/s.

Figure 23 - SEM Image of a substrate with a polished slant displaying a crack in the interconnect

## 4.3.4 Repeated Deposition and Sintering

In an attempt to increase the chances of creating successful interconnects on the polished slant, some substrates underwent the deposition and sintering process multiple times. For these substrates, the process would work as follows: after depositing and sintering the silver track, another few layers of silver were deposited upon the already existing track and sintered once again. By repeating the process multiple times, the new layers of silver were expected to be able to fill in the cracks formed in the previous process and potentially create a good interconnect.

### 4.3.4.1 Optical Imaging Results

One observation that can be noted is that upon multiple deposition and sintering repetitions, the PET around the silver track will appear to melt slightly. This is more evident in experiments where the deposition and sintering process were repeated up to three times, as shown in Figure 24. The silver track in Figure 24 was measured for conductivity during each iteration of the deposition and sintering processes, however none of the measurements showed any conductivity. The melting of the PET may have played a role in creating a non-conductive result due to material stresses that may have formed once the PET began to change shape.

Figure 24 - Top view of a deposited silver track that was sintered multiple times, resulting in a slightly melted area of PET around the silver track

Deposition and sintering iterations are repeated for substrates that contained non-conductive interconnects after the first deposition and sintering process. However, it appears that multiple sintering stages cause the PET around the silver track to melt and possibly add more problems for the silver track. Repeating the deposition and sintering stages once for a total of 2 deposition and sintering stages appears to not melt the PET very much, and has even resulted in some conductive results, but further iterations will change the PET greatly.

### **4.3.4.2 SEM Results**

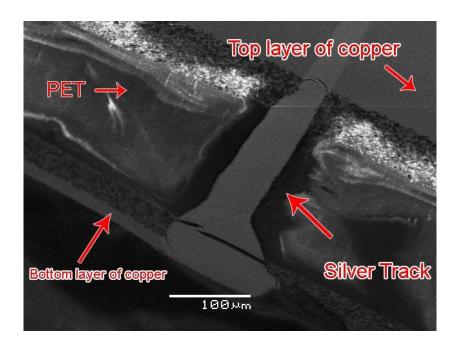

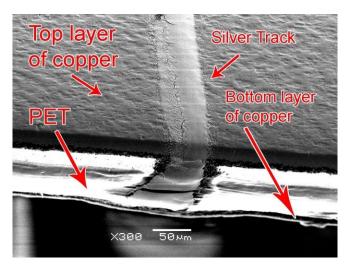

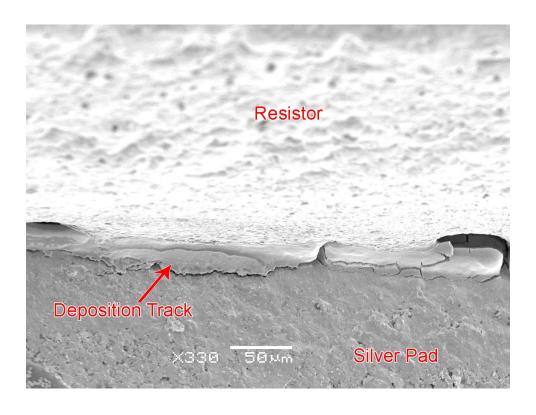

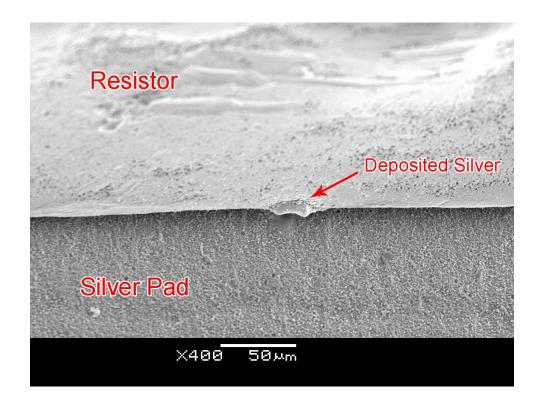

An SEM image of a conductive interconnect that was created through multiple stages of deposition and sintering is shown in Figure 25. The silver track appears to be very solid along the entire slant, with the exception of an extremely fine crack that can be seen near the interface between the top layers of material. Although a crack is present, the interconnect was still able to form a connection between the top and bottom layers of copper. This type of experiment showed

very few cracks compared to experiments that did not repeat the deposition and sintering process. It is likely that the repetition of the deposition process allows previously formed cracks to be filled in with the new deposition of silver, allowing for a solid track to be formed along the polished edge. The reason for the crack is hypothesized to be from the cause of a difference in thermal expansion between materials. More experiments were required to be performed in order to determine if this hypothesis was feasible.

Figure 25 - SEM image of a conductive interconnect formed on a substrate with a polished slant. Two stages of deposition were performed, each with 5 layers at 1 mm/s.

Upon measuring the resistance values of the interconnects with the use of an ohmmeter, the resistances were found to range from 5  $\Omega$  to 8  $\Omega$ . Some of these substrates were analyzed with a source-measure unit for more accurate resistance values, and these values were found to

range from 3.2  $\Omega$  to 4.31  $\Omega$ . This resistance value appears to be much higher than the resistance that can be calculated using the equation involving electrical resistivity, Equation (4.1):

$$R = \rho \frac{l}{A} \tag{4.1}$$

where R is the electrical resistance of the material,  $\rho$  is the electrical resistivity of the material, l is the length of the track, and A is the cross-sectional area of the track. Using the electrical resistivity value of bulk silver (15.87 n $\Omega$  m), the theoretical resistance calculated is 0.017  $\Omega$ . The measured resistance is larger than the theoretical resistance by at least 100 times. This is likely attributed to the formation of pores in the silver tracks during sintering. When the silver nanoparticles are sintered, the evaporation of the solvent material causes pores to be formed within the microstructure of the silver track [48]. Voids and pores that are formed within conductive material have shown to increase the resistance of the material, which is likely the reason that the measured resistance is much higher than the calculated resistance [49].

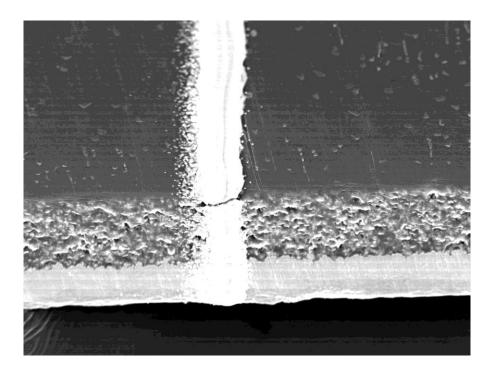

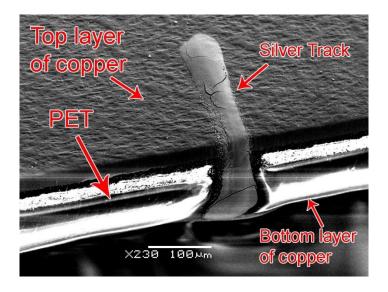

### 4.3.5 Insufficient Heating of Substrate

As noted before, the substrate should be heated during the deposition process in order to allow the silver nano-particles to adhere well upon contact with the surface. When the substrate is not heated sufficiently, the silver track will not stay uniform, as shown in Figure 26. Due to the nature of the polished slant, the silver nano-particles will tend to flow downwards along the slant when the substrate is not heated sufficiently, creating non-uniform shapes for the resultant silver track. Surprisingly, Figure 26 (a) shows this as well as cracks in the silver track while still resulting in forming a successful interconnect between the two layers of copper. Upon inspecting the SEM image closely, it can be seen that there is a small sliver of silver that appears to bridge the crack formed at the bottom of the polished slant. It is most likely due to this extremely small

connection that the entire interconnect is able to bridge the two layers of copper. Figure 26 (b) shows a substrate that demonstrates the same behavior when the substrate is not heated during deposition, but resulted in an unsuccessful interconnect. There appear to be many cracks that have formed at the top and bottom of the interconnect. These cracks are most likely the reason the interconnect was unable to join the two layers of copper.

(a)

(b)

Figure 26 - SEM images of substrates with polished slants after deposition during insufficient substrate heating temperatures. The substrates were sintered with (a) 1.25 W at 1 mm/s, which formed a successful interconnect and (b) 1 W at 2 mm/s, which did not form a successful interconnect.

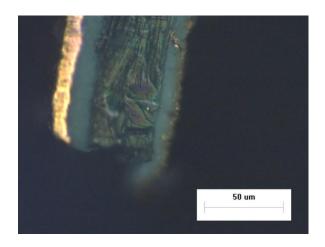

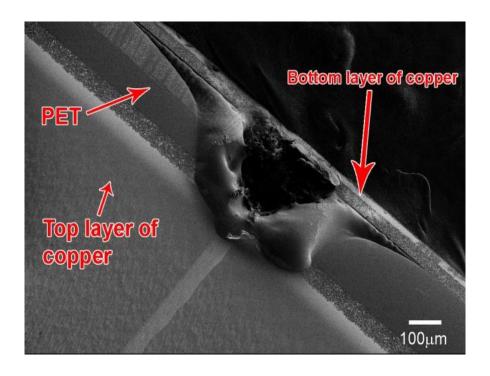

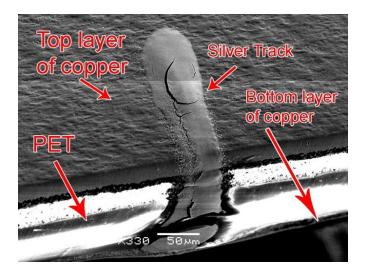

The silver interconnect track at many times appears to be breaking around areas where different materials are joined together. Figure 27 shows another example of this. There appears to be a crack that travels across the track entirely around the region where the bottom layer of epoxy is joined with the PET, as well as small fractures that appear near the top of the interconnect between the top layer of epoxy and the PET.

Figure 27 - SEM images of a substrate with a polished slant after deposition during insufficient substrate heating temperatures. This substrate was sintered at 1.24 W and 1 mm/s.

### 4.3.6 Increasing the Laser Power

When experimenting with higher laser powers, it was noted that the intensity of the laser has the capability to burn the PET layer when the laser power was increased to 3 W. Shown in Figure 28, it can be seen that upon sintering the silver nano-particles, the laser was able to burn the PET surrounding the silver track. However, although the substrate was burned, when measured for conductivity, the results were positive for this particular substrate. This was likely due to coincidence that while burning the PET, the silver nano-particles managed to form a path downwards to the bottom layer of copper. When other burned substrates were measured, the majority did not contain a successful interconnect. For the few substrates that did contain conductive results, the results ranged from  $500 \Omega$  to  $2.5 k\Omega$ . These resistance values are

extremely high compared to the results from the conductive substrates that did not burn. This shows that although the substrates were able to have conductive interconnects after burning, the interconnects would not be usable for any devices as the resistance is much too large.

(a)

(b)

Figure 28 - Images of substrate with polished slant after high-power sintering (3W) at 4 mm/s. Images taken from an (a) optical microscope, and (b) SEM.

## 4.3.7 Alternative Sintering Method