# Simplifying the Creation of Multi-core Processors: An Interconnection Architecture and Tool Framework

by

Samuel R. Grossman

A thesis presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2012

© Samuel R. Grossman 2012

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

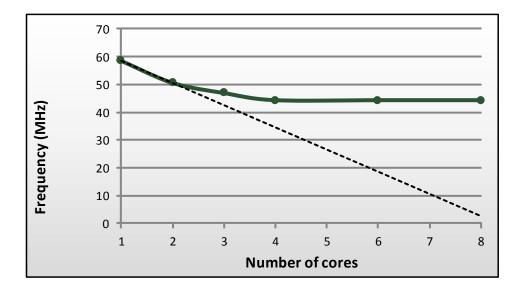

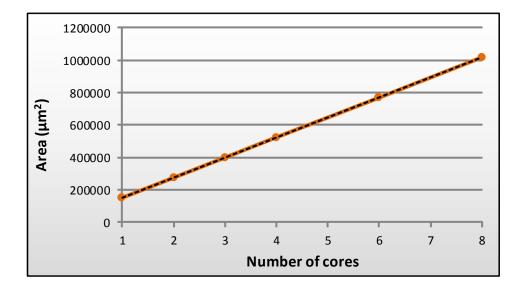

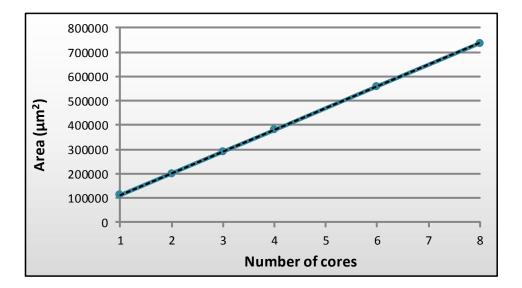

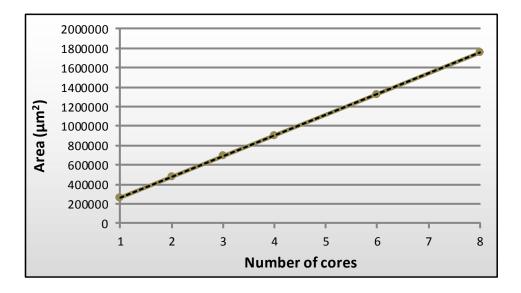

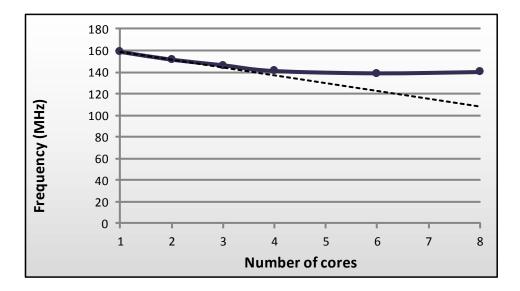

The contribution of this thesis is two-fold: an on-chip interconnection architecture designed specifically for multi-core processors and a tool framework that simplifies the process of designing a multi-core processor. Both contributions primarily target ASIC fabrication, though prototyping on an FPGA is also supported. SG-Multi, the on-chip interconnection architecture, distinguishes itself from other interconnection architectures by emphasizing universal adaptability; that is, a primary design goal is to ensure compatibility with industry-supplied cores originally intended for other architectures. This goal is achieved through the use of bus adapters and without introducing clock cycle latency. SG-Multi is a multi-bus architecture that uses slave-side arbitration and supports multiple simultaneous transactions between independent devices. All transactions are pipelined in two stages, an address phase and a data phase, and for improved performance slave devices must signal their status for a given clock cycle at the beginning of that cycle. SG-Multi Designer, the tool framework which builds systems that use SG-Multi, provides a higher level of abstraction compared to other competing system-building solutions; the set of components with which a designer must be concerned is much more limited, and low-level details such as hardware interface compatibility are removed from active consideration. Experimental results demonstrate that the hardware cost of using SG-Multi is reasonable compared to using a processor's native bus architecture, although the current implementation of arbitration is identifiable as an area for future improvement. It is also shown that SG-Multi is scalable; the reference systems grow linearly with respect to the number of cores when tested for ASIC fabrication and slightly sublinearly when tested for FPGA prototyping, and the maximum achievable clock frequency remains almost constant as the number of cores grows beyond four. Because the reference systems tested are an accurate reflection of the types of systems SG-Multi Designer produces, it is concluded that the abstraction model used by SG-Multi Designer does not over-simplify the design process in a way that causes excessive performance degradation or increased hardware resource consumption.

#### Acknowledgements

I wish to thank my thesis reviewers, Dr. Catherine Gebotys and Dr. Hiren Patel, for their valuable feedback towards improving this thesis. I would also like to thank my supervisor, Dr. William Bishop, for his help and support throughout my degree program.

### Dedication

I dedicate this thesis to my wonderful grandmother, Lillian Bercuson. You have always been a special and beloved light in my life. Although you may be physically far away, remember that light can cross continents in but an instant.

# Contents

| Lis      | st of | Figure  | 2S                                             | ix  |

|----------|-------|---------|------------------------------------------------|-----|

| Lis      | st of | Tables  | 5                                              | xii |

| 1        | Intr  | oducti  | on                                             | 1   |

|          | 1.1   | Goals   | and Motivation                                 | 2   |

|          | 1.2   | Resear  | ch Contributions                               | 3   |

|          |       | 1.2.1   | On-Chip Interconnection Architecture           | 3   |

|          |       | 1.2.2   | Multi-core Rapid Development Framework         | 5   |

|          | 1.3   | Thesis  | Organization                                   | 6   |

| <b>2</b> | Bac   | kgroun  | ıd                                             | 7   |

|          | 2.1   | Hetero  | geneous Multi-core Processors                  | 7   |

|          | 2.2   | Rapid   | Prototyping of Multi-core Processors           | 9   |

|          | 2.3   | Existin | ng Related Interconnection Architectures       | 11  |

|          |       | 2.3.1   | Networks-on-Chip                               | 12  |

|          |       | 2.3.2   | Altera Avalon                                  | 13  |

|          |       | 2.3.3   | ARM AHB-Lite                                   | 17  |

|          |       | 2.3.4   | IBM CoreConnect                                | 20  |

|          | 2.4   | Existir | ng Related System Construction Tools           | 22  |

|          |       | 2.4.1   | Altera Qsys and SoPC Builder                   | 23  |

|          |       | 2.4.2   | Xilinx Platform Studio                         | 24  |

|          |       | 2.4.3   | Tensilica Xtensa Processor Developer's Toolkit | 24  |

|          |       |         |                                                |     |

| 3        | Sys                                                                                      | em Overview 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                              |

|----------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|          | 3.1                                                                                      | High-Level Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                              |

|          | 3.2                                                                                      | SG-Multi Device Wrappers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28                                                              |

|          | 3.3                                                                                      | SG-Multi Arbiters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29                                                              |

| 4        | Arc                                                                                      | itecture Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                                                              |

|          | 4.1                                                                                      | Basic Signal Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33                                                              |

|          |                                                                                          | 4.1.1 Global Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                              |

|          |                                                                                          | 4.1.2 Master Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                                              |

|          |                                                                                          | 4.1.3 Slave Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                              |

|          |                                                                                          | 4.1.4 Internal Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                              |

|          | 4.2                                                                                      | Signal Size Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36                                                              |

|          | 4.3                                                                                      | Transaction Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                              |

|          | 4.4                                                                                      | Device Wrapper Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40                                                              |

|          |                                                                                          | 4.4.1 Master Wrappers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                              |

|          |                                                                                          | 4.4.2 Slave Wrappers and Arbiters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                                                              |

|          |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

| <b>5</b> | Too                                                                                      | s Design 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49                                                              |

| 5        | <b>Too</b><br>5.1                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>49</b><br>49                                                 |

| 5        |                                                                                          | Abstraction Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                               |

| 5        | 5.1                                                                                      | Abstraction Model    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . </td <td>49</td> | 49                                                              |

| 5<br>6   | 5.1<br>5.2<br>5.3                                                                        | Abstraction Model       4         Framework Overview       5         User Interaction       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49<br>53                                                        |

|          | 5.1<br>5.2<br>5.3                                                                        | Abstraction Model       4         Framework Overview       5         User Interaction       5         erimental Results       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49<br>53<br>56                                                  |

|          | 5.1<br>5.2<br>5.3<br><b>Exp</b>                                                          | Abstraction Model       4         Framework Overview       4         User Interaction       4         erimental Results       5         AHB-Lite Comparison       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 49<br>53<br>56<br><b>57</b>                                     |

|          | 5.1<br>5.2<br>5.3<br><b>Exp</b>                                                          | Abstraction Model       4         Framework Overview       4         User Interaction       5         erimental Results       5         AHB-Lite Comparison       5         6.1.1       Benchmark Performance Comparison       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49<br>53<br>56<br><b>57</b><br>59                               |

|          | 5.1<br>5.2<br>5.3<br><b>Exp</b>                                                          | Abstraction Model       4         Framework Overview       5         User Interaction       5         erimental Results       5         AHB-Lite Comparison       5         6.1.1       Benchmark Performance Comparison       5         6.1.2       FPGA Hardware Comparison       6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49<br>53<br>56<br><b>57</b><br>59<br>59                         |

|          | 5.1<br>5.2<br>5.3<br><b>Exp</b>                                                          | Abstraction Model       4         Framework Overview       4         User Interaction       5         erimental Results       5         AHB-Lite Comparison       5         6.1.1       Benchmark Performance Comparison       5         6.1.2       FPGA Hardware Comparison       6         6.1.3       ASIC Hardware Comparison       6                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>53<br>56<br><b>57</b><br>59<br>59<br>60                   |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Exp</li> <li>6.1</li> </ul>              | Abstraction Model       4         Framework Overview       4         User Interaction       5         erimental Results       5         AHB-Lite Comparison       5         6.1.1       Benchmark Performance Comparison       5         6.1.2       FPGA Hardware Comparison       6         6.1.3       ASIC Hardware Comparison       6         Hardware Scalability       6       6                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>53<br>56<br><b>57</b><br>59<br>59<br>60<br>61             |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Exp</li> <li>6.1</li> </ul>              | Abstraction Model       4         Framework Overview       4         User Interaction       4         erimental Results       5         AHB-Lite Comparison       4         6.1.1       Benchmark Performance Comparison       4         6.1.2       FPGA Hardware Comparison       6         6.1.3       ASIC Hardware Comparison       6         6.1.4       FPGA Scalability       6                                                                                                                                                                                                                                                                                                                                                                                       | 49<br>53<br>56<br><b>57</b><br>59<br>60<br>61<br>63             |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Exp</li> <li>6.1</li> </ul>              | Abstraction Model       4         Framework Overview       4         User Interaction       4         erimental Results       5         AHB-Lite Comparison       4         6.1.1 Benchmark Performance Comparison       5         6.1.2 FPGA Hardware Comparison       6         6.1.3 ASIC Hardware Comparison       6         6.1.1 FPGA Scalability Results       6         6.2.2 ASIC Scalability Results       6                                                                                                                                                                                                                                                                                                                                                        | 49<br>53<br>56<br><b>57</b><br>59<br>60<br>61<br>63<br>66       |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Exp</li> <li>6.1</li> <li>6.2</li> </ul> | Abstraction Model       4         Framework Overview       5         User Interaction       5         erimental Results       5         AHB-Lite Comparison       5         6.1.1 Benchmark Performance Comparison       5         6.1.2 FPGA Hardware Comparison       6         6.1.3 ASIC Hardware Comparison       6         6.2.1 FPGA Scalability       6         6.2.2 ASIC Scalability Results       6         Simultaneous Transaction Performance       6                                                                                                                                                                                                                                                                                                           | 49<br>53<br>56<br><b>57</b><br>59<br>60<br>61<br>63<br>66<br>66 |

| <b>7</b>     | Con   | clusio | ns                                      | <b>74</b> |

|--------------|-------|--------|-----------------------------------------|-----------|

|              | 7.1   | Contri | butions Summary                         | 74        |

|              | 7.2   | Experi | iment Conclusions                       | 75        |

|              | 7.3   | Future | e Research Directions                   | 77        |

|              |       | 7.3.1  | Basic Arbitration Improvements          | 78        |

|              |       | 7.3.2  | Other Bus Adapters                      | 78        |

|              |       | 7.3.3  | Multiple Clock Domains                  | 79        |

|              |       | 7.3.4  | Reconfigurable Inter-core Communication | 80        |

| Re           | efere | nces   |                                         | 83        |

| A            | PPE   | NDICI  | ES                                      | 88        |

| $\mathbf{A}$ | SG-   | Multi  | Protocol Specification                  | 89        |

|              | A.1   | Signal | Descriptions                            | 89        |

|              |       | A.1.1  | Global Signals                          | 90        |

|              |       | A.1.2  | Common Signals                          | 90        |

|              |       | A.1.3  | Master Interface Signals                | 91        |

|              |       | A.1.4  | Slave Interface Signals                 | 91        |

|              |       | A.1.5  | Data Bus Alignment                      | 92        |

|              | A.2   | Transa | action Details                          | 93        |

|              |       | A.2.1  | Master Interface Signalling             | 93        |

|              |       | A.2.2  | Slave Interface Signalling              | 98        |

| в            | SG-   | Multi  | Designer XML Specifications             | 100       |

|              | B.1   | Suppo  | rted XML File Types                     | 100       |

|              | B.2   | Variab | les and Macros                          | 100       |

|              | B.3   | XML I  | File Format Details                     | 102       |

|              |       | B.3.1  | Common Nodes                            | 102       |

|              |       | B.3.2  | Master and Slave Device Nodes           | 102       |

|              |       | B.3.3  | Bus Adapter Nodes                       | 105       |

|              | B.4   | Exam   | ple XML Files                           | 106       |

# List of Figures

| 2.1 | Illustration of the two different types of multi-core processors                                                                                                                                   | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Map of application domains of various rapid prototyping platforms $\ldots$ .                                                                                                                       | 12 |

| 2.3 | Two-master example of a system that uses Avalon-MM                                                                                                                                                 | 14 |

| 2.4 | Examples of unpipelined Avalon-MM read and write transactions $\ldots$ .                                                                                                                           | 16 |

| 2.5 | Example of a typical AHB-Lite system                                                                                                                                                               | 18 |

| 2.6 | Two simple AHB-Lite transactions, one with a wait state                                                                                                                                            | 19 |

| 2.7 | Illustration of AHB-Lite error signalling functionality                                                                                                                                            | 20 |

| 2.8 | Simple example of a system based on IBM CoreConnect PLB                                                                                                                                            | 21 |

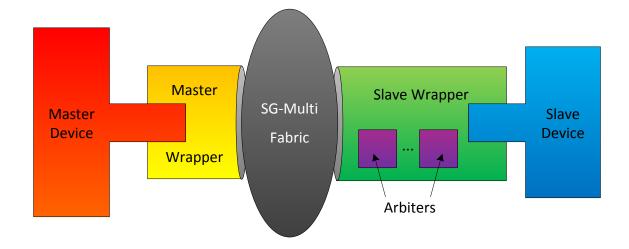

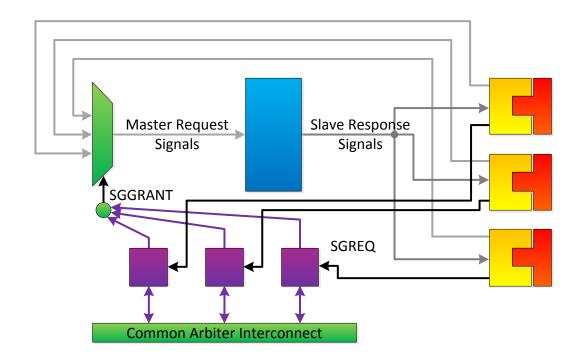

| 3.1 | Overview of an SG-Multi system, illustrating the role of device wrappers $% \left( {{{\left( {{{\left( {{{\left( {{{\left( {{{}}} \right)}} \right)}} \right.}} \right)}_{0,0}}} \right)} \right)$ | 27 |

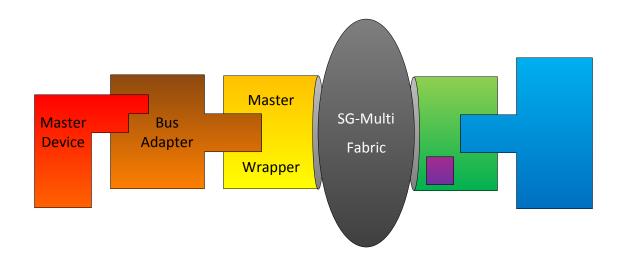

| 3.2 | Overview of an SG-Multi system, illustrating the role of bus adapters $\ . \ .$                                                                                                                    | 28 |

| 3.3 | Hardware components that encapsulate a master device in SG-Multi $% \mathcal{A} = \mathcal{A} = \mathcal{A} = \mathcal{A}$                                                                         | 30 |

| 3.4 | Hardware components that encapsulate a slave device in SG-Multi                                                                                                                                    | 31 |

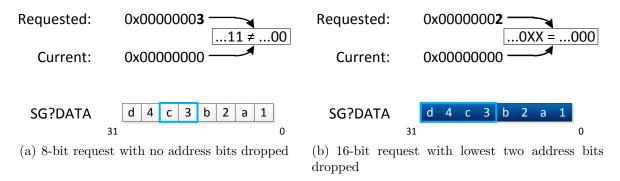

| 4.1 | Signal size multiplexing illustration on a 32-bit data bus                                                                                                                                         | 37 |

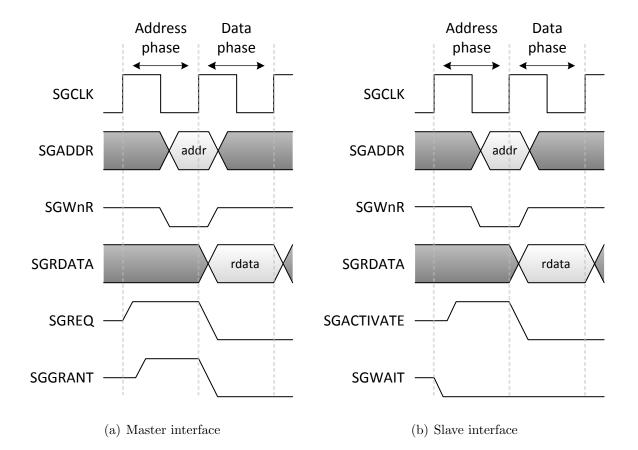

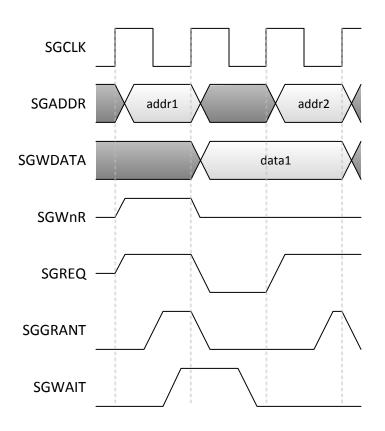

| 4.2 | Simple SG-Multi read transaction at master and slave interfaces $\ldots$ .                                                                                                                         | 38 |

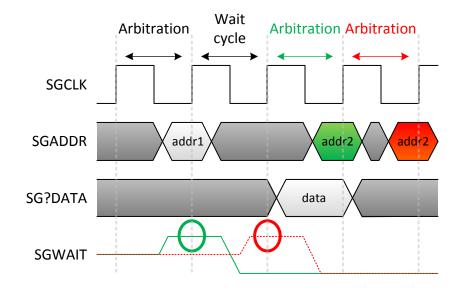

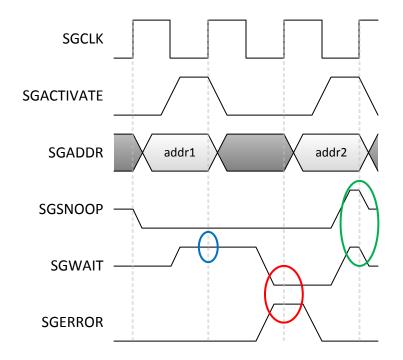

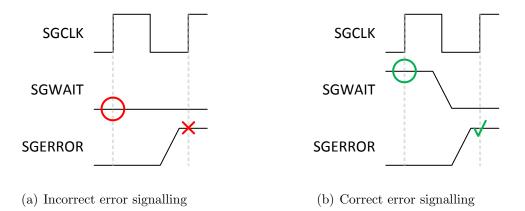

| 4.3 | Illustration of different slave response signalling semantics                                                                                                                                      | 40 |

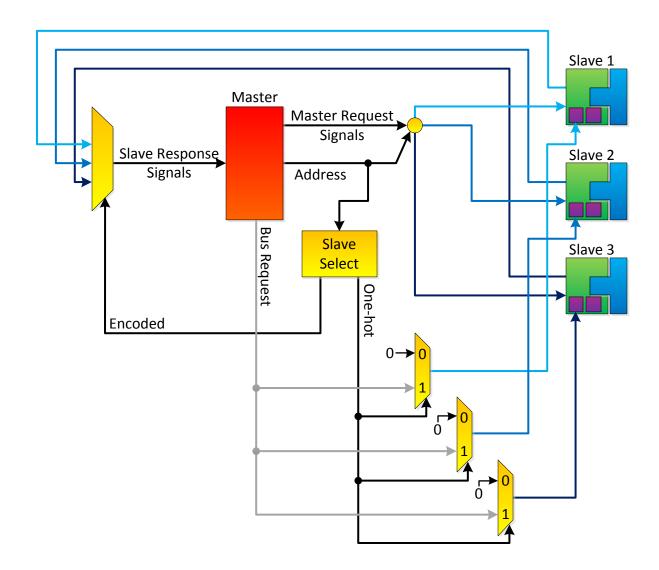

| 4.4 | Master device wrapper signal routing implementation                                                                                                                                                | 41 |

| 4.5 | Address and size matching performed for bus snooping                                                                                                                                               | 43 |

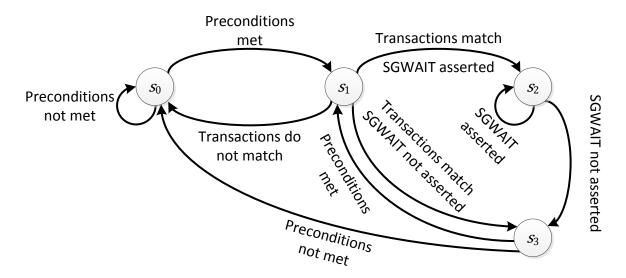

| 4.6 | Bus snooping state machine in the master device wrapper                                                                                                                                            | 44 |

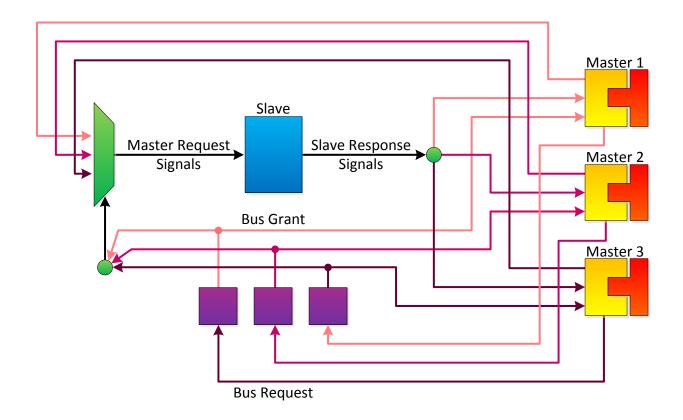

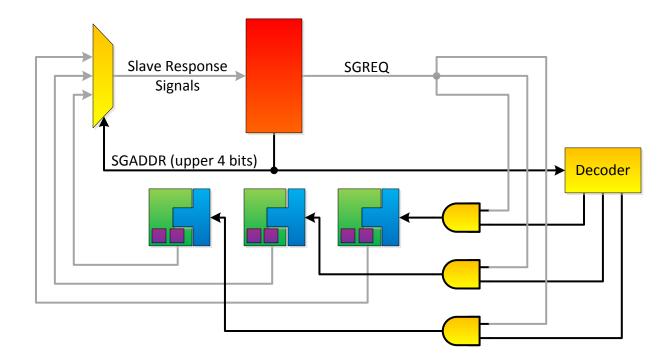

| 4.7 | Slave device wrapper signal routing implementation                                                                                                                                                 | 45 |

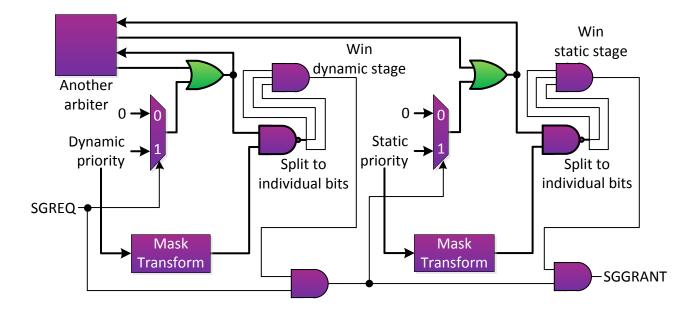

| 4.8 | Combinational logic circuit implementation of an SG-Multi arbiter                                                                                                                                  | 48 |

| 5.1 | Example of a system design modelled using SG-Multi Designer's abstraction                                                                                                                          |    |

|     | $model  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                           | 51 |

| 5.2  | Overview of the SG-Multi Designer framework                                            | 55  |

|------|----------------------------------------------------------------------------------------|-----|

| 5.3  | Representation of SG-Multi Designer's main window                                      | 56  |

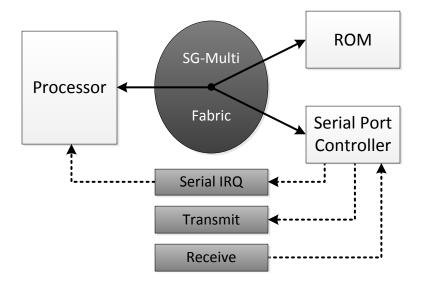

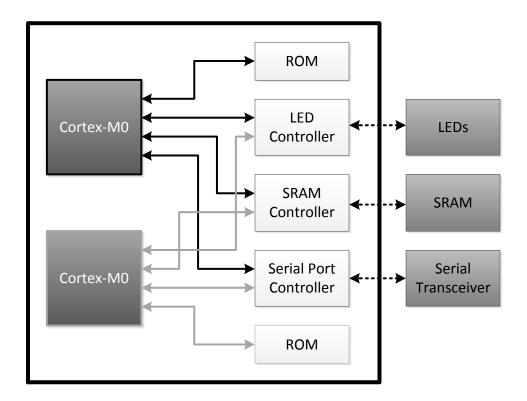

| 6.1  | Single-core and dual-core reference system configurations for experiments .            | 58  |

| 6.2  | Experiment configuration of slaves, with and without arbiters                          | 62  |

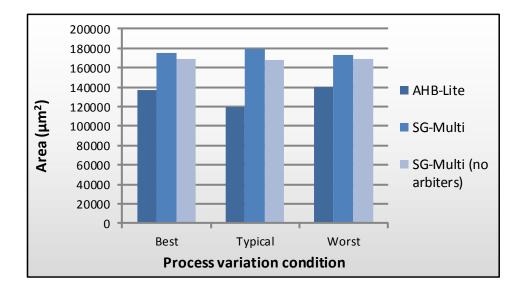

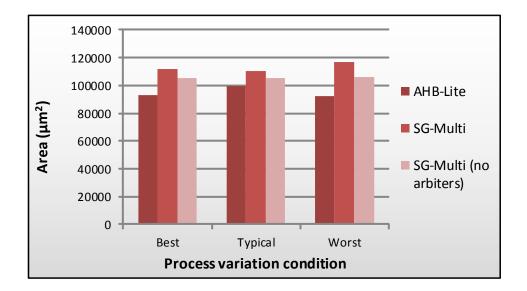

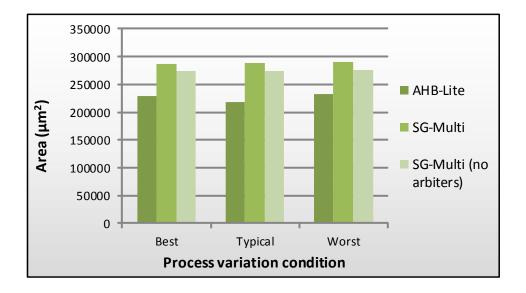

| 6.3  | Combinational area results for comparing AHB-Lite and SG-Multi                         | 64  |

| 6.4  | Noncombinational area results for comparing AHB-Lite and SG-Multi                      | 64  |

| 6.5  | Total area results for comparing AHB-Lite and SG-Multi                                 | 65  |

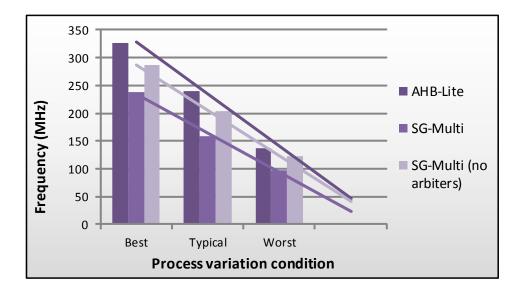

| 6.6  | Maximum clock frequency results for comparing AHB-Lite and SG-Multi .                  | 65  |

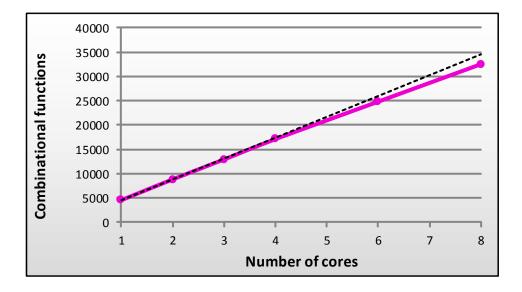

| 6.7  | FPGA combinational functions vs. number of cores in an SG-Multi system                 | 67  |

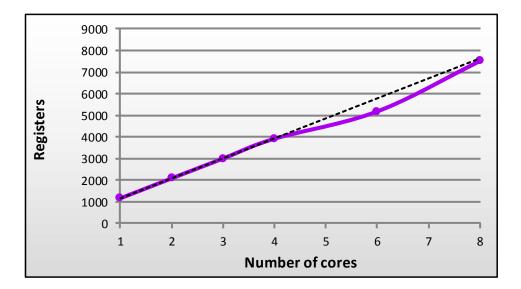

| 6.8  | FPGA registers vs. number of cores in an SG-Multi system                               | 67  |

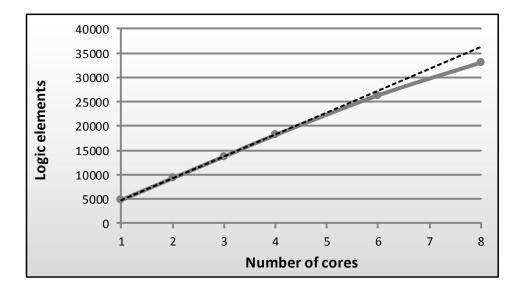

| 6.9  | FPGA total logic elements vs. number of cores in an SG-Multi system $~$ .              | 68  |

| 6.10 | FPGA maximum clock frequency vs. number of cores in an SG-Multi system                 | 68  |

| 6.11 | ASIC combinational area vs. number of cores in an SG-Multi system $~~.~.~$             | 69  |

| 6.12 | ASIC noncombinational area vs. number of cores in an SG-Multi system $% \mathcal{A}$ . | 69  |

| 6.13 | ASIC total area vs. number of cores in an SG-Multi system                              | 70  |

| 6.14 | ASIC maximum clock frequency vs. number of cores in an SG-Multi system                 | 70  |

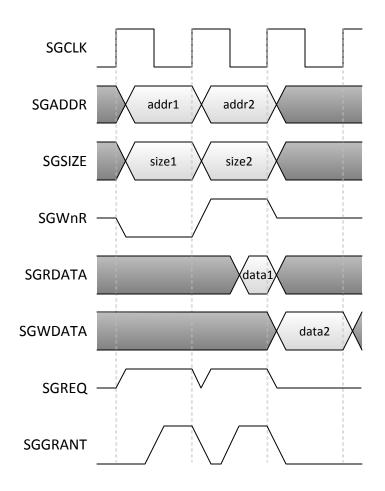

| A.1  | Example read and write SG-Multi transactions at the master interface with              |     |

|      | no waiting                                                                             | 94  |

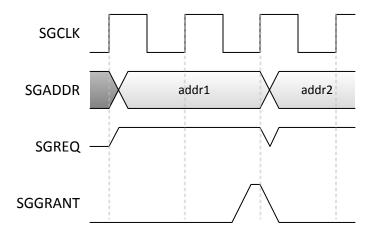

| A.2  | Example of an SG-Multi master interface transaction with a delayed grant               |     |

|      | $\operatorname{signal}$                                                                | 95  |

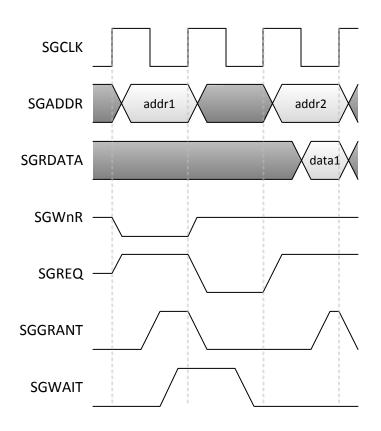

| A.3  | Example of an SG-Multi master interface read transaction with a wait cycle             | 96  |

| A.4  | Example of an SG-Multi master interface write transaction with a wait cycle            | 97  |

| A.5  | Illustration of SG-Multi slave response signalling rules                               | 99  |

| A.6  | Differentiation between incorrect and correct SG-Multi slave error signalling          | 99  |

| B.1  | XML file format for specifying a device's name and friendly name                       | 102 |

| B.2  | XML file format for specifying a device's configurable properties $\ldots$             | 103 |

| B.3  | XML file format for specifying a device's extra signals                                | 104 |

| B.4  | XML file format for specifying a device's executable tool interface $\ldots$ .         | 104 |

| B.5  | XML file format for specifying a master's dependence on a bus adapter $\ .$ .          | 105 |

| B.6  | XML file format for specifying a bus adapter's native signal names                     | 106 |

| B.7 | Example XML file for an AHB-Lite bus adapter module        | 107 |

|-----|------------------------------------------------------------|-----|

| B.8 | Example XML file for an ARM Cortex-M0 master device module | 108 |

# List of Tables

| 1.1 | List and descriptions of SG-Multi core hardware components                     | 4  |

|-----|--------------------------------------------------------------------------------|----|

| 2.1 | List and descriptions of common Avalon-MM signals                              | 15 |

| 2.2 | List and descriptions of common AHB-Lite signals                               | 17 |

| 4.1 | List and descriptions of global SG-Multi signals                               | 34 |

| 4.2 | List and descriptions of SG-Multi master interface signals                     | 35 |

| 4.3 | List and descriptions of SG-Multi slave interface signals                      | 35 |

| 4.4 | List and descriptions of signals internal to SG-Multi's interconnection fabric | 36 |

| 4.5 | State description for master device wrapper bus snooping state machine         | 44 |

| 4.6 | Mask transformation example for arbitration                                    | 47 |

| 5.1 | List and descriptions of components in the SG-Multi Designer abstraction       |    |

|     | $model  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $       | 50 |

| 5.2 | List and descriptions of the types of SG-Multi Designer modules                | 53 |

| 6.1 | Latency comparison of AHB-Lite and SG-Multi systems                            | 60 |

| 6.2 | FPGA-based comparison of AHB-Lite and SG-Multi systems                         | 60 |

| 6.3 | Non-interfering transaction benchmark results                                  | 72 |

| 6.4 | Interfering transaction benchmark results                                      | 73 |

| A.1 | List, types, and descriptions of global SG-Multi signals                       | 90 |

| A.2 | List, directionalities, and descriptions of common SG-Multi interface signals  | 90 |

| A.3 | Values for specifying the size of an SG-Multi transaction                      | 91 |

| A.4 | List, types, and descriptions of SG-Multi master-specific signals              | 91 |

| A.5 | List, types, and descriptions of SG-Multi slave-specific signals               | 92 |

| A.6 | Bit positions used for smaller transactions on wide data busses                            | 93  |

|-----|--------------------------------------------------------------------------------------------|-----|

| B.1 | XML file types supported by SG-Multi Designer                                              | 101 |

| B.2 | Special characters for variable or macro references in an XML file $\ldots$ .              | 101 |

| B.3 | List and descriptions of global variables supported by SG-Multi Designer $% \mathcal{A}$ . | 101 |

| B.4 | List and descriptions of instance parameters supported by SG-Multi Designer                | 102 |

| B.5 | List and descriptions of data types for device properties in an XML file $$ . $$ .         | 103 |

| B.6 | Supported extra signal disconnected state specifiers $\ldots \ldots \ldots \ldots \ldots$  | 104 |

|     |                                                                                            |     |

# Chapter 1

# Introduction

The trend towards increasingly parallel computer systems marks the emergence of new research problems geared towards overcoming the performance-limiting communication bottlenecks, challenges not faced by designers of single-core processors [1]. In the simplest possible design, one would solve the basic logical contention issues and do nothing more, resulting in a system that performs only marginally better than a uniprocessor system and consequently wastes a significant amount of computing resources. Such a system would excel when faced with a set of completely independent tasks but would otherwise falter. On the other hand, one can envision an ideal parallel computing system, in which each processing element operates at its own maximum speed, and no processing element ever encounters communication delays longer than it would if it were the only processing element in the system. If it were possible to construct this type of system in a manner that scales to an arbitrary number of processing elements, the hardware architecture goals of parallel processing research would be achieved. Unfortunately, no such system exists; current research seeks to optimize parallel computing system hardware architectures to improve scalability and limit communication overhead.

As multi-core processors become increasingly pervasive [2], greater emphasis is placed on research towards improving multi-processor system architectures. In order to facilitate this type of research, it is important to be able to rapidly prototype and evaluate proposed architecture designs. Accordingly, a closely-related research area is the construction of tools and platforms capable of assisting with the implementation and verification of parallel computing architectures. These tools and platforms generally attempt to automate and abstract away many of the lower-level details of the system's implementation so as to enable the researchers using them to focus on the higher-level design problems.

The research presented in this thesis contributes meaningfully to both of these areas. The primary goals and motivation are discussed in Section 1.1, and the main research contributions are explicitly outlined in Section 1.2. Section 1.3 describes the organization of the remainder of this thesis.

## **1.1** Goals and Motivation

The primary goal of this work is to create an integrated solution that facilitates the simple and rapid development of both homogeneous and heterogeneous multi-core processors in which cores are interconnected in a virtually arbitrary topology. While the processors built with this solution will be useful in a research setting, a key point of emphasis is ensuring that they are also specifically suitable for industrial applications.

This research contributes to two closely-related research areas: the design of a multicore processor on-chip interconnection architecture and the creation of a tool framework to accelerate the development of complete systems. While an abundance of existing work exists in each of these research areas, none fully addresses the problems solved here; previous work emphasizes theoretical approaches that impose constraints, rendering them unsuitable beyond a research setting. For instance, proposed multi-core interconnection architectures generally require customized processing elements specifically tailored to that specific architecture, the purpose being to enable them to support the new signalling protocols or instructions introduced. Unless a vendor such as ARM adopts the proposed architecture or makes the required customizations, it is impossible for commercial products to be constructed that utilize it. In a similar fashion, existing rapid development tool sets and platforms are designed specifically for the furtherance of research due to their tendency to impose a particular type of underlying hardware on their users. Industry-designed tool sets also exist for the purpose of creating products more appropriate for commercial use, but what ultimately sets this work apart from existing solutions are the emphasis it places on high-level design and the simplicity of the abstraction model it presents to users.

The motivation for this work is to bridge the gap between multi-core architecture research and practical application. This is mainly achieved by avoiding constraints, restrictions, and assumptions that require infeasible modifications to existing widely-used hardware components and by building a solution that is separate from its final hardware implementation. In particular, the solution proposed here fully supports existing industry-produced processor cores and imposes no requirements on the underlying hardware, specifically targeting ASIC (application-specific integrated circuit) implementation but also supporting FPGAs (field-programmable gate arrays) as research and prototyping tools.

## **1.2** Research Contributions

The contribution of this work is two-fold: an on-chip interconnection architecture designed for parallel computing systems and a tool framework for rapidly constructing multi-core processors that make use of this architecture. Sections 1.2.1 and 1.2.2 describe each of these contributions, respectively, in more detail.

## 1.2.1 On-Chip Interconnection Architecture

The first contribution is *SG-Multi*, a <u>s</u>calable, <u>g</u>eneral-purpose <u>multi</u>-core interconnection architecture and signalling protocol. The purpose of SG-Multi is to act as the underlying architecture within a multi-core processor for connecting processing elements to each other and to peripheral devices in a scalable, optimized fashion. The intent is to support both homogeneous and heterogeneous multi-core systems containing individual processor cores of various sizes and performance levels. In keeping with the goal of being suitable for use by industry, SG-Multi is designed specifically for use with existing industry-produced processor cores. Since not all such cores communicate according to the same signalling protocol, the SG-Multi signalling protocol is, to the greatest extent possible, universally adaptable; its design is governed by the notion that it must be possible to create adapter components to convert signals between it and the protocols used by each individual processor core.

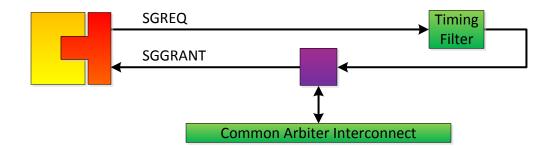

At its core, SG-Multi is a multi-bus system that makes use of slave-side arbitration to allow multiple independent transactions to occur simultaneously. The physical wiring of a master device to a slave device is fixed at implementation time, but no restrictions are imposed on the designer; the set of slaves with which a particular master can communicate is architecturally independent of the sets of slaves with which other masters can communicate. SG-Multi also includes a performance-enhancing feature, known as "snooping," which effectively allows a slave device to service multiple incoming requests at once in some circumstances. While snooping methods are typically utilized for the purposes of maintaining cache coherency [3], SG-Multi allows them to be used for the completion of bus transactions.

A system that implements SG-Multi includes, in addition to the processing elements and peripheral devices themselves, several SG-Multi-specific hardware components. These components are listed and briefly described in Table 1.1. Chapter 3 provides a more detailed overview of SG-Multi.

| Component             | Description                                                      |

|-----------------------|------------------------------------------------------------------|

| Master device wrapper | Implements the core SG-Multi-specific logic needed to connect    |

|                       | a bus master device to an SG-Multi system.                       |

| Slave device wrapper  | Implements the core SG-Multi-specific logic needed to connect    |

|                       | a slave master device to an SG-Multi system.                     |

| Bus adapter           | Required for bus master devices originally designed to use a     |

|                       | signalling protocol other than SG-Multi. This component sits     |

|                       | between the bus master device and the master device wrapper.     |

| Arbiter               | Resolves contention between bus master devices when they at-     |

|                       | tempt to communicate simultaneously with a particular slave.     |

|                       | This component is a sub-unit that exists within the slave device |

|                       | wrapper.                                                         |

Table 1.1: List and descriptions of SG-Multi core hardware components

Devices that support SG-Multi are not required to be aware of the existence of or give any consideration to the actions of other devices in the system. Master devices may be designed under the assumption that they are the only masters in the system, and similarly slave devices need not differentiate between masters. All of the logic required to route transactions correctly and handle contention is incorporated into the master and slave device wrapper components. Consequently, one of the distinguishing features of SG-Multi is its ability to create multi-core processors even out of individual cores not designed or intended for this purpose.

#### 1.2.2 Multi-core Rapid Development Framework

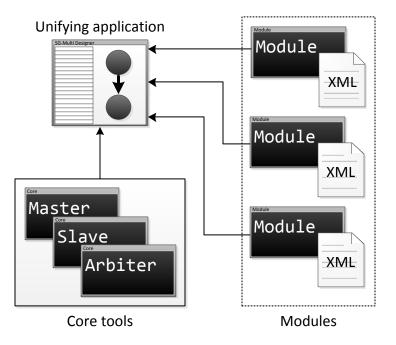

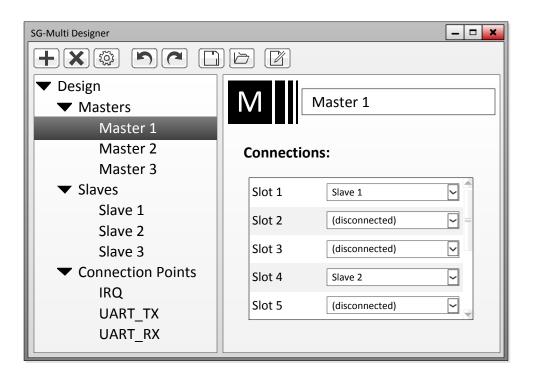

The second contribution is a tool framework, *SG-Multi Designer*, that, given the high-level design of a multi-core processor, produces an SG-Multi implementation of the required interconnection fabric. An abstraction model serves as the basis for the tool framework, the sheer simplicity of which is the primary factor that distinguishes the tool framework from competing solutions. Experimentation will demonstrate the feasibility of providing an extremely simple abstraction model while neither over-simplifying the design process nor reducing the quality of the resulting hardware. At an extremely high level, SG-Multi Designer performs these steps in sequence when a user requests that a specified design be implemented:

- 1. Analyze the input design

- 2. Generate customized versions of each SG-Multi hardware component required to implement the design

- 3. Produce a top-level hardware module that connects all other hardware components according to the topology specified by the input design

SG-Multi Designer is designed to be modular. It consists of one tool for each type of SG-Multi hardware component, as listed in Table 1.1, modules representing specific devices that are available for inclusion in designs, and a unifying tool that controls the entire process and invokes the others. In essence, the lattermost completes steps 1 and 3, and the individual tools and modules each complete a portion of step 2. A fully-working processor is produced by combining the generated interconnection logic with the output of these modules, each of which represents a unit of intellectual property possibly supplied by a third-party. It is assumed that the user is in possession of the requisite intellectual property.

Input and output are human-readable to the greatest extent possible. Input designs are supplied using Extensible Markup Language (XML), and the tools each generate a Verilog file as output. A graphical front-end application serves as the unifying tool and is primarily used to simplify the process of creating XML files containing an input design, and the structure of the XML files is a reflection of the design of the abstraction model.

## **1.3** Thesis Organization

The remainder of this thesis is organized as follows. Chapter 2 provides background information on heterogeneous multi-core processors and their benefits as well as a detailed review of existing related work in the domains of research to which this thesis contributes. In addition to solutions proposed as a result of academic research, the scope of this chapter encompasses industry-produced solutions that are commercially available. Chapter 3 describes SG-Multi at a high level, illustrating how devices in a complete system connect to one another while avoiding discussion of the lower-level details. This is immediately followed by Chapter 4, which houses the technical discussion of SG-Multi. It should be noted that, whether taken individually or as a pair, neither of Chapters 3 and 4 are intended as protocol specifications; rather, they emphasize the architecture as a whole, the design of the individual components, and the rationale that underlies the signalling protocol. Chapter 5 shifts the focus from the architecture to the tool suite, outlining each component separately and demonstrating how they fit together in an integrated package. Chapter 6 describes and shows the results of experiments that were conducted as a means of evaluating SG-Multi and, by extension, SG-Multi Designer. Chapter 7 summarizes the contributions of and the conclusions drawn in this thesis and explores potential future research directions.

This thesis also includes two appendices containing supporting material. Appendix A provides a detailed protocol specification for SG-Multi. It is useful primarily as documentation for building devices that make use of SG-Multi. Appendix B defines the information exchange standards for SG-Multi Designer modules. Its purpose is to provide specifications on the content and format of the XML files that define the interface for communication with an SG-Multi Designer module.

# Chapter 2

# Background

Research related to the advancement of parallel processing technology is abundant. Academic research includes projects designed to accelerate other higher-level research by abstracting away the intricacies involved with building a working multi-core processor. These works facilitate the rapid prototyping of multi-core processors by greatly simplifying the design and implementation process, in many ways offering similar functionality to that of SG-Multi-Designer. The SG-Multi signalling protocol itself lends itself well to comparison with competing industry-supplied interconnection architecture solutions, and SG-Multi Designer can similarly be compared to commercial products that simplify processor and system design.

This chapter begins by defining and differentiating between two types of multi-core processors. It then examines, in sequence, related work in each of the areas outlined previously.

# 2.1 Heterogeneous Multi-core Processors

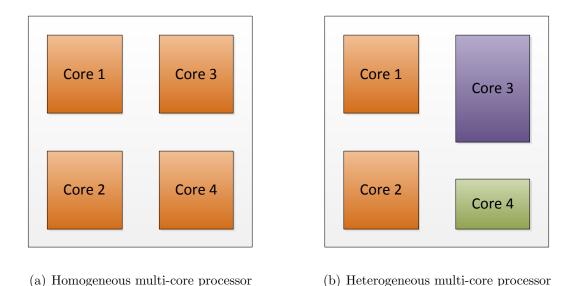

A typical consumer-oriented multi-core processor, such as Intel's Core [4] processor family, is *homogeneous*. A defining characteristic of such a processor is that all of the individual cores are identical in design and performance [5]. By contrast, a *heterogeneous* multi-core processor contains individual cores that may vary in characteristics such as size, instruction set support, raw computational power, and special-purpose hardware optimizations. Figure 2.1 illustrates the difference between them.

Figure 2.1: Illustration of the two different types of multi-core processors

The development and advancement of heterogeneous multi-core processors is motivated by the desire to improve efficiency and reduce power consumption. One approach towards achieving this involves integrating highly specialized processing elements, often called *accelerators*, into the design of the processor. Each accelerator is optimized to perform a small set of tasks more quickly and efficiently than a general-purpose processing element could, and accordingly the software must be designed to make use of each accelerator for its intended purpose [6]. As a result, accelerators are dependent on the existence of a general-purpose processor. The integration of accelerators allows heterogeneous multi-core processors to be custom-tailored in ways that make the results unsuitable for generalpurpose computations but that greatly benefit the intended area of use. Heterogeneous multi-core processors designed in this fashion have applications in, for example, the areas of digital signal processing [7] and wireless communications [8].

Another approach stresses power consumption over performance, the aim being to reduce the system's overall power consumption while ensuring the performance penalty is as negligible as possible. This approach combines more powerful general-purpose processor cores with a less powerful—and less power-hungry—general-purpose processor core, where all the cores support the same instruction set [9]. The assignment of tasks to processor cores happens on-the-fly. In the absence of tasks that demand high amounts of computational power, the more powerful cores are disabled, leaving functions such as those related to system management to be executed on the less powerful core. This type of heterogeneous multi-core processor has mainly seen applications in the design of processors destined for consumer mobile devices, such as NVIDIA's Tegra [10] series of mobile application processors.

## 2.2 Rapid Prototyping of Multi-core Processors

Rapid prototyping platforms greatly accelerate the process of constructing and implementing a working version of a multi-core processor. Compared to pure software simulation of a logic design, it has been shown that a rapid prototyping platform can realistically model the design and achieve 200-times speedup [11]. From a design process standpoint, no concrete figures are available as to the amount of time saved, but anecdotal evidence suggests it is possible to reduce bring-up and verification time from months to weeks [12].

Research-oriented platforms are designed to support experimentation with novel architectures and applications while also offering the performance benefits of rapid prototyping. Instead of relying on software simulators or fabricating real hardware, researchers can implement their designs on these reconfigurable platforms. Whereas commercial-grade platforms emphasize design verification and can therefore be used for general-purpose designs including those not related to multi-core processors, research-oriented platforms tend to be more special-purpose in nature. The rapid prototyping platforms presented in this section are all either designed for multi-core research or offered by industry.

A common feature of many rapid prototyping platforms is their reliance, at least in part, on FPGAs. A particularly well-known rapid prototyping platform, known as Research Accelerator for Multiple Processors (RAMP) [13], is entirely based on FPGAs. RAMP is designed to emulate multiprocessor systems in a cycle-accurate manner. It offers its own description language—RAMP Description Language (RDL)—as a way of recording a system's design such that it can be reconstructed in a way that provides cycle-for-cycle performance equivalence with the original system. In keeping with its focus on emulation, RAMP supports modeling different clock domains by allowing, on a per-component basis, multiple physical clock cycles to correspond to a single logical clock cycle. For instance, a particular component may be clocked such that each physical clock cycle advances its emulated clock by one cycle, whereas a different component may require two or three physical clock cycles to advance its emulated clock by a single cycle. As with SG-Multi, RAMP supports the use of existing industry-supplied processor cores.

A more specialized rapid prototyping platform is the Flexible Architecture for Research Machine (FARM) [14]. Existing prototype systems that use RAMP, such as RAMP White [13] and RAMP Blue [15], are homogeneous multi-core processors, though RAMP does not specifically impose this requirement. FARM, on the other hand, is designed with heterogeneous multi-core processor applications in mind and, also unlike RAMP, does not implement all hardware components in FPGAs. The goal of FARM is to prototype multiprocessor systems consisting of multiple high-performance general-purpose processors connected to an FPGA that implements a hardware accelerator, where the FPGA includes a cache and participates in the same system-wide cache coherency protocols as do the general-purpose processors. FARM is less flexible than RAMP in that it specifies the overall topology of the system and limits reconfigurability to the FPGA part of the system, keeping the rest fixed. System performance would also be less indicative of that of real hardware, since timing behaviour is quite different when real processors interact with an FPGA than when real processors interact with a real accelerator.

A somewhat older rapid prototyping platform, which to a certain extent provides the basis for FARM [14], is the Rapid Prototyping Engine for Multiprocessors (RPM) [16]. Whereas both RAMP and FARM make use of FPGAs for implementing at least some of the processors in the system, the defining characteristic of RPM is that the processors are real off-the-shelf hardware components while the FPGAs are used for the caches, memory controllers, and other support elements. RPM fixes the processors and interconnection topology while allowing FPGA-controlled components to be customized; it is not a truly general-purpose rapid prototyping platform, but it does allow basic experimentation with, for example, different memory hierarchy configurations.

The rapid prototyping platforms described thus far are useful because they greatly accelerate the process of constructing a multiprocessor system that can be used for research activities such as experimentation. They do not, however, produce production-ready systems suitable for chip fabrication. Cadence makes available an FPGA-based commercial rapid prototyping platform designed specifically for industrial use [17]. While such a system could theoretically be used for research, it is intended to accelerate the bring-up process for new system-on-chip designs that will ultimately be fabricated and sold commercially. Cadence provides a complete and comprehensive solution that encompasses all steps occurring after the chip's logic has been designed: compilation, partitioning across multiple FPGAs, insertion and configuration of debugging probes, and execution. Unlike the previouslyintroduced rapid prototyping platforms, Cadence's solution is not specifically optimized for multi-core processor design and can therefore be used in a more general-purpose fashion. However, it targets the verification portion of the design process, whereas the other rapid prototyping platforms target the entire process, from high-level design to verification.

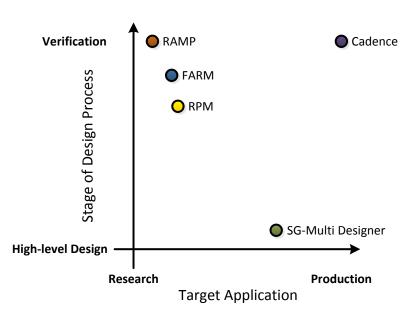

In the rapid prototyping platform space, SG-Multi Designer fits between the research solutions (RAMP, FARM, and RPM) and the commercial one (Cadence), as represented visually in Figure 2.2. It produces complete systems that, when connected to processor cores and peripheral devices, can be downloaded to FPGAs and used either for research or for design verification. It is also the only of the systems discussed that focuses on the "high-level design" stage, as opposed to the "verification" stage, of the hardware design process.

Designs that make use of RAMP, FARM, or RPM are custom-tailored to those specific systems and require the hardware upon which those systems are built, whereas SG-Multi Designer imposes no hardware requirements. Similarly, unlike Cadence's platform, SG-Multi is not tied to a specific set of hardware and software tools; rather, users are free to select hardware and software vendors of their choice when implementing their SG-Multi system.

## 2.3 Existing Related Interconnection Architectures

Several existing interconnection architectures share design features with SG-Multi. They vary in their intended uses, particularly in terms of flexibility, scalability, and suitability for use as the basis of a multi-core processor. SG-Multi is motivated by existing signalling protocols but still contains features to distinguish itself; some of the most comparable existing work, all of which comes from industry, includes Altera's Avalon-MM, ARM's AHB-Lite, and IBM's CoreConnect. After discussing networks-on-chip, a modern but

Figure 2.2: Map of application domains of various rapid prototyping platforms

indirectly related interconnection architecture paradigm, this section examines each of these interconnection architectures in sequence.

#### 2.3.1 Networks-on-Chip

Unlike traditional system interconnection architectures which emphasize point-to-point connections between devices, a *network-on-chip* (NoC) shifts the interconnection architecture paradigm towards that of distributed, networked systems. The distinguishing characteristic of an NoC is that it employs packet-switching techniques to move data between components [18]. NoC-type architectures fall into a tangential but unrelated research area and strive to bring the scalability and performance characteristics inherent in large networked systems to the level of a single chip. Research progression typically involves overcoming problems related to implementation complexity of networking protocols and algorithms, which leads to power and performance penalties.

NoCs currently have a wide range of applications, many of which are research-oriented

and target FPGA devices. For example, an NoC exploration study is documented in [19], with specific emphasis on FPGAs. There are, however, also commercial NoC applications; Altera's latest system construction tool, Qsys, is based on a NoC-type architecture [20]. SG-Multi more closely resembles a traditional system interconnection architecture than it does an NoC and therefore is not faced with the same research challenges that an NoC designer must overcome.

#### 2.3.2 Altera Avalon

Altera makes available several different variants of its Avalon interface specifications, including Avalon-ST for streaming and Avalon-MM for typical master/slave memory-mapped configurations [21]. Because SG-Multi is based on memory mapping, the latter is more directly relevant to it.

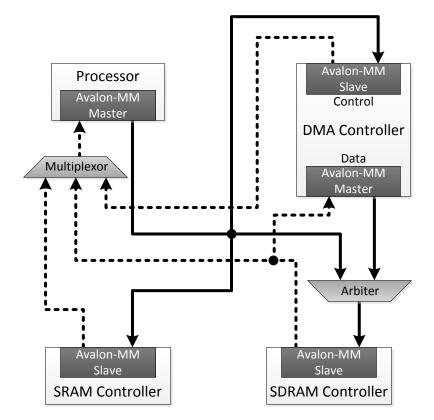

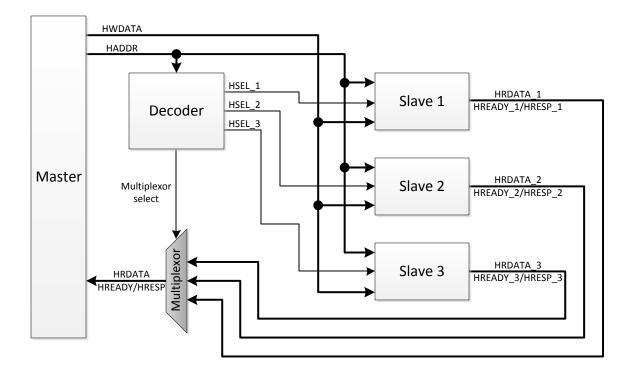

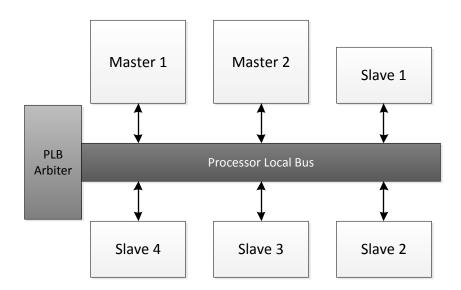

Avalon-MM's interconnection architecture has traditionally been based on a design similar to that of SG-Multi, in which independent transactions can proceed simultaneously. This performance-enhancing ability distinguishes Avalon-MM from single-bus architectures with centralized arbitration schemes, which permit only a single transaction at any given time. Support for simultaneous transactions is achieved by connecting each master directly to each slave, using multiplexors to ensure signals are routed between the correct devices, and performing slave-level arbitration instead of system-level arbitration [22]. Figure 2.3, adapted from [22], provides a simple example of a two-master system based on Avalon-MM; while the architecture supports the use of a tri-state bridge for communication with off-chip slave devices, only the on-chip interconnection portion is shown. Further details can be found in [21] and [22]. Because arbiters are inserted only as needed at the slave ports, it is possible for the processor to communicate with SRAM while the DMA controller communicates simultaneously with SDRAM.

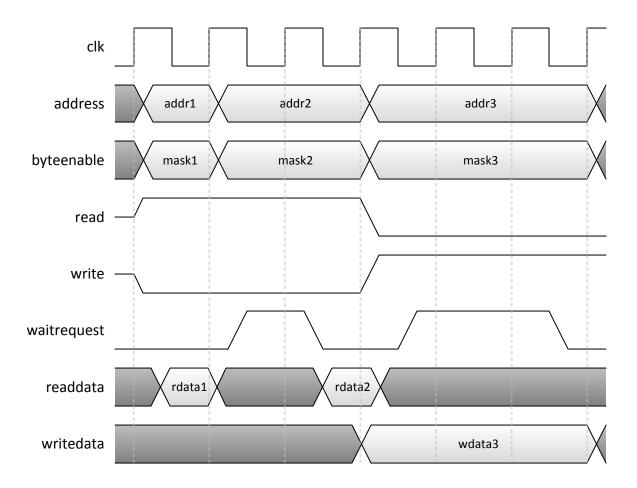

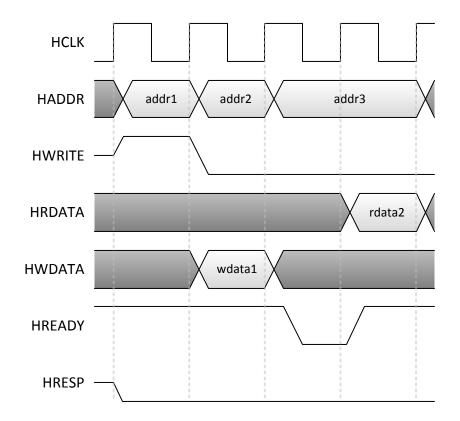

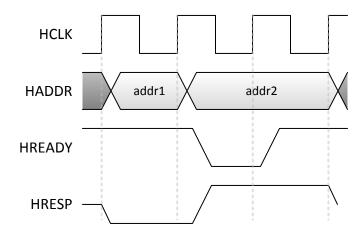

Table 2.1 lists some of the most common Avalon-MM signals used in basic transactions [21]. Basic transactions in Avalon-MM take exactly one clock cycle each, but slave devices not capable of responding to requests in the same cycle as they are issued have the ability to extend the transaction to multiple cycles. This can be accomplished by setting a fixed wait time as a property of the slave or by using the **waitrequest** signal, which allows for a variable wait time. Pipelined transactions are also supported, causing each transaction to complete in at least two cycles and allowing each slave to have a variable

Figure 2.3: Two-master example of a system that uses Avalon-MM

number of outstanding transaction requests (the actual number is a property of an individual slave). A pipelined transaction is effectively split into two distinct phases: *address phase*, the first phase during which address and control information is supplied to the slave, and *data phase*, the second phase during which the slave processes the request. In pipelined transactions, both waitrequest and readdatavalid are used to indicate whether or not the slave has finished its processing, the former being used as in the unpipelined case to indicate delays and the latter being used specifically for read transactions [21].

Figure 2.4 shows an example of a set of simple unpipelined Avalon-MM transactions. The waitrequest signal is the only means by which a slave can extend a transaction beyond a single clock cycle, and a slave wishing to assert it is required to do so prior to

| Signal Name   | Description                                                               |

|---------------|---------------------------------------------------------------------------|

| clk           | Clock signal used to drive transactions                                   |

| address       | Memory address of interest, supplied by master                            |

| byteenable    | Mask to specify which of the bytes within the data bus are used in        |

|               | the current transaction                                                   |

| read          | Specifies that the current transaction request is for the slave to read   |

|               | data and supply it to the master                                          |

| write         | Specifies that the current transaction request is for the slave to accept |

|               | data from the master                                                      |

| readdata      | Data resulting from a read operation, supplied by slave                   |

| writedata     | Data to be written during a write operation, supplied by master           |

| waitrequest   | Indicates whether or not the slave needs more cycles to complete the      |

|               | current transaction                                                       |

| readdatavalid | For slaves that support pipelined transactions, indicates whether or      |

|               | not the slave has completed a read transaction                            |

Table 2.1: List and descriptions of common Avalon-MM signals

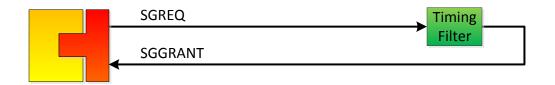

the end of the clock cycle in which it receives its original transaction request [21].