# Multipath Miller Compensation for Switched-Capacitor Systems

by

Zhao Li

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2011

$\bigodot$ Zhao Li 2011

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

A hybrid operational amplifier compensation technique using Miller and multipath compensation is presented for multi-stage amplifier designs. Unconditional stability is achieved by the means of pole-zero cancellation where left-half zeros cancel out the nondominant poles of the operational amplifier. The compensation technique is stable over process, temperature, and voltage variations.

Compared to conventional Miller-compensation, the proposed compensation technique exhibits improved settling response for operational amplifiers with the same gain, bandwidth, power, and area. For the same settling time, the proposed compensation technique will require less area and consume less power than conventional Miller-compensation. Furthermore, the proposed technique exhibits improved output slew rate and lower noise over the conventional Miller-compensation technique.

Two-stage operational amplifiers were designed in a  $0.18 \ \mu m$  CMOS process using the proposed technique and conventional Miller-compensated technique. The design procedure for the two-stage amplifier is applicable for higher-order amplifier designs. The amplifiers were incorporated into a switched-capacitor oscillator where the oscillation harmonics are dependent on the settling behaviour of the op amps. The superior settling response of the proposed compensation technique results in a improved output waveform from the oscillator.

#### Acknowledgements

I would like to thank all the people who helped me along the way. First, I would like to thank my supervisor, David Nairn, for providing advice, encouragement, and most of all patience. I am deeply grateful for the academic freedom he afforded me, but also for reining me in whenever I strayed too far from the objective.

I would also like to thank the rest of the group including Noman, Jason, and Adam. It was a pleasure discussing various circuit and non-circuit topics with you.

Many people outside the group have helped me through my Master's. I would like acknowledge my friends at the university for keeping me same over the last two years. Special thanks to Melissa for her help with editing this dissertation.

Finally, I am indebted to my parents for their unconditional support for my endeavours. This thesis would not have been possible without them.

#### Dedication

To the two most important women in my life: my mother for putting up with all my antics and my paternal grandmother for raising me.

## Contents

| Li       | st of | Tables x                          | vii |

|----------|-------|-----------------------------------|-----|

| Li       | st of | Figures                           | xiv |

| 1        | Intr  | oduction                          | 1   |

|          | 1.1   | Outline                           | 2   |

| <b>2</b> | Bac   | ground Information                | 3   |

|          | 2.1   | Amplifier Requirements            | 4   |

|          |       | 2.1.1 DC Gain                     | 5   |

|          |       | 2.1.2 Bandwidth                   | 6   |

|          | 2.2   | Stability                         | 8   |

|          |       | 2.2.1 Nyquist Stability Criterion | 8   |

|          |       | 2.2.2 Phase Margin                | 10  |

|          | 2.3   | Single-Stage Op Amps              | 10  |

|          | 2.4   | Two-Stage Op Amps                 | 14  |

|   |     | 2.4.1   | Miller Compensation                                                                            | 16 |

|---|-----|---------|------------------------------------------------------------------------------------------------|----|

|   | 2.5 | Multi-  | Stage Op Amps                                                                                  | 19 |

|   |     | 2.5.1   | Nested-Miller Compensation                                                                     | 20 |

|   |     | 2.5.2   | Feedforward Compensation                                                                       | 23 |

|   | 2.6 | Discus  | sion $\ldots$ | 28 |

| 3 | Mu  | ltipath | Miller Compensation                                                                            | 29 |

|   | 3.1 | Two-S   | tage Op-Amp                                                                                    | 30 |

|   |     | 3.1.1   | Miller Capacitor with Lead Compensation                                                        | 32 |

|   | 3.2 | Multi-  | Stage Op-Amps                                                                                  | 34 |

|   | 3.3 | Propo   | sed Design                                                                                     | 35 |

|   | 3.4 | Comp    | arison with Conventional Two-Stage Miller-Compensated Op Amps .                                | 37 |

|   |     | 3.4.1   | Settling Response                                                                              | 37 |

|   |     | 3.4.2   | Noise                                                                                          | 40 |

|   |     | 3.4.3   | Output Slew Rate                                                                               | 42 |

|   | 3.5 | Summ    | ary                                                                                            | 45 |

| 4 | Sys | tem-Le  | evel Design                                                                                    | 47 |

|   | 4.1 | Switch  | ned-Capacitor Sinusoidal Oscillator Design                                                     | 48 |

|   |     | 4.1.1   | Architecture                                                                                   | 49 |

|   |     | 4.1.2   | Analysis                                                                                       | 52 |

|   |      | 4.1.3   | Effects of Finite Op-Amp Gain and Bandwidth 5 | 4 |

|---|------|---------|-----------------------------------------------|---|

|   |      | 4.1.4   | Choice of Filter Coefficients                 | 6 |

|   |      | 4.1.5   | Start-Up Circuit                              | 7 |

|   | 4.2  | Matla   | b Simulation Results                          | 0 |

|   | 4.3  | Summ    | ary                                           | 3 |

| 5 | Cire | cuit De | esign 6                                       | 5 |

|   | 5.1  | Switch  | ned-Capacitor Oscillator Design               | 5 |

|   |      | 5.1.1   | Capacitor Sizing                              | 6 |

|   |      | 5.1.2   | Switch Sizing                                 | 8 |

|   |      | 5.1.3   | Complete Circuit Implementation               | 1 |

|   | 5.2  | Op Ar   | mp Design                                     | 2 |

|   |      | 5.2.1   | Gain                                          | 3 |

|   |      | 5.2.2   | Bandwidth                                     | 5 |

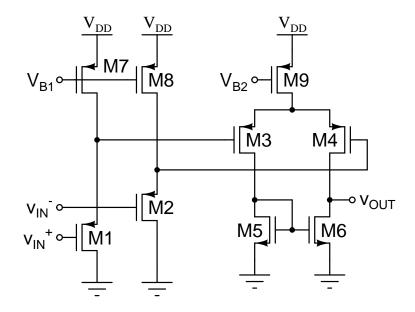

|   |      | 5.2.3   | Topology                                      | 6 |

|   |      | 5.2.4   | Op Amp Implementation                         | 7 |

|   |      | 5.2.5   | Positive Feedback (Neutralizing) Capacitors   | 8 |

|   |      | 5.2.6   | Slew Rate                                     | 0 |

|   |      | 5.2.7   | Output Common-Mode Feedback                   | 1 |

|   |      | 5.2.8   | Input Common-Mode Feedback                    | 3 |

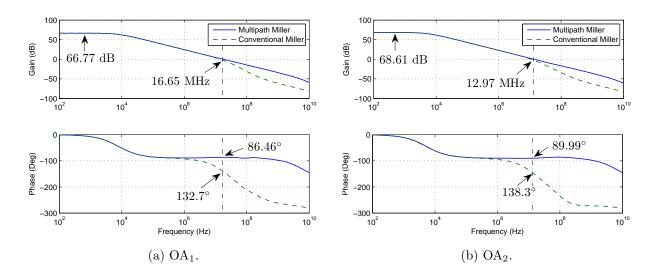

|   |      | 5.2.9   | Simulation Results                            | 5 |

|   | 5.3  | Ancill | ary Circuits                        | 86  |

|---|------|--------|-------------------------------------|-----|

|   |      | 5.3.1  | Dynamic Comparator                  | 86  |

|   |      | 5.3.2  | Comparator Sampling Network         | 88  |

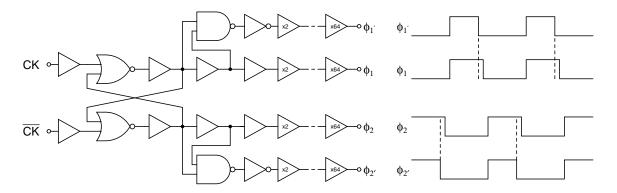

|   |      | 5.3.3  | Non-Overlapping Clock Generator     | 90  |

|   |      | 5.3.4  | Output Buffer                       | 90  |

|   |      | 5.3.5  | Bias Circuit                        | 93  |

|   | 5.4  | System | n Simulation                        | 95  |

| 6 | Test | t Resu | lts and Improvements                | 99  |

|   | 6.1  | Test F | Results                             | 99  |

|   |      | 6.1.1  | Layout                              | 99  |

|   |      | 6.1.2  | Test Board                          | 102 |

|   |      | 6.1.3  | Results                             | 102 |

|   | 6.2  | Impro  | vements                             | 103 |

|   |      | 6.2.1  | Electrostatic Discharge and Latchup | 104 |

|   |      | 6.2.2  | Decoupling Capacitors               | 104 |

|   |      | 6.2.3  | Analog Multiplexers                 | 105 |

|   |      | 6.2.4  | Power and Area                      | 105 |

| 7 | Con  | clusio | ns                                  | 111 |

|   | 7.1  | Contri | ibutions                            | 112 |

|   | 7.2  | Future | e Work                              | 113 |

| A]           | PPE   | NDICI   | ES                                             | 115 |

|--------------|-------|---------|------------------------------------------------|-----|

| A            | Der   | ivatior | of Multipath Miller Transfer Function          | 117 |

| в            | Der   | ivatior | of Effective Gain Equation                     | 121 |

| $\mathbf{C}$ | Der   | ivatior | n of Output Noise                              | 123 |

|              | C.1   | Two-S   | tage Conventional Miller-Compensated Op Amps   | 123 |

|              |       | C.1.1   | Two-Stage Multipath Miller-Compensated Op Amps | 126 |

| Re           | efere | nces    |                                                | 129 |

# List of Tables

| 4.1 | Phase error due to finite op amp gain-bandwidth product   | 55  |

|-----|-----------------------------------------------------------|-----|

| 5.1 | Switched-capacitor oscillator specifications              | 66  |

| 5.2 | Capacitance of capacitors in Fig. 4.7                     | 68  |

| 5.3 | CMFB loop gain simulation results                         | 83  |

| 5.4 | $OA_1$ and $OA_2$ transistor dimensions and bias currents | 86  |

| 5.5 | Miller and load capacitor values for $OA_1$ and $OA_2$    | 86  |

| 5.6 | Output buffer transistor dimensions and bias currents     | 92  |

| 6.1 | Expected and measured bias voltages                       | 103 |

| 6.2 | Expected and measured analog current consumption.         | 103 |

# List of Figures

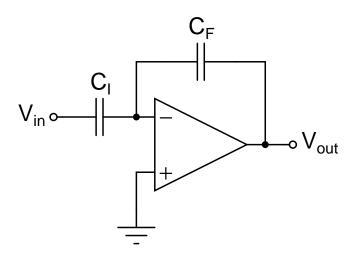

| 2.1  | An inverting amplifier configuration commonly found in integrated circuits.                              | 4  |

|------|----------------------------------------------------------------------------------------------------------|----|

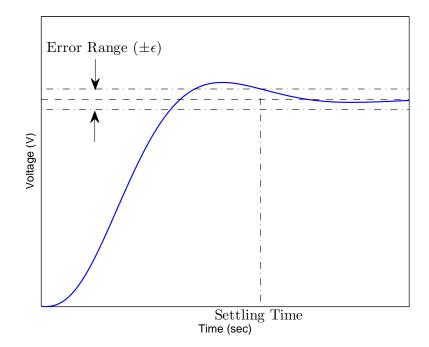

| 2.2  | Step response characteristics of a linear system.                                                        | 6  |

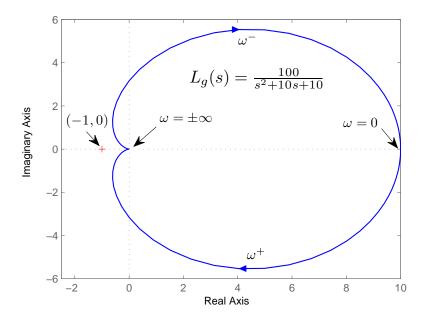

| 2.3  | An example Nyquist plot. The system is stable as there are no encirclements at the point $(-1,0)$ .      | 9  |

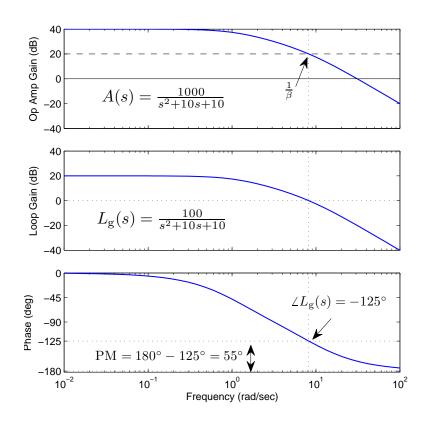

| 2.4  | An example phase margin measurement. The feedback factor, $\beta$ , is 0.1 and is frequency independent. | 11 |

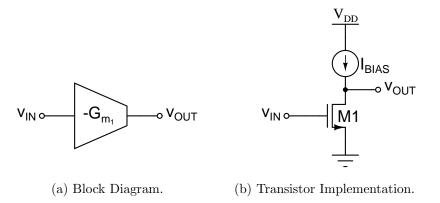

| 2.5  | Block diagram and simple transistor implementation of a single-stage op amp.                             | 12 |

| 2.6  | Small-signal model of a single-stage op amp                                                              | 12 |

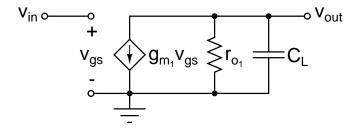

| 2.7  | Settling behaviour of a first-order system                                                               | 13 |

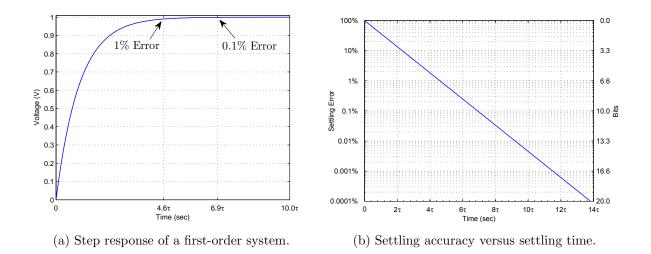

| 2.8  | Block diagram and simple transistor implementation of a single-stage op amp.                             | 14 |

| 2.9  | Small-signal model of a two-stage op amp                                                                 | 15 |

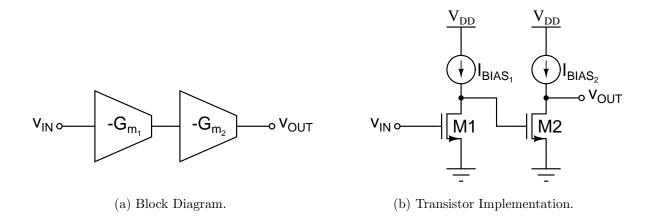

| 2.10 | Block diagram and simple transistor implementation of a single-stage op amp.                             | 16 |

| 2.11 | Small-signal model of a two-stage miller-compensated op amp                                              | 17 |

| 2.12 | Settling behaviour of a second-order system. The error range is 1% ( $\epsilon = 0.01$ ).                | 19 |

| 2.13 | Block diagrams of three-stage nested-miller compensated op amps                                          | 20 |

| 2.14 | Small-signal model of a three-stage nested miller-compensated op amp. $\ . \ .$                                                                                 | 22 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.15 | Settling behaviour of a third-order low-pass butter<br>worth filter. $\omega_0=1~{\rm rad/s}$                                                                   |    |

|      | and $\epsilon = 0.01$                                                                                                                                           | 23 |

| 2.16 | Block diagram and simple transistor implementation of two-stage feedfor-                                                                                        |    |

|      | ward op amp                                                                                                                                                     | 24 |

| 2.17 | Small-signal model of a two-stage feedforward-compensated op amp                                                                                                | 26 |

| 2.18 | Block diagram of a n-stage feedforward op amp                                                                                                                   | 26 |

| 3.1  | Block diagram and simple transistor implementation of two-stage miller with                                                                                     |    |

|      | feedforward-compensated op amp                                                                                                                                  | 30 |

| 3.2  | Small-signal model of a two-stage miller with feedforward-compensated op                                                                                        |    |

|      | amp                                                                                                                                                             | 31 |

| 3.3  | Block digram of a two-stage multipath Miller-compensated op amp with                                                                                            |    |

|      | lead compensation.                                                                                                                                              | 33 |

| 3.4  | Block diagrams of multi-stage miller with feedforward compensated op amps.                                                                                      | 35 |

| 3.5  | A transistor implementation of a two-stage miller and feedforward compen-                                                                                       |    |

|      | sated op amp with lead compensation.                                                                                                                            | 36 |

| 3.6  | Performance improvement as a function of phase margin. $A_0 = 80 \text{ dB}$ and                                                                                |    |

|      | $\epsilon = 0.01 \ (1\%). \ldots \ldots$ | 38 |

| 3.7  | Power and settling time trade-off for two-stage conventional Miller-compensated                                                                                 | l  |

|      | op amps                                                                                                                                                         | 39 |

| 3.8  | Circuit diagram of a two-stage conventional Miller-compensated op amp. $% \mathcal{A}$ .                                                                        | 41 |

| 3.9  | Circuit diagram of a two-stage multipath Miller-compensated op amp                                                                                              | 42 |

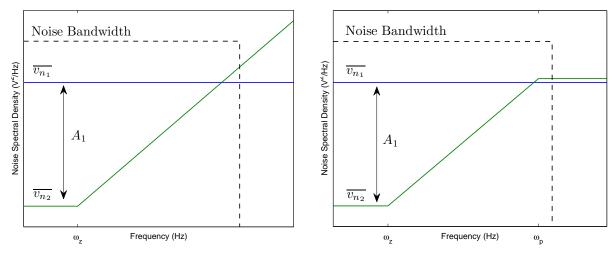

| 3.10 | Approximate input-referred noise spectral density of two-stage op amps in feedback                                                        | 43 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

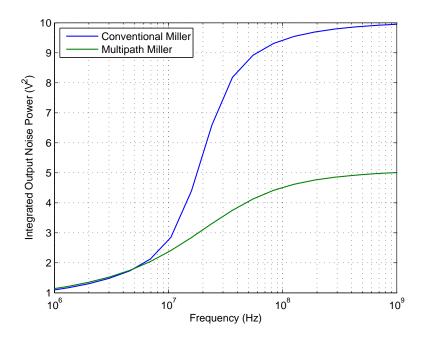

| 3.11 | Simulated integrated output noise power of two two-stage op amps. $\ldots$                                                                | 44 |

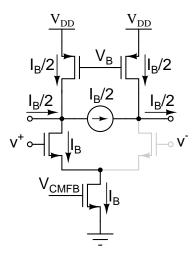

| 3.12 | A two-stage conventional Miller-compensated op amp exhibiting slew-limited behaviour.                                                     | 44 |

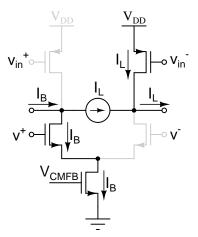

| 3.13 | A two-stage multipath Miller-compensated op amp exhibiting slew-limited behaviour.                                                        | 45 |

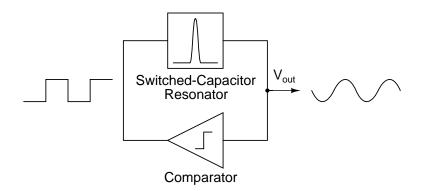

| 4.1  | Conceptual diagram of a switched-capacitor sinusoidal oscillator                                                                          | 49 |

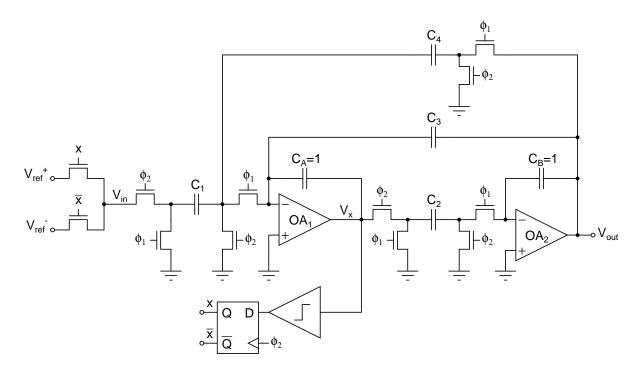

| 4.2  | A switched-capacitor sinusoidal oscillator.                                                                                               | 51 |

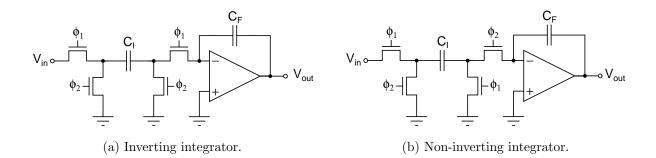

| 4.3  | Two parasitic-insensitive switched-capacitor integrator configurations. Output is sampled at the end of $\phi_1$ .                        | 51 |

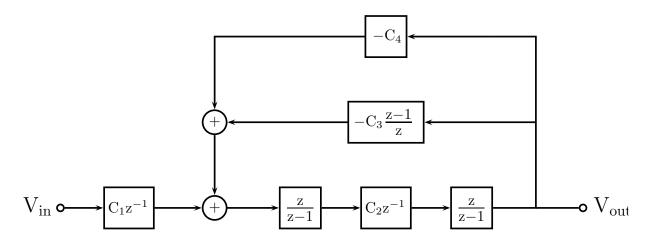

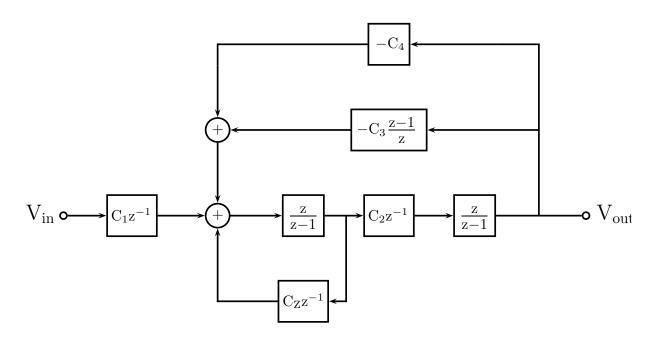

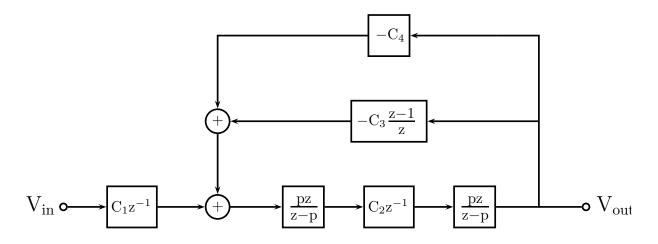

| 4.4  | Signal flow graph of the switched-capacitor resonator in Fig. 4.2                                                                         | 52 |

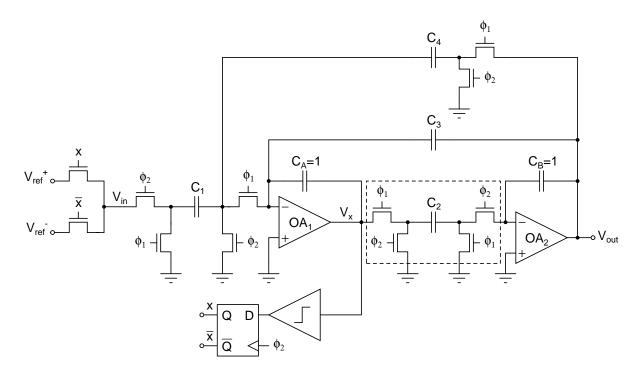

| 4.5  | A switched-capacitor sinusoidal oscillator with reduced sensitivity to finite<br>op amp bandwidth                                         | 53 |

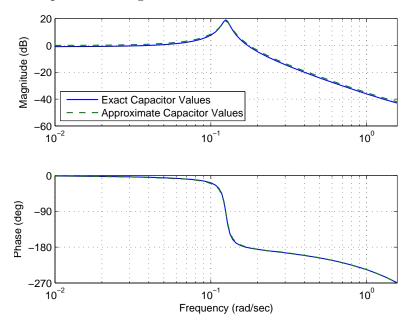

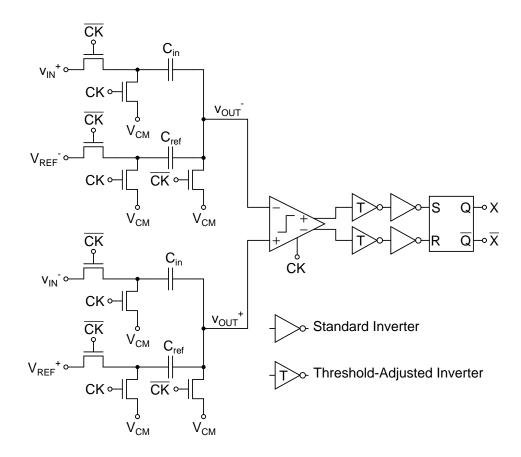

| 4.6  | Frequency response (normalized to $\pi/2$ ) of two resonators. The solid line represents Eq. 4.15 and the dashed line represents Eq. 4.16 | 57 |

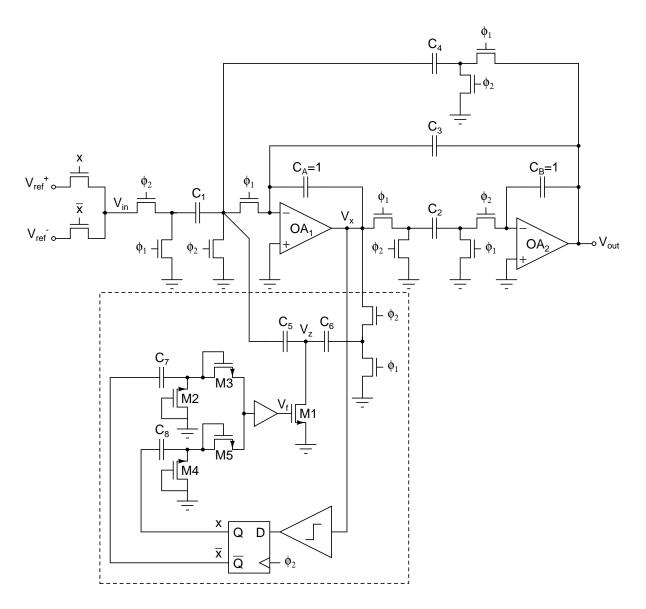

| 4.7  | A switched-capacitor sinusoidal oscillator with start-up circuitry                                                                        | 58 |

| 4.8  | Signal flow graph of the switched-capacitor resonator with start-up circuit.                                                              | 59 |

| 4.9  | Signal flow graph of the switched-capacitor resonator with non-ideal op amps.                                                             | 61 |

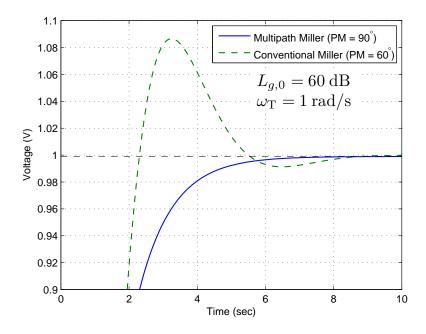

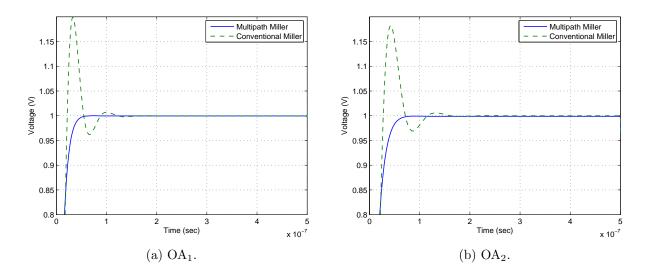

| 4.10 | Step response of multipath Miller ( $PM = 90^{\circ}$ ) and conventional Miller $PM = 60^{\circ}$ op amps.                                | 61 |

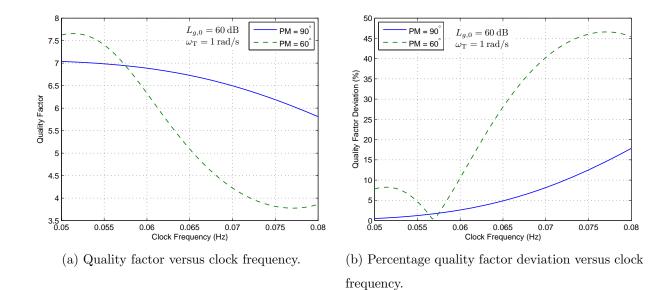

| 4.11 | Matlab simulations of a switched-capacitor resonator's quality factor as the                                                                  |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | clock frequency is varied                                                                                                                     | 63 |

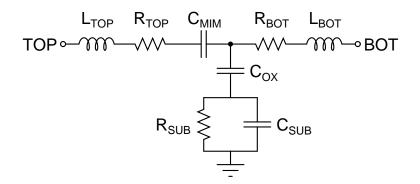

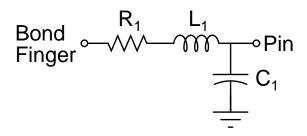

| 5.1  | Equivalent circuit model for the MIM capacitor without shield structure                                                                       | 67 |

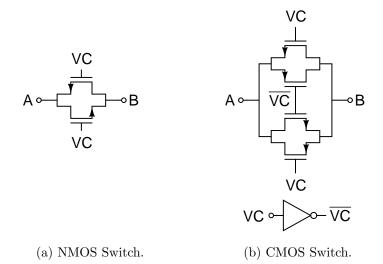

| 5.2  | Schematic of NMOS and CMOS switches                                                                                                           | 69 |

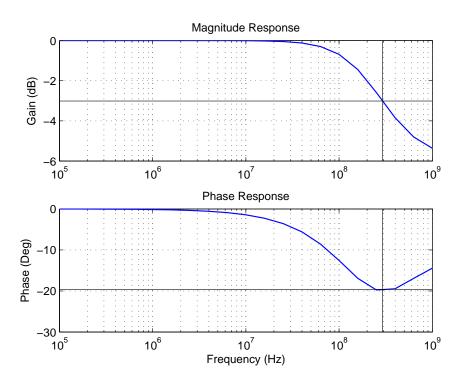

| 5.3  | Frequency response of NMOS switch                                                                                                             | 70 |

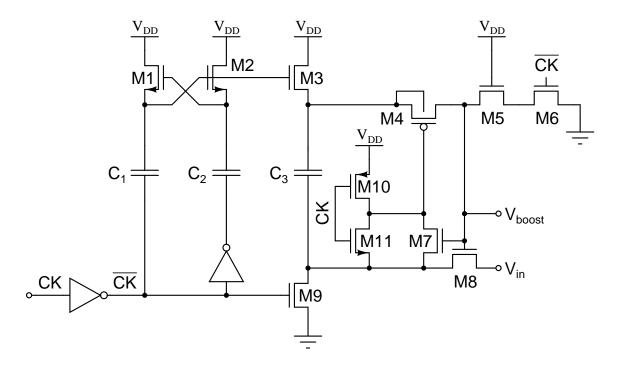

| 5.4  | Schematic of clock bootstrap circuit.                                                                                                         | 71 |

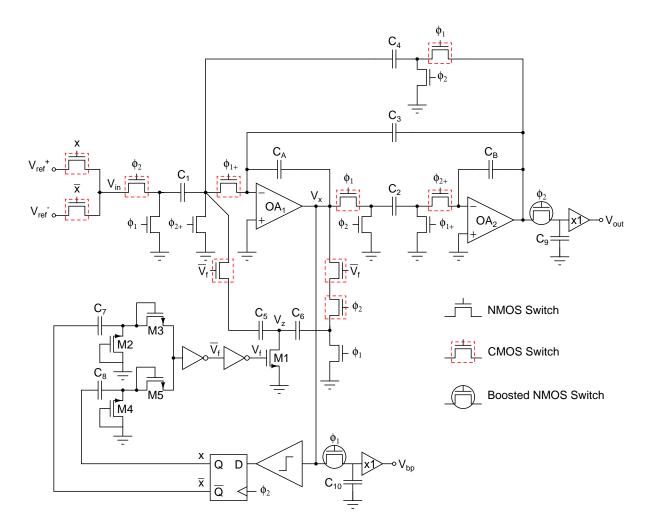

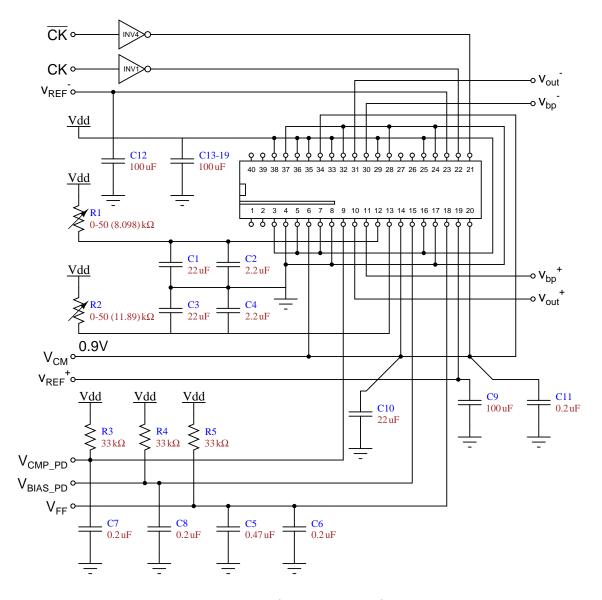

| 5.5  | Complete schematic of switched-capacitor oscillator. The actual circuit is completely differential.                                           | 73 |

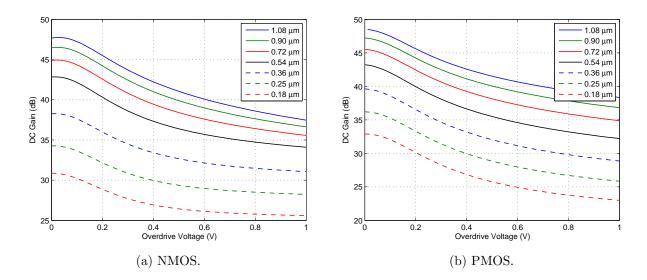

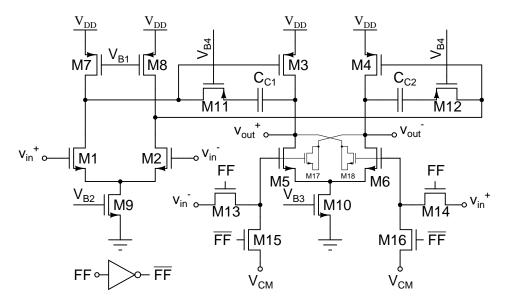

| 5.6  | DC gain versus overdrive voltage for different transistor lengths                                                                             | 75 |

| 5.7  | Gain bandwidth product versus overdrive voltage for different transistor lengths.                                                             | 76 |

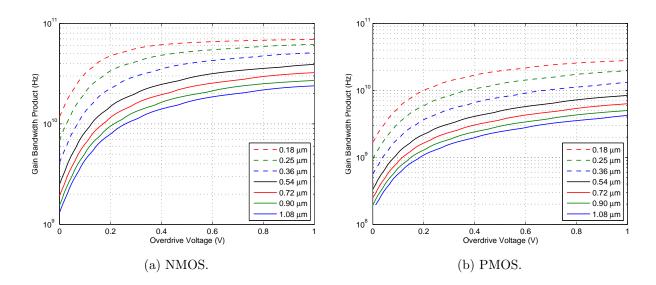

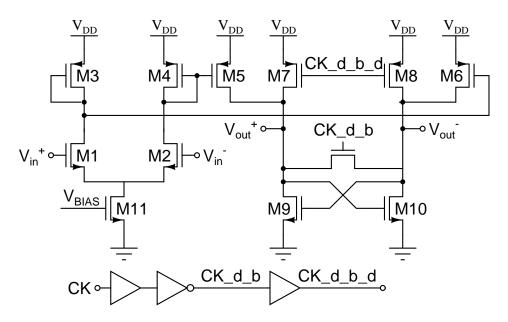

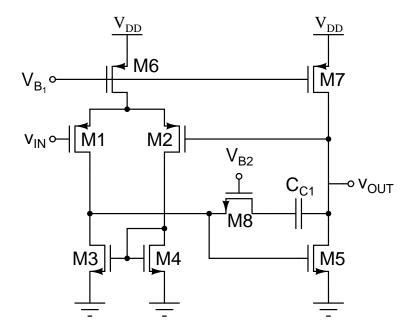

| 5.8  | Schematic of the two-stage op amp used in this design.                                                                                        | 78 |

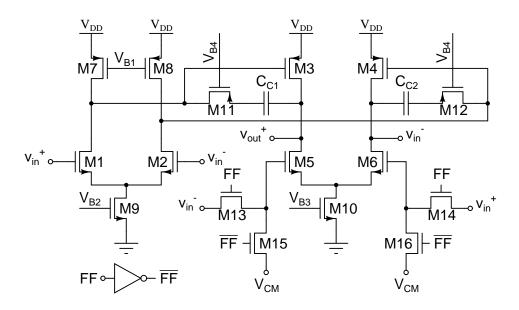

| 5.9  | Schematic of op amp with neutralizing capacitors                                                                                              | 80 |

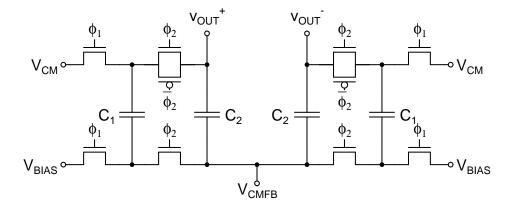

| 5.10 | Switched-capacitor common mode feedback circuit.                                                                                              | 82 |

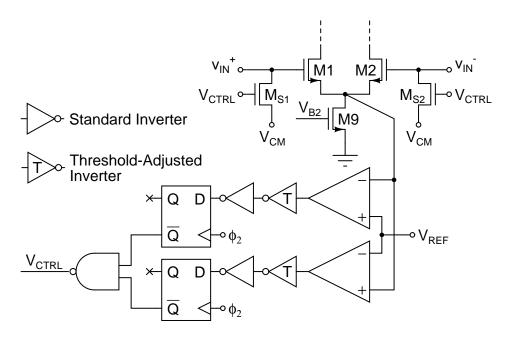

| 5.11 | Technique for setting input common mode                                                                                                       | 84 |

| 5.12 | Schematic of the op amp in the input CMFB circuit (Fig. 5.11)                                                                                 | 85 |

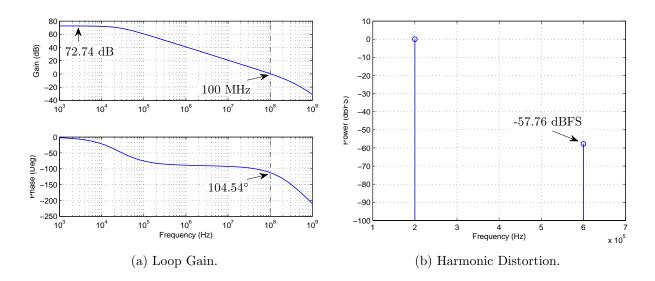

| 5.13 | Loop gain of $OA_1$ and $OA_2$                                                                                                                | 87 |

| 5.14 | Transient response of $OA_1$ and $OA_2$                                                                                                       | 87 |

| 5.15 | Dynamic comparator schematic.                                                                                                                 | 88 |

| 5.16 | Dynamic comparator sampling network. All switches are minimum sized $(W = 2 \times 0.42 \ \mu\text{m}, L = 0.18 \ \mu\text{m})$ CMOS switches | 89 |

| 5.17 | Schematic of the non-overlapping clock generator.                                       | 90  |

|------|-----------------------------------------------------------------------------------------|-----|

| 5.18 | Equivalent circuit model of DIP40 bondpad parasitics                                    | 91  |

| 5.19 | Schematic of output buffer.                                                             | 92  |

| 5.20 | Output buffer bode and distortion plots                                                 | 93  |

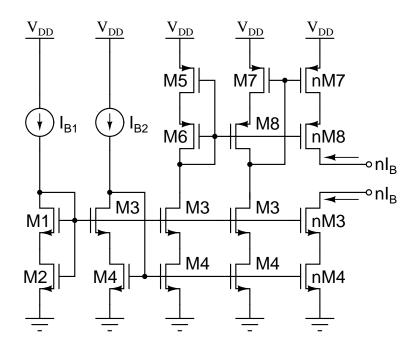

| 5.21 | Schematic of master bias circuit                                                        | 94  |

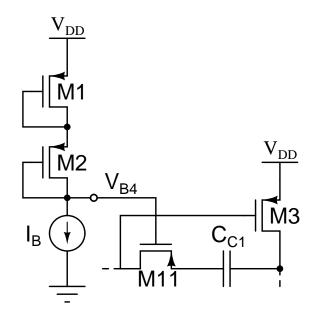

| 5.22 | Schematic of lead compensation bias circuit.                                            | 95  |

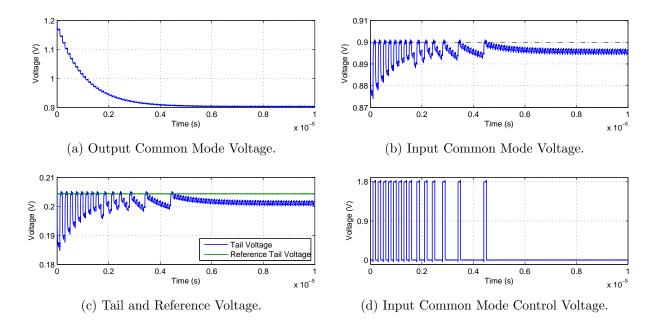

| 5.23 | $OA_2$ common mode settling simulations                                                 | 96  |

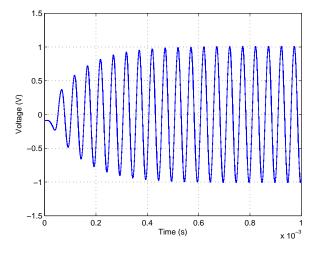

| 5.24 | Oscillator during start-up.                                                             | 97  |

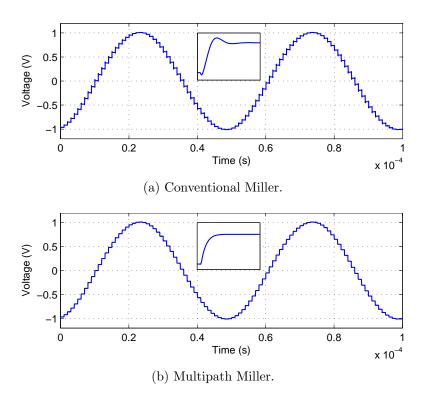

| 5.25 | Oscillator output after start-up transients have settled                                | 98  |

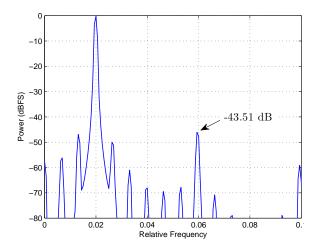

| 5.26 | Oscillator spectrum with a 1600-point Hann window.                                      | 98  |

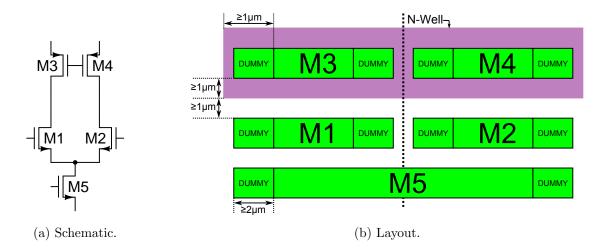

| 6.1  | Example single-stage op amp layout using the symmetry-at-block-level style.             | 100 |

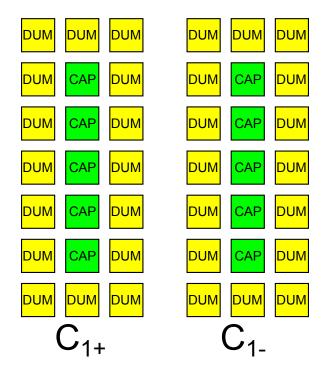

| 6.2  | Layout of capacitor $C_1$ consisting of an array of unit transistors and a ring         |     |

|      | dummies                                                                                 | 101 |

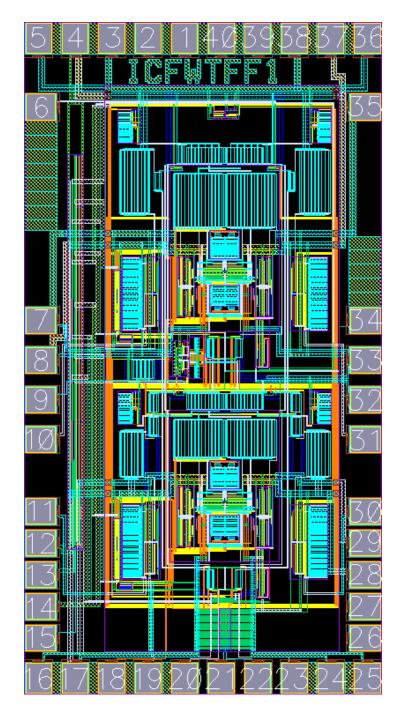

| 6.3  | Test chip top-level layout.                                                             | 106 |

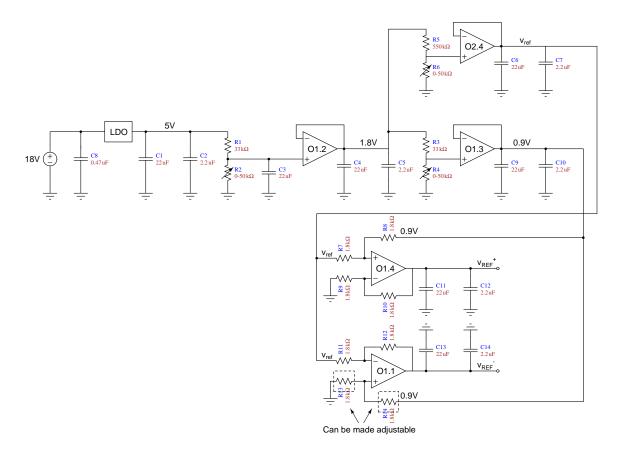

| 6.4  | Test board for generating reference voltages                                            | 107 |

| 6.5  | Test board for testing the fabricated chip.                                             | 108 |

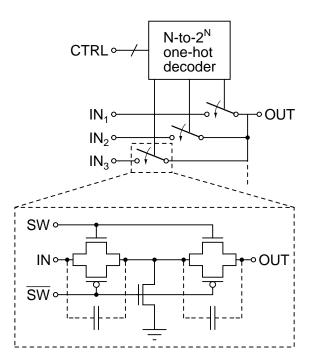

| 6.6  | Schematic of an analog multiplexer with T-switches                                      | 109 |

| A.1  | Block digram of a two-stage multipath Miller-compensated op amp with lead compensation. | 118 |

| A.2  | Small signal digram of a two-stage multipath miller compensated op amp                  |     |

|      | with lead compensation.                                                                 | 118 |

| B.1 | Block diagrams of iGDnverting amplifiers.                                    | 122 |

|-----|------------------------------------------------------------------------------|-----|

| C.1 | Circuit digram of a two-stage conventional Miller-compensated op amp         | 124 |

| C.2 | Small-signal noise model a two-stage conventional Miller-compensated op      |     |

|     | amp                                                                          | 125 |

| C.3 | Circuit digram of a two-stage multipath Miller-compensated op amp. $\ . \ .$ | 127 |

| C.4 | Small-signal noise model a two-stage multipath Miller-compensated op amp.    | 127 |

### Chapter 1

### Introduction

The operational amplifier, or op amp, is the main building block in almost all analog circuits. The performance of most analog and mixed-signal systems are limited by the op amp. For example, the resolution of pipelined ADCs is determined by the gain of its op amps [1,2]. The push for increasingly large scale integration has forced analog and mixedsignal designers to use advanced CMOS processes that suffer from lower transistor gain and supply voltage. A common technique to increase the gain of an op amp is through cascoding (vertical gain enhancement). Cascode circuits require additional voltage headroom but that has not been a major issue in past designs [3]. However, with the aggressive voltage scaling in advanced CMOS processes, it will become increasingly challenging for designers to realize high gain op amps using only the technique of cascoding.

Another method for increasing gain is to cascade multiple amplifiers in series (horizontal gain enhancement). Although cascading does not consume voltage headroom, the presence of additional poles can compromise the stability of the system, once the amplifier is placed in a feedback loop. Pole splitting is the most common technique for stabilizing multi-stage

op amps. However, stability is achieved at the expense of bandwidth. In this work, the effects of feedforward compensation are examined and circuit techniques for overcoming the bandwidth restriction due to pole splitting are developed.

### 1.1 Outline

The thesis is structured as follows: Chapter 2 reviews the simple one-pole model for op amps and provides background information on multi-stage op-amps. Popular techniques for frequency compensating multi-stage op-amps are also discussed. Chapter 3 discusses how feedforward paths can be added to improve the performance of frequency compensated op-amps. In Chapter 4, the system-level design of a switched-capacitor oscillator is introduced. The oscillator is used to compare the performance of op-amps with and without the feedforward paths enabled. Chapter 5 describes the circuit design of the oscillator in a 0.18  $\mu$ m CMOS technology. Improvements to the design are presented in Chapter 6. Chapter 7 concludes the thesis and discusses future work in the area of feedforward compensation.

### Chapter 2

### **Background Information**

In the majority of integrated circuit applications, the op amp is used to drive on-chip capacitive loads. In this thesis, the focus will be on the operational transconductance amplifier (OTA) which is the most popular form of op amp for integrated circuit designs [4,5]. Unlike op-amps, OTAs are amplifiers with a high output impedance. This is sufficient for most applications where the load is capacitive.

This chapter will provide background information on the op amp. Section 2.1 reviews the relationship between system-level specifications and op amp specifications. Section 2.2 discusses the fundamentals of amplifier stability. Characteristics and mathematical models of the single- and two-stage op amps are presented in Section 2.3 and 2.4, respectively. Finally, Section 2.5 reviews multistage op amp architectures.

### 2.1 Amplifier Requirements

Op amps are commonly found in negative feedback systems. Negative feedback is particularly desirable as it can desensitize the gain, improve linearity, increase bandwidth, and reduce noise in a system [6]. A common feedback configuration is the inverting amplifier as depicted in Fig. 2.1. The transfer function of the system is

$$\frac{V_{\rm out}}{V_{\rm in}}(s) = -\frac{C_{\rm I}/C_{\rm F}}{1 + \frac{1 + C_{\rm I}/C_{\rm F}}{A(s)}}$$

(2.1)

where A(s) is the op amp gain. If A(s) is very large, Eq. 2.1 becomes approximately

$$\frac{V_{\rm out}}{V_{\rm in}} \approx -\frac{C_{\rm I}}{C_{\rm F}} \tag{2.2}$$

The above equation shows that if the gain of the op amp is sufficiently large, the closed-loop transfer function of a system will be independent of the op amp's characteristics.

Figure 2.1: An inverting amplifier configuration commonly found in integrated circuits.

### 2.1.1 DC Gain

Unless an op amp has infinite gain, there will be some error in the system's transfer function. For the inverting amplifier in Fig. 2.1, its transfer function, Eq. 2.1, can be rewritten as

$$\frac{V_{\text{out}}}{V_{\text{in}}} = -\left(\frac{C_{\text{I}}}{C_{\text{F}}}\right) \left(\frac{1}{1 + \frac{1 + C_{\text{I}}/C_{\text{F}}}{A_0}}\right)$$

(2.3)

where  $A_0$  is the DC gain of the op amp. Eq. 2.3 can be approximated by its first-order Maclaurin series as

$$\frac{V_{\text{out}}}{V_{\text{in}}} \approx -\left(\frac{C_{\text{I}}}{C_{\text{F}}}\right) \left(1 - \frac{1 + C_{\text{I}}/C_{\text{F}}}{A_0}\right)$$

(2.4)

The error of the closed-loop gain is thus

$$\epsilon = \frac{1 + C_{\rm I}/C_{\rm F}}{A_0} = \frac{1}{\beta A_0} = \frac{1}{L_{\rm g,0}} \tag{2.5}$$

where  $\beta$  is the feedback factor and is defined as the ratio between  $C_F$  and the sum of all the capacitances connected to the inverting node of the op amp. In many systems,  $\beta$ is dimensionless and frequency independent. In this amplifier configuration, the feedback factor is

$$\beta = \frac{C_{\rm F}}{\Sigma C_i} = \frac{C_{\rm F}}{C_{\rm F} + C_{\rm I}} \tag{2.6}$$

The term  $\beta A_0$ , or  $L_{g,0}$ , is a dimensionless parameter known as the DC loop gain. As will be demonstrated later in this chapter, the loop gain ( $L_g = \beta A$ ) is a very important parameter in feedback systems.

In data converter systems, the gain error,  $\epsilon$ , is generally expressed in terms of the number of bits, N, where

$$\epsilon = \frac{1}{2^{N}} \tag{2.7}$$

Substituting Eq. 2.7 into Eq. 2.5 yields the minimum loop gain required to achieve N-bits of accuracy.

$$L_{\rm g} \ge 2^N = 6.02N \; [\rm dB]$$

(2.8)

which means that higher resolution data converters require higher op amp DC gain.

### 2.1.2 Bandwidth

In many applications, such as in switched-capacitor circuits, the maximum speed in which the circuit can operate is determined by its settling time. As illustrated in Fig. 2.2, settling time is defined as the time it takes for the output to settle to within a specified error range. In linear systems, settling time is dependent on the bandwidth or more specifically the gain-bandwidth product of the op amp.

Figure 2.2: Step response characteristics of a linear system.

The transfer function of an one-pole op amp is

$$A(s) = \frac{A_0}{1 + s/\omega_b} \tag{2.9}$$

where  $\omega_b$  is the bandwidth (and pole frequency) of the open-loop op amp.

When the op amp is placed in a negative feedback loop, its high DC gain is traded off for much higher bandwidth. In systems where the frequency of interest is much greater than the open-loop bandwidth, the op amp can be accurately modelled as an integrator [5,7] where

$$A(s) \approx \frac{A_0}{s/\omega_b} = \frac{\omega_{\rm T}}{s} \tag{2.10}$$

where  $\omega_{\rm T}$  is the gain-bandwidth product and is defined as

$$\omega_{\rm T} = A_0 \omega_b \tag{2.11}$$

Substituting Eq. 2.10 into Eq. 2.1 leads to

$$\frac{V_{\rm out}}{V_{\rm in}} = -\frac{C_{\rm I}/C_{\rm F}}{1 + \frac{(1+C_{\rm I}/C_{\rm F})s}{\omega_{\rm T}}} = -\frac{C_{\rm I}/C_{\rm F}}{1 + \frac{s}{\beta\omega_{\rm T}}}$$

(2.12)

where

$$\beta\omega_{\rm T} = \left(\frac{C_{\rm F}}{C_{\rm F} + C_{\rm I}}\right)\omega_{\rm T} \tag{2.13}$$

is the closed-loop bandwidth.

For a first-order system characterized by Eq. 2.12, the step response is

$$V_{\rm out} = -\frac{C_{\rm I}}{C_{\rm F}} \left(1 - e^{-t\beta\omega_{\rm T}}\right) V_{\rm in} \tag{2.14}$$

where the exponential term is the settling error. From Eq. 2.14, the required  $\beta \omega_{\rm T}$  for a specified settling time (shown in Fig. 2.2), T, and error,  $\epsilon$ , is

$$\beta\omega_{\rm T} = \frac{-\ln\epsilon}{T} \tag{2.15}$$

In data converter systems where the output signal generally has to settle to within the least-significant-bit in one half of the clock period (i.e.  $T = \frac{1}{2f_{clk}}$ ), the required closed-loop

bandwidth can be obtained by substituting Eq. 2.7 into 2.15

$$\beta\omega_{\rm T} = 2N f_{\rm clk} \ln 2 \tag{2.16}$$

The above equation shows that the necessary op amp closed-loop bandwidth, and hence the gain-bandwidth product, increases for higher resolution or higher sampling rate data converters.

### 2.2 Stability

When an op amp is placed inside a negative feedback loop, it is possible for the system to become unstable. If a system's transient response to a bounded input is bounded, the system is considered to be BIBO (bounded-input-bounded-output) stable. For linear systems, a necessary and sufficient condition for BIBO stability is if all the poles of the closed-loop system are in the left-hand side of the s-plane [8]. Poles are determined by the roots of the denominator of the system transfer function. A system is conditionally stable if a pair of poles is on the imaginary axis while all other poles are in the left-half plane.

It is extremely difficult and time-consuming for circuit designers to obtain the exact closed-loop transfer function of a system. The problem is compounded when process, temperature, and voltage (PVT) variations need to be accounted for. Fortunately, methods, such as the Nyquist stability criterion and phase margin, have been developed to assess the stability of a system without needing to determine its transfer function.

#### 2.2.1 Nyquist Stability Criterion

The Nyquist stability criterion is a graphical technique for ascertaining the stability of a feedback system by observing its Nyquist plot. A Nyquist plot is generated by plotting

the magnitude and phase response of an open-loop system in polar coordinates as the frequency is varied [6], if the feedback factor,  $\beta$ , is unity for all frequencies. When  $\beta$  is not unity for all frequencies, the plot should be of the loop gain,  $L_{\rm g}(j\omega) = \beta(j\omega)A(j\omega)$ , instead of simply just the op amp's open loop gain  $A(j\omega)$ . An exemplary Nyquist plot is shown in Fig. 2.3. According to the Nyquist stability criterion, a system is stable if the number of clockwise encirclements at the point (-1,0) is exactly  $\aleph = -P$ , where P is the number of open-loop poles (i.e. poles of  $L_{\rm g}(s)$ ) in the right-half plane.

Figure 2.3: An example Nyquist plot. The system is stable as there are no encirclements at the point (-1, 0).

In the usual case where  $P = 0^1$  [8], the Nyquist criterion can be simplified to the following statement: A feedback system is stable, based on the Nyquist criterion, if the Nyquist plot of  $L_g(j\omega)$  has no encirclements at the point (-1,0). The point (-1,0) marks

<sup>&</sup>lt;sup>1</sup>In most feedback designs with op amps, P = 0 since op amps are generally open-loop stable (no poles on the right-half plane).

where the magnitude response is 1 V/V (0 dB) and the phase response is  $-180^{\circ}$ .

### 2.2.2 Phase Margin

Based on the above observations, a linear system's stability can be determined directly from its Bode plot. To ensure no encirclements at the point (-1, 0) in the Nyquist plot, the phase of  $L_{\rm g}(j\omega)$  must be no less than  $-180^{\circ}$  at its unity-gain frequency. Phase margin (PM) is defined as the amount of additional phase lag required of  $L_{\rm g}(j\omega)$  so that the system becomes unstable [8]. It is measured by adding  $180^{\circ}$  to the phase of  $L_{\rm g}(j\omega)$  at the frequency where  $|L_{\rm g}(j\omega)| = 1$ . This is illustrated in Fig. 2.4. A positive phase margin indicates that the system is stable. Phase margin is a means of not only determining the stability of a system but also its relative stability. A higher phase margin is indicative of a system that is more stable and one that is also more robust to PVT variations. In typical op amp designs, a minimum phase margin of 45 degrees is desired [9, 10].

### 2.3 Single-Stage Op Amps

The single-stage op amp is the most basic op amp structure. Its block diagram and a simplified transistor implementation are shown in Fig. 2.5. With only one dominant pole, the single-stage op amp can achieve one of the highest gain-bandwidth products amongst all op amp architectures. However, the architecture suffers from very low DC gains, especially in advanced CMOS processes. The DC gain can be improved through cascoding, but this comes at the expense of reduced voltage headroom and stability margin [11, 12]. Reduced voltage headroom is highly undesirable as it degrades the system's signal-to-noise ratio and increases sensitivity to PVT variations. Furthermore, the reduced supply voltage in

Figure 2.4: An example phase margin measurement. The feedback factor,  $\beta$ , is 0.1 and is frequency independent.

advanced CMOS processes acts as another obstacle to using vertical gain enhancement to meet a specified DC gain requirement.

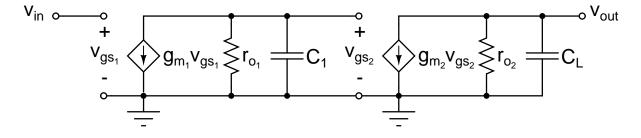

Fig. 2.6 shows the low-to-medium frequency small-signal model of the op amp depicted in Fig. 2.5. The transfer function of the op amp, when driven by a low-impedance source, is

$$\frac{V_{\text{out}}}{V_{\text{in}}} = A(s) = -\frac{g_{m_1} r_{o_1}}{1 + s r_{o_1} C_L}$$

(2.17)

where the DC gain is

$$A_0 = -g_{m_1} r_{o_1} \tag{2.18}$$

Figure 2.5: Block diagram and simple transistor implementation of a single-stage op amp.

The op amp bandwidth is set by the pole at

$$\omega_{p1} = \frac{1}{r_{o_1} C_L} \tag{2.19}$$

and the gain-bandwidth product is

$$\omega_{\rm T} = \frac{g_{m_1}}{C_L} \tag{2.20}$$

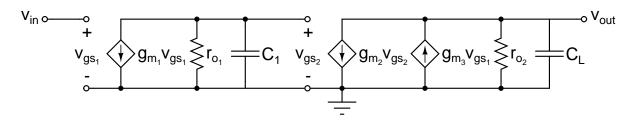

Figure 2.6: Small-signal model of a single-stage op amp.

The advantage of the single-stage op amp lies in its stability and predictability. Since its transfer function has only one pole, the phase response, for all frequencies, will never drop below  $-90^{\circ}$ . This means that the phase margin will always be positive and the amplifier

will be stable for all values of  $\beta$ . The closed-loop step response of 2.17 is

$$V_{\text{out}} = A_{\text{CL}} \left( 1 - e^{-t\beta\omega_{\text{T}}} \right) V_{\text{in}}$$

$$= A_{\text{CL}} \left( 1 - e^{-\frac{t}{\tau}} \right) V_{\text{in}}$$

(2.21)

where  $A_{\rm CL}$  is the closed-loop gain of the amplifier and

$$\tau = \frac{1}{\beta\omega_{\rm T}} \tag{2.22}$$

is the closed-loop time constant. The first-order settling behaviour of the circuit implies predictable settling behaviour. As illustrated in Fig. 2.7a, it takes  $4.6\tau$  to reach 1% settling accuracy and  $6.9\tau$  to reach 0.1% settling accuracy. Fig. 2.7b plots the settling accuracy versus settling time of first-order systems, normalized to  $\tau = unit_{18}$ .

Figure 2.7: Settling behaviour of a first-order system

## 2.4 Two-Stage Op Amps

The two-stage op amp is a very popular approach for realizing high gain amplifiers. This classic architecture is found in many state-of-the-art analog and mixed-signal circuits [13–16]. Fig. 2.8 shows the block diagram and a simple transistor realization of the two-stage op amp. Aside from increasing the DC gain, the two-stage architecture also allows more flexibility in the op amp design. In most two-stage op amps, the second stage is designed to provide high output swing in order to maximize the signal-to-noise ratio. The output swing of the first stage can then be reduced without adversely affecting the system's noise performance. This makes it feasible for designers to use vertical-gain enhancement, or cascoding, in their designs, as long as there is adequate voltage headroom for the transistors to remain in saturation.

Figure 2.8: Block diagram and simple transistor implementation of a single-stage op amp.

The low-to-medium frequency small-signal model of the two-stage op amp is shown in Fig. 2.9. The transfer function of the circuit, neglecting the gate-to-drain capacitance  $C_{gd}$ of M2, is

$$\frac{V_{\text{out}}}{V_{\text{in}}} = A(s) = \frac{g_{m_1} r_{o_1} g_{m_2} r_{o_2}}{\left(1 + s r_{o_1} C_1\right) \left(1 + s r_{o_2} C_L\right)}$$

(2.23)

where  $C_1$  is the capacitance at the output of the first stage and  $C_L$  is the output load capacitance. The DC gain of the op amp is

$$A_0 = g_{m_1} r_{o_1} g_{m_2} r_{o_2} \tag{2.24}$$

The two poles of the op amp are located at

$$\omega_{p_1} = \frac{1}{r_{o_1} C_1} \tag{2.25}$$

$$\omega_{p_2} = \frac{1}{r_{o_2} C_L} \tag{2.26}$$

Assuming  $\omega_{p_1} < \omega_{p_2}$ , the gain-bandwidth product is

$$\omega_{\rm T} = \frac{g_{m_1} g_{m_2} r_{o_2}}{C_1} \tag{2.27}$$

which is a factor of  $g_{m_2}r_{o_2}$  higher than that of the single-stage op amp.

Figure 2.9: Small-signal model of a two-stage op amp.

The main drawback of the two-stage op amp is the decreased stability margin due to the presence of two dominant poles. The op amp should always be stable as there are only two poles in the circuit. However, the desire to maintain a phase margin greater or equal to  $45^{\circ}$ , along with high-frequency parasitic poles and RHP (right-half plane) zeros, which were ignored in the above analysis, can degrade the loop gain's phase margin to below  $0^{\circ}$ . Stability can be improved with frequency compensation techniques but, as will be shown below, at the expense of a lower gain-bandwidth product.

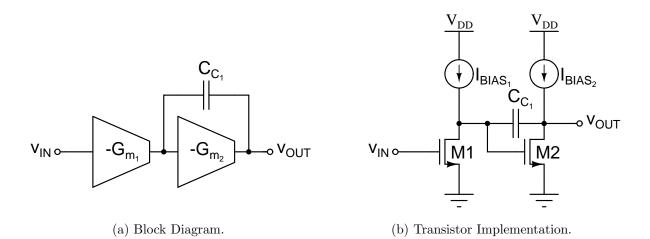

### 2.4.1 Miller Compensation

A two-stage op amp can be stabilized using a variety of compensation techniques [10]. The most popular, and practical, approach is the Miller compensation technique. In this method, a compensation capacitor,  $C_{C_1}$ , is placed between the input and output of the second stage amplifier, as shown in Fig. 2.10. Stability is improved by exploiting the phenomenon of pole splitting [17]. Pole splitting has the effect of pushing one of the two dominant poles to a lower frequency and pushing the other dominant pole to a higher frequency.

Figure 2.10: Block diagram and simple transistor implementation of a single-stage op amp.

The low-to-medium frequency small-signal model of the two-stage Miller-compensated

op amp is shown in Fig. 2.11. With the assumption that  $C_1$  is negligible, the transfer function of the op amp is approximately

$$\frac{V_{\text{out}}}{V_{\text{in}}} = A(s) \approx \frac{g_{m_1} r_{o_1} g_{m_2} r_{o_2} \left(1 - s \frac{C_{C_1}}{g_{m_2}}\right)}{\left(1 + s r_{o_1} g_{m_2} r_{o_2} C_{C_1}\right) \left(1 + s \frac{C_L}{g_{m_2}}\right)}$$

(2.28)

The DC gain of Eq. 2.28 is exactly the same as that of Eq. 2.23. However, there is a significant change in the locations of the poles. When the compensation capacitor is introduced, the pole of the first amplifier stage,  $\omega_{p_1}$ , is pushed down from  $\frac{1}{r_{o_1}C_1}$  to  $\frac{1}{r_{o_1}g_{m_2}r_{o_2}C_{C_1}}$  by the Miller effect [17]. Meanwhile, the pole of the second amplifier stage,  $\omega_{p_2}$ , is pushed up from  $\frac{1}{r_{o_2}C_L}$  to  $\frac{g_{m_2}}{C_L}$ . The compensation capacitor also introduces a right-half plane (RHP) zero located at  $\omega_z = \frac{g_{m_2}}{C_{C_1}}$ . The gain-bandwidth product of the op amp, as defined in Page 15, is

$$\omega_{\rm T} = \frac{g_{m_1}}{C_{C_1}} \tag{2.29}$$

which is similar to the gain-bandwidth product of the single-stage op amp (Eq. 2.20).

Figure 2.11: Small-signal model of a two-stage miller-compensated op amp.

To obtain a desired phase margin, the required separation between the second pole,  $\omega_{p_2}$ , and the closed-loop bandwidth,  $\beta\omega_{\rm T}$ , is given by [5]

$$\frac{\omega_{p_2}}{\beta\omega_{\rm T}} = \frac{1}{\tan\left(90^\circ - \rm{PM}\right)} \tag{2.30}$$

Eq. 2.30 highlights the most significant drawback to pole splitting. In order to obtain adequate stability margin, the closed-loop bandwidth must be lower than the second pole by a certain factor. Since the  $\omega_{p_2}$  is near the same frequency as  $\omega_{\rm T}$  of the single-stage op amp (Eq. 2.20), the maximum achievable closed-loop bandwidth of the two-stage op amp will always be lower than that of the single-stage op amp with a first-order transfer function.

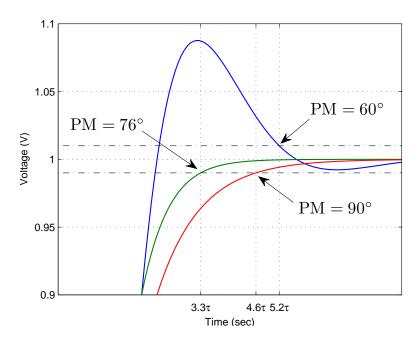

The settling time of a second-order system is difficult to compute and predict as it is highly dependent on both its gain-bandwidth product and its phase margin. As illustrated in Fig. 2.12, the settling time can vary significantly for second-order systems with the same gain-bandwidth product. The phase margin for optimum settling time is approximately given by [18]

$$PM_{opt} \approx 90^{\circ} - \tan^{-1} \left[ \frac{1 + \left(\frac{\pi}{\ln \epsilon}\right)^2}{4} \right]$$

(2.31)

In most applications, a phase margin between 70° to 76° will provide the shortest closed-loop settling time [5]. To meet this requirement, based on Eq. 2.30,  $\omega_{p_2}$  should be placed 3 to 4 times higher than  $\beta\omega_{\rm T}$ . If  $\omega_{p_2}$  is placed at the maximum possible frequency, then the gain-bandwidth product will have to be 3 to 4 times lower than the limits of a given technology. In contrast, the gain-bandwidth product of the single-stage op amp can always be set to the maximum possible frequency of the technology.

The previous analysis neglects the RHP zero in the op amp transfer function (Eq. 2.28). The zero can severely degrade the phase margin and should not be disregarded in the design process. Fortunately, various circuit techniques have been developed to deal with the effects of the Miller zero [19–22].

Figure 2.12: Settling behaviour of a second-order system. The error range is 1% ( $\epsilon = 0.01$ ).

## 2.5 Multi-Stage Op Amps

In an advanced CMOS process where intrinsic transistor gain and supply voltage are low, it may be necessary to cascade three or more amplifier stages to meet a specified DC gain requirement. As with the two-stage op amp, stability is a major concern for multi-stage op amps. Techniques for stabilizing multi-stage op amps have been the focus of much research over the last decade. Multi-stage compensation techniques tend to fall into two categories: nested-Miller [23–31] and feedforward [32–34]. In the former, the op amp is stabilized by the means of pole splitting with Miller capacitors. In the latter, stability is achieved through pole-zero cancellation.

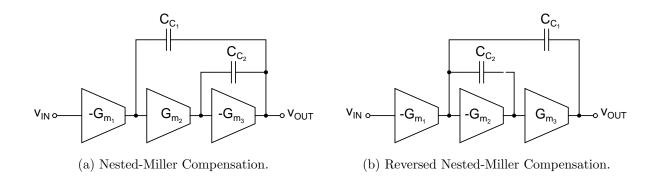

#### 2.5.1 Nested-Miller Compensation

The pole-splitting principle behind two-stage Miller compensation can be extended to stabilize op amps of more than two horizontal gain stages. A popular multi-stage Miller compensation technique is the nested-Miller compensation (NMC) method. Fig. 2.13a describes a conventional third-order NMC op amp. Like two-stage Miller compensation, NMC aims to split the dominant poles so that one pole is pushed to a lower frequency while the others are pushed to higher frequencies. An obvious drawback with the conventional NMC topology is an increased capacitive load since all the Miller capacitors load the output. A larger output capacitance is undesirable since it degrades the op amp bandwidth. The reversed nested-Miller topology, shown in Fig. 2.13b, operates on the same pole-splitting principle as the NMC but provides bandwidth improvement since only the outer Miller capacitor loads the output [23, 30, 35].

Figure 2.13: Block diagrams of three-stage nested-miller compensated op amps.

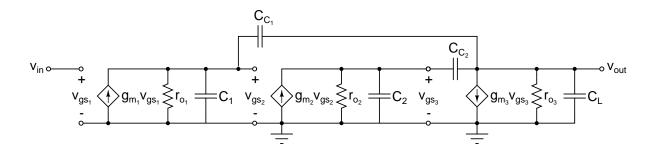

Fig. 2.14 shows the low-to-medium frequency small-signal model of the three-stage NMC op amp in Fig. 2.13a. Assuming  $C_1$  and  $C_2$  are small so that they can be neglected,

the transfer function of the op amp can be approximated with [23, 24, 31, 36, 37]

$$\frac{V_{\text{out}}}{V_{\text{in}}} = A(s) \approx \frac{g_{m_1} r_{o_1} g_{m_2} r_{o_2} g_{m_3} r_{o_3} \left(1 - s \frac{C_{C_2}}{g_{m_3}} - s^2 \frac{C_{C_1} C_{C_2}}{g_{m_2} g_{m_3}}\right)}{\left(1 + s r_{o_1} g_{m_2} r_{o_2} g_{m_3} r_{o_3} C_{C_1}\right) \left(1 + s \frac{C_{C_2}}{g_{m_2}} + s^2 \frac{C_{C_2} C_L}{g_{m_2} g_{m_3}}\right)} \\ \approx \frac{\frac{g_{m_1}}{C_{C_1}} \left(1 - s \frac{C_{C_2}}{g_{m_3}} - s^2 \frac{C_{C_1} C_{C_2}}{g_{m_2} g_{m_3}}\right)}{s \left(1 + s \frac{C_{C_2}}{g_{m_2}} + s^2 \frac{C_{C_2} C_L}{g_{m_2} g_{m_3}}\right)} \tag{2.32}$$

The DC gain is

$$A_0 = -g_{m_1} r_{o_1} g_{m_2} r_{o_2} g_{m_3} r_{o_3} (2.34)$$

which is higher than the DC gain of the single- and two-stage op amp. The poles and zeros of the op amp are located at

$$\omega_{p_1} = \frac{1}{r_{o_1} g_{m_2} r_{o_2} g_{m_3} r_{o_3} C_{C_1}} \tag{2.35}$$

$$\omega_{p_2} \approx \frac{g_{m_2}}{C_{C_2}} \tag{2.36}$$

$$\omega_{p_3} \approx \frac{g_{m_3}}{C_L} \tag{2.37}$$

$$\omega_{z_1} \approx -\frac{g_{m_3}}{C_{C_2}} \tag{2.38}$$

$$\omega_{z_2} \approx \frac{g_{m_2}}{C_{C_1}} \tag{2.39}$$

It is important to note that the first zero  $(\omega_{z_1})$  is a RHP zero and the second zero  $(\omega_{z_2})$  is a LHP zero. The gain-bandwidth product of Eq. 2.33 is

$$\omega_{\mathrm{T}} = \frac{g_{m_1}}{C_{C_1}} \tag{2.40}$$

which is the same as Eq. 2.29.

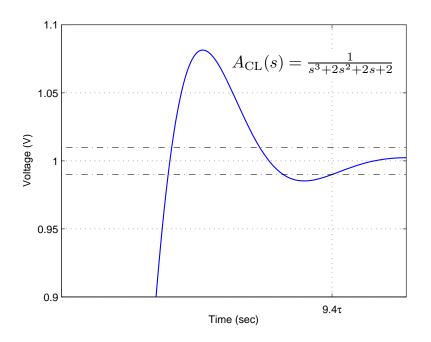

According to current literature, there is no simple design procedure for obtaining optimum settling response for multi-stage op amps [38–40]. The most common design approach

Figure 2.14: Small-signal model of a three-stage nested miller-compensated op amp.

is to aim for a closed-loop frequency response that is maximally flat (i.e. a Butterworth filter). For a three-stage op amp, the closed-loop unity-gain transfer function should be

$$A_{\rm CL}(s) = \frac{A(s)}{1 + A(s)} = \frac{1}{\left(1 + s\frac{2}{\omega_0} + s^2\frac{2}{\omega_0^2} + s^3\frac{1}{\omega_0^3}\right)}$$

(2.41)

where  $A_{\text{CL}(s)}$  and A(s) are the transfer functions of the closed-loop amplifier and the op amp, respectively. From Eq. 2.41, the desired op amp transfer function is

$$A(s) = \frac{A_{\rm CL}(s)}{1 - A_{\rm CL}(s)} = \frac{\frac{\omega_0}{2}}{s\left(1 + s\frac{1}{\omega_0} + s^2\frac{1}{2\omega_0}\right)}$$

(2.42)

Comparing the coefficients of Eq. 2.33 without the zeros, with Eq. 2.42 yields the following pair of design equations:

$$\beta\omega_{\rm T} = \frac{1}{4} \frac{g_{m_3}}{C_L} \tag{2.43}$$

$$\frac{g_{m_2}}{C_{C_1}} = \frac{1}{2} \frac{g_{m_3}}{C_L} \tag{2.44}$$

Compared with Eq. 2.20, the maximum  $\beta\omega_{\rm T}$  will be a factor of 4 lower than that of the single-stage op amp. The step response of Eq. 2.41 is shown in Fig. 2.15. From the figure, it is evident by the transient overshoot that the settling response is not optimum for  $\epsilon < 0.08$ . To obtain near-optimum settling time where  $\epsilon < 0.01$ , the separation between  $\beta\omega_{\rm T}$  and  $\frac{g_{m_3}}{C_L}$  can be tuned numerically but their ratio must be greater than 4.

Figure 2.15: Settling behaviour of a third-order low-pass butterworth filter.  $\omega_0 = 1$  rad/s and  $\epsilon = 0.01$ .

The previous analysis neglected the two zeros in Eq. 2.32. Since only one of the zeros is in the RHP, the overall effect of the zeros on stability is small [31]. However, the presence of Miller zeros cannot be discounted in higher-order amplifiers as they can degrade the stability margin [26, 28]. A number of nested-Miller topologies have been published in literature to offset the effects of the zeros [25–31], most of which are based on the principles referenced in Section 2.4.1.

### 2.5.2 Feedforward Compensation

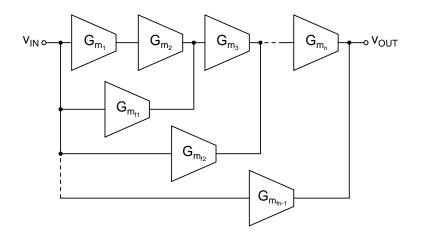

Feedforward compensation aims to improve amplifier stability by introducing feedforward gain stages. A two-stage feedforward-compensated op amp is depicted in Fig. 2.16. This compensation topology creates left-half plane zeros that can be used to offset the negative phase shift from the dominant poles [32–34]. More specifically, the zeros can be placed so that they cancel out all but one of the dominant poles. After pole-zero cancellation, the multi-stage op amp should have the same frequency and transient response as that of a single-stage op amp. Feedforward compensation has two distinct advantages over Miller compensation. Firstly, feedforward op amps do not suffer from the gain-bandwidth product limitations that are inherent with the Miller compensation architecture. Secondly, these amplifiers can be implemented in less area as they do not require compensation capacitors.

Figure 2.16: Block diagram and simple transistor implementation of two-stage feedforward op amp.

Fig. 2.17 shows the low-to-medium-frequency small-signal model of the two-stage feedforward-

compensated op amp in Fig. 2.16. The op amp transfer function is

$$\frac{V_{\text{out}}}{V_{\text{in}}} = A(s) = \frac{\left(g_{m_1}r_{o_1}g_{m_2}r_{o_2} + g_{m_3}r_{o_2}\right)\left(1 + s\frac{g_{m_3}C_1}{g_{m_1}g_{m_2}}\right)}{\left(1 + sr_{o_1}C_1\right)\left(1 + sr_{o_2}C_L\right)} \approx \frac{g_{m_1}r_{o_1}g_{m_2}r_{o_2}\left(1 + s\frac{g_{m_3}C_1}{g_{m_1}g_{m_2}}\right)}{\left(1 + sr_{o_1}C_1\right)\left(1 + sr_{o_2}C_L\right)}$$

(2.45)

the DC gain is

$$A_0 = g_{m_1} r_{o_1} g_{m_2} r_{o_2} \tag{2.46}$$

Assuming  $r_{o_1}C_1 > r_{o_2}C_L$ , the gain-bandwidth product is

$$\omega_{\rm T} = \frac{g_{m_1} g_{m_2} r_{o_2}}{C_1} \tag{2.47}$$

The above two parameters are virtually identical to that of the two-stage op amp (Eq. 2.24 and Eq. 2.27). The open-loop poles and zeros of the op amp are located at

$$\omega_{p_1} = \frac{1}{r_{o_1} C_1} \tag{2.48}$$

$$\omega_{p_2} \approx \frac{1}{r_{o_2} C_L} \tag{2.49}$$

$$\omega_z \approx \frac{g_{m_1}g_{m_2}}{g_{m_3}C_1} \tag{2.50}$$

To obtain an open-loop single-pole response for the op amp, the frequency of the lefthalf plane zero,  $\omega_z$ , should match the frequency of the second pole,  $\omega_{p_2}$ . This means that

$$\frac{g_{m_1}g_{m_2}}{g_{m_3}C_1} = \frac{1}{r_{o_2}C_L} \tag{2.51}$$

Thus, the transconductance of the feedforward stage should be

$$g_{m_3} = \frac{g_{m_1}g_{m_2}r_{o_2}C_L}{C_1} = kg_{m_1} \tag{2.52}$$

where k is the transconductance ratio between  $G_{m_3}$  and  $G_{m_1}$  in Fig. 2.16a. With proper pole-zero cancellation, the two-stage op amp has only one dominant pole and it can be modelled simply as a one-stage op amp. This method can then be repeated to realize an n-stage op amp, as is shown in Fig. 2.18.

Figure 2.17: Small-signal model of a two-stage feedforward-compensated op amp.

Figure 2.18: Block diagram of a n-stage feedforward op amp.

There are two major drawbacks to open-loop pole-zero cancellation. Firstly, the technique scales poorly since the factor k in Eq. 2.52 increases exponentially with each additional stage in the op amp. In multi-stage op amps, the transconductance ratio between  $G_{m_3}$  and  $G_{m_1}$  can be several orders of magnitude. This makes implementing higher-order op amps highly impractical. Secondly, the op amp is highly sensitive to PVT variations since the location of the zero is dependent on the value of the parasitic capacitor  $C_1$ . Inexact pole-zero cancellation leads to pole-zero doublets that may degrade the settling time [41]. Pole-zero doublets are not a problem for continuous-time circuits, but may lead to long start-up transients and increased susceptibility to coupling of clock signals if the pole-zero spacing is left unregulated.

An alternative method for obtaining a single-pole response is to perform pole-zero cancellation after the op amp is placed in feedback [34]. If the condition

$$\frac{4\beta C_L g_{m_1} g_{m_2}}{C_1 \left(\beta g_{m_3} + 1/r_{o_2}\right)^2} = \frac{4\beta k}{r_{o_2} \left(\beta g_{m_3} + 1/r_{o_2}\right)^2} < 0.5$$

(2.53)

is satisfied, then the approximate locations of the closed-loop poles and zero are

$$\omega_{\rm p_1} \approx \frac{\beta g_{m_1} g_{m_2}}{C_1 \left(\beta g_{m_3} + 1/r_{o_2}\right)} \tag{2.54}$$

$$\omega_{\mathbf{p}_2} \approx \frac{\beta g_{m_3} + 1/r_{o_2}}{C_L} \tag{2.55}$$

$$\omega_{\rm z} \approx \frac{g_{m_1}g_{m_2}}{g_{m_3}C_1} \tag{2.56}$$

which means that the zero will always be in proximity of the first closed-loop pole. Unlike open-loop pole-zero cancellation, this scheme is insensitive to PVT variations as both  $\omega_z$ and  $\omega_{p_1}$  have the same dependence on the parasitic capacitance. However, this scheme still requires a high transconductance ratio between  $G_{m_1}$  and  $G_{m_3}$ . In [34], a two-stage feedforward-compensated op amp was implemented using closed-loop pole-zero cancellation where the transconductance ratio between  $A_{v_3}$  and  $A_{v_1}$  was over three orders of magnitude. Another drawback with this scheme is the complex design procedure since the closed-loop poles and zeros must be determined. For higher order op amps, the increased design complexity makes this compensation scheme very unattractive.

## 2.6 Discussion

Vertical and horizontal gain-enhancement are two techniques for improving op amp gain. Vertical gain-enhancement improves gain by increasing the output resistance of the op amp. This technique does not affect the op amp's gain-bandwidth product since  $\omega_{\rm T}$  is not a function of the output resistance (Eq. 2.20). On the other hand, horizontal gain-enhancement improves gain by increasing the effective transconductance of the op amp. As was observed in Section 2.4, this has the effect of increasing both the gain and gain-bandwidth product. While it is possible to increase the op amp  $\omega_{\rm T}$  beyond the limits of a technology, such an op amp cannot have a first-order frequency response. Because of stability and settling time considerations, the  $\omega_{\rm T}$  of horizontal gain-enhanced op amps should not exceed the maximum  $\omega_{\rm T}$  of the technology.

# Chapter 3

# **Multipath Miller Compensation**

The two techniques for stabilizing multi-stage op amps – nested-miller and feedforward compensation – both have inherent disadvantages. The disadvantage of nested-Miller compensation lies with the non-dominant poles that limit the op amp's gain-bandwidth product. The disadvantage of feedforward compensation lies with the PVT-sensitive zero location and the impractically high transconductance required of the feedforward gain stage.

This chapter discusses the operation of op amps that incorporate both compensation capacitors and feedforward gain stages, which can overcome the limitations of nestedmiller and feedforward compensation. Section 3.1 explains the operation of two-stage op amps with a multipath Miller compensation topology. Section 3.2 explores multi-stage implementations of the topologies. Section 3.3 proposes a transistor implementation of a two-stage op amp with this compensation technique.

## 3.1 Two-Stage Op-Amp

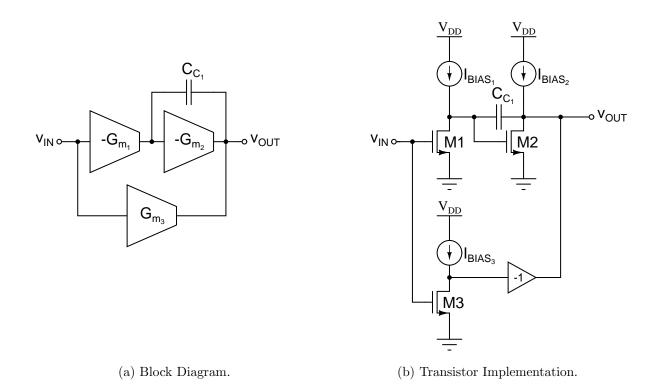

Compensation capacitors can be combined with feedforward gain stages to form a hybrid compensation topology. Fig. 3.1 depicts a two-stage op amp incorporating this compensation technique. In the past, this topology has been used to offset the effects of RHP zeros in miller- and nested-miller compensated op amps [23–25, 36]. By varying the transconductance of the feedforward path, it is possible to create LHP zeros that can be used, in the same fashion as feedforward compensation, to cancel the non-dominant poles of a multi-stage op amp [23,37].

Figure 3.1: Block diagram and simple transistor implementation of two-stage miller with feedforward-compensated op amp.

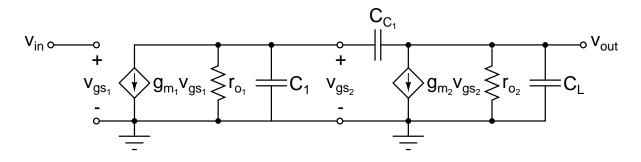

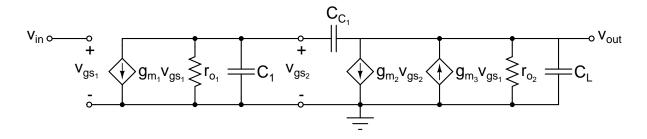

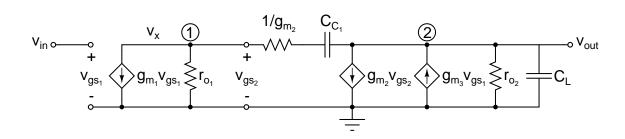

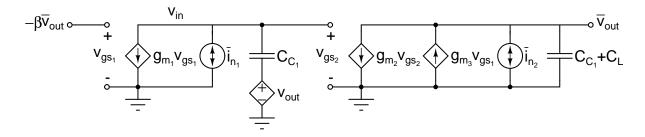

The low-to-medium frequency small-signal model of the compensation topology is shown in Fig. 3.2. Assuming  $C_1$  is negligibility small, the transfer function of the op amp is approximately

$$\frac{V_{\text{out}}}{V_{\text{in}}} = A(s) \approx \frac{g_{m_1} r_{o_1} g_{m_2} r_{o_2} \left(1 - s \frac{C_{C_1} \left(g_{m_1} - g_{m_3}\right)}{g_{m_1} g_{m_2}}\right)}{\left(1 + s r_{o_1} g_{m_2} r_{o_2} C_{C_1}\right) \left(1 + s \frac{C_L}{g_{m_2}}\right)}$$

(3.1)

The DC gain and gain-bandwidth product of the transfer function are identical to those of the two-stage Miller-compensated op amp. The DC gain is

$$A_0 = g_{m_1} r_{o_1} g_{m_2} r_{o_2} \tag{3.2}$$

and the gain-bandwidth is

$$\omega_{\rm T} = \frac{g_{m_1}}{C_{C_1}} \tag{3.3}$$

The poles the op amp are located at

$$\omega_{p_1} = \frac{1}{r_{o_1} g_{m_2} r_{o_2} C_{C_1}} \tag{3.4}$$

$$\omega_{p_2} \approx \frac{g_{m_2}}{C_L} \tag{3.5}$$

Figure 3.2: Small-signal model of a two-stage miller with feedforward-compensated op amp.

The frequency of the zero in Eq. 3.1 is at

$$\omega_{\rm z} = \frac{g_{m_1}g_{m_2}}{C_{C_1}\left(g_{m_1} - g_{m_2}\right)} = \frac{g_{m_2}}{C_{C_1}\left(\frac{g_{m_3}}{g_{m_1}} - 1\right)} = \frac{g_{m_2}}{C_{C_1}\left(k - 1\right)} \tag{3.6}$$

where k is the transconductance ratio between  $A_{v_3}$  and  $A_{v_1}$ . By setting  $g_{m_3} = g_{m_1}$  (k = 1), the RHP zero can be eliminated. Since the transconductance of  $A_{v_1}$  and  $A_{v_3}$  can be matched very accurately in integrated circuits, this is an effective method for offsetting the effects of Miller zeros. More interestingly, by setting  $g_{m_3} > g_{m_1}$  (k > 1), the RHP zero can turned into a LHP zero for the purpose of pole-zero cancellation. To cancel the non-dominant pole,  $\omega_{p_2}$ , with  $\omega_z$ , the transconductance of the feedforward stage should be

$$g_{m_3} = \left(\frac{C_L}{C_{C_1}} + 1\right) g_{m_1} = k_1 g_{m_1} \tag{3.7}$$

Unlike the conventional feedforward compensation technique, the zero from this compensation scheme depends only on parameters that are insensitive to PVT variations. As mentioned previously, the transconductance of gain stages can be matched very accurately. The capacitance of the compensation and load capacitor can also be matched very accurately (on the order of 0.1%) by using MIM (metal-insulator-metal) or MOM (metal-oxide-metal) capacitors, which are commonly available as a technology add-on in advanced CMOS processes [42–44]. Multi-stage op amps incorporating this compensation topology can operate significantly faster than op amps compensated with the conventional nested-miller technique since the gain-bandwidth product of the former is not limited by the frequencies of the non-dominant poles.

#### 3.1.1 Miller Capacitor with Lead Compensation

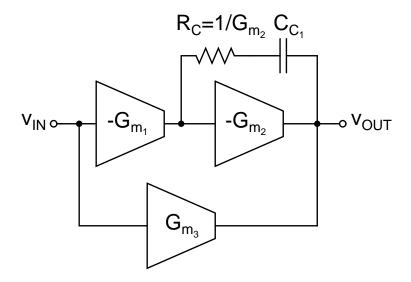

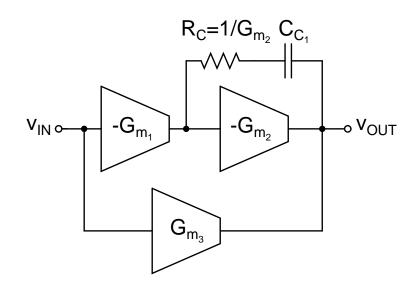

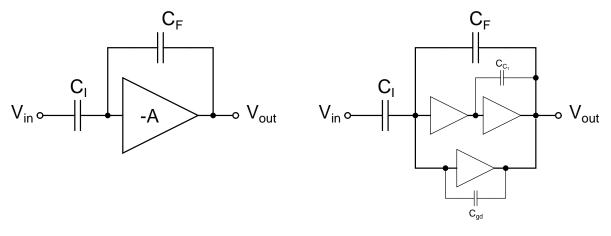

The aforementioned multipath Miller compensation technique can be improved by combining it with other techniques that offset the effects of RHP Miller zeros. Fig. 3.3 illustrates such an example. In this op amp, a resistor of value  $R_C = \frac{1}{G_{m_2}}$  is placed in series with the compensation capacitor  $C_{C_1}$ . This resistor forms a lead compensator and has the effect of reducing the transconductance of  $A_{v_3}$  for pole-zero cancellation.

Figure 3.3: Block digram of a two-stage multipath Miller-compensated op amp with lead compensation.

The transfer function of the circuit in Fig. 3.3 is approximately

$$\frac{V_{\text{out}}}{V_{\text{in}}} = A(s) \approx \frac{g_{m_1} r_{o_1} g_{m_2} r_{o_2} \left(1 + s \frac{g_{m_3} C_{C_1}}{g_{m_1} g_{m_2}}\right)}{\left(1 + s r_{o_1} g_{m_2} r_{o_2} C_{C_1}\right) \left(1 + s \frac{C_L}{g_{m_2}}\right)}$$

(3.8)

The complete derivation of the above transfer function can be found in Appendix A. The DC gain, gain-bandwidth product, and poles of Eq. 3.8 are identical to those of Eq. 3.1. However, the location of the zero has shifted to

$$\omega_{\rm z} = \frac{g_{m_2}}{C_{C_1} \frac{g_{m_3}}{g_{m_1}}} \tag{3.9}$$

A third LHP pole exists in the op amp at

$$\omega_{\rm p_3} = \frac{1}{R_C C_1} \tag{3.10}$$

This pole was neglected in the above calculations as it is at a very high frequency relative to  $\omega_{p_2}$ , assuming  $C_1$  is much smaller than  $C_L$ .

The necessary feedforward transconductance for pole-zero cancellation is

$$g_{m_3} = \frac{C_L}{C_{C_1}} g_{m_1} = k_2 g_{m_1} \tag{3.11}$$

which is smaller than the necessary feedforward transconductance of the op amp without lead compensation (Eq. 3.7). The necessary feedforward transconductance for pole-zero cancellation can be further reduced by choosing a larger  $R_C$ . However, a larger  $R_C$  will lower  $\omega_{p_3}$ , which may lead to a reduced stability margin and degraded settling response.

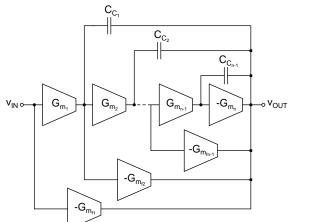

## 3.2 Multi-Stage Op-Amps

Fig. 3.4 depicts two possible multi-stage implementations of multipath Miller compensation.

The compensation topology in Fig. 3.4a is a direct extension of the two-stage multipath Miller compensation scheme shown in Fig. 3.1a. The advantage of this topology lies in its simple design procedure. It can be shown that the necessary transconductance of each feedforward amplifier for pole-zero cancellation is

$$g_{m_{fn}} = \left(\frac{C_L}{C_{C_n}} + 1\right) g_{m_n} \tag{3.12}$$

which is the same as the design equation for the two-stage multpath Miller compensation scheme (Eq. 3.7). The main drawback to this topology is an increased capacitive load since all the Miller capacitors and the feedforward amplifier's output capacitors load the output. An increased load capacitance will not affect the op amp's gain-bandwidth product

(a) Conventional Nested Miller with Feedforward.

(b) Reverse Nested Miller with Feedforward.

Figure 3.4: Block diagrams of multi-stage miller with feedforward compensated op amps.

$(\omega_{\rm T} = \frac{g_{m_1}}{C_{C_1}})$ , but will require more current since the necessary feedforward transconductance for pole-zero cancellation is proportional to the load capacitance,  $C_L$ .

The compensation topology Fig. 3.4b operates on the same pole-zero cancellation principle as the reverse nested Miller with feedforward compensation scheme. The advantage of the reverse nested Miller with feedforward compensation topology is a lower capacitive load at the output, which makes this topology well suited for low-power applications. However, the design process is more complex since the locations of the feedforward zeros cannot be easily determined.

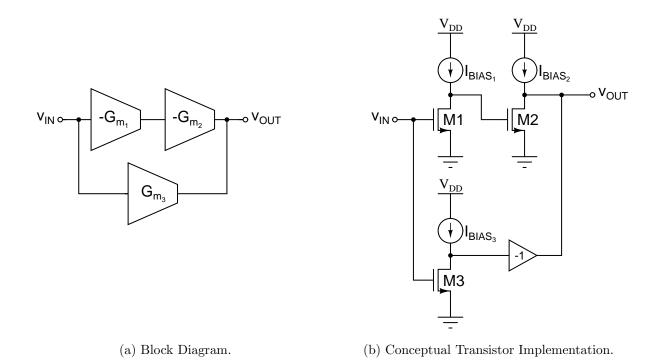

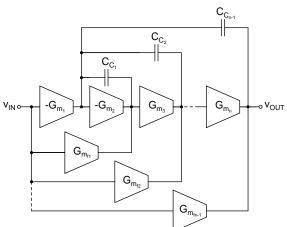

### 3.3 Proposed Design

Fig. 3.5 illustrates a possible transistor implementation of a two-stage multipath Miller compensated op amp with lead compensation in Fig. 3.3. Like most op amps in integrated

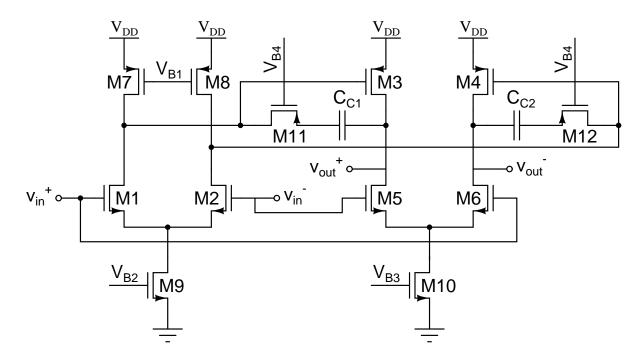

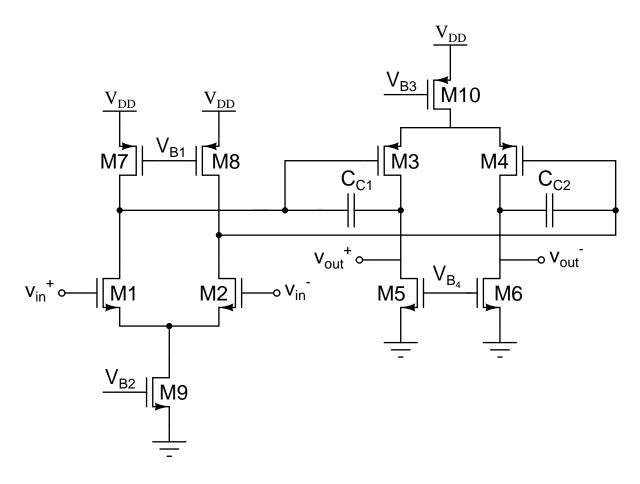

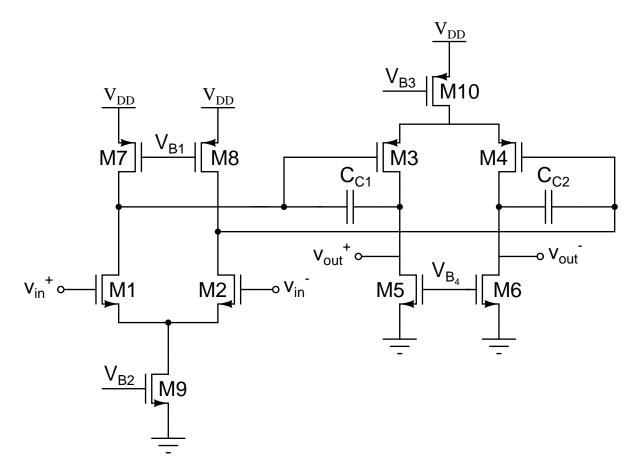

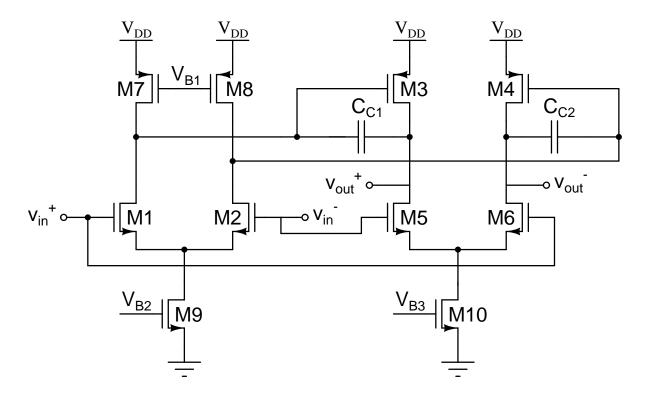

Figure 3.5: A transistor implementation of a two-stage miller and feedforward compensated op amp with lead compensation.

circuits, this op amp was made fully differential in order to take advantage of the benefits of differential signalling, such as improved tolerance to common-mode noise, removal of even-order harmonics, and increased output voltage range [45].

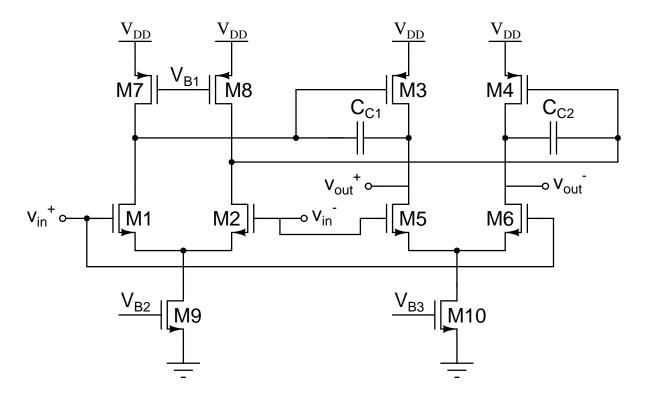

In Fig. 3.5, transistors M1 and M2 form the first transconductance stage  $G_{m_1}$ . Transistors M7 and M8 form the active load of  $G_{m_1}$ . The second transconductance stage,  $G_{m_2}$ , is implemented by transistors M3 and M4. In a conventional two-stage op amp, the output of  $G_{m_1}$  would be connected to the gates of M5 and M6 while M5 and M6 would be biased at a constant gate voltage so that they form the active loads of  $G_{m_2}$ . However, in this op amp, the gates of M5 and M6 are connected to the input so that they form the feedforward transconductance stage  $G_{m_3}$  while the output of  $G_{m_1}$  is connected to the gates of M3 and M4. Combining the active load with the feedforward transconductance stage has a number of advantages over op amps where the two elements are implemented using separate transistors, as in Fig. 2.16b. Firstly, the addition of the feedforward amplifier will not increase the power consumption or area of the op amp. Secondly, the class-AB output increases op amp efficiency and output slew rate. Transistors M9 and M10 implement the tail current sources for  $G_{m_1}$  and  $G_{m_2}/G_{m_3}$ , respectively. These tail current sources are used to increase the common-mode rejection ratio (CMRR) of transistor pairs M1/M2 and M3/M4. Since transistors M3 and M4 are configured as a pseudo differential amplifier, they are very sensitive to common-mode disturbances at the output of  $G_{m_1}$ . This issue can be resolved by regulating the output common-mode of  $G_{m_1}$  with a common-mode feedback (CFMB) circuit. Transistors M11 and M12, biased in the linear region, implement the resistor  $R_C$  in Fig. 3.3. In integrated circuits, transistors biased in the linear region are often used instead of physical resistors as they can be biased such that their resistance will track the transconductance of  $G_{m_2}$  across process and temperature variations [5].

# 3.4 Comparison with Conventional Two-Stage Miller-Compensated Op Amps

#### 3.4.1 Settling Response

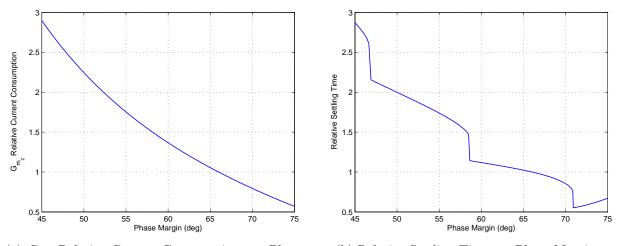

Based on the previous analysis, it was determined that two-stage multipath Miller-compensated op amps have the same DC gain and gain-bandwidth product equations as conventional two-stage Miller-compensated op amps for the same power consumption. However, the closed-loop settling responses of the two types of op amps can be quite different. For the same DC gain and gain-bandwidth product, two-stage multipath Miller-compensated op amps have a constant linear settling time whereas conventional Miller-compensated op amps have a linear settling time that is a function of its phase margin. For moderate-tolow phase margins, the latter will need to consume more current in order to obtain the same linear settling time as the former. This is illustrated in Fig. 3.6a where for the same linear settling time, the second stage of a conventional two-stage Miller-compensated op amp with a 45° phase margin will need to consume almost three times as much current and area as that of a two-stage multipath Miller-compensated op amp. Fig. 3.6b shows that for the same power consumption, the settling time of the conventional two-stage Miller-compensated op amp is almost three times higher than the two-stage multipath Miller-compensated op amp.

(a)  $G_{m_2}$  Relative Current Consumption vs. Phase Margin.

(b) Relative Settling Time vs. Phase Margin.

Figure 3.6: Performance improvement as a function of phase margin.  $A_0 = 80 \text{ dB}$  and  $\epsilon = 0.01 \ (1\%)$ .

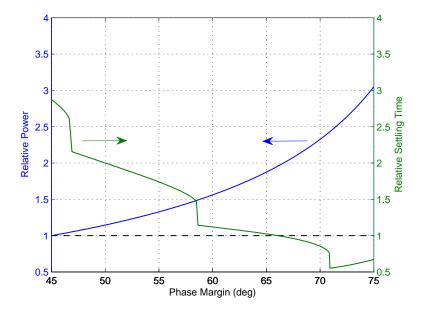

Fig. 3.7 illustrates the power and settling time trade-off two-stage conventional Millercompensated op amps. In the plot, it is assumed that at 45° phase margin, the power consumption of the first and second op amp stage are identical. If the power consumption of the second stage is increased by a factor of 3, then the overall relative power consumption is increased by a factor of 2. The black dashed line in Fig. 3.7 indicates the relative power and settling time achievable with a two-stage multipath Miller-compensated op amp in which a feedforward path is added to a two-stage conventional Miller-compensated op amp with 45° phase margin.

Figure 3.7: Power and settling time trade-off for two-stage conventional Miller-compensated op amps.

#### 3.4.2 Noise

The total output noise of a two-stage conventional Miller-compensated op amp in feedback shown in Fig. 3.8 is

$$\overline{v_{\text{out}_{\text{tot}}}^2} = \frac{2kT\gamma\left(1 + \frac{g_{m_7}}{g_{m_1}}\right)}{\beta C_{C_1}} \left(1 + \frac{\beta C_{C_1}\left(1 + \frac{g_{m_5}}{g_{m_3}}\right)}{(C_{C_1} + C_L)\left(1 + \frac{g_{m_7}}{g_{m_1}}\right)}\right)$$

(3.13)

where k is the Boltzmann constant, T the is temperature in kelvin, and  $\gamma$  is the effective channel resistance, which is approximately 2/3.

The total output noise of a two-stage multipath Miller-compensated op amp in feedback shown in Fig. 3.9 is

$$\overline{v_{\text{outtot}}^2} = \frac{2kT\gamma\left(1 + \frac{g_{m_7}}{g_{m_1}}\right)\beta}{\beta C_{C_1}\left(1 + \frac{\beta g_{m_5}}{g_{m_3}}\right)} \left(1 + \frac{\beta C_{C_1}\left(1 + \frac{g_{m_5}}{g_{m_3}}\right)}{(C_{C_1} + C_L)\left(1 + \frac{g_{m_7}}{g_{m_1}}\right)}\right)$$

(3.14)

Eq. 3.14 and 3.13 assume that the transistors have infinite output resistance  $(r_o = \infty)$ and that the effects of the Miller capacitor is unilateral (i.e. the Miller zero is neglected). The complete derivation of the total output noise for the two op amps can be found in Appendix C.

The lower total input-referred noise for the multipath Miller-compensated op amp, by a factor of  $1 + \beta g_{m_5}/g_{m_3}$ , can be explained by observing the approximate input-referred noise spectral density plots of the two op amps, which are shown in Fig. 3.10 where the transistors are assumed to have finite output resistance. At low frequencies, the noise of the second stage for both op amps is attenuated by the gain of the first stage,  $A_1$ . Beyond the frequency  $\omega_z$ , the gain of the first stage will decrease and hence the noise of the second stage will increase. For the conventional Miller-compensated op amp, the noise of the

Figure 3.8: Circuit diagram of a two-stage conventional Miller-compensated op amp.

second stage will increase for all frequencies since the gain of the first stage collapses at high frequencies. It should be noted that the total input-referred noise itself is bounded because the noise bandwidth (NBW) is finite. For the multipath Miller-compensated op amp, the noise of the second stage will increase beyond the frequency  $\omega_z$  but will flatten at the frequency  $\omega_p$  because after  $\omega_p$ , the noise is input-referred through the feedforward stage instead of the first op amp stage.

Noise simulations were performed on complete transistor implementations of a two-

Figure 3.9: Circuit diagram of a two-stage multipath Miller-compensated op amp.

stage conventional and multipath Miller-compensated op amp and the results are plotted in Fig. 3.11. For the latter op amp, the ratio of  $\beta g_{m_5}/g_{m_3}$  was determined to be 1.1. According to Eq. 3.13-3.14, the total output noise power of the multipath Miller-compensated op amp should be approximately half that of the conventional Miller-compensated op amp. The results of the noise simulations, shown in Fig. 3.11, agree with the above noise analysis.

### 3.4.3 Output Slew Rate

Fig.3.12 shows the output stage of a two-stage conventional Miller-compensated op amp when it is slewing. In this condition, one of the input transistors is turned off and all the

(a) Conventional Miller-compensated op amp.

(b) Multipath Miller-compensated op amp.

Figure 3.10: Approximate input-referred noise spectral density of two-stage op amps in feedback.

tail bias current flows through the other transistor. Since the load transistors will conduct a constant current of  $I_B/2$  on both branches, the maximum differential output slew current is  $I_B/2$ .

Fig.3.13 shows the output stage of a two-stage multipath Miller-compensated op amp when it is slewing. In this condition, one of the input transistors is turned off and all the tail bias current flows through the other transistor. Furthermore, one of the *load* transistors is also turned off while the opposite *load* transistor will conduct a current of  $I_L$ , where  $I_L \ge I_B/2$ . The imbalance of currents flowing through the output will cause the common-mode feedback (CMFB) circuit to force the tail current  $I_B$  to be equal to  $I_L$  by adjusting the voltage  $V_{\text{CMFB}}$ . Hence, the maximum output slew rate is  $I_L$ . Since  $I_L$  can be more than an order of magnitude higher than  $I_B/2$ , the slew rate of a two-stage multipath Miller-compensated op amp should be much higher than that of a two-stage conventional

Figure 3.11: Simulated integrated output noise power of two two-stage op amps.

Figure 3.12: A two-stage conventional Miller-compensated op amp exhibiting slew-limited behaviour.

Miller-compensated op amp. The exact value of  $I_L$  depends on the bias conditions of the *load* transistors.

Figure 3.13: A two-stage multipath Miller-compensated op amp exhibiting slew-limited behaviour.

### 3.5 Summary

Multipath Miller-compensated op amps improve stability by introducing a feedforward path in the op amp topology. By tuning the transconductance of this feedforward path, it is possible to place LHP zeros to cancel out the effects of non-dominant poles in multi-stage op amps. Since the locations the LPH zeros and poles are set by ratios of transconductors and capacitors, this scheme is insensitive to PVT variations.

The proposed two-stage multipath Miller-compensated op amp architecture, as discussed in Section 3.3, can reduce power consumption and improve closed-loop settling time over two-stage conventional Miller-compensated op amps. The proposed multipath op amp also has the benefits of reduced closed-loop input-referred noise and increased output slew rate. Finally, the proposed feedforward transconductance stage can be implemented without any power or area penalty.

# Chapter 4

# System-Level Design