# Amorphous Silicon Dual Gate Thin Film Transistor & Phase Response Touch Screen Readout Scheme for Handheld Electronics Interactive AMOLED Displays

by

Salman Shaikh Humayun Kabir

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2011

©Salman Shaikh Humayun Kabir 2011

# **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

# Abstract

Interactive handheld electronic displays use hydrogenated amorphous silicon (a-Si:H) thin film transistor (TFT) as a backplane and a Touch Screen Panel (TSP) on top as an input device.

a-Si:H TFT used in active matrix liquid crystal displays (LCDs) in which the TFT acts as pixel switches. The low mobility and instability of a-Si:H TFT threshold voltage are major two issues for driving constant current as required for organic light emitting diode (OLED) displays. Low mobility is compensated by increasing transistor width or resorting to more expensive or less reliable material TFTs. On the other hand, the ever increasing threshold voltage degrades the drain current under electrical operation causing OLED display to dim.

Mutual capacitive TSP, the current cell phone standard, requires two layers of metals and a dielectric to be put in front of the display, further dimming the device and adding to visual noise due to sun reflection, not to mention increased integration cost and decreased yield.

This thesis focuses on the aforementioned technological hurdles of a handheld electronic display by proposing a dual-gate TFT used as an OLED current driving TFT and a novel phase response readout scheme that can be applied to a one metal track TSP.

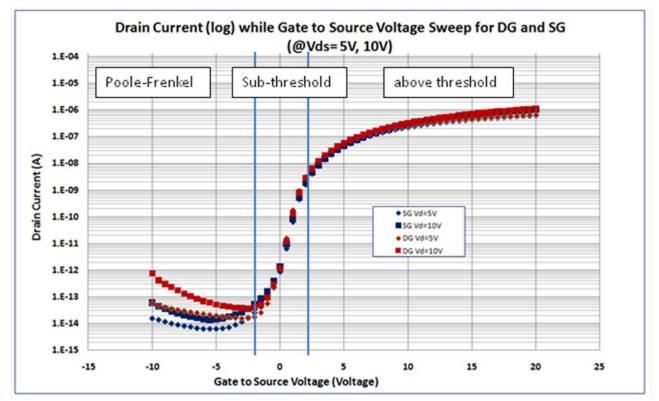

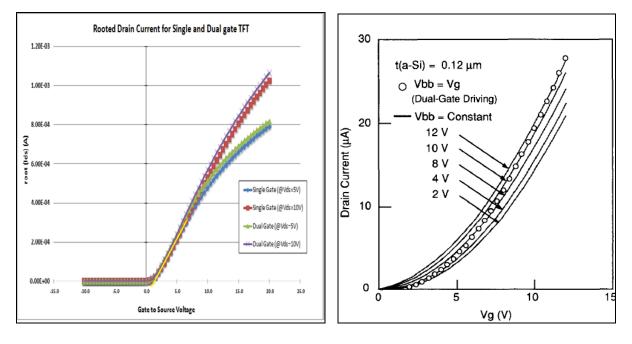

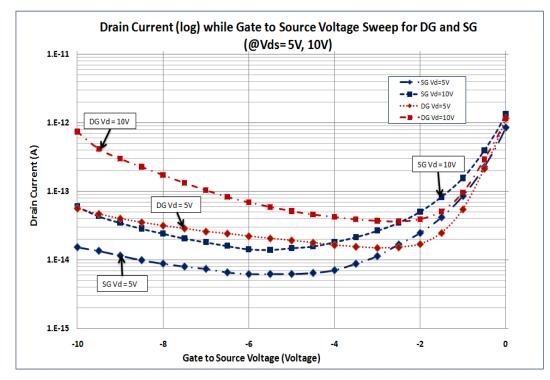

Our dual-gate TFT has shown on average 20% increase in drive current over a single gate TFT fabricated in the same batch, attributed to the aid of a top channel to the convention bottom channel TFT. Furthermore the dual gate TFT shows three times the Poole-Frenkel current than the single gate TFT attributed to the increase in gate to drain overlap.

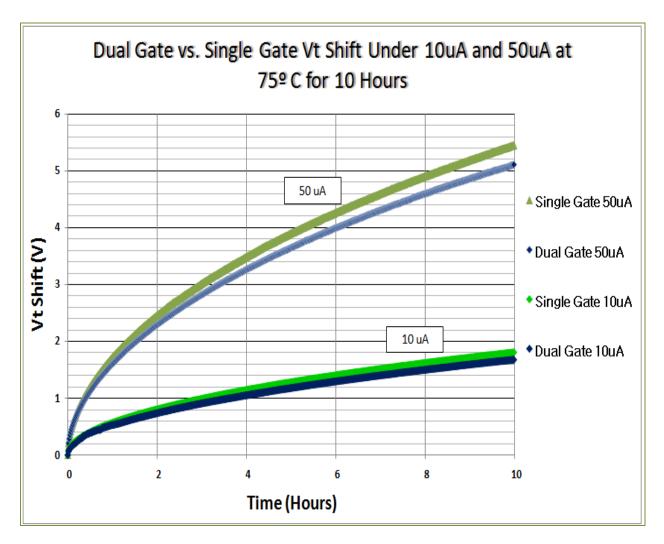

The dual-gate TFT shows a 50% improvement in threshold voltage shift over a single gate TFT at room temperature, but only ~8% improvement under 75°C. This is an important observation as it shows an accelerated threshold voltage shift in the dual-gate. This difference in the rate of threshold voltage change under varying temperature is due to the difference in interface states at the top and bottom channel. Using these results, the dominant

mechanism behind threshold voltage shift is attributed to Libsch and Kanicki's multi-level temperature dependant dielectric trapping model.

The phase response TSP readout scheme requires IC only on one side of the display. Its unique design consisting provides touch signal readability and digitization without an A/D converter. Phase response readout out scheme, using Cadence Spectre simulation, showed that both touch occurrence and touch position can be obtained using only one metal layer.

# Acknowledgements

First off, I would like to thank God for giving me such a wonderful opportunity to gain knowledge in a field that I have passion for. For that I sincerely hope that I can use what I have learned at the University of Waterloo to benefit mankind.

Subsequently, I would like to thank Professor Andrei Sazonov for giving me a chance to work with him in this field of large area electronics, and simply always being nice and cheerful towards me. I am greatly indebted to professor Siva Sivoththaman and Professor William Wong for supporting me in Professor's Sazonov's absence when it was greatly needed. Your support has made this thesis work possible. I would like to follow this up with thanking my reviewers: Professor Sivoththaman, Professor Wong and Professor Karim.

I have been extremely fortunate to be under the care of Wendy Boles for all my academic and financial matters. She was the first one to truly welcome me to the University of Waterloo in person and I will never forget that. She will be dearly missed.

Also, Richard Barber, who was always there to support me in and out of the G2N lab.

I would like to thank Dr. Reza Chaji, Dr. Maryam Moradi and Professor Arokia Nathan from Ignis Innovations for their ideas, motivation, training, mentoring, and going out of their way for our academic well being. Also, a lot of thanks to them for providing the necessary equipment and material that was critical towards my research progress.

I would like to thank K M Azizur Rahman for being the first one to motivate me to do a Master's in Electrical Engineering that involved Electronic Devices. Without that motivation and support, I would not be here today. Aziz, I hope you change the world for the better with your further research in Solar cells. A special gratitude must go towards Melissa, who I had a pleasure of working and learning with; who also reviewed this thesis. Wish you all the success in the future. It would be hard to replace a friend like you.

Also, my good old office mate and great friend/advisor Na'el Suwan, who alone is a wealth of knowledge that I thankfully, got a piece of. And my new office mate, Geoffrey Cheung, who I can't help but advice as I do to my younger brother.

I would also like to thank my group members: Minoli Pathirane and Ehsan Fathi, whom I have had the pleasure to work with and go to an MRS Conference with and have good complaint sessions.

I would also like to thank Zhao Li, Hassan Sarbishaei, Noman Hai and Karan Chahal for all the intellectual conversations we had shared. I have learned a great deal from you guys, especially with analog circuits. Students learn best from students, and you are a prime example of that.

My experience would not be the same without meeting the genius's of Waterloo: Majid Gharghi, Arash Akhavan Fomani, Mohammed Esmaeili Rad and Nino Zahirovic, with whom I have had great intellectual discussions, got useful advice and had very good laughs with. They were my role models in both academic and non-academic aspects.

I would like to thank Professor Sachdev's students: Adame Neale, Jaspal Singh and David Li, who I have had great discussions with during my chip tapeput; as we were all taping out chips together.

I would also like to thank friends from Professor Karim's group: Dr. Hasibul Majid, Dr. Hadi Izadi, Michal Adachi, Umar Shafique, Mohammed Yazdandoost, Dali Wu, Bahman Hadji Yuen Fen, Shiva for all the advice, lunch, dinner that we have shared. Finally, I would like to thank my family for their unconditional support towards my success. I only hope that I learn from their contribution so I can myself provide such support towards someone else's success one day. It will surely be a great challenge. But all these challenges can be overcome with love and dedication.

Dedication

To Ammu, Abbu, Apuni, Choto Apu, Raeed and Rizu bhai for all your patience, love and support.

# **Table of Contents**

| AUTHOR'S DECLARATIONii                                                    |

|---------------------------------------------------------------------------|

| Abstractiii                                                               |

| Acknowledgements                                                          |

| Dedicationvii                                                             |

| Table of Contentsix                                                       |

| List of Figuresxi                                                         |

| List of Tablesxvi                                                         |

| Chapter 1 Introduction 1                                                  |

| 1.1 Displays and Touch Screen Electronics Niche 1                         |

| 1.2 Active Matrix Backplane Technologies                                  |

| 1.2.1 Matrix Displays                                                     |

| 1.2.2 Passive Matrix Displays                                             |

| 1.2.3 Active Matrix Displays5                                             |

| 1.2.4 Drive TFT Implementation and Challenges for AMOLED Displays         |

| 1.2.5 Single Gate TFTs: Bottom Gate vs. Top Gate                          |

| 1.2.6 Industrialization and Manufacturing Capital Cost11                  |

| 1.2.7 Dual-gate TFTs                                                      |

| 1.2.8 Contributions from Dual-Gate TFT13                                  |

| 1.3 Touch Screen Panel (TSP)14                                            |

| 1.3.1 Resistive Touch Screen Panel                                        |

| 1.3.2 Capacitive Touch Screen Panel                                       |

| 1.3.3 Phase Response Touch Readout Method                                 |

| 1.3.4 Contribution from a Phase Response Touch Screen Panel               |

| 1.4 Thesis Organization                                                   |

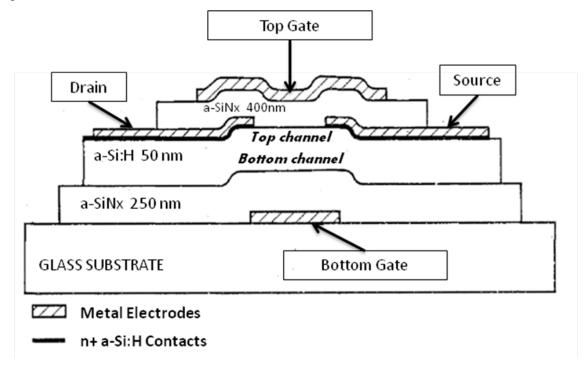

| Chapter 2 Dual-Gate TFT Fabrication, Operation and Superior Current Drive |

| 2.1 Material characteristics of amorphous silicon                         |

| 2.2 Device Fabrication                                            |         |

|-------------------------------------------------------------------|---------|

| 2.2.1 Back Channel Etch (BCE) Process Dual Gate TFT Fabrication   |         |

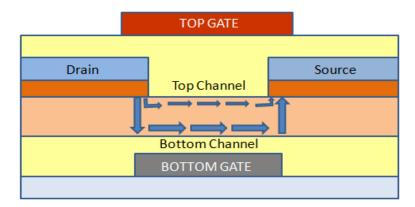

| 2.3 Dual-Gate TFT Device Operation                                |         |

| 2.3.1 Top Channel and Bottom Channel Difference                   |         |

| 2.3.2 Dual Gate TFT Threshold Voltage                             |         |

| 2.3.3 Dual Gate TFT Above Threshold Current Conduction            |         |

| 2.3.4 Drive Current Results and Discussion                        |         |

| 2.3.5 Leakage Current                                             |         |

| 2.3.6 Dual Gate and Single Gate Transfer Characteristics          |         |

| 2.3.7 Poole Frenkel Current                                       |         |

| 2.4 Summary and Future Work                                       |         |

| Chapter 3 a-Si:H TFT Dominant Instability Mechanism and Improveme | ents 47 |

| 3.1 Defect State Creation in Amorphous Silicon                    |         |

| 3.2 Charge Trapping in Silicon Nitride Dielectric                 |         |

| 3.3 Constant Voltage & Constant Current Stress Tests              |         |

| 3.4 Constant Current $V_{t-shift}$ Results and Discussion         |         |

| 3.4.1 Starting Bias Voltage                                       |         |

| 3.4.2 Definition of $V_{t-shift}$                                 | 55      |

| 3.5 Summary and Future Work                                       | 60      |

| 3.6 Future Device Improvement                                     | 61      |

| Chapter 4 Phase Response Touch Screen Panel Readout Scheme        |         |

| 4.1 Conventional Voltage Readout Scheme                           |         |

| 4.2 Novel Phase Response Readout Scheme                           |         |

| 4.2.1 Touch Signal Phase Shift                                    |         |

| 4.2.2 Phase Response Design Consideration                         |         |

| 4.2.3 One-Sided Readout Circuit                                   |         |

| 4.3 Phase Response Readout System Results                         |         |

| 4.4 Future Work                                                   |         |

| Chapter 5 Conclusion                                              |         |

|                                                                   |         |

| Appendix A Dual-Gate TFT MEDICI Simulation Code | . 84 |

|-------------------------------------------------|------|

| Bibliography                                    | . 87 |

# List of Figures

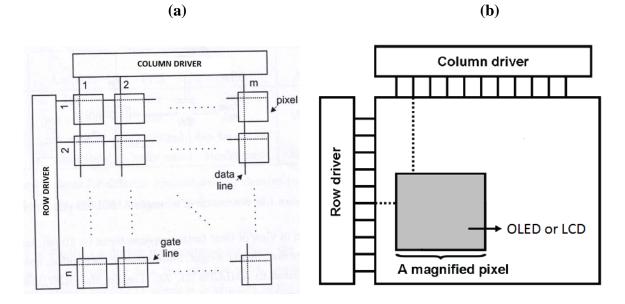

| Figure 1.1: a) Display Matrix Schematic with m x n pixels [25]. b) Display Matrix with a         |

|--------------------------------------------------------------------------------------------------|

| selected pixel [23]                                                                              |

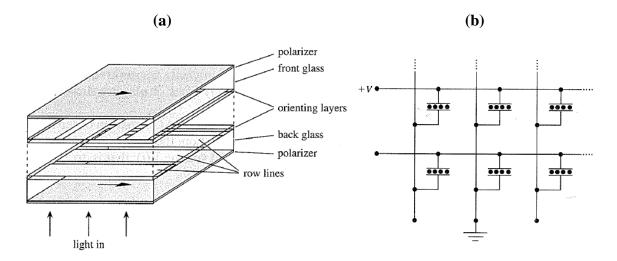

| Figure 1.2: a) PMLCD Display construction with a) perpendicular row and column lines             |

| bonded with Optical polarizers to the front and back surfaces. b) PMLCD equivalent               |

| circuit. A pixel is addressed by applying a voltage +V. Column lines that are not                |

| selected are floating, while the column that is selected is grounded [29]                        |

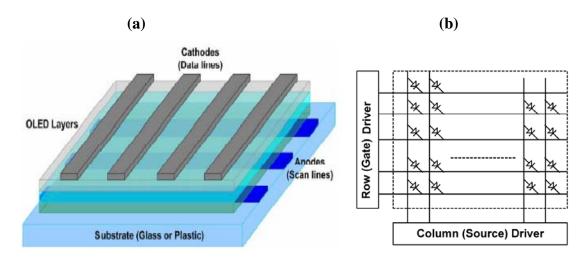

| Figure 1.3: a) PMOLED Display and b) its equivalent circuit [31]                                 |

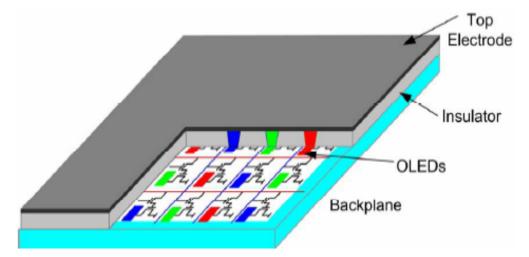

| Figure 1.4: Conventional bottom emission AMOLED display that has a TFT backplane                 |

| (white). The light emitted by the OLEDs go through the clear bottom glass (light blue).          |

| [31]                                                                                             |

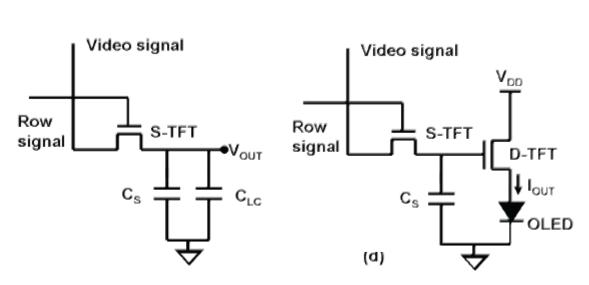

| Figure 1.5: a) LCD pixel circuit schematic where S-TFT is the switch TFT, $C_{LC}$ is the liquid |

| crystal capacitor and $C_S$ is the storage capacitance. b) OLED display pixel circuit            |

| schematic where S-TFT is the switch TFT and D-TFT is the Drive TFT. [32]                         |

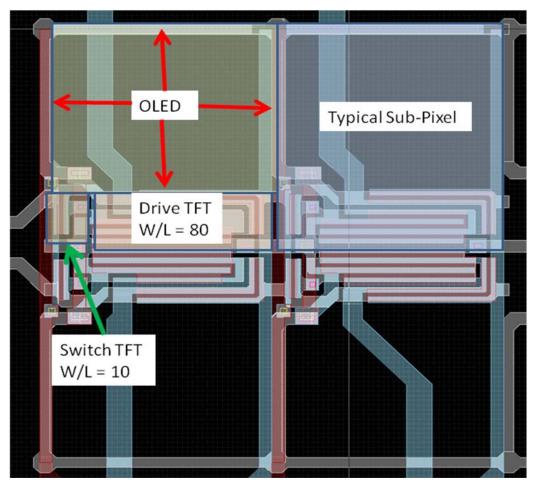

| Figure 1.6: AMOLED pixel circuit with four sub-pixels, each sub-pixel dedicated for Red,         |

| Green Blue and White (RGBW). Notice that the Drive TFT takes up ~15-20% of the                   |

| pixel                                                                                            |

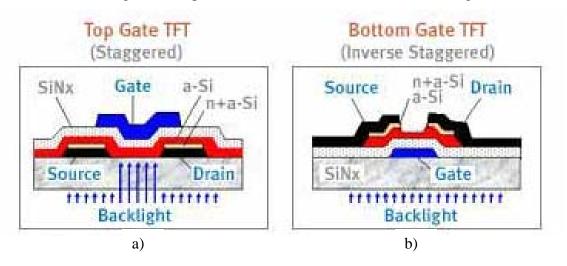

| Figure 1.7: Cross-section of a) Top Gate TFT and b) bottom gate TFT. It also illustrates that    |

| the gate is used as a shield against backlight from penetrating the a-Si layer to cause          |

| photo-induced degradation known as the Staebler and Wronski Effect. [6]9                         |

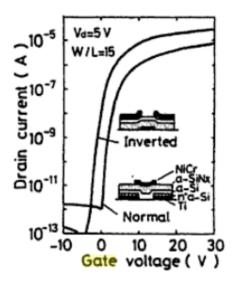

| Figure 1.8: Transfer characteristics of top and bottom gate a-Si:H TFTs with same film           |

| deposition condition [7]10                                                                       |

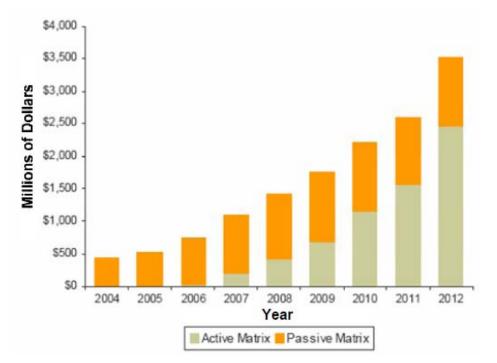

| Figure 1.9: Present and Expected OLED market [27] 11                                             |

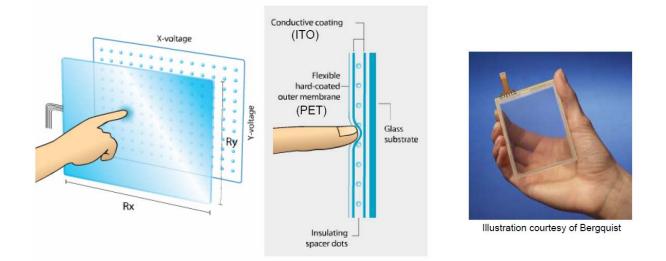

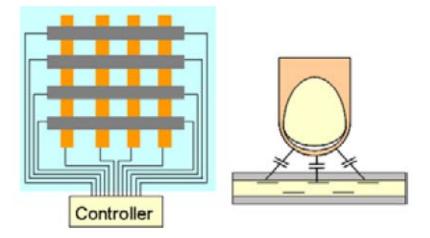

| Figure 1.12: a) Resistive touch screen front view and b) side view while being touched to        |

| input signal and c) real life example [28]15                                                     |

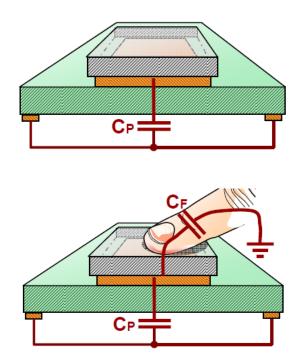

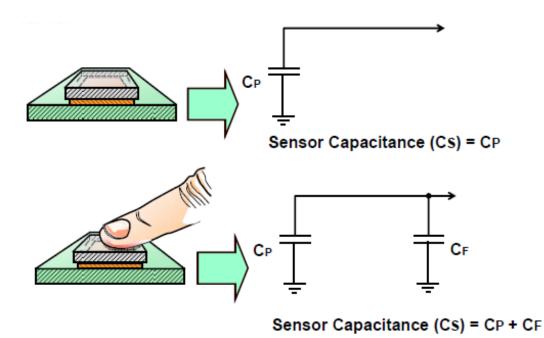

| Figure 1.13a) self-capacitance touch pad showing its intrinsic capacitance and b) increase in    |

| capacitance due to the touch of a finger (grounded conductor) [42]16                             |

| Figure 1.14: a) self-capacitance touch pad showing its intrinsic capacitance and b) increase in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| capacitance due to the touch of a finger (grounded conductor) [43]17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 1.15: a) a mutual capacitive TSP and b) multiple cell detection of finger touch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| allowing higher touch resolution. [24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

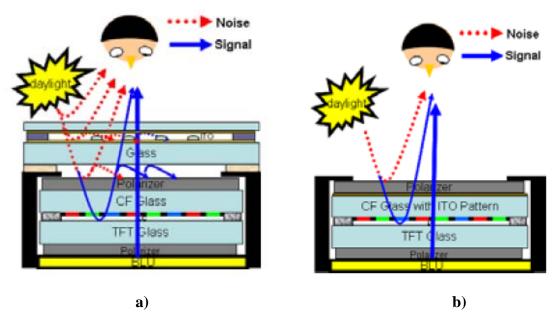

| Figure 1.16: a) Standard display with external TSP which has high visual reflection and b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| integrated TSP with reduced visual reflection [24]18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

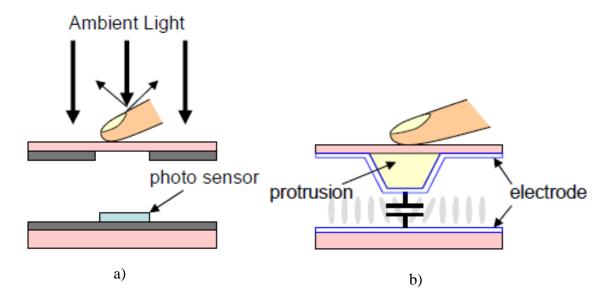

| Figure 1.17: Hybrid TSP integrated with AMLCD with a) photosensing and b) capacitive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| sensing method [15]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

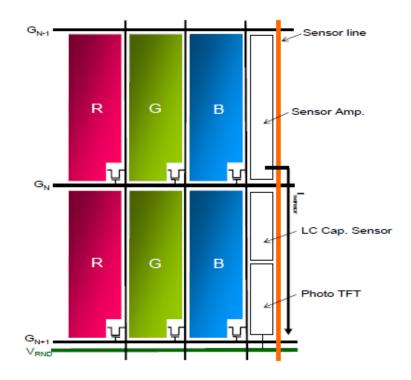

| Figure 1.18: Hybrid TSP integrated with hybrid AMLCD on the same panel [15] 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

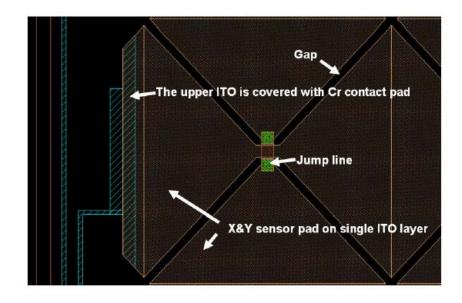

| Figure 1.19: a) Conventional Mutual Capacitive TSP with separate x and y metal track                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| sensors layers with a dielectric in between and b) newly designed TSP with x and y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| metal track sensors on the same layer [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 1.20: Top view of the mutual capacitive TSP with x and y sensors on the same layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| with jumpers to avoid short [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

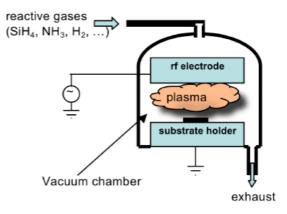

| Figure 2.1: A Plasma Enhanced Chemical Vapour Depostion (PECVD) system [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2.1: A Plasma Enhanced Chemical Vapour Deposition (PECVD) system [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

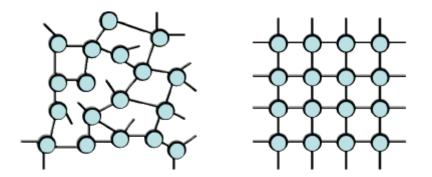

| Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

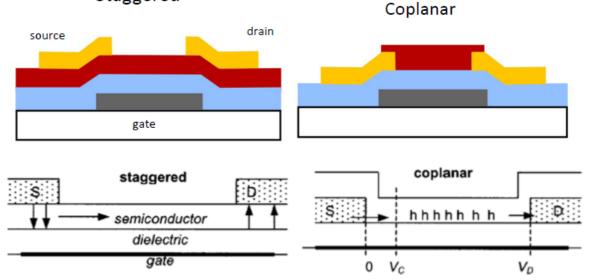

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li> <li>[32]</li> <li>[33]</li> <li>[34]</li> <li>[35]</li> <li>[35]</li> <li>[36]</li> <li>[37]</li> <li>[38]</li> <li>[38]</li> <li>[39]</li> <li>[39]</li> <li>[39]</li> <li>[30]</li> <li>[31]</li> <li>[32]</li> <li>[32]</li> <li>[33]</li> <li>[34]</li> <li>[35]</li> <li>[35]</li> <li>[36]</li> <li>[37]</li> <li>[38]</li> <li>[39]</li> <li>[39]</li> <li>[39]</li> <li>[30]</li> <li>[30]</li> <li>[31]</li> <li>[32]</li> <li>[32]</li> <li>[33]</li> <li>[34]</li> <li>[35]</li> <li>[35]</li> <li>[36]</li> <li>[37]</li> <li>[38]</li> <li>[39]</li> <li>[39]</li> <li>[39]</li> <li>[30]</li> <li>[30]</li> <li>[31]</li> <li>[32]</li> <li>[33]</li> <li>[34]</li> <li>[35]</li> <li>[35]</li> <li>[35]</li> <li>[36]</li> <li>[37]</li> <li>[38]</li> <li>[38]</li> <li>[39]</li> <li>[39]</li> <li>[30]</li> <li>[30]</li> <li>[31]</li> <li>[32]</li> <li>[33]</li> <li>[34]</li> <li>[35]</li> <li>[35]</li> <li>[35]</li> <li>[36]</li> <li>[37]</li> <li>[38]</li> <li>[38]</li> <li>[39]</li> <li>[39]</li> <li>[39]</li> <li>[30]</li> <li>[31]</li> <li>[32]</li> <li>[32]</li> <li>[33]</li> <li>[34]</li> <li>[35]</li> <li>[35]</li> <li>[35]</li> <li>[36]</li> &lt;</ul> |

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Figure 2.2: a) Amorphous silicon atomic structure and b) Crystalline silicon atomic structure [32]</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

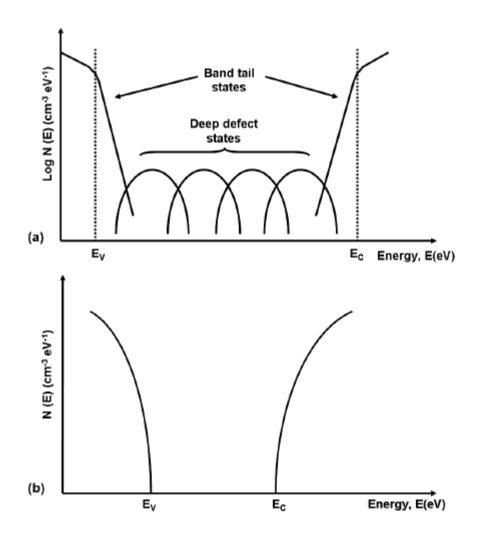

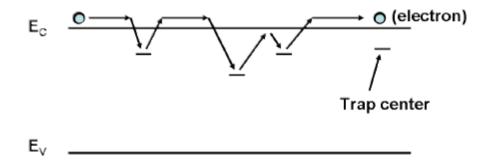

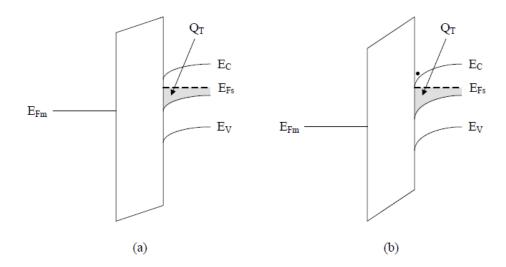

| Figure 2.9: a) Band diagram of a-Si:H TFTs with high channel trap states. a) band bending      |

|------------------------------------------------------------------------------------------------|

| due to small positive gate bias that leads to most of the free electron being captured,        |

| and b) larger positive gate bias leading enough band bending to have sufficient free           |

| electrons in the conduction band (or band tail) [29]                                           |

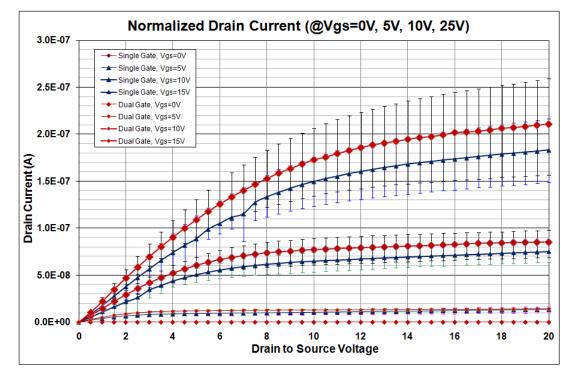

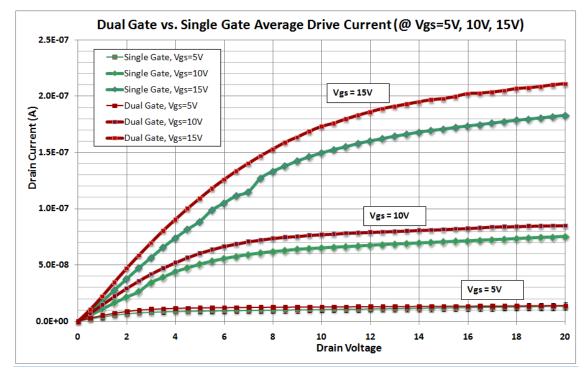

| Figure 2.10: Normalized Drain Current for $Vgs = 0V$ , 5V, 10V and 10V with error bars 35      |

| Figure 2.11: Average Dual Gate and Single Gate Drain Current                                   |

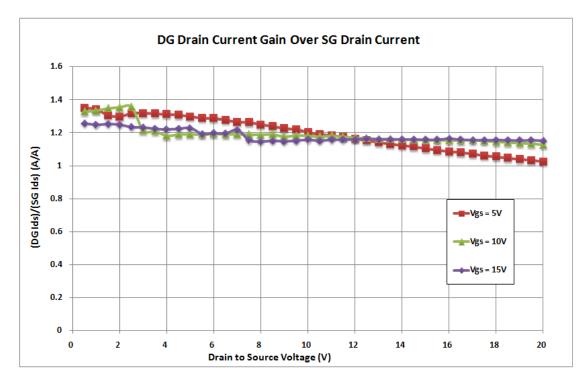

| Figure 2.12: Average Dual Gate TFT drain current gain over Single Gate TFT                     |

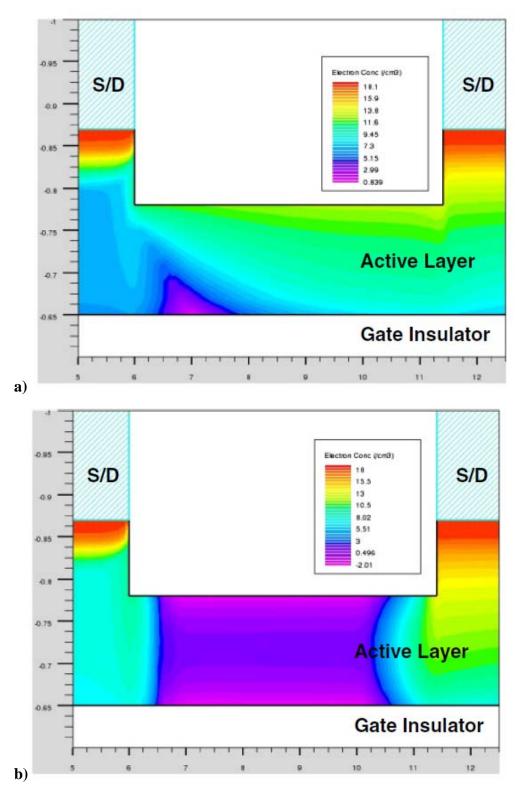

| Figure 2.13: Simulation of electron density in a) single gate, and b) dual gate TFT [41] 38    |

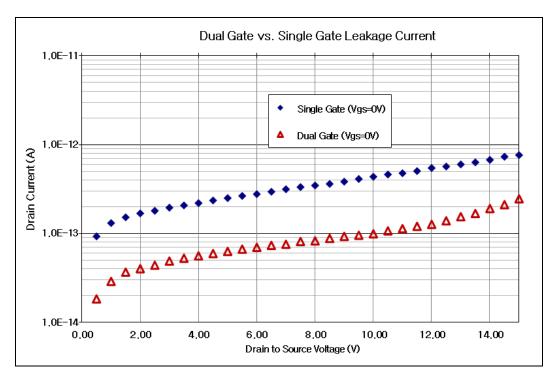

| Figure 2.14: Single Gate and Dual Gate TFT leakage current                                     |

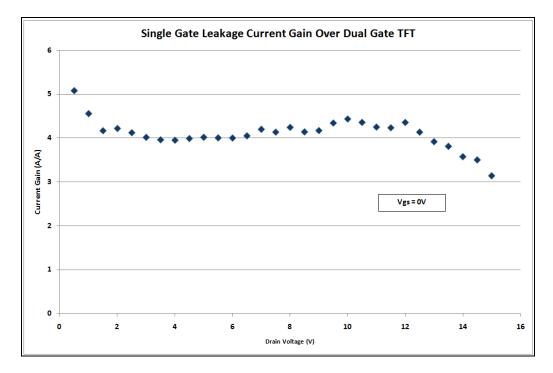

| Figure 2.15: Single Gate leakage current gain over a Dual Gate TFT leakage current             |

| Figure 2.16: Single and Dual Gate I-V curve at drain voltages of 5V and 10V 40                 |

| Figure 2.17: a) Threshold voltage extraction (yellow line) from a root drain current graph for |

| both Dual gate and Single Gate TFTs, and b) previous work showing that shorted dual            |

| gate TFT turn on at the same voltage as a single gate TFT [40]                                 |

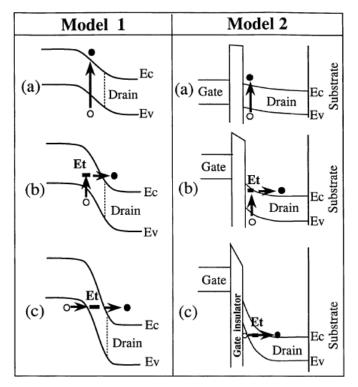

| Figure 2.18: Band diagrams for two models illustrating Pool-Frenkel current where a) is for    |

| weak E-field, b) is for medium E-field and c) is for high E-Field [54]                         |

| Figure 2.19: Poole-Frenkel current conduction for both dual (red) and single (blue) gate TFTs  |

|                                                                                                |

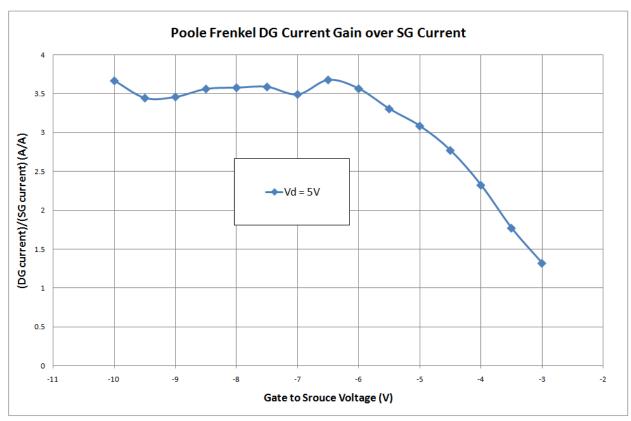

| Figure 2.20: Dual Gate Poole-Frenkel current gain over Single Gate Poole-Frenkel Current44     |

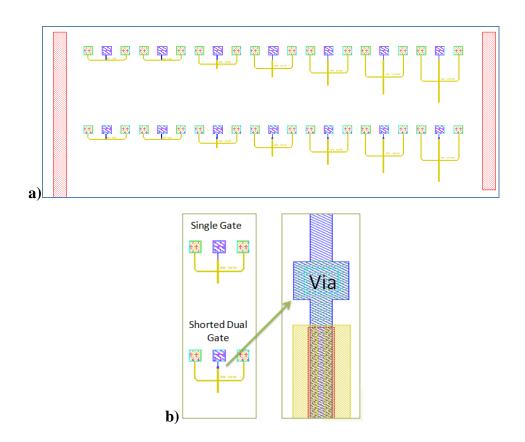

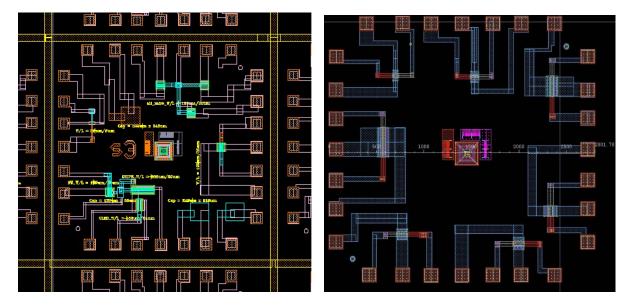

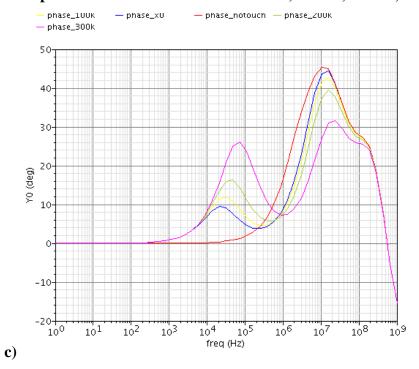

| Figure 2.21: Mask design of new Dual Gate TFTs using Cadence Virtuoso CAD tool 46              |

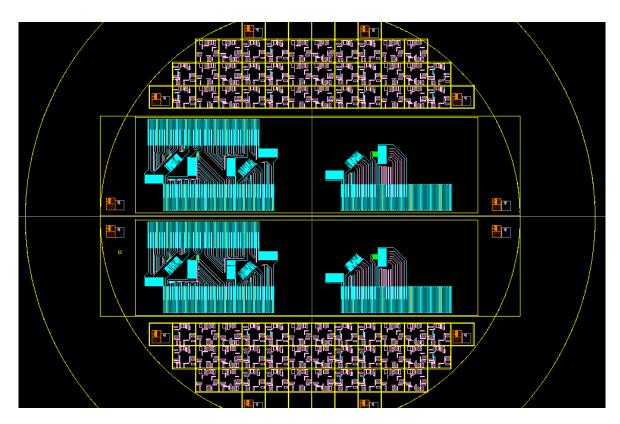

| Figure 2.22: Full wafer mask design                                                            |

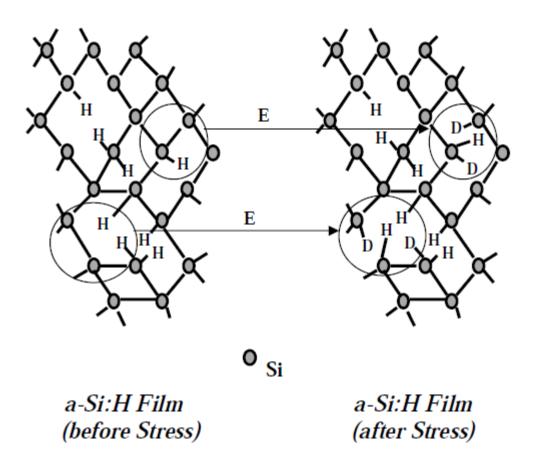

| Figure 3.1: Atomic structure of a-Si:H film before and after stress, where D and H denote the  |

| dangling bonds and hydrogen atoms respectively. E - represents the weak Si-Si bond             |

| breaking associated with Hydrogen motion. [54]49                                               |

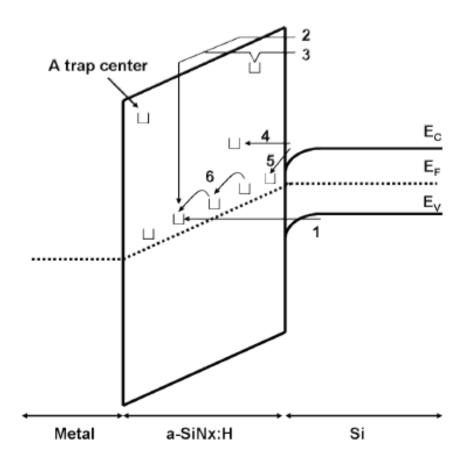

| Figure 3.2: Charge trapping mechanisms: 1- direct tunnelling from valence band, 2- Fowler-     |

| Nordheim injection, 3- trap-assisted injection, 4- constant-energy tunnelling from             |

| silicon conduction band, 5- tunnelling from conduction band into traps close to $E_F$ , and    |

| 6- hopping at the Fermi level [49]50                                                           |

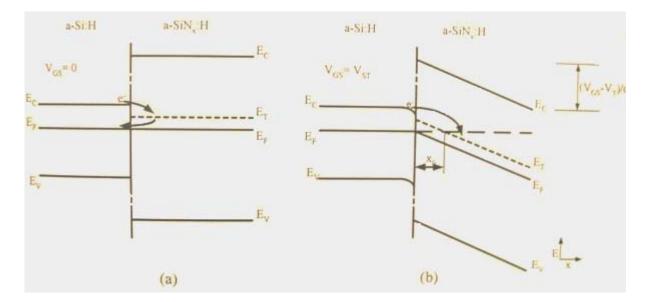

| Figure 3.3: Energy-band diagram at the a-Si:H/dielectric interface at a) Vgs=0V and b)                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Vgs=Vst where Vst is the stress voltage bias. [37]                                                                                            |

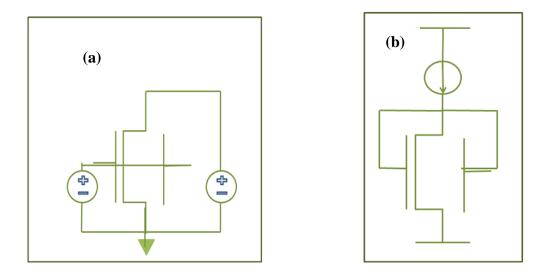

| Figure 3.4: Dual gate TFT stress test with a) constant voltage bias and b) constant current                                                   |

| bias                                                                                                                                          |

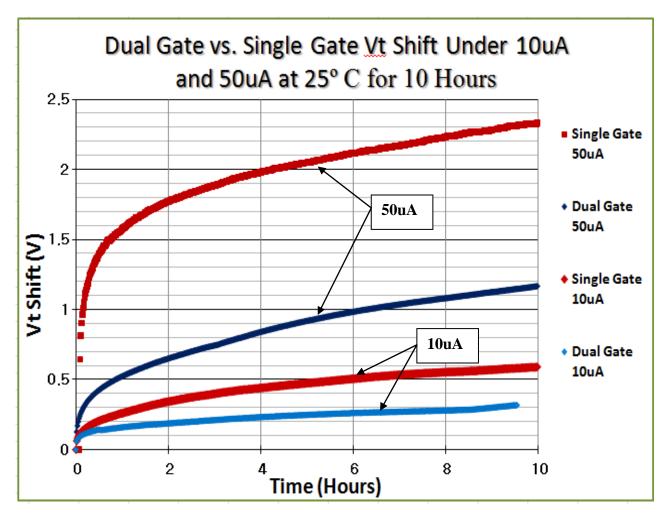

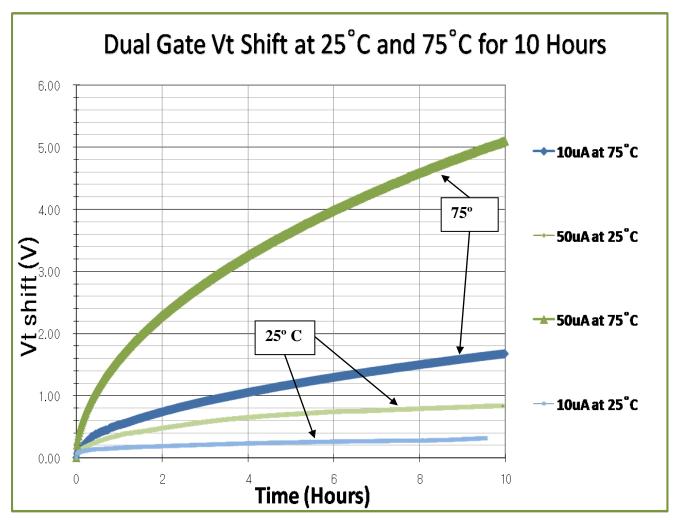

| Figure 3.5: Dual gate and Single gate $V_{t-shift}$ comparison under 10uA and 50uA at 25°C for                                                |

| 10 hours                                                                                                                                      |

| Figure 3.6: Dual gate $V_{t-shift}$ comparison under 10uA and 50uA at 25°C and 75°C for 10                                                    |

| hours                                                                                                                                         |

| Figure 3.7: Dual gate and Single gate $V_{t-shift}$ comparison under 10uA and 50uA at 75°C for                                                |

| 10 hours                                                                                                                                      |

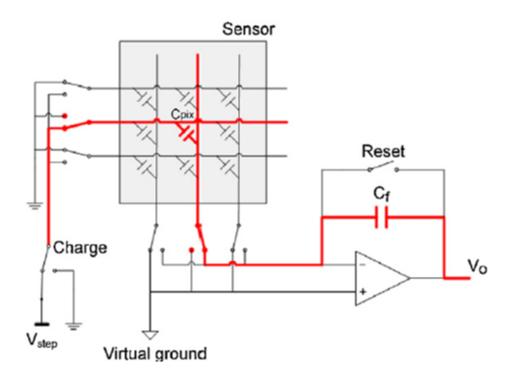

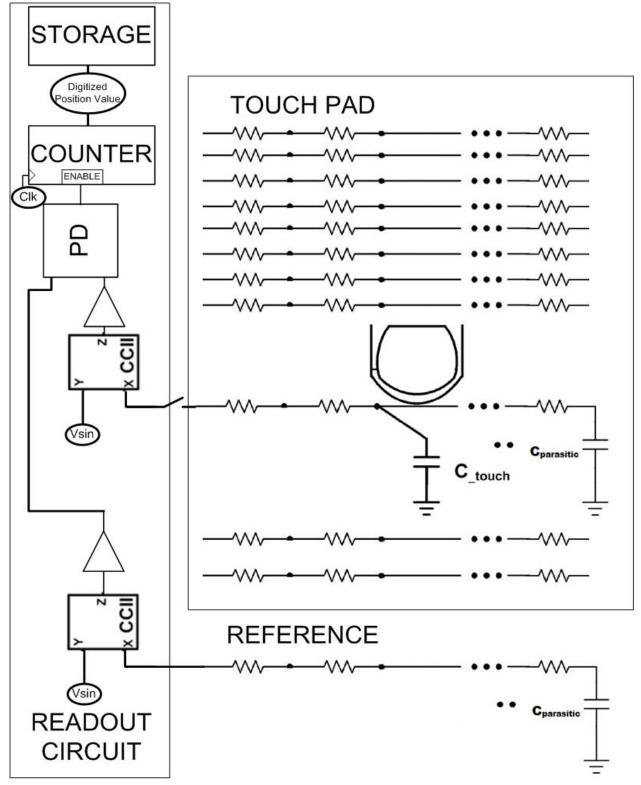

| Figure 4.1: Voltage readout scheme for a mutual capacitive TSP                                                                                |

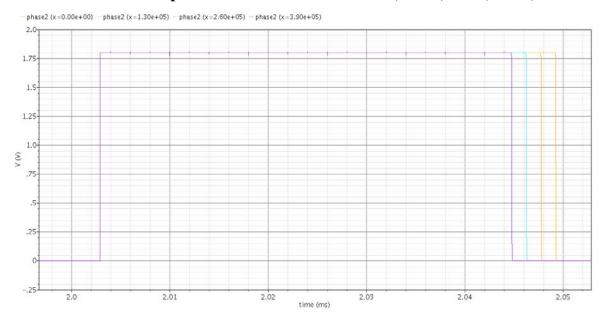

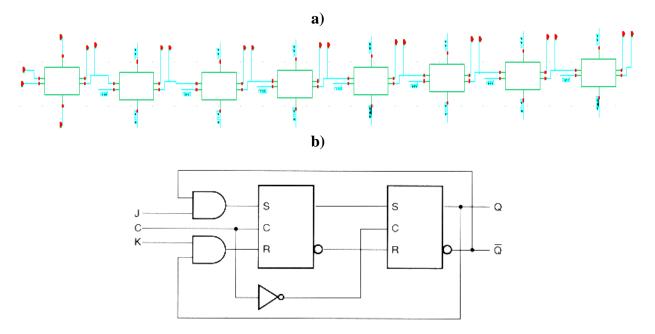

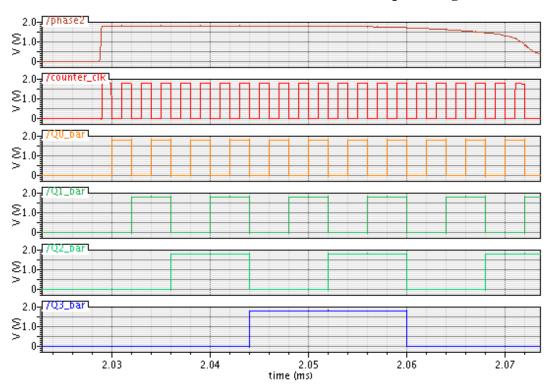

| Figure 4.2: Phase Response TSP System                                                                                                         |

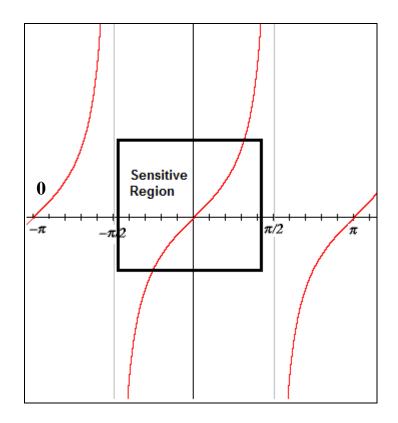

| Figure 4.3: Tangential Curve highlighting the sensitive area                                                                                  |

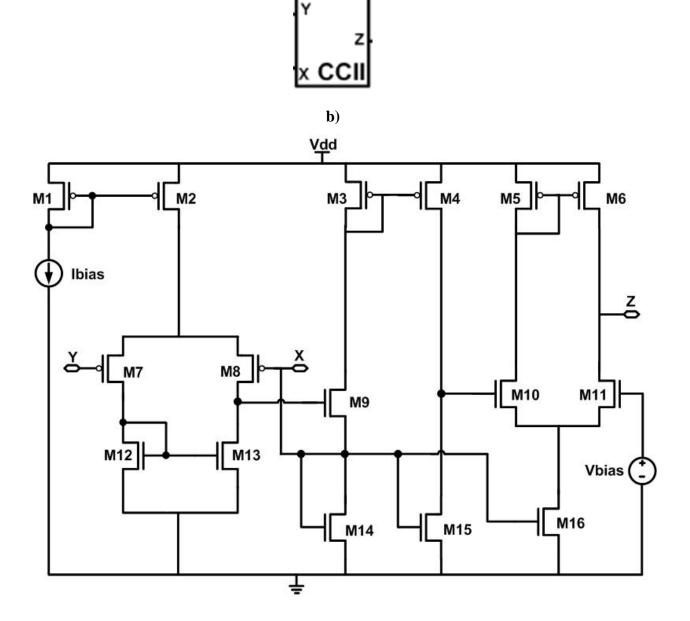

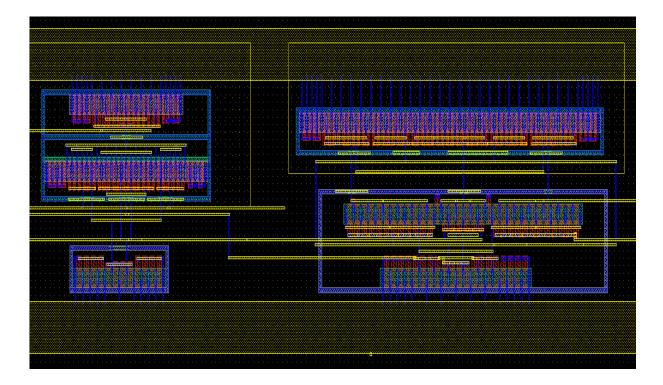

| Figure 4.4: CCII a) symbol and b) circuit diagram                                                                                             |

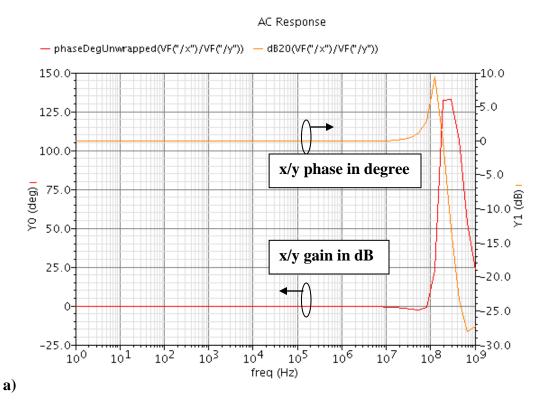

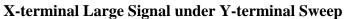

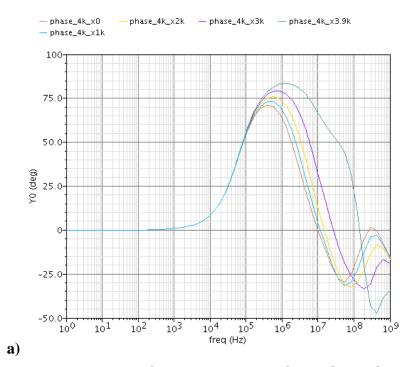

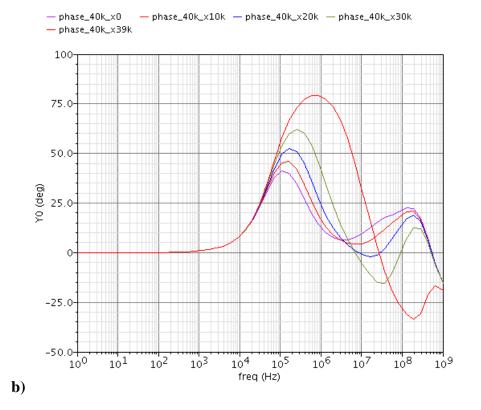

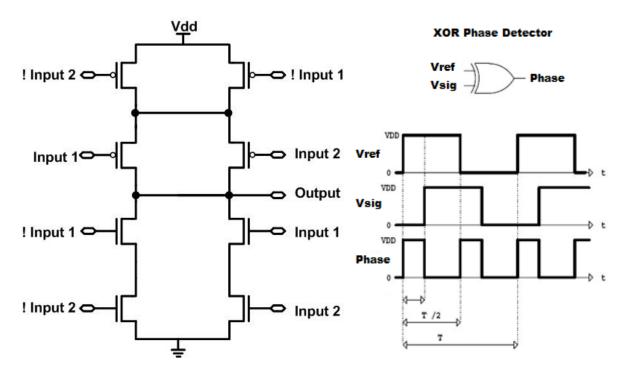

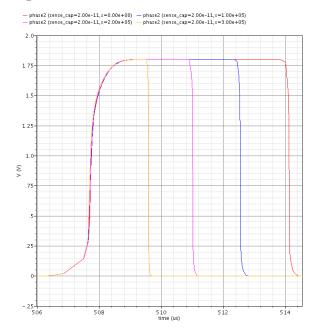

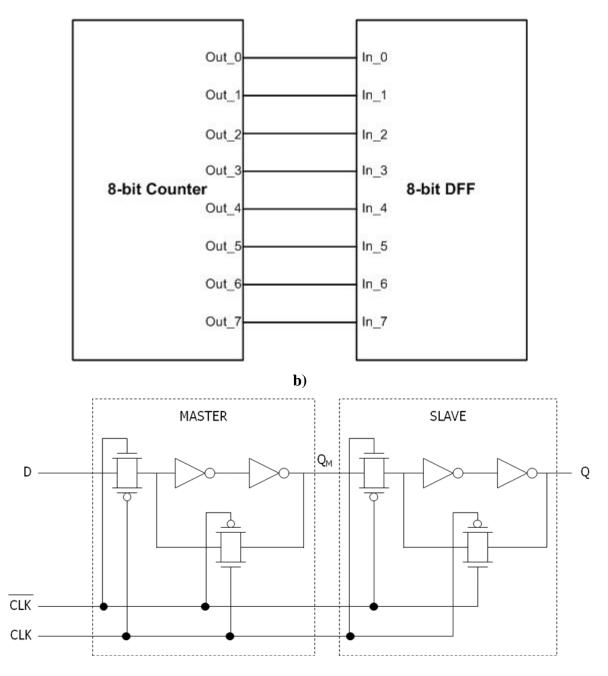

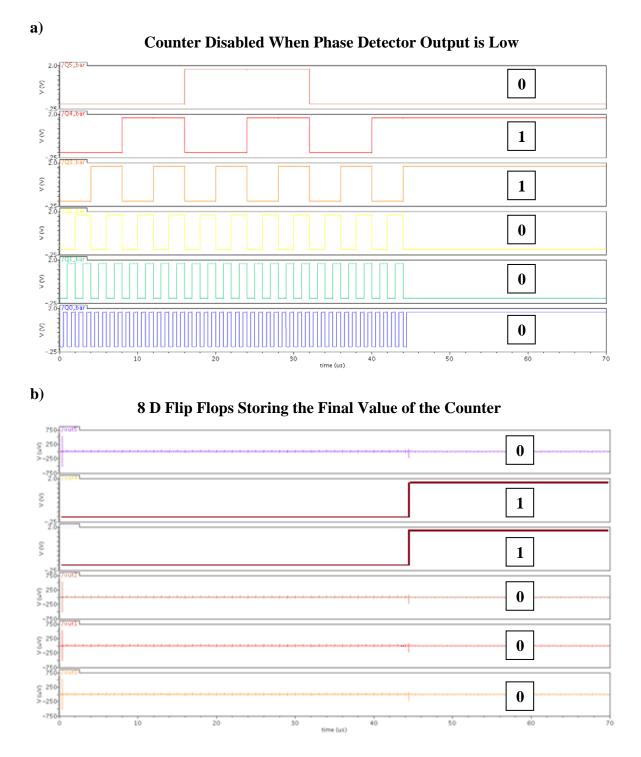

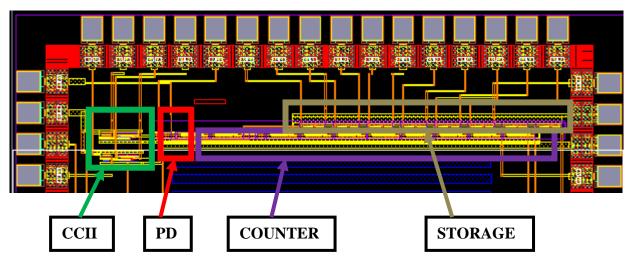

| Figure 4.5: $(\mathbf{v}_{\mathbf{x}} = \mathbf{M}\mathbf{v}_{\mathbf{y}})$ in a) small signal AC response and b) large signal DC response 70 |