# Investigation of Time Domain Modulation and Switching-Mode Power Amplifiers Suitable for Digitally-Assisted Transmitters

by

### Daniel Jordan Frebrowski

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2010

© Daniel Jordan Frebrowski 2010

### **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Daniel Jordan Frebrowski

#### Abstract

Innovation in wireless communication has resulted in accelerating demand for smartphones using multiple communications protocols such as WiFi, Bluetooth and the many cellular standards deployed around the world. The variety of frequency, bandwidth and power requirements associated with each standard typically calls for the implementation of separate radio frequency (RF) front end hardware for each standard. This is a less-than-ideal solution in terms of cost and device area. Software-defined radio (SDR) promises to solve this problem by allowing the RF hardware to be digitally reconfigurable to adapt to any wireless standard. The application of machine learning and cognition algorithms to SDR will enable cognitive radios and cognitive wireless networks, which will be able to intelligently adapt to user needs and surrounding radio spectrum conditions.

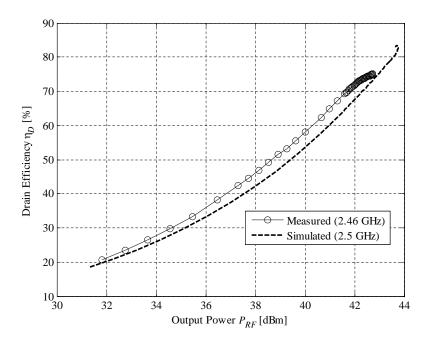

The challenge of fully reconfigurable transceivers is in implementing digitally-controlled RF circuits which have comparable performance to their fixed-frequency counterparts. Switching-mode power amplifiers (SMPA) are likely to be an important part of fully reconfigurable transmitters since their switching operation provides inherent compatibility with digital circuits, with the added benefit of very high efficiency. As a step to understanding the RF requirements of high efficiency and switching PAs, an inverse class F PA in push-pull configuration is implemented. This configuration is chosen for its similarity to the current mode class D (CMCD) topology. The fabricated PA achieves a peak drain efficiency of over 75% with 42.7 dBm (18.6 W) output power at 2.46 GHz.

Since SMPAs cannot directly provide the linearity required by current and future wireless communications standards, amplitude information must be encoded into the RF signal in a different way. Given the superior time resolution of digital integrated circuit (IC) technology, a logical solution is to encode this information into the timing of the signal. The two most common techniques for doing so are pulse width modulation and delta-sigma ( $\Delta\Sigma$ ) modulation. However, the design of  $\Delta\Sigma$  modulators requires simulation as part of the design process due to the lack of closed-form relationships between modulator parameters (such as resolution and oversampling) and performance figures (such as coding efficiency and signal quality). In particular, the coding efficiency is often ignored although it is an important part of ensuring transmitter efficiency with respect to the desired signal. A study of these relationships is carried out to observe the tradeoffs between them. It is found that increasing the speed or complexity of a  $\Delta\Sigma$  modulated system does not necessarily translate to performance benefits as one might expect. These observations can have a strong impact on design choices at the system level.

#### Acknowledgements

First and foremost I would like to thank my supervisor, Dr. Slim Boumaiza, for his support, guidance, encouragement and insight throughout my research. I also thank my fellow members of the Emerging Radio Systems Group (EmRG) for their collaboration, insight and encouragement.

My thanks also go to the faculty at the University of Waterloo and Carleton University who have contributed to my knowledge and passion for engineering and research, as well as the many support staff who have assisted me in various aspects of my academic life. In particular, I thank Dr. Maitham Shams, Dr. Calvin Plett and Dr. Michel Nakhla for encouraging my pursuit of postgraduate studies. In addition, I thank Dr. Mengistu Wolde of the National Research Council of Canada for introducing me to research.

I would like to thank the Natural Sciences and Engineering Research Council (NSERC) and the University of Waterloo for their generous financial support. By extension, I also thank the government and people of Canada for supporting NSERC and supporting Canadian innovation in science and technology.

I would also like to acknowledge industry support from Agilent Technologies, Cree Inc., Rogers Corporation and American Technical Ceramics through their contributions of materials, components, software and technical expertise.

Finally, I would like to thank all of my friends and family who have supported my endeavours in every way imaginable—most of all, Sarah Dowker who has been my constant source of support and inspiration, and without whom my journey to Waterloo may never have happened.

# Contents

| Li               | List of Tables xi   |           |                                                          |    |  |  |  |  |

|------------------|---------------------|-----------|----------------------------------------------------------|----|--|--|--|--|

| Li               | List of Figures xiv |           |                                                          |    |  |  |  |  |

| Nomenclature xix |                     |           |                                                          |    |  |  |  |  |

| 1                | l Introduction      |           |                                                          |    |  |  |  |  |

| 2                | Bacl                | kground   | 1                                                        | 5  |  |  |  |  |

|                  | 2.1                 | Softwa    | re-Defined Radio, Cognitive Radio and Cognitive Networks | 5  |  |  |  |  |

|                  | 2.2                 | Practic   | al Architectures for Reconfigurable Transmitters         | 7  |  |  |  |  |

|                  |                     | 2.2.1     | Quadrature Modulated Transmitters                        | 8  |  |  |  |  |

|                  |                     | 2.2.2     | Polar Transmitters                                       | 11 |  |  |  |  |

|                  | 2.3                 | Switch    | ing-Mode Power Amplifiers                                | 13 |  |  |  |  |

|                  |                     | 2.3.1     | Class D Power Amplifiers                                 | 18 |  |  |  |  |

|                  |                     | 2.3.2     | Class F and Inverse Class F PAs                          | 22 |  |  |  |  |

|                  | 2.4                 | Time I    | Domain Modulation Techniques                             | 25 |  |  |  |  |

|                  |                     | 2.4.1     | Pulse Width Modulation                                   | 26 |  |  |  |  |

|                  |                     | 2.4.2     | Delta-Sigma Modulation                                   | 30 |  |  |  |  |

| 3                | Pusł                | 1-Pull II | nverse Class F Power Amplifier                           | 37 |  |  |  |  |

|                  | 3.1                 | Design    | Specifications                                           | 38 |  |  |  |  |

|                  | 3.2                 | Design    | of Single Class F <sup>-1</sup> PA                       | 41 |  |  |  |  |

| Re | eferen | ces     |                                             | 70 |

|----|--------|---------|---------------------------------------------|----|

| 5  | Con    | clusion | and Future Research Direction               | 63 |

|    | 4.4    | Conclu  | ision                                       | 58 |

|    | 4.3    | Measu   | rement Validation                           | 55 |

|    |        | 4.2.2   | Third-Order Modulator                       | 55 |

|    |        | 4.2.1   | Second-Order Modulator                      | 54 |

|    | 4.2    | Simula  | tion Results                                | 54 |

|    |        | 4.1.3   | $\Delta\Sigma$ Modulator Design Methodology | 53 |

|    |        | 4.1.2   | Simulation Setup                            | 53 |

|    |        | 4.1.1   | Signal Characteristics                      | 52 |

|    | 4.1    | Simula  | tion Framework                              | 52 |

| 4  | Delt   | a-Sigma | a Modulator Study                           | 51 |

|    | 3.5    | Conclu  | sion and Discussion                         | 49 |

|    | 3.4    | Experi  | mental Results                              | 47 |

|    | 3.3    | Balun   | Design and Simulation                       | 46 |

|    |        | 3.2.2   | Simulated Performance of Single-Ended PA    | 44 |

|    |        | 3.2.1   | Matching Network Design                     | 41 |

## **List of Tables**

| 3.1 | Key parameters for RT/duroid 5870 substrate | • | • | • | • | • | • | • | • | <br>• | • | • | • | • | ••• | • | • | 38 |

|-----|---------------------------------------------|---|---|---|---|---|---|---|---|-------|---|---|---|---|-----|---|---|----|

| 4.1 | LTE signal parameters for simulation        |   |   |   |   |   |   |   |   |       |   |   |   |   |     |   |   | 52 |

# **List of Figures**

| 1.1  | Multiple standards using multiple RF FEMs                                      | 2  |

|------|--------------------------------------------------------------------------------|----|

| 2.1  | Comparison of conventional transmitter and ideal SDR                           | 6  |

| 2.2  | Direct digital RF modulator architecture                                       | 9  |

| 2.3  | Digital-to-RF converter                                                        | 9  |

| 2.4  | Delta-sigma RF modulator architecture using DRFC                               | 10 |

| 2.5  | Delta-sigma RF modulator architecture using multiplexers                       | 11 |

| 2.6  | Simplified EER transmitter architecture                                        | 12 |

| 2.7  | EER transmitter with $\Delta\Sigma$ digitized envelope signal                  | 13 |

| 2.8  | Polar transmitter using equally-weighted, digitally-controlled unit amplifiers | 14 |

| 2.9  | Simplified illustration of the DRP platform                                    | 14 |

| 2.10 | Illustration of conduction angle                                               | 16 |

| 2.11 | Single-ended SMPA with resistive load                                          | 17 |

| 2.12 | Voltage-mode class D PA                                                        | 19 |

| 2.13 | VMCD PA with parasitic capacitance                                             | 20 |

| 2.14 | Current-mode class D PA                                                        | 22 |

| 2.15 | Ideal class $F/F^{-1}$ power amplifier                                         | 23 |

| 2.16 | Three-harmonic output matching network structure for class $F^{-1}$            | 24 |

| 2.17 | Pulse width modulation                                                         | 26 |

| 2.18 | PWM system presented by Nielsen and Larsen                                     | 28 |

|      | PWM-based polar transmitter presented by Yang et al                            |    |

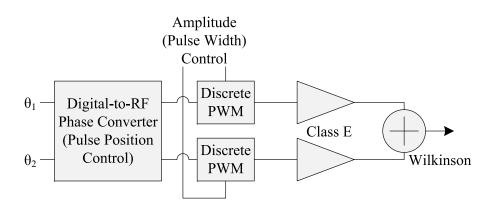

| 2.20 | AMO transmitter with discrete PWM                                              | 29 |

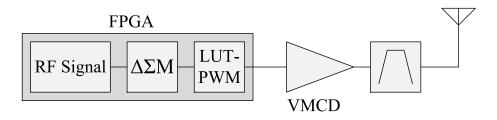

| 2.21 | Multilevel $\Delta\Sigma$ modulator driving a LUT-based PWM and VMCD amplifier                                              | 29 |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

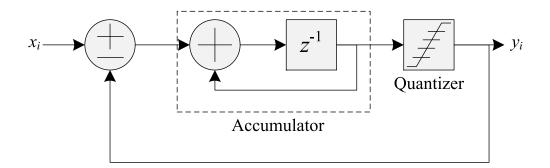

| 2.22 | First-order $\Delta\Sigma$ modulator                                                                                        | 30 |

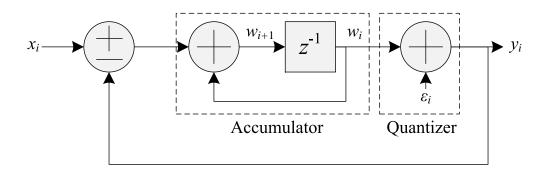

| 2.23 | First-order $\Delta\Sigma$ modulator with the quantizer modeled as an addition of error $\ . \ . \ .$                       | 31 |

| 2.24 | Noise spectrum shaping of first-order $\Delta\Sigma$ modulator                                                              | 32 |

| 2.25 | CIFB form of $\Delta\Sigma$ modulator                                                                                       | 33 |

| 2.26 | Adjustment of zero locations in NTF to minimize in-band noise                                                               | 34 |

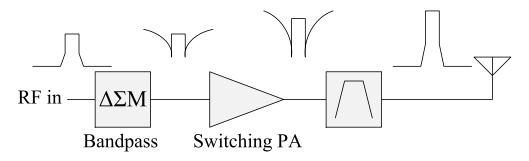

| 2.27 | Class S amplifier system                                                                                                    | 34 |

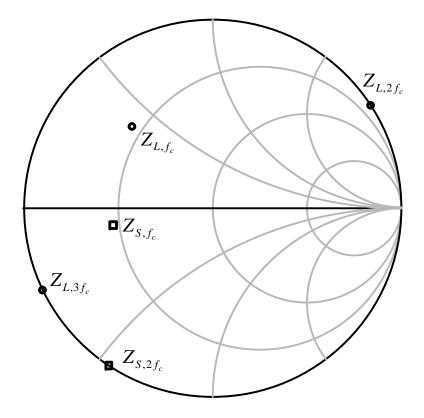

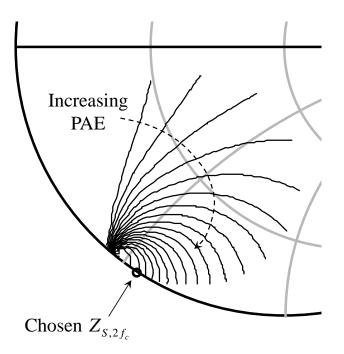

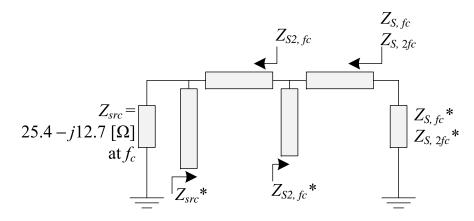

| 3.1  | Design impedances found from source and load pull simulation                                                                | 40 |

| 3.2  | PAE contours from second harmonic source pull simulation                                                                    | 41 |

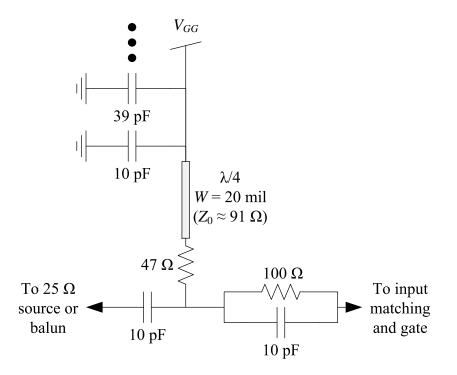

| 3.3  | Input bias and stabilization network                                                                                        | 42 |

| 3.4  | Input matching network structure                                                                                            | 44 |

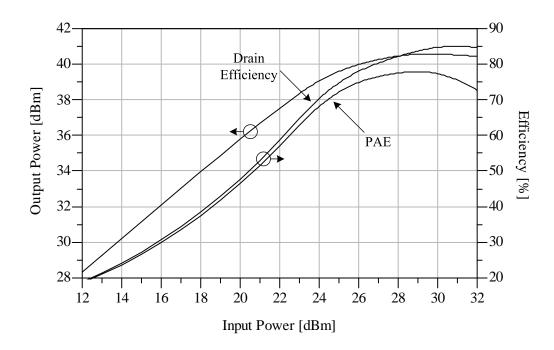

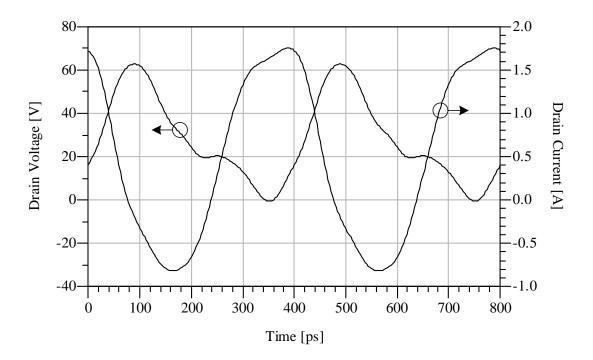

| 3.5  | Simulated performance of the single-ended PA                                                                                | 45 |

| 3.6  | Simulated drain waveforms of the single-ended PA                                                                            | 45 |

| 3.7  | Layout of microstrip balun                                                                                                  | 46 |

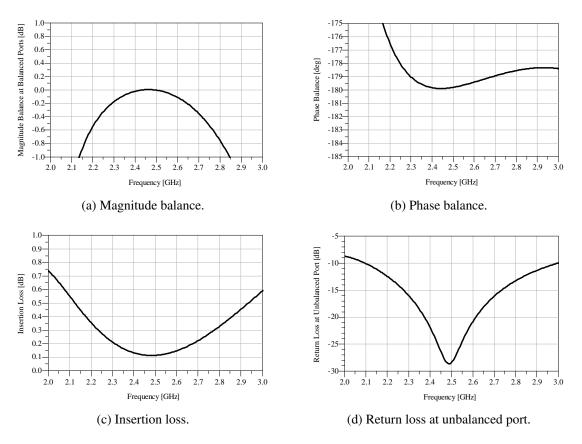

| 3.8  | Simulated performance of balun.                                                                                             | 47 |

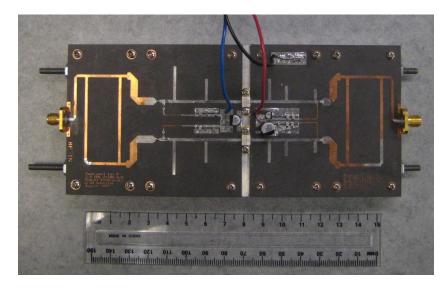

| 3.9  | Photograph of completed push-pull class $F^{-1}$ PA                                                                         | 48 |

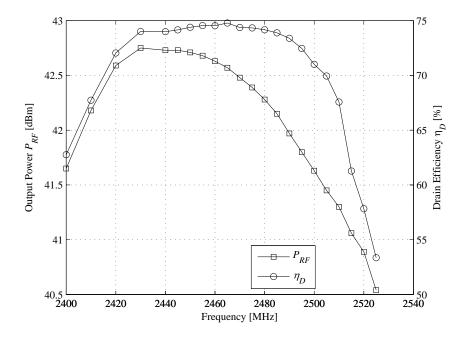

| 3.10 | Performance of fabricated PA versus frequency                                                                               | 48 |

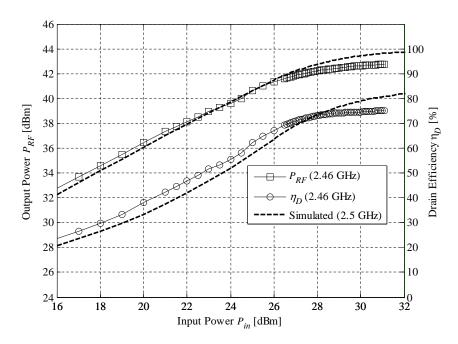

| 3.11 | Performance of fabricated PA versus input power                                                                             | 49 |

| 3.12 | Drain efficiency of fabricated PA versus output power                                                                       | 50 |

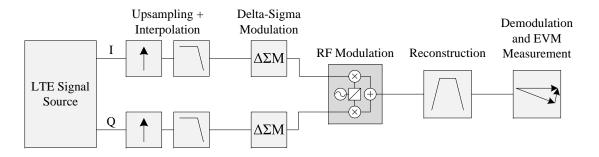

| 4.1  | Schematic of $\Delta\Sigma$ modulator simulation                                                                            | 53 |

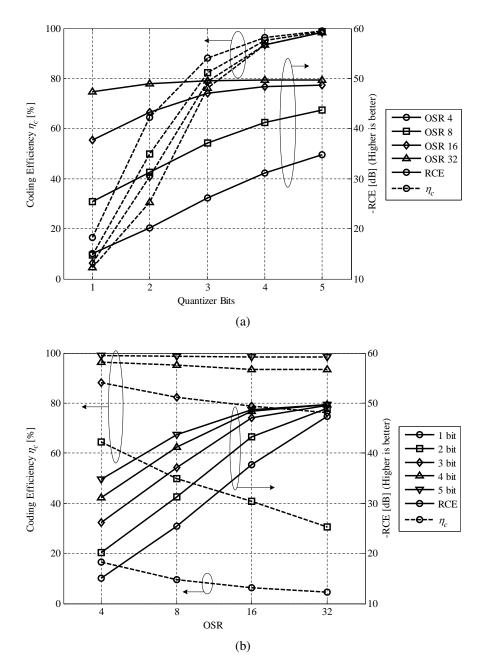

| 4.2  | Performance of second-order $\Delta\Sigma$ modulator $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 56 |

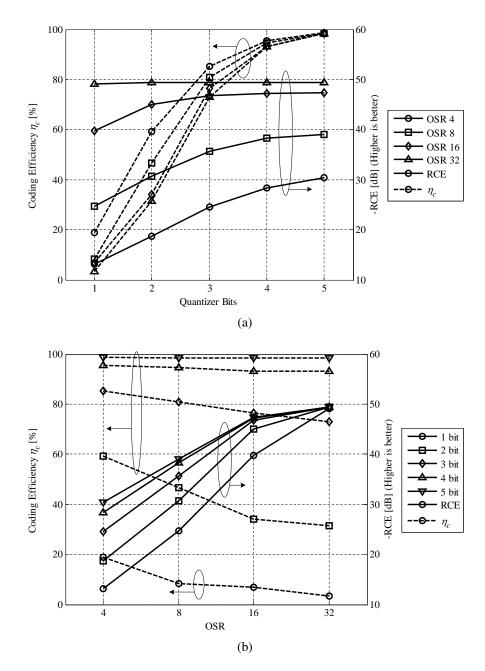

| 4.3  | Performance of third-order $\Delta\Sigma$ modulator $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 57 |

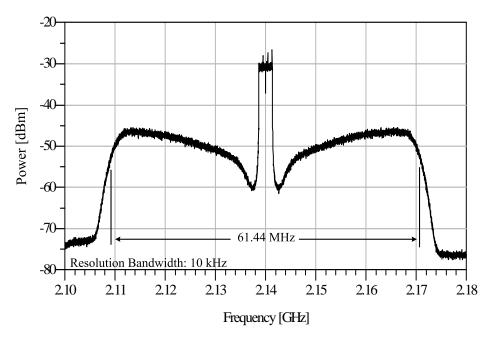

| 4.4  | Measured spectrum of the $\Delta\Sigma$ modulated LTE signal $\ldots \ldots \ldots \ldots \ldots \ldots$                    | 58 |

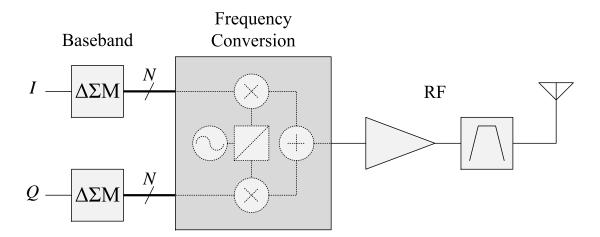

| 4.5  | $I/Q$ -based transmitter with baseband $\Delta\Sigma$ modulators                                                            | 60 |

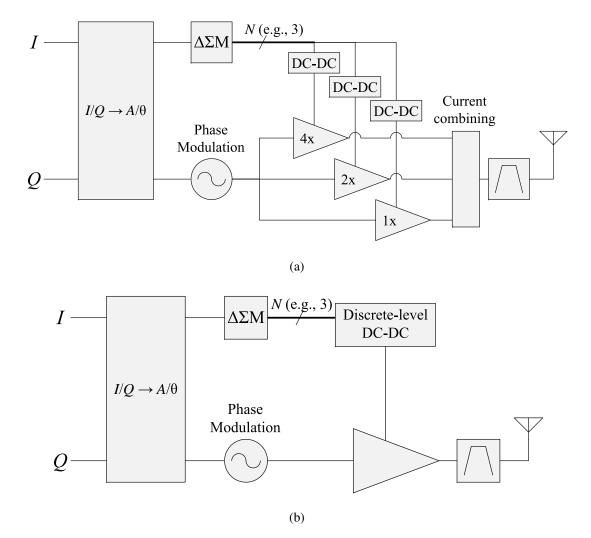

| 4.6  | Polar transmitter with envelope $\Delta\Sigma$ modulation                                                                   | 61 |

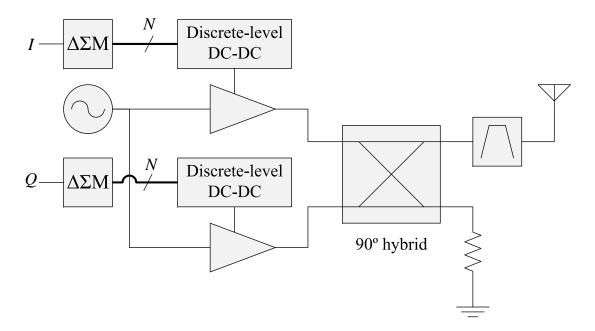

| 4.7  | Combined polar/quadrature $\Delta\Sigma$ transmitter                                                                        | 62 |

# Nomenclature

| $\eta_c$         | Coding efficiency                                           |

|------------------|-------------------------------------------------------------|

| $\eta_D$         | Drain efficiency                                            |

| $\Gamma_{L,n}$   | Load reflection coefficient at the $n^{\text{th}}$ harmonic |

| λ                | Wavelength                                                  |

| $\omega_c$       | Carrier frequency in rad/s                                  |

| $\Theta(t)$      | Phase component of $g(t)$                                   |

| ε <sub>i</sub>   | Quantization error                                          |

| A(t)             | Amplitude component of $g(t)$                               |

| $A_p$            | Amplitude limit for PWM                                     |

| $C_{DS}$         | Parasitic drain-source capacitance                          |

| $f_b$            | Baseband bandwidth                                          |

| $f_c$            | Carrier frequency in Hz                                     |

| $f_s$            | Sampling frequency in Hz                                    |

| g(t)             | Complex envelope signal                                     |

| I(t)             | Real (In-phase) component of $g(t)$                         |

| $I_0$            | DC component of drain current                               |

| $I_Q$            | Quiescent current                                           |

| I <sub>max</sub> | Peak drain current                                          |

| L <sub>ch</sub>       | RF choke inductance                                 |

|-----------------------|-----------------------------------------------------|

| n <sub>i</sub>        | Quantization noise of $\Delta\Sigma$ modulator      |

| p(t)                  | PWM signal                                          |

| $p_n(t)$              | <i>n</i> <sup>th</sup> pulse in a PWM signal        |

| $P_{DC}$              | Supplied DC power                                   |

| Pin                   | RF input power                                      |

| $P_{RF}$              | RF (output) power                                   |

| Q(t)                  | Imaginary ( <b>Q</b> uadrature) component of $g(t)$ |

| $R_L$                 | Load resistance                                     |

| r <sub>o</sub>        | Small signal transistor output resistance           |

| r <sub>on</sub>       | Switch on-state resistance                          |

| s(t)                  | RF signal                                           |

| $T_p$                 | Pulse period                                        |

| $T_s$                 | Sampling period                                     |

| $T_{p,n}$             | Duration of $n^{\text{th}}$ pulse                   |

| V <sub>DD</sub>       | Drain supply voltage                                |

| $V_{DS}$              | Drain-source biasing voltage                        |

| <i>v<sub>DS</sub></i> | Drain-source total voltage                          |

| $V_{GG}$              | Gate supply voltage                                 |

| V <sub>SS</sub>       | Source supply voltage                               |

| $Z_0$                 | Transmission line characteristic impedance          |

| $Z_{L,n}$             | Load impedance at the $n^{\text{th}}$ harmonic      |

| $Z_{S,n}$             | Source impedance at the $n^{\text{th}}$ harmonic    |

| 3GPP                  | 3 <sup>rd</sup> Generation Partnership Project      |

| $\Delta\Sigma$        | Delta-sigma (modulation)                |

|-----------------------|-----------------------------------------|

| ADPLL                 | All-digital phase-locked loop           |

| ADS                   | Agilent Advanced Design System          |

| AM                    | Amplitude modulation                    |

| AMO                   | Asymmetric multilevel outphasing        |

| BiCMOS                | Bipolar CMOS                            |

| BPF                   | Bandpass filter                         |

| bps                   | Bits per second                         |

| CDMA                  | Code division multiple access           |

| CIFB                  | Cascade of integrators with feedback    |

| Class F <sup>-1</sup> | Inverse class F (amplifier)             |

| CMCD                  | Current-mode class D (amplifier)        |

| CMOS                  | Complementary metal-oxide-semiconductor |

| CR                    | Cognitive radio                         |

| CWN                   | Cognitive wireless network              |

| DAC                   | Digital-to-analog converter             |

| DC                    | Direct current                          |

| DCXO                  | Digitally controlled crystal oscillator |

| DDRM                  | Direct digital RF modulator/modulation  |

| DRFC                  | Digital-to-RF converter                 |

| DRP                   | Digital RF Processor                    |

| DSP                   | Digital signal processor/processing     |

|                       |                                         |

| EER                   | Envelope elimination and restoration    |

| Error vector magnitude                         |

|------------------------------------------------|

| Frequency division duplexing                   |

| Front-end module                               |

| Finite impulse response                        |

| Field programmable gate array                  |

| Gallium arsenide                               |

| Gallium nitride                                |

| General purpose processor                      |

| Global Positioning System                      |

| Global System for Mobile Communications        |

| High electron mobility transistor              |

| Integrated circuit                             |

| Intermediate frequency                         |

| Interim Standard 95                            |

| Laterally-diffused metal-oxide-semiconductor   |

| Linear amplification with nonlinear components |

| Local oscillator                               |

| 3GPP Long Term Evolution                       |

| Lookup table                                   |

| Monolithic microwave integrated circuit        |

| Noise transfer function                        |

| Orthogonal frequency division multiplexing     |

| Orthogonal frequency division multiple access  |

| Oversampling ratio                             |

|                                                |

| PA   | Power amplifier                            |

|------|--------------------------------------------|

| PAE  | Power-added efficiency                     |

| PAPR | Peak-to-average power ratio                |

| PCB  | Printed circuit board                      |

| PM   | Phase modulation                           |

| PWM  | Pulse width modulation                     |

| QAM  | Quadrature amplitude modulation            |

| RB   | Resource block                             |

| RCE  | Relative constellation error               |

| RF   | Radio frequency                            |

| SDR  | Software-defined radio                     |

| SiGe | Silicon germanium                          |

| SMPA | Switching-mode power amplifier             |

| SNR  | Signal-to-noise ratio                      |

| STF  | Signal transfer function                   |

| UE   | User equipment                             |

| UMTS | Universal Mobile Telecommunications System |

| VMCD | Voltage-mode class D (amplifier)           |

### Chapter 1

### Introduction

In today's connected world, consumers and organizations are continually searching for more convenient ways of connecting with those around them. The demand for smartphones—capable of much more than just mobile telephony—has increased dramatically in the last decade and continues to accelerate. Such devices use multiple communications protocols and standards depending on the application. For example, cellular network standards, local area standards such as IEEE 802.11 (WiFi), short-range standards such as Bluetooth, and the Global Positioning System (GPS) are commonly found in today's smartphones. In addition, the standards in place vary among geographical locations, especially in the case of cellular networks. For example, the Global System for Mobile Communications (GSM) standard is a common cellular standard used all over the world. However, there are four major frequency bands used for GSM and which one is in use varies with location and service provider.

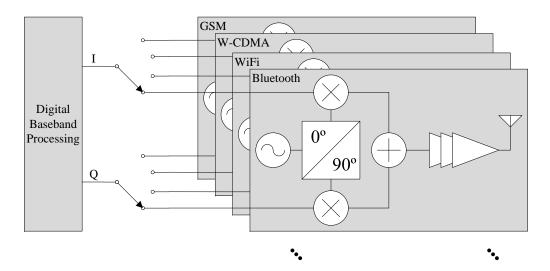

Each of the numerous wireless standards implemented in a particular mobile or base station transceiver has its own RF requirements in terms of carrier frequency, bandwidth and power level. A typical approach is to design and implement each standard separately, each with its own radio frequency (RF) front-end module (FEM), which are then incorporated into a single device as illustrated in Figure 1.1. Indeed, in the case of GSM, handsets supporting the four major bands include separate RF hardware for each band. This requires high cost and device area, both of which are important factors in the competitive mobile communications market.

A more suitable approach would be to use a single, highly reconfigurable FEM to incorporate all the desired functionality, with the possible exception of the ability to use multiple standards simultaneously. The configuration would be controlled through the use of software and, by extension, digital circuits. This can potentially eliminate a large portion of redundant circuitry and allow for adaptability to new wireless standards as they are finalized and deployed. Such software-defined radios (SDR) are the key to enabling cognitive wireless networks: systems allowing for intelligent adaptation of radio hardware and signal processing to the current needs

Figure 1.1: Multiple standards using multiple RF FEMs.

of the user and to the surrounding radio environment. These have the added benefit of using the radio spectrum in a more intelligent and efficient way than currently.

The defining challenge of software-defined radio lies in realizing digitally-controlled circuits which can achieve RF performance comparable to existing solutions in a robust and cost-efficient way. Conventional direct conversion transceivers place the digital-to-analog interface between the digital baseband signal generation (or decoding) circuitry and the mixers. The RF components including mixers, oscillators, amplifiers, switches, filters and antennas are implemented for a single carrier frequency and bandwidth with fixed-value or coarsely tunable components. This fundamentally limits their ability to adapt to the different RF requirements of different standards.

High-performance RF power amplifiers (PA) are a particular example of a challenging building block to implement in a reconfigurable manner. Efficient DC-to-RF power conversion and high linearity are the key performance metrics in a PA design, assuming the basic output power and gain requirements have been met. Since the PA is the most power-hungry RF component in any transceiver, high efficiency is required to maximize battery life in mobile handsets and minimize operating expenses (i.e., electricity) for the wireless infrastructure. In addition, the high peak-to-average power ratio (PAPR) demanded by wireless standards requires a highly linear PA. The linearity and the efficiency are two conflicting requirements, and a typical PA reflects a carefully considered tradeoff between the two. The complexity and difficulty of building reconfigurability into the PA presents an additional challenge.

Several innovations promise to help significantly in the implementation of reconfigurable RF front ends, and in particular PAs. For example, switching-mode PAs (SMPA) may be particularly well-suited for direct amplification of digital signals, due to the operation of the active device as a switch as in digital circuits. In addition to this inherent degree of compatibility with digital

electronics, most classes of SMPA have the advantage of theoretically being able to provide 100% efficiency. Advances in transistor technology have increased the switching frequency of transistors, thereby enabling implementations of high-performance SMPAs with ever-increasing efficiency. However, the amplification of signals with high PAPR remains an important limitation of SMPAs, due to the highly nonlinear switching operation of the transistor. Moreover, the advances in digital integrated circuit (IC) technology have led to lower and lower supply voltages, decreasing the available voltage headroom in which information can be encoded with an acceptable signal-to-noise ratio (SNR).

One solution is to take advantage of the extremely fast switching speeds of digital IC processes and encode information into the time domain, using the timing of the state transitions. For example, pulse width modulation (PWM) encodes amplitude information into the duty cycle of a square wave, and can additionally provide phase information using the positioning of the pulse. Delta-sigma ( $\Delta\Sigma$ ) modulation similarly encodes information into pulse density in the case of two-level  $\Delta\Sigma$  modulator.

This thesis explores the theory and design of SMPA and time-encoded signal generation techniques, and is organized as follows:

- Chapter 2 explains in further detail the key concepts of cognitive wireless networks, reconfigurable transmitters, SMPA and time-encoded signal generation.

- Chapter 3 presents the design and implementation of a class F<sup>-1</sup> PA in push-pull configuration, as an example of a high efficiency PA.

- Chapter 4 studies the performance of  $\Delta\Sigma$  modulation techniques with respect to key parameters.

- Finally, Chapter 5 concludes this thesis with a discussion of the potential for further research in these areas.

### Chapter 2

### Background

As outlined in Chapter 1, all of the constituent RF—and intermediate frequency (IF)—blocks in a transceiver are typically designed and implemented with fixed-value electronic components. This approach allows only a fixed or limited frequency and bandwidth of operation, with the possible exception of the local oscillator (LO). Such components are targeted for a specific application or communications standard in a specific frequency band, so any handset or infrastructure supporting multiple standards must also incorporate an FEM for each supported standard.

Highly reconfigurable RF devices and circuits, which are compatible with existing digital circuits, are an important part of enabling SDR and eventually cognitive wireless networks. This chapter provides relevant background information on cognitive radios (CR) as well as for the particular implementation details which are the subject of this thesis. Section 2.1 describes the concepts of ideal cognitive networks and the key enabling technology of SDR as compared to conventional transceiver techniques. Section 2.2 provides an overview of practical transmitter architectures and circuits which are suitable for reconfigurable and software-defined radio. Section 2.3 studies SMPAs in the context of their potential to provide high performance while being suitable for use in SDR. In particular, the current mode class D (CMCD) amplifier and the inverse class F (F<sup>-1</sup>) amplifier are discussed in detail. Finally, Section 2.4 discusses time-domain signal modulation techniques, which have proven to be a suitable class of techniques for enabling compatibility between RF circuits and digital circuits.

# 2.1 Software-Defined Radio, Cognitive Radio and Cognitive Networks

The idea of SDR first appeared in the late 1990s. Programmable digital signal processors (DSP) and general purpose processors (GPP) were used to perform most of the signal generation, mod-

(b) Ideal SDR.

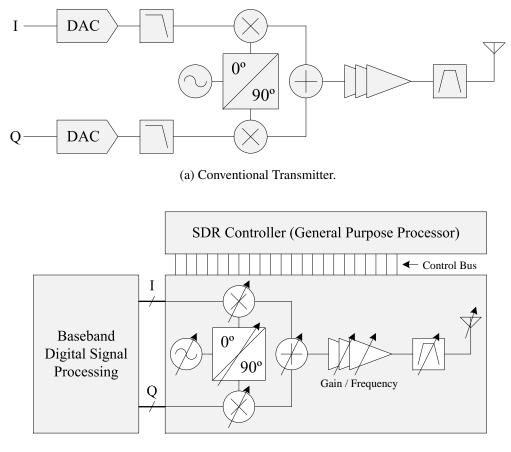

Figure 2.1: Comparison of conventional transmitter and ideal SDR.

ulation and related functions [1]. Manufacturers recognized the potential flexibility afforded by using general-purpose electronics and so used the term "software-defined radio" to express this potential. This functionality was, however, limited to baseband processing.

Over the years the definition of SDR has expanded to include the transfer of RF and IF functions to the digital domain in order to provide increased flexibility of the frequency and bandwidth characteristics of the transceiver. In an SDR the digital-to-analog interface is ideally located directly before the antenna, so that the only analog signal involved is that which is transmitted or received over the air. In the extreme case even the antenna may be digitally reconfigurable to the application at hand (e.g., [2]). Figure 2.1 illustrates the concept of the ideal SDR versus conventional transceivers.

The ideal SDR can support any wireless communication standard since the entire transceiver from baseband to antenna is fully tunable in frequency and bandwidth. Reconfigurable/tunable

implementation of the transceiver and its components is a broad and active area of research. The problem rests on implementing RF/IF components in a robustly reconfigurable way while achieving performance comparable to that of existing analog hardware. Today this is done to an extent by switching between multiple sets of RF/IF hardware depending on the desired frequency band, as is typical in multi-band GSM handsets for example. However, this is not a robust solution as it provides no support for competing standards or for wireless standards to be deployed in the future.

In his doctoral thesis [3] Joseph Mitola III envisioned a layer of machine learning and cognition algorithms to control the SDR: the *cognitive radio*. In this way a user's needs can be met in a broad variety of contexts and applications using a single, highly adaptive and reconfigurable radio. Ideally a CR can use whatever information is available to it through various sensors (e.g., spectral sensing, microphone or camera) to determine the current context and activities of the user and act accordingly. Note that although some confusion exists about the difference between SDR and CR, SDR refers solely to the digitally reconfigurable radio platform and CR refers to the additional cognitive and learning processes which may control an SDR [4].

The deployment and proliferation of CR enables cognitive wireless networks (CWN). One of the first descriptions of cognitive networks appeared in [4]. Thomas et al. defined the cognitive network as having

a cognitive process that can perceive current network conditions, and then plan, decide and act on those conditions. The network can learn from these adaptations and use them to make future decisions, all while taking into account end-to-end goals.

The CWN should possess, among other things, the ability to manage spectral resource efficiently and effectively. RF spectrum shortage is increasingly problematic, especially given the accelerating demand for high-speed mobile data. CWNs are thus a highly active area of research as they promise a solution to this issue, assisting infrastructure operators in making the most effective use of their highly expensive licensed spectrum.

### 2.2 Practical Architectures for Reconfigurable Transmitters

As part of enabling SDR and CR, a number of modifications have been proposed to make the transmitter more reconfigurable and suitable for SDR applications. This section will highlight some examples of recent advances in digitally-assisted and reconfigurable transmitter technology. They fall into two distinct categories: quadrature modulation and polar modulation.

#### 2.2.1 Quadrature Modulated Transmitters

The structure of a simplified conventional direct conversion radio transmitter is shown above in Figure 2.1(a) (page 6). Baseband information is encoded in a complex envelope signal

$$g(t) = I(t) + jQ(t).$$

(2.1)

This modulates the amplitude and phase of the carrier tone according to

$$s(t) = \operatorname{Re}\left[g(t)e^{j\omega_{c}t}\right]$$

(2.2)

$$= I(t)\cos(\omega_c t) - Q(t)\sin(\omega_c t)$$

(2.3)

$$= I(t)\cos(\omega_c t) + Q(t)\cos\left(\omega_c t + \frac{\pi}{2}\right)$$

(2.4)

where s(t) is the transmitted signal and  $\omega_c$  is the carrier frequency in rad/s. I(t) and Q(t) are known as the *in-phase* and *quadrature* components of the information, respectively. This modulation technique is known as quadrature amplitude modulation (QAM) or vector modulation, and is the basis of virtually all modern wireless communications systems.

The *I* and *Q* components arrive at the transmitter in digital form and are converted to analog using a digital-to-analog converter (DAC). They are then filtered to occupy only the allotted bandwidth, then upconverted to the carrier frequency using mixers. The LO for the *Q* mixer leads that for the *I* mixer by  $\pi/2$  or 90°. The two components of the signal are then combined and amplified before being radiated by an antenna. There may also be additional filters and linearization techniques to attenuate unwanted emissions caused by nonidealities of various components, and an IF stage may also be used to suppress LO leakage.

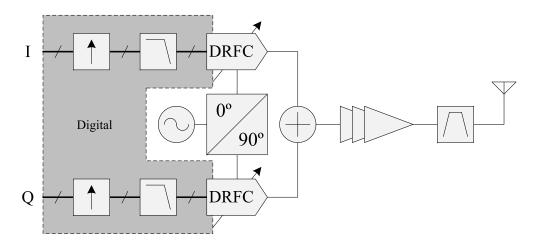

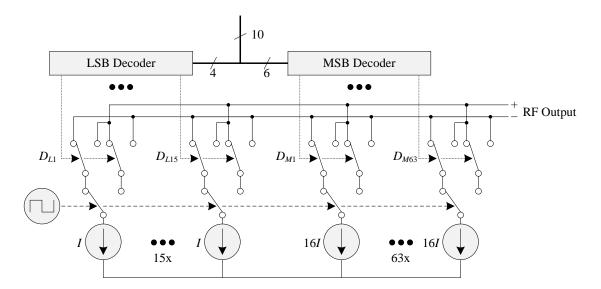

Eloranta et al. proposed direct digital RF modulation (DDRM) as a highly flexible architecture for QAM [5–8], shown in Figure 2.2. The heart of the architecture is the digital-to-RF converter (DRFC) which itself consists primarily of two differently-weighted sets of unit Gilbert cell mixers as shown in Figure 2.3. This circuit moves the digital-analog interface closer to the PA stage by combining the functions of the DAC and mixers. Digital interpolation and filtering is performed on each component to ensure compatibility between the low sampling rate at baseband and the high sampling rate required by the DRFCs. The DRFCs then upconvert each signal component to RF and the two components are combined and amplified in the usual way. The specifications of the system depend primarily on the unsampling filter parameters which are easily reprogrammed. This is the system's principal advantage. However, this system does not address the PA stage, which is one of the most challenging blocks to implement in a reconfigurable way. Nevertheless, the DDRM architecture successfully increases the digital portion of the transmitter, thereby reducing the amount of hardware required for multi-mode operation.

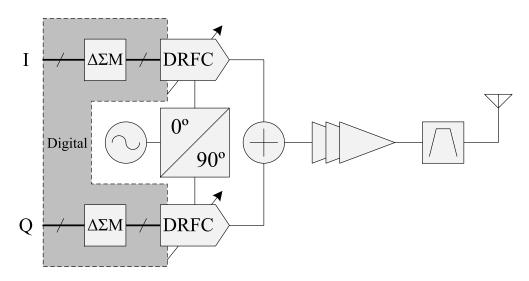

Jerng and Sodini made use of the DRFC architecture in their work, adding a  $\Delta\Sigma$  modulator to the *I* and *Q* paths as shown in Figure 2.4 [9]. The  $\Delta\Sigma$  modulators use 3-bit quantizers to boost

Figure 2.2: Direct digital RF modulator architecture [8].

Figure 2.3: Digital-to-RF converter [8].

Figure 2.4: Delta-sigma RF modulator architecture using DRFC [9].

the SNR to an acceptable level. One could also use higher order 1-bit  $\Delta\Sigma$  modulators to increase the SNR; however, this would result in more stringent reconstruction filter requirements due to the steeper close-in noise shaping. The  $\Delta\Sigma$  modulator approach reduces the number of DRFC unit cells needed to achieve the required dynamic range. A quadrature IF stage is included in the digital domain to mitigate LO leakage and phase mismatch in the quadrature LO. This work also includes an integrated, high quality factor, self-tuned RF filter to attenuate the spurious products of the digital-to-RF conversion and the  $\Delta\Sigma$  modulator quantization noise. The fabricated circuit achieved 1.2 gigabit-per-second (Gbps) using a 200 MHz bandwidth orthogonal frequency division multiplexing (OFDM) signal at 5.25 GHz, consuming 187 mW. The output RF power was -8 dBm, translating to a low system efficiency of about 0.1%. However, the power consumption of this modulator is likely to be insignificant compared to that of the PA, resulting in a low impact on the full transmitter efficiency.

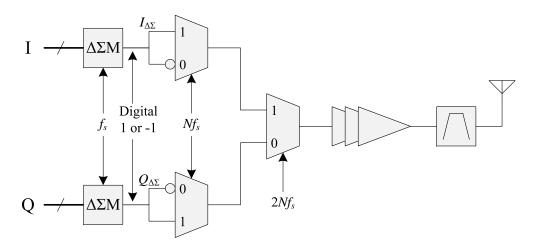

In [10] Helaoui et al. proposed a similar quadrature  $\Delta\Sigma$  modulator approach, but using digital multiplexers to upconvert and combine the *I* and *Q* components as shown in Figure 2.5. By multiplexing the 1-bit  $\Delta\Sigma$  modulated components  $I_{\Delta\Sigma}(t)$  and  $Q_{\Delta\Sigma}(t)$  with their complements at a carrier frequency  $f_c = Nf_s$  which is a multiple *N* of the  $\Delta\Sigma$  modulator sampling frequency  $f_s$ . This amounts to a convolution with an RF pulse train at carrier  $f_c$ . The multiplexing of  $Q_{\Delta\Sigma}$  is  $\pi/2$  offset from that of  $I_{\Delta\Sigma}$ . The third multiplexer works at  $2f_c$ , combining the *I* and *Q* components into a single RF signal at  $f_c$  with odd-harmonic images. In addition to the flexibility gained through use of digital hardware, this transmitter demonstrated the ability to operate at a different  $f_c$  simply by changing the multiplexer frequency.

Figure 2.5: Delta-sigma RF modulator architecture using multiplexers [10].

### 2.2.2 Polar Transmitters

The complex envelope signal g(t) (Equation 2.1) can be equivalently represented in polar form

$$g(t) = A(t)e^{j\theta(t)}$$

(2.5)

where

$$A(t) = \sqrt{I^2(t) + Q^2(t)}$$

(2.6)

$$\Theta(t) = \tan^{-1} \left[ \frac{Q(t)}{I(t)} \right].$$

(2.7)

The transmitted signal then takes the form

$$s(t) = A(t)\cos[\omega_c t + \theta(t)].$$

(2.8)

This form has been used successfully to implement polar transmitters, in which the dynamic range of the RF signal is eliminated from the main signal path and instead applied to separate power control and amplifier biasing circuitry. For reasons to be explained in Section 2.3 this allows efficiency enhancement of the PA stage without sacrificing signal linearity, a highly desirable feature for base station and mobile transmitters alike.

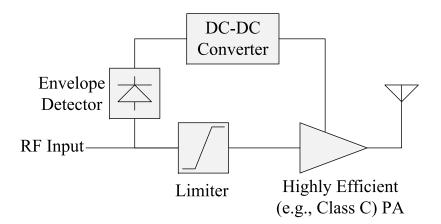

Kahn first demonstrated this technique in 1952 [11]. He proposed amplifying solely the phase-modulated (PM) component of the RF signal using a highly-efficient PA (e.g., class C) and varying the output power according to the signal envelope through the PA's DC bias. Because the

Figure 2.6: Simplified EER transmitter architecture.

signal at the input of the PA has a constant power envelope, this technique is sometimes called envelope elimination and restoration (EER) or simply the Kahn technique. Figure 2.6 shows the architecture of the EER system.

The main drawbacks of this structure are threefold. First, the amplitude and phase components of a complex modulated signal both generally have expanded bandwidth as compared to the rectangular (I and Q) components. This increases the frequency requirements of the PA as well as for the envelope amplifier, DC-DC converter and other components. Second, the biasto-amplitude (DC-AM) characteristic of the PA may be nonlinear, necessitating the use of more than a simple envelope detector and amplifier to provide the proper DC bias for the desired output power. Moreover, the constant-envelope PM input signal can leak through the PA to the output even when the supposed envelope level is zero. Third, the envelope and phase paths through the transmitter are quite different, requiring careful consideration of the alignment at the output to keep the signal fidelity. This is further complicated by the possibly varying or even nonlinear bias-to-phase (DC-PM) characteristics of the PA. Nevertheless, the efficiency enhancement promised by EER and related techniques has encouraged efforts to mitigate these concerns.

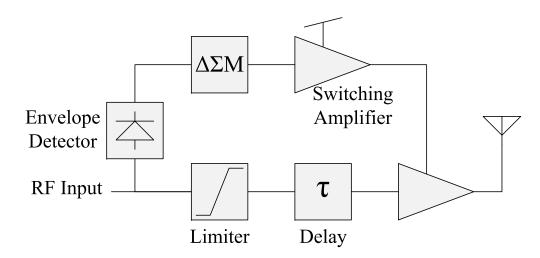

One way to overcome the DC-AM nonlinearity is to digitize the envelope component of the signal, for example using a  $\Delta\Sigma$  modulator [12,13]. This also augments the digital functionality of the transmitter making it more suitable for a fully reconfigurable system, and essentially replaces the envelope detection function in Figure 2.6. The architecture studied by Choi et al. in [13] is shown in Figure 2.7. This transmitter uses a three-level  $\Delta\Sigma$  modulator for the envelope signal. The low number of discrete states makes it easy to correct for the PA distortions versus the drain-source bias voltage  $V_{DS}$  while increasing the SNR as compared to a two-level  $\Delta\Sigma$  modulator. The system achieved 48% overall efficiency at a centre frequency of 40 MHz.

A  $\Delta\Sigma$  modulator is just one way to digitize the envelope signal. In [14], Kavousian et al. demonstrated a polar transmitter in which the digitized envelope signal is used to activate a set of

Figure 2.7: EER transmitter with  $\Delta\Sigma$  digitized envelope signal [12, 13].

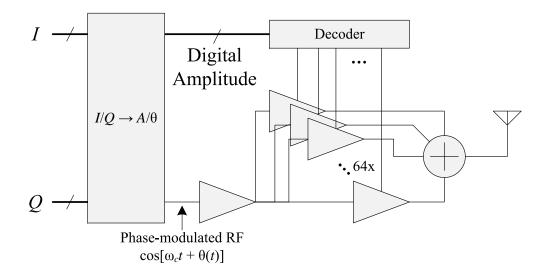

unit PAs which amplify the PM signal (Figure 2.8). In order to satisfy the linearity requirements for the IEEE 802.11g standard, a 6-bit envelope encoder is chosen and 64 unit PAs are included on the chip.

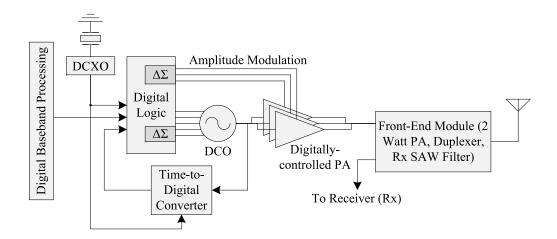

A notable highly digital platform based on the polar transmitter architecture has been the subject of many papers in the last decade: the Digital RF Processor (DRP<sup>1</sup>) by Texas Instruments [15–20]. Figure 2.9 illustrates the basic functionality of the transmitter portion of the chip. The DSP and predistortion functions are included on-chip in the digital domain. Notably, the circuit includes an all-digital phase-locked loop (ADPLL) and frequency synthesizer [21], functions traditionally implemented in analog circuits. The primary motivation in this case for such a digital architecture is compatibility with advanced digital complementary metal-oxide-semiconductor (CMOS) ICs. The limited voltage headroom of deep-submicron CMOS processes limits their suitability for RF circuits. The DRP cleverly exploits the superior time resolution of digital CMOS to mitigate this. However, although the DRP has been demonstrated as a highly reconfigurable platform, the reconfigurability is used primarily as a means to improve manufacturing yield and adaptability to environmental variation [20] rather than as a multi-mode/ multi-standard platform.

### 2.3 Switching-Mode Power Amplifiers

In future SDR systems one of the most challenging design problems will be the implementation of a highly reconfigurable PA which is both highly efficient and highly linear. The PA is the

<sup>&</sup>lt;sup>1</sup>DRP is a trademark of Texas Instruments Inc.

Figure 2.8: Polar transmitter using equally-weighted, digitally-controlled unit amplifiers [14].

Figure 2.9: Simplified illustration of the Digital RF Processor platform [17].

component which consumes the most power in any RF transmitter, a necessity in order to transmit enough power to overcome the path loss and ensure the signal is received with adequate SNR. In mobile applications the PA should transmit the power efficiently to maximize battery life and minimize the heating, also reducing the chance of reliability issues related to overheating. In base stations and infrastructure low efficiency causes power to be wasted as heat in the PA, with the side effect of additional cooling requirements which use even more electricity. For a cellular infrastructure operator the additional cost of this wasted electrical power, multiplied by hundreds or thousands of base stations, is extremely high.

The continually accelerating demand for high mobile data rates and resulting scarcity of RF spectral resource has led to a situation where maximizing the spectral efficiency in terms of bits per second per Hz (bps/Hz) is the defining characteristic of emerging wireless communications standards. Such signals exhibit a high PAPR, meaning a large portion of the information is encoded in the signal amplitude in order to keep the channel bandwidth narrow. The PA must amplify the signal linearly in order to preserve this information, a requirement which is in opposition to the efficiency.

In a highly linear class A PA, the transistor acts as a voltage-controlled current source with a constant transconductance. In order to maintain highly linear operation, the transistor must be biased with a relatively high quiescent current and conducts current over the entire input cycle (i.e., its conduction angle is  $2\pi$ ). This class of PA can reach a maximum theoretical drain (or collector) efficiency  $\eta_D$  of only 50%. The drain efficiency is defined as the ratio of the output RF power to the DC power supplied:

$$\eta_D = \frac{P_{RF}}{P_{DC}}.$$

(2.9)

The maximum  $\eta_D$  occurs for maximum  $P_{RF}$ . Since the primary motivator for using a linear PA is the high PAPR of the signal, the *average*  $\eta_D$  is much lower. Nonidealities such as finite transistor small-signal output resistance  $r_o$ , output impedance matching network insertion loss and other factors further degrade the efficiency. The class A PA is therefore rarely used except in applications where linearity is the sole objective, such as in instrumentation and measurement.

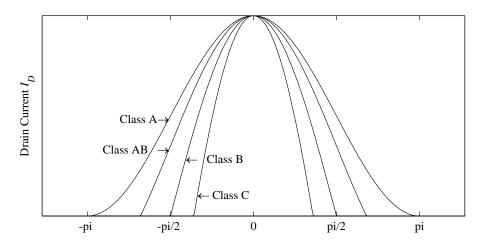

Class AB, B and C have a reduced conduction angle as shown in Figure 2.10 [22]. The conduction angle defines for what portion of the input signal cycle the transistor is conducting current. Reduced conduction angle results in less overlap of the drain current and voltage waveforms, which represents power dissipated as heat inside the transistor. For class B, the conduction angle is  $\pi$ . Class AB signifies any conduction angle between  $\pi$  and  $2\pi$ , and class C signifies a conduction angle of less than  $\pi$ . These PAs have reduced linearity compared to class A, but often a small tradeoff in linearity is acceptable for a relatively large gain in efficiency. This accounts for the relative popularity of class AB PAs in commercial applications.

These classes of PA all treat the transistor as a linear current source when the input is above the threshold voltage. An alternative is to treat the transistor as a switch capable of two states: on and off. This behaviour can be approximated by driving the transistor input with a large

Figure 2.10: Illustration of conduction angle [22].

amplitude input signal or (more appropriately given the two possible switch states) a binarylevel input. Such PAs are called switching-mode PAs (SMPAs), and can theoretically deliver 100% efficiency. Knowing the behaviour of an ideal switch, the reason for 100% efficiency is intuitive: when the switch is open, no current flows so no power is dissipated; and when the switch is closed, there is no voltage across the device so again no power is dissipated. In reality, 100% efficiency is not possible because the switch is not ideal. Two such nonidealities are the nonzero on resistance  $r_{on}$  and the finite leakage current in the off state. Despite this, very high efficiency (> 60%) is regularly reported for continuous-wave input; for example, [23–26].

The principal limitation of SMPAs is their nonlinearity. Since the switch only has two states, there is no way to reduce or "back off" the input power without coming out of switching operation. Indeed, some high-efficiency PA designs in the literature which have been demonstrated under non-unity PAPR use SMPA techniques and principles for the PA design, and linearize the PA using other techniques; for example, the SMPA can be used in a polar transmitter architecture [13, 27]. Another approach is to amplify a digitized (e.g., bandpass  $\Delta\Sigma$  modulated) version of the RF signal [28, 29] or employ the outphasing technique, also called linear amplification with nonlinear components (LINC) [30].

The switching behaviour of the transistor in an SMPA is a feature shared with digital circuits, making them a natural candidate for SDR/CR transmitters. Voltage- and current-mode class D, class F and inverse class F have all been demonstrated to provide very high efficiency operation. Class E is another popular SMPA configuration but will not be considered further in this thesis due to its limited frequency of operation and efficiency degradation under varying duty cycle [31].

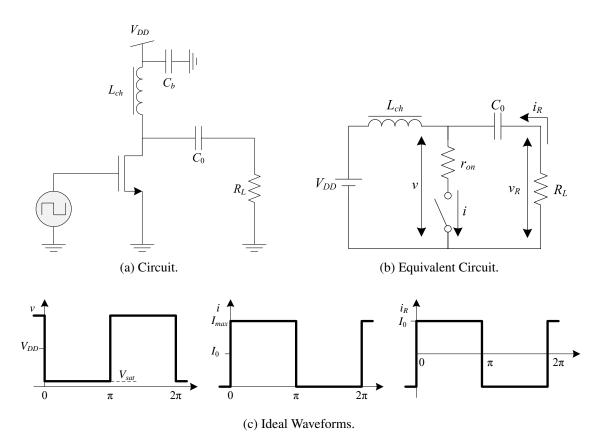

Figure 2.11(a) shows a basic, single-ended SMPA with resistive loading, taken from [32].  $R_L$  represents the resistive load,  $C_0$  the output DC blocking capacitor, and  $L_{ch}$  the RF choke

Figure 2.11: Single-ended SMPA with resistive load [32].

inductor. The transistor is driven as a switch by a square wave input centered about  $V_{GG}$ , the DC gate bias voltage which in the case of an SMPA is usually set to the threshold voltage. This causes the drain voltage  $v_{DS}$  to switch between the supply voltage  $V_{DD}$  and ground (or  $V_{SS}$ ), and the current to switch between the peak  $I_{max}$  and 0 (Figure 2.11(c)). In the equivalent circuit of Figure 2.11(b), the transistor is represented by a small  $r_{on}$  in series with an ideal switch. Since the output voltage and current are not sinusoidal, harmonic power components are present in the spectrum of the signal delivered to the load. The power at the fundamental frequency is

$$P_{RF} = \frac{1}{2}i^2 R_L = \frac{8}{\pi^2} \frac{R_L}{(R_L + r_{on})^2} \frac{V_{DD}^2}{\left(1 + \frac{r_{on}}{R_L + r_{on}}\right)^2}.$$

(2.10)

which is *not* equal to the total DC power supplied to the circuit  $V_{DD}I_0$ . This is because additional power is delivered to the load at the harmonics.

### 2.3.1 Class D Power Amplifiers

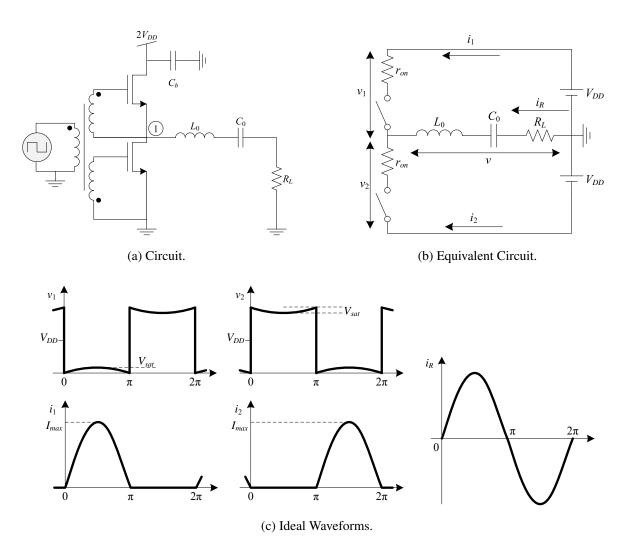

Placing the previous SMPA in push-pull configuration and adding a fundamental-frequency series resonator at the output, the voltage-mode class D (VMCD) PA is formed as shown in Figure 2.12(a) and its equivalent circuit is shown in Figure 2.12(b) [32]. This structure is sometimes referred to as voltage-switching class D since the complementary switching of the top and bottom transistors have the effect of switching the voltage of the output node (1) between  $V_{DD}$  and ground. The supply voltage is doubled due to the two transistors being in series. The series resonator passes only the power at the fundamental frequency, reflecting the rest and resulting in the waveforms being shaped as seen in Figure 2.12(c). The voltage is a square wave and the current is a half rectified sinusoid.

Assuming no losses except in the switch resistance  $r_{on}$  it can be shown [32] that the DC power supplied to the circuit is

$$P_{DC} = V_{DD}I_0 = \frac{2}{\pi^2} \frac{V_{DD}^2}{R_L} \frac{1}{1 + \frac{r_{on}}{R_L}}$$

(2.11)

and the fundamental-frequency power is

$$P_{RF} = \frac{2}{\pi^2} \frac{V_{DD}^2}{R_L} \frac{1}{\left(1 + \frac{r_{on}}{R_L}\right)^2}.$$

(2.12)

The drain efficiency is then

$$\eta_D = \frac{P_{RF}}{P_{DC}} = \frac{1}{1 + \frac{r_{on}}{RL}}.$$

(2.13)

Clearly the VMCD can provide 100% efficiency assuming  $r_{on} = 0$  and no other losses in the circuit. This high efficiency has made it a popular choice in audio applications.

In practice, not only are there finite losses throughout the circuit but the VMCD has a fundamental limitation that is a significant problem at high frequencies. Figure 2.13 shows a VMCD amplifier including the parasitic drain-source capacitances  $C_{DS}$  of the transistors. When the top transistor is on, current flows to node ① charging the  $C_{DS}$  of the bottom transistor and causing the voltage waveform to lose its ideal square shape [31]. The energy stored on this charge cycle is

$$E = \frac{1}{2} C_{DS} V_{DD}^2.$$

(2.14)

On the second half-cycle the bottom transistor is on and the  $C_{DS}$  is discharged. This happens on every switching cycle corresponding to a lost power of

$$P_{lost} = \frac{1}{2} C_{DS} V_{DD}^2 f_c.$$

(2.15)

Figure 2.12: Voltage-mode class D PA [32].

Figure 2.13: VMCD PA with parasitic capacitance [33].

Beginning at hundreds of megahertz this mechanism starts to dominate the losses of the VMCD and for this reason the VMCD is not a popular choice for RF applications [31].

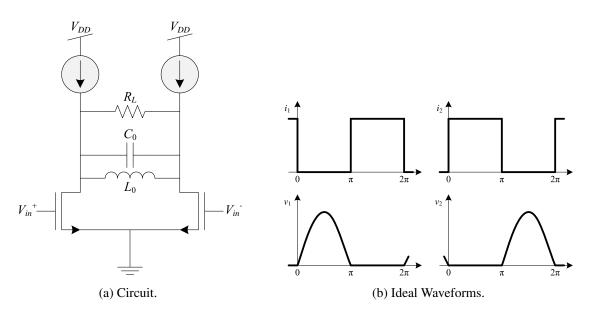

A more appropriate structure for RF applications is the current-mode class D (CMCD), sometimes called current-switching class D or inverse class D. The basic structure of the CMCD is shown in Figure 2.14(a) and the waveforms at each transistor drain are shown in Figure 2.14(b) [32]. As suggested by the name, the current (rather than the voltage) is switched between  $I_{max}$  and 0. The voltage and current waveforms are interchanged with respect to the VMCD configuration. Again assuming no losses other than  $r_{on}$ , the fundamental frequency output power is

$$P_{RF} = \frac{\pi^2}{2} \frac{V_{DD}^2}{R_L} \frac{1}{\left(1 + \frac{\pi^2}{2} \frac{r_{on}}{R_L}\right)^2}$$

(2.16)

and the DC power is

$$P_{DC} = \frac{\pi^2}{2} \frac{V_{DD}^2}{R_L} \frac{1}{1 + \frac{\pi^2}{2} \frac{r_{on}}{R_L}}.$$

(2.17)

The drain efficiency is thus

$$\eta_D = \frac{1}{1 + \frac{\pi^2}{2} \frac{r_{on}}{R_L}}.$$

(2.18)

Note also that the parasitic  $C_{DS}$  of each transistor can now be absorbed into the output resonant network, eliminating its effect on the performance.

Several successful RF implementations of CMCD PAs have appeared in the literature [34–40]. In one particular example demonstrated by Long [36] a rat-race hybrid is used to transform a single-ended input into a differential input to each active device, and a second rat-race hybrid performs the differential to single-ended conversion at the output. Laterally-diffused metal-oxide-semiconductor (LDMOS) transistors were used as the switching devices. This PA output 13 W with a drain efficiency of 60% and gain of 14 dB.

A new approach at RF is to replace the resonant lumped-element output network with a transmission line network which provides the necessary impedances at a finite number of harmonics, resulting in a good approximation of CMCD behaviour and high efficiency. For example, Aflaki et al. demonstrated a CMCD at 2.35 GHz providing 65% power-added efficiency (PAE) while delivering 39.2 dBm [40]. The PAE is defined as

$$\eta_{PAE} = \frac{P_{RF} - P_{in}}{P_{DC}} \tag{2.19}$$

where  $P_{in}$  is the RF input power.

Figure 2.14: Current-mode class D PA [32].

This multiharmonic matching strategy is similar to having two inverse class F PAs operating in push-pull. Whether this structure truly constitutes a CMCD amplifier is not agreed upon in the literature. Long proposes that a CMCD "uses a pair of switches operating in parallel, out of phase across a resonant tank circuit" [36]. The main points of contention are whether the harmonic matching networks of inverse class F are equivalent to the resonant tank of CMCD, and whether a high-power continuous-wave stimulus is an adequate approximation for switching operation. The latter point has implications on the design of the input matching network, which will be explored further in the next chapter.

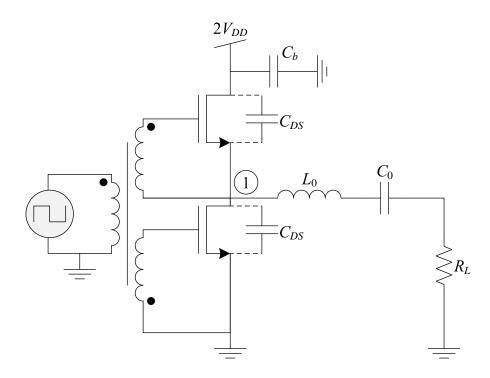

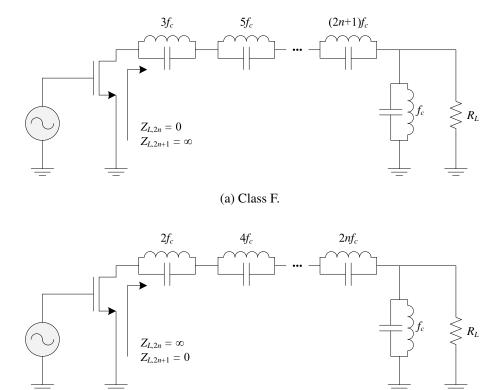

### 2.3.2 Class F and Inverse Class F PAs

Closely related to the VMCD and CMCD amplifiers are the class F and inverse class F (class  $F^{-1}$ ). The class F shares ideal drain waveform behaviour with the VMCD, as the class  $F^{-1}$  does with the CMCD. The class F PA structure is shown in Figure 2.15(a). It consists of a single transistor driven by a high-power input and a multiharmonic output impedance matching network. The high-power input drives the transistor into the nonlinear region, generating harmonic content at the output. The matching network transforms the load impedance into the required harmonic impedances to shape the voltage and current waveforms at the transistor drain into the same non-overlapping shapes as the VMCD (Figure 2.12(c)). Fourier analysis [32] shows the required

(b) Inverse Class F.

Figure 2.15: Ideal class F/F<sup>-1</sup> power amplifier.

harmonic output impedances are

$Z_{L,2n} = 0$  (short circuit) for even harmonics, and  $Z_{L,2n+1} = \infty$  (open circuit) for odd harmonics.

Usually in the design of class F (and  $F^{-1}$ ) PAs, no assumption is made about the shape of the input signal being a switching signal. It must simply be large enough to generate harmonic content at the transistor output.

The dual of the class F PA is the class  $F^{-1}$  (Figure 2.15(b)). The current and voltage waveforms are interchanged from the class F case. Similarly, the required harmonic terminations are interchanged:

$Z_{L,2n} = \infty$  (open circuit) for even harmonics, and  $Z_{L,2n+1} = 0$  (short circuit) for odd harmonics.

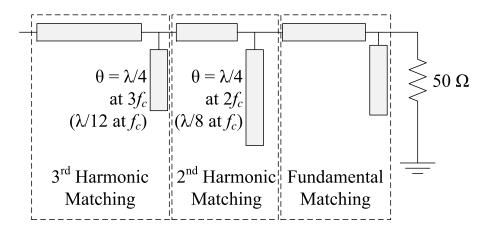

Figure 2.16: Three-harmonic output matching network structure for class F<sup>-1</sup> [23].

Woo et al. showed that a class  $F^{-1}$  amplifier can achieve higher efficiency than a class F for a given  $P_{RF}$ , a difference that increases with  $r_{on}$  [41]. The class  $F^{-1}$  PA has thus become a popular choice when high efficiency is the primary design goal.

It is theoretically possible to achieve ideal class F or  $F^{-1}$  operation, including termination of an infinite number of harmonics, using a quarter-wave transformer [32]. This results in an inherently narrowband PA. A more practical approach is to terminate the first few harmonics, resulting in approximated waveforms at the device drain. More harmonics properly terminated results in better approximation of the ideal waveforms; however, the additional matching network complexity causes additional insertion loss and degrades the efficiency.

In practice, high efficiency can be achieved in class  $F^{-1}$  operation by terminating as few as three harmonics. For example, in [23] Helaoui and Ghannouchi demonstrated a 1 GHz class  $F^{-1}$  PA with three harmonic terminations at the output. The technique used for the matching network is illustrated in Figure 2.16. The harmonic matching conditions are achieved with quarter-wavelength stubs at the second and third harmonics, placed the proper distance away from the transistor to provide the correct open or short condition. The authors demonstrated a PAE of over 80% at 1.01 GHz. This matching technique was also used in [42] to achieve 71% PAE. This matching strategy is described more in-depth in Chapter 3, as applied to a class  $F^{-1}$  PA in push-pull.

Because of their identical drain waveforms the VMCD amplifier is sometimes considered as the push-pull configuration of the class F. Similarly, the CMCD shares drain waveforms with the class F<sup>-1</sup>. However, as can be observed by comparing the ideal PA topologies in Figures 2.12, 2.14 and 2.15, the mechanism which creates these waveforms is subtly different. In the case of the class D PAs, the switching (square wave) behaviour of the waveforms is due to the switching of the transistor. But in the case of the class F/F<sup>-1</sup> PAs, the waveforms are explicitly shaped by the chosen harmonic terminations formed by the output matching network.

These considerations combined with the energy dissipation problem of VMCD described by Equation 2.15 make the CMCD the most appropriate choice for direct amplification of binary-level signals. The design, implementation and testing of a class F<sup>-1</sup> PA in push-pull, a topology very similar to the CMCD, is presented in Chapter 3.

### 2.4 Time Domain Modulation Techniques

Adding full reconfigurability to the already challenging RF PA requirements (i.e., linearity and efficiency) is a challenging proposition. In addition, the most advanced IC fabrication processes and technologies are optimized for high-speed digital applications. Deep submicron CMOS processes have limited power handling and low supply voltage, both of which are enormous advantages for digital circuits. However, these same features are also the major barriers that have prevented RF applications from reaping the benefits of process scaling which digital circuits have enjoyed for years. Interest in SDR and reconfigurable radio is nevertheless growing so there needs to be a means to reconcile the conflicting requirements of RF and digital circuits.

SMPAs are likely to be an important part of the solution. The active device in an SMPA is treated as a switch, providing a degree of inherent compatibility with digital circuits. Also, most classes of SMPA can theoretically provide 100% efficiency. The main limitation of SMPAs is their linearity. They are designed to amplify a constant-envelope input signal, but modern wireless communications standards provide high spectral efficiency by encoding information in the signal amplitude. Therefore, the amplitude information must be provided to the PA in a different way.

There are several ways of accomplishing this which may collectively be summarized as encoding the information into the timing of the level transitions of the switching signal. The time resolution of deep submicron CMOS is vastly superior to the voltage resolution, so the high-tolow and low-to-high transitions in a binary-level digital signal can provide the necessary dynamic range for high PAPR modulated signals. Given the functioning of SMPAs previously discussed, the concept of using a constant-envelope signal to encode varying amplitude (and phase) information is very useful. This enables the PA to become a "more digital" part of the transmitter system.

In order to simplify the RF amplification process, one important requirement is that no special decoding schemes are required to recover the RF signal from the digital signal; a bandpass or lowpass reconstruction filter must suffice.

This section outlines the theory behind two particular time-domain modulation techniques: pulse width modulation, and  $\Delta\Sigma$  modulation. Several examples of successful PA implementations incorporating each technique are also presented.

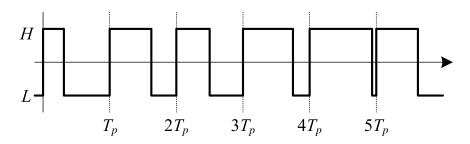

Figure 2.17: Pulse width modulation.

### 2.4.1 Pulse Width Modulation

One of the simplest forms of constant envelope modulation is pulse width modulation (PWM). In this scheme the modulated signal takes the form of a digital pulse train with each pulse varying in width according to the sampled input amplitude:

$$p_n(t) = \begin{cases} H, & nT_p < t \le \left(n + \frac{A_p + a_n}{2A_p}\right) T_p \\ L, & \text{otherwise} \end{cases}$$

(2.20)

where

$$L = \text{ digital "0"},$$

$H = \text{ digital "1"},$

$T_p = \text{ the pulse period},$

$a_n = \text{ the input signal sequence, and}$

$A_p = \text{ a signal limit such that } -A_p \le a_n \le A_p.$

This is illustrated in Figure 2.17. Summing the entire pulse sequence gives the overall signal:

$$p(t) = \sum_{n} p_n(t).$$

(2.21)

One of the main benefits of PWM is its simple method of generation. The slowly varying input signal may simply be compared to a triangular or sawtooth wave. Depending on the shape of the triangular wave, three types of PWM can be generated:

- The rising edge of each pulse is synchronous and the position of the falling edge is modulated (as in Figure 2.17).

- The falling edge of each pulse is synchronous and the position of the rising edge is modulated.

• The pulse centres are synchronous and both edge positions are modulated around the pulse centre.

A PWM signal is essentially a clock with varying duty cycle. By placing the pulse frequency at the carrier frequency, a varying duty cycle corresponds to a varying envelope for the RF signal, plus varying degrees of harmonic content which can be filtered. Fourier expansion of the PWM signal [43] shows the RF envelope and pulse width are related by

$$A_n = \frac{2(H-L)}{\pi} \sin\left(\pi \frac{T_{p,n}}{T_p}\right)$$

(2.22)

where  $A_n$  is the RF amplitude and  $T_{p,n}$  is the pulse duration. Thus the maximum fundamental (RF) envelope occurs when the duty cycle  $T_{p,n}/T_p = 50\%$ . Duty cycles greater than 50% generate the same RF envelope as duty cycles less than 50% by the same amount; that is, a 60% duty cycle has the same fundamental frequency component as a 40% duty cycle.

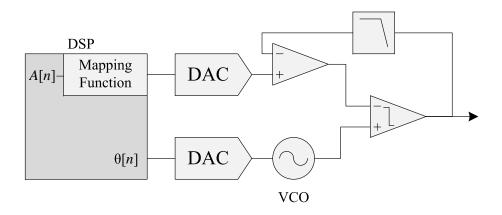

Several papers have described successfully implemented RF PWM systems for PA applications. For example, Nielsen and Larsen presented an RF PWM for a 100 MHz carrier frequency [43] summarized in Figure 2.18. The mapping described by Equation 2.22 is performed in DSP and the comparison in this case is done between the post-mapped amplitude signal  $A_M(t)$ and a phase modulated sinusoid, thereby encoding phase information into the timing of each pulse. To compensate for performance variations due to drift and other causes, which are sources of nonlinearity in the system, feedback is introduced in the envelope path. This is a lowpass rather than bandpass feedback to avoid reducing the system bandwidth. The linearity was an acceptable 17 dB below the emission mask for a Universal Mobile Telecommunications System (UMTS) signal, and the error vector magnitude (EVM) was below 1%. The meaning of EVM is explained in Section 2.4.2.

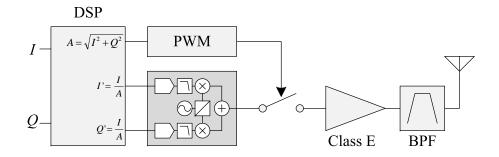

More recently, Yang et al. presented the gate-bias-modulated PWM-based polar transmitter system [44] shown in Figure 2.19. The baseband signal is represented in polar form with the normalized I and Q components generating the phase-modulated RF portion. The envelope component is modulated with PWM and used to pulse the input to two class E PAs. Adequate linearity was achieved without any predistortion and the transmitter showed over 49% peak drain efficiency and PAE over 40% under code division multiple access (CDMA) Interim Standard 95 (IS-95) modulated input.

Also recently, Chung et al. applied the concepts of LINC and PWM to two class E PAs [45], as shown in Figure 2.20. The LINC or outphasing technique attempts to enhance the transmitter efficiency by using two PAs to amplify two constant envelope signals which when recombined produce the desired amplitude and phase through vector addition. Traditionally this technique suffers from poor efficiency at large power backoff (i.e., large outphasing angle), which can be mitigated by using *asymmetric multilevel* outphasing (AMO) [46], where the power level for each branch is chosen from a discrete set of values and the bias level of the PA switched accordingly

Figure 2.18: PWM system presented by Nielsen and Larsen [43].

Figure 2.19: PWM-based polar transmitter presented by Yang et al. [44].

Figure 2.20: AMO transmitter with discrete PWM [45].

Figure 2.21: Multilevel  $\Delta\Sigma$  modulator driving a LUT-based PWM and VMCD amplifier [47].

among the appropriate voltages. In [45], rather than switching the bias levels among discrete values, the power of each branch is adjusted using discrete PWM. This was shown to further enhance the efficiency compared to the original AMO tranmsitter and deliver more than twice the overall system efficiency of standard LINC (36.5% versus 17.1%). The presented results were at a centre frequency of 48 MHz.

As a final example of PWM in the context of SMPA, Podsiadlik et al. proposed using the output of a multilevel, bandpass  $\Delta\Sigma$  modulator as an input to a lookup table- (LUT) based PWM [47]. The authors used a fourth-order  $\Delta\Sigma$  modulator with 11 quantization levels and a 20 bit LUT to generate a two-level RF PWM signal at 741.4 MHz (a function of the chosen field programmable gate array [FPGA] testbed), which then drove a VMCD PA (Figure 2.21). They achieved a 10 dB improvement in dynamic range and 20 dB lower out-of-band noise floor compared to an equivalent upconverted 2-level  $\Delta\Sigma$  modulator alone, in turn lowering the bandpass reconstruction filter requirements at the output. Additionally, the FPGA platform chosen for implementation is inherently reconfigurable.

Figure 2.22: First-order  $\Delta\Sigma$  modulator.

### 2.4.2 Delta-Sigma Modulation

When a sampled signal is quantized, the error between the quantized signal and the original signal is termed *quantization noise*. For a sufficient number and proper placement of the quantization levels according to the statistics of the input signal, the quantization noise present inside the signal band can be reduced to an acceptable level depending on the application. By using feedback in an attempt to cancel the quantization error, and oversampling the signal to a sufficient degree, the quantization noise power can be shaped away from the signal band of interest. This is the essence of  $\Delta\Sigma$  modulation.

This behaviour can be explained by way of example. Figure 2.22 shows the topology of a first-order  $\Delta\Sigma$  modulator. The input discrete-time signal is assumed to be low-pass and band-limited according to the oversampling ratio (OSR)

$$OSR = \frac{f_s}{2f_b}$$

(2.23)

where

$f_s$  = the sampling frequency in Hz, and  $f_b$  = the baseband bandwidth of the desired signal in Hz.

The quantized output value  $y_i$  is subtracted from the input value  $x_i$  and the result is accumulated. On the following clock, the value of the integrator is quantized and sent to the output.

The quantizer can be modeled as an addition of an error signal  $\varepsilon_i$ . This is reflected in Figure 2.23 [48]. The accumulator value  $w_i$  is equal to

$$w_i = w_{i-1} + x_{i-1} - y_{i-1} \tag{2.24}$$

$$=x_{i-1}-\varepsilon_{i-1}.$$

Figure 2.23: First-order  $\Delta\Sigma$  modulator with the quantizer modeled as an addition of error.

This gives at the output

$$y_i = w_i + \varepsilon_i \tag{2.26}$$

$$=x_{i-1}+\varepsilon_i-\varepsilon_{i-1}.$$

(2.27)

The input signal experiences a delay to the output  $(x_{i-1})$ , with an added quantization noise component

$$n_i = \varepsilon_i - \varepsilon_{i-1} \tag{2.28}$$

which has a magnitude spectrum

$$N(f) = E(f)|1 - e^{-j2\pi fT_s}|$$

(2.29)

$$= 2\varepsilon_{rms}\sqrt{2T_s}\sin(\pi fT_s) \tag{2.30}$$

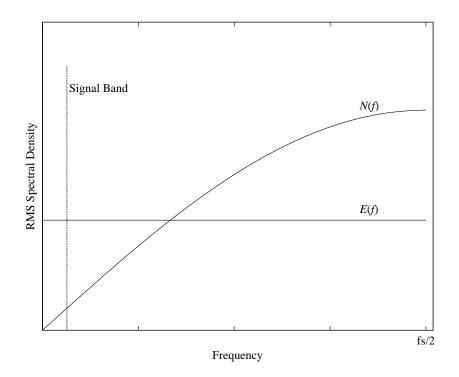

where  $T_s$  is the sampling period. This equation assumes an input signal which is sufficiently busy to apply the *white noise approximation* to  $\varepsilon_i$ . In this case the term  $1 - e^{-j2\pi fT}$  is known as the *noise transfer function* (NTF) of the modulator. Whereas for the quantizer alone  $\varepsilon_i$  has a flat spectrum, the modulator overall has reduced quantization noise around the low frequencies where the desired signal resides as illustrated in Figure 2.24.

In general a  $\Delta\Sigma$  modulator's behaviour in the *z* domain can be described by the following equation:

$$Y(z) = \operatorname{STF}(z)X(z) + \operatorname{NTF}(z)E(z)$$

(2.31)

where X, Y, and E represent the input, output and quantization error, respectively. STF(z) is the *signal transfer function*, which in the first-order modulator example described by Equation 2.27 is equal to  $STF(z) = z^{-1}$ . That is, the full signal is passed from input to output with only a delay; however, it may be obscured by the quantization noise if it is not sufficiently band-limited.

By adding integrators, resonators, feedback and feedforward components, higher-order modulators can be realized. These give more degrees of freedom with which to adjust the NTF and

Figure 2.24: Noise spectrum shaping of first-order  $\Delta\Sigma$  modulator [48].

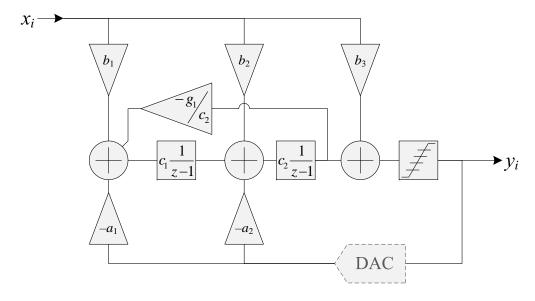

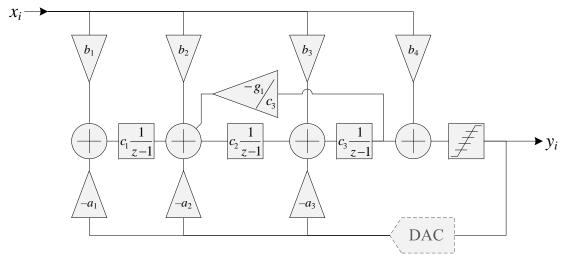

STF of the system. Several topologies have been collected by Schreier and used to implement a MATLAB toolbox which can be used to easily design  $\Delta\Sigma$  modulators [49]. One such form is the cascade of integrators with feedback (CIFB), pictured in Figure 2.25.

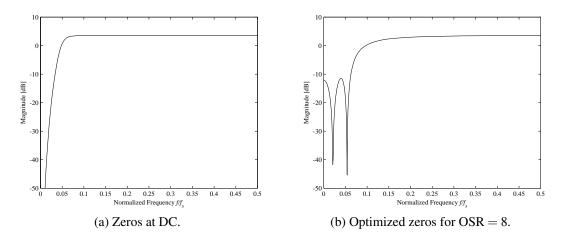

The coefficients  $a_i$ ,  $b_i$ ,  $c_i$  and  $g_i$  can be adjusted to create the desired noise shaping behaviour. (The design of these coefficients is beyond the scope of this thesis.) The most important of these with respect to the noise shaping behaviour are the feedback terms  $a_i$  and  $g_i$ . They can especially be used to optimize the location of the zeros within the stopband of the NTF (i.e., the desired signal band) in order to minimize the in-band quantization noise and distortion, rather than placing all NTF zeros at DC or the centre of the signal band. Figure 2.26 illustrates this behaviour.

For  $\Delta\Sigma$  modulation of baseband signals, the NTF should be a highpass function. The NTF can also be designed as a bandstop function for a signal centered at a frequency other than DC, creating a bandpass  $\Delta\Sigma$  modulator. The previously mentioned standard topologies are all capable of implementing such an NTF (and corresponding bandpass STF), given the correct feedback and feedforward coefficients.

(a) Even order.

(b) Odd order.

Figure 2.25: CIFB form of  $\Delta\Sigma$  modulator [49].

Figure 2.26: Adjustment of zero locations in NTF to minimize in-band noise.

Figure 2.27: Class S amplifier system.

### **Class S Amplifier Systems**

In a class S amplification system a  $\Delta\Sigma$  modulator is used as a driver for a switching amplifier. This technique is quite popular for audio frequencies using a lowpass  $\Delta\Sigma$  modulator. In the past decade, the increasing frequency capabilities of semiconductor processes and signal processing have led to increased interest in bandpass class S systems for RF application (Figure 2.27); for example, [28, 29, 50–52]. In one of the latest of these published results [29], Wentzel et al. used a 1.68 Gbps bandpass  $\Delta\Sigma$  modulator to drive a gallium nitride (GaN) monolithic microwave IC (MMIC) containing a CMCD PA. The bit rate represented 4× oversampling of a 420 MHz RF carrier tone. The authors used the modulator to achieve peak drain efficiency of 41% for the PA.

An RF class S system must also reconstruct the RF signal before transmission. Otherwise, the out of band quantization noise and sampling images would be broadcast, interfering with other channels and violating government regulations. A bandpass filter (BPF) performs this reconstruction. However, due to the proximity of the quantization noise to the signal band as

well as the magnitude of the noise power compared to the signal (recall Figure 2.26) the design specifications of such a filter are very strict in terms of relative bandwidth, rolloff and stopband attenuation. That is, the filter needs to have a very high quality factor Q. This is one of the principal limitations of RF class S systems today.